センサ素子

【目的】 構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供する。

【解決手段】 所定間隔をおいて配置された導電性の上方基板及び導電性の下方基板と、上方基板および下方基板に挟まれた空間内で導電性の重錘体を変位可能に支持する導電性の中間基板と、重錘体の変位に応じた電気信号を導電性の中間基板を介して取り出す検出素子と、を有する。

【解決手段】 所定間隔をおいて配置された導電性の上方基板及び導電性の下方基板と、上方基板および下方基板に挟まれた空間内で導電性の重錘体を変位可能に支持する導電性の中間基板と、重錘体の変位に応じた電気信号を導電性の中間基板を介して取り出す検出素子と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、センサ素子、特に、加速度センサ及び角速度センサに関する。

【背景技術】

【0002】

近年、電気、機械、自動車等の種々の産業分野で加速度センサ(1軸〜3軸)や角速度センサ(ジャイロ)の需要が高まっている。例えば、電気産業分野においては、携帯電話、デジタルカメラ、携帯情報端末、パソコン(PC)、ゲーム機器等の機器や装置に用いられる。また、GPS(グローバル・ポジショニング・システム)等における補正や、異常振動検出によるセキュリティ用途等の幅広い分野への適用が可能なため、今後さらに需要が増大するものと考えられる。このような種々の分野への適用拡大に伴って、小型化、高性能化等、センサのスペックに対する要求が一層高まっている。

【0003】

このようなセンサとしては、従来、静電容量素子を利用した加速度センサ及び角速度センサが知られている(例えば、特許文献1参照)。しかしながら、かかる従来のセンサでは製法及び構造が複雑であり、上記した種々の適用分野において、増大及び高度化する要求を満たすことは困難である。

【0004】

例えば、従来技術の構成においては、上部電極及び下部電極に交流電圧を印加することによって、当該上部及び下部電極間に設けられた重錘体を上下に振動させ、その重錘体に働くコリオリ力を多軸の加速度センサで検知して2軸の角速度センサとして用いている。しかしながら、上部電極及び下部電極に交流電圧を印加する構成では、基板として配線パターン付のガラス基板等が用いられていた。電極の取り出し構造に種々の手法が用いられているが、電極の取り出しのための領域が大きく、また構造も複雑であり、センサを小型化することが困難であった。

【特許文献1】特開2004−144598号公報(第7頁、図7)

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題には、上記した問題が1例として挙げられる。本発明は、上述した問題点に鑑みてなされたものであり、その目的とするところは、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することにある。

【課題を解決するための手段】

【0006】

本発明によるセンサは、所定間隔をおいて配置された導電性の上方基板及び導電性の下方基板と、上方基板および下方基板に挟まれた空間内で導電性の重錘体を変位可能に支持する導電性の中間基板と、重錘体の変位に応じた電気信号を導電性の中間基板を介して取り出す検出素子と、を有することを特徴としている。

【0007】

また、本発明によるセンサは、所定間隔をおいて配置された導電性底面を有する上方基板及び導電性表面を有する下方基板と、上方基板および下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、上方基板の導電性底面と下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ重錘体に交流電圧を印加して重錘体を上下振動させる手段と、上下振動する重錘体の変位に基づいて重錘体に作用した角速度を検出する検出素子と、を有することを特徴としている。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施例について図面を参照しつつ詳細に説明する。なお、以下に示す実施例において、等価な構成要素には同一の参照符を付している。

【実施例1】

【0009】

図1及び図2は、本発明の実施例1であるセンサ10の構成を模式的に示す図である。センサ10は、ピエゾ抵抗素子を検出素子として用い、加速度センサ又は角速度センサとして動作する。

【0010】

より詳細には、図1は、センサ10の構造を模式的に説明する平面図であり、図2は、図1の線A−Aに関する断面構造を模式的に示す断面図である。センサ10は、シリコン等で形成された導電性の下方基板(底部基板:BS)16上に、SiO2により形成された第1絶縁層15、第1シリコン層12、SiO2により形成された第2絶縁層13、第2シリコン層14、SiO2により形成された第3絶縁層18、及びシリコン等で形成された導電性の上方基板(TS)19が順次設けられている。なお、第1シリコン層12、第2絶縁層13及び第2シリコン層14は後述する中間基板(IS)を構成している。さらに、下方基板16及び上方基板19間には、上記各層の一部が除去された空隙部29が形成されている。当該空隙部29内には、第2シリコン層14の一部を除去して十字形状に形成された橋梁部28が形成されている。また、第1シリコン層12の一部を除去することによって、橋梁部28の下方に重錘体25が形成されている。すなわち、第2シリコン層14の4つの橋梁部28が重錘体25を支持している。橋梁部28は可撓性を有し、重錘体25は駆動回路による駆動や外部からの力によって空隙部29内において、x、y及びz方向に変位可能である。また、橋梁部28の各々には1対のピエゾ抵抗素子21A,21Bが形成されている。ピエゾ抵抗素子21A,21Bの抵抗値は、橋梁部28に生ずる応力の大きさに応じて変化する。以下に、センサ10の製造方法、詳細構造及び加速度・角速度検出について図を参照して説明する。

<センサの製造方法>

図3〜4を参照してセンサ10の製造工程(STEP-1〜STEP-5)について説明する。なお、以下の製造工程は、通常の拡散技術、薄膜堆積技術、フォトリソグラフィ技術等のシリコン・プロセスによって行われる。

【0011】

まず、シリコン ・オン・インシュレータ(SOI)構造のウエハ11を用意する(STEP-1)。このSOIウエハ11は、N型の半導体基板12上に絶縁体13及びN型シリコン層14が形成された1層SOIウエハである。例えば、基板12は、CZ法により形成された、面方位(100)のN型シリコン(Si)で、約625μmの厚さを有する。絶縁体13は、厚さが約500nmのSiO2層が設けられている。絶縁体13上には、N型(100)面のシリコン層14が約5μmの厚さで形成されている。なお、ウエハ11は、センサ構造体の中間基板(IS)を構成している。

【0012】

次に、ウエハ11の底面(裏面)側には絶縁膜15が形成される。また、シリコン層14上には、P型ドーパントの拡散によってピエゾ抵抗素子21A,21Bが形成される。その後、シリコン層14上に酸化膜等の絶縁膜18Aを形成し、絶縁膜18Aにコンタクトホールを開けてピエゾ抵抗素子21A,21Bに接続された電極22,23,24を形成する。電極23は、ピエゾ抵抗素子21A,21Bのそれぞれの近端を接続する電極線として形成され、電極22,24は、電極23が接続されていないピエゾ抵抗素子21A,21Bのもう一方の端部(遠端)に接続されている。電極22,23,24の形成後、電極22,23,24を被覆する酸化膜等の絶縁膜18Bを形成する(STEP-2)。また、図には、電極22に接続されるパッド電極22Aが形成されている場合を示している。なお、電極22,23,24は配線電極(図示しない)によって後述する端子に接続されている。

【0013】

次に、ウェハ裏面の加工として通常のフォトエッチ工程で重錘体25及び橋梁部28を含む領域について、絶縁膜15と所定の厚さのシリコン層12をエッチングする(図示しない)。さらに、絶縁膜18B上に保護用のフォトレジストPRを形成する。また、絶縁膜15上にもフォトレジストPRを形成する。フォトリソグラフィによって底面側のフォトレジストPRをパターニングし、シリコン基板12をエッチングで除去することによって重錘体25を形成する(STEP-3)。なお、フォトレジストPRのパターニング、及び絶縁膜15及びシリコン基板12のエッチング除去は、ピエゾ抵抗素子21A,21Bが橋梁部28の両端部に位置するように行われる。

【0014】

さらに、絶縁体13をエッチングで除去し、フォトレジストPRを剥離する(STEP-4)。その後、接着剤等によって裏面の絶縁膜15の下にシリコン等の導電性の下方基板(BS)16を貼り付ける。また、空隙部29に対応する大きさの溝29Aを形成したシリコン等の導電性の上方基板(BS)19を溝29A側を下方、すなわち絶縁膜18B側にして接着剤等によって絶縁膜18B上に貼り付ける(STEP-5)。なお、シリコン基板19の両端部は除去される。シリコン基板19の貼り付けによって溝29Aは、橋梁部28及び重錘体25が上方(+z方向)に変位できるための空隙部を形成する。なお、以下においては、上記した空隙部29に当該空隙部29Aを合わせた領域を空隙部29とも称する。上記製造工程(STEP-1〜STEP-5)により、図5に示すように、センサ10が形成される。なお、絶縁膜18A及び18Bが図1に示す絶縁膜18に対応する。

<角速度の検出>

図6は、上記したセンサ10におけるピエゾ抵抗素子の配線の一例を模式的に示す平面図である。以下においては、図中x方向の橋梁部28に配されたピエゾ抵抗素子(及びその抵抗値)を、x方向に順にR1,R2,R3,R4とし、y方向の橋梁部28に配されたピエゾ抵抗素子(及びその抵抗値)を、y方向に順にR5,R6,R7,R8として説明する。ピエゾ抵抗素子R1〜R8を接続する配線は、端子T1〜T8に接続されている。

【0015】

図7は、図6に示す配線によって形成される検出回路を模式的に示している。図に示すように、ピエゾ抵抗素子R1〜R4、及びピエゾ抵抗素子R5〜R8によってそれぞれホイートストン・ブリッジWB1,WB2が構成されている。ホイートストン・ブリッジWB1において、端子T1及びT3間に電圧Vaを印加し、端子T2及びT4間の電位差ΔVxを検出する。同様に、ホイートストン・ブリッジWB2において、端子T5及びT7間に電圧Vaを印加し、端子T6及びT8間の電位差ΔVyを検出する。

【0016】

次に、角速度を検出する場合に、重錘体25を運動させるための構成及び方法について以下に説明する。図8は、上方基板(TS)19、下方基板(底部基板:BS)16、及び中間基板(IS)のN型シリコン層14へ電圧/電流印加を表す等価回路を示している。より詳細には、図9に示すように、上方基板(電極E5とする)19に直流電位+Vd、例えば+50Vを印加し(図中、一点鎖線で示す)、下方基板(電極E6とする)16には直流電位−Vd、例えば−50Vを印加する(図中、二点鎖線で示す)。N型シリコン層14(電極E0とする)には、正弦波状の交流電位(振幅±Va)を印加する(図中、実線で示す)。かかる交流電位の印加に応じてN型シリコン層14の電荷が変化するため(図9中段)、N型シリコン層14はクーロン力によってz軸方向に振動する(図9下段)。ここで、正弦波交流の周波数は、センサ構造体固有のバネ定数と、重錘体25及び橋梁部28を含む振動部の質量とから定まる共振周波数とするのがエネルギーロスが最小で好ましい。しかしながら、必ずしも当該共振周波数でなくともよい。また、印加する交流電位は正弦波状に限らず、三角波状、方形波状であってもよい。また、電圧駆動の場合を説明したが、正弦波状等の交流電流によりN型シリコン層14に電荷を与えたり、引き抜いたりする電流駆動を行ってもよい。

【0017】

このように中間基板(IS)を正弦波状の交流電位(又は交流電流)により駆動することによって重錘体25はz軸方向に振動する。振動している重錘体25に外力(角速度)が作用すると重錘体25にはコリオリ力が作用する。従って、x軸方向に作用するコリオリ力を検出することによってy軸まわりの角速度を検出することができる。同様にして、y軸方向に作用するコリオリ力を検出することによってx軸まわりの角速度を検出することができる。

【0018】

かかるコリオリ力は、ピエゾ抵抗素子R1〜R8の応力による抵抗変化として検出することができる。すなわち、図7に示すホイートストン・ブリッジWB1,WB2の電位差ΔVx、ΔVyを検出することによって角速度検出を行うことができる。より具体的には、重錘体25がz軸方向に振動する場合、y軸まわりの回転による角速度は当該電圧変化ΔVxとして検出される。また、x軸まわりの回転による角速度は当該電圧変化ΔVyとして検出される。

【0019】

なお、中間基板(IS)のN型シリコン層14が重錘体25に電気的に接続するように構成してもよい。例えば、N型シリコン層14及び重錘体25間の絶縁体13にスルーホール等を開け、当該スルーホール等に導電体を埋め込むプロセスを追加してもよい。

【0020】

上記した構成において、重錘体25を振動させない場合には、電位差ΔVx、ΔVyは外力(加速度)に比例した値となり、センサ10は加速度センサとして機能する。

【0021】

以上、説明したように、本実施例によれば、一般的な半導体ウエハプロセスを利用して、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することができる。また、上方基板19と下方基板16に直流電位を与えるので、中間基板は電気的にシールドされた状態にあり、外部雑音に対して安定動作ができる。

【0022】

尚、上述の構成では、下方基板16及び上方基板19をシリコン基板で構成したが、これに限らず、下方基板16をその表面に電極層(導電性表面)を設けた絶縁基板(ガラス基板など)としてもよく、また、上方基板19をその底面に電極層(導電性底面)を設けた絶縁基板(ガラス基板など)としてもよく、更に、下方基板16及び上方基板19をガラス基板などの絶縁基板で構成し、下方基板16の表面及び上方基板19の底面にそれぞれ電極層を設け、導電性表面を有する下方基板16及び導電性底面を有する上方基板19としても良い。また、2軸の加速度センサとする場合、上方基板16と下方基板19に電位を付与する必要はないため、絶縁基板(ガラス基板など)で構成してもよく、また、上方基板19を設けなくても良い。

【実施例2】

【0023】

図10及び図11は、本発明の実施例2であるセンサ30の構成を模式的に示すブロック図である。センサ30は、キャパシタンス変化に基づいて加速度又は角速度を検出する加速度センサ又は角速度センサとして動作する。

<容量型センサの構造及び製造方法>

より詳細には、図10は、センサ30の構造を模式的に説明する平面図であり、図11は、図10の線A−Aに関する断面構造を模式的に示す断面図である。センサ30は、シリコン等で形成された導電性の下方基板(底部基板:BS)16上に、SiO2により形成された第1絶縁層15、第1シリコン層12、SiO2により形成された第2絶縁層13、第2シリコン層14、SiO2により形成された第3絶縁層18、及びシリコン等で形成された導電性の上方基板(TS)19が順次設けられている。また、空隙部29が形成され、当該空隙部29内に橋梁部28及び橋梁部28の下方に重錘体25が形成されている点は上記した実施例1と同様である。また、橋梁部28は可撓性を有し、重錘体25は駆動回路による駆動や外部からの力によって空隙部29内において、x、y及びz方向に変位可能である。

【0024】

以下に、センサ30の製造方法及び構造について説明する。上記した実施例1と同様な半導体プロセスを用いてセンサ30を製造することができる。すなわち、N型の半導体基板12上に絶縁体13及びN型シリコン層14が形成された1層SOIウエハを用いて製造することができる。センサ30においては、ピエゾ素子は形成されず、重錘体25を四方から囲む側方ブロック(以下、単にブロックともいう。)が設けられている。より具体的には、第1シリコン層12のうち、空隙部29の外側の部分にはアイソレーション用のトレンチ31が形成され、図10の平面投影図に示すように、重錘体25を四方から囲む位置に第1、第2、第3及び第4の側方ブロック33A,33B,33C,33Dが分離形成されている。

【0025】

図11に示すように、N型シリコン層14を貫通し、重錘体25に電気的に接続された導電体34Oが形成されている。導電体34Oは電極端子35Oに接続され、電極端子35Oを介して重錘体25を外部回路に接続できるようになっている。電気的に分離して形成された第1〜第4の側方ブロック33A〜33Dには、それぞれN型シリコン層14を貫通して形成された導電体34A〜34Dが電気的に接続されている。導電体34A〜34Dには電極端子35A〜35Dが接続され、電極端子35A〜35Dを介して第1〜第4の側方ブロック33A〜33Dを外部回路に接続できるようになっている。

【0026】

センサ30は、重錘体25の表面に形成される電極E0と、第1〜第4の側方ブロック33A〜33Dの上記電極E0に対向する面に形成される電極E1〜E4と、のそれぞれ間の容量(キャパシタンス)C1〜C4の変化に基づいて加速度又は角速度を検出するよう構成されている。なお、以下においては、電極E0と、電極E1〜E4と、によって形成されるキャパシタについてもC1〜C4の参照符を付して説明する。

<角速度の検出>

図12は、上記したセンサ30の加速度及び角速度を検出する場合の検出回路の一例を示すブロック図である。

【0027】

角速度を検出する場合には、上記実施例1と同様に、例えば、上方基板19に直流電位+Vdを、下方基板16に直流電位−Vdを印加し、N型シリコン層14には、正弦波状の交流電位(振幅±Va)を印加する(図中、実線で示す)。すなわち、交流電位の印加に応じて重錘体25がz軸方向に振動するようにした状態で後述する容量変化の検出を行う。なお、電圧駆動の場合を説明したが、電流駆動を行ってもよいのは同様である。

【0028】

図12に示すように、x方向に形成されるキャパシタであるキャパシタC1,C3の容量変化が検出される。すなわち、重錘体25の電極E0及び第1ブロックの電極E1によって形成されるキャパシタC1の容量変化は容量−電圧変換回路(CV変換回路)37Aによって電圧変化V1に変換される。さらに、重錘体25の電極E0及び第3ブロックの電極E3によって形成されるキャパシタC3の容量変化はCV変換回路37Cによって電圧変化V3に変換される。減算器38Aにおいて電圧変化V1,V3の差分ΔVxが得られる。電圧差ΔVxによってy軸まわりの回転による角速度が得られる。

【0029】

また、y方向に形成されるキャパシタであるキャパシタC2,C4の容量変化が検出される。すなわち、重錘体25の電極E0及び第2ブロックの電極E2によって形成されるキャパシタC2の容量変化はCV変換回路37Bによって電圧変化V2に変換される。さらに、重錘体25の電極E0及び第4ブロックの電極E4によって形成されるキャパシタC4の容量変化はCV変換回路37Dによって電圧変化V4に変換される。減算器38Cにおいて電圧変化V2,V4の差分ΔVyが得られる。電圧差ΔVyによってx軸まわりの回転による角速度が得られる。

【0030】

上記した構成において、重錘体25を振動させない場合には、電位差ΔVx、ΔVyは加速度に比例した値となり、センサ30は加速度センサとして機能することになる。

【0031】

以上、説明したように、本実施例によれば、一般的な半導体ウエハプロセスを利用して、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することができる。また、上方基板19と下方基板16に直流電位を与えるので、中間基板は電気的にシールドされた状態にあり、外部雑音に対して安定動作ができる。

【0032】

尚、上述の構成では、下方基板16及び上方基板19をシリコン基板で構成したが、これに限らず、下方基板16をその表面に電極層(導電性表面)を設けた絶縁基板(ガラス基板など)としてもよく、また、上方基板19をその底面に電極層(導電性底面)を設けた絶縁基板(ガラス基板など)としてもよく、更に、下方基板16及び上方基板19をガラス基板などの絶縁基板で構成し、下方基板16の表面及び上方基板19の底面にそれぞれ電極層を設け、導電性表面を有する下方基板16及び導電性底面を有する上方基板19としても良い。また、2軸の加速度センサとする場合、上方基板16と下方基板19に電位を付与する必要はないため、絶縁基板(ガラス基板など)で構成してもよく、また、上方基板19を設けなくても良い。

【実施例3】

【0033】

次に、本発明の実施例3について説明する。上記した実施例においては、N型の半導体基板12上に絶縁体13及びN型シリコン層14が形成された1層SOIウエハを用いてセンサを製造する場合について説明したが、多層SOIウエハを用いて製造することも可能である。

【0034】

図13は、2層SOIウエハ41の断面構造を示す断面図である。具体的には、N型の半導体基板16上に、第1絶縁層15、第1シリコン層12、SiO2により形成された第2絶縁層13、第2シリコン層14が順次積層された構造を有している。簡単に言えば、上記実施例においては、1層SOIウエハ基板に第1絶縁層15及び半導体基板16が後のプロセスによって形成されたが、本実施例においては、1層SOIウエハに半導体基板16及び第1絶縁層15を加えた2層SOIウエハが用いられる。

【0035】

例えば、半導体基板16は、CZ法により形成された、面方位(100)のN型シリコン(Si)で、約500μmの厚さを有する(10-20Ωcm)。第1絶縁層15は、厚さが約3μmのSiO2層である。後述するように、第1絶縁層15の厚さによって重錘体25と下方基板16との距離が規定される。第1シリコン層12は、約20μmの厚さを有するN型シリコンである(10-20Ωcm)。第2絶縁層13は、厚さが約300nmのSiO2層である。また、第2シリコン層14は、約2μmの厚さを有するN型シリコンである(10-20Ωcm)。

【0036】

かかる2層SOIウエハ41には、エッチングプロセスによって空隙部29及び重錘体25が形成される。例えば、図14に示すように、エッチング用の孔39を第2シリコン層14上に形成し、順次適切なエッチング液やエッチングガス等を当該エッチング孔39から導入することにより各層を選択エッチングすることができ、2層SOIウエハ41内に空隙部29、重錘体25、橋梁部28等の必要な内部構造を形成することができる。図15は、上記2層SOIウエハ41をエッチングした後の内部構造(断面)を示している。この場合、半導体基板16が上記した導電性の下方基板(底部基板:BS)に、上記第1シリコン層12の中央部の一部が導電性の重錘体25に、上記第2シリコン層14の一部が重錘体25を支持する橋梁部28をそれぞれ構成している。

【0037】

なお、エッチング液等を用いたウエハプロセスにより、空隙部29及び重錘体25を形成する場合を例に説明したが、PSG犠牲層とPoly−Si成膜を利用した表面マイクロマシーニング(surface micro machining)によって内部構造を形成することもできる。

【0038】

以上、説明したように、本実施例によれば、基板の接着等を行うことなく、一連の、しかも一般的な半導体ウエハプロセスを利用して、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することができる。

【実施例4】

【0039】

実施例2における2層SOIウエハ41の代わりに、3層SOIウエハを用いることもできる。図16は、3層SOIウエハ51の断面構造を示す図である。具体的には、半導体基板16は、CZ法により形成された、面方位(100)のN型シリコン(Si)で、約500μmの厚さを有する。半導体基板16上には、第1下層絶縁層15A、間隔規定用シリコン層15B、第1上層絶縁層15Cがこの順で積層されている。第1下層絶縁層15A及び第1上層絶縁層15Cは、厚さが約500nmのSiO2層である。また、間隔規定用シリコン層15Bは、重錘体25と下方基板16との間隔を規定する厚さを有する。すなわち、重錘体25の下方への所望の可動距離(振動可能)に応じた厚さを有する。第1上層絶縁層15C上に形成される第1シリコン層12、第2絶縁層13、第2シリコン層14は、上記した実施例3と同様である。

【0040】

実施例1の場合と同様に、図17に示すように、エッチング孔39を第2シリコン層14上に形成し、順次適切なエッチング液やエッチングガス等を当該エッチング孔39から導入することにより各層を選択エッチングすることができる。図17は、上記3層SOIウエハ51をエッチングした後の内部構造(断面)を示している。絶縁層(SiO2層)は形成後の応力等を考慮するとあまり厚く形成することはできないが、本実施例によれば、重錘体25の所望の可動距離に応じた厚さの間隔規定用シリコン層15Bを設ければよい。従って、感度、ダイナミックレンジ等の所望のセンサ特性に応じた設計が可能である。

【実施例5】

【0041】

図18は、センサの電極配置の構成を模式的に示す断面図である。センサとしては、上記したピエゾ抵抗素子センサ10、容量型センサ30のいずれにおいても適用可能である。一例として、容量型センサ30の場合を例に説明する。

【0042】

上方基板(TS)19として、導電性を有しない材料、例えばガラスが用いられている。絶縁膜18B上の上方基板19との接触部分に絶縁膜54を設け、化学機械研磨(CMP)する。絶縁膜54上に金(Au)の層55を形成している。一方、上方基板19の下面に金層57を形成し、金層55及び金層57をAuSn、AuGe等の合金56を介して加熱して接合する。このように加熱接合する場合、酸素の発生により内部空間の高真空が保持できなくなる虞があるため、非蒸発型のゲッター材(例えば、3mm厚程度のPaGe層又はZrを主とする金属層;図示せず)を金層57上の一部に設けるようにしても良い。また、半導体基板16から直接に、あるいは半導体基板16の下面に形成した金(Au)の金属からなる電極59によって容易に電位を取り出し、あるいは印加することができる。

【0043】

かかる構成により、上方基板19の下面の金層57及び絶縁膜54上の金層55が引き出し電極として利用できる。従って、電極の取り出しのための領域が小さく、また構造も簡易であり、センサを容易に小型化することができる。

【0044】

例えば、図19に示すように、図18に示す金層55を電極として、あるいは金層55上にパッド電極等をさらに形成して、上方基板19とボード60上の端子との間をワイヤボンディング62により配線することができる。また、下方基板16への接続をダイボンディング等により行うことも可能である。

【0045】

上方基板(TS)19がシリコン等の導電性材料で形成されている場合には、上方基板19の上面、側面及び底面を容易に電位を取り出し、あるいは印加することができる。例えば、図19に示すように、上方基板19上にパッド電極63を形成してワイヤボンディング64によりボード60上の端子に接続することができる。あるいは、図20に示すように、上方基板19の上面又は側面に金属電極65又は金属電極67を形成して金属製のバネ等の弾性体66,68により導電をとることも可能である。さらに、上記実施例における電極22A,35A〜35D等又はこれらに接続するように形成されたパッド電極61にワイヤボンディングにより配線することもできる。

【0046】

なお、上記した実施例中において示した数値は例示であって、適宜変更して適用することができる。

【図面の簡単な説明】

【0047】

【図1】本発明の実施例1であるピエゾ抵抗型センサの構成を模式的に示す平面図である。

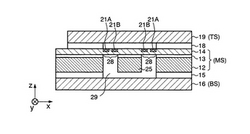

【図2】図1の線A−Aに関する断面構造を模式的に示す断面図である。

【図3】ピエゾ抵抗型センサの製造工程を模式的に示す断面図である。

【図4】ピエゾ抵抗型センサの製造工程を模式的に示す断面図である。

【図5】工程(STEP-1〜STEP-5)により製造したピエゾ抵抗型センサの模式的な断面図である。

【図6】ピエゾ抵抗型センサにおけるピエゾ抵抗素子の配線の一例を模式的に示す平面図である。

【図7】図6に示す配線によって形成される検出回路を模式的に示す回路図である。

【図8】上方基板、下方基板、及びN型中間シリコン層への電圧/電流印加を表す等価回路図である。

【図9】上方基板、下方基板、及び中間シリコン層に電圧印加を行った場合の、印加電位、中間シリコン層の電荷、及び中間シリコン層の位置を表す図である。

【図10】本発明の実施例2である容量型センサの構成を模式的に示す平面図である。

【図11】図10の線A−Aに関する断面構造を模式的に示す断面図である。

【図12】容量型センサの加速度及び角速度を検出する場合の検出回路の一例を示すブロック図である。

【図13】2層SOIウエハの断面構造を示す図である。

【図14】エッチングプロセスに用いられるエッチング孔を模式的に示す平面図である。

【図15】2層SOIウエハをエッチングした後の内部構造を模式的に示す断面図である。

【図16】3層SOIウエハの断面構造を示す図である。

【図17】3層SOIウエハをエッチングした後の内部構造を模式的に示す断面図である。

【図18】センサの電極配置の構成を模式的に示す断面図である。

【図19】ワイヤボンディングにより上方基板の電位を取り出す構成、及び上方基板上にパッド電極を形成して配線する構成を模式的に示す図である。

【図20】バネ等により配線する構成を模式的に示す図である。

【符号の説明】

【0048】

10 ピエゾ抵抗型センサ

12 第1シリコン層

13 第2絶縁層

14 第2シリコン層

15 第1絶縁層

16 下方基板

19 上方基板

21A,21B ピエゾ抵抗素子

25 重錘体

28 橋梁部

29 空隙部

33A〜33D 側方ブロック

37A〜37D CV変換回路

41 2層SOIウエハ

51 3層SOIウエハ

【技術分野】

【0001】

本発明は、センサ素子、特に、加速度センサ及び角速度センサに関する。

【背景技術】

【0002】

近年、電気、機械、自動車等の種々の産業分野で加速度センサ(1軸〜3軸)や角速度センサ(ジャイロ)の需要が高まっている。例えば、電気産業分野においては、携帯電話、デジタルカメラ、携帯情報端末、パソコン(PC)、ゲーム機器等の機器や装置に用いられる。また、GPS(グローバル・ポジショニング・システム)等における補正や、異常振動検出によるセキュリティ用途等の幅広い分野への適用が可能なため、今後さらに需要が増大するものと考えられる。このような種々の分野への適用拡大に伴って、小型化、高性能化等、センサのスペックに対する要求が一層高まっている。

【0003】

このようなセンサとしては、従来、静電容量素子を利用した加速度センサ及び角速度センサが知られている(例えば、特許文献1参照)。しかしながら、かかる従来のセンサでは製法及び構造が複雑であり、上記した種々の適用分野において、増大及び高度化する要求を満たすことは困難である。

【0004】

例えば、従来技術の構成においては、上部電極及び下部電極に交流電圧を印加することによって、当該上部及び下部電極間に設けられた重錘体を上下に振動させ、その重錘体に働くコリオリ力を多軸の加速度センサで検知して2軸の角速度センサとして用いている。しかしながら、上部電極及び下部電極に交流電圧を印加する構成では、基板として配線パターン付のガラス基板等が用いられていた。電極の取り出し構造に種々の手法が用いられているが、電極の取り出しのための領域が大きく、また構造も複雑であり、センサを小型化することが困難であった。

【特許文献1】特開2004−144598号公報(第7頁、図7)

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明が解決しようとする課題には、上記した問題が1例として挙げられる。本発明は、上述した問題点に鑑みてなされたものであり、その目的とするところは、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することにある。

【課題を解決するための手段】

【0006】

本発明によるセンサは、所定間隔をおいて配置された導電性の上方基板及び導電性の下方基板と、上方基板および下方基板に挟まれた空間内で導電性の重錘体を変位可能に支持する導電性の中間基板と、重錘体の変位に応じた電気信号を導電性の中間基板を介して取り出す検出素子と、を有することを特徴としている。

【0007】

また、本発明によるセンサは、所定間隔をおいて配置された導電性底面を有する上方基板及び導電性表面を有する下方基板と、上方基板および下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、上方基板の導電性底面と下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ重錘体に交流電圧を印加して重錘体を上下振動させる手段と、上下振動する重錘体の変位に基づいて重錘体に作用した角速度を検出する検出素子と、を有することを特徴としている。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施例について図面を参照しつつ詳細に説明する。なお、以下に示す実施例において、等価な構成要素には同一の参照符を付している。

【実施例1】

【0009】

図1及び図2は、本発明の実施例1であるセンサ10の構成を模式的に示す図である。センサ10は、ピエゾ抵抗素子を検出素子として用い、加速度センサ又は角速度センサとして動作する。

【0010】

より詳細には、図1は、センサ10の構造を模式的に説明する平面図であり、図2は、図1の線A−Aに関する断面構造を模式的に示す断面図である。センサ10は、シリコン等で形成された導電性の下方基板(底部基板:BS)16上に、SiO2により形成された第1絶縁層15、第1シリコン層12、SiO2により形成された第2絶縁層13、第2シリコン層14、SiO2により形成された第3絶縁層18、及びシリコン等で形成された導電性の上方基板(TS)19が順次設けられている。なお、第1シリコン層12、第2絶縁層13及び第2シリコン層14は後述する中間基板(IS)を構成している。さらに、下方基板16及び上方基板19間には、上記各層の一部が除去された空隙部29が形成されている。当該空隙部29内には、第2シリコン層14の一部を除去して十字形状に形成された橋梁部28が形成されている。また、第1シリコン層12の一部を除去することによって、橋梁部28の下方に重錘体25が形成されている。すなわち、第2シリコン層14の4つの橋梁部28が重錘体25を支持している。橋梁部28は可撓性を有し、重錘体25は駆動回路による駆動や外部からの力によって空隙部29内において、x、y及びz方向に変位可能である。また、橋梁部28の各々には1対のピエゾ抵抗素子21A,21Bが形成されている。ピエゾ抵抗素子21A,21Bの抵抗値は、橋梁部28に生ずる応力の大きさに応じて変化する。以下に、センサ10の製造方法、詳細構造及び加速度・角速度検出について図を参照して説明する。

<センサの製造方法>

図3〜4を参照してセンサ10の製造工程(STEP-1〜STEP-5)について説明する。なお、以下の製造工程は、通常の拡散技術、薄膜堆積技術、フォトリソグラフィ技術等のシリコン・プロセスによって行われる。

【0011】

まず、シリコン ・オン・インシュレータ(SOI)構造のウエハ11を用意する(STEP-1)。このSOIウエハ11は、N型の半導体基板12上に絶縁体13及びN型シリコン層14が形成された1層SOIウエハである。例えば、基板12は、CZ法により形成された、面方位(100)のN型シリコン(Si)で、約625μmの厚さを有する。絶縁体13は、厚さが約500nmのSiO2層が設けられている。絶縁体13上には、N型(100)面のシリコン層14が約5μmの厚さで形成されている。なお、ウエハ11は、センサ構造体の中間基板(IS)を構成している。

【0012】

次に、ウエハ11の底面(裏面)側には絶縁膜15が形成される。また、シリコン層14上には、P型ドーパントの拡散によってピエゾ抵抗素子21A,21Bが形成される。その後、シリコン層14上に酸化膜等の絶縁膜18Aを形成し、絶縁膜18Aにコンタクトホールを開けてピエゾ抵抗素子21A,21Bに接続された電極22,23,24を形成する。電極23は、ピエゾ抵抗素子21A,21Bのそれぞれの近端を接続する電極線として形成され、電極22,24は、電極23が接続されていないピエゾ抵抗素子21A,21Bのもう一方の端部(遠端)に接続されている。電極22,23,24の形成後、電極22,23,24を被覆する酸化膜等の絶縁膜18Bを形成する(STEP-2)。また、図には、電極22に接続されるパッド電極22Aが形成されている場合を示している。なお、電極22,23,24は配線電極(図示しない)によって後述する端子に接続されている。

【0013】

次に、ウェハ裏面の加工として通常のフォトエッチ工程で重錘体25及び橋梁部28を含む領域について、絶縁膜15と所定の厚さのシリコン層12をエッチングする(図示しない)。さらに、絶縁膜18B上に保護用のフォトレジストPRを形成する。また、絶縁膜15上にもフォトレジストPRを形成する。フォトリソグラフィによって底面側のフォトレジストPRをパターニングし、シリコン基板12をエッチングで除去することによって重錘体25を形成する(STEP-3)。なお、フォトレジストPRのパターニング、及び絶縁膜15及びシリコン基板12のエッチング除去は、ピエゾ抵抗素子21A,21Bが橋梁部28の両端部に位置するように行われる。

【0014】

さらに、絶縁体13をエッチングで除去し、フォトレジストPRを剥離する(STEP-4)。その後、接着剤等によって裏面の絶縁膜15の下にシリコン等の導電性の下方基板(BS)16を貼り付ける。また、空隙部29に対応する大きさの溝29Aを形成したシリコン等の導電性の上方基板(BS)19を溝29A側を下方、すなわち絶縁膜18B側にして接着剤等によって絶縁膜18B上に貼り付ける(STEP-5)。なお、シリコン基板19の両端部は除去される。シリコン基板19の貼り付けによって溝29Aは、橋梁部28及び重錘体25が上方(+z方向)に変位できるための空隙部を形成する。なお、以下においては、上記した空隙部29に当該空隙部29Aを合わせた領域を空隙部29とも称する。上記製造工程(STEP-1〜STEP-5)により、図5に示すように、センサ10が形成される。なお、絶縁膜18A及び18Bが図1に示す絶縁膜18に対応する。

<角速度の検出>

図6は、上記したセンサ10におけるピエゾ抵抗素子の配線の一例を模式的に示す平面図である。以下においては、図中x方向の橋梁部28に配されたピエゾ抵抗素子(及びその抵抗値)を、x方向に順にR1,R2,R3,R4とし、y方向の橋梁部28に配されたピエゾ抵抗素子(及びその抵抗値)を、y方向に順にR5,R6,R7,R8として説明する。ピエゾ抵抗素子R1〜R8を接続する配線は、端子T1〜T8に接続されている。

【0015】

図7は、図6に示す配線によって形成される検出回路を模式的に示している。図に示すように、ピエゾ抵抗素子R1〜R4、及びピエゾ抵抗素子R5〜R8によってそれぞれホイートストン・ブリッジWB1,WB2が構成されている。ホイートストン・ブリッジWB1において、端子T1及びT3間に電圧Vaを印加し、端子T2及びT4間の電位差ΔVxを検出する。同様に、ホイートストン・ブリッジWB2において、端子T5及びT7間に電圧Vaを印加し、端子T6及びT8間の電位差ΔVyを検出する。

【0016】

次に、角速度を検出する場合に、重錘体25を運動させるための構成及び方法について以下に説明する。図8は、上方基板(TS)19、下方基板(底部基板:BS)16、及び中間基板(IS)のN型シリコン層14へ電圧/電流印加を表す等価回路を示している。より詳細には、図9に示すように、上方基板(電極E5とする)19に直流電位+Vd、例えば+50Vを印加し(図中、一点鎖線で示す)、下方基板(電極E6とする)16には直流電位−Vd、例えば−50Vを印加する(図中、二点鎖線で示す)。N型シリコン層14(電極E0とする)には、正弦波状の交流電位(振幅±Va)を印加する(図中、実線で示す)。かかる交流電位の印加に応じてN型シリコン層14の電荷が変化するため(図9中段)、N型シリコン層14はクーロン力によってz軸方向に振動する(図9下段)。ここで、正弦波交流の周波数は、センサ構造体固有のバネ定数と、重錘体25及び橋梁部28を含む振動部の質量とから定まる共振周波数とするのがエネルギーロスが最小で好ましい。しかしながら、必ずしも当該共振周波数でなくともよい。また、印加する交流電位は正弦波状に限らず、三角波状、方形波状であってもよい。また、電圧駆動の場合を説明したが、正弦波状等の交流電流によりN型シリコン層14に電荷を与えたり、引き抜いたりする電流駆動を行ってもよい。

【0017】

このように中間基板(IS)を正弦波状の交流電位(又は交流電流)により駆動することによって重錘体25はz軸方向に振動する。振動している重錘体25に外力(角速度)が作用すると重錘体25にはコリオリ力が作用する。従って、x軸方向に作用するコリオリ力を検出することによってy軸まわりの角速度を検出することができる。同様にして、y軸方向に作用するコリオリ力を検出することによってx軸まわりの角速度を検出することができる。

【0018】

かかるコリオリ力は、ピエゾ抵抗素子R1〜R8の応力による抵抗変化として検出することができる。すなわち、図7に示すホイートストン・ブリッジWB1,WB2の電位差ΔVx、ΔVyを検出することによって角速度検出を行うことができる。より具体的には、重錘体25がz軸方向に振動する場合、y軸まわりの回転による角速度は当該電圧変化ΔVxとして検出される。また、x軸まわりの回転による角速度は当該電圧変化ΔVyとして検出される。

【0019】

なお、中間基板(IS)のN型シリコン層14が重錘体25に電気的に接続するように構成してもよい。例えば、N型シリコン層14及び重錘体25間の絶縁体13にスルーホール等を開け、当該スルーホール等に導電体を埋め込むプロセスを追加してもよい。

【0020】

上記した構成において、重錘体25を振動させない場合には、電位差ΔVx、ΔVyは外力(加速度)に比例した値となり、センサ10は加速度センサとして機能する。

【0021】

以上、説明したように、本実施例によれば、一般的な半導体ウエハプロセスを利用して、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することができる。また、上方基板19と下方基板16に直流電位を与えるので、中間基板は電気的にシールドされた状態にあり、外部雑音に対して安定動作ができる。

【0022】

尚、上述の構成では、下方基板16及び上方基板19をシリコン基板で構成したが、これに限らず、下方基板16をその表面に電極層(導電性表面)を設けた絶縁基板(ガラス基板など)としてもよく、また、上方基板19をその底面に電極層(導電性底面)を設けた絶縁基板(ガラス基板など)としてもよく、更に、下方基板16及び上方基板19をガラス基板などの絶縁基板で構成し、下方基板16の表面及び上方基板19の底面にそれぞれ電極層を設け、導電性表面を有する下方基板16及び導電性底面を有する上方基板19としても良い。また、2軸の加速度センサとする場合、上方基板16と下方基板19に電位を付与する必要はないため、絶縁基板(ガラス基板など)で構成してもよく、また、上方基板19を設けなくても良い。

【実施例2】

【0023】

図10及び図11は、本発明の実施例2であるセンサ30の構成を模式的に示すブロック図である。センサ30は、キャパシタンス変化に基づいて加速度又は角速度を検出する加速度センサ又は角速度センサとして動作する。

<容量型センサの構造及び製造方法>

より詳細には、図10は、センサ30の構造を模式的に説明する平面図であり、図11は、図10の線A−Aに関する断面構造を模式的に示す断面図である。センサ30は、シリコン等で形成された導電性の下方基板(底部基板:BS)16上に、SiO2により形成された第1絶縁層15、第1シリコン層12、SiO2により形成された第2絶縁層13、第2シリコン層14、SiO2により形成された第3絶縁層18、及びシリコン等で形成された導電性の上方基板(TS)19が順次設けられている。また、空隙部29が形成され、当該空隙部29内に橋梁部28及び橋梁部28の下方に重錘体25が形成されている点は上記した実施例1と同様である。また、橋梁部28は可撓性を有し、重錘体25は駆動回路による駆動や外部からの力によって空隙部29内において、x、y及びz方向に変位可能である。

【0024】

以下に、センサ30の製造方法及び構造について説明する。上記した実施例1と同様な半導体プロセスを用いてセンサ30を製造することができる。すなわち、N型の半導体基板12上に絶縁体13及びN型シリコン層14が形成された1層SOIウエハを用いて製造することができる。センサ30においては、ピエゾ素子は形成されず、重錘体25を四方から囲む側方ブロック(以下、単にブロックともいう。)が設けられている。より具体的には、第1シリコン層12のうち、空隙部29の外側の部分にはアイソレーション用のトレンチ31が形成され、図10の平面投影図に示すように、重錘体25を四方から囲む位置に第1、第2、第3及び第4の側方ブロック33A,33B,33C,33Dが分離形成されている。

【0025】

図11に示すように、N型シリコン層14を貫通し、重錘体25に電気的に接続された導電体34Oが形成されている。導電体34Oは電極端子35Oに接続され、電極端子35Oを介して重錘体25を外部回路に接続できるようになっている。電気的に分離して形成された第1〜第4の側方ブロック33A〜33Dには、それぞれN型シリコン層14を貫通して形成された導電体34A〜34Dが電気的に接続されている。導電体34A〜34Dには電極端子35A〜35Dが接続され、電極端子35A〜35Dを介して第1〜第4の側方ブロック33A〜33Dを外部回路に接続できるようになっている。

【0026】

センサ30は、重錘体25の表面に形成される電極E0と、第1〜第4の側方ブロック33A〜33Dの上記電極E0に対向する面に形成される電極E1〜E4と、のそれぞれ間の容量(キャパシタンス)C1〜C4の変化に基づいて加速度又は角速度を検出するよう構成されている。なお、以下においては、電極E0と、電極E1〜E4と、によって形成されるキャパシタについてもC1〜C4の参照符を付して説明する。

<角速度の検出>

図12は、上記したセンサ30の加速度及び角速度を検出する場合の検出回路の一例を示すブロック図である。

【0027】

角速度を検出する場合には、上記実施例1と同様に、例えば、上方基板19に直流電位+Vdを、下方基板16に直流電位−Vdを印加し、N型シリコン層14には、正弦波状の交流電位(振幅±Va)を印加する(図中、実線で示す)。すなわち、交流電位の印加に応じて重錘体25がz軸方向に振動するようにした状態で後述する容量変化の検出を行う。なお、電圧駆動の場合を説明したが、電流駆動を行ってもよいのは同様である。

【0028】

図12に示すように、x方向に形成されるキャパシタであるキャパシタC1,C3の容量変化が検出される。すなわち、重錘体25の電極E0及び第1ブロックの電極E1によって形成されるキャパシタC1の容量変化は容量−電圧変換回路(CV変換回路)37Aによって電圧変化V1に変換される。さらに、重錘体25の電極E0及び第3ブロックの電極E3によって形成されるキャパシタC3の容量変化はCV変換回路37Cによって電圧変化V3に変換される。減算器38Aにおいて電圧変化V1,V3の差分ΔVxが得られる。電圧差ΔVxによってy軸まわりの回転による角速度が得られる。

【0029】

また、y方向に形成されるキャパシタであるキャパシタC2,C4の容量変化が検出される。すなわち、重錘体25の電極E0及び第2ブロックの電極E2によって形成されるキャパシタC2の容量変化はCV変換回路37Bによって電圧変化V2に変換される。さらに、重錘体25の電極E0及び第4ブロックの電極E4によって形成されるキャパシタC4の容量変化はCV変換回路37Dによって電圧変化V4に変換される。減算器38Cにおいて電圧変化V2,V4の差分ΔVyが得られる。電圧差ΔVyによってx軸まわりの回転による角速度が得られる。

【0030】

上記した構成において、重錘体25を振動させない場合には、電位差ΔVx、ΔVyは加速度に比例した値となり、センサ30は加速度センサとして機能することになる。

【0031】

以上、説明したように、本実施例によれば、一般的な半導体ウエハプロセスを利用して、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することができる。また、上方基板19と下方基板16に直流電位を与えるので、中間基板は電気的にシールドされた状態にあり、外部雑音に対して安定動作ができる。

【0032】

尚、上述の構成では、下方基板16及び上方基板19をシリコン基板で構成したが、これに限らず、下方基板16をその表面に電極層(導電性表面)を設けた絶縁基板(ガラス基板など)としてもよく、また、上方基板19をその底面に電極層(導電性底面)を設けた絶縁基板(ガラス基板など)としてもよく、更に、下方基板16及び上方基板19をガラス基板などの絶縁基板で構成し、下方基板16の表面及び上方基板19の底面にそれぞれ電極層を設け、導電性表面を有する下方基板16及び導電性底面を有する上方基板19としても良い。また、2軸の加速度センサとする場合、上方基板16と下方基板19に電位を付与する必要はないため、絶縁基板(ガラス基板など)で構成してもよく、また、上方基板19を設けなくても良い。

【実施例3】

【0033】

次に、本発明の実施例3について説明する。上記した実施例においては、N型の半導体基板12上に絶縁体13及びN型シリコン層14が形成された1層SOIウエハを用いてセンサを製造する場合について説明したが、多層SOIウエハを用いて製造することも可能である。

【0034】

図13は、2層SOIウエハ41の断面構造を示す断面図である。具体的には、N型の半導体基板16上に、第1絶縁層15、第1シリコン層12、SiO2により形成された第2絶縁層13、第2シリコン層14が順次積層された構造を有している。簡単に言えば、上記実施例においては、1層SOIウエハ基板に第1絶縁層15及び半導体基板16が後のプロセスによって形成されたが、本実施例においては、1層SOIウエハに半導体基板16及び第1絶縁層15を加えた2層SOIウエハが用いられる。

【0035】

例えば、半導体基板16は、CZ法により形成された、面方位(100)のN型シリコン(Si)で、約500μmの厚さを有する(10-20Ωcm)。第1絶縁層15は、厚さが約3μmのSiO2層である。後述するように、第1絶縁層15の厚さによって重錘体25と下方基板16との距離が規定される。第1シリコン層12は、約20μmの厚さを有するN型シリコンである(10-20Ωcm)。第2絶縁層13は、厚さが約300nmのSiO2層である。また、第2シリコン層14は、約2μmの厚さを有するN型シリコンである(10-20Ωcm)。

【0036】

かかる2層SOIウエハ41には、エッチングプロセスによって空隙部29及び重錘体25が形成される。例えば、図14に示すように、エッチング用の孔39を第2シリコン層14上に形成し、順次適切なエッチング液やエッチングガス等を当該エッチング孔39から導入することにより各層を選択エッチングすることができ、2層SOIウエハ41内に空隙部29、重錘体25、橋梁部28等の必要な内部構造を形成することができる。図15は、上記2層SOIウエハ41をエッチングした後の内部構造(断面)を示している。この場合、半導体基板16が上記した導電性の下方基板(底部基板:BS)に、上記第1シリコン層12の中央部の一部が導電性の重錘体25に、上記第2シリコン層14の一部が重錘体25を支持する橋梁部28をそれぞれ構成している。

【0037】

なお、エッチング液等を用いたウエハプロセスにより、空隙部29及び重錘体25を形成する場合を例に説明したが、PSG犠牲層とPoly−Si成膜を利用した表面マイクロマシーニング(surface micro machining)によって内部構造を形成することもできる。

【0038】

以上、説明したように、本実施例によれば、基板の接着等を行うことなく、一連の、しかも一般的な半導体ウエハプロセスを利用して、構造が簡便で軽量化、小型化に適すると共に、製造も容易で高性能化に適したセンサを提供することができる。

【実施例4】

【0039】

実施例2における2層SOIウエハ41の代わりに、3層SOIウエハを用いることもできる。図16は、3層SOIウエハ51の断面構造を示す図である。具体的には、半導体基板16は、CZ法により形成された、面方位(100)のN型シリコン(Si)で、約500μmの厚さを有する。半導体基板16上には、第1下層絶縁層15A、間隔規定用シリコン層15B、第1上層絶縁層15Cがこの順で積層されている。第1下層絶縁層15A及び第1上層絶縁層15Cは、厚さが約500nmのSiO2層である。また、間隔規定用シリコン層15Bは、重錘体25と下方基板16との間隔を規定する厚さを有する。すなわち、重錘体25の下方への所望の可動距離(振動可能)に応じた厚さを有する。第1上層絶縁層15C上に形成される第1シリコン層12、第2絶縁層13、第2シリコン層14は、上記した実施例3と同様である。

【0040】

実施例1の場合と同様に、図17に示すように、エッチング孔39を第2シリコン層14上に形成し、順次適切なエッチング液やエッチングガス等を当該エッチング孔39から導入することにより各層を選択エッチングすることができる。図17は、上記3層SOIウエハ51をエッチングした後の内部構造(断面)を示している。絶縁層(SiO2層)は形成後の応力等を考慮するとあまり厚く形成することはできないが、本実施例によれば、重錘体25の所望の可動距離に応じた厚さの間隔規定用シリコン層15Bを設ければよい。従って、感度、ダイナミックレンジ等の所望のセンサ特性に応じた設計が可能である。

【実施例5】

【0041】

図18は、センサの電極配置の構成を模式的に示す断面図である。センサとしては、上記したピエゾ抵抗素子センサ10、容量型センサ30のいずれにおいても適用可能である。一例として、容量型センサ30の場合を例に説明する。

【0042】

上方基板(TS)19として、導電性を有しない材料、例えばガラスが用いられている。絶縁膜18B上の上方基板19との接触部分に絶縁膜54を設け、化学機械研磨(CMP)する。絶縁膜54上に金(Au)の層55を形成している。一方、上方基板19の下面に金層57を形成し、金層55及び金層57をAuSn、AuGe等の合金56を介して加熱して接合する。このように加熱接合する場合、酸素の発生により内部空間の高真空が保持できなくなる虞があるため、非蒸発型のゲッター材(例えば、3mm厚程度のPaGe層又はZrを主とする金属層;図示せず)を金層57上の一部に設けるようにしても良い。また、半導体基板16から直接に、あるいは半導体基板16の下面に形成した金(Au)の金属からなる電極59によって容易に電位を取り出し、あるいは印加することができる。

【0043】

かかる構成により、上方基板19の下面の金層57及び絶縁膜54上の金層55が引き出し電極として利用できる。従って、電極の取り出しのための領域が小さく、また構造も簡易であり、センサを容易に小型化することができる。

【0044】

例えば、図19に示すように、図18に示す金層55を電極として、あるいは金層55上にパッド電極等をさらに形成して、上方基板19とボード60上の端子との間をワイヤボンディング62により配線することができる。また、下方基板16への接続をダイボンディング等により行うことも可能である。

【0045】

上方基板(TS)19がシリコン等の導電性材料で形成されている場合には、上方基板19の上面、側面及び底面を容易に電位を取り出し、あるいは印加することができる。例えば、図19に示すように、上方基板19上にパッド電極63を形成してワイヤボンディング64によりボード60上の端子に接続することができる。あるいは、図20に示すように、上方基板19の上面又は側面に金属電極65又は金属電極67を形成して金属製のバネ等の弾性体66,68により導電をとることも可能である。さらに、上記実施例における電極22A,35A〜35D等又はこれらに接続するように形成されたパッド電極61にワイヤボンディングにより配線することもできる。

【0046】

なお、上記した実施例中において示した数値は例示であって、適宜変更して適用することができる。

【図面の簡単な説明】

【0047】

【図1】本発明の実施例1であるピエゾ抵抗型センサの構成を模式的に示す平面図である。

【図2】図1の線A−Aに関する断面構造を模式的に示す断面図である。

【図3】ピエゾ抵抗型センサの製造工程を模式的に示す断面図である。

【図4】ピエゾ抵抗型センサの製造工程を模式的に示す断面図である。

【図5】工程(STEP-1〜STEP-5)により製造したピエゾ抵抗型センサの模式的な断面図である。

【図6】ピエゾ抵抗型センサにおけるピエゾ抵抗素子の配線の一例を模式的に示す平面図である。

【図7】図6に示す配線によって形成される検出回路を模式的に示す回路図である。

【図8】上方基板、下方基板、及びN型中間シリコン層への電圧/電流印加を表す等価回路図である。

【図9】上方基板、下方基板、及び中間シリコン層に電圧印加を行った場合の、印加電位、中間シリコン層の電荷、及び中間シリコン層の位置を表す図である。

【図10】本発明の実施例2である容量型センサの構成を模式的に示す平面図である。

【図11】図10の線A−Aに関する断面構造を模式的に示す断面図である。

【図12】容量型センサの加速度及び角速度を検出する場合の検出回路の一例を示すブロック図である。

【図13】2層SOIウエハの断面構造を示す図である。

【図14】エッチングプロセスに用いられるエッチング孔を模式的に示す平面図である。

【図15】2層SOIウエハをエッチングした後の内部構造を模式的に示す断面図である。

【図16】3層SOIウエハの断面構造を示す図である。

【図17】3層SOIウエハをエッチングした後の内部構造を模式的に示す断面図である。

【図18】センサの電極配置の構成を模式的に示す断面図である。

【図19】ワイヤボンディングにより上方基板の電位を取り出す構成、及び上方基板上にパッド電極を形成して配線する構成を模式的に示す図である。

【図20】バネ等により配線する構成を模式的に示す図である。

【符号の説明】

【0048】

10 ピエゾ抵抗型センサ

12 第1シリコン層

13 第2絶縁層

14 第2シリコン層

15 第1絶縁層

16 下方基板

19 上方基板

21A,21B ピエゾ抵抗素子

25 重錘体

28 橋梁部

29 空隙部

33A〜33D 側方ブロック

37A〜37D CV変換回路

41 2層SOIウエハ

51 3層SOIウエハ

【特許請求の範囲】

【請求項1】

所定間隔をおいて配置された導電性の上方基板及び導電性の下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で導電性の重錘体を変位可能に支持する導電性の中間基板と、

前記重錘体の変位に応じた電気信号を前記導電性の中間基板を介して取り出す検出素子と、を有することを特徴とするセンサ。

【請求項2】

前記上方基板、下方基板及び中間基板は、シリコンで構成されていることを特徴とする請求項1記載のセンサ。

【請求項3】

前記中間基板及び下方基板は、シリコン基板上に第1絶縁層、第1シリコン層、第2絶縁層及び第2シリコン層が順次積層された2層SOI基板を用いて形成され、前記のシリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部をそれぞれ構成することを特徴とする請求項1記載のセンサ。

【請求項4】

前記中間基板及び下方基板は、シリコン基板上に第1下層絶縁層、間隔規定用シリコン層、第1上層絶縁層、第1シリコン層、第2絶縁層、第2シリコン層が順次積層形成された3層SOI基板を用いて形成され、前記シリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部を構成し、前記第1下層絶縁層、間隔規定用シリコン層及び第1上層絶縁層が前記下方基板と前記重錘体との間の間隙を規定することを特徴とする請求項1記載のセンサ。

【請求項5】

前記上方基板に第1の直流電位を印加すると共に前記下方基板に第2の直流電位を印加し、かつ前記重錘体に交流電圧を印加する電圧印加手段を備え、交流電圧印加により前記重錘体を上下振動させ、前記重錘体に作用した角速度を前記検出素子により検出することを特徴とする請求項1記載のセンサ。

【請求項6】

前記中間基板は、前記重錘体を支持するとともに前記検出素子としてのピエゾ抵抗素子を含む橋梁部を有することを特徴とする請求項1記載のセンサ。

【請求項7】

前記重錘体は各々が電極として機能する4つの側面を有し、前記第1シリコン層は、各々が前記重錘体の4つの側面に対向する対向電極として機能する対向面を有する4つのブロック部を含み、前記検出素子は前記重錘体の4つの側面及び前記4つのブロック部によって形成される4組の容量性素子によって構成されることを特徴とする請求項3又は4記載のセンサ。

【請求項8】

前記ブロック部は、トレンチ構造の絶縁層によって前記中間基板の他の部分と分離されていることを特徴とする請求項7記載のセンサ。

【請求項9】

前記交流電圧は、前記第1の直流電位と第2の直流電位との間で振動する振幅を有することを特徴とする請求項5記載のセンサ。

【請求項10】

前記第1の直流電位は正の所定電位であり、前記第2の直流電位は負の所定電位であることを特徴とする請求項5記載のセンサ。

【請求項11】

前記下方基板は、前記下方基板の底面に形成された電位取り出し電極を有することを特徴とする請求項1記載のセンサ。

【請求項12】

前記上方基板の上面及び側面のいずれかが電位取り出し電極であることを特徴とする請求項1記載のセンサ。

【請求項13】

前記上方基板に電気的に接続され、前記中間基板の表面に形成された前記上方基板の電位取り出し電極を有することを特徴とする請求項1記載のセンサ。

【請求項14】

所定間隔をおいて配置された導電性底面を有する上方基板及び導電性表面を有する下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、

前記上方基板の導電性底面と前記下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ前記重錘体に交流電圧を印加して前記重錘体を上下振動させる手段と、

上下振動する前記重錘体の変位に基づいて前記重錘体に作用した角速度を検出する検出素子と、を有することを特徴とするセンサ。

【請求項15】

所定間隔をおいて配置された導電性の上方基板及び導電性表面を有する下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、

前記導電性の上方基板と前記下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ前記重錘体に交流電圧を印加して前記重錘体を上下振動させる手段と、

上下振動する前記重錘体の変位に基づいて前記重錘体に作用した角速度を検出する検出素子と、を有することを特徴とするセンサ。

【請求項16】

所定間隔をおいて配置された導電性底面を有する上方基板及び導電性の下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、

前記上方基板の導電性底面と前記下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ前記重錘体に交流電圧を印加して前記重錘体を上下振動させる手段と、

上下振動する前記重錘体の変位に基づいて前記重錘体に作用した角速度を検出する検出素子と、を有することを特徴とするセンサ。

【請求項17】

所定間隔をおいて配置された導電性の下方基板と、

前記上方基板および前記下方基板間に設けられ、導電性の重錘体を変位可能に支持する導電性の中間基板と、

前記重錘体の変位に応じた電気信号を前記導電性の中間基板を介して取り出す検出素子と、を有し、

前記基板及び下方基板は、シリコン基板上に第1下層絶縁層、間隔規定用シリコン層、第1上層絶縁層、第1シリコン層、第2絶縁層、第2シリコン層が順次積層形成された3層SOI基板を用いて形成され、前記シリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部を構成し、前記第1下層絶縁層、間隔規定用シリコン層及び第1上層絶縁層が前記下方基板と前記重錘体との間の間隙を規定することを特徴とするセンサ。

【請求項18】

所定間隔をおいて配置された導電性の下方基板と、

前記上方基板および前記下方基板間に設けられ、導電性の重錘体を変位可能に支持する導電性の中間基板と、

前記重錘体の変位に応じた電気信号を前記導電性の基板を介して取り出す検出素子と、を有し、

前記基板及び下方基板は、シリコン基板上に第1下層絶縁層、間隔規定用シリコン層、第1上層絶縁層、第1シリコン層、第2絶縁層、第2シリコン層が順次積層形成された3層SOI基板を用いて形成され、前記シリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部を構成し、間隔規定用シリコン層が前記下方基板と前記重錘体との間の間隙を規定することを特徴とするセンサ。

【請求項1】

所定間隔をおいて配置された導電性の上方基板及び導電性の下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で導電性の重錘体を変位可能に支持する導電性の中間基板と、

前記重錘体の変位に応じた電気信号を前記導電性の中間基板を介して取り出す検出素子と、を有することを特徴とするセンサ。

【請求項2】

前記上方基板、下方基板及び中間基板は、シリコンで構成されていることを特徴とする請求項1記載のセンサ。

【請求項3】

前記中間基板及び下方基板は、シリコン基板上に第1絶縁層、第1シリコン層、第2絶縁層及び第2シリコン層が順次積層された2層SOI基板を用いて形成され、前記のシリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部をそれぞれ構成することを特徴とする請求項1記載のセンサ。

【請求項4】

前記中間基板及び下方基板は、シリコン基板上に第1下層絶縁層、間隔規定用シリコン層、第1上層絶縁層、第1シリコン層、第2絶縁層、第2シリコン層が順次積層形成された3層SOI基板を用いて形成され、前記シリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部を構成し、前記第1下層絶縁層、間隔規定用シリコン層及び第1上層絶縁層が前記下方基板と前記重錘体との間の間隙を規定することを特徴とする請求項1記載のセンサ。

【請求項5】

前記上方基板に第1の直流電位を印加すると共に前記下方基板に第2の直流電位を印加し、かつ前記重錘体に交流電圧を印加する電圧印加手段を備え、交流電圧印加により前記重錘体を上下振動させ、前記重錘体に作用した角速度を前記検出素子により検出することを特徴とする請求項1記載のセンサ。

【請求項6】

前記中間基板は、前記重錘体を支持するとともに前記検出素子としてのピエゾ抵抗素子を含む橋梁部を有することを特徴とする請求項1記載のセンサ。

【請求項7】

前記重錘体は各々が電極として機能する4つの側面を有し、前記第1シリコン層は、各々が前記重錘体の4つの側面に対向する対向電極として機能する対向面を有する4つのブロック部を含み、前記検出素子は前記重錘体の4つの側面及び前記4つのブロック部によって形成される4組の容量性素子によって構成されることを特徴とする請求項3又は4記載のセンサ。

【請求項8】

前記ブロック部は、トレンチ構造の絶縁層によって前記中間基板の他の部分と分離されていることを特徴とする請求項7記載のセンサ。

【請求項9】

前記交流電圧は、前記第1の直流電位と第2の直流電位との間で振動する振幅を有することを特徴とする請求項5記載のセンサ。

【請求項10】

前記第1の直流電位は正の所定電位であり、前記第2の直流電位は負の所定電位であることを特徴とする請求項5記載のセンサ。

【請求項11】

前記下方基板は、前記下方基板の底面に形成された電位取り出し電極を有することを特徴とする請求項1記載のセンサ。

【請求項12】

前記上方基板の上面及び側面のいずれかが電位取り出し電極であることを特徴とする請求項1記載のセンサ。

【請求項13】

前記上方基板に電気的に接続され、前記中間基板の表面に形成された前記上方基板の電位取り出し電極を有することを特徴とする請求項1記載のセンサ。

【請求項14】

所定間隔をおいて配置された導電性底面を有する上方基板及び導電性表面を有する下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、

前記上方基板の導電性底面と前記下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ前記重錘体に交流電圧を印加して前記重錘体を上下振動させる手段と、

上下振動する前記重錘体の変位に基づいて前記重錘体に作用した角速度を検出する検出素子と、を有することを特徴とするセンサ。

【請求項15】

所定間隔をおいて配置された導電性の上方基板及び導電性表面を有する下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、

前記導電性の上方基板と前記下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ前記重錘体に交流電圧を印加して前記重錘体を上下振動させる手段と、

上下振動する前記重錘体の変位に基づいて前記重錘体に作用した角速度を検出する検出素子と、を有することを特徴とするセンサ。

【請求項16】

所定間隔をおいて配置された導電性底面を有する上方基板及び導電性の下方基板と、

前記上方基板および前記下方基板に挟まれた空間内で変位可能に支持された導電性の重錘体を含む中間基板と、

前記上方基板の導電性底面と前記下方基板の導電性表面とに各々所定の直流電圧を印加し、かつ前記重錘体に交流電圧を印加して前記重錘体を上下振動させる手段と、

上下振動する前記重錘体の変位に基づいて前記重錘体に作用した角速度を検出する検出素子と、を有することを特徴とするセンサ。

【請求項17】

所定間隔をおいて配置された導電性の下方基板と、

前記上方基板および前記下方基板間に設けられ、導電性の重錘体を変位可能に支持する導電性の中間基板と、

前記重錘体の変位に応じた電気信号を前記導電性の中間基板を介して取り出す検出素子と、を有し、

前記基板及び下方基板は、シリコン基板上に第1下層絶縁層、間隔規定用シリコン層、第1上層絶縁層、第1シリコン層、第2絶縁層、第2シリコン層が順次積層形成された3層SOI基板を用いて形成され、前記シリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部を構成し、前記第1下層絶縁層、間隔規定用シリコン層及び第1上層絶縁層が前記下方基板と前記重錘体との間の間隙を規定することを特徴とするセンサ。

【請求項18】

所定間隔をおいて配置された導電性の下方基板と、

前記上方基板および前記下方基板間に設けられ、導電性の重錘体を変位可能に支持する導電性の中間基板と、

前記重錘体の変位に応じた電気信号を前記導電性の基板を介して取り出す検出素子と、を有し、

前記基板及び下方基板は、シリコン基板上に第1下層絶縁層、間隔規定用シリコン層、第1上層絶縁層、第1シリコン層、第2絶縁層、第2シリコン層が順次積層形成された3層SOI基板を用いて形成され、前記シリコン基板が前記導電性の下方基板、前記第1シリコン層の一部が前記導電性の重錘体、前記第2シリコン層の一部が前記重錘体を支持する橋梁部を構成し、間隔規定用シリコン層が前記下方基板と前記重錘体との間の間隙を規定することを特徴とするセンサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2006−153689(P2006−153689A)

【公開日】平成18年6月15日(2006.6.15)

【国際特許分類】

【出願番号】特願2004−345616(P2004−345616)

【出願日】平成16年11月30日(2004.11.30)

【出願人】(000005016)パイオニア株式会社 (3,620)

【出願人】(503213291)パイオニア・マイクロ・テクノロジー株式会社 (25)

【公開日】平成18年6月15日(2006.6.15)

【国際特許分類】

【出願日】平成16年11月30日(2004.11.30)

【出願人】(000005016)パイオニア株式会社 (3,620)

【出願人】(503213291)パイオニア・マイクロ・テクノロジー株式会社 (25)

[ Back to top ]