センサ装置の製造方法

【課題】多軸方向に関する検出が可能な小型のセンサ装置の製造コストを低減することができる製造方法を提供する。

【解決手段】連結部110によって互いに連結された第1および第2のセンサ素子101、102が基板100上に形成される。第1および第2のセンサ素子101、102のそれぞれを支持する第1および第2の部分P1、P2に基板100が分割される。この分割の後に、連結部110を曲げながら第1のセンサ素子101に対して第2のセンサ素子102の向きが変えられる。

【解決手段】連結部110によって互いに連結された第1および第2のセンサ素子101、102が基板100上に形成される。第1および第2のセンサ素子101、102のそれぞれを支持する第1および第2の部分P1、P2に基板100が分割される。この分割の後に、連結部110を曲げながら第1のセンサ素子101に対して第2のセンサ素子102の向きが変えられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のセンサ素子を有するセンサ装置の製造方法に関するものである。

【背景技術】

【0002】

たとえば自動車のエアバッグシステムにおいて、多軸方向の加速度を検出するためのセンサが用いられている。このような多軸力学量検出センサは、X、Yの2軸方向、あるいはX、Y、Zの3軸方向の力学量の検出を1つのセンサで行なうことができる。よって限られたスペースにおいて多軸方向の力学量を検出する必要がある場合に、多軸力学量センサは特に好適に用いられる。

【0003】

このようなセンサの製造方法は、たとえば、特開2003−28646号公報に開示されている。この公報によれば、まず複数のセンサブロックの各々に半導体センサの素子が設けられる。次に複数のセンサブロックが互いに固定されることで、多軸半導体センサが形成される。

【特許文献1】特開2003−28646号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記の公報の技術において多軸半導体センサ(センサ装置)を十分に小型化しようとすると、センサ素子の大きさとほとんど同程度までセンサブロックを小さくする必要がある。このように微細な複数のセンサブロックを互いに固定する工程は、煩雑であり、また通常の半導体製造装置と異なる専用の組立装置を必要とする。このため上記従来の技術では、センサ装置の製造コストが高くなるという問題があった。

【0005】

本発明は、上記課題に鑑みてなされたものであり、本発明の目的は、多軸方向に関する検出が可能な小型のセンサ装置の製造コストを低減することができる製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明のセンサ装置の製造方法は、以下の工程を有する。

連結部によって互いに連結された第1および第2のセンサ素子が基板上に形成される。第1および第2のセンサ素子のそれぞれを支持する第1および第2の部分に基板が分割される。この分割の後に、連結部を曲げながら第1のセンサ素子に対して第2のセンサ素子の向きが変えられる。

【発明の効果】

【0007】

本発明のセンサ装置によれば、装置が小型であっても、第1のセンサ素子に対する第2のセンサ素子の向きを連結部を曲げるだけで変えることができる。このため、多軸方向に関する検出が可能な小型のセンサ装置の製造コストを低減することができる。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施の形態について図に基づいて説明する。

(実施の形態1)

はじめに本実施の形態におけるセンサ装置としての多軸加速度センサチップの製造方法の概要について説明する。

【0009】

まずMEMS(Micro Electro Mechanical Systems)製造技術により、1軸方向の力学量を検出することができる構成を有するセンサ素子が、検出軸の方向が同一の方向(第1の方向)となるように基板表面上に多数形成される。この多数のセンサ素子は、特定の基準チップ(第1のセンサ素子)と、この基準チップの周囲に配置されたチップ(第2のセンサ素子)とを含む。第1および第2のセンサ素子は、電気信号の入出力電極に関して異なる配置を有するが、MEMS構造に関しては同一の構造を有する。

【0010】

次に第1および第2のセンサ素子の電気信号入出力電極がポリシリコン膜(連結部)によって架橋配線される。このポリシリコン膜は、上記のMEMS構造の形成と同時に、あるいは引き続いて、同様の形成技術によって形成することができる。

【0011】

次に基板のうち第2のセンサ素子の直下の部分の膜厚が、異方性ドライエッチングや異方性ウエットエッチングなどの加工技術によって薄くされる。続いて同様の加工技術によって、基板のうち第2のセンサ素子の周囲の部分が完全に除去される。この除去によって、基板は、第1および第2のセンサ素子のそれぞれを支持する第1および第2の部分に分割される。この第1の部分は、エッチングによって除去された領域を介して第2の部分と対向する側面を有する。

【0012】

次に、この側面または第2の部分の底面の少なくともいずれかに接着材が塗布される。次に架橋配線が弾力性に富むことを利用して、架橋配線が折り曲げられる。これにより第1の部分の側面上に、第2の部分の裏面が固定される。この折り曲げ操作により、第2のセンサ素子の力学量検出方向は、第1のセンサ素子の検出方向と異なる方向(第2の方向)とされる。これにより、第1および第2の方向に関して力学量を検出することができる構成が得られる。

【0013】

次に基板のダイシングが行なわれる。これにより、最初に多数のセンサ素子が形成された1つの基板から、多数のセンサ装置が切り出される。このセンサ装置は、必要に応じて、リードフレームにダイボンドされ、ワイヤボンドされ、最後にモールド樹脂により封止される。

【0014】

上記の製造工程において、前半のウエハレベル工程はMEMS技術を用いたバッチ処理によって、また後半の組立工程はIC(Integrated Circuit)チップと同じ組立設備によって行なうことができる。

【0015】

なお上記のエッチングが異方性ドライエッチングの場合には、エッチングによって基板表面と直交する側面が形成されるので、第1および第2のセンサ素子の検出軸は互いに直交する。

【0016】

また上記製造工程の初期段階において基板上に形成される多数のセンサ素子は、第3のセンサ素子を含んでもよい。この場合、第2および第3のセンサ素子の各々は、平面視において、第1のセンサ素子からの方位が直交するように配置されることが好ましい。この第3のセンサ素子の検出軸が上述した折り曲げ操作と同様の方法によって変化されることで、3軸センサを得ることができる。

【0017】

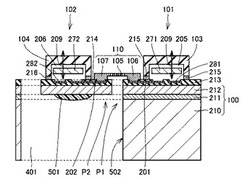

次に本実施の形態におけるセンサ装置の構成について説明する。図1は、本発明の実施の形態1におけるセンサ装置の構成を概略的に示す平面図である。図2は、図1の線II−IIに沿った概略断面図である。

【0018】

図1および図2を参照して、本実施の形態のセンサ装置は、第1検出軸AX1および第2検出軸AX2の2つの検出軸を有する多軸加速度センサチップ801である。多軸加速度センサチップ801(センサ装置)は、主に、SOI(Silicon On Insulator)基板100と、第1および第2の加速度センサ101、102(第1および第2のセンサ素子)と、連結部110と、接続パッド108とを有する。

【0019】

第1の加速度センサ101は、SOI基板100の主面(図2の上面)上に形成されている。第2の加速度センサ102は、SOI基板100の側面(図2の左面)上に接着材501によって固定されている。第1および第2の加速度センサ101、102のそれぞれは、第1および第2検出軸AX1、AX2に沿った加速度を検出する機能を有する。第1検出軸AX1はSOI基板100の主面に垂直な方向を有する。第2検出軸AX2は第1検出軸AX1と直交している。

【0020】

第1の加速度センサ101は、固定電極281と、可動電極271と、ガラスキャップ103と、ポリシリコン配線201とを有する。固定電極281はSOI基板100上に設けられている。可動電極271は、固定電極281と間隔を介して対向しており、かつ第1検出軸AX1に沿った加速度に応じて第1検出軸AX1に沿って変位する構成を有する。この構成により、固定電極281と可動電極271との間の静電容量を測定することで、第1検出軸AX1方向の加速度を検出することができる。

【0021】

第2の加速度センサ102は、固定電極282と、可動電極272と、ガラスキャップ104と、ポリシリコン配線202とを有する。固定電極282はSOI基板100上に設けられている。可動電極272は、固定電極282と間隔を介して対向しており、かつ第2検出軸AX2に沿った加速度に応じて第2検出軸AX2に沿って変位する構成を有する。この構成により、固定電極282と可動電極272との間の静電容量を測定することで、第2検出軸AX2方向の加速度を検出することができる。第2の加速度センサ102のガラスキャップ104内における構造は、ポリシリコン配線の引き回し、および検出軸の向きを除いて、第1の加速度センサ101のガラスキャップ103内における構造と同一の構造を有する。

【0022】

連結部110は、ポリシリコン架橋配線105と、ポリシリコンパッド106、107とを有する。ポリシリコンパッド106、107のそれぞれは、第1および第2の加速度センサ101、102の側に配置されている。ポリシリコン架橋配線105はポリシリコンパッド106および107を架橋している。連結部110は、第1および第2の加速度センサ101、102を互いに連結することで、第1および第2の加速度センサ101、102を互いに電気的に接続している。

【0023】

接続パッド108は、SOI基板100上に設けられている。接続パッド108は、第1および第2の加速度センサ101、102を、ASIC(Application Specific Integrated Circuit)などの外部機器と接続するためのものである。接続パッド108と第1の加速度センサ101との間は、SOI基板100の主面上の配線によって電気的に接続されている。また接続パッド108と第2の加速度センサとの間は、SOI基板100の主面上の配線と連結部110とによって電気的に接続されている。接続パッド108は、ポリシリコンパッド上に形成されたクロムや金などのフッ酸に耐久性のある金属薄膜であり、蒸着法やスパッタ法によって形成することができる。

【0024】

本実施の形態の多軸加速度センサチップ801は、SOI基板を用いた通常のICチップと同様に、SOI基板100と、この半導体基板の主面上に形成された接続パッド108とを有している。これにより多軸加速度センサチップ801は、通常のICチップと同様に取り扱うことができる。具体的には、たとえばリードフレームを取り付けることや、さらに樹脂モールドを用いてパッケージングすることが、通常のICと同様に可能である。

【0025】

なおガラスキャップ103および104のそれぞれは、ポリシリコン部215および216を介して絶縁膜213上に配置されている。ガラスキャップ103および104のそれぞれは、陽極接合境界面で周囲環境から完全に遮断されたキャビティ205および206を有し、第1および第2の加速度センサ101および102の可動構造体を気密封止している。

【0026】

SOI基板100は、単結晶シリコン部210と、埋込酸化膜211と、SOI層212とを有する。シリコン層212の表面の一部、すなわちSOI基板100の主面の一部は、必要に応じて絶縁膜213によって被覆されている。SOI層212の厚さはガラスキャップ103、104の各々の厚さと同じであることが好ましく、典型的には約300μmである。

【0027】

ポリシリコン配線201および202のそれぞれは、ガラスキャップ103および104内部の可動構造体と外部とを電気的に接続するように、ポリシリコン部215および216の直下を横断している。またポリシリコン配線201、202は、絶縁膜213に埋め込まれることで、周囲から電気的に絶縁分離されている。絶縁膜213は、たとえば上層窒化膜と下層酸化膜とからなる二層構造を有する。

【0028】

絶縁膜214は、ポリシリコン配線201および202のそれぞれとポリシリコン部215および216との間を絶縁するように設けられている。絶縁膜214は、たとえば上層が窒化膜、下層が酸化膜からなる二層構造を有する。

【0029】

次に多軸加速度センサチップ801の製造方法について説明する。図3は、本発明の実施の形態1におけるセンサ装置の製造方法の第1工程を概略的に示す部分平面図である。また図4は、図3の線IV−IVに沿った概略的な部分断面図である。図5〜図7のそれぞれは、本発明の実施の形態1におけるセンサ装置の製造方法の第2〜第4工程を概略的に示す部分断面図である。図8は、本発明の実施の形態1におけるセンサ装置の製造方法の第5工程を概略的に示す部分平面図である。また図9は、図8の線IX−IXに沿った概略的な部分断面図である。図10は、本発明の実施の形態1におけるセンサ装置の製造方法の第6工程を概略的に示す部分平面図である。また図11は、図10の線XI−XIに沿った概略的な部分断面図である。

【0030】

図3および図4を参照して、SOI基板100上に第1および第2の加速度センサ101、102を含む多数の加速度センサが、MEMS製造技術により形成される。第1の加速度センサ101および第2の加速度センサ102は、ポリシリコンで構成された同一寸法、同一形状の可動構造体を有し、かつ一の方向209に沿った検出軸を有する。

【0031】

この可動構造体を保護するために、ガラスキャップ103、104が公知の陽極接合技術によりSOI基板100と接合される。具体的には、まずウエハ形状のガラス板上に、フッ酸によるウエットエッチングやサンドブラストによる物理機械的加工により、可動構造体が収納可能な凹状の窪みが形成される。このガラス板がSOI基板100上に陽極接合される。そしてガラス板の不要部位が、たとえば回転刃を有するダイサーを用いて切除される。これにより、ガラス板からガラスキャップ103および104の各々が切り出される。

【0032】

また第1および第2の加速度センサ101、102を互いに連結するように、連結部110が形成される。具体的には、まず第1の加速度センサ101の第2の加速度センサ102側にポリシリコンパッド106が形成され、第2の加速度センサ102の第1の加速度センサ101側にポリシリコンパッド107が形成される。次にポリシリコンパッド106と107とがポリシリコン架橋配線105によって結線される。導電性を有するポリシリコンからなる連結部110により連結されることで、第1および第2の加速度センサ101、102は互いに電気的に接続される。

【0033】

図5を参照して、第1および第2の加速度センサ101、102と、連結部110とを保護するための、厚いホトレジスト層901が塗布法により形成される。またSOI基板100の裏面(図5の下面)上にもホトレジスト層902が形成される。次に表側のパターンを基準に裏面側を写真製版することが可能ないわゆる両面露光器を使用して、ホトレジスト層902が露光される。続いてホトレジスト層902の現像によって、ホトレジスト層902のうち、第2の加速度センサ102に相当する領域およびそれを取り囲む領域が除去される。この現像によりパターニングされたホトレジスト層902をホトレジストマスクとして、単結晶シリコン部210が異方性ドライエッチングにより除去される。このエッチングにより単結晶シリコン部210に貫通孔401が形成される。このエッチングの際、SOI基板100中の埋込酸化膜211をエッチングストッパとして用いることができる。次にホトレジスト層901、902が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0034】

図6を参照して、ホトレジスト層901(図5)と同様のホトレジスト層903が形成される。またSOI基板100の裏面(図6の下面)上にもホトレジスト層904が形成される。この時すでにSOI基板100裏面には単結晶シリコン部210の厚さに相当する深い穴が形成されているので、スピンコート方式によってホトレジストを均一に塗布することは困難である。そのためホトレジスト層904の形成は、段差の激しい部位に塗布が可能であるスプレー方式により行なわれることが好ましい。次に両面露光器を使用してホトレジスト層904が露光される。続いてホトレジスト層904の現像によって、ホトレジスト層904のうち第2の加速度センサ102を取り囲む領域が除去される。

【0035】

図7を参照して、上記除去によりパターニングされたホトレジスト層904をホトレジストマスクとして、埋込酸化膜211およびSOI層212が異方性ドライエッチングによりリング状に除去される。このエッチングの際、絶縁膜213をエッチングストッパとして用いることができる。次にホトレジスト層903、904が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0036】

図8および図9を参照して、絶縁膜213の露出部が除去される。具体的には、まずウエハ全体(図7に示す構造全体)がフッ酸液に浸漬されることで、絶縁膜213の下層酸化膜が除去される。次に軽いドライエッチングにより絶縁膜213の上層窒化膜が除去される。第2の加速度センサ102は、ポリシリコン架橋配線105によって支持されることで、貫通孔401の上方に浮いた状態とされる。

【0037】

なお上記のフッ酸液への浸漬の際において、ウエハ表面には窒化膜やポリシリコンやガラスキャップなどが露出しているが、ガラスキャップ以外はフッ酸に耐性があり、これらの材料で構成された露出部はフッ酸による酸化膜エッチング中にエッチングされることはない。また接続パッド108はフッ酸に耐性があるのでエッチングされることはない。一方、ガラスキャップはフッ酸でエッチングされてしまうが、その厚さを十分に大きくすればエッチングによる厚さの減少は無視することができる。たとえば、絶縁膜213の下層酸化膜の厚さは概略1〜2μm程度とされ、ガラスキャップの厚さは概略300μm程度とされる。

【0038】

またポリシリコン架橋配線105は窒化膜とのエッチング選択比に乏しいポリシリコン膜からなるので、上記の軽いエッチングの際に膜厚が減少する。しかし、絶縁膜213の上層窒化膜の厚さを十分薄くすることにより、ポリシリコン架橋配線105の膜厚の減少は無視することができる。たとえば、絶縁膜213の上層窒化膜の厚さは約0.2μmとされる。

【0039】

上記の一連のエッチングによって、図9に示すように、SOI基板100は、第1の加速度センサ101を支持する第1の部分P1と、第2の加速度センサ102を支持する第2の部分P2とに分割される。

【0040】

次にウエハ(図9に示す構造)が反転され、貫通孔401を通じてSOI層212上に、たとえば導電性ペーストからなる接着材501が塗布される。この塗布は、たとえばディスペンサを用いて行なうことができる。次にこのウエハが再度反転される。

【0041】

図10および図11を参照して、ポリシリコン架橋配線105の弾力性を利用してポリシリコン架橋配線105がウエハの表側(図11の上側)から押し曲げられる。これにより第2の加速度センサ102は、第1の加速度センサ101に対して向きを変えながら貫通孔401に入れられ、SOI基板側面502に貼り付けられる。この結果、第1および第2の加速度センサのそれぞれの検出軸は互いに直交化される。

【0042】

次にダイシングライン701(図10)に沿ってウエハが切断されることで、多軸加速度センサチップ801(図1および図2)が切り出される。

【0043】

本実施の形態によれば、第1の加速度センサ101に対する第2の加速度センサ102の向きを連結部110を曲げるだけで変えることができる。このため、第1および第2検出軸AX1、AX2に対応する多軸方向に関する検出が可能な小型の多軸加速度センサチップ801の製造コストを低減することができる。

【0044】

また図5に示すように、SOI基板100の埋込酸化膜211をエッチングストッパとして用いることができる。これにより第2の部分P2(図9)の厚さを安定化することができる。よって、第1および第2の部分P1、P2を接着材501を用いて貼り付ける条件が安定化されるので製造効率が向上する。

【0045】

また第2の加速度センサ102の周囲のシリコンをエッチングで除く作業は、裏面側(図5〜図7における下面側)からのみ実施される。これにより、ポリシリコン架橋配線105がエッチングによって損傷することを防止することができる。

【0046】

(実施の形態2)

図12は、本発明の実施の形態2におけるセンサ装置の構成を概略的に示す断面図である。図12を参照して、本実施の形態の多軸加速度センサチップ802は、実施の形態1におけるSOI基板100(図2)の代わりにシリコン基板200を有する。

【0047】

図13〜図16のそれぞれは、本発明の実施の形態2におけるセンサ装置の製造方法の第1〜4工程を概略的に示す部分断面図である。

【0048】

図13を参照して、シリコン基板200上に、実施の形態1と同様の工程(図4)によって第1および第2の加速度センサ101、102が形成される。

【0049】

図14を参照して、実施の形態1と同様の工程(図5)によって、ホトレジスト層901、902が形成される。次にホトレジスト層902をホトレジストマスクとして、異方性ドライエッチングによりシリコン基板200が所定の時間エッチングされる。これによりホトレジストマスクの露出部においてシリコン基板200の厚さがガラスキャップの厚さ(たとえば300μm)と同程度にまで薄くされる。次にホトレジスト層901、902が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0050】

図15を参照して、実施の形態1と同様の工程(図6)によって、ホトレジスト層903、904が形成される。

【0051】

図16を参照して、ホトレジスト層904をホトレジストマスクとして、シリコン基板200が異方性ドライエッチングによりリング状に除去される。このエッチングの際、絶縁膜213をエッチングストッパとして用いることができる。次にホトレジスト層903、904が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0052】

次に、実施の形態1と同様の工程(図8〜図11)によって、本実施の多軸加速度センサチップ802が製造される。

【0053】

なお、上記以外の構成については、上述した実施の形態1の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0054】

本実施の形態によれば、SOI基板に比してより安価なシリコン基板200を用いて多軸加速度センサチップ802を製造することができる。

【0055】

(実施の形態3)

図17は、本発明の実施の形態3におけるセンサ装置の構成を概略的に示す断面図である。図17を参照して、本実施の形態の多軸加速度センサチップ803は、実施の形態2における連結部110の代わりに金メッキ架橋配線1301を有する。

【0056】

図18および図19のそれぞれは、本発明の実施の形態3におけるセンサ装置の製造方法の第1および第2工程を概略的に示す部分断面図である。

【0057】

図18を参照して、第1および第2の加速度センサ101、102の形成後、かつ金メッキ架橋配線1301(図17)の形成前に、第2の加速度センサ102の周囲の絶縁膜213がホトレジストマスク(図示せず)を用いた写真製版技術によってリング状に除去される。これによりシリコン基板200の主面(図18の上面)の一部が露出する。次にホトレジストマスクが除去される。

【0058】

次に上記の露出したシリコンを除く部分を写真製版により新たなホトレジスト層で厚く保護した後、表側(図18の上面側)からシリコン基板200の異方性ドライエッチングが行なわれる。これにより第2の加速度センサ102の周囲においてリング状の溝1201が形成される。

【0059】

次に溝1201の一部がホトレジスト層1202によって埋め込まれる。ホトレジスト層1202の厚さは概略200μm以上である。

【0060】

なお上記のシリコン基板200のエッチングにおいて、シリコン基板200が単結晶のシリコン基板の場合には、ガラスキャップの厚み(概略300μm)程度の深さまでシリコンがエッチングされるようエッチング時間が設定される。またシリコン基板200がSOI基板の場合には、SOI層の厚み分エッチングしたところで埋め込み酸化膜が露出し、そこでエッチングが自動的にストップする。

【0061】

図19を参照して、ポリシリコンパッド上に蒸着法やスパッタ法でクロム薄膜が形成され、その上にシード層として金薄膜が蒸着法やスパッタ法で形成され、さらにメッキ法により厚さ数十μmの金メッキ膜が形成される。これにより第1および第2の加速度センサ101、102を互いに連結し、かつポリシリコン配線201および202を互いに電気的に接続する金メッキ架橋配線1301が形成される。

【0062】

次に実施の形態1または実施の形態2と同様に、裏側(図19の下面側)からシリコン基板200の一部が異方性ドライエッチングで除去される。エッチング面が溝1201の底に到達した時点でエチングが停止される。このエッチングによって、ホトレジスト層1202が露出する。次にこのホトレジスト層1202が酸素プラズマを用いたレジストアッシャによって灰化されることで除去される。

【0063】

こうして、第2の加速度センサ102が第1の加速度センサ101に金メッキ架橋配線1301を介して支えられて宙吊りにされた構成が得られる。以降の製造過程は、すでに説明した実施の形態1または実施の形態2と同様である。

【0064】

以上により本実施の形態の多軸加速度センサチップ803(図17)が得られる。

なお、上記以外の構成については、上述した実施の形態1または2の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0065】

本実施の形態によれば、深い凹部内にホトレジスト層を形成することで写真製版を行なうという技術的に難易度の高い工程(たとえば図15に示す工程)が不要となる。よって、より容易にセンサ装置を製造することができる。

【0066】

また金メッキ架橋配線1301は、金を含むので曲げられても破損しにくい。また金メッキ架橋配線1301は、図19に示すように溝1201の部分で大きく湾曲した形で形成されるが、最終的には図17に示すように引き延ばして用いることができる。

【0067】

(実施の形態4)

上記の実施の形態1〜3においては、第1の加速度センサ101を支持する基板が、第2の加速度センサ102を支持する基板の支持台とされている。すなわち第1の部分P1(図9)の側面502上に第2の部分P2が貼り付けられる。一方、本実施の形態においては、第1の加速度センサ101を支持する基板と、第2の加速度センサ102を支持する基板との両方を支持する支持台が別途設けられる。

【0068】

図20は、本発明の実施の形態4におけるセンサ装置の構成を概略的に示す断面図である。図20を参照して、本実施の形態の多軸加速度センサチップ804は、支持台1700を有する。この支持台1700に、連結部110によって互いに連結された第1および第2の加速度センサ101、102が貼り付けられている。

【0069】

図21および図22のそれぞれは、本発明の実施の形態4におけるセンサ装置の製造方法の第1および第2工程を概略的に示す部分断面図である。

【0070】

図21を参照して、まず実施の形態2と同様に、シリコン基板200上に第1および第2の加速度センサ101、102が形成される。その後、裏面を研削することで、シリコン基板200の厚さがガラスキャップの厚さと同じ概略300μmとされる。続いてシリコン基板200の表面および裏面のそれぞれにホトレジスト層905および906が塗布される。次に両面露光器を使用してホトレジスト層906が露光される。続いてホトレジスト層906の現像によって、ホトレジスト層906のうち第2の加速度センサ102を取り囲む領域が除去される。

【0071】

パターニングされたホトレジスト層906をホトレジストマスクとして、シリコン基板200が異方性ドライエッチングによりリング状に除去される。このエッチングの際、絶縁膜213をエッチングストッパとして用いることができる。このエッチングによって、シリコン基板200にリング状の貫通孔402が形成される。

【0072】

次にホトレジスト層905、906が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。次に実施の形態1と同様の工程(図8および図9)によって、絶縁膜213の露出部が除去される。

【0073】

上記の一連の加工によって、シリコン基板200は、第1の加速度センサ101を支持する第1の部分Q1と、第2の加速度センサ102を支持する第2の部分Q2とに分割される。すなわち、第2の加速度センサ102は、ポリシリコン架橋配線105によって支持されることで、貫通孔402内において浮いた状態とされる。次に、ダイシングライン701(図10)に沿ってダイシングが行なわれる。

【0074】

図22を参照して、上記のダイシングによって、連結部110のみによって互いに連結された第1および第2の加速度センサ101、102からなる部材が切り出される。この切り出された部材は専用のトレイにいったん収納される。また支持台1700の上面および側面の各々に導電性ペーストなどの接着材501が塗布される。

【0075】

次にガラスキャップ103および104の両方の天面が真空吸着コレットなどの吸着治具によって保持され、支持台1700の近くに搬送される。次に第1の加速度センサ101が支持台1700の上面に接着材501を介して貼り付けられる。これにより第2の加速度センサは、連結部110によって中空に支持される。

【0076】

次に連結部110のポリシリコン架橋配線105の弾力性を利用してポリシリコン架橋配線105が押し曲げられる。これにより第2の加速度センサ102は、第1の加速度センサ101に対して向きを変え、支持台1700の側面に接着材501を介して貼り付けられる。この結果、第1および第2の加速度センサ101、102のそれぞれの検出軸は互いに直交化される。

【0077】

以上により本実施の形態の多軸加速度センサチップ804が製造される。

なお、上記以外の構成については、上述した実施の形態2の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0078】

また連結部110の代わりに金メッキ架橋配線1301が用いられてもよい。

本実施の形態によれば、シリコン基板200の裏面からのエッチングの回数を1回のみとすることができるので、エッチング工程を簡略化することができる。

【0079】

また支持台1700の形状を自由に選択することができる。

また第1および第2の加速度センサ101、102の間は、連結部110によって電気的に接続されている。これにより支持台1700に配線構造を形成しておく必要がない。

【0080】

また多軸加速度センサチップ804は、通常のICチップと同様の取り扱いが可能である。

【0081】

なお上記の各実施の形態においては、製造方法の初期段階において基板の主面に垂直な方向209を(図4)を検出軸とするセンサ素子が基板上に形成されるが、本発明はこれに限定されるものではなく、たとえば基板の主面内の方向を検出軸とするセンサ素子が形成されてもよい。

【0082】

また上記の各実施の形態においては力学量センサについて説明したが、本発明はこれに限定されるものではなく、電磁波センサ、音波センサ、超音波センサ、磁界センサなどに適用することもできる。

【0083】

今回開示された各実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることを意図される。

【産業上の利用可能性】

【0084】

本発明は複数のセンサ素子を有するセンサ装置に特に有利に適用され得る。

【図面の簡単な説明】

【0085】

【図1】本発明の実施の形態1におけるセンサ装置の構成を概略的に示す平面図である。

【図2】図1の線II−IIに沿った概略断面図である。

【図3】本発明の実施の形態1におけるセンサ装置の製造方法の第1工程を概略的に示す部分平面図である。

【図4】図3の線IV−IVに沿った概略的な部分断面図である。

【図5】本発明の実施の形態1におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【図6】本発明の実施の形態1におけるセンサ装置の製造方法の第3工程を概略的に示す部分断面図である。

【図7】本発明の実施の形態1におけるセンサ装置の製造方法の第4工程を概略的に示す部分断面図である。

【図8】本発明の実施の形態1におけるセンサ装置の製造方法の第5工程を概略的に示す部分平面図である。

【図9】図8の線IX−IXに沿った概略的な部分断面図である。

【図10】本発明の実施の形態1におけるセンサ装置の製造方法の第6工程を概略的に示す部分平面図である。

【図11】図10の線XI−XIに沿った概略的な部分断面図である。

【図12】本発明の実施の形態2におけるセンサ装置の構成を概略的に示す断面図である。

【図13】本発明の実施の形態2におけるセンサ装置の製造方法の第1工程を概略的に示す部分断面図である。

【図14】本発明の実施の形態2におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【図15】本発明の実施の形態2におけるセンサ装置の製造方法の第3工程を概略的に示す部分断面図である。

【図16】本発明の実施の形態2におけるセンサ装置の製造方法の第4工程を概略的に示す部分断面図である。

【図17】本発明の実施の形態3におけるセンサ装置の構成を概略的に示す断面図である。

【図18】本発明の実施の形態3におけるセンサ装置の製造方法の第1工程を概略的に示す部分断面図である。

【図19】本発明の実施の形態3におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【図20】本発明の実施の形態4におけるセンサ装置の構成を概略的に示す断面図である。

【図21】本発明の実施の形態4におけるセンサ装置の製造方法の第1工程を概略的に示す部分断面図である。

【図22】本発明の実施の形態4におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【符号の説明】

【0086】

AX1 第1検出軸、AX2 第2検出軸、P1,Q1 第1の部分、P2,Q2 第2の部分、100 SOI基板、101 第1の加速度センサ(第1のセンサ素子)、102 第2の加速度センサ(第2のセンサ素子)、103,104 ガラスキャップ、105 ポリシリコン架橋配線、106,107 ポリシリコンパッド、108 接続パッド、200 シリコン基板、210 単結晶シリコン部、211 埋込酸化膜、212 SOI層、501 接着材、801〜804 多軸加速度センサチップ(センサ装置)、1301 金メッキ架橋配線、1700 支持台。

【技術分野】

【0001】

本発明は、複数のセンサ素子を有するセンサ装置の製造方法に関するものである。

【背景技術】

【0002】

たとえば自動車のエアバッグシステムにおいて、多軸方向の加速度を検出するためのセンサが用いられている。このような多軸力学量検出センサは、X、Yの2軸方向、あるいはX、Y、Zの3軸方向の力学量の検出を1つのセンサで行なうことができる。よって限られたスペースにおいて多軸方向の力学量を検出する必要がある場合に、多軸力学量センサは特に好適に用いられる。

【0003】

このようなセンサの製造方法は、たとえば、特開2003−28646号公報に開示されている。この公報によれば、まず複数のセンサブロックの各々に半導体センサの素子が設けられる。次に複数のセンサブロックが互いに固定されることで、多軸半導体センサが形成される。

【特許文献1】特開2003−28646号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記の公報の技術において多軸半導体センサ(センサ装置)を十分に小型化しようとすると、センサ素子の大きさとほとんど同程度までセンサブロックを小さくする必要がある。このように微細な複数のセンサブロックを互いに固定する工程は、煩雑であり、また通常の半導体製造装置と異なる専用の組立装置を必要とする。このため上記従来の技術では、センサ装置の製造コストが高くなるという問題があった。

【0005】

本発明は、上記課題に鑑みてなされたものであり、本発明の目的は、多軸方向に関する検出が可能な小型のセンサ装置の製造コストを低減することができる製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明のセンサ装置の製造方法は、以下の工程を有する。

連結部によって互いに連結された第1および第2のセンサ素子が基板上に形成される。第1および第2のセンサ素子のそれぞれを支持する第1および第2の部分に基板が分割される。この分割の後に、連結部を曲げながら第1のセンサ素子に対して第2のセンサ素子の向きが変えられる。

【発明の効果】

【0007】

本発明のセンサ装置によれば、装置が小型であっても、第1のセンサ素子に対する第2のセンサ素子の向きを連結部を曲げるだけで変えることができる。このため、多軸方向に関する検出が可能な小型のセンサ装置の製造コストを低減することができる。

【発明を実施するための最良の形態】

【0008】

以下、本発明の実施の形態について図に基づいて説明する。

(実施の形態1)

はじめに本実施の形態におけるセンサ装置としての多軸加速度センサチップの製造方法の概要について説明する。

【0009】

まずMEMS(Micro Electro Mechanical Systems)製造技術により、1軸方向の力学量を検出することができる構成を有するセンサ素子が、検出軸の方向が同一の方向(第1の方向)となるように基板表面上に多数形成される。この多数のセンサ素子は、特定の基準チップ(第1のセンサ素子)と、この基準チップの周囲に配置されたチップ(第2のセンサ素子)とを含む。第1および第2のセンサ素子は、電気信号の入出力電極に関して異なる配置を有するが、MEMS構造に関しては同一の構造を有する。

【0010】

次に第1および第2のセンサ素子の電気信号入出力電極がポリシリコン膜(連結部)によって架橋配線される。このポリシリコン膜は、上記のMEMS構造の形成と同時に、あるいは引き続いて、同様の形成技術によって形成することができる。

【0011】

次に基板のうち第2のセンサ素子の直下の部分の膜厚が、異方性ドライエッチングや異方性ウエットエッチングなどの加工技術によって薄くされる。続いて同様の加工技術によって、基板のうち第2のセンサ素子の周囲の部分が完全に除去される。この除去によって、基板は、第1および第2のセンサ素子のそれぞれを支持する第1および第2の部分に分割される。この第1の部分は、エッチングによって除去された領域を介して第2の部分と対向する側面を有する。

【0012】

次に、この側面または第2の部分の底面の少なくともいずれかに接着材が塗布される。次に架橋配線が弾力性に富むことを利用して、架橋配線が折り曲げられる。これにより第1の部分の側面上に、第2の部分の裏面が固定される。この折り曲げ操作により、第2のセンサ素子の力学量検出方向は、第1のセンサ素子の検出方向と異なる方向(第2の方向)とされる。これにより、第1および第2の方向に関して力学量を検出することができる構成が得られる。

【0013】

次に基板のダイシングが行なわれる。これにより、最初に多数のセンサ素子が形成された1つの基板から、多数のセンサ装置が切り出される。このセンサ装置は、必要に応じて、リードフレームにダイボンドされ、ワイヤボンドされ、最後にモールド樹脂により封止される。

【0014】

上記の製造工程において、前半のウエハレベル工程はMEMS技術を用いたバッチ処理によって、また後半の組立工程はIC(Integrated Circuit)チップと同じ組立設備によって行なうことができる。

【0015】

なお上記のエッチングが異方性ドライエッチングの場合には、エッチングによって基板表面と直交する側面が形成されるので、第1および第2のセンサ素子の検出軸は互いに直交する。

【0016】

また上記製造工程の初期段階において基板上に形成される多数のセンサ素子は、第3のセンサ素子を含んでもよい。この場合、第2および第3のセンサ素子の各々は、平面視において、第1のセンサ素子からの方位が直交するように配置されることが好ましい。この第3のセンサ素子の検出軸が上述した折り曲げ操作と同様の方法によって変化されることで、3軸センサを得ることができる。

【0017】

次に本実施の形態におけるセンサ装置の構成について説明する。図1は、本発明の実施の形態1におけるセンサ装置の構成を概略的に示す平面図である。図2は、図1の線II−IIに沿った概略断面図である。

【0018】

図1および図2を参照して、本実施の形態のセンサ装置は、第1検出軸AX1および第2検出軸AX2の2つの検出軸を有する多軸加速度センサチップ801である。多軸加速度センサチップ801(センサ装置)は、主に、SOI(Silicon On Insulator)基板100と、第1および第2の加速度センサ101、102(第1および第2のセンサ素子)と、連結部110と、接続パッド108とを有する。

【0019】

第1の加速度センサ101は、SOI基板100の主面(図2の上面)上に形成されている。第2の加速度センサ102は、SOI基板100の側面(図2の左面)上に接着材501によって固定されている。第1および第2の加速度センサ101、102のそれぞれは、第1および第2検出軸AX1、AX2に沿った加速度を検出する機能を有する。第1検出軸AX1はSOI基板100の主面に垂直な方向を有する。第2検出軸AX2は第1検出軸AX1と直交している。

【0020】

第1の加速度センサ101は、固定電極281と、可動電極271と、ガラスキャップ103と、ポリシリコン配線201とを有する。固定電極281はSOI基板100上に設けられている。可動電極271は、固定電極281と間隔を介して対向しており、かつ第1検出軸AX1に沿った加速度に応じて第1検出軸AX1に沿って変位する構成を有する。この構成により、固定電極281と可動電極271との間の静電容量を測定することで、第1検出軸AX1方向の加速度を検出することができる。

【0021】

第2の加速度センサ102は、固定電極282と、可動電極272と、ガラスキャップ104と、ポリシリコン配線202とを有する。固定電極282はSOI基板100上に設けられている。可動電極272は、固定電極282と間隔を介して対向しており、かつ第2検出軸AX2に沿った加速度に応じて第2検出軸AX2に沿って変位する構成を有する。この構成により、固定電極282と可動電極272との間の静電容量を測定することで、第2検出軸AX2方向の加速度を検出することができる。第2の加速度センサ102のガラスキャップ104内における構造は、ポリシリコン配線の引き回し、および検出軸の向きを除いて、第1の加速度センサ101のガラスキャップ103内における構造と同一の構造を有する。

【0022】

連結部110は、ポリシリコン架橋配線105と、ポリシリコンパッド106、107とを有する。ポリシリコンパッド106、107のそれぞれは、第1および第2の加速度センサ101、102の側に配置されている。ポリシリコン架橋配線105はポリシリコンパッド106および107を架橋している。連結部110は、第1および第2の加速度センサ101、102を互いに連結することで、第1および第2の加速度センサ101、102を互いに電気的に接続している。

【0023】

接続パッド108は、SOI基板100上に設けられている。接続パッド108は、第1および第2の加速度センサ101、102を、ASIC(Application Specific Integrated Circuit)などの外部機器と接続するためのものである。接続パッド108と第1の加速度センサ101との間は、SOI基板100の主面上の配線によって電気的に接続されている。また接続パッド108と第2の加速度センサとの間は、SOI基板100の主面上の配線と連結部110とによって電気的に接続されている。接続パッド108は、ポリシリコンパッド上に形成されたクロムや金などのフッ酸に耐久性のある金属薄膜であり、蒸着法やスパッタ法によって形成することができる。

【0024】

本実施の形態の多軸加速度センサチップ801は、SOI基板を用いた通常のICチップと同様に、SOI基板100と、この半導体基板の主面上に形成された接続パッド108とを有している。これにより多軸加速度センサチップ801は、通常のICチップと同様に取り扱うことができる。具体的には、たとえばリードフレームを取り付けることや、さらに樹脂モールドを用いてパッケージングすることが、通常のICと同様に可能である。

【0025】

なおガラスキャップ103および104のそれぞれは、ポリシリコン部215および216を介して絶縁膜213上に配置されている。ガラスキャップ103および104のそれぞれは、陽極接合境界面で周囲環境から完全に遮断されたキャビティ205および206を有し、第1および第2の加速度センサ101および102の可動構造体を気密封止している。

【0026】

SOI基板100は、単結晶シリコン部210と、埋込酸化膜211と、SOI層212とを有する。シリコン層212の表面の一部、すなわちSOI基板100の主面の一部は、必要に応じて絶縁膜213によって被覆されている。SOI層212の厚さはガラスキャップ103、104の各々の厚さと同じであることが好ましく、典型的には約300μmである。

【0027】

ポリシリコン配線201および202のそれぞれは、ガラスキャップ103および104内部の可動構造体と外部とを電気的に接続するように、ポリシリコン部215および216の直下を横断している。またポリシリコン配線201、202は、絶縁膜213に埋め込まれることで、周囲から電気的に絶縁分離されている。絶縁膜213は、たとえば上層窒化膜と下層酸化膜とからなる二層構造を有する。

【0028】

絶縁膜214は、ポリシリコン配線201および202のそれぞれとポリシリコン部215および216との間を絶縁するように設けられている。絶縁膜214は、たとえば上層が窒化膜、下層が酸化膜からなる二層構造を有する。

【0029】

次に多軸加速度センサチップ801の製造方法について説明する。図3は、本発明の実施の形態1におけるセンサ装置の製造方法の第1工程を概略的に示す部分平面図である。また図4は、図3の線IV−IVに沿った概略的な部分断面図である。図5〜図7のそれぞれは、本発明の実施の形態1におけるセンサ装置の製造方法の第2〜第4工程を概略的に示す部分断面図である。図8は、本発明の実施の形態1におけるセンサ装置の製造方法の第5工程を概略的に示す部分平面図である。また図9は、図8の線IX−IXに沿った概略的な部分断面図である。図10は、本発明の実施の形態1におけるセンサ装置の製造方法の第6工程を概略的に示す部分平面図である。また図11は、図10の線XI−XIに沿った概略的な部分断面図である。

【0030】

図3および図4を参照して、SOI基板100上に第1および第2の加速度センサ101、102を含む多数の加速度センサが、MEMS製造技術により形成される。第1の加速度センサ101および第2の加速度センサ102は、ポリシリコンで構成された同一寸法、同一形状の可動構造体を有し、かつ一の方向209に沿った検出軸を有する。

【0031】

この可動構造体を保護するために、ガラスキャップ103、104が公知の陽極接合技術によりSOI基板100と接合される。具体的には、まずウエハ形状のガラス板上に、フッ酸によるウエットエッチングやサンドブラストによる物理機械的加工により、可動構造体が収納可能な凹状の窪みが形成される。このガラス板がSOI基板100上に陽極接合される。そしてガラス板の不要部位が、たとえば回転刃を有するダイサーを用いて切除される。これにより、ガラス板からガラスキャップ103および104の各々が切り出される。

【0032】

また第1および第2の加速度センサ101、102を互いに連結するように、連結部110が形成される。具体的には、まず第1の加速度センサ101の第2の加速度センサ102側にポリシリコンパッド106が形成され、第2の加速度センサ102の第1の加速度センサ101側にポリシリコンパッド107が形成される。次にポリシリコンパッド106と107とがポリシリコン架橋配線105によって結線される。導電性を有するポリシリコンからなる連結部110により連結されることで、第1および第2の加速度センサ101、102は互いに電気的に接続される。

【0033】

図5を参照して、第1および第2の加速度センサ101、102と、連結部110とを保護するための、厚いホトレジスト層901が塗布法により形成される。またSOI基板100の裏面(図5の下面)上にもホトレジスト層902が形成される。次に表側のパターンを基準に裏面側を写真製版することが可能ないわゆる両面露光器を使用して、ホトレジスト層902が露光される。続いてホトレジスト層902の現像によって、ホトレジスト層902のうち、第2の加速度センサ102に相当する領域およびそれを取り囲む領域が除去される。この現像によりパターニングされたホトレジスト層902をホトレジストマスクとして、単結晶シリコン部210が異方性ドライエッチングにより除去される。このエッチングにより単結晶シリコン部210に貫通孔401が形成される。このエッチングの際、SOI基板100中の埋込酸化膜211をエッチングストッパとして用いることができる。次にホトレジスト層901、902が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0034】

図6を参照して、ホトレジスト層901(図5)と同様のホトレジスト層903が形成される。またSOI基板100の裏面(図6の下面)上にもホトレジスト層904が形成される。この時すでにSOI基板100裏面には単結晶シリコン部210の厚さに相当する深い穴が形成されているので、スピンコート方式によってホトレジストを均一に塗布することは困難である。そのためホトレジスト層904の形成は、段差の激しい部位に塗布が可能であるスプレー方式により行なわれることが好ましい。次に両面露光器を使用してホトレジスト層904が露光される。続いてホトレジスト層904の現像によって、ホトレジスト層904のうち第2の加速度センサ102を取り囲む領域が除去される。

【0035】

図7を参照して、上記除去によりパターニングされたホトレジスト層904をホトレジストマスクとして、埋込酸化膜211およびSOI層212が異方性ドライエッチングによりリング状に除去される。このエッチングの際、絶縁膜213をエッチングストッパとして用いることができる。次にホトレジスト層903、904が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0036】

図8および図9を参照して、絶縁膜213の露出部が除去される。具体的には、まずウエハ全体(図7に示す構造全体)がフッ酸液に浸漬されることで、絶縁膜213の下層酸化膜が除去される。次に軽いドライエッチングにより絶縁膜213の上層窒化膜が除去される。第2の加速度センサ102は、ポリシリコン架橋配線105によって支持されることで、貫通孔401の上方に浮いた状態とされる。

【0037】

なお上記のフッ酸液への浸漬の際において、ウエハ表面には窒化膜やポリシリコンやガラスキャップなどが露出しているが、ガラスキャップ以外はフッ酸に耐性があり、これらの材料で構成された露出部はフッ酸による酸化膜エッチング中にエッチングされることはない。また接続パッド108はフッ酸に耐性があるのでエッチングされることはない。一方、ガラスキャップはフッ酸でエッチングされてしまうが、その厚さを十分に大きくすればエッチングによる厚さの減少は無視することができる。たとえば、絶縁膜213の下層酸化膜の厚さは概略1〜2μm程度とされ、ガラスキャップの厚さは概略300μm程度とされる。

【0038】

またポリシリコン架橋配線105は窒化膜とのエッチング選択比に乏しいポリシリコン膜からなるので、上記の軽いエッチングの際に膜厚が減少する。しかし、絶縁膜213の上層窒化膜の厚さを十分薄くすることにより、ポリシリコン架橋配線105の膜厚の減少は無視することができる。たとえば、絶縁膜213の上層窒化膜の厚さは約0.2μmとされる。

【0039】

上記の一連のエッチングによって、図9に示すように、SOI基板100は、第1の加速度センサ101を支持する第1の部分P1と、第2の加速度センサ102を支持する第2の部分P2とに分割される。

【0040】

次にウエハ(図9に示す構造)が反転され、貫通孔401を通じてSOI層212上に、たとえば導電性ペーストからなる接着材501が塗布される。この塗布は、たとえばディスペンサを用いて行なうことができる。次にこのウエハが再度反転される。

【0041】

図10および図11を参照して、ポリシリコン架橋配線105の弾力性を利用してポリシリコン架橋配線105がウエハの表側(図11の上側)から押し曲げられる。これにより第2の加速度センサ102は、第1の加速度センサ101に対して向きを変えながら貫通孔401に入れられ、SOI基板側面502に貼り付けられる。この結果、第1および第2の加速度センサのそれぞれの検出軸は互いに直交化される。

【0042】

次にダイシングライン701(図10)に沿ってウエハが切断されることで、多軸加速度センサチップ801(図1および図2)が切り出される。

【0043】

本実施の形態によれば、第1の加速度センサ101に対する第2の加速度センサ102の向きを連結部110を曲げるだけで変えることができる。このため、第1および第2検出軸AX1、AX2に対応する多軸方向に関する検出が可能な小型の多軸加速度センサチップ801の製造コストを低減することができる。

【0044】

また図5に示すように、SOI基板100の埋込酸化膜211をエッチングストッパとして用いることができる。これにより第2の部分P2(図9)の厚さを安定化することができる。よって、第1および第2の部分P1、P2を接着材501を用いて貼り付ける条件が安定化されるので製造効率が向上する。

【0045】

また第2の加速度センサ102の周囲のシリコンをエッチングで除く作業は、裏面側(図5〜図7における下面側)からのみ実施される。これにより、ポリシリコン架橋配線105がエッチングによって損傷することを防止することができる。

【0046】

(実施の形態2)

図12は、本発明の実施の形態2におけるセンサ装置の構成を概略的に示す断面図である。図12を参照して、本実施の形態の多軸加速度センサチップ802は、実施の形態1におけるSOI基板100(図2)の代わりにシリコン基板200を有する。

【0047】

図13〜図16のそれぞれは、本発明の実施の形態2におけるセンサ装置の製造方法の第1〜4工程を概略的に示す部分断面図である。

【0048】

図13を参照して、シリコン基板200上に、実施の形態1と同様の工程(図4)によって第1および第2の加速度センサ101、102が形成される。

【0049】

図14を参照して、実施の形態1と同様の工程(図5)によって、ホトレジスト層901、902が形成される。次にホトレジスト層902をホトレジストマスクとして、異方性ドライエッチングによりシリコン基板200が所定の時間エッチングされる。これによりホトレジストマスクの露出部においてシリコン基板200の厚さがガラスキャップの厚さ(たとえば300μm)と同程度にまで薄くされる。次にホトレジスト層901、902が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0050】

図15を参照して、実施の形態1と同様の工程(図6)によって、ホトレジスト層903、904が形成される。

【0051】

図16を参照して、ホトレジスト層904をホトレジストマスクとして、シリコン基板200が異方性ドライエッチングによりリング状に除去される。このエッチングの際、絶縁膜213をエッチングストッパとして用いることができる。次にホトレジスト層903、904が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。

【0052】

次に、実施の形態1と同様の工程(図8〜図11)によって、本実施の多軸加速度センサチップ802が製造される。

【0053】

なお、上記以外の構成については、上述した実施の形態1の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0054】

本実施の形態によれば、SOI基板に比してより安価なシリコン基板200を用いて多軸加速度センサチップ802を製造することができる。

【0055】

(実施の形態3)

図17は、本発明の実施の形態3におけるセンサ装置の構成を概略的に示す断面図である。図17を参照して、本実施の形態の多軸加速度センサチップ803は、実施の形態2における連結部110の代わりに金メッキ架橋配線1301を有する。

【0056】

図18および図19のそれぞれは、本発明の実施の形態3におけるセンサ装置の製造方法の第1および第2工程を概略的に示す部分断面図である。

【0057】

図18を参照して、第1および第2の加速度センサ101、102の形成後、かつ金メッキ架橋配線1301(図17)の形成前に、第2の加速度センサ102の周囲の絶縁膜213がホトレジストマスク(図示せず)を用いた写真製版技術によってリング状に除去される。これによりシリコン基板200の主面(図18の上面)の一部が露出する。次にホトレジストマスクが除去される。

【0058】

次に上記の露出したシリコンを除く部分を写真製版により新たなホトレジスト層で厚く保護した後、表側(図18の上面側)からシリコン基板200の異方性ドライエッチングが行なわれる。これにより第2の加速度センサ102の周囲においてリング状の溝1201が形成される。

【0059】

次に溝1201の一部がホトレジスト層1202によって埋め込まれる。ホトレジスト層1202の厚さは概略200μm以上である。

【0060】

なお上記のシリコン基板200のエッチングにおいて、シリコン基板200が単結晶のシリコン基板の場合には、ガラスキャップの厚み(概略300μm)程度の深さまでシリコンがエッチングされるようエッチング時間が設定される。またシリコン基板200がSOI基板の場合には、SOI層の厚み分エッチングしたところで埋め込み酸化膜が露出し、そこでエッチングが自動的にストップする。

【0061】

図19を参照して、ポリシリコンパッド上に蒸着法やスパッタ法でクロム薄膜が形成され、その上にシード層として金薄膜が蒸着法やスパッタ法で形成され、さらにメッキ法により厚さ数十μmの金メッキ膜が形成される。これにより第1および第2の加速度センサ101、102を互いに連結し、かつポリシリコン配線201および202を互いに電気的に接続する金メッキ架橋配線1301が形成される。

【0062】

次に実施の形態1または実施の形態2と同様に、裏側(図19の下面側)からシリコン基板200の一部が異方性ドライエッチングで除去される。エッチング面が溝1201の底に到達した時点でエチングが停止される。このエッチングによって、ホトレジスト層1202が露出する。次にこのホトレジスト層1202が酸素プラズマを用いたレジストアッシャによって灰化されることで除去される。

【0063】

こうして、第2の加速度センサ102が第1の加速度センサ101に金メッキ架橋配線1301を介して支えられて宙吊りにされた構成が得られる。以降の製造過程は、すでに説明した実施の形態1または実施の形態2と同様である。

【0064】

以上により本実施の形態の多軸加速度センサチップ803(図17)が得られる。

なお、上記以外の構成については、上述した実施の形態1または2の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0065】

本実施の形態によれば、深い凹部内にホトレジスト層を形成することで写真製版を行なうという技術的に難易度の高い工程(たとえば図15に示す工程)が不要となる。よって、より容易にセンサ装置を製造することができる。

【0066】

また金メッキ架橋配線1301は、金を含むので曲げられても破損しにくい。また金メッキ架橋配線1301は、図19に示すように溝1201の部分で大きく湾曲した形で形成されるが、最終的には図17に示すように引き延ばして用いることができる。

【0067】

(実施の形態4)

上記の実施の形態1〜3においては、第1の加速度センサ101を支持する基板が、第2の加速度センサ102を支持する基板の支持台とされている。すなわち第1の部分P1(図9)の側面502上に第2の部分P2が貼り付けられる。一方、本実施の形態においては、第1の加速度センサ101を支持する基板と、第2の加速度センサ102を支持する基板との両方を支持する支持台が別途設けられる。

【0068】

図20は、本発明の実施の形態4におけるセンサ装置の構成を概略的に示す断面図である。図20を参照して、本実施の形態の多軸加速度センサチップ804は、支持台1700を有する。この支持台1700に、連結部110によって互いに連結された第1および第2の加速度センサ101、102が貼り付けられている。

【0069】

図21および図22のそれぞれは、本発明の実施の形態4におけるセンサ装置の製造方法の第1および第2工程を概略的に示す部分断面図である。

【0070】

図21を参照して、まず実施の形態2と同様に、シリコン基板200上に第1および第2の加速度センサ101、102が形成される。その後、裏面を研削することで、シリコン基板200の厚さがガラスキャップの厚さと同じ概略300μmとされる。続いてシリコン基板200の表面および裏面のそれぞれにホトレジスト層905および906が塗布される。次に両面露光器を使用してホトレジスト層906が露光される。続いてホトレジスト層906の現像によって、ホトレジスト層906のうち第2の加速度センサ102を取り囲む領域が除去される。

【0071】

パターニングされたホトレジスト層906をホトレジストマスクとして、シリコン基板200が異方性ドライエッチングによりリング状に除去される。このエッチングの際、絶縁膜213をエッチングストッパとして用いることができる。このエッチングによって、シリコン基板200にリング状の貫通孔402が形成される。

【0072】

次にホトレジスト層905、906が酸素プラズマを用いたレジストアッシャにより灰化されることで除去される。次に実施の形態1と同様の工程(図8および図9)によって、絶縁膜213の露出部が除去される。

【0073】

上記の一連の加工によって、シリコン基板200は、第1の加速度センサ101を支持する第1の部分Q1と、第2の加速度センサ102を支持する第2の部分Q2とに分割される。すなわち、第2の加速度センサ102は、ポリシリコン架橋配線105によって支持されることで、貫通孔402内において浮いた状態とされる。次に、ダイシングライン701(図10)に沿ってダイシングが行なわれる。

【0074】

図22を参照して、上記のダイシングによって、連結部110のみによって互いに連結された第1および第2の加速度センサ101、102からなる部材が切り出される。この切り出された部材は専用のトレイにいったん収納される。また支持台1700の上面および側面の各々に導電性ペーストなどの接着材501が塗布される。

【0075】

次にガラスキャップ103および104の両方の天面が真空吸着コレットなどの吸着治具によって保持され、支持台1700の近くに搬送される。次に第1の加速度センサ101が支持台1700の上面に接着材501を介して貼り付けられる。これにより第2の加速度センサは、連結部110によって中空に支持される。

【0076】

次に連結部110のポリシリコン架橋配線105の弾力性を利用してポリシリコン架橋配線105が押し曲げられる。これにより第2の加速度センサ102は、第1の加速度センサ101に対して向きを変え、支持台1700の側面に接着材501を介して貼り付けられる。この結果、第1および第2の加速度センサ101、102のそれぞれの検出軸は互いに直交化される。

【0077】

以上により本実施の形態の多軸加速度センサチップ804が製造される。

なお、上記以外の構成については、上述した実施の形態2の構成とほぼ同じであるため、同一または対応する要素について同一の符号を付し、その説明を繰り返さない。

【0078】

また連結部110の代わりに金メッキ架橋配線1301が用いられてもよい。

本実施の形態によれば、シリコン基板200の裏面からのエッチングの回数を1回のみとすることができるので、エッチング工程を簡略化することができる。

【0079】

また支持台1700の形状を自由に選択することができる。

また第1および第2の加速度センサ101、102の間は、連結部110によって電気的に接続されている。これにより支持台1700に配線構造を形成しておく必要がない。

【0080】

また多軸加速度センサチップ804は、通常のICチップと同様の取り扱いが可能である。

【0081】

なお上記の各実施の形態においては、製造方法の初期段階において基板の主面に垂直な方向209を(図4)を検出軸とするセンサ素子が基板上に形成されるが、本発明はこれに限定されるものではなく、たとえば基板の主面内の方向を検出軸とするセンサ素子が形成されてもよい。

【0082】

また上記の各実施の形態においては力学量センサについて説明したが、本発明はこれに限定されるものではなく、電磁波センサ、音波センサ、超音波センサ、磁界センサなどに適用することもできる。

【0083】

今回開示された各実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることを意図される。

【産業上の利用可能性】

【0084】

本発明は複数のセンサ素子を有するセンサ装置に特に有利に適用され得る。

【図面の簡単な説明】

【0085】

【図1】本発明の実施の形態1におけるセンサ装置の構成を概略的に示す平面図である。

【図2】図1の線II−IIに沿った概略断面図である。

【図3】本発明の実施の形態1におけるセンサ装置の製造方法の第1工程を概略的に示す部分平面図である。

【図4】図3の線IV−IVに沿った概略的な部分断面図である。

【図5】本発明の実施の形態1におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【図6】本発明の実施の形態1におけるセンサ装置の製造方法の第3工程を概略的に示す部分断面図である。

【図7】本発明の実施の形態1におけるセンサ装置の製造方法の第4工程を概略的に示す部分断面図である。

【図8】本発明の実施の形態1におけるセンサ装置の製造方法の第5工程を概略的に示す部分平面図である。

【図9】図8の線IX−IXに沿った概略的な部分断面図である。

【図10】本発明の実施の形態1におけるセンサ装置の製造方法の第6工程を概略的に示す部分平面図である。

【図11】図10の線XI−XIに沿った概略的な部分断面図である。

【図12】本発明の実施の形態2におけるセンサ装置の構成を概略的に示す断面図である。

【図13】本発明の実施の形態2におけるセンサ装置の製造方法の第1工程を概略的に示す部分断面図である。

【図14】本発明の実施の形態2におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【図15】本発明の実施の形態2におけるセンサ装置の製造方法の第3工程を概略的に示す部分断面図である。

【図16】本発明の実施の形態2におけるセンサ装置の製造方法の第4工程を概略的に示す部分断面図である。

【図17】本発明の実施の形態3におけるセンサ装置の構成を概略的に示す断面図である。

【図18】本発明の実施の形態3におけるセンサ装置の製造方法の第1工程を概略的に示す部分断面図である。

【図19】本発明の実施の形態3におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【図20】本発明の実施の形態4におけるセンサ装置の構成を概略的に示す断面図である。

【図21】本発明の実施の形態4におけるセンサ装置の製造方法の第1工程を概略的に示す部分断面図である。

【図22】本発明の実施の形態4におけるセンサ装置の製造方法の第2工程を概略的に示す部分断面図である。

【符号の説明】

【0086】

AX1 第1検出軸、AX2 第2検出軸、P1,Q1 第1の部分、P2,Q2 第2の部分、100 SOI基板、101 第1の加速度センサ(第1のセンサ素子)、102 第2の加速度センサ(第2のセンサ素子)、103,104 ガラスキャップ、105 ポリシリコン架橋配線、106,107 ポリシリコンパッド、108 接続パッド、200 シリコン基板、210 単結晶シリコン部、211 埋込酸化膜、212 SOI層、501 接着材、801〜804 多軸加速度センサチップ(センサ装置)、1301 金メッキ架橋配線、1700 支持台。

【特許請求の範囲】

【請求項1】

連結部によって互いに連結された第1および第2のセンサ素子を基板上に形成する工程と、

前記第1および第2のセンサ素子のそれぞれを支持する第1および第2の部分に前記基板を分割する工程と、

前記分割する工程の後に、前記連結部を曲げながら前記第1のセンサ素子に対して前記第2のセンサ素子の向きを変える工程とを備えた、センサ装置の製造方法。

【請求項2】

前記第1および第2のセンサのそれぞれは、互いに異なる第1および第2の方向に関してベクトル量の成分を検出するためのものである、請求項1に記載のセンサ装置の製造方法。

【請求項3】

前記ベクトル量は力学量である、請求項2に記載のセンサ装置の製造方法。

【請求項4】

前記第1および第2のセンサ素子を形成する工程は、同一の構造および同一の向きを有する複数のセンサを基板上に形成することにより行なわれる、請求項1〜3のいずれかに記載のセンサ装置の製造方法。

【請求項5】

前記連結部は、前記第1および第2のセンサ素子を互いに電気的に接続している、請求項1〜4のいずれかに記載のセンサ装置の製造方法。

【請求項6】

前記連結部はポリシリコン膜を含む、請求項1〜5のいずれかに記載のセンサ装置の製造方法。

【請求項7】

前記連結部は金メッキ膜を含む、請求項1〜5のいずれかに記載のセンサ装置の製造方法。

【請求項8】

前記向きを変える工程の後に、前記第1および第2の部分を互いに固定する工程をさらに備えた、請求項1〜7のいずれかに記載のセンサ装置の製造方法。

【請求項9】

前記固定する工程は、前記第1および第2の部分の各々を支持部に固定することにより行なわれる、請求項8に記載のセンサ装置の製造方法。

【請求項10】

前記基板はSOI基板である、請求項1〜9のいずれかに記載のセンサ装置の製造方法。

【請求項1】

連結部によって互いに連結された第1および第2のセンサ素子を基板上に形成する工程と、

前記第1および第2のセンサ素子のそれぞれを支持する第1および第2の部分に前記基板を分割する工程と、

前記分割する工程の後に、前記連結部を曲げながら前記第1のセンサ素子に対して前記第2のセンサ素子の向きを変える工程とを備えた、センサ装置の製造方法。

【請求項2】

前記第1および第2のセンサのそれぞれは、互いに異なる第1および第2の方向に関してベクトル量の成分を検出するためのものである、請求項1に記載のセンサ装置の製造方法。

【請求項3】

前記ベクトル量は力学量である、請求項2に記載のセンサ装置の製造方法。

【請求項4】

前記第1および第2のセンサ素子を形成する工程は、同一の構造および同一の向きを有する複数のセンサを基板上に形成することにより行なわれる、請求項1〜3のいずれかに記載のセンサ装置の製造方法。

【請求項5】

前記連結部は、前記第1および第2のセンサ素子を互いに電気的に接続している、請求項1〜4のいずれかに記載のセンサ装置の製造方法。

【請求項6】

前記連結部はポリシリコン膜を含む、請求項1〜5のいずれかに記載のセンサ装置の製造方法。

【請求項7】

前記連結部は金メッキ膜を含む、請求項1〜5のいずれかに記載のセンサ装置の製造方法。

【請求項8】

前記向きを変える工程の後に、前記第1および第2の部分を互いに固定する工程をさらに備えた、請求項1〜7のいずれかに記載のセンサ装置の製造方法。

【請求項9】

前記固定する工程は、前記第1および第2の部分の各々を支持部に固定することにより行なわれる、請求項8に記載のセンサ装置の製造方法。

【請求項10】

前記基板はSOI基板である、請求項1〜9のいずれかに記載のセンサ装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2010−139313(P2010−139313A)

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願番号】特願2008−314527(P2008−314527)

【出願日】平成20年12月10日(2008.12.10)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願日】平成20年12月10日(2008.12.10)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]