ソリッドステートリレー

【課題】 部品点数を減らして小型化及び低コスト化を図った交流・直流兼用型のソリッドステートリレーを提供すること。

【解決手段】 一対の入力端子と、前記一対の入力端子間に接続される発光素子と、前記発光素子の発光を光電変換して電流を出力する光電変換素子と、前記光電変換素子の出力によって導通するスイッチング素子と、交流電源又は直流電源と負荷とが接続される一対の出力端子と、対角する一対の端子が前記スイッチング素子の電流入力端と電流出力端との間に接続され、対角する他の一対の端子が前記一対の出力端子間に接続されるブリッジ型の整流素子とを含む、ソリッドステートリレー。

【解決手段】 一対の入力端子と、前記一対の入力端子間に接続される発光素子と、前記発光素子の発光を光電変換して電流を出力する光電変換素子と、前記光電変換素子の出力によって導通するスイッチング素子と、交流電源又は直流電源と負荷とが接続される一対の出力端子と、対角する一対の端子が前記スイッチング素子の電流入力端と電流出力端との間に接続され、対角する他の一対の端子が前記一対の出力端子間に接続されるブリッジ型の整流素子とを含む、ソリッドステートリレー。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ソリッドステートリレーに関する。

【背景技術】

【0002】

ソリッドステートリレーは、接点が無く、動作速度が速いという利点があるため、例えばモータ等の様々な電子機器の制御等に用いられている。ソリッドステートリレーには、直流電力を継電するタイプ、交流電力を継電するタイプ、及び直流電力及び交流電力の両方を継電する兼用タイプがある。

【0003】

図1は、従来の交流専用のソリッドステートリレーの回路の一例を示す図である。

【0004】

図1に示すソリッドステートリレーは、1次側を構成する入力端子1A、1B、及び入力回路2と、2次側を構成するトリガー回路3、トライアック4、スナバ回路5、バリスタ6、及び出力端子7A、7Bと、1次側と2次側の間に配設されるフォトアイソレータ10を有する。フォトアイソレータは、1次側の入力回路2に接続されるフォトダイオード10Aと、2次側のトリガー回路3に接続されるフォトトライアック10Bとを有する。

【0005】

入力端子1A、1B間に所定の電圧が印加されると、フォトダイオード10Aが発光し、この光を受光したフォトトライアック10Bが電流を出力し、トリガー回路3に電流が流れる。トリガー回路3は、フォトトライアック10Bから電流が入力されるとトライアック4を導通させる。これにより、出力端子7A、7B間が導通し、ソリッドステートリレーがオンになる。

【0006】

出力端子7A、7B間には交流電源とモータ等の負荷とが直列に接続されているため、トライアック4が導通すると、交流電源から供給される交流電力が負荷に供給される。

【0007】

以上より、図1に示すソリッドステートリレーでは、入力端子1A、1Bの入力電圧を制御することにより、出力端子7A、7B間に接続された負荷に交流電力を供給することができる。

【0008】

図2は、従来の交流・直流兼用のソリッドステートリレーの回路の一例を示す図である。

【0009】

図2に示すソリッドステートリレーは、2次側の回路構成が図1に示す交流専用のソリッドステートリレーと異なり、3つの出力端子11A、11B、11Cを有する。

【0010】

出力端子11A、11Bの間と、出力端子11B、11Cの間には、それぞれ、Pチャネル型のFET(Field Effect Transistor:電界効果型トランジスタ)12A、12B、ダイオード13A、13Bが接続されている。

【0011】

また、1次側と2次側の間には、一対のフォトアイソレータ10が接続されている。フォトアイソレータ10は、1次側に接続されるフォトダイオード10Aと、2次側に接続される受光素子10Cとを有する。

【0012】

出力端子11A及び11Cの間に交流電源及び負荷を接続している場合の動作は次の通りである。入力端子1A、1B間に所定の電圧を印加すると、フォトダイオード10Aが発光し、受光素子10Cで光電変換され、FET12A、12Bのゲートに電圧が印加され、FET12A、12Bが導通する。これにより、出力端子11Aに正の電圧が印加されているときは、FET12A及びダイオード13Bを通じて出力端子11Cに電流が流れ、負荷に電力が供給される。また、出力端子11Cに正の電圧が印加されているときには、FET12B及びダイオード13Aを通じて出力端子11Aに電流が流れ、負荷に電力が供給される。これにより、出力端子11A、11C間に接続された負荷に交流電力を供給することができる。

【0013】

また、出力端子11A、11B間、及び出力端子11C、11B間にそれぞれ直流電源及び負荷が接続されている場合は(出力端子11A及び11Cに直流電源の正端子が接続され、出力端子11Bに直流電源の負端子が接続される)、受光素子10Cで光電変換されてFET12A、12Bが導通すると、出力端子11A、11Cから出力端子11Bに向けて電流が流れ、負荷に直流電力が供給される。

【0014】

以上より、図2に示すソリッドステートリレーでは、入力端子1A、1Bの入力電圧を制御することにより、出力端子11A、11B、11C間に交流電流又は直流電流を流すことができる(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平05−7143号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

ソリッドステートリレーは、交流・直流兼用型の方が用途が広がるため、生産性も向上し、低コストで生産しやすくなる。

【0017】

しかしながら、従来の交流・直流兼用型のソリッドステートリレーは、交流専用型のソリッドステートリレーに比べて部品点数が大幅に増えるため、大型化が避けられないという課題があった。

【0018】

そこで、本発明は、部品点数を減らして小型化及び低コスト化を図った交流・直流兼用型のソリッドステートリレーを提供することを目的とする。

【課題を解決するための手段】

【0019】

本発明の実施の形態の一観点のソリッドステートリレーは、一対の入力端子と、前記一対の入力端子間に接続される発光素子と、前記発光素子の発光を光電変換して電流を出力する光電変換素子と、前記光電変換素子の出力によって導通するスイッチング素子と、交流電源又は直流電源と負荷とが接続される一対の出力端子と、対角する一対の端子が前記スイッチング素子の電流入力端と電流出力端との間に接続され、対角する他の一対の端子が前記一対の出力端子間に接続されるブリッジ型の整流素子とを含む。

【0020】

また、前記発光素子は、互いに逆極性の一対の発光整流素子を含んでもよい。

【0021】

また、前記光電変換素子は、フォトトランジスタ、又はフォトダイオードであってもよい。

【0022】

また、前記スイッチング素子は、FET、又はバイポーラトランジスタであってもよい。

【0023】

また、前記ブリッジ型の整流素子は、ダイオードスタックであってもよい。

【0024】

また、前記一対の出力端子間に、保護素子を含んでもよい。

【0025】

また、前記入力端子及び前記出力端子以外の各素子は、半導体プロセスで製造され、ワンパッケージにされてもよい。

【発明の効果】

【0026】

部品点数を減らして小型化及び低コスト化を図った交流・直流兼用型のソリッドステートリレーを提供できる。

【図面の簡単な説明】

【0027】

【図1】従来の交流専用のソリッドステートリレーの回路の一例を示す図である。

【図2】従来の交流・直流兼用のソリッドステートリレーの回路の一例を示す図である。

【図3】実施の形態1のソリッドステートリレーのパッケージの内部構造を示す図である。

【図4】実施の形態1のソリッドステートリレーの回路構成を示す図である。

【図5】実施の形態2のソリッドステートリレーの回路構成を示す図である。

【図6】実施の形態3のソリッドステートリレーの回路構成を示す図である。

【図7】実施の形態4のソリッドステートリレーの回路構成を示す図である。

【図8】実施の形態5のソリッドステートリレーの回路構成を示す図である。

【発明を実施するための形態】

【0028】

以下、本発明のソリッドステートリレーを適用した実施の形態について説明する。

【0029】

実施の形態1.

図3は、実施の形態1のソリッドステートリレーのパッケージの内部構造を示す図である。

【0030】

ソリッドステートリレー100は、断面で示す筐体101内に、入力端子102A、102B、抵抗器103A、103B、フォトアイソレータ104、抵抗器105、FET106、DS(Diode Stack:ダイオードスタック)107、第1保護素子108、第2保護素子109、及び出力端子110A、110Bを含む。入力端子102A、102B間には、入力電圧(直流電圧)を印加するための電源(図示せず)が接続され、出力端子110A、110B間には、交流電源又は直流電源と負荷(図示せず)とが接続される。

【0031】

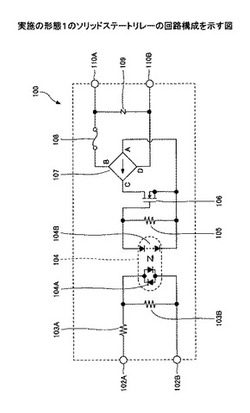

図4は、実施の形態1のソリッドステートリレーの回路構成を示す図である。

【0032】

ソリッドステートリレー100は、フォトアイソレータ104内に、逆極性で並列接続された一対のフォトダイオード104Aと、受光素子104Bとを有する。また、第1保護素子はヒューズであり、第2保護素子109はバリスタである。

【0033】

1次側では、入力端子102Aに抵抗器103Aが接続され、抵抗器103Aと入力端子102Bとの間に、抵抗器103Bとフォトダイオード104Aが並列に接続されている。

【0034】

また、2次側では、受光素子104Bに抵抗器105が並列に接続され、フォトダイオード104Aの入力端子、及び抵抗器105の一端(図中で上側の端子)は、Nチャネル型のFET106のゲートに接続されている。フォトダイオード104A、抵抗器105の他端(図中で下側の端子)、及びFET106のドレインは、DS107の端子Aに接続されている。

【0035】

FET106のソースは、DS107の端子Cに接続されており、DS107の端子B、Dは、それぞれ、出力端子110A、110Bに接続されている。DS107の端子Bと出力端子110Aとの間には、ヒューズ108が挿入され、出力端子110A、110B間にはバリスタ109が挿入されている。

【0036】

なお、DS107は、端子Aから端子B、端子Aから端子D、端子Bから端子C、及び端子Dから端子Cの向きに電流を流す整流素子であり、4つのダイオードを含むブリッジ回路と同一の整流作用を有する。

【0037】

次に、このような実施の形態1のソリッドステートリレー100において、出力端子110A、110B間に交流電源及び負荷が接続されている場合の動作について説明する。

【0038】

入力端子102A、102B間に、入力端子102Aの方が電位が高くなるように(順方向の)所定の電圧を印加すると、入力端子102Aからフォトダイオード104Aを経て入力端子104Bの方向に電流が流れ、これによりフォトダイオード104Aが発光する。

【0039】

この発光は受光素子104Bで光電変換され、図中下向きに電流が流れるため、FET106が導通する。

【0040】

このとき、出力端子110Aに交流電圧の正電圧、出力端子110Bに交流電圧の負電圧が印加されているとすると、出力端子110A、DS107の端子B、同端子C、FET106、DS107の端子A、同端子D、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0041】

一方、出力端子110Aに交流電圧の負電圧、出力端子110Bに交流電圧の正電圧が印加されているとすると、出力端子110B、DS107の端子D、同端子C、FET106、DS107の端子A、同端子B、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0042】

また、入力端子102A、102B間に、入力端子102Aの方が電位が低くなるように(逆方向の)所定の電圧を印加すると、入力端子102Bからフォトダイオード104Aを経て入力端子104Aの方向に電流が流れ、これによりフォトダイオード104Aが発光する。

【0043】

この発光は受光素子104Bで光電変換され、図中下向きに電流が流れるため、FET106が導通するFET106が導通した場合に、出力端子110A、110B間に交流電圧が供給されると、入力端子102A、102B間に印加される電圧の極性が順方向の場合と同様に2次側の回路内に電流が流れるため、出力端子110Aから出力端子110Bの向き、又は、出力端子110Bから出力端子110Aの向きに電流が流れる。これにより、負荷に電力が供給される。

【0044】

このように、実施の形態1のソリッドステートリレー100によれば、出力端子110A、110B間に交流電源が接続されている場合に、入力端子102A、102B間に印加する電圧値を制御することにより、出力端子110A、110B間に接続された負荷に交流電力を供給することができる。

【0045】

次に、出力端子110A、110B間に直流電源と負荷が接続されている場合について説明する。

【0046】

まず、出力端子110Aに直流電源の正端子が接続され、出力端子110Bに直流電源の負端子が接続されている場合において、入力端子102A、102B間に順方向又は逆方向の電圧が印加されると、いずれの場合においてもフォトダイオード104Aが発光するため、これにより受光素子104Bで光電変換が行われ、FET106が導通する。

【0047】

FET106が導通している間は、出力端子110A、DS107の端子B、同端子C、FET106、DS107の端子A、同端子D、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0048】

一方、出力端子110Aに直流電源の負端子が接続され、出力端子110Bに直流電源の正端子が接続されている場合において、入力端子102A、102B間に順方向又は逆方向の電圧が印加されると、いずれの場合においてもフォトダイオード104Aが発光するため、これにより受光素子104Bで光電変換が行われ、FET106が導通する。

【0049】

FET106が導通している間は、出力端子110B、DS107の端子D、同端子C、FET106、DS107の端子A、同端子B、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0050】

このように、実施の形態1のソリッドステートリレー100によれば、出力端子110A、110B間に直流電源が接続されている場合においても、入力端子102A、102B間に印加する電圧値を制御することにより、出力端子110A、110B間に接続された負荷に直流電力を供給することができる。

【0051】

以上、実施の形態1によれば、図4に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー100を提供することができる。

【0052】

抵抗器103A、103B、フォトアイソレータ104、抵抗器105、FET106、DS107、ヒューズ108、及びバリスタ109は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態1のソリッドステートリレー100によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0053】

このため、実施の形態1によれば、低コストで製造可能で小型化を図った交流・直流兼用型のソリッドステートリレー100を提供することができる。また、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0054】

なお、ヒューズ108とバリスタ109はソリッドステートリレー100が用いられる環境によっては不要な場合もある。このため、ヒューズ108とバリスタ109のいずれか一方、又は両方を含まないように構成してもよい。このような場合には、図3に示す第1保護素子及び/又は第2保護素子109が不要になるため、パッケージの小型化がより図りやすくなる。

【0055】

実施の形態2.

図5は、実施の形態2のソリッドステートリレーの回路構成を示す図である。

【0056】

実施の形態2のソリッドステートリレー200は、実施の形態1のソリッドステートリレー100におけるDS7の代わりに、ダイオードD1〜D4で構成されるブリッジ回路127を含む。その他の構成要素は実施の形態1のソリッドステートリレー100と同一であるため、同一又は同等の構成要素には同一符号を付し、その説明を省略する。

【0057】

ブリッジ回路127の4端子の接続は、実施の形態1のDS107の端子A〜Dと同一であるため、出力端子110A、110B間に交流電源と負荷が接続されても、直流電源と負荷が接続されても、電流の流れる経路は実施の形態1のソリッドステートリレー100と同一である。

【0058】

入力端子102A、102B間に、所定の電圧を印加されてフォトダイオード104Aが発光すると、受光素子104Bが光電変換を行い、図中下向きに電流が流れるため、FET106が導通する。

【0059】

このとき、出力端子110Aに交流電圧の正電圧、出力端子110Bに交流電圧の負電圧が印加されているとすると、出力端子110A、ブリッジ回路127のD1、FET106、ブリッジ回路127のD4、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0060】

一方、出力端子110Aに交流電圧の負電圧、出力端子110Bに交流電圧の正電圧が印加されているとすると、出力端子110B、ブリッジ回路127のD2、FET106、ブリッジ回路127のD3、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0061】

出力端子110A、110B間に直流電源が接続された場合に2次側の回路内で電流の流れる方向は、交流電源が接続されて出力端子110A、110B間に印加される電圧の極性がいずれかの場合と同一である。

【0062】

以上より、実施の形態2によれば、図5に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー200を提供することができる。また、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0063】

抵抗器103A、103B、フォトアイソレータ104、抵抗器105、FET106、ブリッジ回路127、ヒューズ108、及びバリスタ109は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態2のソリッドステートリレー200によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0064】

実施の形態3.

図6は、実施の形態3のソリッドステートリレーの回路構成を示す図である。

【0065】

実施の形態3のソリッドステートリレー300は、フォトアイソレータ134、抵抗器135、バイポーラトランジスタ136、ダイオード137、及びキャパシタ138を含む点が実施の形態2のソリッドステートリレー200と異なる。その他の構成要素は実施の形態2のソリッドステートリレー200と同一であるため、同一又は同等の構成要素には同一符号を付し、その説明を省略する。

【0066】

フォトアイソレータ134は、フォトダイオード104と、NPN型のフォトトランジスタ134Bとを有する。フォトトランジスタ134Bは、コレクタがブリッジ回路127のD1とD2の出力側に接続されており、エミッタが抵抗器135を介してブリッジ回路127のD3とD4の入力側に接続されている。

【0067】

NPN型のバイポーラトランジスタ136は、ベースがフォトトランジスタ134Bのエミッタに接続されており、エミッタ電流によって導通するように構成されている。バイポーラトランジスタ136のコレクタは、ブリッジ回路127のD1とD2の出力側に接続され、バイポーラトランジスタ136のエミッタは、ブリッジ回路127のD3とD4の入力側に接続されている。

【0068】

整流用のダイオード137とコンデンサ138は、バイポーラトランジスタ136のコレクタ−エミッタ間に並列に接続されている。

【0069】

入力端子102A、102B間に、所定の電圧を印加されてフォトダイオード104Aが発光すると、フォトトランジスタ134Bが電流を出力し、図中下向きに電流が流れるため、バイポーラトランジスタ136が導通する。

【0070】

このとき、出力端子110Aに交流電圧の正電圧、出力端子110Bに交流電圧の負電圧が印加されているとすると、出力端子110A、ブリッジ回路127のD1、バイポーラトランジスタ136、ブリッジ回路127のD4、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0071】

一方、出力端子110Aに交流電圧の負電圧、出力端子110Bに交流電圧の正電圧が印加されているとすると、出力端子110B、ブリッジ回路127のD2、バイポーラトランジスタ136、ブリッジ回路127のD3、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0072】

出力端子110A、110B間に直流電源と負荷が接続された場合に2次側の回路内で電流の流れる方向は、交流電源と負荷が接続されて出力端子110A、110B間に印加される電圧の極性がいずれかの場合と同一である。このため重複説明は省略する。

【0073】

以上より、実施の形態3によれば、図6に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー300を提供することができる。また、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0074】

抵抗器103A、103B、フォトアイソレータ134、抵抗器135、バイポーラトランジスタ136、ブリッジ回路127、抵抗器137、及びコンデンサ138は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態3のソリッドステートリレー300によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0075】

実施の形態4.

図7は、実施の形態4のソリッドステートリレーの回路構成を示す図である。

【0076】

実施の形態4のソリッドステートリレー400は、実施の形態2のソリッドステートリレー200(図5参照)からヒューズ108及びバリスタ109を取り除いた回路構成を有する。

【0077】

このため、実施の形態4のソリッドステートリレー400の動作は、実施の形態2のソリッドステートリレー200と同一である。

【0078】

実施の形態2のソリッドステートリレー200に含まれるヒューズ108とバリスタ109(図5参照)は、ソリッドステートリレーが用いられる環境によっては不要な場合もあるため、図7に示すように含まないように構成してもよい。このような場合には、パッケージの小型化がより図りやすくなる。

【0079】

実施の形態4によれば、より小型化を図った交流・直流兼用型のソリッドステートリレー400を提供することができる。なお、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0080】

実施の形態5.

図8は、実施の形態5のソリッドステートリレーの回路構成を示す図である。

【0081】

実施の形態5のソリッドステートリレー500は、実施の形態3のソリッドステートリレー300のバイポーラトランジスタ136(図6参照)の代わりに、Nチャネル型のFET156を含むようにしたものである。

【0082】

FET156は、ゲートがフォトトランジスタ134Bのエミッタに接続されている。このため、フォトトランジスタ134Bが受光して電流を出力すると、FET156は導通される。FET156のソースは、ブリッジ回路127のD1とD2の出力側に接続され、FET156のドレインは、ブリッジ回路127のD3とD4の入力側に接続される。

【0083】

このため、回路の動作は、実施の形態3のソリッドステートリレー300と同一である。

【0084】

以上より、実施の形態5によれば、図8に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー500を提供することができる。なお、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0085】

抵抗器103A、103B、フォトアイソレータ134、抵抗器135、FET156、ブリッジ回路127、抵抗器137、及びコンデンサ138は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態5のソリッドステートリレー500によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0086】

以上、本発明の例示的な実施の形態のソリッドステートリレーについて説明したが、本発明は、具体的に開示された実施の形態に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【符号の説明】

【0087】

100、200、300、400、500 ソリッドステートリレー

101 筐体

102A、102B 入力端子

103A、103B 抵抗器

104 フォトアイソレータ

104A フォトダイオード

104B 受光素子

105 抵抗器

106 FET

107 DS

108 ヒューズ

109 バリスタ

110A、110B 出力端子

127 ブリッジ回路

134 フォトアイソレータ

135 抵抗器

136 バイポーラトランジスタ

137 ダイオード

138 キャパシタ

156 FET

【技術分野】

【0001】

本発明は、ソリッドステートリレーに関する。

【背景技術】

【0002】

ソリッドステートリレーは、接点が無く、動作速度が速いという利点があるため、例えばモータ等の様々な電子機器の制御等に用いられている。ソリッドステートリレーには、直流電力を継電するタイプ、交流電力を継電するタイプ、及び直流電力及び交流電力の両方を継電する兼用タイプがある。

【0003】

図1は、従来の交流専用のソリッドステートリレーの回路の一例を示す図である。

【0004】

図1に示すソリッドステートリレーは、1次側を構成する入力端子1A、1B、及び入力回路2と、2次側を構成するトリガー回路3、トライアック4、スナバ回路5、バリスタ6、及び出力端子7A、7Bと、1次側と2次側の間に配設されるフォトアイソレータ10を有する。フォトアイソレータは、1次側の入力回路2に接続されるフォトダイオード10Aと、2次側のトリガー回路3に接続されるフォトトライアック10Bとを有する。

【0005】

入力端子1A、1B間に所定の電圧が印加されると、フォトダイオード10Aが発光し、この光を受光したフォトトライアック10Bが電流を出力し、トリガー回路3に電流が流れる。トリガー回路3は、フォトトライアック10Bから電流が入力されるとトライアック4を導通させる。これにより、出力端子7A、7B間が導通し、ソリッドステートリレーがオンになる。

【0006】

出力端子7A、7B間には交流電源とモータ等の負荷とが直列に接続されているため、トライアック4が導通すると、交流電源から供給される交流電力が負荷に供給される。

【0007】

以上より、図1に示すソリッドステートリレーでは、入力端子1A、1Bの入力電圧を制御することにより、出力端子7A、7B間に接続された負荷に交流電力を供給することができる。

【0008】

図2は、従来の交流・直流兼用のソリッドステートリレーの回路の一例を示す図である。

【0009】

図2に示すソリッドステートリレーは、2次側の回路構成が図1に示す交流専用のソリッドステートリレーと異なり、3つの出力端子11A、11B、11Cを有する。

【0010】

出力端子11A、11Bの間と、出力端子11B、11Cの間には、それぞれ、Pチャネル型のFET(Field Effect Transistor:電界効果型トランジスタ)12A、12B、ダイオード13A、13Bが接続されている。

【0011】

また、1次側と2次側の間には、一対のフォトアイソレータ10が接続されている。フォトアイソレータ10は、1次側に接続されるフォトダイオード10Aと、2次側に接続される受光素子10Cとを有する。

【0012】

出力端子11A及び11Cの間に交流電源及び負荷を接続している場合の動作は次の通りである。入力端子1A、1B間に所定の電圧を印加すると、フォトダイオード10Aが発光し、受光素子10Cで光電変換され、FET12A、12Bのゲートに電圧が印加され、FET12A、12Bが導通する。これにより、出力端子11Aに正の電圧が印加されているときは、FET12A及びダイオード13Bを通じて出力端子11Cに電流が流れ、負荷に電力が供給される。また、出力端子11Cに正の電圧が印加されているときには、FET12B及びダイオード13Aを通じて出力端子11Aに電流が流れ、負荷に電力が供給される。これにより、出力端子11A、11C間に接続された負荷に交流電力を供給することができる。

【0013】

また、出力端子11A、11B間、及び出力端子11C、11B間にそれぞれ直流電源及び負荷が接続されている場合は(出力端子11A及び11Cに直流電源の正端子が接続され、出力端子11Bに直流電源の負端子が接続される)、受光素子10Cで光電変換されてFET12A、12Bが導通すると、出力端子11A、11Cから出力端子11Bに向けて電流が流れ、負荷に直流電力が供給される。

【0014】

以上より、図2に示すソリッドステートリレーでは、入力端子1A、1Bの入力電圧を制御することにより、出力端子11A、11B、11C間に交流電流又は直流電流を流すことができる(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開平05−7143号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

ソリッドステートリレーは、交流・直流兼用型の方が用途が広がるため、生産性も向上し、低コストで生産しやすくなる。

【0017】

しかしながら、従来の交流・直流兼用型のソリッドステートリレーは、交流専用型のソリッドステートリレーに比べて部品点数が大幅に増えるため、大型化が避けられないという課題があった。

【0018】

そこで、本発明は、部品点数を減らして小型化及び低コスト化を図った交流・直流兼用型のソリッドステートリレーを提供することを目的とする。

【課題を解決するための手段】

【0019】

本発明の実施の形態の一観点のソリッドステートリレーは、一対の入力端子と、前記一対の入力端子間に接続される発光素子と、前記発光素子の発光を光電変換して電流を出力する光電変換素子と、前記光電変換素子の出力によって導通するスイッチング素子と、交流電源又は直流電源と負荷とが接続される一対の出力端子と、対角する一対の端子が前記スイッチング素子の電流入力端と電流出力端との間に接続され、対角する他の一対の端子が前記一対の出力端子間に接続されるブリッジ型の整流素子とを含む。

【0020】

また、前記発光素子は、互いに逆極性の一対の発光整流素子を含んでもよい。

【0021】

また、前記光電変換素子は、フォトトランジスタ、又はフォトダイオードであってもよい。

【0022】

また、前記スイッチング素子は、FET、又はバイポーラトランジスタであってもよい。

【0023】

また、前記ブリッジ型の整流素子は、ダイオードスタックであってもよい。

【0024】

また、前記一対の出力端子間に、保護素子を含んでもよい。

【0025】

また、前記入力端子及び前記出力端子以外の各素子は、半導体プロセスで製造され、ワンパッケージにされてもよい。

【発明の効果】

【0026】

部品点数を減らして小型化及び低コスト化を図った交流・直流兼用型のソリッドステートリレーを提供できる。

【図面の簡単な説明】

【0027】

【図1】従来の交流専用のソリッドステートリレーの回路の一例を示す図である。

【図2】従来の交流・直流兼用のソリッドステートリレーの回路の一例を示す図である。

【図3】実施の形態1のソリッドステートリレーのパッケージの内部構造を示す図である。

【図4】実施の形態1のソリッドステートリレーの回路構成を示す図である。

【図5】実施の形態2のソリッドステートリレーの回路構成を示す図である。

【図6】実施の形態3のソリッドステートリレーの回路構成を示す図である。

【図7】実施の形態4のソリッドステートリレーの回路構成を示す図である。

【図8】実施の形態5のソリッドステートリレーの回路構成を示す図である。

【発明を実施するための形態】

【0028】

以下、本発明のソリッドステートリレーを適用した実施の形態について説明する。

【0029】

実施の形態1.

図3は、実施の形態1のソリッドステートリレーのパッケージの内部構造を示す図である。

【0030】

ソリッドステートリレー100は、断面で示す筐体101内に、入力端子102A、102B、抵抗器103A、103B、フォトアイソレータ104、抵抗器105、FET106、DS(Diode Stack:ダイオードスタック)107、第1保護素子108、第2保護素子109、及び出力端子110A、110Bを含む。入力端子102A、102B間には、入力電圧(直流電圧)を印加するための電源(図示せず)が接続され、出力端子110A、110B間には、交流電源又は直流電源と負荷(図示せず)とが接続される。

【0031】

図4は、実施の形態1のソリッドステートリレーの回路構成を示す図である。

【0032】

ソリッドステートリレー100は、フォトアイソレータ104内に、逆極性で並列接続された一対のフォトダイオード104Aと、受光素子104Bとを有する。また、第1保護素子はヒューズであり、第2保護素子109はバリスタである。

【0033】

1次側では、入力端子102Aに抵抗器103Aが接続され、抵抗器103Aと入力端子102Bとの間に、抵抗器103Bとフォトダイオード104Aが並列に接続されている。

【0034】

また、2次側では、受光素子104Bに抵抗器105が並列に接続され、フォトダイオード104Aの入力端子、及び抵抗器105の一端(図中で上側の端子)は、Nチャネル型のFET106のゲートに接続されている。フォトダイオード104A、抵抗器105の他端(図中で下側の端子)、及びFET106のドレインは、DS107の端子Aに接続されている。

【0035】

FET106のソースは、DS107の端子Cに接続されており、DS107の端子B、Dは、それぞれ、出力端子110A、110Bに接続されている。DS107の端子Bと出力端子110Aとの間には、ヒューズ108が挿入され、出力端子110A、110B間にはバリスタ109が挿入されている。

【0036】

なお、DS107は、端子Aから端子B、端子Aから端子D、端子Bから端子C、及び端子Dから端子Cの向きに電流を流す整流素子であり、4つのダイオードを含むブリッジ回路と同一の整流作用を有する。

【0037】

次に、このような実施の形態1のソリッドステートリレー100において、出力端子110A、110B間に交流電源及び負荷が接続されている場合の動作について説明する。

【0038】

入力端子102A、102B間に、入力端子102Aの方が電位が高くなるように(順方向の)所定の電圧を印加すると、入力端子102Aからフォトダイオード104Aを経て入力端子104Bの方向に電流が流れ、これによりフォトダイオード104Aが発光する。

【0039】

この発光は受光素子104Bで光電変換され、図中下向きに電流が流れるため、FET106が導通する。

【0040】

このとき、出力端子110Aに交流電圧の正電圧、出力端子110Bに交流電圧の負電圧が印加されているとすると、出力端子110A、DS107の端子B、同端子C、FET106、DS107の端子A、同端子D、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0041】

一方、出力端子110Aに交流電圧の負電圧、出力端子110Bに交流電圧の正電圧が印加されているとすると、出力端子110B、DS107の端子D、同端子C、FET106、DS107の端子A、同端子B、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0042】

また、入力端子102A、102B間に、入力端子102Aの方が電位が低くなるように(逆方向の)所定の電圧を印加すると、入力端子102Bからフォトダイオード104Aを経て入力端子104Aの方向に電流が流れ、これによりフォトダイオード104Aが発光する。

【0043】

この発光は受光素子104Bで光電変換され、図中下向きに電流が流れるため、FET106が導通するFET106が導通した場合に、出力端子110A、110B間に交流電圧が供給されると、入力端子102A、102B間に印加される電圧の極性が順方向の場合と同様に2次側の回路内に電流が流れるため、出力端子110Aから出力端子110Bの向き、又は、出力端子110Bから出力端子110Aの向きに電流が流れる。これにより、負荷に電力が供給される。

【0044】

このように、実施の形態1のソリッドステートリレー100によれば、出力端子110A、110B間に交流電源が接続されている場合に、入力端子102A、102B間に印加する電圧値を制御することにより、出力端子110A、110B間に接続された負荷に交流電力を供給することができる。

【0045】

次に、出力端子110A、110B間に直流電源と負荷が接続されている場合について説明する。

【0046】

まず、出力端子110Aに直流電源の正端子が接続され、出力端子110Bに直流電源の負端子が接続されている場合において、入力端子102A、102B間に順方向又は逆方向の電圧が印加されると、いずれの場合においてもフォトダイオード104Aが発光するため、これにより受光素子104Bで光電変換が行われ、FET106が導通する。

【0047】

FET106が導通している間は、出力端子110A、DS107の端子B、同端子C、FET106、DS107の端子A、同端子D、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0048】

一方、出力端子110Aに直流電源の負端子が接続され、出力端子110Bに直流電源の正端子が接続されている場合において、入力端子102A、102B間に順方向又は逆方向の電圧が印加されると、いずれの場合においてもフォトダイオード104Aが発光するため、これにより受光素子104Bで光電変換が行われ、FET106が導通する。

【0049】

FET106が導通している間は、出力端子110B、DS107の端子D、同端子C、FET106、DS107の端子A、同端子B、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0050】

このように、実施の形態1のソリッドステートリレー100によれば、出力端子110A、110B間に直流電源が接続されている場合においても、入力端子102A、102B間に印加する電圧値を制御することにより、出力端子110A、110B間に接続された負荷に直流電力を供給することができる。

【0051】

以上、実施の形態1によれば、図4に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー100を提供することができる。

【0052】

抵抗器103A、103B、フォトアイソレータ104、抵抗器105、FET106、DS107、ヒューズ108、及びバリスタ109は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態1のソリッドステートリレー100によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0053】

このため、実施の形態1によれば、低コストで製造可能で小型化を図った交流・直流兼用型のソリッドステートリレー100を提供することができる。また、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0054】

なお、ヒューズ108とバリスタ109はソリッドステートリレー100が用いられる環境によっては不要な場合もある。このため、ヒューズ108とバリスタ109のいずれか一方、又は両方を含まないように構成してもよい。このような場合には、図3に示す第1保護素子及び/又は第2保護素子109が不要になるため、パッケージの小型化がより図りやすくなる。

【0055】

実施の形態2.

図5は、実施の形態2のソリッドステートリレーの回路構成を示す図である。

【0056】

実施の形態2のソリッドステートリレー200は、実施の形態1のソリッドステートリレー100におけるDS7の代わりに、ダイオードD1〜D4で構成されるブリッジ回路127を含む。その他の構成要素は実施の形態1のソリッドステートリレー100と同一であるため、同一又は同等の構成要素には同一符号を付し、その説明を省略する。

【0057】

ブリッジ回路127の4端子の接続は、実施の形態1のDS107の端子A〜Dと同一であるため、出力端子110A、110B間に交流電源と負荷が接続されても、直流電源と負荷が接続されても、電流の流れる経路は実施の形態1のソリッドステートリレー100と同一である。

【0058】

入力端子102A、102B間に、所定の電圧を印加されてフォトダイオード104Aが発光すると、受光素子104Bが光電変換を行い、図中下向きに電流が流れるため、FET106が導通する。

【0059】

このとき、出力端子110Aに交流電圧の正電圧、出力端子110Bに交流電圧の負電圧が印加されているとすると、出力端子110A、ブリッジ回路127のD1、FET106、ブリッジ回路127のD4、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0060】

一方、出力端子110Aに交流電圧の負電圧、出力端子110Bに交流電圧の正電圧が印加されているとすると、出力端子110B、ブリッジ回路127のD2、FET106、ブリッジ回路127のD3、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0061】

出力端子110A、110B間に直流電源が接続された場合に2次側の回路内で電流の流れる方向は、交流電源が接続されて出力端子110A、110B間に印加される電圧の極性がいずれかの場合と同一である。

【0062】

以上より、実施の形態2によれば、図5に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー200を提供することができる。また、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0063】

抵抗器103A、103B、フォトアイソレータ104、抵抗器105、FET106、ブリッジ回路127、ヒューズ108、及びバリスタ109は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態2のソリッドステートリレー200によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0064】

実施の形態3.

図6は、実施の形態3のソリッドステートリレーの回路構成を示す図である。

【0065】

実施の形態3のソリッドステートリレー300は、フォトアイソレータ134、抵抗器135、バイポーラトランジスタ136、ダイオード137、及びキャパシタ138を含む点が実施の形態2のソリッドステートリレー200と異なる。その他の構成要素は実施の形態2のソリッドステートリレー200と同一であるため、同一又は同等の構成要素には同一符号を付し、その説明を省略する。

【0066】

フォトアイソレータ134は、フォトダイオード104と、NPN型のフォトトランジスタ134Bとを有する。フォトトランジスタ134Bは、コレクタがブリッジ回路127のD1とD2の出力側に接続されており、エミッタが抵抗器135を介してブリッジ回路127のD3とD4の入力側に接続されている。

【0067】

NPN型のバイポーラトランジスタ136は、ベースがフォトトランジスタ134Bのエミッタに接続されており、エミッタ電流によって導通するように構成されている。バイポーラトランジスタ136のコレクタは、ブリッジ回路127のD1とD2の出力側に接続され、バイポーラトランジスタ136のエミッタは、ブリッジ回路127のD3とD4の入力側に接続されている。

【0068】

整流用のダイオード137とコンデンサ138は、バイポーラトランジスタ136のコレクタ−エミッタ間に並列に接続されている。

【0069】

入力端子102A、102B間に、所定の電圧を印加されてフォトダイオード104Aが発光すると、フォトトランジスタ134Bが電流を出力し、図中下向きに電流が流れるため、バイポーラトランジスタ136が導通する。

【0070】

このとき、出力端子110Aに交流電圧の正電圧、出力端子110Bに交流電圧の負電圧が印加されているとすると、出力端子110A、ブリッジ回路127のD1、バイポーラトランジスタ136、ブリッジ回路127のD4、出力端子110Bの順に電流が流れる。これにより、出力端子110Aから出力端子110Bの向きに電流が流れ、負荷に電力が供給される。

【0071】

一方、出力端子110Aに交流電圧の負電圧、出力端子110Bに交流電圧の正電圧が印加されているとすると、出力端子110B、ブリッジ回路127のD2、バイポーラトランジスタ136、ブリッジ回路127のD3、出力端子110Aの順に電流が流れる。これにより、出力端子110Bから出力端子110Aの向きに電流が流れ、負荷に電力が供給される。

【0072】

出力端子110A、110B間に直流電源と負荷が接続された場合に2次側の回路内で電流の流れる方向は、交流電源と負荷が接続されて出力端子110A、110B間に印加される電圧の極性がいずれかの場合と同一である。このため重複説明は省略する。

【0073】

以上より、実施の形態3によれば、図6に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー300を提供することができる。また、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0074】

抵抗器103A、103B、フォトアイソレータ134、抵抗器135、バイポーラトランジスタ136、ブリッジ回路127、抵抗器137、及びコンデンサ138は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態3のソリッドステートリレー300によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0075】

実施の形態4.

図7は、実施の形態4のソリッドステートリレーの回路構成を示す図である。

【0076】

実施の形態4のソリッドステートリレー400は、実施の形態2のソリッドステートリレー200(図5参照)からヒューズ108及びバリスタ109を取り除いた回路構成を有する。

【0077】

このため、実施の形態4のソリッドステートリレー400の動作は、実施の形態2のソリッドステートリレー200と同一である。

【0078】

実施の形態2のソリッドステートリレー200に含まれるヒューズ108とバリスタ109(図5参照)は、ソリッドステートリレーが用いられる環境によっては不要な場合もあるため、図7に示すように含まないように構成してもよい。このような場合には、パッケージの小型化がより図りやすくなる。

【0079】

実施の形態4によれば、より小型化を図った交流・直流兼用型のソリッドステートリレー400を提供することができる。なお、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0080】

実施の形態5.

図8は、実施の形態5のソリッドステートリレーの回路構成を示す図である。

【0081】

実施の形態5のソリッドステートリレー500は、実施の形態3のソリッドステートリレー300のバイポーラトランジスタ136(図6参照)の代わりに、Nチャネル型のFET156を含むようにしたものである。

【0082】

FET156は、ゲートがフォトトランジスタ134Bのエミッタに接続されている。このため、フォトトランジスタ134Bが受光して電流を出力すると、FET156は導通される。FET156のソースは、ブリッジ回路127のD1とD2の出力側に接続され、FET156のドレインは、ブリッジ回路127のD3とD4の入力側に接続される。

【0083】

このため、回路の動作は、実施の形態3のソリッドステートリレー300と同一である。

【0084】

以上より、実施の形態5によれば、図8に示すような簡単な回路構成で、交流・直流兼用型のソリッドステートリレー500を提供することができる。なお、直流電源はいずれの極性によっても入力端子102A、102Bに接続することができる。

【0085】

抵抗器103A、103B、フォトアイソレータ134、抵抗器135、FET156、ブリッジ回路127、抵抗器137、及びコンデンサ138は、全て半導体プロセスによって作製し、ワンパッケージ化することができる。また、従来の交流・直流兼用型のソリッドステートリレー(図2参照)ように、フォトアイソレータ及びFETをそれぞれ2つ設ける必要がなく、スナバ回路も不要である。特に、スナバ回路は、半導体プロセスで作製するのではなく、比較的容量の大きい抵抗器とコンデンサを実装していため、不要にできることのメリットは大きい。以上、実施の形態5のソリッドステートリレー500によれば、部品点数を少なく抑えることができ、パッケージの小型化を図ることができる。

【0086】

以上、本発明の例示的な実施の形態のソリッドステートリレーについて説明したが、本発明は、具体的に開示された実施の形態に限定されるものではなく、特許請求の範囲から逸脱することなく、種々の変形や変更が可能である。

【符号の説明】

【0087】

100、200、300、400、500 ソリッドステートリレー

101 筐体

102A、102B 入力端子

103A、103B 抵抗器

104 フォトアイソレータ

104A フォトダイオード

104B 受光素子

105 抵抗器

106 FET

107 DS

108 ヒューズ

109 バリスタ

110A、110B 出力端子

127 ブリッジ回路

134 フォトアイソレータ

135 抵抗器

136 バイポーラトランジスタ

137 ダイオード

138 キャパシタ

156 FET

【特許請求の範囲】

【請求項1】

一対の入力端子と、

前記一対の入力端子間に接続される発光素子と、

前記発光素子の発光を光電変換して電流を出力する光電変換素子と、

前記光電変換素子の出力によって導通するスイッチング素子と、

交流電源又は直流電源と負荷とが接続される一対の出力端子と、

対角する一対の端子が前記スイッチング素子の電流入力端と電流出力端との間に接続され、対角する他の一対の端子が前記一対の出力端子間に接続されるブリッジ型の整流素子と

を含む、ソリッドステートリレー。

【請求項2】

前記発光素子は、互いに逆極性の一対の発光整流素子を含む、請求項1に記載のソリッドステートリレー。

【請求項3】

前記光電変換素子は、フォトトランジスタ、又はフォトダイオードである、請求項1又は2に記載のソリッドステートリレー。

【請求項4】

前記スイッチング素子は、FET、又はバイポーラトランジスタである、請求項1乃至3のいずれか一項に記載のソリッドステートリレー。

【請求項5】

前記ブリッジ型の整流素子は、ダイオードスタックである、請求項1乃至4のいずれか一項に記載のソリッドステートリレー。

【請求項6】

前記一対の出力端子間に、保護素子を含む、請求項1乃至5のいずれか一項に記載のソリッドステートリレー。

【請求項7】

前記入力端子及び前記出力端子以外の各素子は、半導体プロセスで製造され、ワンパッケージにされる、請求項1乃至6のいずれか一項に記載のソリッドステートリレー。

【請求項1】

一対の入力端子と、

前記一対の入力端子間に接続される発光素子と、

前記発光素子の発光を光電変換して電流を出力する光電変換素子と、

前記光電変換素子の出力によって導通するスイッチング素子と、

交流電源又は直流電源と負荷とが接続される一対の出力端子と、

対角する一対の端子が前記スイッチング素子の電流入力端と電流出力端との間に接続され、対角する他の一対の端子が前記一対の出力端子間に接続されるブリッジ型の整流素子と

を含む、ソリッドステートリレー。

【請求項2】

前記発光素子は、互いに逆極性の一対の発光整流素子を含む、請求項1に記載のソリッドステートリレー。

【請求項3】

前記光電変換素子は、フォトトランジスタ、又はフォトダイオードである、請求項1又は2に記載のソリッドステートリレー。

【請求項4】

前記スイッチング素子は、FET、又はバイポーラトランジスタである、請求項1乃至3のいずれか一項に記載のソリッドステートリレー。

【請求項5】

前記ブリッジ型の整流素子は、ダイオードスタックである、請求項1乃至4のいずれか一項に記載のソリッドステートリレー。

【請求項6】

前記一対の出力端子間に、保護素子を含む、請求項1乃至5のいずれか一項に記載のソリッドステートリレー。

【請求項7】

前記入力端子及び前記出力端子以外の各素子は、半導体プロセスで製造され、ワンパッケージにされる、請求項1乃至6のいずれか一項に記載のソリッドステートリレー。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−30011(P2011−30011A)

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願番号】特願2009−174529(P2009−174529)

【出願日】平成21年7月27日(2009.7.27)

【出願人】(501398606)富士通コンポーネント株式会社 (848)

【Fターム(参考)】

【公開日】平成23年2月10日(2011.2.10)

【国際特許分類】

【出願日】平成21年7月27日(2009.7.27)

【出願人】(501398606)富士通コンポーネント株式会社 (848)

【Fターム(参考)】

[ Back to top ]