タイミング調整装置

【課題】温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

【解決手段】高速揮発性メモリ3にデータを書き込む場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行う。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、書き込み用DLL14から出力される。また、高速揮発性メモリ3からデータを読み出す場合には、CPU温度検出部6にCPU2の温度を検出させて、この検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行う。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU2の温度に応じた時間分遅延して、読み出し用DLL11から出力される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリアクセスのタイミングを調整するタイミング調整装置に関する。

【背景技術】

【0002】

DDR2メモリ等の高速揮発性メモリを使用する場合には、データ信号とデータ取り込み信号との間のタイミングのずれが問題となる。例えば、図14(a)に示すように、DDR2メモリ110からコアLSI120へデータ信号DQとデータ取り込み信号DQSを出力する場合において、DDR2メモリ110から信号が出力された直後(図14(a)の指示n11を参照)は、図14(b)に示すように、データ信号DQとデータ取り込み信号DQSとの間のタイミングが合っている。しかし、コアLSI120で取り込む直前(図14(a)の指示n12を参照)は、図14(c)に示すように、ボードのスキューでデータ信号DQとデータ取り込み信号DQSとの間のタイミングがずれる(図14(c)の矢印Y11を参照)。

【0003】

そこで、コアLSI120は、タイミング調整回路(図14(a)中のDLL121)を備え、図14(d)に示すように、このタイミング調整回路(DLL121)でデータ取り込み信号DQSを遅延調整することで(図14(d)の矢印Y12を参照)、ボード設計毎のスキューを吸収するように設計される。

【0004】

ところで、カーナビゲーション用LSI等の車載LSIには、大容量の揮発性メモリが搭載されている。そして車載LSIに搭載される揮発性メモリは、広い温度範囲(例えば−40℃〜95℃)での正常動作が要求される。

【0005】

しかし今後、揮発性メモリが533MHzから667MHz、800MHz、1GHzと高速化すると、タイミング調整できるウィンドウが狭くなる。このため、タイミング調整量がボードに対して一定では、図15(a)に示すように、或る温度(図では−40℃)では、タイミング調整回路による調整(図15(a)の矢印Y21を参照)によってタイミングのずれを調整することができるが、図15(b)に示すように、別の温度(図では85℃)では、タイミング調整回路による調整(図15(b)の矢印Y22を参照)によってタイミングのずれを調整することができなくなる(図中の指示n21を参照)おそれがある。

【0006】

そして、上記のようなタイミングのずれを調整するために、従来、データ信号の入力に対してデータ取り込み信号の入力が速いか遅いかを検出し、この検出結果に基づいて、データ信号とデータ取り込み信号との間のタイミングのずれを調整する技術が知られている(例えば、特許文献1参照)。

【特許文献1】特開平8−237101号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1に記載の技術では、タイミングのずれを検出し、次回以降のデータ信号の入力におけるタイミングのずれを調整する。このため、タイミングのずれを検出した時点では、タイミングのずれを調整することができず、データ信号の取り込みの際に、データ信号の示す内容を正確に取り込むことができないというデータの不一致が発生するおそれがあった。

【0008】

本発明は、こうした問題に鑑みなされたものであり、温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制する技術を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するためになされた請求項1に記載のタイミング調整装置では、CPU温度情報取得手段が、CPUの温度についての情報であるCPU温度情報を取得する。そして温度ずれ調整手段が、CPU温度情報取得手段により取得されたCPU温度情報に基づいて、データ取り込み信号の入出力を予め設定された遅延時間遅らせることによって、データ信号とデータ取り込み信号との間のタイミングのずれを調整する。

【0010】

このように構成されたタイミング調整装置によれば、CPUの温度変化に起因したデータ信号とデータ取り込み信号との間のタイミング(以下、信号間タイミングともいう)のずれによるデータ不一致が発生する前に、CPUの温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0011】

また請求項1に記載のタイミング調整装置では、請求項2に記載のように、CPUの温度を検出するCPU温度検出手段を備え、CPU温度情報は、CPU温度検出手段により検出された温度を示すものであるようにするとよい。

【0012】

なお、CPUがメモリへ頻繁にアクセスする場合はCPU内部の動作率も一般的に高く、メモリアクセスによりCPU温度が上昇すると考えられる。

そこで請求項1に記載のタイミング調整装置では、請求項3に記載のように、CPU温度検出手段がCPUの温度を検出するとともに、メモリバス監視手段が、CPUがメモリへのアクセスを行うアクセス頻度を検出し、更に、CPU温度予測手段が、メモリバス監視手段により検出されたアクセス頻度と、CPU温度検出手段により検出されたCPUの温度とに基づいて、その後のCPUの温度を予測し、CPU温度情報は、CPU温度予測手段により予測された温度を示すものであるようにしてもよい。

【0013】

このように構成されたタイミング調整装置よれば、CPU温度の変化を予測することにより、その変化を見越して事前に信号間タイミングを調整することが可能となり、データ不一致の発生を更に抑制することができる。

【0014】

そして、一般にCPUの動作電力は、CPUがメモリへアクセスしている時間であるアクセス長と、データ信号がローレベルからハイレベルまたはハイレベルからローレベルへ変化する変化率であるトグル率に比例すると考えられるので、メモリアクセスによるCPUの温度上昇も、アクセス長とトグル率に比例すると考えられる。

【0015】

そこで請求項3に記載のタイミング調整装置では、請求項4に記載のように、メモリバス監視手段は、アクセス長とトグル率をアクセス頻度として検出し、CPU温度予測手段は、アクセス長とトグル率との積に基づいて、CPUがメモリへのアクセスを行うことによるCPUの温度上昇を予測するようにしてもよい。

【0016】

また、CPUがメモリにアクセスしているときに、データ信号とデータ取り込み信号との間のタイミングを変化させると、当該アクセスが不安定になるおそれがあるので、請求項1から請求項4の何れかに記載のタイミング調整装置では、請求項5に記載のように、CPUがメモリにアクセスしている場合に、温度ずれ調整手段の動作を禁止する調整禁止手段を備えるようにするとよい。

【0017】

また、放熱の機構によってはCPUとメモリとの温度が大きく異なる場合があり、この場合には、メモリの温度によって信号間タイミングが変化する可能性があるので、請求項1から請求項5の何れかに記載のタイミング調整装置では、請求項6に記載のように、メモリの温度を検出するメモリ温度検出手段を備え、温度ずれ調整手段は、CPU温度情報取得手段により取得されたCPU温度情報に加えて、更に、メモリ温度検出手段により検出されたメモリの温度に基づいて、データ信号とデータ取り込み信号との間のタイミングのずれを調整するようにするとよい。

【発明を実施するための最良の形態】

【0018】

(第1実施形態)

以下に本発明の第1実施形態について図面とともに説明する。

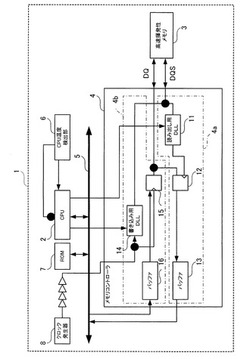

図1は、本発明が適用された実施形態のLSI1の構成を示すブロック図である。

【0019】

LSI1は、カーナビゲーションシステムに適用されるシステムLSIである。

LSI1は、図1に示すように、LSI1を制御するためのデータが格納されたROM7と、ROM7から読み込んだデータ等を一時的に格納する高速揮発性メモリ3(例えば、DDR2メモリ)と、高速揮発性メモリ3に対するデータの書き込みと読み込みを制御するメモリコントローラ4と、メモリコントローラ4の動作を制御するCPU2と、CPU2とROM7とメモリコントローラ4とをデータ入出力可能に接続するシステムバス5と、CPU2の温度を検出するCPU温度検出部6と、データ取り込み信号DQSを出力するクロック発生器8を備える。

【0020】

これらのうちメモリコントローラ4は、高速揮発性メモリ3からデータを読み出す読み出し部4aと、高速揮発性メモリ3にデータを書き込む書き込み部4bとから構成される。

【0021】

読み出し部4aは、読み出し用DLL11と、Dタイプのフリップフロップ(DFF)回路12と、バッファ13とを備える。

そして読み出し用DLL11は、高速揮発性メモリ3から入力したデータ取り込み信号DQSをCPU2によるレジスタ設定で設定された時間分遅延させて出力する。またDFF回路12は、読み出し用DLL11からデータ取り込み信号DQSを入力するとともに高速揮発性メモリ3からデータ信号DQを入力し、データ信号DQがハイレベルの時にデータ取り込み信号DQSがローレベルからハイレベルに変化するとハイレベルにセットし、このハイレベルの信号をバッファ13に出力する。更にバッファ13は、DFF回路12から入力した信号を一時的に記憶し、その後、システムバス5を介してCPU2に出力する。

【0022】

書き込み部4bは、書き込み用DLL14と、Dタイプのフリップフロップ(DFF)回路15と、バッファ16とを備える。

そして書き込み用DLL14は、クロック発生器8から入力したデータ取り込み信号DQSをCPU2によるレジスタ設定で設定された時間分遅延させて高速揮発性メモリ3に出力する。またバッファ16は、CPU2からシステムバス5を介して入力したデータ信号DQを一時的に記憶し、その後DFF回路15に出力する。またDFF回路15は、クロック発生器8からデータ取り込み信号DQSを入力するとともに、バッファ16からデータ信号DQを入力し、データ信号DQがハイレベルの時にデータ取り込み信号DQSがローレベルからハイレベルに変化するとハイレベルにセットし、このハイレベルの信号を高速揮発性メモリ3に出力する。

【0023】

このように構成されたLSI1において、CPU2は、高速揮発性メモリ3にデータを書き込む書き込み処理と、高速揮発性メモリ3からデータを読み出す読み出し処理を実行する。

【0024】

まず、CPU2が実行する書き込み処理の手順を、図2を用いて説明する。図2は書き込み処理を示すフローチャートである。この書き込み処理は、CPU2が起動(電源オン)している間に繰り返し実行される処理である。

【0025】

この書き込み処理が実行されると、CPU2は、まずS10にて、高速揮発性メモリ3にデータを書き込むための書き込み要求があるか否かを判断する。ここで、書き込み要求がない場合には(S10:NO)、書き込み処理を一旦終了する。一方、書き込み要求がある場合には(S10:YES)、S20にて、CPU温度検出部6にCPU2の温度を検出させて、S30にて、CPU温度検出部6による検出結果に基づいて、書き込み用DLL14によるタイミング調整が必要であるか否かを判断する。

【0026】

ここで、タイミング調整が必要でないと判断した場合には(S30:NO)、書き込み処理を一旦終了する。一方、タイミング調整が必要であると判断した場合には(S30:YES)、S40にて、CPU温度検出部6による検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行うことにより、遅延時間を調整する。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU温度検出部6による検出結果に応じた時間分遅延して、書き込み用DLL14から出力される。そしてS50にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3にデータを書き込み、書き込み処理を一旦終了する。

【0027】

次に、CPU2が実行する読み出し処理の手順を、図3を用いて説明する。図3は読み出し処理を示すフローチャートである。この読み出し処理は、CPU2が起動(電源オン)している間に繰り返し実行される処理である。

【0028】

この読み出し処理が実行されると、CPU2は、まずS110にて、高速揮発性メモリ3からデータを読み出すための読み出し要求があるか否かを判断する。ここで、読み出し要求がない場合には(S110:NO)、読み出し処理を一旦終了する。一方、読み出し要求がある場合には(S110:YES)、S120にて、CPU温度検出部6にCPU2の温度を検出させて、S130にて、CPU温度検出部6による検出結果に基づいて、読み出し用DLL11によるタイミング調整が必要であるか否かを判断する。

【0029】

ここで、タイミング調整が必要でないと判断した場合には(S130:NO)、読み出し処理を一旦終了する。一方、タイミング調整が必要であると判断した場合には(S130:YES)、S140にて、CPU温度検出部6による検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行うことにより、遅延時間を調整する。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU温度検出部6による検出結果に応じた時間分遅延して、読み出し用DLL11から出力される。そしてS150にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3からデータを読み出し、読み出し処理を一旦終了する。

【0030】

このように構成されたLSI1では、CPU2の温度を検出し(S20,S120)、CPU2の温度に応じた時間分遅延して、データ取り込み信号DQSを出力する(S40,S140)。

【0031】

このため、CPU2の温度変化に起因したデータ信号DQとデータ取り込み信号DQSとの間のタイミング(以下、信号間タイミングともいう)のずれによるデータ不一致が発生する前に、CPU2の温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0032】

以上説明した実施形態において、LSI1は本発明におけるタイミング調整装置、S20及びS120の処理は本発明におけるCPU温度情報取得手段、S40及びS140の処理は本発明における温度ずれ調整手段、CPU温度検出部6は本発明におけるCPU温度検出手段である。

【0033】

(第2実施形態)

以下に本発明の第2実施形態について図面とともに説明する。尚、第2実施形態では、第1実施形態と異なる部分のみを説明する。

【0034】

第2実施形態におけるLSI1は、読み出し用DLL11及び書き込み用DLL14の構成が変更された点と、温度比較器26を設けてCPU2の代わりに温度比較器26がタイミング調整を行うように構成された点以外は第1実施形態と同じである。

【0035】

図4(a)は、第2実施形態の高速揮発性メモリ3、メモリコントローラ4及び温度比較器26を示すブロック図である。

読み出し用DLL11は、図4(a)に示すように、遅延時間の異なる4つのDLL21〜24と、セレクタ25とから構成される。

【0036】

DLL21〜24はそれぞれ、高速揮発性メモリ3からデータ取り込み信号DQSを入力し、このデータ取り込み信号DQSを予め設定された遅延時間遅らせて出力するように構成されている。尚、DLL21→DLL22→DLL23→DLL24の順に遅延時間が長くなるように設定されている。またセレクタ25は、DLL21〜24からの信号を入力して、温度比較器26からの選択信号(後述)に基づき、DLL21〜24の何れかの信号を出力する。

【0037】

温度比較器26は、CPU温度検出部6(図4(a)では不図示)による検出結果を示す信号を入力し、この信号に基づいて、DLL21〜24の何れかを選択するための選択信号を出力する。具体的には、温度比較器26は、図4(b)に示すように、温度がt1未満ではDLL21を選択し、温度がt1以上t2未満ではDLL22を選択し、温度がt2以上t3未満ではDLL23を選択し、温度がt3以上ではDLL23を選択する選択信号を出力する。

【0038】

また、第2実施形態の書き込み用DLL14は、第2実施形態の読み出し用DLL11と同様に構成される。

このように構成されたLSI1では、CPU温度検出部6による検出結果を示す信号を入力し、この信号に基づいて、DLL21〜24の何れかを選択することにより、CPU2の温度に応じた時間分遅延して、データ取り込み信号DQSを出力する。

【0039】

このため、CPU2の温度変化に起因したデータ信号DQとデータ取り込み信号DQSとの間のタイミング(信号間タイミング)のずれによるデータ不一致が発生する前に、CPU2の温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0040】

以上説明した実施形態において、温度比較器26は本発明におけるCPU温度情報取得手段、温度比較器26、読み出し用DLL11及び書き込み用DLL14は本発明における温度ずれ調整手段である。

【0041】

(第3実施形態)

以下に本発明の第3実施形態について図面とともに説明する。尚、第3実施形態では、第1実施形態と異なる部分のみを説明する。

【0042】

第3実施形態におけるLSI1は、読み出し用DLL11及び書き込み用DLL14の構成が変更された点と、メモリI/Fシーケンサ37及びMAX温度検出回路38を設けてCPU2の代わりにメモリI/Fシーケンサ37及びMAX温度検出回路38を用いてタイミング調整を行うように構成された点以外は第1実施形態と同じである。

【0043】

図5(a)は、第3実施形態の高速揮発性メモリ3、メモリコントローラ4及びMAX温度検出回路38を示すブロック図である。

メモリコントローラ4は、読み出し用DLL11、DFF回路12及びバッファ13等に加えてメモリI/Fシーケンサ37を備える。

【0044】

メモリI/Fシーケンサ37は、CPU2が高速揮発性メモリ3にアクセス中であるか否かを監視し、アクセス中である場合には、その旨を示すアクセス中信号を出力する。

MAX温度検出回路38は、CPU温度検出部6(図5(a)では不図示)による検出結果を示す信号を入力し、この信号に基づいて、CPU2の最高温度を保持するとともに、この最高温度を示す値を示す信号(以下、CPU最高温度信号という)を例えば2bitに正規化して出力する。

【0045】

読み出し用DLL11は、図5(a)に示すように、遅延時間の異なる4つのDLL31〜34と、セレクタ35と、DFF回路36とから構成される。

DLL31〜34はそれぞれ、高速揮発性メモリ3からデータ取り込み信号DQSを入力し、このデータ取り込み信号DQSを予め設定された遅延時間遅らせて出力するように構成されている。尚、DLL31〜34は、DLL31→DLL32→DLL33→DLL34の順に遅延時間が長くなるように設定されている。またセレクタ35は、DLL31〜34からの信号を入力して、MAX温度検出回路38からのCPU最高温度信号に基づき、DLL31〜34の何れかの信号を出力する。

【0046】

またDFF回路36は、メモリI/Fシーケンサ37からのアクセス中信号を反転させた信号(以下、反転アクセス中信号という)を入力するとともに、MAX温度検出回路38からCPU最高温度信号を入力し、反転アクセス中信号がローレベルからハイレベルに変化したとき(即ち、アクセス中から非アクセス中に切り替わった時点)のCPU最高温度信号を保持して、出力する。

【0047】

これによりLSI1は、図5(b)に示すように、CPU2が高速揮発性メモリ3にアクセス中の最高温度(指示m1,m2,m3を参照)を保持し、動作中から非動作中に変化したタイミング(タイミングth1,th2,th3を参照)で、最高温度に対応したDLL31〜34の何れかに設定する。

【0048】

また、第3実施形態の書き込み用DLL14は、第3実施形態の読み出し用DLL11と同様に構成される。

このように構成されたLSI1では、アクセス中におけるCPU最高温度を保持し、アクセス中から非アクセス中に切り替わった時点で、この保持したCPU最高温度に応じた時間分遅延して、データ取り込み信号DQSを出力する。

【0049】

このため、アクセス中において急にデータ信号DQとデータ取り込み信号DQSとの間のタイミングのずれが変化することがなくなり、高速揮発性メモリ3へのアクセスを安定させることができる。

【0050】

以上説明した実施形態において、MAX温度検出回路38は本発明におけるCPU温度情報取得手段、MAX温度検出回路38、読み出し用DLL11及び書き込み用DLL14は本発明における温度ずれ調整手段、メモリI/Fシーケンサ37及びDFF回路36は本発明における調整禁止手段である。

【0051】

(第4実施形態)

以下に本発明の第4実施形態について図面とともに説明する。尚、第4実施形態では、第1実施形態と異なる部分のみを説明する。

【0052】

第4実施形態におけるLSI1は、書き込み処理と読み出し処理の代わりに書き込み・読み出し処理を実行する点以外は第1実施形態と同じである。

ここで、CPU2が実行する書き込み・読み出し処理の手順を、図6を用いて説明する。図6は書き込み・読み出し処理を示すフローチャートである。この書き込み・読み出し処理は、CPU2が起動(電源オン)すると開始される処理である。

【0053】

この書き込み・読み出し処理が実行されると、CPU2は、まずS210にて、リセットを行い、読み出し用DLL11及び書き込み用DLL14の遅延時間を設定するための情報(以下、遅延時間設定情報ともいう)を初期化する。例えば、遅延時間がないことを示す値に遅延時間設定情報を設定する。

【0054】

そしてS220にて、CPU温度検出部6にCPU2の温度を検出させて、S230にて、CPU温度検出部6による検出結果に基づいて、読み出し用DLL11及び書き込み用DLL14に対してレジスタ設定を行うことにより、遅延時間を設定する。

【0055】

その後S240にて、CPU温度検出部6による検出結果に基づいて、CPU2の最高温度を検出したか否かを判断する。ここで、最高温度を検出していない場合には(S240:NO)、S270に移行する。一方、最高温度を検出した場合には(S240:YES)、S250にて、CPU2が高速揮発性メモリ3にアクセス中であるか否かを判断する。

【0056】

ここで、アクセス中である場合には(S250:YES)、S250の処理を繰り返す。一方、アクセス中でない場合には(S250:NO)、S260にて、検出した最高温度に基づいて、読み出し用DLL11及び書き込み用DLL14に対してレジスタ設定をするための設定値(以下、DLL設定値という)を決定し、このDLL設定値で、読み出し用DLL11及び書き込み用DLL14に対してレジスタ設定を行うことにより、遅延時間を調整する。

【0057】

尚、DLL設定値は、本実施形態では、DLL0,DLL1,DLL2,DLL3の4種類有り、DLL0→DLL1→DLL2→DLL3の順に遅延時間が長くなるように設定されている。

【0058】

そしてS270に移行すると、高速揮発性メモリ3にデータを書き込むための書き込み要求があるか否かを判断する。ここで、書き込み要求がない場合には(S270:NO)、S290に移行する。一方、書き込み要求がある場合には(S270:YES)、S280にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3にデータを書き込み、S290に移行する。

【0059】

そしてS290に移行すると、高速揮発性メモリ3からデータを読み出すための読み出し要求があるか否かを判断する。ここで、読み出し要求がない場合には(S290:NO)、240に移行し、上述の処理を繰り返す。一方、読み出し要求がある場合には(S290:YES)、S300にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3からデータを読み出す。その後に240に移行し、上述の処理を繰り返す。

【0060】

これによりLSI1は、図7に示すように、CPU2が高速揮発性メモリ3にアクセス中に最高温度(指示m11,m12,m13を参照)となると、動作中から非動作中に変化したタイミング(タイミングth11,th12,th13を参照)で、最高温度に対応したDLL設定値(DLL0,DLL1,DLL2,DLL3の何れか)に設定する。

【0061】

このように構成されたLSI1では、アクセス中から非アクセス中に切り替わった時点で、CPU2の最高温度に応じた時間分遅延して、データ取り込み信号DQSを出力する(S250,S260)。

【0062】

このため、アクセス中において急にデータ信号DQとデータ取り込み信号DQSとの間のタイミングのずれが変化することがなくなり、高速揮発性メモリ3へのアクセスを安定させることができる。

【0063】

以上説明した実施形態において、S240の処理は本発明におけるCPU温度情報取得手段、S260の処理は本発明における温度ずれ調整手段、S250の処理は本発明における調整禁止手段である。

【0064】

(第5実施形態)

以下に本発明の第5実施形態について図面とともに説明する。

図8は、第5実施形態のLSI50の構成を示すブロック図である。

【0065】

LSI50は、図1に示すように、DDR2メモリ55と、DDR2メモリ55へのアクセスを行うためのメモリバス53と、DDR2メモリ55へのアクセスを制御するDDR2I/F54と、DDR2I/F54の動作を制御するCPU51と、CPU51とメモリバス53とをデータ入出力可能に接続するシステムバス52と、メモリバス53の状態を監視するバスモニタ56と、CPU51の温度を検出する温度検出部57とを備える。

【0066】

これらのうちDDR2I/F54は、DDR2メモリ55から入力したデータ取り込み信号をCPU51によるレジスタ設定で設定された時間分遅延させて出力する読み出し用DLL(不図示)と、不図示の信号発生回路から入力したデータ取り込み信号をCPU51によるレジスタ設定で設定された時間分遅延させてDDR2メモリ55に出力する書き込み用DLL(不図示)とを備える。

【0067】

このように構成されたLSI50において、CPU51は、DDR2I/F54の読み出し用DLLと書き込み用DLLの遅延時間を調整するDLL調整処理を実行する。

ここで、CPU51が実行するDLL調整処理の手順を、図9を用いて説明する。図9はDLL調整処理を示すフローチャートである。このDLL調整処理は、CPU51が起動(電源オン)している間に繰り返し実行される処理である。

【0068】

このDLL調整処理が実行されると、CPU51は、まずS410にて、バスモニタ56による監視結果に基づいて、DDR2メモリ55へのアクセス頻度を算出する。またS420にて、温度検出部57にCPU51の温度を検出させる。

【0069】

そしてS430にて、S410にて算出されたアクセス頻度と、S420で検出したCPU51の温度に基づいて、CPU51の温度を予測する。

例えば、DDR2メモリ55へのアクセスによりCPU51の温度が上昇する場合におけるCPU51の予測温度Tc1は、下式(1)により算出される。

【0070】

Tc1 = Tc0 + α × LNG × t ・・・(1)

尚、式(1)における「Tc0」はS420で検出されたCPU51の温度、「α」はボードにより決定される定数、「LNG」はDDR2メモリ55へアクセスしている時間を示すアクセス長、「t」はデータ信号がローレベルからハイレベルまたはハイレベルからローレベルへ変化する変化率を示すトグル率を表す。

【0071】

その後440にて、S430で予測したCPU51の温度に基づいて、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定をするための設定値(以下、DLL設定値という)を決定し、このDLL設定値で、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定を行うことにより、遅延時間を調整し、DLL調整処理を一旦終了する。尚、DLL設定値は、DLL0,DLL1,DLL2,DLL3の4種類存在し、DLL0→DLL1→DLL2→DLL3の順に遅延時間が長くなるように設定されている。

【0072】

このように構成されたLSI50のDLL調整の例を図10に示す。

図10に示すように、タイミングTh21では、シングルアクセスSGLが行われることによるCPU51の温度を予測した結果、DLL設定値をDLL1からDLL2へ変更する。またタイミングTh22では、シングルアクセスSGLが行われることによるCPU51の温度を予測した結果、DLL設定値の変更を行わない。またタイミングTh23では、アクセスが暫くないことによるCPU51の温度を予測した結果、DLL設定値をDLL2からDLL1へ変更する。またタイミングTh24では、8バーストアクセスBUST8が行われることによるCPU51の温度を予測した結果、DLL設定値をDLL1からDLL3へ変更する。またタイミングTh25では、アクセスが暫くないことによるCPU51の温度を予測した結果、DLL設定値をDLL3からDLL2へ変更する。またタイミングTh26では、4バーストアクセスBUST4が行われることによるCPU51の温度を予測した結果、DLL設定値の変更を行わない。

【0073】

このように構成されたLSI50では、バスモニタ56によりメモリバス53の状態を監視し、この監視結果に基づいて、DDR2メモリ55へのアクセス頻度を算出するとともに(S410)、CPU2の温度を検出し(S420)、更に、算出したアクセス頻度と、検出したCPU2の温度とに基づいて、CPU51の温度を予測する(S430)。そして、予測したCPU2の温度に応じた時間分遅延して、データ取り込み信号DQSを出力する(S440)。

【0074】

このため、CPU温度の変化を見越して事前に、データ信号DQとデータ取り込み信号DQSとの間のタイミング(信号間タイミング)を調整することが可能となり、データ不一致の発生を更に抑制することができる。

【0075】

以上説明した実施形態において、S420の処理は本発明におけるCPU温度検出手段、バスモニタ56及びS410の処理は本発明におけるメモリバス監視手段、S430の処理はCPU温度予測手段である。

【0076】

(第6実施形態)

以下に本発明の第6実施形態について図面とともに説明する。尚、第6実施形態では、第5実施形態と異なる部分のみを説明する。

【0077】

第6実施形態におけるLSI50は、LSI50の構成と、DLL調整処理が変更される点以外は第5実施形態と同じである。

図11は、第6実施形態のLSI50の構成を示すブロック図である。

【0078】

第6実施形態のLSI50は、図11に示すように、DDR2メモリ55の温度を検出する温度検出部58が追加された点以外は第5実施形態と同じである。

次に、CPU51が実行するDLL調整処理の手順を、図12を用いて説明する。図12は第6実施形態のDLL調整処理を示すフローチャートである。このDLL調整処理は、CPU51が起動(電源オン)している間に繰り返し実行される処理である。

【0079】

このDLL調整処理が実行されると、CPU51は、まずS510にて、DDR2メモリ55にデータを書き込むための書き込み要求、またはDDR2メモリ55からデータを読み出すための読み出し要求(以下、書き込み要求と読み出し要求とをまとめて動作要求という)があるか否かを判断する。ここで、動作要求がない場合には(S510:NO)、DLL調整処理を一旦終了する。一方、動作要求がある場合には(S510:YES)、S520にて、温度検出部57にCPU51の温度Tc(CPU)を検出させる。更にS530にて、温度検出部58にDDR2メモリ55の温度Tc(DDR2)を検出させる。

【0080】

そしてS540にて、S520で検出した温度Tc(CPU)と、S530で検出した温度Tc(DDR2)に基づいて、図13に示すDLL設定テーブルT1を参照して、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定をするための設定値(以下、DLL設定値という)を決定し、このDLL設定値で、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定を行うことにより、遅延時間を調整し、DLL調整処理を一旦終了する。

【0081】

尚、DLL設定テーブルT1では、図13に示すように、温度Tc(CPU)及び温度Tc(DDR2)それぞれを、4つの温度範囲T0(−40℃〜0℃)、T1(0℃〜60℃)、T2(60℃〜85℃)、T3(85℃〜115℃)に分けて、温度Tc(CPU)の4つの温度範囲と、温度Tc(DDR2)の4つの温度範囲の組合せに応じて、DLL設定値(図13中のDLL0,DLL1,DLL2,DLL3)が設定されている。また、DLL設定値は、DLL0→DLL1→DLL2→DLL3の順に遅延時間が長くなるように設定されている。

【0082】

このように構成されたLSI50では、CPU51の温度に加えて、更に、DDR2メモリ55の温度に基づいて、データ信号DQとデータ取り込み信号DQSとの間のタイミング(信号間タイミング)を調整する(S540)。

【0083】

このため、CPU51及びDDR2メモリ55の温度変化に起因した信号間タイミングのずれによるデータ不一致が発生する前に、CPU51及びDDR2メモリ55の温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0084】

以上、本発明の一実施形態について説明したが、本発明は上記実施形態に限定されるものではなく、本発明の技術的範囲に属する限り種々の形態を採ることができる。

例えば上記実施形態においては、CPUと高速揮発性メモリとの間の信号間タイミングを調整するものを示したが、高速揮発性メモリに限定されるものではなく、データ信号とデータ取り込み信号とを用いてデータの書き込み及び読み出しを行うメモリであればよい。

【図面の簡単な説明】

【0085】

【図1】LSI1の構成を示すブロック図である。

【図2】書き込み処理を示すフローチャートである。

【図3】読み出し処理を示すフローチャートである。

【図4】第2実施形態のメモリコントローラ4及び温度比較器26を示すブロック図である。

【図5】第3実施形態のメモリコントローラ4及びMAX温度検出回路38を示すブロック図、及びDLL調整タイミングを説明する図である。

【図6】書き込み・読み出し処理を示すフローチャートである。

【図7】第4実施形態のDLL調整タイミングを説明する図である。

【図8】第5実施形態のLSI50の構成を示すブロック図である。

【図9】第5実施形態のDLL調整処理を示すフローチャートである。

【図10】第5実施形態のDLL調整を説明する図である。

【図11】第6実施形態のLSI50の構成を示すブロック図である。

【図12】第6実施形態のDLL調整処理を示すフローチャートである。

【図13】DLL設定テーブルT1の構成を示す図である。

【図14】データ信号DQとデータ取り込み信号DQSとの間のタイミングずれを説明する図である。

【図15】データ信号DQとデータ取り込み信号DQSとの間の温度によるタイミングずれを説明する図である。

【符号の説明】

【0086】

1,50…LSI、2,51…CPU3…高速揮発性メモリ、4…メモリコントローラ、4a…読み出し部、4b…書き込み部、5…システムバス、6…CPU温度検出部、7…ROM、8…クロック発生器、11…読み出し用DLL、12,15,36…DFF回路、14…書き込み用DLL、13,16…バッファ、21〜24,31〜34…DLL、25,35…セレクタ、26…温度比較器、37…メモリI/Fシーケンサ、38…MAX温度検出回路、52…システムバス、53…メモリバス、54…DDR2I/F、55…DDR2メモリ、56…バスモニタ、57,58…温度検出部、DQ…データ信号、DQS…データ取り込み信号

【技術分野】

【0001】

本発明は、メモリアクセスのタイミングを調整するタイミング調整装置に関する。

【背景技術】

【0002】

DDR2メモリ等の高速揮発性メモリを使用する場合には、データ信号とデータ取り込み信号との間のタイミングのずれが問題となる。例えば、図14(a)に示すように、DDR2メモリ110からコアLSI120へデータ信号DQとデータ取り込み信号DQSを出力する場合において、DDR2メモリ110から信号が出力された直後(図14(a)の指示n11を参照)は、図14(b)に示すように、データ信号DQとデータ取り込み信号DQSとの間のタイミングが合っている。しかし、コアLSI120で取り込む直前(図14(a)の指示n12を参照)は、図14(c)に示すように、ボードのスキューでデータ信号DQとデータ取り込み信号DQSとの間のタイミングがずれる(図14(c)の矢印Y11を参照)。

【0003】

そこで、コアLSI120は、タイミング調整回路(図14(a)中のDLL121)を備え、図14(d)に示すように、このタイミング調整回路(DLL121)でデータ取り込み信号DQSを遅延調整することで(図14(d)の矢印Y12を参照)、ボード設計毎のスキューを吸収するように設計される。

【0004】

ところで、カーナビゲーション用LSI等の車載LSIには、大容量の揮発性メモリが搭載されている。そして車載LSIに搭載される揮発性メモリは、広い温度範囲(例えば−40℃〜95℃)での正常動作が要求される。

【0005】

しかし今後、揮発性メモリが533MHzから667MHz、800MHz、1GHzと高速化すると、タイミング調整できるウィンドウが狭くなる。このため、タイミング調整量がボードに対して一定では、図15(a)に示すように、或る温度(図では−40℃)では、タイミング調整回路による調整(図15(a)の矢印Y21を参照)によってタイミングのずれを調整することができるが、図15(b)に示すように、別の温度(図では85℃)では、タイミング調整回路による調整(図15(b)の矢印Y22を参照)によってタイミングのずれを調整することができなくなる(図中の指示n21を参照)おそれがある。

【0006】

そして、上記のようなタイミングのずれを調整するために、従来、データ信号の入力に対してデータ取り込み信号の入力が速いか遅いかを検出し、この検出結果に基づいて、データ信号とデータ取り込み信号との間のタイミングのずれを調整する技術が知られている(例えば、特許文献1参照)。

【特許文献1】特開平8−237101号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1に記載の技術では、タイミングのずれを検出し、次回以降のデータ信号の入力におけるタイミングのずれを調整する。このため、タイミングのずれを検出した時点では、タイミングのずれを調整することができず、データ信号の取り込みの際に、データ信号の示す内容を正確に取り込むことができないというデータの不一致が発生するおそれがあった。

【0008】

本発明は、こうした問題に鑑みなされたものであり、温度変化に起因したタイミングのずれによるデータ不一致の発生を抑制する技術を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するためになされた請求項1に記載のタイミング調整装置では、CPU温度情報取得手段が、CPUの温度についての情報であるCPU温度情報を取得する。そして温度ずれ調整手段が、CPU温度情報取得手段により取得されたCPU温度情報に基づいて、データ取り込み信号の入出力を予め設定された遅延時間遅らせることによって、データ信号とデータ取り込み信号との間のタイミングのずれを調整する。

【0010】

このように構成されたタイミング調整装置によれば、CPUの温度変化に起因したデータ信号とデータ取り込み信号との間のタイミング(以下、信号間タイミングともいう)のずれによるデータ不一致が発生する前に、CPUの温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0011】

また請求項1に記載のタイミング調整装置では、請求項2に記載のように、CPUの温度を検出するCPU温度検出手段を備え、CPU温度情報は、CPU温度検出手段により検出された温度を示すものであるようにするとよい。

【0012】

なお、CPUがメモリへ頻繁にアクセスする場合はCPU内部の動作率も一般的に高く、メモリアクセスによりCPU温度が上昇すると考えられる。

そこで請求項1に記載のタイミング調整装置では、請求項3に記載のように、CPU温度検出手段がCPUの温度を検出するとともに、メモリバス監視手段が、CPUがメモリへのアクセスを行うアクセス頻度を検出し、更に、CPU温度予測手段が、メモリバス監視手段により検出されたアクセス頻度と、CPU温度検出手段により検出されたCPUの温度とに基づいて、その後のCPUの温度を予測し、CPU温度情報は、CPU温度予測手段により予測された温度を示すものであるようにしてもよい。

【0013】

このように構成されたタイミング調整装置よれば、CPU温度の変化を予測することにより、その変化を見越して事前に信号間タイミングを調整することが可能となり、データ不一致の発生を更に抑制することができる。

【0014】

そして、一般にCPUの動作電力は、CPUがメモリへアクセスしている時間であるアクセス長と、データ信号がローレベルからハイレベルまたはハイレベルからローレベルへ変化する変化率であるトグル率に比例すると考えられるので、メモリアクセスによるCPUの温度上昇も、アクセス長とトグル率に比例すると考えられる。

【0015】

そこで請求項3に記載のタイミング調整装置では、請求項4に記載のように、メモリバス監視手段は、アクセス長とトグル率をアクセス頻度として検出し、CPU温度予測手段は、アクセス長とトグル率との積に基づいて、CPUがメモリへのアクセスを行うことによるCPUの温度上昇を予測するようにしてもよい。

【0016】

また、CPUがメモリにアクセスしているときに、データ信号とデータ取り込み信号との間のタイミングを変化させると、当該アクセスが不安定になるおそれがあるので、請求項1から請求項4の何れかに記載のタイミング調整装置では、請求項5に記載のように、CPUがメモリにアクセスしている場合に、温度ずれ調整手段の動作を禁止する調整禁止手段を備えるようにするとよい。

【0017】

また、放熱の機構によってはCPUとメモリとの温度が大きく異なる場合があり、この場合には、メモリの温度によって信号間タイミングが変化する可能性があるので、請求項1から請求項5の何れかに記載のタイミング調整装置では、請求項6に記載のように、メモリの温度を検出するメモリ温度検出手段を備え、温度ずれ調整手段は、CPU温度情報取得手段により取得されたCPU温度情報に加えて、更に、メモリ温度検出手段により検出されたメモリの温度に基づいて、データ信号とデータ取り込み信号との間のタイミングのずれを調整するようにするとよい。

【発明を実施するための最良の形態】

【0018】

(第1実施形態)

以下に本発明の第1実施形態について図面とともに説明する。

図1は、本発明が適用された実施形態のLSI1の構成を示すブロック図である。

【0019】

LSI1は、カーナビゲーションシステムに適用されるシステムLSIである。

LSI1は、図1に示すように、LSI1を制御するためのデータが格納されたROM7と、ROM7から読み込んだデータ等を一時的に格納する高速揮発性メモリ3(例えば、DDR2メモリ)と、高速揮発性メモリ3に対するデータの書き込みと読み込みを制御するメモリコントローラ4と、メモリコントローラ4の動作を制御するCPU2と、CPU2とROM7とメモリコントローラ4とをデータ入出力可能に接続するシステムバス5と、CPU2の温度を検出するCPU温度検出部6と、データ取り込み信号DQSを出力するクロック発生器8を備える。

【0020】

これらのうちメモリコントローラ4は、高速揮発性メモリ3からデータを読み出す読み出し部4aと、高速揮発性メモリ3にデータを書き込む書き込み部4bとから構成される。

【0021】

読み出し部4aは、読み出し用DLL11と、Dタイプのフリップフロップ(DFF)回路12と、バッファ13とを備える。

そして読み出し用DLL11は、高速揮発性メモリ3から入力したデータ取り込み信号DQSをCPU2によるレジスタ設定で設定された時間分遅延させて出力する。またDFF回路12は、読み出し用DLL11からデータ取り込み信号DQSを入力するとともに高速揮発性メモリ3からデータ信号DQを入力し、データ信号DQがハイレベルの時にデータ取り込み信号DQSがローレベルからハイレベルに変化するとハイレベルにセットし、このハイレベルの信号をバッファ13に出力する。更にバッファ13は、DFF回路12から入力した信号を一時的に記憶し、その後、システムバス5を介してCPU2に出力する。

【0022】

書き込み部4bは、書き込み用DLL14と、Dタイプのフリップフロップ(DFF)回路15と、バッファ16とを備える。

そして書き込み用DLL14は、クロック発生器8から入力したデータ取り込み信号DQSをCPU2によるレジスタ設定で設定された時間分遅延させて高速揮発性メモリ3に出力する。またバッファ16は、CPU2からシステムバス5を介して入力したデータ信号DQを一時的に記憶し、その後DFF回路15に出力する。またDFF回路15は、クロック発生器8からデータ取り込み信号DQSを入力するとともに、バッファ16からデータ信号DQを入力し、データ信号DQがハイレベルの時にデータ取り込み信号DQSがローレベルからハイレベルに変化するとハイレベルにセットし、このハイレベルの信号を高速揮発性メモリ3に出力する。

【0023】

このように構成されたLSI1において、CPU2は、高速揮発性メモリ3にデータを書き込む書き込み処理と、高速揮発性メモリ3からデータを読み出す読み出し処理を実行する。

【0024】

まず、CPU2が実行する書き込み処理の手順を、図2を用いて説明する。図2は書き込み処理を示すフローチャートである。この書き込み処理は、CPU2が起動(電源オン)している間に繰り返し実行される処理である。

【0025】

この書き込み処理が実行されると、CPU2は、まずS10にて、高速揮発性メモリ3にデータを書き込むための書き込み要求があるか否かを判断する。ここで、書き込み要求がない場合には(S10:NO)、書き込み処理を一旦終了する。一方、書き込み要求がある場合には(S10:YES)、S20にて、CPU温度検出部6にCPU2の温度を検出させて、S30にて、CPU温度検出部6による検出結果に基づいて、書き込み用DLL14によるタイミング調整が必要であるか否かを判断する。

【0026】

ここで、タイミング調整が必要でないと判断した場合には(S30:NO)、書き込み処理を一旦終了する。一方、タイミング調整が必要であると判断した場合には(S30:YES)、S40にて、CPU温度検出部6による検出結果に基づいて、書き込み用DLL14に対してレジスタ設定を行うことにより、遅延時間を調整する。これにより、書き込み用DLL14に入力したデータ取り込み信号DQSは、CPU温度検出部6による検出結果に応じた時間分遅延して、書き込み用DLL14から出力される。そしてS50にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3にデータを書き込み、書き込み処理を一旦終了する。

【0027】

次に、CPU2が実行する読み出し処理の手順を、図3を用いて説明する。図3は読み出し処理を示すフローチャートである。この読み出し処理は、CPU2が起動(電源オン)している間に繰り返し実行される処理である。

【0028】

この読み出し処理が実行されると、CPU2は、まずS110にて、高速揮発性メモリ3からデータを読み出すための読み出し要求があるか否かを判断する。ここで、読み出し要求がない場合には(S110:NO)、読み出し処理を一旦終了する。一方、読み出し要求がある場合には(S110:YES)、S120にて、CPU温度検出部6にCPU2の温度を検出させて、S130にて、CPU温度検出部6による検出結果に基づいて、読み出し用DLL11によるタイミング調整が必要であるか否かを判断する。

【0029】

ここで、タイミング調整が必要でないと判断した場合には(S130:NO)、読み出し処理を一旦終了する。一方、タイミング調整が必要であると判断した場合には(S130:YES)、S140にて、CPU温度検出部6による検出結果に基づいて、読み出し用DLL11に対してレジスタ設定を行うことにより、遅延時間を調整する。これにより、読み出し用DLL11に入力したデータ取り込み信号DQSは、CPU温度検出部6による検出結果に応じた時間分遅延して、読み出し用DLL11から出力される。そしてS150にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3からデータを読み出し、読み出し処理を一旦終了する。

【0030】

このように構成されたLSI1では、CPU2の温度を検出し(S20,S120)、CPU2の温度に応じた時間分遅延して、データ取り込み信号DQSを出力する(S40,S140)。

【0031】

このため、CPU2の温度変化に起因したデータ信号DQとデータ取り込み信号DQSとの間のタイミング(以下、信号間タイミングともいう)のずれによるデータ不一致が発生する前に、CPU2の温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0032】

以上説明した実施形態において、LSI1は本発明におけるタイミング調整装置、S20及びS120の処理は本発明におけるCPU温度情報取得手段、S40及びS140の処理は本発明における温度ずれ調整手段、CPU温度検出部6は本発明におけるCPU温度検出手段である。

【0033】

(第2実施形態)

以下に本発明の第2実施形態について図面とともに説明する。尚、第2実施形態では、第1実施形態と異なる部分のみを説明する。

【0034】

第2実施形態におけるLSI1は、読み出し用DLL11及び書き込み用DLL14の構成が変更された点と、温度比較器26を設けてCPU2の代わりに温度比較器26がタイミング調整を行うように構成された点以外は第1実施形態と同じである。

【0035】

図4(a)は、第2実施形態の高速揮発性メモリ3、メモリコントローラ4及び温度比較器26を示すブロック図である。

読み出し用DLL11は、図4(a)に示すように、遅延時間の異なる4つのDLL21〜24と、セレクタ25とから構成される。

【0036】

DLL21〜24はそれぞれ、高速揮発性メモリ3からデータ取り込み信号DQSを入力し、このデータ取り込み信号DQSを予め設定された遅延時間遅らせて出力するように構成されている。尚、DLL21→DLL22→DLL23→DLL24の順に遅延時間が長くなるように設定されている。またセレクタ25は、DLL21〜24からの信号を入力して、温度比較器26からの選択信号(後述)に基づき、DLL21〜24の何れかの信号を出力する。

【0037】

温度比較器26は、CPU温度検出部6(図4(a)では不図示)による検出結果を示す信号を入力し、この信号に基づいて、DLL21〜24の何れかを選択するための選択信号を出力する。具体的には、温度比較器26は、図4(b)に示すように、温度がt1未満ではDLL21を選択し、温度がt1以上t2未満ではDLL22を選択し、温度がt2以上t3未満ではDLL23を選択し、温度がt3以上ではDLL23を選択する選択信号を出力する。

【0038】

また、第2実施形態の書き込み用DLL14は、第2実施形態の読み出し用DLL11と同様に構成される。

このように構成されたLSI1では、CPU温度検出部6による検出結果を示す信号を入力し、この信号に基づいて、DLL21〜24の何れかを選択することにより、CPU2の温度に応じた時間分遅延して、データ取り込み信号DQSを出力する。

【0039】

このため、CPU2の温度変化に起因したデータ信号DQとデータ取り込み信号DQSとの間のタイミング(信号間タイミング)のずれによるデータ不一致が発生する前に、CPU2の温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0040】

以上説明した実施形態において、温度比較器26は本発明におけるCPU温度情報取得手段、温度比較器26、読み出し用DLL11及び書き込み用DLL14は本発明における温度ずれ調整手段である。

【0041】

(第3実施形態)

以下に本発明の第3実施形態について図面とともに説明する。尚、第3実施形態では、第1実施形態と異なる部分のみを説明する。

【0042】

第3実施形態におけるLSI1は、読み出し用DLL11及び書き込み用DLL14の構成が変更された点と、メモリI/Fシーケンサ37及びMAX温度検出回路38を設けてCPU2の代わりにメモリI/Fシーケンサ37及びMAX温度検出回路38を用いてタイミング調整を行うように構成された点以外は第1実施形態と同じである。

【0043】

図5(a)は、第3実施形態の高速揮発性メモリ3、メモリコントローラ4及びMAX温度検出回路38を示すブロック図である。

メモリコントローラ4は、読み出し用DLL11、DFF回路12及びバッファ13等に加えてメモリI/Fシーケンサ37を備える。

【0044】

メモリI/Fシーケンサ37は、CPU2が高速揮発性メモリ3にアクセス中であるか否かを監視し、アクセス中である場合には、その旨を示すアクセス中信号を出力する。

MAX温度検出回路38は、CPU温度検出部6(図5(a)では不図示)による検出結果を示す信号を入力し、この信号に基づいて、CPU2の最高温度を保持するとともに、この最高温度を示す値を示す信号(以下、CPU最高温度信号という)を例えば2bitに正規化して出力する。

【0045】

読み出し用DLL11は、図5(a)に示すように、遅延時間の異なる4つのDLL31〜34と、セレクタ35と、DFF回路36とから構成される。

DLL31〜34はそれぞれ、高速揮発性メモリ3からデータ取り込み信号DQSを入力し、このデータ取り込み信号DQSを予め設定された遅延時間遅らせて出力するように構成されている。尚、DLL31〜34は、DLL31→DLL32→DLL33→DLL34の順に遅延時間が長くなるように設定されている。またセレクタ35は、DLL31〜34からの信号を入力して、MAX温度検出回路38からのCPU最高温度信号に基づき、DLL31〜34の何れかの信号を出力する。

【0046】

またDFF回路36は、メモリI/Fシーケンサ37からのアクセス中信号を反転させた信号(以下、反転アクセス中信号という)を入力するとともに、MAX温度検出回路38からCPU最高温度信号を入力し、反転アクセス中信号がローレベルからハイレベルに変化したとき(即ち、アクセス中から非アクセス中に切り替わった時点)のCPU最高温度信号を保持して、出力する。

【0047】

これによりLSI1は、図5(b)に示すように、CPU2が高速揮発性メモリ3にアクセス中の最高温度(指示m1,m2,m3を参照)を保持し、動作中から非動作中に変化したタイミング(タイミングth1,th2,th3を参照)で、最高温度に対応したDLL31〜34の何れかに設定する。

【0048】

また、第3実施形態の書き込み用DLL14は、第3実施形態の読み出し用DLL11と同様に構成される。

このように構成されたLSI1では、アクセス中におけるCPU最高温度を保持し、アクセス中から非アクセス中に切り替わった時点で、この保持したCPU最高温度に応じた時間分遅延して、データ取り込み信号DQSを出力する。

【0049】

このため、アクセス中において急にデータ信号DQとデータ取り込み信号DQSとの間のタイミングのずれが変化することがなくなり、高速揮発性メモリ3へのアクセスを安定させることができる。

【0050】

以上説明した実施形態において、MAX温度検出回路38は本発明におけるCPU温度情報取得手段、MAX温度検出回路38、読み出し用DLL11及び書き込み用DLL14は本発明における温度ずれ調整手段、メモリI/Fシーケンサ37及びDFF回路36は本発明における調整禁止手段である。

【0051】

(第4実施形態)

以下に本発明の第4実施形態について図面とともに説明する。尚、第4実施形態では、第1実施形態と異なる部分のみを説明する。

【0052】

第4実施形態におけるLSI1は、書き込み処理と読み出し処理の代わりに書き込み・読み出し処理を実行する点以外は第1実施形態と同じである。

ここで、CPU2が実行する書き込み・読み出し処理の手順を、図6を用いて説明する。図6は書き込み・読み出し処理を示すフローチャートである。この書き込み・読み出し処理は、CPU2が起動(電源オン)すると開始される処理である。

【0053】

この書き込み・読み出し処理が実行されると、CPU2は、まずS210にて、リセットを行い、読み出し用DLL11及び書き込み用DLL14の遅延時間を設定するための情報(以下、遅延時間設定情報ともいう)を初期化する。例えば、遅延時間がないことを示す値に遅延時間設定情報を設定する。

【0054】

そしてS220にて、CPU温度検出部6にCPU2の温度を検出させて、S230にて、CPU温度検出部6による検出結果に基づいて、読み出し用DLL11及び書き込み用DLL14に対してレジスタ設定を行うことにより、遅延時間を設定する。

【0055】

その後S240にて、CPU温度検出部6による検出結果に基づいて、CPU2の最高温度を検出したか否かを判断する。ここで、最高温度を検出していない場合には(S240:NO)、S270に移行する。一方、最高温度を検出した場合には(S240:YES)、S250にて、CPU2が高速揮発性メモリ3にアクセス中であるか否かを判断する。

【0056】

ここで、アクセス中である場合には(S250:YES)、S250の処理を繰り返す。一方、アクセス中でない場合には(S250:NO)、S260にて、検出した最高温度に基づいて、読み出し用DLL11及び書き込み用DLL14に対してレジスタ設定をするための設定値(以下、DLL設定値という)を決定し、このDLL設定値で、読み出し用DLL11及び書き込み用DLL14に対してレジスタ設定を行うことにより、遅延時間を調整する。

【0057】

尚、DLL設定値は、本実施形態では、DLL0,DLL1,DLL2,DLL3の4種類有り、DLL0→DLL1→DLL2→DLL3の順に遅延時間が長くなるように設定されている。

【0058】

そしてS270に移行すると、高速揮発性メモリ3にデータを書き込むための書き込み要求があるか否かを判断する。ここで、書き込み要求がない場合には(S270:NO)、S290に移行する。一方、書き込み要求がある場合には(S270:YES)、S280にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3にデータを書き込み、S290に移行する。

【0059】

そしてS290に移行すると、高速揮発性メモリ3からデータを読み出すための読み出し要求があるか否かを判断する。ここで、読み出し要求がない場合には(S290:NO)、240に移行し、上述の処理を繰り返す。一方、読み出し要求がある場合には(S290:YES)、S300にて、メモリコントローラ4を制御することにより、高速揮発性メモリ3からデータを読み出す。その後に240に移行し、上述の処理を繰り返す。

【0060】

これによりLSI1は、図7に示すように、CPU2が高速揮発性メモリ3にアクセス中に最高温度(指示m11,m12,m13を参照)となると、動作中から非動作中に変化したタイミング(タイミングth11,th12,th13を参照)で、最高温度に対応したDLL設定値(DLL0,DLL1,DLL2,DLL3の何れか)に設定する。

【0061】

このように構成されたLSI1では、アクセス中から非アクセス中に切り替わった時点で、CPU2の最高温度に応じた時間分遅延して、データ取り込み信号DQSを出力する(S250,S260)。

【0062】

このため、アクセス中において急にデータ信号DQとデータ取り込み信号DQSとの間のタイミングのずれが変化することがなくなり、高速揮発性メモリ3へのアクセスを安定させることができる。

【0063】

以上説明した実施形態において、S240の処理は本発明におけるCPU温度情報取得手段、S260の処理は本発明における温度ずれ調整手段、S250の処理は本発明における調整禁止手段である。

【0064】

(第5実施形態)

以下に本発明の第5実施形態について図面とともに説明する。

図8は、第5実施形態のLSI50の構成を示すブロック図である。

【0065】

LSI50は、図1に示すように、DDR2メモリ55と、DDR2メモリ55へのアクセスを行うためのメモリバス53と、DDR2メモリ55へのアクセスを制御するDDR2I/F54と、DDR2I/F54の動作を制御するCPU51と、CPU51とメモリバス53とをデータ入出力可能に接続するシステムバス52と、メモリバス53の状態を監視するバスモニタ56と、CPU51の温度を検出する温度検出部57とを備える。

【0066】

これらのうちDDR2I/F54は、DDR2メモリ55から入力したデータ取り込み信号をCPU51によるレジスタ設定で設定された時間分遅延させて出力する読み出し用DLL(不図示)と、不図示の信号発生回路から入力したデータ取り込み信号をCPU51によるレジスタ設定で設定された時間分遅延させてDDR2メモリ55に出力する書き込み用DLL(不図示)とを備える。

【0067】

このように構成されたLSI50において、CPU51は、DDR2I/F54の読み出し用DLLと書き込み用DLLの遅延時間を調整するDLL調整処理を実行する。

ここで、CPU51が実行するDLL調整処理の手順を、図9を用いて説明する。図9はDLL調整処理を示すフローチャートである。このDLL調整処理は、CPU51が起動(電源オン)している間に繰り返し実行される処理である。

【0068】

このDLL調整処理が実行されると、CPU51は、まずS410にて、バスモニタ56による監視結果に基づいて、DDR2メモリ55へのアクセス頻度を算出する。またS420にて、温度検出部57にCPU51の温度を検出させる。

【0069】

そしてS430にて、S410にて算出されたアクセス頻度と、S420で検出したCPU51の温度に基づいて、CPU51の温度を予測する。

例えば、DDR2メモリ55へのアクセスによりCPU51の温度が上昇する場合におけるCPU51の予測温度Tc1は、下式(1)により算出される。

【0070】

Tc1 = Tc0 + α × LNG × t ・・・(1)

尚、式(1)における「Tc0」はS420で検出されたCPU51の温度、「α」はボードにより決定される定数、「LNG」はDDR2メモリ55へアクセスしている時間を示すアクセス長、「t」はデータ信号がローレベルからハイレベルまたはハイレベルからローレベルへ変化する変化率を示すトグル率を表す。

【0071】

その後440にて、S430で予測したCPU51の温度に基づいて、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定をするための設定値(以下、DLL設定値という)を決定し、このDLL設定値で、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定を行うことにより、遅延時間を調整し、DLL調整処理を一旦終了する。尚、DLL設定値は、DLL0,DLL1,DLL2,DLL3の4種類存在し、DLL0→DLL1→DLL2→DLL3の順に遅延時間が長くなるように設定されている。

【0072】

このように構成されたLSI50のDLL調整の例を図10に示す。

図10に示すように、タイミングTh21では、シングルアクセスSGLが行われることによるCPU51の温度を予測した結果、DLL設定値をDLL1からDLL2へ変更する。またタイミングTh22では、シングルアクセスSGLが行われることによるCPU51の温度を予測した結果、DLL設定値の変更を行わない。またタイミングTh23では、アクセスが暫くないことによるCPU51の温度を予測した結果、DLL設定値をDLL2からDLL1へ変更する。またタイミングTh24では、8バーストアクセスBUST8が行われることによるCPU51の温度を予測した結果、DLL設定値をDLL1からDLL3へ変更する。またタイミングTh25では、アクセスが暫くないことによるCPU51の温度を予測した結果、DLL設定値をDLL3からDLL2へ変更する。またタイミングTh26では、4バーストアクセスBUST4が行われることによるCPU51の温度を予測した結果、DLL設定値の変更を行わない。

【0073】

このように構成されたLSI50では、バスモニタ56によりメモリバス53の状態を監視し、この監視結果に基づいて、DDR2メモリ55へのアクセス頻度を算出するとともに(S410)、CPU2の温度を検出し(S420)、更に、算出したアクセス頻度と、検出したCPU2の温度とに基づいて、CPU51の温度を予測する(S430)。そして、予測したCPU2の温度に応じた時間分遅延して、データ取り込み信号DQSを出力する(S440)。

【0074】

このため、CPU温度の変化を見越して事前に、データ信号DQとデータ取り込み信号DQSとの間のタイミング(信号間タイミング)を調整することが可能となり、データ不一致の発生を更に抑制することができる。

【0075】

以上説明した実施形態において、S420の処理は本発明におけるCPU温度検出手段、バスモニタ56及びS410の処理は本発明におけるメモリバス監視手段、S430の処理はCPU温度予測手段である。

【0076】

(第6実施形態)

以下に本発明の第6実施形態について図面とともに説明する。尚、第6実施形態では、第5実施形態と異なる部分のみを説明する。

【0077】

第6実施形態におけるLSI50は、LSI50の構成と、DLL調整処理が変更される点以外は第5実施形態と同じである。

図11は、第6実施形態のLSI50の構成を示すブロック図である。

【0078】

第6実施形態のLSI50は、図11に示すように、DDR2メモリ55の温度を検出する温度検出部58が追加された点以外は第5実施形態と同じである。

次に、CPU51が実行するDLL調整処理の手順を、図12を用いて説明する。図12は第6実施形態のDLL調整処理を示すフローチャートである。このDLL調整処理は、CPU51が起動(電源オン)している間に繰り返し実行される処理である。

【0079】

このDLL調整処理が実行されると、CPU51は、まずS510にて、DDR2メモリ55にデータを書き込むための書き込み要求、またはDDR2メモリ55からデータを読み出すための読み出し要求(以下、書き込み要求と読み出し要求とをまとめて動作要求という)があるか否かを判断する。ここで、動作要求がない場合には(S510:NO)、DLL調整処理を一旦終了する。一方、動作要求がある場合には(S510:YES)、S520にて、温度検出部57にCPU51の温度Tc(CPU)を検出させる。更にS530にて、温度検出部58にDDR2メモリ55の温度Tc(DDR2)を検出させる。

【0080】

そしてS540にて、S520で検出した温度Tc(CPU)と、S530で検出した温度Tc(DDR2)に基づいて、図13に示すDLL設定テーブルT1を参照して、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定をするための設定値(以下、DLL設定値という)を決定し、このDLL設定値で、DDR2I/F54の読み出し用DLLまたは書き込み用DLLに対してレジスタ設定を行うことにより、遅延時間を調整し、DLL調整処理を一旦終了する。

【0081】

尚、DLL設定テーブルT1では、図13に示すように、温度Tc(CPU)及び温度Tc(DDR2)それぞれを、4つの温度範囲T0(−40℃〜0℃)、T1(0℃〜60℃)、T2(60℃〜85℃)、T3(85℃〜115℃)に分けて、温度Tc(CPU)の4つの温度範囲と、温度Tc(DDR2)の4つの温度範囲の組合せに応じて、DLL設定値(図13中のDLL0,DLL1,DLL2,DLL3)が設定されている。また、DLL設定値は、DLL0→DLL1→DLL2→DLL3の順に遅延時間が長くなるように設定されている。

【0082】

このように構成されたLSI50では、CPU51の温度に加えて、更に、DDR2メモリ55の温度に基づいて、データ信号DQとデータ取り込み信号DQSとの間のタイミング(信号間タイミング)を調整する(S540)。

【0083】

このため、CPU51及びDDR2メモリ55の温度変化に起因した信号間タイミングのずれによるデータ不一致が発生する前に、CPU51及びDDR2メモリ55の温度に応じて信号間タイミングを調整することが可能となり、データ不一致の発生を抑制することができる。

【0084】

以上、本発明の一実施形態について説明したが、本発明は上記実施形態に限定されるものではなく、本発明の技術的範囲に属する限り種々の形態を採ることができる。

例えば上記実施形態においては、CPUと高速揮発性メモリとの間の信号間タイミングを調整するものを示したが、高速揮発性メモリに限定されるものではなく、データ信号とデータ取り込み信号とを用いてデータの書き込み及び読み出しを行うメモリであればよい。

【図面の簡単な説明】

【0085】

【図1】LSI1の構成を示すブロック図である。

【図2】書き込み処理を示すフローチャートである。

【図3】読み出し処理を示すフローチャートである。

【図4】第2実施形態のメモリコントローラ4及び温度比較器26を示すブロック図である。

【図5】第3実施形態のメモリコントローラ4及びMAX温度検出回路38を示すブロック図、及びDLL調整タイミングを説明する図である。

【図6】書き込み・読み出し処理を示すフローチャートである。

【図7】第4実施形態のDLL調整タイミングを説明する図である。

【図8】第5実施形態のLSI50の構成を示すブロック図である。

【図9】第5実施形態のDLL調整処理を示すフローチャートである。

【図10】第5実施形態のDLL調整を説明する図である。

【図11】第6実施形態のLSI50の構成を示すブロック図である。

【図12】第6実施形態のDLL調整処理を示すフローチャートである。

【図13】DLL設定テーブルT1の構成を示す図である。

【図14】データ信号DQとデータ取り込み信号DQSとの間のタイミングずれを説明する図である。

【図15】データ信号DQとデータ取り込み信号DQSとの間の温度によるタイミングずれを説明する図である。

【符号の説明】

【0086】

1,50…LSI、2,51…CPU3…高速揮発性メモリ、4…メモリコントローラ、4a…読み出し部、4b…書き込み部、5…システムバス、6…CPU温度検出部、7…ROM、8…クロック発生器、11…読み出し用DLL、12,15,36…DFF回路、14…書き込み用DLL、13,16…バッファ、21〜24,31〜34…DLL、25,35…セレクタ、26…温度比較器、37…メモリI/Fシーケンサ、38…MAX温度検出回路、52…システムバス、53…メモリバス、54…DDR2I/F、55…DDR2メモリ、56…バスモニタ、57,58…温度検出部、DQ…データ信号、DQS…データ取り込み信号

【特許請求の範囲】

【請求項1】

CPUとメモリとの間において送受信されるデータ信号と、該データ信号の取り込みタイミングを規定するために前記CPUと前記メモリとの間において送受信されるデータ取り込み信号との間のタイミングのずれを調整するタイミング調整装置であって、

前記CPUの温度についての情報であるCPU温度情報を取得するCPU温度情報取得手段と、

前記CPU温度情報取得手段により取得された前記CPU温度情報に基づいて、前記データ取り込み信号の入出力を予め設定された遅延時間遅らせることによって、前記データ信号と前記データ取り込み信号との間のタイミングのずれを調整する温度ずれ調整手段と

を備えることを特徴とするタイミング調整装置。

【請求項2】

前記CPUの温度を検出するCPU温度検出手段を備え、

前記CPU温度情報は、前記CPU温度検出手段により検出された温度を示すものである

ことを特徴とする請求項1に記載のタイミング調整装置。

【請求項3】

前記CPUと前記メモリとの間には、前記CPUが前記メモリへのアクセスを行うためのメモリバスが設けられ、

前記CPUの温度を検出するCPU温度検出手段と、

前記メモリバスを監視して、前記CPUが前記メモリへのアクセスを行うアクセス頻度を検出するメモリバス監視手段と、

前記メモリバス監視手段により検出されたアクセス頻度と、前記CPU温度検出手段により検出された前記CPUの温度とに基づいて、その後の前記CPUの温度を予測するCPU温度予測手段とを備え、

前記CPU温度情報は、前記CPU温度予測手段により予測された温度を示すものである

ことを特徴とする請求項1に記載のタイミング調整装置。

【請求項4】

前記メモリバス監視手段は、

前記CPUが前記メモリへアクセスしている時間であるアクセス長と、前記データ信号がローレベルからハイレベルまたはハイレベルからローレベルへ変化する変化率であるトグル率を前記アクセス頻度として検出し、

前記CPU温度予測手段は、

前記アクセス長と前記トグル率との積に基づいて、前記CPUが前記メモリへのアクセスを行うことによる前記CPUの温度上昇を予測する

ことを特徴とする請求項3に記載のタイミング調整装置。

【請求項5】

前記CPUが前記メモリにアクセスしている場合に、前記温度ずれ調整手段の動作を禁止する調整禁止手段を備える

ことを特徴とする請求項1から請求項4の何れかに記載のタイミング調整装置。

【請求項6】

前記メモリの温度を検出するメモリ温度検出手段を備え、

前記温度ずれ調整手段は、

前記CPU温度情報取得手段により取得された前記CPU温度情報に加えて、更に、前記メモリ温度検出手段により検出された前記メモリの温度に基づいて、前記データ信号と前記データ取り込み信号との間のタイミングのずれを調整する

ことを特徴とする請求項1から請求項5の何れかに記載のタイミング調整装置。

【請求項1】

CPUとメモリとの間において送受信されるデータ信号と、該データ信号の取り込みタイミングを規定するために前記CPUと前記メモリとの間において送受信されるデータ取り込み信号との間のタイミングのずれを調整するタイミング調整装置であって、

前記CPUの温度についての情報であるCPU温度情報を取得するCPU温度情報取得手段と、

前記CPU温度情報取得手段により取得された前記CPU温度情報に基づいて、前記データ取り込み信号の入出力を予め設定された遅延時間遅らせることによって、前記データ信号と前記データ取り込み信号との間のタイミングのずれを調整する温度ずれ調整手段と

を備えることを特徴とするタイミング調整装置。

【請求項2】

前記CPUの温度を検出するCPU温度検出手段を備え、

前記CPU温度情報は、前記CPU温度検出手段により検出された温度を示すものである

ことを特徴とする請求項1に記載のタイミング調整装置。

【請求項3】

前記CPUと前記メモリとの間には、前記CPUが前記メモリへのアクセスを行うためのメモリバスが設けられ、

前記CPUの温度を検出するCPU温度検出手段と、

前記メモリバスを監視して、前記CPUが前記メモリへのアクセスを行うアクセス頻度を検出するメモリバス監視手段と、

前記メモリバス監視手段により検出されたアクセス頻度と、前記CPU温度検出手段により検出された前記CPUの温度とに基づいて、その後の前記CPUの温度を予測するCPU温度予測手段とを備え、

前記CPU温度情報は、前記CPU温度予測手段により予測された温度を示すものである

ことを特徴とする請求項1に記載のタイミング調整装置。

【請求項4】

前記メモリバス監視手段は、

前記CPUが前記メモリへアクセスしている時間であるアクセス長と、前記データ信号がローレベルからハイレベルまたはハイレベルからローレベルへ変化する変化率であるトグル率を前記アクセス頻度として検出し、

前記CPU温度予測手段は、

前記アクセス長と前記トグル率との積に基づいて、前記CPUが前記メモリへのアクセスを行うことによる前記CPUの温度上昇を予測する

ことを特徴とする請求項3に記載のタイミング調整装置。

【請求項5】

前記CPUが前記メモリにアクセスしている場合に、前記温度ずれ調整手段の動作を禁止する調整禁止手段を備える

ことを特徴とする請求項1から請求項4の何れかに記載のタイミング調整装置。

【請求項6】

前記メモリの温度を検出するメモリ温度検出手段を備え、

前記温度ずれ調整手段は、

前記CPU温度情報取得手段により取得された前記CPU温度情報に加えて、更に、前記メモリ温度検出手段により検出された前記メモリの温度に基づいて、前記データ信号と前記データ取り込み信号との間のタイミングのずれを調整する

ことを特徴とする請求項1から請求項5の何れかに記載のタイミング調整装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2009−81523(P2009−81523A)

【公開日】平成21年4月16日(2009.4.16)

【国際特許分類】

【出願番号】特願2007−247393(P2007−247393)

【出願日】平成19年9月25日(2007.9.25)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成21年4月16日(2009.4.16)

【国際特許分類】

【出願日】平成19年9月25日(2007.9.25)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]