ターゲット材料の包装方法、及びターゲットの取り付け方法

【課題】水素原子を含む化合物等、大気に由来する不純物による汚染が少ない薄膜を成膜するターゲット材料の包装方法を提供することを課題の一とする。また、該不純物による汚染が少ない薄膜を成膜するターゲットの取り付け方法を提供することを課題の一とする。

【解決手段】上記目的を達成するために、ターゲットの製造後から当該ターゲットを取り付けた成膜装置を排気するまでの間、当該ターゲット中のターゲット材料を大気にさらすことなく密封状態を保つ。

【解決手段】上記目的を達成するために、ターゲットの製造後から当該ターゲットを取り付けた成膜装置を排気するまでの間、当該ターゲット中のターゲット材料を大気にさらすことなく密封状態を保つ。

【発明の詳細な説明】

【技術分野】

【0001】

ターゲット材料の包装方法、及び装置へのターゲットの取り付け方法に関する。具体的には、成膜材料を含むスパッタリング用ターゲット材料の包装方法、及び成膜装置へのターゲットの取り付け方法に関する。

【背景技術】

【0002】

ターゲットを用いた物理的蒸着法は幅広い材料の薄膜を成形できる特徴を有する。ターゲットを用いた物理的蒸着法としては、スパッタリング法やパルスレーザー蒸着法が挙げられる。特に、スパッタリング法は大面積基板への成膜が容易である上、例えば、融点が高く蒸気圧が低い材料であっても成膜が可能であるという利点を備える。また、反応性ガスを成膜室に導入することにより、金属酸化物や金属窒化物等を基板上に成膜することが可能である。また、基板へのダメージが比較的小さいことなどの特長があり、薄膜形成技術における重要な技術の一つである。

【0003】

スパッタリング法はターゲット材料(スパッタリングに用いる)を原材料とするため、成膜された薄膜の特性はターゲット材料に付着したゴミや不純物の影響を受ける。そのため、ターゲット材料の汚染を防ぐための種々の技術が開示されており、例えばターゲット材料の表面を保護する包装技術が特許文献1に開示されている。

【0004】

また、ガラス基板などの基板に酸化物半導体膜を形成し、それを用いて作製したトランジスタを電子デバイスや光デバイスに応用する技術が注目されている。例えば、半導体材料として酸化亜鉛、In−Ga−Zn−O系酸化物半導体を用いてトランジスタを作製し、画像表示装置のスイッチング素子などに用いる技術が特許文献2及び特許文献3で開示されている。

【0005】

酸化物半導体膜はスパッタリング法などによって比較的低温で膜形成が可能であり、薄膜トランジスタ(TFT:Thin Film Transistorともいう)に好適である。酸化物半導体膜を用いたTFTは多結晶シリコン膜を用いたTFTよりも製造工程が簡単である。また、酸化物半導体にチャネル形成領域(チャネル領域ともいう)を設けたTFTは、アモルファスシリコンを用いたTFTよりも高い電界効果移動度が得られている。

【0006】

酸化物半導体を用いたトランジスタは、ガラス基板だけでなく、プラスチック基板上にも形成できるため、液晶ディスプレイ、エレクトロルミネセンスディスプレイ(ELディスプレイともいう)または電子ペーパーなどの表示装置への応用が期待されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4−231461号公報

【特許文献2】特開2007−123861号公報

【特許文献3】特開2007−96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、酸化物半導体膜を用いて作製した半導体素子の特性は未だ充分なものとは言えない。例えば、酸化物半導体膜を用いたトランジスタには、制御された閾値電圧、速い動作速度、製造工程が比較的簡単であること、そして十分な信頼性が求められている。

【0009】

特に、酸化物半導体膜を用いたトランジスタの閾値電圧は、酸化物半導体膜に含まれるキャリア濃度に影響される。また、酸化物半導体膜に含まれるキャリアは、酸化物半導体膜に含まれる不純物により発生する。例えば、成膜された酸化物半導体膜に含まれるH2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物は、酸化物半導体膜のキャリア濃度を高める効果を有する。

【0010】

従って、酸化物半導体膜を用いて、閾値電圧が制御されたトランジスタを提供するには、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物を可能な限り減らす必要がある。

【0011】

しかし、酸化物半導体膜の成膜用ターゲット材料は、金属酸化物等に代表される極性が強い物質を含むため、大気中の不純物(例えば、水分等)を吸着または吸収し易い。そして、不純物を吸着または吸収したターゲット材料を用いて成膜した酸化物半導体膜は、不純物に汚染されてしまうという問題が生じる。

【0012】

また、金属膜の成膜用に金属を含むターゲット材料も同様であり、大気中の不純物(例えば、水分等)を吸着または吸収し易い。不純物を吸着または吸収した金属を含むターゲット材料を用いて成膜した金属膜は、不純物に汚染されてしまう。

【0013】

なお、大気中の不純物に汚染された金属膜を酸化物半導体膜に接して成膜すると、水分等の水素原子を含む不純物等が金属膜から酸化物半導体膜へ拡散してしまうという問題が生じる。本発明は、このような技術的背景のもとでなされたものである。

【0014】

本発明の一態様の目的は、大気に由来する不純物(例えば水素原子を含む化合物等)による汚染が少ない薄膜を成膜することができるターゲット材料の、包装方法を提供することを課題の一とする。また、該不純物による汚染が少ない薄膜を成膜することができるターゲットの取り付け方法を提供することを課題の一とする。

【課題を解決するための手段】

【0015】

上記目的を達成するために、ターゲット材料(例えば焼結体)の製造後、当該ターゲット材料を取り付けた成膜装置の成膜室を排気するまでの間、ターゲット材料を大気にさらすことなく密封状態を保てばよい。

【0016】

すなわち、本発明の一態様は、被装着部への取り付け部を有するバッキングプレートと、バッキングプレートに固定された焼結体と、取り付け部を覆うことなく焼結体を内包するようにバッキングプレートに装着される包装体とを有する。また、包装体の内側は乾燥気体が充填されていることを特徴とする包装されたスパッタリング用ターゲットである。

【0017】

また、本発明の一態様は、包装体の内側が露点−40℃以下の気体で満たされた、上記の包装されたスパッタリング用ターゲットである。

【0018】

また、本発明の一態様は、焼結体が金属酸化物を含む、上記の包装されたスパッタリング用ターゲットである。

【0019】

また、本発明の一態様は、金属酸化物がインジウムと、ガリウムと、亜鉛を含む、上記の包装されたスパッタリング用ターゲットである。

【0020】

また、本発明の一態様は、焼結体が金属を含む上記の包装されたスパッタリング用ターゲットである。

【0021】

また、本発明の一態様は、金属がAl、Cu、Cr、Ta、Ti、Mo、またはWの少なくとも一つを含む、上記の包装されたスパッタリング用ターゲットである。

【0022】

また、本発明の一態様は、露点−40℃以下の乾燥した雰囲気下で、被装着部への取り付け部を有するバッキングプレートに焼結体を固定し、取り付け部を覆うことなく焼結体を内包するように前記バッキングプレートに包装体を装着することを特徴とするスパッタリング用ターゲットの包装方法である。

【0023】

また、本発明の一態様は、露点−40℃以下の乾燥した雰囲気下で、被装着部への取り付け部を覆うことなく、ターゲット材料を包装体に収納し、包装体に収納されたターゲット材料を、バッキングプレートを介して成膜装置の成膜室の装着部に取り付け、成膜室を排気し、排気された成膜室内で包装体を開封する包装されたスパッタリング用ターゲットの取り付け方法である。

【0024】

なお、本明細書において、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0025】

また、本明細書において、酸化窒化物とは、その組成として、窒素原子よりも酸素原子の数が多い物質のことを指し、窒化酸化物とは、その組成として、酸素原子より窒素原子の数が多い物質のことを指す。例えば、酸化窒化シリコン膜とは、その組成として、窒素原子よりも酸素原子の数が多く、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素が50%以上70原子%以下、窒素が0.5%以上15原子%以下、シリコンが25%以上35原子%以下、水素が0.1%以上10原子%以下の範囲で含まれるものをいう。また、窒化酸化シリコン膜とは、その組成として、酸素原子より窒素原子の数が多く、RBS及びHFSを用いて測定した場合に、濃度範囲として酸素が5%以上30原子%以下、窒素が20%以上55原子%以下、シリコンが25%以上35原子%以下、水素が10%以上30原子%以下の範囲で含まれるものをいう。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0026】

なお、本明細書において、EL層とは発光素子の一対の電極間に設けられた層を示すものとする。従って、電極間に挟まれた発光物質である有機化合物を含む発光層はEL層の一態様である。

【0027】

なお、本明細書中において、発光装置とは画像表示デバイス、発光デバイス、もしくは光源(照明装置含む)を指す。また、発光装置にコネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または発光素子が形成された基板にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て発光装置に含むものとする。

【発明の効果】

【0028】

本発明によれば、例えば水素原子を含む化合物等、大気に含まれる不純物による汚染が少ない薄膜を成膜するターゲット材料の包装方法を提供できる。また、該不純物による汚染が少ない薄膜を成膜するターゲットの取り付け方法を提供できる。

【図面の簡単な説明】

【0029】

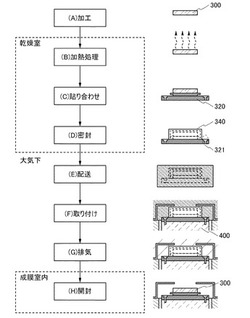

【図1】実施の形態に係わるターゲットの製造から開封工程を説明する図。

【図2】実施の形態に係わるターゲットの取り付け工程を説明する図。

【図3】実施の形態に係わるターゲット材料の密封方法を説明する図。

【図4】実施の形態に係わる半導体装置を説明する図。

【図5】実施の形態に係わる半導体装置の作製方法を説明する図。

【図6】実施の形態に係わる表示装置のブロック図。

【図7】実施の形態に係わる信号線駆動回路の構成を説明する図。

【図8】シフトレジスタの構成を示す回路図。

【図9】シフトレジスタの動作を説明する回路およびタイミングチャート。

【図10】実施の形態に係わる半導体装置を説明する図。

【図11】実施の形態に係わる半導体装置を説明する図。

【図12】実施の形態に係わる半導体装置を説明する図。

【図13】実施の形態に係わる半導体装置を説明する図。

【図14】実施の形態に係わる半導体装置を説明する図。

【図15】実施の形態に係わる半導体装置を説明する図。

【図16】電子ペーパーの使用形態の例を説明する図

【図17】電子書籍の一例を示す外観図。

【図18】テレビジョン装置およびデジタルフォトフレームの例を示す外観図。

【図19】遊技機の例を示す外観図。

【図20】携帯電話機の一例を示す外観図。

【図21】酸化物半導体を用いた逆スタガ型のトランジスタの縦断面図。

【図22】図21に示すA−A’断面におけるエネルギーバンド図(模式図)。

【図23】図21におけるB−B’間におけるエネルギーバンド図。

【図24】図21に示すB−B’間における(A)ゲート(GE1)に正の電位(VG>0)が印加された状態を示し、(B)ゲート(GE1)に負の電位(VG<0)が印加された状態示す図。

【図25】図21に示すB−B’間における真空準位と金属の仕事関数(φM)、酸化物半導体の電子親和力(χ)の関係を示す図。

【発明を実施するための形態】

【0030】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0031】

(実施の形態1)

本実施の形態では、被装着部への取り付け部を有するバッキングプレートと、バッキングプレートに固定されたターゲット材料と、取り付け部を覆うことなくターゲット材料を内包するようにバッキングプレートに装着される包装体とを有し、乾燥気体が包装体の内側に充填されているスパッタリング用ターゲットの製造から該ターゲットを開封するまでの工程について図1を用いて説明する。なお、当該工程は、「(A)加工、(B)熱処理、(C)貼り合わせ、(D)密封、(E)配送、(F)取り付け、(G)排気、(H)開封」、の8つの工程からなる。また、焼結体はターゲット材料の一態様である。

【0032】

はじめに、焼成により作製した原材料を焼結体300の形状に加工する。ターゲットを使用する成膜装置に合わせて、原材料の外形寸法や、表面の凹凸を機械加工により整える。なお、この工程は図1に示す「(A)加工」に相当する。また、鍛造等により原材料を所望の形状に加工してもよい。

【0033】

酸化物半導体膜を成膜するターゲット材料の一例は、原材料として酸化マグネシウム(MgO)、酸化亜鉛(ZnO)、アルミナ(Al2O3)、酸化ガリウム(Ga2O3)、酸化インジウム(In2O3)、または酸化スズ(SnO2)等を適宜混合し、焼成して焼結体に加工すればよい。

【0034】

また、原材料はSiO2を2重量%以上10重量%以下添加し、SiOx(X>0)を上記焼結体に含ませたものであってもよい。焼結体にSiOx(X>0)を含ませることにより、酸化物半導体膜の結晶化を阻害できる。特に、脱水化または脱水素化のための加熱処理を行う場合、過度の結晶化を抑制できるため好ましい。

【0035】

このような組成を含むターゲット材料をスパッタリングすることで、四元系金属酸化物であるIn−Sn−Ga−Zn−O膜や、三元系金属酸化物であるIn−Ga−Zn−O膜、In−Sn−Zn−O膜、In−Al−Zn−O膜、Sn−Ga−Zn−O膜、Al−Ga−Zn−O膜、Sn−Al−Zn−O膜や、二元系金属酸化物であるIn−Zn−O膜、Sn−Zn−O膜、Al−Zn−O膜、Zn−Mg−O膜、Sn−Mg−O膜、In−Mg−O膜、In−Ga−O膜や、In−O膜、Sn−O膜、Zn−O膜などの酸化物半導体膜を成膜できる。また、上記酸化物半導体膜は酸化珪素を含ませてもよい。酸化物半導体膜に結晶化を阻害する酸化珪素(SiOx(X>0))を含ませることで、結晶化してしまうのを抑制することができる。

【0036】

また、InMO3(ZnO)m(m>0)で表記される薄膜を成膜することができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。InMO3(ZnO)m(m>0)で表記される構造の酸化物半導体膜のうち、MとしてGaを含む構造の酸化物半導体を、上記したIn−Ga−Zn−O系酸化物半導体とよび、その薄膜をIn−Ga−Zn−O膜ともよぶこととする。

【0037】

また、酸化物半導体膜を成膜するターゲット材料として用いる焼結体は充填率が90%以上100%以下、好ましくは95%以上99.9%以下のものを用いる。充填率の高い酸化物半導体ターゲットの焼結体を用いることにより、水分等の不純物が吸着する空隙を取り除くことができるだけでなく、ノジュールの発生を防止し、均一な放電が可能になり、パーティクルの発生を抑制できる。また、成膜した酸化物半導体膜は緻密な膜となる。その結果、不純物濃度が抑制され、均質な品質の酸化物半導体膜を得ることができる。

【0038】

本実施の形態では、In−Ga−Zn−O系膜を成膜するターゲット材料として、In、Ga、及びZnを含む酸化物半導体の焼結体(具体的な組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol%]、In:Ga:Zn=1:1:0.5[at.%])を例示する。

【0039】

また、ターゲット材料の一例として、例えば導電性の金属酸化物膜を形成するターゲットの場合は、酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

【0040】

また、ターゲット材料の一例として、例えば金属膜を形成するターゲットの場合は、Al、Cu、Cr、Ta、Ti、Mo、Wなどの金属材料、または該金属材料を成分とする合金材料をその例に挙げることができる。また、Alに、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素を添加して用いると、金属膜の耐熱性を向上できる。

【0041】

なお、酸化物半導体膜と接し、トランジスタのソース電極層及びドレイン電極層となる導電膜を成膜する場合は、水素原子等の不純物が酸化物半導体層に拡散しないように、不純物の含有量を極力減らした金属を原材料に用いる。また、酸素親和性の高い金属を含む材料、例えば、チタン(Ti)、マンガン(Mn)、マグネシウム(Mg)、ジルコニウム、ベリリウム、トリウムのいずれか一または複数から選択された材料が好ましい。

【0042】

原材料を焼結体300の形状に加工後、必要であればパーティクルの発生源とならないよう、クリーンルーム内で洗浄を行う。

【0043】

次いで、成膜装置に適合すべく加工した焼結体300を高純度の不活性ガス中で加熱処理し、不純物を除去する。加熱処理の温度は焼結体300の変性、変形が起こらない範囲であればよい。なお、この工程は図1に示す「(B)加熱処理」に相当する。

【0044】

また、大気中の不純物が焼結体300に吸着しないように、工程「(B)加熱処理」から、工程「(D)密封」までの間は乾燥室等の清浄化された雰囲気で焼結体300を取り扱う。具体的には、グローブボックス、ドライルーム等を用いて、不純物を含まない雰囲気下(例えば、水分については露点−40℃以下、好ましくは露点−50℃以下)で取り扱う。

【0045】

露点の測定方法としては、多孔質な絶縁体部分に水分子が吸着することによっておこる静電容量の変化を捉える方法や、冷却した鏡面に水分が結露することによって起こる光の反射率の変化を捉える方法を用いればよい。

【0046】

なお、加熱処理において、窒素は焼結体300が窒化されない場合にのみ用いることができる。また、焼結体300が酸化物であれば、高純度に精製した酸素を添加した雰囲気下で加熱処理を行い、酸素欠損が生じないようにしてもよい。また、焼結体300を構成する主成分の組成に変化を生じない範囲で減圧しながら加熱処理を行ってもよい。

【0047】

次いで、焼結体300をバッキングプレート320に固定する。バッキングプレート320は成膜装置の気密を保つ形態と成膜装置への取り付け部321を有し、成膜装置へ取り付けることができる。

【0048】

バッキングプレートを介してターゲットの焼結体300の温度を調整する場合は、バッキングプレートは銅など熱伝導性の高い材料が好適である。

【0049】

また、焼結体300とバッキングプレート320はろう材を用いて貼り合わせることができる。ろう材としては、インジウム(In)を主に用いる。なお、この工程は図1に示す「(C)貼り合わせ」に相当する。

【0050】

なお、ろう材の融点より高い温度で焼結体300を加熱しながら成膜を行う場合はろう材を用いず、フランジで焼結体300をバッキングプレートに固定すればよい。また、ろう材の種類によりろう材が使える温度範囲は異なるが、焼結体300を加熱する温度が150℃から300℃を越える場合は、フランジを用いて焼結体300をバッキングプレート320に固定すればよい。

【0051】

次いで、ガスバリア性を有する包装体340で焼結体300を覆って密封する。本実施の形態で用いる包装体340は、バッキングプレート320の成膜装置への取り付け部321を覆うことなく、焼結体300と大気の接触を防ぐ。焼結体300を含む空間は水分等の水素原子を含む不純物が取り除かれ、具体的には露点−40℃以下、好ましくは露点−50℃以下とする。なお、この工程は図1に示す「(D)密封」に相当する。

【0052】

ガスバリア性を有する包装体340としては、金属板、金属箔、無機薄膜を蒸着した高分子フィルムなどを用いることができる。具体的には、SUS板、アルミ板、アルミ箔、アルミ蒸着フィルム、窒化珪素蒸着フィルム、酸化珪素蒸着フィルム等をその例に挙げることができる。

【0053】

包装体340で仕切られた焼結体300を含む空間を高純度の不活性ガスで満たしてもよい。さらに、内部の圧力を外部の圧力より高くしてもよい。圧力を高めることで、外気が焼結体300を含む空間に侵入し難くなる。また、包装体340にガスの導入口を設け、大気圧より高い高純度な不活性ガスを蓄えた容器を接続してもよい。また、レギュレーターを介して該容器を接続すると内圧を一定に保てるため、外気が内部に浸入しがたくなる。

【0054】

包装体340で仕切られた焼結体300を含む空間を満たす不活性ガスとしては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスを用いることができる。また、不活性ガスは、不純物(例えば、水、水素など水素原子を含む物質)を含んでいないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0055】

また、包装体340で仕切られた焼結体300を含む空間を減圧してもよい。減圧することで包装体340とバッキングプレート320の密着がよくなり、外気の浸入を防ぐことができる。また、包装体340に排気口を設け、排気装置で内部を真空に保っても良い。内部を真空に保つことで、外気がターゲット材料に触れることがない。

【0056】

さらに、焼結体300、バッキングプレート320、及び包装体340を、ガスバリア性を有する袋で梱包してもよい。多重に梱包することで、不純物が焼結体300に吸着することを防ぐだけでなく、焼結体300と共にパーティクルをクリーンルームに持ち込むことを防止できる。

【0057】

次いで、梱包された焼結体300を成膜装置に配送する。なお、この工程は図1に示す「(E)配送」に相当する。

【0058】

次いで、焼結体300はバッキングプレート320の取り付け部321を介して成膜装置の成膜室400に取り付ける。なお、この工程は図1に示す「(F)取り付け」に相当する。ターゲット材料は包装体で覆われた状態で取り付けられるため、大気と接触することはない。

【0059】

次いで、焼結体300が取り付けられた成膜室400を排気する。成膜室400の内壁、バッキングプレート320、及び包装体340に吸着した大気中の水分等の不純物が排気される。排気は少なくとも露点−40℃以下、好ましくは−50℃以下の雰囲気になるまで行う。また、必要に応じて成膜室400を加熱して、成膜室400内に吸着した物質の脱離を促してもよい。なお、この工程は図1に示す「(G)排気」に相当する。

【0060】

なお、成膜室400の圧力低下に伴って相対的に高まる包装体340内の圧力を低下するため、包装体340にガス抜き用の弁を設けることが好ましい。

【0061】

次いで、焼結体300を覆う包装体340を開封し、取り外す。なお、この工程は図1に示す「(H)開封」に相当する。

【0062】

減圧された成膜室400内で包装体340を開封、及び取り外す場合は、成膜室400に開封機構を設けて、包装体340を開封、及び取り外せばよい。また、成膜室400内の大気を排気し、成膜室400を大気圧の高純度な不活性ガスで満たした後、成膜室400内で包装体340を開封する場合は、成膜室400に設けたグローブを使って包装体340を開封してもよい。

【0063】

以上の方法によれば、大気に由来する不純物(例えば水素原子を含む化合物等)の吸着、及び含有量が少ないターゲット材料を製造できる。また、不純物の少ないターゲット材料を大気にさらすことなく成膜室に取り付け、使用することができる。その結果、不純物による汚染が少ない薄膜を成膜できる。

【0064】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0065】

(実施の形態2)

本実施の形態では、実施の形態1で説明したターゲットの製造から該ターゲットを開封するまでの工程の中で、ターゲットを成膜装置に取り付け、成膜室内を排気した後、ターゲットから包装体を外してターゲットを開封する方法について、図2、及び図3を用いてさらに詳細に説明する。

【0066】

図2(A)に示す成膜室400aには、バッキングプレート320を介して焼結体300が取り付けられている。また、成膜室を囲う壁面の一つにはグローブ401が取り付けられ、成膜室の内部を大気に曝すことなく作業できる。なお、図示していないが、成膜用基板の搬送機構、成膜用基板の支持機構、及び成膜室内を排気する排気装置が取り付けられている。

【0067】

なお、成膜室内の不純物(例えば、水、水素など水素原子を含む物質)を排気するために、排気装置としてはクライオポンプ、またはターボポンプにコールドトラップを加えたものが望ましい。

【0068】

実施の形態1の説明に従い、バッキングプレート320を介して焼結体300を成膜室400aに取り付けた後、成膜室内を排気する。排気後、成膜室400aを大気圧の高純度な不活性ガスで満たし、グローブ401を用いて包装体340を開封する。

【0069】

ターゲット材料を密封する包装体の構成について、一例をあげて説明する。図2(A)に例示する包装体の場合、例えば図3(A)の如くバッキングプレート320aに勘合用ピン325aを設け、また、包装体340aに勘合用切り込み部345a、及び圧力調整弁335を設ければよい。

【0070】

嵌合用切り込み部345aに勘合用ピン325aを挿入し、互いに勘合するように回転すれば、包装体340aは焼結体300を密封できる。なお、包装体340aとバッキングプレート320aが接する部分には気密性を高めるパッキング等を挟むと好ましい。さらに、シール性を高める接着剤等を用いてもよいが、不純物や、ゴミの発生源となるため、勘合により物理的に圧着して気密を確保する方法が好ましい。

【0071】

また、バッキングプレートと包装体をネジ式とし、ターゲット材料を密封してもよい。

【0072】

なお、圧力調整弁335は、包装体で密封されたターゲット材料を含む空間の圧力が外部の圧力よりも例えば1気圧以上高くなると弁を開き、内圧がそれ以上高まらないよう機能する。

【0073】

図2(A)とは異なる開封方法を次に説明する。図2(B)に示す成膜室400bには、バッキングプレート320を介して焼結体300が取り付けられている。また、焼結体300を覆う包装体340を移動するターゲットの開封機構405を有している。なお、図2(A)と同様、成膜室400bには図示していない成膜用基板の搬送機構、成膜用基板の支持機構、及び成膜室内を排気する排気装置が取り付けられている。

【0074】

実施の形態1の説明に従い、バッキングプレート320を介して焼結体300を成膜室400bに取り付けた後、成膜室内を排気する。排気後、ターゲットの開封機構405を用いて包装体340を移動して開封する。

【0075】

ターゲットの開封機構405に適した構成について、一例をあげて説明する。図3(B−1)、及び(B−2)に例示する包装体は、一方向への移動によりターゲットを開封できる。

【0076】

図3(B−1)は焼結体300、及びバッキングプレート320bと、包装体340bの側面図である。また、図3(B−2)は、図3(B−1)の矢印方向から観察した焼結体300、及びバッキングプレート320bに、包装体340bを脱着する構成の側面図である。

【0077】

バッキングプレート320bは勘合用レール325bと、気密部材330と、圧力調整弁335を有し、包装体340bは摺動部材345bを有する。摺動部材345bは勘合用レール325bと勘合し、気密部材330に突き当たるまで図3(B−2)の矢印方向に自在に移動する。

【0078】

摺動部材345bと勘合用レール325bを勘合し、気密部材330に突き当て、包装体340bで焼結体300を密封する。なお、包装体340bとバッキングプレート320bが接する部分には気密性を高めるパッキング等を挟むと好ましい。

【0079】

図3(B−1)に示す方法によれば、包装体340bを一方向に移動するだけでターゲットを開封できるため、ターゲットの開封機構405を簡便にできる。

【0080】

また、ターゲットの開封機構405に適した別の構成について説明する。図3(C−1)、及び(C−2)に例示する包装体は、二方向への移動によりターゲットを開封できる。

【0081】

図3(C−1)は焼結体300、及びバッキングプレート320cと、包装体340cの側面図である。また、図3(C−2)は、図3(C−1)の矢印方向から観察した焼結体300、及びバッキングプレート320cに、包装体340cを脱着する構成の側面図である。

【0082】

バッキングプレート320cは複数に分断された勘合用レール325cと、気密部材330と、圧力調整弁335を有する。包装体340cは複数に分断された摺動部材345cを有する。なお、分断された摺動部材345cの長さは、分断された勘合用レール325cの間隔より短い。

【0083】

摺動部材345cは勘合用レール325cと勘合し、気密部材330に突き当たるまで図3(C−2)の矢印方向に自在に移動する。分断された勘合用レール325cの間に、分断された摺動部材345cを通して、バッキングプレート320cと包装体340cを接した後、包装体340cを気密部材330に突き当て、包装体340cで焼結体300を密封する。なお、包装体340cとバッキングプレート320cが接する部分には気密性を高めるパッキング等を挟むと好ましい

【0084】

図3(C−1)に示す方法によれば、包装体340cが摺動する距離が分断された勘合用レール325cの間隔より短く、ターゲットの開封が容易である。

【0085】

また、ターゲットの開封機構405に適した別の構成について説明する。図3(D−1)、及び(D−2)に例示する包装体は、一方向への移動によりターゲットを開封できる。

【0086】

図3(D−1)は焼結体300、及びバッキングプレート320dと、包装体340dの側面図である。また、図3(D−2)は、図3(D−1)の矢印方向から観察した焼結体300、及びバッキングプレート320dに、包装体340dを脱着する構成の側面図である。

【0087】

バッキングプレート320dは勘合用レール325dと、気密部材330と、圧力調整弁335を有し、包装体340dは摺動部材345dを有する。摺動部材345dは勘合用レール325dと勘合し、気密部材330に突き当たるまで図3(D−2)の矢印方向に自在に移動する。

【0088】

摺動部材345dと勘合用レール325dを勘合し、気密部材330に突き当て、包装体340dで焼結体300を密封する。なお、包装体340dとバッキングプレート320dが接する部分には気密性を高めるパッキング等を挟むと好ましい。

【0089】

図3(D−1)に示すバッキングプレート320dは加工が容易である。

【0090】

以上の方法によれば、不純物の少ないターゲット材料を大気にさらすことなく成膜室に取り付け、使用することができる。その結果、不純物による汚染が少ない薄膜を成膜できる。

【0091】

また、本実施の形態で例示した、勘合用レールを有するバッキングプレートと、摺動部材を有する包装体を用いてターゲット材料を密封すれば、ターゲットの開封機構を搭載した成膜室に適用できるため、包装体の開封が容易であり、生産性が向上する。

【0092】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0093】

(実施の形態3)

本実施の形態では、実施の形態1及び実施の形態2で説明した包装方法を適用したターゲットを用いて、半導体素子を作製する方法について説明する。なお、本実施の形態では、該半導体素子の一例として、図4に示す薄膜トランジスタの構成とその作製方法を説明する。

【0094】

本実施の形態の薄膜トランジスタ151の断面図を図4に示す。薄膜トランジスタ151は、基板100上にゲート電極111a、及びゲート配線層111bを有し、ゲート電極111a、及びゲート配線層111b上にゲート絶縁層102が形成されている。ゲート絶縁層102は第1のゲート絶縁層102a、及び第2のゲート絶縁層102bを積層して形成されている。ゲート絶縁層102を介してゲート電極111a上に酸化物半導体層123が形成されている。ゲート電極111aに端部を重畳してソース電極層、及びドレイン電極層(115a、115b)が形成されている。また、ゲート電極111a上のソース電極層、及びドレイン電極層(115a、115b)に挟まれた酸化物半導体層123に接して酸化物絶縁膜107が、設けられ、酸化物絶縁膜107上に保護絶縁層108が設けられている。

【0095】

また、ゲート配線層111bに到達するコンタクトホール128がゲート絶縁層102に形成され、コンタクトホール128を介してゲート配線層111bと第2配線層115cが接続している。

【0096】

本実施の形態の薄膜トランジスタ151の作製方法について図5(A)、図5(B)、図5(C)、及び図5(D)を用いて説明する。図5は本実施の形態における薄膜トランジスタの作製方法を示す断面図である。

【0097】

基板100に用いるガラス基板としては、加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いると良い。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。酸化ホウ素と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、B2O3よりBaOを多く含むガラス基板を用いることが好ましい。

【0098】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体からなる基板を用いても良い。他にも、結晶化ガラスなどを用いることができる。

【0099】

また、下地膜となる絶縁膜を基板100と、次に説明するゲート電極111a、及びゲート配線層111bの間に設けてもよい。下地膜は、基板100からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、または酸化窒化珪素膜から選ばれた一または複数の膜による積層構造により形成することができる。

【0100】

絶縁表面を有する基板100上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極111a、及びゲート配線層111bを含む第1配線層を形成する。なお、形成されたゲート電極の端部はテーパ形状であることが好ましい。

【0101】

なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0102】

ゲート電極111a、及びゲート配線層111bを形成する導電膜としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、上述した金属に加え、銅、ネオジム、またはスカンジウムなどの金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することもできる。なお、透光性を有する導電膜を用いてゲート電極を形成することもできる。透光性を有する導電膜としては、透明導電性酸化物等をその例に挙げることができる。

【0103】

次いで、ゲート絶縁層102を成膜する。ゲート絶縁層102は酸化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、窒化シリコン層、酸化アルミニウム層、酸化タンタル層などの単層膜または積層膜を用いることができる。また、膜厚を50nm以上250nm以下とし、CVD法やスパッタ法などで形成する。また、膜中にリン(P)や硼素(B)がドープされていても良い。

【0104】

ゲート絶縁層102は酸化物半導体層と接する側に酸化物絶縁層を有する構成が好ましい。本実施の形態では第1のゲート絶縁層102aとして窒化珪素、第2のゲート絶縁層102bとして酸化珪素を用いる。また、本実施の形態で用いる、不純物を除去することによりi型化または実質的にi型化された酸化物半導体(高純度化された酸化物半導体)は界面準位、界面電荷に対して極めて敏感であるため、絶縁膜との界面は重要である。そのため高純度化された酸化物半導体に接する絶縁膜は、高品質化が要求される。

【0105】

例えば、μ波(2.45GHz)を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

【0106】

また、高密度プラズマCVD装置により得られた絶縁膜は、一定した厚さの膜形成ができるため段差被覆性に優れている。また、高密度プラズマCVD装置により得られる絶縁膜は、薄い膜の厚みを精密に制御することができる。

【0107】

もちろん、ゲート絶縁膜として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、酸化物半導体との界面特性が改質される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

【0108】

ゲート絶縁層102の形成は、高密度プラズマCVD装置により行う。ここでは、高密度プラズマCVD装置は、1×1011/cm3以上のプラズマ密度を達成できる装置を指している。例えば、3kW〜6kWのマイクロ波電力を印加してプラズマを発生させて、絶縁膜の成膜を行う。

【0109】

チャンバーに材料ガスとしてモノシランガス(SiH4)と亜酸化窒素(N2O)と希ガスを導入し、10Pa〜30Paの圧力下で高密度プラズマを発生させてガラス等の絶縁表面を有する基板上に絶縁膜を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素(N2O)と希ガスとを導入して絶縁膜表面にプラズマ処理を行ってもよい。少なくとも亜酸化窒素(N2O)と希ガスとを導入して絶縁膜表面に行われるプラズマ処理は、絶縁膜の成膜より後に行う。上記プロセス順序を経た絶縁膜は、膜厚が薄く、例えば100nm未満であっても信頼性を確保することができる絶縁膜である。

【0110】

ゲート絶縁層102の形成の際、チャンバーに導入するモノシランガス(SiH4)と亜酸化窒素(N2O)との流量比は、1:10から1:200の範囲とする。また、チャンバーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用いることができるが、中でも安価であるアルゴンを用いることが好ましい。

【0111】

また、高密度プラズマ装置により得られた絶縁膜は、一定した厚さの膜形成ができるため段差被覆性に優れている。また、高密度プラズマ装置により得られる絶縁膜は、薄い膜の厚みを精密に制御することができる。

【0112】

上記プロセス順序を経た絶縁膜は、従来の平行平板型のPCVD装置で得られる絶縁膜とは大きく異なっており、同じエッチャントを用いてエッチング速度を比較した場合において、平行平板型のPCVD装置で得られる絶縁膜の10%以上または20%以上遅く、高密度プラズマ装置で得られる絶縁膜は緻密な膜と言える。

【0113】

また、ゲート絶縁層102として、有機シランガスを用いたCVD法により酸化シリコン層を形成することも可能である。有機シランガスとしては、珪酸エチル(TEOS:化学式Si(OC2H5)4)、テトラメチルシラン(TMS:化学式Si(CH3)4)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OC2H5)3)、トリスジメチルアミノシラン(SiH(N(CH3)2)3)等のシリコン含有化合物を用いることができる。

【0114】

なお、ゲート絶縁層102として、アルミニウム、イットリウム、またはハフニウムの酸化物、窒化物、酸化窒化物、または窒化酸化物の一種または少なくとも2種以上含む化合物を用いることもできる。

【0115】

また、ゲート絶縁層102と酸化物半導体層103を連続成膜してもよい。例えば、珪素もしくは酸化珪素(人工石英)からなるターゲット材料と、酸化物半導体膜用のターゲット材料を備えたマルチチャンバー型のスパッタリング装置を用いれば、成膜後のゲート絶縁層102を大気にさらすことなく連続成膜できる。

【0116】

次いで、酸化物半導体膜をゲート絶縁層102上に形成する。酸化物半導体膜としては、四元系金属酸化物であるIn−Sn−Ga−Zn−O膜や、三元系金属酸化物であるIn−Ga−Zn−O膜、In−Sn−Zn−O膜、In−Al−Zn−O膜、Sn−Ga−Zn−O膜、Al−Ga−Zn−O膜、Sn−Al−Zn−O膜や、二元系金属酸化物であるIn−Zn−O膜、Sn−Zn−O膜、Al−Zn−O膜、Zn−Mg−O膜、Sn−Mg−O膜、In−Mg−O膜、In−Ga−O膜や、In−O膜、Sn−O膜、Zn−O膜などの酸化物半導体膜を用いることができる。また、上記酸化物半導体膜にSiO2を含んでもよい。

【0117】

また、酸化物半導体膜は、InMO3(ZnO)m(m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。InMO3(ZnO)m(m>0)で表記される構造の酸化物半導体膜のうち、MとしてGaを含む構造の酸化物半導体を、上記したIn−Ga−Zn−O系酸化物半導体とよび、その薄膜をIn−Ga−Zn−O膜ともよぶこととする。

【0118】

酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

【0119】

酸化物半導体膜は実施の形態1、または実施の形態2で説明した方法を適用して製造したターゲットを用いて、スパッタリング法により成膜する。当該ターゲットを用いて成膜した酸化物半導体膜は大気に由来する不純物(例えば水素原子を含む化合物等)の含有量が少なく、例えば、水素は5×1019cm−3以下、好ましくは5×1018cm−3以下、さらに好ましくは5×1017cm−3以下、または1×1016cm−3未満となる。

【0120】

本実施の形態では、ターゲット材料に、In、Ga、及びZnを含む酸化物半導体(組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol%]、In:Ga:Zn=1:1:0.5[at.%])を用い、In−Ga−Zn−O系膜を成膜する。また、基板とターゲット材料の間の距離は、例えば100mmとする。

【0121】

なお、酸化物半導体膜を成膜する成膜室は、排気手段としてクライオポンプを備えている。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。

【0122】

成膜室を、クライオポンプ、またはターボポンプにコールドトラップを加えて排気すると、例えば、H2Oに代表される水素原子を含む化合物や炭素原子を含む化合物を排気できる。本実施の形態においては、加熱によりターゲット材料から脱離する不純物を排気できるため特に有効である。

【0123】

また、酸化物半導体膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において、スパッタ法により成膜する。本実施の形態では、スパッタリングガスとして、酸素(酸素流量比率100%)を用い、圧力0.6Paで成膜を行う。

【0124】

本発明の一態様のターゲットに適用可能なスパッタ法としては、例えば、スパッタ用電源に高周波電源を用いるRFスパッタ法と、DCスパッタ法があり、さらにパルス的にバイアスを与えるパルスDCスパッタ法もある。RFスパッタ法は主に絶縁膜を成膜する場合に用いられ、DCスパッタ法は主に金属導電膜を成膜する場合に用いられる。

【0125】

また、チャンバー内部に磁石機構を備えたマグネトロンスパッタ法を用いるスパッタ装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタ法を用いる装置がある。

【0126】

また、スパッタ法を用いる成膜方法として、成膜中にターゲット材料とスパッタガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタ法や、成膜中に基板にも電圧をかけるバイアススパッタ法もある。

【0127】

また、材料の異なるターゲット材料を複数設置する多元スパッタ法もある。多元スパッタ法は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時にスパッタリングして混合物を成膜することもできる。

【0128】

本実施の形態では、電源として、直流(DC)電源0.5kWを用いる。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均一となるために好ましい。

【0129】

実施の形態1または実施の形態2で説明した方法で包装したターゲットを用いて成膜した酸化物半導体膜は、H2Oに代表される水素原子を含む化合物や炭素原子を含む化合物、もしくは水素原子や炭素原子等の不純物の含有量が少ない。例えば水素濃度を本発明の技術思想的には、ゼロまたはゼロに近いことを理想とした酸化物半導体膜が成膜できる。

【0130】

なお、酸化物半導体層を形成した後、酸化物半導体層に第1の加熱処理を施してもよい。第1の加熱処理の詳細については、一連の薄膜トランジスタの作製工程の説明のあとに説明する。

【0131】

なお、酸化物半導体膜を成膜する前に、スパッタ装置にアルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層102の表面に付着しているゴミを除去することが好ましい。逆スパッタとは、アルゴン雰囲気下で基板にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

【0132】

次いで、酸化物半導体層103を第2のフォトリソグラフィ工程により島状に加工し、酸化物半導体層113を形成する。

【0133】

なお、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0134】

次いで、コンタクトホール128を第3のフォトリソグラフィ工程によりゲート絶縁層102に形成する。なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体層及びゲート絶縁層102の表面に付着しているレジスト残渣などを除去することが好ましい。また、この段階での断面図を図5(B)に示す。

【0135】

なお、本実施の形態では、第3のフォトリソグラフィ工程によりゲート絶縁層を選択的にエッチングしてゲート配線層111bに達するコンタクトホール128を形成するが、この方法に限定されない。酸化物半導体膜を成膜した後、酸化物半導体膜上にレジストマスクを形成し、ゲート電極111aに達するコンタクトホールを形成してもよい。コンタクトホールを形成した後、レジストマスクを除去し、別のフォトマスクを用いて酸化物半導体膜上にレジストマスクを形成し、酸化物半導体膜を選択的にエッチングして島状の酸化物半導体層に加工する工程としてもよい。

【0136】

次いで、薄膜トランジスタのソース電極層及びドレイン電極層となる導電膜をゲート絶縁層102、酸化物半導体層113、及びコンタクトホール128を介してゲート配線層111b上に成膜する。

【0137】

ソース電極層及びドレイン電極層となる導電膜は、実施の形態1、または実施の形態2で説明した方法を適用して包装したターゲットを用いて、スパッタリング法により成膜する。

【0138】

ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)を形成する導電膜としては、Al、Cu、Cr、Ta、Ti、Mo、Wなどの金属材料、または該金属材料を成分とする合金材料で形成する。また、Al、Cuなどの金属膜の一方または双方にCr、Ta、Ti、Mo、Wなどの高融点金属膜を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されているAl材料を用いることで耐熱性を向上させることが可能となる。

【0139】

ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)は導電性の金属酸化物膜で形成しても良い。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

【0140】

酸化物半導体層113に接する導電膜は酸素親和性の高い金属を含む材料が好ましい。酸素親和性の高い金属としては、チタン(Ti)、マンガン(Mn)、マグネシウム(Mg)、ジルコニウム、ベリリウム、トリウムのいずれか一または複数から選択された材料であることが好ましい。本実施の形態では、チタン膜(膜厚100nm)とアルミニウム膜(膜厚200nm)とチタン膜(膜厚100nm)の3層構造の導電膜を形成する。また、Ti膜に変えて窒化チタン膜を用いてもよい。

【0141】

なお、200℃〜600℃の熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に持たせることが好ましい。例えばヒロック防止元素が添加されたアルミニウム合金や、耐熱性導電膜と積層した導電膜を用いることが好ましい。なお、導電膜の成膜方法は、スパッタ法や真空蒸着法(電子ビーム蒸着法など)や、アーク放電イオンプレーティング法や、スプレー法を用いる。また、銀、金、銅などの導電性ナノペーストを用いてスクリーン印刷法、インクジェット法などを用いて吐出し焼成して形成しても良い。

【0142】

次いで、第4のフォトリソグラフィ工程によりレジストマスクを形成し、導電膜を選択的にエッチング除去してソース電極層、ドレイン電極層を含む第2配線層(115a、115b、115c)を形成する(図5(C)参照。)。また、図5(C)に示すように、コンタクトホール128を介してゲート配線層111bに第2配線層115cが直接接続する。

【0143】

また、第4のフォトリソグラフィ工程においては、酸化物半導体層上に接する導電膜のみを選択的に除去する部分がある。酸化物半導体層上に接する導電膜のみを選択的に除去するため、アルカリ性のエッチャントとしてアンモニア過水(組成の重量比として、過酸化水素:アンモニア:水=5:2:2)などを用いると、導電膜を選択的に除去し、In−Ga−Zn−O系酸化物半導体からなる酸化物半導体層を残存させることができる。

【0144】

また、エッチング条件にもよるが第4のフォトリソグラフィ工程において酸化物半導体層の露出領域がエッチングされる場合がある。その場合、ソース電極層とドレイン電極層に挟まれる領域(115aと115bに挟まれる領域)の酸化物半導体層の厚みは、ゲート電極111a上でソース電極層が重なる領域の酸化物半導体層の厚み、またはドレイン電極層が重なる領域の酸化物半導体層の厚みに比べ、薄くなる。(図5(C)参照)。

【0145】

なお、ソース電極層及びドレイン電極層を含む第2配線層(115a、115b、及び115c)を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0146】

次いで、酸化物絶縁膜107を、ゲート絶縁層102、酸化物半導体層113上に形成する。この段階で、酸化物半導体層と酸化物絶縁膜107が接する領域が形成される。なお、ゲート電極111aに重畳し、酸化物絶縁膜107とゲート絶縁層102に接して挟まれる酸化物半導体層の領域がチャネル形成領域となる。

【0147】

H2Oに代表される水素原子を含む化合物や炭素原子を含む化合物、もしくは水素原子や炭素原子等の不純物の含有量が少ない酸化物半導体層に接する酸化物絶縁膜は、水分や、水素イオンや、OH−などの不純物を含まず、これらが外部から侵入することをブロックする。代表的には酸化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。また、酸化物絶縁膜107は、少なくとも1nm以上の膜厚とし、スパッタリング法など、酸化物絶縁膜107に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。

【0148】

本実施の形態では、スパッタリング法を用いて酸化物絶縁膜107として酸化珪素膜を成膜する。成膜時の基板温度は室温以上600℃以下、好ましくは200℃以上400℃以下とすればよく、本実施の形態では100℃とする。酸化珪素膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガス(代表的にはアルゴン)及び酸素雰囲気下において行うことができる。なお、スパッタ法で形成した酸化物絶縁膜は特に緻密であり、接する層へ不純物が拡散する現象を抑制する保護膜として単層であっても利用することができる。また、リン(P)や硼素(B)をドープしたターゲット材料を用い、酸化物絶縁膜にリン(P)や硼素(B)を添加することもできる。

【0149】

また、スパッタ法に用いるターゲット材料としては、酸化珪素または珪素を用いることができ、特に珪素が好ましい。珪素を用いて、酸素、及び希ガス雰囲気下でスパッタリング法により成膜した酸化珪素膜は、珪素原子または酸素原子の不対結合手(ダングリングボンド)を多く含んでいる。

【0150】

酸化物絶縁膜107は不対結合手を多く含むため、酸化物半導体層113に残存する不純物は、酸化物半導体層113と酸化物絶縁膜107が接する界面を介して、酸化物絶縁膜107に拡散し易くなる。具体的には、酸化物半導体層113に含まれる水素原子や、H2Oなど水素原子を含む化合物が酸化物絶縁膜107に拡散移動し易くなる。

【0151】

本実施の形態では、純度が6Nであり、柱状多結晶Bドープの珪素ターゲット材料(抵抗率0.01Ωcm)を用い、基板とターゲット材料の間の距離(T−S間距離)を89mm、圧力0.4Pa、直流(DC)電源6kW、酸素(酸素流量比率100%)雰囲気下でパルスDCスパッタ法により成膜する。膜厚は300nmとする。

【0152】

なお、酸化物絶縁膜107は酸化物半導体層のチャネル形成領域となる領域上に接して設けられ、チャネル保護層として機能する。

【0153】

次いで、保護絶縁層108を酸化物絶縁膜107上に形成する(図5(D)参照。)。保護絶縁層108としては、窒化珪素膜、窒化酸化珪素膜、または窒化アルミニウム膜などを用いる。本実施の形態では、RFスパッタ法を用いて窒化珪素膜の保護絶縁層108を形成する。

【0154】

酸化物絶縁膜107の形成後、第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350℃以下)を不活性ガス雰囲気下、または窒素ガス雰囲気下で行ってもよい。

【0155】

例えば、窒素雰囲気下で250℃、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層113の一部が酸化物絶縁膜107と接した状態で加熱され、また、酸化物半導体層113の他の一部が第2配線層(115a、及び115b)と接した状態で加熱される。

【0156】

酸化物半導体層113が、酸化物絶縁膜107と接した状態で第2の加熱処理が施されると、酸化物半導体層113の酸化物絶縁膜107が接する領域は高抵抗化(I型化)する。

【0157】

薄膜トランジスタ151はチャネル形成領域に高抵抗化(I型化)された酸化物半導体層が形成されているため、閾値電圧が正の値を示し、エンハンスメント型の挙動を示す。

【0158】

また、酸化物半導体に酸素親和性の強い金属導電膜が接する場合、加熱処理を行うと該金属導電膜側に酸素が移動しやすくなり、該酸化物半導体層はN型化する。従って、第2の加熱処理を行うと、酸化物半導体層113とチタンなど酸素親和性の強い金属導電膜からなるソース電極層、及びドレイン電極層(115a、及び115b)が接する領域はN型化する。

【0159】

なお、第2の加熱処理を行うタイミングは、第4のフォトリソグラフィ工程の終了直後に限定されず、第4のフォトリソグラフィ工程よりも後の工程であれば特に限定されない。

【0160】

以上の工程により、薄膜トランジスタ151を作製することができる。

【0161】

なお、本実施の形態では、第3のフォトリソグラフィ工程によりゲート絶縁層を選択的にエッチングしてゲート配線層111bに達するコンタクトホール128を形成するが、この方法に限定されない。例えば、ゲート絶縁層102を形成した後、ゲート絶縁層上にレジストマスクを形成し、ゲート配線層111bに達するコンタクトホールを形成してもよい。

【0162】

酸化物半導体層を形成した後、酸化物半導体層に残存する不純物濃度、代表的には水素濃度を本発明の技術思想的には、ゼロまたはゼロに近いことを理想として、酸化物半導体層に残留する水素濃度をさらに低減する必要があれば、第1の加熱処理を施して脱水化または脱水素化を行ってもよい。

【0163】

脱水化または脱水素化を行う第1の加熱処理の温度は、400℃以上であって750℃未満、好ましくは425℃以上とする。なお、425℃以上であれば熱処理時間は1時間以下でよいが、425℃未満であれば加熱処理時間は、1時間よりも長時間行うこととする。第1の加熱処理では、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下において加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、脱水化または脱水素化された酸化物半導体層を得る。酸化物半導体層の脱水化または脱水素化を行う加熱温度Tから、再び水が入らないような十分な温度まで同じ炉を用い、具体的には加熱温度Tよりも100℃以上下がるまで窒素雰囲気下で徐冷する。また、窒素雰囲気に限定されず、ヘリウム、ネオン、アルゴン等下において脱水化または脱水素化を行う。

【0164】

なお、加熱処理装置は電気炉に限られず、例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、上記のランプから発する光による熱輻射、およびランプから発する光で気体を加熱し、加熱された気体からの熱伝導によって、被処理物を加熱する装置である。気体には、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。また、LRTA装置、GRTA装置には、ランプだけでなく、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。

【0165】

また、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0166】

なお、第1の加熱処理の条件、または酸化物半導体層の材料によっては、結晶化し、微結晶膜または多結晶膜となる場合もある。例えば、結晶化率が90%以上、または80%以上の微結晶の酸化物半導体膜となる場合もある。また、第1の加熱処理の条件、または酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体膜となる場合もある。

【0167】

第1の加熱処理後に、酸化物半導体層は酸素欠乏型となり、低抵抗化する。第1の加熱処理後の酸化物半導体層は、成膜直後の酸化物半導体膜よりもキャリア濃度が高まり、1×1018/cm3以上のキャリア濃度を有する酸化物半導体層となる。そのため、第1の加熱処理を施した場合は、第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350℃以下)を不活性ガス雰囲気下、または窒素ガス雰囲気下で行う。

【0168】

なお、ゲート電極111a、及びゲート配線層111bは、第1の加熱処理の条件、またはその材料によっては、結晶化し、微結晶膜または多結晶膜となる場合もある。例えば、ゲート電極111a、及びゲート配線層111bとして、酸化インジウム酸化スズ合金膜を用いる場合は450℃1時間の第1の熱処理で結晶化し、ゲート電極111a、及びゲート配線層111bとして、酸化珪素を含む酸化インジウム酸化スズ合金膜を用いる場合は結晶化しない。

【0169】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、第4のフォトリソグラフィ工程を行う。

【0170】

図21は、酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図を示す。ゲート電極(GE1)上にゲート絶縁膜(GI)を介して酸化物半導体層(OS)が設けられ、その上にソース電極(S)及びドレイン電極(D)が設けられている。さらに、その上に絶縁層を介してバックゲート(GE2)が設けられている。

【0171】

図22は、図21に示すA−A’断面におけるエネルギーバンド図(模式図)を示す。図22(A)はソースとドレインの間の電圧を等電位(VD=0V)とした場合を示し、図22(B)はソースに対しドレインに正の電位(VD>0)を加えた場合を示す。

【0172】

図23、図24は、図21におけるB−B’間におけるエネルギーバンド図(模式図)を表す。図23はゲート電圧が0Vの場合の状態を示す。図24(A)はゲート(GE1)に正の電位(VG>0)が印加された状態であり、ソースとドレイン間にキャリア(電子)が流れるオン状態を示している。また、図24(B)は、ゲート(GE1)に負の電位(VG<0)が印加された状態であり、オフ状態(少数キャリアは流れない)である場合を示す。酸化物半導体の厚さが50nm程度であり、酸化物半導体が高純度化されたことによりドナー濃度が1×1018/cm3以下であれば、オフ状態において空乏層は酸化物半導体の全体に渡って広がる。すなわち完全空乏型の状態とみなすことができる。

【0173】

図25は、真空準位と金属の仕事関数(φM)、酸化物半導体の電子親和力(χ)の関係を示す。

【0174】

金属は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体はn型であり、そのフェルミ準位(EF)は、バンドギャップ中央に位置する真性フェルミ準位(Ei)から離れて、伝導帯寄りに位置している。なお、酸化物半導体において含有される水素の一部はドナーとなりN型化する一つの要因であることが知られている。

【0175】

これに対して本発明に係る酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性(I型)とし、又は真性型にしようとしたものである。すなわち、不純物を添加してI型化するのでなく、水素や水等の不純物を極力除去したことにより、高純度化されたI型(真性半導体)又はそれに近づけることを特徴としている。そうすることにより、フェルミ準位(EF)は真性フェルミ準位(Ei)と同じレベルにまですることができる。

【0176】

酸化物半導体のバンドギャップ(Eg)が3.15eVである場合、電子親和力(χ)は4.3eVと言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力(χ)とほぼ等しい。この場合、金属−酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

【0177】

すなわち、金属の仕事関数(φM)と酸化物半導体の電子親和力(χ)が等しい場合、両者が接触すると図22(A)で示すようなエネルギーバンド図(模式図)が示される。

【0178】

図22(B)において黒丸(●)は電子を示し、図22(B)において、ドレインに正の電圧(VD>0)を印加した上で、ゲートに電圧を印加しない場合(VG=0)を破線で示し、ゲートに正の電圧(VG>0)を印加した場合を実線で示す。ゲートに正の電圧(VG>0)を印加した場合、ドレインに正の電位が印加されると、電子はバリア(h)をこえて酸化物半導体に注入され、ドレインに向かって流れる。この場合、バリア(h)の高さは、ゲート電圧とドレイン電圧に依存して変化するが、ゲートに正の電圧(VG>0)を印加し正のドレイン電圧が印加された場合には、電圧印加のない図22(A)のバリアの高さすなわちバンドギャップ(Eg)の1/2よりもバリアの高さ(h)は小さい値となる。ゲートに電圧を印加しない場合は、高いポテンシャル障壁のために、電極から酸化物半導体側へキャリア(電子)が注入されず、電流を流さないオフ状態を示す。一方、ゲートに正の電圧を印加すると、ポテンシャル障壁が低下し、電流を流すオン状態を示す。

【0179】

このとき酸化物半導体に注入された電子は、図24(A)で示すように酸化物半導体中を流れる。

【0180】

また、図24(B)において、ゲート電極(GE1)に負の電位が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

【0181】

このように酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性(I型)とし、又は実質的に真性型とすることで、ゲート絶縁膜との界面特性顕在化し、バルクの特性と分離して考える必要がある。そのためゲート絶縁膜は、酸化物半導体と良好な界面を形成できるものが必要となる。例えば、VHF帯〜マイクロ波帯の電源周波数で生成される高密度プラズマを用いたCVD法で作製される絶縁膜、又はスパッタリング法で作製される絶縁膜を用いることが好ましい。

【0182】

酸化物半導体を高純度化しつつ、酸化物半導体とゲート絶縁膜との界面を良好なものとすることにより、薄膜トランジスタの特性としてチャネル幅Wが1×104μmでチャネル長が3μmの素子であっても、常温オフ電流が10−13A以下であり、サブスレッショルドスイング値(S値)が0.1V/dec.(ゲート絶縁膜厚100nm)が十分に期待される。

【0183】

このように、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより、薄膜トランジスタの動作を良好なものとすることができる。

【0184】

本実施の形態で例示された半導体素子は、製造からスパッタリング装置に取り付けるまで間に、大気にさらされることなく取り扱われたターゲット材料を用いて成膜した酸化物半導体膜を有している。大気にさらされることなく取り扱われたターゲット材料を用いて成膜した酸化物半導体膜に含まれる不純物は少なく、例えば水素濃度を本発明の技術思想的には、ゼロまたはゼロに近いことが理想とした酸化物半導体膜が成膜できる。なお、酸化物半導体層中の水素濃度測定は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectroscopy)で行えばよい。

【0185】

また、大気にさらされることなく取り扱われたターゲット材料を用いて成膜した、本実施の形態で例示された半導体素子が有する酸化物半導体膜のキャリア濃度は、1×1012cm−3、好ましくは1×1011cm−3の測定限界以下である。

【0186】

酸化物半導体のエネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上のものを用い、酸化物半導体層に含まれる水素を徹底的に除去することにより高純度化された酸化物半導体層を用いる。キャリア濃度を、限りなくゼロに近づけた酸化物半導体層をチャネル形成領域に適用して、薄膜トランジスタを構成する。キャリア濃度が限りなくゼロに近い酸化物半導体層を薄膜トランジスタのチャネル形成領域に用いることで、オフ電流値が極めて小さい薄膜トランジスタを提供できる。

【0187】

例えば、高純度化された酸化物半導体層を用いた薄膜トランジスタのチャネル長が3μm、チャネル幅が10mmの場合であっても、ドレイン電圧が1V及び10Vの場合において、ゲート電圧が−5Vから−20Vの範囲(オフ状態)において、ドレイン電流は1×10−13A以下となるように作用する。

【0188】

本実施の形態で例示する半導体素子は、不純物濃度が少ない酸化物半導体膜をチャネル形成領域に用いているため優れた電気特性と高い信頼性を有する。具体的には、オフ電流が極めて低く、閾値電圧が制御された薄膜トランジスタを提供できる。また、動作速度が速く、製造工程が比較的簡単であり、十分な信頼性を有する、酸化物半導体を用いた薄膜トランジスタを提供できる。

【0189】

また、BTストレス試験(バイアス・温度ストレス試験)を行った際のしきい値電圧のシフト量を低減することができ、信頼性の高い薄膜トランジスタを得ることができる。なお、本明細書中で、BTストレス試験(バイアス・温度ストレス試験)とは、薄膜トランジスタに高温雰囲気下で、高ゲート電圧を印加する試験のことを指す。

【0190】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0191】

(実施の形態4)

本実施の形態では、同一基板上に少なくとも駆動回路の一部と、画素部に配置する薄膜トランジスタを作製する例について以下に説明する。

【0192】

画素部に配置する薄膜トランジスタは、実施の形態3に従って形成する。また、実施の形態3に示す薄膜トランジスタはnチャネル型TFTであるため、駆動回路のうち、nチャネル型TFTで構成することができる駆動回路の一部を画素部の薄膜トランジスタと同一基板上に形成する。

【0193】

アクティブマトリクス型表示装置のブロック図の一例を図6(A)に示す。表示装置の基板5300上には、画素部5301、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304を有する。画素部5301には、複数の信号線が信号線駆動回路5304から延伸して配置され、複数の走査線が第1の走査線駆動回路5302、及び走査線駆動回路5303から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板5300はFPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路5305(コントローラ、制御ICともいう)に接続されている。

【0194】

図6(A)では、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304は、画素部5301と同じ基板5300上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板5300外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板5300上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0195】

なお、タイミング制御回路5305は、第1の走査線駆動回路5302に対し、一例として、第1の走査線駆動回路用スタート信号(GSP1)、走査線駆動回路用クロック信号(GCK1)を供給する。また、タイミング制御回路5305は、第2の走査線駆動回路5303に対し、一例として、第2の走査線駆動回路用スタート信号(GSP2)(スタートパルスともいう)、走査線駆動回路用クロック信号(GCK2)を供給する。信号線駆動回路5304に、信号線駆動回路用スタート信号(SSP)、信号線駆動回路用クロック信号(SCK)、ビデオ信号用データ(DATA)(単にビデオ信号ともいう)、ラッチ信号(LAT)を供給するものとする。なお各クロック信号は、周期のずれた複数のクロック信号でもよいし、クロック信号を反転させた信号(CKB)とともに供給されるものであってもよい。なお、第1の走査線駆動回路5302と第2の走査線駆動回路5303との一方を省略することが可能である。

【0196】

図6(B)では、駆動周波数が低い回路(例えば、第1の走査線駆動回路5302、第2の走査線駆動回路5303)を画素部5301と同じ基板5300に形成し、信号線駆動回路5304を画素部5301とは別の基板に形成する構成について示している。当該構成により、基板5300に形成する薄膜トランジスタよりも電界効果移動度が大きい単結晶半導体を用いたトランジスタによって、信号線駆動回路5304を構成することができる。したがって、表示装置の大型化、工程数の削減、コストの低減、又は歩留まりの向上などを図ることができる。

【0197】

また、実施の形態4に示す薄膜トランジスタは、nチャネル型TFTである。図7(A)、図7(B)ではnチャネル型TFTで構成する信号線駆動回路の構成、動作について一例を示し説明する。

【0198】

信号線駆動回路は、シフトレジスタ5601、及びスイッチング回路5602を有する。スイッチング回路5602は、スイッチング回路5602_1〜5602_N(Nは自然数)という複数の回路を有する。スイッチング回路5602_1〜5602_Nは、各々、薄膜トランジスタ5603_1〜5603_k(kは自然数)という複数のトランジスタを有する。薄膜トランジスタ5603_1〜5603_kは、Nチャネル型TFTである例を説明する。

【0199】

信号線駆動回路の接続関係について、スイッチング回路5602_1を例にして説明する。薄膜トランジスタ5603_1〜5603_kの第1端子は、各々、配線5604_1〜5604_kと接続される。薄膜トランジスタ5603_1〜5603_kの第2端子は、各々、信号線S1〜Skと接続される。薄膜トランジスタ5603_1〜5603_kのゲートは、配線5605_1と接続される。

【0200】

シフトレジスタ5601は、配線5605_1〜5605_Nに順番にHレベル(H信号、高電源電位レベル、ともいう)の信号を出力し、スイッチング回路5602_1〜5602_Nを順番に選択する機能を有する。

【0201】

スイッチング回路5602_1は、配線5604_1〜5604_kと信号線S1〜Skとの導通状態(第1端子と第2端子との間の導通)に制御する機能、即ち配線5604_1〜5604_kの電位を信号線S1〜Skに供給するか否かを制御する機能を有する。このように、スイッチング回路5602_1は、セレクタとしの機能を有する。また薄膜トランジスタ5603_1〜5603_kは、各々、配線5604_1〜5604_kと信号線S1〜Skとの導通状態を制御する機能、即ち配線5604_1〜5604_kの電位を信号線S1〜Skに供給する機能を有する。このように、薄膜トランジスタ5603_1〜5603_kは、各々、スイッチとしての機能を有する。

【0202】

なお、配線5604_1〜5604_kには、各々、ビデオ信号用データ(DATA)が入力される。ビデオ信号用データ(DATA)は、画像情報又は画像信号に応じたアナログ信号である場合が多い。

【0203】

次に、図7(A)の信号線駆動回路の動作について、図7(B)のタイミングチャートを参照して説明する。図7(B)には、信号Sout_1〜Sout_N、及び信号Vdata_1〜Vdata_kの一例を示す。信号Sout_1〜Sout_Nは、各々、シフトレジスタ5601の出力信号の一例であり、信号Vdata_1〜Vdata_kは、各々、配線5604_1〜5604_kに入力される信号の一例である。なお、信号線駆動回路の1動作期間は、表示装置における1ゲート選択期間に対応する。1ゲート選択期間は、一例として、期間T1〜期間TNに分割される。期間T1〜TNは、各々、選択された行に属する画素にビデオ信号用データ(DATA)を書き込むための期間である。

【0204】

期間T1〜期間TNにおいて、シフトレジスタ5601は、Hレベルの信号を配線5605_1〜5605_Nに順番に出力する。例えば、期間T1において、シフトレジスタ5601は、ハイレベルの信号を配線5605_1に出力する。すると、薄膜トランジスタ5603_1〜5603_kはオンになるので、配線5604_1〜5604_kと、信号線S1〜Skとが導通状態になる。このとき、配線5604_1〜5604_kには、Data(S1)〜Data(Sk)が入力される。Data(S1)〜Data(Sk)は、各々、薄膜トランジスタ5603_1〜5603_kを介して、選択される行に属する画素のうち、1列目〜k列目の画素に書き込まれる。こうして、期間T1〜TNにおいて、選択された行に属する画素に、k列ずつ順番にビデオ信号用データ(DATA)が書き込まれる。

【0205】

以上のように、ビデオ信号用データ(DATA)が複数の列ずつ画素に書き込まれることによって、ビデオ信号用データ(DATA)の数、又は配線の数を減らすことができる。よって、外部回路との接続数を減らすことができる。また、ビデオ信号が複数の列ずつ画素に書き込まれることによって、書き込み時間を長くすることができ、ビデオ信号の書き込み不足を防止することができる。

【0206】

なお、シフトレジスタ5601及びスイッチング回路5602としては、実施の形態3に示す薄膜トランジスタで構成される回路を用いることが可能である。この場合、シフトレジスタ5601が有する全てのトランジスタの極性をNチャネル型、又はPチャネル型のいずれかの極性のみで構成することができる。

【0207】

また、走査線駆動回路の構成について説明する。走査線駆動回路は、シフトレジスタを有している。また場合によってはレベルシフタやバッファ等を有していても良い。走査線駆動回路において、シフトレジスタにクロック信号(CK)及びスタートパルス信号(SP)が入力されることによって、選択信号が生成される。生成された選択信号はバッファにおいて緩衝増幅され、対応する走査線に供給される。走査線には、1ライン分の画素のトランジスタのゲート電極が接続されている。そして、1ライン分の画素のトランジスタを一斉にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

【0208】

走査線駆動回路及び/または信号線駆動回路の一部に用いるシフトレジスタの一形態について図8及び図9を用いて説明する。

【0209】

走査線駆動回路、信号線駆動回路のシフトレジスタについて、図8及び図9を参照して説明する。シフトレジスタは、第1のパルス出力回路10_1乃至第Nのパルス出力回路10_N(N≧3の自然数)を有している(図8(A)参照)。図8(A)に示すシフトレジスタの第1のパルス出力回路10_1乃至第Nのパルス出力回路10_Nには、第1の配線11より第1のクロック信号CK1、第2の配線12より第2のクロック信号CK2、第3の配線13より第3のクロック信号CK3、第4の配線14より第4のクロック信号CK4が供給される。また第1のパルス出力回路10_1では、第5の配線15からのスタートパルスSP1(第1のスタートパルス)が入力される。また2段目以降の第nのパルス出力回路10_n(nは、2≦n≦Nの自然数)では、一段前段のパルス出力回路からの信号(前段信号OUT(n−1)という)(n≧2の自然数)が入力される。また第1のパルス出力回路10_1では、2段後段の第3のパルス出力回路10_3からの信号が入力される。同様に、2段目以降の第nのパルス出力回路10_nでは、2段後段の第(n+2)のパルス出力回路10_(n+2)からの信号(後段信号OUT(n+2)という)が入力される。従って、各段のパルス出力回路からは、後段及び/または二つ前段のパルス出力回路に入力するための第1の出力信号OUT(1)(SR)〜OUT(N)(SR))、別の配線等に電気的に接続される第2の出力信号(OUT(1)〜OUT(N))が出力される。なお、図8(A)に示すように、シフトレジスタの最終段の2つの段には、後段信号OUT(n+2)が入力されないが、一例としては、別途第6の配線16より第2のスタートパルスSP2、第7の配線17より第3のスタートパルスSP3をそれぞれ入力する構成とすればよい。または、別途シフトレジスタの内部で生成された信号であってもよい。例えば、画素部へのパルス出力に寄与しない第(n+1)のパルス出力回路10_(n+1)、第(n+2)のパルス出力回路10_(n+2)を設け(ダミー段ともいう)、当該ダミー段より第2のスタートパルス(SP2)及び第3のスタートパルス(SP3)に相当する信号を生成する構成としてもよい。

【0210】

なお、クロック信号(CK)は、一定の間隔でHレベルとLレベル(L信号、低電源電位レベル、ともいう)を繰り返す信号である。ここで、第1のクロック信号(CK1)〜第4のクロック信号(CK4)は、順に1/4周期分遅延している。本実施の形態では、第1のクロック信号(CK1)〜第4のクロック信号(CK4)を利用して、パルス出力回路の駆動の制御等を行う。なお、クロック信号は、入力される駆動回路に応じて、GCK、SCKということもあるが、ここではCKとして説明を行う。

【0211】

第1の入力端子21、第2の入力端子22及び第3の入力端子23は、第1の配線11〜第4の配線14のいずれかと電気的に接続されている。例えば、図8(A)において、第1のパルス出力回路10_1は、第1の入力端子21が第1の配線11と電気的に接続され、第2の入力端子22が第2の配線12と電気的に接続され、第3の入力端子23が第3の配線13と電気的に接続されている。また、第2のパルス出力回路10_2は、第1の入力端子21が第2の配線12と電気的に接続され、第2の入力端子22が第3の配線13と電気的に接続され、第3の入力端子23が第4の配線14と電気的に接続されている。

【0212】

第1のパルス出力回路10_1〜第Nのパルス出力回路10_Nの各々は、第1の入力端子21、第2の入力端子22、第3の入力端子23、第4の入力端子24、第5の入力端子25、第1の出力端子26、第2の出力端子27を有しているとする(図8(B)参照)。第1のパルス出力回路10_1において、第1の入力端子21に第1のクロック信号CK1が入力され、第2の入力端子22に第2のクロック信号CK2が入力され、第3の入力端子23に第3のクロック信号CK3が入力され、第4の入力端子24にスタートパルスが入力され、第5の入力端子25に後段信号OUT(3)が入力され、第1の出力端子26より第1の出力信号OUT(1)(SR)が出力され、第2の出力端子27より第2の出力信号OUT(1)が出力されていることとなる。

【0213】

次に、パルス出力回路の具体的な回路構成の一例について、図8(C)で説明する。

【0214】

第1のパルス出力回路10_1は、第1のトランジスタ31〜第11のトランジスタ41を有している(図8(C)参照)。また、上述した第1の入力端子21〜第5の入力端子25、及び第1の出力端子26、第2の出力端子27に加え、第1の高電源電位VDDが供給される電源線51、第2の高電源電位VCCが供給される電源線52、低電源電位VSSが供給される電源線53から、第1のトランジスタ31〜第11のトランジスタ41に信号、または電源電位が供給される。ここで図8(C)における各電源線の電源電位の大小関係は、第1の高電源電位VDDは第2の高電源電位VCC以上の電位とし、第2の高電源電位VCCは第3の電源電位VSSより大きい電位とする。なお、第1のクロック信号(CK1)〜第4のクロック信号(CK4)は、一定の間隔でHレベルとLレベルを繰り返す信号であるが、HレベルのときVDD、LレベルのときVSSであるとする。なお電源線51の電位VDDを、電源線52の電位VCCより高くすることにより、動作に影響を与えることなく、トランジスタのゲート電極に印加される電位を低く抑えることができ、トランジスタのしきい値のシフトを低減し、劣化を抑制することができる。

【0215】

図8(C)において、第1のトランジスタ31は、第1端子が電源線51に電気的に接続され、第2端子が第9のトランジスタ39の第1端子に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第4の入力端子24に電気的に接続されている。第2のトランジスタ32は、第1端子が電源線53に電気的に接続され、第2端子が第9のトランジスタ39の第1端子に電気的に接続され、ゲート電極が第4のトランジスタ34のゲート電極に電気的に接続されている。第3のトランジスタ33は、第1端子が第1の入力端子21に電気的に接続され、第2端子が第1の出力端子26に電気的に接続されている。第4のトランジスタ34は、第1端子が電源線53に電気的に接続され、第2端子が第1の出力端子26に電気的に接続されている。第5のトランジスタ35は、第1端子が電源線53に電気的に接続され、第2端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極が第4の入力端子24に電気的に接続されている。第6のトランジスタ36は、第1端子が電源線52に電気的に接続され、第2端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第5の入力端子25に電気的に接続されている。第7のトランジスタ37は、第1端子が電源線52に電気的に接続され、第2端子が第8のトランジスタ38の第2端子に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第3の入力端子23に電気的に接続されている。第8のトランジスタ38は、第1端子が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が第2の入力端子22に電気的に接続されている。第9のトランジスタ39は、第1端子が第1のトランジスタ31の第2端子及び第2のトランジスタ32の第2端子に電気的に接続され、第2端子が第3のトランジスタ33のゲート電極及び第10のトランジスタ40のゲート電極に電気的に接続され、ゲート電極(下方のゲート電極及び上方のゲート電極)が電源線52に電気的に接続されている。第10のトランジスタ40は、第1端子が第1の入力端子21に電気的に接続され、第2端子が第2の出力端子27に電気的に接続され、ゲート電極が第9のトランジスタ39の第2端子に電気的に接続されている。第11のトランジスタ41は、第1端子が電源線53に電気的に接続され、第2端子が第2の出力端子27に電気的に接続され、ゲート電極が第2のトランジスタ32のゲート電極及び第4のトランジスタ34のゲート電極に電気的に接続されている。

【0216】

図8(C)において、第3のトランジスタ33のゲート電極、第10のトランジスタ40のゲート電極、及び第9のトランジスタ39の第2端子の接続箇所をノードAとする。また、第2のトランジスタ32のゲート電極、第4のトランジスタ34のゲート電極、第5のトランジスタ35の第2端子、第6のトランジスタ36の第2端子、第8のトランジスタ38の第1端子、及び第11のトランジスタ41のゲート電極の接続箇所をノードBとする(図9(A)参照)。

【0217】

なお、薄膜トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。ここで、ソースとドレインとは、薄膜トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。

【0218】

ここで、図9(A)に示したパルス出力回路を複数具備するシフトレジスタのタイミングチャートについて図9(B)に示す。なおシフトレジスタが走査線駆動回路である場合、図9(B)中の期間61は垂直帰線期間であり、期間62はゲート選択期間に相当する。

【0219】

なお、図9(A)に示すように、ゲートに第2の電源電位VCCが印加される第9のトランジスタ39を設けておくことにより、ブートストラップ動作の前後において、以下のような利点がある。

【0220】

ゲート電極に第2の電源電位VCCが印加される第9のトランジスタ39がない場合、ブートストラップ動作によりノードAの電位が上昇すると、第1のトランジスタ31の第2端子であるソースの電位が上昇していき、第1の電源電位VDDより大きくなる。そして、第1のトランジスタ31のソースが第1端子側、即ち電源線51側に切り替わる。そのため、第1のトランジスタ31においては、ゲートとソースの間、ゲートとドレインの間ともに、大きなバイアス電圧が印加されるために大きなストレスがかかり、トランジスタの劣化の要因となりうる。そこで、ゲート電極に第2の電源電位VCCが印加される第9のトランジスタ39を設けておくことにより、ブートストラップ動作によりノードAの電位は上昇するものの、第1のトランジスタ31の第2端子の電位の上昇を生じないようにすることができる。つまり、第9のトランジスタ39を設けることにより、第1のトランジスタ31のゲートとソースの間に印加される負のバイアス電圧の値を小さくすることができる。よって、本実施の形態の回路構成とすることにより、第1のトランジスタ31のゲートとソースの間に印加される負のバイアス電圧も小さくできるため、ストレスによる第1のトランジスタ31の劣化を抑制することができる。

【0221】

なお、第9のトランジスタ39を設ける箇所については、第1のトランジスタ31の第2端子と第3のトランジスタ33のゲートとの間に第1端子と第2端子を介して接続されるように設ける構成であればよい。なお、本実施形態でのパルス出力回路を複数具備するシフトレジスタの場合、走査線駆動回路より段数の多い信号線駆動回路では、第9のトランジスタ39を省略してもよく、トランジスタ数を削減する利点がある。

【0222】

なお第1のトランジスタ31乃至第11のトランジスタ41の半導体層として、酸化物半導体を用いることにより、薄膜トランジスタのオフ電流を低減すると共に、オン電流及び電界効果移動度を高めることが出来ると共に、劣化の度合いを低減することが出来るため、回路内の誤動作を低減することができる。また酸化物半導体を用いたトランジスタは、アモルファスシリコンを用いたトランジスタに比べ、ゲート電極に高電位が印加されることによるトランジスタの劣化の程度が小さい。そのため、第2の電源電位VCCを供給する電源線に、第1の電源電位VDDを供給しても同様の動作が得られ、且つ回路間を引き回す電源線の数を低減することができるため、回路の小型化を図ることが出来る。

【0223】

なお、第7のトランジスタ37のゲート電極に第3の入力端子23によって供給されるクロック信号、第8のトランジスタ38のゲート電極に第2の入力端子22によって供給されるクロック信号は、第7のトランジスタのゲート電極に第2の入力端子22によって供給されるクロック信号、第8のトランジスタのゲート電極に第3の入力端子23によって供給されるクロック信号となるように、結線関係を入れ替えても同様の作用を奏する。なお、図9(A)に示すシフトレジスタにおいて、第7のトランジスタ37及び第8のトランジスタ38が共にオンの状態から、第7のトランジスタ37がオフ、第8のトランジスタ38がオンの状態、次いで第7のトランジスタ37がオフ、第8のトランジスタ38がオフの状態とすることによって、第2の入力端子22及び第3の入力端子23の電位が低下することで生じる、ノードBの電位の低下が第7のトランジスタ37のゲート電極の電位の低下、及び第8のトランジスタ38のゲート電極の電位の低下に起因して2回生じることとなる。一方、図9(A)に示すシフトレジスタにおいて、第7のトランジスタ37及び第8のトランジスタ38が共にオンの状態から、第7のトランジスタ37がオン、第8のトランジスタ38がオフの状態、次いで、第7のトランジスタ37がオフ、第8のトランジスタ38がオフの状態とすることによって、第2の入力端子22及び第3の入力端子23の電位が低下することで生じるノードBの電位の低下を、第8のトランジスタ38のゲート電極の電位の低下による一回に低減することができる。そのため、第7のトランジスタ37のゲート電極に第3の入力端子23からクロック信号CK3、第8のトランジスタ38のゲート電極に第2の入力端子22からクロック信号CK2が供給される結線関係とすることが好適である。なぜなら、ノードBの電位の変動回数が減少され、ノイズを低減することが出来るため好適である。

【0224】

このように、第1の出力端子26及び第2の出力端子27の電位をLレベルに保持する期間に、ノードBに定期的にHレベルの信号が供給される構成とすることにより、パルス出力回路の誤動作を抑制することができる。

【0225】

(実施の形態5)

実施の形態3に示す薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、実施の形態3に示す薄膜トランジスタを駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

【0226】

表示装置は表示素子を含む。表示素子としては液晶素子(液晶表示素子ともいう)、発光素子(発光表示素子ともいう)を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(Electro Luminescence)素子、有機EL素子等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

【0227】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに、該表示装置を作製する過程における、表示素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッチングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

【0228】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源(照明装置含む)を指す。また、コネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

【0229】

本実施の形態では、半導体装置の一形態に相当する液晶表示パネルの外観及び断面について、図10を用いて説明する。図10(A1)(A2)は、第1の基板4001上に形成された実施の形態3で示したIn−Ga−Zn−O系膜を酸化物半導体層として含む信頼性の高い薄膜トランジスタ4010、4011、及び液晶素子4013を、第1の基板4001と第2の基板4006との間にシール材4005によって封止した、パネルの上面図であり、図10(B)は、図10(A1)(A2)のM−Nにおける断面図に相当する。

【0230】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。また第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003が実装されている。

【0231】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG法、ワイヤボンディング法、或いはTAB法などを用いることができる。図10(A1)は、COG法により信号線駆動回路4003を実装する例であり、図10(A2)は、TAB法により信号線駆動回路4003を実装する例である。

【0232】

また第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、薄膜トランジスタを複数有しており、図10(B)では、画素部4002に含まれる薄膜トランジスタ4010と、走査線駆動回路4004に含まれる薄膜トランジスタ4011とを例示している。薄膜トランジスタ4010、4011上には絶縁層4020、4021が設けられている。

【0233】

薄膜トランジスタ4010、4011は、In−Ga−Zn−O系膜を酸化物半導体層として含む信頼性の高い実施の形態3に示す薄膜トランジスタを適用することができる。本実施の形態において、薄膜トランジスタ4010、4011はnチャネル型薄膜トランジスタである。

【0234】

また、液晶素子4013が有する画素電極層4030は、薄膜トランジスタ4010と電気的に接続されている。そして液晶素子4013の対向電極層4031は第2の基板4006上に形成されている。画素電極層4030と対向電極層4031と液晶層4008とが重なっている部分が、液晶素子4013に相当する。なお、画素電極層4030、対向電極層4031はそれぞれ配向膜として機能する絶縁層4032、4033が設けられ、絶縁層4032、4033を介して液晶層4008を挟持している。なお、図示はしていないが、カラーフィルタは第1の基板4001または第2の基板4006のどちら側に設けても良い。

【0235】

なお、第1の基板4001、第2の基板4006としては、ガラス、金属(代表的にはステンレス)、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルム、またはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

【0236】

また4035は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、画素電極層4030と対向電極層4031との間の距離(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていても良い。また、対向電極層4031は、薄膜トランジスタ4010と同一基板上に設けられる共通電位線と電気的に接続される。共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極層4031と共通電位線とを電気的に接続することができる。なお、導電性粒子はシール材4005に含有させる。

【0237】

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために5重量%以上のカイラル剤を混合させた液晶組成物を液晶層4008に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が10μsec.以上100μsec.以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

【0238】

なお本実施の形態は透過型液晶表示装置の例であるが、本発明は反射型液晶表示装置でも半透過型液晶表示装置でも適用できる。

【0239】

また、本実施の形態の液晶表示装置では、基板の外側(視認側)に偏光板を設け、内側に着色層、表示素子に用いる電極層という順に設ける例を示すが、偏光板は基板の内側に設けてもよい。また、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、ブラックマトリクスとして機能する遮光膜を設けてもよい。

【0240】

また、本実施の形態では、薄膜トランジスタの表面凹凸を低減するため、及び薄膜トランジスタの信頼性を向上させるため、実施の形態3で得られた薄膜トランジスタを保護膜や平坦化絶縁膜として機能する絶縁層(絶縁層4020、絶縁層4021)で覆う構成となっている。なお、保護膜は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。保護膜は、スパッタ法を用いて、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜の単層、又は積層で形成すればよい。本実施の形態では保護膜をスパッタ法で形成する例を示すが、特に限定されず種々の方法で形成すればよい。

【0241】

ここでは、保護膜として積層構造の絶縁層4020を形成する。ここでは、絶縁層4020の一層目として、スパッタ法を用いて酸化シリコン膜を形成する。保護膜として酸化シリコン膜を用いると、ソース電極層及びドレイン電極層として用いるアルミニウム膜のヒロック防止に効果がある。

【0242】

また、保護膜の二層目として絶縁層を形成する。ここでは、絶縁層4020の二層目として、スパッタ法を用いて窒化シリコン膜を形成する。保護膜として窒化シリコン膜を用いると、ナトリウム等の可動イオンが半導体領域中に侵入して、TFTの電気特性を変化させることを抑制することができる。

【0243】

また、保護膜を形成した後に、酸化物半導体層のアニール(300℃以上400℃以下)を行ってもよい。

【0244】

また、平坦化絶縁膜として絶縁層4021を形成する。絶縁層4021としては、アクリル、ポリイミド、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層4021を形成してもよい。

【0245】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi−O−Si結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基(例えばアルキル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有していても良い。

【0246】

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いることができる。絶縁層4021を材料液を用いて形成する場合、ベークする工程で同時に、酸化物半導体層のアニール(300℃以上400℃以下)を行ってもよい。絶縁層4021の焼成工程と酸化物半導体層のアニールを兼ねることで効率よく半導体装置を作製することが可能となる。

【0247】

画素電極層4030、対向電極層4031は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

【0248】

また、画素電極層4030、対向電極層4031として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000Ω/□以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1Ω・cm以下であることが好ましい。

【0249】

導電性高分子としては、いわゆるπ電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

【0250】

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC4018から供給されている。

【0251】

本実施の形態では、接続端子電極4015が、液晶素子4013が有する画素電極層4030と同じ導電膜から形成され、端子電極4016は、薄膜トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

【0252】

接続端子電極4015は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

【0253】

また図10においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

【0254】

図11は、実施の形態3に示すTFTを適用して作製されるTFT基板2600を用いて半導体装置として液晶表示モジュールを構成する一例を示している。

【0255】

図11は液晶表示モジュールの一例であり、TFT基板2600と対向基板2601がシール材2602により固着され、その間にTFT等を含む画素部2603、液晶層を含む表示素子2604、着色層2605が設けられ表示領域を形成している。着色層2605はカラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。TFT基板2600と対向基板2601の外側には偏光板2606、偏光板2607、拡散板2613が配設されている。光源は冷陰極管2610と反射板2611により構成され、回路基板2612は、フレキシブル配線基板2609によりTFT基板2600の配線回路部2608と接続され、コントロール回路や電源回路などの外部回路が組みこまれている。また偏光板と、液晶層との間に位相差板を有した状態で積層してもよい。

【0256】

液晶表示モジュールには、TN(Twisted Nematic)モード、IPS(In−Plane−Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi−domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASM(Axially Symmetric aligned Micro−cell)モード、OCB(Optical Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モードなどを用いることができる。

【0257】

以上の工程により、半導体装置として信頼性の高い液晶表示パネルを作製することができる。

【0258】

なお、本実施の形態に示す構成は、他の実施の形態に示した構成を適宜組み合わせて用いることができることとする。

【0259】

(実施の形態6)

本実施の形態では、実施の形態3に示す薄膜トランジスタを適用した半導体装置として電子ペーパーの例を示す。

【0260】

図12は、半導体装置の例としてアクティブマトリクス型の電子ペーパーを示す。半導体装置に用いられる薄膜トランジスタ581としては、実施の形態3で示す薄膜トランジスタを適用することができる。

【0261】

図12の電子ペーパーは、ツイストボール表示方式を用いた表示装置の例である。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせて球形粒子の向きを制御することにより、表示を行う方法である。

【0262】

基板580と基板596との間に封止される薄膜トランジスタ581はボトムゲート構造の薄膜トランジスタであり、ソース電極層又はドレイン電極層は、第1の電極層587と、絶縁層583、および585に形成する開口で接しており電気的に接続している。第1の電極層587と第2の電極層588との間には黒色領域590a及び白色領域590bを有し、周りに液体で満たされているキャビティ594を含む球形粒子589が設けられており、球形粒子589の周囲は樹脂等の充填材595で充填されている(図12参照。)。本実施の形態においては、第1の電極層587が画素電極に相当し、第2の電極層588が共通電極に相当する。第2の電極層588は、薄膜トランジスタ581と同一基板上に設けられる共通電位線と電気的に接続される。基板580と596の間に配置される導電性粒子を介して第2の電極層588と共通電位線とを電気的に接続することができる。

【0263】

また、ツイストボールの代わりに、電気泳動素子を用いることも可能である。透明な液体と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径10μm以上200μm以下程度のマイクロカプセルを用いる。第1の電極層と第2の電極層との間に設けられるマイクロカプセルは、第1の電極層と第2の電極層によって、電場が与えられると、白い微粒子と、黒い微粒子が互いに逆の方向に移動し、白または黒を表示することができる。この原理を応用した表示素子が電気泳動表示素子であり、一般的に電子ペーパーとよばれている。電気泳動表示素子は、液晶表示素子に比べて反射率が高いため、補助ライトは不要であり、また消費電力が小さく、薄暗い場所でも表示部を認識することが可能である。また、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能であるため、電波発信源から表示機能付き半導体装置(単に表示装置、又は表示装置を具備する半導体装置ともいう)を遠ざけた場合であっても、表示された像を保存しておくことが可能となる。

【0264】

以上の工程により、半導体装置として信頼性の高い電子ペーパーを作製することができる。

【0265】

なお、本実施の形態に示す構成は、他の実施の形態に示した構成を適宜組み合わせて用いることができることとする。

【0266】

(実施の形態7)

本実施の形態では、実施の形態3に示す薄膜トランジスタを適用した半導体装置として発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0267】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子及び正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子及び正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0268】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

【0269】

図13は、本発明を適用した半導体装置の例としてデジタル時間階調駆動を適用可能な画素構成の一例を示す図である。

【0270】

デジタル時間階調駆動を適用可能な画素の構成及び画素の動作について説明する。ここでは、実施の形態3で示した、酸化物半導体層(In−Ga−Zn−O系膜)をチャネル形成領域に用いるnチャネル型のトランジスタを、1つの画素に2つ用いる例を示す。

【0271】

画素6400は、スイッチング用トランジスタ6401、駆動用トランジスタ6402、発光素子6404及び容量素子6403を有している。スイッチング用トランジスタ6401はゲートが走査線6406に接続され、第1電極(ソース電極及びドレイン電極の一方)が信号線6405に接続され、第2電極(ソース電極及びドレイン電極の他方)が駆動用トランジスタ6402のゲートに接続されている。駆動用トランジスタ6402は、ゲートが容量素子6403を介して電源線6407に接続され、第1電極が電源線6407に接続され、第2電極が発光素子6404の第1電極(画素電極)に接続されている。発光素子6404の第2電極は共通電極6408に相当する。共通電極6408は、同一基板上に形成される共通電位線と電気的に接続される。その接続部分を共通接続部とすればよい。

【0272】

なお、発光素子6404の第2電極(共通電極6408)には低電源電位が設定されている。なお、低電源電位とは、電源線6407に設定される高電源電位を基準にして低電源電位<高電源電位を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子6404に印加して、発光素子6404に電流を流して発光素子6404を発光させるため、高電源電位と低電源電位との電位差が発光素子6404の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

【0273】

なお、容量素子6403は駆動用トランジスタ6402のゲート容量を代用して省略することも可能である。駆動用トランジスタ6402のゲート容量については、チャネル領域とゲート電極との間で容量が形成されていてもよい。

【0274】

ここで、電圧入力電圧駆動方式の場合には、駆動用トランジスタ6402のゲートには、駆動用トランジスタ6402が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。つまり、駆動用トランジスタ6402は線形領域で動作させる。駆動用トランジスタ6402は線形領域で動作させるため、電源線6407の電圧よりも高い電圧を駆動用トランジスタ6402のゲートにかける。なお、信号線6405には、(電源線電圧+駆動用トランジスタ6402のVth)以上の電圧をかける。

【0275】

また、デジタル時間階調駆動に代えて、アナログ階調駆動を行う場合も信号の入力を異ならせることで、図13と同じ画素構成を用いることができる。

【0276】

アナログ階調駆動を行う場合、駆動用トランジスタ6402のゲートに発光素子6404の順方向電圧+駆動用トランジスタ6402のVth以上の電圧をかける。発光素子6404の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。なお、駆動用トランジスタ6402が飽和領域で動作するようなビデオ信号を入力することで、発光素子6404に電流を流すことができる。駆動用トランジスタ6402を飽和領域で動作させるため、電源線6407の電位は、駆動用トランジスタ6402のゲート電位よりも高くする。ビデオ信号をアナログとすることで、発光素子6404にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

【0277】

なお、図13に示す画素構成は、これに限定されない。例えば、図13に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ又は論理回路などを追加してもよい。

【0278】

次に、発光素子の構成について、図14を用いて説明する。ここでは、駆動用TFTがn型の場合を例に挙げて、画素の断面構造について説明する。図14(A)(B)(C)の半導体装置に用いられる駆動用TFT7001、7011、7021は、実施の形態3で示す薄膜トランジスタと同様に作製でき、In−Ga−Zn−O系膜を酸化物半導体層として含む信頼性の高い薄膜トランジスタである。

【0279】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に薄膜トランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の画素構成はどの射出構造の発光素子にも適用することができる。

【0280】

下面射出構造の発光素子について図14(A)を用いて説明する。

【0281】

駆動用TFT7011がn型で、発光素子7012から発せられる光が第1の電極7013側に射出する場合の、画素の断面図を示す。図14(A)では、駆動用TFT7011のドレイン電極層と電気的に接続された可視光に対する透光性を有する導電膜7017上に、発光素子7012の第1の電極7013が形成されており、第1の電極7013上にEL層7014、第2の電極7015が順に積層されている。

【0282】

可視光に対する透光性を有する導電膜7017としては、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの可視光に対する透光性を有する導電膜を用いることができる。

【0283】

また、発光素子の第1の電極7013は様々な材料を用いることができる。例えば、第1の電極7013を陰極として用いる場合には、仕事関数が小さい材料、具体的には、例えば、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、及びこれらを含む合金(Mg:Ag、Al:Liなど)の他、YbやEr等の希土類金属等が好ましい。図14(A)では、第1の電極7013の膜厚は、可視光を透過する程度(好ましくは、5nm〜30nm程度)とする。例えば20nmの膜厚を有するアルミニウム膜を、第1の電極7013として用いる。

【0284】

なお、可視光に対する透光性を有する導電膜とアルミニウム膜を積層成膜した後、選択的にエッチングして可視光に対する透光性を有する導電膜7017と第1の電極7013を形成してもよく、この場合、同じマスクを用いてエッチングすることができるため、好ましい。

【0285】

また、第1の電極7013の周縁部は、隔壁7019で覆う。隔壁7019は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁7019は、特に感光性の樹脂材料を用い、第1の電極7013上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。隔壁7019として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

【0286】

また、第1の電極7013及び隔壁7019上に形成するEL層7014は、少なくとも発光層を含めば良く、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。EL層7014が複数の層で構成されている場合、陰極として機能する第1の電極7013上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。

【0287】

また、上記積層順に限定されず、第1の電極7013を陽極として機能させ、第1の電極7013上にホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層してもよい。ただし、消費電力を比較する場合、第1の電極7013を陰極として機能させ、第1の電極7013上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層するほうが、駆動回路部の電圧上昇を抑制でき、消費電力を少なくできるため好ましい。

【0288】

また、EL層7014上に形成する第2の電極7015としては、様々な材料を用いることができる。例えば、第2の電極7015を陽極として用いる場合、仕事関数が大きい材料(具体的には4.0eV以上)、例えば、ZrN、Ti、W、Ni、Pt、Cr等や、ITO、IZO、ZnOなどの透明導電性材料が好ましい。また、第2の電極7015上に遮蔽膜7016、例えば光を遮光する金属、光を反射する金属等を用いる。本実施の形態では、第2の電極7015としてITO膜を用い、遮蔽膜7016としてTi膜を用いる。

【0289】

第1の電極7013及び第2の電極7015で、発光層を含むEL層7014を挟んでいる領域が発光素子7012に相当する。図14(A)に示した素子構造の場合、発光素子7012から発せられる光は、矢印で示すように第1の電極7013側に射出する。

【0290】

なお、図14(A)において、発光素子7012から発せられる光は、カラーフィルタ層7033を通過し、絶縁層7032b、酸化物絶縁層7032a、ゲート絶縁層7031、及び基板7030を通過して射出させる。

【0291】

カラーフィルタ層7033はインクジェット法などの液滴吐出法や、印刷法、フォトリソグラフィ技術を用いたエッチング方法などでそれぞれ形成する。

【0292】

また、カラーフィルタ層7033はオーバーコート層7034で覆われ、さらに保護絶縁層7035によって覆う。なお、図14(A)ではオーバーコート層7034は薄い膜厚で図示したが、オーバーコート層7034は、アクリル樹脂などの樹脂材料を用い、カラーフィルタ層7033に起因する凹凸を平坦化する機能を有している。

【0293】

また、保護絶縁層7035及び絶縁層7032に形成され、且つ、ドレイン電極層に達するコンタクトホールは、隔壁7019と重なる位置に配置する。

【0294】

次に、両面射出構造の発光素子について、図14(B)を用いて説明する。

【0295】

図14(B)では、基板7040上に設けられた駆動用TFT7021のドレイン電極層と電気的に接続された可視光に対する透光性を有する導電膜7027上に、発光素子7022の第1の電極7023が形成されており、第1の電極7023上にEL層7024、第2の電極7025が順に積層されている。

【0296】

可視光に対する透光性を有する導電膜7027としては、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの可視光に対する透光性を有する導電性導電膜を用いることができる。

【0297】

また、第1の電極7023は様々な材料を用いることができる。例えば、第1の電極7023を陰極として用いる場合、仕事関数が小さい材料、具体的には、例えば、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、及びこれらを含む合金(Mg:Ag、Al:Liなど)の他、YbやEr等の希土類金属等が好ましい。本実施の形態では、第1の電極7023を陰極として用い、その膜厚は、可視光を透過する程度(好ましくは、5nm〜30nm程度)とする。例えば20nmの膜厚を有するアルミニウム膜を、第1の電極7023として用いる。

【0298】

なお、可視光に対する透光性を有する導電膜とアルミニウム膜を積層成膜した後、選択的にエッチングして可視光に対する透光性を有する導電膜7027と第1の電極7023を形成してもよく、この場合、同じマスクを用いてエッチングすることができ、好ましい。

【0299】

また、第1の電極7023の周縁部は、隔壁7029で覆う。隔壁7029は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁7029は、特に感光性の樹脂材料を用い、第1の電極7023上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。隔壁7029として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

【0300】

また、第1の電極7023及び隔壁7029上に形成するEL層7024は、発光層を含めば良く、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。EL層7024が複数の層で構成されている場合、陰極として機能する第1の電極7023上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。

【0301】

また、上記積層順に限定されず、第1の電極7023を陽極として用い、陽極上にホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層してもよい。ただし、消費電力を比較する場合、第1の電極7023を陰極として用い、陰極上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層するほうが消費電力が少ないため好ましい。

【0302】

また、EL層7024上に形成する第2の電極7025としては、様々な材料を用いることができる。例えば、第2の電極7025を陽極として用いる場合、仕事関数が大きい材料、例えば、ITO、IZO、ZnOなどの透明導電性材料を好ましく用いることができる。本実施の形態では、第2の電極7025を陽極として用い、酸化珪素を含むITO膜を形成する。

【0303】

第1の電極7023及び第2の電極7025で、発光層を含むEL層7024を挟んでいる領域が発光素子7022に相当する。図14(B)に示した素子構造の場合、発光素子7022から発せられる光は、矢印で示すように第2の電極7025側と第1の電極7023側の両方に射出する。

【0304】

なお、図14(B)において、発光素子7022から第1の電極7023側に発せられる一方の光は、カラーフィルタ層7043を通過し、絶縁層7042b、酸化物絶縁層7042a、ゲート絶縁層7041、及び基板7040を通過して射出させる。

【0305】

カラーフィルタ層7043はインクジェット法などの液滴吐出法や、印刷法、フォトリソグラフィ技術を用いたエッチング方法などでそれぞれ形成する。

【0306】

また、カラーフィルタ層7043はオーバーコート層7044で覆われ、さらに保護絶縁層7045によって覆う。

【0307】

また、保護絶縁層7045及び絶縁層7042に形成され、且つ、ドレイン電極層に達するコンタクトホールは、隔壁7029と重なる位置に配置する。

【0308】

ただし、両面射出構造の発光素子を用い、どちらの表示面もフルカラー表示とする場合、第2の電極7025側からの光はカラーフィルタ層7043を通過しないため、別途カラーフィルタ層を備えた封止基板を第2の電極7025上方に設けることが好ましい。

【0309】

次に、上面射出構造の発光素子について、図14(C)を用いて説明する。

【0310】

図14(C)に、駆動用TFT7001がn型で、発光素子7002から発せられる光が第2の電極7005側に抜ける場合の、画素の断面図を示す。図14(C)では、駆動用TFT7001のドレイン電極層と電気的に接続された発光素子7002の第1の電極7003が形成されており、第1の電極7003上にEL層7004、第2の電極7005が順に積層されている。

【0311】

また、第1の電極7003は様々な材料を用いることができる。例えば、第1の電極7003を陰極として用いる場合、仕事関数が小さい材料、具体的には、例えば、LiやCs等のアルカリ金属、及びMg、Ca、Sr等のアルカリ土類金属、及びこれらを含む合金(Mg:Ag、Al:Liなど)の他、YbやEr等の希土類金属等が好ましい。

【0312】

また、第1の電極7003の周縁部は、隔壁7009で覆う。隔壁7009は、ポリイミド、アクリル、ポリアミド、エポキシ等の有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。隔壁7009は、特に感光性の樹脂材料を用い、第1の電極7003上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。隔壁7009として感光性の樹脂材料を用いる場合、レジストマスクを形成する工程を省略することができる。

【0313】

また、第1の電極7003及び隔壁7009上に形成するEL層7004は、少なくとも発光層を含めば良く、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。EL層7004が複数の層で構成されている場合、陰極として用いる第1の電極7003上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。

【0314】

また、上記積層順に限定されず、陽極として用いる第1の電極7003上にホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層してもよい。

【0315】

図14(C)ではTi膜、アルミニウム膜、Ti膜の順に積層した積層膜上に、ホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層し、その上にMg:Ag合金薄膜とITOとの積層を形成する。

【0316】

ただし、駆動用TFT7001がn型の場合、第1の電極7003上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層するほうが、駆動回路における電圧上昇を抑制することができ、消費電力を少なくできるため好ましい。

【0317】

第2の電極7005は可視光に対する透光性を有する導電性材料を用いて形成し、例えば酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの可視光に対する透光性を有する導電性導電膜を用いても良い。

【0318】

第1の電極7003及び第2の電極7005で発光層を含むEL層7004を挟んでいる領域が発光素子7002に相当する。図14(C)に示した画素の場合、発光素子7002から発せられる光は、矢印で示すように第2の電極7005側に射出する。

【0319】

また、図14(C)において、駆動用TFT7001のドレイン電極層は、酸化物絶縁層7052a、保護絶縁層7052b及び平坦化絶縁層7053に設けられたコンタクトホールを介して第1の電極7003と電気的に接続する。平坦化絶縁層7053は、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の樹脂材料を用いることができる。また上記樹脂材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁層7053を形成してもよい。平坦化絶縁層7053の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いることができる。

【0320】

また、第1の電極7003と、隣り合う画素の第1の電極7008とを絶縁するために隔壁7009を設ける。

【0321】

また、図14(C)の構造においては、フルカラー表示を行う場合、例えば発光素子7002として緑色発光素子とし、隣り合う一方の発光素子を赤色発光素子とし、もう一方の発光素子を青色発光素子とする。また、3種類の発光素子だけでなく白色素子を加えた4種類の発光素子でフルカラー表示ができる発光表示装置を作製してもよい。

【0322】

また、図14(C)の構造においては、配置する複数の発光素子を全て白色発光素子として、発光素子7002上方にカラーフィルタなどを有する封止基板を配置する構成とし、フルカラー表示ができる発光表示装置を作製してもよい。白色などの単色の発光を示す材料を形成し、カラーフィルタや色変換層を組み合わせることによりフルカラー表示を行うことができる。

【0323】

もちろん単色発光の表示を行ってもよい。例えば、白色発光を用いて照明装置を形成してもよいし、単色発光を用いてエリアカラータイプの発光装置を形成してもよい。

【0324】

また、必要があれば、円偏光板などの偏光フィルムなどの光学フィルムを設けてもよい。

【0325】

なお、ここでは、発光素子として有機EL素子について述べたが、発光素子として無機EL素子を設けることも可能である。

【0326】

なお、発光素子の駆動を制御する薄膜トランジスタ(駆動用TFT)と発光素子が電気的に接続されている例を示したが、駆動用TFTと発光素子との間に電流制御用TFTが接続されている構成であってもよい。

【0327】

なお本実施の形態で示す半導体装置は、図14に示した構成に限定されるものではなく、本発明の技術的思想に基づく各種の変形が可能である。

【0328】

次に、実施の形態3に示す薄膜トランジスタを適用した半導体装置の一形態に相当する発光表示パネル(発光パネルともいう)の外観及び断面について、図15を用いて説明する。図15(A)は、第1の基板上に形成された薄膜トランジスタ及び発光素子を、第2の基板との間にシール材によって封止した、パネルの上面図であり、図15(B)は、図15(A)のH−Iにおける断面図に相当する。

【0329】

第1の基板4501上に設けられた画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bを囲むようにして、シール材4505が設けられている。また画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bの上に第2の基板4506が設けられている。よって画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bは、第1の基板4501とシール材4505と第2の基板4506とによって、充填材4507と共に密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

【0330】

また第1の基板4501上に設けられた画素部4502、信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bは、薄膜トランジスタを複数有しており、図15(B)では、画素部4502に含まれる薄膜トランジスタ4510と、信号線駆動回路4503aに含まれる薄膜トランジスタ4509とを例示している。

【0331】

薄膜トランジスタ4509、4510は、In−Ga−Zn−O系膜を酸化物半導体層として含む信頼性の高い実施の形態3に示す薄膜トランジスタを適用することができる。本実施の形態において、薄膜トランジスタ4509、4510はnチャネル型薄膜トランジスタである。

【0332】

絶縁層4544上において駆動回路用の薄膜トランジスタ4509の酸化物半導体層のチャネル形成領域と重なる位置に導電層4540が設けられている。導電層4540を酸化物半導体層のチャネル形成領域と重なる位置に設けることによって、BT試験前後における薄膜トランジスタ4509のしきい値電圧の変化量を低減することができる。また、導電層4540は、電位が薄膜トランジスタ4509のゲート電極層と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層4540の電位がGND、0V、或いはフローティング状態であってもよい。

【0333】

また4511は発光素子に相当し、発光素子4511が有する画素電極である第1の電極層4517は、薄膜トランジスタ4510のソース電極層またはドレイン電極層と電気的に接続されている。なお発光素子4511の構成は、第1の電極層4517、電界発光層4512、第2の電極層4513の積層構造であるが、本実施の形態に示した構成に限定されない。発光素子4511から取り出す光の方向などに合わせて、発光素子4511の構成は適宜変えることができる。

【0334】

隔壁4520は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、第1の電極層4517上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0335】

電界発光層4512は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0336】

発光素子4511に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4513及び隔壁4520上に保護膜を形成してもよい。保護膜としては、窒化シリコン膜、窒化酸化シリコン膜、DLC膜等を形成することができる。

【0337】

また、信号線駆動回路4503a、4503b、走査線駆動回路4504a、4504b、または画素部4502に与えられる各種信号及び電位は、FPC4518a、4518bから供給されている。

【0338】

本実施の形態では、接続端子電極4515が、発光素子4511が有する第1の電極層4517と同じ導電膜から形成され、端子電極4516は、薄膜トランジスタ4509、4510が有するソース電極層及びドレイン電極層と同じ導電膜から形成されている。

【0339】

接続端子電極4515は、FPC4518aが有する端子と、異方性導電膜4519を介して電気的に接続されている。

【0340】

発光素子4511からの光の取り出し方向に位置する第2の基板は可視光に対し透光性を有していなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような可視光に対する透光性を有する材料を用いる。

【0341】

また、充填材4507としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施の形態は充填材として窒素を用いた。

【0342】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(λ/4板、λ/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【0343】

信号線駆動回路4503a、4503b、及び走査線駆動回路4504a、4504bは、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜によって形成された駆動回路で実装されていてもよい。また、信号線駆動回路のみ、或いは一部、又は走査線駆動回路のみ、或いは一部のみを別途形成して実装しても良く、本実施の形態は図15の構成に限定されない。

【0344】

以上の工程により、半導体装置として信頼性の高い発光表示装置(表示パネル)を作製することができる。

【0345】

なお、本実施の形態に示す構成は、他の実施の形態に示した構成を適宜組み合わせて用いることができることとする。

【0346】

(実施の形態8)

実施の形態3に示す薄膜トランジスタを適用した半導体装置は、電子ペーパーとして適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図16、図17に示す。

【0347】

図16(A)は、電子ペーパーで作られたポスター2631を示している。広告媒体が紙の印刷物である場合には、広告の交換は人手によって行われるが、電子ペーパーを用いれば短時間で広告の表示を変えることができる。また、表示も崩れることなく安定した画像が得られる。なお、ポスターは無線で情報を送受信できる構成としてもよい。

【0348】

また、図16(B)は、電車などの乗り物の車内広告2632を示している。広告媒体が紙の印刷物である場合には、広告の交換は人手によって行われるが、電子ペーパーを用いれば人手を多くかけることなく短時間で広告の表示を変えることができる。また表示も崩れることなく安定した画像が得られる。なお、車内広告は無線で情報を送受信できる構成としてもよい。

【0349】

また、図17は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701及び筐体2703の2つの筐体で構成されている。筐体2701及び筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

【0350】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705及び表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部(図17では表示部2705)に文章を表示し、左側の表示部(図17では表示部2707)に画像を表示することができる。

【0351】

また、図17では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

【0352】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0353】

なお、本実施の形態に示す構成は、他の実施の形態に示した構成を適宜組み合わせて用いることができることとする。

【0354】

(実施の形態9)

実施の形態3に示す薄膜トランジスタを用いた半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラなどのカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

【0355】

図18(A)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。

【0356】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機9610により行うことができる。リモコン操作機9610が備える操作キー9609により、チャンネルや音量の操作を行うことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機9610に、当該リモコン操作機9610から出力する情報を表示する表示部9607を設ける構成としてもよい。

【0357】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

【0358】

図18(B)は、デジタルフォトフレームの一例を示している。例えば、デジタルフォトフレーム9700は、筐体9701に表示部9703が組み込まれている。表示部9703は、各種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

【0359】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子(USB端子、USBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

【0360】

また、デジタルフォトフレーム9700は、無線で情報を送受信できる構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

【0361】

図19(A)は携帯型遊技機であり、筐体9881と筐体9891の2つの筐体で構成されており、連結部9893により、開閉可能に連結されている。筐体9881には表示部9882が組み込まれ、筐体9891には表示部9883が組み込まれている。また、図19(A)に示す携帯型遊技機は、その他、スピーカ部9884、記録媒体挿入部9886、LEDランプ9890、入力手段(操作キー9885、接続端子9887、センサ9888(力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの)、マイクロフォン9889)等を備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、少なくとも本発明に係る半導体装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。図19(A)に示す携帯型遊技機は、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図19(A)に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

【0362】

図19(B)は大型遊技機であるスロットマシンの一例を示している。スロットマシン9900は、筐体9901に表示部9903が組み込まれている。また、スロットマシン9900は、その他、スタートレバーやストップスイッチなどの操作手段、コイン投入口、スピーカなどを備えている。もちろん、スロットマシン9900の構成は上述のものに限定されず、少なくとも本発明に係る半導体装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。

【0363】

図20(A)は、携帯電話機の一例を示している。携帯電話機1000は、筐体1001に組み込まれた表示部1002の他、操作ボタン1003、外部接続ポート1004、スピーカ1005、マイク1006などを備えている。

【0364】

図20(A)に示す携帯電話機1000は、表示部1002を指などで触れることで、情報を入力することができる。また、電話を掛ける、或いはメールを作成するなどの操作は、表示部1002を指などで触れることにより行うことができる。

【0365】

表示部1002の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

【0366】

例えば、電話を掛ける、或いはメールを作成する場合は、表示部1002を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部1002の画面のほとんどにキーボードまたは番号ボタンを表示させることが好ましい。

【0367】

また、携帯電話機1000内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機1000の向き(縦か横か)を判断して、表示部1002の画面表示を自動的に切り替えるようにすることができる。

【0368】

また、画面モードの切り替えは、表示部1002を触れること、又は筐体1001の操作ボタン1003の操作により行われる。また、表示部1002に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

【0369】

また、入力モードにおいて、表示部1002の光センサで検出される信号を検知し、表示部1002のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

【0370】

表示部1002は、イメージセンサとして機能させることもできる。例えば、表示部1002に掌や指で触れ、掌紋、指紋等を撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

【0371】

図20(B)も携帯電話機の一例である。図20(B)の携帯電話機は、筐体9411に、表示部9412、及び操作ボタン9413を含む表示装置9410と、筐体9401に操作ボタン9402、外部入力端子9403、マイク9404、スピーカ9405、及び着信時に発光する発光部9406を含む通信装置9400とを有しており、表示機能を有する表示装置9410は電話機能を有する通信装置9400と矢印の2方向に脱着可能である。よって、表示装置9410と通信装置9400の短軸同士を取り付けることも、表示装置9410と通信装置9400の長軸同士を取り付けることもできる。また、表示機能のみを必要とする場合、通信装置9400より表示装置9410を取り外し、表示装置9410を単独で用いることもできる。通信装置9400と表示装置9410とは無線通信又は有線通信により画像又は入力情報を授受することができ、それぞれ充電可能なバッテリーを有する。

【0372】

なお、本実施の形態に示す構成は、他の実施の形態に示した構成を適宜組み合わせて用いることができることとする。

【符号の説明】

【0373】

10 パルス出力回路

11 配線

12 配線

13 配線

14 配線

15 配線

16 配線

17 配線

21 入力端子

22 入力端子

23 入力端子

24 入力端子

25 入力端子

26 出力端子

27 出力端子

31 トランジスタ

32 トランジスタ

33 トランジスタ

34 トランジスタ

35 トランジスタ

36 トランジスタ

37 トランジスタ

38 トランジスタ

39 トランジスタ

40 トランジスタ

41 トランジスタ

51 電源線

52 電源線

53 電源線

61 期間

62 期間

100 基板

102 ゲート絶縁層

102a ゲート絶縁層

102b ゲート絶縁層

103 酸化物半導体層

107 酸化物絶縁膜

108 保護絶縁層

111a ゲート電極

111b ゲート配線層

113 酸化物半導体層

115c 配線層

123 酸化物半導体層

128 コンタクトホール

151 薄膜トランジスタ

300 焼結体

320 バッキングプレート

320a バッキングプレート

320b バッキングプレート

320c バッキングプレート

320d バッキングプレート

321 取り付け部

325a 勘合用ピン

325b 勘合用レール

325c 勘合用レール

325d 勘合用レール

330 気密部材

335 圧力調整弁

340 包装体

340a 包装体

340b 包装体

340c 包装体

340d 包装体

345a 部

345b 摺動部材

345c 摺動部材

345d 摺動部材

400 成膜室

400a 成膜室

400b 成膜室

401 グローブ

405 開封機構

580 基板

581 薄膜トランジスタ

583 絶縁層

585 絶縁層

587 電極層

588 電極層

589 球形粒子

590a 黒色領域

590b 白色領域

594 キャビティ

595 充填材

596 基板

1000 携帯電話機

1001 筐体

1002 表示部

1003 操作ボタン

1004 外部接続ポート

1005 スピーカ

1006 マイク

2600 TFT基板

2601 対向基板

2602 シール材

2603 画素部

2604 表示素子

2605 着色層

2606 偏光板

2607 偏光板

2608 配線回路部

2609 フレキシブル配線基板

2610 冷陰極管

2611 反射板

2612 回路基板

2613 拡散板

2631 ポスター

2632 車内広告

2700 電子書籍

2701 筐体

2703 筐体

2705 表示部

2707 表示部

2711 軸部

2721 電源

2723 操作キー

2725 スピーカ

4001 基板

4002 画素部

4003 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4008 液晶層

4010 薄膜トランジスタ

4011 薄膜トランジスタ

4013 液晶素子

4015 接続端子電極

4016 端子電極

4018 FPC

4019 異方性導電膜

4020 絶縁層

4021 絶縁層

4030 画素電極層

4031 対向電極層

4032 絶縁層

4501 基板

4502 画素部

4503a 信号線駆動回路

4504a 走査線駆動回路

4505 シール材

4506 基板

4507 充填材

4509 薄膜トランジスタ

4510 薄膜トランジスタ

4511 発光素子

4512 電界発光層

4513 電極層

4515 接続端子電極

4516 端子電極

4517 電極層

4518a FPC

4519 異方性導電膜

4520 隔壁

4540 導電層

4544 絶縁層

5300 基板

5301 画素部

5302 走査線駆動回路

5303 走査線駆動回路

5304 信号線駆動回路

5305 タイミング制御回路

5601 シフトレジスタ

5602 スイッチング回路

5603 薄膜トランジスタ

5604 配線

5605 配線

6400 画素

6401 スイッチング用トランジスタ

6402 駆動用トランジスタ

6403 容量素子

6404 発光素子

6405 信号線

6406 走査線

6407 電源線

6408 共通電極

7001 駆動用TFT

7002 発光素子

7003 電極

7004 EL層

7005 電極

7008 電極

7009 隔壁

7011 駆動用TFT

7012 発光素子

7013 電極

7014 EL層

7015 電極

7016 遮蔽膜

7017 導電膜

7019 隔壁

7021 駆動用TFT

7022 発光素子

7023 電極

7024 EL層

7025 電極

7027 導電膜

7029 隔壁

7030 基板

7031 ゲート絶縁層

7032 絶縁層

7032a 酸化物絶縁層

7032b 絶縁層

7033 カラーフィルタ層

7034 オーバーコート層

7035 保護絶縁層

7040 基板

7041 ゲート絶縁層

7042 絶縁層

7042a 酸化物絶縁層

7042b 絶縁層

7043 カラーフィルタ層

7044 オーバーコート層

7045 保護絶縁層

7052a 酸化物絶縁層

7052b 保護絶縁層

7053 平坦化絶縁層

9400 通信装置

9401 筐体

9402 操作ボタン

9403 外部入力端子

9404 マイク

9405 スピーカ

9406 発光部

9410 表示装置

9411 筐体

9412 表示部

9413 操作ボタン

9600 テレビジョン装置

9601 筐体

9603 表示部

9605 スタンド

9607 表示部

9609 操作キー

9610 リモコン操作機

9700 デジタルフォトフレーム

9701 筐体

9703 表示部

9881 筐体

9882 表示部

9883 表示部

9884 スピーカ部

9885 操作キー

9886 記録媒体挿入部

9887 接続端子

9888 センサ

9889 マイクロフォン

9890 LEDランプ

9891 筐体

9893 連結部

9900 スロットマシン

9901 筐体

9903 表示部

【技術分野】

【0001】

ターゲット材料の包装方法、及び装置へのターゲットの取り付け方法に関する。具体的には、成膜材料を含むスパッタリング用ターゲット材料の包装方法、及び成膜装置へのターゲットの取り付け方法に関する。

【背景技術】

【0002】

ターゲットを用いた物理的蒸着法は幅広い材料の薄膜を成形できる特徴を有する。ターゲットを用いた物理的蒸着法としては、スパッタリング法やパルスレーザー蒸着法が挙げられる。特に、スパッタリング法は大面積基板への成膜が容易である上、例えば、融点が高く蒸気圧が低い材料であっても成膜が可能であるという利点を備える。また、反応性ガスを成膜室に導入することにより、金属酸化物や金属窒化物等を基板上に成膜することが可能である。また、基板へのダメージが比較的小さいことなどの特長があり、薄膜形成技術における重要な技術の一つである。

【0003】

スパッタリング法はターゲット材料(スパッタリングに用いる)を原材料とするため、成膜された薄膜の特性はターゲット材料に付着したゴミや不純物の影響を受ける。そのため、ターゲット材料の汚染を防ぐための種々の技術が開示されており、例えばターゲット材料の表面を保護する包装技術が特許文献1に開示されている。

【0004】

また、ガラス基板などの基板に酸化物半導体膜を形成し、それを用いて作製したトランジスタを電子デバイスや光デバイスに応用する技術が注目されている。例えば、半導体材料として酸化亜鉛、In−Ga−Zn−O系酸化物半導体を用いてトランジスタを作製し、画像表示装置のスイッチング素子などに用いる技術が特許文献2及び特許文献3で開示されている。

【0005】

酸化物半導体膜はスパッタリング法などによって比較的低温で膜形成が可能であり、薄膜トランジスタ(TFT:Thin Film Transistorともいう)に好適である。酸化物半導体膜を用いたTFTは多結晶シリコン膜を用いたTFTよりも製造工程が簡単である。また、酸化物半導体にチャネル形成領域(チャネル領域ともいう)を設けたTFTは、アモルファスシリコンを用いたTFTよりも高い電界効果移動度が得られている。

【0006】

酸化物半導体を用いたトランジスタは、ガラス基板だけでなく、プラスチック基板上にも形成できるため、液晶ディスプレイ、エレクトロルミネセンスディスプレイ(ELディスプレイともいう)または電子ペーパーなどの表示装置への応用が期待されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4−231461号公報

【特許文献2】特開2007−123861号公報

【特許文献3】特開2007−96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、酸化物半導体膜を用いて作製した半導体素子の特性は未だ充分なものとは言えない。例えば、酸化物半導体膜を用いたトランジスタには、制御された閾値電圧、速い動作速度、製造工程が比較的簡単であること、そして十分な信頼性が求められている。

【0009】

特に、酸化物半導体膜を用いたトランジスタの閾値電圧は、酸化物半導体膜に含まれるキャリア濃度に影響される。また、酸化物半導体膜に含まれるキャリアは、酸化物半導体膜に含まれる不純物により発生する。例えば、成膜された酸化物半導体膜に含まれるH2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物は、酸化物半導体膜のキャリア濃度を高める効果を有する。

【0010】

従って、酸化物半導体膜を用いて、閾値電圧が制御されたトランジスタを提供するには、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物を可能な限り減らす必要がある。

【0011】

しかし、酸化物半導体膜の成膜用ターゲット材料は、金属酸化物等に代表される極性が強い物質を含むため、大気中の不純物(例えば、水分等)を吸着または吸収し易い。そして、不純物を吸着または吸収したターゲット材料を用いて成膜した酸化物半導体膜は、不純物に汚染されてしまうという問題が生じる。

【0012】

また、金属膜の成膜用に金属を含むターゲット材料も同様であり、大気中の不純物(例えば、水分等)を吸着または吸収し易い。不純物を吸着または吸収した金属を含むターゲット材料を用いて成膜した金属膜は、不純物に汚染されてしまう。

【0013】

なお、大気中の不純物に汚染された金属膜を酸化物半導体膜に接して成膜すると、水分等の水素原子を含む不純物等が金属膜から酸化物半導体膜へ拡散してしまうという問題が生じる。本発明は、このような技術的背景のもとでなされたものである。

【0014】

本発明の一態様の目的は、大気に由来する不純物(例えば水素原子を含む化合物等)による汚染が少ない薄膜を成膜することができるターゲット材料の、包装方法を提供することを課題の一とする。また、該不純物による汚染が少ない薄膜を成膜することができるターゲットの取り付け方法を提供することを課題の一とする。

【課題を解決するための手段】

【0015】

上記目的を達成するために、ターゲット材料(例えば焼結体)の製造後、当該ターゲット材料を取り付けた成膜装置の成膜室を排気するまでの間、ターゲット材料を大気にさらすことなく密封状態を保てばよい。

【0016】

すなわち、本発明の一態様は、被装着部への取り付け部を有するバッキングプレートと、バッキングプレートに固定された焼結体と、取り付け部を覆うことなく焼結体を内包するようにバッキングプレートに装着される包装体とを有する。また、包装体の内側は乾燥気体が充填されていることを特徴とする包装されたスパッタリング用ターゲットである。

【0017】

また、本発明の一態様は、包装体の内側が露点−40℃以下の気体で満たされた、上記の包装されたスパッタリング用ターゲットである。

【0018】

また、本発明の一態様は、焼結体が金属酸化物を含む、上記の包装されたスパッタリング用ターゲットである。

【0019】

また、本発明の一態様は、金属酸化物がインジウムと、ガリウムと、亜鉛を含む、上記の包装されたスパッタリング用ターゲットである。

【0020】

また、本発明の一態様は、焼結体が金属を含む上記の包装されたスパッタリング用ターゲットである。

【0021】

また、本発明の一態様は、金属がAl、Cu、Cr、Ta、Ti、Mo、またはWの少なくとも一つを含む、上記の包装されたスパッタリング用ターゲットである。

【0022】

また、本発明の一態様は、露点−40℃以下の乾燥した雰囲気下で、被装着部への取り付け部を有するバッキングプレートに焼結体を固定し、取り付け部を覆うことなく焼結体を内包するように前記バッキングプレートに包装体を装着することを特徴とするスパッタリング用ターゲットの包装方法である。

【0023】

また、本発明の一態様は、露点−40℃以下の乾燥した雰囲気下で、被装着部への取り付け部を覆うことなく、ターゲット材料を包装体に収納し、包装体に収納されたターゲット材料を、バッキングプレートを介して成膜装置の成膜室の装着部に取り付け、成膜室を排気し、排気された成膜室内で包装体を開封する包装されたスパッタリング用ターゲットの取り付け方法である。

【0024】

なお、本明細書において、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0025】

また、本明細書において、酸化窒化物とは、その組成として、窒素原子よりも酸素原子の数が多い物質のことを指し、窒化酸化物とは、その組成として、酸素原子より窒素原子の数が多い物質のことを指す。例えば、酸化窒化シリコン膜とは、その組成として、窒素原子よりも酸素原子の数が多く、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素が50%以上70原子%以下、窒素が0.5%以上15原子%以下、シリコンが25%以上35原子%以下、水素が0.1%以上10原子%以下の範囲で含まれるものをいう。また、窒化酸化シリコン膜とは、その組成として、酸素原子より窒素原子の数が多く、RBS及びHFSを用いて測定した場合に、濃度範囲として酸素が5%以上30原子%以下、窒素が20%以上55原子%以下、シリコンが25%以上35原子%以下、水素が10%以上30原子%以下の範囲で含まれるものをいう。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0026】

なお、本明細書において、EL層とは発光素子の一対の電極間に設けられた層を示すものとする。従って、電極間に挟まれた発光物質である有機化合物を含む発光層はEL層の一態様である。

【0027】

なお、本明細書中において、発光装置とは画像表示デバイス、発光デバイス、もしくは光源(照明装置含む)を指す。また、発光装置にコネクター、例えばFPC(Flexible printed circuit)もしくはTAB(Tape Automated Bonding)テープもしくはTCP(Tape Carrier Package)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または発光素子が形成された基板にCOG(Chip On Glass)方式によりIC(集積回路)が直接実装されたモジュールも全て発光装置に含むものとする。

【発明の効果】

【0028】

本発明によれば、例えば水素原子を含む化合物等、大気に含まれる不純物による汚染が少ない薄膜を成膜するターゲット材料の包装方法を提供できる。また、該不純物による汚染が少ない薄膜を成膜するターゲットの取り付け方法を提供できる。

【図面の簡単な説明】

【0029】

【図1】実施の形態に係わるターゲットの製造から開封工程を説明する図。

【図2】実施の形態に係わるターゲットの取り付け工程を説明する図。

【図3】実施の形態に係わるターゲット材料の密封方法を説明する図。

【図4】実施の形態に係わる半導体装置を説明する図。

【図5】実施の形態に係わる半導体装置の作製方法を説明する図。

【図6】実施の形態に係わる表示装置のブロック図。

【図7】実施の形態に係わる信号線駆動回路の構成を説明する図。

【図8】シフトレジスタの構成を示す回路図。

【図9】シフトレジスタの動作を説明する回路およびタイミングチャート。

【図10】実施の形態に係わる半導体装置を説明する図。

【図11】実施の形態に係わる半導体装置を説明する図。

【図12】実施の形態に係わる半導体装置を説明する図。