ダイバーシティ組合せデータ検出のシステムおよび方法

【課題】データ処理に関するシステムおよび方法を提供すること。

【解決手段】たとえば、本発明のいくつかの実施形態は、それぞれが同一の一連のデータ・サンプルを受け取り、第1検出データ出力および第2検出データ出力を供給するように動作可能な少なくとも2つのデータ検出器回路を有するパターン検出回路を含むデータ処理回路を提供する。さらに、パターン検出回路は、少なくとも部分的に第1検出データ出力および第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路を含む。

【解決手段】たとえば、本発明のいくつかの実施形態は、それぞれが同一の一連のデータ・サンプルを受け取り、第1検出データ出力および第2検出データ出力を供給するように動作可能な少なくとも2つのデータ検出器回路を有するパターン検出回路を含むデータ処理回路を提供する。さらに、パターン検出回路は、少なくとも部分的に第1検出データ出力および第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ処理のシステムおよび方法に関し、より具体的には、データ処理システムでのパターン検出に関する。

【背景技術】

【0002】

通常のストレージ・デバイスは、記憶媒体上で磁気的に表される情報を格納する磁気記憶媒体を含む。ヘッドが、記憶媒体に対して配置され、このヘッドは、磁気的に表される情報を感知し、磁気的に表される情報に対応する電気信号を供給する。この電気信号は、最終的にデータ検出回路に渡され、このデータ検出回路は、記憶媒体に最初に書き込まれた情報を回復するために、1つまたは複数のデータ検出プロセスを実行する。記憶媒体上で維持される情報は、通常、ユーザ・データと同期データとの両方を含む。ユーザ・データは、ランダム・パターンと考えることができ、一方同期データは、一般に、たとえば記憶媒体上の位置を識別するのに使用できる、定義されたパターンである。

【0003】

さまざまな既存のデータ処理システムは、たとえば、しきい値検出器回路を利用して、受け取られた同期データを処理し、位置データを識別する。そのような回路は、受け取られるディジタル・サンプルが、雑音を考慮に入れるために正しく前処理される場合には良く動作する。しかし、いくつかの場合に、そのような前処理が最適未満である場合がある。これは、位置を確立することができないことをもたらし、これによって性能を劣化させる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国仮出願第12/851,475号

【非特許文献】

【0005】

【非特許文献1】J.HagenauerおよびP.Hoeher、「A Viterbi algorithm with soft−decision outputs and its applications」、Proc.IEEE GLOBECOM、47.11〜47.17頁、米国テキサス州ダラス、1989年11月

【発明の概要】

【発明が解決しようとする課題】

【0006】

したがって、少なくとも前述の理由から、データ処理に関する高度なシステムおよび方法の必要性が、当技術分野には存在する。

【課題を解決するための手段】

【0007】

本発明は、データ処理のシステムおよび方法に関し、より具体的には、データ処理システムでのパターン検出に関する。

【0008】

本発明のさまざまな実施形態は、パターン検出回路を含むデータ処理回路を提供する。パターン検出回路は、それぞれが同一の一連のデータ・サンプルを受け取り、第1検出データ出力および第2検出データ出力を供給するように動作可能な少なくとも2つのデータ検出器回路を含む。さらに、パターン検出回路は、少なくとも部分的に第1検出データ出力および第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路を含む。

【0009】

前述の実施形態のいくつかの実例では、結果組合せ回路は、第1比較器回路、第2比較器回路、およびコンバイナ回路をさらに含む。第1比較器回路は、第1検出データ出力をパターンと比較し、第1検出データ出力とパターンとの間の一致が発生する時に第1予備パターン発見表示をアサートするように動作可能である。第2比較器回路は、第2検出データ出力をパターンと比較し、第2検出データ出力とパターンとの間の一致が発生する時に第2予備パターン発見表示をアサートするように動作可能である。コンバイナ回路は、少なくとも部分的に第1予備パターン発見表示および第2予備パターン発見表示に基づいてパターン発見出力をアサートするように動作可能である。特定の事例では、コンバイナ回路は、第1予備パターン発見表示と第2予備パターン発見表示との両方がパターン発見を示す時にパターン発見出力をアサートするように動作可能である。他の事例では、コンバイナ回路は、第1予備パターン発見表示および第2予備パターン発見表示のうちの1つがパターン発見を示す時にパターン発見出力をアサートするように動作可能である。

【0010】

前述の実施形態のさまざまな実例では、第1データ検出器回路は、第2データ検出器回路によって適用される第2データ検出アルゴリズムとは異なる第1データ検出アルゴリズムを適用する。いくつかのそのような事例では、第1データ検出器回路および第2データ検出器回路は、しきい値検出器回路、2状態検出器回路、またはビタビ・アルゴリズム検出器回路とすることができるが、これらに限定はされない。いくつかの事例では、第1データ検出器回路は、第2データ検出器回路と一致して並列に一連のデータ・サンプルの同一のサブセットに作用する。

【0011】

前述の実施形態のいくつかの実例では、パターン検出回路は、第3データ検出器回路をさらに含む。第3データ検出器回路は、一連のデータ・サンプルを受け取り、第3検出データ出力を供給するように動作可能である。そのような実例では、結果組合せ回路は、少なくとも部分的に第1検出データ出力、第2検出データ出力、および第3検出データ出力に基づいてパターン発見出力をアサートするように動作可能である。いくつかのそのような実例では、第1データ検出器回路は、ビタビ・アルゴリズム検出器回路であり、第2データ検出器回路は、しきい値検出器回路であり、第3データ検出器回路は、2状態検出器回路である。

【0012】

本発明の他の実施形態は、一連のデータ・サンプルを受け取ることと、第1検出出力を作るために一連のデータ・サンプルに対して第1データ検出を実行することと、第2検出出力を作るために一連のデータ・サンプルに対して第2データ検出を実行することと、少なくとも部分的に第1検出出力および第2検出出力に基づいてパターン発見信号をアサートすることとを含む、パターン検出の方法を提供する。第2データ検出は、第1データ検出とは異なる。いくつかの事例では、第1データ検出および第2データ検出は、並列に実行される。

【0013】

前述の実施形態のいくつかの実例では、第1データ検出は、しきい値データ検出、2状態データ検出、またはビタビ・アルゴリズム・データ検出であり、第2データ検出は、しきい値データ検出、2状態データ検出、またはビタビ・アルゴリズム・データ検出である。前述の実施形態のいくつかの実例では、この方法は、第3検出出力を作るために一連のデータ・サンプルに対して第3データ検出を実行することをさらに含む。そのような事例では、第3データ検出は、第1データ検出および第2データ検出とは異なり、この方法は、少なくとも部分的に第1検出出力、第2検出出力、および第3検出出力に基づいてパターン発見信号をアサートすることをさらに含む。いくつかのそのような事例では、第1データ検出は、ビタビ・アルゴリズム・データ検出であり、第2データ検出は、しきい値データ検出であり、第3データ検出は、2状態データ検出である。1つまたは複数の事例では、第1データ検出、第2データ検出、および第3データ検出は、並列に実行される。

【0014】

この要約は、本発明のいくつかの実施形態の全般的概要だけを提供する。本発明の多数の他の目的、特徴、利益、および他の実施形態は、次の詳細な説明、添付の特許請求の範囲、および添付図面からより十分に明白になる。

【0015】

本発明のさまざまな実施形態のさらなる理解は、本明細書の残りの部分で説明される図面を参照することによって実現することができる。図面では、同様の符号が、複数の図面を通じて同様のコンポーネントを参照するのに使用される。いくつかの場合に、小文字からなるサブラベルが、複数の同様のコンポーネントのうちの1つを表すために符号に関連付けられる。参照が、既存サブレベルへの指定を伴わずに符号に対して行われるときには、これは、すべてのそのような複数の同様のコンポーネントを参照することが意図されている。

【図面の簡単な説明】

【0016】

【図1】既知の磁気記憶媒体およびセクタ・データ方式を示すブロック図である。

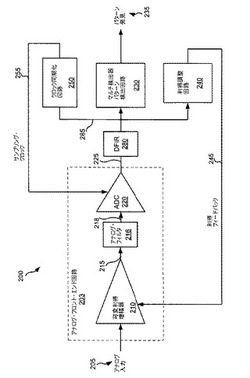

【図2】本発明のさまざまな実施形態によるマルチ検出器位置検出回路を含むデータ処理回路を示す図である。

【図3】本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路を示す図である。

【図4】本発明の他の実施形態による別のマルチ検出器位置検出回路を示す図である。

【図5】本発明のいくつかの実施形態によるマルチ検出器位置検出回路と共に読取チャネル回路を含むストレージ・デバイスを示す図である。

【図6】本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路と共に受信機を含む伝送システムを示す図である。

【図7】マルチ検出器手法を使用するデータ処理に関する本発明のさまざまな実施形態による方法を示す流れ図である。

【図8】本発明の1つまたは複数の実施形態に関連して使用できるようなデータ検出の例を示す流れ図である。

【発明を実施するための形態】

【0017】

本発明は、データ処理のシステムおよび方法に関し、より具体的には、データ処理システムでのパターン検出に関する。

【0018】

本発明のいくつかの実施形態は、パターン識別における柔軟性を提供するサーボまたは他のパターン・データ処理のシステムおよび方法を提供する。たとえば、諸実施形態は、データ・パターンを全く見落とさないながらもデータ・パターンを誤識別すること(すなわち、パターンを不正に識別すること)と、誤識別(すなわち、パターンを不正に識別すること)を減らしながらも識別を見落とすこと(すなわち、パターンを識別できないこと)との間のトレードオフを可能にすることができる。たとえば、本発明のいくつかの実施形態は、それぞれが受け取ったデータ・セット内の同一のパターンを識別するように動作する、複数のデータ検出器回路を使用する。これらのデータ検出回路のそれぞれからの結果が、パターンが見つかったか否かの単一の識別に組み合わされる。

【0019】

図1に移ると、破線として示された2つの例示的なトラック20および22と共に、記憶媒体1が示されている。これらのトラックは、くさび19および18内に書き込まれるサーボ・データによって分離される。これらのくさびは、記憶媒体1上の所望の位置の上での読取/書込ヘッド・アセンブリの制御および同期に使用されるサーボ・データ10を含む。具体的に言うと、このサーボ・データは、一般に、プリアンブル・パターン11と、それに続くセクタ・アドレス・マーク12(SAM)とを含む。セクタ・アドレス・マーク12には、グレイ・コード13が続き、グレイ・コード13には、バースト情報14が続く。2つのトラックおよび2つのくさびが示されているが、通常は、数百個のトラックおよびくさびが、所与の記憶媒体に含まれることに留意されたい。さらに、サーボ・データ・セットが、バースト情報の複数のフィールドを有する場合があることに留意されたい。さらに、バースト情報14の後に現れることができる、たとえば繰返し回転振れ(repeatable run−out)情報などの異なる情報をサーボ・フィールドに含めることができることに留意されたい。サーボ・データ・ビット・パターン10aと10bとの間に、ユーザ・データ領域16が設けられる。

【0020】

動作中に、記憶媒体1は、センサに関して回転され、このセンサは、記憶媒体から情報を感知する。読取動作では、センサは、くさび19から(すなわち、サーボ・データ期間中に)サーボ・データを感知し、その後、くさび19とくさび18との間のユーザ・データ領域から(すなわち、ユーザ・データ期間中に)ユーザ・データを感知し、その後、くさび18からサーボ・データを感知する。書込動作では、センサは、くさび19からサーボ・データを感知し、その後、データをくさび19とくさび18との間のユーザ・データ領域に書き込む。その後、センサは、ユーザ・データ領域の残りの部分およびその後のくさび18からのサーボ・データを感知するために切り替えられる。

【0021】

図2に移ると、本発明のさまざまな実施形態によるマルチ検出器位置検出回路を含むデータ処理回路200が示されている。データ処理回路200は、アナログ・フロント・エンド回路203を含み、アナログ・フロント・エンド回路203は、受け取られたアナログ入力信号205に対してさまざまなアナログ処理を実行する。図示の実施態様では、アナログ・フロント・エンド回路203は、可変利得増幅器回路210、アナログ・フィルタ回路216、およびアナログ−ディジタル変換器回路220を含む。可変利得増幅器回路210は、利得フィードバック245として示される利得だけアナログ入力信号205を増幅する。可変利得増幅器回路210は、受け取られた入力に可変利得を適用することのできる当技術分野で既知の任意の回路とすることができる。可変利得増幅器回路210は、増幅された信号を増幅済み出力215として供給する。増幅済み出力215は、アナログ・フィルタ回路216に供給され、アナログ・フィルタ回路216では、増幅済み出力215が、たとえば増幅済み出力215内の雑音を減らすためにフィルタリングされる。フィルタリングされた信号は、フィルタリング済み出力218としてアナログ−ディジタル変換器回路220に供給される。アナログ−ディジタル変換器回路220は、サンプリング・クロック255によって制御される位相および周波数でフィルタリング済み出力218をサンプリングして、一連のディジタル・サンプル225を作る。アナログ−ディジタル変換器回路220は、アナログ入力信号を対応する一連のディジタル・サンプルに変換することのできる当技術分野で既知の任意の回路とすることができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまなアナログ・フロント・エンド回路を認めるであろう。

【0022】

ディジタル・サンプル225は、ディジタル有限インパルス応答回路280に供給され、ディジタル有限インパルス応答回路280は、受け取られたサンプルに対してフィルタリング・プロセスを実行して、フィルタリング済み出力285を作る。フィルタリング済み出力285は、クロック同期化回路250に供給され、クロック同期化回路250は、サンプリング・クロック255を受け取られたアナログ入力信号205の位相および周波数に同期させるように動作可能である。クロック同期化回路250は、データ入力に同期することのできる当技術分野で既知の任意の回路とすることができる。本発明のいくつかの実施形態では、クロック同期化回路250は、位相ロック・ループ回路を含む。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまな同期化回路を認めるであろう。フィルタリング済み出力285は、利得調整回路240に供給され、利得調整回路240は、可変利得増幅器回路210に供給される利得フィードバック245として供給される利得調整を作るように動作可能である。利得調整回路240は、利得調整を提供することのできる当技術分野で既知の任意の回路とすることができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまな利得フィードバック回路を認めるであろう。

【0023】

フィルタリング済み出力285は、マルチ検出器パターン検出回路230にも供給される。マルチ検出器パターン検出回路230は、パターン発見出力235を作るためにそれぞれがフィルタリング済み出力285に作用する複数のデータ検出器回路を含む。この複数のデータ検出器回路のそれぞれからの結果が、パターン発見出力235をアサートすべきかどうかを決定するために組み合わされる。本発明の一特定の実施形態では、パターン発見出力235は、パターンが見つかったことを複数のデータ検出器回路のうちの1つが示す時に、必ずアサートされる。その代わりに、本発明の他の実施形態では、パターン発見出力235は、パターンが見つかったことを複数のデータ検出器回路のすべてが示す時に、必ずアサートされる。本発明のさらに他の実施形態では、発見出力235は、パターンが見つかったことを複数のデータ検出器回路のうちの複数またはすべてより少数が示す時に、必ずアサートされる。

【0024】

いくつかの場合に、マルチ検出器パターン検出回路230は、ランダム雑音環境でパターン検出の性能を改善するためにそれぞれが別個のデータ検出アルゴリズム(たとえば、ビタビ・アルゴリズム、2状態アルゴリズム、またはしきい値ベースのアルゴリズム)を実施する複数の検出器回路を使用する。その場合に、受け取られたサンプルの同一のセットが、この複数の検出器回路のそれぞれに供給される。必ずしも、検出器のそれぞれに供給されるデータ・セットの間に、位相シフトまたはオフセットあるのではない。マルチ検出器パターン検出回路230に含まれる検出器は、その互いからの独立のゆえに選択され得る。たとえば、受け取られたサンプル・セット内のピークに頼る、ある検出器が、選択され得、別の検出器が、受け取られたサンプルとターゲットにされるサンプルとの間の誤差を最小にするために動作し、もう1つの検出器が、異なるビット遷移について整合フィルタ出力を最大にする。前述の検出器のそれぞれは、異なる形で失敗する。各検出器が異なって失敗するので、3つすべての検出器がサンプルの同一セットについて同時に失敗する可能性は、低くなる。

【0025】

図3に移ると、本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路300が示されている。マルチ検出器位置検出回路300を、マルチ検出器位置検出回路230の代わりに使用することができる。マルチ検出器位置検出回路300は、それぞれサンプル入力305を介してデータを受け取る2つのデータ検出器回路310および330(データ検出器回路Aおよびデータ検出器回路B)を含む。サンプル入力305は、フィルタリング済み出力285を受け取る。データ検出器回路A 310は、データ検出器回路B 330によって適用されるものとは異なる検出アルゴリズムを適用する。データ検出器回路A 310およびデータ検出器回路B 330のそれぞれは、たとえば、ビタビ・アルゴリズム・データ検出器回路、2状態データ検出器回路、またはしきい値検出器回路とすることができる。一例として、本発明の一実施形態では、データ検出器回路A 310は、ビタビ・アルゴリズム検出器回路であり、データ検出器回路Bは、しきい値検出器回路である。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまなタイプの検出器およびその組合せを認めるであろう。

【0026】

たとえば、データ検出器回路A 310がしきい値検出アルゴリズムを実施する場合に、実施されるしきい値アルゴリズムは、サンプル入力305を介して受け取られる一連のサンプルに適用されて、パターン比較器回路320に供給される一連の2進サンプル315を作る。一例として、一連のサンプルが、+20の値から−20の値に及ぶ場合に、0を超える値は、2進「1」になると定義することができ、0以下の値は、2進「0」になると定義することができる。したがって、一連のサンプル20,10,0,−1,−10,−20,−20,1,10は、しきい値検出器を介して処理された後に、次の2進シリーズ、1,1,0,0,0,0,1,1をもたらすはずである。いくつかの場合に、それを超えるとサンプルが2進「1」として識別され、それ未満ではサンプルが2進「0」として識別されるしきい値を、プログラム可能とすることができ、これによって、DCオフセットまたは他の要因について補償するためのしきい値検出器動作の実施後調整が可能になる。一連の2進値を、その後、さらなる処理に使用することができる。

【0027】

いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化される(wide bi−phase encoded)。その場合に、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号される。たとえば、ワイド・バイフェーズ符号化が、パターン「1100」によって「0」を表すことと、パターン「0011」によって「1」を表すこととを含み、受け取られるサンプルが、20,10,0,−10,−20,0,20,1,−20,−10,5,10,20,3,−20,0である場合には、しきい値検出プロセスは、まず、すべての0以下の値に2進「0」を割り当て、0を超えるすべての値に2進「1」を割り当てて、次のバイフェーズ符号化されたパターン、1100,0011,0011,1100を作る。次に、先行するバイフェーズ符号化されたパターンが復号されて、次の一連の2進値、0,1,1,0を作る。その後、この一連の2進値を、さらなる処理に使用することができる。

【0028】

次に、データ検出器回路A 310によって実施されるしきい値データ検出処理から回復された一連の2進値は、事前定義のまたはプログラム可能なパターン350と比較される。本発明の一特定の実施形態では、パターン350は、セクタ・アドレス・マーク・パターンである。本発明の他の実施形態では、パターン350は、グレイ・コード・パターンである。本明細書で提供される開示に基づいて、当業者は、パターン350として使用できるさまざまなパターンを認めるであろう。パターン350と2進サンプル315との間で一致が見つかる場合には、パターン発見の予備表示325が、コンバイナ回路360に供給される。

【0029】

たとえば、データ検出器回路Bがビタビ・アルゴリズム検出プロセスを実施する場合には、実施されるビタビ・アルゴリズムは、サンプル入力305を介して受け取られる一連のサンプルに適用されて、パターン比較器回路340に供給される一連の2進サンプル335を作る。このビタビ・アルゴリズム検出プロセスは、当技術分野で既知の任意のビタビ・アルゴリズム検出プロセスと一貫するものとすることができる。例のビタビ・アルゴリズムは、J.HagenauerおよびP.Hoeher、「A Viterbi algorithm with soft−decision outputs and its applications」、Proc.IEEE GLOBECOM、47.11〜47.17頁、米国テキサス州ダラス、1989年11月に記載されている。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化されている。その場合には、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号され、この一連の2進値は、さらなる処理のために供給される。ワイド・バイフェーズ符号化が使用されない場合には、ビタビ・アルゴリズム検出プロセスによって供給される2進値が、さらなる処理のために供給される。その後、データ検出器回路B 330によって実施されるしきい値データ検出処理から回復された一連の2進値が、パターン350と比較される。パターン350と2進サンプル335との間で一致が見つかる場合には、パターン発見の予備表示345が、コンバイナ回路360に供給される。

【0030】

データ検出器回路A 310またはデータ検出器回路B 330のいずれかを、2状態データ検出器回路によって置換できることに留意されたい。そのような2状態データ検出器回路は、2010年8月5日にAnnampedu他によって出願された米国仮出願第12/851,475号、名称「Systems and Methods for Sequence Detection in Data Processing」で述べられるものと一貫して動作する。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。

【0031】

予備表示325および予備表示345は、コンバイナ回路360によって組み合わされて、パターン発見出力365を作る。コンバイナ回路360を、次の擬似コードに従って、パターンが見つかったことを予備表示325および予備表示345の一方または両方が示す時に必ずパターン発見出力365がアサートされるように実施することができる。

If (予備表示325がアサートされている OR 予備表示345がアサートされている)

{

パターン発見出力365をアサートする

}

Else

{

パターン発見出力365をデアサートする

}

本発明の他の実施形態では、コンバイナ回路360を、次の擬似コードに従って、パターンが見つかったことを予備表示325と予備表示345との両方が示す時に限ってパターン発見出力365がアサートされるように実施することができる。

If (予備表示325がアサートされている AND 予備表示345がアサートされている)

{

パターン発見出力365をアサートする

}

Else

{

パターン発見出力365をデアサートする

}

【0032】

図4に移ると、本発明の他の実施形態による別のマルチ検出器位置検出回路400が示されている。マルチ検出器位置検出回路400を、マルチ検出器位置検出回路230の代わりに使用することができる。マルチ検出器位置検出回路400は、それぞれサンプル入力405を介してデータを受け取る3つのデータ検出器回路410、430、および470(データ検出器回路A、データ検出器回路B、およびデータ検出器回路C)を含む。サンプル入力405は、フィルタリング済み出力285を受け取る。データ検出器回路A 410は、どちらでもよいがデータ検出器回路B 430によって適用されるものとは異なる検出アルゴリズムを適用し、データ検出器回路B 430は、データ検出器回路C 470によって適用されるものとは異なる検出アルゴリズムを適用する。データ検出器回路A 410、データ検出器回路B 430、およびデータ検出器回路C 470のそれぞれは、たとえば、ビタビ・アルゴリズム・データ検出器回路、2状態データ検出器回路、またはしきい値検出器回路とすることができる。一例として、本発明の一実施形態では、データ検出器回路A 410は、ビタビ・アルゴリズム検出器回路であり、データ検出器回路Bは、しきい値検出器回路であり、データ検出器回路Cは、2状態検出器回路である。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまなタイプの検出器およびその組合せを認めるであろう。

【0033】

データ検出器A 410は、一連の2進サンプル415をパターン比較器回路420に供給する。次に、データ検出器A 410によって実施されるしきい値データ検出処理から回復された一連の2進データが、事前定義のまたはプログラム可能なパターン450と比較される。本発明の一特定の実施形態では、パターン450は、セクタ・アドレス・マーク・パターンである。本発明の他の実施形態では、パターン450は、グレイ・コード・パターンである。本明細書で提供される開示に基づいて、当業者は、パターン450として使用できるさまざまなパターンを認めるであろう。パターン450と2進サンプル415との間で一致が見つかる場合には、パターン発見の予備表示425が、コンバイナ回路460に供給される。

【0034】

データ検出器B 430は、パターン比較器回路440に一連の2進サンプル435を供給する。次に、データ検出器回路B 430によって実施されるビタビ・アルゴリズム検出処理から回復された一連の2進データが、パターン450と比較される。パターン450と2進サンプル435との間で一致が見つかる場合には、パターン発見の予備表示445が、コンバイナ回路460に供給される。データ検出器C 470は、パターン比較器回路480に一連の2進サンプル475を供給する。次に、データ検出器回路C 470によって実施される2状態アルゴリズム検出処理から回復された一連の2進データが、パターン450と比較される。パターン450と2進サンプル475との間で一致が見つかる場合には、パターン発見の予備表示485が、コンバイナ回路460に供給される。

【0035】

予備表示425、予備表示445、および予備表示485は、コンバイナ回路460によって組み合わされて、パターン発見出力465を作る。コンバイナ回路460を、次の擬似コードに従って、パターンが見つかったことを予備表示425、予備表示445、および予備表示485のうちの1つまたは複数が示す時に必ずパターン発見出力465がアサートされるように実施することができる。

If (予備表示425がアサートされている OR 予備表示445がアサートされている OR 予備表示485がアサートされている)

{

パターン発見出力465をアサートする

}

Else

{

パターン発見出力465をデアサートする

}

本発明の他の実施形態では、コンバイナ回路460を、次の擬似コードに従って、パターンが見つかったことを予備表示425、予備表示445、および予備表示485のすべてが示す時に限ってパターン発見出力465がアサートされるように実施することができる。

If (予備表示425がアサートされている AND 予備表示445がアサートされている AND 予備表示485がアサートされている)

{

パターン発見出力465をアサートする

}

Else

{

パターン発見出力465をデアサートする

}

本発明のさらに他の実施形態では、コンバイナ回路460を、次の擬似コードに従って、パターンが見つかったことを予備表示425、予備表示445、および予備表示485のうちの複数が示す時に必ずパターン発見出力465がアサートされるように実施することができる。

If ((予備表示425がアサートされている AND 予備表示445がアサートされている)

OR

(予備表示425がアサートされている AND 予備表示485がアサートされている)

OR

(予備表示445がアサートされている AND 予備表示485がアサートされている)

)

{

パターン発見出力465をアサートする

}

Else

{

パターン発見出力465をデアサートする

}

【0036】

図5に移ると、本発明のいくつかの実施形態によるマルチ検出器位置検出回路と共に読取チャネル回路510を含むストレージ・システム500が示されている。ストレージ・システム500は、たとえば、ハード・ディスク・ドライブとすることができる。ストレージ・システム500は、前置増幅器570、インターフェース・コントローラ520、ハード・ディスク・コントローラ566、モーター・コントローラ568、スピンドル・モーター572、ディスク・プラッタ578、および読取/書込ヘッド576をも含む。インターフェース・コントローラ520は、ディスク・プラッタ578へ/からのデータのアドレッシングおよびタイミングを制御する。ディスク・プラッタ578上のデータは、読取/書込ヘッド・アセンブリ576がディスク・プラッタ578の上で正しく位置決めされている時にこのアセンブリによって検出できる磁気信号のグループからなる。一実施形態では、ディスク・プラッタ578は、長手記録方式または垂直記録方式のいずれかに従って記録された磁気信号を含む。

【0037】

通常の読取動作では、読取/書込ヘッド・アセンブリ576は、ディスク・プラッタ578上の所望のデータ・トラックの上で、モーター・コントローラ568によって正確に位置決めされる。モーター・コントローラ568は、ハード・ディスク・コントローラ566の指示の下でディスク・プラッタ578上の正しいデータ・トラックに読取/書込ヘッド・アセンブリを移動することによって、ディスク・プラッタ578に関して読取/書込ヘッド・アセンブリ576を正確に位置決めすると同時に、スピンドル・モーター572を駆動する。スピンドル・モーター572は、ディスク・プラッタ578を決定されたスピン・レート(RPM)で回転させる。読取/書込ヘッド・アセンブリ576が、正しいデータ・トラックに隣接して位置決めされた後に、ディスク・プラッタ578がスピンドル・モーター572によって回転されるにつれて、ディスク・プラッタ578上のデータを表す磁気信号が、読取/書込ヘッド・アセンブリ576によって感知される。感知された磁気信号は、ディスク・プラッタ578上の磁気データを表す連続する微細なアナログ信号として供給される。この微細なアナログ信号は、読取/書込ヘッド・アセンブリ576から前置増幅器570を介して読取チャネル・モジュール564に転送される。前置増幅器570は、ディスク・プラッタ578からアクセスされる微細なアナログ信号を増幅するように動作可能である。読取チャネル回路510は、受け取られたアナログ信号を復号し、ディジタル化して、ディスク・プラッタ578に最初に書き込まれた情報を再作成する。このデータは、受け取る回路に読取データ503として供給される。受け取られた情報の復号の一部として、読取チャネル回路510は、データ検出を実行して、データ内のセクタ・アドレス・マークを識別する。このデータ検出プロセスは、マルチ検出器位置検出回路を利用する。そのようなマルチ検出器位置検出回路は、図2、図3、および/または図4に関して上で述べたものに類似する回路網を含むことができ、かつ/あるいは図7に関して下で述べる方法と一貫して動作することができる。書込動作は、実質的に先行する読取動作の逆であり、書込データ501は、読取チャネル回路510に供給される。このデータは、その後、符号化され、ディスク・プラッタ578に書き込まれる。

【0038】

ストレージ・システム500を、たとえばRAID(redundant array of inexpensive disksまたはredundant array of independent disks)ベースのストレージ・システムなどのより大きいストレージ・システムに一体化することができることに留意されたい。ストレージ・システム500のさまざまな機能またはブロックをソフトウェアまたはファームウェアのいずれかで実施でき、他の機能またはブロックがハードウェアで実施されることにも留意されたい。

【0039】

図6に移ると、本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路と共に受信機620を含む伝送システム600が示されている。伝送システム600は、当技術分野で既知のように符号化された情報を転送媒体630を介して送信するように動作可能である送信機610を含む。符号化されたデータは、転送媒体630から受信機620によって受信される。受信機620は、マルチ検出器位置検出回路を組み込む。そのようなマルチ検出器位置検出回路は、図2、図3、および/または図4に関して上で述べたものに類似する回路網を含むことができ、かつ/あるいは図7に関して下で述べる方法と一貫して動作することができる。

【0040】

図7に移ると、流れ図700は、マルチ検出器手法を使用するデータ処理に関する本発明のさまざまな実施形態による方法を示す。流れ図700に従うと、アナログ信号が受け取られる(ブロック705)。このアナログ信号は、たとえば、記憶媒体に格納された情報を感知することによって、または無線伝送デバイスを介する情報の受信の一部として、導出することができる。本明細書で提供される開示に基づいて、当業者は、アナログ信号のさまざまな源を認めるであろう。可変利得増幅をアナログ信号に適用して、増幅された信号を作る(ブロック710)。この増幅で適用される利得は、利得フィードバックに基づく。可変利得増幅に関する当技術分野で既知の任意の手法を使用することができる。いくつかの場合に、固定増幅プロセスを、可変利得増幅の代わりに使用できることにも留意されたい。アナログ(すなわち、連続時間)フィルタリングを増幅された信号に適用して、フィルタリングされた信号を作る(ブロック715)。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に従って使用できるさまざまなアナログ・フィルタおよび/またはフィルタリング・プロセスを認めるであろう。さらに、いくつかの場合には、フィルタリングは適用されない。フィルタリング済み信号をアナログ−ディジタル変換器回路に供給し、ここで、フィルタリング済み信号は、一連のディジタル・サンプルに変換される(ブロック720)。このディジタル・サンプルは、サンプリング・クロックによって管理される位相および周波数での増幅された出力に対応する。当技術分野で既知の任意のアナログ−ディジタル変換プロセスを使用することができる。

【0041】

供給された一連のディジタル・サンプルを使用して、クロック生成プロセスを実行して、入力データ・ストリームに同期化されたサンプリング・クロックを作成する(ブロック725)。このクロック生成は、入力データ・セットの位相/周波数に同期化されたクロックを生成する、当技術分野で既知の任意のプロセスに従って行うことができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関して使用できるさまざまなクロック生成プロセスを認めるであろう。

【0042】

さらに、可変利得増幅プロセスの利得を制御する利得フィードバックを、供給された一連のディジタル・サンプルを使用して生成する(ブロック730)。この利得フィードバック生成は、可変利得増幅器の利得を確立する、当技術分野で既知の任意のプロセスに従って行うことができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関して使用できるさまざまな利得フィードバック生成プロセスを認めるであろう。

【0043】

しきい値検出アルゴリズムを一連のディジタル・サンプルに適用して、一連の2進サンプルを作る(ブロック735)。たとえば、ディジタル・サンプルが、+20の値から−20の値に及ぶ場合に、0を超える値は、2進「1」になると定義することができ、0以下の値は、2進「0」になると定義することができる。したがって、一連のディジタル・サンプル20,10,0,−1,−10,−20,−20,1,10は、しきい値検出器を介して処理された後に、次の2進シリーズ、1,1,0,0,0,0,1,1をもたらすはずである。いくつかの場合に、それを超えるとサンプルが2進「1」として識別され、それ未満ではサンプルが2進「0」として識別されるしきい値を、プログラム可能とすることができ、これによって、DCオフセットまたは他の要因について補償するためのしきい値検出器動作の実施後調整が可能になる。一連の2進値を、その後、さらなる処理に使用することができる。

【0044】

いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化される。その場合に、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号される。たとえば、ワイド・バイフェーズ符号化が、パターン「1100」によって「0」を表すことと、パターン「0011」によって「1」1を表すこととを含み、受け取られるサンプルが、20,10,0,−10,−20,0,20,1,−20,−10,5,10,20,3,−20,0である場合には、しきい値検出プロセスは、まず、すべての0以下の値に2進「0」を割り当て、0を超えるすべての値に2進「1」を割り当てて、次のワイド・バイフェーズ符号化されたパターン、1100,0011,0011,1100を作る。次に、先行するバイフェーズ符号化されたパターンが復号されて、次の一連の2進値、0,1,1,0を作る。その後、この一連の2進値を、さらなる処理に使用することができる。

【0045】

次に、しきい値データ検出処理(ブロック735)から回復された一連の2進値を、事前定義のまたはプログラム可能なセクタ・アドレス・マーク・パターンと比較する(ブロック740)。本発明の一特定の実施形態では、セクタ・アドレス・マーク・パターンは、データ・セット内の特定の位置を表す、受け取られたデータ・セット内の同期マークとして働く9ビット・パターンである。セクタ・アドレス・マーク・パターンと受け取られた一連の2進値との間で一致が見つかる場合には(ブロック740)、セクタ・アドレス・マークの第1予備表示が供給される。

【0046】

2状態データ検出を一連のディジタル・サンプルに適用して、一連の2進サンプルを作る(ブロック745)。図8は、本発明の1つまたは複数の実施形態に関連して使用できるデータ検出の例を示す流れ図800である。流れ図800に従うと、4Tサンプルが受け取られたかどうかを判定する(ブロック810)。前に説明したように、4Tサンプルは、ビット遷移ごとに4つのサンプルを暗示する。ビット遷移あたりのより多数またはより少数のサンプルを、本発明の異なる実施形態に関連して使用できることに留意されたい。規定された個数のサンプルを受け取った後に(ブロック810)、受け取られたサンプルは、それぞれの相関器値によって乗算されて、0から0へ、0から1へ、1から0へ、および1から1への遷移のパス値を作る。一例として、4つのサンプルは、51,−35,−102,−112である。以前の0状態値は、「12」であり、以前の1状態値は、「124」である。具体的に言うと、0から1への遷移の枝メトリック(branch metric)を、0から1への遷移に対応する相関器値(「−1 0 1 1」)を使用して計算する(ブロック822)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(−1*51)+(0*−35)+(1*−102)+(1*−112)=−265

同様に、1から1への遷移の枝メトリックを、1から1への遷移に対応する相関器値(「0 −1 0 1」)を使用して計算する(ブロック824)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(0*51)+(−1*−35)+(0*−102)+(1*−112)=−77

1から0への遷移の枝メトリックを、1から0への遷移に対応する相関器値(「1 0 −1 −1」)を使用して計算する(ブロック826)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(1*51)+(0*−35)+(−1*−102)+(−1*−112)=265

さらに、0から0への遷移の枝メトリックを、0から0への遷移に対応する相関器値(「0 1 0 −1」)を使用して計算する(ブロック828)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(0*51)+(1*−35)+(0*−102)+(−1*−112)=77

【0047】

枝メトリックが使用可能になった後に、枝メトリックを、その枝メトリックがそこから導出された状態の値に加算する。具体的に言うと、状態メトリックを0から1への遷移状態について計算して、第1中間状態を作る(ブロック832)。前述の例の入力を使用すると、第1中間状態値は、次式に従って計算される。

第1中間値=以前の0状態値+0→1枝メトリック=12−265=−253

状態メトリックを1から1への遷移状態について計算して、第2中間状態を作る(ブロック834)。前述の例の入力を使用すると、第2中間状態値は、次式に従って計算される。

第2中間値=以前の1状態値+1→1枝メトリック=124−77=−47

状態メトリックを0から0への遷移状態について計算して、第3中間状態を作る(ブロック836)。前述の例の入力を使用すると、第3中間状態値は、次式に従って計算される。

第3中間値=以前の0状態値+1→0枝メトリック=124+265=389

さらに、状態メトリックを1から0への遷移状態について計算して、第4中間状態を作る(ブロック838)。前述の例の入力を使用すると、第4中間状態値は、次式に従って計算される。

第4中間値=以前の0状態値+0→0枝メトリック=12+77=89

【0048】

第1の生き残っている状態メトリックを、以前に計算された第1中間値と第2中間値との間で選択する(ブロック842)。これは、第1中間値および第2中間値のうちでより大きいものを選択することによって行われ、より大きいものは、この例では「47」である。この値を、次の一連のデータ・サンプルを乗算する際に(たとえば、ブロック222、224、226、228で)使用するために、以前の1状態メトリックとして格納する。さらに、第2の生き残っている状態メトリックを、以前に計算された第3中間値と第4中間値との間で選択する(ブロック844)。これは、第3中間値および第4中間値のうちでより大きいものを選択することによって行われ、より大きいものは、この例では「389」である。この値を、次の一連のデータ・サンプルを乗算する際に(たとえば、ブロック222、224、226、228で)使用するために、以前の0状態メトリックとして格納する。以前に判定された第1の生き残っている中間状態および第2の生き残っている中間状態に基づいて、生き残っている状態メトリックを選択する(ブロック852)。これは、第1の生き残っている中間状態および第2の生き残っている中間状態のうちでより大きいものを選択することによって行われ、より大きいものは、この例では「389」である。この場合の生き残っている状態メトリックは、0状態である。この生き残っている状態メトリックは、検出されたシーケンス内の最も最近のビットに対応し、所望の個数のビットにまたがって検出されたビット・シーケンスを作るために、間に合ってトレース・バックするのに使用される(ブロック862)。これは、生き残っている状態メトリックの値の計算を最終的にもたらしたパス内の以前の状態メトリックを判定することによって行われる。次に、識別されたビット・シーケンスを出力として供給し(ブロック872)、このプロセスを、受け取られる次の一連のディジタル・サンプルについて繰り返す(ブロック810)。2状態アルゴリズムの追加の議論が、2010年8月5日にAnnampedu他によって出願された米国仮出願許第12/851,475号、名称「Systems and Methods for Sequence Detection in Data Processing」に記載されている。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。

【0049】

図7に戻って、最も最近の結果の2進サンプル(ブロック745)を、セクタ・アドレス・マーク・パターンと比較する(ブロック750)。やはり、本発明の一特定の実施形態では、セクタ・アドレス・マーク・パターンは、データ・セット内の特定の位置を表す、受け取られたデータ・セット内の同期マークとして働く9ビット・パターンである。セクタ・アドレス・マーク・パターンと受け取られた一連の2進値との間で一致が見つかる場合には(ブロック750)、セクタ・アドレス・マークの第2予備表示が供給される。

【0050】

ビタビ・アルゴリズム・データ検出プロセスを一連のディジタル・サンプルに適用して、一連の2進サンプルを作る(ブロック755)。このビタビ・アルゴリズム検出プロセスは、当技術分野で既知の任意のビタビ・アルゴリズム検出プロセスと一貫するものとすることができる。例のビタビ・アルゴリズムが、J.HagenauerおよびP.Hoeher、「A Viterbi algorithm with soft−decision outputs and its applications」、Proc.IEEE GLOBECOM、47.11〜47.17頁、米国テキサス州ダラス、1989年11月に記載されている。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化されている。その場合に、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号され、この一連の2進値は、さらなる処理のために供給される。ワイド・バイフェーズ符号化が使用されない場合には、ビタビ・アルゴリズム検出プロセスによって供給される2進値が、さらなる処理のために供給される。

【0051】

その後、ビタビ・アルゴリズム・データ検出処理から回復された一連の2進値(ブロック755)を、事前定義のまたはプログラム可能なセクタ・アドレス・マーク・パターンと比較する(ブロック760)。やはり、本発明の一特定の実施形態では、セクタ・アドレス・マーク・パターンは、データ・セット内の特定の位置を表す、受け取られたデータ・セット内の同期マークとして働く9ビット・パターンである。セクタ・アドレス・マーク・パターンと受け取られた一連の2進値との間で一致が見つかる場合には(ブロック760)、セクタ・アドレス・マークの第3予備表示が供給される。

【0052】

第1予備表示、第2予備表示、および第3予備表示のそれぞれを組み合わせて、セクタ・アドレス・マークをアサートすべきかどうかを判定する(ブロック770)。本発明の一特定の実施形態では、セクタ・アドレス・マークは、第1予備表示、第2予備表示、または第3予備表示のいずれかがアサートされる時に、必ず識別される。その代わりに、本発明の他の実施形態では、セクタ・アドレス・マークは、第1予備表示、第2予備表示、または第3予備表示のうちの複数がアサートされる時に、必ず識別される。本発明のさらに他の実施形態では、セクタ・アドレス・マークは、第1予備表示、第2予備表示、および第3予備表示のすべてがアサートされる時に、必ず識別される。見つかったものとしてセクタ・アドレス・マークを識別すべきかどうかの選択を、第1予備表示、第2予備表示、または第3予備表示のうちの1つだけがアサートされることを要求することによって、セクタ・アドレス・マークの時折の誤識別を犠牲にしてセクタ・アドレス・マークを識別することに向けて偏らせることができる。その代わりに、この選択を、セクタ・アドレス・マークの識別の間でよりバランスのとれたものにすると同時に、第1予備表示、第2予備表示、または第3予備表示のうちの複数のアサートを要求することによって誤識別を防ぐことができる。もう1つの代替案として、この選択を、すべての検出プロセスがセクタ・アドレス・マークを識別することを要求することによって、セクタ・アドレス・マークを見落とすことを犠牲にして、セクタ・アドレス・マークの誤識別を回避することに向けて偏らせることができる。

【0053】

セクタ・アドレス・マークが、第1予備表示、第2予備表示、および/または第3予備表示に基づいて識別される場合には(ブロック780)、SAM発見信号をアサートする(ブロック790)。その代わりに、セクタ・アドレス・マークが、第1予備表示、第2予備表示、および/または第3予備表示に基づいて識別されない場合には(ブロック780)、SAM発見信号は、デアサートされたままになる。

【0054】

上の適用例で述べたさまざまなブロックを、他の機能性と一緒に集積回路内で実施できることに留意されたい。そのような集積回路は、所与のブロック、システム、または回路の機能のすべて、あるいはブロック、システム、または回路のサブセットのみを含むことができる。さらに、ブロック、システム、または回路の要素を、複数の集積回路にまたがって実施することができる。そのような集積回路は、モノリシック集積回路、フリップ・チップ集積回路、マルチチップ・モジュール集積回路、および/または混合信号集積回路を含むがこれに限定はされない当技術分野で既知の任意のタイプの集積回路とすることができる。本明細書で述べたブロック、システム、または回路のさまざまな機能を、ソフトウェアまたはファームウェアのいずれかで実施できることにも留意されたい。その場合に、システム全体、ブロック、または回路を、そのソフトウェア同等物またはファームウェア同等物を使用して実施することができる。他の場合には、所与のシステム、ブロック、または回路の1つの部分をソフトウェアまたはファームウェアで実施することができ、他の部分は、ハードウェアで実施される。

【0055】

結論として、本発明は、データ処理に関する新規のシステム、デバイス、方法、および配置を提供する。本発明の1つまたは複数の実施形態の詳細な説明を上で与えたが、本発明の趣旨から逸脱しない、さまざまな代替形態、修正形態、および同等物が、当業者に明白であろう。たとえば、本発明の1つまたは複数の実施形態を、たとえばテープ・レコーディング・システム、光ディスク・ドライブ、無線システム、およびディジタル加入者回線システムなどのさまざまなデータ・ストレージ・システムおよびディジタル通信システムに適用することができる。さらに、マルチ検出器位置検出回路を、並列に動作する2つまたは3つのデータ検出器回路を有するものとして説明したが、4つ以上のデータ検出器回路を、並列、直列、または並列および直列のある組合せのいずれかで使用できることに留意されたい。さらに、前述の実施形態は、別個のタイプのデータ検出プロセスを使用するものとして説明されたが、たとえば最大事後確率データ検出プロセスなどの他のデータ検出プロセスを、上で説明されたプロセスの代わりにまたはこれに加えて使用できることに留意されたい。したがって、上の説明を、本発明の範囲を限定するものと解釈してはならず、本発明の範囲は、添付の特許請求の範囲によって定義される。

【技術分野】

【0001】

本発明は、データ処理のシステムおよび方法に関し、より具体的には、データ処理システムでのパターン検出に関する。

【背景技術】

【0002】

通常のストレージ・デバイスは、記憶媒体上で磁気的に表される情報を格納する磁気記憶媒体を含む。ヘッドが、記憶媒体に対して配置され、このヘッドは、磁気的に表される情報を感知し、磁気的に表される情報に対応する電気信号を供給する。この電気信号は、最終的にデータ検出回路に渡され、このデータ検出回路は、記憶媒体に最初に書き込まれた情報を回復するために、1つまたは複数のデータ検出プロセスを実行する。記憶媒体上で維持される情報は、通常、ユーザ・データと同期データとの両方を含む。ユーザ・データは、ランダム・パターンと考えることができ、一方同期データは、一般に、たとえば記憶媒体上の位置を識別するのに使用できる、定義されたパターンである。

【0003】

さまざまな既存のデータ処理システムは、たとえば、しきい値検出器回路を利用して、受け取られた同期データを処理し、位置データを識別する。そのような回路は、受け取られるディジタル・サンプルが、雑音を考慮に入れるために正しく前処理される場合には良く動作する。しかし、いくつかの場合に、そのような前処理が最適未満である場合がある。これは、位置を確立することができないことをもたらし、これによって性能を劣化させる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国仮出願第12/851,475号

【非特許文献】

【0005】

【非特許文献1】J.HagenauerおよびP.Hoeher、「A Viterbi algorithm with soft−decision outputs and its applications」、Proc.IEEE GLOBECOM、47.11〜47.17頁、米国テキサス州ダラス、1989年11月

【発明の概要】

【発明が解決しようとする課題】

【0006】

したがって、少なくとも前述の理由から、データ処理に関する高度なシステムおよび方法の必要性が、当技術分野には存在する。

【課題を解決するための手段】

【0007】

本発明は、データ処理のシステムおよび方法に関し、より具体的には、データ処理システムでのパターン検出に関する。

【0008】

本発明のさまざまな実施形態は、パターン検出回路を含むデータ処理回路を提供する。パターン検出回路は、それぞれが同一の一連のデータ・サンプルを受け取り、第1検出データ出力および第2検出データ出力を供給するように動作可能な少なくとも2つのデータ検出器回路を含む。さらに、パターン検出回路は、少なくとも部分的に第1検出データ出力および第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路を含む。

【0009】

前述の実施形態のいくつかの実例では、結果組合せ回路は、第1比較器回路、第2比較器回路、およびコンバイナ回路をさらに含む。第1比較器回路は、第1検出データ出力をパターンと比較し、第1検出データ出力とパターンとの間の一致が発生する時に第1予備パターン発見表示をアサートするように動作可能である。第2比較器回路は、第2検出データ出力をパターンと比較し、第2検出データ出力とパターンとの間の一致が発生する時に第2予備パターン発見表示をアサートするように動作可能である。コンバイナ回路は、少なくとも部分的に第1予備パターン発見表示および第2予備パターン発見表示に基づいてパターン発見出力をアサートするように動作可能である。特定の事例では、コンバイナ回路は、第1予備パターン発見表示と第2予備パターン発見表示との両方がパターン発見を示す時にパターン発見出力をアサートするように動作可能である。他の事例では、コンバイナ回路は、第1予備パターン発見表示および第2予備パターン発見表示のうちの1つがパターン発見を示す時にパターン発見出力をアサートするように動作可能である。

【0010】

前述の実施形態のさまざまな実例では、第1データ検出器回路は、第2データ検出器回路によって適用される第2データ検出アルゴリズムとは異なる第1データ検出アルゴリズムを適用する。いくつかのそのような事例では、第1データ検出器回路および第2データ検出器回路は、しきい値検出器回路、2状態検出器回路、またはビタビ・アルゴリズム検出器回路とすることができるが、これらに限定はされない。いくつかの事例では、第1データ検出器回路は、第2データ検出器回路と一致して並列に一連のデータ・サンプルの同一のサブセットに作用する。

【0011】

前述の実施形態のいくつかの実例では、パターン検出回路は、第3データ検出器回路をさらに含む。第3データ検出器回路は、一連のデータ・サンプルを受け取り、第3検出データ出力を供給するように動作可能である。そのような実例では、結果組合せ回路は、少なくとも部分的に第1検出データ出力、第2検出データ出力、および第3検出データ出力に基づいてパターン発見出力をアサートするように動作可能である。いくつかのそのような実例では、第1データ検出器回路は、ビタビ・アルゴリズム検出器回路であり、第2データ検出器回路は、しきい値検出器回路であり、第3データ検出器回路は、2状態検出器回路である。

【0012】

本発明の他の実施形態は、一連のデータ・サンプルを受け取ることと、第1検出出力を作るために一連のデータ・サンプルに対して第1データ検出を実行することと、第2検出出力を作るために一連のデータ・サンプルに対して第2データ検出を実行することと、少なくとも部分的に第1検出出力および第2検出出力に基づいてパターン発見信号をアサートすることとを含む、パターン検出の方法を提供する。第2データ検出は、第1データ検出とは異なる。いくつかの事例では、第1データ検出および第2データ検出は、並列に実行される。

【0013】

前述の実施形態のいくつかの実例では、第1データ検出は、しきい値データ検出、2状態データ検出、またはビタビ・アルゴリズム・データ検出であり、第2データ検出は、しきい値データ検出、2状態データ検出、またはビタビ・アルゴリズム・データ検出である。前述の実施形態のいくつかの実例では、この方法は、第3検出出力を作るために一連のデータ・サンプルに対して第3データ検出を実行することをさらに含む。そのような事例では、第3データ検出は、第1データ検出および第2データ検出とは異なり、この方法は、少なくとも部分的に第1検出出力、第2検出出力、および第3検出出力に基づいてパターン発見信号をアサートすることをさらに含む。いくつかのそのような事例では、第1データ検出は、ビタビ・アルゴリズム・データ検出であり、第2データ検出は、しきい値データ検出であり、第3データ検出は、2状態データ検出である。1つまたは複数の事例では、第1データ検出、第2データ検出、および第3データ検出は、並列に実行される。

【0014】

この要約は、本発明のいくつかの実施形態の全般的概要だけを提供する。本発明の多数の他の目的、特徴、利益、および他の実施形態は、次の詳細な説明、添付の特許請求の範囲、および添付図面からより十分に明白になる。

【0015】

本発明のさまざまな実施形態のさらなる理解は、本明細書の残りの部分で説明される図面を参照することによって実現することができる。図面では、同様の符号が、複数の図面を通じて同様のコンポーネントを参照するのに使用される。いくつかの場合に、小文字からなるサブラベルが、複数の同様のコンポーネントのうちの1つを表すために符号に関連付けられる。参照が、既存サブレベルへの指定を伴わずに符号に対して行われるときには、これは、すべてのそのような複数の同様のコンポーネントを参照することが意図されている。

【図面の簡単な説明】

【0016】

【図1】既知の磁気記憶媒体およびセクタ・データ方式を示すブロック図である。

【図2】本発明のさまざまな実施形態によるマルチ検出器位置検出回路を含むデータ処理回路を示す図である。

【図3】本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路を示す図である。

【図4】本発明の他の実施形態による別のマルチ検出器位置検出回路を示す図である。

【図5】本発明のいくつかの実施形態によるマルチ検出器位置検出回路と共に読取チャネル回路を含むストレージ・デバイスを示す図である。

【図6】本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路と共に受信機を含む伝送システムを示す図である。

【図7】マルチ検出器手法を使用するデータ処理に関する本発明のさまざまな実施形態による方法を示す流れ図である。

【図8】本発明の1つまたは複数の実施形態に関連して使用できるようなデータ検出の例を示す流れ図である。

【発明を実施するための形態】

【0017】

本発明は、データ処理のシステムおよび方法に関し、より具体的には、データ処理システムでのパターン検出に関する。

【0018】

本発明のいくつかの実施形態は、パターン識別における柔軟性を提供するサーボまたは他のパターン・データ処理のシステムおよび方法を提供する。たとえば、諸実施形態は、データ・パターンを全く見落とさないながらもデータ・パターンを誤識別すること(すなわち、パターンを不正に識別すること)と、誤識別(すなわち、パターンを不正に識別すること)を減らしながらも識別を見落とすこと(すなわち、パターンを識別できないこと)との間のトレードオフを可能にすることができる。たとえば、本発明のいくつかの実施形態は、それぞれが受け取ったデータ・セット内の同一のパターンを識別するように動作する、複数のデータ検出器回路を使用する。これらのデータ検出回路のそれぞれからの結果が、パターンが見つかったか否かの単一の識別に組み合わされる。

【0019】

図1に移ると、破線として示された2つの例示的なトラック20および22と共に、記憶媒体1が示されている。これらのトラックは、くさび19および18内に書き込まれるサーボ・データによって分離される。これらのくさびは、記憶媒体1上の所望の位置の上での読取/書込ヘッド・アセンブリの制御および同期に使用されるサーボ・データ10を含む。具体的に言うと、このサーボ・データは、一般に、プリアンブル・パターン11と、それに続くセクタ・アドレス・マーク12(SAM)とを含む。セクタ・アドレス・マーク12には、グレイ・コード13が続き、グレイ・コード13には、バースト情報14が続く。2つのトラックおよび2つのくさびが示されているが、通常は、数百個のトラックおよびくさびが、所与の記憶媒体に含まれることに留意されたい。さらに、サーボ・データ・セットが、バースト情報の複数のフィールドを有する場合があることに留意されたい。さらに、バースト情報14の後に現れることができる、たとえば繰返し回転振れ(repeatable run−out)情報などの異なる情報をサーボ・フィールドに含めることができることに留意されたい。サーボ・データ・ビット・パターン10aと10bとの間に、ユーザ・データ領域16が設けられる。

【0020】

動作中に、記憶媒体1は、センサに関して回転され、このセンサは、記憶媒体から情報を感知する。読取動作では、センサは、くさび19から(すなわち、サーボ・データ期間中に)サーボ・データを感知し、その後、くさび19とくさび18との間のユーザ・データ領域から(すなわち、ユーザ・データ期間中に)ユーザ・データを感知し、その後、くさび18からサーボ・データを感知する。書込動作では、センサは、くさび19からサーボ・データを感知し、その後、データをくさび19とくさび18との間のユーザ・データ領域に書き込む。その後、センサは、ユーザ・データ領域の残りの部分およびその後のくさび18からのサーボ・データを感知するために切り替えられる。

【0021】

図2に移ると、本発明のさまざまな実施形態によるマルチ検出器位置検出回路を含むデータ処理回路200が示されている。データ処理回路200は、アナログ・フロント・エンド回路203を含み、アナログ・フロント・エンド回路203は、受け取られたアナログ入力信号205に対してさまざまなアナログ処理を実行する。図示の実施態様では、アナログ・フロント・エンド回路203は、可変利得増幅器回路210、アナログ・フィルタ回路216、およびアナログ−ディジタル変換器回路220を含む。可変利得増幅器回路210は、利得フィードバック245として示される利得だけアナログ入力信号205を増幅する。可変利得増幅器回路210は、受け取られた入力に可変利得を適用することのできる当技術分野で既知の任意の回路とすることができる。可変利得増幅器回路210は、増幅された信号を増幅済み出力215として供給する。増幅済み出力215は、アナログ・フィルタ回路216に供給され、アナログ・フィルタ回路216では、増幅済み出力215が、たとえば増幅済み出力215内の雑音を減らすためにフィルタリングされる。フィルタリングされた信号は、フィルタリング済み出力218としてアナログ−ディジタル変換器回路220に供給される。アナログ−ディジタル変換器回路220は、サンプリング・クロック255によって制御される位相および周波数でフィルタリング済み出力218をサンプリングして、一連のディジタル・サンプル225を作る。アナログ−ディジタル変換器回路220は、アナログ入力信号を対応する一連のディジタル・サンプルに変換することのできる当技術分野で既知の任意の回路とすることができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまなアナログ・フロント・エンド回路を認めるであろう。

【0022】

ディジタル・サンプル225は、ディジタル有限インパルス応答回路280に供給され、ディジタル有限インパルス応答回路280は、受け取られたサンプルに対してフィルタリング・プロセスを実行して、フィルタリング済み出力285を作る。フィルタリング済み出力285は、クロック同期化回路250に供給され、クロック同期化回路250は、サンプリング・クロック255を受け取られたアナログ入力信号205の位相および周波数に同期させるように動作可能である。クロック同期化回路250は、データ入力に同期することのできる当技術分野で既知の任意の回路とすることができる。本発明のいくつかの実施形態では、クロック同期化回路250は、位相ロック・ループ回路を含む。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまな同期化回路を認めるであろう。フィルタリング済み出力285は、利得調整回路240に供給され、利得調整回路240は、可変利得増幅器回路210に供給される利得フィードバック245として供給される利得調整を作るように動作可能である。利得調整回路240は、利得調整を提供することのできる当技術分野で既知の任意の回路とすることができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまな利得フィードバック回路を認めるであろう。

【0023】

フィルタリング済み出力285は、マルチ検出器パターン検出回路230にも供給される。マルチ検出器パターン検出回路230は、パターン発見出力235を作るためにそれぞれがフィルタリング済み出力285に作用する複数のデータ検出器回路を含む。この複数のデータ検出器回路のそれぞれからの結果が、パターン発見出力235をアサートすべきかどうかを決定するために組み合わされる。本発明の一特定の実施形態では、パターン発見出力235は、パターンが見つかったことを複数のデータ検出器回路のうちの1つが示す時に、必ずアサートされる。その代わりに、本発明の他の実施形態では、パターン発見出力235は、パターンが見つかったことを複数のデータ検出器回路のすべてが示す時に、必ずアサートされる。本発明のさらに他の実施形態では、発見出力235は、パターンが見つかったことを複数のデータ検出器回路のうちの複数またはすべてより少数が示す時に、必ずアサートされる。

【0024】

いくつかの場合に、マルチ検出器パターン検出回路230は、ランダム雑音環境でパターン検出の性能を改善するためにそれぞれが別個のデータ検出アルゴリズム(たとえば、ビタビ・アルゴリズム、2状態アルゴリズム、またはしきい値ベースのアルゴリズム)を実施する複数の検出器回路を使用する。その場合に、受け取られたサンプルの同一のセットが、この複数の検出器回路のそれぞれに供給される。必ずしも、検出器のそれぞれに供給されるデータ・セットの間に、位相シフトまたはオフセットあるのではない。マルチ検出器パターン検出回路230に含まれる検出器は、その互いからの独立のゆえに選択され得る。たとえば、受け取られたサンプル・セット内のピークに頼る、ある検出器が、選択され得、別の検出器が、受け取られたサンプルとターゲットにされるサンプルとの間の誤差を最小にするために動作し、もう1つの検出器が、異なるビット遷移について整合フィルタ出力を最大にする。前述の検出器のそれぞれは、異なる形で失敗する。各検出器が異なって失敗するので、3つすべての検出器がサンプルの同一セットについて同時に失敗する可能性は、低くなる。

【0025】

図3に移ると、本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路300が示されている。マルチ検出器位置検出回路300を、マルチ検出器位置検出回路230の代わりに使用することができる。マルチ検出器位置検出回路300は、それぞれサンプル入力305を介してデータを受け取る2つのデータ検出器回路310および330(データ検出器回路Aおよびデータ検出器回路B)を含む。サンプル入力305は、フィルタリング済み出力285を受け取る。データ検出器回路A 310は、データ検出器回路B 330によって適用されるものとは異なる検出アルゴリズムを適用する。データ検出器回路A 310およびデータ検出器回路B 330のそれぞれは、たとえば、ビタビ・アルゴリズム・データ検出器回路、2状態データ検出器回路、またはしきい値検出器回路とすることができる。一例として、本発明の一実施形態では、データ検出器回路A 310は、ビタビ・アルゴリズム検出器回路であり、データ検出器回路Bは、しきい値検出器回路である。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまなタイプの検出器およびその組合せを認めるであろう。

【0026】

たとえば、データ検出器回路A 310がしきい値検出アルゴリズムを実施する場合に、実施されるしきい値アルゴリズムは、サンプル入力305を介して受け取られる一連のサンプルに適用されて、パターン比較器回路320に供給される一連の2進サンプル315を作る。一例として、一連のサンプルが、+20の値から−20の値に及ぶ場合に、0を超える値は、2進「1」になると定義することができ、0以下の値は、2進「0」になると定義することができる。したがって、一連のサンプル20,10,0,−1,−10,−20,−20,1,10は、しきい値検出器を介して処理された後に、次の2進シリーズ、1,1,0,0,0,0,1,1をもたらすはずである。いくつかの場合に、それを超えるとサンプルが2進「1」として識別され、それ未満ではサンプルが2進「0」として識別されるしきい値を、プログラム可能とすることができ、これによって、DCオフセットまたは他の要因について補償するためのしきい値検出器動作の実施後調整が可能になる。一連の2進値を、その後、さらなる処理に使用することができる。

【0027】

いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化される(wide bi−phase encoded)。その場合に、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号される。たとえば、ワイド・バイフェーズ符号化が、パターン「1100」によって「0」を表すことと、パターン「0011」によって「1」を表すこととを含み、受け取られるサンプルが、20,10,0,−10,−20,0,20,1,−20,−10,5,10,20,3,−20,0である場合には、しきい値検出プロセスは、まず、すべての0以下の値に2進「0」を割り当て、0を超えるすべての値に2進「1」を割り当てて、次のバイフェーズ符号化されたパターン、1100,0011,0011,1100を作る。次に、先行するバイフェーズ符号化されたパターンが復号されて、次の一連の2進値、0,1,1,0を作る。その後、この一連の2進値を、さらなる処理に使用することができる。

【0028】

次に、データ検出器回路A 310によって実施されるしきい値データ検出処理から回復された一連の2進値は、事前定義のまたはプログラム可能なパターン350と比較される。本発明の一特定の実施形態では、パターン350は、セクタ・アドレス・マーク・パターンである。本発明の他の実施形態では、パターン350は、グレイ・コード・パターンである。本明細書で提供される開示に基づいて、当業者は、パターン350として使用できるさまざまなパターンを認めるであろう。パターン350と2進サンプル315との間で一致が見つかる場合には、パターン発見の予備表示325が、コンバイナ回路360に供給される。

【0029】

たとえば、データ検出器回路Bがビタビ・アルゴリズム検出プロセスを実施する場合には、実施されるビタビ・アルゴリズムは、サンプル入力305を介して受け取られる一連のサンプルに適用されて、パターン比較器回路340に供給される一連の2進サンプル335を作る。このビタビ・アルゴリズム検出プロセスは、当技術分野で既知の任意のビタビ・アルゴリズム検出プロセスと一貫するものとすることができる。例のビタビ・アルゴリズムは、J.HagenauerおよびP.Hoeher、「A Viterbi algorithm with soft−decision outputs and its applications」、Proc.IEEE GLOBECOM、47.11〜47.17頁、米国テキサス州ダラス、1989年11月に記載されている。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化されている。その場合には、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号され、この一連の2進値は、さらなる処理のために供給される。ワイド・バイフェーズ符号化が使用されない場合には、ビタビ・アルゴリズム検出プロセスによって供給される2進値が、さらなる処理のために供給される。その後、データ検出器回路B 330によって実施されるしきい値データ検出処理から回復された一連の2進値が、パターン350と比較される。パターン350と2進サンプル335との間で一致が見つかる場合には、パターン発見の予備表示345が、コンバイナ回路360に供給される。

【0030】

データ検出器回路A 310またはデータ検出器回路B 330のいずれかを、2状態データ検出器回路によって置換できることに留意されたい。そのような2状態データ検出器回路は、2010年8月5日にAnnampedu他によって出願された米国仮出願第12/851,475号、名称「Systems and Methods for Sequence Detection in Data Processing」で述べられるものと一貫して動作する。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。

【0031】

予備表示325および予備表示345は、コンバイナ回路360によって組み合わされて、パターン発見出力365を作る。コンバイナ回路360を、次の擬似コードに従って、パターンが見つかったことを予備表示325および予備表示345の一方または両方が示す時に必ずパターン発見出力365がアサートされるように実施することができる。

If (予備表示325がアサートされている OR 予備表示345がアサートされている)

{

パターン発見出力365をアサートする

}

Else

{

パターン発見出力365をデアサートする

}

本発明の他の実施形態では、コンバイナ回路360を、次の擬似コードに従って、パターンが見つかったことを予備表示325と予備表示345との両方が示す時に限ってパターン発見出力365がアサートされるように実施することができる。

If (予備表示325がアサートされている AND 予備表示345がアサートされている)

{

パターン発見出力365をアサートする

}

Else

{

パターン発見出力365をデアサートする

}

【0032】

図4に移ると、本発明の他の実施形態による別のマルチ検出器位置検出回路400が示されている。マルチ検出器位置検出回路400を、マルチ検出器位置検出回路230の代わりに使用することができる。マルチ検出器位置検出回路400は、それぞれサンプル入力405を介してデータを受け取る3つのデータ検出器回路410、430、および470(データ検出器回路A、データ検出器回路B、およびデータ検出器回路C)を含む。サンプル入力405は、フィルタリング済み出力285を受け取る。データ検出器回路A 410は、どちらでもよいがデータ検出器回路B 430によって適用されるものとは異なる検出アルゴリズムを適用し、データ検出器回路B 430は、データ検出器回路C 470によって適用されるものとは異なる検出アルゴリズムを適用する。データ検出器回路A 410、データ検出器回路B 430、およびデータ検出器回路C 470のそれぞれは、たとえば、ビタビ・アルゴリズム・データ検出器回路、2状態データ検出器回路、またはしきい値検出器回路とすることができる。一例として、本発明の一実施形態では、データ検出器回路A 410は、ビタビ・アルゴリズム検出器回路であり、データ検出器回路Bは、しきい値検出器回路であり、データ検出器回路Cは、2状態検出器回路である。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関連して使用できるさまざまなタイプの検出器およびその組合せを認めるであろう。

【0033】

データ検出器A 410は、一連の2進サンプル415をパターン比較器回路420に供給する。次に、データ検出器A 410によって実施されるしきい値データ検出処理から回復された一連の2進データが、事前定義のまたはプログラム可能なパターン450と比較される。本発明の一特定の実施形態では、パターン450は、セクタ・アドレス・マーク・パターンである。本発明の他の実施形態では、パターン450は、グレイ・コード・パターンである。本明細書で提供される開示に基づいて、当業者は、パターン450として使用できるさまざまなパターンを認めるであろう。パターン450と2進サンプル415との間で一致が見つかる場合には、パターン発見の予備表示425が、コンバイナ回路460に供給される。

【0034】

データ検出器B 430は、パターン比較器回路440に一連の2進サンプル435を供給する。次に、データ検出器回路B 430によって実施されるビタビ・アルゴリズム検出処理から回復された一連の2進データが、パターン450と比較される。パターン450と2進サンプル435との間で一致が見つかる場合には、パターン発見の予備表示445が、コンバイナ回路460に供給される。データ検出器C 470は、パターン比較器回路480に一連の2進サンプル475を供給する。次に、データ検出器回路C 470によって実施される2状態アルゴリズム検出処理から回復された一連の2進データが、パターン450と比較される。パターン450と2進サンプル475との間で一致が見つかる場合には、パターン発見の予備表示485が、コンバイナ回路460に供給される。

【0035】

予備表示425、予備表示445、および予備表示485は、コンバイナ回路460によって組み合わされて、パターン発見出力465を作る。コンバイナ回路460を、次の擬似コードに従って、パターンが見つかったことを予備表示425、予備表示445、および予備表示485のうちの1つまたは複数が示す時に必ずパターン発見出力465がアサートされるように実施することができる。

If (予備表示425がアサートされている OR 予備表示445がアサートされている OR 予備表示485がアサートされている)

{

パターン発見出力465をアサートする

}

Else

{

パターン発見出力465をデアサートする

}

本発明の他の実施形態では、コンバイナ回路460を、次の擬似コードに従って、パターンが見つかったことを予備表示425、予備表示445、および予備表示485のすべてが示す時に限ってパターン発見出力465がアサートされるように実施することができる。

If (予備表示425がアサートされている AND 予備表示445がアサートされている AND 予備表示485がアサートされている)

{

パターン発見出力465をアサートする

}

Else

{

パターン発見出力465をデアサートする

}

本発明のさらに他の実施形態では、コンバイナ回路460を、次の擬似コードに従って、パターンが見つかったことを予備表示425、予備表示445、および予備表示485のうちの複数が示す時に必ずパターン発見出力465がアサートされるように実施することができる。

If ((予備表示425がアサートされている AND 予備表示445がアサートされている)

OR

(予備表示425がアサートされている AND 予備表示485がアサートされている)

OR

(予備表示445がアサートされている AND 予備表示485がアサートされている)

)

{

パターン発見出力465をアサートする

}

Else

{

パターン発見出力465をデアサートする

}

【0036】

図5に移ると、本発明のいくつかの実施形態によるマルチ検出器位置検出回路と共に読取チャネル回路510を含むストレージ・システム500が示されている。ストレージ・システム500は、たとえば、ハード・ディスク・ドライブとすることができる。ストレージ・システム500は、前置増幅器570、インターフェース・コントローラ520、ハード・ディスク・コントローラ566、モーター・コントローラ568、スピンドル・モーター572、ディスク・プラッタ578、および読取/書込ヘッド576をも含む。インターフェース・コントローラ520は、ディスク・プラッタ578へ/からのデータのアドレッシングおよびタイミングを制御する。ディスク・プラッタ578上のデータは、読取/書込ヘッド・アセンブリ576がディスク・プラッタ578の上で正しく位置決めされている時にこのアセンブリによって検出できる磁気信号のグループからなる。一実施形態では、ディスク・プラッタ578は、長手記録方式または垂直記録方式のいずれかに従って記録された磁気信号を含む。

【0037】

通常の読取動作では、読取/書込ヘッド・アセンブリ576は、ディスク・プラッタ578上の所望のデータ・トラックの上で、モーター・コントローラ568によって正確に位置決めされる。モーター・コントローラ568は、ハード・ディスク・コントローラ566の指示の下でディスク・プラッタ578上の正しいデータ・トラックに読取/書込ヘッド・アセンブリを移動することによって、ディスク・プラッタ578に関して読取/書込ヘッド・アセンブリ576を正確に位置決めすると同時に、スピンドル・モーター572を駆動する。スピンドル・モーター572は、ディスク・プラッタ578を決定されたスピン・レート(RPM)で回転させる。読取/書込ヘッド・アセンブリ576が、正しいデータ・トラックに隣接して位置決めされた後に、ディスク・プラッタ578がスピンドル・モーター572によって回転されるにつれて、ディスク・プラッタ578上のデータを表す磁気信号が、読取/書込ヘッド・アセンブリ576によって感知される。感知された磁気信号は、ディスク・プラッタ578上の磁気データを表す連続する微細なアナログ信号として供給される。この微細なアナログ信号は、読取/書込ヘッド・アセンブリ576から前置増幅器570を介して読取チャネル・モジュール564に転送される。前置増幅器570は、ディスク・プラッタ578からアクセスされる微細なアナログ信号を増幅するように動作可能である。読取チャネル回路510は、受け取られたアナログ信号を復号し、ディジタル化して、ディスク・プラッタ578に最初に書き込まれた情報を再作成する。このデータは、受け取る回路に読取データ503として供給される。受け取られた情報の復号の一部として、読取チャネル回路510は、データ検出を実行して、データ内のセクタ・アドレス・マークを識別する。このデータ検出プロセスは、マルチ検出器位置検出回路を利用する。そのようなマルチ検出器位置検出回路は、図2、図3、および/または図4に関して上で述べたものに類似する回路網を含むことができ、かつ/あるいは図7に関して下で述べる方法と一貫して動作することができる。書込動作は、実質的に先行する読取動作の逆であり、書込データ501は、読取チャネル回路510に供給される。このデータは、その後、符号化され、ディスク・プラッタ578に書き込まれる。

【0038】

ストレージ・システム500を、たとえばRAID(redundant array of inexpensive disksまたはredundant array of independent disks)ベースのストレージ・システムなどのより大きいストレージ・システムに一体化することができることに留意されたい。ストレージ・システム500のさまざまな機能またはブロックをソフトウェアまたはファームウェアのいずれかで実施でき、他の機能またはブロックがハードウェアで実施されることにも留意されたい。

【0039】

図6に移ると、本発明の1つまたは複数の実施形態によるマルチ検出器位置検出回路と共に受信機620を含む伝送システム600が示されている。伝送システム600は、当技術分野で既知のように符号化された情報を転送媒体630を介して送信するように動作可能である送信機610を含む。符号化されたデータは、転送媒体630から受信機620によって受信される。受信機620は、マルチ検出器位置検出回路を組み込む。そのようなマルチ検出器位置検出回路は、図2、図3、および/または図4に関して上で述べたものに類似する回路網を含むことができ、かつ/あるいは図7に関して下で述べる方法と一貫して動作することができる。

【0040】

図7に移ると、流れ図700は、マルチ検出器手法を使用するデータ処理に関する本発明のさまざまな実施形態による方法を示す。流れ図700に従うと、アナログ信号が受け取られる(ブロック705)。このアナログ信号は、たとえば、記憶媒体に格納された情報を感知することによって、または無線伝送デバイスを介する情報の受信の一部として、導出することができる。本明細書で提供される開示に基づいて、当業者は、アナログ信号のさまざまな源を認めるであろう。可変利得増幅をアナログ信号に適用して、増幅された信号を作る(ブロック710)。この増幅で適用される利得は、利得フィードバックに基づく。可変利得増幅に関する当技術分野で既知の任意の手法を使用することができる。いくつかの場合に、固定増幅プロセスを、可変利得増幅の代わりに使用できることにも留意されたい。アナログ(すなわち、連続時間)フィルタリングを増幅された信号に適用して、フィルタリングされた信号を作る(ブロック715)。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に従って使用できるさまざまなアナログ・フィルタおよび/またはフィルタリング・プロセスを認めるであろう。さらに、いくつかの場合には、フィルタリングは適用されない。フィルタリング済み信号をアナログ−ディジタル変換器回路に供給し、ここで、フィルタリング済み信号は、一連のディジタル・サンプルに変換される(ブロック720)。このディジタル・サンプルは、サンプリング・クロックによって管理される位相および周波数での増幅された出力に対応する。当技術分野で既知の任意のアナログ−ディジタル変換プロセスを使用することができる。

【0041】

供給された一連のディジタル・サンプルを使用して、クロック生成プロセスを実行して、入力データ・ストリームに同期化されたサンプリング・クロックを作成する(ブロック725)。このクロック生成は、入力データ・セットの位相/周波数に同期化されたクロックを生成する、当技術分野で既知の任意のプロセスに従って行うことができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関して使用できるさまざまなクロック生成プロセスを認めるであろう。

【0042】

さらに、可変利得増幅プロセスの利得を制御する利得フィードバックを、供給された一連のディジタル・サンプルを使用して生成する(ブロック730)。この利得フィードバック生成は、可変利得増幅器の利得を確立する、当技術分野で既知の任意のプロセスに従って行うことができる。本明細書で提供される開示に基づいて、当業者は、本発明の異なる実施形態に関して使用できるさまざまな利得フィードバック生成プロセスを認めるであろう。

【0043】

しきい値検出アルゴリズムを一連のディジタル・サンプルに適用して、一連の2進サンプルを作る(ブロック735)。たとえば、ディジタル・サンプルが、+20の値から−20の値に及ぶ場合に、0を超える値は、2進「1」になると定義することができ、0以下の値は、2進「0」になると定義することができる。したがって、一連のディジタル・サンプル20,10,0,−1,−10,−20,−20,1,10は、しきい値検出器を介して処理された後に、次の2進シリーズ、1,1,0,0,0,0,1,1をもたらすはずである。いくつかの場合に、それを超えるとサンプルが2進「1」として識別され、それ未満ではサンプルが2進「0」として識別されるしきい値を、プログラム可能とすることができ、これによって、DCオフセットまたは他の要因について補償するためのしきい値検出器動作の実施後調整が可能になる。一連の2進値を、その後、さらなる処理に使用することができる。

【0044】

いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化される。その場合に、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号される。たとえば、ワイド・バイフェーズ符号化が、パターン「1100」によって「0」を表すことと、パターン「0011」によって「1」1を表すこととを含み、受け取られるサンプルが、20,10,0,−10,−20,0,20,1,−20,−10,5,10,20,3,−20,0である場合には、しきい値検出プロセスは、まず、すべての0以下の値に2進「0」を割り当て、0を超えるすべての値に2進「1」を割り当てて、次のワイド・バイフェーズ符号化されたパターン、1100,0011,0011,1100を作る。次に、先行するバイフェーズ符号化されたパターンが復号されて、次の一連の2進値、0,1,1,0を作る。その後、この一連の2進値を、さらなる処理に使用することができる。

【0045】

次に、しきい値データ検出処理(ブロック735)から回復された一連の2進値を、事前定義のまたはプログラム可能なセクタ・アドレス・マーク・パターンと比較する(ブロック740)。本発明の一特定の実施形態では、セクタ・アドレス・マーク・パターンは、データ・セット内の特定の位置を表す、受け取られたデータ・セット内の同期マークとして働く9ビット・パターンである。セクタ・アドレス・マーク・パターンと受け取られた一連の2進値との間で一致が見つかる場合には(ブロック740)、セクタ・アドレス・マークの第1予備表示が供給される。

【0046】

2状態データ検出を一連のディジタル・サンプルに適用して、一連の2進サンプルを作る(ブロック745)。図8は、本発明の1つまたは複数の実施形態に関連して使用できるデータ検出の例を示す流れ図800である。流れ図800に従うと、4Tサンプルが受け取られたかどうかを判定する(ブロック810)。前に説明したように、4Tサンプルは、ビット遷移ごとに4つのサンプルを暗示する。ビット遷移あたりのより多数またはより少数のサンプルを、本発明の異なる実施形態に関連して使用できることに留意されたい。規定された個数のサンプルを受け取った後に(ブロック810)、受け取られたサンプルは、それぞれの相関器値によって乗算されて、0から0へ、0から1へ、1から0へ、および1から1への遷移のパス値を作る。一例として、4つのサンプルは、51,−35,−102,−112である。以前の0状態値は、「12」であり、以前の1状態値は、「124」である。具体的に言うと、0から1への遷移の枝メトリック(branch metric)を、0から1への遷移に対応する相関器値(「−1 0 1 1」)を使用して計算する(ブロック822)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(−1*51)+(0*−35)+(1*−102)+(1*−112)=−265

同様に、1から1への遷移の枝メトリックを、1から1への遷移に対応する相関器値(「0 −1 0 1」)を使用して計算する(ブロック824)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(0*51)+(−1*−35)+(0*−102)+(1*−112)=−77

1から0への遷移の枝メトリックを、1から0への遷移に対応する相関器値(「1 0 −1 −1」)を使用して計算する(ブロック826)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(1*51)+(0*−35)+(−1*−102)+(−1*−112)=265

さらに、0から0への遷移の枝メトリックを、0から0への遷移に対応する相関器値(「0 1 0 −1」)を使用して計算する(ブロック828)。前述の例の入力を使用すると、この枝メトリックは、次の式に従って計算される。

枝メトリック=(0*51)+(1*−35)+(0*−102)+(−1*−112)=77

【0047】

枝メトリックが使用可能になった後に、枝メトリックを、その枝メトリックがそこから導出された状態の値に加算する。具体的に言うと、状態メトリックを0から1への遷移状態について計算して、第1中間状態を作る(ブロック832)。前述の例の入力を使用すると、第1中間状態値は、次式に従って計算される。

第1中間値=以前の0状態値+0→1枝メトリック=12−265=−253

状態メトリックを1から1への遷移状態について計算して、第2中間状態を作る(ブロック834)。前述の例の入力を使用すると、第2中間状態値は、次式に従って計算される。

第2中間値=以前の1状態値+1→1枝メトリック=124−77=−47

状態メトリックを0から0への遷移状態について計算して、第3中間状態を作る(ブロック836)。前述の例の入力を使用すると、第3中間状態値は、次式に従って計算される。

第3中間値=以前の0状態値+1→0枝メトリック=124+265=389

さらに、状態メトリックを1から0への遷移状態について計算して、第4中間状態を作る(ブロック838)。前述の例の入力を使用すると、第4中間状態値は、次式に従って計算される。

第4中間値=以前の0状態値+0→0枝メトリック=12+77=89

【0048】

第1の生き残っている状態メトリックを、以前に計算された第1中間値と第2中間値との間で選択する(ブロック842)。これは、第1中間値および第2中間値のうちでより大きいものを選択することによって行われ、より大きいものは、この例では「47」である。この値を、次の一連のデータ・サンプルを乗算する際に(たとえば、ブロック222、224、226、228で)使用するために、以前の1状態メトリックとして格納する。さらに、第2の生き残っている状態メトリックを、以前に計算された第3中間値と第4中間値との間で選択する(ブロック844)。これは、第3中間値および第4中間値のうちでより大きいものを選択することによって行われ、より大きいものは、この例では「389」である。この値を、次の一連のデータ・サンプルを乗算する際に(たとえば、ブロック222、224、226、228で)使用するために、以前の0状態メトリックとして格納する。以前に判定された第1の生き残っている中間状態および第2の生き残っている中間状態に基づいて、生き残っている状態メトリックを選択する(ブロック852)。これは、第1の生き残っている中間状態および第2の生き残っている中間状態のうちでより大きいものを選択することによって行われ、より大きいものは、この例では「389」である。この場合の生き残っている状態メトリックは、0状態である。この生き残っている状態メトリックは、検出されたシーケンス内の最も最近のビットに対応し、所望の個数のビットにまたがって検出されたビット・シーケンスを作るために、間に合ってトレース・バックするのに使用される(ブロック862)。これは、生き残っている状態メトリックの値の計算を最終的にもたらしたパス内の以前の状態メトリックを判定することによって行われる。次に、識別されたビット・シーケンスを出力として供給し(ブロック872)、このプロセスを、受け取られる次の一連のディジタル・サンプルについて繰り返す(ブロック810)。2状態アルゴリズムの追加の議論が、2010年8月5日にAnnampedu他によって出願された米国仮出願許第12/851,475号、名称「Systems and Methods for Sequence Detection in Data Processing」に記載されている。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。

【0049】

図7に戻って、最も最近の結果の2進サンプル(ブロック745)を、セクタ・アドレス・マーク・パターンと比較する(ブロック750)。やはり、本発明の一特定の実施形態では、セクタ・アドレス・マーク・パターンは、データ・セット内の特定の位置を表す、受け取られたデータ・セット内の同期マークとして働く9ビット・パターンである。セクタ・アドレス・マーク・パターンと受け取られた一連の2進値との間で一致が見つかる場合には(ブロック750)、セクタ・アドレス・マークの第2予備表示が供給される。

【0050】

ビタビ・アルゴリズム・データ検出プロセスを一連のディジタル・サンプルに適用して、一連の2進サンプルを作る(ブロック755)。このビタビ・アルゴリズム検出プロセスは、当技術分野で既知の任意のビタビ・アルゴリズム検出プロセスと一貫するものとすることができる。例のビタビ・アルゴリズムが、J.HagenauerおよびP.Hoeher、「A Viterbi algorithm with soft−decision outputs and its applications」、Proc.IEEE GLOBECOM、47.11〜47.17頁、米国テキサス州ダラス、1989年11月に記載されている。前述の参考文献の全体が、すべての目的において参照によって本明細書に組み込まれている。いくつかの場合に、受け取られるデータは、ワイド・バイフェーズ符号化されている。その場合に、ワイド・バイフェーズ符号化は、オリジナルの一連の2進値だけを残して復号され、この一連の2進値は、さらなる処理のために供給される。ワイド・バイフェーズ符号化が使用されない場合には、ビタビ・アルゴリズム検出プロセスによって供給される2進値が、さらなる処理のために供給される。

【0051】

その後、ビタビ・アルゴリズム・データ検出処理から回復された一連の2進値(ブロック755)を、事前定義のまたはプログラム可能なセクタ・アドレス・マーク・パターンと比較する(ブロック760)。やはり、本発明の一特定の実施形態では、セクタ・アドレス・マーク・パターンは、データ・セット内の特定の位置を表す、受け取られたデータ・セット内の同期マークとして働く9ビット・パターンである。セクタ・アドレス・マーク・パターンと受け取られた一連の2進値との間で一致が見つかる場合には(ブロック760)、セクタ・アドレス・マークの第3予備表示が供給される。

【0052】

第1予備表示、第2予備表示、および第3予備表示のそれぞれを組み合わせて、セクタ・アドレス・マークをアサートすべきかどうかを判定する(ブロック770)。本発明の一特定の実施形態では、セクタ・アドレス・マークは、第1予備表示、第2予備表示、または第3予備表示のいずれかがアサートされる時に、必ず識別される。その代わりに、本発明の他の実施形態では、セクタ・アドレス・マークは、第1予備表示、第2予備表示、または第3予備表示のうちの複数がアサートされる時に、必ず識別される。本発明のさらに他の実施形態では、セクタ・アドレス・マークは、第1予備表示、第2予備表示、および第3予備表示のすべてがアサートされる時に、必ず識別される。見つかったものとしてセクタ・アドレス・マークを識別すべきかどうかの選択を、第1予備表示、第2予備表示、または第3予備表示のうちの1つだけがアサートされることを要求することによって、セクタ・アドレス・マークの時折の誤識別を犠牲にしてセクタ・アドレス・マークを識別することに向けて偏らせることができる。その代わりに、この選択を、セクタ・アドレス・マークの識別の間でよりバランスのとれたものにすると同時に、第1予備表示、第2予備表示、または第3予備表示のうちの複数のアサートを要求することによって誤識別を防ぐことができる。もう1つの代替案として、この選択を、すべての検出プロセスがセクタ・アドレス・マークを識別することを要求することによって、セクタ・アドレス・マークを見落とすことを犠牲にして、セクタ・アドレス・マークの誤識別を回避することに向けて偏らせることができる。

【0053】

セクタ・アドレス・マークが、第1予備表示、第2予備表示、および/または第3予備表示に基づいて識別される場合には(ブロック780)、SAM発見信号をアサートする(ブロック790)。その代わりに、セクタ・アドレス・マークが、第1予備表示、第2予備表示、および/または第3予備表示に基づいて識別されない場合には(ブロック780)、SAM発見信号は、デアサートされたままになる。

【0054】

上の適用例で述べたさまざまなブロックを、他の機能性と一緒に集積回路内で実施できることに留意されたい。そのような集積回路は、所与のブロック、システム、または回路の機能のすべて、あるいはブロック、システム、または回路のサブセットのみを含むことができる。さらに、ブロック、システム、または回路の要素を、複数の集積回路にまたがって実施することができる。そのような集積回路は、モノリシック集積回路、フリップ・チップ集積回路、マルチチップ・モジュール集積回路、および/または混合信号集積回路を含むがこれに限定はされない当技術分野で既知の任意のタイプの集積回路とすることができる。本明細書で述べたブロック、システム、または回路のさまざまな機能を、ソフトウェアまたはファームウェアのいずれかで実施できることにも留意されたい。その場合に、システム全体、ブロック、または回路を、そのソフトウェア同等物またはファームウェア同等物を使用して実施することができる。他の場合には、所与のシステム、ブロック、または回路の1つの部分をソフトウェアまたはファームウェアで実施することができ、他の部分は、ハードウェアで実施される。

【0055】

結論として、本発明は、データ処理に関する新規のシステム、デバイス、方法、および配置を提供する。本発明の1つまたは複数の実施形態の詳細な説明を上で与えたが、本発明の趣旨から逸脱しない、さまざまな代替形態、修正形態、および同等物が、当業者に明白であろう。たとえば、本発明の1つまたは複数の実施形態を、たとえばテープ・レコーディング・システム、光ディスク・ドライブ、無線システム、およびディジタル加入者回線システムなどのさまざまなデータ・ストレージ・システムおよびディジタル通信システムに適用することができる。さらに、マルチ検出器位置検出回路を、並列に動作する2つまたは3つのデータ検出器回路を有するものとして説明したが、4つ以上のデータ検出器回路を、並列、直列、または並列および直列のある組合せのいずれかで使用できることに留意されたい。さらに、前述の実施形態は、別個のタイプのデータ検出プロセスを使用するものとして説明されたが、たとえば最大事後確率データ検出プロセスなどの他のデータ検出プロセスを、上で説明されたプロセスの代わりにまたはこれに加えて使用できることに留意されたい。したがって、上の説明を、本発明の範囲を限定するものと解釈してはならず、本発明の範囲は、添付の特許請求の範囲によって定義される。

【特許請求の範囲】

【請求項1】

一連のデータ・サンプルを受け取り、第1検出データ出力を供給するように動作可能な第1データ検出器回路と、

前記一連のデータ・サンプルを受け取り、第2検出データ出力を供給するように動作可能な第2データ検出器回路と、

少なくとも部分的に前記第1検出データ出力および前記第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路と

を含むパターン検出回路

を含むデータ処理回路。

【請求項2】

前記結果組合せ回路は、

前記第1検出データ出力をパターンと比較し、前記第1検出データ出力と前記パターンとの間の一致が発生する時に第1予備パターン発見表示をアサートするように動作可能な第1比較器回路と、

前記第2検出データ出力を前記パターンと比較し、前記第2検出データ出力と前記パターンとの間の一致が発生する時に第2予備パターン発見表示をアサートするように動作可能な第2比較器回路と、

少なくとも部分的に前記第1予備パターン発見表示および前記第2予備パターン発見表示に基づいて前記パターン発見出力をアサートするように動作可能なコンバイナ回路と

をさらに含む、請求項1に記載のデータ処理回路。

【請求項3】

前記コンバイナ回路は、前記第1予備パターン発見表示と前記第2予備パターン発見表示との両方がパターン発見を示す時に前記パターン発見出力をアサートするように動作可能である、請求項2に記載のデータ処理回路。

【請求項4】

前記コンバイナ回路は、前記第1予備パターン発見表示および前記第2予備パターン発見表示のうちの1つがパターン発見を示す時に前記パターン発見出力をアサートするように動作可能である、請求項2に記載のデータ処理回路。

【請求項5】

前記第1データ検出器回路は、前記第2データ検出器回路によって適用される第2データ検出アルゴリズムとは異なる第1データ検出アルゴリズムを適用する、請求項1に記載のデータ処理回路。

【請求項6】

前記第1データ検出器回路は、しきい値検出器回路、2状態検出器回路、およびビタビ・アルゴリズム検出器回路からなる群から選択され、

前記第2データ検出器回路は、しきい値検出器回路、2状態検出器回路、およびビタビ・アルゴリズム検出器回路からなる群から選択される

請求項5に記載のデータ処理回路。

【請求項7】

前記第1データ検出器回路は、前記第2データ検出器回路と一致して並列に前記一連のデータ・サンプルの同一のサブセットに作用する、請求項1に記載のデータ処理回路。

【請求項8】

前記パターン検出回路は、

前記一連のデータ・サンプルを受け取り、第3検出データ出力を供給するように動作可能な第3データ検出器回路

をさらに含み、前記結果組合せ回路は、少なくとも部分的に前記第1検出データ出力、前記第2検出データ出力、および前記第3検出データ出力に基づいて前記パターン発見出力をアサートするように動作可能である

請求項1に記載のデータ処理回路。

【請求項9】

前記第1データ検出器回路は、ビタビ・アルゴリズム検出器回路であり、前記第2データ検出器回路は、しきい値検出器回路であり、前記第3データ検出器回路は、2状態検出器回路である、請求項8に記載のデータ処理回路。

【請求項10】

前記データ処理回路は、ストレージ・デバイスおよびデータ受信機からなる群から選択される電子デバイスの一部として実施される、請求項1に記載のデータ処理回路。

【請求項11】

前記データ処理回路は、集積回路として実施される、請求項1に記載のデータ処理回路。

【請求項12】

前記データ処理回路は、

アナログ信号を受け取り、一連のサンプルを供給するように動作可能なアナログ・フロント・エンド回路であって、前記一連のデータ・サンプルは、前記一連のサンプルからの派生物である、アナログ・フロント・エンド回路

をさらに含む、請求項1に記載のデータ処理回路。

【請求項13】

前記アナログ・フロント・エンド回路は、

前記アナログ信号を受け取り、増幅済み出力を供給するように動作可能な増幅器回路と、

前記増幅済み出力を受け取り、前記増幅済み出力の前記派生物に対応する前記一連のサンプルを供給するように動作可能なアナログ−ディジタル変換器回路と

を含む、請求項12に記載のデータ処理回路。

【請求項14】

前記一連のデータ・サンプルは、前記一連のサンプルの前記派生物と同一であり、前記増幅済み出力の前記派生物は、前記増幅済み出力と同一である、請求項13に記載のデータ処理回路。

【請求項15】

一連のデータ・サンプルを受け取ることと、

第1検出出力を作るために前記一連のデータ・サンプルに対して第1データ検出を実行することと、

第2検出出力を作るために前記一連のデータ・サンプルに対して第2データ検出を実行することであって、前記第2データ検出は、前記第1データ検出とは異なる、実行することと、

少なくとも部分的に前記第1検出出力および前記第2検出出力に基づいてパターン発見信号をアサートすることと

を含む、パターン検出の方法。

【請求項16】

前記第1データ検出は、しきい値データ検出、2状態データ検出、およびビタビ・アルゴリズム・データ検出からなる群から選択され、

前記第2データ検出は、しきい値データ検出、2状態データ検出、およびビタビ・アルゴリズム・データ検出からなる群から選択される

請求項15に記載の方法。

【請求項17】

前記方法は、

第3検出出力を作るために前記一連のデータ・サンプルに対して第3データ検出を実行することであって、前記第3データ検出は、前記第1データ検出および前記第2データ検出とは異なる、実行することと、

少なくとも部分的に前記第1検出出力、前記第2検出出力、および前記第3検出出力に基づいて前記パターン発見信号をアサートすることと

をさらに含む、請求項15に記載の方法。

【請求項18】

前記第1データ検出は、ビタビ・アルゴリズム・データ検出であり、

前記第2データ検出は、しきい値データ検出であり、

前記第3データ検出は、2状態データ検出である

請求項17に記載の方法。

【請求項19】

前記第1データ検出、前記第2データ検出、および前記第3データ検出は、並列に実行される、請求項17に記載の方法。

【請求項20】

前記第1データ検出および第2データ検出は、並列に実行される、請求項15に記載の方法。

【請求項21】

情報を含む記憶媒体と、

前記記憶媒体に関連して配置された読取ヘッドであって、前記読取ヘッドは、前記情報を感知し、対応するアナログ信号を供給するように動作可能である、読取ヘッドと、

前記アナログ信号を受け取り、一連のサンプルを供給するように動作可能なアナログ・フロント・エンド回路であって、

前記アナログ信号を受け取り、増幅済み出力を供給するように動作可能な増幅器回路と、

前記増幅済み出力を受け取り、前記増幅済み出力の派生物に対応する前記一連のサンプルを供給するように動作可能なアナログ−ディジタル変換器回路と、

を含むアナログ・フロント・エンド回路と、

パターン検出回路であって、

一連のデータ・サンプルを受け取り、第1検出データ出力を供給するように動作可能なビタビ・アルゴリズム検出器回路と、

前記一連のデータ・サンプルを受け取り、第2検出データ出力を供給するように動作可能なしきい値検出器回路と、

前記一連のデータ・サンプルを受け取り、第3検出データ出力を供給するように動作可能な2状態検出器回路と、

少なくとも部分的に前記第1検出データ出力、前記第2検出データ出力、および前記第3検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路と

を含むパターン検出回路と

を含むストレージ・デバイス。

【請求項1】

一連のデータ・サンプルを受け取り、第1検出データ出力を供給するように動作可能な第1データ検出器回路と、

前記一連のデータ・サンプルを受け取り、第2検出データ出力を供給するように動作可能な第2データ検出器回路と、

少なくとも部分的に前記第1検出データ出力および前記第2検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路と

を含むパターン検出回路

を含むデータ処理回路。

【請求項2】

前記結果組合せ回路は、

前記第1検出データ出力をパターンと比較し、前記第1検出データ出力と前記パターンとの間の一致が発生する時に第1予備パターン発見表示をアサートするように動作可能な第1比較器回路と、

前記第2検出データ出力を前記パターンと比較し、前記第2検出データ出力と前記パターンとの間の一致が発生する時に第2予備パターン発見表示をアサートするように動作可能な第2比較器回路と、

少なくとも部分的に前記第1予備パターン発見表示および前記第2予備パターン発見表示に基づいて前記パターン発見出力をアサートするように動作可能なコンバイナ回路と

をさらに含む、請求項1に記載のデータ処理回路。

【請求項3】

前記コンバイナ回路は、前記第1予備パターン発見表示と前記第2予備パターン発見表示との両方がパターン発見を示す時に前記パターン発見出力をアサートするように動作可能である、請求項2に記載のデータ処理回路。

【請求項4】

前記コンバイナ回路は、前記第1予備パターン発見表示および前記第2予備パターン発見表示のうちの1つがパターン発見を示す時に前記パターン発見出力をアサートするように動作可能である、請求項2に記載のデータ処理回路。

【請求項5】

前記第1データ検出器回路は、前記第2データ検出器回路によって適用される第2データ検出アルゴリズムとは異なる第1データ検出アルゴリズムを適用する、請求項1に記載のデータ処理回路。

【請求項6】

前記第1データ検出器回路は、しきい値検出器回路、2状態検出器回路、およびビタビ・アルゴリズム検出器回路からなる群から選択され、

前記第2データ検出器回路は、しきい値検出器回路、2状態検出器回路、およびビタビ・アルゴリズム検出器回路からなる群から選択される

請求項5に記載のデータ処理回路。

【請求項7】

前記第1データ検出器回路は、前記第2データ検出器回路と一致して並列に前記一連のデータ・サンプルの同一のサブセットに作用する、請求項1に記載のデータ処理回路。

【請求項8】

前記パターン検出回路は、

前記一連のデータ・サンプルを受け取り、第3検出データ出力を供給するように動作可能な第3データ検出器回路

をさらに含み、前記結果組合せ回路は、少なくとも部分的に前記第1検出データ出力、前記第2検出データ出力、および前記第3検出データ出力に基づいて前記パターン発見出力をアサートするように動作可能である

請求項1に記載のデータ処理回路。

【請求項9】

前記第1データ検出器回路は、ビタビ・アルゴリズム検出器回路であり、前記第2データ検出器回路は、しきい値検出器回路であり、前記第3データ検出器回路は、2状態検出器回路である、請求項8に記載のデータ処理回路。

【請求項10】

前記データ処理回路は、ストレージ・デバイスおよびデータ受信機からなる群から選択される電子デバイスの一部として実施される、請求項1に記載のデータ処理回路。

【請求項11】

前記データ処理回路は、集積回路として実施される、請求項1に記載のデータ処理回路。

【請求項12】

前記データ処理回路は、

アナログ信号を受け取り、一連のサンプルを供給するように動作可能なアナログ・フロント・エンド回路であって、前記一連のデータ・サンプルは、前記一連のサンプルからの派生物である、アナログ・フロント・エンド回路

をさらに含む、請求項1に記載のデータ処理回路。

【請求項13】

前記アナログ・フロント・エンド回路は、

前記アナログ信号を受け取り、増幅済み出力を供給するように動作可能な増幅器回路と、

前記増幅済み出力を受け取り、前記増幅済み出力の前記派生物に対応する前記一連のサンプルを供給するように動作可能なアナログ−ディジタル変換器回路と

を含む、請求項12に記載のデータ処理回路。

【請求項14】

前記一連のデータ・サンプルは、前記一連のサンプルの前記派生物と同一であり、前記増幅済み出力の前記派生物は、前記増幅済み出力と同一である、請求項13に記載のデータ処理回路。

【請求項15】

一連のデータ・サンプルを受け取ることと、

第1検出出力を作るために前記一連のデータ・サンプルに対して第1データ検出を実行することと、

第2検出出力を作るために前記一連のデータ・サンプルに対して第2データ検出を実行することであって、前記第2データ検出は、前記第1データ検出とは異なる、実行することと、

少なくとも部分的に前記第1検出出力および前記第2検出出力に基づいてパターン発見信号をアサートすることと

を含む、パターン検出の方法。

【請求項16】

前記第1データ検出は、しきい値データ検出、2状態データ検出、およびビタビ・アルゴリズム・データ検出からなる群から選択され、

前記第2データ検出は、しきい値データ検出、2状態データ検出、およびビタビ・アルゴリズム・データ検出からなる群から選択される

請求項15に記載の方法。

【請求項17】

前記方法は、

第3検出出力を作るために前記一連のデータ・サンプルに対して第3データ検出を実行することであって、前記第3データ検出は、前記第1データ検出および前記第2データ検出とは異なる、実行することと、

少なくとも部分的に前記第1検出出力、前記第2検出出力、および前記第3検出出力に基づいて前記パターン発見信号をアサートすることと

をさらに含む、請求項15に記載の方法。

【請求項18】

前記第1データ検出は、ビタビ・アルゴリズム・データ検出であり、

前記第2データ検出は、しきい値データ検出であり、

前記第3データ検出は、2状態データ検出である

請求項17に記載の方法。

【請求項19】

前記第1データ検出、前記第2データ検出、および前記第3データ検出は、並列に実行される、請求項17に記載の方法。

【請求項20】

前記第1データ検出および第2データ検出は、並列に実行される、請求項15に記載の方法。

【請求項21】

情報を含む記憶媒体と、

前記記憶媒体に関連して配置された読取ヘッドであって、前記読取ヘッドは、前記情報を感知し、対応するアナログ信号を供給するように動作可能である、読取ヘッドと、

前記アナログ信号を受け取り、一連のサンプルを供給するように動作可能なアナログ・フロント・エンド回路であって、

前記アナログ信号を受け取り、増幅済み出力を供給するように動作可能な増幅器回路と、

前記増幅済み出力を受け取り、前記増幅済み出力の派生物に対応する前記一連のサンプルを供給するように動作可能なアナログ−ディジタル変換器回路と、

を含むアナログ・フロント・エンド回路と、

パターン検出回路であって、

一連のデータ・サンプルを受け取り、第1検出データ出力を供給するように動作可能なビタビ・アルゴリズム検出器回路と、

前記一連のデータ・サンプルを受け取り、第2検出データ出力を供給するように動作可能なしきい値検出器回路と、

前記一連のデータ・サンプルを受け取り、第3検出データ出力を供給するように動作可能な2状態検出器回路と、

少なくとも部分的に前記第1検出データ出力、前記第2検出データ出力、および前記第3検出データ出力に基づいてパターン発見出力をアサートするように動作可能な結果組合せ回路と

を含むパターン検出回路と

を含むストレージ・デバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−155827(P2012−155827A)

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願番号】特願2011−106759(P2011−106759)

【出願日】平成23年5月12日(2011.5.12)

【出願人】(508243639)エルエスアイ コーポレーション (124)

【Fターム(参考)】

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願日】平成23年5月12日(2011.5.12)

【出願人】(508243639)エルエスアイ コーポレーション (124)

【Fターム(参考)】

[ Back to top ]