ダイレクト・デジタル・シンセサイザ回路

【課題】 正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路を提供する。

【解決手段】 周波数設定データをデータ分離部1で上位ビットと下位ビットに分離し、位相内挿補正値出力部10が下位ビットの累積によるオーバーフローで補正パラメータ1を出力し、下位ビットの積分値から得られた補正値を補正パラメータ2として出力し、上位ビットのデータに補正パラメータ1を正弦波ROMアドレス生成部2で加算して積分して正弦波ROMテーブル5で対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部6で直交成分に補正パラメータ2を乗算し、同相成分との差分を演算することで、位相補正を行うDDS回路である。

【解決手段】 周波数設定データをデータ分離部1で上位ビットと下位ビットに分離し、位相内挿補正値出力部10が下位ビットの累積によるオーバーフローで補正パラメータ1を出力し、下位ビットの積分値から得られた補正値を補正パラメータ2として出力し、上位ビットのデータに補正パラメータ1を正弦波ROMアドレス生成部2で加算して積分して正弦波ROMテーブル5で対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部6で直交成分に補正パラメータ2を乗算し、同相成分との差分を演算することで、位相補正を行うDDS回路である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、無線通信の送受信装置に用いられるダイレクト・デジタル・シンセサイザ回路(DDS回路又は直接デジタル周波数シンセサイザ)に係り、特に、メモリ規模を増大させることなく位相誤差を低減できるDDS回路に関する。

【背景技術】

【0002】

DDS回路は、加算器とラッチ回路でアキュムレータを構成し、動作周波数(クロック)に同期して周波数設定値(周波数設定データ)を累積し、周波数設定値に比例した速度のノコギリ波形のデジタルデータが得られ、当該データは出力波形の位相に相当するので、波形データを記憶する正弦波ROMテーブルから対応する波形が得られるものである。

【0003】

[従来のDDS回路:図6]

従来のDDS回路について図6を参照しながら説明する。図6は、従来のDDS回路の構成ブロック図である。

従来のDDS回路は、図6に示すように、加算器103と、ラッチ回路(D)104と、乗算器110と、正弦波ROM(Read Only Memory)テーブル105と、D/A(Digital/Analogue)コンバータ107と、フィルタ108とを有している。

尚、加算器103、ラッチ回路104、乗算器110でアキュムレータを構成している。

【0004】

[従来のDDS回路の動作]

従来のDDS回路では、周波数設定データ(FSET)が加算器103に入力され、加算器103ではラッチ回路104からの出力と加算してラッチ回路104に出力する。

ラッチ回路104は、動作周波数fsでデータのラッチを行い、出力を加算器103と乗算器110に出力する。

【0005】

乗算器110では、ラッチ回路104からの出力に1/2^n(2-n)を乗算して丸め処理を行い、乗算器110からのデータに基づき正弦波ROMテーブル105を参照して正弦波データをD/Aコンバータ107に出力する。

【0006】

D/Aコンバータ107では、正弦波データをデジタルからアナログに変換してフィルタ108に出力する。フィルタ108では、アナログ信号を平滑化して出力する。

このように、従来のDDS回路は動作するようになっている。

【0007】

[従来のDDS回路における周波数設定精度]

図6において、動作周波数fs、所望周波数設定精度をkとした場合、周波数設定データFSETの必要ビット数Aは、以下のようになる。

A=log2(fs/k)

例えば、fs=200MHz、k=0.1Hzとした場合、

A=log2(200e6/0.1)=約30.9 つまり、31ビット必要となる。

【0008】

しかし、上記例の仕様で実際の回路を実現する場合、正弦波ROMテーブル105のデータ数が31bit相当(=2,147,483,648)必要になるため、回路規模が増大することになる。

【0009】

図6では、現実的な回路規模に抑えるために、乗算器110で2-nを乗算して丸め処理を行い、Bbit相当にビット数を削減した場合、所望の周波数設定精度が得られないものとなっていた。

【0010】

[関連技術]

尚、関連する先行技術として、特開平06−252645号公報「直接デジタル周波数シンセサイザ」(出願人:日本電気株式会社/特許文献1)、特開平11−031924号公報「直接デジタル周波数シンセサイザ」(出願人:三菱電機株式会社/特許文献2)、特表2000−506713号公報「所望の関数に応答して信号振幅を発生する方法及びコンバータ」(出願人:ノキア テレコミュニカシオンス オサケ ユキチュア/特許文献3)、特開平03−088504号公報「任意波形発生器」(出願人:横河電機株式会社/特許文献4)、特開平05−291829号公報「任意波形発生器」(出願人:ソニー・テクトロニクス株式会社/特許文献5)、特開2002−280838号公報「ダイレクト・デジタル・シンセサイザ」(出願人:安藤電気株式会社/特許文献6)がある。

【0011】

特許文献1には、DDSにおいて、位相アキュムレータからの位相データの上位ビットにより正弦波信号及びコサイン波信号を生成し、位相データの下位ビットにより位相誤差信号を生成し、乗算器でコサイン波信号と位相誤差信号とを乗算してスプリアスキャンセル信号を合成し、減算器で正弦波信号からスプリアスキャンセル信号を減算してスプリアスのない正弦波信号を得ることが示されている。

【0012】

特許文献2には、DDSにおいて、位相アキュムレータからの位相データの上位ビットに基づきメモリから正弦波の振幅データを出力し、当該上位ビットから余弦波を演算し、下位ビットから2πθ2を演算して乗算し、振幅補正値を出力し、正弦波の振幅データに振幅補正値を加算することが示されている。

【0013】

特許文献3には、コンバータにおいて、分割手段がビットの変数データを上位ビットと下位ビットに分割し、上位ビットに基づいて直線の傾斜と定数項をメモリから出力し、下位ビットと定数項により原点を通過する直線に対応する振幅データを出力し、当該振幅データに定数項を加算して丸め処理を行うことが示されている。

【0014】

特許文献4には、任意波形発生器において、DA変換器3からの出力に対して誤差補正テーブル11に基づいて演算・制御回路10が波形メモリ1の波形データを補正することが示されている。

【0015】

特許文献5には、任意波形発生器において、歪検出手段が、測定波形データと基準波形データとを比較し、振幅歪及び微分係数歪を検出し、補正手段が、検出された歪に応じて波形メモリに記憶された波形データを補正することが示されている。

【0016】

特許文献6には、ダイレクト・デジタル・シンセサイザにおいて、位相角−振幅変換テーブルからの振幅デジタル値を上位ビットと下位ビットに分割し、それぞれをDA変換して減衰させ、振幅デジタル値をDA変換する第1のDA変換手段の出力に加算することが示されている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開平06−252645号公報

【特許文献2】特開平11−031924号公報

【特許文献3】特表2000−506713号公報

【特許文献4】特開平03−088504号公報

【特許文献5】特開平05−291829号公報

【特許文献6】特開2002−280838号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

しかしながら、従来のDDS回路では、所望の周波数設定精度を要求した場合、正弦波ROMテーブルのデータ数が増大し、回路規模が増大するという問題点があり、また、回路規模を抑えると所望の周波数設定精度が得られないという問題点があった。

【0019】

[位相誤差:図7]

ここで、従来のDDS回路において、丸め処理における位相誤差について図7を参照しながら説明する。図7は、位相誤差を説明するための図である。

DDS回路で生成する正弦波を複素座標上の円運動で考えた場合、図7に示すように、bit数Aは「・」点となるが、bit数Bに丸めると「・」を「○」で囲った点のポイントしか動かず、間のポイントとの差が位相誤差となってしまう。

【0020】

また、特許文献1では、演算式に適合するようスプリアスキャンセル信号をアナログ処理で生成するものであるから、設定周波数が変更になると、レベル調整等をやり直す必要があり、手間が掛かるものとなっていた。

【0021】

また、特許文献2では、cos(2πθ1)と2πθ2を演算手段で実現してメモリ容量を小さくするものではあるが、そのために演算処理の構成が複雑になってしまうものであった。

特許文献3も、メモリサイズを小さくするものではあるが、演算処理の構成が複雑になってしまうものであった。

【0022】

また、特許文献4は、メモリサイズを小さくするものではなく、演算・制御回路が波形メモリにおける波形データを補正するものであるから、波形メモリから波形データを出力する処理が複雑になってしまうものであった。

また、特許文献5も、メモリサイズを小さくするものではなく、補正手段が、検出された歪に応じて波形メモリに記憶された波形データを補正するものであるから、

【0023】

また、特許文献6は、位相角−振幅変換テーブルからの振幅デジタル値を上位ビットと下位ビットに分割しているものの、振幅デジタル値のDA変換出力を上位ビットと下位ビットの減衰値を加算しているに過ぎず、周波数設定データを上位ビットと下位ビットに分割するものではない。

【0024】

本発明は上記実情に鑑みて為されたもので、正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路を提供することを目的とする。

【課題を解決するための手段】

【0025】

上記従来例の問題点を解決するための本発明は、ダイレクト・デジタル・シンセサイザ回路であって、周波数設定データを上位ビットと下位ビットに分離する分離部と、下位ビットを累積してオーバーフローにより第1の補正パラメータを出力すると共に、累積した下位ビットを基に得られた補正値を第2の補正パラメータとして出力する位相内挿補正値出力部と、上位ビットに第1の補正パラメータを加算し、当該加算した値を積分する正弦波アドレス生成部と、正弦波の波形データを記憶し、正弦波アドレス生成部からの出力データに対応した波形データの同相成分と直交成分を出力する正弦波テーブルと、直交成分に第2の補正パラメータを乗算し、同相成分と当該乗算された値との差分値を演算する位相内挿補正部と、位相内挿補正部で演算された差分値をデジタルからアナログに変換する第1のD/Aコンバータと、第1のD/Aコンバータから出力されるアナログ信号を平滑化する第1のフィルタとを有することを特徴とする。

【0026】

本発明は、上記ダイレクト・デジタル・シンセサイザ回路において、位相内挿補正部が、正弦波テーブルから出力される同相成分と位相内挿補正値出力部からの第2の補正パラメータとを乗算し、正弦波テーブルから出力される直交成分と当該乗算された値との加算値を演算するものであり、位相内挿補正部で演算された加算値をデジタルからアナログに変換する第2のD/Aコンバータと、第2のD/Aコンバータから出力されるアナログ信号を平滑化する第2のフィルタとを有することを特徴とする。

【0027】

本発明は、上記ダイレクト・デジタル・シンセサイザ回路において、位相内挿補正値出力部が、下位ビットのデータを累積加算する積分を行う積分器と、積分器におけるオーバーフローを検出し、第1の補正パラメータを正弦波アドレス生成部に出力する飽和検出器と、積分器からの出力に対応付けて第2の補正パラメータを記憶し、積分器で積分された値が入力されると対応する第2の補正パラメータを出力する補正テーブルとを有することを特徴とする。

【0028】

本発明は、上記ダイレクト・デジタル・シンセサイザ回路において、位相内挿補正値出力部の補正テーブルに記憶される第2の補正パラメータは、上位ビットにおける位相角に下位ビットの位相角を近似させるための値としたことを特徴とする。

【発明の効果】

【0029】

本発明によれば、分離部が、周波数設定データを上位ビットと下位ビットに分離し、位相内挿補正値出力部が、下位ビットを累積してオーバーフローにより第1の補正パラメータを出力すると共に、累積した下位ビットを基に得られた補正値を第2の補正パラメータとして出力し、正弦波アドレス生成部が、上位ビットに第1の補正パラメータを加算し、当該加算した値を積分し、正弦波テーブルが、正弦波の波形データを記憶し、正弦波アドレス生成部からの出力データに対応した波形データの同相成分と直交成分を出力し、位相内挿補正部が、直交成分に第2の補正パラメータを乗算し、同相成分と当該乗算された値との差分値を演算し、第1のD/Aコンバータが、位相内挿補正部で演算された差分値をデジタルからアナログに変換し、第1のフィルタが、第1のD/Aコンバータから出力されるアナログ信号を平滑化するダイレクト・デジタル・シンセサイザ回路としているので、正弦波テーブルのメモリ規模を増大させることなく、位相補正を行うことで位相誤差を低減できる効果がある。

【図面の簡単な説明】

【0030】

【図1】本発明の実施の形態に係るDDS回路の構成ブロック図である。

【図2】位相内挿補正値出力部の具体的構成図である。

【図3】位相補正の概要を説明する図である。

【図4】位相補正の動作1を説明する図である。

【図5】位相補正の動作2を説明する図である。

【図6】従来のDDS回路の構成ブロック図である。

【図7】位相誤差を説明するための図である。

【発明を実施するための形態】

【0031】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係るダイレクト・デジタル・シンセサイザ回路(DDS回路)は、周波数設定データをデータ分離部で上位ビットと下位ビットに分離し、位相内挿補正値出力部で下位ビットの累積によるオーバーフローにより第1の補正パラメータを出力し、下位ビットの累積加算から得られた補正値を第2の補正パラメータとして出力し、上位ビットのデータに第1の補正パラメータを正弦波ROMアドレス生成部で加算して積分し、正弦波ROMテーブルのアドレスを生成し、正弦波ROMテーブルで対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部で直交成分に第2の補正パラメータを乗算し、同相成分との差分値を演算することで、位相補正を行うものであり、正弦波ROMテーブルのメモリ容量を増大させることなく、位相誤差を低減できるものである。

【0032】

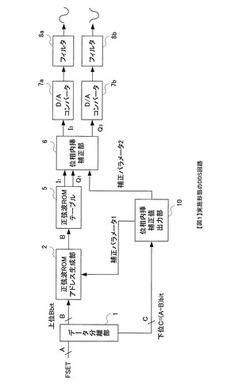

[DDS回路の構成:図1]

本発明の実施の形態に係るDDS回路について図1を参照しながら説明する。図1は、本発明の実施の形態に係るDDS回路の構成ブロック図である。

本発明の実施の形態に係るDDS回路(本DDS回路)は、図1に示すように、データ分離部1と、正弦波ROMアドレス生成部2と、正弦波ROMテーブル5と、位相内挿補正部6と、D/Aコンバータ7a,7bと、フィルタ8a,8bと、位相内挿補正値出力部10とを基本的に有している。

尚、正弦波ROMアドレス生成部2の一部は、アキュムレータを構成している。

【0033】

[DDS回路の各部]

本DDS回路の各部について具体的に説明する。

データ分離部1は、周波数設定データFSET(Aビット)を入力し、上位ビット(Bビット)と下位ビット(Cビット)に分離し、上位ビットを正弦波ROMアドレス生成部2に出力し、下位ビットを位相内挿補正値出力部10に出力する。

従って、下位Cビット=(A−B)ビットとなる。

【0034】

正弦波ROMアドレス生成部2は、データ分離部1から入力される上位ビットと位相内挿補正値出力部10から入力される補正パラメータ1とを加算する加算器と、その加算器からの出力を積分する積分器とを有している。

正弦波ROMアドレス生成部2から出力されるデータは、Bビットであり、正弦波ROMテーブル5に出力される。

【0035】

正弦波ROMテーブル5は、正弦波ROMアドレス生成部2から入力される周波数データに対して正弦波の値をテーブルとして記憶するメモリであり、入力される周波数データに対応した正弦波の値を同相成分I1と直交成分Q1で位相内挿補正部6に出力する。

【0036】

位相内挿補正部6は、正弦波ROMテーブル5から入力される同相成分I1と直交成分Q1と、位相内挿補正値出力部10から入力される補正パラメータ2とを用いて、位相内挿の補正を行い、位相誤差を低減し、補正された同相成分I3をD/Aコンバータ7aに、補正された直交成分Q3をD/Aコンバータ7bに出力する。

位相内挿補正部6の構成及び動作については後述する。

【0037】

D/Aコンバータ7aは、位相内挿補正部6から入力される補正された同相成分I3をデジタルデータからアナログ信号に変換してフィルタ8aに出力する。

D/Aコンバータ7bは、位相内挿補正部6から入力される補正された直交成分Q3をデジタルデータからアナログ信号に変換してフィルタ8bに出力する。

フィルタ8aは、D/Aコンバータ7aから入力されたアナログ信号を平滑化して出力する。

フィルタ8bは、D/Aコンバータ7bから入力されたアナログ信号を平滑化して出力する。

そして、フィルタ8aから出力された同相成分のアナログ波形とフィルタ8bから出力された直交成分のアナログ波形から直交検波を行うようになっている。

【0038】

位相内挿補正値出力部10は、データ分離部1からの下位ビットを入力し、位相内挿の補正を行うための補正値を補正パラメータ1,2として算出し、補正パラメータ1を正弦波ROMアドレス生成部2に、補正パラメータ2を位相内挿補正部6に出力する。

位相内挿補正値出力部10の具体的な構成及び動作については後述する。

【0039】

[位相内挿補正値出力部10:図2]

次に、位相内挿補正値出力部10について図2を参照しながら説明する。図2は、位相内挿補正値出力部の具体的構成図である。

位相内挿補正値出力部10は、図2に示すように、積分器11と、飽和検出器12と、補正ROMテーブル13とを備えている。

【0040】

[位相内挿補正値出力部10の各部]

積分器11は、データ分離部1からの下位ビットを入力し、入力データを積分して飽和検出器12と補正ROMテーブル13に出力する。

積分器11は、動作周波数fsで動作するデジタル演算器であり、初期値から累積加算する積分を行ってオーバーフローすると、また初期値から累積加算の積分を行う処理を繰返すものである。

【0041】

飽和検出器12は、積分器11からの出力を監視し、下位ビットのオーバーフロー(飽和)を検出すると、補正パラメータ1を正弦波ROMアドレス生成部2に出力する。

補正パラメータ1は、データ分離部1からの上位ビットの値に対して加算される「1」の値となるものである。例えば、上位ビットが14ビットであるとすると、14ビットのデータで「1」を表すデータが補正パラメータ1ということになる。

【0042】

補正ROMテーブル13は、積分器11から出力されるデジタルの積分値をアドレスとして、当該アドレスに対応する補正パラメータ2の値(補正値)が格納されている。尚、補正値は、下位ビットの積分値に応じて予め適正な補正値が演算又はシミュレーション等で求められて設定されている。

尚、補正ROMテーブル13のアドレスは、係数Yとすると、Y×(積分値)/(飽和積分値)で求められる。飽和積分値は、積分器11がオーバーフローする場合の値である。

【0043】

補正ROMテーブル13の具体的動作は、積分器11からの値を入力し、当該値をアドレスとして対応する補正パラメータ2を読み出し、位相内挿補正部6に補正パラメータ2を出力する。

この補正パラメータ2は、上位ビットにおける位相角θに下位ビットの位相角を近似させるための値となっている。

従って、補正パラメータ2は、下位ビットから算出される補正値の直交成分Q(Q2)を出力するものとなっている。

また、位相内挿補正値出力部10において、補正ROMテーブル13の代わりに、加算器、ラッチ回路、乗算器等を用いて演算処理にて対応する直交成分(Q2)を出力させるようにしてもよい。

【0044】

[位相内挿補正部6]

次に、位相内挿補正部6について説明する。

位相内挿補正部6は、複数の乗算器と、複数の加算器とを備えている。

位相内挿補正部6は、正弦波ROMテーブル5から出力された直交成分Q1と位相内挿補正値出力部10から出力された補正パラメータ2(Q2)を乗算器で乗算し、正弦波ROMテーブル5から出力された同相成分I1と当該乗算されたデータとの差分を加算器(減算器)で演算して同相成分I3として出力するものである。

上記加算器は、同相成分I1のデータをプラス(+)とし、乗算器からのデータを符号反転してマイナス(−)とし、両者を加算することで、差分を演算している。

【0045】

また、位相内挿補正部6は、正弦波ROMテーブル5から出力された同相成分I1と位相内挿補正値出力部10から出力された補正パラメータ2(Q2)を乗算器で乗算し、当該乗算器からの出力と正弦波ROMテーブル5から出力された直交成分Q1とを加算器で加算して直交成分Q3として出力する。

【0046】

[位相補正:図3]

次に、位相補正の概要について図3を参照しながら説明する。図3は、位相補正の概要を説明する図である。

正弦波を複素座標上の円運動で表現した場合、図3に示した3本の矢印の内、本当は角度(θ0)だけ移動させた中央の矢印が本来求めるポイントとすると、従来のDDS回路では、例えば、角度(θa)までしか移動できない下側の矢印のポイントに来てしまうものである。

【0047】

本DDS回路では、差分の角度(θ0−θa)分だけ追加で回転させて所望の角度(θ0)に持っていくことで、つまり、中央の矢印のポイントに移動させることで、所望のポイントに持っていく位相補正を行うものとなっている。

【0048】

[位相補正の動作1,2:図4,5]

更に、位相補正の具体的な動作について図4、図5を参照しながら説明する。図4は、位相補正の動作1を説明する図であり、図5は、位相補正の動作2を説明する図である。

[位相補正の動作1:図4]

図4に、例えば、上位ビットの同相成分I1と直交成分Q1の回転ベクトル[I1,Q1](DDS生成ベクトル)を示し、下位ビットの同相成分I2と直交成分Q2の補正用回転ベクトル[I2,Q2]を示している。

そして、DDS生成ベクトル[I1,Q1]を補正用回転ベクトル[I2,Q2]を用いて補正した位相補正後ベクトル[I3,Q3]が示されている。

【0049】

ここで、DDS生成ベクトル[I1,Q1]と補正用回転ベクトル[I2,Q2]は、以下の式で表される。

[I1,Q1]=(I1+jQ1)

[I2,Q2]=(I2+jQ2)

【0050】

更に、位相補正後ベクトル[I3,Q3]は、DDS生成ベクトルと補正用回転ベクトルを乗算したものであるから、

[I3,Q3]=(I1+jQ1)*(I2+jQ2)

=(I1・I2−Q1・Q2)+j(I2・Q1+I1・Q2)

【0051】

最終的には、位相補正後ベクトル[I3,Q3]の実数部分(I1・I2−Q1・Q2)の演算結果を最終信号I3として出力することで、位相補正されたデータが得られるものである。

また、位相補正後ベクトル[I3,Q3]の虚数部分(I2・Q1+I1・Q2)の演算結果を最終信号Q3として出力することで、位相補正されたデータが得られるものである。

【0052】

[位相補正の動作2:図5]

上位ビット(Bビット)における位相角θは、θ=2π/2Bとなる。

下位ビット(Cビット)については、図5に示すように、2π>>θの場合であるので、XとYの辺を備えた三角形とみなすことができ、tanθ=Y/Xで表すことができる。

Y=2Cとすれば、X=2C/tanθに近似できる。

【0053】

上述したI3の式は、I2=X(一定値:Constant値)=1とおくと、

I3=I1・I2−Q1・Q2

=I1−Q1・Q2

よって、上記Y(=Q2)のみの補正パラメータとして生成することで補正処理を行うことが可能となるものである。

【0054】

また、上述したQ3の式は、I2=X=1とおくと、

Q3=I2・Q1+I1・Q2

=Q1+I1・Q2

よって、上記Y(=Q2)のみの補正パラメータとして生成することで補正処理を行うことが可能となるものである。

【0055】

上記の式の演算を位相内挿補正部6の回路で実現している。

補正パラメータ2がQ2に相当し、I1とQ1は正弦波ROMテーブル5から出力されたデータであり、(Q1・Q2)の乗算が乗算器で実現され、I1−(Q1・Q2)の演算が加算器で実現されるものである。

また、(I1・Q2)の乗算が乗算器で実現され、Q1+(I1・Q2)の演算が加算器で実現されるものである。

【0056】

[実施の形態の効果]

本DDS回路によれば、周波数設定データをデータ分離部1で上位ビットと下位ビットに分離し、位相内挿補正値出力部10が下位ビットの累積によるオーバーフローで補正パラメータ1を出力し、下位ビットの積分値から得られた補正値を補正パラメータ2として出力し、上位ビットのデータに補正パラメータ1を加算してアキュムレータで累積して正弦波ROMテーブル5で対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部6で直交成分に補正パラメータ2を乗算し、それと同相成分との差分値を演算することで、位相補正を行うようにしているので、正弦波ROMテーブル5のメモリ容量を増大させることなく、位相誤差を低減できる効果がある。

【0057】

また、本DDS回路をスイープ周波数ジェネレータに適用することも可能である。

【0058】

尚、請求項に記載の構成と実施形態の構成との対応を説明すると、正弦波アドレス生成部は正弦波ROMアドレス生成部2に、正弦波テーブルは正弦波ROMテーブル5に、補正テーブルは補正ROMテーブル13に相当している。

【産業上の利用可能性】

【0059】

本発明は、正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路に好適である。

【符号の説明】

【0060】

1…データ分離部、 2…正弦波ROMアドレス生成部、 5…正弦波ROMテーブル、 6…位相内挿補正部、 7a,7b…D/Aコンバータ、 8a,8b…フィルタ、 10…位相内挿補正値出力部、 11…積分器、 12…飽和検出器、 13…補正ROMテーブル、 103…加算器、 104…ラッチ回路、 105…正弦波ROMテーブル、 107…D/Aコンバータ、 108…フィルタ、 110…乗算器

【技術分野】

【0001】

本発明は、無線通信の送受信装置に用いられるダイレクト・デジタル・シンセサイザ回路(DDS回路又は直接デジタル周波数シンセサイザ)に係り、特に、メモリ規模を増大させることなく位相誤差を低減できるDDS回路に関する。

【背景技術】

【0002】

DDS回路は、加算器とラッチ回路でアキュムレータを構成し、動作周波数(クロック)に同期して周波数設定値(周波数設定データ)を累積し、周波数設定値に比例した速度のノコギリ波形のデジタルデータが得られ、当該データは出力波形の位相に相当するので、波形データを記憶する正弦波ROMテーブルから対応する波形が得られるものである。

【0003】

[従来のDDS回路:図6]

従来のDDS回路について図6を参照しながら説明する。図6は、従来のDDS回路の構成ブロック図である。

従来のDDS回路は、図6に示すように、加算器103と、ラッチ回路(D)104と、乗算器110と、正弦波ROM(Read Only Memory)テーブル105と、D/A(Digital/Analogue)コンバータ107と、フィルタ108とを有している。

尚、加算器103、ラッチ回路104、乗算器110でアキュムレータを構成している。

【0004】

[従来のDDS回路の動作]

従来のDDS回路では、周波数設定データ(FSET)が加算器103に入力され、加算器103ではラッチ回路104からの出力と加算してラッチ回路104に出力する。

ラッチ回路104は、動作周波数fsでデータのラッチを行い、出力を加算器103と乗算器110に出力する。

【0005】

乗算器110では、ラッチ回路104からの出力に1/2^n(2-n)を乗算して丸め処理を行い、乗算器110からのデータに基づき正弦波ROMテーブル105を参照して正弦波データをD/Aコンバータ107に出力する。

【0006】

D/Aコンバータ107では、正弦波データをデジタルからアナログに変換してフィルタ108に出力する。フィルタ108では、アナログ信号を平滑化して出力する。

このように、従来のDDS回路は動作するようになっている。

【0007】

[従来のDDS回路における周波数設定精度]

図6において、動作周波数fs、所望周波数設定精度をkとした場合、周波数設定データFSETの必要ビット数Aは、以下のようになる。

A=log2(fs/k)

例えば、fs=200MHz、k=0.1Hzとした場合、

A=log2(200e6/0.1)=約30.9 つまり、31ビット必要となる。

【0008】

しかし、上記例の仕様で実際の回路を実現する場合、正弦波ROMテーブル105のデータ数が31bit相当(=2,147,483,648)必要になるため、回路規模が増大することになる。

【0009】

図6では、現実的な回路規模に抑えるために、乗算器110で2-nを乗算して丸め処理を行い、Bbit相当にビット数を削減した場合、所望の周波数設定精度が得られないものとなっていた。

【0010】

[関連技術]

尚、関連する先行技術として、特開平06−252645号公報「直接デジタル周波数シンセサイザ」(出願人:日本電気株式会社/特許文献1)、特開平11−031924号公報「直接デジタル周波数シンセサイザ」(出願人:三菱電機株式会社/特許文献2)、特表2000−506713号公報「所望の関数に応答して信号振幅を発生する方法及びコンバータ」(出願人:ノキア テレコミュニカシオンス オサケ ユキチュア/特許文献3)、特開平03−088504号公報「任意波形発生器」(出願人:横河電機株式会社/特許文献4)、特開平05−291829号公報「任意波形発生器」(出願人:ソニー・テクトロニクス株式会社/特許文献5)、特開2002−280838号公報「ダイレクト・デジタル・シンセサイザ」(出願人:安藤電気株式会社/特許文献6)がある。

【0011】

特許文献1には、DDSにおいて、位相アキュムレータからの位相データの上位ビットにより正弦波信号及びコサイン波信号を生成し、位相データの下位ビットにより位相誤差信号を生成し、乗算器でコサイン波信号と位相誤差信号とを乗算してスプリアスキャンセル信号を合成し、減算器で正弦波信号からスプリアスキャンセル信号を減算してスプリアスのない正弦波信号を得ることが示されている。

【0012】

特許文献2には、DDSにおいて、位相アキュムレータからの位相データの上位ビットに基づきメモリから正弦波の振幅データを出力し、当該上位ビットから余弦波を演算し、下位ビットから2πθ2を演算して乗算し、振幅補正値を出力し、正弦波の振幅データに振幅補正値を加算することが示されている。

【0013】

特許文献3には、コンバータにおいて、分割手段がビットの変数データを上位ビットと下位ビットに分割し、上位ビットに基づいて直線の傾斜と定数項をメモリから出力し、下位ビットと定数項により原点を通過する直線に対応する振幅データを出力し、当該振幅データに定数項を加算して丸め処理を行うことが示されている。

【0014】

特許文献4には、任意波形発生器において、DA変換器3からの出力に対して誤差補正テーブル11に基づいて演算・制御回路10が波形メモリ1の波形データを補正することが示されている。

【0015】

特許文献5には、任意波形発生器において、歪検出手段が、測定波形データと基準波形データとを比較し、振幅歪及び微分係数歪を検出し、補正手段が、検出された歪に応じて波形メモリに記憶された波形データを補正することが示されている。

【0016】

特許文献6には、ダイレクト・デジタル・シンセサイザにおいて、位相角−振幅変換テーブルからの振幅デジタル値を上位ビットと下位ビットに分割し、それぞれをDA変換して減衰させ、振幅デジタル値をDA変換する第1のDA変換手段の出力に加算することが示されている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開平06−252645号公報

【特許文献2】特開平11−031924号公報

【特許文献3】特表2000−506713号公報

【特許文献4】特開平03−088504号公報

【特許文献5】特開平05−291829号公報

【特許文献6】特開2002−280838号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

しかしながら、従来のDDS回路では、所望の周波数設定精度を要求した場合、正弦波ROMテーブルのデータ数が増大し、回路規模が増大するという問題点があり、また、回路規模を抑えると所望の周波数設定精度が得られないという問題点があった。

【0019】

[位相誤差:図7]

ここで、従来のDDS回路において、丸め処理における位相誤差について図7を参照しながら説明する。図7は、位相誤差を説明するための図である。

DDS回路で生成する正弦波を複素座標上の円運動で考えた場合、図7に示すように、bit数Aは「・」点となるが、bit数Bに丸めると「・」を「○」で囲った点のポイントしか動かず、間のポイントとの差が位相誤差となってしまう。

【0020】

また、特許文献1では、演算式に適合するようスプリアスキャンセル信号をアナログ処理で生成するものであるから、設定周波数が変更になると、レベル調整等をやり直す必要があり、手間が掛かるものとなっていた。

【0021】

また、特許文献2では、cos(2πθ1)と2πθ2を演算手段で実現してメモリ容量を小さくするものではあるが、そのために演算処理の構成が複雑になってしまうものであった。

特許文献3も、メモリサイズを小さくするものではあるが、演算処理の構成が複雑になってしまうものであった。

【0022】

また、特許文献4は、メモリサイズを小さくするものではなく、演算・制御回路が波形メモリにおける波形データを補正するものであるから、波形メモリから波形データを出力する処理が複雑になってしまうものであった。

また、特許文献5も、メモリサイズを小さくするものではなく、補正手段が、検出された歪に応じて波形メモリに記憶された波形データを補正するものであるから、

【0023】

また、特許文献6は、位相角−振幅変換テーブルからの振幅デジタル値を上位ビットと下位ビットに分割しているものの、振幅デジタル値のDA変換出力を上位ビットと下位ビットの減衰値を加算しているに過ぎず、周波数設定データを上位ビットと下位ビットに分割するものではない。

【0024】

本発明は上記実情に鑑みて為されたもので、正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路を提供することを目的とする。

【課題を解決するための手段】

【0025】

上記従来例の問題点を解決するための本発明は、ダイレクト・デジタル・シンセサイザ回路であって、周波数設定データを上位ビットと下位ビットに分離する分離部と、下位ビットを累積してオーバーフローにより第1の補正パラメータを出力すると共に、累積した下位ビットを基に得られた補正値を第2の補正パラメータとして出力する位相内挿補正値出力部と、上位ビットに第1の補正パラメータを加算し、当該加算した値を積分する正弦波アドレス生成部と、正弦波の波形データを記憶し、正弦波アドレス生成部からの出力データに対応した波形データの同相成分と直交成分を出力する正弦波テーブルと、直交成分に第2の補正パラメータを乗算し、同相成分と当該乗算された値との差分値を演算する位相内挿補正部と、位相内挿補正部で演算された差分値をデジタルからアナログに変換する第1のD/Aコンバータと、第1のD/Aコンバータから出力されるアナログ信号を平滑化する第1のフィルタとを有することを特徴とする。

【0026】

本発明は、上記ダイレクト・デジタル・シンセサイザ回路において、位相内挿補正部が、正弦波テーブルから出力される同相成分と位相内挿補正値出力部からの第2の補正パラメータとを乗算し、正弦波テーブルから出力される直交成分と当該乗算された値との加算値を演算するものであり、位相内挿補正部で演算された加算値をデジタルからアナログに変換する第2のD/Aコンバータと、第2のD/Aコンバータから出力されるアナログ信号を平滑化する第2のフィルタとを有することを特徴とする。

【0027】

本発明は、上記ダイレクト・デジタル・シンセサイザ回路において、位相内挿補正値出力部が、下位ビットのデータを累積加算する積分を行う積分器と、積分器におけるオーバーフローを検出し、第1の補正パラメータを正弦波アドレス生成部に出力する飽和検出器と、積分器からの出力に対応付けて第2の補正パラメータを記憶し、積分器で積分された値が入力されると対応する第2の補正パラメータを出力する補正テーブルとを有することを特徴とする。

【0028】

本発明は、上記ダイレクト・デジタル・シンセサイザ回路において、位相内挿補正値出力部の補正テーブルに記憶される第2の補正パラメータは、上位ビットにおける位相角に下位ビットの位相角を近似させるための値としたことを特徴とする。

【発明の効果】

【0029】

本発明によれば、分離部が、周波数設定データを上位ビットと下位ビットに分離し、位相内挿補正値出力部が、下位ビットを累積してオーバーフローにより第1の補正パラメータを出力すると共に、累積した下位ビットを基に得られた補正値を第2の補正パラメータとして出力し、正弦波アドレス生成部が、上位ビットに第1の補正パラメータを加算し、当該加算した値を積分し、正弦波テーブルが、正弦波の波形データを記憶し、正弦波アドレス生成部からの出力データに対応した波形データの同相成分と直交成分を出力し、位相内挿補正部が、直交成分に第2の補正パラメータを乗算し、同相成分と当該乗算された値との差分値を演算し、第1のD/Aコンバータが、位相内挿補正部で演算された差分値をデジタルからアナログに変換し、第1のフィルタが、第1のD/Aコンバータから出力されるアナログ信号を平滑化するダイレクト・デジタル・シンセサイザ回路としているので、正弦波テーブルのメモリ規模を増大させることなく、位相補正を行うことで位相誤差を低減できる効果がある。

【図面の簡単な説明】

【0030】

【図1】本発明の実施の形態に係るDDS回路の構成ブロック図である。

【図2】位相内挿補正値出力部の具体的構成図である。

【図3】位相補正の概要を説明する図である。

【図4】位相補正の動作1を説明する図である。

【図5】位相補正の動作2を説明する図である。

【図6】従来のDDS回路の構成ブロック図である。

【図7】位相誤差を説明するための図である。

【発明を実施するための形態】

【0031】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係るダイレクト・デジタル・シンセサイザ回路(DDS回路)は、周波数設定データをデータ分離部で上位ビットと下位ビットに分離し、位相内挿補正値出力部で下位ビットの累積によるオーバーフローにより第1の補正パラメータを出力し、下位ビットの累積加算から得られた補正値を第2の補正パラメータとして出力し、上位ビットのデータに第1の補正パラメータを正弦波ROMアドレス生成部で加算して積分し、正弦波ROMテーブルのアドレスを生成し、正弦波ROMテーブルで対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部で直交成分に第2の補正パラメータを乗算し、同相成分との差分値を演算することで、位相補正を行うものであり、正弦波ROMテーブルのメモリ容量を増大させることなく、位相誤差を低減できるものである。

【0032】

[DDS回路の構成:図1]

本発明の実施の形態に係るDDS回路について図1を参照しながら説明する。図1は、本発明の実施の形態に係るDDS回路の構成ブロック図である。

本発明の実施の形態に係るDDS回路(本DDS回路)は、図1に示すように、データ分離部1と、正弦波ROMアドレス生成部2と、正弦波ROMテーブル5と、位相内挿補正部6と、D/Aコンバータ7a,7bと、フィルタ8a,8bと、位相内挿補正値出力部10とを基本的に有している。

尚、正弦波ROMアドレス生成部2の一部は、アキュムレータを構成している。

【0033】

[DDS回路の各部]

本DDS回路の各部について具体的に説明する。

データ分離部1は、周波数設定データFSET(Aビット)を入力し、上位ビット(Bビット)と下位ビット(Cビット)に分離し、上位ビットを正弦波ROMアドレス生成部2に出力し、下位ビットを位相内挿補正値出力部10に出力する。

従って、下位Cビット=(A−B)ビットとなる。

【0034】

正弦波ROMアドレス生成部2は、データ分離部1から入力される上位ビットと位相内挿補正値出力部10から入力される補正パラメータ1とを加算する加算器と、その加算器からの出力を積分する積分器とを有している。

正弦波ROMアドレス生成部2から出力されるデータは、Bビットであり、正弦波ROMテーブル5に出力される。

【0035】

正弦波ROMテーブル5は、正弦波ROMアドレス生成部2から入力される周波数データに対して正弦波の値をテーブルとして記憶するメモリであり、入力される周波数データに対応した正弦波の値を同相成分I1と直交成分Q1で位相内挿補正部6に出力する。

【0036】

位相内挿補正部6は、正弦波ROMテーブル5から入力される同相成分I1と直交成分Q1と、位相内挿補正値出力部10から入力される補正パラメータ2とを用いて、位相内挿の補正を行い、位相誤差を低減し、補正された同相成分I3をD/Aコンバータ7aに、補正された直交成分Q3をD/Aコンバータ7bに出力する。

位相内挿補正部6の構成及び動作については後述する。

【0037】

D/Aコンバータ7aは、位相内挿補正部6から入力される補正された同相成分I3をデジタルデータからアナログ信号に変換してフィルタ8aに出力する。

D/Aコンバータ7bは、位相内挿補正部6から入力される補正された直交成分Q3をデジタルデータからアナログ信号に変換してフィルタ8bに出力する。

フィルタ8aは、D/Aコンバータ7aから入力されたアナログ信号を平滑化して出力する。

フィルタ8bは、D/Aコンバータ7bから入力されたアナログ信号を平滑化して出力する。

そして、フィルタ8aから出力された同相成分のアナログ波形とフィルタ8bから出力された直交成分のアナログ波形から直交検波を行うようになっている。

【0038】

位相内挿補正値出力部10は、データ分離部1からの下位ビットを入力し、位相内挿の補正を行うための補正値を補正パラメータ1,2として算出し、補正パラメータ1を正弦波ROMアドレス生成部2に、補正パラメータ2を位相内挿補正部6に出力する。

位相内挿補正値出力部10の具体的な構成及び動作については後述する。

【0039】

[位相内挿補正値出力部10:図2]

次に、位相内挿補正値出力部10について図2を参照しながら説明する。図2は、位相内挿補正値出力部の具体的構成図である。

位相内挿補正値出力部10は、図2に示すように、積分器11と、飽和検出器12と、補正ROMテーブル13とを備えている。

【0040】

[位相内挿補正値出力部10の各部]

積分器11は、データ分離部1からの下位ビットを入力し、入力データを積分して飽和検出器12と補正ROMテーブル13に出力する。

積分器11は、動作周波数fsで動作するデジタル演算器であり、初期値から累積加算する積分を行ってオーバーフローすると、また初期値から累積加算の積分を行う処理を繰返すものである。

【0041】

飽和検出器12は、積分器11からの出力を監視し、下位ビットのオーバーフロー(飽和)を検出すると、補正パラメータ1を正弦波ROMアドレス生成部2に出力する。

補正パラメータ1は、データ分離部1からの上位ビットの値に対して加算される「1」の値となるものである。例えば、上位ビットが14ビットであるとすると、14ビットのデータで「1」を表すデータが補正パラメータ1ということになる。

【0042】

補正ROMテーブル13は、積分器11から出力されるデジタルの積分値をアドレスとして、当該アドレスに対応する補正パラメータ2の値(補正値)が格納されている。尚、補正値は、下位ビットの積分値に応じて予め適正な補正値が演算又はシミュレーション等で求められて設定されている。

尚、補正ROMテーブル13のアドレスは、係数Yとすると、Y×(積分値)/(飽和積分値)で求められる。飽和積分値は、積分器11がオーバーフローする場合の値である。

【0043】

補正ROMテーブル13の具体的動作は、積分器11からの値を入力し、当該値をアドレスとして対応する補正パラメータ2を読み出し、位相内挿補正部6に補正パラメータ2を出力する。

この補正パラメータ2は、上位ビットにおける位相角θに下位ビットの位相角を近似させるための値となっている。

従って、補正パラメータ2は、下位ビットから算出される補正値の直交成分Q(Q2)を出力するものとなっている。

また、位相内挿補正値出力部10において、補正ROMテーブル13の代わりに、加算器、ラッチ回路、乗算器等を用いて演算処理にて対応する直交成分(Q2)を出力させるようにしてもよい。

【0044】

[位相内挿補正部6]

次に、位相内挿補正部6について説明する。

位相内挿補正部6は、複数の乗算器と、複数の加算器とを備えている。

位相内挿補正部6は、正弦波ROMテーブル5から出力された直交成分Q1と位相内挿補正値出力部10から出力された補正パラメータ2(Q2)を乗算器で乗算し、正弦波ROMテーブル5から出力された同相成分I1と当該乗算されたデータとの差分を加算器(減算器)で演算して同相成分I3として出力するものである。

上記加算器は、同相成分I1のデータをプラス(+)とし、乗算器からのデータを符号反転してマイナス(−)とし、両者を加算することで、差分を演算している。

【0045】

また、位相内挿補正部6は、正弦波ROMテーブル5から出力された同相成分I1と位相内挿補正値出力部10から出力された補正パラメータ2(Q2)を乗算器で乗算し、当該乗算器からの出力と正弦波ROMテーブル5から出力された直交成分Q1とを加算器で加算して直交成分Q3として出力する。

【0046】

[位相補正:図3]

次に、位相補正の概要について図3を参照しながら説明する。図3は、位相補正の概要を説明する図である。

正弦波を複素座標上の円運動で表現した場合、図3に示した3本の矢印の内、本当は角度(θ0)だけ移動させた中央の矢印が本来求めるポイントとすると、従来のDDS回路では、例えば、角度(θa)までしか移動できない下側の矢印のポイントに来てしまうものである。

【0047】

本DDS回路では、差分の角度(θ0−θa)分だけ追加で回転させて所望の角度(θ0)に持っていくことで、つまり、中央の矢印のポイントに移動させることで、所望のポイントに持っていく位相補正を行うものとなっている。

【0048】

[位相補正の動作1,2:図4,5]

更に、位相補正の具体的な動作について図4、図5を参照しながら説明する。図4は、位相補正の動作1を説明する図であり、図5は、位相補正の動作2を説明する図である。

[位相補正の動作1:図4]

図4に、例えば、上位ビットの同相成分I1と直交成分Q1の回転ベクトル[I1,Q1](DDS生成ベクトル)を示し、下位ビットの同相成分I2と直交成分Q2の補正用回転ベクトル[I2,Q2]を示している。

そして、DDS生成ベクトル[I1,Q1]を補正用回転ベクトル[I2,Q2]を用いて補正した位相補正後ベクトル[I3,Q3]が示されている。

【0049】

ここで、DDS生成ベクトル[I1,Q1]と補正用回転ベクトル[I2,Q2]は、以下の式で表される。

[I1,Q1]=(I1+jQ1)

[I2,Q2]=(I2+jQ2)

【0050】

更に、位相補正後ベクトル[I3,Q3]は、DDS生成ベクトルと補正用回転ベクトルを乗算したものであるから、

[I3,Q3]=(I1+jQ1)*(I2+jQ2)

=(I1・I2−Q1・Q2)+j(I2・Q1+I1・Q2)

【0051】

最終的には、位相補正後ベクトル[I3,Q3]の実数部分(I1・I2−Q1・Q2)の演算結果を最終信号I3として出力することで、位相補正されたデータが得られるものである。

また、位相補正後ベクトル[I3,Q3]の虚数部分(I2・Q1+I1・Q2)の演算結果を最終信号Q3として出力することで、位相補正されたデータが得られるものである。

【0052】

[位相補正の動作2:図5]

上位ビット(Bビット)における位相角θは、θ=2π/2Bとなる。

下位ビット(Cビット)については、図5に示すように、2π>>θの場合であるので、XとYの辺を備えた三角形とみなすことができ、tanθ=Y/Xで表すことができる。

Y=2Cとすれば、X=2C/tanθに近似できる。

【0053】

上述したI3の式は、I2=X(一定値:Constant値)=1とおくと、

I3=I1・I2−Q1・Q2

=I1−Q1・Q2

よって、上記Y(=Q2)のみの補正パラメータとして生成することで補正処理を行うことが可能となるものである。

【0054】

また、上述したQ3の式は、I2=X=1とおくと、

Q3=I2・Q1+I1・Q2

=Q1+I1・Q2

よって、上記Y(=Q2)のみの補正パラメータとして生成することで補正処理を行うことが可能となるものである。

【0055】

上記の式の演算を位相内挿補正部6の回路で実現している。

補正パラメータ2がQ2に相当し、I1とQ1は正弦波ROMテーブル5から出力されたデータであり、(Q1・Q2)の乗算が乗算器で実現され、I1−(Q1・Q2)の演算が加算器で実現されるものである。

また、(I1・Q2)の乗算が乗算器で実現され、Q1+(I1・Q2)の演算が加算器で実現されるものである。

【0056】

[実施の形態の効果]

本DDS回路によれば、周波数設定データをデータ分離部1で上位ビットと下位ビットに分離し、位相内挿補正値出力部10が下位ビットの累積によるオーバーフローで補正パラメータ1を出力し、下位ビットの積分値から得られた補正値を補正パラメータ2として出力し、上位ビットのデータに補正パラメータ1を加算してアキュムレータで累積して正弦波ROMテーブル5で対応する正弦波の同相成分と直交成分を出力し、位相内挿補正部6で直交成分に補正パラメータ2を乗算し、それと同相成分との差分値を演算することで、位相補正を行うようにしているので、正弦波ROMテーブル5のメモリ容量を増大させることなく、位相誤差を低減できる効果がある。

【0057】

また、本DDS回路をスイープ周波数ジェネレータに適用することも可能である。

【0058】

尚、請求項に記載の構成と実施形態の構成との対応を説明すると、正弦波アドレス生成部は正弦波ROMアドレス生成部2に、正弦波テーブルは正弦波ROMテーブル5に、補正テーブルは補正ROMテーブル13に相当している。

【産業上の利用可能性】

【0059】

本発明は、正弦波ROMテーブルのメモリ規模を増大させることなく、位相誤差を低減できるダイレクト・デジタル・シンセサイザ回路に好適である。

【符号の説明】

【0060】

1…データ分離部、 2…正弦波ROMアドレス生成部、 5…正弦波ROMテーブル、 6…位相内挿補正部、 7a,7b…D/Aコンバータ、 8a,8b…フィルタ、 10…位相内挿補正値出力部、 11…積分器、 12…飽和検出器、 13…補正ROMテーブル、 103…加算器、 104…ラッチ回路、 105…正弦波ROMテーブル、 107…D/Aコンバータ、 108…フィルタ、 110…乗算器

【特許請求の範囲】

【請求項1】

ダイレクト・デジタル・シンセサイザ回路であって、

周波数設定データを上位ビットと下位ビットに分離する分離部と、

前記下位ビットを累積してオーバーフローにより第1の補正パラメータを出力すると共に、前記累積した下位ビットを基に得られた補正値を第2の補正パラメータとして出力する位相内挿補正値出力部と、

前記上位ビットに前記第1の補正パラメータを加算し、当該加算した値を積分する正弦波アドレス生成部と、

正弦波の波形データを記憶し、前記正弦波アドレス生成部からの出力データに対応した波形データの同相成分と直交成分を出力する正弦波テーブルと、

前記直交成分に前記第2の補正パラメータを乗算し、前記同相成分と当該乗算された値との差分値を演算する位相内挿補正部と、

前記位相内挿補正部で演算された差分値をデジタルからアナログに変換する第1のD/Aコンバータと、

前記第1のD/Aコンバータから出力されるアナログ信号を平滑化する第1のフィルタとを有することを特徴とするダイレクト・デジタル・シンセサイザ回路。

【請求項2】

位相内挿補正部は、正弦波テーブルから出力される同相成分と位相内挿補正値出力部からの第2の補正パラメータとを乗算し、前記正弦波テーブルから出力される直交成分と当該乗算された値との加算値を演算するものであり、

前記位相内挿補正部で演算された加算値をデジタルからアナログに変換する第2のD/Aコンバータと、

前記第2のD/Aコンバータから出力されるアナログ信号を平滑化する第2のフィルタとを有することを特徴とする請求項1記載のダイレクト・デジタル・シンセサイザ回路。

【請求項3】

位相内挿補正値出力部は、下位ビットのデータを累積加算する積分を行う積分器と、

前記積分器におけるオーバーフローを検出し、第1の補正パラメータを正弦波アドレス生成部に出力する飽和検出器と、

前記積分器からの出力に対応付けて第2の補正パラメータを記憶し、前記積分器で積分された値が入力されると対応する第2の補正パラメータを出力する補正テーブルとを有することを特徴とする請求項1又は2記載のダイレクト・デジタル・シンセサイザ回路。

【請求項4】

位相内挿補正値出力部の補正テーブルに記憶される第2の補正パラメータは、上位ビットにおける位相角に下位ビットの位相角を近似させるための値としたことを特徴とする請求項3記載のダイレクト・デジタル・シンセサイザ回路。

【請求項1】

ダイレクト・デジタル・シンセサイザ回路であって、

周波数設定データを上位ビットと下位ビットに分離する分離部と、

前記下位ビットを累積してオーバーフローにより第1の補正パラメータを出力すると共に、前記累積した下位ビットを基に得られた補正値を第2の補正パラメータとして出力する位相内挿補正値出力部と、

前記上位ビットに前記第1の補正パラメータを加算し、当該加算した値を積分する正弦波アドレス生成部と、

正弦波の波形データを記憶し、前記正弦波アドレス生成部からの出力データに対応した波形データの同相成分と直交成分を出力する正弦波テーブルと、

前記直交成分に前記第2の補正パラメータを乗算し、前記同相成分と当該乗算された値との差分値を演算する位相内挿補正部と、

前記位相内挿補正部で演算された差分値をデジタルからアナログに変換する第1のD/Aコンバータと、

前記第1のD/Aコンバータから出力されるアナログ信号を平滑化する第1のフィルタとを有することを特徴とするダイレクト・デジタル・シンセサイザ回路。

【請求項2】

位相内挿補正部は、正弦波テーブルから出力される同相成分と位相内挿補正値出力部からの第2の補正パラメータとを乗算し、前記正弦波テーブルから出力される直交成分と当該乗算された値との加算値を演算するものであり、

前記位相内挿補正部で演算された加算値をデジタルからアナログに変換する第2のD/Aコンバータと、

前記第2のD/Aコンバータから出力されるアナログ信号を平滑化する第2のフィルタとを有することを特徴とする請求項1記載のダイレクト・デジタル・シンセサイザ回路。

【請求項3】

位相内挿補正値出力部は、下位ビットのデータを累積加算する積分を行う積分器と、

前記積分器におけるオーバーフローを検出し、第1の補正パラメータを正弦波アドレス生成部に出力する飽和検出器と、

前記積分器からの出力に対応付けて第2の補正パラメータを記憶し、前記積分器で積分された値が入力されると対応する第2の補正パラメータを出力する補正テーブルとを有することを特徴とする請求項1又は2記載のダイレクト・デジタル・シンセサイザ回路。

【請求項4】

位相内挿補正値出力部の補正テーブルに記憶される第2の補正パラメータは、上位ビットにおける位相角に下位ビットの位相角を近似させるための値としたことを特徴とする請求項3記載のダイレクト・デジタル・シンセサイザ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−172199(P2011−172199A)

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願番号】特願2010−60497(P2010−60497)

【出願日】平成22年3月17日(2010.3.17)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願日】平成22年3月17日(2010.3.17)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]