ダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法

【課題】複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータを提供することである。

【解決手段】本発明にかかるダウンコンバータは、ダウンコンバータ回路1、2と、水平偏波信号が供給される増幅器LNA1と、垂直偏波信号が供給される増幅器LNA2とを少なくとも備える増幅部3とを有する。ダウンコンバータ回路1が備える制御回路19は、Tone/Pola信号が省電力モードを示す場合、局部発振器16および周波数変換部17を非動作状態とし、且つLNA1に電源が供給されるようにLNAバイアス回路18を制御する。

【解決手段】本発明にかかるダウンコンバータは、ダウンコンバータ回路1、2と、水平偏波信号が供給される増幅器LNA1と、垂直偏波信号が供給される増幅器LNA2とを少なくとも備える増幅部3とを有する。ダウンコンバータ回路1が備える制御回路19は、Tone/Pola信号が省電力モードを示す場合、局部発振器16および周波数変換部17を非動作状態とし、且つLNA1に電源が供給されるようにLNAバイアス回路18を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法に関し、特に受信された偏波信号をダウンコンバートするダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法に関する。

【背景技術】

【0002】

受信した衛星放送電波を、ケーブルで伝送可能な中間周波数(以下、IF周波数ともいう)に周波数変換するために、ローノイズブロックダウンコンバータ(LNB:Low Noise Block Downcoverter)が用いられている。

【0003】

図14は、特許文献1に開示されている衛星放送受信用コンバータ(ダウンコンバータ)を説明するためのブロック図である。図14に示す衛星放送受信用コンバータにおいて、パラボナアンテナ(図示せず)にて受信される水平偏波又は垂直偏波のBS信号は、BS信号端子221および222から入力され、BS信号端子221および222の後段には、初段の増幅回路223、224および2段目の増幅回路225が配置されている。初段の増幅回路223、224は、それぞれBS信号端子221および222から入力された水平偏波又は垂直偏波のBS信号を増幅する。そして、2段目の増幅回路225は、初段の増幅回路223または224のいずれかの出力をさらに増幅する。

【0004】

増幅回路223〜225は、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)等を用いて高周波で動作する低雑音の高周波増幅回路である。増幅回路223または増幅回路224が、水平偏波又は垂直偏波のいずれかを受信するためには、これらの増幅回路に供給する電圧を選択的に切り替える必要がある。このため、衛星放送用コンバータIC201に内蔵したスイッチ回路310にて増幅回路223または増幅回路224に供給する電圧を選択的に切り替える。すなわち、受信するBS信号が水平偏波であるか垂直偏波であるかに応じて、端子211および212、または端子213および214から、増幅回路223または224に必要な電圧を供給する。また、2段目の増幅回路225は、水平偏波又は垂直偏波のBS信号のいずれかを増幅するため、BS信号の受信中は常に端子215および216から必要な電圧が供給される。

【0005】

増幅回路225の出力は、衛星放送用コンバータIC201に内蔵された増幅回路311にてさらに増幅され、周波数変換回路312において中間周波数であるBS−IF信号に変換される。上記BS−IF信号は、後段増幅回路313でさらに増幅された後、キャパシタ204にてDC成分を除去され、ケーブル(図示せず)を介してBSチューナ(図示せず)へ送られる。

【0006】

また、局部発信回路を含むPLL回路314は、10.7GHz〜12.75GHzの受信周波数において、ローバンドの10.7GHz〜11.7GHz帯とハイバンドの11.7GHz〜12.75GHz帯とをBS−IF信号の周波数に周波数変換するための局部発振信号を出力する。

【0007】

スイッチ回路310には、BSチューナから受信偏波の切り替え制御のためのDC電圧信号が入力される。すなわち、スイッチ回路310には、電源電圧を兼ねる13V又は18VのDC電圧信号のいずれかが入力され、スイッチ回路310は、入力されたDC電圧信号の大きさを検出することで初段の増幅回路223および224のどちらを使用するか決定する。

【0008】

スイッチ回路310で検出されたDC電圧信号の電圧の大きさにより、正および負電圧を発生する電圧発生源315は、端子211〜216を通し、増幅回路223および224のいずれか及び増幅回路225に正及び負の電圧を供給する。

【0009】

増幅回路223〜225に使用する高電子移動度トランジスタ(HEMT)は、通常、ゲート端子に負電圧を供給し、ドレイン端子に正電圧を供給することで動作する。例えば、増幅回路223を使用する場合は、衛星放送受信用コンバータIC201は、端子213から負電圧を発生し、HEMTのゲート端子にこの負電圧を供給する。同時に、端子214から正電圧を発生し、HEMTのドレイン端子に正電圧を供給する。このとき、使用しない増幅回路224への電圧供給は、増幅回路224に使用するHEMTが動作しない電圧を端子211および212から供給する。

【0010】

上記した構成において、増幅回路223の出力信号は増幅回路225に供給される。増幅回路225も増幅回路223と同様に動作し、衛星放送受信用コンバータIC201の端子215から出力される負電圧がHEMTのゲート端子に供給される。同時に、端子216から出力される正電圧がHEMTのドレイン端子に供給される。これにより、増幅回路225で増幅されたBS信号は、衛星放送受信用コンバータIC201の増幅回路311に供給される。

【0011】

増幅回路224を使用する場合は、端子211から負電圧を発生し、HEMTのゲート端子に電圧を供給する。同時に、端子212から正電圧を発生し、HEMTのドレイン端子に電圧を供給する。このとき、使用しない増幅回路223へは、増幅回路223に使用するHEMTが動作しない電圧を供給する。

【0012】

図14に示した衛星放送受信用コンバータでは、増幅回路223および224を切り替えるためのスイッチ回路310が、衛星放送受信用コンバータIC201に内蔵されている。すなわち、衛星放送受信用コンバータIC201において、水平偏波又は垂直偏波のいずれかを受信するための増幅回路223または増幅回路224を動作させるための負電圧を発生する回路を備えている。

【0013】

また、特許文献2には、LNB全体のアイソレーションを高めることができるダウンコンバータに関する技術が開示されている。特許文献3には、一つで複数のチャンネルを同時に受信することができるチューナ装置に関する技術が開示されている。非特許文献1には、ユニバーサルシングル型のLNBに関する技術が開示されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2010−268296号公報

【特許文献2】特開2002−190749号公報

【特許文献3】特開2003−198401号公報

【非特許文献】

【0015】

【非特許文献1】Tino Copani, "A 12-GHz Silicon Bipolar Dual-Conversion Receiver for Digital Satellite Applications" IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 6, JUNE 2005

【発明の概要】

【発明が解決しようとする課題】

【0016】

特許文献1に開示されているダウンコンバータICを用いてユニバーサルデュアル(Universal Dual)のダウンコンバータを構成した場合は、例えば図9に示す構成が考えられる(図9に示す構成は、本願発明者により導かれた構成である)。ここで、ユニバーサルデュアルとは、例えばDisEqC(Digital Satellite Equipment Control)の仕様において、中間周波数信号を2つ出力することができる構成である。図9に示すダウンコンバータでは、水平偏波信号(H)105および垂直偏波信号(V)106を1つのパラボラアンテナで受信し、ダウンコンバータ回路101および102からそれぞれ、ダウンコンバート後の中間周波数信号OUT101およびOUT102を出力する。

【0017】

図9に示すダウンコンバータは、増幅部103と、ダウンコンバータ回路101と、ダウンコンバータ回路102とを備える。増幅部103は、パラボラアンテナ104で受信された水平偏波信号105および垂直偏波信号106を増幅する複数の増幅器(低雑音増幅器(LNA:Low Noise Amplifier))を備える。

【0018】

パラボラアンテナ104で受信された水平偏波信号105は、LNA111で増幅されて、LNA113およびLNA114に出力される。LNA113は、LNA111で増幅された水平偏波信号を増幅して、ダウンコンバータ回路101の入力端子131に出力する。LNA114は、LNA111で増幅された水平偏波信号を増幅して、ダウンコンバータ回路102の入力端子141に出力する。

【0019】

パラボラアンテナ104で受信された垂直偏波信号106は、LNA112で増幅されて、LNA115およびLNA116に出力される。LNA115は、LNA112で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路101の入力端子131に出力する。LNA116は、LNA112で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路102の入力端子141に出力する。

【0020】

すなわち、ダウンコンバータ回路101の入力端子131には、LNA111およびLNA113を経由して水平偏波信号105が供給され、LNA112およびLNA115を経由して垂直偏波信号106が供給される。また、ダウンコンバータ回路102の入力端子141には、LNA111およびLNA114を経由して水平偏波信号105が供給され、LNA112およびLNA116を経由して垂直偏波信号106が供給される。

【0021】

ダウンコンバータ回路101は、基準信号生成器115、局部発振器116、周波数変換部117、LNAバイアス回路118、および制御回路119を有する。基準信号生成器115は、クリスタル発振回路REF111とバッファB111とを有する。クリスタル発振回路REF111は、所定の基準周波数を有する基準信号154を生成し、局部発振器116に出力する。ここで、クリスタル発振回路REF111は、端子133に接続された水晶振動子X'tal(111)を用いて基準信号154を生成する。局部発振器116は、基準信号154を用いて局部発振周波数信号153を生成する。

【0022】

周波数変換部117は、プリアンプAMP111と、ミキサーMIXER111と、ローパスフィルタF111と、IFアンプAMP112とを備える。プリアンプAMP111は入力端子131に入力された垂直偏波信号または水平偏波信号を増幅し、ミキサーMIXER111に出力する。ミキサーMIXER111は、局部発振器116から出力された局部発振周波数信号153を用いて、プリアンプAMP111から出力された増幅された垂直偏波信号または水平偏波信号をダウンコンバートする。ダウンコンバートされた垂直偏波信号または水平偏波信号は、フィルタF111で不要成分が除去され、更にIFアンプAMP112で増幅されて、出力端子132から中間周波数信号OUT101として出力される。

【0023】

LNAバイアス回路118は、端子137を介してLNA111に電源を供給し、端子136を介してLNA113に電源を供給し、端子138を介してLNA115に電源を供給する。制御回路119は、制御信号入力端子135から入力されたTone/Pola信号に応じて、LNAバイアス回路118および局部発振器116を制御する。

【0024】

図10は、Tone/Pola信号の一例を示す図である。図10に示すように、Pola(Polarization)信号は、例えば13Vまたは18VのDC電圧信号である。また、Tone信号は、AC成分(22kHz)の信号であり、DC成分であるPola信号に重畳されている。

【0025】

図10に示すように、Tone/Pola信号のDC成分が18Vである場合、制御回路119は、ダウンコンバータ回路101の入力端子131に水平偏波信号が供給されるようにLNAバイアス回路118を制御する。一方、Tone/Pola信号のDC成分が13Vである場合、制御回路119は、ダウンコンバータ回路101の入力端子131に垂直偏波信号が供給されるようにLNAバイアス回路118を制御する。

【0026】

また、Tone/Pola信号のAC成分として22kHzの信号が供給されている場合、制御回路119は、高バンドの局部発振周波数信号153(10.6GHz)が出力されるように局部発振器116を制御する。一方、Tone/Pola信号のAC成分がオフ状態である場合は、制御回路119は、低バンドの局部発振周波数信号153(9.75GHz)が出力されるように局部発振器116を制御する。

【0027】

ダウンコンバータ回路102は、基準信号生成器125、局部発振器126、周波数変換部127、LNAバイアス回路128、および制御回路129を有する。ここで、ダウンコンバータ回路102の構成は、ダウンコンバータ回路101の構成と同様であるので重複した説明は省略する。なお、LNAバイアス回路128は、端子148を介してLNA112に電源を供給し、端子146を介してLNA114に電源を供給し、端子147を介してLNA116に電源を供給する。

【0028】

図11は、図9に示したダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。ダウンコンバータ回路101でダウンコンバートされた中間周波数信号OUT101は、容量素子C112でDC成分が除去されて、ケーブルを介してチューナ(Tuner101)に供給される。一方、チューナ(Tuner101)は、中間周波数信号OUT101を伝送したケーブルと同一のケーブルを介して、ダウンコンバータ回路101に電源およびTone/Pola信号を供給する。ここで、ダウンコンバータ回路101に供給される電源として、Tone/Pola信号のDC成分(13Vまたは18V)が用いられる。

【0029】

Tone/Pola信号のDC成分(13Vまたは18V)は、ストリップラインSL112を介してレギュレータREG111に供給される。レギュレータREG111は、13Vまたは18Vの電圧を、ダウンコンバータ回路101の最大定格にあった電圧に調整してダウンコンバータ回路101の電源端子VDDに供給する。

【0030】

また、Tone/Pola信号は、ストリップラインSL111を介して抵抗素子R112と容量素子C111に供給される。ここで、Pola信号のDC成分は、抵抗素子R111と抵抗素子R112とによって分割される。つまり、Pola信号は、抵抗素子R111と抵抗素子R112とを用いてダウンコンバータ回路101の最大定格にあった電圧に下げられて、制御信号入力端子135に供給される。一方、Tone信号は、容量C111を通過し、ダウンコンバータ回路101の内部でパルスの有無が検出される。

【0031】

また、増幅部103が備えるLNA111、LNA113、およびLNA115には、LNAバイアス回路128を介して電源が供給される。なお、ダウンコンバータ回路102に電源およびTone/Pola信号が供給される場合についても、ダウンコンバータ回路101に電源およびTone/Pola信号が供給される場合と同様である。

【0032】

図12は、図9に示したダウンコンバータの動作を説明するための表である。

中間周波数信号OUT101およびOUT102が出力されない場合は、チューナ(Tuner101、Tuner102)からダウンコンバータ回路101、102に電源が供給されないため、ダウンコンバータ回路101、102はオフ状態となる。これによりLNA111〜116もオフ状態となる。

【0033】

一方、中間周波数信号OUT101およびOUT102が出力される場合、ダウンコンバータ回路101には、LNA111およびLNA113を経由して水平偏波信号105が、またはLNA112およびLNA115を経由して垂直偏波信号106が供給される。また、ダウンコンバータ回路102には、LNA111およびLNA114を経由して水平偏波信号105が、またはLNA112およびLNA116を経由して垂直偏波信号106が供給される。このとき、LNA111およびLNA112は常にオン状態となる。

【0034】

Pola信号がHigh(18V)の場合、LNA113はオン状態、LNA115はオフ状態となり、ダウンコンバータ回路101には水平偏波信号105が供給される。一方、Pola信号がLow(13V)の場合、LNA113はオフ状態、LNA115はオン状態となり、ダウンコンバータ回路101には垂直偏波信号106が供給される。

【0035】

同様に、Pola信号がHigh(18V)の場合、LNA114はオン状態、LNA116はオフ状態となり、ダウンコンバータ回路102には水平偏波信号105が供給される。一方、Pola信号がLow(13V)の場合、LNA114はオフ状態、LNA116はオン状態となり、ダウンコンバータ回路102には垂直偏波信号106が供給される。

【0036】

また、図12に示すように、Tone信号がオフ状態の場合は、局部発振周波数信号153、163として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号153、163として高バンド(10.6GHz)の信号が出力される。なお、中間周波数信号OUT101およびOUT102が出力される場合、チューナ(Tuner101、Tuner102)からダウンコンバータ回路101、102に電源が供給される。

【0037】

次に、中間周波数信号OUT101またはOUT102のみが出力される場合について、図13を用いて説明する。一方の中間周波数信号のみが出力される場合は、中間周波数信号が出力されない方のダウンコンバータ回路をオフ状態とする。これにより、ダウンコンバータの消費電力を低減することができる。

【0038】

まず、中間周波数信号OUT101が出力され、中間周波数信号OUT102が出力されない場合(OUT101がON、OUT102がOFFの場合)について説明する。この場合、ダウンコンバータ回路101には、LNA111およびLNA113がオン状態の時に水平偏波信号105が供給される。一方、中間周波数信号OUT102が出力されない場合は、図11に示すチューナ(Tuner102)からダウンコンバータ回路102に電源が供給されない。このため、垂直偏波信号106を増幅するLNA112に電源が供給されないため、ダウンコンバータ回路101には垂直偏波信号106が供給されない。

【0039】

中間周波数信号OUT102が出力され、中間周波数信号OUT101が出力されない場合(OUT101がOFF、OUT102がONの場合)について説明する。この場合、ダウンコンバータ回路102には、LNA112およびLNA116がオン状態の時に垂直偏波信号106が供給される。一方、中間周波数信号OUT101が出力されない場合は、図11に示すチューナ(Tuner101)からダウンコンバータ回路101に電源が供給されない。このため、水平偏波信号105を増幅するLNA111に電源が供給されないため、ダウンコンバータ回路102には水平偏波信号105が供給されない。

【0040】

換言すると、図9に示すダウンコンバータでは、ダウンコンバータ回路102のLNAバイアス回路128を用いてLNA112に電源を供給している。このため、ダウンコンバータ回路102をオフ状態とするとLNAバイアス回路128もオフ状態となり、LNA112への電源供給も遮断されるため、ダウンコンバータ回路101に垂直偏波信号106を出力することができなくなる。

【0041】

同様に、図9に示すダウンコンバータでは、ダウンコンバータ回路101のLNAバイアス回路118を用いてLNA111に電源を供給している。このため、ダウンコンバータ回路101をオフ状態とするとLNAバイアス回路118もオフ状態となり、LNA111への電源供給も遮断されるため、ダウンコンバータ回路102に水平偏波信号105を出力することができなくなる。これは、ダウンコンバータ回路101および102で、LNA111およびLNA112を共有していることに起因する。

【0042】

このように、特許文献1に開示されているダウンコンバータICを用いてユニバーサルデュアル(Universal Dual)のダウンコンバータを構成した場合、一方のダウンコンバータ回路(101または102)がオフ状態となるとダウンコンバータが正常に動作しないという問題があった。

【課題を解決するための手段】

【0043】

本発明にかかるダウンコンバータは、第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備える。前記第1の制御回路は、前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、前記第2の制御回路は、前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する。

【0044】

本発明にかかるダウンコンバータでは、第1の制御信号が省電力モードを示す信号である場合、第1の局部発振器および第1の周波数変換部を非動作状態とし、且つ第1の増幅器に電源が供給されるように第1のバイアス回路を制御し、第2の制御信号が省電力モードを示す信号である場合、第2の局部発振器および第2の周波数変換部を非動作状態とし、且つ第2の増幅器に電源が供給されるように第2のバイアス回路を制御している。よって、第1のダウンコンバータ回路が省電力モードであっても第1の増幅器をオン状態とすることができるので、第2のダウンコンバータ回路に偏波信号を供給することができる。また、第2のダウンコンバータ回路が省電力モードであっても第2の増幅器をオン状態とすることができるので、第1のダウンコンバータ回路に偏波信号を供給することができる。したがって、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータを提供することができる。

【0045】

本発明にかかるダウンコンバータICは、所定の基準周波数を有する基準信号を生成する基準信号生成器と、前記基準信号を用いて局部発振周波数信号を生成する局部発振器と、増幅器で増幅された偏波信号を前記局部発振周波数信号を用いて中間周波数信号に変換する周波数変換部と、前記増幅器に電源を供給するバイアス回路と、前記基準信号生成器、前記局部発振器、前記周波数変換部、および前記バイアス回路を制御信号に応じて制御する制御回路と、を備える。前記制御回路は、前記制御信号が省電力モードを示す信号である場合、前記局部発振器および前記周波数変換部を非動作状態とし、且つ前記増幅器に電源が供給されるように前記バイアス回路を制御する。

【0046】

本発明にかかるダウンコンバータの制御方法は、第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備えるダウンコンバータの制御方法であって、前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する。

【0047】

本発明にかかるダウンコンバータの制御方法では、第1の制御信号が省電力モードを示す信号である場合、第1の局部発振器および第1の周波数変換部を非動作状態とし、且つ第1の増幅器に電源が供給されるように第1のバイアス回路を制御し、第2の制御信号が省電力モードを示す信号である場合、第2の局部発振器および第2の周波数変換部を非動作状態とし、且つ第2の増幅器に電源が供給されるように第2のバイアス回路を制御している。よって、第1のダウンコンバータ回路が省電力モードであっても第1の増幅器をオン状態とすることができるので、第2のダウンコンバータ回路に偏波信号を供給することができる。また、第2のダウンコンバータ回路が省電力モードであっても第2の増幅器をオン状態とすることができるので、第1のダウンコンバータ回路に偏波信号を供給することができる。したがって、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータの制御方法を提供することができる。

【発明の効果】

【0048】

本発明により、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法を提供することができる。

【図面の簡単な説明】

【0049】

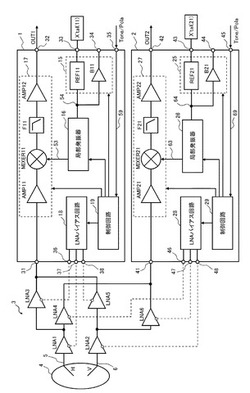

【図1】実施の形態1にかかるダウンコンバータを示すブロック図である。

【図2】実施の形態1にかかるダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。

【図3】実施の形態1にかかるダウンコンバータの動作を説明するための表である。

【図4】実施の形態1にかかるダウンコンバータの動作を説明するための表である。

【図5】実施の形態1にかかるダウンコンバータに用いられるTone/Pola信号を説明するための図である。

【図6】実施の形態1にかかるダウンコンバータが備える局部発振器の一例を示すブロック図である。

【図7】1/1.6分周器の一例を示すブロック図である。

【図8】実施の形態2にかかるダウンコンバータを示すブロック図である。

【図9】本発明の課題を説明するための図である。

【図10】図9に示すダウンコンバータに用いられるTone/Pola信号を説明するための図である。

【図11】図9に示すダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。

【図12】図9に示すダウンコンバータの動作を説明するための表である。

【図13】図9に示すダウンコンバータの動作を説明するための表である。

【図14】特許文献1に開示されているダウンコンバータを説明するためのブロック図である。

【発明を実施するための形態】

【0050】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。

図1は本発明の実施の形態1にかかるダウンコンバータを示すブロック図である。図1に示すダウンコンバータは、例えばDisEqC(Digital Satellite Equipment Control)の仕様において、中間周波数信号を2つ出力することができるユニバーサルデュアル(Universal Dual)構成のダウンコンバータである。すなわち、図1に示すダウンコンバータでは、水平偏波信号(H)5および垂直偏波信号(V)6を1つのパラボラアンテナ4で受信し、ダウンコンバータ回路1および2からそれぞれ、ダウンコンバート後の中間周波数信号OUT1およびOUT2を出力する。

【0051】

図1に示すダウンコンバータは、増幅部3と、ダウンコンバータ回路1と、ダウンコンバータ回路2とを備える。ここで、例えば各ダウンコンバータ回路1、2はそれぞれ、1つのICチップに形成されている。すなわち、中間周波数信号を2つ出力することができるユニバーサルデュアル構成のダウンコンバータは、2つのICチップ(ダウンコンバータ回路)を用いて構成することができる。

【0052】

増幅部3は、パラボラアンテナ4で受信された水平偏波信号5および垂直偏波信号6を増幅する複数の増幅器(低雑音増幅器(LNA:Low Noise Amplifier))を備える。ここで、各LNAには、例えば高電子移動度トランジスタ(HEMT)を用いることができる。

【0053】

パラボラアンテナ4で受信された水平偏波信号5は、LNA1(第1の増幅器)で増幅されて、LNA3(第3の増幅器)およびLNA4(第4の増幅器)に出力される。LNA3は、LNA1で増幅された水平偏波信号を増幅して、ダウンコンバータ回路1の入力端子31に出力する。LNA4は、LNA1で増幅された水平偏波信号を増幅して、ダウンコンバータ回路2の入力端子41に出力する。

【0054】

パラボラアンテナ4で受信された垂直偏波信号6は、LNA2(第2の増幅器)で増幅されて、LNA5(第5の増幅器)およびLNA6(第6の増幅器)に出力される。LNA5は、LNA2で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路1の入力端子31に出力する。LNA6は、LNA2で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路2の入力端子41に出力する。

【0055】

すなわち、ダウンコンバータ回路1の入力端子31には、LNA1およびLNA3を経由して水平偏波信号5が供給され、LNA2およびLNA5を経由して垂直偏波信号6が供給される。また、ダウンコンバータ回路2の入力端子41には、LNA1およびLNA4を経由して水平偏波信号5が供給され、LNA2およびLNA6を経由して垂直偏波信号6が供給される。

【0056】

ダウンコンバータ回路1(第1のダウンコンバータ回路)は、基準信号生成器15(第1の基準信号生成器)、局部発振器16(第1の局部発振器)、周波数変換部17(第1の周波数変換部)、LNAバイアス回路18(第1のバイアス回路)、および制御回路19(第1の制御回路)を有する。

【0057】

基準信号生成器15は、クリスタル発振回路REF11とバッファB11とを有する。クリスタル発振回路REF11は、所定の基準周波数を有する基準信号54(第1の基準信号)を生成し、局部発振器16に出力する。ここで、クリスタル発振回路REF11は、端子33に接続された水晶振動子X'tal(11)を用いて基準信号54を生成する。局部発振器16は、基準信号54を用いて局部発振周波数信号53を生成する。

【0058】

周波数変換部17は、プリアンプAMP11と、ミキサーMIXER11と、ローパスフィルタF11と、IFアンプAMP12とを備える。プリアンプAMP11は入力端子31に入力された垂直偏波信号または水平偏波信号を増幅し、ミキサーMIXER11に出力する。ミキサーMIXER11は、局部発振器16から出力された局部発振周波数信号53を用いて、プリアンプAMP11から出力された増幅された垂直偏波信号または水平偏波信号をダウンコンバートする。ダウンコンバートされた垂直偏波信号または水平偏波信号は、フィルタF11で不要成分が除去され、更にIFアンプAMP12で増幅されて、出力端子32から中間周波数信号OUT1として出力される。

【0059】

LNAバイアス回路18は、端子37を介してLNA1に電源を供給し、端子36を介してLNA3に電源を供給し、端子38を介してLNA5に電源を供給する。制御回路19は、制御信号入力端子35から入力されたTone/Pola信号59に応じて、基準信号生成器15、局部発振器16、周波数変換部17、およびLNAバイアス回路18を制御する。

【0060】

ダウンコンバータ回路2(第2のダウンコンバータ回路)は、基準信号生成器25(第2の基準信号生成器)、局部発振器26(第2の局部発振器)、周波数変換部27(第2の周波数変換部)、LNAバイアス回路28(第2のバイアス回路)、および制御回路29(第2の制御回路)を有する。基準信号生成器25は、クリスタル発振回路REF21とバッファB21とを有する。

【0061】

クリスタル発振回路REF21は、所定の基準周波数を有する基準信号64(第2の基準信号)を生成し、局部発振器26に出力する。ここで、クリスタル発振回路REF21は、端子43に接続された水晶振動子X'tal(21)を用いて基準信号64を生成する。なお、基準信号54と基準信号64の周波数は典型的には同一である。局部発振器26は、基準信号64を用いて局部発振周波数信号63を生成する。

【0062】

周波数変換部27は、プリアンプAMP21と、ミキサーMIXER21と、ローパスフィルタF21と、IFアンプAMP22とを備える。プリアンプAMP21は入力端子41に入力された垂直偏波信号または水平偏波信号を増幅し、ミキサーMIXER21に出力する。ミキサーMIXER21は、局部発振器26から出力された局部発振周波数信号63を用いて、プリアンプAMP21から出力された増幅された垂直偏波信号または水平偏波信号をダウンコンバートする。ダウンコンバートされた垂直偏波信号または水平偏波信号は、フィルタF21で不要成分が除去され、更にIFアンプAMP22で増幅されて、出力端子42から中間周波数信号OUT2として出力される。

【0063】

LNAバイアス回路28は、端子48を介してLNA2に電源を供給し、端子46を介してLNA4に電源を供給し、端子47を介してLNA6に電源を供給する。制御回路29は、制御信号入力端子45から入力されたTone/Pola信号69に応じて、基準信号生成器25、局部発振器26、周波数変換部27、およびLNAバイアス回路28を制御する。

【0064】

図2は、本実施の形態にかかるダウンコンバータで用いられるTone/Pola信号の一例を示す図である。図2に示すように、Pola(Polarization)信号は、例えば18VのDC電圧信号、13VのDC電圧信号、または10Vよりも小さいDC電圧信号である。ここで、10Vよりも小さいDC電圧信号が供給される場合とは、典型的にはPola信号が供給されない場合、つまりPola信号のDC信号が非通電の場合である。換言すると、図3に示すチューナからダウンコンバータ回路にDC成分が供給されない場合である。図3に示すチューナからダウンコンバータ回路にDC成分が供給されない場合、抵抗R11、R12を介して制御信号入力端子35で検出される電圧は理想的には0Vである。以下では、Pola信号が供給されない場合を、10Vよりも小さいDC電圧信号が供給される場合の代表例として説明する。

【0065】

Pola信号(第1のモード選択信号)が18VのDC電圧信号である場合、制御回路19は、ダウンコンバータ回路1の入力端子31に水平偏波信号が供給されるようにLNAバイアス回路18を制御する。Pola信号が13VのDC電圧信号である場合、制御回路19は、ダウンコンバータ回路1の入力端子31に垂直偏波信号が供給されるようにLNAバイアス回路18を制御する。このとき、ダウンコンバータ回路1の動作モードは通常動作モードである。一方、Pola信号が供給されない場合、ダウンコンバータ回路1は省電力モードとなる。ダウンコンバータ回路1が省電力モードである場合、制御回路19は、局部発振器16および周波数変換部17を非動作状態とし、LNAバイアス回路18の動作状態を維持する。なお、基準信号生成器15については非動作状態としてもよく、また動作状態を維持してもよい。

【0066】

また、Pola信号(第2のモード選択信号)が18VのDC電圧信号である場合、制御回路29は、ダウンコンバータ回路2の入力端子41に水平偏波信号が供給されるようにLNAバイアス回路28を制御する。Pola信号が13VのDC電圧信号である場合、制御回路29は、ダウンコンバータ回路2の入力端子41に垂直偏波信号が供給されるようにLNAバイアス回路28を制御する。このとき、ダウンコンバータ回路2の動作モードは通常動作モードである。一方、Pola信号が供給されない場合、ダウンコンバータ回路2は省電力モードとなる。ダウンコンバータ回路2が省電力モードである場合、制御回路29は、局部発振器26および周波数変換部27を非動作状態とし、LNAバイアス回路28の動作状態を維持する。なお、基準信号生成器25については非動作状態としてもよく、また動作状態を維持してもよい。

【0067】

図2に示すように、Tone信号は、AC成分(22kHz)の信号であり、DC成分であるPola信号に重畳されている。Tone/Pola信号のAC成分として22kHzのTone信号(第1のバンド選択信号)が供給されている場合、制御回路19は、高バンドの局部発振周波数信号53(例えば、Ku帯の場合は10.6GHz)が出力されるように局部発振器16を制御する。一方、Tone/Pola信号のAC成分がオフ状態である場合は、制御回路19は、低バンドの局部発振周波数信号53(例えば、Ku帯の場合は9.75GHz)が出力されるように局部発振器16を制御する。

【0068】

同様に、Tone/Pola信号のAC成分として22kHzのTone信号(第2のバンド選択信号)が供給されている場合、制御回路29は、高バンドの局部発振周波数信号63(例えば、10.6GHz)が出力されるように局部発振器26を制御する。一方、Tone/Pola信号のAC成分がオフ状態である場合は、制御回路29は、低バンドの局部発振周波数信号63(例えば、9.75GHz)が出力されるように局部発振器26を制御する。

【0069】

図9に示したダウンコンバータでは、図10に示すように18VのDC電圧信号および13VのDC電圧信号のみを使用していた。これに対して本実施の形態にかかるダウンコンバータでは、18VのDC電圧信号および13VのDC電圧信号を用いると共に、10Vよりも小さいDC電圧信号(典型的には、Pola信号が供給されない場合)に新たに省電力モードを設定している。すなわち、本実施の形態にかかるダウンコンバータでは、Pola信号を2bit化することで、制御回路19、29において、(1)水平偏波信号が供給される場合(通常動作モード)、(2)垂直偏波信号が供給される場合(通常動作モード)、(3)省電力モードの3状態を検出することができる。

【0070】

図6は、本実施の形態にかかるダウンコンバータが備える局部発振器16の一例を示すブロック図である(局部発振器26についても同様である)。図6に示すように、局部発振器16は、位相比較器PFDと、ローパスフィルタLPFと、電圧制御発振器VCO11と、複数の分周器FDと、を備える。

【0071】

位相比較器PFDは、クリスタル発振回路REF11で生成された基準信号54と、複数の分周器FDで分周された信号とを入力し、これらの信号の位相差を電圧に変換した信号を出力する。ローパスフィルタLPFは、位相比較器PFDから出力された信号に含まれる不要な成分を除去する。電圧制御発振器VCO11は、ローパスフィルタLPFから出力された信号の電圧に応じて出力信号の周波数を制御する。電圧制御発振器VCO11で生成された出力信号は局部発振周波数信号53として出力される。

【0072】

また、電圧制御発振器VCO11から出力された局部発振周波数信号53は、分周器FD(1/4)、分周器FD(1/2)、および分周器FD(1/39)を経由する第1のパス、または分周器FD(1/4)、分周器FD(1/1.6)、および分周器FD(1/53)を経由する第2のパスで分周される。第1および第2のパスの切り替えは、制御回路19から出力された制御信号を用いてスイッチSW11、SW12を切り替えることで実施することができる。

【0073】

基準信号54の周波数が31.25MHzである場合、制御回路19が第1のパスを選択することで、10.6GHz(=31.25MHz×1/4×1/2×1/39)の局部発振周波数信号(低バンド)53を生成することができる。一方、制御回路19が第2のパスを選択することで、9.75GHz(=31.25MHz×1/4×1/1.6×1/53)の局部発振周波数信号(高バンド)53を生成することができる。

【0074】

ここで、分周器FD(1/1.6)は、例えば図7に示すように、分周器FD(1/2)、分周器FD(1/4)、およびイメージ除去ミキサーIRM(Image rejection mixer)を用いて構成することができる。

【0075】

図3は、図1に示したダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。ダウンコンバータ回路1でダウンコンバートされた中間周波数信号OUT1は、容量素子C12でDC成分が除去されて、ケーブルを介してチューナ(Tuner1:第1のチューナ)に供給される。一方、チューナ(Tuner1)は、中間周波数信号OUT1を伝送したケーブルと同一のケーブルを介して、ダウンコンバータ回路1に電源およびTone/Pola信号を供給する。ここで、ダウンコンバータ回路1には電源として、Tone/Pola信号のDC成分(18VのDC電圧信号、13VのDC電圧信号、または10Vよりも小さいDC電圧信号(典型的には0Vであり、この場合、DC成分は非通電となる))が供給される。

【0076】

Tone/Pola信号のDC成分(13Vまたは18V)は、ストリップラインSL12を介してレギュレータREG11(第1のレギュレータ)に供給される。レギュレータREG11は、13Vまたは18Vの電圧を、ダウンコンバータ回路1の最大定格にあった電圧に調整してダウンコンバータ回路1の電源端子VDDに供給する。

【0077】

また、Tone/Pola信号は、ストリップラインSL11を介して抵抗素子R12と容量素子C11に供給される。ここで、Pola信号のDC成分は、抵抗素子R11と抵抗素子R12とによって分割される。つまり、Pola信号は、抵抗素子R11と抵抗素子R12とを用いてダウンコンバータ回路1の最大定格にあった電圧に下げられて、制御信号入力端子35に供給される。一方、Tone信号は、容量C11を通過し、ダウンコンバータ回路1の内部でパルスの有無が検出される。増幅部3が備えるLNA1、LNA3、およびLNA5には、LNAバイアス回路28を介して電源が供給される。

【0078】

同様に、ダウンコンバータ回路2でダウンコンバートされた中間周波数信号OUT2は、容量素子C22でDC成分が除去されて、ケーブルを介してチューナ(Tuner2:第2のチューナ)に供給される。一方、チューナ(Tuner2)は、中間周波数信号OUT2を伝送したケーブルと同一のケーブルを介して、ダウンコンバータ回路2に電源およびTone/Pola信号を供給する。ここで、ダウンコンバータ回路2には電源として、Tone/Pola信号のDC成分(18VのDC電圧信号、13VのDC電圧信号、または10Vよりも小さいDC電圧信号(典型的には0Vであり、この場合、DC成分は非通電となる))が供給される。

【0079】

Tone/Pola信号のDC成分(13Vまたは18V)は、ストリップラインSL22を介してレギュレータREG21(第2のレギュレータ)に供給される。レギュレータREG21は、13Vまたは18Vの電圧を、ダウンコンバータ回路2の最大定格にあった電圧に調整してダウンコンバータ回路2の電源端子VDDに供給する。

【0080】

また、Tone/Pola信号は、ストリップラインSL21を介して抵抗素子R22と容量素子C21に供給される。ここで、Pola信号のDC成分は、抵抗素子R21と抵抗素子R22とによって分割される。つまり、Pola信号は、抵抗素子R21と抵抗素子R22とを用いてダウンコンバータ回路2の最大定格にあった電圧に下げられて、制御信号入力端子45に供給される。一方、Tone信号は、容量C21を通過し、ダウンコンバータ回路2の内部でパルスの有無が検出される。増幅部3が備えるLNA2、LNA4、およびLNA6には、LNAバイアス回路28を介して電源が供給される。

【0081】

ここで、本実施の形態にかかるダウンコンバータでは、レギュレータREG11からダウンコンバータ回路2の電源端子VDDにも電源が供給可能に構成されている。また、レギュレータREG21からダウンコンバータ回路1の電源端子VDDにも電源が供給可能に構成されている。すなわち、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1に電源が供給されない場合、つまりダウンコンバータ回路1にTone/Pola信号が供給されない場合、レギュレータREG11からダウンコンバータ回路1の電源端子VDDに電源を供給することができない。しかし、この場合は、ダウンコンバータ回路2に電源が供給されているので(つまり、ダウンコンバータ回路2には電源としてTone/Pola信号のDC成分(13Vまたは18V)が供給されているので)、レギュレータREG21からダウンコンバータ回路1の電源端子VDDに電源を供給することができる。

【0082】

同様に、ダウンコンバータ回路2に電源が供給されない場合、つまりダウンコンバータ回路2にTone/Pola信号が供給されない場合、レギュレータREG21からダウンコンバータ回路2の電源端子VDDに電源を供給することができない。しかし、この場合は、ダウンコンバータ回路1に電源が供給されているので(つまり、ダウンコンバータ回路1には電源としてTone/Pola信号のDC成分(13Vまたは18V)が供給されているので)、レギュレータREG11からダウンコンバータ回路2の電源端子VDDに電源を供給することができる。

【0083】

図4は、図1に示したダウンコンバータの動作を説明するための表である。

中間周波数信号OUT1およびOUT2が出力されない場合は、チューナ(Tuner1、Tuner2)からダウンコンバータ回路1、2に電源が供給されないため、ダウンコンバータ回路1、2はオフ状態となる。これによりLNA1〜6もオフ状態となる。

【0084】

一方、中間周波数信号OUT1およびOUT2が出力される場合、ダウンコンバータ回路1には、LNA1およびLNA3を経由して水平偏波信号105が、またはLNA2およびLNA5を経由して垂直偏波信号6が供給される。また、ダウンコンバータ回路2には、LNA1およびLNA4を経由して水平偏波信号5が、またはLNA2およびLNA6を経由して垂直偏波信号6が供給される。このとき、LNA1およびLNA2は常にオン状態となる。

【0085】

また、Pola信号がHigh(18V)の場合、LNA3はオン状態、LNA5はオフ状態となり、ダウンコンバータ回路1には水平偏波信号5が供給される。一方、Pola信号がLow(13V)の場合、LNA3はオフ状態、LNA5はオン状態となり、ダウンコンバータ回路1には垂直偏波信号6が供給される。なお、LNA1、LNA3、およびLNA5のオン状態・オフ状態の切り替えは、LNAバイアス回路18からの電源供給の有無を切り替えることで実施することができる。また、LNAバイアス回路18からの電源供給の有無は、制御回路19から出力される制御信号によって制御される。

【0086】

同様に、Pola信号がHigh(18V)の場合、LNA4はオン状態、LNA6はオフ状態となり、ダウンコンバータ回路2には水平偏波信号5が供給される。一方、Pola信号がLow(13V)の場合、LNA4はオフ状態、LNA6はオン状態となり、ダウンコンバータ回路2には垂直偏波信号6が供給される。なお、LNA2、LNA4、およびLNA6のオン状態・オフ状態の切り替えは、LNAバイアス回路28からの電源供給の有無を切り替えることで実施することができる。また、LNAバイアス回路28からの電源供給の有無は、制御回路29から出力される制御信号によって制御される。

【0087】

また、図4に示すように、Tone信号がオフ状態の場合は、局部発振周波数信号53、63として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号53、63として高バンド(10.6GHz)の信号が出力される。なお、中間周波数信号OUT1およびOUT2が出力される場合、チューナ(Tuner1、Tuner2)からダウンコンバータ回路1、2に電源が供給される。

【0088】

次に、中間周波数信号OUT1またはOUT2のみが出力される場合について、図5を用いて説明する。一方の中間周波数信号のみが出力される場合は、中間周波数信号が出力されない方のダウンコンバータ回路をオフ状態とする。これにより、ダウンコンバータの消費電力を低減することができる。

【0089】

まず、中間周波数信号OUT1が出力され、中間周波数信号OUT2が出力されない場合(OUT1がON、OUT2がOFFの場合)について説明する。このとき、ダウンコンバータ回路2が省電力モードとなるので、制御回路29は、基準信号生成器25、局部発振器26、および周波数変換部27を非動作状態とし、更にLNA2に電源が供給されるようにLNAバイアス回路28を制御する。なお、この場合、レギュレータREG11からダウンコンバータ回路2に電源が供給される。

【0090】

LNA1およびLNA3がオン状態の時、ダウンコンバータ回路1には水平偏波信号5が供給される。一方、LNA2およびLNA5がオン状態の時、ダウンコンバータ回路1には垂直偏波信号6が供給される。また、Tone信号がオフ状態の場合は、局部発振周波数信号53として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号53として高バンド(10.6GHz)の信号が出力される。

【0091】

次に、中間周波数信号OUT2が出力され、中間周波数信号OUT1が出力されない場合(OUT1がOFF、OUT2がONの場合)について説明する。このとき、ダウンコンバータ回路1が省電力モードとなるので、制御回路19は、基準信号生成器15、局部発振器16、および周波数変換部17を非動作状態とし、更にLNA1に電源が供給されるようにLNAバイアス回路18を制御する。なお、この場合、レギュレータREG21からダウンコンバータ回路1に電源が供給される。

【0092】

LNA1およびLNA4がオン状態の時、ダウンコンバータ回路2には水平偏波信号5が供給される。一方、LNA2およびLNA6がオン状態の時、ダウンコンバータ回路1には垂直偏波信号6が供給される。また、Tone信号がオフ状態の場合は、局部発振周波数信号63として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号63として高バンド(10.6GHz)の信号が出力される。

【0093】

図9に示したダウンコンバータでは、ダウンコンバータ回路102のLNAバイアス回路128を用いてLNA112に電源を供給していた。このため、ダウンコンバータ回路102をオフ状態とするとLNAバイアス回路128もオフ状態となり、LNA112への電源供給も遮断されるため、ダウンコンバータ回路101に垂直偏波信号106を出力することができなかった。また、図9に示したダウンコンバータでは、ダウンコンバータ回路101のLNAバイアス回路118を用いてLNA111に電源を供給していた。このため、ダウンコンバータ回路101をオフ状態とするとLNAバイアス回路118もオフ状態となり、LNA111への電源供給も遮断されるため、ダウンコンバータ回路102に水平偏波信号105を出力することができなかった。

【0094】

このように、特許文献1に開示されているダウンコンバータICを用いてユニバーサルデュアル(Universal Dual)のダウンコンバータを構成した場合、一方のダウンコンバータ回路(101または102)がオフ状態となるとダウンコンバータが正常に動作しないという問題があった。したがって、特許文献1に開示されているダウンコンバータICはユニバーサルシングル(Universal Single)の構成にしか使用できなかった。また、特許文献1に開示されているダウンコンバータICをユニバーサルデュアル(Universal Dual)のダウンコンバータに使用する場合には、LNAへの電源供給を別電源を用いて供給する必要があった。この場合は、消費電力およびコストが増加し、またダウンコンバータの仕様が複雑になるという問題があった。

【0095】

これに対して、図1に示した本実施の形態にかかるダウンコンバータでは、18VのDC電圧信号および13VのDC電圧信号を用いると共に、10Vよりも小さいDC電圧信号(典型的には、Pola信号が供給されない場合)に新たに省電力モードを設定している。すなわち、本実施の形態にかかるダウンコンバータでは、Pola信号を2bit化することで、制御回路19、29において、(1)水平偏波信号が供給される場合(通常動作モード)、(2)垂直偏波信号が供給される場合(通常動作モード)、(3)省電力モードの3状態を検出することができる。

【0096】

そして、制御回路19は、制御信号(Pola信号)が省電力モードを示す信号である場合、局部発振器16および周波数変換部17を非動作状態とし、更にLNA1に電源が供給されるようにLNAバイアス回路18を制御している。また、制御回路29は、制御信号(Pola信号)が省電力モードを示す信号である場合、局部発振器26および周波数変換部27を非動作状態とし、更にLNA2に電源が供給されるようにLNAバイアス回路28を制御している。よって、ダウンコンバータ回路1が省電力モードであってもLNA1をオン状態とすることができるので、ダウンコンバータ回路2に水平偏波信号5を供給することができる。また、ダウンコンバータ回路2が省電力モードであってもLNA2をオン状態とすることができるので、ダウンコンバータ回路1に垂直偏波信号6を供給することができる。

【0097】

また、本実施の形態にかかるダウンコンバータでは、レギュレータREG11からダウンコンバータ回路2の電源端子VDDに電源が供給可能に構成されている。同様に、レギュレータREG21からダウンコンバータ回路1の電源端子VDDに電源が供給可能に構成されている。

【0098】

すなわち、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1に電源が供給されない場合、レギュレータREG11からダウンコンバータ回路1の電源端子VDDに電源を供給することができない。しかし、この場合は、レギュレータREG21からダウンコンバータ回路1の電源端子VDDに電源を供給することができる。同様に、ダウンコンバータ回路2に電源が供給されない場合、レギュレータREG21からダウンコンバータ回路2の電源端子VDDに電源を供給することができない。しかし、この場合は、レギュレータREG11からダウンコンバータ回路2の電源端子VDDに電源を供給することができる。よって、一方のダウンコンバータ回路が省電力モードであったとしても、他方のダウンコンバータ回路から一方のダウンコンバータに電源を供給することができる。

【0099】

以上で説明したように、本実施の形態にかかるダウンコンバータにより、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法を提供することができる。

【0100】

実施の形態2

次に、本発明の実施の形態2について説明する。図8は、本実施の形態にかかるダウンコンバータを示すブロック図である。図8に示すダウンコンバータでは、ダウンコンバータ回路1のみが水晶振動子X'tal(11)を備えている点が、実施の形態1にかかるダウンコンバータと異なる。これ以外は実施の形態1にかかるダウンコンバータと同様であるので、同一の構成要素には同一の符号を付して重複した説明は省略する。

【0101】

図8に示すように、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1の端子33に水晶振動子X'tal(11)が接続されている。そして、クリスタル発振回路REF11は、水晶振動子X'tal(11)を用いて所定の基準周波数を有する基準信号54を生成し、局部発振器16に出力する。また、基準信号54はバッファB11で増幅されて、ダウンコンバータ回路1の端子34からダウンコンバータ回路2の端子43に出力される。

【0102】

ダウンコンバータ回路2の基準信号生成器25は、ダウンコンバータ回路1から出力された基準信号60(基準信号54をバッファB11で増幅した信号)を用いて基準信号64を生成する。ここで、基準信号54と基準信号64の周波数は典型的には同一である。よって、この場合、ダウンコンバータ回路2が備えるクリスタル発振回路REF21は、ダウンコンバータ回路1から出力された基準信号60を増幅するバッファとして働く。

【0103】

本実施の形態にかかるダウンコンバータでは、中間周波数信号OUT1が出力され、中間周波数信号OUT2が出力されない場合(OUT1がON、OUT2がOFFの場合)、ダウンコンバータ回路2が省電力モードとなる。この場合、制御回路29は、基準信号生成器25、局部発振器26、および周波数変換部27を非動作状態とし、更にLNA2に電源が供給されるようにLNAバイアス回路28を制御する。

【0104】

一方、中間周波数信号OUT2が出力され、中間周波数信号OUT1が出力されない場合(OUT1がOFF、OUT2がONの場合)、ダウンコンバータ回路1が省電力モードとなる。この場合、制御回路19は、局部発振器16および周波数変換部17を非動作状態、基準信号生成器15を動作状態とし、更にLNA1に電源が供給されるようにLNAバイアス回路18を制御する。

【0105】

すなわち、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1が省電力モードの場合(OUT1がOFF、OUT2がONの場合)に、基準信号生成器15を動作状態とすることで、ダウンコンバータ回路2に基準信号60を出力することができる。これにより、ダウンコンバータ回路2の端子43に接続される水晶振動子X'tal(21)(実施の形態1参照)を省略することがでる。水晶振動子はコストの高い部品であるので、水晶振動子を省略することでダウンコンバータの製造コストおよびスペースを効果的に低減することができる。

【0106】

なお、上記ではダウンコンバータ回路2が省電力モードとなる場合、制御回路29が基準信号生成器25を非動作状態としていた。しかし、ダウンコンバータ回路2が省電力モードとなる場合であっても、基準信号生成器25の動作状態を維持するようにしてもよい。

【0107】

また、上記ではダウンコンバータ回路1に水晶振動子を接続した場合について説明した。しかし、ダウンコンバータ回路1に水晶振動子を接続せずにダウンコンバータ回路2の端子43に水晶振動子を接続し、端子44から出力された基準信号をダウンコンバータ回路1の端子33に出力するように構成してもよい。

【0108】

また、上記実施の形態1および2では、垂直偏波信号および水平偏波信号を受信した場合について説明したが、偏波信号として左旋偏波信号および右旋偏波信号を用いてもよい。

【0109】

以上、本発明を上記実施形態に即して説明したが、上記実施形態の構成にのみ限定されるものではなく、本願特許請求の範囲の請求項の発明の範囲内で当業者であればなし得る各種変形、修正、組み合わせを含むことは勿論である。

【符号の説明】

【0110】

1、2 ダウンコンバータ回路

3 増幅部

4 パラボラアンテナ

5 水平偏波信号

6 垂直偏波信号

15、25 基準信号生成器

16、26 局部発振器

17、27 周波数変換部

18、28 LNAバイアス回路

19、29 制御回路

【技術分野】

【0001】

本発明はダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法に関し、特に受信された偏波信号をダウンコンバートするダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法に関する。

【背景技術】

【0002】

受信した衛星放送電波を、ケーブルで伝送可能な中間周波数(以下、IF周波数ともいう)に周波数変換するために、ローノイズブロックダウンコンバータ(LNB:Low Noise Block Downcoverter)が用いられている。

【0003】

図14は、特許文献1に開示されている衛星放送受信用コンバータ(ダウンコンバータ)を説明するためのブロック図である。図14に示す衛星放送受信用コンバータにおいて、パラボナアンテナ(図示せず)にて受信される水平偏波又は垂直偏波のBS信号は、BS信号端子221および222から入力され、BS信号端子221および222の後段には、初段の増幅回路223、224および2段目の増幅回路225が配置されている。初段の増幅回路223、224は、それぞれBS信号端子221および222から入力された水平偏波又は垂直偏波のBS信号を増幅する。そして、2段目の増幅回路225は、初段の増幅回路223または224のいずれかの出力をさらに増幅する。

【0004】

増幅回路223〜225は、高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)等を用いて高周波で動作する低雑音の高周波増幅回路である。増幅回路223または増幅回路224が、水平偏波又は垂直偏波のいずれかを受信するためには、これらの増幅回路に供給する電圧を選択的に切り替える必要がある。このため、衛星放送用コンバータIC201に内蔵したスイッチ回路310にて増幅回路223または増幅回路224に供給する電圧を選択的に切り替える。すなわち、受信するBS信号が水平偏波であるか垂直偏波であるかに応じて、端子211および212、または端子213および214から、増幅回路223または224に必要な電圧を供給する。また、2段目の増幅回路225は、水平偏波又は垂直偏波のBS信号のいずれかを増幅するため、BS信号の受信中は常に端子215および216から必要な電圧が供給される。

【0005】

増幅回路225の出力は、衛星放送用コンバータIC201に内蔵された増幅回路311にてさらに増幅され、周波数変換回路312において中間周波数であるBS−IF信号に変換される。上記BS−IF信号は、後段増幅回路313でさらに増幅された後、キャパシタ204にてDC成分を除去され、ケーブル(図示せず)を介してBSチューナ(図示せず)へ送られる。

【0006】

また、局部発信回路を含むPLL回路314は、10.7GHz〜12.75GHzの受信周波数において、ローバンドの10.7GHz〜11.7GHz帯とハイバンドの11.7GHz〜12.75GHz帯とをBS−IF信号の周波数に周波数変換するための局部発振信号を出力する。

【0007】

スイッチ回路310には、BSチューナから受信偏波の切り替え制御のためのDC電圧信号が入力される。すなわち、スイッチ回路310には、電源電圧を兼ねる13V又は18VのDC電圧信号のいずれかが入力され、スイッチ回路310は、入力されたDC電圧信号の大きさを検出することで初段の増幅回路223および224のどちらを使用するか決定する。

【0008】

スイッチ回路310で検出されたDC電圧信号の電圧の大きさにより、正および負電圧を発生する電圧発生源315は、端子211〜216を通し、増幅回路223および224のいずれか及び増幅回路225に正及び負の電圧を供給する。

【0009】

増幅回路223〜225に使用する高電子移動度トランジスタ(HEMT)は、通常、ゲート端子に負電圧を供給し、ドレイン端子に正電圧を供給することで動作する。例えば、増幅回路223を使用する場合は、衛星放送受信用コンバータIC201は、端子213から負電圧を発生し、HEMTのゲート端子にこの負電圧を供給する。同時に、端子214から正電圧を発生し、HEMTのドレイン端子に正電圧を供給する。このとき、使用しない増幅回路224への電圧供給は、増幅回路224に使用するHEMTが動作しない電圧を端子211および212から供給する。

【0010】

上記した構成において、増幅回路223の出力信号は増幅回路225に供給される。増幅回路225も増幅回路223と同様に動作し、衛星放送受信用コンバータIC201の端子215から出力される負電圧がHEMTのゲート端子に供給される。同時に、端子216から出力される正電圧がHEMTのドレイン端子に供給される。これにより、増幅回路225で増幅されたBS信号は、衛星放送受信用コンバータIC201の増幅回路311に供給される。

【0011】

増幅回路224を使用する場合は、端子211から負電圧を発生し、HEMTのゲート端子に電圧を供給する。同時に、端子212から正電圧を発生し、HEMTのドレイン端子に電圧を供給する。このとき、使用しない増幅回路223へは、増幅回路223に使用するHEMTが動作しない電圧を供給する。

【0012】

図14に示した衛星放送受信用コンバータでは、増幅回路223および224を切り替えるためのスイッチ回路310が、衛星放送受信用コンバータIC201に内蔵されている。すなわち、衛星放送受信用コンバータIC201において、水平偏波又は垂直偏波のいずれかを受信するための増幅回路223または増幅回路224を動作させるための負電圧を発生する回路を備えている。

【0013】

また、特許文献2には、LNB全体のアイソレーションを高めることができるダウンコンバータに関する技術が開示されている。特許文献3には、一つで複数のチャンネルを同時に受信することができるチューナ装置に関する技術が開示されている。非特許文献1には、ユニバーサルシングル型のLNBに関する技術が開示されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2010−268296号公報

【特許文献2】特開2002−190749号公報

【特許文献3】特開2003−198401号公報

【非特許文献】

【0015】

【非特許文献1】Tino Copani, "A 12-GHz Silicon Bipolar Dual-Conversion Receiver for Digital Satellite Applications" IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 40, NO. 6, JUNE 2005

【発明の概要】

【発明が解決しようとする課題】

【0016】

特許文献1に開示されているダウンコンバータICを用いてユニバーサルデュアル(Universal Dual)のダウンコンバータを構成した場合は、例えば図9に示す構成が考えられる(図9に示す構成は、本願発明者により導かれた構成である)。ここで、ユニバーサルデュアルとは、例えばDisEqC(Digital Satellite Equipment Control)の仕様において、中間周波数信号を2つ出力することができる構成である。図9に示すダウンコンバータでは、水平偏波信号(H)105および垂直偏波信号(V)106を1つのパラボラアンテナで受信し、ダウンコンバータ回路101および102からそれぞれ、ダウンコンバート後の中間周波数信号OUT101およびOUT102を出力する。

【0017】

図9に示すダウンコンバータは、増幅部103と、ダウンコンバータ回路101と、ダウンコンバータ回路102とを備える。増幅部103は、パラボラアンテナ104で受信された水平偏波信号105および垂直偏波信号106を増幅する複数の増幅器(低雑音増幅器(LNA:Low Noise Amplifier))を備える。

【0018】

パラボラアンテナ104で受信された水平偏波信号105は、LNA111で増幅されて、LNA113およびLNA114に出力される。LNA113は、LNA111で増幅された水平偏波信号を増幅して、ダウンコンバータ回路101の入力端子131に出力する。LNA114は、LNA111で増幅された水平偏波信号を増幅して、ダウンコンバータ回路102の入力端子141に出力する。

【0019】

パラボラアンテナ104で受信された垂直偏波信号106は、LNA112で増幅されて、LNA115およびLNA116に出力される。LNA115は、LNA112で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路101の入力端子131に出力する。LNA116は、LNA112で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路102の入力端子141に出力する。

【0020】

すなわち、ダウンコンバータ回路101の入力端子131には、LNA111およびLNA113を経由して水平偏波信号105が供給され、LNA112およびLNA115を経由して垂直偏波信号106が供給される。また、ダウンコンバータ回路102の入力端子141には、LNA111およびLNA114を経由して水平偏波信号105が供給され、LNA112およびLNA116を経由して垂直偏波信号106が供給される。

【0021】

ダウンコンバータ回路101は、基準信号生成器115、局部発振器116、周波数変換部117、LNAバイアス回路118、および制御回路119を有する。基準信号生成器115は、クリスタル発振回路REF111とバッファB111とを有する。クリスタル発振回路REF111は、所定の基準周波数を有する基準信号154を生成し、局部発振器116に出力する。ここで、クリスタル発振回路REF111は、端子133に接続された水晶振動子X'tal(111)を用いて基準信号154を生成する。局部発振器116は、基準信号154を用いて局部発振周波数信号153を生成する。

【0022】

周波数変換部117は、プリアンプAMP111と、ミキサーMIXER111と、ローパスフィルタF111と、IFアンプAMP112とを備える。プリアンプAMP111は入力端子131に入力された垂直偏波信号または水平偏波信号を増幅し、ミキサーMIXER111に出力する。ミキサーMIXER111は、局部発振器116から出力された局部発振周波数信号153を用いて、プリアンプAMP111から出力された増幅された垂直偏波信号または水平偏波信号をダウンコンバートする。ダウンコンバートされた垂直偏波信号または水平偏波信号は、フィルタF111で不要成分が除去され、更にIFアンプAMP112で増幅されて、出力端子132から中間周波数信号OUT101として出力される。

【0023】

LNAバイアス回路118は、端子137を介してLNA111に電源を供給し、端子136を介してLNA113に電源を供給し、端子138を介してLNA115に電源を供給する。制御回路119は、制御信号入力端子135から入力されたTone/Pola信号に応じて、LNAバイアス回路118および局部発振器116を制御する。

【0024】

図10は、Tone/Pola信号の一例を示す図である。図10に示すように、Pola(Polarization)信号は、例えば13Vまたは18VのDC電圧信号である。また、Tone信号は、AC成分(22kHz)の信号であり、DC成分であるPola信号に重畳されている。

【0025】

図10に示すように、Tone/Pola信号のDC成分が18Vである場合、制御回路119は、ダウンコンバータ回路101の入力端子131に水平偏波信号が供給されるようにLNAバイアス回路118を制御する。一方、Tone/Pola信号のDC成分が13Vである場合、制御回路119は、ダウンコンバータ回路101の入力端子131に垂直偏波信号が供給されるようにLNAバイアス回路118を制御する。

【0026】

また、Tone/Pola信号のAC成分として22kHzの信号が供給されている場合、制御回路119は、高バンドの局部発振周波数信号153(10.6GHz)が出力されるように局部発振器116を制御する。一方、Tone/Pola信号のAC成分がオフ状態である場合は、制御回路119は、低バンドの局部発振周波数信号153(9.75GHz)が出力されるように局部発振器116を制御する。

【0027】

ダウンコンバータ回路102は、基準信号生成器125、局部発振器126、周波数変換部127、LNAバイアス回路128、および制御回路129を有する。ここで、ダウンコンバータ回路102の構成は、ダウンコンバータ回路101の構成と同様であるので重複した説明は省略する。なお、LNAバイアス回路128は、端子148を介してLNA112に電源を供給し、端子146を介してLNA114に電源を供給し、端子147を介してLNA116に電源を供給する。

【0028】

図11は、図9に示したダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。ダウンコンバータ回路101でダウンコンバートされた中間周波数信号OUT101は、容量素子C112でDC成分が除去されて、ケーブルを介してチューナ(Tuner101)に供給される。一方、チューナ(Tuner101)は、中間周波数信号OUT101を伝送したケーブルと同一のケーブルを介して、ダウンコンバータ回路101に電源およびTone/Pola信号を供給する。ここで、ダウンコンバータ回路101に供給される電源として、Tone/Pola信号のDC成分(13Vまたは18V)が用いられる。

【0029】

Tone/Pola信号のDC成分(13Vまたは18V)は、ストリップラインSL112を介してレギュレータREG111に供給される。レギュレータREG111は、13Vまたは18Vの電圧を、ダウンコンバータ回路101の最大定格にあった電圧に調整してダウンコンバータ回路101の電源端子VDDに供給する。

【0030】

また、Tone/Pola信号は、ストリップラインSL111を介して抵抗素子R112と容量素子C111に供給される。ここで、Pola信号のDC成分は、抵抗素子R111と抵抗素子R112とによって分割される。つまり、Pola信号は、抵抗素子R111と抵抗素子R112とを用いてダウンコンバータ回路101の最大定格にあった電圧に下げられて、制御信号入力端子135に供給される。一方、Tone信号は、容量C111を通過し、ダウンコンバータ回路101の内部でパルスの有無が検出される。

【0031】

また、増幅部103が備えるLNA111、LNA113、およびLNA115には、LNAバイアス回路128を介して電源が供給される。なお、ダウンコンバータ回路102に電源およびTone/Pola信号が供給される場合についても、ダウンコンバータ回路101に電源およびTone/Pola信号が供給される場合と同様である。

【0032】

図12は、図9に示したダウンコンバータの動作を説明するための表である。

中間周波数信号OUT101およびOUT102が出力されない場合は、チューナ(Tuner101、Tuner102)からダウンコンバータ回路101、102に電源が供給されないため、ダウンコンバータ回路101、102はオフ状態となる。これによりLNA111〜116もオフ状態となる。

【0033】

一方、中間周波数信号OUT101およびOUT102が出力される場合、ダウンコンバータ回路101には、LNA111およびLNA113を経由して水平偏波信号105が、またはLNA112およびLNA115を経由して垂直偏波信号106が供給される。また、ダウンコンバータ回路102には、LNA111およびLNA114を経由して水平偏波信号105が、またはLNA112およびLNA116を経由して垂直偏波信号106が供給される。このとき、LNA111およびLNA112は常にオン状態となる。

【0034】

Pola信号がHigh(18V)の場合、LNA113はオン状態、LNA115はオフ状態となり、ダウンコンバータ回路101には水平偏波信号105が供給される。一方、Pola信号がLow(13V)の場合、LNA113はオフ状態、LNA115はオン状態となり、ダウンコンバータ回路101には垂直偏波信号106が供給される。

【0035】

同様に、Pola信号がHigh(18V)の場合、LNA114はオン状態、LNA116はオフ状態となり、ダウンコンバータ回路102には水平偏波信号105が供給される。一方、Pola信号がLow(13V)の場合、LNA114はオフ状態、LNA116はオン状態となり、ダウンコンバータ回路102には垂直偏波信号106が供給される。

【0036】

また、図12に示すように、Tone信号がオフ状態の場合は、局部発振周波数信号153、163として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号153、163として高バンド(10.6GHz)の信号が出力される。なお、中間周波数信号OUT101およびOUT102が出力される場合、チューナ(Tuner101、Tuner102)からダウンコンバータ回路101、102に電源が供給される。

【0037】

次に、中間周波数信号OUT101またはOUT102のみが出力される場合について、図13を用いて説明する。一方の中間周波数信号のみが出力される場合は、中間周波数信号が出力されない方のダウンコンバータ回路をオフ状態とする。これにより、ダウンコンバータの消費電力を低減することができる。

【0038】

まず、中間周波数信号OUT101が出力され、中間周波数信号OUT102が出力されない場合(OUT101がON、OUT102がOFFの場合)について説明する。この場合、ダウンコンバータ回路101には、LNA111およびLNA113がオン状態の時に水平偏波信号105が供給される。一方、中間周波数信号OUT102が出力されない場合は、図11に示すチューナ(Tuner102)からダウンコンバータ回路102に電源が供給されない。このため、垂直偏波信号106を増幅するLNA112に電源が供給されないため、ダウンコンバータ回路101には垂直偏波信号106が供給されない。

【0039】

中間周波数信号OUT102が出力され、中間周波数信号OUT101が出力されない場合(OUT101がOFF、OUT102がONの場合)について説明する。この場合、ダウンコンバータ回路102には、LNA112およびLNA116がオン状態の時に垂直偏波信号106が供給される。一方、中間周波数信号OUT101が出力されない場合は、図11に示すチューナ(Tuner101)からダウンコンバータ回路101に電源が供給されない。このため、水平偏波信号105を増幅するLNA111に電源が供給されないため、ダウンコンバータ回路102には水平偏波信号105が供給されない。

【0040】

換言すると、図9に示すダウンコンバータでは、ダウンコンバータ回路102のLNAバイアス回路128を用いてLNA112に電源を供給している。このため、ダウンコンバータ回路102をオフ状態とするとLNAバイアス回路128もオフ状態となり、LNA112への電源供給も遮断されるため、ダウンコンバータ回路101に垂直偏波信号106を出力することができなくなる。

【0041】

同様に、図9に示すダウンコンバータでは、ダウンコンバータ回路101のLNAバイアス回路118を用いてLNA111に電源を供給している。このため、ダウンコンバータ回路101をオフ状態とするとLNAバイアス回路118もオフ状態となり、LNA111への電源供給も遮断されるため、ダウンコンバータ回路102に水平偏波信号105を出力することができなくなる。これは、ダウンコンバータ回路101および102で、LNA111およびLNA112を共有していることに起因する。

【0042】

このように、特許文献1に開示されているダウンコンバータICを用いてユニバーサルデュアル(Universal Dual)のダウンコンバータを構成した場合、一方のダウンコンバータ回路(101または102)がオフ状態となるとダウンコンバータが正常に動作しないという問題があった。

【課題を解決するための手段】

【0043】

本発明にかかるダウンコンバータは、第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備える。前記第1の制御回路は、前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、前記第2の制御回路は、前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する。

【0044】

本発明にかかるダウンコンバータでは、第1の制御信号が省電力モードを示す信号である場合、第1の局部発振器および第1の周波数変換部を非動作状態とし、且つ第1の増幅器に電源が供給されるように第1のバイアス回路を制御し、第2の制御信号が省電力モードを示す信号である場合、第2の局部発振器および第2の周波数変換部を非動作状態とし、且つ第2の増幅器に電源が供給されるように第2のバイアス回路を制御している。よって、第1のダウンコンバータ回路が省電力モードであっても第1の増幅器をオン状態とすることができるので、第2のダウンコンバータ回路に偏波信号を供給することができる。また、第2のダウンコンバータ回路が省電力モードであっても第2の増幅器をオン状態とすることができるので、第1のダウンコンバータ回路に偏波信号を供給することができる。したがって、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータを提供することができる。

【0045】

本発明にかかるダウンコンバータICは、所定の基準周波数を有する基準信号を生成する基準信号生成器と、前記基準信号を用いて局部発振周波数信号を生成する局部発振器と、増幅器で増幅された偏波信号を前記局部発振周波数信号を用いて中間周波数信号に変換する周波数変換部と、前記増幅器に電源を供給するバイアス回路と、前記基準信号生成器、前記局部発振器、前記周波数変換部、および前記バイアス回路を制御信号に応じて制御する制御回路と、を備える。前記制御回路は、前記制御信号が省電力モードを示す信号である場合、前記局部発振器および前記周波数変換部を非動作状態とし、且つ前記増幅器に電源が供給されるように前記バイアス回路を制御する。

【0046】

本発明にかかるダウンコンバータの制御方法は、第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備えるダウンコンバータの制御方法であって、前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する。

【0047】

本発明にかかるダウンコンバータの制御方法では、第1の制御信号が省電力モードを示す信号である場合、第1の局部発振器および第1の周波数変換部を非動作状態とし、且つ第1の増幅器に電源が供給されるように第1のバイアス回路を制御し、第2の制御信号が省電力モードを示す信号である場合、第2の局部発振器および第2の周波数変換部を非動作状態とし、且つ第2の増幅器に電源が供給されるように第2のバイアス回路を制御している。よって、第1のダウンコンバータ回路が省電力モードであっても第1の増幅器をオン状態とすることができるので、第2のダウンコンバータ回路に偏波信号を供給することができる。また、第2のダウンコンバータ回路が省電力モードであっても第2の増幅器をオン状態とすることができるので、第1のダウンコンバータ回路に偏波信号を供給することができる。したがって、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータの制御方法を提供することができる。

【発明の効果】

【0048】

本発明により、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法を提供することができる。

【図面の簡単な説明】

【0049】

【図1】実施の形態1にかかるダウンコンバータを示すブロック図である。

【図2】実施の形態1にかかるダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。

【図3】実施の形態1にかかるダウンコンバータの動作を説明するための表である。

【図4】実施の形態1にかかるダウンコンバータの動作を説明するための表である。

【図5】実施の形態1にかかるダウンコンバータに用いられるTone/Pola信号を説明するための図である。

【図6】実施の形態1にかかるダウンコンバータが備える局部発振器の一例を示すブロック図である。

【図7】1/1.6分周器の一例を示すブロック図である。

【図8】実施の形態2にかかるダウンコンバータを示すブロック図である。

【図9】本発明の課題を説明するための図である。

【図10】図9に示すダウンコンバータに用いられるTone/Pola信号を説明するための図である。

【図11】図9に示すダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。

【図12】図9に示すダウンコンバータの動作を説明するための表である。

【図13】図9に示すダウンコンバータの動作を説明するための表である。

【図14】特許文献1に開示されているダウンコンバータを説明するためのブロック図である。

【発明を実施するための形態】

【0050】

実施の形態1

以下、図面を参照して本発明の実施の形態について説明する。

図1は本発明の実施の形態1にかかるダウンコンバータを示すブロック図である。図1に示すダウンコンバータは、例えばDisEqC(Digital Satellite Equipment Control)の仕様において、中間周波数信号を2つ出力することができるユニバーサルデュアル(Universal Dual)構成のダウンコンバータである。すなわち、図1に示すダウンコンバータでは、水平偏波信号(H)5および垂直偏波信号(V)6を1つのパラボラアンテナ4で受信し、ダウンコンバータ回路1および2からそれぞれ、ダウンコンバート後の中間周波数信号OUT1およびOUT2を出力する。

【0051】

図1に示すダウンコンバータは、増幅部3と、ダウンコンバータ回路1と、ダウンコンバータ回路2とを備える。ここで、例えば各ダウンコンバータ回路1、2はそれぞれ、1つのICチップに形成されている。すなわち、中間周波数信号を2つ出力することができるユニバーサルデュアル構成のダウンコンバータは、2つのICチップ(ダウンコンバータ回路)を用いて構成することができる。

【0052】

増幅部3は、パラボラアンテナ4で受信された水平偏波信号5および垂直偏波信号6を増幅する複数の増幅器(低雑音増幅器(LNA:Low Noise Amplifier))を備える。ここで、各LNAには、例えば高電子移動度トランジスタ(HEMT)を用いることができる。

【0053】

パラボラアンテナ4で受信された水平偏波信号5は、LNA1(第1の増幅器)で増幅されて、LNA3(第3の増幅器)およびLNA4(第4の増幅器)に出力される。LNA3は、LNA1で増幅された水平偏波信号を増幅して、ダウンコンバータ回路1の入力端子31に出力する。LNA4は、LNA1で増幅された水平偏波信号を増幅して、ダウンコンバータ回路2の入力端子41に出力する。

【0054】

パラボラアンテナ4で受信された垂直偏波信号6は、LNA2(第2の増幅器)で増幅されて、LNA5(第5の増幅器)およびLNA6(第6の増幅器)に出力される。LNA5は、LNA2で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路1の入力端子31に出力する。LNA6は、LNA2で増幅された垂直偏波信号を増幅して、ダウンコンバータ回路2の入力端子41に出力する。

【0055】

すなわち、ダウンコンバータ回路1の入力端子31には、LNA1およびLNA3を経由して水平偏波信号5が供給され、LNA2およびLNA5を経由して垂直偏波信号6が供給される。また、ダウンコンバータ回路2の入力端子41には、LNA1およびLNA4を経由して水平偏波信号5が供給され、LNA2およびLNA6を経由して垂直偏波信号6が供給される。

【0056】

ダウンコンバータ回路1(第1のダウンコンバータ回路)は、基準信号生成器15(第1の基準信号生成器)、局部発振器16(第1の局部発振器)、周波数変換部17(第1の周波数変換部)、LNAバイアス回路18(第1のバイアス回路)、および制御回路19(第1の制御回路)を有する。

【0057】

基準信号生成器15は、クリスタル発振回路REF11とバッファB11とを有する。クリスタル発振回路REF11は、所定の基準周波数を有する基準信号54(第1の基準信号)を生成し、局部発振器16に出力する。ここで、クリスタル発振回路REF11は、端子33に接続された水晶振動子X'tal(11)を用いて基準信号54を生成する。局部発振器16は、基準信号54を用いて局部発振周波数信号53を生成する。

【0058】

周波数変換部17は、プリアンプAMP11と、ミキサーMIXER11と、ローパスフィルタF11と、IFアンプAMP12とを備える。プリアンプAMP11は入力端子31に入力された垂直偏波信号または水平偏波信号を増幅し、ミキサーMIXER11に出力する。ミキサーMIXER11は、局部発振器16から出力された局部発振周波数信号53を用いて、プリアンプAMP11から出力された増幅された垂直偏波信号または水平偏波信号をダウンコンバートする。ダウンコンバートされた垂直偏波信号または水平偏波信号は、フィルタF11で不要成分が除去され、更にIFアンプAMP12で増幅されて、出力端子32から中間周波数信号OUT1として出力される。

【0059】

LNAバイアス回路18は、端子37を介してLNA1に電源を供給し、端子36を介してLNA3に電源を供給し、端子38を介してLNA5に電源を供給する。制御回路19は、制御信号入力端子35から入力されたTone/Pola信号59に応じて、基準信号生成器15、局部発振器16、周波数変換部17、およびLNAバイアス回路18を制御する。

【0060】

ダウンコンバータ回路2(第2のダウンコンバータ回路)は、基準信号生成器25(第2の基準信号生成器)、局部発振器26(第2の局部発振器)、周波数変換部27(第2の周波数変換部)、LNAバイアス回路28(第2のバイアス回路)、および制御回路29(第2の制御回路)を有する。基準信号生成器25は、クリスタル発振回路REF21とバッファB21とを有する。

【0061】

クリスタル発振回路REF21は、所定の基準周波数を有する基準信号64(第2の基準信号)を生成し、局部発振器26に出力する。ここで、クリスタル発振回路REF21は、端子43に接続された水晶振動子X'tal(21)を用いて基準信号64を生成する。なお、基準信号54と基準信号64の周波数は典型的には同一である。局部発振器26は、基準信号64を用いて局部発振周波数信号63を生成する。

【0062】

周波数変換部27は、プリアンプAMP21と、ミキサーMIXER21と、ローパスフィルタF21と、IFアンプAMP22とを備える。プリアンプAMP21は入力端子41に入力された垂直偏波信号または水平偏波信号を増幅し、ミキサーMIXER21に出力する。ミキサーMIXER21は、局部発振器26から出力された局部発振周波数信号63を用いて、プリアンプAMP21から出力された増幅された垂直偏波信号または水平偏波信号をダウンコンバートする。ダウンコンバートされた垂直偏波信号または水平偏波信号は、フィルタF21で不要成分が除去され、更にIFアンプAMP22で増幅されて、出力端子42から中間周波数信号OUT2として出力される。

【0063】

LNAバイアス回路28は、端子48を介してLNA2に電源を供給し、端子46を介してLNA4に電源を供給し、端子47を介してLNA6に電源を供給する。制御回路29は、制御信号入力端子45から入力されたTone/Pola信号69に応じて、基準信号生成器25、局部発振器26、周波数変換部27、およびLNAバイアス回路28を制御する。

【0064】

図2は、本実施の形態にかかるダウンコンバータで用いられるTone/Pola信号の一例を示す図である。図2に示すように、Pola(Polarization)信号は、例えば18VのDC電圧信号、13VのDC電圧信号、または10Vよりも小さいDC電圧信号である。ここで、10Vよりも小さいDC電圧信号が供給される場合とは、典型的にはPola信号が供給されない場合、つまりPola信号のDC信号が非通電の場合である。換言すると、図3に示すチューナからダウンコンバータ回路にDC成分が供給されない場合である。図3に示すチューナからダウンコンバータ回路にDC成分が供給されない場合、抵抗R11、R12を介して制御信号入力端子35で検出される電圧は理想的には0Vである。以下では、Pola信号が供給されない場合を、10Vよりも小さいDC電圧信号が供給される場合の代表例として説明する。

【0065】

Pola信号(第1のモード選択信号)が18VのDC電圧信号である場合、制御回路19は、ダウンコンバータ回路1の入力端子31に水平偏波信号が供給されるようにLNAバイアス回路18を制御する。Pola信号が13VのDC電圧信号である場合、制御回路19は、ダウンコンバータ回路1の入力端子31に垂直偏波信号が供給されるようにLNAバイアス回路18を制御する。このとき、ダウンコンバータ回路1の動作モードは通常動作モードである。一方、Pola信号が供給されない場合、ダウンコンバータ回路1は省電力モードとなる。ダウンコンバータ回路1が省電力モードである場合、制御回路19は、局部発振器16および周波数変換部17を非動作状態とし、LNAバイアス回路18の動作状態を維持する。なお、基準信号生成器15については非動作状態としてもよく、また動作状態を維持してもよい。

【0066】

また、Pola信号(第2のモード選択信号)が18VのDC電圧信号である場合、制御回路29は、ダウンコンバータ回路2の入力端子41に水平偏波信号が供給されるようにLNAバイアス回路28を制御する。Pola信号が13VのDC電圧信号である場合、制御回路29は、ダウンコンバータ回路2の入力端子41に垂直偏波信号が供給されるようにLNAバイアス回路28を制御する。このとき、ダウンコンバータ回路2の動作モードは通常動作モードである。一方、Pola信号が供給されない場合、ダウンコンバータ回路2は省電力モードとなる。ダウンコンバータ回路2が省電力モードである場合、制御回路29は、局部発振器26および周波数変換部27を非動作状態とし、LNAバイアス回路28の動作状態を維持する。なお、基準信号生成器25については非動作状態としてもよく、また動作状態を維持してもよい。

【0067】

図2に示すように、Tone信号は、AC成分(22kHz)の信号であり、DC成分であるPola信号に重畳されている。Tone/Pola信号のAC成分として22kHzのTone信号(第1のバンド選択信号)が供給されている場合、制御回路19は、高バンドの局部発振周波数信号53(例えば、Ku帯の場合は10.6GHz)が出力されるように局部発振器16を制御する。一方、Tone/Pola信号のAC成分がオフ状態である場合は、制御回路19は、低バンドの局部発振周波数信号53(例えば、Ku帯の場合は9.75GHz)が出力されるように局部発振器16を制御する。

【0068】

同様に、Tone/Pola信号のAC成分として22kHzのTone信号(第2のバンド選択信号)が供給されている場合、制御回路29は、高バンドの局部発振周波数信号63(例えば、10.6GHz)が出力されるように局部発振器26を制御する。一方、Tone/Pola信号のAC成分がオフ状態である場合は、制御回路29は、低バンドの局部発振周波数信号63(例えば、9.75GHz)が出力されるように局部発振器26を制御する。

【0069】

図9に示したダウンコンバータでは、図10に示すように18VのDC電圧信号および13VのDC電圧信号のみを使用していた。これに対して本実施の形態にかかるダウンコンバータでは、18VのDC電圧信号および13VのDC電圧信号を用いると共に、10Vよりも小さいDC電圧信号(典型的には、Pola信号が供給されない場合)に新たに省電力モードを設定している。すなわち、本実施の形態にかかるダウンコンバータでは、Pola信号を2bit化することで、制御回路19、29において、(1)水平偏波信号が供給される場合(通常動作モード)、(2)垂直偏波信号が供給される場合(通常動作モード)、(3)省電力モードの3状態を検出することができる。

【0070】

図6は、本実施の形態にかかるダウンコンバータが備える局部発振器16の一例を示すブロック図である(局部発振器26についても同様である)。図6に示すように、局部発振器16は、位相比較器PFDと、ローパスフィルタLPFと、電圧制御発振器VCO11と、複数の分周器FDと、を備える。

【0071】

位相比較器PFDは、クリスタル発振回路REF11で生成された基準信号54と、複数の分周器FDで分周された信号とを入力し、これらの信号の位相差を電圧に変換した信号を出力する。ローパスフィルタLPFは、位相比較器PFDから出力された信号に含まれる不要な成分を除去する。電圧制御発振器VCO11は、ローパスフィルタLPFから出力された信号の電圧に応じて出力信号の周波数を制御する。電圧制御発振器VCO11で生成された出力信号は局部発振周波数信号53として出力される。

【0072】

また、電圧制御発振器VCO11から出力された局部発振周波数信号53は、分周器FD(1/4)、分周器FD(1/2)、および分周器FD(1/39)を経由する第1のパス、または分周器FD(1/4)、分周器FD(1/1.6)、および分周器FD(1/53)を経由する第2のパスで分周される。第1および第2のパスの切り替えは、制御回路19から出力された制御信号を用いてスイッチSW11、SW12を切り替えることで実施することができる。

【0073】

基準信号54の周波数が31.25MHzである場合、制御回路19が第1のパスを選択することで、10.6GHz(=31.25MHz×1/4×1/2×1/39)の局部発振周波数信号(低バンド)53を生成することができる。一方、制御回路19が第2のパスを選択することで、9.75GHz(=31.25MHz×1/4×1/1.6×1/53)の局部発振周波数信号(高バンド)53を生成することができる。

【0074】

ここで、分周器FD(1/1.6)は、例えば図7に示すように、分周器FD(1/2)、分周器FD(1/4)、およびイメージ除去ミキサーIRM(Image rejection mixer)を用いて構成することができる。

【0075】

図3は、図1に示したダウンコンバータに電源およびTone/Pola信号を供給する場合を説明するための図である。ダウンコンバータ回路1でダウンコンバートされた中間周波数信号OUT1は、容量素子C12でDC成分が除去されて、ケーブルを介してチューナ(Tuner1:第1のチューナ)に供給される。一方、チューナ(Tuner1)は、中間周波数信号OUT1を伝送したケーブルと同一のケーブルを介して、ダウンコンバータ回路1に電源およびTone/Pola信号を供給する。ここで、ダウンコンバータ回路1には電源として、Tone/Pola信号のDC成分(18VのDC電圧信号、13VのDC電圧信号、または10Vよりも小さいDC電圧信号(典型的には0Vであり、この場合、DC成分は非通電となる))が供給される。

【0076】

Tone/Pola信号のDC成分(13Vまたは18V)は、ストリップラインSL12を介してレギュレータREG11(第1のレギュレータ)に供給される。レギュレータREG11は、13Vまたは18Vの電圧を、ダウンコンバータ回路1の最大定格にあった電圧に調整してダウンコンバータ回路1の電源端子VDDに供給する。

【0077】

また、Tone/Pola信号は、ストリップラインSL11を介して抵抗素子R12と容量素子C11に供給される。ここで、Pola信号のDC成分は、抵抗素子R11と抵抗素子R12とによって分割される。つまり、Pola信号は、抵抗素子R11と抵抗素子R12とを用いてダウンコンバータ回路1の最大定格にあった電圧に下げられて、制御信号入力端子35に供給される。一方、Tone信号は、容量C11を通過し、ダウンコンバータ回路1の内部でパルスの有無が検出される。増幅部3が備えるLNA1、LNA3、およびLNA5には、LNAバイアス回路28を介して電源が供給される。

【0078】

同様に、ダウンコンバータ回路2でダウンコンバートされた中間周波数信号OUT2は、容量素子C22でDC成分が除去されて、ケーブルを介してチューナ(Tuner2:第2のチューナ)に供給される。一方、チューナ(Tuner2)は、中間周波数信号OUT2を伝送したケーブルと同一のケーブルを介して、ダウンコンバータ回路2に電源およびTone/Pola信号を供給する。ここで、ダウンコンバータ回路2には電源として、Tone/Pola信号のDC成分(18VのDC電圧信号、13VのDC電圧信号、または10Vよりも小さいDC電圧信号(典型的には0Vであり、この場合、DC成分は非通電となる))が供給される。

【0079】

Tone/Pola信号のDC成分(13Vまたは18V)は、ストリップラインSL22を介してレギュレータREG21(第2のレギュレータ)に供給される。レギュレータREG21は、13Vまたは18Vの電圧を、ダウンコンバータ回路2の最大定格にあった電圧に調整してダウンコンバータ回路2の電源端子VDDに供給する。

【0080】

また、Tone/Pola信号は、ストリップラインSL21を介して抵抗素子R22と容量素子C21に供給される。ここで、Pola信号のDC成分は、抵抗素子R21と抵抗素子R22とによって分割される。つまり、Pola信号は、抵抗素子R21と抵抗素子R22とを用いてダウンコンバータ回路2の最大定格にあった電圧に下げられて、制御信号入力端子45に供給される。一方、Tone信号は、容量C21を通過し、ダウンコンバータ回路2の内部でパルスの有無が検出される。増幅部3が備えるLNA2、LNA4、およびLNA6には、LNAバイアス回路28を介して電源が供給される。

【0081】

ここで、本実施の形態にかかるダウンコンバータでは、レギュレータREG11からダウンコンバータ回路2の電源端子VDDにも電源が供給可能に構成されている。また、レギュレータREG21からダウンコンバータ回路1の電源端子VDDにも電源が供給可能に構成されている。すなわち、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1に電源が供給されない場合、つまりダウンコンバータ回路1にTone/Pola信号が供給されない場合、レギュレータREG11からダウンコンバータ回路1の電源端子VDDに電源を供給することができない。しかし、この場合は、ダウンコンバータ回路2に電源が供給されているので(つまり、ダウンコンバータ回路2には電源としてTone/Pola信号のDC成分(13Vまたは18V)が供給されているので)、レギュレータREG21からダウンコンバータ回路1の電源端子VDDに電源を供給することができる。

【0082】

同様に、ダウンコンバータ回路2に電源が供給されない場合、つまりダウンコンバータ回路2にTone/Pola信号が供給されない場合、レギュレータREG21からダウンコンバータ回路2の電源端子VDDに電源を供給することができない。しかし、この場合は、ダウンコンバータ回路1に電源が供給されているので(つまり、ダウンコンバータ回路1には電源としてTone/Pola信号のDC成分(13Vまたは18V)が供給されているので)、レギュレータREG11からダウンコンバータ回路2の電源端子VDDに電源を供給することができる。

【0083】

図4は、図1に示したダウンコンバータの動作を説明するための表である。

中間周波数信号OUT1およびOUT2が出力されない場合は、チューナ(Tuner1、Tuner2)からダウンコンバータ回路1、2に電源が供給されないため、ダウンコンバータ回路1、2はオフ状態となる。これによりLNA1〜6もオフ状態となる。

【0084】

一方、中間周波数信号OUT1およびOUT2が出力される場合、ダウンコンバータ回路1には、LNA1およびLNA3を経由して水平偏波信号105が、またはLNA2およびLNA5を経由して垂直偏波信号6が供給される。また、ダウンコンバータ回路2には、LNA1およびLNA4を経由して水平偏波信号5が、またはLNA2およびLNA6を経由して垂直偏波信号6が供給される。このとき、LNA1およびLNA2は常にオン状態となる。

【0085】

また、Pola信号がHigh(18V)の場合、LNA3はオン状態、LNA5はオフ状態となり、ダウンコンバータ回路1には水平偏波信号5が供給される。一方、Pola信号がLow(13V)の場合、LNA3はオフ状態、LNA5はオン状態となり、ダウンコンバータ回路1には垂直偏波信号6が供給される。なお、LNA1、LNA3、およびLNA5のオン状態・オフ状態の切り替えは、LNAバイアス回路18からの電源供給の有無を切り替えることで実施することができる。また、LNAバイアス回路18からの電源供給の有無は、制御回路19から出力される制御信号によって制御される。

【0086】

同様に、Pola信号がHigh(18V)の場合、LNA4はオン状態、LNA6はオフ状態となり、ダウンコンバータ回路2には水平偏波信号5が供給される。一方、Pola信号がLow(13V)の場合、LNA4はオフ状態、LNA6はオン状態となり、ダウンコンバータ回路2には垂直偏波信号6が供給される。なお、LNA2、LNA4、およびLNA6のオン状態・オフ状態の切り替えは、LNAバイアス回路28からの電源供給の有無を切り替えることで実施することができる。また、LNAバイアス回路28からの電源供給の有無は、制御回路29から出力される制御信号によって制御される。

【0087】

また、図4に示すように、Tone信号がオフ状態の場合は、局部発振周波数信号53、63として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号53、63として高バンド(10.6GHz)の信号が出力される。なお、中間周波数信号OUT1およびOUT2が出力される場合、チューナ(Tuner1、Tuner2)からダウンコンバータ回路1、2に電源が供給される。

【0088】

次に、中間周波数信号OUT1またはOUT2のみが出力される場合について、図5を用いて説明する。一方の中間周波数信号のみが出力される場合は、中間周波数信号が出力されない方のダウンコンバータ回路をオフ状態とする。これにより、ダウンコンバータの消費電力を低減することができる。

【0089】

まず、中間周波数信号OUT1が出力され、中間周波数信号OUT2が出力されない場合(OUT1がON、OUT2がOFFの場合)について説明する。このとき、ダウンコンバータ回路2が省電力モードとなるので、制御回路29は、基準信号生成器25、局部発振器26、および周波数変換部27を非動作状態とし、更にLNA2に電源が供給されるようにLNAバイアス回路28を制御する。なお、この場合、レギュレータREG11からダウンコンバータ回路2に電源が供給される。

【0090】

LNA1およびLNA3がオン状態の時、ダウンコンバータ回路1には水平偏波信号5が供給される。一方、LNA2およびLNA5がオン状態の時、ダウンコンバータ回路1には垂直偏波信号6が供給される。また、Tone信号がオフ状態の場合は、局部発振周波数信号53として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号53として高バンド(10.6GHz)の信号が出力される。

【0091】

次に、中間周波数信号OUT2が出力され、中間周波数信号OUT1が出力されない場合(OUT1がOFF、OUT2がONの場合)について説明する。このとき、ダウンコンバータ回路1が省電力モードとなるので、制御回路19は、基準信号生成器15、局部発振器16、および周波数変換部17を非動作状態とし、更にLNA1に電源が供給されるようにLNAバイアス回路18を制御する。なお、この場合、レギュレータREG21からダウンコンバータ回路1に電源が供給される。

【0092】

LNA1およびLNA4がオン状態の時、ダウンコンバータ回路2には水平偏波信号5が供給される。一方、LNA2およびLNA6がオン状態の時、ダウンコンバータ回路1には垂直偏波信号6が供給される。また、Tone信号がオフ状態の場合は、局部発振周波数信号63として低バンド(9.75GHz)の信号が出力される。一方、22kHzのTone信号が重畳されている場合は、局部発振周波数信号63として高バンド(10.6GHz)の信号が出力される。

【0093】

図9に示したダウンコンバータでは、ダウンコンバータ回路102のLNAバイアス回路128を用いてLNA112に電源を供給していた。このため、ダウンコンバータ回路102をオフ状態とするとLNAバイアス回路128もオフ状態となり、LNA112への電源供給も遮断されるため、ダウンコンバータ回路101に垂直偏波信号106を出力することができなかった。また、図9に示したダウンコンバータでは、ダウンコンバータ回路101のLNAバイアス回路118を用いてLNA111に電源を供給していた。このため、ダウンコンバータ回路101をオフ状態とするとLNAバイアス回路118もオフ状態となり、LNA111への電源供給も遮断されるため、ダウンコンバータ回路102に水平偏波信号105を出力することができなかった。

【0094】

このように、特許文献1に開示されているダウンコンバータICを用いてユニバーサルデュアル(Universal Dual)のダウンコンバータを構成した場合、一方のダウンコンバータ回路(101または102)がオフ状態となるとダウンコンバータが正常に動作しないという問題があった。したがって、特許文献1に開示されているダウンコンバータICはユニバーサルシングル(Universal Single)の構成にしか使用できなかった。また、特許文献1に開示されているダウンコンバータICをユニバーサルデュアル(Universal Dual)のダウンコンバータに使用する場合には、LNAへの電源供給を別電源を用いて供給する必要があった。この場合は、消費電力およびコストが増加し、またダウンコンバータの仕様が複雑になるという問題があった。

【0095】

これに対して、図1に示した本実施の形態にかかるダウンコンバータでは、18VのDC電圧信号および13VのDC電圧信号を用いると共に、10Vよりも小さいDC電圧信号(典型的には、Pola信号が供給されない場合)に新たに省電力モードを設定している。すなわち、本実施の形態にかかるダウンコンバータでは、Pola信号を2bit化することで、制御回路19、29において、(1)水平偏波信号が供給される場合(通常動作モード)、(2)垂直偏波信号が供給される場合(通常動作モード)、(3)省電力モードの3状態を検出することができる。

【0096】

そして、制御回路19は、制御信号(Pola信号)が省電力モードを示す信号である場合、局部発振器16および周波数変換部17を非動作状態とし、更にLNA1に電源が供給されるようにLNAバイアス回路18を制御している。また、制御回路29は、制御信号(Pola信号)が省電力モードを示す信号である場合、局部発振器26および周波数変換部27を非動作状態とし、更にLNA2に電源が供給されるようにLNAバイアス回路28を制御している。よって、ダウンコンバータ回路1が省電力モードであってもLNA1をオン状態とすることができるので、ダウンコンバータ回路2に水平偏波信号5を供給することができる。また、ダウンコンバータ回路2が省電力モードであってもLNA2をオン状態とすることができるので、ダウンコンバータ回路1に垂直偏波信号6を供給することができる。

【0097】

また、本実施の形態にかかるダウンコンバータでは、レギュレータREG11からダウンコンバータ回路2の電源端子VDDに電源が供給可能に構成されている。同様に、レギュレータREG21からダウンコンバータ回路1の電源端子VDDに電源が供給可能に構成されている。

【0098】

すなわち、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1に電源が供給されない場合、レギュレータREG11からダウンコンバータ回路1の電源端子VDDに電源を供給することができない。しかし、この場合は、レギュレータREG21からダウンコンバータ回路1の電源端子VDDに電源を供給することができる。同様に、ダウンコンバータ回路2に電源が供給されない場合、レギュレータREG21からダウンコンバータ回路2の電源端子VDDに電源を供給することができない。しかし、この場合は、レギュレータREG11からダウンコンバータ回路2の電源端子VDDに電源を供給することができる。よって、一方のダウンコンバータ回路が省電力モードであったとしても、他方のダウンコンバータ回路から一方のダウンコンバータに電源を供給することができる。

【0099】

以上で説明したように、本実施の形態にかかるダウンコンバータにより、複数のダウンコンバータ回路を用いてユニバーサルデュアルのダウンコンバータを構成した場合であっても、正常に動作させることができるダウンコンバータ、ダウンコンバータIC、およびダウンコンバータの制御方法を提供することができる。

【0100】

実施の形態2

次に、本発明の実施の形態2について説明する。図8は、本実施の形態にかかるダウンコンバータを示すブロック図である。図8に示すダウンコンバータでは、ダウンコンバータ回路1のみが水晶振動子X'tal(11)を備えている点が、実施の形態1にかかるダウンコンバータと異なる。これ以外は実施の形態1にかかるダウンコンバータと同様であるので、同一の構成要素には同一の符号を付して重複した説明は省略する。

【0101】

図8に示すように、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1の端子33に水晶振動子X'tal(11)が接続されている。そして、クリスタル発振回路REF11は、水晶振動子X'tal(11)を用いて所定の基準周波数を有する基準信号54を生成し、局部発振器16に出力する。また、基準信号54はバッファB11で増幅されて、ダウンコンバータ回路1の端子34からダウンコンバータ回路2の端子43に出力される。

【0102】

ダウンコンバータ回路2の基準信号生成器25は、ダウンコンバータ回路1から出力された基準信号60(基準信号54をバッファB11で増幅した信号)を用いて基準信号64を生成する。ここで、基準信号54と基準信号64の周波数は典型的には同一である。よって、この場合、ダウンコンバータ回路2が備えるクリスタル発振回路REF21は、ダウンコンバータ回路1から出力された基準信号60を増幅するバッファとして働く。

【0103】

本実施の形態にかかるダウンコンバータでは、中間周波数信号OUT1が出力され、中間周波数信号OUT2が出力されない場合(OUT1がON、OUT2がOFFの場合)、ダウンコンバータ回路2が省電力モードとなる。この場合、制御回路29は、基準信号生成器25、局部発振器26、および周波数変換部27を非動作状態とし、更にLNA2に電源が供給されるようにLNAバイアス回路28を制御する。

【0104】

一方、中間周波数信号OUT2が出力され、中間周波数信号OUT1が出力されない場合(OUT1がOFF、OUT2がONの場合)、ダウンコンバータ回路1が省電力モードとなる。この場合、制御回路19は、局部発振器16および周波数変換部17を非動作状態、基準信号生成器15を動作状態とし、更にLNA1に電源が供給されるようにLNAバイアス回路18を制御する。

【0105】

すなわち、本実施の形態にかかるダウンコンバータでは、ダウンコンバータ回路1が省電力モードの場合(OUT1がOFF、OUT2がONの場合)に、基準信号生成器15を動作状態とすることで、ダウンコンバータ回路2に基準信号60を出力することができる。これにより、ダウンコンバータ回路2の端子43に接続される水晶振動子X'tal(21)(実施の形態1参照)を省略することがでる。水晶振動子はコストの高い部品であるので、水晶振動子を省略することでダウンコンバータの製造コストおよびスペースを効果的に低減することができる。

【0106】

なお、上記ではダウンコンバータ回路2が省電力モードとなる場合、制御回路29が基準信号生成器25を非動作状態としていた。しかし、ダウンコンバータ回路2が省電力モードとなる場合であっても、基準信号生成器25の動作状態を維持するようにしてもよい。

【0107】

また、上記ではダウンコンバータ回路1に水晶振動子を接続した場合について説明した。しかし、ダウンコンバータ回路1に水晶振動子を接続せずにダウンコンバータ回路2の端子43に水晶振動子を接続し、端子44から出力された基準信号をダウンコンバータ回路1の端子33に出力するように構成してもよい。

【0108】

また、上記実施の形態1および2では、垂直偏波信号および水平偏波信号を受信した場合について説明したが、偏波信号として左旋偏波信号および右旋偏波信号を用いてもよい。

【0109】

以上、本発明を上記実施形態に即して説明したが、上記実施形態の構成にのみ限定されるものではなく、本願特許請求の範囲の請求項の発明の範囲内で当業者であればなし得る各種変形、修正、組み合わせを含むことは勿論である。

【符号の説明】

【0110】

1、2 ダウンコンバータ回路

3 増幅部

4 パラボラアンテナ

5 水平偏波信号

6 垂直偏波信号

15、25 基準信号生成器

16、26 局部発振器

17、27 周波数変換部

18、28 LNAバイアス回路

19、29 制御回路

【特許請求の範囲】

【請求項1】

第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、

第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、

第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備え、

前記第1の制御回路は、前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、

前記第2の制御回路は、前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する、

ダウンコンバータ。

【請求項2】

前記第1の基準信号生成器は水晶振動子を用いて前記第1の基準信号を生成する水晶発振回路を備え、

前記第2の基準信号生成器は前記第1の基準信号生成器で生成された前記第1の基準信号を前記第2の基準信号とし、

前記第1の制御回路は、前記第1の制御信号が省電力モードを示す信号であっても、前記第1の基準信号生成器を動作状態とする、

請求項1に記載のダウンコンバータ。

【請求項3】

前記第1の制御信号は、増幅された前記第1の偏波信号を前記増幅部が前記第1のダウンコンバータ回路に出力する状態と、増幅された前記第2の偏波信号を前記増幅部が第1のダウンコンバータ回路に出力する状態と、前記第1のダウンコンバータ回路を省電力モードとする状態と、を切り替える第1のモード選択信号を含み、

前記第2の制御信号は、増幅された前記第1の偏波信号を前記増幅部が前記第2のダウンコンバータ回路に出力する状態と、増幅された前記第2の偏波信号を前記増幅部が前記第2のダウンコンバータ回路に出力する状態と、前記第2のダウンコンバータ回路を省電力モードとする状態と、を切り替える第2のモード選択信号を含む、

請求項1または2に記載のダウンコンバータ。

【請求項4】

前記第1および第2のモード選択信号はDC成分の信号であり、3つの電位状態を用いて前記各状態のうちのいずれかを選択する、請求項3に記載のダウンコンバータ。

【請求項5】

前記第1の制御信号は、前記第1の局部発振器から出力される前記第1の局部発振周波数信号の周波数を切り替える第1のバンド選択信号を含み、

前記第2の制御信号は、前記第2の局部発振器から出力される前記第2の局部発振周波数信号の周波数を切り替える第2のバンド選択信号を含み、

前記第1および第2のバンド選択信号はそれぞれ前記第1および第2のモード選択信号に重畳されたAC成分の信号である、

請求項3または4に記載のダウンコンバータ。

【請求項6】

前記第1のダウンコンバータ回路から出力された中間周波数信号が第1の出力端子を介して供給される第1のチューナから前記第1の出力端子を介して供給された直流電圧を調整し前記第1および第2のダウンコンバータ回路に出力する第1のレギュレータと、

前記第2のダウンコンバータ回路から出力された中間周波数信号が第2の出力端子を介して供給される第2のチューナから前記第2の出力端子を介して供給された直流電圧を調整し前記第1および第2のダウンコンバータ回路に出力する第2のレギュレータと、を備える

請求項1乃至5のいずれか一項に記載のダウンコンバータ。

【請求項7】

前記第1および第2の周波数変換部はそれぞれ、

前記増幅部で増幅された信号を増幅するプリアンプと、

前記プリアンプから出力された信号を前記第1または第2の局部発振周波数信号を用いて中間周波数信号に変換するミキサーと、

前記ミキサーから出力された信号の高周波成分を除去する第1のローパスフィルタと、

前記第1のローパスフィルタから出力された信号を増幅するIFアンプと、

を有する請求項1乃至6のいずれか一項に記載のダウンコンバータ。

【請求項8】

前記増幅部は更に、

前記第1の増幅器から出力された信号を入力し、当該信号を増幅して前記第1のダウンコンバータ回路に出力する第3の増幅器と、

前記第1の増幅器から出力された信号を入力し、当該信号を増幅して前記第2のダウンコンバータ回路に出力する第4の増幅器と、

前記第2の増幅器から出力された信号を入力し、当該信号を増幅して前記第1のダウンコンバータ回路に出力する第5の増幅器と、

前記第2の増幅器から出力された信号を入力し、当該信号を増幅して前記第2のダウンコンバータ回路に出力する第6の増幅器と、を備え

前記第1の増幅器、前記第3の増幅器、および前記第5の増幅器は前記第1のバイアス回路から電源が供給され、

前記第2の増幅器、前記第4の増幅器、および前記第6の増幅器は前記第2のバイアス回路から電源が供給される、

請求項1乃至7のいずれか一項に記載のダウンコンバータ。

【請求項9】

前記第1および第2の局部発振器はそれぞれ、

位相比較器と、

前記位相比較器から出力された信号の不要成分を除去する第2のローパスフィルタと、

前記第2のローパスフィルタから出力された信号の電圧に応じて出力信号の周波数を制御する電圧制御発振器と、

前記電圧制御発振器から出力された出力信号を分周する分周器と、を備え、

前記分周器は、前記電圧制御発振器から出力された出力信号を第1の分周比に分周する第1のパスと、前記電圧制御発振器から出力された出力信号を第2の分周比に分周する第2のパスとを有し、前記第1および第2のバンド選択信号に応じて前記電圧制御発振器から出力された出力信号を分周するパスを切り替える、

請求項1乃至8のいずれか一項に記載のダウンコンバータ。

【請求項10】

前記第1の偏波信号は垂直偏波信号および水平偏波信号のうちのいずれか一方であり、前記第2の偏波信号は前記垂直偏波信号および前記水平偏波信号のうちの他方である、請求項1乃至9のいずれか一項に記載のダウンコンバータ。

【請求項11】

前記第1のダウンコンバータ回路および前記第2のダウンコンバータ回路はそれぞれ、1つのICチップに形成されている、請求項1乃至10のいずれか一項に記載のダウンコンバータ。

【請求項12】

所定の基準周波数を有する基準信号を生成する基準信号生成器と、

前記基準信号を用いて局部発振周波数信号を生成する局部発振器と、

増幅器で増幅された偏波信号を前記局部発振周波数信号を用いて中間周波数信号に変換する周波数変換部と、

前記増幅器に電源を供給するバイアス回路と、

前記基準信号生成器、前記局部発振器、前記周波数変換部、および前記バイアス回路を制御信号に応じて制御する制御回路と、を備え、

前記制御回路は、前記制御信号が省電力モードを示す信号である場合、前記局部発振器および前記周波数変換部を非動作状態とし、且つ前記増幅器に電源が供給されるように前記バイアス回路を制御する、

ダウンコンバータIC。

【請求項13】

第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、

第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、

第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備えるダウンコンバータの制御方法であって、

前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、

前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する、

ダウンコンバータの制御方法。

【請求項1】

第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、

第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、

第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備え、

前記第1の制御回路は、前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、

前記第2の制御回路は、前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する、

ダウンコンバータ。

【請求項2】

前記第1の基準信号生成器は水晶振動子を用いて前記第1の基準信号を生成する水晶発振回路を備え、

前記第2の基準信号生成器は前記第1の基準信号生成器で生成された前記第1の基準信号を前記第2の基準信号とし、

前記第1の制御回路は、前記第1の制御信号が省電力モードを示す信号であっても、前記第1の基準信号生成器を動作状態とする、

請求項1に記載のダウンコンバータ。

【請求項3】

前記第1の制御信号は、増幅された前記第1の偏波信号を前記増幅部が前記第1のダウンコンバータ回路に出力する状態と、増幅された前記第2の偏波信号を前記増幅部が第1のダウンコンバータ回路に出力する状態と、前記第1のダウンコンバータ回路を省電力モードとする状態と、を切り替える第1のモード選択信号を含み、

前記第2の制御信号は、増幅された前記第1の偏波信号を前記増幅部が前記第2のダウンコンバータ回路に出力する状態と、増幅された前記第2の偏波信号を前記増幅部が前記第2のダウンコンバータ回路に出力する状態と、前記第2のダウンコンバータ回路を省電力モードとする状態と、を切り替える第2のモード選択信号を含む、

請求項1または2に記載のダウンコンバータ。

【請求項4】

前記第1および第2のモード選択信号はDC成分の信号であり、3つの電位状態を用いて前記各状態のうちのいずれかを選択する、請求項3に記載のダウンコンバータ。

【請求項5】

前記第1の制御信号は、前記第1の局部発振器から出力される前記第1の局部発振周波数信号の周波数を切り替える第1のバンド選択信号を含み、

前記第2の制御信号は、前記第2の局部発振器から出力される前記第2の局部発振周波数信号の周波数を切り替える第2のバンド選択信号を含み、

前記第1および第2のバンド選択信号はそれぞれ前記第1および第2のモード選択信号に重畳されたAC成分の信号である、

請求項3または4に記載のダウンコンバータ。

【請求項6】

前記第1のダウンコンバータ回路から出力された中間周波数信号が第1の出力端子を介して供給される第1のチューナから前記第1の出力端子を介して供給された直流電圧を調整し前記第1および第2のダウンコンバータ回路に出力する第1のレギュレータと、

前記第2のダウンコンバータ回路から出力された中間周波数信号が第2の出力端子を介して供給される第2のチューナから前記第2の出力端子を介して供給された直流電圧を調整し前記第1および第2のダウンコンバータ回路に出力する第2のレギュレータと、を備える

請求項1乃至5のいずれか一項に記載のダウンコンバータ。

【請求項7】

前記第1および第2の周波数変換部はそれぞれ、

前記増幅部で増幅された信号を増幅するプリアンプと、

前記プリアンプから出力された信号を前記第1または第2の局部発振周波数信号を用いて中間周波数信号に変換するミキサーと、

前記ミキサーから出力された信号の高周波成分を除去する第1のローパスフィルタと、

前記第1のローパスフィルタから出力された信号を増幅するIFアンプと、

を有する請求項1乃至6のいずれか一項に記載のダウンコンバータ。

【請求項8】

前記増幅部は更に、

前記第1の増幅器から出力された信号を入力し、当該信号を増幅して前記第1のダウンコンバータ回路に出力する第3の増幅器と、

前記第1の増幅器から出力された信号を入力し、当該信号を増幅して前記第2のダウンコンバータ回路に出力する第4の増幅器と、

前記第2の増幅器から出力された信号を入力し、当該信号を増幅して前記第1のダウンコンバータ回路に出力する第5の増幅器と、

前記第2の増幅器から出力された信号を入力し、当該信号を増幅して前記第2のダウンコンバータ回路に出力する第6の増幅器と、を備え

前記第1の増幅器、前記第3の増幅器、および前記第5の増幅器は前記第1のバイアス回路から電源が供給され、

前記第2の増幅器、前記第4の増幅器、および前記第6の増幅器は前記第2のバイアス回路から電源が供給される、

請求項1乃至7のいずれか一項に記載のダウンコンバータ。

【請求項9】

前記第1および第2の局部発振器はそれぞれ、

位相比較器と、

前記位相比較器から出力された信号の不要成分を除去する第2のローパスフィルタと、

前記第2のローパスフィルタから出力された信号の電圧に応じて出力信号の周波数を制御する電圧制御発振器と、

前記電圧制御発振器から出力された出力信号を分周する分周器と、を備え、

前記分周器は、前記電圧制御発振器から出力された出力信号を第1の分周比に分周する第1のパスと、前記電圧制御発振器から出力された出力信号を第2の分周比に分周する第2のパスとを有し、前記第1および第2のバンド選択信号に応じて前記電圧制御発振器から出力された出力信号を分周するパスを切り替える、

請求項1乃至8のいずれか一項に記載のダウンコンバータ。

【請求項10】

前記第1の偏波信号は垂直偏波信号および水平偏波信号のうちのいずれか一方であり、前記第2の偏波信号は前記垂直偏波信号および前記水平偏波信号のうちの他方である、請求項1乃至9のいずれか一項に記載のダウンコンバータ。

【請求項11】

前記第1のダウンコンバータ回路および前記第2のダウンコンバータ回路はそれぞれ、1つのICチップに形成されている、請求項1乃至10のいずれか一項に記載のダウンコンバータ。

【請求項12】

所定の基準周波数を有する基準信号を生成する基準信号生成器と、

前記基準信号を用いて局部発振周波数信号を生成する局部発振器と、

増幅器で増幅された偏波信号を前記局部発振周波数信号を用いて中間周波数信号に変換する周波数変換部と、

前記増幅器に電源を供給するバイアス回路と、

前記基準信号生成器、前記局部発振器、前記周波数変換部、および前記バイアス回路を制御信号に応じて制御する制御回路と、を備え、

前記制御回路は、前記制御信号が省電力モードを示す信号である場合、前記局部発振器および前記周波数変換部を非動作状態とし、且つ前記増幅器に電源が供給されるように前記バイアス回路を制御する、

ダウンコンバータIC。

【請求項13】

第1の偏波信号が供給される第1の増幅器と、第2の偏波信号が供給される第2の増幅器とを少なくとも備える増幅部と、

第1の基準周波数を有する第1の基準信号を生成する第1の基準信号生成器と、前記第1の基準信号を用いて第1の局部発振周波数信号を生成する第1の局部発振器と、前記増幅部で増幅された信号を前記第1の局部発振周波数信号を用いて中間周波数信号に変換する第1の周波数変換部と、前記第1の増幅器に電源を供給する第1のバイアス回路と、前記第1の基準信号生成器、前記第1の局部発振器、前記第1の周波数変換部、および前記第1のバイアス回路を第1の制御信号に応じて制御する第1の制御回路と、を有する第1のダウンコンバータ回路と、

第2の基準周波数を有する第2の基準信号を生成する第2の基準信号生成器と、前記第2の基準信号を用いて第2の局部発振周波数信号を生成する第2の局部発振器と、前記増幅部で増幅された信号を前記第2の局部発振周波数信号を用いて中間周波数信号に変換する第2の周波数変換部と、前記第2の増幅器に電源を供給する第2のバイアス回路と、前記第2の基準信号生成器、前記第2の局部発振器、前記第2の周波数変換部、および前記第2のバイアス回路を第2の制御信号に応じて制御する第2の制御回路と、を有する第2のダウンコンバータ回路と、を備えるダウンコンバータの制御方法であって、

前記第1の制御信号が省電力モードを示す信号である場合、前記第1の局部発振器および前記第1の周波数変換部を非動作状態とし、且つ前記第1の増幅器に電源が供給されるように前記第1のバイアス回路を制御し、

前記第2の制御信号が省電力モードを示す信号である場合、前記第2の局部発振器および前記第2の周波数変換部を非動作状態とし、且つ前記第2の増幅器に電源が供給されるように前記第2のバイアス回路を制御する、

ダウンコンバータの制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−244236(P2012−244236A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−109529(P2011−109529)

【出願日】平成23年5月16日(2011.5.16)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月16日(2011.5.16)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]