ダマシン配線の形成方法

【課題】基板に形成された溝部に配線材料を埋め込むダマシン配線の形成方法であって、カバレッジの悪いシード層を修理することができ、電解めっき時に配線材料を安定的に成長させ、ボイド等の不具合発生を抑制することのできるダマシン配線の形成方法を提供する。

【解決手段】スパッタ成膜されたシード層5に、分散剤に溶かした配線材料のナノパーティクル含有溶液7を塗布するステップと、前記ナノパーティクル含有溶液7上に有機溶媒を塗布しエッチバックするステップと、前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行する。

【解決手段】スパッタ成膜されたシード層5に、分散剤に溶かした配線材料のナノパーティクル含有溶液7を塗布するステップと、前記ナノパーティクル含有溶液7上に有機溶媒を塗布しエッチバックするステップと、前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、カバレッジの悪いシード層を修理するダマシン配線の形成方法に関する。

【背景技術】

【0002】

半導体デバイスの高集積化、高性能化に伴い、従来のアルミニウム(Al)配線よりも電気抵抗率の低い銅(Cu)配線の適用が検討されている。この銅配線は、基板上へのドライエッチングによる配線処理が困難であることから、絶縁素材の基板に形成された溝部に銅配線を埋め込むダマシン法が主流である。

【0003】

ダマシン法では、層間絶縁膜に予め所定の溝を形成しておき、その溝に配線材料を埋め込み、その後に溝外の余剰な配線材料を化学的機械研磨(CMPプロセス)等によって除去する。

具体的手順を図11に示す。多層膜配線基板200において、先ず、銅配線200bが形成された絶縁基板200c上に絶縁膜200dが成膜され、この絶縁膜200dにおける銅配線200bの上方に溝部200aが形成される。そして溝部200aの内壁にタンタル系バリアメタル201をスパッタ成膜する(図11(a)参照)。次いで、バリアメタル膜201の表面に銅シード層202をスパッタ成膜する(図11(b)参照)。そして、電解めっき法により溝部200aにおいて銅を成長させ、溝部200aを銅めっき203で埋め込んだ後(図11(c)参照)、CMPプロセスによって余剰な配線材料を除去する(図11(d)参照)。尚、このようなダマシン法による銅配線技術については、例えば特許文献1に記載されている。

【特許文献1】特開2002−118109号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、前記ダマシン法において、タンタル系バリアメタル膜及び銅シード層は、iPVD(イオン物理蒸着)と呼ばれるスパッタ技術によって成膜されているが、配線パターンの微細化が進むと、成膜後のカバレッジ(被膜状態)が悪化することが予想されている。

例えば、図12(a)に示すように、銅シード層202を形成しても、トレンチ等の溝部のボトム周辺において、金属膜(銅膜)により被膜されない、或いは被膜が薄い箇所204が生じる虞があった。その結果、電解めっき時に銅が安定的に成長しないだけでなく、銅シード層202が剥がれ易い等の不具合が生じるという課題があった。

さらに、このように銅シード層202のカバレッジが悪い場合、電解めっき時に電流が流れず、図12(b)に示すように銅めっき203中にボイド(空隙)205が生じ、その結果、断線などの故障が発生し易くなるという課題があった。

【0005】

本発明は、前記したような事情の下になされたものであり、基板に形成された溝部に配線材料を埋め込むダマシン配線の形成方法であって、カバレッジの悪いシード層を修理することができ、電解めっき時に配線材料を安定的に成長させ、ボイド等の不具合発生を抑制することのできるダマシン配線の形成方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

前記した課題を解決するために、本発明に係るダマシン配線の形成方法は、絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、前記ナノパーティクル含有溶液上に有機溶媒を塗布しエッチバックするステップと、前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することに特徴を有する。

【0007】

また、前記した課題を解決するために、本発明に係るダマシン配線の形成方法は、絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、前記ナノパーティクルの溶媒を蒸発させるベーク処理を行うステップと、前記ナノパーティクル上に有機溶媒を塗布しエッチバックするステップと、前記有機溶媒を蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することに特徴を有する。

【0008】

このように、カバレッジの悪いシード層にナノパーティクル含有溶液を塗布し、その後エッチバックを行うことにより、トレンチ等の溝部のボトム周辺等、シード層の被膜がなされ難い箇所にナノパーティクル層が形成されて、アニール処理後にはコンフォーマルなカバレッジ層(金属膜)を得ることができる。

【0009】

また、前記カバレッジ層を形成するステップ後、電解めっき、もしくはCVDにより前記溝部を前記配線材料で埋め込むステップを実行することが望ましい。

これにより、溝部に安定的に金属を成長させることができ、ボイド等の不具合の発生しない配線を得ることができる。

また、前記配線材料は銅(Cu)または銀(Ag)であることが望ましく、前記エッチバックに用いる有機溶媒はトルエンであることが望ましい。

【発明の効果】

【0010】

本発明によれば、基板に形成された溝部に配線材料を埋め込むダマシン配線の形成方法であって、カバレッジの悪いシード層を修理することができ、電解めっきやCVD時に配線材料を安定的に成長させ、ボイド等の不具合発生を抑制することのできるダマシン配線の形成方法を得ることができる。

【発明を実施するための最良の形態】

【0011】

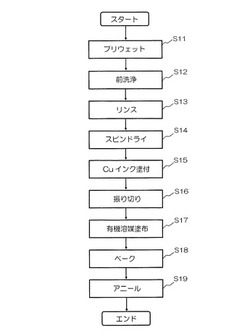

以下、本発明にかかる実施の形態につき、図に基づいて説明する。図1は、本発明に係るダマシン配線の形成方法の全体の流れを示すフロー図である。図2、図3は、図1のフローに対応する状態を示す基板の断面図である。

【0012】

図1のフローに沿って、対応する図2、図3の断面図を用いながらダマシン配線全体のプロセスを説明する。

先ず、図2(a)に示すように半導体基板1(以下、基板1と称呼する)上にエッチストッパ層10を形成し、さらにその上に絶縁膜2(例えば酸化シリコン膜)を成長させる(図1のステップS1)。次いで絶縁膜2上にフォトレジスト4を塗布し、露光、現像により、図2(b)に示すようにビアや配線パターン4aを形成する(図1のステップS2)。尚、配線パターン4aは、この例では基板1上に形成された銅配線3の上方に形成されている。そして、ステップS2で形成したパターン4aをマスクとして、ビアや配線となる絶縁膜部分をエッチングする(図1のステップS3)。これにより、図2(c)に示すように配線パターンの溝部2aが形成される。尚、溝部2aは、異なる幅のパターン4aを用いて2回エッチングを行うことにより、段差を有する形状を示している。

【0013】

次いで図3(a)に示すように、基板1上の配線パターンの溝部2aに対し、スパッタリングにより配線材料である銅(Cu)の拡散防止用としてのバリアメタル膜11を形成し、さらにバリアメタル膜11上に銅シード層5を成膜する(図1のステップS4)。

ここで、ステップS4で形成した銅シード層5はカバレッジが悪いため、図示するように溝部2aのボトム周辺(特にコーナー部分)において、被膜されない、あるいは薄い部分5a等が生じている。このため、カバレッジの悪い銅シード層5を修正し、状態を向上するためにシードリペア(シード層の修理工程)が行われる(図1のステップS5)。このシードリペアについては、本発明の特徴となるプロセスであり詳細に後述する。

【0014】

シードリペア後、電解めっき法により、図3(b)に示すように配線パターンの溝部2aに銅めっき6が埋め込まれ(図1のステップS6)、CMP法により余分な銅めっき6が除去されると共に図3(c)に示すように平坦化処理が行われ、ダマシン配線による銅配線が形成される(図1のステップS7)。

【0015】

続いて、図1のステップS5において行われるシードリペア方法について説明する。図4は、シードリペア工程のプロセスの流れを示すフローである。また、図5は、図4のフローの主要プロセスに対応する基板状態を示す基板の断面図である。

また、このシードリペア工程においては、基板1は鉛直軸周りに回転制御可能なスピンチャック(図示せず)上に、その下面が吸着保持、もしくは基板円周を機械的に保持されて処理されるものとする。

【0016】

先ず、図5(a)に示すようにカバレッジが悪い銅シード層5に対し、濡れ性助長のために純水によるプリウェット処理を行う(図4のステップS11)。このプリウェット処理においては、0〜300回転の範囲で基板1を回転させ、上方から純水を銅シード層5上に吐出することにより行われる。尚、このとき濡れ性が悪い場合、ノズルをスキャンさせ、全面の濡れ性を向上させることができる。

【0017】

次いで、基板1を0〜1000回転の範囲で回転させ、上方から有機酸を銅シード層5上に吐出し、銅配線表面の酸化銅を排除する前洗浄を行う(図4のステップS12)。

前洗浄後、基板1を0〜1000回転の範囲で回転させ、純水を銅シード層5上に吐出してリンス処理を行い(図4のステップS13)、続けて基板1を300〜1500回転の範囲で高速回転させ、スピンドライによる乾燥処理(図4のステップS14)を行う。

【0018】

次いで、図5(b)に示すように、分散剤に溶かした銅ナノパーティクル含有溶液、即ち銅インク7を塗布により銅シード層5上に成膜する(図4のステップS15)。この成膜処理においては、基板1が0〜300回転の範囲で回転され、上方から銅シード層5上に銅インク7が吐出され、スピンコーティング法により塗布される。そして、基板回転数を100〜1500回転とする振り切り処理によって余分な銅インク7を除去し、これにより面内均一性が確保される(図4のステップS16)。

【0019】

次いで、基板1を0〜300回転の範囲で回転し、上方から銅インク7(膜)上に銅ナノパーティクル含有溶液の溶媒となる有機溶媒を吐出し、スピンコーティング法により銅インク7(膜)上に有機溶媒を塗布する(図4のステップS17)。これによりトレンチ等の溝部の入口付近に厚く形成された銅ナノパーティクルが除去され、エッチバック(平坦化処理)がなされる。尚、有機溶媒としては、例えばトルエンを用いることができる。

有機溶媒の塗布後、銅シード層5上の銅インク7(膜)に対し、窒素(N2)もしくはアルゴン(Ar)の雰囲気中、50℃〜250℃の温度でベーク処理が施される。この処理により銅ナノパーティクル含有溶液の有機溶媒が蒸発される(図4のステップS18)。

【0020】

そして、さらに窒素(N2)もしくはアルゴン(Ar)雰囲気中、100℃〜1000℃の温度で、銅ナノパーティクルの分散剤を蒸発させ、銅ナノパーティクルを金属膜とするためのアニール処理(熱処理)が行われる(図4のステップS19)。このアニール処理によって、図5(c)に示すように銅シード層5は修理され、カバレッジ層8とされる。

【0021】

尚、図4に示したフローでは、有機溶媒の塗布によるエッチバックは、ベーク処理の前に行うようにしたが、該ベーク処理の後に行ってもよい。

その場合、図6のフローに示すように、銅インク7の振り切り処理(図6のステップS16)までは、図4のフローと同じプロセスで処理を行う。

そして、銅ナノパーティクル含有溶液の振り切り処理後、窒素(N2)もしくはアルゴン(Ar)の雰囲気中、50℃〜250℃の温度で銅ナノパーティクルの溶媒を蒸発させるためのベーク処理を行う(図6のステップS21)。これにより銅ナノパーティクルは銅シード層5上に定着される。

【0022】

ベーク処理後、銅ナノパーティクル上に有機溶媒(例えばトルエン)を塗布することにより、エッチバック(平坦化処理)を行う(図6のステップS22)。これにより、トレンチ等の溝部の入口付近に厚く成膜された銅ナノパーティクルが除去される。

有機溶媒の塗布後、窒素(N2)もしくはアルゴン(Ar)の雰囲気中、50℃〜250℃の温度で有機溶媒を蒸発させるためのベーク処理を行う(図6のステップS23)。

【0023】

そして最後に、窒素(N2)もしくはアルゴン(Ar)雰囲気中、100℃〜1000℃の温度で、銅ナノパーティクルの分散剤を蒸発させるアニール処理(熱処理)を行い、銅ナノパーティクルを金属膜とする。これにより、銅シード層5は被膜されない箇所や被膜が薄い箇所が無い状態、即ちコンフォーマルな形状に修理されたカバレッジ層8とされる。このように、銅ナノパーティクル含有溶液の溶媒を蒸発させるベーク処理によって銅ナノパーティクルを銅シード層5に定着させた後、有機溶媒の塗布によるエッチバックを行うことにより、より均一性を向上させて銅シード層5のカバレッジを修理することができる。

【0024】

以上の本発明に係る実施の形態によれば、カバレッジの悪い銅シード層5に対し、銅ナノパーティクル含有溶液を塗布し、さらに有機溶媒によるエッチバックにより余分な銅ナノパーティクルが除去される。これにより、トレンチ等の溝部のボトム周辺等、シード層の被膜がなされ難い箇所に金属膜を形成することができ、アニール処理後にはコンフォーマル(膜厚が均一)なカバレッジ層(金属膜)を得ることができる。また、その後の電解めっき、もしくはCVD工程において安定的に銅を成長させることができ、ボイド等の不具合の発生しない配線を得ることができる。

【0025】

尚、前記実施の形態においては、配線材料として銅(Cu)を用いたが、より低抵抗の銀(Ag)を用いてもよい。その場合、ベーク処理及びアニール処理における雰囲気は、窒素(N2)、アルゴン(Ar)の他、特に分散剤除去に有効な酸素(O2)添加ガスを用いてもよい。

また、本発明は、半導体デバイスの微細化により、孔や溝の底においてiPVDでは成膜され難い箇所を、ウェットプロセスの利点であるカバレッジを用いて修理する技術である。

【実施例】

【0026】

続いて、本発明に係るダマシン配線の形成方法について、実施例に基づきさらに説明する。本実施例では、前記実施の形態に示した方法に基づき、実際に実験を行うことにより、その効果を検証した。

【0027】

[実施例1]

実施例1では、本発明に係るダマシン配線の形成方法を検証するため、図4に示したフローに基づきシードリペア工程を実施した。即ち、図7に示すカバレッジの悪い銅シード層(初期状態)50に対するシードリペア工程において、銅ナノパーティクルを銅シード層に定着させるベーク前に、有機溶媒によるエッチバックを行った。

尚、図7の多層膜断面写真はSEM像(走査型電子顕微鏡による断面写真)である。

【0028】

この実験の結果として、図8(a)にベーク後の多層膜断面写真(SEM像)を示し、図8(b)にアニール後の多層膜断面写真(SEM像)を示す。

また、比較例として、図9(a)に有機溶媒によるエッチバックを行わない場合のベーク後の多層膜断面写真(SEM像)を示し、図9(b)にアニール後の多層膜断面写真(SEM像)を示す。

尚、これらの写真において、金属膜の部分は、二次電子放出率が高いため白く表示されている。

【0029】

これらの写真から分かるように、エッチバックを行った場合には、ベーク後、図8(a)に示すように、トレンチ(溝部)のボトム周辺や側壁に銅ナノパーティクル層51が形成され、アニール後には図8(b)に示すようにコンフォーマルな形状の銅膜であるカバレッジ層52が得られた。

【0030】

一方、エッチバックを行わない場合、ベーク後、図9(a)に示すように銅ナノパーティクル層53がトレンチの入口を完全に塞ぎ、そのためにアニール後において、図9(b)に示すように分散剤が蒸発され金属膜となされた銅ナノパーティクルの層は、体積のシュリンクを生じ、ボイド54(黒く表示される空隙)が形成された。

【0031】

[実施例2]

実施例2では、本発明に係るダマシン配線の形成方法を検証するため、図6に示したフローに基づきシードリペア工程を実施した。即ち、銅ナノパーティクルを銅シード層に定着させるベーク後に、有機溶剤によるエッチバックを行った。

図10(a)にベーク後の状態、図10(b)にアニール後の状態の多層膜断面写真を示す。これらの写真から分かるように、第一の実施例と同様にエッチバックを行った場合には、ベーク後、図10(a)に示すようにトレンチのボトム周辺や側壁に銅ナノパーティクル層55が形成され、アニール後には図10(b)に示すように修理された銅膜であるカバレッジ層56が得られた。

【0032】

以上の実施例1、2の結果から、本発明に係るダマシン配線の形成方法によれば、トレンチ等の溝部のボトム周辺や側壁等、シード層の被膜がなされ難い箇所にも充分な金属膜を形成でき、コンフォーマル(膜厚が均一)な形状のカバレッジ層を得ることができることを確認した。

【産業上の利用可能性】

【0033】

本発明は、半導体基板におけるダマシン配線の形成方法に適用でき、半導体製造業界、電子デバイス製造業界等において好適に用いることができる。

【図面の簡単な説明】

【0034】

【図1】図1は、本発明に係るダマシン配線の形成方法の全体の流れを示すフロー図である。

【図2】図2は、図1のフローに対応する状態を示す基板の断面図である。

【図3】図3は、図1のフローに対応する状態を示す基板の断面図である。

【図4】図4は、シードリペア工程のプロセスの流れを示すフローである。

【図5】図5は、図4のフローの主要プロセスに対応する基板状態を示す基板の断面図である。

【図6】図6は、シードリペア工程の他の形態の流れを示すフロー図である。

【図7】図7は、実施例において、初期状態としての銅シード層を示す多層膜断面写真である。

【図8】図8は、実施例1の結果を示す多層膜断面写真である。

【図9】図9は、比較例の結果を示す多層膜断面写真である。

【図10】図10は、実施例2の結果を示す多層膜断面写真である。

【図11】図11は、ダマシン配線方法を説明するための図である。

【図12】図12は、従来の課題を説明するための図である。

【符号の説明】

【0035】

1 半導体基板

2 絶縁膜

2a 溝部

3 銅配線

4 フォトレジスト

4a 配線パターン

5 銅シード層(シード層)

6 銅

7 銅インク(ナノパーティクル含有溶液)

10 エッチストッパ層

11 バリアメタル層

【技術分野】

【0001】

本発明は、カバレッジの悪いシード層を修理するダマシン配線の形成方法に関する。

【背景技術】

【0002】

半導体デバイスの高集積化、高性能化に伴い、従来のアルミニウム(Al)配線よりも電気抵抗率の低い銅(Cu)配線の適用が検討されている。この銅配線は、基板上へのドライエッチングによる配線処理が困難であることから、絶縁素材の基板に形成された溝部に銅配線を埋め込むダマシン法が主流である。

【0003】

ダマシン法では、層間絶縁膜に予め所定の溝を形成しておき、その溝に配線材料を埋め込み、その後に溝外の余剰な配線材料を化学的機械研磨(CMPプロセス)等によって除去する。

具体的手順を図11に示す。多層膜配線基板200において、先ず、銅配線200bが形成された絶縁基板200c上に絶縁膜200dが成膜され、この絶縁膜200dにおける銅配線200bの上方に溝部200aが形成される。そして溝部200aの内壁にタンタル系バリアメタル201をスパッタ成膜する(図11(a)参照)。次いで、バリアメタル膜201の表面に銅シード層202をスパッタ成膜する(図11(b)参照)。そして、電解めっき法により溝部200aにおいて銅を成長させ、溝部200aを銅めっき203で埋め込んだ後(図11(c)参照)、CMPプロセスによって余剰な配線材料を除去する(図11(d)参照)。尚、このようなダマシン法による銅配線技術については、例えば特許文献1に記載されている。

【特許文献1】特開2002−118109号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、前記ダマシン法において、タンタル系バリアメタル膜及び銅シード層は、iPVD(イオン物理蒸着)と呼ばれるスパッタ技術によって成膜されているが、配線パターンの微細化が進むと、成膜後のカバレッジ(被膜状態)が悪化することが予想されている。

例えば、図12(a)に示すように、銅シード層202を形成しても、トレンチ等の溝部のボトム周辺において、金属膜(銅膜)により被膜されない、或いは被膜が薄い箇所204が生じる虞があった。その結果、電解めっき時に銅が安定的に成長しないだけでなく、銅シード層202が剥がれ易い等の不具合が生じるという課題があった。

さらに、このように銅シード層202のカバレッジが悪い場合、電解めっき時に電流が流れず、図12(b)に示すように銅めっき203中にボイド(空隙)205が生じ、その結果、断線などの故障が発生し易くなるという課題があった。

【0005】

本発明は、前記したような事情の下になされたものであり、基板に形成された溝部に配線材料を埋め込むダマシン配線の形成方法であって、カバレッジの悪いシード層を修理することができ、電解めっき時に配線材料を安定的に成長させ、ボイド等の不具合発生を抑制することのできるダマシン配線の形成方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

前記した課題を解決するために、本発明に係るダマシン配線の形成方法は、絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、前記ナノパーティクル含有溶液上に有機溶媒を塗布しエッチバックするステップと、前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することに特徴を有する。

【0007】

また、前記した課題を解決するために、本発明に係るダマシン配線の形成方法は、絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、前記ナノパーティクルの溶媒を蒸発させるベーク処理を行うステップと、前記ナノパーティクル上に有機溶媒を塗布しエッチバックするステップと、前記有機溶媒を蒸発させるベーク処理を行うステップと、前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することに特徴を有する。

【0008】

このように、カバレッジの悪いシード層にナノパーティクル含有溶液を塗布し、その後エッチバックを行うことにより、トレンチ等の溝部のボトム周辺等、シード層の被膜がなされ難い箇所にナノパーティクル層が形成されて、アニール処理後にはコンフォーマルなカバレッジ層(金属膜)を得ることができる。

【0009】

また、前記カバレッジ層を形成するステップ後、電解めっき、もしくはCVDにより前記溝部を前記配線材料で埋め込むステップを実行することが望ましい。

これにより、溝部に安定的に金属を成長させることができ、ボイド等の不具合の発生しない配線を得ることができる。

また、前記配線材料は銅(Cu)または銀(Ag)であることが望ましく、前記エッチバックに用いる有機溶媒はトルエンであることが望ましい。

【発明の効果】

【0010】

本発明によれば、基板に形成された溝部に配線材料を埋め込むダマシン配線の形成方法であって、カバレッジの悪いシード層を修理することができ、電解めっきやCVD時に配線材料を安定的に成長させ、ボイド等の不具合発生を抑制することのできるダマシン配線の形成方法を得ることができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明にかかる実施の形態につき、図に基づいて説明する。図1は、本発明に係るダマシン配線の形成方法の全体の流れを示すフロー図である。図2、図3は、図1のフローに対応する状態を示す基板の断面図である。

【0012】

図1のフローに沿って、対応する図2、図3の断面図を用いながらダマシン配線全体のプロセスを説明する。

先ず、図2(a)に示すように半導体基板1(以下、基板1と称呼する)上にエッチストッパ層10を形成し、さらにその上に絶縁膜2(例えば酸化シリコン膜)を成長させる(図1のステップS1)。次いで絶縁膜2上にフォトレジスト4を塗布し、露光、現像により、図2(b)に示すようにビアや配線パターン4aを形成する(図1のステップS2)。尚、配線パターン4aは、この例では基板1上に形成された銅配線3の上方に形成されている。そして、ステップS2で形成したパターン4aをマスクとして、ビアや配線となる絶縁膜部分をエッチングする(図1のステップS3)。これにより、図2(c)に示すように配線パターンの溝部2aが形成される。尚、溝部2aは、異なる幅のパターン4aを用いて2回エッチングを行うことにより、段差を有する形状を示している。

【0013】

次いで図3(a)に示すように、基板1上の配線パターンの溝部2aに対し、スパッタリングにより配線材料である銅(Cu)の拡散防止用としてのバリアメタル膜11を形成し、さらにバリアメタル膜11上に銅シード層5を成膜する(図1のステップS4)。

ここで、ステップS4で形成した銅シード層5はカバレッジが悪いため、図示するように溝部2aのボトム周辺(特にコーナー部分)において、被膜されない、あるいは薄い部分5a等が生じている。このため、カバレッジの悪い銅シード層5を修正し、状態を向上するためにシードリペア(シード層の修理工程)が行われる(図1のステップS5)。このシードリペアについては、本発明の特徴となるプロセスであり詳細に後述する。

【0014】

シードリペア後、電解めっき法により、図3(b)に示すように配線パターンの溝部2aに銅めっき6が埋め込まれ(図1のステップS6)、CMP法により余分な銅めっき6が除去されると共に図3(c)に示すように平坦化処理が行われ、ダマシン配線による銅配線が形成される(図1のステップS7)。

【0015】

続いて、図1のステップS5において行われるシードリペア方法について説明する。図4は、シードリペア工程のプロセスの流れを示すフローである。また、図5は、図4のフローの主要プロセスに対応する基板状態を示す基板の断面図である。

また、このシードリペア工程においては、基板1は鉛直軸周りに回転制御可能なスピンチャック(図示せず)上に、その下面が吸着保持、もしくは基板円周を機械的に保持されて処理されるものとする。

【0016】

先ず、図5(a)に示すようにカバレッジが悪い銅シード層5に対し、濡れ性助長のために純水によるプリウェット処理を行う(図4のステップS11)。このプリウェット処理においては、0〜300回転の範囲で基板1を回転させ、上方から純水を銅シード層5上に吐出することにより行われる。尚、このとき濡れ性が悪い場合、ノズルをスキャンさせ、全面の濡れ性を向上させることができる。

【0017】

次いで、基板1を0〜1000回転の範囲で回転させ、上方から有機酸を銅シード層5上に吐出し、銅配線表面の酸化銅を排除する前洗浄を行う(図4のステップS12)。

前洗浄後、基板1を0〜1000回転の範囲で回転させ、純水を銅シード層5上に吐出してリンス処理を行い(図4のステップS13)、続けて基板1を300〜1500回転の範囲で高速回転させ、スピンドライによる乾燥処理(図4のステップS14)を行う。

【0018】

次いで、図5(b)に示すように、分散剤に溶かした銅ナノパーティクル含有溶液、即ち銅インク7を塗布により銅シード層5上に成膜する(図4のステップS15)。この成膜処理においては、基板1が0〜300回転の範囲で回転され、上方から銅シード層5上に銅インク7が吐出され、スピンコーティング法により塗布される。そして、基板回転数を100〜1500回転とする振り切り処理によって余分な銅インク7を除去し、これにより面内均一性が確保される(図4のステップS16)。

【0019】

次いで、基板1を0〜300回転の範囲で回転し、上方から銅インク7(膜)上に銅ナノパーティクル含有溶液の溶媒となる有機溶媒を吐出し、スピンコーティング法により銅インク7(膜)上に有機溶媒を塗布する(図4のステップS17)。これによりトレンチ等の溝部の入口付近に厚く形成された銅ナノパーティクルが除去され、エッチバック(平坦化処理)がなされる。尚、有機溶媒としては、例えばトルエンを用いることができる。

有機溶媒の塗布後、銅シード層5上の銅インク7(膜)に対し、窒素(N2)もしくはアルゴン(Ar)の雰囲気中、50℃〜250℃の温度でベーク処理が施される。この処理により銅ナノパーティクル含有溶液の有機溶媒が蒸発される(図4のステップS18)。

【0020】

そして、さらに窒素(N2)もしくはアルゴン(Ar)雰囲気中、100℃〜1000℃の温度で、銅ナノパーティクルの分散剤を蒸発させ、銅ナノパーティクルを金属膜とするためのアニール処理(熱処理)が行われる(図4のステップS19)。このアニール処理によって、図5(c)に示すように銅シード層5は修理され、カバレッジ層8とされる。

【0021】

尚、図4に示したフローでは、有機溶媒の塗布によるエッチバックは、ベーク処理の前に行うようにしたが、該ベーク処理の後に行ってもよい。

その場合、図6のフローに示すように、銅インク7の振り切り処理(図6のステップS16)までは、図4のフローと同じプロセスで処理を行う。

そして、銅ナノパーティクル含有溶液の振り切り処理後、窒素(N2)もしくはアルゴン(Ar)の雰囲気中、50℃〜250℃の温度で銅ナノパーティクルの溶媒を蒸発させるためのベーク処理を行う(図6のステップS21)。これにより銅ナノパーティクルは銅シード層5上に定着される。

【0022】

ベーク処理後、銅ナノパーティクル上に有機溶媒(例えばトルエン)を塗布することにより、エッチバック(平坦化処理)を行う(図6のステップS22)。これにより、トレンチ等の溝部の入口付近に厚く成膜された銅ナノパーティクルが除去される。

有機溶媒の塗布後、窒素(N2)もしくはアルゴン(Ar)の雰囲気中、50℃〜250℃の温度で有機溶媒を蒸発させるためのベーク処理を行う(図6のステップS23)。

【0023】

そして最後に、窒素(N2)もしくはアルゴン(Ar)雰囲気中、100℃〜1000℃の温度で、銅ナノパーティクルの分散剤を蒸発させるアニール処理(熱処理)を行い、銅ナノパーティクルを金属膜とする。これにより、銅シード層5は被膜されない箇所や被膜が薄い箇所が無い状態、即ちコンフォーマルな形状に修理されたカバレッジ層8とされる。このように、銅ナノパーティクル含有溶液の溶媒を蒸発させるベーク処理によって銅ナノパーティクルを銅シード層5に定着させた後、有機溶媒の塗布によるエッチバックを行うことにより、より均一性を向上させて銅シード層5のカバレッジを修理することができる。

【0024】

以上の本発明に係る実施の形態によれば、カバレッジの悪い銅シード層5に対し、銅ナノパーティクル含有溶液を塗布し、さらに有機溶媒によるエッチバックにより余分な銅ナノパーティクルが除去される。これにより、トレンチ等の溝部のボトム周辺等、シード層の被膜がなされ難い箇所に金属膜を形成することができ、アニール処理後にはコンフォーマル(膜厚が均一)なカバレッジ層(金属膜)を得ることができる。また、その後の電解めっき、もしくはCVD工程において安定的に銅を成長させることができ、ボイド等の不具合の発生しない配線を得ることができる。

【0025】

尚、前記実施の形態においては、配線材料として銅(Cu)を用いたが、より低抵抗の銀(Ag)を用いてもよい。その場合、ベーク処理及びアニール処理における雰囲気は、窒素(N2)、アルゴン(Ar)の他、特に分散剤除去に有効な酸素(O2)添加ガスを用いてもよい。

また、本発明は、半導体デバイスの微細化により、孔や溝の底においてiPVDでは成膜され難い箇所を、ウェットプロセスの利点であるカバレッジを用いて修理する技術である。

【実施例】

【0026】

続いて、本発明に係るダマシン配線の形成方法について、実施例に基づきさらに説明する。本実施例では、前記実施の形態に示した方法に基づき、実際に実験を行うことにより、その効果を検証した。

【0027】

[実施例1]

実施例1では、本発明に係るダマシン配線の形成方法を検証するため、図4に示したフローに基づきシードリペア工程を実施した。即ち、図7に示すカバレッジの悪い銅シード層(初期状態)50に対するシードリペア工程において、銅ナノパーティクルを銅シード層に定着させるベーク前に、有機溶媒によるエッチバックを行った。

尚、図7の多層膜断面写真はSEM像(走査型電子顕微鏡による断面写真)である。

【0028】

この実験の結果として、図8(a)にベーク後の多層膜断面写真(SEM像)を示し、図8(b)にアニール後の多層膜断面写真(SEM像)を示す。

また、比較例として、図9(a)に有機溶媒によるエッチバックを行わない場合のベーク後の多層膜断面写真(SEM像)を示し、図9(b)にアニール後の多層膜断面写真(SEM像)を示す。

尚、これらの写真において、金属膜の部分は、二次電子放出率が高いため白く表示されている。

【0029】

これらの写真から分かるように、エッチバックを行った場合には、ベーク後、図8(a)に示すように、トレンチ(溝部)のボトム周辺や側壁に銅ナノパーティクル層51が形成され、アニール後には図8(b)に示すようにコンフォーマルな形状の銅膜であるカバレッジ層52が得られた。

【0030】

一方、エッチバックを行わない場合、ベーク後、図9(a)に示すように銅ナノパーティクル層53がトレンチの入口を完全に塞ぎ、そのためにアニール後において、図9(b)に示すように分散剤が蒸発され金属膜となされた銅ナノパーティクルの層は、体積のシュリンクを生じ、ボイド54(黒く表示される空隙)が形成された。

【0031】

[実施例2]

実施例2では、本発明に係るダマシン配線の形成方法を検証するため、図6に示したフローに基づきシードリペア工程を実施した。即ち、銅ナノパーティクルを銅シード層に定着させるベーク後に、有機溶剤によるエッチバックを行った。

図10(a)にベーク後の状態、図10(b)にアニール後の状態の多層膜断面写真を示す。これらの写真から分かるように、第一の実施例と同様にエッチバックを行った場合には、ベーク後、図10(a)に示すようにトレンチのボトム周辺や側壁に銅ナノパーティクル層55が形成され、アニール後には図10(b)に示すように修理された銅膜であるカバレッジ層56が得られた。

【0032】

以上の実施例1、2の結果から、本発明に係るダマシン配線の形成方法によれば、トレンチ等の溝部のボトム周辺や側壁等、シード層の被膜がなされ難い箇所にも充分な金属膜を形成でき、コンフォーマル(膜厚が均一)な形状のカバレッジ層を得ることができることを確認した。

【産業上の利用可能性】

【0033】

本発明は、半導体基板におけるダマシン配線の形成方法に適用でき、半導体製造業界、電子デバイス製造業界等において好適に用いることができる。

【図面の簡単な説明】

【0034】

【図1】図1は、本発明に係るダマシン配線の形成方法の全体の流れを示すフロー図である。

【図2】図2は、図1のフローに対応する状態を示す基板の断面図である。

【図3】図3は、図1のフローに対応する状態を示す基板の断面図である。

【図4】図4は、シードリペア工程のプロセスの流れを示すフローである。

【図5】図5は、図4のフローの主要プロセスに対応する基板状態を示す基板の断面図である。

【図6】図6は、シードリペア工程の他の形態の流れを示すフロー図である。

【図7】図7は、実施例において、初期状態としての銅シード層を示す多層膜断面写真である。

【図8】図8は、実施例1の結果を示す多層膜断面写真である。

【図9】図9は、比較例の結果を示す多層膜断面写真である。

【図10】図10は、実施例2の結果を示す多層膜断面写真である。

【図11】図11は、ダマシン配線方法を説明するための図である。

【図12】図12は、従来の課題を説明するための図である。

【符号の説明】

【0035】

1 半導体基板

2 絶縁膜

2a 溝部

3 銅配線

4 フォトレジスト

4a 配線パターン

5 銅シード層(シード層)

6 銅

7 銅インク(ナノパーティクル含有溶液)

10 エッチストッパ層

11 バリアメタル層

【特許請求の範囲】

【請求項1】

絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、

スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、

前記ナノパーティクル含有溶液上に有機溶媒を塗布しエッチバックするステップと、

前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、

前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することを特徴とするダマシン配線の形成方法。

【請求項2】

絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、

スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、

前記ナノパーティクルの溶媒を蒸発させるベーク処理を行うステップと、

前記ナノパーティクル上に有機溶媒を塗布しエッチバックするステップと、

前記有機溶媒を蒸発させるベーク処理を行うステップと、

前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することを特徴とするダマシン配線の形成方法。

【請求項3】

前記カバレッジ層を形成するステップ後、電解めっき、もしくはCVDにより前記溝部を前記配線材料で埋め込むステップを実行することを特徴とする請求項1または請求項2に記載されたダマシン配線の形成方法。

【請求項4】

前記配線材料は銅(Cu)または銀(Ag)であることを特徴とする請求項1乃至請求項3のいずれかに記載されたダマシン配線の形成方法。

【請求項5】

前記エッチバックに用いる有機溶媒はトルエンであることを特徴とする請求項1乃至請求項4のいずれかに記載されたダマシン配線の形成方法。

【請求項1】

絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、

スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、

前記ナノパーティクル含有溶液上に有機溶媒を塗布しエッチバックするステップと、

前記ナノパーティクルの溶媒と前記有機溶媒とを蒸発させるベーク処理を行うステップと、

前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することを特徴とするダマシン配線の形成方法。

【請求項2】

絶縁膜に形成された溝部に配線材料のシード層をスパッタ成膜し、前記溝部を配線材料で埋め込むダマシン配線の形成方法であって、

スパッタ成膜された前記シード層に、分散剤に溶かした配線材料のナノパーティクル含有溶液を塗布するステップと、

前記ナノパーティクルの溶媒を蒸発させるベーク処理を行うステップと、

前記ナノパーティクル上に有機溶媒を塗布しエッチバックするステップと、

前記有機溶媒を蒸発させるベーク処理を行うステップと、

前記分散剤を蒸発させナノパーティクルを金属膜にするアニール処理を行うステップとを実行することを特徴とするダマシン配線の形成方法。

【請求項3】

前記カバレッジ層を形成するステップ後、電解めっき、もしくはCVDにより前記溝部を前記配線材料で埋め込むステップを実行することを特徴とする請求項1または請求項2に記載されたダマシン配線の形成方法。

【請求項4】

前記配線材料は銅(Cu)または銀(Ag)であることを特徴とする請求項1乃至請求項3のいずれかに記載されたダマシン配線の形成方法。

【請求項5】

前記エッチバックに用いる有機溶媒はトルエンであることを特徴とする請求項1乃至請求項4のいずれかに記載されたダマシン配線の形成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2007−173686(P2007−173686A)

【公開日】平成19年7月5日(2007.7.5)

【国際特許分類】

【出願番号】特願2005−371893(P2005−371893)

【出願日】平成17年12月26日(2005.12.26)

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【Fターム(参考)】

【公開日】平成19年7月5日(2007.7.5)

【国際特許分類】

【出願日】平成17年12月26日(2005.12.26)

【出願人】(000219967)東京エレクトロン株式会社 (5,184)

【Fターム(参考)】

[ Back to top ]