チップセットセキュリティオフロードエンジン

【課題】 デジタルコンテンツ保護を提供するための改良された装置、システム及び方法を提供する。

【解決手段】 セキュリティエンジンを有するブリッジが開示される。このブリッジは、暗号化サービスを中央処理装置からブリッジへとオフロードすることを可能にする。

【解決手段】 セキュリティエンジンを有するブリッジが開示される。このブリッジは、暗号化サービスを中央処理装置からブリッジへとオフロードすることを可能にする。

【発明の詳細な説明】

【関連出願の相互参照】

【0001】

[0001]本出願は、本出願人へ共に譲渡され、且つ、本願と同日に米国特許商標庁に出願された「Apparatus, System, and Method for Digital Content Protection」と題する米国特許出願(代理人管理番号NVID−106/02US)に関連するものであり、当該米国特許出願の内容を本明細書に援用する。

【発明の分野】

【0002】

[0002]本発明は、一般に、デジタルコンテンツの保護を提供するための技術に関するものである。より詳細には、本発明は、中央処理装置(CPU)からデジタルコンテンツの保護の側面をオフロード(移動)する技術に関するものである。

【発明の背景】

【0003】

[0003]多くの消費者向け製品における問題の一つは、傍受されてしまうことのある信号経路に沿ってデジタルコンテンツが送信されねばならいことである。その結果として、デジタルコンテンツプロバイダーは、ハッカーによるデジタルコンテンツの許可されていないコピーについて心配しなければならない。例えば、ホームエンターテイメントシステムは、パーソナルコンピュータ(PC)、グラフィックサブシステム、高精細テレビジョン、セットトップボックス、デジタルビデオレコーダ及びプレーヤ、並びにデジタル汎用ディスク(DVD)プレーヤを含み得る。従って、暗号化されていないデジタルコンテンツ(しばしば「クリアテキスト」コンテンツとして知られる)は、ハッカーが、例えば、一以上の信号バスの出力を使用することによって傍受されてしまうというリスクがある。

【0004】

[0004]デジタルコンテンツの保護は、オーディオ及びビデオコンテンツが許可なしにコピーされないようにするために、その重要性を増してきている。デジタルコンテンツの保護は、とりわけ、傍受され得るような信号バスを通して送信されるコンテンツを暗号化するためのプロトコルを含む。デジタル送信コンテンツ保護(DTCP)スキームは、1998年に五つの会社(5C)によって開発され、日立、インテルコーポレーション、松下電器産業、ソニーコーポレーション及び東芝コーポレーションによって1998年7月に刊行された文献「5C Digital Transmission Content Protection」に記載されており、当該文献の内容を本明細書に援用する。このDTCPの方法のより詳細な点については、日立、インテルコーポレーション、松下電器産業、ソニーコーポレーション及び東芝コーポレーションによって2004年1月に刊行された「Digital Transmission Content Protection Specification」改訂1.3に記載されており、その内容を本明細書に援用する。DTCPの方法は、米国電気電子技術者協会(IEEE)1394マルチメディアバスに使用し得るものであり、ソースデバイス及びシンクデバイス(コンテンツストリームを受け取る装置)のためのプロトコルであってコンテンツの安全な送信を確立するためのプロセスを含んでいる。DTCPの方法は、認証及びキー交換(AKE)プロトコル、コンテンツ暗号化、並びに、暗号化モードインジケータ(EMI)を使用するコピーコントロール情報(CCI)を含む。

【0005】

[0005]DTCPのようなデジタルコンテンツの保護のスキームの1つの欠点は、コンテンツがデバイス間のシステムバスにて暗号化されるにもかかわらず、クリアテキストデータが一以上の内部データバスで盗まれやすいというものである。例えば、PCベースのマルチメディアシステムにおけるDVDの再生について考える。DVDコンテンツは、DVDプレーヤから暗号化された形式にて中央処理装置(CPU)によって受け取られる。CPUは、受け取ったデジタルコンテンツを復号する。次いで、CPUは、そのデータを表示装置へ書き込む前にそのDVDデータを再暗号化する。しかしながら、CPUによって行われる復号及び再暗号化では、通常、クリアテキストデータをシステムメモリへ書き込む必要があり、この場合には、コンテンツがメモリバスにて盗まれ易いのである。

【0006】

[0006]デジタルコンテンツの保護スキームの別の欠点は、高精細ビデオの暗号化及び復号を行うのにCPUに相当の負荷を掛けてしまうということである。例えば、アドバンスド暗号化標準(AES)は、略16サイクル/バイト(B)の暗号化コストを要する。圧縮フォーマット高精細テレビジョン(HDTV)は、約50MB/sの暗号化帯域幅に相当し、各圧縮HDTVコンテンツストリームは利用可能なCPUクロックサイクルの800MHzに相当する。これは、数ギガヘルツのクロックレートで動作するCPUには相当の負荷である。その上、幾つかのマルチメディアシステムにおいては、同時に幾つかのビデオストリームを取り扱う能力を有することが望まれており、これによって、最悪のケースのシナリオでは、CPUに対する暗号化/復号の全負荷がCPUクロックサイクルの大部分を消費することがある。

【0007】

[0007]従って、デジタルコンテンツの保護を提供するための改良された装置、システム及び方法が望まれている。

【発明の概要】

【0008】

[0008]中央処理装置をシステムの他のコンポーネントへ接続(ブリッジ)するためのブリッジについて開示する。ブリッジにおけるセキュリティエンジンは、暗号化サービスが中央処理装置からブリッジへと移動されるようにする。一実施の形態では、セキュリティエンジンは、ブリッジの非安全なインターフェイスにおいて、保護されるべきデータを暗号テキストとして暗号化する。

【0009】

[0009]本発明は、添付図面と共に以下なされる詳細な説明を参照することによって、より十分に理解されよう。これら図を通して対応する部分を、同様の参照符号によって指し示す。

【発明の詳細な説明】

【0010】

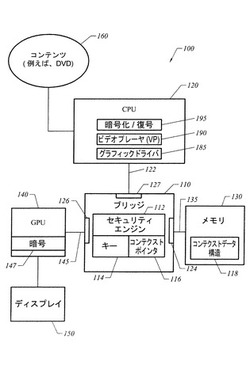

[0018]図1は、本発明の一実施の形態によるデジタルコンテンツシステム100のブロック図である。デジタルコンテンツシステム100は、セキュリティエンジン112を有するブリッジ110を含む。本発明の一実施の形態によれば、セキュリティサービスは、CPU120より下流の少なくとも一つのデバイス用のデータの暗号化といったものであり、CPU120からセキュリティエンジン112を使用するブリッジ110へ移動される。

【0011】

[0019]ブリッジ110は、単一チップとして、一群のチップとして、又はCPU120が形成されているチップの一部分として実装し得るものである。以下に詳述するように、ブリッジ110は、中央処理装置(CPU)120を他のデバイスへと接続(ブリッジ)するためのチップセットの部分として使用される任意のブリッジを含み得るものであり、例えば、ノースブリッジチップ、サウスブリッジチップ、又は、ノースブリッジチップ及びサウスブリッジチップの組み合わせといったものである。

【0012】

[0020]セキュリティエンジン112は、ブリッジ110内で暗号化サービスを実行する。典型的な暗号化サービスとしては、暗号化、復号、及びトランスコード(すなわち、異なる暗号化フォーマット間の変換)がある。暗号化サービスは、例えば、保護される必要のあるデータクラスに適用し得る。あるアプリケーションでは、ブリッジを通るデータの全てが暗号化サービスを必要とする。しかしながら、より一般的には、保護を必要とするデータ、例えば、デジタルコンテンツの保護を必要とするデータのようなデータのみが、暗号化サービスを必要とする。セキュリティエンジン112によって提供される暗号化サービスを利用して、ハッキングを受けやすいデジタルコンテンツシステム100の各部におけるデータ(例えば、ビデオコンテンツのようなデジタルコンテンツ)を保護してもよい。

【0013】

[0021]暗号化サービスは、データ書込みオペレーションのようなデータアクセスオペレーション中に提供することが可能である。暗号化/復号キー114は、暗号化サービスをサポートするためにセキュリティエンジン112に記憶されている。単一の暗号化及び/又は復号キーが記憶されているが、より一般的には、暗号化、復号、又はトランスコードのうち一以上のタイプをサポートするために追加のキーを記憶してもよい。一実施の形態では、コンテクストポインター116が、メモリ130内のコンテクストデータ118といったコンテクストデータのソースを指示する。コンテクストデータ118は、特定のソース/宛先アドレスに対してセキュリティエンジン112によって行われるべき特定の暗号化サービス(例えば、暗号化、復号又はトランスコード)をコンテクストスイッチが選択できるようにするデータ構造体を含む。各コンテクストが、また、特定の暗号化/復号キーを指示してもよい。

【0014】

[0022]一実施の形態においては、セキュリティエンジン112は、圧縮又は非圧縮データの標準暗号化及び復号技法(例えば、アドバンスド暗号化標準(AES)、トリプルデータ暗号化標準(3DES)、又はパブリック/プライベートキーリモートサーバー管理(RSM))をサポートする。しかしながら、セキュリティエンジン112は、また、他の暗号化プロトコルをサポートするように構成されていてもよい。典型的なトランスコードアプリケーションとしては、一つの暗号化標準のフォーマットから別の一つの暗号化標準のフォーマットへの変換、又は、二つの異なる暗号化キーの間の変換、例えば、第1キーでのAESと第2キーでのAESとの間の変換の実行がある。セキュリティエンジン112は、好ましくは、専用の改竄防止暗号化ハードウェアを少なくとも部分的に用いて実装されており、これにより、ソフトウェアのみによる暗号化/復号アルゴリズムの実行と比較してセキュリティが改善されるという利点が得られる。また、セキュリティエンジン112を専用ハードウェアで実施することによって、更に、性能及び電力消費における改善が可能となる。

【0015】

[0023]ブリッジ110は、CPU120、メモリ130、及びグラフィック処理装置(GPU)140(図示の例ではディスプレイ150に結合されている)といった他の装置を結合している。ブリッジ110は、フロントサイドバス(FSB)のようなバスインターフェイス121を有するバス122によって、CPU120に結合されている。CPUをブリッジに結合するバスインターフェイス121は、典型的には、専用高速インターフェイスであり、当該専用高速インターフェイスは、半田接続、埋め込み回路パス、及び高速なデータ速度のために、バスへのハッキングを困難なものとするのであり、本来的にセキュリティの高いものである。従って、以下の説明を通じて、クリアテキストデータがCPU120からブリッジ110へバスインターフェイス121を通して安全に送信できることが理解されるであろう。これは、アセンブルされたユニットにおいては、バスインターフェイス121からハッカーがデータを傍受することが、非常に難しいものであるからである。

【0016】

[0024]システム100においては、ブリッジ110とコンポーネント130及び140のような他のコンポーネントとの間に非安全なリンクを有する幾つかの経路がある。リンクが安全でないのは、例えば、ブリッジインターフェイス124又は126及びそれに関連するバス135又は145が潜在的にハッカーによってアクセスできる場合である。例えば、メモリバス135又はGPU140へのバス145は、それらバス135又は145が、確実に半田付けされていないか、及び/又は、それらバス135又は145へのハッキングが可能であるような低いデータレートを有する場合には、安全ではないことがある。

【0017】

[0025]入力経路としては、CPU120からブリッジ110への直接書込みのような、他のデバイスからブリッジ110への入力データの書込み経路がある。出力経路としては、GPU140への書込み又はメモリ130への書込みのように、ピアツーピア技法を使用する他のデバイスへのブリッジ110からの出力データの直接書込み経路がある。更に、直接メモリアクセス経路としては、CPU110がメモリ130へ書き込む直接メモリアクセスのようなメモリ130への直接書込み経路がある。ブリッジ110は、一つのデバイスから別の一つのデバイスへデータを書き込みすることが可能であり且つ直接メモリアクセスを可能とする任意のインターフェイスを利用できる。一実施の形態では、ブリッジ110は、GPU140のような少なくとも一つ他のデバイスとの高速インターフェイスとして、周辺コンポーネントインターフェイスエクスプレス(PCI-E)を使用するようになっている。PCI-Eは、周辺コンポーネントインターフェイススペシャルインタレストグループ(PCI-SIG)によって刊行された「PCIeベース仕様書」に記載された高速インターフェイス標準であり、この仕様書の内容を本明細書に援用する。しかしながら、より一般的には、CPU110をブリッジ110へ結合するPCI-Eの代わりに周辺コンポーネントインターフェイス(PCI)のような他の工業標準インターフェイスを使用することも可能である。

【0018】

[0026]一実施の形態では、セキュリティエンジン112は、PCIデバイスであり、当該PCIデバイスを、例えば、PCIバス0に実装して、セキュリティエンジン112をマザーボード製造時に認証及び承認することを可能にしている。PCIアーキテクチャーにおいては、一次バス番号、二次バス番号、及び下位バス番号に対応する異なるバス番号がある。PCIバス0は、ホストブリッジが接続するバスであるものと定義され、当該ホストブリッジは、CPUをPCIシステムへ接続する。暗号化/復号キーをセキュリティエンジン112へロードするために特権書込みを使用してもよい。

【0019】

[0027]図1は、CPU120においてビデオプレーヤ(VP)アプリケーション190及びグラフィックドライバー185を実行する典型的なアプリケーション185を例示している。暗号化されたデジタルコンテンツは、DVDプレーヤのようなデジタルコンテンツソースプレーヤ160から受け取られる(例示のために、デジタルコンテンツソースプレーヤ160を、直接的にCPU120に取り付けているように示しているが、より正確には、プレーヤ160は入力デバイスポートに接続される)。デジタルコンテンツ保護プロトコルに従って、CPU120は、暗号化/復号ソフトウェア195を有しており、デジタルコンテンツソース160から暗号化されたデジタルコンテンツを読み取り、暗号化/復号ソフトウェア195を使用して暗号化されたコンテンツの初期復号を実行する。VPアプリケーション190は、一以上のビデオストリームの再生及び/又は記憶を管理するためのオペレーションを実行する。

【0020】

[0028]GPU140は、ビデオフレームを生成するためのコマンドをCPU120から受け取り、また、通常、メモリ130からビデオデータを受け取る。GPU140の一つの特徴は、CPU140の使用を減少させるためにビデオ処理オペレーションをGPU140へ移動し得ることである。しかしながら、GPU140の別の特徴は、改善された表示特性を有するビデオフレームを生成し得ることである。ビデオコンテンツは、例えば、パーソナルコンピュータ又は高精細テレビジョンにおいて表示するのに最適化されていないようなオリジナルフォーマットで生成されることがある。例えば、カリフォルニア州サンタクララのNvidiaコーポレーションによって販売されているNvidia PureVideo Decoderは、GeForce6及び7シリーズのGPUで作動する。GeForce6及び7シリーズのGPUは、プログラマブルビデオプロセッサ、MPEG-2復号エンジン、及び運動推定エンジンを備えている。Nvidia PureVideo Decoderは、ハードウェアアクセラレーションを使用して、フィルタリング、スケーリング、フォーマット変換、及びその他のオペレーションを行い、ビデオの再生を加速する。さらに、種々なオペレーションを利用して、デスクトップパーソナルコンピュータ、ノートブックパーソナルコンピュータ(PC)及び高精細テレビジョン(HDTV)でのビデオコンテンツの表示を、エイリアシング効果を減少させるサブピクセル計算を含む視覚アーチファクトの除去によって、改善してもよい。従って、本明細書を通じて、一実施の形態では、GPU140が、ビデオ再生を改善し、且つ、CPUの使用を減少させる一以上の特徴、例えば、プログラマブルビデオ処理、MPEG-2デコーディング、デインターレーシング、逆テレシネ、フィルタリング、スケーリング、フォーマット変換、及び運動推定を、サポートするものと理解されるであろう。

【0021】

[0029]CPU120は、任意の適当なマイクロプロセッサに基づくことができる。一実施形態として、CPU120は、仮想マシンの実装をサポートするマイクロプロセッサであってもよい。仮想マシンの実装は、マイクロプロセッサCPUを、種々の機能を実行する専用の別々のパーティションへと論理的に分割することを可能にする。デジタルコンテンツアプリケーションでは、これによって、例えば、あるパーティションを、デジタルコンテンツサービスに専用のものとすることが可能である。例示的な実施の形態として、仮想マシンにおける一つのパーティションが、ビデオプレーヤソフトウェアに専用のものとされてもよい。仮想マシンの実装では、ビデオプレーヤのパーティションが、他のパーティションから分離され、その結果、他のソフトウェアが、ビデオプレーヤのデータを読み取ったり変更したりすることがなくなる。仮想マシンは、ソフトウェアの攻撃に対して改善されたセキュリティを提供し、一方、セキュリティエンジン112は、ハードウェアの攻撃に対して改善されたセキュリティを提供する。仮想マシンとして動作するように設計されたCPUの一実施の形態として、インテルが、ワシントン州レドモンドのマイクロソフトコーポレーションのWindows(登録商標)オペレーティングシステムのコードネーム「ロングホーン(Longhorn)」バージョンをサポートするように設計された統合セキュリティ特徴を有する64ビットペンティアムマイクロプロセッサを開発している。

【0022】

[0030]従来のコンテンツ保護スキームによれば、バス145にてGPU140へ送られるコマンドストリームは、暗号化される必要があり、次いで、GPU復号エンジン147を使用してGPU140にて復号される。従来においては、CPU120が、また、バス145の出力が暗号化されるよう、ブリッジ110へ送られるデジタルコンテンツを再暗号化する機能を実行しなければならなかったであろう。しかしながら、本発明によれば、ブリッジ110が、データの任意の必要な再暗号化を実行する。従って、再暗号化機能が、CPU120からオフロードされ、それによって、CPU性能が改善される。その上、セキュリティエンジン112は、CPU195内のソフトウェアベースの暗号化/復号に比べて暗号化/復号に必要とされる電力消費を低減する専用ハードウェアを有することが可能である。さらに、一実施の形態では、ブリッジ110は、メモリ130での記憶のためにメモリバス135を通して送信されるデータを暗号化し、それによって、セキュリティを改善する。

【0023】

[0031]図2は、セキュリティエンジン112の典型的な実装形態を示している。一実施の形態では、セキュリティエンジン112は、レジスタスペース210、マイクロコントローラ220、及び読取り専用メモリ(ROM)コードストア230を備えている。サポートされた暗号化アルゴリズムの各々は、暗号化/復号アルゴリズムを実行するためのものであってチップメモリバッファ245に関連付けられた専用の改竄防止暗号化ハードウェアモジュール240(通常「暗号化ハードウェア」として知られている)を含むことができる。通信モジュール250は、直接メモリアクセス(DMA)及びシステム100の他のコンポーネントとのピアツーピア(P2P)通信をサポートする。

【0024】

[0032]図3は、ノースブリッジアーキテクチャーを例示している。この実施の形態では、セキュリティエンジン112が、ノースブリッジチップ305内に設けられている。通常のサウスブリッジチップ310が、ノースブリッジチップ305に結合されている。

【0025】

[0033]図4は、サウスブリッジアーキテクチャーを例示している。この実施の形態では、セキュリティエンジン112が、サウスブリッジチップ410内に設けられている。サウスブリッジチップ410は、ノースブリッジチップ405に結合されていてもよい。しかしながら、AMD K8プロセッサのようなマイクロプロセッサCPUは、統合ノースブリッジ機能を有している。したがって、この場合には、サウスブリッジチップ410が、CPU120に直接に接続されることが理解されるであろう。

【0026】

[0034]前述したように、一実施の形態では、セキュリティエンジン112は、PCIアーキテクチャー環境(例えば、PCI-E仕様書又はPCI2.2仕様書に記載されているようなPCI-エクスプレス環境。これら仕様書は、共にPCI-SIGによって刊行されており、その内容を参照することによって本明細書に援用する。)にて動作するように設計されている。PCIアーキテクチャーは、CPU及びデバイスのメモリに対する読取り書込みトランザクション、並びに特殊コンフィギュレーションによるデバイスに対する読取り書込みトランザクション、I/O、及びメモリマップI/O(MMIO)トランザクションをサポートする。各PCI準拠デバイスは、当該デバイスを検出し、当該デバイスに問い合わせを行い、当該デバイスを設定することを可能にする「コンフィギュレーションスペース」をサポートする。各「コンフィギュレーションスペース」は、CPU及び他のデバイスがそのデバイスに対して読取り書込みを行うアドレス領域を任意にサポートしてもよい。これらの領域は、「ベースアドレスレジスタ」(BAR)によって定義される。

【0027】

[0035]図5は、CPU又は他のデバイスからメモリマップの読取り及び書込みを介してメモリマップアドレス領域へのアクセスを可能にするベースアドレスレジスタ520を有するPCIコンフィギュレーションスペース510を例示している。デバイス制御及びデータ構造体は、BARによって指示されるアドレス領域に埋め込むことができる。例えば、以下に説明する制御及びデータ構造体は、セキュリティエンジン112の一実施の形態ではBARによって指示される一以上のアドレス領域に埋め込むことができる。

【0028】

[0036]図6は、コンテクストスイッチを実装するための典型的なコンテクストデータ構造体610を例示している。一実施の形態では、セキュリティエンジン112は、コンテクストデータ構造体610のM個のインスタンスに対応する整数M個の同時セッションをサポートすることができる。キー配列630は、異なるキー(又は一つより多いキー)を必要とする種々の暗号化、復号、又はトランスコーディングアルゴリズムを使用することを可能とする。一実施の形態では、整数N個のキーがキー配列630によってサポートされる。コンテクストは、ソースアドレス、宛先アドレス、及びメモリ属性(例えば、直接メモリアドレス)に基づいて選択される。典型的なコンテクストデータ構造体610は、暗号化又は復号のいずれが実行されるべきかを定めるコンテクスト情報e/dフィールド612、使用されるべき暗号化/復号アルゴリズムを定めるe/dアルゴリズムフィールド614、DMAが使用されるか否かを定めるフィールド616、メモリからのDMA用にデバイスによって必要とされるパラメータを定めるDMA入力記述子フィールド618、デバイスからの出力のために必要とされるパラメータを定める出力記述子フィールド620、キーアレイ630における第1のキーを特定するインデックスフィールド622、及び暗号化/復号アルゴリズムによって使用されるキーの数を指示するナンバーフィールド624を含む。

【0029】

[0037]典型的なコンテクストデータ構造体610を、また、疑似コードとして表してもよい。一実施の形態では、セキュリティエンジンが、整数M個のコンテクスト及び整数N個のオンチップキーをサポートする。各コンテクストは、種々の数のキーを使用してもよい。さらに、各コンテクストは、入力データを読み取ることができるようにする(又は入力データをそれに書き込ませる)のに必要な情報、及び出力データを書き込むことができるようにするのに必要な情報を有する。DMAアドレス記述子テーブル又は他の記述子を備えて、DMAアクセスをサポートしてもよい。また、現在のコンテクストへのインデックスを提供しており、これによって、(コンテクストを変更し、現在のインデックスを変更するための)高速コンテクストスイッチを可能にしている。ベースアドレスレジスタからのオフセットを提供して、セキュリティエンジン112を単一PCIデバイスにおける幾つかの機能の一つとして実施できるようにしている。疑似コードにおいては、これらデータ構造体が、一以上のセキュリティエンジンBARへ次のようにマッピングされる。

Integer N

Integer M

Index current_context

Offset_from_base_address_MMIO_input

Key keys[N]

【0030】

典型的なコンテクストデータ構造体は次の通りである。

Struct {

Boolean encrypt_not decrypt;

Enumerated encryption_decryption_algorithm;

Boolean use_dma

DMA_input dma_input

Output output

Index start_key(index into keys)

Integer number_of_keys

(numberof keys must be consistent with encryption decryption algorithm)

} Contexts[M]

ここで、

struct DMA input{

Address data_descript_table

Integer length

}

Struct Output{

Address addr

Integer limit

}

【0031】

[0038]本発明によれば、セキュリティエンジン112を使用して、暗号化、復号又はトランスコードを行う幾つかの異なる入力モードが可能になる。セキュリティエンジン112への入力は、CPUからの直接的書込み、別のデバイスからの直接的書込み、又は直接メモリアクセスを通してなされる入力であることが可能である。一例として、デバイスへのメモリマップ書込みは、CPUによって、又はピアツーピアトランザクションを介した別のデバイスによって行うことが可能である。一例として、CPUは、クリアテキストをセキュリティエンジンへ書き込むことが可能である。次いで、セキュリティエンジンは、暗号化を実行して暗号テキストを宛先へ書き込む。別の例として、CPU又は他のデバイスが、暗号テキストをセキュリティエンジン112へ書き込むことが可能である。この場合には、セキュリティエンジン112が、その暗号テキストを復号してクリアテキストの出力を宛先へ書き込む。直接メモリアクセス入力の場合には、直接メモリアクセスを使用して、CPU又は別のデバイスによって書き込まれるコンテンツデータをメモリから読み取る。直接メモリアクセスがクリアテキストデータに対するものである場合には、セキュリティエンジン112が、暗号テキストの暗号化及び書込みを行う。直接メモリアクセスがクリアテキストデータに対するものである場合には、セキュリティエンジン112は、復号してクリアテキストデータを書き込む。

【0032】

[0039]出力は、物理メモリに対して成すことが可能であり、又はピアツーピアを使用して別のデバイスに対して成すことも可能である。一実施の形態では、出力は、プログラマブルアドレスによって決定される。例えば、プログラマブルアドレスは、物理メモリ又は別のデバイスのメモリスペースにおける出力アドレス領域であることができる。

【0033】

[0040]入力モードは、CPU120によるMIMO書き込み、又はピアツーピア書込みを使用する他のデバイスによるMMIO書込みを含む。出力モードは、メモリに対する直接的メモリアクセス、及びピアツーピアを含む。1つの実施形態では、CPU120は、クリアテキストデータを暗号化エンジン112へ直接的に書き込むことができる。暗号化エンジンは、暗号化されたデータをメモリ130へ書き込むことができ、クリアデータテキストデータをメモリ130に記憶する必要をなくすることができる。

【0034】

[0041]本発明の典型的なアプリケーションとしては、再生用のビデオの暗号化及び復号のアプリケーション、ネットワーク記憶のような記憶アプリケーションのための異なる標準間の暗号化及び復号(すなわち、トランスコーディング)、ネットワークトラフィックの暗号化、復号、及びトランスコーディング、並びに、パーソナルビデオレコーダーシステムにおけるコンテンツの暗号化及び復号のアプリケーションがある。

【0035】

[0042]図7は、ビデオを安全に表示するためのオペレーションの典型的なシーケンスを示している。例示として、ブリッジ110が、ノースブリッジチップ610-A及びサウスブリッジチップ610-Bとして示されている。コンポーネント間のバスは、図を簡単化するために省略されている。矢印701によって示されるように、CPU120は、ビデオコンテンツソース160からビデオデータを読み取る。コンテンツ保護プロトコルによれば、コンテンツは暗号化される。CPU120は、ソフトウェア復号技法を使用してCPU120内で復号702を行う。クリアテキストデータが、矢印703で示されるようにCPU120によってセキュリティエンジン112へ送られる。フロントサイドバスは傍受され難いので、CPU120からセキュリティエンジン112へのクリアテキストデータの送信は、本来的に安全である。セキュリティエンジン112は、データ704を暗号化する。次いで、セキュリティエンジン112は、直接メモリアクセスを使用して、暗号テキストをメモリ130に書き込む(705)。その結果、メモリバス(図示していない)を通して送信されるコンテンツは安全となる。次いで、GPU140が、直接メモリアクセスを使用して、暗号テキストを読み取る(706)。次に、GPU140は、そのコンテンツを復号し表示する(707)。

【0036】

[0043]図7を参照するに、本発明によって提供される一つの利点は、ハッキングを受け易いシステムの各部においてコンテンツが暗号テキストとして送信され記憶されるという点である。従って、デジタルコンテンツ保護が改善される。加えて、コンテンツの暗号化に関連したCPUのオーバーヘッドが減少され、CPUの性能が改善される。さらに、セキュリティエンジン112は、好ましくは、暗号化及び復号オペレーションを行うのにCPU120よりもより良い電力効率を有するように設計される。その結果、セキュリティエンジン112への暗号化/復号オペレーションのオフロードによって、電力消費を減少することが可能である。

【0037】

[0044]本発明の別のアプリケーションとして、パーソナルビデオレコーダー(PVR)アプリケーションがある。PVRは、HDTV信号といったテレビジョン信号を記録する。図8は、デジタルテレビジョン(DTV)のための典型的なPVRシステム800を例示している。PVRシステム800は、例えば、CPU120、GPU140、ディスプレイ150、メモリ130、及びブリッジ110のような少なくとも一つのブリッジを有するメディアセンターパーソナルコンピュータであってもよい。ビデオキャプチャ(VC)モジュール805が、PVRシステム800に含まれており、例えば、ブリッジ110に含まれていてもよい。VCモジュール805は、記憶のためブロードキャスト信号を取り込む。HDTV受信器802が、ブロードキャスト信号を受け取るためPVRシステム800に結合されていてもよい。HDTV受信器802は、例えば、復調及び復号を実行して、復調データパケットのトランスポートストリームの形態でビデオ信号810を生成してもよい。ビデオ信号810は、その実装形態に依存して、ブリッジ110により直接的に受け取られてもよく、又は、別のコンポーネントからブリッジ110へ結合されてもよい。

【0038】

[0045]将来のテレビジョン受信器は、ブロードキャストフラグを認識する必要があり、そのブロードキャストフラグの検出に応答してデジタルコンテンツ保護スキームを実施し、取り入れたビデオがインターネット又はその他のマス方法を介して分配されないようにすることが提案されている。その結果、受信されたブロードキャストHDTV信号のコピーは、保護されたフォーマットにて維持され、これによって、エンドユーザがビデオコンテンツの保護されていないコピーを分配することが困難なものとされる。ブロードキャストフラグを、例えば、プログラム及びシステム情報プロトコル(PSIP)に従ってアドバンスドテレビジョンシステムコミッティ(ATSC)のヘッダーに含めてもよい。本発明の一実施の形態では、PVRシステム800は、ブロードキャストフラグがビデオ信号810に存在するか否かを検出する。ブロードキャストフラグが存在する場合には、デジタルコンテンツ保護をサポートするのに必要とされる暗号化/復号サービスがセキュリティエンジン112へ移動される。PVRアプリケーションの場合には、多くのプロセスは、データのソースがブロードキャスト信号であること、及び、ブロードキャストフラグの存在が監視されることを除けば、図7に記載したプロセスと同一である。例えば、PVRシステム800は、メモリ130に記憶して後に再生するために受信したビデオ信号のコピーを暗号化し、その後の再生に必要な復号を行ってもよい。

【0039】

[0046]本発明の典型的なアプリケーションについて説明してきたが、より一般的には、本発明を利用して、種々の異なるタイプのデバイス及びメモリのための暗号化、復号又はトランスコーディングサービスを提供し得る。暗号化、復号又はトランスコーディングサービスは、メモリスティック又はネットワーク記憶デバイスに対して提供することができる。例えば、ネットワーク記憶デバイスでは、セキュリティエンジン112を使用して、記憶用のデータを暗号化してもよい。ネットワーク記憶装置の一実施の形態では、セキュリティエンジン112は、暗号化フォーマットが第1の暗号化フォーマット(例えば、ネットワークを通して送信されるデータのための暗号化フォーマット)から第2の暗号化フォーマット(例えば、データ記憶のための暗号化フォーマット)へ変換されるようなトランスコーディングを実行する。

【0040】

[0047]一実施の形態では、セキュリティエンジン112は、ブリッジ110とは別の分離したデバイスに形成される。例えば、セキュリティエンジン112が、ブリッジ110とは異なるチップに形成されてもよい。この実施形態では、PCI-Eのような入力/出力インターフェイスを使用して、セキュリティエンジン112をチップセットにおける他のコンポーネントへ結合してもよい。この代替の実装形態の一つの利点は、セキュリティエンジン112の機能的な利点を異なる物理的パーティショニングを用いてチップセットにて達成できることである。一例として、基本的なチップセットは、セキュリティエンジン112なしに設計できる。高いセキュリティを必要とするマーケットの場合には、セキュリティエンジン112を含むデバイスを、I/Oインターフェイスを介して基本チップセット構造に結合して、高いセキュリティを有したチップセットとすることができる。

【0041】

[0048]前述したように、コンテクスト状態は、複数のコンテクストの使用をサポートするためメモリに記憶される。仮想マシンの実装形態(例えば、ロングホーン)では、パーティションによって、前述したように、ソフトウェアの攻撃に対して高度の保護が提供される。しかしながら、Linux又はWinXpを実行するシステムのように、コンテナの分離を提供するパーティションを有していないシステムにおいては、セキュリティを増すためにメモリに記憶されたコンテクスト情報の付加的保護を提供することが望ましい。一実施の形態では、メモリに記憶されるコンテクスト状態を暗号化/復号するためのキーがセキュリティエンジン112のハードウェアに記憶される。これによって、コンテクスト状態が暗号テキストとしてメモリに記憶させられ、コンテクスト状態情報をクリアテキストとしてメモリに記憶するのに比べて、セキュリティが改善される。

【0042】

[0049]本発明の一実施の形態は、種々のコンピュータ実装のオペレーションを実行するウためのコンピュータコードを有するコンピュータ読取り可能な媒体を備えたコンピュータ記憶製品に関する。媒体及びコンピュータコードは、本発明の目的のために特別に設計及び構成されたものであってもよいし、又は、コンピュータソフトウェア技術の分野において当業者に良く知られて利用可能となっている種類のものであってもよい。コンピュータ読取り可能な媒体の例として、これに限定されないが、ハードディスク、フロッピーディスク、及び磁気テープのような磁気媒体、CD-ROM及びホログラフィックデバイスのような光学的媒体、光ディスクのような磁気-光媒体、並びに、特定用途向け集積回路(ASIC)、プログラマブル論理デバイス(PLD)、ROM及びRAMデバイスのようにプログラムコードを記憶し実行するように特別に構成されたハードウェアデバイスがある。コンピュータコードの例としては、コンパイラによって生成されるようなマシンコード、及びインタープリタを使用してコンピュータにより実行されるようなより高レベルのコードを含むファイルがある。例えば、本発明の一実施の形態は、Java、C++、又は他のオブジェクト指向プログラミング言語及び開発ツールを使用して実施できる。本発明の別の実施の形態は、適宜、マシン実行可能なソフトウェア命令の代わりに、又はマシン実行可能なソフトウェア命令と組み合わせて、ハード・ワイヤード回路でも実施し得る。

[0050]前述の記載では、本発明を完全に理解させるために特定の用語を使用した。しかしながら、特定の細部が本発明の実施に必要でないことが当業者に明らかであろう。従って、前述の本発明の特定の実施形態についての記載は、単なる例示に過ぎない。それらの記載はそれに尽きるものでなく、又、本発明を、それら説明した細部の構成に限定しようとするものではなく、前述の記載に鑑みれば、多くの変形例が可能であることは明らかであろう。前述の実施形態は、本発明の原理及びその実際的な応用について最も良く説明するために選択されたものであり、従って、当業者であれば、本発明及び種々な実施形態について意図する特定の使用に適合するような種々な変形を加えて最も良く利用することができるであろう。特許請求の範囲及びその等効物は、本発明の範囲を定めることを意図したものである。

【図面の簡単な説明】

【0043】

【図1】本発明の一実施の形態によるブリッジに配置されたセキュリティエンジンを有するデジタルコンテンツ保護システムのブロック図である。

【図2】本発明の一実施形の態によるセキュリティエンジンのブロック図である。

【図3】本発明の一実施の形態によるノースブリッジの実装形態のブロック図である。

【図4】本発明の一実施の形態によるサウスブリッジの実装形態のブロック図である。

【図5】本発明の一実施の形態によるPCIコンフィギュレーションスペースを示す図である。

【図6】本発明の一実施の形態によるコンテクストデータ構造を示す図である。

【図7】本発明の一実施の形態によるデジタルコンテンツの保護のためのオペレーションの典型的シーケンスを示す図である。

【図8】本発明の一実施の形態によるビデオデータのためのデジタルコンテンツ保護システムのブロック図である。

【符号の説明】

【0044】

110…ブリッジ、112…セキュリティエンジン、114…キー、116…コンテクストポインター、118…コンテクストデータ構造、130…メモリ、147…復号、150…ディスプレイ、160…コンテンツ、185…グラフィックドライバー、190…ビデオプレーヤ、195…暗号化/復号、210…レジスタスペース、220…マイクロコントローラ、230…ROMコードストア

【関連出願の相互参照】

【0001】

[0001]本出願は、本出願人へ共に譲渡され、且つ、本願と同日に米国特許商標庁に出願された「Apparatus, System, and Method for Digital Content Protection」と題する米国特許出願(代理人管理番号NVID−106/02US)に関連するものであり、当該米国特許出願の内容を本明細書に援用する。

【発明の分野】

【0002】

[0002]本発明は、一般に、デジタルコンテンツの保護を提供するための技術に関するものである。より詳細には、本発明は、中央処理装置(CPU)からデジタルコンテンツの保護の側面をオフロード(移動)する技術に関するものである。

【発明の背景】

【0003】

[0003]多くの消費者向け製品における問題の一つは、傍受されてしまうことのある信号経路に沿ってデジタルコンテンツが送信されねばならいことである。その結果として、デジタルコンテンツプロバイダーは、ハッカーによるデジタルコンテンツの許可されていないコピーについて心配しなければならない。例えば、ホームエンターテイメントシステムは、パーソナルコンピュータ(PC)、グラフィックサブシステム、高精細テレビジョン、セットトップボックス、デジタルビデオレコーダ及びプレーヤ、並びにデジタル汎用ディスク(DVD)プレーヤを含み得る。従って、暗号化されていないデジタルコンテンツ(しばしば「クリアテキスト」コンテンツとして知られる)は、ハッカーが、例えば、一以上の信号バスの出力を使用することによって傍受されてしまうというリスクがある。

【0004】

[0004]デジタルコンテンツの保護は、オーディオ及びビデオコンテンツが許可なしにコピーされないようにするために、その重要性を増してきている。デジタルコンテンツの保護は、とりわけ、傍受され得るような信号バスを通して送信されるコンテンツを暗号化するためのプロトコルを含む。デジタル送信コンテンツ保護(DTCP)スキームは、1998年に五つの会社(5C)によって開発され、日立、インテルコーポレーション、松下電器産業、ソニーコーポレーション及び東芝コーポレーションによって1998年7月に刊行された文献「5C Digital Transmission Content Protection」に記載されており、当該文献の内容を本明細書に援用する。このDTCPの方法のより詳細な点については、日立、インテルコーポレーション、松下電器産業、ソニーコーポレーション及び東芝コーポレーションによって2004年1月に刊行された「Digital Transmission Content Protection Specification」改訂1.3に記載されており、その内容を本明細書に援用する。DTCPの方法は、米国電気電子技術者協会(IEEE)1394マルチメディアバスに使用し得るものであり、ソースデバイス及びシンクデバイス(コンテンツストリームを受け取る装置)のためのプロトコルであってコンテンツの安全な送信を確立するためのプロセスを含んでいる。DTCPの方法は、認証及びキー交換(AKE)プロトコル、コンテンツ暗号化、並びに、暗号化モードインジケータ(EMI)を使用するコピーコントロール情報(CCI)を含む。

【0005】

[0005]DTCPのようなデジタルコンテンツの保護のスキームの1つの欠点は、コンテンツがデバイス間のシステムバスにて暗号化されるにもかかわらず、クリアテキストデータが一以上の内部データバスで盗まれやすいというものである。例えば、PCベースのマルチメディアシステムにおけるDVDの再生について考える。DVDコンテンツは、DVDプレーヤから暗号化された形式にて中央処理装置(CPU)によって受け取られる。CPUは、受け取ったデジタルコンテンツを復号する。次いで、CPUは、そのデータを表示装置へ書き込む前にそのDVDデータを再暗号化する。しかしながら、CPUによって行われる復号及び再暗号化では、通常、クリアテキストデータをシステムメモリへ書き込む必要があり、この場合には、コンテンツがメモリバスにて盗まれ易いのである。

【0006】

[0006]デジタルコンテンツの保護スキームの別の欠点は、高精細ビデオの暗号化及び復号を行うのにCPUに相当の負荷を掛けてしまうということである。例えば、アドバンスド暗号化標準(AES)は、略16サイクル/バイト(B)の暗号化コストを要する。圧縮フォーマット高精細テレビジョン(HDTV)は、約50MB/sの暗号化帯域幅に相当し、各圧縮HDTVコンテンツストリームは利用可能なCPUクロックサイクルの800MHzに相当する。これは、数ギガヘルツのクロックレートで動作するCPUには相当の負荷である。その上、幾つかのマルチメディアシステムにおいては、同時に幾つかのビデオストリームを取り扱う能力を有することが望まれており、これによって、最悪のケースのシナリオでは、CPUに対する暗号化/復号の全負荷がCPUクロックサイクルの大部分を消費することがある。

【0007】

[0007]従って、デジタルコンテンツの保護を提供するための改良された装置、システム及び方法が望まれている。

【発明の概要】

【0008】

[0008]中央処理装置をシステムの他のコンポーネントへ接続(ブリッジ)するためのブリッジについて開示する。ブリッジにおけるセキュリティエンジンは、暗号化サービスが中央処理装置からブリッジへと移動されるようにする。一実施の形態では、セキュリティエンジンは、ブリッジの非安全なインターフェイスにおいて、保護されるべきデータを暗号テキストとして暗号化する。

【0009】

[0009]本発明は、添付図面と共に以下なされる詳細な説明を参照することによって、より十分に理解されよう。これら図を通して対応する部分を、同様の参照符号によって指し示す。

【発明の詳細な説明】

【0010】

[0018]図1は、本発明の一実施の形態によるデジタルコンテンツシステム100のブロック図である。デジタルコンテンツシステム100は、セキュリティエンジン112を有するブリッジ110を含む。本発明の一実施の形態によれば、セキュリティサービスは、CPU120より下流の少なくとも一つのデバイス用のデータの暗号化といったものであり、CPU120からセキュリティエンジン112を使用するブリッジ110へ移動される。

【0011】

[0019]ブリッジ110は、単一チップとして、一群のチップとして、又はCPU120が形成されているチップの一部分として実装し得るものである。以下に詳述するように、ブリッジ110は、中央処理装置(CPU)120を他のデバイスへと接続(ブリッジ)するためのチップセットの部分として使用される任意のブリッジを含み得るものであり、例えば、ノースブリッジチップ、サウスブリッジチップ、又は、ノースブリッジチップ及びサウスブリッジチップの組み合わせといったものである。

【0012】

[0020]セキュリティエンジン112は、ブリッジ110内で暗号化サービスを実行する。典型的な暗号化サービスとしては、暗号化、復号、及びトランスコード(すなわち、異なる暗号化フォーマット間の変換)がある。暗号化サービスは、例えば、保護される必要のあるデータクラスに適用し得る。あるアプリケーションでは、ブリッジを通るデータの全てが暗号化サービスを必要とする。しかしながら、より一般的には、保護を必要とするデータ、例えば、デジタルコンテンツの保護を必要とするデータのようなデータのみが、暗号化サービスを必要とする。セキュリティエンジン112によって提供される暗号化サービスを利用して、ハッキングを受けやすいデジタルコンテンツシステム100の各部におけるデータ(例えば、ビデオコンテンツのようなデジタルコンテンツ)を保護してもよい。

【0013】

[0021]暗号化サービスは、データ書込みオペレーションのようなデータアクセスオペレーション中に提供することが可能である。暗号化/復号キー114は、暗号化サービスをサポートするためにセキュリティエンジン112に記憶されている。単一の暗号化及び/又は復号キーが記憶されているが、より一般的には、暗号化、復号、又はトランスコードのうち一以上のタイプをサポートするために追加のキーを記憶してもよい。一実施の形態では、コンテクストポインター116が、メモリ130内のコンテクストデータ118といったコンテクストデータのソースを指示する。コンテクストデータ118は、特定のソース/宛先アドレスに対してセキュリティエンジン112によって行われるべき特定の暗号化サービス(例えば、暗号化、復号又はトランスコード)をコンテクストスイッチが選択できるようにするデータ構造体を含む。各コンテクストが、また、特定の暗号化/復号キーを指示してもよい。

【0014】

[0022]一実施の形態においては、セキュリティエンジン112は、圧縮又は非圧縮データの標準暗号化及び復号技法(例えば、アドバンスド暗号化標準(AES)、トリプルデータ暗号化標準(3DES)、又はパブリック/プライベートキーリモートサーバー管理(RSM))をサポートする。しかしながら、セキュリティエンジン112は、また、他の暗号化プロトコルをサポートするように構成されていてもよい。典型的なトランスコードアプリケーションとしては、一つの暗号化標準のフォーマットから別の一つの暗号化標準のフォーマットへの変換、又は、二つの異なる暗号化キーの間の変換、例えば、第1キーでのAESと第2キーでのAESとの間の変換の実行がある。セキュリティエンジン112は、好ましくは、専用の改竄防止暗号化ハードウェアを少なくとも部分的に用いて実装されており、これにより、ソフトウェアのみによる暗号化/復号アルゴリズムの実行と比較してセキュリティが改善されるという利点が得られる。また、セキュリティエンジン112を専用ハードウェアで実施することによって、更に、性能及び電力消費における改善が可能となる。

【0015】

[0023]ブリッジ110は、CPU120、メモリ130、及びグラフィック処理装置(GPU)140(図示の例ではディスプレイ150に結合されている)といった他の装置を結合している。ブリッジ110は、フロントサイドバス(FSB)のようなバスインターフェイス121を有するバス122によって、CPU120に結合されている。CPUをブリッジに結合するバスインターフェイス121は、典型的には、専用高速インターフェイスであり、当該専用高速インターフェイスは、半田接続、埋め込み回路パス、及び高速なデータ速度のために、バスへのハッキングを困難なものとするのであり、本来的にセキュリティの高いものである。従って、以下の説明を通じて、クリアテキストデータがCPU120からブリッジ110へバスインターフェイス121を通して安全に送信できることが理解されるであろう。これは、アセンブルされたユニットにおいては、バスインターフェイス121からハッカーがデータを傍受することが、非常に難しいものであるからである。

【0016】

[0024]システム100においては、ブリッジ110とコンポーネント130及び140のような他のコンポーネントとの間に非安全なリンクを有する幾つかの経路がある。リンクが安全でないのは、例えば、ブリッジインターフェイス124又は126及びそれに関連するバス135又は145が潜在的にハッカーによってアクセスできる場合である。例えば、メモリバス135又はGPU140へのバス145は、それらバス135又は145が、確実に半田付けされていないか、及び/又は、それらバス135又は145へのハッキングが可能であるような低いデータレートを有する場合には、安全ではないことがある。

【0017】

[0025]入力経路としては、CPU120からブリッジ110への直接書込みのような、他のデバイスからブリッジ110への入力データの書込み経路がある。出力経路としては、GPU140への書込み又はメモリ130への書込みのように、ピアツーピア技法を使用する他のデバイスへのブリッジ110からの出力データの直接書込み経路がある。更に、直接メモリアクセス経路としては、CPU110がメモリ130へ書き込む直接メモリアクセスのようなメモリ130への直接書込み経路がある。ブリッジ110は、一つのデバイスから別の一つのデバイスへデータを書き込みすることが可能であり且つ直接メモリアクセスを可能とする任意のインターフェイスを利用できる。一実施の形態では、ブリッジ110は、GPU140のような少なくとも一つ他のデバイスとの高速インターフェイスとして、周辺コンポーネントインターフェイスエクスプレス(PCI-E)を使用するようになっている。PCI-Eは、周辺コンポーネントインターフェイススペシャルインタレストグループ(PCI-SIG)によって刊行された「PCIeベース仕様書」に記載された高速インターフェイス標準であり、この仕様書の内容を本明細書に援用する。しかしながら、より一般的には、CPU110をブリッジ110へ結合するPCI-Eの代わりに周辺コンポーネントインターフェイス(PCI)のような他の工業標準インターフェイスを使用することも可能である。

【0018】

[0026]一実施の形態では、セキュリティエンジン112は、PCIデバイスであり、当該PCIデバイスを、例えば、PCIバス0に実装して、セキュリティエンジン112をマザーボード製造時に認証及び承認することを可能にしている。PCIアーキテクチャーにおいては、一次バス番号、二次バス番号、及び下位バス番号に対応する異なるバス番号がある。PCIバス0は、ホストブリッジが接続するバスであるものと定義され、当該ホストブリッジは、CPUをPCIシステムへ接続する。暗号化/復号キーをセキュリティエンジン112へロードするために特権書込みを使用してもよい。

【0019】

[0027]図1は、CPU120においてビデオプレーヤ(VP)アプリケーション190及びグラフィックドライバー185を実行する典型的なアプリケーション185を例示している。暗号化されたデジタルコンテンツは、DVDプレーヤのようなデジタルコンテンツソースプレーヤ160から受け取られる(例示のために、デジタルコンテンツソースプレーヤ160を、直接的にCPU120に取り付けているように示しているが、より正確には、プレーヤ160は入力デバイスポートに接続される)。デジタルコンテンツ保護プロトコルに従って、CPU120は、暗号化/復号ソフトウェア195を有しており、デジタルコンテンツソース160から暗号化されたデジタルコンテンツを読み取り、暗号化/復号ソフトウェア195を使用して暗号化されたコンテンツの初期復号を実行する。VPアプリケーション190は、一以上のビデオストリームの再生及び/又は記憶を管理するためのオペレーションを実行する。

【0020】

[0028]GPU140は、ビデオフレームを生成するためのコマンドをCPU120から受け取り、また、通常、メモリ130からビデオデータを受け取る。GPU140の一つの特徴は、CPU140の使用を減少させるためにビデオ処理オペレーションをGPU140へ移動し得ることである。しかしながら、GPU140の別の特徴は、改善された表示特性を有するビデオフレームを生成し得ることである。ビデオコンテンツは、例えば、パーソナルコンピュータ又は高精細テレビジョンにおいて表示するのに最適化されていないようなオリジナルフォーマットで生成されることがある。例えば、カリフォルニア州サンタクララのNvidiaコーポレーションによって販売されているNvidia PureVideo Decoderは、GeForce6及び7シリーズのGPUで作動する。GeForce6及び7シリーズのGPUは、プログラマブルビデオプロセッサ、MPEG-2復号エンジン、及び運動推定エンジンを備えている。Nvidia PureVideo Decoderは、ハードウェアアクセラレーションを使用して、フィルタリング、スケーリング、フォーマット変換、及びその他のオペレーションを行い、ビデオの再生を加速する。さらに、種々なオペレーションを利用して、デスクトップパーソナルコンピュータ、ノートブックパーソナルコンピュータ(PC)及び高精細テレビジョン(HDTV)でのビデオコンテンツの表示を、エイリアシング効果を減少させるサブピクセル計算を含む視覚アーチファクトの除去によって、改善してもよい。従って、本明細書を通じて、一実施の形態では、GPU140が、ビデオ再生を改善し、且つ、CPUの使用を減少させる一以上の特徴、例えば、プログラマブルビデオ処理、MPEG-2デコーディング、デインターレーシング、逆テレシネ、フィルタリング、スケーリング、フォーマット変換、及び運動推定を、サポートするものと理解されるであろう。

【0021】

[0029]CPU120は、任意の適当なマイクロプロセッサに基づくことができる。一実施形態として、CPU120は、仮想マシンの実装をサポートするマイクロプロセッサであってもよい。仮想マシンの実装は、マイクロプロセッサCPUを、種々の機能を実行する専用の別々のパーティションへと論理的に分割することを可能にする。デジタルコンテンツアプリケーションでは、これによって、例えば、あるパーティションを、デジタルコンテンツサービスに専用のものとすることが可能である。例示的な実施の形態として、仮想マシンにおける一つのパーティションが、ビデオプレーヤソフトウェアに専用のものとされてもよい。仮想マシンの実装では、ビデオプレーヤのパーティションが、他のパーティションから分離され、その結果、他のソフトウェアが、ビデオプレーヤのデータを読み取ったり変更したりすることがなくなる。仮想マシンは、ソフトウェアの攻撃に対して改善されたセキュリティを提供し、一方、セキュリティエンジン112は、ハードウェアの攻撃に対して改善されたセキュリティを提供する。仮想マシンとして動作するように設計されたCPUの一実施の形態として、インテルが、ワシントン州レドモンドのマイクロソフトコーポレーションのWindows(登録商標)オペレーティングシステムのコードネーム「ロングホーン(Longhorn)」バージョンをサポートするように設計された統合セキュリティ特徴を有する64ビットペンティアムマイクロプロセッサを開発している。

【0022】

[0030]従来のコンテンツ保護スキームによれば、バス145にてGPU140へ送られるコマンドストリームは、暗号化される必要があり、次いで、GPU復号エンジン147を使用してGPU140にて復号される。従来においては、CPU120が、また、バス145の出力が暗号化されるよう、ブリッジ110へ送られるデジタルコンテンツを再暗号化する機能を実行しなければならなかったであろう。しかしながら、本発明によれば、ブリッジ110が、データの任意の必要な再暗号化を実行する。従って、再暗号化機能が、CPU120からオフロードされ、それによって、CPU性能が改善される。その上、セキュリティエンジン112は、CPU195内のソフトウェアベースの暗号化/復号に比べて暗号化/復号に必要とされる電力消費を低減する専用ハードウェアを有することが可能である。さらに、一実施の形態では、ブリッジ110は、メモリ130での記憶のためにメモリバス135を通して送信されるデータを暗号化し、それによって、セキュリティを改善する。

【0023】

[0031]図2は、セキュリティエンジン112の典型的な実装形態を示している。一実施の形態では、セキュリティエンジン112は、レジスタスペース210、マイクロコントローラ220、及び読取り専用メモリ(ROM)コードストア230を備えている。サポートされた暗号化アルゴリズムの各々は、暗号化/復号アルゴリズムを実行するためのものであってチップメモリバッファ245に関連付けられた専用の改竄防止暗号化ハードウェアモジュール240(通常「暗号化ハードウェア」として知られている)を含むことができる。通信モジュール250は、直接メモリアクセス(DMA)及びシステム100の他のコンポーネントとのピアツーピア(P2P)通信をサポートする。

【0024】

[0032]図3は、ノースブリッジアーキテクチャーを例示している。この実施の形態では、セキュリティエンジン112が、ノースブリッジチップ305内に設けられている。通常のサウスブリッジチップ310が、ノースブリッジチップ305に結合されている。

【0025】

[0033]図4は、サウスブリッジアーキテクチャーを例示している。この実施の形態では、セキュリティエンジン112が、サウスブリッジチップ410内に設けられている。サウスブリッジチップ410は、ノースブリッジチップ405に結合されていてもよい。しかしながら、AMD K8プロセッサのようなマイクロプロセッサCPUは、統合ノースブリッジ機能を有している。したがって、この場合には、サウスブリッジチップ410が、CPU120に直接に接続されることが理解されるであろう。

【0026】

[0034]前述したように、一実施の形態では、セキュリティエンジン112は、PCIアーキテクチャー環境(例えば、PCI-E仕様書又はPCI2.2仕様書に記載されているようなPCI-エクスプレス環境。これら仕様書は、共にPCI-SIGによって刊行されており、その内容を参照することによって本明細書に援用する。)にて動作するように設計されている。PCIアーキテクチャーは、CPU及びデバイスのメモリに対する読取り書込みトランザクション、並びに特殊コンフィギュレーションによるデバイスに対する読取り書込みトランザクション、I/O、及びメモリマップI/O(MMIO)トランザクションをサポートする。各PCI準拠デバイスは、当該デバイスを検出し、当該デバイスに問い合わせを行い、当該デバイスを設定することを可能にする「コンフィギュレーションスペース」をサポートする。各「コンフィギュレーションスペース」は、CPU及び他のデバイスがそのデバイスに対して読取り書込みを行うアドレス領域を任意にサポートしてもよい。これらの領域は、「ベースアドレスレジスタ」(BAR)によって定義される。

【0027】

[0035]図5は、CPU又は他のデバイスからメモリマップの読取り及び書込みを介してメモリマップアドレス領域へのアクセスを可能にするベースアドレスレジスタ520を有するPCIコンフィギュレーションスペース510を例示している。デバイス制御及びデータ構造体は、BARによって指示されるアドレス領域に埋め込むことができる。例えば、以下に説明する制御及びデータ構造体は、セキュリティエンジン112の一実施の形態ではBARによって指示される一以上のアドレス領域に埋め込むことができる。

【0028】

[0036]図6は、コンテクストスイッチを実装するための典型的なコンテクストデータ構造体610を例示している。一実施の形態では、セキュリティエンジン112は、コンテクストデータ構造体610のM個のインスタンスに対応する整数M個の同時セッションをサポートすることができる。キー配列630は、異なるキー(又は一つより多いキー)を必要とする種々の暗号化、復号、又はトランスコーディングアルゴリズムを使用することを可能とする。一実施の形態では、整数N個のキーがキー配列630によってサポートされる。コンテクストは、ソースアドレス、宛先アドレス、及びメモリ属性(例えば、直接メモリアドレス)に基づいて選択される。典型的なコンテクストデータ構造体610は、暗号化又は復号のいずれが実行されるべきかを定めるコンテクスト情報e/dフィールド612、使用されるべき暗号化/復号アルゴリズムを定めるe/dアルゴリズムフィールド614、DMAが使用されるか否かを定めるフィールド616、メモリからのDMA用にデバイスによって必要とされるパラメータを定めるDMA入力記述子フィールド618、デバイスからの出力のために必要とされるパラメータを定める出力記述子フィールド620、キーアレイ630における第1のキーを特定するインデックスフィールド622、及び暗号化/復号アルゴリズムによって使用されるキーの数を指示するナンバーフィールド624を含む。

【0029】

[0037]典型的なコンテクストデータ構造体610を、また、疑似コードとして表してもよい。一実施の形態では、セキュリティエンジンが、整数M個のコンテクスト及び整数N個のオンチップキーをサポートする。各コンテクストは、種々の数のキーを使用してもよい。さらに、各コンテクストは、入力データを読み取ることができるようにする(又は入力データをそれに書き込ませる)のに必要な情報、及び出力データを書き込むことができるようにするのに必要な情報を有する。DMAアドレス記述子テーブル又は他の記述子を備えて、DMAアクセスをサポートしてもよい。また、現在のコンテクストへのインデックスを提供しており、これによって、(コンテクストを変更し、現在のインデックスを変更するための)高速コンテクストスイッチを可能にしている。ベースアドレスレジスタからのオフセットを提供して、セキュリティエンジン112を単一PCIデバイスにおける幾つかの機能の一つとして実施できるようにしている。疑似コードにおいては、これらデータ構造体が、一以上のセキュリティエンジンBARへ次のようにマッピングされる。

Integer N

Integer M

Index current_context

Offset_from_base_address_MMIO_input

Key keys[N]

【0030】

典型的なコンテクストデータ構造体は次の通りである。

Struct {

Boolean encrypt_not decrypt;

Enumerated encryption_decryption_algorithm;

Boolean use_dma

DMA_input dma_input

Output output

Index start_key(index into keys)

Integer number_of_keys

(numberof keys must be consistent with encryption decryption algorithm)

} Contexts[M]

ここで、

struct DMA input{

Address data_descript_table

Integer length

}

Struct Output{

Address addr

Integer limit

}

【0031】

[0038]本発明によれば、セキュリティエンジン112を使用して、暗号化、復号又はトランスコードを行う幾つかの異なる入力モードが可能になる。セキュリティエンジン112への入力は、CPUからの直接的書込み、別のデバイスからの直接的書込み、又は直接メモリアクセスを通してなされる入力であることが可能である。一例として、デバイスへのメモリマップ書込みは、CPUによって、又はピアツーピアトランザクションを介した別のデバイスによって行うことが可能である。一例として、CPUは、クリアテキストをセキュリティエンジンへ書き込むことが可能である。次いで、セキュリティエンジンは、暗号化を実行して暗号テキストを宛先へ書き込む。別の例として、CPU又は他のデバイスが、暗号テキストをセキュリティエンジン112へ書き込むことが可能である。この場合には、セキュリティエンジン112が、その暗号テキストを復号してクリアテキストの出力を宛先へ書き込む。直接メモリアクセス入力の場合には、直接メモリアクセスを使用して、CPU又は別のデバイスによって書き込まれるコンテンツデータをメモリから読み取る。直接メモリアクセスがクリアテキストデータに対するものである場合には、セキュリティエンジン112が、暗号テキストの暗号化及び書込みを行う。直接メモリアクセスがクリアテキストデータに対するものである場合には、セキュリティエンジン112は、復号してクリアテキストデータを書き込む。

【0032】

[0039]出力は、物理メモリに対して成すことが可能であり、又はピアツーピアを使用して別のデバイスに対して成すことも可能である。一実施の形態では、出力は、プログラマブルアドレスによって決定される。例えば、プログラマブルアドレスは、物理メモリ又は別のデバイスのメモリスペースにおける出力アドレス領域であることができる。

【0033】

[0040]入力モードは、CPU120によるMIMO書き込み、又はピアツーピア書込みを使用する他のデバイスによるMMIO書込みを含む。出力モードは、メモリに対する直接的メモリアクセス、及びピアツーピアを含む。1つの実施形態では、CPU120は、クリアテキストデータを暗号化エンジン112へ直接的に書き込むことができる。暗号化エンジンは、暗号化されたデータをメモリ130へ書き込むことができ、クリアデータテキストデータをメモリ130に記憶する必要をなくすることができる。

【0034】

[0041]本発明の典型的なアプリケーションとしては、再生用のビデオの暗号化及び復号のアプリケーション、ネットワーク記憶のような記憶アプリケーションのための異なる標準間の暗号化及び復号(すなわち、トランスコーディング)、ネットワークトラフィックの暗号化、復号、及びトランスコーディング、並びに、パーソナルビデオレコーダーシステムにおけるコンテンツの暗号化及び復号のアプリケーションがある。

【0035】

[0042]図7は、ビデオを安全に表示するためのオペレーションの典型的なシーケンスを示している。例示として、ブリッジ110が、ノースブリッジチップ610-A及びサウスブリッジチップ610-Bとして示されている。コンポーネント間のバスは、図を簡単化するために省略されている。矢印701によって示されるように、CPU120は、ビデオコンテンツソース160からビデオデータを読み取る。コンテンツ保護プロトコルによれば、コンテンツは暗号化される。CPU120は、ソフトウェア復号技法を使用してCPU120内で復号702を行う。クリアテキストデータが、矢印703で示されるようにCPU120によってセキュリティエンジン112へ送られる。フロントサイドバスは傍受され難いので、CPU120からセキュリティエンジン112へのクリアテキストデータの送信は、本来的に安全である。セキュリティエンジン112は、データ704を暗号化する。次いで、セキュリティエンジン112は、直接メモリアクセスを使用して、暗号テキストをメモリ130に書き込む(705)。その結果、メモリバス(図示していない)を通して送信されるコンテンツは安全となる。次いで、GPU140が、直接メモリアクセスを使用して、暗号テキストを読み取る(706)。次に、GPU140は、そのコンテンツを復号し表示する(707)。

【0036】

[0043]図7を参照するに、本発明によって提供される一つの利点は、ハッキングを受け易いシステムの各部においてコンテンツが暗号テキストとして送信され記憶されるという点である。従って、デジタルコンテンツ保護が改善される。加えて、コンテンツの暗号化に関連したCPUのオーバーヘッドが減少され、CPUの性能が改善される。さらに、セキュリティエンジン112は、好ましくは、暗号化及び復号オペレーションを行うのにCPU120よりもより良い電力効率を有するように設計される。その結果、セキュリティエンジン112への暗号化/復号オペレーションのオフロードによって、電力消費を減少することが可能である。

【0037】

[0044]本発明の別のアプリケーションとして、パーソナルビデオレコーダー(PVR)アプリケーションがある。PVRは、HDTV信号といったテレビジョン信号を記録する。図8は、デジタルテレビジョン(DTV)のための典型的なPVRシステム800を例示している。PVRシステム800は、例えば、CPU120、GPU140、ディスプレイ150、メモリ130、及びブリッジ110のような少なくとも一つのブリッジを有するメディアセンターパーソナルコンピュータであってもよい。ビデオキャプチャ(VC)モジュール805が、PVRシステム800に含まれており、例えば、ブリッジ110に含まれていてもよい。VCモジュール805は、記憶のためブロードキャスト信号を取り込む。HDTV受信器802が、ブロードキャスト信号を受け取るためPVRシステム800に結合されていてもよい。HDTV受信器802は、例えば、復調及び復号を実行して、復調データパケットのトランスポートストリームの形態でビデオ信号810を生成してもよい。ビデオ信号810は、その実装形態に依存して、ブリッジ110により直接的に受け取られてもよく、又は、別のコンポーネントからブリッジ110へ結合されてもよい。

【0038】

[0045]将来のテレビジョン受信器は、ブロードキャストフラグを認識する必要があり、そのブロードキャストフラグの検出に応答してデジタルコンテンツ保護スキームを実施し、取り入れたビデオがインターネット又はその他のマス方法を介して分配されないようにすることが提案されている。その結果、受信されたブロードキャストHDTV信号のコピーは、保護されたフォーマットにて維持され、これによって、エンドユーザがビデオコンテンツの保護されていないコピーを分配することが困難なものとされる。ブロードキャストフラグを、例えば、プログラム及びシステム情報プロトコル(PSIP)に従ってアドバンスドテレビジョンシステムコミッティ(ATSC)のヘッダーに含めてもよい。本発明の一実施の形態では、PVRシステム800は、ブロードキャストフラグがビデオ信号810に存在するか否かを検出する。ブロードキャストフラグが存在する場合には、デジタルコンテンツ保護をサポートするのに必要とされる暗号化/復号サービスがセキュリティエンジン112へ移動される。PVRアプリケーションの場合には、多くのプロセスは、データのソースがブロードキャスト信号であること、及び、ブロードキャストフラグの存在が監視されることを除けば、図7に記載したプロセスと同一である。例えば、PVRシステム800は、メモリ130に記憶して後に再生するために受信したビデオ信号のコピーを暗号化し、その後の再生に必要な復号を行ってもよい。

【0039】

[0046]本発明の典型的なアプリケーションについて説明してきたが、より一般的には、本発明を利用して、種々の異なるタイプのデバイス及びメモリのための暗号化、復号又はトランスコーディングサービスを提供し得る。暗号化、復号又はトランスコーディングサービスは、メモリスティック又はネットワーク記憶デバイスに対して提供することができる。例えば、ネットワーク記憶デバイスでは、セキュリティエンジン112を使用して、記憶用のデータを暗号化してもよい。ネットワーク記憶装置の一実施の形態では、セキュリティエンジン112は、暗号化フォーマットが第1の暗号化フォーマット(例えば、ネットワークを通して送信されるデータのための暗号化フォーマット)から第2の暗号化フォーマット(例えば、データ記憶のための暗号化フォーマット)へ変換されるようなトランスコーディングを実行する。

【0040】

[0047]一実施の形態では、セキュリティエンジン112は、ブリッジ110とは別の分離したデバイスに形成される。例えば、セキュリティエンジン112が、ブリッジ110とは異なるチップに形成されてもよい。この実施形態では、PCI-Eのような入力/出力インターフェイスを使用して、セキュリティエンジン112をチップセットにおける他のコンポーネントへ結合してもよい。この代替の実装形態の一つの利点は、セキュリティエンジン112の機能的な利点を異なる物理的パーティショニングを用いてチップセットにて達成できることである。一例として、基本的なチップセットは、セキュリティエンジン112なしに設計できる。高いセキュリティを必要とするマーケットの場合には、セキュリティエンジン112を含むデバイスを、I/Oインターフェイスを介して基本チップセット構造に結合して、高いセキュリティを有したチップセットとすることができる。

【0041】

[0048]前述したように、コンテクスト状態は、複数のコンテクストの使用をサポートするためメモリに記憶される。仮想マシンの実装形態(例えば、ロングホーン)では、パーティションによって、前述したように、ソフトウェアの攻撃に対して高度の保護が提供される。しかしながら、Linux又はWinXpを実行するシステムのように、コンテナの分離を提供するパーティションを有していないシステムにおいては、セキュリティを増すためにメモリに記憶されたコンテクスト情報の付加的保護を提供することが望ましい。一実施の形態では、メモリに記憶されるコンテクスト状態を暗号化/復号するためのキーがセキュリティエンジン112のハードウェアに記憶される。これによって、コンテクスト状態が暗号テキストとしてメモリに記憶させられ、コンテクスト状態情報をクリアテキストとしてメモリに記憶するのに比べて、セキュリティが改善される。

【0042】

[0049]本発明の一実施の形態は、種々のコンピュータ実装のオペレーションを実行するウためのコンピュータコードを有するコンピュータ読取り可能な媒体を備えたコンピュータ記憶製品に関する。媒体及びコンピュータコードは、本発明の目的のために特別に設計及び構成されたものであってもよいし、又は、コンピュータソフトウェア技術の分野において当業者に良く知られて利用可能となっている種類のものであってもよい。コンピュータ読取り可能な媒体の例として、これに限定されないが、ハードディスク、フロッピーディスク、及び磁気テープのような磁気媒体、CD-ROM及びホログラフィックデバイスのような光学的媒体、光ディスクのような磁気-光媒体、並びに、特定用途向け集積回路(ASIC)、プログラマブル論理デバイス(PLD)、ROM及びRAMデバイスのようにプログラムコードを記憶し実行するように特別に構成されたハードウェアデバイスがある。コンピュータコードの例としては、コンパイラによって生成されるようなマシンコード、及びインタープリタを使用してコンピュータにより実行されるようなより高レベルのコードを含むファイルがある。例えば、本発明の一実施の形態は、Java、C++、又は他のオブジェクト指向プログラミング言語及び開発ツールを使用して実施できる。本発明の別の実施の形態は、適宜、マシン実行可能なソフトウェア命令の代わりに、又はマシン実行可能なソフトウェア命令と組み合わせて、ハード・ワイヤード回路でも実施し得る。

[0050]前述の記載では、本発明を完全に理解させるために特定の用語を使用した。しかしながら、特定の細部が本発明の実施に必要でないことが当業者に明らかであろう。従って、前述の本発明の特定の実施形態についての記載は、単なる例示に過ぎない。それらの記載はそれに尽きるものでなく、又、本発明を、それら説明した細部の構成に限定しようとするものではなく、前述の記載に鑑みれば、多くの変形例が可能であることは明らかであろう。前述の実施形態は、本発明の原理及びその実際的な応用について最も良く説明するために選択されたものであり、従って、当業者であれば、本発明及び種々な実施形態について意図する特定の使用に適合するような種々な変形を加えて最も良く利用することができるであろう。特許請求の範囲及びその等効物は、本発明の範囲を定めることを意図したものである。

【図面の簡単な説明】

【0043】

【図1】本発明の一実施の形態によるブリッジに配置されたセキュリティエンジンを有するデジタルコンテンツ保護システムのブロック図である。

【図2】本発明の一実施形の態によるセキュリティエンジンのブロック図である。

【図3】本発明の一実施の形態によるノースブリッジの実装形態のブロック図である。

【図4】本発明の一実施の形態によるサウスブリッジの実装形態のブロック図である。

【図5】本発明の一実施の形態によるPCIコンフィギュレーションスペースを示す図である。

【図6】本発明の一実施の形態によるコンテクストデータ構造を示す図である。

【図7】本発明の一実施の形態によるデジタルコンテンツの保護のためのオペレーションの典型的シーケンスを示す図である。

【図8】本発明の一実施の形態によるビデオデータのためのデジタルコンテンツ保護システムのブロック図である。

【符号の説明】

【0044】

110…ブリッジ、112…セキュリティエンジン、114…キー、116…コンテクストポインター、118…コンテクストデータ構造、130…メモリ、147…復号、150…ディスプレイ、160…コンテンツ、185…グラフィックドライバー、190…ビデオプレーヤ、195…暗号化/復号、210…レジスタスペース、220…マイクロコントローラ、230…ROMコードストア

【特許請求の範囲】

【請求項1】

中央処理装置(CPU)をシステム内の他のコンポーネントへ接続するためのブリッジであって、

セキュリティエンジンを備え、

前記ブリッジは、前記ブリッジを介して行われるデータアクセスオペレーションに暗号化サービスを提供するよう動作することによって、暗号化サービスを前記CPUから前記ブリッジへ移動する、ブリッジ。

【請求項2】

前記暗号化サービスは、暗号化、復号及びトランスコーディングのうちの少なくとも一つを含む、請求項1に記載のブリッジ。

【請求項3】

前記ブリッジは、暗号テキスト入力を受け取り、前記暗号テキスト入力を復号し、クリアテキスト出力を宛先へ書き込むようになっている、請求項1に記載のブリッジ。

【請求項4】

前記ブリッジは、クリアテキスト入力を受け取り、前記クリアテキスト入力を暗号化し、暗号テキスト出力を宛先へ書き込むようになっている、請求項1に記載のブリッジ。

【請求項5】

前記ブリッジは、第1の暗号フォーマットで暗号テキスト入力を受け取り、トランスコーディングを実行して、第2の暗号フォーマットで暗号テキスト出力を宛先へ書き込むようになっている、請求項1に記載のブリッジ。

【請求項6】

前記ブリッジは、前記CPUから受け取ったクリアテキスト入力を暗号テキストとして暗号化し、該暗号テキストをメモリへ書き込むようになっている、請求項1に記載のブリッジ。

【請求項7】

前記ブリッジは、前記暗号テキストを、前記ブリッジに結合されたグラフィック処理装置(GPU)へ提供するようになっている、請求項6に記載のブリッジ。

【請求項8】

前記ブリッジは、前記CPUから受け取ったコマンドストリームを暗号化し、暗号化されたコマンドストリームを前記ブリッジに結合されたグラフィック処理装置へ提供するようになっている、請求項1に記載のブリッジ。

【請求項9】

改善されたデジタルコンテンツの保護を有するデジタルコンテンツシステムにおいて、

デジタルコンテンツに対応するクリアテキストデジタルデータを生成するようになっている中央処理装置(CPU)と、

前記CPUに結合され、デジタルコンテンツに対応する前記クリアテキストデータを受け取るブリッジと、

前記ブリッジに結合されたメモリと、

前記ブリッジに結合されたグラフィック処理装置(GPU)と、

前記ブリッジ内に設けられたセキュリティエンジンであって、前記デジタルコンテンツを保護するために、前記クリアテキストデジタルデータが該セキュリティエンジンによって暗号化されて、前記ブリッジを介して暗号テキストとして非安全なデータ経路を通して転送されるように暗号化サービスを提供する、該セキュリティエンジンと、

を備えるデジタルコンテンツシステム。

【請求項10】

前記ブリッジは、ビデオ信号を受け取り、該ビデオ信号のビデオキャプチャ用のコンテンツ保護を提供するよう暗号化サービスを実行するようになっている、請求項1に記載のブリッジ。

【請求項1】

中央処理装置(CPU)をシステム内の他のコンポーネントへ接続するためのブリッジであって、

セキュリティエンジンを備え、

前記ブリッジは、前記ブリッジを介して行われるデータアクセスオペレーションに暗号化サービスを提供するよう動作することによって、暗号化サービスを前記CPUから前記ブリッジへ移動する、ブリッジ。

【請求項2】

前記暗号化サービスは、暗号化、復号及びトランスコーディングのうちの少なくとも一つを含む、請求項1に記載のブリッジ。

【請求項3】

前記ブリッジは、暗号テキスト入力を受け取り、前記暗号テキスト入力を復号し、クリアテキスト出力を宛先へ書き込むようになっている、請求項1に記載のブリッジ。

【請求項4】

前記ブリッジは、クリアテキスト入力を受け取り、前記クリアテキスト入力を暗号化し、暗号テキスト出力を宛先へ書き込むようになっている、請求項1に記載のブリッジ。

【請求項5】

前記ブリッジは、第1の暗号フォーマットで暗号テキスト入力を受け取り、トランスコーディングを実行して、第2の暗号フォーマットで暗号テキスト出力を宛先へ書き込むようになっている、請求項1に記載のブリッジ。

【請求項6】

前記ブリッジは、前記CPUから受け取ったクリアテキスト入力を暗号テキストとして暗号化し、該暗号テキストをメモリへ書き込むようになっている、請求項1に記載のブリッジ。

【請求項7】

前記ブリッジは、前記暗号テキストを、前記ブリッジに結合されたグラフィック処理装置(GPU)へ提供するようになっている、請求項6に記載のブリッジ。

【請求項8】

前記ブリッジは、前記CPUから受け取ったコマンドストリームを暗号化し、暗号化されたコマンドストリームを前記ブリッジに結合されたグラフィック処理装置へ提供するようになっている、請求項1に記載のブリッジ。

【請求項9】

改善されたデジタルコンテンツの保護を有するデジタルコンテンツシステムにおいて、

デジタルコンテンツに対応するクリアテキストデジタルデータを生成するようになっている中央処理装置(CPU)と、

前記CPUに結合され、デジタルコンテンツに対応する前記クリアテキストデータを受け取るブリッジと、

前記ブリッジに結合されたメモリと、

前記ブリッジに結合されたグラフィック処理装置(GPU)と、

前記ブリッジ内に設けられたセキュリティエンジンであって、前記デジタルコンテンツを保護するために、前記クリアテキストデジタルデータが該セキュリティエンジンによって暗号化されて、前記ブリッジを介して暗号テキストとして非安全なデータ経路を通して転送されるように暗号化サービスを提供する、該セキュリティエンジンと、

を備えるデジタルコンテンツシステム。

【請求項10】

前記ブリッジは、ビデオ信号を受け取り、該ビデオ信号のビデオキャプチャ用のコンテンツ保護を提供するよう暗号化サービスを実行するようになっている、請求項1に記載のブリッジ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2007−215159(P2007−215159A)

【公開日】平成19年8月23日(2007.8.23)

【国際特許分類】

【外国語出願】

【出願番号】特願2006−337403(P2006−337403)

【出願日】平成18年12月14日(2006.12.14)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.Linux

2.フロッピー

3.JAVA

4.ペンティアム

【出願人】(501261300)エヌヴィディア コーポレイション (166)

【Fターム(参考)】

【公開日】平成19年8月23日(2007.8.23)

【国際特許分類】

【出願番号】特願2006−337403(P2006−337403)

【出願日】平成18年12月14日(2006.12.14)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.Linux

2.フロッピー

3.JAVA

4.ペンティアム

【出願人】(501261300)エヌヴィディア コーポレイション (166)

【Fターム(参考)】

[ Back to top ]