チップ型電子部品

【課題】はんだ喰われを防止しつつ、応力緩和が可能な端子電極を有するチップ型電子部品を提供すること。

【解決手段】チップ型電子部品Cは、セラミック素体Lと、セラミック素体Lの内部に配置され、かつ、セラミック素体Lの表面に一部が露出した内部電極20と、セラミック素体の表面に配置された端子電極10とを含み、端子電極10は、第1の導電性材料12a、12bを含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層12と、第1の電極層12よりもセラミック素体の表面から離れた位置に配置される導電性めっき層14と、はんだ成分を含む第2の導電性材料16aと樹脂16cとを含むとともに、導電性めっき層14よりもセラミック素体の表面から離れた位置に配置される第2の電極層16と、を含む。

【解決手段】チップ型電子部品Cは、セラミック素体Lと、セラミック素体Lの内部に配置され、かつ、セラミック素体Lの表面に一部が露出した内部電極20と、セラミック素体の表面に配置された端子電極10とを含み、端子電極10は、第1の導電性材料12a、12bを含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層12と、第1の電極層12よりもセラミック素体の表面から離れた位置に配置される導電性めっき層14と、はんだ成分を含む第2の導電性材料16aと樹脂16cとを含むとともに、導電性めっき層14よりもセラミック素体の表面から離れた位置に配置される第2の電極層16と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、チップ型電子部品、特にセラミック材料を用いたチップ型電子部品に関する。

【背景技術】

【0002】

セラミック素体の表面に端子電極を有するチップ型電子部品が知られている。近年は、導電性材料と樹脂とを含む導電性樹脂をチップ型電子部品の端子電極に用いたものが知られている(特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平03−266404号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記特許文献1に記載のチップ型電子部品においては、導電性樹脂層の上にはんだ層が形成されることから、はんだ層のはんだ成分が導電性樹脂層に拡散し、導電性樹脂層の金属成分を溶融したり、はんだ層自体が消失したりする不具合、いわゆるはんだ喰われが生じることがあった。

【0005】

本発明は、上記課題を解決するためになされたものであり、はんだ喰われを抑制できる端子電極を有するチップ型電子部品を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明のチップ型電子部品は、セラミック素体と、セラミック素体の内部に配置され、かつ、セラミック素体の表面に一部が露出した内部電極と、セラミック素体の表面に配置された端子電極とを含み、端子電極は、第1の導電性材料を含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層と、第1の電極層よりもセラミック素体の表面から離れた位置に配置される導電性めっき層と、はんだ成分を含む第2の導電性材料と樹脂とを含むとともに、導電性めっき層よりもセラミック素体の表面から離れた位置に配置される第2の電極層と、を含むことを特徴としている。

【0007】

上述したチップ型電子部品によると、第1の電極層と、はんだ成分を含む第2の電極層との間に、緻密な導電性めっき層が配置されるので、第2の電極層のはんだ成分が第1の電極層へ拡散することを抑制できる。従って、第1の電極層の導電性材料がはんだによって溶融することを防止できるうえ、はんだ成分を含む第2の電極層が消失するのを抑制することができる

【0008】

本発明において、導電性めっき層は第1の電極層を覆うとともに、第2の電極層は導電性めっき層を覆い、かつ、導電性めっき層は第1の電極層と第2の電極層との両方に接触していることが好ましい。

【0009】

上述したチップ型電子部品によると、導電性めっき層は第1の電極層を覆うことから、導電性めっき層よりもセラミック素体の表面から離れた位置に配置される第2の電極層におけるはんだ成分が、第1の電極層に拡散することをより確実に抑制できる。また、また、第2の電極層は導電性めっき層を覆い、なおかつ、緻密な導電性めっき層が第1の電極層と第2の電極層との両方に接触していることから、第1の電極層と導電性めっき層、および、導電性めっき層と第2の電極層との接触抵抗を低減させることができる。

【0010】

本発明において、第1の電極層は第1の導電性材料と樹脂とを含有するのが好ましい。

【0011】

上述したチップ型電子部品によると、第1の電極層、および、第2の電極層いずれもが導電性樹脂電極層となるので、確実に応力緩和することができる。また、第1の電極層が導電性樹脂電極層であることから、第1の電極層の表面に導電性めっき層を形成する際、セラミック素体表面に露出した内部電極にめっき液が浸入することを抑制できるので、絶縁抵抗などの信頼性を向上させることができる。

【0012】

本発明において、第1の導電性材料は、第1の導電性粒子と、第1の導電性粒子よりも粒径の大きい第2の導電性粒子とを有することが好ましい。

【0013】

上述したチップ型電子部品によると、低融点となる粒径の小さい第1の導電性粒子が、セラミック素体表面に露出した内部電極、および、高融点となる粒径の大きい第2の導電性粒子と結合するので、内部電極と第1の電極層との接続性や接触抵抗低減を確実なものとできる。また、粒径の大きい第2の導電性粒子によって、セラミック素体の表面と第1の電極層との固着強度を向上させることができたり、接触抵抗を低減させることができる。

【0014】

本発明において、セラミック素体は、誘電体層と、前記内部電極とが積層されており、第1の導電性粒子の粒径が、内部電極の厚みよりも小さいことが好ましい。

【0015】

上述したチップ型電子部品によると、内部電極の厚みに対して、複数の第1の導電性粒子がセラミック素体の表面に露出した内部電極と結合するので、より確実に接続不良を抑制できる。

【0016】

本発明において、セラミック素体は、誘電体層と、内部電極とが積層されており、第2の導電性粒子の粒径が、内部電極の厚みよりも大きいことが好ましい。

【0017】

上述したチップ型電子部品によると、内部電極の厚みよりも大きい第2の導電性粒子を有することから、接触抵抗の増加を低減することができる。また、セラミック素体の表面と第1の電極層との固着強度を確実に向上させることができる。

【0018】

本発明において、第1の導電性粒子の粒径が0.5μm以下であることが好ましく、第2の導電性粒子の粒径が1μm以上10μm以下であることが好ましい。

【0019】

上述したチップ型電子部品によると、第1の導電性粒子の粒径を0.5μm以下とすることで、セラミック素体表面に露出した内部電極、および、第2の導電性粒子との結合をいっそう確実なものとすることができる。また、第1の導電性粒子の粒径は、0.1μm以下とすることがいっそう好ましい。このようにすることで、セラミック素体表面に露出した内部電極、および、第2の導電性粒子との結合をさらに確実なものとすることができる。また、第2の導電性粒子の粒径を1μm以上10μm以下とすることで、セラミック素体の表面と第1の電極層との固着強度を向上させることができたり、接触抵抗の低減を確実なものとすることができる。

【0020】

本発明において、第1の導電性材料は、CuとNiとのうち少なくとも一方を含有していることが好ましい。

【0021】

上述したチップ型電子部品によると、セラミック素体の表面に露出した内部電極と、第1の電極層との接続性をいっそう確実なものとすることができる。

【0022】

本発明において、第2の電極層は最外層であり、はんだ成分は、少なくともSnを含んでいることが好ましい。

【0023】

上述したチップ型電子部品によると、第2の電極層と回路基板とを確実にはんだで実装することができる。

【0024】

本発明において、第2の導電性材料は、NiとCuとの少なくとも一方をさらに含むことが好ましい。

【0025】

上述したチップ型電子部品によると、はんだ実装時においてはんだ成分が溶融しても、確実に第2の電極層の保形性を維持することができる。

【0026】

本発明において、第2の導電性材料は、少なくとも一部がSnによって被覆されたNi粒子と少なくとも一部がSnによって被覆されたCu粒子との少なくとも一方を含むことが好ましい。

【0027】

上述したチップ型電子部品によると、はんだ実装時においてはんだ成分が溶融しても、確実に第2の電極層の保形性を維持することができる。

【0028】

本発明において、導電性めっき層の導電性材料は、Niを含有していることが好ましい。

【0029】

上述したチップ型電子部品によると、Niははんだに比べて高融点であるので、確実にはんだ成分が第1の電極層に拡散することを抑制できる。

【0030】

本発明において、第1の電極層および第2の電極層は、ガラスフリットを含有しないことが好ましい。

【0031】

上述したチップ型電子部品によると、端子電極の導電性をいっそう向上させることができる。

【発明の効果】

【0032】

本発明によると、はんだ喰われを抑制できる端子電極を有するチップ型電子部品を提供できる。

【図面の簡単な説明】

【0033】

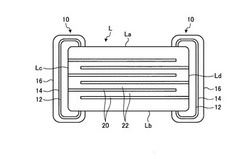

【図1】図1は、積層コンデンサを示す概略斜視図である。

【図2】図2は、図1におけるII−II線に沿った断面図である。

【図3】図3は、実施形態における、第1の電極層の拡大模式図である。

【図4】図4は、実施形態における、第2の電極層の拡大模式図である。

【図5】図5は、第2の電極層の第1変形例を示す拡大模式図である。

【図6】図6は、第2の電極層の第1変形例を示す拡大模式図である。

【図7】図7は、第2の電極層の第2変形例を示す拡大模式図である。

【発明を実施するための形態】

【0034】

本発明を実施するための形態(実施形態)につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成要素には、当業者が容易に想定できるもの、実質的に同一のもの、均等の範囲のものが含まれる。さらに、以下に記載した構成要素は適宜組み合わせることが可能である。また、本発明の要旨を逸脱しない範囲で構成の種々の省略、置換または変更を行うことができる。

【0035】

[実施形態]

まず、本実施形態に係るチップ型電子部品としての積層コンデンサCの構成を説明する。図1は本実施形態に係る積層コンデンサの概観斜視図であり、図2は、図1におけるII−II線に沿った断面図である。図1、図2に示されるように、本実施形態に係る積層コンデンサCは、セラミック素体Lと、セラミック素体Lの外表面に配置される2つの端子電極10とを備えている。

【0036】

セラミック素体Lは、略直方体形状を呈しており、その外表面として、対向する第1および第2の主面La、Lbと、対向する第1および第2の端面Lc、Ldと、対向する第1および第2の側面Le、Lfとを有する。第1および第2の端面Lc、Ldは、第1および第2の主面間を連結するように第1および第2の主面La、Lbの短辺方向に伸びている。第1および第2の側面Le、Lfは、第1および第2の主面La、Lb間を連結するように第1および第2の主面La、Lbの長辺方向に伸びている。

【0037】

セラミック素体Lでは、内部電極20が誘電体層22を介して積層されている。各誘電体層22は、例えば誘電体セラミックを含むセラミックグリーンシートの焼結体から構成される。実際の積層コンデンサCでは、誘電体層22の間の境界が視認できない程度に一体化されている。

【0038】

セラミック素体L内に配置された内部電極20は、セラミック素体Lにおける第1の端面Lcと第2の端面Ldとに交互に引き出されるように積層されている。積層方向における隣接する内部電極20、20間の距離は、およそ誘電体層22の厚みに相当する。内部電極20は、積層型の電気素子の内部電極として通常用いられる導電性材料から構成される。本実施形態では、内部電極20は、卑金属であるNiを主成分として含んでいる。なお、主成分とは、複数の成分を備える材料において、最も含有率(重量%)が高い成分をいう(以下同様)。

【0039】

なお、積層方向における誘電体層22の厚みは、例えば0.5μm〜8.0μm程度であり、積層方向における内部電極20の厚みは、例えば0.5μm〜5.0μm程度である。

【0040】

端子電極10は、セラミック素体Lの外表面上に配置されている。端子電極10は、第1の電極層12と、導電性めっき層14と、第2の電極層16とを含んでいる。

【0041】

第1の電極層12は、ガラスフリットを含有する焼付電極層、または、導電性樹脂電極層いずれでもよいが、本実施形態では、導電性樹脂電極層を適用する場合について、説明する。

【0042】

第1の電極層12は、第1の導電性粒子12aと第2の導電性粒子12bとを含む第1の導電性材料と、熱硬化された樹脂12cとを含んだ層である。このようにすることで、第1の電極層12は導電性を有する。第1の電極層12は、セラミック素体Lにおける第1および第2の端面Lc、Ldから、第1および第2の主面La、Lb並びに第1および第2の側面Le、Lfに回り込むように形成されている。そして、第1の電極層12は、第1および第2の端面Lc、Ldに露出した内部電極20を覆うように、内部電極20と物理的かつ電気的に接続されている。第1の導電性樹脂電極層の厚みは、例えば、20μm〜100μm程度である。

【0043】

本実施形態では、第1の電極層12における第1の導電性粒子12aおよび第2の導電性粒子12bをCuとしているが、卑金属であるCu、または、Niを少なくとも主成分として含んでいることが好ましい。第1および第2の導電性粒子12a、12bをCu、または、Niを主成分とすることで、内部電極20の主成分であるNiとの電気的接続性や接合強度を確実なものとすることができる。

【0044】

また、本実施形態では、第1の電極層12は、第1の導電性粒子12aと、第1の導電性粒子よりも粒径の大きな第2の導電性粒子12bを含んでいる。第1の導電性粒子12aの粒径は、好ましくは0.5μm以下、いっそう好ましくは0.1μm以下である。また、第2の導電性粒子12bの粒径は、好ましくは1μm以上10μm以下である。

【0045】

第1の導電性粒子12aの粒径は、第2の導電性粒子12bの粒径よりも小さく、0.5μm以下、いっそう好ましくは0.1μm以下が好ましい。このようにすることで、第1の導電性粒子12aを介して、セラミック素体表面に露出した内部電極20と、第2の導電性粒子12bとを連結させることができることから、内部電極20と第1の電極層12との電気的な接続を確実なものとすることができる。また、第2の導電性粒子12bの粒径を第1の導電性粒子12aの粒径よりも大きく、1μm以上10μm以下とすることが好ましい。このようにすることで、第1の電極層16の接触抵抗を低減させることや、セラミック素体Lおよび導電性めっき層14との密着性を向上できることや、第1の電極層12を熱硬化する際の収縮率が小さくなることにより応力クラックを低減することができる。

【0046】

なお、第1の導電性粒子12aの粒径、および、第2の導電性粒子12bの粒径は、例えば、第1の電極層12の断面を切断し、SEM(Scanning Electron Microscope:走査型電子顕微鏡)像等から平均粒径を導出すればよい。

【0047】

また、第1の導電性粒子12aの粒径は、内部電極間の厚みよりも小さいほうが好ましく、第2の導電性粒子12bの粒径は、内部電極間の厚みよりも大きいほうが好ましい。

【0048】

第1の導電性粒子12aの粒径を内部電極の厚みよりも小さくすることで、複数の第1の導電性粒子12aがセラミック素体の端面Lc、Ldに露出した内部電極20と結合するので、内部電極20との接続をいっそう確実なものとすることができる。また、第2の導電性粒子12bの粒径を内部電極の厚みよりも大きくすることで、第1の電極層16と導電性めっき層14との接触抵抗低減、セラミック素体Lc、Ldや導電性めっき層14との密着性向上、第1の電極層12が熱硬化する際の収縮率が小さくなることによる応力クラック低減などの効果が得られる。

【0049】

本実施形態では、第1の導電性材料は、第1の導電性粒子12aと第2の導電性粒子12bとを含んでいるが、両方を含んでいなくてもよい。すなわち、第1の導電性材料は、第1の導電性粒子12aと第2の導電性粒子12bとの少なくとも一方を含んでいればよい。なお、第1の導電性材料が複数種類の粒子(本実施形態では、第1の導電性粒子12aおよび第2の導電性粒子12b)を含むようにすることで、端子電極10に要求される性能を実現しやすくなるので好ましい。

【0050】

第1の電極層12は、第1の導電性材料と樹脂としての熱硬化型樹脂とを含んだペースト状の第1の樹脂層形成用組成物を用いて、浸漬法、または、印刷法などで形成し、その後、乾燥および熱硬化を行えばよい。乾燥温度や熱硬化温度は、使用する硬化性樹脂に応じて適宜調整される。

【0051】

本実施形態では、第1の樹脂層形成用組成物が含む熱硬化性樹脂としてエポキシ系の樹脂を使用しているが、熱硬化性樹脂の種類は特に制限されるものではなく、エポキシ樹脂以外にも、例えば、フェノール樹脂、アクリル樹脂、シリコーン樹脂、ポリイミド樹脂等を用いることができる。なお、第1の樹脂層形成用組成物中の第1および第2の導電性粒子12a、12bの含有量は、樹脂層形成用組成物の固形分全量を基準として30体積%〜60体積%程度とすることができる。

【0052】

樹脂層形成用組成物は、必要に応じて溶媒をさらに含むものである。溶媒としては、上記熱硬化性樹脂を溶解または分解可能なものであれば公知の溶媒を特に制限なく使用することができる。溶媒として具体的には、例えば、メチルカルビトール、ブチルカルビトール、ブチルカルビトールアセテート、セロソルブ、ブチルセロソルブ、ブチルセロソルブアセテート、テルピネオール等が挙げられる。

【0053】

また、第1の電極層12における樹脂層形成用組成物には、ガラスフリットを含有していない。これにより、第1の電極層12における導電性を高めることができる。

【0054】

導電性めっき層14は、第1の電極層12よりもセラミック素体Lの表面から離れた位置に配置される。本実施形態においては、導電性めっき層14は、第1の電極層12の表面に、第1の電極層12を覆うように配置されており、導電性めっき層14と第1の電極層12とが、物理的かつ電気的に接続されている。導電性めっき層14は、通常の電気めっき法により形成された金属電極層であり、本実施形態ではNiを主成分としており、厚みは1μm〜3μm程度が好ましい。

【0055】

導電性めっき層14は、第1の電極層12よりもセラミック素体Lの表面から離れた位置に配置されていればよい。このため、第1の電極層12と導電性めっき層14との間には、導電性を有する層が設けられていてもよい。このようにすることで、チップ型電子部品(本実施形態ではセラミックコンデンサC)の仕様に合わせた適切な性能を端子電極10に持たせることもできる。

【0056】

第2の電極層16は、導電性めっき層16よりもセラミック素体Lの表面から離れた位置に配置される。本実施形態においては、第2の電極層16は、導電性めっき層14の表面に、導電性めっき層14を覆うように配置されており、第2の電極層16と導電性めっき層14とが、物理的かつ電気的に接続されている。また、第2の電極層16は、端子電極10の最外層となるように配置されている。上述したように、導電性めっき層16は、第1の電気層12を覆い、第2の電極層12は導電性めっき層16を覆う。このような構造により、導電性めっき層16は、第1の電極層12と第2の電極層16との両方に接触している。本実施形態において、第2の電極層16は、端子電極10の最外層であるが、導電性めっき層16よりもセラミック素体Lの表面から離れた位置に配置されていればよい。従って、第2の電極層16の表面に、さらに電極層を設けてもよい。

【0057】

第2の電極層16は、はんだ粒子16aを含む第2の導電性材料と、熱硬化された樹脂16cとを含んだ層である。このようにすることで、第2の電極層16は導電性を有する。第2の電極層16の厚みは、例えば20μm〜100μm程度である。

【0058】

なお、本実施形態では、第2の導電性材料としてはんだ粒子16aを用いたが、第2の導電性材料は、はんだ成分を含有していれば形状は必ずしも粒状である必要はない。例えば、第2の導電性材料は、膜状、扁平状、針状のものであってもよい。

【0059】

第2の電極層16は、第2の導電性材料と樹脂としての熱硬化型樹脂とを含んだペースト状の第2の樹脂層形成用組成物を用いて、浸漬法、または、印刷法などで形成し、その後、乾燥および熱硬化を行えばよい。乾燥温度や熱硬化温度は、使用する熱硬化性樹脂に応じて適宜調整される。また、乾燥温度や熱硬化温度は、はんだ粒子16aの融点以下とすることが好ましい。

【0060】

本実施形態では、第2の導電性材料となるはんだ粒子16aとして、Snが用いられている。なお、第2の導電性材料は、Snに加えて、Ni、Cu、Ag等その他の成分をさらに含んでいてもよい。この第2の導電性材料がSn以外の成分をさらに含む場合、特にNi、Cuのうち少なくとも一方が好ましい。このようにすれば、第2の電極層16を直接に回路基板にはんだ実装した場合であっても、はんだに比べて融点の高いCu、Niによって第2の電極層16の保形性を確実に維持できる。また、導電性めっき層14のNi成分と、第2の電極層16のCu、Niによって、導電性めっき層14と第2の電極層16との接合強度を向上させて、両者の接合をより確実なものとすることができる。

【0061】

また、第2の導電性材料が含むはんだ成分は、Snに限定されるものではなく、例えば、Snを含まないはんだ成分であってもよい。一般に、回路基板に積層コンデンサC等の電子部品を実装する場合には、Snを含むはんだが用いられる。このため、第2の導電性材料が含むはんだ成分が少なくともSnを含むようにすると、第2の電極層16に対するはんだの濡れ性が向上するので、積層コンデンサCを回路基板へ確実に実装することができる。

【0062】

第2の樹脂層形成用組成物が含む熱硬化性樹脂としては特に制限されないが、例えば、フェノール樹脂、アクリル樹脂、シリコーン樹脂、エポキシ樹脂、ポリイミド樹脂等といった、上述した第1の樹脂層形成用組成物が含む熱硬化性樹脂と同様の材料を用いることができる。なお、第2の樹脂層形成用組成物と第1の樹脂層形成用組成物とで、使用する熱硬化性樹脂を異ならせてもよい。

【0063】

上記第2の樹脂層形成用組成物中のはんだ粒子16aの含有量は、第2の樹脂層形成用組成物の固形分全量を基準として30体積%〜60体積%程度とすることができる。

【0064】

第2の樹脂層形成用組成物は、上述した第1の樹脂層形成用組成物と同様に、必要に応じて溶媒をさらに含むものである。溶媒としては、上記熱硬化性樹脂を溶解または分解可能なものであれば公知の溶媒を特に制限なく使用することができる。溶媒として具体的には、例えば、メチルカルビトール、ブチルカルビトール、ブチルカルビトールアセテート、セロソルブ、ブチルセロソルブ、ブチルセロソルブアセテート、テルピネオール等が挙げられる。なお、第2の樹脂層形成用組成物と第1の樹脂層形成用組成物とで、使用する溶媒を異ならせてもよい。

【0065】

また、第2の電極層16における樹脂層形成用組成物には、ガラスフリットを含有していない。これにより、第2の電極層16における導電性をいっそう高めることができる。

【0066】

以上のように、本実施形態に係る積層コンデンサCでは、第1の電極層12と、はんだ粒子を含んだ第2の電極層16との間に、緻密な導電性めっき層14が配置されるので、第2の電極層16のはんだ成分が第1の電極層12へ拡散することを抑制できる。従って、第1の電極層12の導電性粒子12a、12bがはんだによって溶融することを抑制できるうえ、はんだ粒子16aを含む第2の電極層16の保形性が維持できるとともに、第2の電極層16が消失する、いわゆるはんだ喰われを抑制することができる。

【0067】

また、本実施形態の積層コンデンサCでは、第1の電極層12、および、第2の電極層16いずれもが導電性樹脂電極層となるので、確実に応力を緩和することができる。すなわち、導電性樹脂電極層からなる第1の電極層12が、セラミック素体Lの表面に形成されるので、第1の電極層12が有する樹脂が、誘電体層22の電歪振動による内部応力を緩和したり、積層コンデンサCによる振動音の発生を抑制することに有効に作用する。また、導電性樹脂電極層からなる第2の電極層16が、端子電極10の最外層に形成されるので、第2の電極層16が有する樹脂が、積層コンデンサCを回路基板に実装した際の外部応力の緩和に有効に作用する。そして、応力による積層コンデンサCのクラック発生を抑制することができる。

【0068】

また、第1の電極層12が導電性樹脂電極層であることから、ガラスフリット入りの焼付電極層の場合に必要な高温焼付処理が不要となり、熱応力や内部応力によって素体Lにクラックが入ることを確実に防止できる。

【0069】

さらに、第1の電極層12を有することで、第1の電極層12の表面に導電性めっき層14を形成する際、セラミック素体表面に露出した内部電極20にめっき液が浸入することを抑制できることとなり、絶縁抵抗などの信頼性を向上させることができる。

【0070】

また、本実施形態においては、最外層となる第2の電極層16の導電性材料がはんだを主成分としているので、第2の電極層16の表面にめっき層を形成しなくても回路基板に実装することができる。また、導電性樹脂層である第2の電極層16を、回路基板の実装部に実装できるので、回路基板からの外部応力や熱応力を直接的に第2の電極層16で緩和させることが可能となる。

【0071】

なお、本実施形態においては、第1の電極層12として導電性樹脂電極層を用いる場合を説明したが、第1の電極層12は、ガラスフリット入りの焼付電極層であってもよい。第1の電極層12を焼付電極層とした場合には、セラミック素体Lと第1の電極層12との固着強度いっそう向上させることができ、また、第1の電極層12と導電性めっき層14との接触抵抗をいっそう低減させることができる。

【0072】

[本実施形態に係るチップ型電子部品の製造方法]

次に、本実施形態に係るチップ型電子部品としての積層コンデンサCの製造方法を簡単に説明する。積層コンデンサCを製造するにあたり、表面に内部電極20の一部が露出した引出部を有するセラミック素体Lを準備する。引出部は、セラミック素体Lの第1および第2の端面Lc、Ldに引き出されている。

【0073】

次に、内部電極20の一部が引出部として露出したセラミック素体Lの第1及び第2端面Lc、Ldに、第1の樹脂層形成用組成物を浸漬法または印刷法などで形成し、その後、第1の樹脂層形成用組成物を乾燥させてから熱硬化させる。このようにして、第1電極層12がセラミック素体Lの第1及び第2端面Lc、Ldに形成される。第1電極層12は、内部電極20の一部と電気的及び物理的に接続されている。

【0074】

次に、第1電極層12の表面に導電性めっき層14を形成する。本実施形態において、Niを主成分とした金属材料を、例えば、電解めっきを用いて第1電極層12の表面に成膜することにより、導電性めっき層14が形成される。次に、導電性めっき層14の表面に、第2の樹脂層形成用組成物を浸漬法または印刷法などで形成する。その後、第2の樹脂層形成用組成物を乾燥させてから熱硬化させることで、第2電極層16が導電性めっき層14の表面に形成される。このような手順により、セラミック素体Lの第1及び第2端面Lc、Ldに、第1の電極層12、導電性めっき層14及び第2の電極層16を有する端子電極10が形成された積層コンデンサCが完成する。

【0075】

[第1変形例]

図5、図6は、第2の電極層の第1変形例を示す拡大模式図である。本変形例は、はんだ粒子16aの他に、他の導電性粒子16e、または、16fを有する点が前述した実施形態とは異なる。すなわち、本変形例は、第2の導電性材料として、はんだ成分の他に他の元素(本変形例ではNiまたはCu)を含んでいる点が前述した実施形態とは異なる。本変形例は、第1の電極層12の態様は前述した実施形態と同じである。他の導電性粒子16e、16fは、はんだ粒子16aよりも融点が高いことが好ましい。本変形例においては、はんだ粒子16aとしてSn粒子、他の導電性粒子16eとしてCu粒子、または、Ni粒子を含んでいる。

【0076】

他の導電性粒子16e、16fは、はんだ粒子16aに対して40重量%〜70重量%含まれているのが好ましい。

【0077】

図5、6に示すように、第2の導電性材料として、はんだ粒子16aとなるSn粒子の他に、他の導電性粒子16e、16fとなるCu粒子やNi粒子を有することで、第2の電極層16を直接的に回路基板にはんだ実装した場合であっても、はんだに比べて融点の高いCu粒子やNi粒子によって第2の電極層16の保形性を確実に維持できる。また、導電性めっき層14のNi成分と、第2の電極層16が含む他の導電性粒子16e、16fであるCu粒子やNi粒子によって、導電性めっき層14と、第2の電極層16との接合強度を向上させて、両者の接合をより確実なものとすることができる。

【0078】

なお、前述したように、第1変形例においてははんだ粒子以外の他の導電性粒子として、Cu粒子、Ni粒子を挙げたが、少なくとも主成分としてCu成分やNi成分を含有していればよく、例えば、Cu粒子とNi粒子との混合物や、Cu−Niなどの合金粒子であってもよい。

【0079】

また、本変形例では、第2の導電性材料としてはんだ粒子16aを用いたが、第2の導電性材料は、はんだ成分を含有していれば形状は必ずしも粒状である必要はなく、例えば、膜状、扁平状、針状のものであってもよい。

【0080】

[第2変形例]

図7は、第2の電極層の第2変形例を示す拡大模式図である。本変形例においては、第2の電極層16において、はんだ被膜16gが導電性粒子16hの表面に形成されている点が前述した実施形態とは異なる。第1の電極層12の態様は前述した実施形態と同じである。本変形例において、はんだ被膜16はSnを含む。このため、本変形例において、導電性粒子16hは少なくとも一部がSnによって被覆されている。導電性粒子16hは、はんだ被膜16gよりも融点が高いことが好ましい。本変形例においては、はんだ被膜16gはSn被膜であり、導電性粒子16hとしてNi粒子を含んでいる。

【0081】

図7に示すように、第2の電極層16において、Snで少なくとも一部が被膜されたNi粒子を第2の導電性材料が含むことで、第2の電極層を直接的に回路基板にはんだ実装した場合であっても、融点の高いNi粒子によって、第2の電極層16の保形性を確実に維持できる。また、導電性めっき層14のNiと、第2の電極層16の導電性材料となるNi粒子とによって、導電性めっき層14と、第2の電極層16との接合強度を向上させて、両者の接合をより確実なものとすることができる。さらに、第2の電極層16ははんだ被膜となるSnを含有することから、第2の電極層16と回路基板とを確実に実装させることができる。

【0082】

なお、第2変形例においては、導電性粒子16hとしてNi粒子を挙げたが、Cu粒子でもよいし、Cu−Niなどの合金粒子であってもよい。さらに、導電性粒子16hは、少なくとも一部Snで被覆されたNi粒子と、少なくとも一部Snで被覆されたCu粒子との両方であってもよい。このようにしても、上述した保形性の維持および第2の電極層16と回路基板との確実な実装といった効果を得ることができる。

【0083】

本実施形態では、本発明を積層コンデンサに適用した例を示しているが、これに限ることはない。本発明は、他のチップ型電子部品、例えば、圧電体素子(圧電アクチュエータ)、インダクタ、バリスタ、サーミスタ等にも適用可能である。

【符号の説明】

【0084】

10 端子電極

12 第1の電極層

12a 第1の導電性粒子(第1の導電性材料)

12b 第2の導電性粒子(第1の導電性材料)

12c 熱硬化性樹脂

14 導電性めっき層

16 第2の電極層

16a はんだ粒子(第2の導電性材料)

16c 熱硬化性樹脂

16e、16f 他の導電性粒子(第2の導電性材料)

16g Sn被膜(第2の導電性材料)

16h 導電性粒子(第2の導電性材料)

20 内部電極

22 誘電体層

C 積層コンデンサ

L セラミック素体

La 第1の主面

Lb 第2の主面

Lc 第1の端面

Ld 第2の端面

Le 第1の側面

Lf 第2の側面

【技術分野】

【0001】

本発明は、チップ型電子部品、特にセラミック材料を用いたチップ型電子部品に関する。

【背景技術】

【0002】

セラミック素体の表面に端子電極を有するチップ型電子部品が知られている。近年は、導電性材料と樹脂とを含む導電性樹脂をチップ型電子部品の端子電極に用いたものが知られている(特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平03−266404号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記特許文献1に記載のチップ型電子部品においては、導電性樹脂層の上にはんだ層が形成されることから、はんだ層のはんだ成分が導電性樹脂層に拡散し、導電性樹脂層の金属成分を溶融したり、はんだ層自体が消失したりする不具合、いわゆるはんだ喰われが生じることがあった。

【0005】

本発明は、上記課題を解決するためになされたものであり、はんだ喰われを抑制できる端子電極を有するチップ型電子部品を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明のチップ型電子部品は、セラミック素体と、セラミック素体の内部に配置され、かつ、セラミック素体の表面に一部が露出した内部電極と、セラミック素体の表面に配置された端子電極とを含み、端子電極は、第1の導電性材料を含むとともに、内部電極の露出した部分および内部電極が露出しているセラミック素体の表面を覆う第1の電極層と、第1の電極層よりもセラミック素体の表面から離れた位置に配置される導電性めっき層と、はんだ成分を含む第2の導電性材料と樹脂とを含むとともに、導電性めっき層よりもセラミック素体の表面から離れた位置に配置される第2の電極層と、を含むことを特徴としている。

【0007】

上述したチップ型電子部品によると、第1の電極層と、はんだ成分を含む第2の電極層との間に、緻密な導電性めっき層が配置されるので、第2の電極層のはんだ成分が第1の電極層へ拡散することを抑制できる。従って、第1の電極層の導電性材料がはんだによって溶融することを防止できるうえ、はんだ成分を含む第2の電極層が消失するのを抑制することができる

【0008】

本発明において、導電性めっき層は第1の電極層を覆うとともに、第2の電極層は導電性めっき層を覆い、かつ、導電性めっき層は第1の電極層と第2の電極層との両方に接触していることが好ましい。

【0009】

上述したチップ型電子部品によると、導電性めっき層は第1の電極層を覆うことから、導電性めっき層よりもセラミック素体の表面から離れた位置に配置される第2の電極層におけるはんだ成分が、第1の電極層に拡散することをより確実に抑制できる。また、また、第2の電極層は導電性めっき層を覆い、なおかつ、緻密な導電性めっき層が第1の電極層と第2の電極層との両方に接触していることから、第1の電極層と導電性めっき層、および、導電性めっき層と第2の電極層との接触抵抗を低減させることができる。

【0010】

本発明において、第1の電極層は第1の導電性材料と樹脂とを含有するのが好ましい。

【0011】

上述したチップ型電子部品によると、第1の電極層、および、第2の電極層いずれもが導電性樹脂電極層となるので、確実に応力緩和することができる。また、第1の電極層が導電性樹脂電極層であることから、第1の電極層の表面に導電性めっき層を形成する際、セラミック素体表面に露出した内部電極にめっき液が浸入することを抑制できるので、絶縁抵抗などの信頼性を向上させることができる。

【0012】

本発明において、第1の導電性材料は、第1の導電性粒子と、第1の導電性粒子よりも粒径の大きい第2の導電性粒子とを有することが好ましい。

【0013】

上述したチップ型電子部品によると、低融点となる粒径の小さい第1の導電性粒子が、セラミック素体表面に露出した内部電極、および、高融点となる粒径の大きい第2の導電性粒子と結合するので、内部電極と第1の電極層との接続性や接触抵抗低減を確実なものとできる。また、粒径の大きい第2の導電性粒子によって、セラミック素体の表面と第1の電極層との固着強度を向上させることができたり、接触抵抗を低減させることができる。

【0014】

本発明において、セラミック素体は、誘電体層と、前記内部電極とが積層されており、第1の導電性粒子の粒径が、内部電極の厚みよりも小さいことが好ましい。

【0015】

上述したチップ型電子部品によると、内部電極の厚みに対して、複数の第1の導電性粒子がセラミック素体の表面に露出した内部電極と結合するので、より確実に接続不良を抑制できる。

【0016】

本発明において、セラミック素体は、誘電体層と、内部電極とが積層されており、第2の導電性粒子の粒径が、内部電極の厚みよりも大きいことが好ましい。

【0017】

上述したチップ型電子部品によると、内部電極の厚みよりも大きい第2の導電性粒子を有することから、接触抵抗の増加を低減することができる。また、セラミック素体の表面と第1の電極層との固着強度を確実に向上させることができる。

【0018】

本発明において、第1の導電性粒子の粒径が0.5μm以下であることが好ましく、第2の導電性粒子の粒径が1μm以上10μm以下であることが好ましい。

【0019】

上述したチップ型電子部品によると、第1の導電性粒子の粒径を0.5μm以下とすることで、セラミック素体表面に露出した内部電極、および、第2の導電性粒子との結合をいっそう確実なものとすることができる。また、第1の導電性粒子の粒径は、0.1μm以下とすることがいっそう好ましい。このようにすることで、セラミック素体表面に露出した内部電極、および、第2の導電性粒子との結合をさらに確実なものとすることができる。また、第2の導電性粒子の粒径を1μm以上10μm以下とすることで、セラミック素体の表面と第1の電極層との固着強度を向上させることができたり、接触抵抗の低減を確実なものとすることができる。

【0020】

本発明において、第1の導電性材料は、CuとNiとのうち少なくとも一方を含有していることが好ましい。

【0021】

上述したチップ型電子部品によると、セラミック素体の表面に露出した内部電極と、第1の電極層との接続性をいっそう確実なものとすることができる。

【0022】

本発明において、第2の電極層は最外層であり、はんだ成分は、少なくともSnを含んでいることが好ましい。

【0023】

上述したチップ型電子部品によると、第2の電極層と回路基板とを確実にはんだで実装することができる。

【0024】

本発明において、第2の導電性材料は、NiとCuとの少なくとも一方をさらに含むことが好ましい。

【0025】

上述したチップ型電子部品によると、はんだ実装時においてはんだ成分が溶融しても、確実に第2の電極層の保形性を維持することができる。

【0026】

本発明において、第2の導電性材料は、少なくとも一部がSnによって被覆されたNi粒子と少なくとも一部がSnによって被覆されたCu粒子との少なくとも一方を含むことが好ましい。

【0027】

上述したチップ型電子部品によると、はんだ実装時においてはんだ成分が溶融しても、確実に第2の電極層の保形性を維持することができる。

【0028】

本発明において、導電性めっき層の導電性材料は、Niを含有していることが好ましい。

【0029】

上述したチップ型電子部品によると、Niははんだに比べて高融点であるので、確実にはんだ成分が第1の電極層に拡散することを抑制できる。

【0030】

本発明において、第1の電極層および第2の電極層は、ガラスフリットを含有しないことが好ましい。

【0031】

上述したチップ型電子部品によると、端子電極の導電性をいっそう向上させることができる。

【発明の効果】

【0032】

本発明によると、はんだ喰われを抑制できる端子電極を有するチップ型電子部品を提供できる。

【図面の簡単な説明】

【0033】

【図1】図1は、積層コンデンサを示す概略斜視図である。

【図2】図2は、図1におけるII−II線に沿った断面図である。

【図3】図3は、実施形態における、第1の電極層の拡大模式図である。

【図4】図4は、実施形態における、第2の電極層の拡大模式図である。

【図5】図5は、第2の電極層の第1変形例を示す拡大模式図である。

【図6】図6は、第2の電極層の第1変形例を示す拡大模式図である。

【図7】図7は、第2の電極層の第2変形例を示す拡大模式図である。

【発明を実施するための形態】

【0034】

本発明を実施するための形態(実施形態)につき、図面を参照しつつ詳細に説明する。以下の実施形態に記載した内容により本発明が限定されるものではない。また、以下に記載した構成要素には、当業者が容易に想定できるもの、実質的に同一のもの、均等の範囲のものが含まれる。さらに、以下に記載した構成要素は適宜組み合わせることが可能である。また、本発明の要旨を逸脱しない範囲で構成の種々の省略、置換または変更を行うことができる。

【0035】

[実施形態]

まず、本実施形態に係るチップ型電子部品としての積層コンデンサCの構成を説明する。図1は本実施形態に係る積層コンデンサの概観斜視図であり、図2は、図1におけるII−II線に沿った断面図である。図1、図2に示されるように、本実施形態に係る積層コンデンサCは、セラミック素体Lと、セラミック素体Lの外表面に配置される2つの端子電極10とを備えている。

【0036】

セラミック素体Lは、略直方体形状を呈しており、その外表面として、対向する第1および第2の主面La、Lbと、対向する第1および第2の端面Lc、Ldと、対向する第1および第2の側面Le、Lfとを有する。第1および第2の端面Lc、Ldは、第1および第2の主面間を連結するように第1および第2の主面La、Lbの短辺方向に伸びている。第1および第2の側面Le、Lfは、第1および第2の主面La、Lb間を連結するように第1および第2の主面La、Lbの長辺方向に伸びている。

【0037】

セラミック素体Lでは、内部電極20が誘電体層22を介して積層されている。各誘電体層22は、例えば誘電体セラミックを含むセラミックグリーンシートの焼結体から構成される。実際の積層コンデンサCでは、誘電体層22の間の境界が視認できない程度に一体化されている。

【0038】

セラミック素体L内に配置された内部電極20は、セラミック素体Lにおける第1の端面Lcと第2の端面Ldとに交互に引き出されるように積層されている。積層方向における隣接する内部電極20、20間の距離は、およそ誘電体層22の厚みに相当する。内部電極20は、積層型の電気素子の内部電極として通常用いられる導電性材料から構成される。本実施形態では、内部電極20は、卑金属であるNiを主成分として含んでいる。なお、主成分とは、複数の成分を備える材料において、最も含有率(重量%)が高い成分をいう(以下同様)。

【0039】

なお、積層方向における誘電体層22の厚みは、例えば0.5μm〜8.0μm程度であり、積層方向における内部電極20の厚みは、例えば0.5μm〜5.0μm程度である。

【0040】

端子電極10は、セラミック素体Lの外表面上に配置されている。端子電極10は、第1の電極層12と、導電性めっき層14と、第2の電極層16とを含んでいる。

【0041】

第1の電極層12は、ガラスフリットを含有する焼付電極層、または、導電性樹脂電極層いずれでもよいが、本実施形態では、導電性樹脂電極層を適用する場合について、説明する。

【0042】

第1の電極層12は、第1の導電性粒子12aと第2の導電性粒子12bとを含む第1の導電性材料と、熱硬化された樹脂12cとを含んだ層である。このようにすることで、第1の電極層12は導電性を有する。第1の電極層12は、セラミック素体Lにおける第1および第2の端面Lc、Ldから、第1および第2の主面La、Lb並びに第1および第2の側面Le、Lfに回り込むように形成されている。そして、第1の電極層12は、第1および第2の端面Lc、Ldに露出した内部電極20を覆うように、内部電極20と物理的かつ電気的に接続されている。第1の導電性樹脂電極層の厚みは、例えば、20μm〜100μm程度である。

【0043】

本実施形態では、第1の電極層12における第1の導電性粒子12aおよび第2の導電性粒子12bをCuとしているが、卑金属であるCu、または、Niを少なくとも主成分として含んでいることが好ましい。第1および第2の導電性粒子12a、12bをCu、または、Niを主成分とすることで、内部電極20の主成分であるNiとの電気的接続性や接合強度を確実なものとすることができる。

【0044】

また、本実施形態では、第1の電極層12は、第1の導電性粒子12aと、第1の導電性粒子よりも粒径の大きな第2の導電性粒子12bを含んでいる。第1の導電性粒子12aの粒径は、好ましくは0.5μm以下、いっそう好ましくは0.1μm以下である。また、第2の導電性粒子12bの粒径は、好ましくは1μm以上10μm以下である。

【0045】

第1の導電性粒子12aの粒径は、第2の導電性粒子12bの粒径よりも小さく、0.5μm以下、いっそう好ましくは0.1μm以下が好ましい。このようにすることで、第1の導電性粒子12aを介して、セラミック素体表面に露出した内部電極20と、第2の導電性粒子12bとを連結させることができることから、内部電極20と第1の電極層12との電気的な接続を確実なものとすることができる。また、第2の導電性粒子12bの粒径を第1の導電性粒子12aの粒径よりも大きく、1μm以上10μm以下とすることが好ましい。このようにすることで、第1の電極層16の接触抵抗を低減させることや、セラミック素体Lおよび導電性めっき層14との密着性を向上できることや、第1の電極層12を熱硬化する際の収縮率が小さくなることにより応力クラックを低減することができる。

【0046】

なお、第1の導電性粒子12aの粒径、および、第2の導電性粒子12bの粒径は、例えば、第1の電極層12の断面を切断し、SEM(Scanning Electron Microscope:走査型電子顕微鏡)像等から平均粒径を導出すればよい。

【0047】

また、第1の導電性粒子12aの粒径は、内部電極間の厚みよりも小さいほうが好ましく、第2の導電性粒子12bの粒径は、内部電極間の厚みよりも大きいほうが好ましい。

【0048】

第1の導電性粒子12aの粒径を内部電極の厚みよりも小さくすることで、複数の第1の導電性粒子12aがセラミック素体の端面Lc、Ldに露出した内部電極20と結合するので、内部電極20との接続をいっそう確実なものとすることができる。また、第2の導電性粒子12bの粒径を内部電極の厚みよりも大きくすることで、第1の電極層16と導電性めっき層14との接触抵抗低減、セラミック素体Lc、Ldや導電性めっき層14との密着性向上、第1の電極層12が熱硬化する際の収縮率が小さくなることによる応力クラック低減などの効果が得られる。

【0049】

本実施形態では、第1の導電性材料は、第1の導電性粒子12aと第2の導電性粒子12bとを含んでいるが、両方を含んでいなくてもよい。すなわち、第1の導電性材料は、第1の導電性粒子12aと第2の導電性粒子12bとの少なくとも一方を含んでいればよい。なお、第1の導電性材料が複数種類の粒子(本実施形態では、第1の導電性粒子12aおよび第2の導電性粒子12b)を含むようにすることで、端子電極10に要求される性能を実現しやすくなるので好ましい。

【0050】

第1の電極層12は、第1の導電性材料と樹脂としての熱硬化型樹脂とを含んだペースト状の第1の樹脂層形成用組成物を用いて、浸漬法、または、印刷法などで形成し、その後、乾燥および熱硬化を行えばよい。乾燥温度や熱硬化温度は、使用する硬化性樹脂に応じて適宜調整される。

【0051】

本実施形態では、第1の樹脂層形成用組成物が含む熱硬化性樹脂としてエポキシ系の樹脂を使用しているが、熱硬化性樹脂の種類は特に制限されるものではなく、エポキシ樹脂以外にも、例えば、フェノール樹脂、アクリル樹脂、シリコーン樹脂、ポリイミド樹脂等を用いることができる。なお、第1の樹脂層形成用組成物中の第1および第2の導電性粒子12a、12bの含有量は、樹脂層形成用組成物の固形分全量を基準として30体積%〜60体積%程度とすることができる。

【0052】

樹脂層形成用組成物は、必要に応じて溶媒をさらに含むものである。溶媒としては、上記熱硬化性樹脂を溶解または分解可能なものであれば公知の溶媒を特に制限なく使用することができる。溶媒として具体的には、例えば、メチルカルビトール、ブチルカルビトール、ブチルカルビトールアセテート、セロソルブ、ブチルセロソルブ、ブチルセロソルブアセテート、テルピネオール等が挙げられる。

【0053】

また、第1の電極層12における樹脂層形成用組成物には、ガラスフリットを含有していない。これにより、第1の電極層12における導電性を高めることができる。

【0054】

導電性めっき層14は、第1の電極層12よりもセラミック素体Lの表面から離れた位置に配置される。本実施形態においては、導電性めっき層14は、第1の電極層12の表面に、第1の電極層12を覆うように配置されており、導電性めっき層14と第1の電極層12とが、物理的かつ電気的に接続されている。導電性めっき層14は、通常の電気めっき法により形成された金属電極層であり、本実施形態ではNiを主成分としており、厚みは1μm〜3μm程度が好ましい。

【0055】

導電性めっき層14は、第1の電極層12よりもセラミック素体Lの表面から離れた位置に配置されていればよい。このため、第1の電極層12と導電性めっき層14との間には、導電性を有する層が設けられていてもよい。このようにすることで、チップ型電子部品(本実施形態ではセラミックコンデンサC)の仕様に合わせた適切な性能を端子電極10に持たせることもできる。

【0056】

第2の電極層16は、導電性めっき層16よりもセラミック素体Lの表面から離れた位置に配置される。本実施形態においては、第2の電極層16は、導電性めっき層14の表面に、導電性めっき層14を覆うように配置されており、第2の電極層16と導電性めっき層14とが、物理的かつ電気的に接続されている。また、第2の電極層16は、端子電極10の最外層となるように配置されている。上述したように、導電性めっき層16は、第1の電気層12を覆い、第2の電極層12は導電性めっき層16を覆う。このような構造により、導電性めっき層16は、第1の電極層12と第2の電極層16との両方に接触している。本実施形態において、第2の電極層16は、端子電極10の最外層であるが、導電性めっき層16よりもセラミック素体Lの表面から離れた位置に配置されていればよい。従って、第2の電極層16の表面に、さらに電極層を設けてもよい。

【0057】

第2の電極層16は、はんだ粒子16aを含む第2の導電性材料と、熱硬化された樹脂16cとを含んだ層である。このようにすることで、第2の電極層16は導電性を有する。第2の電極層16の厚みは、例えば20μm〜100μm程度である。

【0058】

なお、本実施形態では、第2の導電性材料としてはんだ粒子16aを用いたが、第2の導電性材料は、はんだ成分を含有していれば形状は必ずしも粒状である必要はない。例えば、第2の導電性材料は、膜状、扁平状、針状のものであってもよい。

【0059】

第2の電極層16は、第2の導電性材料と樹脂としての熱硬化型樹脂とを含んだペースト状の第2の樹脂層形成用組成物を用いて、浸漬法、または、印刷法などで形成し、その後、乾燥および熱硬化を行えばよい。乾燥温度や熱硬化温度は、使用する熱硬化性樹脂に応じて適宜調整される。また、乾燥温度や熱硬化温度は、はんだ粒子16aの融点以下とすることが好ましい。

【0060】

本実施形態では、第2の導電性材料となるはんだ粒子16aとして、Snが用いられている。なお、第2の導電性材料は、Snに加えて、Ni、Cu、Ag等その他の成分をさらに含んでいてもよい。この第2の導電性材料がSn以外の成分をさらに含む場合、特にNi、Cuのうち少なくとも一方が好ましい。このようにすれば、第2の電極層16を直接に回路基板にはんだ実装した場合であっても、はんだに比べて融点の高いCu、Niによって第2の電極層16の保形性を確実に維持できる。また、導電性めっき層14のNi成分と、第2の電極層16のCu、Niによって、導電性めっき層14と第2の電極層16との接合強度を向上させて、両者の接合をより確実なものとすることができる。

【0061】

また、第2の導電性材料が含むはんだ成分は、Snに限定されるものではなく、例えば、Snを含まないはんだ成分であってもよい。一般に、回路基板に積層コンデンサC等の電子部品を実装する場合には、Snを含むはんだが用いられる。このため、第2の導電性材料が含むはんだ成分が少なくともSnを含むようにすると、第2の電極層16に対するはんだの濡れ性が向上するので、積層コンデンサCを回路基板へ確実に実装することができる。

【0062】

第2の樹脂層形成用組成物が含む熱硬化性樹脂としては特に制限されないが、例えば、フェノール樹脂、アクリル樹脂、シリコーン樹脂、エポキシ樹脂、ポリイミド樹脂等といった、上述した第1の樹脂層形成用組成物が含む熱硬化性樹脂と同様の材料を用いることができる。なお、第2の樹脂層形成用組成物と第1の樹脂層形成用組成物とで、使用する熱硬化性樹脂を異ならせてもよい。

【0063】

上記第2の樹脂層形成用組成物中のはんだ粒子16aの含有量は、第2の樹脂層形成用組成物の固形分全量を基準として30体積%〜60体積%程度とすることができる。

【0064】

第2の樹脂層形成用組成物は、上述した第1の樹脂層形成用組成物と同様に、必要に応じて溶媒をさらに含むものである。溶媒としては、上記熱硬化性樹脂を溶解または分解可能なものであれば公知の溶媒を特に制限なく使用することができる。溶媒として具体的には、例えば、メチルカルビトール、ブチルカルビトール、ブチルカルビトールアセテート、セロソルブ、ブチルセロソルブ、ブチルセロソルブアセテート、テルピネオール等が挙げられる。なお、第2の樹脂層形成用組成物と第1の樹脂層形成用組成物とで、使用する溶媒を異ならせてもよい。

【0065】

また、第2の電極層16における樹脂層形成用組成物には、ガラスフリットを含有していない。これにより、第2の電極層16における導電性をいっそう高めることができる。

【0066】

以上のように、本実施形態に係る積層コンデンサCでは、第1の電極層12と、はんだ粒子を含んだ第2の電極層16との間に、緻密な導電性めっき層14が配置されるので、第2の電極層16のはんだ成分が第1の電極層12へ拡散することを抑制できる。従って、第1の電極層12の導電性粒子12a、12bがはんだによって溶融することを抑制できるうえ、はんだ粒子16aを含む第2の電極層16の保形性が維持できるとともに、第2の電極層16が消失する、いわゆるはんだ喰われを抑制することができる。

【0067】

また、本実施形態の積層コンデンサCでは、第1の電極層12、および、第2の電極層16いずれもが導電性樹脂電極層となるので、確実に応力を緩和することができる。すなわち、導電性樹脂電極層からなる第1の電極層12が、セラミック素体Lの表面に形成されるので、第1の電極層12が有する樹脂が、誘電体層22の電歪振動による内部応力を緩和したり、積層コンデンサCによる振動音の発生を抑制することに有効に作用する。また、導電性樹脂電極層からなる第2の電極層16が、端子電極10の最外層に形成されるので、第2の電極層16が有する樹脂が、積層コンデンサCを回路基板に実装した際の外部応力の緩和に有効に作用する。そして、応力による積層コンデンサCのクラック発生を抑制することができる。

【0068】

また、第1の電極層12が導電性樹脂電極層であることから、ガラスフリット入りの焼付電極層の場合に必要な高温焼付処理が不要となり、熱応力や内部応力によって素体Lにクラックが入ることを確実に防止できる。

【0069】

さらに、第1の電極層12を有することで、第1の電極層12の表面に導電性めっき層14を形成する際、セラミック素体表面に露出した内部電極20にめっき液が浸入することを抑制できることとなり、絶縁抵抗などの信頼性を向上させることができる。

【0070】

また、本実施形態においては、最外層となる第2の電極層16の導電性材料がはんだを主成分としているので、第2の電極層16の表面にめっき層を形成しなくても回路基板に実装することができる。また、導電性樹脂層である第2の電極層16を、回路基板の実装部に実装できるので、回路基板からの外部応力や熱応力を直接的に第2の電極層16で緩和させることが可能となる。

【0071】

なお、本実施形態においては、第1の電極層12として導電性樹脂電極層を用いる場合を説明したが、第1の電極層12は、ガラスフリット入りの焼付電極層であってもよい。第1の電極層12を焼付電極層とした場合には、セラミック素体Lと第1の電極層12との固着強度いっそう向上させることができ、また、第1の電極層12と導電性めっき層14との接触抵抗をいっそう低減させることができる。

【0072】

[本実施形態に係るチップ型電子部品の製造方法]

次に、本実施形態に係るチップ型電子部品としての積層コンデンサCの製造方法を簡単に説明する。積層コンデンサCを製造するにあたり、表面に内部電極20の一部が露出した引出部を有するセラミック素体Lを準備する。引出部は、セラミック素体Lの第1および第2の端面Lc、Ldに引き出されている。

【0073】

次に、内部電極20の一部が引出部として露出したセラミック素体Lの第1及び第2端面Lc、Ldに、第1の樹脂層形成用組成物を浸漬法または印刷法などで形成し、その後、第1の樹脂層形成用組成物を乾燥させてから熱硬化させる。このようにして、第1電極層12がセラミック素体Lの第1及び第2端面Lc、Ldに形成される。第1電極層12は、内部電極20の一部と電気的及び物理的に接続されている。

【0074】

次に、第1電極層12の表面に導電性めっき層14を形成する。本実施形態において、Niを主成分とした金属材料を、例えば、電解めっきを用いて第1電極層12の表面に成膜することにより、導電性めっき層14が形成される。次に、導電性めっき層14の表面に、第2の樹脂層形成用組成物を浸漬法または印刷法などで形成する。その後、第2の樹脂層形成用組成物を乾燥させてから熱硬化させることで、第2電極層16が導電性めっき層14の表面に形成される。このような手順により、セラミック素体Lの第1及び第2端面Lc、Ldに、第1の電極層12、導電性めっき層14及び第2の電極層16を有する端子電極10が形成された積層コンデンサCが完成する。

【0075】

[第1変形例]

図5、図6は、第2の電極層の第1変形例を示す拡大模式図である。本変形例は、はんだ粒子16aの他に、他の導電性粒子16e、または、16fを有する点が前述した実施形態とは異なる。すなわち、本変形例は、第2の導電性材料として、はんだ成分の他に他の元素(本変形例ではNiまたはCu)を含んでいる点が前述した実施形態とは異なる。本変形例は、第1の電極層12の態様は前述した実施形態と同じである。他の導電性粒子16e、16fは、はんだ粒子16aよりも融点が高いことが好ましい。本変形例においては、はんだ粒子16aとしてSn粒子、他の導電性粒子16eとしてCu粒子、または、Ni粒子を含んでいる。

【0076】

他の導電性粒子16e、16fは、はんだ粒子16aに対して40重量%〜70重量%含まれているのが好ましい。

【0077】

図5、6に示すように、第2の導電性材料として、はんだ粒子16aとなるSn粒子の他に、他の導電性粒子16e、16fとなるCu粒子やNi粒子を有することで、第2の電極層16を直接的に回路基板にはんだ実装した場合であっても、はんだに比べて融点の高いCu粒子やNi粒子によって第2の電極層16の保形性を確実に維持できる。また、導電性めっき層14のNi成分と、第2の電極層16が含む他の導電性粒子16e、16fであるCu粒子やNi粒子によって、導電性めっき層14と、第2の電極層16との接合強度を向上させて、両者の接合をより確実なものとすることができる。

【0078】

なお、前述したように、第1変形例においてははんだ粒子以外の他の導電性粒子として、Cu粒子、Ni粒子を挙げたが、少なくとも主成分としてCu成分やNi成分を含有していればよく、例えば、Cu粒子とNi粒子との混合物や、Cu−Niなどの合金粒子であってもよい。

【0079】

また、本変形例では、第2の導電性材料としてはんだ粒子16aを用いたが、第2の導電性材料は、はんだ成分を含有していれば形状は必ずしも粒状である必要はなく、例えば、膜状、扁平状、針状のものであってもよい。

【0080】

[第2変形例]

図7は、第2の電極層の第2変形例を示す拡大模式図である。本変形例においては、第2の電極層16において、はんだ被膜16gが導電性粒子16hの表面に形成されている点が前述した実施形態とは異なる。第1の電極層12の態様は前述した実施形態と同じである。本変形例において、はんだ被膜16はSnを含む。このため、本変形例において、導電性粒子16hは少なくとも一部がSnによって被覆されている。導電性粒子16hは、はんだ被膜16gよりも融点が高いことが好ましい。本変形例においては、はんだ被膜16gはSn被膜であり、導電性粒子16hとしてNi粒子を含んでいる。

【0081】

図7に示すように、第2の電極層16において、Snで少なくとも一部が被膜されたNi粒子を第2の導電性材料が含むことで、第2の電極層を直接的に回路基板にはんだ実装した場合であっても、融点の高いNi粒子によって、第2の電極層16の保形性を確実に維持できる。また、導電性めっき層14のNiと、第2の電極層16の導電性材料となるNi粒子とによって、導電性めっき層14と、第2の電極層16との接合強度を向上させて、両者の接合をより確実なものとすることができる。さらに、第2の電極層16ははんだ被膜となるSnを含有することから、第2の電極層16と回路基板とを確実に実装させることができる。

【0082】

なお、第2変形例においては、導電性粒子16hとしてNi粒子を挙げたが、Cu粒子でもよいし、Cu−Niなどの合金粒子であってもよい。さらに、導電性粒子16hは、少なくとも一部Snで被覆されたNi粒子と、少なくとも一部Snで被覆されたCu粒子との両方であってもよい。このようにしても、上述した保形性の維持および第2の電極層16と回路基板との確実な実装といった効果を得ることができる。

【0083】

本実施形態では、本発明を積層コンデンサに適用した例を示しているが、これに限ることはない。本発明は、他のチップ型電子部品、例えば、圧電体素子(圧電アクチュエータ)、インダクタ、バリスタ、サーミスタ等にも適用可能である。

【符号の説明】

【0084】

10 端子電極

12 第1の電極層

12a 第1の導電性粒子(第1の導電性材料)

12b 第2の導電性粒子(第1の導電性材料)

12c 熱硬化性樹脂

14 導電性めっき層

16 第2の電極層

16a はんだ粒子(第2の導電性材料)

16c 熱硬化性樹脂

16e、16f 他の導電性粒子(第2の導電性材料)

16g Sn被膜(第2の導電性材料)

16h 導電性粒子(第2の導電性材料)

20 内部電極

22 誘電体層

C 積層コンデンサ

L セラミック素体

La 第1の主面

Lb 第2の主面

Lc 第1の端面

Ld 第2の端面

Le 第1の側面

Lf 第2の側面

【特許請求の範囲】

【請求項1】

セラミック素体と、

前記セラミック素体の内部に配置され、かつ、前記セラミック素体の表面に一部が露出した内部電極と、

前記セラミック素体の表面に配置された端子電極と、を含み、

前記端子電極は、

第1の導電性材料を含むとともに、前記内部電極の露出した部分および前記内部電極が露出している前記セラミック素体の表面を覆う第1の電極層と、

前記第1の電極層よりも前記セラミック素体の表面から離れた位置に配置される導電性めっき層と、

はんだ成分を含む第2の導電性材料と樹脂とを含むとともに、前記導電性めっき層よりも前記セラミック素体の表面から離れた位置に配置される第2の電極層と、を含むことを特徴とするチップ型電子部品。

【請求項2】

前記導電性めっき層は前記第1の電極層を覆うとともに、前記第2の電極層は前記導電性めっき層を覆い、かつ、前記導電性めっき層は前記第1の電極層と前記第2の電極層との両方に接触していることを特徴とする請求項1に記載のチップ型電子部品。

【請求項3】

前記第1の電極層は、前記第1の導電性材料と樹脂とを含有することを特徴とする請求項1または2に記載のチップ型電子部品。

【請求項4】

前記第1の導電性材料は、第1の導電性粒子と、前記第1の導電性粒子よりも粒径の大きい第2の導電性粒子とを有することを特徴とする請求項3に記載のチップ型電子部品。

【請求項5】

前記セラミック素体は、誘電体層と、前記内部電極とが積層されており、

前記第1の導電性粒子の粒径が、前記内部電極の厚みよりも小さいことを特徴とする請求項4に記載のチップ型電子部品。

【請求項6】

前記セラミック素体は、誘電体層と、前記内部電極とが積層されており、

前記第2の導電性粒子の粒径が、前記内部電極の厚みよりも大きいことを特徴とする請求項4または5に記載のチップ型電子部品。

【請求項7】

前記第1の導電性粒子の粒径が0.5μm以下であり、前記第2の導電性粒子の粒径が1μm以上10μm以下であることを特徴とする請求項4〜6のいずれか一項に記載のチップ型電子部品。

【請求項8】

前記第1の導電性材料は、CuとNiとのうち少なくとも一方を含有することを特徴とする請求項1〜7のいずれか一項に記載のチップ型電子部品。

【請求項9】

前記第2の電極層は最外層であり、前記はんだ成分は、少なくともSnを含むことを特徴とする請求項1〜8のいずれか一項に記載のチップ型電子部品。

【請求項10】

前記第2の導電性材料は、NiとCuとの少なくとも一方をさらに含むことを特徴とする請求項1〜9のいずれか一項に記載のチップ型電子部品。

【請求項11】

前記第2の導電性材料は、少なくとも一部がSnによって被覆されたNi粒子と少なくとも一部がSnによって被覆されたCu粒子との少なくとも一方を含むことを特徴とする請求項1〜9のいずれか一項に記載のチップ型電子部品。

【請求項12】

前記導電性めっき層の導電性材料は、Niを含有することを特徴とする請求項1〜11のいずれか一項に記載のチップ型電子部品。

【請求項13】

前記第1の電極層および前記第2の電極層は、ガラスフリットを含有しないことを特徴とする請求項3〜12のいずれか一項に記載のチップ型電子部品。

【請求項1】

セラミック素体と、

前記セラミック素体の内部に配置され、かつ、前記セラミック素体の表面に一部が露出した内部電極と、

前記セラミック素体の表面に配置された端子電極と、を含み、

前記端子電極は、

第1の導電性材料を含むとともに、前記内部電極の露出した部分および前記内部電極が露出している前記セラミック素体の表面を覆う第1の電極層と、

前記第1の電極層よりも前記セラミック素体の表面から離れた位置に配置される導電性めっき層と、

はんだ成分を含む第2の導電性材料と樹脂とを含むとともに、前記導電性めっき層よりも前記セラミック素体の表面から離れた位置に配置される第2の電極層と、を含むことを特徴とするチップ型電子部品。

【請求項2】

前記導電性めっき層は前記第1の電極層を覆うとともに、前記第2の電極層は前記導電性めっき層を覆い、かつ、前記導電性めっき層は前記第1の電極層と前記第2の電極層との両方に接触していることを特徴とする請求項1に記載のチップ型電子部品。

【請求項3】

前記第1の電極層は、前記第1の導電性材料と樹脂とを含有することを特徴とする請求項1または2に記載のチップ型電子部品。

【請求項4】

前記第1の導電性材料は、第1の導電性粒子と、前記第1の導電性粒子よりも粒径の大きい第2の導電性粒子とを有することを特徴とする請求項3に記載のチップ型電子部品。

【請求項5】

前記セラミック素体は、誘電体層と、前記内部電極とが積層されており、

前記第1の導電性粒子の粒径が、前記内部電極の厚みよりも小さいことを特徴とする請求項4に記載のチップ型電子部品。

【請求項6】

前記セラミック素体は、誘電体層と、前記内部電極とが積層されており、

前記第2の導電性粒子の粒径が、前記内部電極の厚みよりも大きいことを特徴とする請求項4または5に記載のチップ型電子部品。

【請求項7】

前記第1の導電性粒子の粒径が0.5μm以下であり、前記第2の導電性粒子の粒径が1μm以上10μm以下であることを特徴とする請求項4〜6のいずれか一項に記載のチップ型電子部品。

【請求項8】

前記第1の導電性材料は、CuとNiとのうち少なくとも一方を含有することを特徴とする請求項1〜7のいずれか一項に記載のチップ型電子部品。

【請求項9】

前記第2の電極層は最外層であり、前記はんだ成分は、少なくともSnを含むことを特徴とする請求項1〜8のいずれか一項に記載のチップ型電子部品。

【請求項10】

前記第2の導電性材料は、NiとCuとの少なくとも一方をさらに含むことを特徴とする請求項1〜9のいずれか一項に記載のチップ型電子部品。

【請求項11】

前記第2の導電性材料は、少なくとも一部がSnによって被覆されたNi粒子と少なくとも一部がSnによって被覆されたCu粒子との少なくとも一方を含むことを特徴とする請求項1〜9のいずれか一項に記載のチップ型電子部品。

【請求項12】

前記導電性めっき層の導電性材料は、Niを含有することを特徴とする請求項1〜11のいずれか一項に記載のチップ型電子部品。

【請求項13】

前記第1の電極層および前記第2の電極層は、ガラスフリットを含有しないことを特徴とする請求項3〜12のいずれか一項に記載のチップ型電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−110372(P2013−110372A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−256675(P2011−256675)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]