チップ状電子部品及びチップ状電子部品の搭載方法

【課題】狭ピッチの部品でも、部品や基板の破壊発生がなく容易に目的のチップ状電子部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法を提供する。

【解決手段】電子回路基板に搭載するチップ状電子部品であって、チップ状電子部品の搭載面の反対面には、該搭載面と電気的に導通すると共に、一端が前記チップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有する。

【解決手段】電子回路基板に搭載するチップ状電子部品であって、チップ状電子部品の搭載面の反対面には、該搭載面と電気的に導通すると共に、一端が前記チップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子回路基板に搭載するチップ状電子部品及びチップ状電子部品の搭載方法に係わり、特に狭ピッチの部品でも、部品や基板破壊の発生がなく容易に目的の部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法に関する。

【背景技術】

【0002】

電子回路基板上のIC等リード端子を有するチップ状電子部品の測定を行う際、測定用プローブを直接、対象の端子へ当て測定する方法が一般的であり、既に知られている。

【0003】

例えば特許文献1では、配線回路において、配線回路の電気的な動作特性の測定に用いられるチェック用チップ状電子部品であって、フラックスがチェック用チップ状電子部品に付着しても従来は有機溶剤を使用しており接触不良の問題は顕在化しなかったが、無洗浄状態でフラックスがチェック用チップ状電子部品に付着した場合でも高い接触信頼性とコストを抑えるという目的で、ほぼ中央部に孔を有する絶縁基板に上面電極及び裏面電極を設け、ほぼ中央部に孔を有する電気的接続するチェック用チップ状電子部品の構造とすることで、ピン状の測定端子、フック状の測定端子のいずれでも容易に使用でき、接触不良を起こすことなく電気的な動作回路を測定できる構成が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載されている方法では、チップ状電子部品の端子数が多く配線間の狭ピッチ化に対するプロービング測定を容易に行うことができないという問題があった。

【0005】

また、今までのチェック用プローブを端子へ直接あてる測定方法では、特に、端子の数が多く狭ピッチとなっているチップ状電子部品の特定端子のみを、正確かつ安定にプロービングすることが難しいという問題があった。

【0006】

さらに、チェック用プローブが隣接端子と接触することによるショート、チェック用プローブを直接端子へ当てることでの端子への負荷、これらによる部品や基板の破壊発生、またフラックスによるチェック用プローブ−端子間の接触不良による測定ミスの発生という問題があった。

【0007】

そこで本発明は、上記問題点に鑑みてなされたもので、狭ピッチの部品でも、部品や基板の破壊発生がなく容易に目的のチップ状電子部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するため、本発明に係るチップ状電子部品は、電子回路基板に搭載するチップ状電子部品であって、チップ状電子部品の搭載面の反対面には、該搭載面と電気的に導通すると共に、一端が前記チップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有することを特徴とする。

【0009】

また本発明に係るチップ状電子部品は、上記に記載のチップ状電子部品が絶縁部を介して複数並べて連結されたことを特徴とする。

【0010】

また本発明に係るチップ状電子部品の搭載方法は、電子回路基板に上記のチップ状電子部品を搭載する搭載方法であって、電子回路基板の略平行な配線パターンの個々のパターンに前記チップ状電子部品を配置するときに、該配線パターンをX軸方向とした場合、配置する隣り合う部品は直交するY軸方向においてX座標方向が段階的に異なるように複数のチップ状電子部品を1つのセットとして配置して、該セットの配置を繰り返して配置することを特徴とする。

【発明の効果】

【0011】

本発明により、狭ピッチの部品でも、部品や基板の破壊発生がなく容易に目的のチップ状電子部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法を提供することが可能になる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施形態に係る測定用チップ状電子部品(U字型)の斜視図である。

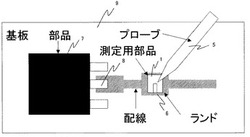

【図2】本発明の実施形態に係るチップ状電子部品をプローブで測定するときの状態を説明する図である。

【図3】チップ状電子部品を搭載した従来の電子回路基板の側面図である。

【図4】チップ状電子部品を搭載した従来の電子回路基板の上面図である。

【図5】本発明の実施形態に係るチップ状電子部品を搭載した電子回路基板の側面図である。

【図6】本発明の実施形態に係るチップ状電子部品を搭載した電子回路基板の上面図である。

【図7】本発明の実施形態に係るU字溝型チップ状電子部品の詳細図である。

【図8】本発明の実施形態に係るV字溝型チップ状電子部品の斜視図である。

【図9】本発明の実施形態に係るV字溝型チップ状電子部品の詳細図である。

【図10】本発明の実施形態に係る壁側が深いV字溝型チップ状電子部品の斜視図である。

【図11】本発明の実施形態に係る壁側が深いV字溝型チップ状電子部品の詳細図である。

【図12】本発明の実施形態に係る壁側が深くて狭いチップ状電子部品の斜視図である。

【図13】本発明の実施形態に係る壁側が深くて狭いチップ状電子部品の斜視図である。

【図14】本発明の実施形態に係るV字溝を両面に設けたチップ状電子部品の詳細図である。

【図15】本発明の実施形態に係るV字溝型を連結したチップ状電子部品の斜視図である。

【図16】本発明の実施形態に係るV字溝型を連結したチップ状電子部品の詳細図である。

【図17】本発明の実施形態に係る電子回路基板に搭載時のチップ状電子部品の配置図である。

【図18】本発明の実施形態に係る電子回路基板に搭載時のチップ状電子部品の配置図である。

【発明を実施するための形態】

【0013】

本発明は、プリント基板へ実装されたチップ状電子部品における計測器を用いた端子部の計測に際して、以下の特徴を有する。要するに、本発明は、チップ状電子部品の端子付近にプロービング可能な部品を実装することにより、測定プローブで目的の電子部品の被測定端子に測定する際に、容易にプローブ可能となり、被測定端子の信号計測ができることが特徴である。

【0014】

具体的には、プリント基板へ実装されたチップ状電子部品における測定用部品を用いた計測に際して、チップ状電子部品の端子とプリント基板とが半田によって接合されているプリント基板の配線先のランドパターンに測定用部品を取り付け、測定プローブを測定用部品に当てる際に、測定プローブを凹型の溝へ当てることで、測定プローブとチップ状電子部品に隣接する端子とPWBを接触させることなく、チップ状電子部品の計測を行なう。さらに測定用チップ状電子部品が小さいので、チップ状電子部品が小型化・狭ピッチしても、目的のチップ状電子部品の被測定端子に測定する際に、容易にプローブが可能なことが特徴である。

【0015】

本発明の好適な実施の形態について以下に図面を参照して詳細に説明する。

【0016】

図1は、プリント基板の配線回路において電気的特性の測定に用いられるチェック用チップ状電子部品(U字型)の斜視図である。

【0017】

チップ状電子部品1の一方の面にはレール状にU字型やV字型の溝2を有しており、レール端の一方はチップ状電子部品側面3に達しているが、もう他方の端はチップ状電子部品面内で途切れた壁4となっている。この溝2の窪みの最大の深さは0.5mm以上(プローブピンが引っかかる深さ)が望ましい。また、本実施形態のチップ状電子部品1はプリント基板上のランドパターンへ半田実装するものである。またチップ状電子部品1は、例えばステンレス鋼板に窪み2を設けニッケル下地にSnメッキをした金属である。

【0018】

また、本実施形態のチップ状電子部品1の製造には特許文献2に記載されるようなチップジャンパの製造工程を用いることができる。この場合は使用時に電極が上下になるような使い方となる。この製造工程はチップ抵抗を作る工程と同等なので、後で説明するように、はんだ付け面とチェック面の間に所定の抵抗値を持たせることもできるし、複数のチップ状電子部品1を連結させた部品の製造に対応することもできる。その他、公知のチップ状電子部品の製造方法が適用可能である。

【0019】

またチップ状電子部品1の高さは、0.5mm以上の高さであれば構造上の問題はないが、高さを上げるに従い、リフロー搭載時にフラックスのかかる量も減少するという効果がある。

【0020】

図2は、図1に示したチップ状電子部品をプリント基板実装後にプローブで測定するときの状態を説明する図である。

【0021】

まず、プローブ5を窪み2に当てて、力を加えることによりプローブ先端5は窪み2の最深部へ移動し、レール端4へスライドさせ突き当てることによって安定した接触を可能とする。また、プローブ5を突き当てることで、小型化可能で、配線間隔が狭くても、実装可能である。

【0022】

本実施形態のチップ状電子部品1の大きさは、一般的な呼称で言えば、1005(1.0mm×0.5mm)、0603(0.6mm×0.3mm)くらいであるが、2125(2mm×1.25mm)や3216(3.2mm×1.6mm)などの大きい形状であっても安定した測定が可能である。

【0023】

一方、本実施形態のチップ状電子部品1の高さは、前述したように0.5mm程度まで低くすることはできるが、必要とする溝2の深さ、製造する材料、加工方法による制約が生じる。

【0024】

図3は、チップ状電子部品を搭載した従来の電子回路基板の側面図であり、図4は、従来の電子回路基板の上面図である。

【0025】

従来は部品端子8と半田付けされている配線パターン上のランドパターン6へ直接プローブを接触させ測定を実施していたが、ランドパターン6へ付着しているフラックスを削りとる作業によるパターンへの損傷の可能性がある。また、ランドバターン6が平面であるため安定した接触を維持することは難しかった。

【0026】

図5は、本実施形態のチップ状電子部品を搭載した電子回路基板の側面図であり、図6は、電子回路基板の上面図である。

【0027】

本実施形態では、半田実装により測定用チップ状電子部品1を固定する。これにより測定用チップ状電子部品1にフラックスが付着していてもランドパターン6を傷つけることなく削りとることが可能となる。なお、測定用チップ状電子部品1の配置方向は図示したものに限るものではなく、端子からのパターン6引出し方向を0°としたときに、チップ状電子部品1の開放部が0°、90°、180°、270°など、どちらに向けてもかまわない。図6は、270°の例を示している。

【0028】

図7は、図1で示したU字溝型の詳細図であり、(a)上面図、(b)前面図、(c)側面図である。一方の面にはレール状にU字型の溝2を有しており、溝部の一方はチップ状電子部品側面3に達しているが、もう他方の端はチップ状電子部品面内で途切れた壁4となっている。所謂、一端がチップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有している。

【0029】

図8は、V字溝型の斜視図である。図9は、V字溝型の詳細図であり、(a)上面図、(b)前面図、(c)側面図である。一方の面にはレール状にV字型の溝2を有しており、溝部の一方はチップ状電子部品側面3に達しているが、もう他方の端はチップ状電子部品面内で途切れた壁4となっている。所謂、一端がチップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有している。

【0030】

図10は、壁側が深いV字溝型の斜視図である。図11は、壁側が深いV字溝型の詳細図であり、(a)上面図、(b)前面図、(c)側面図である。

【0031】

図10は、図8に示すV字溝型の壁側4の深さを深くしている。この構造により測定時にプローブが外れにくくなる。なお、U字溝型でも同様の構成が可能である。さらに壁側4の幅を開放側に比べて狭くしても良い。この場合は、図1及び図8と比較し、プローブが測定チップ状電子部品にガイドに誘い込みやすくした構造となることを特徴とする。

【0032】

図12は、溝部の壁側が深くて狭いチップ状電子部品を示す図である。また図13は、溝部の壁側が深くて狭いチップ状電子部品を示す図である。

【0033】

図12及び図13は、溝部の壁側4が深くて、幅が狭い例であるが、溝2の深さは変えずに幅だけを変えてもプローブ誘い込みの効果を得ることができる。また、この図13に示すようにU字型、V字型でなく溝部2を平面とすることもできる。また、溝2を設ける面においては、電気的なチェックに用いる溝部2以外の面部に着色することが望ましい。本実施形態では、1つの基板に多数の部品が搭載されるので、作業者が見たときにパターンを判別し易くすることができる。着色する色としては例えば、抵抗器の色コードに従って、0:黒、1:茶、2:赤、3:橙、4:黄、5:緑、6:青、7:紫、8:灰、9:白、などが好ましい。また、着色は電気的チェックに影響がなければ溝部を着色しても良いし、他の面(側面)を着色しても良い。

【0034】

図14は、V字溝を両面に設けた実施形態を示す図である。本実施形態のように、溝部2はチップの1面に限る必要はなく、図14のようにV字溝を2面に備えても良い。この場合はリフローではなく手搭載する時にチップ状電子部品1の表裏を気にする必要がない。さらに、チップ状電子部品1サイズ(特に高さ)が大きければ他の面に溝を設けることもできる。この場合、上面からのプローブ接触以外にも側面からの接触も可能となる。

【0035】

図15は、V字溝型を連結した実施形態の斜視図である。図16は、V字溝型を連結した実施形態の詳細図であり(a)上面図、(b)前面図である。

【0036】

図15及び図16は、V字溝型のチップ状電子部品1を連結した実施形態である。各チップ部分は上述した実施形態の説明と同様であり他の溝形状でもかまわない。

【0037】

製造方法としては前述したようにチップジャンパやチップ抵抗器の製造に準ずる。即ち、ベース材をセラミックなどにすることで絶縁部を介して複数のチップを一体にして製造するものである。この場合1つの部品としての搭載面積が増えるので溝部の幅は単独部品と同じままで溝部2両脇のスペースを減らして絶縁部の領域を捻出しても良い。これにより1005や0603ピッチでの連結部品の作成が容易となる。なお、公知のチップ状電子部品の製造方法が適用可能である。

【0038】

また各チップが安定してはんだ付けされるように基板の搭載面と隙間があくように絶縁部の高さを調整すると良い。

【0039】

本実施形態は狭ピッチのチップ状電子部品1から引き出されたパターン6のチェックにも適用できるので、図17、図18で説明するように搭載時の配置方法も考慮する必要がある。このような時には図15、図16に示す連結したチップ状電子部品10を用いると良い。このとき、作業者が判別しやすいように連結の隣り合うチップ状電子部品1が判別できるように、溝形状をU字とV字を交互に並べる、あるいは着色を交互に変えると良い。さらに前述のように0〜9に対応した色で着色すると良い。ただし、単独のチップ状電子部品1に比べれば配置の自由度は低下する。

【0040】

また、製造方法としてチップジャンパやチップ抵抗器の製造工程を用いる場合は、はんだ付け面と溝部の間に所定の抵抗値を設定することができる。また、チェック用測定器とのインピーダンス整合などに利用することができる。

【0041】

図17は、本実施形態のチップ状電子部品1の配置を示す上面図である。本実施形態は、図6に示したものと同様の考え方である。すなわち、本実施形態では、半田実装により測定用チップ状電子部品1を固定する。これにより測定用チップ状電子部品に1フラックスが付着していてもランドパターンを傷つけることなく削りとることが可能となる。

【0042】

このように、測定チップ状電子部品1の隣接間をずらし配置することにより、配線間ピッチが短くても測定チップ状電子部品1が実装可能である。またピン番号の識別を容易化できる。さらにプローブ5を測定チップ状電子部品1に当て易くなる。

【0043】

図18は、本実施形態のチップ状電子部品1の配置を示す上面図である。本実施形態は、図6に示したものと同様の考え方である。すなわち、本実施形態では、半田実装により測定用チップ状電子部品1を固定する。これにより測定用チップ状電子部品1にフラックスが付着していてもランドパターンを傷つけることなく削りとることが可能となる。

【0044】

このように、測定チップ状電子部品1の隣接間を交互ずらし配置することにより、配線間ピッチが短くても測定チップ状電子部品1が実装可能である。また測定チップ状電子部品1を部品の近くに配置可能である。またピン番号の識別を容易化できる。またプローブ5を測定チップ状電子部品1に当て易くなる。

【0045】

上記の実施形態によれば、チップ状電子部品の端子数が多く配線間の狭ピッチ化しても、目的の部品端子の信号にプローブを接触不良なく測定することが可能となる。

【0046】

また上記の実施形態によれば、チップ状電子部品の端子数が多く配線間の狭ピッチ化しても目的の被測定端子の信号を確実にプロービングすることができる。

【0047】

また上記の実施形態によれば、チップ状電子部品や基板破壊の破損等を防止できる。

【0048】

また上記の実施形態によれば、チップ状電子部品が加工容易で、小型化できるので、被測定端子の信号近くにプロービング可能なチップ状電子部品を実装でき確実にプロービングすることができる。

【0049】

また上記の実施形態によれば、プローブがチップ状電子部品や基板に直接触れないので破損等を防止できる。

【0050】

なお、上述する実施形態は、本発明の好適な実施形態であり、上記実施形態のみに本発明の範囲を限定するものではなく、本発明の要旨を逸脱しない範囲において種々の変更を施した形態での実施が可能である。

【0051】

本発明に係るチップ状電子部品の前記溝部は、U字形状あるいはV字形状の彫り込み形状であることを特徴とする。

【0052】

また本発明に係るチップ状電子部品の前記溝部は、開放側から壁部側の端部に向かって彫り込み深さが深くなることを特徴とする。

【0053】

また本発明に係るチップ状電子部品の前記溝部は、開放側から壁部側の端部に向かって彫り込み幅が狭くなることを特徴とする。

【0054】

また本発明に係るチップ状電子部品の前記搭載面と前記溝部は所定の抵抗値を介して電気的に導通していることを特徴とする。

【0055】

また本発明に係るチップ状電子部品の前記反対面は、前記溝部以外が該溝部とは異なる色に着色されていることを特徴とする。

【0056】

また本発明に係るチップ状電子部品の前記溝部は、壁部側の端部の深さが0.5mm以上であることを特徴とする。

【0057】

また本発明に係るチップ状電子部品の前記連結されたチップ状電子部品は、前記溝部の彫り込み形状がU字形状とV字形状とが交互に配置されていることを特徴とする。

【0058】

また本発明に係るチップ状電子部品の前記連結されたチップ状電子部品は、前記反対面の前記溝部以外の色が、少なくとも隣り合うチップ状電子部品において異なるように着色されていることを特徴とする。

【0059】

また本発明に係るチップ状電子部品の前記異なる着色は、少なくとも3色以上を1つの配色として、該配色が繰り返し設定されていることを特徴とする。

【産業上の利用可能性】

【0060】

本発明によれば、チップ状電子部品、チップ状電子部品及び電子回路基板などの用途に適用できる。

【符号の説明】

【0061】

1 チップ状電子部品

2 溝(レール状の窪み)

3 チップ状電子部品側面

4 壁

5 プローブ

6 ランドパターン(配線パターン)

7 部品

8 部品端子

9 基板

10 連結したチップ状電子部品

【先行技術文献】

【特許文献】

【0062】

【特許文献1】特開平07−006806号公報

【特許文献2】特開平07−326411号公報

【技術分野】

【0001】

本発明は、電子回路基板に搭載するチップ状電子部品及びチップ状電子部品の搭載方法に係わり、特に狭ピッチの部品でも、部品や基板破壊の発生がなく容易に目的の部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法に関する。

【背景技術】

【0002】

電子回路基板上のIC等リード端子を有するチップ状電子部品の測定を行う際、測定用プローブを直接、対象の端子へ当て測定する方法が一般的であり、既に知られている。

【0003】

例えば特許文献1では、配線回路において、配線回路の電気的な動作特性の測定に用いられるチェック用チップ状電子部品であって、フラックスがチェック用チップ状電子部品に付着しても従来は有機溶剤を使用しており接触不良の問題は顕在化しなかったが、無洗浄状態でフラックスがチェック用チップ状電子部品に付着した場合でも高い接触信頼性とコストを抑えるという目的で、ほぼ中央部に孔を有する絶縁基板に上面電極及び裏面電極を設け、ほぼ中央部に孔を有する電気的接続するチェック用チップ状電子部品の構造とすることで、ピン状の測定端子、フック状の測定端子のいずれでも容易に使用でき、接触不良を起こすことなく電気的な動作回路を測定できる構成が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載されている方法では、チップ状電子部品の端子数が多く配線間の狭ピッチ化に対するプロービング測定を容易に行うことができないという問題があった。

【0005】

また、今までのチェック用プローブを端子へ直接あてる測定方法では、特に、端子の数が多く狭ピッチとなっているチップ状電子部品の特定端子のみを、正確かつ安定にプロービングすることが難しいという問題があった。

【0006】

さらに、チェック用プローブが隣接端子と接触することによるショート、チェック用プローブを直接端子へ当てることでの端子への負荷、これらによる部品や基板の破壊発生、またフラックスによるチェック用プローブ−端子間の接触不良による測定ミスの発生という問題があった。

【0007】

そこで本発明は、上記問題点に鑑みてなされたもので、狭ピッチの部品でも、部品や基板の破壊発生がなく容易に目的のチップ状電子部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するため、本発明に係るチップ状電子部品は、電子回路基板に搭載するチップ状電子部品であって、チップ状電子部品の搭載面の反対面には、該搭載面と電気的に導通すると共に、一端が前記チップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有することを特徴とする。

【0009】

また本発明に係るチップ状電子部品は、上記に記載のチップ状電子部品が絶縁部を介して複数並べて連結されたことを特徴とする。

【0010】

また本発明に係るチップ状電子部品の搭載方法は、電子回路基板に上記のチップ状電子部品を搭載する搭載方法であって、電子回路基板の略平行な配線パターンの個々のパターンに前記チップ状電子部品を配置するときに、該配線パターンをX軸方向とした場合、配置する隣り合う部品は直交するY軸方向においてX座標方向が段階的に異なるように複数のチップ状電子部品を1つのセットとして配置して、該セットの配置を繰り返して配置することを特徴とする。

【発明の効果】

【0011】

本発明により、狭ピッチの部品でも、部品や基板の破壊発生がなく容易に目的のチップ状電子部品端子の信号にプローブを接触不良なく測定することが可能なチップ状電子部品及びチップ状電子部品の搭載方法を提供することが可能になる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施形態に係る測定用チップ状電子部品(U字型)の斜視図である。

【図2】本発明の実施形態に係るチップ状電子部品をプローブで測定するときの状態を説明する図である。

【図3】チップ状電子部品を搭載した従来の電子回路基板の側面図である。

【図4】チップ状電子部品を搭載した従来の電子回路基板の上面図である。

【図5】本発明の実施形態に係るチップ状電子部品を搭載した電子回路基板の側面図である。

【図6】本発明の実施形態に係るチップ状電子部品を搭載した電子回路基板の上面図である。

【図7】本発明の実施形態に係るU字溝型チップ状電子部品の詳細図である。

【図8】本発明の実施形態に係るV字溝型チップ状電子部品の斜視図である。

【図9】本発明の実施形態に係るV字溝型チップ状電子部品の詳細図である。

【図10】本発明の実施形態に係る壁側が深いV字溝型チップ状電子部品の斜視図である。

【図11】本発明の実施形態に係る壁側が深いV字溝型チップ状電子部品の詳細図である。

【図12】本発明の実施形態に係る壁側が深くて狭いチップ状電子部品の斜視図である。

【図13】本発明の実施形態に係る壁側が深くて狭いチップ状電子部品の斜視図である。

【図14】本発明の実施形態に係るV字溝を両面に設けたチップ状電子部品の詳細図である。

【図15】本発明の実施形態に係るV字溝型を連結したチップ状電子部品の斜視図である。

【図16】本発明の実施形態に係るV字溝型を連結したチップ状電子部品の詳細図である。

【図17】本発明の実施形態に係る電子回路基板に搭載時のチップ状電子部品の配置図である。

【図18】本発明の実施形態に係る電子回路基板に搭載時のチップ状電子部品の配置図である。

【発明を実施するための形態】

【0013】

本発明は、プリント基板へ実装されたチップ状電子部品における計測器を用いた端子部の計測に際して、以下の特徴を有する。要するに、本発明は、チップ状電子部品の端子付近にプロービング可能な部品を実装することにより、測定プローブで目的の電子部品の被測定端子に測定する際に、容易にプローブ可能となり、被測定端子の信号計測ができることが特徴である。

【0014】

具体的には、プリント基板へ実装されたチップ状電子部品における測定用部品を用いた計測に際して、チップ状電子部品の端子とプリント基板とが半田によって接合されているプリント基板の配線先のランドパターンに測定用部品を取り付け、測定プローブを測定用部品に当てる際に、測定プローブを凹型の溝へ当てることで、測定プローブとチップ状電子部品に隣接する端子とPWBを接触させることなく、チップ状電子部品の計測を行なう。さらに測定用チップ状電子部品が小さいので、チップ状電子部品が小型化・狭ピッチしても、目的のチップ状電子部品の被測定端子に測定する際に、容易にプローブが可能なことが特徴である。

【0015】

本発明の好適な実施の形態について以下に図面を参照して詳細に説明する。

【0016】

図1は、プリント基板の配線回路において電気的特性の測定に用いられるチェック用チップ状電子部品(U字型)の斜視図である。

【0017】

チップ状電子部品1の一方の面にはレール状にU字型やV字型の溝2を有しており、レール端の一方はチップ状電子部品側面3に達しているが、もう他方の端はチップ状電子部品面内で途切れた壁4となっている。この溝2の窪みの最大の深さは0.5mm以上(プローブピンが引っかかる深さ)が望ましい。また、本実施形態のチップ状電子部品1はプリント基板上のランドパターンへ半田実装するものである。またチップ状電子部品1は、例えばステンレス鋼板に窪み2を設けニッケル下地にSnメッキをした金属である。

【0018】

また、本実施形態のチップ状電子部品1の製造には特許文献2に記載されるようなチップジャンパの製造工程を用いることができる。この場合は使用時に電極が上下になるような使い方となる。この製造工程はチップ抵抗を作る工程と同等なので、後で説明するように、はんだ付け面とチェック面の間に所定の抵抗値を持たせることもできるし、複数のチップ状電子部品1を連結させた部品の製造に対応することもできる。その他、公知のチップ状電子部品の製造方法が適用可能である。

【0019】

またチップ状電子部品1の高さは、0.5mm以上の高さであれば構造上の問題はないが、高さを上げるに従い、リフロー搭載時にフラックスのかかる量も減少するという効果がある。

【0020】

図2は、図1に示したチップ状電子部品をプリント基板実装後にプローブで測定するときの状態を説明する図である。

【0021】

まず、プローブ5を窪み2に当てて、力を加えることによりプローブ先端5は窪み2の最深部へ移動し、レール端4へスライドさせ突き当てることによって安定した接触を可能とする。また、プローブ5を突き当てることで、小型化可能で、配線間隔が狭くても、実装可能である。

【0022】

本実施形態のチップ状電子部品1の大きさは、一般的な呼称で言えば、1005(1.0mm×0.5mm)、0603(0.6mm×0.3mm)くらいであるが、2125(2mm×1.25mm)や3216(3.2mm×1.6mm)などの大きい形状であっても安定した測定が可能である。

【0023】

一方、本実施形態のチップ状電子部品1の高さは、前述したように0.5mm程度まで低くすることはできるが、必要とする溝2の深さ、製造する材料、加工方法による制約が生じる。

【0024】

図3は、チップ状電子部品を搭載した従来の電子回路基板の側面図であり、図4は、従来の電子回路基板の上面図である。

【0025】

従来は部品端子8と半田付けされている配線パターン上のランドパターン6へ直接プローブを接触させ測定を実施していたが、ランドパターン6へ付着しているフラックスを削りとる作業によるパターンへの損傷の可能性がある。また、ランドバターン6が平面であるため安定した接触を維持することは難しかった。

【0026】

図5は、本実施形態のチップ状電子部品を搭載した電子回路基板の側面図であり、図6は、電子回路基板の上面図である。

【0027】

本実施形態では、半田実装により測定用チップ状電子部品1を固定する。これにより測定用チップ状電子部品1にフラックスが付着していてもランドパターン6を傷つけることなく削りとることが可能となる。なお、測定用チップ状電子部品1の配置方向は図示したものに限るものではなく、端子からのパターン6引出し方向を0°としたときに、チップ状電子部品1の開放部が0°、90°、180°、270°など、どちらに向けてもかまわない。図6は、270°の例を示している。

【0028】

図7は、図1で示したU字溝型の詳細図であり、(a)上面図、(b)前面図、(c)側面図である。一方の面にはレール状にU字型の溝2を有しており、溝部の一方はチップ状電子部品側面3に達しているが、もう他方の端はチップ状電子部品面内で途切れた壁4となっている。所謂、一端がチップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有している。

【0029】

図8は、V字溝型の斜視図である。図9は、V字溝型の詳細図であり、(a)上面図、(b)前面図、(c)側面図である。一方の面にはレール状にV字型の溝2を有しており、溝部の一方はチップ状電子部品側面3に達しているが、もう他方の端はチップ状電子部品面内で途切れた壁4となっている。所謂、一端がチップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有している。

【0030】

図10は、壁側が深いV字溝型の斜視図である。図11は、壁側が深いV字溝型の詳細図であり、(a)上面図、(b)前面図、(c)側面図である。

【0031】

図10は、図8に示すV字溝型の壁側4の深さを深くしている。この構造により測定時にプローブが外れにくくなる。なお、U字溝型でも同様の構成が可能である。さらに壁側4の幅を開放側に比べて狭くしても良い。この場合は、図1及び図8と比較し、プローブが測定チップ状電子部品にガイドに誘い込みやすくした構造となることを特徴とする。

【0032】

図12は、溝部の壁側が深くて狭いチップ状電子部品を示す図である。また図13は、溝部の壁側が深くて狭いチップ状電子部品を示す図である。

【0033】

図12及び図13は、溝部の壁側4が深くて、幅が狭い例であるが、溝2の深さは変えずに幅だけを変えてもプローブ誘い込みの効果を得ることができる。また、この図13に示すようにU字型、V字型でなく溝部2を平面とすることもできる。また、溝2を設ける面においては、電気的なチェックに用いる溝部2以外の面部に着色することが望ましい。本実施形態では、1つの基板に多数の部品が搭載されるので、作業者が見たときにパターンを判別し易くすることができる。着色する色としては例えば、抵抗器の色コードに従って、0:黒、1:茶、2:赤、3:橙、4:黄、5:緑、6:青、7:紫、8:灰、9:白、などが好ましい。また、着色は電気的チェックに影響がなければ溝部を着色しても良いし、他の面(側面)を着色しても良い。

【0034】

図14は、V字溝を両面に設けた実施形態を示す図である。本実施形態のように、溝部2はチップの1面に限る必要はなく、図14のようにV字溝を2面に備えても良い。この場合はリフローではなく手搭載する時にチップ状電子部品1の表裏を気にする必要がない。さらに、チップ状電子部品1サイズ(特に高さ)が大きければ他の面に溝を設けることもできる。この場合、上面からのプローブ接触以外にも側面からの接触も可能となる。

【0035】

図15は、V字溝型を連結した実施形態の斜視図である。図16は、V字溝型を連結した実施形態の詳細図であり(a)上面図、(b)前面図である。

【0036】

図15及び図16は、V字溝型のチップ状電子部品1を連結した実施形態である。各チップ部分は上述した実施形態の説明と同様であり他の溝形状でもかまわない。

【0037】

製造方法としては前述したようにチップジャンパやチップ抵抗器の製造に準ずる。即ち、ベース材をセラミックなどにすることで絶縁部を介して複数のチップを一体にして製造するものである。この場合1つの部品としての搭載面積が増えるので溝部の幅は単独部品と同じままで溝部2両脇のスペースを減らして絶縁部の領域を捻出しても良い。これにより1005や0603ピッチでの連結部品の作成が容易となる。なお、公知のチップ状電子部品の製造方法が適用可能である。

【0038】

また各チップが安定してはんだ付けされるように基板の搭載面と隙間があくように絶縁部の高さを調整すると良い。

【0039】

本実施形態は狭ピッチのチップ状電子部品1から引き出されたパターン6のチェックにも適用できるので、図17、図18で説明するように搭載時の配置方法も考慮する必要がある。このような時には図15、図16に示す連結したチップ状電子部品10を用いると良い。このとき、作業者が判別しやすいように連結の隣り合うチップ状電子部品1が判別できるように、溝形状をU字とV字を交互に並べる、あるいは着色を交互に変えると良い。さらに前述のように0〜9に対応した色で着色すると良い。ただし、単独のチップ状電子部品1に比べれば配置の自由度は低下する。

【0040】

また、製造方法としてチップジャンパやチップ抵抗器の製造工程を用いる場合は、はんだ付け面と溝部の間に所定の抵抗値を設定することができる。また、チェック用測定器とのインピーダンス整合などに利用することができる。

【0041】

図17は、本実施形態のチップ状電子部品1の配置を示す上面図である。本実施形態は、図6に示したものと同様の考え方である。すなわち、本実施形態では、半田実装により測定用チップ状電子部品1を固定する。これにより測定用チップ状電子部品に1フラックスが付着していてもランドパターンを傷つけることなく削りとることが可能となる。

【0042】

このように、測定チップ状電子部品1の隣接間をずらし配置することにより、配線間ピッチが短くても測定チップ状電子部品1が実装可能である。またピン番号の識別を容易化できる。さらにプローブ5を測定チップ状電子部品1に当て易くなる。

【0043】

図18は、本実施形態のチップ状電子部品1の配置を示す上面図である。本実施形態は、図6に示したものと同様の考え方である。すなわち、本実施形態では、半田実装により測定用チップ状電子部品1を固定する。これにより測定用チップ状電子部品1にフラックスが付着していてもランドパターンを傷つけることなく削りとることが可能となる。

【0044】

このように、測定チップ状電子部品1の隣接間を交互ずらし配置することにより、配線間ピッチが短くても測定チップ状電子部品1が実装可能である。また測定チップ状電子部品1を部品の近くに配置可能である。またピン番号の識別を容易化できる。またプローブ5を測定チップ状電子部品1に当て易くなる。

【0045】

上記の実施形態によれば、チップ状電子部品の端子数が多く配線間の狭ピッチ化しても、目的の部品端子の信号にプローブを接触不良なく測定することが可能となる。

【0046】

また上記の実施形態によれば、チップ状電子部品の端子数が多く配線間の狭ピッチ化しても目的の被測定端子の信号を確実にプロービングすることができる。

【0047】

また上記の実施形態によれば、チップ状電子部品や基板破壊の破損等を防止できる。

【0048】

また上記の実施形態によれば、チップ状電子部品が加工容易で、小型化できるので、被測定端子の信号近くにプロービング可能なチップ状電子部品を実装でき確実にプロービングすることができる。

【0049】

また上記の実施形態によれば、プローブがチップ状電子部品や基板に直接触れないので破損等を防止できる。

【0050】

なお、上述する実施形態は、本発明の好適な実施形態であり、上記実施形態のみに本発明の範囲を限定するものではなく、本発明の要旨を逸脱しない範囲において種々の変更を施した形態での実施が可能である。

【0051】

本発明に係るチップ状電子部品の前記溝部は、U字形状あるいはV字形状の彫り込み形状であることを特徴とする。

【0052】

また本発明に係るチップ状電子部品の前記溝部は、開放側から壁部側の端部に向かって彫り込み深さが深くなることを特徴とする。

【0053】

また本発明に係るチップ状電子部品の前記溝部は、開放側から壁部側の端部に向かって彫り込み幅が狭くなることを特徴とする。

【0054】

また本発明に係るチップ状電子部品の前記搭載面と前記溝部は所定の抵抗値を介して電気的に導通していることを特徴とする。

【0055】

また本発明に係るチップ状電子部品の前記反対面は、前記溝部以外が該溝部とは異なる色に着色されていることを特徴とする。

【0056】

また本発明に係るチップ状電子部品の前記溝部は、壁部側の端部の深さが0.5mm以上であることを特徴とする。

【0057】

また本発明に係るチップ状電子部品の前記連結されたチップ状電子部品は、前記溝部の彫り込み形状がU字形状とV字形状とが交互に配置されていることを特徴とする。

【0058】

また本発明に係るチップ状電子部品の前記連結されたチップ状電子部品は、前記反対面の前記溝部以外の色が、少なくとも隣り合うチップ状電子部品において異なるように着色されていることを特徴とする。

【0059】

また本発明に係るチップ状電子部品の前記異なる着色は、少なくとも3色以上を1つの配色として、該配色が繰り返し設定されていることを特徴とする。

【産業上の利用可能性】

【0060】

本発明によれば、チップ状電子部品、チップ状電子部品及び電子回路基板などの用途に適用できる。

【符号の説明】

【0061】

1 チップ状電子部品

2 溝(レール状の窪み)

3 チップ状電子部品側面

4 壁

5 プローブ

6 ランドパターン(配線パターン)

7 部品

8 部品端子

9 基板

10 連結したチップ状電子部品

【先行技術文献】

【特許文献】

【0062】

【特許文献1】特開平07−006806号公報

【特許文献2】特開平07−326411号公報

【特許請求の範囲】

【請求項1】

電子回路基板に搭載するチップ状電子部品であって、

チップ状電子部品の搭載面の反対面には、該搭載面と電気的に導通すると共に、一端が前記チップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有することを特徴とするチップ状電子部品。

【請求項2】

前記溝部は、U字形状あるいはV字形状の彫り込み形状であることを特徴とする請求項1に記載のチップ状電子部品。

【請求項3】

前記溝部は、開放側から壁部側の端部に向かって彫り込み深さが深くなることを特徴とする請求項1または2に記載のチップ状電子部品。

【請求項4】

前記溝部は、開放側から壁部側の端部に向かって彫り込み幅が狭くなることを特徴とする請求項1から3のいずれか1項に記載のチップ状電子部品。

【請求項5】

前記搭載面と前記溝部は所定の抵抗値を介して電気的に導通していることを特徴とする請求項1から4のいずれか1項に記載のチップ状電子部品。

【請求項6】

前記反対面は、前記溝部以外が該溝部とは異なる色に着色されていることを特徴とする請求項1から4のいずれか1項に記載のチップ状電子部品。

【請求項7】

前記溝部は、壁部側の端部の深さが0.5mm以上であることを特徴とする請求項1から6のいずれか1項に記載のチップ状電子部品。

【請求項8】

請求項1から7に記載のチップ状電子部品が絶縁部を介して複数並べて連結されたことを特徴とするチップ状電子部品。

【請求項9】

前記連結されたチップ状電子部品は、前記溝部の彫り込み形状がU字形状とV字形状とが交互に配置されていることを特徴とする請求項8に記載のチップ状電子部品。

【請求項10】

前記連結されたチップ状電子部品は、前記反対面の前記溝部以外の色が、少なくとも隣り合うチップ状電子部品において異なるように着色されていることを特徴とする請求項8に記載のチップ状電子部品。

【請求項11】

前記異なる着色は、少なくとも3色以上を1つの配色として、該配色が繰り返し設定されていることを特徴とする請求項10に記載のチップ状電子部品。

【請求項12】

電子回路基板に請求項1〜7のチップ状電子部品を搭載する搭載方法であって、

電子回路基板の略平行な配線パターンの個々のパターンに前記チップ状電子部品を配置するときに、該配線パターンをX軸方向とした場合、配置する隣り合う部品は直交するY軸方向においてX座標方向が段階的に異なるように複数のチップ状電子部品を1つのセットとして配置して、該セットの配置を繰り返して配置することを特徴とするチップ状電子部品の搭載方法。

【請求項1】

電子回路基板に搭載するチップ状電子部品であって、

チップ状電子部品の搭載面の反対面には、該搭載面と電気的に導通すると共に、一端が前記チップ状電子部品の側面に開放されて他端が壁部となっている彫り込み方向の溝部を有することを特徴とするチップ状電子部品。

【請求項2】

前記溝部は、U字形状あるいはV字形状の彫り込み形状であることを特徴とする請求項1に記載のチップ状電子部品。

【請求項3】

前記溝部は、開放側から壁部側の端部に向かって彫り込み深さが深くなることを特徴とする請求項1または2に記載のチップ状電子部品。

【請求項4】

前記溝部は、開放側から壁部側の端部に向かって彫り込み幅が狭くなることを特徴とする請求項1から3のいずれか1項に記載のチップ状電子部品。

【請求項5】

前記搭載面と前記溝部は所定の抵抗値を介して電気的に導通していることを特徴とする請求項1から4のいずれか1項に記載のチップ状電子部品。

【請求項6】

前記反対面は、前記溝部以外が該溝部とは異なる色に着色されていることを特徴とする請求項1から4のいずれか1項に記載のチップ状電子部品。

【請求項7】

前記溝部は、壁部側の端部の深さが0.5mm以上であることを特徴とする請求項1から6のいずれか1項に記載のチップ状電子部品。

【請求項8】

請求項1から7に記載のチップ状電子部品が絶縁部を介して複数並べて連結されたことを特徴とするチップ状電子部品。

【請求項9】

前記連結されたチップ状電子部品は、前記溝部の彫り込み形状がU字形状とV字形状とが交互に配置されていることを特徴とする請求項8に記載のチップ状電子部品。

【請求項10】

前記連結されたチップ状電子部品は、前記反対面の前記溝部以外の色が、少なくとも隣り合うチップ状電子部品において異なるように着色されていることを特徴とする請求項8に記載のチップ状電子部品。

【請求項11】

前記異なる着色は、少なくとも3色以上を1つの配色として、該配色が繰り返し設定されていることを特徴とする請求項10に記載のチップ状電子部品。

【請求項12】

電子回路基板に請求項1〜7のチップ状電子部品を搭載する搭載方法であって、

電子回路基板の略平行な配線パターンの個々のパターンに前記チップ状電子部品を配置するときに、該配線パターンをX軸方向とした場合、配置する隣り合う部品は直交するY軸方向においてX座標方向が段階的に異なるように複数のチップ状電子部品を1つのセットとして配置して、該セットの配置を繰り返して配置することを特徴とするチップ状電子部品の搭載方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−42432(P2012−42432A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2010−186519(P2010−186519)

【出願日】平成22年8月23日(2010.8.23)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成22年8月23日(2010.8.23)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]