チップ間通信用のアーキテクチャ及び技術

本発明はアナログ信号チャンネルが種々の集積回路チップ(IC)を通過する電気システムを含んでいる。チャンネルは1以上のアナログ信号を伝播できる。各ICはそこを通過する信号を変更でき、それを別のICまたはシステムコンポーネントへ通過する。チャンネルはプログラム可能であることができる。各ICは別のICまたはシステムコンポーネントからチャンネル信号を受信し、それを別のIC又はシステムコンポーネントへ送信する前に受信された信号を変更するための比較装置またはマルチプレクサを含むことができる。比較装置またはマルチプレクサはプログラム可能であることができ、チャンネルからの入来する信号を種々の他の信号又はしきい値と比較し、或いは単にゲートを通るフローとして作用し、信号が任意の変更なしに通過することを可能にするように選択的に構成されることができる。比較は比較装置の出力を決定できる。比較装置、マルチプレクサ及びチャンネルの動作及びプログラミングはシステム制御装置により中央で制御されることができ、ICまたはその組合せにより独立して制御されることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は集積回路チップ(IC)用の装置及び技術に関する。

【背景技術】

【0002】

電子システムは多数のICを含むことができる。これらのIC間の通信は直接的または間接的に行われることができる。直接通信は直接的に情報を交換する2つのICを含むことができる。間接通信は、mSilica社の制御装置ICにより間接的に情報を交換する2つのICを含むことができ、本発明の代理人はチップ間通信が行われる電気システムを設計し、開発した。例えばmSilica社は米国特許出願第11/942,239号明細書(発明の名称“Apparatus and Technique for Modular Electronics Display Control”)の出願人であり、この発明は液晶ディスプレイのバックライト制御の優秀なモジュラ方法を開示している。この方法によれば、幾つかのドライバICはシステム制御装置の仕事負荷を共有し、バックライトシステムのLEDストリングを制御するために使用される。各ドライバICはストリングの一部を制御する。米国特許出願第11/942,239号明細書はその全体がここで参考文献として組み込まれている。このようなシステムでは、IC間の実時間通信が望まれる。本発明は効率的で、実行が容易で、実時間で行われることができるチップ間通信のための優秀なアーキテクチャ及び技術を提供する。

【発明の概要】

【0003】

本発明はアナログ信号チャンネルが種々の集積回路チップ(IC)を通過する電気システムを含んでいる。チャンネルは1以上のアナログ信号を伝送できる。各ICはそこを通過する信号を変更でき、それを別のICまたはシステムコンポーネントへ送る。チャンネルはプログラム可能にすることができる。各ICは別のICまたはシステムコンポーネントからチャンネル信号を受信し、それを別のIC又はシステムコンポーネントへ送信する前に受信された信号を変更するための比較装置またはマルチプレクサを含むことができる。比較装置またはマルチプレクサはプログラム可能にすることができ、チャンネルから入来する信号を種々の他の信号又はしきい値と比較し、或いは単にゲートを通るフローとして作用し、信号が何等の変更なしに通過することを可能にするように選択的に構成されることができる。比較は比較装置の出力を決定できる。比較装置、マルチプレクサ及びチャンネルの動作及びプログラミングはシステム制御装置により中央で制御されることができ、ICまたはその組合せにより独立して制御されることができる。

【0004】

本発明の前述及び他の目的と利点は添付図面を伴った以下の詳細な説明を考察して明白になるであろう。ここで同じ参照符合は全体を通して類似の部分を指している。

【図面の簡単な説明】

【0005】

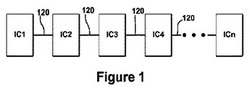

【図1】本発明のシステムの例示的な機能ブロック図である。

【図2】本発明のシステムの別の例示的な機能ブロック図である。

【図3】本発明の集積回路チップ(IC)の例示的な機能ブロック図である。

【図4】本発明の応用の例示的なフローチャートである。

【発明を実施するための形態】

【0006】

図1は本発明のシステムの例示的なアーキテクチャを示している。図1はデイジー・チェイン方式で整列され、共に信号チャンネル120により結合されている複数のIC番号1、2、3、4、nを示している。信号チャンネル120はチップ間アナログ信号伝送を行うために使用されることができるワイヤ、電気導体、トレース等を含むことができる。信号チャンネル120は種々のIC 1−n間で伝送されることのできる情報流を含むことができ、ここで情報は種々のIC 1−nにより調節されることができる。

【0007】

図2は本発明のシステムの別の例示的なアーキテクチャを示している。図2では、信号チャンネル120はそれぞれIC 1-n内の信号調節ブロック201、202、203、204、205を通過する。1実施形態では、信号調節ブロック201-205は信号チャンネル120を通って流れるアナログ信号のレベルを調節できる。1実施形態では、信号調節ブロック201-205は信号チャンネル120から受信されたアナログ信号を別の信号と比較でき、その比較に基づいてアナログ信号のレベルを調節できる。1実施形態では、信号調節ブロック201-205は信号チャンネル120から受信されたアナログ信号をしきい値電圧又は電流値と比較することができ、その比較に基づいてアナログ信号のレベルを調節できる。当業者はアナログ信号がアナログ信号の瞬間値、平均値、二乗平均平方根(値)等を比較することにより比較されることができる。

【0008】

1実施形態では、信号調節ブロック201-205は信号チャンネル120から受信されたアナログ信号を多数の信号と比較し、その比較に基づいてアナログ信号のレベルを調節することができる。1実施形態では、信号調節ブロック201-205はプログラム可能にすることができる。信号調節ブロック201-205はハードウェア、ソフトウェア、またはファームウェアで実行されることができる。1実施形態では、信号調節ブロック201-205はマルチプレクサを含むことができる。1実施形態では信号調節ブロック201-205は演算増幅器を含んでいる。1実施形態では信号調節ブロック201-205は比較装置を含んでいる。1実施形態では信号調節ブロック201-205の幾つか又は全てが同じまたは類似の構造及び機能を有することができる。

【0009】

図3は本発明のICの機能ブロック図を示しており、これは任意又は全てのIC 1−nを表すことができる。この例では、調節ブロックは2入力比較装置310を含んでいる。比較装置310の1入力は信号チャンネル120へ結合されている。比較装置310の他方の入力は別の信号源312へ結合されている。比較装置310は信号チャンネル120により与えられた信号と信号源312により与えられた信号を比較する。比較の結果は信号チャンネル120により送信された信号のレベルを調節するために使用されることができる。1実施形態では、信号チャンネル120により伝送された信号のレベルは比較装置310の2つの入力の高い方のレベルに調節されることができる。1実施形態では、信号チャンネル120により伝送された信号のレベルは比較装置310の2つの入力の低い方のレベルに調節されることができる。

【0010】

当業者は比較装置310が3以上の入力を含むことができ、信号チャンネル120により伝送された信号のレベルはこれらの入力の比較結果に基づいて調節されることができることを理解するであろう。当業者は比較装置310がプログラム可能な装置であることができ、比較に基づいている信号を出力するようにプログラムされることができ、出力信号のレベルは比較装置310の入力信号のいずれかのレベルとは異なる可能性があることを理解するであろう。1実施形態では、比較装置310は比較を行わず、何等の調節なしに信号チャンネル120上で信号を通過するようにゲートを通るフローとして作用するように選択的にプログラムされることができる。

【0011】

1実施形態では、比較装置310はマルチプレクサと置換されることができる。マルチプレクサは信号チャンネル120上の信号を含むその入力を多重化し、それらを別のチップまたはシステムコンポーネントへ送信することができる。1実施形態では、全てのIC 1−nのマルチプレクサにより多重化された全ての信号は目的地のICまたはシステムコンポーネントにより受信される。目的地のIC又はシステムコンポーネントはその後全ての信号を解析し、例えば最低の信号レベルおよび/または多重化された信号の最低の信号レベルを有する信号を決定する。

【0012】

図4は本発明の電気システムの例示的な応用のフローチャート400を示している。この明細書では、IC 1−nはLCDのバックライトシステム用のLEDのストリングを駆動するために使用される。各IC 1−nはLEDストリングの異なるセットを駆動する。各セットは例えば6個のLEDストリングを含むことができる。各IC 1−nはそれが制御している各LEDストリングを通って流れる電流を示すフィードバック信号を受信することができる。ブロック410で、IC 1は6個の信号(FB1)の最低レベルを有するフィードバック信号を駆動してそれをIC2へ送信する6個のLEDストリングに関する6個のフィードバック信号を比較する。ブロック420で、IC2はFB1をその6個のストリングから受信する6個のフィードバック信号の最低の信号と比較し、それらの2個の信号(FB2)の低いレベルを有する信号をIC3へ送る。ブロック430で、IC3はFB2をその6個のストリングから受信する6個のフィードバック信号の最低の信号と比較し、それらの2個の信号(FB3)の最低レベルを有する信号をIC4へ送る。ブロック440で、IC4はFB3をその6個のストリングから受信する6個のフィードバック信号の最低レベルの信号と比較し、それらの2個の信号(FB4)の低いレベルを有する信号をIC5(図示せず)に送る。ブロック450で、チェインの最後のICはチェイン中のその先行するIC(IC(n−1))から受信された信号とその6個のストリングから受信する6個のフィードバック信号の最低レベルの信号との最終的な比較を行う。システムの最低のLEDストリング駆動電流はしたがって決定される。

【0013】

本発明はアナログチャンネルが多数のチップと相互接続する特有で的確な技術を提供する。比較は、デイジーチェインの逐次的なチップのアナログ出力信号と、デイジーチェイン中の次のチップの出力と比較するために選択された2個の信号の高い方又は低い方との間で漸進的に行われることができる。このようにして、デイジーチェイン中の全てのチップにより発生される全ての出力信号の最終的に最高又は最低のものが決定される。当業者は前述の本発明の技術、構造、方法が例示であることを認識するであろう。本発明は、本発明の技術的範囲から逸脱せずに種々の実施形態で実行することができる。

【技術分野】

【0001】

本発明は集積回路チップ(IC)用の装置及び技術に関する。

【背景技術】

【0002】

電子システムは多数のICを含むことができる。これらのIC間の通信は直接的または間接的に行われることができる。直接通信は直接的に情報を交換する2つのICを含むことができる。間接通信は、mSilica社の制御装置ICにより間接的に情報を交換する2つのICを含むことができ、本発明の代理人はチップ間通信が行われる電気システムを設計し、開発した。例えばmSilica社は米国特許出願第11/942,239号明細書(発明の名称“Apparatus and Technique for Modular Electronics Display Control”)の出願人であり、この発明は液晶ディスプレイのバックライト制御の優秀なモジュラ方法を開示している。この方法によれば、幾つかのドライバICはシステム制御装置の仕事負荷を共有し、バックライトシステムのLEDストリングを制御するために使用される。各ドライバICはストリングの一部を制御する。米国特許出願第11/942,239号明細書はその全体がここで参考文献として組み込まれている。このようなシステムでは、IC間の実時間通信が望まれる。本発明は効率的で、実行が容易で、実時間で行われることができるチップ間通信のための優秀なアーキテクチャ及び技術を提供する。

【発明の概要】

【0003】

本発明はアナログ信号チャンネルが種々の集積回路チップ(IC)を通過する電気システムを含んでいる。チャンネルは1以上のアナログ信号を伝送できる。各ICはそこを通過する信号を変更でき、それを別のICまたはシステムコンポーネントへ送る。チャンネルはプログラム可能にすることができる。各ICは別のICまたはシステムコンポーネントからチャンネル信号を受信し、それを別のIC又はシステムコンポーネントへ送信する前に受信された信号を変更するための比較装置またはマルチプレクサを含むことができる。比較装置またはマルチプレクサはプログラム可能にすることができ、チャンネルから入来する信号を種々の他の信号又はしきい値と比較し、或いは単にゲートを通るフローとして作用し、信号が何等の変更なしに通過することを可能にするように選択的に構成されることができる。比較は比較装置の出力を決定できる。比較装置、マルチプレクサ及びチャンネルの動作及びプログラミングはシステム制御装置により中央で制御されることができ、ICまたはその組合せにより独立して制御されることができる。

【0004】

本発明の前述及び他の目的と利点は添付図面を伴った以下の詳細な説明を考察して明白になるであろう。ここで同じ参照符合は全体を通して類似の部分を指している。

【図面の簡単な説明】

【0005】

【図1】本発明のシステムの例示的な機能ブロック図である。

【図2】本発明のシステムの別の例示的な機能ブロック図である。

【図3】本発明の集積回路チップ(IC)の例示的な機能ブロック図である。

【図4】本発明の応用の例示的なフローチャートである。

【発明を実施するための形態】

【0006】

図1は本発明のシステムの例示的なアーキテクチャを示している。図1はデイジー・チェイン方式で整列され、共に信号チャンネル120により結合されている複数のIC番号1、2、3、4、nを示している。信号チャンネル120はチップ間アナログ信号伝送を行うために使用されることができるワイヤ、電気導体、トレース等を含むことができる。信号チャンネル120は種々のIC 1−n間で伝送されることのできる情報流を含むことができ、ここで情報は種々のIC 1−nにより調節されることができる。

【0007】

図2は本発明のシステムの別の例示的なアーキテクチャを示している。図2では、信号チャンネル120はそれぞれIC 1-n内の信号調節ブロック201、202、203、204、205を通過する。1実施形態では、信号調節ブロック201-205は信号チャンネル120を通って流れるアナログ信号のレベルを調節できる。1実施形態では、信号調節ブロック201-205は信号チャンネル120から受信されたアナログ信号を別の信号と比較でき、その比較に基づいてアナログ信号のレベルを調節できる。1実施形態では、信号調節ブロック201-205は信号チャンネル120から受信されたアナログ信号をしきい値電圧又は電流値と比較することができ、その比較に基づいてアナログ信号のレベルを調節できる。当業者はアナログ信号がアナログ信号の瞬間値、平均値、二乗平均平方根(値)等を比較することにより比較されることができる。

【0008】

1実施形態では、信号調節ブロック201-205は信号チャンネル120から受信されたアナログ信号を多数の信号と比較し、その比較に基づいてアナログ信号のレベルを調節することができる。1実施形態では、信号調節ブロック201-205はプログラム可能にすることができる。信号調節ブロック201-205はハードウェア、ソフトウェア、またはファームウェアで実行されることができる。1実施形態では、信号調節ブロック201-205はマルチプレクサを含むことができる。1実施形態では信号調節ブロック201-205は演算増幅器を含んでいる。1実施形態では信号調節ブロック201-205は比較装置を含んでいる。1実施形態では信号調節ブロック201-205の幾つか又は全てが同じまたは類似の構造及び機能を有することができる。

【0009】

図3は本発明のICの機能ブロック図を示しており、これは任意又は全てのIC 1−nを表すことができる。この例では、調節ブロックは2入力比較装置310を含んでいる。比較装置310の1入力は信号チャンネル120へ結合されている。比較装置310の他方の入力は別の信号源312へ結合されている。比較装置310は信号チャンネル120により与えられた信号と信号源312により与えられた信号を比較する。比較の結果は信号チャンネル120により送信された信号のレベルを調節するために使用されることができる。1実施形態では、信号チャンネル120により伝送された信号のレベルは比較装置310の2つの入力の高い方のレベルに調節されることができる。1実施形態では、信号チャンネル120により伝送された信号のレベルは比較装置310の2つの入力の低い方のレベルに調節されることができる。

【0010】

当業者は比較装置310が3以上の入力を含むことができ、信号チャンネル120により伝送された信号のレベルはこれらの入力の比較結果に基づいて調節されることができることを理解するであろう。当業者は比較装置310がプログラム可能な装置であることができ、比較に基づいている信号を出力するようにプログラムされることができ、出力信号のレベルは比較装置310の入力信号のいずれかのレベルとは異なる可能性があることを理解するであろう。1実施形態では、比較装置310は比較を行わず、何等の調節なしに信号チャンネル120上で信号を通過するようにゲートを通るフローとして作用するように選択的にプログラムされることができる。

【0011】

1実施形態では、比較装置310はマルチプレクサと置換されることができる。マルチプレクサは信号チャンネル120上の信号を含むその入力を多重化し、それらを別のチップまたはシステムコンポーネントへ送信することができる。1実施形態では、全てのIC 1−nのマルチプレクサにより多重化された全ての信号は目的地のICまたはシステムコンポーネントにより受信される。目的地のIC又はシステムコンポーネントはその後全ての信号を解析し、例えば最低の信号レベルおよび/または多重化された信号の最低の信号レベルを有する信号を決定する。

【0012】

図4は本発明の電気システムの例示的な応用のフローチャート400を示している。この明細書では、IC 1−nはLCDのバックライトシステム用のLEDのストリングを駆動するために使用される。各IC 1−nはLEDストリングの異なるセットを駆動する。各セットは例えば6個のLEDストリングを含むことができる。各IC 1−nはそれが制御している各LEDストリングを通って流れる電流を示すフィードバック信号を受信することができる。ブロック410で、IC 1は6個の信号(FB1)の最低レベルを有するフィードバック信号を駆動してそれをIC2へ送信する6個のLEDストリングに関する6個のフィードバック信号を比較する。ブロック420で、IC2はFB1をその6個のストリングから受信する6個のフィードバック信号の最低の信号と比較し、それらの2個の信号(FB2)の低いレベルを有する信号をIC3へ送る。ブロック430で、IC3はFB2をその6個のストリングから受信する6個のフィードバック信号の最低の信号と比較し、それらの2個の信号(FB3)の最低レベルを有する信号をIC4へ送る。ブロック440で、IC4はFB3をその6個のストリングから受信する6個のフィードバック信号の最低レベルの信号と比較し、それらの2個の信号(FB4)の低いレベルを有する信号をIC5(図示せず)に送る。ブロック450で、チェインの最後のICはチェイン中のその先行するIC(IC(n−1))から受信された信号とその6個のストリングから受信する6個のフィードバック信号の最低レベルの信号との最終的な比較を行う。システムの最低のLEDストリング駆動電流はしたがって決定される。

【0013】

本発明はアナログチャンネルが多数のチップと相互接続する特有で的確な技術を提供する。比較は、デイジーチェインの逐次的なチップのアナログ出力信号と、デイジーチェイン中の次のチップの出力と比較するために選択された2個の信号の高い方又は低い方との間で漸進的に行われることができる。このようにして、デイジーチェイン中の全てのチップにより発生される全ての出力信号の最終的に最高又は最低のものが決定される。当業者は前述の本発明の技術、構造、方法が例示であることを認識するであろう。本発明は、本発明の技術的範囲から逸脱せずに種々の実施形態で実行することができる。

【特許請求の範囲】

【請求項1】

複数の集積回路チップと、

アナログ信号を伝送するための電気チャンネルとを具備し、

前記電気チャンネルは前記複数の集積回路チップのそれぞれに結合され、各集積回路チップは前記アナログ信号のレベルを変更可能である電気システム。

【請求項2】

前記複数の集積回路チップの1つの集積回路チップは前記アナログ信号のレベルを変更するための比較装置を含んでいる請求項1記載の電気システム。

【請求項3】

前記比較装置はプログラム可能な比較装置を含んでいる請求項2記載の電気システム。

【請求項4】

前記比較装置は前記アナログ信号を別の信号と比較する請求項2記載の電気システム。

【請求項5】

前記比較装置の出力は前記比較に基づいている請求項4記載の電気システム。

【請求項6】

前記比較装置の出力は別の集積回路チップに送られる請求項5記載の電気システム。

【請求項7】

前記比較装置の出力は比較されている前記信号の低い方のレベルを有する信号を含んでいる請求項5記載の電気システム。

【請求項8】

前記比較装置の出力は比較されている信号の高い方のレベルを有する信号を含んでいる請求項5記載の電気システム。

【請求項9】

前記アナログ信号と前記別の信号は発光ダイオードのストリングを通って流れる電流を表している請求項4記載の電気システム。

【請求項10】

前記比較装置の出力は前記2つの信号の前記低い電流を表す信号を含んでいる請求項9記載の電気システム。

【請求項11】

複数の集積回路チップを含むバックライト回路と、

アナログ信号を伝送するための電気チャンネルとを具備し、

前記電気チャンネルは前記複数の集積回路チップのそれぞれに結合され、

各集積回路チップは前記アナログ信号のレベルを変更でき、

前記複数の集積回路チップは発光ダイオードの複数のストリングを駆動するためのものである液晶ディスプレイ。

【請求項12】

前記複数の集積回路チップの1つの前記集積回路チップは前記アナログ信号のレベルを変更するための比較装置を含んでいる請求項11記載の電気システム。

【請求項13】

前記比較装置はプログラム可能な比較装置を具備している請求項12記載の電気システム。

【請求項14】

前記比較装置は前記アナログ信号を別の信号と比較する請求項12記載の電気システム。

【請求項15】

前記比較装置の出力は前記比較に基づいている請求項14記載の電気システム。

【請求項16】

さらに、前記比較装置の出力は別の集積回路チップに伝送される請求項15記載の電気システム。

【請求項17】

前記比較装置の出力は比較されている前記信号の低い方のレベルを有する信号を含んでいる請求項15記載の電気システム。

【請求項18】

前記比較装置の出力は比較されている信号の高い方のレベルを有する信号を含んでいる請求項15記載の電気システム。

【請求項19】

前記アナログ信号と前記別の信号は発光ダイオードのストリングを通って流れる電流を表している請求項14記載の電気システム。

【請求項20】

アナログ信号を複数の集積回路チップへ送信するための電気チャンネルを結合し、

前記アナログ信号のレベルを変更するために各集積回路チップを構成するステップを含んでいる方法。

【請求項1】

複数の集積回路チップと、

アナログ信号を伝送するための電気チャンネルとを具備し、

前記電気チャンネルは前記複数の集積回路チップのそれぞれに結合され、各集積回路チップは前記アナログ信号のレベルを変更可能である電気システム。

【請求項2】

前記複数の集積回路チップの1つの集積回路チップは前記アナログ信号のレベルを変更するための比較装置を含んでいる請求項1記載の電気システム。

【請求項3】

前記比較装置はプログラム可能な比較装置を含んでいる請求項2記載の電気システム。

【請求項4】

前記比較装置は前記アナログ信号を別の信号と比較する請求項2記載の電気システム。

【請求項5】

前記比較装置の出力は前記比較に基づいている請求項4記載の電気システム。

【請求項6】

前記比較装置の出力は別の集積回路チップに送られる請求項5記載の電気システム。

【請求項7】

前記比較装置の出力は比較されている前記信号の低い方のレベルを有する信号を含んでいる請求項5記載の電気システム。

【請求項8】

前記比較装置の出力は比較されている信号の高い方のレベルを有する信号を含んでいる請求項5記載の電気システム。

【請求項9】

前記アナログ信号と前記別の信号は発光ダイオードのストリングを通って流れる電流を表している請求項4記載の電気システム。

【請求項10】

前記比較装置の出力は前記2つの信号の前記低い電流を表す信号を含んでいる請求項9記載の電気システム。

【請求項11】

複数の集積回路チップを含むバックライト回路と、

アナログ信号を伝送するための電気チャンネルとを具備し、

前記電気チャンネルは前記複数の集積回路チップのそれぞれに結合され、

各集積回路チップは前記アナログ信号のレベルを変更でき、

前記複数の集積回路チップは発光ダイオードの複数のストリングを駆動するためのものである液晶ディスプレイ。

【請求項12】

前記複数の集積回路チップの1つの前記集積回路チップは前記アナログ信号のレベルを変更するための比較装置を含んでいる請求項11記載の電気システム。

【請求項13】

前記比較装置はプログラム可能な比較装置を具備している請求項12記載の電気システム。

【請求項14】

前記比較装置は前記アナログ信号を別の信号と比較する請求項12記載の電気システム。

【請求項15】

前記比較装置の出力は前記比較に基づいている請求項14記載の電気システム。

【請求項16】

さらに、前記比較装置の出力は別の集積回路チップに伝送される請求項15記載の電気システム。

【請求項17】

前記比較装置の出力は比較されている前記信号の低い方のレベルを有する信号を含んでいる請求項15記載の電気システム。

【請求項18】

前記比較装置の出力は比較されている信号の高い方のレベルを有する信号を含んでいる請求項15記載の電気システム。

【請求項19】

前記アナログ信号と前記別の信号は発光ダイオードのストリングを通って流れる電流を表している請求項14記載の電気システム。

【請求項20】

アナログ信号を複数の集積回路チップへ送信するための電気チャンネルを結合し、

前記アナログ信号のレベルを変更するために各集積回路チップを構成するステップを含んでいる方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公表番号】特表2011−520134(P2011−520134A)

【公表日】平成23年7月14日(2011.7.14)

【国際特許分類】

【出願番号】特願2010−550742(P2010−550742)

【出願日】平成21年2月26日(2009.2.26)

【国際出願番号】PCT/US2009/035334

【国際公開番号】WO2009/114283

【国際公開日】平成21年9月17日(2009.9.17)

【出願人】(510246013)エムシリカ・インコーポレイテッド (1)

【Fターム(参考)】

【公表日】平成23年7月14日(2011.7.14)

【国際特許分類】

【出願日】平成21年2月26日(2009.2.26)

【国際出願番号】PCT/US2009/035334

【国際公開番号】WO2009/114283

【国際公開日】平成21年9月17日(2009.9.17)

【出願人】(510246013)エムシリカ・インコーポレイテッド (1)

【Fターム(参考)】

[ Back to top ]