チャージポンプ回路およびそれを用いた半導体装置

【課題】起動時の消費電流を小さく抑制できるチャージポンプ回路を提供する。

【解決手段】このチャージポンプ回路30では、ポンプ回路10の起動期間は分周クロック信号CLKDをポンプ回路10に与えてポンプ回路10の電流供給能力を低く設定し、起動期間の終了後はクロック信号CLKをポンプ回路10に与えてポンプ回路10の電流供給能力を高く設定する。したがって、起動期間はポンプ回路10の消費電流を小さく抑制し、起動期間の終了後はポンプ回路10の電流供給能力を高めることができる。

【解決手段】このチャージポンプ回路30では、ポンプ回路10の起動期間は分周クロック信号CLKDをポンプ回路10に与えてポンプ回路10の電流供給能力を低く設定し、起動期間の終了後はクロック信号CLKをポンプ回路10に与えてポンプ回路10の電流供給能力を高く設定する。したがって、起動期間はポンプ回路10の消費電流を小さく抑制し、起動期間の終了後はポンプ回路10の電流供給能力を高めることができる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明はチャージポンプ回路およびそれを用いた半導体装置に関し、特に、ポンプクロック信号によって駆動されて電流を供給するチャージポンプ回路と、それを用いた半導体装置に関する。

【背景技術】

【0002】

フラッシュメモリでは、プログラム動作時や消去動作時に高電圧が使用される。このため、フラッシュメモリには、電源電圧を昇圧して高電圧を生成するチャージポンプ回路が設けられている。このチャージポンプ回路の動作時には大きな電流が消費される。チャージポンプ回路の起動時には特に大きな電流が消費される。このため、フラッシュメモリを搭載したIC(Integrated Circuit)製品の消費電流の最大値は、チャージポンプ回路の起動時の消費電流値であることが多い。

【0003】

なお、特許文献1には、互いに周波数の異なる複数のクロック信号のうちのいずれかのクロック信号を選択するセレクタと、セレクタによって選択されたクロック信号によって駆動されるチャージポンプ回路とを備えた半導体装置が開示されている。この半導体装置では、電源投入時には最高周波数のクロック信号が選択され、昇圧時間の短縮化が図られる。

【0004】

また、特許文献2には、クロック信号を生成する発振回路と、チャージポンプ回路と、昇圧電圧が動作モードに応じた所定の電圧になるように発振回路の発振動作を制御するレベルセンス回路とを備えた昇圧回路が開示されている。

【0005】

また、特許文献3には、クロック制御信号に応じて昇圧用クロックを可変的に発生できるクロック発生回路と、昇圧用クロックを用いて昇圧した電圧を発生する昇圧回路と、昇圧回路の出力電圧に基づいてクロック制御信号を生成する電圧レベル検知回路とを備えた半導体装置が開示されている。この半導体装置では、電源投入時には高い周波数の昇圧クロックが生成され、昇圧時間の短縮化が図られる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−236657号公報

【特許文献2】特開2003−217291号公報

【特許文献3】特開平11−306781号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

フラッシュメモリを搭載したIC製品は様々な用途に使用されている。モバイル機器などの最大消費電流の制限が厳しい用途向けのIC製品では、チャージポンプ回路の起動時の消費電流が問題になる可能性がある。

【0008】

それゆえに、この発明の主たる目的は、起動時の消費電流を小さく抑制することが可能なチャージポンプ回路およびそれを用いた半導体装置を提供することである。

【課題を解決するための手段】

【0009】

この発明に係るチャージポンプ回路は、ポンプクロック信号によって駆動されて電源ノードに電流を供給するポンプ回路と、電源ノードの電圧を検出し、検出値が目標電圧に到達していない場合はポンプ回路を活性化させ、検出値が目標電圧に到達した場合はポンプ回路を非活性化させる検出回路と、ポンプ回路の起動期間はポンプ回路の電流供給能力を第1のレベルに設定し、起動期間の終了後はポンプ回路の電流供給能力を第1のレベルよりも高い第2のレベルに設定する制御回路とを備えたものである。

【発明の効果】

【0010】

この発明に係るチャージポンプ回路では、起動期間におけるポンプ回路の電流供給能力が、起動期間の終了後におけるポンプ回路の電流供給能力よりも低いレベルに設定される。したがって、起動期間の消費電流を小さく抑制することができる。

【図面の簡単な説明】

【0011】

【図1】本願発明の基礎となるマイコンチップの構成を示すブロック図である。

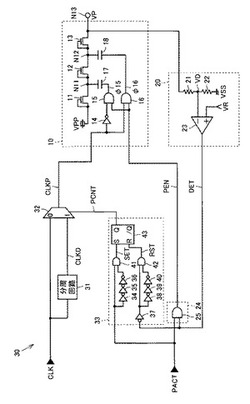

【図2】図1に示したチャージポンプ回路の構成を示す回路図である。

【図3】図2に示したチャージポンプ回路の動作を示すタイムチャートである。

【図4】この発明の実施の形態1によるチャージポンプ回路の構成を示す回路ブロック図である。

【図5】図4に示した分周回路の構成を示す回路ブロック図である。

【図6】図4に示したセレクタの構成を示す回路図である。

【図7】図4に示したチャージポンプ回路の動作を示すタイムチャートである。

【図8】この発明の実施の形態2によるチャージポンプ回路の構成を示す回路ブロック図である。

【図9】図8に示したチャージポンプ回路を備えたマイコンチップの構成を示すブロック図である。

【発明を実施するための形態】

【0012】

本願発明の実施の形態について説明する前に、まず本願発明の基礎となるマイコンチップ1について説明する。マイコンチップ1は、図1に示すように、四角形の半導体基板2を備える。半導体基板2の表面には、CPU(Central Processing Unit)コア3、フラッシュメモリ4、SRAM(Static Random Access Memory)6、周辺回路7、複数の信号入出力端子8、および電源端子9が設けられている。フラッシュメモリ4にはチャージポンプ回路(CP)5が設けられている。

【0013】

チャージポンプ回路5は、CPUコア3からポンプ起動信号PACTおよびクロック信号CLKを受けるとともに、外部から電源端子9を介して外部電源電圧VPPを受ける。チャージポンプ回路5は、ポンプ起動信号PACTに応答して活性化され、クロック信号CLKによって駆動され、外部電源電圧VPPを昇圧して高電圧VPを生成する。高電圧VPは、フラッシュメモリ4のプログラム動作時や消去動作時に使用される。

【0014】

このようなマイコンチップ1は様々な用途に使用される。モバイル機器などの最大消費電流の制限が厳しい用途向けのマイコンチップ1では、チャージポンプ回路5の起動開始時の消費電流が問題になる可能性がある。

【0015】

詳しく説明すると、チャージポンプ回路5は、図2に示すように、ポンプ回路10、レベル検出回路20、およびポンプ制御回路24を備える。ポンプ回路10は、複数(たとえば3個)のNチャネルMOSトランジスタ11〜13、インバータ14、ANDゲート15,16、およびキャパシタ17,18を含む。

【0016】

NチャネルMOSトランジスタ11〜13は、外部電源電圧VPPのラインと電源ノードN13との間に直列接続される。トランジスタ11〜13のゲートは、それぞれトランジスタ11〜13のドレインに接続される。すなわち、トランジスタ11〜13の各々はダイオード接続されている。

【0017】

クロック信号CLKは、インバータ14を介してANDゲート15の一方入力ノードに与えられるとともに、ANDゲート16の一方入力ノードに直接与えられる。ANDゲート15,16の他方入力ノードは、ともにポンプ活性化信号PENを受ける。ANDゲート15の出力信号φ15は、キャパシタ17を介してトランジスタ11のソース(ノードN11)に与えられる。ANDゲート16の出力信号φ16は、キャパシタ18を介してトランジスタ12のソース(ノードN12)に与えられる。

【0018】

ポンプ活性化信号PENが活性化レベルの「H」レベルである場合は、ANDゲート15の出力信号φ15はクロック信号CLKの反転信号/CLKとなり、ANDゲート16の出力信号φ16はクロック信号CLKとなる。信号φ15,φ16がそれぞれ「L」レベルおよび「H」レベルにされると、外部電源電圧VPPのラインからトランジスタ11を介してキャパシタ17に電流が流れ、キャパシタ17が充電される。また、キャパシタ18からトランジスタ13を介して電源ノードN13に電流が流れ、電源ノードN13の電圧が上昇する。

【0019】

信号φ15,φ16がそれぞれ「H」レベルおよび「L」レベルにされると、キャパシタ17からトランジスタ12を介してキャパシタ18に電流が流れ、キャパシタ18が充電される。したがって、クロック信号CLKが「L」レベルから「H」レベルに立ち上げられる毎に電源ノードN13に電流が供給され、電源ノードN13の電圧が上昇する。

【0020】

ポンプ活性化信号PENが非活性化レベルの「L」レベルである場合は、ANDゲート15,16の出力信号φ15,φ16はともに「L」レベルに固定され、ポンプ回路10は非活性化される。

【0021】

レベル検出回路20は、抵抗素子21,22およびコンパレータ23を含む。抵抗素子21,22は、電源ノードN13と接地電圧VSSのラインとの間に直列接続される。電源ノードN13の電圧VPは、抵抗素子21,22によって分圧されて電圧VDとなる。コンパレータ23は、電圧VDと参照電圧VRの高低を比較し、比較結果を示す信号DETを出力する。VD<VRである場合は検出信号DETが「H」レベルになり、VD>VRである場合は検出信号DETが「L」レベルになる。

【0022】

ポンプ制御回路24は、ANDゲート25を含み、ポンプ起動信号PACTと検出信号DETの論理積信号をポンプ活性化信号PENとして出力する。ポンプ制御回路24は、ポンプ起動信号PACTと検出信号DETの両方が「H」レベルである場合だけポンプ回路10を活性化させる。

【0023】

図3(a)〜(h)は、チャージポンプ回路5の動作を示すタイムチャートである。初期状態では、ポンプ起動信号PACTが非活性化レベルの「L」レベルにされており、ポンプ活性化信号PENが「L」レベルになっている。また、ポンプ活性化信号PENが「L」レベルであるので、ANDゲート15,16の出力信号φ15,φ16はともに「L」レベルに固定されており、ポンプ回路10は非活性化されている。またポンプ起動信号PACTが「L」レベルである場合は参照電圧VRが0Vにされており、コンパレータ23の出力信号である検出信号DETは「L」レベルになっている。

【0024】

ある時刻t0においてポンプ起動信号PACTが活性化レベルの「H」レベルに立ち上げられると、所定時間経過後の時刻t1において参照電圧VRが所定の電圧に立ち上げられ、検出信号DETが「H」レベルに立ち上げられる。これにより、ポンプ活性化信号PENが「H」レベルとなり、ANDゲート15の出力信号φ15がクロック信号CLKの反転信号/CLKになるとともに、ANDゲート16の出力信号φ16がクロック信号CLKとなる。

【0025】

信号φ15,φ16が交互に「L」レベルから「H」レベルに立ち上げられると、外部電源電圧VPPのラインからトランジスタ11〜13を介して電源ノードN13に電荷が転送され、電源ノードN13の電圧VPが上昇する。その後、時刻t7において昇圧電圧VPが目標電圧VTに到達すると、VD>VRとなって検出信号DETが「L」レベルになり、ポンプ活性化信号PENが「L」レベルになる。ポンプ活性化信号PENが「L」レベルになると、信号φ15,φ16がともに「L」レベルに固定されてポンプ回路10が非活性化され、電源ノードN13への電荷の供給が停止される。

【0026】

ポンプ回路10が非活性化されると、電源ノードN13の電圧VPが徐々に低下する。昇圧電圧VPが目標電圧VTよりも低下すると、VD<VRとなって検出信号DETが「H」レベルになり、ポンプ活性化信号PENが「H」レベルになる。ポンプ活性化信号PENが「H」レベルになると、ポンプ回路10が活性化されて電源ノードN13に電荷が供給される。このようにポンプ回路10の活性化と非活性化を繰り返すことにより、昇圧電圧VPが所定の目標電圧VTに維持される。

【0027】

このようなチャージポンプ回路5の電流供給能力は、所定のセットアップ時間内に昇圧電圧VPが目標電圧VTに到達することができ、かつ昇圧電圧VPが目標電圧VTに到達したときに要求される電流を供給することができるように設定される。チャージポンプ回路5の電流供給能力は、ポンプ回路10のキャパシタ17,18の容量値、クロック信号CLKの周波数などで決まる。チャージポンプ回路5の電流供給能力を大きくすると、当然のことながら、チャージポンプ回路5の消費電流も大きくなる。

【0028】

また、チャージポンプ回路5の電流供給能力は出力電圧VPに依存し、出力電圧VPが高くなるにつれて電流供給能力が低下する。チャージポンプ回路5を停止状態から起動させる場合、起動初期はチャージポンプ回路5の出力電圧VPは低いため供給電流は大きくなり、出力電圧VPが目標電圧VTに近づくにつれて供給電流は低下する。したがって、図3(h)に示すように、チャージポンプ回路5の消費電流IPは、起動初期に最も大きくなり、出力電圧VPが目標電圧VTに近づくにつれて低下する。

【0029】

一般にチャージポンプ回路5は消費電流が大きく、チャージポンプ回路5を使用するシステムの電源の電流容量が小さい場合、上記のチャージポンプ回路5の起動初期の消費電流IPの大きさが問題になる可能性がある。

【0030】

本願発明は、チャージポンプ回路の起動初期にチャージポンプ回路の電流供給能力を調整することにより、昇圧電圧VPが目標電圧VTに到達したときの電流供給能力を変えることなく、起動初期の消費電流を抑制するものである。

【0031】

[実施の形態1]

図4は、この発明の実施の形態1によるチャージポンプ回路30の構成を示す回路ブロック図であって、図2と対比される図である。図4を参照して、このチャージポンプ回路30が図2のチャージポンプ回路5と異なる点は、分周回路31、セレクタ32、およびポンプ能力制御回路33が追加されている点である。

【0032】

分周回路31は、クロック信号CLKを分周して、クロック信号CLKよりも低い周波数の分周クロック信号CLKDを生成する。分周回路31は、図5に示すように、Dフリップフロップ45およびインバータ46を含む。クロック信号CLKは、Dフリップフロップ45のクロック端子(CK)に与えられる。インバータ46は、Dフリップフロップ45の出力端子(Q)と入力端子(D)の間に接続される。Dフリップフロップ45の出力信号が分周クロック信号CLKDとなる。図5の分周回路31では、分周クロック信号CLKDの周波数は、クロック信号CLKの周波数の1/2倍になる。

【0033】

セレクタ32は、図6に示すように、インバータ50およびNANDゲート51〜53を含む。ポンプ能力制御信号PCNTは、インバータ50を介してNANDゲート51の一方入力ノードに与えられるとともに、NANDゲート52の一方入力ノードに直接与えられる。クロック信号CLKおよび分周クロック信号CLKDは、それぞれNANDゲート51,52の他方入力ノードに与えられる。NANDゲート53は、NANDゲート51,52の出力信号を受け、ポンプクロック信号CLKPを出力する。ポンプクロック信号CLKPは、ポンプ回路10のインバータ14およびNANDゲート16に与えられる。

【0034】

ポンプ能力制御信号PCNTが「L」レベルである場合は、NANDゲート52の出力信号が「H」レベルに固定され、NANDゲート51,53の各々がインバータとして動作し、クロック信号CLKがポンプクロック信号CLKPとして出力される。

【0035】

また、ポンプ能力制御信号PCNTが「H」レベルである場合は、NANDゲート51の出力信号が「H」レベルに固定され、NANDゲート52,53の各々がインバータとして動作し、分周クロック信号CLKDがポンプクロック信号CLKPとして出力される。

【0036】

ポンプ能力制御回路33は、図4に示すように、インバータ34〜40、ANDゲート41,42、およびRSフリップフロップ43を含む。インバータ34〜36およびANDゲート41は、パルス発生回路を構成し、ポンプ起動信号PACTの立ち上がりエッジに応答してワンショットパルス信号SETを出力する。インバータ37〜40およびANDゲート42は、パルス発生回路を構成し、検出信号DETの立ち下がりエッジに応答してワンショットパルス信号RSTを出力する。ワンショットパルス信号SET,RSTは、それぞれRSフリップフロップ43のセット端子(S)およびリセット端子(R)に与えられる。RSフリップフロップ43の出力信号がポンプ能力制御信号PCNTとなる。

【0037】

図7(a)〜(m)は、チャージポンプ回路30の起動時の動作を示すタイムチャートであって、図3(a)〜(h)と対比される図である。初期状態では、ポンプ起動信号PACTが非活性化レベルの「L」レベルにされており、ポンプ活性化信号PENが「L」レベルになっている。また、ポンプ活性化信号PENが「L」レベルであるので、ANDゲート15,16の出力信号φ15,φ16はともに「L」レベルに固定されており、ポンプ回路10は非活性化されている。

【0038】

また、RSフリップフロップ43はリセットされており、ポンプ能力制御信号PCNTは「L」レベルになっている。このため、クロック信号CLKがセレクタ32を通過してポンプクロック信号CLKPとなっている。またポンプ起動信号PACTが「L」レベルである場合は参照電圧VRが0Vにされており、コンパレータ23の出力信号である検出信号DETは「L」レベルになっている。

【0039】

ある時刻t0においてポンプ起動信号PACTが活性化レベルの「H」レベルに立ち上げられると、ワンショットパルス信号SETが生成されてRSフリップフロップ43がセットされ、ポンプ能力制御信号PCNTが「H」レベルにされる。これにより、分周クロック信号CLKDがセレクタ32を通過してポンプクロック信号CLKPとなる。

【0040】

時刻t0から所定時間経過後の時刻t1において参照電圧VRが所定の電圧に立ち上げられ、検出信号DETが「H」レベルに立ち上げられる。これにより、ポンプ活性化信号PENが「H」レベルとなり、ANDゲート15の出力信号φ15がポンプクロック信号CLKPの反転信号/CLKPになるとともに、ANDゲート16の出力信号φ16がポンプクロック信号CLKPとなる。

【0041】

信号φ15,φ16が交互に「L」レベルから「H」レベルに立ち上げられると、外部電源電圧VPPのラインからトランジスタ11〜13を介して電源ノードN13に電荷が転送され、電源ノードN13の電圧VPが上昇する。ポンプクロック信号CLKPは分周クロック信号CLKDであるので、図3の場合に比べ、昇圧電圧VPが目標電圧VTに到達するまでの期間が長くなる。

【0042】

時刻t7において昇圧電圧VPが目標電圧VTに到達すると、VD>VRとなって検出信号DETが「L」レベルになり、ポンプ活性化信号PENが「L」レベルになる。ポンプ活性化信号PENが「L」レベルになると、信号φ15,φ16がともに「L」レベルに固定されてポンプ回路10が非活性化され、電源ノードN13への電荷の供給が停止される。

【0043】

また、検出信号DETの立ち下がりエッジに応答してワンショットパルス信号RSTが生成され、RSフリップフロップ43がリセットされてポンプ能力制御信号PCNTが「L」レベルにされる。これにより、クロック信号CLKがセレクタ32を通過してポンプクロック信号CLKPとなる。

【0044】

ポンプ回路10が非活性化されると、電源ノードN13の電圧VPが徐々に低下する。昇圧電圧VPが目標電圧VTよりも低くなると、VD<VRとなって検出信号DETが「H」レベルになり、ポンプ活性化信号PENが「H」レベルになる。ポンプ活性化信号PENが「H」レベルになると、ポンプ回路10が活性化されて電源ノードN13に電荷が供給される。このようにポンプ回路10の活性化と非活性化を繰り返すことにより、昇圧電圧VPが所定の目標電圧VTに維持される。

【0045】

本実施の形態1のチャージポンプ回路30では、ポンプ起動信号PACTが活性化レベルの「H」レベルに立ち上げられてから検出信号DETが最初に「L」レベルに立ち下げられるまでの期間(t1〜t7)、すなわち、ポンプ回路10を起動させてから最初に昇圧電圧VPが目標電圧VTに到達するまでの期間、ポンプ回路10は分周クロック信号CLKDによって駆動される。したがって、ポンプ回路10が常にクロック信号CLKによって駆動されるチャージポンプ回路5に比べ、起動時におけるポンプ回路10の電流供給能力が小さくなり、消費電流IPが小さく抑制される。

【0046】

また、このチャージポンプ回路30では、昇圧電圧VPが目標電圧VTに到達した後(時刻t7以降)は、ポンプ回路10は通常のクロック信号CLKによって駆動される。したがって、昇圧電圧VPが目標電圧VTに到達した場合におけるポンプ回路10の電流供給能力はチャージポンプ回路5と変わらない。したがって、このチャージポンプ回路30では、昇圧電圧VPが目標電圧VTに到達した後におけるポンプ回路10の電流供給能力を変えることなく、起動時の消費電流を削減することができる。

【0047】

なお、この実施の形態1では、ポンプ回路10の電流供給能力を小さくする方法としてポンプ回路10の動作クロック周波数を遅くする方法を示したが、ポンプ回路の電流供給能力を小さくする方法はこれ以外にもあり、それらを適用しても同等の効果が得られる。

【0048】

[実施の形態2]

実施の形態1では、ポンプ回路10の起動時の電流供給能力を小さくすることにより消費電流を削減した。しかし、起動時の電流供給能力を小さくするとポンプ回路10の起動時間が長くなり、フラッシュメモリ4のプログラム動作、消去動作などの動作時間が長くなる。特に、高速動作を特徴とするIC製品においては、保証する動作時間のスペックを満たせなくなる可能性がある。この実施の形態2では、この問題の解決が図られる。

【0049】

図8は、この発明の実施の形態2によるチャージポンプ回路60の構成を示す回路ブロック図であって、図4と対比される図である。図8を参照して、このチャージポンプ回路60が図4のチャージポンプ回路30と異なる点は、ポンプ能力選択回路61が追加されている点である。

【0050】

ポンプ能力選択回路61は、ANDゲート62を含み、ポンプ能力選択信号PCNTENとポンプ能力制御信号PCNTの論理積信号をセレクタ32に与える。ポンプ能力選択信号PCNTENが「H」レベルである場合は、ポンプ能力制御信号PCNTがANDゲート62を通過してセレクタ32に与えられる。この場合、チャージポンプ回路60は、チャージポンプ回路30と同じ構成になる。また、ポンプ能力選択信号PCNTENが「L」レベルである場合は、「L」レベルの信号がセレクタ32に与えられ、クロック信号CLKがポンプクロック信号CLKPとなる。つまり、このチャージポンプ回路60では、ポンプ能力選択信号PCNTENの論理レベルによって、ポンプ回路10の能力調整を行なうか否かを選択することが可能となっている。

【0051】

IC製品の仕様において、消費電流の低減化よりも動作速度の高速化の要求が強いモードではポンプ能力選択信号PCNTENを非活性化レベルの「L」レベルにし、動作速度の高速化よりも消費電流の低減化の要求の強いモードではポンプ能力選択信号PCNTENを活性化レベルの「H」レベルにする。これにより、同一製品においても異なる要求を満足することが可能となる。

【0052】

図9は、チャージポンプ回路60を含むフラッシュメモリ4を搭載したマイコンチップ65の構成を示すブロック図である。マイコンチップ65の仕様に消費電流に関する動作モードを設け、そのモード設定によりCPUコア3からフラッシュメモリ4に入力されるポンプ能力選択信号PCNTENの論理レベルを内部で変更することにより、同一マイコンチップ65において、消費電流の低減化の要求と動作速度の高速化の要求のうちのいずれか一方の要求を選択的に満たすことが可能となる。

【0053】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0054】

1,65 マイコンチップ、2 半導体基板、3 CPUコア、4 フラッシュメモリ、5,30,60 チャージポンプ回路、6 SRAM、7 周辺回路、8 信号入出力端子、9 電源端子、10 ポンプ回路、11〜13 NチャネルMOSトランジスタ、14,34〜40,46,50 インバータ、15,16,25,41,42,62 ANDゲート、17,18 キャパシタ、20 レベル検出回路、21,22 抵抗素子、23 コンパレータ、24 ポンプ制御回路、31 分周回路、32 セレクタ、33 ポンプ能力制御回路、43 RSフリップフロップ、45 Dフリップフロップ、51〜53 NANDゲート、61 ポンプ能力選択回路。

【技術分野】

【0001】

この発明はチャージポンプ回路およびそれを用いた半導体装置に関し、特に、ポンプクロック信号によって駆動されて電流を供給するチャージポンプ回路と、それを用いた半導体装置に関する。

【背景技術】

【0002】

フラッシュメモリでは、プログラム動作時や消去動作時に高電圧が使用される。このため、フラッシュメモリには、電源電圧を昇圧して高電圧を生成するチャージポンプ回路が設けられている。このチャージポンプ回路の動作時には大きな電流が消費される。チャージポンプ回路の起動時には特に大きな電流が消費される。このため、フラッシュメモリを搭載したIC(Integrated Circuit)製品の消費電流の最大値は、チャージポンプ回路の起動時の消費電流値であることが多い。

【0003】

なお、特許文献1には、互いに周波数の異なる複数のクロック信号のうちのいずれかのクロック信号を選択するセレクタと、セレクタによって選択されたクロック信号によって駆動されるチャージポンプ回路とを備えた半導体装置が開示されている。この半導体装置では、電源投入時には最高周波数のクロック信号が選択され、昇圧時間の短縮化が図られる。

【0004】

また、特許文献2には、クロック信号を生成する発振回路と、チャージポンプ回路と、昇圧電圧が動作モードに応じた所定の電圧になるように発振回路の発振動作を制御するレベルセンス回路とを備えた昇圧回路が開示されている。

【0005】

また、特許文献3には、クロック制御信号に応じて昇圧用クロックを可変的に発生できるクロック発生回路と、昇圧用クロックを用いて昇圧した電圧を発生する昇圧回路と、昇圧回路の出力電圧に基づいてクロック制御信号を生成する電圧レベル検知回路とを備えた半導体装置が開示されている。この半導体装置では、電源投入時には高い周波数の昇圧クロックが生成され、昇圧時間の短縮化が図られる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−236657号公報

【特許文献2】特開2003−217291号公報

【特許文献3】特開平11−306781号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

フラッシュメモリを搭載したIC製品は様々な用途に使用されている。モバイル機器などの最大消費電流の制限が厳しい用途向けのIC製品では、チャージポンプ回路の起動時の消費電流が問題になる可能性がある。

【0008】

それゆえに、この発明の主たる目的は、起動時の消費電流を小さく抑制することが可能なチャージポンプ回路およびそれを用いた半導体装置を提供することである。

【課題を解決するための手段】

【0009】

この発明に係るチャージポンプ回路は、ポンプクロック信号によって駆動されて電源ノードに電流を供給するポンプ回路と、電源ノードの電圧を検出し、検出値が目標電圧に到達していない場合はポンプ回路を活性化させ、検出値が目標電圧に到達した場合はポンプ回路を非活性化させる検出回路と、ポンプ回路の起動期間はポンプ回路の電流供給能力を第1のレベルに設定し、起動期間の終了後はポンプ回路の電流供給能力を第1のレベルよりも高い第2のレベルに設定する制御回路とを備えたものである。

【発明の効果】

【0010】

この発明に係るチャージポンプ回路では、起動期間におけるポンプ回路の電流供給能力が、起動期間の終了後におけるポンプ回路の電流供給能力よりも低いレベルに設定される。したがって、起動期間の消費電流を小さく抑制することができる。

【図面の簡単な説明】

【0011】

【図1】本願発明の基礎となるマイコンチップの構成を示すブロック図である。

【図2】図1に示したチャージポンプ回路の構成を示す回路図である。

【図3】図2に示したチャージポンプ回路の動作を示すタイムチャートである。

【図4】この発明の実施の形態1によるチャージポンプ回路の構成を示す回路ブロック図である。

【図5】図4に示した分周回路の構成を示す回路ブロック図である。

【図6】図4に示したセレクタの構成を示す回路図である。

【図7】図4に示したチャージポンプ回路の動作を示すタイムチャートである。

【図8】この発明の実施の形態2によるチャージポンプ回路の構成を示す回路ブロック図である。

【図9】図8に示したチャージポンプ回路を備えたマイコンチップの構成を示すブロック図である。

【発明を実施するための形態】

【0012】

本願発明の実施の形態について説明する前に、まず本願発明の基礎となるマイコンチップ1について説明する。マイコンチップ1は、図1に示すように、四角形の半導体基板2を備える。半導体基板2の表面には、CPU(Central Processing Unit)コア3、フラッシュメモリ4、SRAM(Static Random Access Memory)6、周辺回路7、複数の信号入出力端子8、および電源端子9が設けられている。フラッシュメモリ4にはチャージポンプ回路(CP)5が設けられている。

【0013】

チャージポンプ回路5は、CPUコア3からポンプ起動信号PACTおよびクロック信号CLKを受けるとともに、外部から電源端子9を介して外部電源電圧VPPを受ける。チャージポンプ回路5は、ポンプ起動信号PACTに応答して活性化され、クロック信号CLKによって駆動され、外部電源電圧VPPを昇圧して高電圧VPを生成する。高電圧VPは、フラッシュメモリ4のプログラム動作時や消去動作時に使用される。

【0014】

このようなマイコンチップ1は様々な用途に使用される。モバイル機器などの最大消費電流の制限が厳しい用途向けのマイコンチップ1では、チャージポンプ回路5の起動開始時の消費電流が問題になる可能性がある。

【0015】

詳しく説明すると、チャージポンプ回路5は、図2に示すように、ポンプ回路10、レベル検出回路20、およびポンプ制御回路24を備える。ポンプ回路10は、複数(たとえば3個)のNチャネルMOSトランジスタ11〜13、インバータ14、ANDゲート15,16、およびキャパシタ17,18を含む。

【0016】

NチャネルMOSトランジスタ11〜13は、外部電源電圧VPPのラインと電源ノードN13との間に直列接続される。トランジスタ11〜13のゲートは、それぞれトランジスタ11〜13のドレインに接続される。すなわち、トランジスタ11〜13の各々はダイオード接続されている。

【0017】

クロック信号CLKは、インバータ14を介してANDゲート15の一方入力ノードに与えられるとともに、ANDゲート16の一方入力ノードに直接与えられる。ANDゲート15,16の他方入力ノードは、ともにポンプ活性化信号PENを受ける。ANDゲート15の出力信号φ15は、キャパシタ17を介してトランジスタ11のソース(ノードN11)に与えられる。ANDゲート16の出力信号φ16は、キャパシタ18を介してトランジスタ12のソース(ノードN12)に与えられる。

【0018】

ポンプ活性化信号PENが活性化レベルの「H」レベルである場合は、ANDゲート15の出力信号φ15はクロック信号CLKの反転信号/CLKとなり、ANDゲート16の出力信号φ16はクロック信号CLKとなる。信号φ15,φ16がそれぞれ「L」レベルおよび「H」レベルにされると、外部電源電圧VPPのラインからトランジスタ11を介してキャパシタ17に電流が流れ、キャパシタ17が充電される。また、キャパシタ18からトランジスタ13を介して電源ノードN13に電流が流れ、電源ノードN13の電圧が上昇する。

【0019】

信号φ15,φ16がそれぞれ「H」レベルおよび「L」レベルにされると、キャパシタ17からトランジスタ12を介してキャパシタ18に電流が流れ、キャパシタ18が充電される。したがって、クロック信号CLKが「L」レベルから「H」レベルに立ち上げられる毎に電源ノードN13に電流が供給され、電源ノードN13の電圧が上昇する。

【0020】

ポンプ活性化信号PENが非活性化レベルの「L」レベルである場合は、ANDゲート15,16の出力信号φ15,φ16はともに「L」レベルに固定され、ポンプ回路10は非活性化される。

【0021】

レベル検出回路20は、抵抗素子21,22およびコンパレータ23を含む。抵抗素子21,22は、電源ノードN13と接地電圧VSSのラインとの間に直列接続される。電源ノードN13の電圧VPは、抵抗素子21,22によって分圧されて電圧VDとなる。コンパレータ23は、電圧VDと参照電圧VRの高低を比較し、比較結果を示す信号DETを出力する。VD<VRである場合は検出信号DETが「H」レベルになり、VD>VRである場合は検出信号DETが「L」レベルになる。

【0022】

ポンプ制御回路24は、ANDゲート25を含み、ポンプ起動信号PACTと検出信号DETの論理積信号をポンプ活性化信号PENとして出力する。ポンプ制御回路24は、ポンプ起動信号PACTと検出信号DETの両方が「H」レベルである場合だけポンプ回路10を活性化させる。

【0023】

図3(a)〜(h)は、チャージポンプ回路5の動作を示すタイムチャートである。初期状態では、ポンプ起動信号PACTが非活性化レベルの「L」レベルにされており、ポンプ活性化信号PENが「L」レベルになっている。また、ポンプ活性化信号PENが「L」レベルであるので、ANDゲート15,16の出力信号φ15,φ16はともに「L」レベルに固定されており、ポンプ回路10は非活性化されている。またポンプ起動信号PACTが「L」レベルである場合は参照電圧VRが0Vにされており、コンパレータ23の出力信号である検出信号DETは「L」レベルになっている。

【0024】

ある時刻t0においてポンプ起動信号PACTが活性化レベルの「H」レベルに立ち上げられると、所定時間経過後の時刻t1において参照電圧VRが所定の電圧に立ち上げられ、検出信号DETが「H」レベルに立ち上げられる。これにより、ポンプ活性化信号PENが「H」レベルとなり、ANDゲート15の出力信号φ15がクロック信号CLKの反転信号/CLKになるとともに、ANDゲート16の出力信号φ16がクロック信号CLKとなる。

【0025】

信号φ15,φ16が交互に「L」レベルから「H」レベルに立ち上げられると、外部電源電圧VPPのラインからトランジスタ11〜13を介して電源ノードN13に電荷が転送され、電源ノードN13の電圧VPが上昇する。その後、時刻t7において昇圧電圧VPが目標電圧VTに到達すると、VD>VRとなって検出信号DETが「L」レベルになり、ポンプ活性化信号PENが「L」レベルになる。ポンプ活性化信号PENが「L」レベルになると、信号φ15,φ16がともに「L」レベルに固定されてポンプ回路10が非活性化され、電源ノードN13への電荷の供給が停止される。

【0026】

ポンプ回路10が非活性化されると、電源ノードN13の電圧VPが徐々に低下する。昇圧電圧VPが目標電圧VTよりも低下すると、VD<VRとなって検出信号DETが「H」レベルになり、ポンプ活性化信号PENが「H」レベルになる。ポンプ活性化信号PENが「H」レベルになると、ポンプ回路10が活性化されて電源ノードN13に電荷が供給される。このようにポンプ回路10の活性化と非活性化を繰り返すことにより、昇圧電圧VPが所定の目標電圧VTに維持される。

【0027】

このようなチャージポンプ回路5の電流供給能力は、所定のセットアップ時間内に昇圧電圧VPが目標電圧VTに到達することができ、かつ昇圧電圧VPが目標電圧VTに到達したときに要求される電流を供給することができるように設定される。チャージポンプ回路5の電流供給能力は、ポンプ回路10のキャパシタ17,18の容量値、クロック信号CLKの周波数などで決まる。チャージポンプ回路5の電流供給能力を大きくすると、当然のことながら、チャージポンプ回路5の消費電流も大きくなる。

【0028】

また、チャージポンプ回路5の電流供給能力は出力電圧VPに依存し、出力電圧VPが高くなるにつれて電流供給能力が低下する。チャージポンプ回路5を停止状態から起動させる場合、起動初期はチャージポンプ回路5の出力電圧VPは低いため供給電流は大きくなり、出力電圧VPが目標電圧VTに近づくにつれて供給電流は低下する。したがって、図3(h)に示すように、チャージポンプ回路5の消費電流IPは、起動初期に最も大きくなり、出力電圧VPが目標電圧VTに近づくにつれて低下する。

【0029】

一般にチャージポンプ回路5は消費電流が大きく、チャージポンプ回路5を使用するシステムの電源の電流容量が小さい場合、上記のチャージポンプ回路5の起動初期の消費電流IPの大きさが問題になる可能性がある。

【0030】

本願発明は、チャージポンプ回路の起動初期にチャージポンプ回路の電流供給能力を調整することにより、昇圧電圧VPが目標電圧VTに到達したときの電流供給能力を変えることなく、起動初期の消費電流を抑制するものである。

【0031】

[実施の形態1]

図4は、この発明の実施の形態1によるチャージポンプ回路30の構成を示す回路ブロック図であって、図2と対比される図である。図4を参照して、このチャージポンプ回路30が図2のチャージポンプ回路5と異なる点は、分周回路31、セレクタ32、およびポンプ能力制御回路33が追加されている点である。

【0032】

分周回路31は、クロック信号CLKを分周して、クロック信号CLKよりも低い周波数の分周クロック信号CLKDを生成する。分周回路31は、図5に示すように、Dフリップフロップ45およびインバータ46を含む。クロック信号CLKは、Dフリップフロップ45のクロック端子(CK)に与えられる。インバータ46は、Dフリップフロップ45の出力端子(Q)と入力端子(D)の間に接続される。Dフリップフロップ45の出力信号が分周クロック信号CLKDとなる。図5の分周回路31では、分周クロック信号CLKDの周波数は、クロック信号CLKの周波数の1/2倍になる。

【0033】

セレクタ32は、図6に示すように、インバータ50およびNANDゲート51〜53を含む。ポンプ能力制御信号PCNTは、インバータ50を介してNANDゲート51の一方入力ノードに与えられるとともに、NANDゲート52の一方入力ノードに直接与えられる。クロック信号CLKおよび分周クロック信号CLKDは、それぞれNANDゲート51,52の他方入力ノードに与えられる。NANDゲート53は、NANDゲート51,52の出力信号を受け、ポンプクロック信号CLKPを出力する。ポンプクロック信号CLKPは、ポンプ回路10のインバータ14およびNANDゲート16に与えられる。

【0034】

ポンプ能力制御信号PCNTが「L」レベルである場合は、NANDゲート52の出力信号が「H」レベルに固定され、NANDゲート51,53の各々がインバータとして動作し、クロック信号CLKがポンプクロック信号CLKPとして出力される。

【0035】

また、ポンプ能力制御信号PCNTが「H」レベルである場合は、NANDゲート51の出力信号が「H」レベルに固定され、NANDゲート52,53の各々がインバータとして動作し、分周クロック信号CLKDがポンプクロック信号CLKPとして出力される。

【0036】

ポンプ能力制御回路33は、図4に示すように、インバータ34〜40、ANDゲート41,42、およびRSフリップフロップ43を含む。インバータ34〜36およびANDゲート41は、パルス発生回路を構成し、ポンプ起動信号PACTの立ち上がりエッジに応答してワンショットパルス信号SETを出力する。インバータ37〜40およびANDゲート42は、パルス発生回路を構成し、検出信号DETの立ち下がりエッジに応答してワンショットパルス信号RSTを出力する。ワンショットパルス信号SET,RSTは、それぞれRSフリップフロップ43のセット端子(S)およびリセット端子(R)に与えられる。RSフリップフロップ43の出力信号がポンプ能力制御信号PCNTとなる。

【0037】

図7(a)〜(m)は、チャージポンプ回路30の起動時の動作を示すタイムチャートであって、図3(a)〜(h)と対比される図である。初期状態では、ポンプ起動信号PACTが非活性化レベルの「L」レベルにされており、ポンプ活性化信号PENが「L」レベルになっている。また、ポンプ活性化信号PENが「L」レベルであるので、ANDゲート15,16の出力信号φ15,φ16はともに「L」レベルに固定されており、ポンプ回路10は非活性化されている。

【0038】

また、RSフリップフロップ43はリセットされており、ポンプ能力制御信号PCNTは「L」レベルになっている。このため、クロック信号CLKがセレクタ32を通過してポンプクロック信号CLKPとなっている。またポンプ起動信号PACTが「L」レベルである場合は参照電圧VRが0Vにされており、コンパレータ23の出力信号である検出信号DETは「L」レベルになっている。

【0039】

ある時刻t0においてポンプ起動信号PACTが活性化レベルの「H」レベルに立ち上げられると、ワンショットパルス信号SETが生成されてRSフリップフロップ43がセットされ、ポンプ能力制御信号PCNTが「H」レベルにされる。これにより、分周クロック信号CLKDがセレクタ32を通過してポンプクロック信号CLKPとなる。

【0040】

時刻t0から所定時間経過後の時刻t1において参照電圧VRが所定の電圧に立ち上げられ、検出信号DETが「H」レベルに立ち上げられる。これにより、ポンプ活性化信号PENが「H」レベルとなり、ANDゲート15の出力信号φ15がポンプクロック信号CLKPの反転信号/CLKPになるとともに、ANDゲート16の出力信号φ16がポンプクロック信号CLKPとなる。

【0041】

信号φ15,φ16が交互に「L」レベルから「H」レベルに立ち上げられると、外部電源電圧VPPのラインからトランジスタ11〜13を介して電源ノードN13に電荷が転送され、電源ノードN13の電圧VPが上昇する。ポンプクロック信号CLKPは分周クロック信号CLKDであるので、図3の場合に比べ、昇圧電圧VPが目標電圧VTに到達するまでの期間が長くなる。

【0042】

時刻t7において昇圧電圧VPが目標電圧VTに到達すると、VD>VRとなって検出信号DETが「L」レベルになり、ポンプ活性化信号PENが「L」レベルになる。ポンプ活性化信号PENが「L」レベルになると、信号φ15,φ16がともに「L」レベルに固定されてポンプ回路10が非活性化され、電源ノードN13への電荷の供給が停止される。

【0043】

また、検出信号DETの立ち下がりエッジに応答してワンショットパルス信号RSTが生成され、RSフリップフロップ43がリセットされてポンプ能力制御信号PCNTが「L」レベルにされる。これにより、クロック信号CLKがセレクタ32を通過してポンプクロック信号CLKPとなる。

【0044】

ポンプ回路10が非活性化されると、電源ノードN13の電圧VPが徐々に低下する。昇圧電圧VPが目標電圧VTよりも低くなると、VD<VRとなって検出信号DETが「H」レベルになり、ポンプ活性化信号PENが「H」レベルになる。ポンプ活性化信号PENが「H」レベルになると、ポンプ回路10が活性化されて電源ノードN13に電荷が供給される。このようにポンプ回路10の活性化と非活性化を繰り返すことにより、昇圧電圧VPが所定の目標電圧VTに維持される。

【0045】

本実施の形態1のチャージポンプ回路30では、ポンプ起動信号PACTが活性化レベルの「H」レベルに立ち上げられてから検出信号DETが最初に「L」レベルに立ち下げられるまでの期間(t1〜t7)、すなわち、ポンプ回路10を起動させてから最初に昇圧電圧VPが目標電圧VTに到達するまでの期間、ポンプ回路10は分周クロック信号CLKDによって駆動される。したがって、ポンプ回路10が常にクロック信号CLKによって駆動されるチャージポンプ回路5に比べ、起動時におけるポンプ回路10の電流供給能力が小さくなり、消費電流IPが小さく抑制される。

【0046】

また、このチャージポンプ回路30では、昇圧電圧VPが目標電圧VTに到達した後(時刻t7以降)は、ポンプ回路10は通常のクロック信号CLKによって駆動される。したがって、昇圧電圧VPが目標電圧VTに到達した場合におけるポンプ回路10の電流供給能力はチャージポンプ回路5と変わらない。したがって、このチャージポンプ回路30では、昇圧電圧VPが目標電圧VTに到達した後におけるポンプ回路10の電流供給能力を変えることなく、起動時の消費電流を削減することができる。

【0047】

なお、この実施の形態1では、ポンプ回路10の電流供給能力を小さくする方法としてポンプ回路10の動作クロック周波数を遅くする方法を示したが、ポンプ回路の電流供給能力を小さくする方法はこれ以外にもあり、それらを適用しても同等の効果が得られる。

【0048】

[実施の形態2]

実施の形態1では、ポンプ回路10の起動時の電流供給能力を小さくすることにより消費電流を削減した。しかし、起動時の電流供給能力を小さくするとポンプ回路10の起動時間が長くなり、フラッシュメモリ4のプログラム動作、消去動作などの動作時間が長くなる。特に、高速動作を特徴とするIC製品においては、保証する動作時間のスペックを満たせなくなる可能性がある。この実施の形態2では、この問題の解決が図られる。

【0049】

図8は、この発明の実施の形態2によるチャージポンプ回路60の構成を示す回路ブロック図であって、図4と対比される図である。図8を参照して、このチャージポンプ回路60が図4のチャージポンプ回路30と異なる点は、ポンプ能力選択回路61が追加されている点である。

【0050】

ポンプ能力選択回路61は、ANDゲート62を含み、ポンプ能力選択信号PCNTENとポンプ能力制御信号PCNTの論理積信号をセレクタ32に与える。ポンプ能力選択信号PCNTENが「H」レベルである場合は、ポンプ能力制御信号PCNTがANDゲート62を通過してセレクタ32に与えられる。この場合、チャージポンプ回路60は、チャージポンプ回路30と同じ構成になる。また、ポンプ能力選択信号PCNTENが「L」レベルである場合は、「L」レベルの信号がセレクタ32に与えられ、クロック信号CLKがポンプクロック信号CLKPとなる。つまり、このチャージポンプ回路60では、ポンプ能力選択信号PCNTENの論理レベルによって、ポンプ回路10の能力調整を行なうか否かを選択することが可能となっている。

【0051】

IC製品の仕様において、消費電流の低減化よりも動作速度の高速化の要求が強いモードではポンプ能力選択信号PCNTENを非活性化レベルの「L」レベルにし、動作速度の高速化よりも消費電流の低減化の要求の強いモードではポンプ能力選択信号PCNTENを活性化レベルの「H」レベルにする。これにより、同一製品においても異なる要求を満足することが可能となる。

【0052】

図9は、チャージポンプ回路60を含むフラッシュメモリ4を搭載したマイコンチップ65の構成を示すブロック図である。マイコンチップ65の仕様に消費電流に関する動作モードを設け、そのモード設定によりCPUコア3からフラッシュメモリ4に入力されるポンプ能力選択信号PCNTENの論理レベルを内部で変更することにより、同一マイコンチップ65において、消費電流の低減化の要求と動作速度の高速化の要求のうちのいずれか一方の要求を選択的に満たすことが可能となる。

【0053】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0054】

1,65 マイコンチップ、2 半導体基板、3 CPUコア、4 フラッシュメモリ、5,30,60 チャージポンプ回路、6 SRAM、7 周辺回路、8 信号入出力端子、9 電源端子、10 ポンプ回路、11〜13 NチャネルMOSトランジスタ、14,34〜40,46,50 インバータ、15,16,25,41,42,62 ANDゲート、17,18 キャパシタ、20 レベル検出回路、21,22 抵抗素子、23 コンパレータ、24 ポンプ制御回路、31 分周回路、32 セレクタ、33 ポンプ能力制御回路、43 RSフリップフロップ、45 Dフリップフロップ、51〜53 NANDゲート、61 ポンプ能力選択回路。

【特許請求の範囲】

【請求項1】

ポンプクロック信号によって駆動されて電源ノードに電流を供給するポンプ回路と、

前記電源ノードの電圧を検出し、検出値が目標電圧に到達していない場合は前記ポンプ回路を活性化させ、検出値が前記目標電圧に到達した場合は前記ポンプ回路を非活性化させる検出回路と、

前記ポンプ回路の起動期間は前記ポンプ回路の電流供給能力を第1のレベルに設定し、前記起動期間の終了後は前記ポンプ回路の電流供給能力を前記第1のレベルよりも高い第2のレベルに設定する制御回路とを備える、チャージポンプ回路。

【請求項2】

前記制御回路は、

クロック信号を分周する分周回路と、

前記起動期間は前記分周回路の出力信号を前記ポンプクロック信号として出力し、前記起動期間の終了後は前記クロック信号を前記ポンプクロック信号として出力するセレクタとを含む、請求項1に記載のチャージポンプ回路。

【請求項3】

前記起動期間は、前記ポンプ回路の起動が指示されてから前記検出回路によって前記電源ノードの電圧が前記目標電圧に到達したことが最初に検出されるまでの期間である、請求項1または請求項2に記載のチャージポンプ回路。

【請求項4】

前記制御回路は、選択信号が活性化レベルである場合は前記起動期間と前記起動期間の終了後で前記ポンプ回路の電流供給能力を切換え、前記選択信号が非活性化レベルである場合は前記ポンプ回路の電流供給能力を前記第2のレベルに固定する、請求項1から請求項3までのいずれかに記載のチャージポンプ回路。

【請求項5】

請求項4に記載のチャージポンプ回路と、

消費電流の低減化が要求される第1のモードでは前記選択信号を活性化レベルにし、動作速度の高速化が要求される第2のモードでは前記選択信号を非活性化レベルにする信号発生回路とを備える、半導体装置。

【請求項1】

ポンプクロック信号によって駆動されて電源ノードに電流を供給するポンプ回路と、

前記電源ノードの電圧を検出し、検出値が目標電圧に到達していない場合は前記ポンプ回路を活性化させ、検出値が前記目標電圧に到達した場合は前記ポンプ回路を非活性化させる検出回路と、

前記ポンプ回路の起動期間は前記ポンプ回路の電流供給能力を第1のレベルに設定し、前記起動期間の終了後は前記ポンプ回路の電流供給能力を前記第1のレベルよりも高い第2のレベルに設定する制御回路とを備える、チャージポンプ回路。

【請求項2】

前記制御回路は、

クロック信号を分周する分周回路と、

前記起動期間は前記分周回路の出力信号を前記ポンプクロック信号として出力し、前記起動期間の終了後は前記クロック信号を前記ポンプクロック信号として出力するセレクタとを含む、請求項1に記載のチャージポンプ回路。

【請求項3】

前記起動期間は、前記ポンプ回路の起動が指示されてから前記検出回路によって前記電源ノードの電圧が前記目標電圧に到達したことが最初に検出されるまでの期間である、請求項1または請求項2に記載のチャージポンプ回路。

【請求項4】

前記制御回路は、選択信号が活性化レベルである場合は前記起動期間と前記起動期間の終了後で前記ポンプ回路の電流供給能力を切換え、前記選択信号が非活性化レベルである場合は前記ポンプ回路の電流供給能力を前記第2のレベルに固定する、請求項1から請求項3までのいずれかに記載のチャージポンプ回路。

【請求項5】

請求項4に記載のチャージポンプ回路と、

消費電流の低減化が要求される第1のモードでは前記選択信号を活性化レベルにし、動作速度の高速化が要求される第2のモードでは前記選択信号を非活性化レベルにする信号発生回路とを備える、半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−106463(P2013−106463A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249682(P2011−249682)

【出願日】平成23年11月15日(2011.11.15)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]