チャージポンプ回路及びこれを用いた電源装置

【課題】容易にかつ適切にFETのオン/オフ制御を行う。

【解決手段】チャージポンプ回路1は、キャパシタC1の充放電用スイッチとして用いられるFET103(104)と、FET103(104)に流れる電流またはFET103(104)の両端電圧に応じて検出信号S11(S12)を生成する検出部109(110)と、検出信号S11(S12)に応じてFET103(104)の駆動信号G11(G12)を生成する駆動部107(108)と、を有する。

【解決手段】チャージポンプ回路1は、キャパシタC1の充放電用スイッチとして用いられるFET103(104)と、FET103(104)に流れる電流またはFET103(104)の両端電圧に応じて検出信号S11(S12)を生成する検出部109(110)と、検出信号S11(S12)に応じてFET103(104)の駆動信号G11(G12)を生成する駆動部107(108)と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、チャージポンプ回路及びこれを用いた電源装置に関するものである。

【背景技術】

【0002】

チャージポンプ回路は、電圧の正昇圧や負昇圧(反転)が可能であり、主に電流供給能力が必要のない場面で使用される。一般的なチャージポンプ回路では、フライングキャパシタの充放電用スイッチとしてダイオードが用いられる。ただし、ダイオードは順方向降下電圧が大きいので、出力電圧範囲が狭くなる。そのため、出力電圧範囲を広げる必要がある場合には、順方向降下電圧の大きいダイオードに代えて、より降下電圧の小さいFET[field effect transistor]を用いた同期整流方式が採用されていた。

【0003】

なお、本発明に関連する従来技術の一例としては、特許文献1を挙げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第2008/065941号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

同期整流方式のチャージポンプ回路では、複数設けられたFETのうち、同時にオンすべきでないFETが同時にオンしてしまうと、誤動作や効率低下を生じるおそれがある。そのため、適切にFETのオン/オフ制御を行うことが重要である。しかしながら、回路定数(特にフライングキャパシタの容量値)や素子レイアウト等を考慮して、FETのオン/オフ制御を最適化することは困難であった。

【0006】

本発明は、本願の発明者らにより見出された上記の問題点に鑑み、容易にかつ適切にFETのオン/オフ制御を行うことが可能なチャージポンプ回路、及び、これを用いた電源装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明に係るチャージポンプ回路は、キャパシタの充放電用スイッチとして用いられるFETと、前記FETに流れる電流または前記FETの両端電圧に応じて検出信号を生成する検出部と、前記検出信号に応じて前記FETの駆動信号を生成する駆動部と、を有する構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成るチャージポンプ回路は、前記キャパシタの第1端と第1電圧の印加端との間に接続された第1FETと、前記キャパシタの第1端と接地電圧の印加端との間に接続された第2FETと、前記キャパシタの第2端と第2電圧の印加端との間に接続された第3FETと、前記キャパシタの第2端と出力電圧の印加端との間に接続された第4FETと、クロック信号を生成するオシレータと、前記クロック信号に応じて前記第1FETと前記第2FETの駆動信号を生成する第1駆動部と、前記第3FETに流れる電流または前記第3FETの両端電圧に応じて第1検出信号を生成する第1検出部と、前記第4FETに流れる電流または前記第4FETの両端電圧に応じて第2検出信号を生成する第2検出部と、前記第1検出信号に応じて前記第3FETの駆動信号を生成する第2駆動部と、前記第2検出信号に応じて前記第4FETの駆動信号を生成する第3駆動部と、を有する構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成るチャージポンプ回路において、前記第2駆動部は、前記第1検出信号と前記クロック信号の双方に応じて前記第3FETの駆動信号を生成し、前記第3駆動部は、前記第2検出信号と前記クロック信号の双方に応じて前記第4FETの駆動信号を生成する構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成るチャージポンプ回路は、前記第3FETの駆動信号に応じて第1オフ検出信号を生成する第1オフ検出部と、前記第4FETの駆動信号に応じて第2オフ検出信号を生成する第2オフ検出部と、前記第1オフ検出信号と前記第2オフ検出信号に応じて前記クロック信号に遅延を与える遅延部と、を有する構成(第4の構成)にするとよい。

【0011】

また、上記第2〜第4いずれかの構成から成るチャージポンプ回路において、前記第1電圧と前記第2電圧は、いずれも正電圧である構成(第5の構成)にするとよい。

【0012】

また、上記第5の構成から成るチャージポンプ回路において、前記第1FET、前記第3FET、及び、前記第4FETはいずれもPチャネル型であり、前記第2FETはNチャネル型である構成(第6の構成)にするとよい。

【0013】

また、上記第2〜第4いずれかの構成から成るチャージポンプ回路において、前記第1電圧は正電圧であり、前記第2電圧は負電圧である構成(第7の構成)にするとよい。

【0014】

また、上記第7の構成から成るチャージポンプ回路において、前記第1FETはPチャネル型であり、前記第2FET、前記第3FET、及び、前記第4FETはいずれもNチャネル型である構成(第8の構成)にするとよい。

【0015】

また、上記第8の構成から成るチャージポンプ回路において、前記第1FETと、前記第2FETと、前記第1駆動部と、前記オシレータは、基板に接地電圧が印加された第1半導体装置に集積化されており、前記第3FETと、前記第4FETと、前記第1検出部と、前記第2検出部と、前記第2駆動部と、前記第3駆動部は、基板に負電圧が印加された第2半導体装置に集積化されている構成(第9の構成)にするとよい。

【0016】

また、本発明に係る電源装置は、上記第1〜第9いずれかの構成から成るチャージポンプ回路を有する構成(第10の構成)とされている。

【発明の効果】

【0017】

本発明によれば、容易にかつ適切にFETのオン/オフ制御を行うことが可能なチャージポンプ回路、及び、これを用いた電源装置を提供することができる。

【図面の簡単な説明】

【0018】

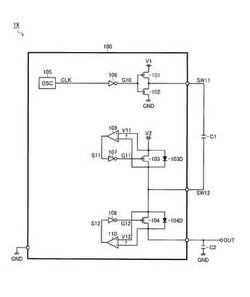

【図1】チャージポンプ回路の第1実施形態(正出力型)を示す図

【図2】チャージポンプ回路1Xの一動作例を示すタイミングチャート

【図3】チャージポンプ回路の第2実施形態(正出力型)を示す図

【図4】チャージポンプ回路1Yの一動作例を示すタイミングチャート

【図5】チャージポンプ回路の第3実施形態(正出力型)を示す図

【図6】チャージポンプ回路1Zの一動作例を示すタイミングチャート

【図7】チャージポンプ回路の第4実施形態(負出力型)を示す図

【図8】チャージポンプ回路2Xの一動作例を示すタイミングチャート

【図9】チャージポンプ回路の第5実施形態(負出力型)を示す図

【図10】チャージポンプ回路2Yの一動作例を示すタイミングチャート

【図11】チャージポンプ回路の第6実施形態(負出力型)を示す図

【図12】チャージポンプ回路2Zの一動作例を示すタイミングチャート

【発明を実施するための形態】

【0019】

<第1実施形態>

図1は、チャージポンプ回路の第1実施形態(正出力型)を示す図である。第1実施形態のチャージポンプ回路1Xは、半導体装置100と、フライングキャパシタC1と、出力キャパシタC2を有する。なお、チャージポンプ回路1Xを用いた電源装置は、LCD−TV、PDP−TV、DVDレコーダ、BDレコーダなど、様々なアプリケーションの電源として利用することが可能である。

【0020】

半導体装置100には、PMOSFET[P channel type metal oxide semiconductor field effect transitor]101と、NMOSFET[N channel type MOSFET]102と、PMOSFET103及び104と、オシレータ105と、インバータ106〜108と、コンパレータ109及び110と、が集積化されている。半導体装置100の基板には、接地電圧GND(=0V)が印加されている。

【0021】

FET101のソースは、正電圧V1(>0V)の印加端に接続されている。FET101及び102の各ドレインは、いずれもフライングキャパシタC1の第1端(スイッチ電圧SW11の印加端)に接続されている。FET102のソースは、接地電圧GNDの印加端に接続されている。FET101及び102の各ゲートは、いずれもインバータ106の出力端(駆動信号G10の印加端)に接続されている。インバータ106の入力端は、オシレータ105の出力端(クロック信号CLKの印加端)に接続されている。

【0022】

FET103のドレインは、正電圧V2(>0V)の印加端に接続されている。FET103のソースとFET104のドレインは、いずれもフライングキャパシタC1の第2端(スイッチ電圧SW12の印加端)に接続されている。FET104のソースは、出力電圧OUTの印加端に接続されている。FET103及び104には、各々のドレインをアノードとし、各々のソースをカソードとするボディダイオード103D及び104Dが付随する。出力電圧OUTの印加端と接地電圧GNDの印加端との間には、出力キャパシタC2が接続されている。

【0023】

コンパレータ109の非反転入力端(+)は、FET103のドレインに接続されている。一方、コンパレータ109の反転入力端(−)は、FET103のソースに接続されている。コンパレータ109の出力端(検出信号S11の印加端)は、インバータ107の入力端に接続されている。インバータ107の出力端(駆動信号G11の印加端)は、FET103のゲートに接続されている。

【0024】

コンパレータ110の非反転入力端(+)は、FET104のドレインに接続されている。一方、コンパレータ110の反転入力端(−)は、FET104のソースに接続されている。コンパレータ110の出力端(検出信号S12の印加端)は、インバータ108の入力端に接続されている。インバータ108の出力端(駆動信号G12の印加端)は、FET104のゲートに接続されている。

【0025】

FET101〜104は、いずれもフライングキャパシタC1の充放電用スイッチとして用いられる。FET101は、フライングキャパシタC1の第1端と正電圧V1の印加端との間に接続された第1FETに相当する。FET102は、フライングキャパシタC1の第1端と接地電圧GNDの印加端との間に接続された第2FETに相当する。FET103は、フライングキャパシタC1の第2端と正電圧V2の印加端との間に接続された第3FETに相当する。FET104は、フライングキャパシタC1の第2端と出力電圧OUTの印加端との間に接続された第4FETに相当する。

【0026】

オシレータ105は、一定周波数のクロック信号CLKを生成する。

【0027】

インバータ106は、クロック信号CLKに応じてFET101及び102の駆動信号G10を生成する第1駆動部に相当する。駆動信号G10は、クロック信号CLKの論理反転信号となる。

【0028】

インバータ107は、コンパレータ109から入力される検出信号S11に応じてFET103の駆動信号G11を生成する第2駆動部に相当する。駆動信号G11は、検出信号S11の論理反転信号となる。

【0029】

インバータ108は、コンパレータ110から入力される検出信号S12に応じてFET104の駆動信号G12を生成する第3駆動部に相当する。駆動信号G12は、検出信号S12の論理反転信号となる。

【0030】

コンパレータ109は、FET103の両端電圧V11(=V2−SW12)に応じて検出信号S11を生成する第1検出部に相当する。検出信号S11は、FET103の両端電圧V11が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S11は、正電圧V2の印加端からスイッチ電圧SW12の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、スイッチ電圧SW12の印加端から正電圧V2の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET103またはボディダイオード103Dを介して流れる電流の向きを検出する手法は、FET103の両端電圧V11を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0031】

コンパレータ110は、FET104の両端電圧V12(=SW12−OUT)に応じて検出信号S12を生成する第2検出部に相当する。検出信号S12は、FET104の両端電圧V12が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S12は、スイッチ電圧SW12の印加端から出力電圧OUTの印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、出力電圧OUTの印加端からスイッチ電圧SW12の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET104またはボディダイオード104Dを介して流れる電流の向きを検出する手法は、FET104の両端電圧V12を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0032】

まず、チャージポンプ回路1Xの基本動作について概略的に説明する。FET101及び104がオフとなり、FET102及び103がオンとなる第1フェイズ(充電フェイズ)では、正電圧V2の印加端から、FET103、フライングキャパシタC1、及び、FET102を介して、接地電圧GNDの印加端に至る経路を流れる電流によって、フライングキャパシタC1の充電が行われる。このとき、スイッチ電圧SW11は、ほぼ接地電圧GND(より正確には、接地電圧GNDにFET102の降下電圧を足し合わせた電圧)となり、スイッチ電圧SW12は、ほぼ正電圧V2(より正確には、正電圧V2からFET103の降下電圧を差し引いた電圧)となる。従って、フライングキャパシタC1には、スイッチ電圧SW11とスイッチ電圧SW12との差分電圧(ほぼ正電圧V2)に相当する電荷が蓄えられる。

【0033】

その後、FET101及び104がオンとなり、FET102及び103がオフとなる第2フェイズ(放電フェイズ/電荷転送フェイズ)では、正電圧V1の印加端から、FET101、フライングキャパシタC1、及び、FET104を介して、出力電圧OUTの印加端に至る経路が導通されて、フライングキャパシタC1の放電(出力キャパシタC2への電荷転送)が行われる。このとき、スイッチ電圧SW11は、ほぼ正電圧V1(より正確には、正電圧V1にFET101の降下電圧を足し合わせた電圧)となり、スイッチ電圧SW12は、スイッチ電圧SW11にフライングキャパシタC1の両端電圧を足し合わせた電圧(ほぼV1+V2)となる。

【0034】

従って、チャージポンプ回路1Xでは、FET101〜104をオン/オフさせてフライングキャパシタC1の充放電を繰り返すことにより、正電圧V1及びV2を足し合わせた正の出力電圧OUT(=V1+V2)を生成することができる。

【0035】

次に、FET101〜104のオン/オフ制御について詳細に説明する。図2は、チャージポンプ回路1Xの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G10、スイッチ電圧SW11及びSW12、検出信号S11及びS12、並びに、駆動信号G11及びG12が描写されている。

【0036】

図2の例では、時刻t11まで、FET101及び104がオンされており、FET102及び103がオフされている。この状態は先述の第2フェイズに相当し、スイッチ電圧SW12の印加端からFET104を介する経路で出力電圧OUTの印加端に向けた電流が流れている。このとき、スイッチ電圧SW12は、出力電圧OUTにFET104の降下電圧を足し合わせた電圧となっている。

【0037】

時刻t11において、クロック信号CLKがハイレベルからローレベルに立ち下がると駆動信号G10がローレベルからハイレベルに立ち上がるので、FET101がオフし、FET102がオンする。その結果、フライングキャパシタC1の第1端がFET102を介して接地電圧GNDの印加端に導通されるので、スイッチ電圧SW11が低下し始める。また、スイッチ電圧SW12についても、フライングキャパシタC1の電荷保存則に従い、スイッチ電圧SW11と同様の挙動で低下し始める。

【0038】

スイッチ電圧SW12の低下に伴い、時刻t12において、FET104の両端電圧V12(=SW12−OUT)がコンパレータ110の閾値電圧を下回ると、検出信号S12がハイレベルからローレベルに切り替わる。すなわち、出力電圧OUTの印加端からFET104を介する経路でスイッチ電圧SW12の印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S12がハイレベルからローレベルに切り替わる。その結果、FET104の駆動信号G12がローレベルからハイレベルに切り替わり、FET104がオフとなる。従って、FET104に流れる逆流電流を遅滞なく遮断することができる。

【0039】

スイッチ電圧SW12がさらに低下し、時刻t13において、FET103の両端電圧V11(=V2−SW12)がコンパレータ109の閾値電圧を上回ると、検出信号S11がローレベルからハイレベルに切り替わる。すなわち、正電圧V2の印加端からボディダイオード103Dを介する経路でスイッチ電圧SW12の印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S11がローレベルからハイレベルに切り替わる。その結果、FET103の駆動信号G11がハイレベルからローレベルに切り替わり、FET103がオンとなる。この状態は先述の第1フェイズに相当し、正電圧V2の印加端から、FET103、フライングキャパシタC1、及び、FET102を介して、接地電圧GNDの印加端に至る経路で電流が流れ始める。このとき、スイッチ電圧SW12は、正電圧V2からFET103の降下電圧を差し引いた電圧となる。

【0040】

なお、FET103が十分にオンするまでの間、FET103よりも順方向電圧の大きいボディダイオード103Dを介して電流が流れるので、スイッチ電圧SW12(及びSW11)にはアンダーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路1Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0041】

その後、時刻t14において、クロック信号CLKがローレベルからハイレベルに立ち上がると駆動信号G10がハイレベルからローレベルに立ち下がるので、FET101がオンし、FET102がオフする。その結果、フライングキャパシタC1の第1端がFET101を介して正電圧V1の印加端に導通されるので、スイッチ電圧SW11が上昇し始める。また、スイッチ電圧SW12についても、フライングキャパシタC1の電荷保存則に従い、スイッチ電圧SW11と同様の挙動で上昇し始める。

【0042】

スイッチ電圧SW12の上昇に伴い、時刻t15において、FET103の両端電圧V11(=V2−SW12)がコンパレータ109の閾値電圧を下回ると、検出信号S11がハイレベルからローレベルに切り替わる。すなわち、スイッチ電圧SW12の印加端からFET103を介する経路で正電圧V2の印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S11がハイレベルからローレベルに切り替わる。その結果、FET103の駆動信号G11がローレベルからハイレベルに切り替わり、FET103がオフとなる。従って、FET103に流れる逆流電流を遅滞なく遮断することができる。

【0043】

スイッチ電圧SW12がさらに上昇し、時刻t16において、FET104の両端電圧V12(=SW12−OUT)がコンパレータ110の閾値電圧を上回ると、検出信号S12がローレベルからハイレベルに切り替わる。すなわち、スイッチ電圧SW12の印加端からボディダイオード104Dを介する経路で出力電圧OUTの印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S12がローレベルからハイレベルに切り替わる。その結果、FET104の駆動信号G12がハイレベルからローレベルに切り替わり、FET104がオンとなる。この状態は先の第2フェイズに相当し、スイッチ電圧SW12の印加端からFET104を介する経路で出力電圧OUTの印加端に向けた電流が流れ始める。このとき、スイッチ電圧SW12は、出力電圧OUTにFET104の降下電圧を足し合わせた電圧となる。

【0044】

なお、FET104が十分にオンするまでの間、FET104よりも順方向電圧の大きいボディダイオード104Dを介して電流が流れるので、スイッチ電圧SW12(及びSW11)にはオーバーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路1Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0045】

上記で説明したように、第1実施形態のチャージポンプ回路1Xでは、FET103及び104について、意図した方向に電流が流れる状態となった方がオンされて、意図とは逆方向に電流が流れる状態となった方がオフされる。従って、FET101及び102のスイッチング途中でFET103及び104がオンされることはないので、FET101とFET103の同時オンやFET102とFET104の同時オンを確実に防止することができる。また、第1実施形態のチャージポンプ回路1Xであれば、必ず、FET103及び104の一方がオフされてから他方がオンされるので、FET103とFET104の同時オンも確実に防止することができる。

【0046】

このように、第1実施形態のチャージポンプ回路1Xであれば、各FETのオン/オフタイミングに予め一定の遅延を与えておく遅延生成方式や、一方のFETのゲート電圧がオフレベルに切り替えられたことを確認して他方のFETのゲート電圧をオンレベルに切り替えるゲート電圧モニタ方式と比べて、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、容易にかつ適切にFETのオン/オフ制御を行うことが可能となる。

【0047】

特に、フライングキャパシタの容量値に応じてスイッチ電圧の挙動が大きく変動する正出力型チャージポンプ回路の誤動作や効率低下を解消するためには、遅延生成方式やゲート電圧モニタ方式ではなく、第1実施形態の構成を採用することが望ましい。

【0048】

<第2実施形態>

図3は、チャージポンプ回路の第2実施形態(正出力型)を示す図である。第2実施形態のチャージポンプ回路1Yは、基本的に第1実施形態と同様の構成であり、インバータ107及び108に代えて、ORゲート111とNANDゲート112を設けた点に特徴を有する。そこで、第1実施形態と同様の構成要素については、図1と同一の符号を付すことで重複した説明を割愛し、以下では、第2実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0049】

ORゲート111の第1反転入力端は、コンパレータ109の出力端(検出信号S11の印加端)に接続されている。ORゲート111の第2入力端は、オシレータ105の出力端(クロック信号CLKの印加端)に接続されている。ORゲート111の出力端(駆動信号G11の印加端)は、FET103のゲートに接続されている。ORゲート111は、コンパレータ109から入力される検出信号S11とオシレータ105から入力されるクロック信号CLKの双方に応じてFET103の駆動信号G11を生成する第2駆動部に相当する。駆動信号G11は、検出信号S11がハイレベルでクロック信号CLKがローレベルであるときにローレベルとなり、その余の場合にハイレベルとなる。

【0050】

NANDゲート112の第1入力端は、コンパレータ110の出力端(検出信号S12の印加端)に接続されている。NANDゲート112の第2入力端は、オシレータ105の出力端(クロック信号CLKの印加端)に接続されている。NANDゲート112の出力端(駆動信号G12の印加端)は、FET104のゲートに接続されている。NANDゲート112は、コンパレータ110から入力される検出信号S12とオシレータ105から入力されるクロック信号CLKの双方に応じてFET104の駆動信号G12を生成する第3駆動部に相当する。駆動信号G12は、検出信号S12とクロック信号CLKがいずれもハイレベルであるときにローレベルとなり、その余の場合にハイレベルとなる。

【0051】

図4は、チャージポンプ回路1Yの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G10、スイッチ電圧SW11及びSW12、検出信号S11及びS12、並びに、駆動信号G11及びG12が描写されている。

【0052】

チャージポンプ回路1Yの動作について、特に注目すべき点は、駆動信号G11及びG12の立上げタイミング、すなわち、FET103及び104のオフタイミングである。図4で示すように、チャージポンプ回路1Yでは、クロック信号CLKの立下がりエッジ(時刻t11など)をトリガとして駆動信号G12が立ち上がり、クロック信号CLKの立上がりエッジ(時刻t14など)をトリガとして駆動信号G11が立ち上がる。

【0053】

このように、第2実施形態のチャージポンプ回路1Yでは、FET103及び104に逆流電流が流れ始める前にFET103及び104をオフさせる構成が採用されている。従って、FET103及び104に逆流電流が流れることはないので、チャージポンプ回路1Yの誤動作や効率低下をより確実に防止することが可能となる。

【0054】

なお、チャージポンプ回路1Yでは、FET103の両端電圧V11がコンパレータ109の閾値電圧を上回っている状態のまま、FET103がオフされるので、ボディダイオード103Dに電流が流れてスイッチ電圧SW12(及びSW11)のアンダーシュートを生じる場合がある。同様に、チャージポンプ回路1Yでは、FET104の両端電圧V12がコンパレータ110の閾値電圧を上回っている状態のまま、FET104がオフされるので、ボディダイオード104Dに電流が流れてスイッチ電圧SW12(及びSW11)のオーバーシュートを生じる場合がある。ただし、このような状態はいずれも短期間であるので、チャージポンプ回路1Yの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0055】

<第3実施形態>

図5は、チャージポンプ回路の第3実施形態(正出力型)を示す図である。第3実施形態のチャージポンプ回路1Zは、基本的に第2実施形態と同様の構成であり、オフ検出部113及び114と遅延部115を追加した点に特徴を有する。そこで、第2実施形態と同様の構成要素については、図3と同一の符号を付すことで重複した説明を割愛し、以下では、第3実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0056】

オフ検出部113は、FET103の駆動信号G11に応じてオフ検出信号D11を生成する。オフ検出信号D11は、駆動信号G11がオフ検出用の閾値電圧を上回っていればハイレベルとなり、下回っていればローレベルとなる。

【0057】

オフ検出部114は、FET104の駆動信号G12に応じてオフ検出信号D12を生成する。オフ検出信号D12は、駆動信号G12がオフ検出用の閾値電圧を上回っていればハイレベルとなり、下回っていればローレベルとなる。

【0058】

遅延部115は、オフ検出信号D11及びD12に応じてクロック信号CLKに遅延を与える。具体的に述べると、遅延部115は、オフ検出信号D11がハイレベルに切り替わるまでクロック信号CLKの立上がりを遅らせ、また、オフ検出信号D12がハイレベルに切り替わるまでクロック信号CLKの立下りを遅らせる。なお、遅延部115で遅延が与えられたクロック信号CLKは、インバータ106に送出される。

【0059】

図6は、チャージポンプ回路1Zの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLKと駆動信号G10〜G12が描写されている。第3実施形態のチャージポンプ回路1Zであれば、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、第1フェイズ(PHASE1)から第2フェイズ(PHASE2)へ移行する際には、まずFET103をオフし、次いでFET101をオンしてFET102をオフしてから、最後にFET104をオンするという一連のシーケンスを実現し、逆に、第2フェイズ(PHASE2)から第1フェイズ(PHASE1)へ移行する際には、まずFET104をオフし、次いでFET101をオフしてFET102をオンしてから、最後にFET103をオンするという一連のシーケンスを実現することが可能となる。

【0060】

<第4実施形態>

図7は、チャージポンプ回路の第4実施形態(負出力型)を示す図である。第4実施形態のチャージポンプ回路2Xは、半導体装置200Aと、半導体装置200Bと、フライングキャパシタC1と、出力キャパシタC2と、を有する。なお、チャージポンプ回路2Xを用いた電源装置は、LCD−TV、PDP−TV、DVDレコーダ、BDレコーダなど、様々なアプリケーションの電源として利用することが可能である。

【0061】

半導体装置200Aには、PMOSFET201、NMOSFET202、オシレータ205、及び、インバータ206が集積化されている。半導体装置200Aの基板には、接地電圧GND(=0V)が印加されている。

【0062】

半導体装置200Bには、NMOSFET203及び204と、ドライバ207及び208と、コンパレータ209及び210が集積化されている。半導体装置200Bの基板には、負電圧NV(<0V)が印加されている。

【0063】

FET201のソースは、正電圧V1(>0V)の印加端に接続されている。FET201及び202の各ドレインは、いずれもフライングキャパシタC1の第1端(スイッチ電圧SW21の印加端)に接続されている。FET202のソースは、接地電圧GNDの印加端に接続されている。FET201及び202の各ゲートは、いずれもインバータ206の出力端(駆動信号G20の印加端)に接続されている。インバータ206の入力端は、オシレータ205の出力端(クロック信号CLKの印加端)に接続されている。

【0064】

FET203のドレインは、負電圧V2(<0V)の印加端に接続されている。FET203のソースとFET204のドレインは、いずれもフライングキャパシタC1の第2端(スイッチ電圧SW22の印加端)に接続されている。FET204のソースは、出力電圧OUTの印加端に接続されている。FET203及び204には、各々のソースをアノードとし、各々のドレインをカソードとするボディダイオード203D及び204Dが付随する。出力電圧OUTの印加端と接地電圧GNDの印加端との間には、出力キャパシタC2が接続されている。

【0065】

コンパレータ209の非反転入力端(+)はFET203のソースに接続されている。一方、コンパレータ209の反転入力端(−)は、FET103のドレインに接続されている。コンパレータ209の出力端(検出信号S21の印加端)は、ドライバ207の入力端に接続されている。インバータ207の出力端(駆動信号G21の印加端)は、FET203のゲートに接続されている。

【0066】

コンパレータ210の非反転入力端(+)はFET204のソースに接続されている。一方、コンパレータ210の反転入力端(−)は、FET204のドレインに接続されている。コンパレータ210の出力端(検出信号S22の印加端)は、ドライバ208の入力端に接続されている。ドライバ208の出力端(駆動信号G22の印加端)は、FET204のゲートに接続されている。

【0067】

FET201〜204は、いずれもフライングキャパシタC1の充放電用スイッチとして用いられる。FET201は、フライングキャパシタC1の第1端と正電圧V1の印加端との間に接続された第1FETに相当する。FET202は、フライングキャパシタC1の第1端と接地電圧GNDの印加端との間に接続された第2FETに相当する。FET203は、フライングキャパシタC1の第2端と負電圧V2の印加端との間に接続された第3FETに相当する。FET204は、フライングキャパシタC1の第2端と出力電圧OUTの印加端との間に接続された第4FETに相当する。

【0068】

オシレータ205は、一定周波数のクロック信号CLKを生成する。

【0069】

インバータ206は、クロック信号CLKに応じてFET201及び202の駆動信号G20を生成する第1駆動部に相当する。駆動信号G20は、クロック信号CLKの論理反転信号となる。

【0070】

ドライバ207は、コンパレータ209から入力される検出信号S21に応じてFET203の駆動信号G21を生成する第2駆動部に相当する。駆動信号G21は、検出信号S21と同一の論理信号となる。

【0071】

ドライバ208は、コンパレータ210から入力される検出信号S22に応じてFET204の駆動信号G22を生成する第3駆動部に相当する。駆動信号G22は、検出信号S22と同一の論理信号となる。

【0072】

コンパレータ209は、FET203の両端電圧V21(=SW22−V2)に応じて検出信号S21を生成する第1検出部に相当する。検出信号S21は、FET203の両端電圧V21が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S21は、スイッチ電圧SW22の印加端から負電圧V2の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、負電圧V2の印加端からスイッチ電圧SW22の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET203またはボディダイオード203Dを介して流れる電流の向きを検出する手法は、FET203の両端電圧V21を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0073】

コンパレータ210は、FET204の両端電圧V22(=OUT−SW22)に応じて検出信号S22を生成する第2検出部に相当する。検出信号S22は、FET204の両端電圧V22が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S22は、出力電圧OUTの印加端からスイッチ電圧SW22の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、スイッチ電圧SW22の印加端から出力電圧OUTの印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET204またはボディダイオード204Dを介して流れる電流の向きを検出する手法は、FET204の両端電圧V22を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0074】

まず、チャージポンプ回路2Xの基本動作について概略的に説明する。FET202及び204がオフとなり、FET201及び203がオンとなる第1フェイズ(充電フェイズ)では、正電圧V1の印加端から、FET201、フライングキャパシタC1、及び、FET203を介して、負電圧V2の印加端に至る経路を流れる電流によって、フライングキャパシタC1の充電が行われる。このとき、スイッチ電圧SW21は、ほぼ正電圧V1(より正確には、正電圧V1からFET201の降下電圧を差し引いた電圧)となり、スイッチ電圧SW22は、ほぼ負電圧V2(より正確には、負電圧V2にFET203の降下電圧を足し合わせた電圧)となる。従って、フライングキャパシタC1には、スイッチ電圧SW21とスイッチ電圧SW22との差分電圧(ほぼV1−V2)に相当する電荷が蓄えられる。

【0075】

その後、FET202及び204がオンとなり、FET201及び203がオフとなる第2フェイズ(放電フェイズ/電荷転送フェイズ)では、接地電圧GNDの印加端から、FET202、フライングキャパシタC1、及び、FET204を介して、出力電圧OUTの印加端に至る経路が導通されて、フライングキャパシタC1の放電(出力キャパシタC2への電荷転送)が行われる。このとき、スイッチ電圧SW21は、ほぼ接地電圧GND(より正確には、接地電圧GNDにFET202の降下電圧を足し合わせた電圧)となり、スイッチ電圧SW22は、スイッチ電圧SW21からフライングキャパシタC1の両端電圧を差し引いた電圧(ほぼV2−V1)となる。

【0076】

従って、チャージポンプ回路2Xでは、FET201〜204をオン/オフさせてフライングキャパシタC1の充放電を繰り返すことにより、負電圧V2から正電圧V1を差し引いた負の出力電圧OUT(=V2−V1)を生成することができる。

【0077】

次に、FET201〜204のオン/オフ制御について詳細に説明する。図8は、チャージポンプ回路2Xの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G20、スイッチ電圧SW21及びSW22、検出信号S21及びS22、並びに、駆動信号G21及びG22が描写されている。

【0078】

図8の例では、時刻t21まで、FET202及び204がオンされており、FET201及び203がオフされている。この状態は先述の第2フェイズに相当し、出力電圧OUTの印加端からFET204を介する経路でスイッチ電圧SW22の印加端に向けた電流が流れている。このとき、スイッチ電圧SW22は、出力電圧OUTからFET204の降下電圧を差し引いた電圧となっている。

【0079】

時刻t21において、クロック信号CLKがローレベルからハイレベルに立ち上がると駆動信号G20がハイレベルからローレベルに立ち下がるので、FET201がオンし、FET202がオフする。その結果、フライングキャパシタC1の第1端がFET201を介して正電圧V1の印加端に導通されるので、スイッチ電圧SW21が上昇し始める。また、スイッチ電圧SW22についても、フライングキャパシタC1の電荷保存則に従って、スイッチ電圧SW21と同様の挙動で上昇し始める。

【0080】

スイッチ電圧SW22の上昇に伴い、時刻t22において、FET204の両端電圧V22(=OUT−SW22)がコンパレータ210の閾値電圧を下回ると、検出信号S22がハイレベルからローレベルに切り替わる。すなわち、スイッチ電圧SW22の印加端からFET204を介する経路で出力電圧OUTの印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S22がハイレベルからローレベルに切り替わる。その結果、FET204の駆動信号G22がハイレベルからローレベルに切り替わり、FET204がオフとなる。従って、FET204に流れる逆流電流を遅滞なく遮断することができる。

【0081】

スイッチ電圧SW22がさらに低下し、時刻t23において、FET203の両端電圧V21(=SW22−V2)がコンパレータ209の閾値電圧を上回ると、検出信号S21がローレベルからハイレベルに切り替わる。すなわち、スイッチ電圧SW22の印加端からボディダイオード203Dを介する経路で負電圧V2の印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S21がローレベルからハイレベルに切り替わる。その結果、FET203の駆動信号G21がローレベルからハイレベルに切り替わり、FET203がオンとなる。この状態は先述の第1フェイズに相当し、正電圧V1の印加端から、FET201、フライングキャパシタC1、及び、FET203を介して、負電圧V2の印加端に至る経路で電流が流れ始める。このとき、スイッチ電圧SW22は、負電圧V2にFET203の降下電圧を足し合わせた電圧となる。

【0082】

なお、FET203が十分にオンするまでの間、FET203よりも順方向電圧の大きいボディダイオード203Dを介して電流が流れるので、スイッチ電圧SW22(及びSW21)にはオーバーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路2Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0083】

その後、時刻t24において、クロック信号CLKがハイレベルからローレベルに立ち下がると駆動信号G20がローレベルからハイレベルに立ち下がるので、FET201がオフし、FET202がオンする。その結果、フライングキャパシタC1の第1端がFET202を介して接地電圧GNDの印加端に導通されるので、スイッチ電圧SW21が低下し始める。また、スイッチ電圧SW22についても、フライングキャパシタC1の電荷保存則に従い、スイッチ電圧SW21と同様の挙動で低下し始める。

【0084】

スイッチ電圧SW22の低下に伴い、時刻t25において、FET203の両端電圧V21(=SW22−V2)がコンパレータ209の閾値電圧を下回ると、検出信号S21がハイレベルからローレベルに切り替わる。すなわち、負電圧V2の印加端からFET203を介する経路でスイッチ電圧SW22の印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S21がハイレベルからローレベルに切り替わる。その結果、FET203の駆動信号G21がハイレベルからローレベルに切り替わり、FET203がオフとなる。従って、FET203に流れる逆流電流を遅滞なく遮断することができる。

【0085】

スイッチ電圧SW22がさらに低下し、時刻t26において、FET204の両端電圧V22(=OUT−SW22)がコンパレータ210の閾値電圧を上回ると、検出信号S22がローレベルからハイレベルに切り替わる。すなわち、出力電圧OUTの印加端からボディダイオード204Dを介する経路でスイッチ電圧SW22の印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S22がローレベルからハイレベルに切り替わる。その結果、FET204の駆動信号G22がローレベルからハイレベルに切り替わり、FET204がオンとなる。この状態は先の第2フェイズに相当し、出力電圧OUTの印加端からFET204を介する経路でスイッチ電圧SW22の印加端に向けた電流が流れ始める。このとき、スイッチ電圧SW22は、出力電圧OUTからFET204の降下電圧を差し引いた電圧となる。

【0086】

なお、FET204が十分にオンするまでの間、FET204よりも順方向電圧の大きいボディダイオード204Dを介して電流が流れるので、スイッチ電圧SW22(及びSW21)にはアンダーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路2Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0087】

上記で説明したように、第4実施形態のチャージポンプ回路2Xでは、FET203及び204について、意図した方向に電流が流れる状態となった方がオンされて、意図とは逆方向に電流が流れる状態となった方がオフされる。従って、FET201及び202のスイッチング途中でFET203及び204がオンされることはないので、FET201とFET203の同時オンやFET202とFET204の同時オンを確実に防止することができる。また、第4実施形態のチャージポンプ回路2Xであれば、必ず、FET203及び204の一方がオフされてから他方がオンされるので、FET203とFET204の同時オンも確実に防止することができる。

【0088】

このように、第4実施形態のチャージポンプ回路2Xであれば、各FETのオン/オフタイミングに予め一定の遅延を与えておく遅延生成方式や、一方のFETのゲート電圧がオフレベルに切り替えられたことを確認して他方のFETのゲート電圧をオンレベルに切り替えるゲート電圧モニタ方式と比べて、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、容易にかつ適切にFETのオン/オフ制御を行うことが可能となる。

【0089】

特に、フライングキャパシタの容量値に応じてスイッチ電圧の挙動が大きく変動する負出力型チャージポンプ回路の誤動作や効率低下を解消するためには、遅延生成方式やゲート電圧モニタ方式ではなく、第4実施形態の構成を採用することが望ましい。

【0090】

<第5実施形態>

図9は、チャージポンプ回路の第5実施形態(負出力型)を示す図である。第5実施形態のチャージポンプ回路2Yは、基本的に第4実施形態と同様の構成であり、ドライバ207及び208に代えて、ANDゲート211及び212を設けた点に特徴を有する。そこで、第4実施形態と同様の構成要素については、図7と同一の符号を付すことで重複した説明を割愛し、以下では、第5実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0091】

ANDゲート211の第1入力端は、コンパレータ209の出力端(検出信号S21の印加端)に接続されている。ANDゲート211の第2入力端は、オシレータ205の出力端(クロック信号CLKの印加端)に接続されている。ANDゲート211の出力端(駆動信号G21の印加端)は、FET203のゲートに接続されている。ANDゲート211は、コンパレータ209から入力される検出信号S21とオシレータ205から入力されるクロック信号CLKの双方に応じてFET203の駆動信号G21を生成する第2駆動部に相当する。駆動信号G21は、検出信号S21とクロック信号CLKがいずれもハイレベルであるときにハイレベルとなり、その余の場合にローレベルとなる。

【0092】

ANDゲート212の第1入力端は、コンパレータ210の出力端(検出信号S22の印加端)に接続されている。ANDゲート212の第2反転入力端は、オシレータ205の出力端(クロック信号CLKの印加端)に接続されている。ANDゲート212の出力端(駆動信号G22の印加端)は、FET204のゲートに接続されている。ANDゲート212は、コンパレータ210から入力される検出信号S22とオシレータ205から入力されるクロック信号CLKの双方に応じてFET204の駆動信号G22を生成する第3駆動部に相当する。駆動信号G22は、検出信号S22がハイレベルでクロック信号CLKがローレベルであるときにハイレベルとなり、その余の場合にローレベルとなる。

【0093】

図10は、チャージポンプ回路2Yの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G20、スイッチ電圧SW21及びSW22、検出信号S21及びS22、並びに、駆動信号G21及びG22が描写されている。

【0094】

チャージポンプ回路2Yの動作について、特に注目すべき点は、駆動信号G21及びG22の立下げタイミング、すなわち、FET203及び204のオフタイミングである。図10で示すように、チャージポンプ回路2Yでは、クロック信号CLKの立上がりエッジ(時刻t21など)をトリガとして駆動信号G22が立ち下がり、クロック信号CLKの立下がりエッジ(時刻t24など)をトリガとして駆動信号G21が立ち下がる。

【0095】

このように、第5実施形態のチャージポンプ回路2Yでは、FET203及び204に逆流電流が流れ始める前にFET203及び204をオフさせる構成が採用されている。従って、FET203及び204に逆流電流が流れることはないので、チャージポンプ回路2Yの誤動作や効率低下をより確実に防止することが可能となる。

【0096】

なお、チャージポンプ回路2Yでは、FET203の両端電圧V21がコンパレータ209の閾値電圧を上回っている状態のまま、FET203がオフされるので、ボディダイオード203Dに電流が流れてスイッチ電圧SW22(及びSW21)のオーバーシュートを生じる場合がある。同様に、チャージポンプ回路2Yでは、FET204の両端電圧V22がコンパレータ210の閾値電圧を上回っている状態のまま、FET204がオフされるので、ボディダイオード204Dに電流が流れてスイッチ電圧SW22(及びSW21)のアンダーシュートを生じる場合がある。ただし、このような状態はいずれも短期間であるので、チャージポンプ回路2Yの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0097】

<第6実施形態>

図11は、チャージポンプ回路の第6実施形態(負出力型)を示す図である。第6実施形態のチャージポンプ回路2Zは、基本的に第5実施形態と同様の構成であり、オフ検出部213及び214と遅延部215を追加した点に特徴を有する。そこで、第6実施形態と同様の構成要素については、図9と同一の符号を付すことで重複した説明を割愛し、以下では、第6実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0098】

オフ検出部213は、FET203の駆動信号G21に応じてオフ検出信号D21を生成する。オフ検出信号D21は、駆動信号G21がオフ検出用の閾値電圧を下回っていればハイレベルとなり、上回っていればローレベルとなる。

【0099】

オフ検出部214は、FET204の駆動信号G22に応じてオフ検出信号D22を生成する。オフ検出信号D22は、駆動信号G22がオフ検出用の閾値電圧を下回っていればハイレベルとなり、上回っていればローレベルとなる。

【0100】

遅延部215は、オフ検出信号D21及びD22に応じてクロック信号CLKに遅延を与える。具体的に述べると、遅延部215は、オフ検出信号D21がローレベルに切り替わるまでクロック信号CLKの立下がりを遅らせ、また、オフ検出信号D22がローレベルに切り替わるまでクロック信号CLKの立上りを遅らせる。なお、遅延部215で遅延が与えられたクロック信号CLKは、インバータ206に送出される。

【0101】

図12は、チャージポンプ回路2Zの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLKと駆動信号G20〜G22が描写されている。第6実施形態のチャージポンプ回路2Zであれば、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、第1フェイズ(PHASE1)から第2フェイズ(PHASE2)へ移行する際には、まずFET203をオフし、次いでFET201をオフしてFET202をオンしてから、最後にFET204をオンするという一連のシーケンスを実現し、逆に、第2フェイズ(PHASE2)から第1フェイズ(PHASE1)へ移行する際には、まずFET204をオフし、次いでFET201をオンしてFET202をオフしてから、最後にFET203をオンするという一連のシーケンスを実現することが可能となる。

【0102】

特に、複数の半導体装置間でクロック信号のやり取りを行う負出力型のチャージポンプ回路では、上記した第6実施形態の構成を採用することが望ましい。

【0103】

<その他の変形例>

なお、本明細書中に開示されている種々の技術的特徴は、上記実施形態のほか、その技術的創作の主旨を逸脱しない範囲で種々の変更を加えることが可能である。例えば、各種信号の論理レベル反転は任意である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0104】

本発明に係る電源装置は、LCD−TV、PDP−TV、DVDレコーダ、BDレコーダなど、様々なアプリケーションの電源として利用することが可能である。

【符号の説明】

【0105】

1X、1Y、1Z チャージポンプ回路(正出力型)

100 半導体装置

101、103、104 PMOSFET

102 NMOSFET

103D、104D ボディダイオード

105 オシレータ

106〜108 インバータ

109、110 コンパレータ

111 ORゲート

112 NANDゲート

113、114 オフ検出部

115 遅延部

2X、2Y、2Z チャージポンプ回路(負出力型)

200A、200B 半導体装置

201 PMOSFET

202〜204 NMOSFET

203D、204D ボディダイオード

205 オシレータ

206 インバータ

207、208 ドライバ

209、210 コンパレータ

211、212 ANDゲート

213、214 オフ検出部

215 遅延部

C1 フライングキャパシタ

C2 出力キャパシタ

【技術分野】

【0001】

本発明は、チャージポンプ回路及びこれを用いた電源装置に関するものである。

【背景技術】

【0002】

チャージポンプ回路は、電圧の正昇圧や負昇圧(反転)が可能であり、主に電流供給能力が必要のない場面で使用される。一般的なチャージポンプ回路では、フライングキャパシタの充放電用スイッチとしてダイオードが用いられる。ただし、ダイオードは順方向降下電圧が大きいので、出力電圧範囲が狭くなる。そのため、出力電圧範囲を広げる必要がある場合には、順方向降下電圧の大きいダイオードに代えて、より降下電圧の小さいFET[field effect transistor]を用いた同期整流方式が採用されていた。

【0003】

なお、本発明に関連する従来技術の一例としては、特許文献1を挙げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】国際公開第2008/065941号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

同期整流方式のチャージポンプ回路では、複数設けられたFETのうち、同時にオンすべきでないFETが同時にオンしてしまうと、誤動作や効率低下を生じるおそれがある。そのため、適切にFETのオン/オフ制御を行うことが重要である。しかしながら、回路定数(特にフライングキャパシタの容量値)や素子レイアウト等を考慮して、FETのオン/オフ制御を最適化することは困難であった。

【0006】

本発明は、本願の発明者らにより見出された上記の問題点に鑑み、容易にかつ適切にFETのオン/オフ制御を行うことが可能なチャージポンプ回路、及び、これを用いた電源装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明に係るチャージポンプ回路は、キャパシタの充放電用スイッチとして用いられるFETと、前記FETに流れる電流または前記FETの両端電圧に応じて検出信号を生成する検出部と、前記検出信号に応じて前記FETの駆動信号を生成する駆動部と、を有する構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成るチャージポンプ回路は、前記キャパシタの第1端と第1電圧の印加端との間に接続された第1FETと、前記キャパシタの第1端と接地電圧の印加端との間に接続された第2FETと、前記キャパシタの第2端と第2電圧の印加端との間に接続された第3FETと、前記キャパシタの第2端と出力電圧の印加端との間に接続された第4FETと、クロック信号を生成するオシレータと、前記クロック信号に応じて前記第1FETと前記第2FETの駆動信号を生成する第1駆動部と、前記第3FETに流れる電流または前記第3FETの両端電圧に応じて第1検出信号を生成する第1検出部と、前記第4FETに流れる電流または前記第4FETの両端電圧に応じて第2検出信号を生成する第2検出部と、前記第1検出信号に応じて前記第3FETの駆動信号を生成する第2駆動部と、前記第2検出信号に応じて前記第4FETの駆動信号を生成する第3駆動部と、を有する構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成るチャージポンプ回路において、前記第2駆動部は、前記第1検出信号と前記クロック信号の双方に応じて前記第3FETの駆動信号を生成し、前記第3駆動部は、前記第2検出信号と前記クロック信号の双方に応じて前記第4FETの駆動信号を生成する構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成るチャージポンプ回路は、前記第3FETの駆動信号に応じて第1オフ検出信号を生成する第1オフ検出部と、前記第4FETの駆動信号に応じて第2オフ検出信号を生成する第2オフ検出部と、前記第1オフ検出信号と前記第2オフ検出信号に応じて前記クロック信号に遅延を与える遅延部と、を有する構成(第4の構成)にするとよい。

【0011】

また、上記第2〜第4いずれかの構成から成るチャージポンプ回路において、前記第1電圧と前記第2電圧は、いずれも正電圧である構成(第5の構成)にするとよい。

【0012】

また、上記第5の構成から成るチャージポンプ回路において、前記第1FET、前記第3FET、及び、前記第4FETはいずれもPチャネル型であり、前記第2FETはNチャネル型である構成(第6の構成)にするとよい。

【0013】

また、上記第2〜第4いずれかの構成から成るチャージポンプ回路において、前記第1電圧は正電圧であり、前記第2電圧は負電圧である構成(第7の構成)にするとよい。

【0014】

また、上記第7の構成から成るチャージポンプ回路において、前記第1FETはPチャネル型であり、前記第2FET、前記第3FET、及び、前記第4FETはいずれもNチャネル型である構成(第8の構成)にするとよい。

【0015】

また、上記第8の構成から成るチャージポンプ回路において、前記第1FETと、前記第2FETと、前記第1駆動部と、前記オシレータは、基板に接地電圧が印加された第1半導体装置に集積化されており、前記第3FETと、前記第4FETと、前記第1検出部と、前記第2検出部と、前記第2駆動部と、前記第3駆動部は、基板に負電圧が印加された第2半導体装置に集積化されている構成(第9の構成)にするとよい。

【0016】

また、本発明に係る電源装置は、上記第1〜第9いずれかの構成から成るチャージポンプ回路を有する構成(第10の構成)とされている。

【発明の効果】

【0017】

本発明によれば、容易にかつ適切にFETのオン/オフ制御を行うことが可能なチャージポンプ回路、及び、これを用いた電源装置を提供することができる。

【図面の簡単な説明】

【0018】

【図1】チャージポンプ回路の第1実施形態(正出力型)を示す図

【図2】チャージポンプ回路1Xの一動作例を示すタイミングチャート

【図3】チャージポンプ回路の第2実施形態(正出力型)を示す図

【図4】チャージポンプ回路1Yの一動作例を示すタイミングチャート

【図5】チャージポンプ回路の第3実施形態(正出力型)を示す図

【図6】チャージポンプ回路1Zの一動作例を示すタイミングチャート

【図7】チャージポンプ回路の第4実施形態(負出力型)を示す図

【図8】チャージポンプ回路2Xの一動作例を示すタイミングチャート

【図9】チャージポンプ回路の第5実施形態(負出力型)を示す図

【図10】チャージポンプ回路2Yの一動作例を示すタイミングチャート

【図11】チャージポンプ回路の第6実施形態(負出力型)を示す図

【図12】チャージポンプ回路2Zの一動作例を示すタイミングチャート

【発明を実施するための形態】

【0019】

<第1実施形態>

図1は、チャージポンプ回路の第1実施形態(正出力型)を示す図である。第1実施形態のチャージポンプ回路1Xは、半導体装置100と、フライングキャパシタC1と、出力キャパシタC2を有する。なお、チャージポンプ回路1Xを用いた電源装置は、LCD−TV、PDP−TV、DVDレコーダ、BDレコーダなど、様々なアプリケーションの電源として利用することが可能である。

【0020】

半導体装置100には、PMOSFET[P channel type metal oxide semiconductor field effect transitor]101と、NMOSFET[N channel type MOSFET]102と、PMOSFET103及び104と、オシレータ105と、インバータ106〜108と、コンパレータ109及び110と、が集積化されている。半導体装置100の基板には、接地電圧GND(=0V)が印加されている。

【0021】

FET101のソースは、正電圧V1(>0V)の印加端に接続されている。FET101及び102の各ドレインは、いずれもフライングキャパシタC1の第1端(スイッチ電圧SW11の印加端)に接続されている。FET102のソースは、接地電圧GNDの印加端に接続されている。FET101及び102の各ゲートは、いずれもインバータ106の出力端(駆動信号G10の印加端)に接続されている。インバータ106の入力端は、オシレータ105の出力端(クロック信号CLKの印加端)に接続されている。

【0022】

FET103のドレインは、正電圧V2(>0V)の印加端に接続されている。FET103のソースとFET104のドレインは、いずれもフライングキャパシタC1の第2端(スイッチ電圧SW12の印加端)に接続されている。FET104のソースは、出力電圧OUTの印加端に接続されている。FET103及び104には、各々のドレインをアノードとし、各々のソースをカソードとするボディダイオード103D及び104Dが付随する。出力電圧OUTの印加端と接地電圧GNDの印加端との間には、出力キャパシタC2が接続されている。

【0023】

コンパレータ109の非反転入力端(+)は、FET103のドレインに接続されている。一方、コンパレータ109の反転入力端(−)は、FET103のソースに接続されている。コンパレータ109の出力端(検出信号S11の印加端)は、インバータ107の入力端に接続されている。インバータ107の出力端(駆動信号G11の印加端)は、FET103のゲートに接続されている。

【0024】

コンパレータ110の非反転入力端(+)は、FET104のドレインに接続されている。一方、コンパレータ110の反転入力端(−)は、FET104のソースに接続されている。コンパレータ110の出力端(検出信号S12の印加端)は、インバータ108の入力端に接続されている。インバータ108の出力端(駆動信号G12の印加端)は、FET104のゲートに接続されている。

【0025】

FET101〜104は、いずれもフライングキャパシタC1の充放電用スイッチとして用いられる。FET101は、フライングキャパシタC1の第1端と正電圧V1の印加端との間に接続された第1FETに相当する。FET102は、フライングキャパシタC1の第1端と接地電圧GNDの印加端との間に接続された第2FETに相当する。FET103は、フライングキャパシタC1の第2端と正電圧V2の印加端との間に接続された第3FETに相当する。FET104は、フライングキャパシタC1の第2端と出力電圧OUTの印加端との間に接続された第4FETに相当する。

【0026】

オシレータ105は、一定周波数のクロック信号CLKを生成する。

【0027】

インバータ106は、クロック信号CLKに応じてFET101及び102の駆動信号G10を生成する第1駆動部に相当する。駆動信号G10は、クロック信号CLKの論理反転信号となる。

【0028】

インバータ107は、コンパレータ109から入力される検出信号S11に応じてFET103の駆動信号G11を生成する第2駆動部に相当する。駆動信号G11は、検出信号S11の論理反転信号となる。

【0029】

インバータ108は、コンパレータ110から入力される検出信号S12に応じてFET104の駆動信号G12を生成する第3駆動部に相当する。駆動信号G12は、検出信号S12の論理反転信号となる。

【0030】

コンパレータ109は、FET103の両端電圧V11(=V2−SW12)に応じて検出信号S11を生成する第1検出部に相当する。検出信号S11は、FET103の両端電圧V11が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S11は、正電圧V2の印加端からスイッチ電圧SW12の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、スイッチ電圧SW12の印加端から正電圧V2の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET103またはボディダイオード103Dを介して流れる電流の向きを検出する手法は、FET103の両端電圧V11を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0031】

コンパレータ110は、FET104の両端電圧V12(=SW12−OUT)に応じて検出信号S12を生成する第2検出部に相当する。検出信号S12は、FET104の両端電圧V12が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S12は、スイッチ電圧SW12の印加端から出力電圧OUTの印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、出力電圧OUTの印加端からスイッチ電圧SW12の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET104またはボディダイオード104Dを介して流れる電流の向きを検出する手法は、FET104の両端電圧V12を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0032】

まず、チャージポンプ回路1Xの基本動作について概略的に説明する。FET101及び104がオフとなり、FET102及び103がオンとなる第1フェイズ(充電フェイズ)では、正電圧V2の印加端から、FET103、フライングキャパシタC1、及び、FET102を介して、接地電圧GNDの印加端に至る経路を流れる電流によって、フライングキャパシタC1の充電が行われる。このとき、スイッチ電圧SW11は、ほぼ接地電圧GND(より正確には、接地電圧GNDにFET102の降下電圧を足し合わせた電圧)となり、スイッチ電圧SW12は、ほぼ正電圧V2(より正確には、正電圧V2からFET103の降下電圧を差し引いた電圧)となる。従って、フライングキャパシタC1には、スイッチ電圧SW11とスイッチ電圧SW12との差分電圧(ほぼ正電圧V2)に相当する電荷が蓄えられる。

【0033】

その後、FET101及び104がオンとなり、FET102及び103がオフとなる第2フェイズ(放電フェイズ/電荷転送フェイズ)では、正電圧V1の印加端から、FET101、フライングキャパシタC1、及び、FET104を介して、出力電圧OUTの印加端に至る経路が導通されて、フライングキャパシタC1の放電(出力キャパシタC2への電荷転送)が行われる。このとき、スイッチ電圧SW11は、ほぼ正電圧V1(より正確には、正電圧V1にFET101の降下電圧を足し合わせた電圧)となり、スイッチ電圧SW12は、スイッチ電圧SW11にフライングキャパシタC1の両端電圧を足し合わせた電圧(ほぼV1+V2)となる。

【0034】

従って、チャージポンプ回路1Xでは、FET101〜104をオン/オフさせてフライングキャパシタC1の充放電を繰り返すことにより、正電圧V1及びV2を足し合わせた正の出力電圧OUT(=V1+V2)を生成することができる。

【0035】

次に、FET101〜104のオン/オフ制御について詳細に説明する。図2は、チャージポンプ回路1Xの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G10、スイッチ電圧SW11及びSW12、検出信号S11及びS12、並びに、駆動信号G11及びG12が描写されている。

【0036】

図2の例では、時刻t11まで、FET101及び104がオンされており、FET102及び103がオフされている。この状態は先述の第2フェイズに相当し、スイッチ電圧SW12の印加端からFET104を介する経路で出力電圧OUTの印加端に向けた電流が流れている。このとき、スイッチ電圧SW12は、出力電圧OUTにFET104の降下電圧を足し合わせた電圧となっている。

【0037】

時刻t11において、クロック信号CLKがハイレベルからローレベルに立ち下がると駆動信号G10がローレベルからハイレベルに立ち上がるので、FET101がオフし、FET102がオンする。その結果、フライングキャパシタC1の第1端がFET102を介して接地電圧GNDの印加端に導通されるので、スイッチ電圧SW11が低下し始める。また、スイッチ電圧SW12についても、フライングキャパシタC1の電荷保存則に従い、スイッチ電圧SW11と同様の挙動で低下し始める。

【0038】

スイッチ電圧SW12の低下に伴い、時刻t12において、FET104の両端電圧V12(=SW12−OUT)がコンパレータ110の閾値電圧を下回ると、検出信号S12がハイレベルからローレベルに切り替わる。すなわち、出力電圧OUTの印加端からFET104を介する経路でスイッチ電圧SW12の印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S12がハイレベルからローレベルに切り替わる。その結果、FET104の駆動信号G12がローレベルからハイレベルに切り替わり、FET104がオフとなる。従って、FET104に流れる逆流電流を遅滞なく遮断することができる。

【0039】

スイッチ電圧SW12がさらに低下し、時刻t13において、FET103の両端電圧V11(=V2−SW12)がコンパレータ109の閾値電圧を上回ると、検出信号S11がローレベルからハイレベルに切り替わる。すなわち、正電圧V2の印加端からボディダイオード103Dを介する経路でスイッチ電圧SW12の印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S11がローレベルからハイレベルに切り替わる。その結果、FET103の駆動信号G11がハイレベルからローレベルに切り替わり、FET103がオンとなる。この状態は先述の第1フェイズに相当し、正電圧V2の印加端から、FET103、フライングキャパシタC1、及び、FET102を介して、接地電圧GNDの印加端に至る経路で電流が流れ始める。このとき、スイッチ電圧SW12は、正電圧V2からFET103の降下電圧を差し引いた電圧となる。

【0040】

なお、FET103が十分にオンするまでの間、FET103よりも順方向電圧の大きいボディダイオード103Dを介して電流が流れるので、スイッチ電圧SW12(及びSW11)にはアンダーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路1Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0041】

その後、時刻t14において、クロック信号CLKがローレベルからハイレベルに立ち上がると駆動信号G10がハイレベルからローレベルに立ち下がるので、FET101がオンし、FET102がオフする。その結果、フライングキャパシタC1の第1端がFET101を介して正電圧V1の印加端に導通されるので、スイッチ電圧SW11が上昇し始める。また、スイッチ電圧SW12についても、フライングキャパシタC1の電荷保存則に従い、スイッチ電圧SW11と同様の挙動で上昇し始める。

【0042】

スイッチ電圧SW12の上昇に伴い、時刻t15において、FET103の両端電圧V11(=V2−SW12)がコンパレータ109の閾値電圧を下回ると、検出信号S11がハイレベルからローレベルに切り替わる。すなわち、スイッチ電圧SW12の印加端からFET103を介する経路で正電圧V2の印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S11がハイレベルからローレベルに切り替わる。その結果、FET103の駆動信号G11がローレベルからハイレベルに切り替わり、FET103がオフとなる。従って、FET103に流れる逆流電流を遅滞なく遮断することができる。

【0043】

スイッチ電圧SW12がさらに上昇し、時刻t16において、FET104の両端電圧V12(=SW12−OUT)がコンパレータ110の閾値電圧を上回ると、検出信号S12がローレベルからハイレベルに切り替わる。すなわち、スイッチ電圧SW12の印加端からボディダイオード104Dを介する経路で出力電圧OUTの印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S12がローレベルからハイレベルに切り替わる。その結果、FET104の駆動信号G12がハイレベルからローレベルに切り替わり、FET104がオンとなる。この状態は先の第2フェイズに相当し、スイッチ電圧SW12の印加端からFET104を介する経路で出力電圧OUTの印加端に向けた電流が流れ始める。このとき、スイッチ電圧SW12は、出力電圧OUTにFET104の降下電圧を足し合わせた電圧となる。

【0044】

なお、FET104が十分にオンするまでの間、FET104よりも順方向電圧の大きいボディダイオード104Dを介して電流が流れるので、スイッチ電圧SW12(及びSW11)にはオーバーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路1Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0045】

上記で説明したように、第1実施形態のチャージポンプ回路1Xでは、FET103及び104について、意図した方向に電流が流れる状態となった方がオンされて、意図とは逆方向に電流が流れる状態となった方がオフされる。従って、FET101及び102のスイッチング途中でFET103及び104がオンされることはないので、FET101とFET103の同時オンやFET102とFET104の同時オンを確実に防止することができる。また、第1実施形態のチャージポンプ回路1Xであれば、必ず、FET103及び104の一方がオフされてから他方がオンされるので、FET103とFET104の同時オンも確実に防止することができる。

【0046】

このように、第1実施形態のチャージポンプ回路1Xであれば、各FETのオン/オフタイミングに予め一定の遅延を与えておく遅延生成方式や、一方のFETのゲート電圧がオフレベルに切り替えられたことを確認して他方のFETのゲート電圧をオンレベルに切り替えるゲート電圧モニタ方式と比べて、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、容易にかつ適切にFETのオン/オフ制御を行うことが可能となる。

【0047】

特に、フライングキャパシタの容量値に応じてスイッチ電圧の挙動が大きく変動する正出力型チャージポンプ回路の誤動作や効率低下を解消するためには、遅延生成方式やゲート電圧モニタ方式ではなく、第1実施形態の構成を採用することが望ましい。

【0048】

<第2実施形態>

図3は、チャージポンプ回路の第2実施形態(正出力型)を示す図である。第2実施形態のチャージポンプ回路1Yは、基本的に第1実施形態と同様の構成であり、インバータ107及び108に代えて、ORゲート111とNANDゲート112を設けた点に特徴を有する。そこで、第1実施形態と同様の構成要素については、図1と同一の符号を付すことで重複した説明を割愛し、以下では、第2実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0049】

ORゲート111の第1反転入力端は、コンパレータ109の出力端(検出信号S11の印加端)に接続されている。ORゲート111の第2入力端は、オシレータ105の出力端(クロック信号CLKの印加端)に接続されている。ORゲート111の出力端(駆動信号G11の印加端)は、FET103のゲートに接続されている。ORゲート111は、コンパレータ109から入力される検出信号S11とオシレータ105から入力されるクロック信号CLKの双方に応じてFET103の駆動信号G11を生成する第2駆動部に相当する。駆動信号G11は、検出信号S11がハイレベルでクロック信号CLKがローレベルであるときにローレベルとなり、その余の場合にハイレベルとなる。

【0050】

NANDゲート112の第1入力端は、コンパレータ110の出力端(検出信号S12の印加端)に接続されている。NANDゲート112の第2入力端は、オシレータ105の出力端(クロック信号CLKの印加端)に接続されている。NANDゲート112の出力端(駆動信号G12の印加端)は、FET104のゲートに接続されている。NANDゲート112は、コンパレータ110から入力される検出信号S12とオシレータ105から入力されるクロック信号CLKの双方に応じてFET104の駆動信号G12を生成する第3駆動部に相当する。駆動信号G12は、検出信号S12とクロック信号CLKがいずれもハイレベルであるときにローレベルとなり、その余の場合にハイレベルとなる。

【0051】

図4は、チャージポンプ回路1Yの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G10、スイッチ電圧SW11及びSW12、検出信号S11及びS12、並びに、駆動信号G11及びG12が描写されている。

【0052】

チャージポンプ回路1Yの動作について、特に注目すべき点は、駆動信号G11及びG12の立上げタイミング、すなわち、FET103及び104のオフタイミングである。図4で示すように、チャージポンプ回路1Yでは、クロック信号CLKの立下がりエッジ(時刻t11など)をトリガとして駆動信号G12が立ち上がり、クロック信号CLKの立上がりエッジ(時刻t14など)をトリガとして駆動信号G11が立ち上がる。

【0053】

このように、第2実施形態のチャージポンプ回路1Yでは、FET103及び104に逆流電流が流れ始める前にFET103及び104をオフさせる構成が採用されている。従って、FET103及び104に逆流電流が流れることはないので、チャージポンプ回路1Yの誤動作や効率低下をより確実に防止することが可能となる。

【0054】

なお、チャージポンプ回路1Yでは、FET103の両端電圧V11がコンパレータ109の閾値電圧を上回っている状態のまま、FET103がオフされるので、ボディダイオード103Dに電流が流れてスイッチ電圧SW12(及びSW11)のアンダーシュートを生じる場合がある。同様に、チャージポンプ回路1Yでは、FET104の両端電圧V12がコンパレータ110の閾値電圧を上回っている状態のまま、FET104がオフされるので、ボディダイオード104Dに電流が流れてスイッチ電圧SW12(及びSW11)のオーバーシュートを生じる場合がある。ただし、このような状態はいずれも短期間であるので、チャージポンプ回路1Yの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0055】

<第3実施形態>

図5は、チャージポンプ回路の第3実施形態(正出力型)を示す図である。第3実施形態のチャージポンプ回路1Zは、基本的に第2実施形態と同様の構成であり、オフ検出部113及び114と遅延部115を追加した点に特徴を有する。そこで、第2実施形態と同様の構成要素については、図3と同一の符号を付すことで重複した説明を割愛し、以下では、第3実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0056】

オフ検出部113は、FET103の駆動信号G11に応じてオフ検出信号D11を生成する。オフ検出信号D11は、駆動信号G11がオフ検出用の閾値電圧を上回っていればハイレベルとなり、下回っていればローレベルとなる。

【0057】

オフ検出部114は、FET104の駆動信号G12に応じてオフ検出信号D12を生成する。オフ検出信号D12は、駆動信号G12がオフ検出用の閾値電圧を上回っていればハイレベルとなり、下回っていればローレベルとなる。

【0058】

遅延部115は、オフ検出信号D11及びD12に応じてクロック信号CLKに遅延を与える。具体的に述べると、遅延部115は、オフ検出信号D11がハイレベルに切り替わるまでクロック信号CLKの立上がりを遅らせ、また、オフ検出信号D12がハイレベルに切り替わるまでクロック信号CLKの立下りを遅らせる。なお、遅延部115で遅延が与えられたクロック信号CLKは、インバータ106に送出される。

【0059】

図6は、チャージポンプ回路1Zの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLKと駆動信号G10〜G12が描写されている。第3実施形態のチャージポンプ回路1Zであれば、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、第1フェイズ(PHASE1)から第2フェイズ(PHASE2)へ移行する際には、まずFET103をオフし、次いでFET101をオンしてFET102をオフしてから、最後にFET104をオンするという一連のシーケンスを実現し、逆に、第2フェイズ(PHASE2)から第1フェイズ(PHASE1)へ移行する際には、まずFET104をオフし、次いでFET101をオフしてFET102をオンしてから、最後にFET103をオンするという一連のシーケンスを実現することが可能となる。

【0060】

<第4実施形態>

図7は、チャージポンプ回路の第4実施形態(負出力型)を示す図である。第4実施形態のチャージポンプ回路2Xは、半導体装置200Aと、半導体装置200Bと、フライングキャパシタC1と、出力キャパシタC2と、を有する。なお、チャージポンプ回路2Xを用いた電源装置は、LCD−TV、PDP−TV、DVDレコーダ、BDレコーダなど、様々なアプリケーションの電源として利用することが可能である。

【0061】

半導体装置200Aには、PMOSFET201、NMOSFET202、オシレータ205、及び、インバータ206が集積化されている。半導体装置200Aの基板には、接地電圧GND(=0V)が印加されている。

【0062】

半導体装置200Bには、NMOSFET203及び204と、ドライバ207及び208と、コンパレータ209及び210が集積化されている。半導体装置200Bの基板には、負電圧NV(<0V)が印加されている。

【0063】

FET201のソースは、正電圧V1(>0V)の印加端に接続されている。FET201及び202の各ドレインは、いずれもフライングキャパシタC1の第1端(スイッチ電圧SW21の印加端)に接続されている。FET202のソースは、接地電圧GNDの印加端に接続されている。FET201及び202の各ゲートは、いずれもインバータ206の出力端(駆動信号G20の印加端)に接続されている。インバータ206の入力端は、オシレータ205の出力端(クロック信号CLKの印加端)に接続されている。

【0064】

FET203のドレインは、負電圧V2(<0V)の印加端に接続されている。FET203のソースとFET204のドレインは、いずれもフライングキャパシタC1の第2端(スイッチ電圧SW22の印加端)に接続されている。FET204のソースは、出力電圧OUTの印加端に接続されている。FET203及び204には、各々のソースをアノードとし、各々のドレインをカソードとするボディダイオード203D及び204Dが付随する。出力電圧OUTの印加端と接地電圧GNDの印加端との間には、出力キャパシタC2が接続されている。

【0065】

コンパレータ209の非反転入力端(+)はFET203のソースに接続されている。一方、コンパレータ209の反転入力端(−)は、FET103のドレインに接続されている。コンパレータ209の出力端(検出信号S21の印加端)は、ドライバ207の入力端に接続されている。インバータ207の出力端(駆動信号G21の印加端)は、FET203のゲートに接続されている。

【0066】

コンパレータ210の非反転入力端(+)はFET204のソースに接続されている。一方、コンパレータ210の反転入力端(−)は、FET204のドレインに接続されている。コンパレータ210の出力端(検出信号S22の印加端)は、ドライバ208の入力端に接続されている。ドライバ208の出力端(駆動信号G22の印加端)は、FET204のゲートに接続されている。

【0067】

FET201〜204は、いずれもフライングキャパシタC1の充放電用スイッチとして用いられる。FET201は、フライングキャパシタC1の第1端と正電圧V1の印加端との間に接続された第1FETに相当する。FET202は、フライングキャパシタC1の第1端と接地電圧GNDの印加端との間に接続された第2FETに相当する。FET203は、フライングキャパシタC1の第2端と負電圧V2の印加端との間に接続された第3FETに相当する。FET204は、フライングキャパシタC1の第2端と出力電圧OUTの印加端との間に接続された第4FETに相当する。

【0068】

オシレータ205は、一定周波数のクロック信号CLKを生成する。

【0069】

インバータ206は、クロック信号CLKに応じてFET201及び202の駆動信号G20を生成する第1駆動部に相当する。駆動信号G20は、クロック信号CLKの論理反転信号となる。

【0070】

ドライバ207は、コンパレータ209から入力される検出信号S21に応じてFET203の駆動信号G21を生成する第2駆動部に相当する。駆動信号G21は、検出信号S21と同一の論理信号となる。

【0071】

ドライバ208は、コンパレータ210から入力される検出信号S22に応じてFET204の駆動信号G22を生成する第3駆動部に相当する。駆動信号G22は、検出信号S22と同一の論理信号となる。

【0072】

コンパレータ209は、FET203の両端電圧V21(=SW22−V2)に応じて検出信号S21を生成する第1検出部に相当する。検出信号S21は、FET203の両端電圧V21が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S21は、スイッチ電圧SW22の印加端から負電圧V2の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、負電圧V2の印加端からスイッチ電圧SW22の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET203またはボディダイオード203Dを介して流れる電流の向きを検出する手法は、FET203の両端電圧V21を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0073】

コンパレータ210は、FET204の両端電圧V22(=OUT−SW22)に応じて検出信号S22を生成する第2検出部に相当する。検出信号S22は、FET204の両端電圧V22が閾値電圧を上回っているときにハイレベルとなり、閾値電圧を下回っているときにローレベルとなる。すなわち、検出信号S22は、出力電圧OUTの印加端からスイッチ電圧SW22の印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にハイレベルとなり、逆に、スイッチ電圧SW22の印加端から出力電圧OUTの印加端に向けて電流が流れているとき(または同方向に電流が流れ得る状態であるとき)にローレベルとなる。なお、FET204またはボディダイオード204Dを介して流れる電流の向きを検出する手法は、FET204の両端電圧V22を監視する構成に限定されるものではなく、他の構成(例えばセンス抵抗の両端電圧を監視する構成)を採用しても構わない。

【0074】

まず、チャージポンプ回路2Xの基本動作について概略的に説明する。FET202及び204がオフとなり、FET201及び203がオンとなる第1フェイズ(充電フェイズ)では、正電圧V1の印加端から、FET201、フライングキャパシタC1、及び、FET203を介して、負電圧V2の印加端に至る経路を流れる電流によって、フライングキャパシタC1の充電が行われる。このとき、スイッチ電圧SW21は、ほぼ正電圧V1(より正確には、正電圧V1からFET201の降下電圧を差し引いた電圧)となり、スイッチ電圧SW22は、ほぼ負電圧V2(より正確には、負電圧V2にFET203の降下電圧を足し合わせた電圧)となる。従って、フライングキャパシタC1には、スイッチ電圧SW21とスイッチ電圧SW22との差分電圧(ほぼV1−V2)に相当する電荷が蓄えられる。

【0075】

その後、FET202及び204がオンとなり、FET201及び203がオフとなる第2フェイズ(放電フェイズ/電荷転送フェイズ)では、接地電圧GNDの印加端から、FET202、フライングキャパシタC1、及び、FET204を介して、出力電圧OUTの印加端に至る経路が導通されて、フライングキャパシタC1の放電(出力キャパシタC2への電荷転送)が行われる。このとき、スイッチ電圧SW21は、ほぼ接地電圧GND(より正確には、接地電圧GNDにFET202の降下電圧を足し合わせた電圧)となり、スイッチ電圧SW22は、スイッチ電圧SW21からフライングキャパシタC1の両端電圧を差し引いた電圧(ほぼV2−V1)となる。

【0076】

従って、チャージポンプ回路2Xでは、FET201〜204をオン/オフさせてフライングキャパシタC1の充放電を繰り返すことにより、負電圧V2から正電圧V1を差し引いた負の出力電圧OUT(=V2−V1)を生成することができる。

【0077】

次に、FET201〜204のオン/オフ制御について詳細に説明する。図8は、チャージポンプ回路2Xの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G20、スイッチ電圧SW21及びSW22、検出信号S21及びS22、並びに、駆動信号G21及びG22が描写されている。

【0078】

図8の例では、時刻t21まで、FET202及び204がオンされており、FET201及び203がオフされている。この状態は先述の第2フェイズに相当し、出力電圧OUTの印加端からFET204を介する経路でスイッチ電圧SW22の印加端に向けた電流が流れている。このとき、スイッチ電圧SW22は、出力電圧OUTからFET204の降下電圧を差し引いた電圧となっている。

【0079】

時刻t21において、クロック信号CLKがローレベルからハイレベルに立ち上がると駆動信号G20がハイレベルからローレベルに立ち下がるので、FET201がオンし、FET202がオフする。その結果、フライングキャパシタC1の第1端がFET201を介して正電圧V1の印加端に導通されるので、スイッチ電圧SW21が上昇し始める。また、スイッチ電圧SW22についても、フライングキャパシタC1の電荷保存則に従って、スイッチ電圧SW21と同様の挙動で上昇し始める。

【0080】

スイッチ電圧SW22の上昇に伴い、時刻t22において、FET204の両端電圧V22(=OUT−SW22)がコンパレータ210の閾値電圧を下回ると、検出信号S22がハイレベルからローレベルに切り替わる。すなわち、スイッチ電圧SW22の印加端からFET204を介する経路で出力電圧OUTの印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S22がハイレベルからローレベルに切り替わる。その結果、FET204の駆動信号G22がハイレベルからローレベルに切り替わり、FET204がオフとなる。従って、FET204に流れる逆流電流を遅滞なく遮断することができる。

【0081】

スイッチ電圧SW22がさらに低下し、時刻t23において、FET203の両端電圧V21(=SW22−V2)がコンパレータ209の閾値電圧を上回ると、検出信号S21がローレベルからハイレベルに切り替わる。すなわち、スイッチ電圧SW22の印加端からボディダイオード203Dを介する経路で負電圧V2の印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S21がローレベルからハイレベルに切り替わる。その結果、FET203の駆動信号G21がローレベルからハイレベルに切り替わり、FET203がオンとなる。この状態は先述の第1フェイズに相当し、正電圧V1の印加端から、FET201、フライングキャパシタC1、及び、FET203を介して、負電圧V2の印加端に至る経路で電流が流れ始める。このとき、スイッチ電圧SW22は、負電圧V2にFET203の降下電圧を足し合わせた電圧となる。

【0082】

なお、FET203が十分にオンするまでの間、FET203よりも順方向電圧の大きいボディダイオード203Dを介して電流が流れるので、スイッチ電圧SW22(及びSW21)にはオーバーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路2Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0083】

その後、時刻t24において、クロック信号CLKがハイレベルからローレベルに立ち下がると駆動信号G20がローレベルからハイレベルに立ち下がるので、FET201がオフし、FET202がオンする。その結果、フライングキャパシタC1の第1端がFET202を介して接地電圧GNDの印加端に導通されるので、スイッチ電圧SW21が低下し始める。また、スイッチ電圧SW22についても、フライングキャパシタC1の電荷保存則に従い、スイッチ電圧SW21と同様の挙動で低下し始める。

【0084】

スイッチ電圧SW22の低下に伴い、時刻t25において、FET203の両端電圧V21(=SW22−V2)がコンパレータ209の閾値電圧を下回ると、検出信号S21がハイレベルからローレベルに切り替わる。すなわち、負電圧V2の印加端からFET203を介する経路でスイッチ電圧SW22の印加端に向けて電流が逆流し始めたとき(または電流が逆流し得る状態となったとき)に、検出信号S21がハイレベルからローレベルに切り替わる。その結果、FET203の駆動信号G21がハイレベルからローレベルに切り替わり、FET203がオフとなる。従って、FET203に流れる逆流電流を遅滞なく遮断することができる。

【0085】

スイッチ電圧SW22がさらに低下し、時刻t26において、FET204の両端電圧V22(=OUT−SW22)がコンパレータ210の閾値電圧を上回ると、検出信号S22がローレベルからハイレベルに切り替わる。すなわち、出力電圧OUTの印加端からボディダイオード204Dを介する経路でスイッチ電圧SW22の印加端に向けて電流が流れ始めたとき(または同方向に電流が流れ得る状態となったとき)に、検出信号S22がローレベルからハイレベルに切り替わる。その結果、FET204の駆動信号G22がローレベルからハイレベルに切り替わり、FET204がオンとなる。この状態は先の第2フェイズに相当し、出力電圧OUTの印加端からFET204を介する経路でスイッチ電圧SW22の印加端に向けた電流が流れ始める。このとき、スイッチ電圧SW22は、出力電圧OUTからFET204の降下電圧を差し引いた電圧となる。

【0086】

なお、FET204が十分にオンするまでの間、FET204よりも順方向電圧の大きいボディダイオード204Dを介して電流が流れるので、スイッチ電圧SW22(及びSW21)にはアンダーシュートが生じる。ただし、このような状態は短期間であるので、チャージポンプ回路2Xの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0087】

上記で説明したように、第4実施形態のチャージポンプ回路2Xでは、FET203及び204について、意図した方向に電流が流れる状態となった方がオンされて、意図とは逆方向に電流が流れる状態となった方がオフされる。従って、FET201及び202のスイッチング途中でFET203及び204がオンされることはないので、FET201とFET203の同時オンやFET202とFET204の同時オンを確実に防止することができる。また、第4実施形態のチャージポンプ回路2Xであれば、必ず、FET203及び204の一方がオフされてから他方がオンされるので、FET203とFET204の同時オンも確実に防止することができる。

【0088】

このように、第4実施形態のチャージポンプ回路2Xであれば、各FETのオン/オフタイミングに予め一定の遅延を与えておく遅延生成方式や、一方のFETのゲート電圧がオフレベルに切り替えられたことを確認して他方のFETのゲート電圧をオンレベルに切り替えるゲート電圧モニタ方式と比べて、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、容易にかつ適切にFETのオン/オフ制御を行うことが可能となる。

【0089】

特に、フライングキャパシタの容量値に応じてスイッチ電圧の挙動が大きく変動する負出力型チャージポンプ回路の誤動作や効率低下を解消するためには、遅延生成方式やゲート電圧モニタ方式ではなく、第4実施形態の構成を採用することが望ましい。

【0090】

<第5実施形態>

図9は、チャージポンプ回路の第5実施形態(負出力型)を示す図である。第5実施形態のチャージポンプ回路2Yは、基本的に第4実施形態と同様の構成であり、ドライバ207及び208に代えて、ANDゲート211及び212を設けた点に特徴を有する。そこで、第4実施形態と同様の構成要素については、図7と同一の符号を付すことで重複した説明を割愛し、以下では、第5実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0091】

ANDゲート211の第1入力端は、コンパレータ209の出力端(検出信号S21の印加端)に接続されている。ANDゲート211の第2入力端は、オシレータ205の出力端(クロック信号CLKの印加端)に接続されている。ANDゲート211の出力端(駆動信号G21の印加端)は、FET203のゲートに接続されている。ANDゲート211は、コンパレータ209から入力される検出信号S21とオシレータ205から入力されるクロック信号CLKの双方に応じてFET203の駆動信号G21を生成する第2駆動部に相当する。駆動信号G21は、検出信号S21とクロック信号CLKがいずれもハイレベルであるときにハイレベルとなり、その余の場合にローレベルとなる。

【0092】

ANDゲート212の第1入力端は、コンパレータ210の出力端(検出信号S22の印加端)に接続されている。ANDゲート212の第2反転入力端は、オシレータ205の出力端(クロック信号CLKの印加端)に接続されている。ANDゲート212の出力端(駆動信号G22の印加端)は、FET204のゲートに接続されている。ANDゲート212は、コンパレータ210から入力される検出信号S22とオシレータ205から入力されるクロック信号CLKの双方に応じてFET204の駆動信号G22を生成する第3駆動部に相当する。駆動信号G22は、検出信号S22がハイレベルでクロック信号CLKがローレベルであるときにハイレベルとなり、その余の場合にローレベルとなる。

【0093】

図10は、チャージポンプ回路2Yの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLK、駆動信号G20、スイッチ電圧SW21及びSW22、検出信号S21及びS22、並びに、駆動信号G21及びG22が描写されている。

【0094】

チャージポンプ回路2Yの動作について、特に注目すべき点は、駆動信号G21及びG22の立下げタイミング、すなわち、FET203及び204のオフタイミングである。図10で示すように、チャージポンプ回路2Yでは、クロック信号CLKの立上がりエッジ(時刻t21など)をトリガとして駆動信号G22が立ち下がり、クロック信号CLKの立下がりエッジ(時刻t24など)をトリガとして駆動信号G21が立ち下がる。

【0095】

このように、第5実施形態のチャージポンプ回路2Yでは、FET203及び204に逆流電流が流れ始める前にFET203及び204をオフさせる構成が採用されている。従って、FET203及び204に逆流電流が流れることはないので、チャージポンプ回路2Yの誤動作や効率低下をより確実に防止することが可能となる。

【0096】

なお、チャージポンプ回路2Yでは、FET203の両端電圧V21がコンパレータ209の閾値電圧を上回っている状態のまま、FET203がオフされるので、ボディダイオード203Dに電流が流れてスイッチ電圧SW22(及びSW21)のオーバーシュートを生じる場合がある。同様に、チャージポンプ回路2Yでは、FET204の両端電圧V22がコンパレータ210の閾値電圧を上回っている状態のまま、FET204がオフされるので、ボディダイオード204Dに電流が流れてスイッチ電圧SW22(及びSW21)のアンダーシュートを生じる場合がある。ただし、このような状態はいずれも短期間であるので、チャージポンプ回路2Yの変換効率や出力電圧範囲に大きな影響を及ぼすものではない。

【0097】

<第6実施形態>

図11は、チャージポンプ回路の第6実施形態(負出力型)を示す図である。第6実施形態のチャージポンプ回路2Zは、基本的に第5実施形態と同様の構成であり、オフ検出部213及び214と遅延部215を追加した点に特徴を有する。そこで、第6実施形態と同様の構成要素については、図9と同一の符号を付すことで重複した説明を割愛し、以下では、第6実施形態の特徴部分についてのみ重点的な説明を行うことにする。

【0098】

オフ検出部213は、FET203の駆動信号G21に応じてオフ検出信号D21を生成する。オフ検出信号D21は、駆動信号G21がオフ検出用の閾値電圧を下回っていればハイレベルとなり、上回っていればローレベルとなる。

【0099】

オフ検出部214は、FET204の駆動信号G22に応じてオフ検出信号D22を生成する。オフ検出信号D22は、駆動信号G22がオフ検出用の閾値電圧を下回っていればハイレベルとなり、上回っていればローレベルとなる。

【0100】

遅延部215は、オフ検出信号D21及びD22に応じてクロック信号CLKに遅延を与える。具体的に述べると、遅延部215は、オフ検出信号D21がローレベルに切り替わるまでクロック信号CLKの立下がりを遅らせ、また、オフ検出信号D22がローレベルに切り替わるまでクロック信号CLKの立上りを遅らせる。なお、遅延部215で遅延が与えられたクロック信号CLKは、インバータ206に送出される。

【0101】

図12は、チャージポンプ回路2Zの一動作例を示すタイミングチャートであり、上から順に、クロック信号CLKと駆動信号G20〜G22が描写されている。第6実施形態のチャージポンプ回路2Zであれば、配線の寄生容量や駆動回路の遅延ばらつきに依ることなく、第1フェイズ(PHASE1)から第2フェイズ(PHASE2)へ移行する際には、まずFET203をオフし、次いでFET201をオフしてFET202をオンしてから、最後にFET204をオンするという一連のシーケンスを実現し、逆に、第2フェイズ(PHASE2)から第1フェイズ(PHASE1)へ移行する際には、まずFET204をオフし、次いでFET201をオンしてFET202をオフしてから、最後にFET203をオンするという一連のシーケンスを実現することが可能となる。

【0102】

特に、複数の半導体装置間でクロック信号のやり取りを行う負出力型のチャージポンプ回路では、上記した第6実施形態の構成を採用することが望ましい。

【0103】

<その他の変形例>

なお、本明細書中に開示されている種々の技術的特徴は、上記実施形態のほか、その技術的創作の主旨を逸脱しない範囲で種々の変更を加えることが可能である。例えば、各種信号の論理レベル反転は任意である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0104】

本発明に係る電源装置は、LCD−TV、PDP−TV、DVDレコーダ、BDレコーダなど、様々なアプリケーションの電源として利用することが可能である。

【符号の説明】

【0105】

1X、1Y、1Z チャージポンプ回路(正出力型)

100 半導体装置

101、103、104 PMOSFET

102 NMOSFET

103D、104D ボディダイオード

105 オシレータ

106〜108 インバータ

109、110 コンパレータ

111 ORゲート

112 NANDゲート

113、114 オフ検出部

115 遅延部

2X、2Y、2Z チャージポンプ回路(負出力型)

200A、200B 半導体装置

201 PMOSFET

202〜204 NMOSFET

203D、204D ボディダイオード

205 オシレータ

206 インバータ

207、208 ドライバ

209、210 コンパレータ

211、212 ANDゲート

213、214 オフ検出部

215 遅延部

C1 フライングキャパシタ

C2 出力キャパシタ

【特許請求の範囲】

【請求項1】

キャパシタの充放電用スイッチとして用いられるFETと、

前記FETに流れる電流または前記FETの両端電圧に応じて検出信号を生成する検出部と、

前記検出信号に応じて前記FETの駆動信号を生成する駆動部と、

を有することを特徴とするチャージポンプ回路。

【請求項2】

前記キャパシタの第1端と第1電圧の印加端との間に接続された第1FETと、

前記キャパシタの第1端と接地電圧の印加端との間に接続された第2FETと、

前記キャパシタの第2端と第2電圧の印加端との間に接続された第3FETと、

前記キャパシタの第2端と出力電圧の印加端との間に接続された第4FETと、

クロック信号を生成するオシレータと、

前記クロック信号に応じて前記第1FETと前記第2FETの駆動信号を生成する第1駆動部と、

前記第3FETに流れる電流または前記第3FETの両端電圧に応じて第1検出信号を生成する第1検出部と、

前記第4FETに流れる電流または前記第4FETの両端電圧に応じて第2検出信号を生成する第2検出部と、

前記第1検出信号に応じて前記第3FETの駆動信号を生成する第2駆動部と、

前記第2検出信号に応じて前記第4FETの駆動信号を生成する第3駆動部と、

を有することを特徴とする請求項1に記載のチャージポンプ回路。

【請求項3】

前記第2駆動部は、前記第1検出信号と前記クロック信号の双方に応じて前記第3FETの駆動信号を生成し、

前記第3駆動部は、前記第2検出信号と前記クロック信号の双方に応じて前記第4FETの駆動信号を生成する、

ことを特徴とする請求項2に記載のチャージポンプ回路。

【請求項4】

前記第3FETの駆動信号に応じて第1オフ検出信号を生成する第1オフ検出部と、

前記第4FETの駆動信号に応じて第2オフ検出信号を生成する第2オフ検出部と、

前記第1オフ検出信号と前記第2オフ検出信号に応じて前記クロック信号に遅延を与える遅延部と、

を有することを特徴とする請求項3に記載のチャージポンプ回路。

【請求項5】

前記第1電圧と前記第2電圧は、いずれも正電圧であることを特徴とする請求項2〜請求項4のいずれか一項に記載のチャージポンプ回路。

【請求項6】

前記第1FET、前記第3FET、及び、前記第4FETはいずれもPチャネル型であり、前記第2FETはNチャネル型であることを特徴とする請求項5に記載のチャージポンプ回路。

【請求項7】

前記第1電圧は正電圧であり、前記第2電圧は負電圧であることを特徴とする請求項2〜請求項4のいずれか一項に記載のチャージポンプ回路。

【請求項8】

前記第1FETはPチャネル型であり、前記第2FET、前記第3FET、及び、前記第4FETはいずれもNチャネル型であることを特徴とする請求項7に記載のチャージポンプ回路。

【請求項9】

前記第1FETと、前記第2FETと、前記第1駆動部と、前記オシレータは、いずれも基板に接地電圧が印加された第1半導体装置に集積化されており、

前記第3FETと、前記第4FETと、前記第1検出部と、前記第2検出部と、前記第2駆動部と、前記第3駆動部は、いずれも基板に負電圧が印加された第2半導体装置に集積化されている、

ことを特徴とする請求項8に記載のチャージポンプ回路。

【請求項10】

請求項1〜請求項9のいずれか一項に記載のチャージポンプ回路を有することを特徴とする電源装置。

【請求項1】

キャパシタの充放電用スイッチとして用いられるFETと、

前記FETに流れる電流または前記FETの両端電圧に応じて検出信号を生成する検出部と、

前記検出信号に応じて前記FETの駆動信号を生成する駆動部と、

を有することを特徴とするチャージポンプ回路。

【請求項2】

前記キャパシタの第1端と第1電圧の印加端との間に接続された第1FETと、

前記キャパシタの第1端と接地電圧の印加端との間に接続された第2FETと、

前記キャパシタの第2端と第2電圧の印加端との間に接続された第3FETと、

前記キャパシタの第2端と出力電圧の印加端との間に接続された第4FETと、

クロック信号を生成するオシレータと、

前記クロック信号に応じて前記第1FETと前記第2FETの駆動信号を生成する第1駆動部と、

前記第3FETに流れる電流または前記第3FETの両端電圧に応じて第1検出信号を生成する第1検出部と、

前記第4FETに流れる電流または前記第4FETの両端電圧に応じて第2検出信号を生成する第2検出部と、

前記第1検出信号に応じて前記第3FETの駆動信号を生成する第2駆動部と、

前記第2検出信号に応じて前記第4FETの駆動信号を生成する第3駆動部と、

を有することを特徴とする請求項1に記載のチャージポンプ回路。

【請求項3】

前記第2駆動部は、前記第1検出信号と前記クロック信号の双方に応じて前記第3FETの駆動信号を生成し、

前記第3駆動部は、前記第2検出信号と前記クロック信号の双方に応じて前記第4FETの駆動信号を生成する、

ことを特徴とする請求項2に記載のチャージポンプ回路。

【請求項4】

前記第3FETの駆動信号に応じて第1オフ検出信号を生成する第1オフ検出部と、

前記第4FETの駆動信号に応じて第2オフ検出信号を生成する第2オフ検出部と、

前記第1オフ検出信号と前記第2オフ検出信号に応じて前記クロック信号に遅延を与える遅延部と、

を有することを特徴とする請求項3に記載のチャージポンプ回路。

【請求項5】

前記第1電圧と前記第2電圧は、いずれも正電圧であることを特徴とする請求項2〜請求項4のいずれか一項に記載のチャージポンプ回路。

【請求項6】

前記第1FET、前記第3FET、及び、前記第4FETはいずれもPチャネル型であり、前記第2FETはNチャネル型であることを特徴とする請求項5に記載のチャージポンプ回路。

【請求項7】

前記第1電圧は正電圧であり、前記第2電圧は負電圧であることを特徴とする請求項2〜請求項4のいずれか一項に記載のチャージポンプ回路。

【請求項8】

前記第1FETはPチャネル型であり、前記第2FET、前記第3FET、及び、前記第4FETはいずれもNチャネル型であることを特徴とする請求項7に記載のチャージポンプ回路。

【請求項9】

前記第1FETと、前記第2FETと、前記第1駆動部と、前記オシレータは、いずれも基板に接地電圧が印加された第1半導体装置に集積化されており、

前記第3FETと、前記第4FETと、前記第1検出部と、前記第2検出部と、前記第2駆動部と、前記第3駆動部は、いずれも基板に負電圧が印加された第2半導体装置に集積化されている、

ことを特徴とする請求項8に記載のチャージポンプ回路。

【請求項10】

請求項1〜請求項9のいずれか一項に記載のチャージポンプ回路を有することを特徴とする電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−110908(P2013−110908A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−255809(P2011−255809)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]