ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ディジタル制御発振装置および高周波信号処理装置に関し、特に、無線通信システム用のDCO(Digitally controlled oscillator)回路、DCO回路を含むPLL(Phase Locked Loop)回路、ならびにPLL回路を含む無線通信用高周波信号処理装置に適用して有効な技術に関する。

【背景技術】

【0002】

例えば、非特許文献1には、シグマデルタ変調回路を用いて分数容量を実現する方式が示されている。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Robert Bogdan Staszewski、他3名、“Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS process”、IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing、VOL.50、NO.11、p.815-828、2003年11月

【発明の概要】

【発明が解決しようとする課題】

【0004】

例えば、携帯電話機を代表とする無線通信システムには、主にベースバンド信号と高周波信号との間の周波数変換を担う高周波信号処理装置が備わっている。このような高周波信号処理装置は、例えば、PLL回路やミキサ回路等を備え、PLL回路によって生成した送信用/受信用のキャリア信号(ローカル信号、局部発振信号)をミキサ回路に入力することで周波数変換を行う。こうした中、従来において広く用いられていたアナログPLL回路を、ディジタル回路で構成されるディジタルPLL回路に置き換える技術が注目されている。ディジタルPLL回路は、ADPLL(All Digital Phase Locked Loop)等とも呼ばれる。ディジタルPLL回路を用いると、例えば、CMOS(Complementary Metal Oxide Semiconductor)プロセスによる微細化技術を享受できるため、その進歩に伴い小面積化、低電源電圧化、高性能化(高速化)等が図れる。

【0005】

図20は、本発明の前提として検討したディジタル制御発振装置において、その概略構成例を示すブロック図である。図20に示すディジタル制御発振装置DPLLcは、時間差検出回路TDC、ディジタルロウパスフィルタDLPF、ディジタル制御発振回路DCOc、マルチモジュラス周波数分周回路MMD、シグマデルタ変調回路SDM、ならびにDCO用シグマデルタ変調回路SDDCOを備えている。DCOcから出力された発振出力信号PLLOUTは、MMDによって分周され、TDCは、当該分周発振信号FDIVと基準発振信号REFとの時間差(位相差)を検出する。DLPFは、TDCの検出結果を平滑化し、その結果に基づく整数容量値制御信号W_INTをDCOcに出力する。また、DLPFの出力は、SDDCOを介して、分数容量値制御信号W_FRACとしてDCOcに入力される。

【0006】

SDMは、分周比設定コードDAT−DIVNに基づいて、MMDに分周比を設定すると共に、当該分周比を時系列的に可変制御することで小数部分を含んだ分周比を設定する。この分周比の変化は、TDC、DLPFを介して整数容量値制御信号W_INTに反映される。DCOcは、例えば無線通信システム用等の場合、図示は省略するが、通常、LC共振型で構成され、このC(容量)の値(具体的には発振ノードに接続する容量の個数)を順次制御することで発振周波数の制御を行う。この際の容量の個数は、W_INTによって定められ、この場合の発振周波数の設定分解能は、容量1個分の変化量に依存して定められる。

【0007】

しかしながら、容量1個分の変化量では、所望の発振周波数の設定分解能が得られない場合がある。すなわち、SDMがMMDに対して設定した小数部分を含んだ分周比を高精度に実現できない場合がある。そこで、SDDCOは、MMDの出力ならびにDLPFの出力を受けて、等価的に容量1個分よりも小さい容量の変化量を実現できるように、W_FRACを用いてDCOcを制御する。具体的には、例えば、W_INTに応じて1個の容量を発振ノードに接続する(便宜上オンと呼ぶ)期間をTonとすると、W_FRACによって、当該1個の容量を例えば(Ton/8)の期間でオンに駆動する。その結果、等価的に、1/8個の容量が実現できることになる。なお、SDDCOは、実際には、この容量をオンに制御するタイミングを適宜可変制御する。

【0008】

このように、DCO用シグマデルタ変調回路SDDCOを用いると、発振周波数の設定分解能を向上(DCO利得を低減)させることが可能になる。シグマデルタ変調回路は、広く知られているようにオーバーサンプリングやノイズシェービングによって発振周波数近傍の雑音特性を抑制している。ただし、その代わりに遠方の雑音特性が劣化する(発振周波数を基準にオフセット周波数の高い方の雑音が増加する)ことになる。したがって、例えば、図20のようなDPLLcをFDD(Frequency Division Duplex)方式の無線通信システムの送信部に適用した場合、前述した発振周波数遠方の雑音が、送信帯域から所定の周波数離れた受信帯域に影響を及ぼす恐れがある。

【0009】

これを回避するためには、例えば、シグマデルタ変調回路のサンプリング周波数を高くすることが考えられる。この場合、消費電力や面積が増大する恐れがある。また、送信部にSAW(Surface Acoustic Wave)フィルタを設け、これによって発振周波数遠方の雑音を抑制することが考えられる。ただし、SAWフィルタは、通常、単体の外部部品となるため、無線通信システムにおけるコストの低減や小型化が困難となる恐れがある。

【0010】

そこで、本発明の目的の一つは、発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供することにある。本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

【0012】

本実施の形態によるディジタル制御発振装置は、相補の発振出力信号が出力される第1及び第2発振出力ノードと、コイル素子と、複数の容量ユニットと、負性抵抗生成回路とを備える。コイル素子(LP,LM)は、第1発振出力ノード(OscP)と前記第2発振出力ノード(OscM)の間に結合される。複数の容量ユニット(CIU)は、それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備える。負性抵抗生成回路(AMPBK)は、第1発振出力ノードと第2発振出力ノードの間に負性抵抗を生成する。ここで、複数の容量ユニットの一部は複数の第1容量ユニットとして第1容量バンク(CINT)を構成し、複数の容量ユニットの他の一部は第2容量バンク(CFRAC)を構成する。複数の第1容量ユニットの第1ノードは第1発振出力ノードに、第2ノードは第2発振出力ノードにそれぞれ結合される。第2容量バンクは、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロック(CFBK)を含む。容量ブロックは、N個の容量ユニットの1個となる第2容量ユニット(CIU[1])と、第2容量ユニット以外となる(N−1)個の第3容量ユニット(CIU[2]〜CIU[k])とを備える。第2容量ユニットの第1ノードは第1発振出力ノードに、第2ノードは第2発振出力ノードにそれぞれ結合される。(N−1)個の第3容量ユニットにおける第1及び第2ノードは、交流的な接地電源電圧(V6)に結合される。第2容量ユニットにおける第1容量素子の第1スイッチ側のノード(SWFD)は、(N−1)個の第3容量ユニットにおける第1容量素子の第1スイッチ側のノードと共通に結合される。第2容量ユニットにおける第2容量素子の第1スイッチ側のノード(SWFS)は、(N−1)個の第3容量ユニットにおける第2容量素子の第1スイッチ側のノードと共通に結合される。第2容量ユニット及び(N−1)個の第3容量ユニットにおける第1スイッチ(SWF1)は、オン・オフが共通に制御される。

【0013】

このような構成を用いると、DCO用シグマデルタ変調回路を用いずに分数容量を実現することが可能になり、発振周波数遠方の雑音を低減することが可能になる。また、高精度な分数容量を実現可能になる。

【発明の効果】

【0014】

本願において開示される発明のうち、代表的な実施の形態によって得られる効果を簡単に説明すると、発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置が実現可能になる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的な構成例を示す回路図である。

【図2】図1のディジタル制御発振回路において、その各単位容量ユニット内のスイッチ周りの詳細な構成例を示す回路図である。

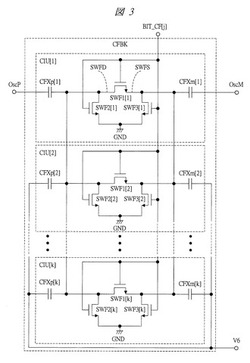

【図3】図1のディジタル制御発振回路において、その容量バンク(分数値用)内の分数値用容量ブロックの詳細な構成例を示す回路図である。

【図4】図3の分数値用容量ブロックの動作原理の一例を表す説明図である。

【図5】(a)、(b)は、図3の分数値用容量ブロックの動作原理の一例を表す説明図である。

【図6】図1のディジタル制御発振回路において、その容量バンク(分数値用)の概略構成例を示すブロック図である。

【図7】本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的なレイアウト構成例を示す平面図である。

【図8】図7のディジタル制御発振回路において、その容量バンク(整数値用)周りのレイアウト概要の一例を表す模式図である。

【図9】図7のディジタル制御発振回路において、その容量バンク(分数値用)のレイアウト概要の一例を表す模式図である。

【図10】図9における分数値用容量ブロック(1/8用)周りのレイアウト概要の一例を示す模式図である。

【図11】図8のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例ならびにデバイス断面構造例を示す平面図および断面図である。

【図12】図10のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例を示す平面図である。

【図13】本発明の実施の形態1によるディジタル制御発振装置において、図1のディジタル制御発振回路を適用したディジタルPLL回路の概略構成例を示すブロック図である。

【図14】図6および図13の動作例を表す概念図である。

【図15】図13のディジタルPLL回路を対象に行ったノイズ特性の検証結果の一例を示す図である。

【図16】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示すブロック図である。

【図17】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す他のブロック図である。

【図18】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。

【図19】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。

【図20】本発明の前提として検討したディジタル制御発振装置において、その概略構成例を示すブロック図である。

【図21】図3の分数値用容量ブロックの比較例を示すものであり、(a)はその構成例を示す回路図、(b)は、(a)において各スイッチをオンに制御した場合の等価回路図、(c)は、(a)において各スイッチをオフに制御した場合の等価回路図である。

【発明を実施するための形態】

【0016】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0017】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0018】

また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。なお、実施の形態では、MISFET(Metal Insulator Semiconductor Field Effect Transistor)の一例としてMOSFET(Metal Oxide Semiconductor Field Effect Transistor)(MOSトランジスタと略す)を用いるが、ゲート絶縁膜として非酸化膜を除外するものではない。

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0020】

(実施の形態1)

《ディジタル制御発振回路の概略回路構成》

図1は、本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的な構成例を示す回路図である。図1に示すディジタル制御発振回路DCOは、アンプ回路ブロックAMPBKと、コイル素子LP,LMと、3系統の容量バンクCABS,CINT,CFRACと、デコーダ回路DECを備えている。AMPBKは、負性抵抗回路として機能し、正極側発振出力ノードOscPを入力、負極側発振出力ノードOscMを出力として反転動作を行うアンプ回路AMPMと、その逆に、OscMを入力、OscPを出力として反転動作を行うアンプ回路AMPPを備える。

【0021】

AMPP,AMPMのそれぞれは、特に限定はされないが、代表的にはPMOSトランジスタとNMOSトランジスタからなるCMOSインバータ回路で構成される。AMPP,AMPMは、高電位側の固定電圧(例えば電源電圧VDD1)V1と低電位側の固定電圧(例えば接地電源電圧GND1)V2によって動作する。なお、AMPP,AMPMのそれぞれは、場合によっては1個のNMOSトランジスタで構成する(すなわちAMPBKをクロスカップル接続(一方のゲートが他方のドレインに接続)された2個のNMOSトランジスタで構成する)ことも可能である。LPは、一端がOscPに接続され、LMは、一端がOscMに接続され、LP,LMの他端には固定電圧(例えばVDD1又はGND1)V3が供給される。

【0022】

CABSは、周波数帯(バンド)調整用であり、一端がOscPに接続される容量素子CApと、一端がOscMに接続される容量素子CAmと、CApの他端とCAmの他端の間に接続されるスイッチSWAを備える。ここでは、CAp,SWA,CAmからなる一組の回路が代表的に示されているが、実際には、このような回路がOscPとOscMの間に複数組設けられる。CINTは、整数値調整用であり、一端がOscPに接続される容量素子CIpと、一端がOscMに接続される容量素子CImと、CIpの他端とCImの他端の間に接続されるスイッチSWIを備え、実際には、このような回路がOscPとOscMの間に複数組設けられる。CFRACは、分数値調整用であり、一端がOscPに接続される容量素子CFpと、一端がOscMに接続される容量素子CFmと、CFpの他端とCFmの他端の間に接続されるスイッチSWFを備え、実際には、このような回路がOscPとOscMの間に複数組設けられる。

【0023】

SWAは、自動バンド制御信号W_ABSによってオン・オフが制御され、SWI,SWFは、デコーダ回路DECによってオン・オフが制御される。DECは、高電位側の固定電圧(例えば電源電圧VDD2)V4と低電位側の固定電圧(例えば接地電源電圧GND2)V5によって動作する。DECは、整数容量値制御信号W_INT、および分数容量値制御信号W_FRACを入力とし、W_INTに応じてオン・オフ制御線(オン・オフ制御信号)BIT_CIを介してSWIのオン・オフを制御し、W_FRACに応じてオン・オフ制御線(オン・オフ制御信号)BIT_CFを介してSWFのオン・オフを制御する。

【0024】

ここでは、CINT内のCIp,SWI,CImからなる1組を単位容量ユニットCIUと呼ぶ。また、CFRAC内のCFp,SWF,CFmからなる1組を分数値用容量ブロックCFBKと呼ぶ。BIT_CIは、前述したように、CINT内に複数組のCIUが設けられるため、これに応じて複数本で構成され、BIT_CFも同様に複数本で構成される。DECは、例えば、W_INTの値が「1」変動する毎に、BIT_CIを介してSWIをオンに制御するCIUの数を「1」ずつ変動させる。

【0025】

このようなディジタル制御発振回路DCOは、コイル素子LP,LMと容量バンクCABS,CINT,CFRAC内の各容量素子によるLC共振型の構成となっており、OscP,OscMに相補の発振出力信号を出力する。この際に、AMPBKは、当該LC部分の寄生抵抗成分を打ち消す負性抵抗回路として機能する。当該発振回路の発振周波数は、CABS,CINT,CFRAC内の各スイッチのオン・オフによって制御され、主として、スイッチがオンに制御された組に含まれる容量素子が発振周波数を定めるパラメータとして寄与する。

【0026】

ここで、CABS,CINT,CFRAC内の各容量素子の実効的な容量値の関係は、CAp(=CAm)>CIp(=CIm)>CFp(=CFm)となっている。これにより、例えば、W_ABS(CABS)によって2MHz単位、W_INT(CINT)によって10kHz単位、W_FRAC(CFRAC)によって0.625kHz単位でそれぞれ発振周波数が調整される。特に限定はされないが、CABSでは、2MHz単位で512ステップ(約1GHzレンジ)の調整が行われ、CINTでは、10kHz単位で、2048ステップ(約20MHzレンジ)の調整が行われる。

【0027】

このような構成において、本実施の形態1のディジタル制御発振装置の主要な特徴の一つは、詳細は後述するが、CFRAC内のCFBKが、CINT内のCIUと同一の回路構成および略同一のレイアウト構成を持つ容量ユニットを複数組み合わせて構成され、これによって、CINTよりも小さい周波数分解能を実現する点にある。このようなCFBKを設けることで、シグマデルタ変調回路(すなわち図20のSDDCO)等を使用することなく、所定の周波数分解能を実現できるため、代表的には発振周波数遠方の雑音を低減することが可能になる。その結果、前述したようにシグマデルタ変調回路のサンプリング周波数を上げることによる消費電力の増大や面積の増大を抑制でき、また、送信部においてSAWフィルタ等が不要となることから、無線通信システムにおけるコストの低減や小型化等が図れる。

【0028】

《スイッチの詳細構成》

図2は、図1のディジタル制御発振回路において、その各単位容量ユニット内のスイッチ周りの詳細な構成例を示す回路図である。図2には、図1における容量バンクCINT内の1個の単位容量ユニットCIUを代表として、その構成例が示されている。図2の例では、スイッチSWIが、容量素子CIpとCImの間に設けられた3個のスイッチSWI1〜SWI3で構成される。SWI1は、CIpの一端(ノードSWID)とCImの一端(ノードSWIS)との間にソース・ドレイン経路が形成されたNMOSトランジスタで構成される。SWI2は、SWIDと接地電源電圧GNDの間にソース・ドレイン経路が形成されたNMOSトランジスタで構成され、SWI3は、SWISとGNDの間にソース・ドレイン経路が形成されたNMOSトランジスタで構成される。GNDは、例えば図1におけるGND2が用いられる。SWI1〜SWI3を構成する各NMOSトランジスタのゲートは、CIUが備えるオン・オフ制御ノードBITNDに接続され、このBITNDが前述した複数のオン・オフ制御線BIT_CIのいずれか1本(BIT_CI[n])で駆動される。

【0029】

ここで、BIT_CI[n]が‘H’レベルに駆動された場合、SWIDとSWISが電気的に接続されると共にGNDに短絡される。この場合、CIp,CImは、発振出力ノードOscP,OscMにおいて発振周波数を設定する際のパラメータとして寄与する。一方、BIT_CI[n]が‘L’レベルに駆動された場合、SWIDとSWISは、電気的に分離され、共にハイインピーダンス状態となる。この場合、CIp,CImは、理想的には、発振周波数を設定する際のパラメータとして寄与しない。すなわち、オン・オフ制御ノードBITNDは、発振周波数を設定する際のパラメータとして容量素子CIp,CImを寄与させるか否かを選択する機能を持つ。

【0030】

なお、スイッチSWIの構成は、勿論、図2のような構成に限定されるものではなく、様々に変更することが可能である。例えば、図2において、原理的には、SWI1をオンに駆動することでノードSWID,SWISは交流的に仮想接地とみなせるため、SWI2,SWI3は不要である。ただし、実際には、差動バランスのミスマッチや、SWI1の時定数等に応じて仮想接地からの誤差が生じ得るため、SWID,SWISを交流的に接地するスイッチ(図2の例ではSWI2,SWI3)を設ける方が望ましい。また、容量素子CIp,CImは、特に限定はされないが、特性ばらつきを低減する観点等から例えばMIM(Metal Insulator Metal)容量やMOM(Metal Oxide Metal)容量等を用いるとよい。

【0031】

《容量バンク(分数値用)の構成(本実施の形態1の主要な特徴)》

図3は、図1のディジタル制御発振回路において、その容量バンク(分数値用)内の分数値用容量ブロックの詳細な構成例を示す回路図である。図3に示す分数値用容量ブロックCFBKは、前述した整数値用容量バンクCINT内の単位容量ユニットと同一の回路構成を持つk(kは2以上の整数)個の単位容量ユニットCIU[1]〜CIU[k]を備えている。CIU[1]は、図2の構成例と同様に、図2のCIp,CImに対応する容量素子CFXp[1],CFXm[1]と、図2のSWI1,SWI2,SWI3に対応するスイッチSWF1[1],SWF2[1],SWF3[1]を備える。同様に、CIU[k]は、図2のCIp,CImに対応する容量素子CFXp[k],CFXm[k]と、図2のSWI1,SWI2,SWI3に対応するスイッチSWF1[k],SWF2[k],SWF3[k]を備える。

【0032】

CIU[1]〜CIU[k]において、発振出力ノードOscP側の容量素子CFXp[1]〜CFXp[k]は、スイッチ側のノードSWFDが共通に接続され、同様に、発振出力ノードOscM側の容量素子CFXm[1]〜CFXm[k]も、スイッチ側のノードSWFSが共通に接続される。一方、OscP側のCFXp[1]〜CFXp[k]において、スイッチ側のノードSWFDと対向する側のノードは、CFXp[1]のみがOscPに接続され、残りのCFXp[2]〜CFXp[k]は共通に固定電圧V6に接続される。同様に、OscM側のCFXm[1]〜CFXm[k]において、スイッチ側のノードSWFSと対向する側のノードは、CFXm[1]のみがOscMに接続され、残りのCFXm[2]〜CFXm[k]は共通にV6に接続される。V6は、交流的な接地電源電圧であり、特に限定はされないが、例えば、図1におけるGND2やGND1等を用いればよい。また、各スイッチ(SWF1[1],SWF2[1],SWF3[1])〜(SWF1[k],SWF2[k],SWF3[k])のオン・オフは、図1における複数のオン・オフ制御線BIT_CFのいずれか1本(BIT_CF[j])によって共通に制御される。

【0033】

図4および図5(a)、(b)は、図3の分数値用容量ブロックの動作原理の一例を表す説明図である。図4には、図3の分数値用容量ブロックCFBKに含まれる単位容量ユニットCIU[1]〜CIU[k]の内のCIU[1]が示されている。ここでは、当該CIU[1]を、CIU[2]〜CIU[k]と区別して基準単位容量ユニットと呼ぶ。基準単位容量ユニットCIU[1]は、図4に示すように、前述した容量素子CFXp,CFXmおよびスイッチSWF1〜SWF3に加えて、実際には、寄生容量CPp,CPmを含んでいる。CPpは、ノードSWFDと接地電源電圧GNDの間に存在し、CPmは、ノードSWFSとGNDの間に存在する。ここで、CFXp,CFXmの容量値を共にC1とし、CPp,CPmの容量値を共にCPとする。

【0034】

図5(a)には、図4におけるスイッチSWF1〜SWF3が共にオンに駆動された場合の等価回路が示されている。この場合、OscPから当該基準単位容量ユニットCIU[1]側を見た場合の容量値Conは、図4のノードSWFDがGNDに接続されるためCon=C1となる。一方、図5(b)には、図4におけるSWF1〜SWF3が共にオフに駆動された場合の等価回路が示されている。この場合、OscPから当該基準単位容量ユニットCIU[1]側を見た場合の容量値Coffは、図4のノードSWFDがハイインピーダンスとなるため、CFXpとCPpとの直列接続に伴い式(1)となる。その結果、SWF1〜SWF3のオン・オフに伴う容量値の変化量ΔCintは、式(2)となる。

【0035】

Coff=(C1・CP)/(C1+CP) (1)

ΔCint=Con−Coff=C12/(C1+CP) (2)

ここで、図5のCPをCP’に置き換えることで、ΔCintの容量値を1/Kにすることを考える。すなわち、基準単位容量ユニットCIU[1]における容量値の変化量(図1のCINT内のCIUにおける変化量に等しい)を1/Kとし、発振周波数の分解能をCINT内のCIUのK倍(DCO利得を1/K)に向上させることを考える。この場合、目的とする変化量ΔCfは、式(2)を用いて式(3)で与えられる。そして、式(3)より、式(4)の関係が導かれる。

【0036】

ΔCf=C12/(C1+CP’)=ΔCint/K=C12/(K・(C1+CP)) (3)

Cp’=(K−1)・C1+K・CP (4)

式(4)から判るように、ΔCintの容量値を1/Kにするためには、図5(a)、(b)におけるCPp(容量値CP)の代わりに、(K−1)個のC1とK個のCPとを並列に接続すればよい。これを実現したものが前述した図3の回路構成である。すなわち、図3において、ノードSWFDとV6(=GND)の間には、CFXp[2]〜CFXp[k]に伴う(K−1)個のC1が並列接続され、更に、SWFDには、CIU[1]〜CIU[k]に伴うK個のCPが並列接続される。なお、ここでは、OscP側を例として説明を行ったが、勿論、OscM側に関しても同様である。

【0037】

これにより、例えば、ΔCintの1/2の容量変化量を実現する分数値用容量ブロックCFBKは、図3においてCIU[1]とCIU[2]を備えた構成となり、また、ΔCintの1/4の容量変化量を実現するCFBKは、図3においてCIU[1]〜CIU[4]を備えた構成となる。この際に、各CIU[1]〜CIU[4]は、同一の回路構成(実質的に同一のレイアウト構成)を備えているため、それぞれの各容量素子CFXp,CFXmの容量値を高精度に同一値(C1)に設定できることに加えて、各寄生容量CPp,CPmの容量値も高精度に同一値(CP)に設定できる。その結果、CINT内のCIUを基準として、そのK倍の発振周波数の分解能を高精度に実現可能となり、図1で述べた各種効果に加えて、例えばDNL(Differential Non linearity)の向上等が図れる。

【0038】

図6は、図1のディジタル制御発振回路において、その容量バンク(分数値用)の概略構成例を示すブロック図である。図6に示す容量バンクCFRACは、発振出力ノードOscPとOscMとの間に、複数(ここでは4個)の分数値用容量ブロックCFBK_N2,CFBK_N4,CFBK_N8,CFBK_N16を備えている。CFBK_N2は、容量バンク(整数値用)CINT内の各単位容量ユニットCIUにおける容量変化量の1/2の変化量を実現する。具体的には、図3におけるCIU[1],CIU[2]を備え、その各スイッチSWF1([1][2])〜SWF3([1][2])がオン・オフ制御線BIT_CF[2]で制御される。

【0039】

また、CFBK_N4は、CINT内のCIUにおける容量変化量の1/4の変化量を実現し、図3におけるCIU[1]〜CIU[4]を備える。同様に、CFBK_N8は、CINT内のCIUにおける容量変化量の1/8の変化量を実現するため図3におけるCIU[1]〜CIU[8]を備え、CFBK_N16は、CINT内のCIUにおける容量変化量の1/16の変化量を実現するため図3におけるCIU[1]〜CIU[16]を備える。CFBK_N4,CFBK_N8,CFBK_N16内の各スイッチは、それぞれオン・オフ制御線BIT_CF[4],BIT_CF[8],BIT_CF[16]で制御される。

【0040】

これによって、例えば、CINT内のCIUにおける発振周波数の調整幅を10kHzとして、BIT_CF[16]によるオン・オフ制御によって0.625(=10/16)kHzの調整幅が実現でき、BIT_CF[8]によるオン・オフ制御によって1.25(=10/8)kHzの調整幅が実現できる。また、例えば、BIT_CF[16]によるオン・オフ制御とBIT_CF[8]によるオン・オフ制御を組み合わせることで、1.875(0.625+1.25)kHzの調整幅が実現できる。以降、同様にして、各BIT_CF([2],[4],[8],[16])を適宜組み合わせることで、10kHzの間を0.625kHz単位(16階調)で任意に調整することが可能になる。なお、ここでは、(1/24)を実現するCFBK_N16までの分数値用容量ブロックを設けたが、勿論、同様にして(1/2N)(Nは5以上の整数)対応の分数値用容量ブロックを設けることで、順次、分解能の向上が図れる。

【0041】

《容量バンク(分数値用)の構成(比較例)》

図21は、図3の分数値用容量ブロックの比較例を示すものであり、図21(a)はその構成例を示す回路図、図21(b)は、図21(a)において各スイッチをオンに制御した場合の等価回路図、図21(c)は、図21(a)において各スイッチをオフに制御した場合の等価回路図である。図21(a)に示すように、例えば、CINT内のCIUにおける容量変化量の分数を、単純に複数の容量素子の直列接続によって実現する方式が考えられる。図21(a)の例では、1/2の分数を実現するため、例えばOscPとスイッチ側のノードSWFDとの間に、OscP側から順に容量素子CFp2とCFp1が接続されている。

【0042】

当該方式において、図3の場合と同様にして、各スイッチがオンに駆動された際(図21(b)の際)の容量値Conと、各スイッチがオフに駆動された際(図21(c)の際)の容量値Coffとの変化量ΔCf2(=Con−Coff)を求めると、式(5)が得られる。式(5)において、CP1は、CFp1のスイッチ側のノードSWFDに存在する寄生容量CPp1の容量値であり、CP2は、CFp1とCFp2との間のノードに存在する寄生容量CPp2の容量値である。

【0043】

【数1】

【0044】

一方、CINT内のCIUにおける容量変化量は、前述した式(2)のΔCintで与えられる。そこで、ΔCf2=(1/2)・ΔCintとしてその解を求めると、式(6)が得られる。

【0045】

(4・CP1+3・CP2)C12+CP1・CP22=2・CP・C12 (6)

式(6)を満たす一つの解は、「CP1=CP/2」かつ「CP2=0」である。ただし、寄生容量をゼロにする後者の解は事実上不可能であり、前者は、配線とスイッチの寄生容量を含めてCP1を高精度にCP(すなわちCINT内のCIUの寄生容量)の1/2に設計することを意味し、非常に困難と言える。仮にスイッチのサイズにより調整できたとしてもデバイスばらつきや温度変動で変動してしまうため、高い歩留まりが求められる高周波信号処理等に適用することは困難である。上記以外にも解はあるものの、いずれもCP1およびCP2をCP以下に設計する必要があり、結局、当該容量ユニットとCINT内のCIUとの間の相対ばらつきの問題に帰結する。一方、図3の方式を用いると、CINT内のCIUと同じ構成のCIUを用いて分数容量が形成されるため、CINT内のCIUとの間で相対ばらつきが少なく、さらに各半導体チップ毎のデバイスばらつきもCINT内のCIUとほぼ均一に生じるため、高精度な分周容量が実現可能になる。

【0046】

《ディジタル制御発振回路の概略レイアウト構成》

図7は、本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的なレイアウト構成例を示す平面図である。図7に示す各符号は、図1に示した各符号に対応している。図7に示すディジタル制御発振回路DCOは、略リング状に形成され、Y軸対称に配置されたメタル配線(LP,LM)を備えている。当該メタル配線は、その中点(中点タップ)に固定電圧(交流的な接地電源電圧)V3が印加され、当該中点タップを基準として一方の側でコイル素子LPを実現し、他方の側でコイル素子LMを実現する。当該リングの内側には、Y軸方向に向けて順に第1領域AR1、第2領域AR2、第3領域AR3が設けられる。

【0047】

AR2には、容量バンクCINT,CFARCが配置され、AR3には、ロジック回路LOGが配置される。LOGは、当該リング(LP,LM)の外側に配置されたロジック制御回路IOLを含めて図1のデコーダ回路DECを構成し、IOLからの制御に応じてCINT,CFRAC内の各単位容量ユニットを制御する。ここで、CINT,CFRACは、前述したように実質的に同一のレイアウトを持つ複数の単位容量ユニットCIUによって構成され、詳細は後述するが、その一部でCINTが構成され、他の一部でCFRACが構成される。Y軸方向において、CINT,CFRACの両側の一方にはLPから分岐してX軸方向に沿って延伸する配線が配置され、他方にはLMから分岐してX軸方向に沿って延伸する配線が配置される。前者の配線は発振出力ノードOscPとなり、後者の配線は発振出力ノードOscMとなる。

【0048】

AR1には、X軸方向においてアンプ回路AMPP,AMPMを挟んで両側に容量バンクCABSが分割して配置される。Z軸方向において、AMPP,AMPMおよびCABSの上層には、LPから分岐してX軸方向に沿って延伸する配線(すなわちOscP)と、LMから分岐してX軸方向に沿って延伸する配線(すなわちOscM)が配置され、AMPP,AMPM,CABSは、当該OscP,OscMに適宜接続される。ここで、AR1は、Y軸方向において当該リング(LP,LM)の略中間部分に配置され、これに伴いAMPP,AMPMは、当該リングの略中心部分に配置される。このようなAMPP,AMPMの配置によって、LC回路における共振周波数を1個に設定することが可能となり、発振周波数の高精度化や発振出力信号の高品質化等が図れる。

【0049】

すなわち、例えば、AMPP,AMPNを当該リング(LP,LM)の端部(例えば図7においてAR3を挟んでAR2と対向する領域等)に配置した場合を想定する。この場合、AMPP,AMPNMからLC回路側を見た場合に、CABSが最も大きな容量であるため、等価的に、LP,LMの一部(AMPP,AMPMからCABSまでの配線)を介してCABS,CINT,CFRACとLP,LMの他の部分に伴う第1のLC回路が見える。そのため、上述したLP,LMの一部とCABS,CINT,CFRACに伴う第2の直列LC回路がAMPP,AMPMから見え、これが不要な共振周波数を発生させる。この不要な共振周波数が必要な共振周波数よりも十分大きい場合は問題とならないが、不要な共振周波数は、AMPP,AMPMからCABSまでの距離が長いほど低くなる。したがってAMPP,AMPMとCABSはできるだけ近づける必要がある。図7のようなレイアウト構成例を用いると、AMPP,AMPMが当該リング(LP,LM)の略中心部分に配置されるため、このような遠近差の影響を緩和できる。

【0050】

《容量バンク(整数値用)のレイアウト概要》

図8は、図7のディジタル制御発振回路において、その容量バンク(整数値用)周りのレイアウト概要の一例を表す模式図である。図8に示す容量バンクCINTでは、簡略化して、8行×4列のマトリックス状に32個の単位容量ユニットCIUが配置されている。ただし、CINTは、実際には、例えば、32行×64列のマトリックスに伴う2048個のCIUを備える。図8において、発振出力ノードOscPは、行方向に沿って延伸する発振出力ノード(発振出力配線)OscPrと、そこから等間隔で分岐し、列方向に沿って並んで延伸する4本の発振出力ノード(発振出力配線)OscPc[0]〜OscPc[3]を含む。同様に、発振出力ノードOscMは、行方向に沿って延伸する発振出力ノード(発振出力配線)OscMrと、そこから等間隔で分岐し、列方向に沿って並んで延伸する4本の発振出力ノード(発振出力配線)OscMc[0]〜OscMc[3]を含む。

【0051】

OscPc[0]とOscMc[0]は互いに近接して配置され、以降同様にして、OscPc[3]とOscMc[3]も互いに近接して配置される。また、OscPrとOscMrは、32個のCIUを列方向で挟んで両側に配置される。OscPc[0],OscMc[0]の配線経路上には、1列目となる8個のCIUが順次配置され、当該各CIUは、OscPc[0],OscMc[0]に対して接続される。以降同様にして、OscPc[3],OscMc[3]の配線経路上には、4列目となる8個のCIUが順次配置され、当該各CIUは、OscPc[3],OscMc[3]に対して接続される。

【0052】

また、1列目となる8個のCIUの近傍には、列方向に沿って並んで延伸する複数本(ここでは4本)のオン・オフ制御線BIT_CI[0]〜BIT_CI[3]が配置される。2列目、3列目および4列目に対しても同様に、各列を構成する8個のCIUの近傍に、列方向に沿って並んで延伸する複数本(ここでは4本)のオン・オフ制御線が各列毎に配置される。1列目に対応するオン・オフ制御線は、ロジック回路LOG[0]によって駆動され、以降同様にして、2列目、3列目、4列目の対応するオン・オフ制御線は、それぞれロジック回路LOG[1],LOG[2],LOG[3]によって駆動される。ロジック回路LOG[0]〜LOG[3]は、ロジック制御回路IOLと共にデコーダ回路DECを構成する。DECは、CIUのマトリックス領域のいずれか一辺(ここではOscMr側の一辺)に沿って配置される。

【0053】

LOG[0]は、1列目に含まれる8個のCIUを対象に、BIT_CI[0]を用いて1個のCIUを制御し、BIT_CI[1]を用いて2個のCIUを制御し、BIT_CI[2]を用いて4個のCIUを制御し、BIT_CI[3]を用いて1個のCIUを制御する。具体的には、例えばBIT_CI[1]を用いて2個のCIU内に含まれる各スイッチ(図2のSWI1〜SWI3)のオン・オフを共通に制御する。したがって、例えば、BIT_CI[0]のみをオンレベルに駆動すれば、OscPc[0],OscMc[0]にそれぞれ1個の容量素子(図2のCIp,CIm)が付加され、BIT_CI[1]のみをオンレベルに駆動すれば、OscPc[0],OscMc[0]にそれぞれ2個の容量素子が付加される。更に、BIT_CI[0],BIT_CI[1]をオンレベルに駆動すれば、OscPc[0],OscMc[0]にそれぞれ3個の容量素子が付加される。以降、同様にしてBIT_CI[0]〜BIT_CI[3]のオンレベル・オフレベルを適宜組み合わせることで、OscPc[0],OscMc[0]に対して4個〜8個の容量素子を付加することが可能になる。

【0054】

LOG[2]〜LOG[3]に関しても同様であり、例えば、LOG[3]は、BIT_CI[0]〜BIT_CI[3]のオンレベル・オフレベルを適宜組み合わせることで、OscPc[3],OscMc[3]に対して0個〜8個の容量素子を適宜付加することが可能になる。また、ロジック制御回路IOLは、LOG[0]〜LOG[3]のいずれかを選択して、前述したBIT_CI[0]〜BIT_CI[3]のオンレベル・オフレベルの指示を与えると共に、LOG[0]〜LOG[3]のそれぞれに対して、BIT_CI[0]〜BIT_CI[3]全体をオンレベル又はオフレベルに駆動するための命令を与える。これによって、例えば、OscP,OscMに対してそれぞれ9個の容量素子を付加する場合には、LOG[0]においてBIT_CI[0]〜BIT_CI[3]全体をオンレベルに駆動させた状態で、LOG[1]を選択し、LOG[1]においてBIT_CI[0]のみを駆動させればよい。

【0055】

《容量バンク(分数値用)のレイアウト概要》

図9は、図7のディジタル制御発振回路において、その容量バンク(分数値用)のレイアウト概要の一例を表す模式図である。図9の例では、分数値用の容量バンクCFRACは、整数値用の容量バンクCINTと隣接して配置される。言い換えれば、図8に示したように、複数の単位容量ユニットがマトリックス状に配置され、その一部の領域によってCINTが構成され、他の一部の領域によってCFRACが構成される。これによって、図21等でも述べたように、CINT内のCIUとCFRAC内のCIUとの間で相対的なプロセスばらつきを低減でき、また、各半導体チップ毎のデバイスばらつきの影響を抑制できる。この観点で、CFRACは、必ずしも図9の例のようにCINTの端部に配置される必要はなく、適宜変更することが可能である。

【0056】

CFRACは、ここでは、34行×3列に配置されたCIUを用いて実現されている。ただし、1列目はダミーとして用いられ、また1行目と34行目もダミーとして用いられるため、実質的には、32行×2列となる。ダミーは、例えば、各CIUに対してその周辺のレイアウトパターン(パターン密度)を均一にするために設けられ、周辺パターンに依存して製造ばらつきが生じる事態を抑制するために設けられる。なお、前述したCINTに関しても同様であり、実際には端の行と端の列にダミーが設けられる。

【0057】

CFRACにおいて、2列目のCIUには、2行目〜9行目の8個のCIUを用いて図6の分数値用容量ブロックCFBK_N8が形成され、18行目〜33行目の16個のCIUを用いて図6の分数値用容量ブロックCFBK_N16が形成される。また、3列目のCIUには、2行目〜3行目の2個のCIUを用いて図6の分数値用容量ブロックCFBK_N2が形成され、30行目〜33行目の4個のCIUを用いて図6の分数値用容量ブロックCFBK_N4が形成される。なお、2列目および3列目において、残りの行に対応するCIUはダミーとなる。

【0058】

図10は、図9における分数値用容量ブロック(1/8用)周りのレイアウト概要の一例を示す模式図である。図10に示すように、例えば分数値用容量ブロックCFBK_N8は、同一列上に順次並んで配置された8個のCIUによって構成される。ここで、図10での1行目のCIUは、図3で述べた基準単位容量ユニット(図3のCIU[1])となり、2個の容量素子(図3のCFXp,CFXmに該当)の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、図10での2行目〜8行目のCIUでは、2個の容量素子の一方の一端が列方向に沿って延伸する配線GLNpに接続され、2個の容量素子の他方の一端が列方向に沿って延伸する配線GLNmに接続される。当該2本の配線GLNp,GLNmは、固定電圧(交流的な接地電源電圧)V6用の配線となる。

【0059】

また、図10での1行目〜8行目のCIUにおいて、2個の容量素子の一方(CFXp側)の他端は、列方向に沿って延伸する配線(ノードSWFD)に共通に接続され、2個の容量素子の他方(CFXm側)の他端も、列方向に沿って延伸する配線(ノードSWFS)に共通に接続される。1行目〜8行目のCIUに含まれるスイッチ(図3のSWF1〜SWF3に該当)は、列方向に沿って延伸するオン・オフ制御線BIT_CF[8]によって共通に制御される。当該BIT_CF[8]は、分数値用ロジック回路LOG_Fによって駆動される。LOG_Fは、例えば図7に示したロジック回路LOG内に配置され、BIT_CF[8]に加えて他のオン・オフ制御線BIT_CF([16],[2],[4])も駆動する。

【0060】

ここで、図10での1行目のCIU(図3の基準単位容量ユニットCIU[1])は、図9における2行目2列目のCIUに該当する。同様に、図9におけるCFBK_N2の基準単位容量ユニットも、2行目のCIUに該当する。また、図9におけるCFBK_N16の基準単位容量ユニットは、図9における33行目のCIUに該当し、同様に、図9におけるCFBK_N4の基準単位容量ユニットも33行目のCIUに該当する。このように各分数値用容量ブロックCFBKの基準単位容量ユニットをダミーを除いた端の行に配置することで、中間の行のダミー(例えば図9におけるCFBK_N8とCFBK_N16の間に位置する各ダミー)のノードをOscP,OscMでなく例えば図3のV6に接続することができるため、ダミーによる余分な寄生容量を低減できる。

【0061】

《単位容量ユニットの周りの詳細構成》

図11は、図8のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例ならびにデバイス断面構造例を示す平面図および断面図である。図12は、図10のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例を示す平面図である。図11には、整数値用の容量バンクCINTに含まれる単位容量ユニットCIUが示され、図12には、分数値用の容量バンクCFRACに含まれる単位容量ユニットCIUが示されている。

【0062】

まず、図11において、単位容量ユニットCIU内の各符号は、前述した図2の各符号に対応している。図2に示されない各符号において、M1,M2,M3,M4は、それぞれ第1、第2、第3、第4メタル配線層であり、CTは各メタル配線層間を適宜接続するコンタクト層であり、ISLは各メタル配線層を覆う絶縁膜である。また、図11に示す断面図(A−A’間断面およびB−B’間断面)では、メタル配線層の部分が抽出して示されているが、実際には、その下層(Z軸方向)に半導体基板が存在する。

【0063】

図11の平面図では、1個の単位容量ユニットCIUをX軸方向(行方向)で挟んだ両側に、Y軸方向(列方向)に沿って並んで延伸する複数本(ここでは簡易的に3本表示)のオン・オフ制御線BIT_CIが配置される。BIT_CIは、そのX側方向の片側(ここでは右側)に隣接して配置されたCIUを制御する。CIUは、A−A’間断面図に示されるように、X軸方向でスイッチSWI(ここではSWIの詳細構造例は省略)を挟んで一方側に容量素子CIpが形成され、他方側に容量素子CImが形成される。CIpは、M3で形成されたノードSWIDを備え、SWIDは、複数のCTおよびM1,M2を介してSWIの一端(具体的には図示しない半導体基板内のドレイン拡散層)に接続される。

【0064】

SWIDのZ軸方向における上層(M4)と下層(M2)には、それぞれ絶縁膜ISLを介して発振出力ノードOscPが形成される。当該M4,M2のOscPは、複数のCTおよびM3を介して接続される。これによって、図11の平面図に示すように、SWIDとOscP(M4)の重複部分で容量素子CIpの一部が形成され、SWIDとOscP(M2)の重複部分でCIpの他の一部が形成される。すなわち、ここでは、2個の容量素子の並列接続によってCIpを構成している。ただし、勿論、M4,M2のいずれか一方のみでOscPを形成することも可能である。このような容量素子CIpは、MIM容量における絶縁膜(I)の部分を通常のメタル配線層の層間絶縁膜(代表的にはシリコン酸化膜)を利用して形成する意味で、MOM容量と呼ばれる場合がある。

【0065】

また、図11の平面図およびA−A’間断面図おいて、CIUとX軸方向で隣接する箇所に(ここでは左側に)、M2によって形成された3本のオン・オフ制御線BIT_CIが配置される。ここで、BIT_CIは、A−A’間断面図から判るように、その周辺が前述したシールド部GSによって覆われている。すなわち、BIT_CIを基準に、Z軸方向の下層および上層はM1およびM4の配線(GS)で覆われ、X軸方向の左右は当該M1とM4間を接続する複数のCTおよびM2,M3の配線(GS)で覆われている。当該M2,M3の配線は、図11の平面図に示すように、Y軸方向においてある程度の長さを持ち、この長さは、OscP(M4),OscP(M2)のY軸方向の長さと同等となっている。これによって、CIU外に配置されたBIT_CIとOscPとの間がシールドされる。その結果、BIT_CIとOscPとの間の直接的なカップリング結合が低減され、例えばBIT_CIの駆動状態に応じてOscPのインピーダンスが不規則に変動するような事態を抑制でき、DNLの向上等が図れる。

【0066】

また、図11の平面図に示すように、この3本のBIT_CIの内のいずれか1本(ここでは真ん中)は、CTによってM3の配線に接続され、当該M3の配線がX軸方向において隣接するCIUに向けて延伸している。当該M3の配線は、CIU内で複数のCTおよびM2を介してM1の配線に接続され、当該M1の配線が、X軸方向に沿って延伸したのちスイッチSWI(NMOSトランジスタ)のゲートに接続される。ここで、当該M1の配線(すなわちBIT_CI)は、B−B’間断面図および平面図から判るように、Y軸方向においてはM1からなるシールド部GS(M1)で保護され、Z軸方向においてはM2からなるシールド部GS(M2)で保護されている。これによって、B−B’間断面図および平面図から判るように、CIU内に配置されたBIT_CIとOscP,OscMとの間がシールドされる。

【0067】

一方、図12において、単位容量ユニットCIU[1],CIU[2]内の各符号は、前述した図3の各符号に対応している。図3に示されない各符号は、前述した図11の場合と同様である。図12に示すレイアウトは、図11に示したCIUの構成例(平面図)をY軸方向に2個繋げ、一方をCIU[1]、他方をCIU[2]としたような構成例となっている。ただし、CINTとCFRACの違いに伴い、ノードSWID,SWISがSWFD,SWFSに変更され、スイッチSWIがSWFに変更され、オン・オフ制御線BIT_CIがBIT_CFに変更されている。なお、BIT_CFは、CIUを挟んだ一方側に3本配置されているが、図9の例の場合には2本でよく、例えば、残りの1本はダミー等とすればよい。

【0068】

ここで、CFRACでは、図12に示すように、CIU[1],CIU[2]のノードSWFDが、Y軸方向に沿って延伸する第3メタル配線層M3のメタル配線SWFMLで共通に接続され、同様にCIU[1],CIU[2]のノードSWFSも、M3のメタル配線で共通に接続される。一方、CINTにおいては、本来、このようなメタル配線SWFMLは不要である。ただし、SWFMLの存在によって、CINT内のCIUとCFRAC内のCIUとで、容量素子(図2のCIpと図4のCFXp)の容量値や寄生容量(図4のCPp)の容量値が異なり得る。そこで、本実施の形態1では、図11に示すように、CINT内のCIUにおいても、図12のSWFMLを反映したM3のダミーメタル配線DMが備わっている。これによって、CINT内のCIUとCFRAC内のCIUとは実質的に同一(略同一)のレイアウト構成を備えることになり、分数容量の使用に際し、高精度化が図れる。

【0069】

また、図11および図12に示した単位容量ユニットCIUの周りの構成は、前述したダミーメタル配線DMやオン・オフ制御線のシールド部GSの特徴に加えて、図11の平面図やA−A’間断面図から判るように、CIU外のBIT_CIとOscP(M2)の下層において広い領域にM1の配線が備わった点も特徴となっている。当該M1の配線は、シールド部GSとなるが、BIT_CIとOscPとの間のシールド機能に加えて、図示しない半導体基板からのノイズに対するシールド機能も兼ね備えている。これによって、発振出力信号における信号品質の向上が実現可能となり、結果的に、DNLの向上にも寄与し得る。

【0070】

なお、例えば図11のA−A’間断面図および平面図に示す容量素子CImの構造に関しては、前述した容量素子CIpの構造をY軸対称で折り返したような構造となるため、詳細な説明は省略する。また、例えば、図11では1個のCIU周りの構成を示したが、実際には、図8に示したように、図11のCIUがY軸方向において複数個(図8の例では8個)配置され、各CIU内のOscP,OscM同士が共通の配線(図8の例えばOscPc[0],OscMc[0]等)で接続される構成となる。この場合、当該共通の配線は、特に限定はされないが、図11においてM4の上層に位置する例えば第5メタル配線層(図示せず)で形成される。また、図8のOscPr,OscMrおよびこれに対応する図7のOscP,OscMは、特に限定はされないが、例えば第5メタル配線層の上層に位置する第6メタル配線層(図示せず)で図7のLP,LMと共に形成される。

【0071】

《ディジタルPLL回路の概略構成》

図13は、本発明の実施の形態1によるディジタル制御発振装置において、図1のディジタル制御発振回路を適用したディジタルPLL回路の概略構成例を示すブロック図である。図13に示すディジタルPLL回路(ディジタル制御発振装置)DPLLは、時間差検出回路(ディジタル位相比較部)TDC、ディジタルロウパスフィルタ(ディジタルループフィルタ)DLPFと、ディジタル制御発振回路DCO、マルチモジュラス周波数分周回路(分周部)MMD、シグマデルタ変調回路(又はデルタシグマ変調回路)SDMを備えている。このDCOに図1等の構成例が適用される。

【0072】

時間差検出回路TDCは、水晶発振回路等によって生成された基準発振周波数(例えば26MHz)を持つ基準発振信号REFと、マルチモジュラス周波数分周回路(分周部)MMDによって生成された分周発振信号FDIVとの位相差(時間差)を検出する。TDCは、例えば、複数段の単位遅延回路(CMOSインバータ回路)を含み、FDIVを単位遅延回路で順次遅延させ、各単位遅延回路の出力をREFに同期してラッチし、このラッチ結果によって位相差(時間差)を検出する。CMOS製造プロセスの微細化に伴い当該単位遅延回路の遅延量が小さくなるほど、位相差(時間差)検出結果の高精度化が図れる。

【0073】

ディジタルロウパスフィルタDLPFは、TDCからの位相比較結果となるディジタルコードCODE1を対象として、平均化処理を行う。DLPFは、代表的には、IIR(Infinite Impulse Response)フィルタや、FIR(Finite Impulse Response)フィルタや、これらの組合せ等である。DCOは、このDLPFの処理結果となるディジタルコードを受けて、当該ディジタルコードの値に応じた発振周波数を持つ発振出力信号PLLOUTを生成する。当該ディジタルコードは、図1における整数容量値制御信号W_INTや分数容量値制御信号W_FRACに該当する。なお、図示は省略しているが、実際には、カウンタ回路等を備えた周波数差検出回路等がTDCと共に備わっている。図1の自動バンド制御信号W_ABSは、当該周波数差検出回路等によって生成される。

【0074】

シグマデルタ変調部SDMは、分周比設定コードDAT−DIVNに基づいてマルチモジュラス周波数分周回路MMDに分周比を設定すると共に当該分周比を可変制御する。例えば、DAT−DIVNは、小数部分を含む分周比を表し、SDMは、MMDに対して、時系列的に異なる整数分周比を設定することで、平均的に小数部分を含んだ分周比を設定する。MMDは、SDMによって設定された分周比で発振出力信号PLLOUTを分周し、その結果を分周発振信号FDIVとしてTDCに帰還する。

【0075】

このような構成および動作において、DCOは、前述した分数値用の容量バンクCFRACを用いることで、TDCによって検出された位相差(時間差)をW_FRACを介して高精度にPLLOUTの発振周波数に反映させることができる。その結果、位相誤差が小さい高精度な発振出力信号が得られる。また、この際には分数容量を実現するためのシグマデルタ変調回路を用いないため(すなわち、図20のDPLLcにおけるSDDCOが不要となるため)、発振周波数遠方の雑音を低減することが可能になる。

【0076】

図14は、図6および図13の動作例を表す概念図である。図14において、横軸には整数コードが示され、縦軸には発振周波数が示されている。整数コードにおける「1」の変化量は、図13における整数容量値制御信号W_INTの1ビット分に対応する。図14に示すように、図13のDPLLにおけるDCOに図6のような分数値用の容量バンクCFRACを適用することで、整数コードの「1」の変化量に対応する発振周波数の変動量ΔFINTの間を更に16分割(ΔFINT/16)した状態で発振周波数の制御を行うことが可能になる。この際には、前述したように、CFRACによる分周容量を高精度に実現できることから、DNL(すなわち図14における傾き特性の線形性の程度)の向上等も図れる。

【0077】

《ディジタルPLL回路の検証結果》

図15は、図13のディジタルPLL回路を対象に行ったノイズ特性の検証結果の一例を示す図である。図15では、横軸は所定の発振出力周波数を基準としたオフセット周波数(Hz)を示し、縦軸はノイズ(dBm/Hz)を示している。また、ここでは、図13のディジタルPLL回路を用いた場合(本方式)と併せて、ディジタルPLL回路を開ループとした場合と、本方式を用いずにDCO用シグマデルタ変調回路を用いない場合(ΣΔ無)と、図20のようにDCO用シグマデルタ変調回路を用いた場合(ΣΔ有)とが示されている。

【0078】

図15に示すように、DCO用シグマデルタ変調回路を用いない場合(ΣΔ無)では、開ループ時に比べて量子化雑音により発振周波数近傍の雑音が悪化する。一方、DCO用シグマデルタ変調回路を用いた場合(ΣΔ有)には、近傍雑音は改善するものの発振周波数遠方の雑音が悪化してしまう。一方、本方式を用いることで、分数容量の高精度化(すなわち量子化雑音の低減)により発振周波数近傍の雑音が改善され、シグマデルタ変調回路を用いないことにより、発振周波数遠方の雑音も改善する。

【0079】

以上、本実施の形態1のディジタル制御発振装置を用いることで、代表的には、発振周波数遠方の雑音を低減することが可能になる。また、加えて、発振周波数近傍の雑音を低減することが可能になる。

【0080】

(実施の形態2)

《高周波信号処理装置の各種概略構成》

本実施の形態2では、実施の形態1で説明したようなディジタル制御発振装置を備えた各種無線通信システム(代表的には携帯電話機)用の高周波信号処理装置の各種構成例について説明する。

【0081】

図16は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示すブロック図である。図16に示す高周波信号処理装置RFIC1は、例えば、一つの半導体チップによって構成される。当該RFIC1は、時間差検出回路TDC、ディジタルロウパスフィルタDLPFと、ディジタル制御発振回路DCO、マルチモジュラス周波数分周回路MMD、シグマデルタ変調回路SDM、および合成回路ADD1,ADD2を備える。ここで、当該DCOに、実施の形態1で述べたような構成例が適用される。RFIC1内の各回路は、例えば、無線通信システムにおける送信回路の一部を構成する。

【0082】

図16のRFIC1は、図13で述べたディジタルPLL回路DPLLに対して、ADD1,ADD2が加わった構成となっている。以降、図7と重複する部分に関しては、詳細な説明は省略する。ADD1は、DLPFの出力と位相変調用コードDAT−PMとを合成し、その合成結果をディジタルコードとしてDCOに出力する。当該ディジタルコードは、整数容量値制御信号W_INTおよび分数容量値制御信号W_FRACに該当する。ADD2は、DAT−PMと分周比設定コードDAT−DIVNとを合成し、SDMに入力する。その結果、DCOからは、所定の発振周波数を基準にDAT−PMに応じた位相変調が加えられた発振出力信号PLLOUTが生成される。PLLOUTは、例えば図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。

【0083】

このように、DCOに対してADD1を介してDAT−PMに伴う位相変調を直接行うと共に、MMD(SDM)に対してADD2を介してDAT−PMに伴う位相変調を行う方式は、2ポイント変調方式と呼ばれる。仮に、MMD(SDM)に対する変調パスのみの場合、当該パスはロウパスフィルタ特性となり、そのループ帯域は帯域外雑音やスプリアスの観点から例えば数百kHz程度等に制限されるため、高域の送信データが欠落してしまう(すなわち送信データレートの高速化が困難となる)恐れがある。一方、DCOに対する変調パスのみの場合、当該パスはハイパスフィルタ特性となるため、低域の周波数成分が十分に得られず、また、ループ帯域外の制御となるためオープンループ制御に近い状態となり、変調精度が低下する恐れがある。そこで、2ポイント変調方式を用いると、このロウパスフィルタ特性とハイパスフィルタ特性が相互に補完され、広帯域での通信が実現可能となる。

【0084】

図16のRFIC1を用いると、前述した2ポイント変調方式による効果に加えて、本実施の形態のDCOによって発振周波数遠方および近傍の雑音を低減できるため、高精度又は高品質な発振出力信号PLLOUTを生成できる。その結果、図示しないアンテナを介してスペクトラムの劣化が少なく、高精度な変調精度(高いEVM(Error Vector Magnitude)特性)を持つ高周波信号が送出可能になる。また、DCO用のシグマデルタ変調回路が不要となるため、消費電力の低減等が図れる。なお、特に限定はされないが、当該RFIC1は、例えばGMSK(Gaussian filtered Minimum Shift Keying)変調が用いられるGSM(Global System for Mobile Communications)規格系の携帯電話システムや、OQPSK(offset quadrature phase shift keying)変調が用いられるZigBee(登録商標)システム等に適用できる。

【0085】

図17は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す他のブロック図である。図17に示す高周波信号処理装置RFIC2は、例えば、一つの半導体チップによって構成される。当該RFIC2は、送信回路として、ロウパスフィルタLPFT−I,LPFT−Q、可変増幅回路VGA−I,VGA−Q、送信用ミキサ回路MIXT−I,MIXT−Q、合成回路ADD3、可変ドライバ回路VDRV、送信用ディジタルPLL回路DPLL_TX、および分周回路DIVN−Tを備える。また、受信回路として、ロウノイズアンプ回路LNA、受信用ミキサ回路MIXR−I,MIXR−Q、プログラマブルゲイン回路PGA−I,PGA−Q、ロウパスフィルタLPFR−I,LPFR−Q、受信用ディジタルPLL回路DPLL_RX、および分周回路DIVN−Rを備える。ここで、当該DPLL_TX,DPLL_RXに、実施の形態1の図13で述べたような構成例が適用され、図13内のDCOに、実施の形態1で述べたような構成例が適用される。

【0086】

図17において、送信動作時には、直交信号となる送信ベースバンド信号TXIN−I,TXIN−QがLPFT−I,LPFT−Qを介して伝送され、VGA−I,VGA−Qで適宜増幅が行われたのちMIXT−I,MIXT−Qに入力される。MIXT−I,MIXT−Qは、DIVN−Tから出力されるローカル信号(キャリア信号、局部発振信号)を用いて、VGA−I,VGA−Qを介して出力される送信ベースバンド信号を所定の高周波信号にアップコンバート(周波数変換)する。この際に、DIVN−Tは、DPLL_TXから出力される発振出力信号を適宜分周し、加えて、90°位相が異なる2個のローカル信号を生成し、その一方をMIXT−Iに、他方をMIXT−Qに出力する。ADD3は、MIXT−Iの出力とMIXT−Qの出力をベクトル合成し、VDRVは、このベクトル合成された高周波信号を所定のゲインで増幅して、送信高周波信号TXOUTを生成する。TXOUTは、図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。

【0087】

図17において、受信動作時には、図示しないアンテナによって受信された受信高周波信号RXINがLNAに入力され、LNAによって増幅された高周波信号がMIXR−I,MIXR−Qに入力される。MIXR−I,MIXR−Qは、DIVN−Rから出力されるローカル信号(キャリア信号、局部発振信号)を用いて、LNAから出力される高周波信号を所定のベースバンド信号にダウンコンバート(周波数変換)する。この際に、DIVN−Rは、DPLL_RXから出力される発振出力信号を適宜分周し、加えて、90°位相が異なる2個のローカル信号を生成し、その一方をMIXR−Iに、他方をMIXR−Qに出力する。MIXR−I,MIXR−Qの出力信号は、PGA−I,PGA−Qで適宜増幅が行われたのち、LPFR−I,LPFR−Qを介して出力される。当該出力信号は直交信号である受信ベースバンド信号RXOUT−I,RXOUT−Qとなる。

【0088】

図17のRFIC2を用いると、例えば、送信動作時には、DPLL−TXに伴い高精度又は高品質なローカル信号を生成できるため、送信高周波信号における位相誤差の低減やスペクトラムの改善等が図れる。また、受信動作時には、DPLL−RXに伴い位相雑音が小さいローカル信号を生成できるため、BER(Bit Error Rate)の低減等が図れる。当該RFIC2は、様々な位相変調または加えて振幅変調を実現できるため、所謂2G(例えばGSM規格)、3G(例えばW−CDMA(Wideband Code Division Multiple Access規格)、3.9G(例えばLTE(Long Term Evolution)規格)といった様々な携帯電話システムに適用できる。

【0089】

例えば、3Gや3.9G等では、FDD方式が用いられるため、所定の送信周波数帯を持つTXOUTが所定の受信周波数帯を持つRXINに影響を及ぼさないようにする必要がある。前述したように、仮にDPLL_TXにDCO用シグマデルタ変調回路を適用した場合、TXOUTに発振周波数遠方の雑音が生じ、これが受信周波数帯に影響を及ぼす(例えば重畳する)恐れがあるため、これを抑制するためのSAWフィルタ等がTXOUTの先に必要とされる場合がある。一方、本実施の形態のDPLL_TXを用いると、このような遠方雑音が低減されるため、SAWフィルタ等が不要となり、無線通信システムの小型化や低コスト化等が図れる。なお、当該RFIC2は、勿論、携帯電話システムに限らず、無線LAN(Local Area Network)、Bluetooth(登録商標)、ZigBee(登録商標)システム等といった様々な無線通信システムに適用可能である。

【0090】

図18は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。図18に示す高周波信号処理装置RFIC3は、例えば、一つの半導体チップによって構成される。当該RFIC3は、PLL制御回路PLLCTL、ディジタル制御発振回路DCO、分周回路DIV1,DIV2、およびドライバ回路DRV1,DRV2を備える。ここで、当該DCOに、実施の形態1で述べたような構成例が適用される。RFIC3内の各回路は、例えば、無線通信システムにおける送信回路の一部を構成する。

【0091】

PLLCTLは、例えば、位相比較回路、ループフィルタ回路、分周回路等を含み、DCOからの発振出力信号に対して所定の分周比の分周信号を生成し、その分周信号の位相と基準発振信号REFとの位相とが一致するようにDCOの発振周波数を制御する。また、PLLCTLは、位相変調用コードDAT−PMが入力され、当該コードに基づいて変調を行う。具体的には、DCOに対して直接変調を行ったり、または図16で述べたような2ポイント変調を行う。例えば、変調指数が0.5のFSK(frequency shift keying)を行うことで、MSK(Minimum Shift Keying)変調が可能になることが知られており、これにガウスフィルタを組み合わせることで、GSM規格等で用いられるGMSK変調が可能となる。

【0092】

DIV1は、このようなDCOの発振出力信号を例えば1/2分周し、DRV1は、DIV1の出力を受けて送信高周波信号TXOUT1を出力する。TXOUT1は、図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。TXOUT1は、例えば、1850MHz〜1910MHzの送信周波数帯と1930MHz〜1990MHzの受信周波数帯を持つPCS(Personal Communications Service)規格や、1710MHz〜1785MHzの送信周波数帯と1805MHz〜1880MHzの受信周波数帯を持つDCS(Digital Cellular System)規格の信号である。なお、PCS規格やDCS規格は、GSM規格のハイバンド等とも呼ばれる。

【0093】

DIV2は、DIV1の出力信号を更に例えば1/2分周し、DRV2は、DIV2の出力を受けて送信高周波信号TXOUT2を出力する。TXOUT2は、図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。TXOUT2は、例えば、824MHz〜849MHzの送信周波数帯と869MHz〜894MHzの受信周波数帯を持つGSM850規格や、880MHz〜915MHzの送信周波数帯と925MHz〜960MHzの受信周波数帯を持つGSM900規格の信号である。なお、DRV1とDRV2は、通信モードの設定に応じていずれか一方が活性化される。図18のRFIC3を用いると、本実施の形態のDCOに伴い高精度又は高品質な発振出力信号を生成できる。その結果、図示しないアンテナを介してスペクトラムの劣化が少なく、高精度な変調精度(高いEVM特性)を持つ高周波信号が送出可能になる。

【0094】

図19は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。図19に示す高周波信号処理装置RFIC4は、例えば、一つの半導体チップによって構成される。当該RFIC4は、図18のRFIC3に対して2個の振幅変調用ミキサ回路MIX−HA,MIX−LAが加わった構成となっている。これ以外の構成に関しては、図18と同様であるため詳細な説明は省略する。MIX−HAは、DRV1の入出力と並列に設けられ、DIV1の出力を振幅変調用コードDAT−AMで振幅変調し、TXOUT1として出力する。同様に、MIX−LAは、DRV2の入出力と並列に設けられ、DIV2の出力をDAT−AMで振幅変調し、TXOUT2として出力する。

【0095】

DRV1,MIX−HA,DRV2,MIX−LAは、いずれか1個が活性化される。DRV1が活性化された場合には、TXOUT1として前述したようなPCS規格やDCS規格の信号が出力され、DRV2が活性化された場合には、TXOUT2として前述したようなGSM850規格やGSM900規格の信号が出力される。一方、MIX−HAが活性化された場合には、TXOUT1としてPCS規格やDCS規格のEDGE(Enhanced Data rates for GSM Evolutions)モードの信号が出力され、MIX−LAが活性化された場合には、TXOUT2としてGSM850規格やGSM900規格のEDGEモードの信号が出力される。EDGEモードでは、包括線変動が生じないGMSK変調とは異なり包括線変動が生じる8PSK(Phase Shift Keying)変調等が用いられるため、MIX−HA,MIX−LAによる振幅制御が必要となる。

【0096】

以上のように、本実施の形態2による高周波信号処理装置を用いることで、発振周波数の設定精度に加えて、変調精度や復調精度の向上が図れるため、代表的には、送信信号・受信信号の信号品質を向上させることが可能になる。更に、発振周波数遠方の雑音を低減できることから、例えばFDD方式では、送信信号と受信信号の干渉等を抑制でき、TDD方式においても、例えば、ある送信チャネルが他の送信チャネルに影響を及ぼすような事態を抑制できる。その結果、送信回路におけるSAWフィルタ等が不要となり、無線通信システムの小型化や低コスト化が図れる。

【0097】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。例えば、ここでは、本実施の形態によるディジタル制御発振回路を無線通信システムに適用したが、場合によっては有線の通信システムに適用することも可能である。

【符号の説明】

【0098】

ADD 合成回路

AMPBK アンプ回路ブロック

AMPM,AMPP アンプ回路

AR 領域

BIT_CI,BIT_CF オン・オフ制御線(オン・オフ制御信号)

BITND オン・オフ制御ノード

CA,CI,CF,CFX 容量素子

CABS,CINT,CFRAC 容量バンク

CFBK 容量ブロック

CIU 単位容量ユニット

CODE ディジタルコード

COX ゲート絶縁膜

CP 寄生容量

CT コンタクト層

DAT−AM 振幅変調用コード

DAT−DIVN 分周比設定コード

DAT−PM 位相変調用コード

DCO ディジタル制御発振回路

DEC デコーダ回路

DF 拡散層

DIV,DIVN 分周回路

DLPF ディジタルロウパスフィルタ

DPLL ディジタルPLL回路

DRV ドライバ回路

FDIV 分周発振信号

GLN 配線

GND 接地電源電圧

GS シールド部

GT ゲート層

IOL ロジック制御回路

ISL 絶縁膜

LNA ロウノイズアンプ回路

LP,LM コイル素子

LPFT,LPFR ロウパスフィルタ

M メタル配線層

MIX 振幅変調用ミキサ回路

MIXR 受信用ミキサ回路

MIXT 送信用ミキサ回路

MMD マルチモジュラス周波数分周回路

OscP,OscM 発振出力ノード

PGA プログラマブルゲイン回路

PLLCTL PLL制御回路

PLLOUT 発振出力信号

REF 基準発振信号

RFIC 高周波信号処理装置

RXIN 受信高周波信号

SDDCO DCO用シグマデルタ変調回路

SDM シグマデルタ変調回路

SUB 半導体基板

SWA,SWI,SWF スイッチ

TDC 時間差検出回路

TXIN 送信ベースバンド信号

TXOUT 送信高周波信号

V 固定電圧

VDD 電源電圧

VDRV 可変ドライバ回路

VGA 可変増幅回路

W_ABS 自動バンド制御信号

W_FRAC 分数容量値制御信号

W_INT 整数容量値制御信号

【技術分野】

【0001】

本発明は、ディジタル制御発振装置および高周波信号処理装置に関し、特に、無線通信システム用のDCO(Digitally controlled oscillator)回路、DCO回路を含むPLL(Phase Locked Loop)回路、ならびにPLL回路を含む無線通信用高周波信号処理装置に適用して有効な技術に関する。

【背景技術】

【0002】

例えば、非特許文献1には、シグマデルタ変調回路を用いて分数容量を実現する方式が示されている。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】Robert Bogdan Staszewski、他3名、“Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS process”、IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing、VOL.50、NO.11、p.815-828、2003年11月

【発明の概要】

【発明が解決しようとする課題】

【0004】

例えば、携帯電話機を代表とする無線通信システムには、主にベースバンド信号と高周波信号との間の周波数変換を担う高周波信号処理装置が備わっている。このような高周波信号処理装置は、例えば、PLL回路やミキサ回路等を備え、PLL回路によって生成した送信用/受信用のキャリア信号(ローカル信号、局部発振信号)をミキサ回路に入力することで周波数変換を行う。こうした中、従来において広く用いられていたアナログPLL回路を、ディジタル回路で構成されるディジタルPLL回路に置き換える技術が注目されている。ディジタルPLL回路は、ADPLL(All Digital Phase Locked Loop)等とも呼ばれる。ディジタルPLL回路を用いると、例えば、CMOS(Complementary Metal Oxide Semiconductor)プロセスによる微細化技術を享受できるため、その進歩に伴い小面積化、低電源電圧化、高性能化(高速化)等が図れる。

【0005】

図20は、本発明の前提として検討したディジタル制御発振装置において、その概略構成例を示すブロック図である。図20に示すディジタル制御発振装置DPLLcは、時間差検出回路TDC、ディジタルロウパスフィルタDLPF、ディジタル制御発振回路DCOc、マルチモジュラス周波数分周回路MMD、シグマデルタ変調回路SDM、ならびにDCO用シグマデルタ変調回路SDDCOを備えている。DCOcから出力された発振出力信号PLLOUTは、MMDによって分周され、TDCは、当該分周発振信号FDIVと基準発振信号REFとの時間差(位相差)を検出する。DLPFは、TDCの検出結果を平滑化し、その結果に基づく整数容量値制御信号W_INTをDCOcに出力する。また、DLPFの出力は、SDDCOを介して、分数容量値制御信号W_FRACとしてDCOcに入力される。

【0006】

SDMは、分周比設定コードDAT−DIVNに基づいて、MMDに分周比を設定すると共に、当該分周比を時系列的に可変制御することで小数部分を含んだ分周比を設定する。この分周比の変化は、TDC、DLPFを介して整数容量値制御信号W_INTに反映される。DCOcは、例えば無線通信システム用等の場合、図示は省略するが、通常、LC共振型で構成され、このC(容量)の値(具体的には発振ノードに接続する容量の個数)を順次制御することで発振周波数の制御を行う。この際の容量の個数は、W_INTによって定められ、この場合の発振周波数の設定分解能は、容量1個分の変化量に依存して定められる。

【0007】

しかしながら、容量1個分の変化量では、所望の発振周波数の設定分解能が得られない場合がある。すなわち、SDMがMMDに対して設定した小数部分を含んだ分周比を高精度に実現できない場合がある。そこで、SDDCOは、MMDの出力ならびにDLPFの出力を受けて、等価的に容量1個分よりも小さい容量の変化量を実現できるように、W_FRACを用いてDCOcを制御する。具体的には、例えば、W_INTに応じて1個の容量を発振ノードに接続する(便宜上オンと呼ぶ)期間をTonとすると、W_FRACによって、当該1個の容量を例えば(Ton/8)の期間でオンに駆動する。その結果、等価的に、1/8個の容量が実現できることになる。なお、SDDCOは、実際には、この容量をオンに制御するタイミングを適宜可変制御する。

【0008】

このように、DCO用シグマデルタ変調回路SDDCOを用いると、発振周波数の設定分解能を向上(DCO利得を低減)させることが可能になる。シグマデルタ変調回路は、広く知られているようにオーバーサンプリングやノイズシェービングによって発振周波数近傍の雑音特性を抑制している。ただし、その代わりに遠方の雑音特性が劣化する(発振周波数を基準にオフセット周波数の高い方の雑音が増加する)ことになる。したがって、例えば、図20のようなDPLLcをFDD(Frequency Division Duplex)方式の無線通信システムの送信部に適用した場合、前述した発振周波数遠方の雑音が、送信帯域から所定の周波数離れた受信帯域に影響を及ぼす恐れがある。

【0009】

これを回避するためには、例えば、シグマデルタ変調回路のサンプリング周波数を高くすることが考えられる。この場合、消費電力や面積が増大する恐れがある。また、送信部にSAW(Surface Acoustic Wave)フィルタを設け、これによって発振周波数遠方の雑音を抑制することが考えられる。ただし、SAWフィルタは、通常、単体の外部部品となるため、無線通信システムにおけるコストの低減や小型化が困難となる恐れがある。

【0010】

そこで、本発明の目的の一つは、発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供することにある。本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的な実施の形態の概要を簡単に説明すれば、次のとおりである。

【0012】

本実施の形態によるディジタル制御発振装置は、相補の発振出力信号が出力される第1及び第2発振出力ノードと、コイル素子と、複数の容量ユニットと、負性抵抗生成回路とを備える。コイル素子(LP,LM)は、第1発振出力ノード(OscP)と前記第2発振出力ノード(OscM)の間に結合される。複数の容量ユニット(CIU)は、それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備える。負性抵抗生成回路(AMPBK)は、第1発振出力ノードと第2発振出力ノードの間に負性抵抗を生成する。ここで、複数の容量ユニットの一部は複数の第1容量ユニットとして第1容量バンク(CINT)を構成し、複数の容量ユニットの他の一部は第2容量バンク(CFRAC)を構成する。複数の第1容量ユニットの第1ノードは第1発振出力ノードに、第2ノードは第2発振出力ノードにそれぞれ結合される。第2容量バンクは、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロック(CFBK)を含む。容量ブロックは、N個の容量ユニットの1個となる第2容量ユニット(CIU[1])と、第2容量ユニット以外となる(N−1)個の第3容量ユニット(CIU[2]〜CIU[k])とを備える。第2容量ユニットの第1ノードは第1発振出力ノードに、第2ノードは第2発振出力ノードにそれぞれ結合される。(N−1)個の第3容量ユニットにおける第1及び第2ノードは、交流的な接地電源電圧(V6)に結合される。第2容量ユニットにおける第1容量素子の第1スイッチ側のノード(SWFD)は、(N−1)個の第3容量ユニットにおける第1容量素子の第1スイッチ側のノードと共通に結合される。第2容量ユニットにおける第2容量素子の第1スイッチ側のノード(SWFS)は、(N−1)個の第3容量ユニットにおける第2容量素子の第1スイッチ側のノードと共通に結合される。第2容量ユニット及び(N−1)個の第3容量ユニットにおける第1スイッチ(SWF1)は、オン・オフが共通に制御される。

【0013】

このような構成を用いると、DCO用シグマデルタ変調回路を用いずに分数容量を実現することが可能になり、発振周波数遠方の雑音を低減することが可能になる。また、高精度な分数容量を実現可能になる。

【発明の効果】

【0014】

本願において開示される発明のうち、代表的な実施の形態によって得られる効果を簡単に説明すると、発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置が実現可能になる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的な構成例を示す回路図である。

【図2】図1のディジタル制御発振回路において、その各単位容量ユニット内のスイッチ周りの詳細な構成例を示す回路図である。

【図3】図1のディジタル制御発振回路において、その容量バンク(分数値用)内の分数値用容量ブロックの詳細な構成例を示す回路図である。

【図4】図3の分数値用容量ブロックの動作原理の一例を表す説明図である。

【図5】(a)、(b)は、図3の分数値用容量ブロックの動作原理の一例を表す説明図である。

【図6】図1のディジタル制御発振回路において、その容量バンク(分数値用)の概略構成例を示すブロック図である。

【図7】本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的なレイアウト構成例を示す平面図である。

【図8】図7のディジタル制御発振回路において、その容量バンク(整数値用)周りのレイアウト概要の一例を表す模式図である。

【図9】図7のディジタル制御発振回路において、その容量バンク(分数値用)のレイアウト概要の一例を表す模式図である。

【図10】図9における分数値用容量ブロック(1/8用)周りのレイアウト概要の一例を示す模式図である。

【図11】図8のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例ならびにデバイス断面構造例を示す平面図および断面図である。

【図12】図10のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例を示す平面図である。

【図13】本発明の実施の形態1によるディジタル制御発振装置において、図1のディジタル制御発振回路を適用したディジタルPLL回路の概略構成例を示すブロック図である。

【図14】図6および図13の動作例を表す概念図である。

【図15】図13のディジタルPLL回路を対象に行ったノイズ特性の検証結果の一例を示す図である。

【図16】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示すブロック図である。

【図17】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す他のブロック図である。

【図18】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。

【図19】本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。

【図20】本発明の前提として検討したディジタル制御発振装置において、その概略構成例を示すブロック図である。

【図21】図3の分数値用容量ブロックの比較例を示すものであり、(a)はその構成例を示す回路図、(b)は、(a)において各スイッチをオンに制御した場合の等価回路図、(c)は、(a)において各スイッチをオフに制御した場合の等価回路図である。

【発明を実施するための形態】

【0016】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

【0017】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0018】

また、実施の形態の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。なお、実施の形態では、MISFET(Metal Insulator Semiconductor Field Effect Transistor)の一例としてMOSFET(Metal Oxide Semiconductor Field Effect Transistor)(MOSトランジスタと略す)を用いるが、ゲート絶縁膜として非酸化膜を除外するものではない。

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0020】

(実施の形態1)

《ディジタル制御発振回路の概略回路構成》

図1は、本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的な構成例を示す回路図である。図1に示すディジタル制御発振回路DCOは、アンプ回路ブロックAMPBKと、コイル素子LP,LMと、3系統の容量バンクCABS,CINT,CFRACと、デコーダ回路DECを備えている。AMPBKは、負性抵抗回路として機能し、正極側発振出力ノードOscPを入力、負極側発振出力ノードOscMを出力として反転動作を行うアンプ回路AMPMと、その逆に、OscMを入力、OscPを出力として反転動作を行うアンプ回路AMPPを備える。

【0021】

AMPP,AMPMのそれぞれは、特に限定はされないが、代表的にはPMOSトランジスタとNMOSトランジスタからなるCMOSインバータ回路で構成される。AMPP,AMPMは、高電位側の固定電圧(例えば電源電圧VDD1)V1と低電位側の固定電圧(例えば接地電源電圧GND1)V2によって動作する。なお、AMPP,AMPMのそれぞれは、場合によっては1個のNMOSトランジスタで構成する(すなわちAMPBKをクロスカップル接続(一方のゲートが他方のドレインに接続)された2個のNMOSトランジスタで構成する)ことも可能である。LPは、一端がOscPに接続され、LMは、一端がOscMに接続され、LP,LMの他端には固定電圧(例えばVDD1又はGND1)V3が供給される。

【0022】

CABSは、周波数帯(バンド)調整用であり、一端がOscPに接続される容量素子CApと、一端がOscMに接続される容量素子CAmと、CApの他端とCAmの他端の間に接続されるスイッチSWAを備える。ここでは、CAp,SWA,CAmからなる一組の回路が代表的に示されているが、実際には、このような回路がOscPとOscMの間に複数組設けられる。CINTは、整数値調整用であり、一端がOscPに接続される容量素子CIpと、一端がOscMに接続される容量素子CImと、CIpの他端とCImの他端の間に接続されるスイッチSWIを備え、実際には、このような回路がOscPとOscMの間に複数組設けられる。CFRACは、分数値調整用であり、一端がOscPに接続される容量素子CFpと、一端がOscMに接続される容量素子CFmと、CFpの他端とCFmの他端の間に接続されるスイッチSWFを備え、実際には、このような回路がOscPとOscMの間に複数組設けられる。

【0023】

SWAは、自動バンド制御信号W_ABSによってオン・オフが制御され、SWI,SWFは、デコーダ回路DECによってオン・オフが制御される。DECは、高電位側の固定電圧(例えば電源電圧VDD2)V4と低電位側の固定電圧(例えば接地電源電圧GND2)V5によって動作する。DECは、整数容量値制御信号W_INT、および分数容量値制御信号W_FRACを入力とし、W_INTに応じてオン・オフ制御線(オン・オフ制御信号)BIT_CIを介してSWIのオン・オフを制御し、W_FRACに応じてオン・オフ制御線(オン・オフ制御信号)BIT_CFを介してSWFのオン・オフを制御する。

【0024】

ここでは、CINT内のCIp,SWI,CImからなる1組を単位容量ユニットCIUと呼ぶ。また、CFRAC内のCFp,SWF,CFmからなる1組を分数値用容量ブロックCFBKと呼ぶ。BIT_CIは、前述したように、CINT内に複数組のCIUが設けられるため、これに応じて複数本で構成され、BIT_CFも同様に複数本で構成される。DECは、例えば、W_INTの値が「1」変動する毎に、BIT_CIを介してSWIをオンに制御するCIUの数を「1」ずつ変動させる。

【0025】

このようなディジタル制御発振回路DCOは、コイル素子LP,LMと容量バンクCABS,CINT,CFRAC内の各容量素子によるLC共振型の構成となっており、OscP,OscMに相補の発振出力信号を出力する。この際に、AMPBKは、当該LC部分の寄生抵抗成分を打ち消す負性抵抗回路として機能する。当該発振回路の発振周波数は、CABS,CINT,CFRAC内の各スイッチのオン・オフによって制御され、主として、スイッチがオンに制御された組に含まれる容量素子が発振周波数を定めるパラメータとして寄与する。

【0026】

ここで、CABS,CINT,CFRAC内の各容量素子の実効的な容量値の関係は、CAp(=CAm)>CIp(=CIm)>CFp(=CFm)となっている。これにより、例えば、W_ABS(CABS)によって2MHz単位、W_INT(CINT)によって10kHz単位、W_FRAC(CFRAC)によって0.625kHz単位でそれぞれ発振周波数が調整される。特に限定はされないが、CABSでは、2MHz単位で512ステップ(約1GHzレンジ)の調整が行われ、CINTでは、10kHz単位で、2048ステップ(約20MHzレンジ)の調整が行われる。

【0027】

このような構成において、本実施の形態1のディジタル制御発振装置の主要な特徴の一つは、詳細は後述するが、CFRAC内のCFBKが、CINT内のCIUと同一の回路構成および略同一のレイアウト構成を持つ容量ユニットを複数組み合わせて構成され、これによって、CINTよりも小さい周波数分解能を実現する点にある。このようなCFBKを設けることで、シグマデルタ変調回路(すなわち図20のSDDCO)等を使用することなく、所定の周波数分解能を実現できるため、代表的には発振周波数遠方の雑音を低減することが可能になる。その結果、前述したようにシグマデルタ変調回路のサンプリング周波数を上げることによる消費電力の増大や面積の増大を抑制でき、また、送信部においてSAWフィルタ等が不要となることから、無線通信システムにおけるコストの低減や小型化等が図れる。

【0028】

《スイッチの詳細構成》

図2は、図1のディジタル制御発振回路において、その各単位容量ユニット内のスイッチ周りの詳細な構成例を示す回路図である。図2には、図1における容量バンクCINT内の1個の単位容量ユニットCIUを代表として、その構成例が示されている。図2の例では、スイッチSWIが、容量素子CIpとCImの間に設けられた3個のスイッチSWI1〜SWI3で構成される。SWI1は、CIpの一端(ノードSWID)とCImの一端(ノードSWIS)との間にソース・ドレイン経路が形成されたNMOSトランジスタで構成される。SWI2は、SWIDと接地電源電圧GNDの間にソース・ドレイン経路が形成されたNMOSトランジスタで構成され、SWI3は、SWISとGNDの間にソース・ドレイン経路が形成されたNMOSトランジスタで構成される。GNDは、例えば図1におけるGND2が用いられる。SWI1〜SWI3を構成する各NMOSトランジスタのゲートは、CIUが備えるオン・オフ制御ノードBITNDに接続され、このBITNDが前述した複数のオン・オフ制御線BIT_CIのいずれか1本(BIT_CI[n])で駆動される。

【0029】

ここで、BIT_CI[n]が‘H’レベルに駆動された場合、SWIDとSWISが電気的に接続されると共にGNDに短絡される。この場合、CIp,CImは、発振出力ノードOscP,OscMにおいて発振周波数を設定する際のパラメータとして寄与する。一方、BIT_CI[n]が‘L’レベルに駆動された場合、SWIDとSWISは、電気的に分離され、共にハイインピーダンス状態となる。この場合、CIp,CImは、理想的には、発振周波数を設定する際のパラメータとして寄与しない。すなわち、オン・オフ制御ノードBITNDは、発振周波数を設定する際のパラメータとして容量素子CIp,CImを寄与させるか否かを選択する機能を持つ。

【0030】

なお、スイッチSWIの構成は、勿論、図2のような構成に限定されるものではなく、様々に変更することが可能である。例えば、図2において、原理的には、SWI1をオンに駆動することでノードSWID,SWISは交流的に仮想接地とみなせるため、SWI2,SWI3は不要である。ただし、実際には、差動バランスのミスマッチや、SWI1の時定数等に応じて仮想接地からの誤差が生じ得るため、SWID,SWISを交流的に接地するスイッチ(図2の例ではSWI2,SWI3)を設ける方が望ましい。また、容量素子CIp,CImは、特に限定はされないが、特性ばらつきを低減する観点等から例えばMIM(Metal Insulator Metal)容量やMOM(Metal Oxide Metal)容量等を用いるとよい。

【0031】

《容量バンク(分数値用)の構成(本実施の形態1の主要な特徴)》

図3は、図1のディジタル制御発振回路において、その容量バンク(分数値用)内の分数値用容量ブロックの詳細な構成例を示す回路図である。図3に示す分数値用容量ブロックCFBKは、前述した整数値用容量バンクCINT内の単位容量ユニットと同一の回路構成を持つk(kは2以上の整数)個の単位容量ユニットCIU[1]〜CIU[k]を備えている。CIU[1]は、図2の構成例と同様に、図2のCIp,CImに対応する容量素子CFXp[1],CFXm[1]と、図2のSWI1,SWI2,SWI3に対応するスイッチSWF1[1],SWF2[1],SWF3[1]を備える。同様に、CIU[k]は、図2のCIp,CImに対応する容量素子CFXp[k],CFXm[k]と、図2のSWI1,SWI2,SWI3に対応するスイッチSWF1[k],SWF2[k],SWF3[k]を備える。

【0032】

CIU[1]〜CIU[k]において、発振出力ノードOscP側の容量素子CFXp[1]〜CFXp[k]は、スイッチ側のノードSWFDが共通に接続され、同様に、発振出力ノードOscM側の容量素子CFXm[1]〜CFXm[k]も、スイッチ側のノードSWFSが共通に接続される。一方、OscP側のCFXp[1]〜CFXp[k]において、スイッチ側のノードSWFDと対向する側のノードは、CFXp[1]のみがOscPに接続され、残りのCFXp[2]〜CFXp[k]は共通に固定電圧V6に接続される。同様に、OscM側のCFXm[1]〜CFXm[k]において、スイッチ側のノードSWFSと対向する側のノードは、CFXm[1]のみがOscMに接続され、残りのCFXm[2]〜CFXm[k]は共通にV6に接続される。V6は、交流的な接地電源電圧であり、特に限定はされないが、例えば、図1におけるGND2やGND1等を用いればよい。また、各スイッチ(SWF1[1],SWF2[1],SWF3[1])〜(SWF1[k],SWF2[k],SWF3[k])のオン・オフは、図1における複数のオン・オフ制御線BIT_CFのいずれか1本(BIT_CF[j])によって共通に制御される。

【0033】

図4および図5(a)、(b)は、図3の分数値用容量ブロックの動作原理の一例を表す説明図である。図4には、図3の分数値用容量ブロックCFBKに含まれる単位容量ユニットCIU[1]〜CIU[k]の内のCIU[1]が示されている。ここでは、当該CIU[1]を、CIU[2]〜CIU[k]と区別して基準単位容量ユニットと呼ぶ。基準単位容量ユニットCIU[1]は、図4に示すように、前述した容量素子CFXp,CFXmおよびスイッチSWF1〜SWF3に加えて、実際には、寄生容量CPp,CPmを含んでいる。CPpは、ノードSWFDと接地電源電圧GNDの間に存在し、CPmは、ノードSWFSとGNDの間に存在する。ここで、CFXp,CFXmの容量値を共にC1とし、CPp,CPmの容量値を共にCPとする。

【0034】

図5(a)には、図4におけるスイッチSWF1〜SWF3が共にオンに駆動された場合の等価回路が示されている。この場合、OscPから当該基準単位容量ユニットCIU[1]側を見た場合の容量値Conは、図4のノードSWFDがGNDに接続されるためCon=C1となる。一方、図5(b)には、図4におけるSWF1〜SWF3が共にオフに駆動された場合の等価回路が示されている。この場合、OscPから当該基準単位容量ユニットCIU[1]側を見た場合の容量値Coffは、図4のノードSWFDがハイインピーダンスとなるため、CFXpとCPpとの直列接続に伴い式(1)となる。その結果、SWF1〜SWF3のオン・オフに伴う容量値の変化量ΔCintは、式(2)となる。

【0035】

Coff=(C1・CP)/(C1+CP) (1)

ΔCint=Con−Coff=C12/(C1+CP) (2)

ここで、図5のCPをCP’に置き換えることで、ΔCintの容量値を1/Kにすることを考える。すなわち、基準単位容量ユニットCIU[1]における容量値の変化量(図1のCINT内のCIUにおける変化量に等しい)を1/Kとし、発振周波数の分解能をCINT内のCIUのK倍(DCO利得を1/K)に向上させることを考える。この場合、目的とする変化量ΔCfは、式(2)を用いて式(3)で与えられる。そして、式(3)より、式(4)の関係が導かれる。

【0036】

ΔCf=C12/(C1+CP’)=ΔCint/K=C12/(K・(C1+CP)) (3)

Cp’=(K−1)・C1+K・CP (4)

式(4)から判るように、ΔCintの容量値を1/Kにするためには、図5(a)、(b)におけるCPp(容量値CP)の代わりに、(K−1)個のC1とK個のCPとを並列に接続すればよい。これを実現したものが前述した図3の回路構成である。すなわち、図3において、ノードSWFDとV6(=GND)の間には、CFXp[2]〜CFXp[k]に伴う(K−1)個のC1が並列接続され、更に、SWFDには、CIU[1]〜CIU[k]に伴うK個のCPが並列接続される。なお、ここでは、OscP側を例として説明を行ったが、勿論、OscM側に関しても同様である。

【0037】

これにより、例えば、ΔCintの1/2の容量変化量を実現する分数値用容量ブロックCFBKは、図3においてCIU[1]とCIU[2]を備えた構成となり、また、ΔCintの1/4の容量変化量を実現するCFBKは、図3においてCIU[1]〜CIU[4]を備えた構成となる。この際に、各CIU[1]〜CIU[4]は、同一の回路構成(実質的に同一のレイアウト構成)を備えているため、それぞれの各容量素子CFXp,CFXmの容量値を高精度に同一値(C1)に設定できることに加えて、各寄生容量CPp,CPmの容量値も高精度に同一値(CP)に設定できる。その結果、CINT内のCIUを基準として、そのK倍の発振周波数の分解能を高精度に実現可能となり、図1で述べた各種効果に加えて、例えばDNL(Differential Non linearity)の向上等が図れる。

【0038】

図6は、図1のディジタル制御発振回路において、その容量バンク(分数値用)の概略構成例を示すブロック図である。図6に示す容量バンクCFRACは、発振出力ノードOscPとOscMとの間に、複数(ここでは4個)の分数値用容量ブロックCFBK_N2,CFBK_N4,CFBK_N8,CFBK_N16を備えている。CFBK_N2は、容量バンク(整数値用)CINT内の各単位容量ユニットCIUにおける容量変化量の1/2の変化量を実現する。具体的には、図3におけるCIU[1],CIU[2]を備え、その各スイッチSWF1([1][2])〜SWF3([1][2])がオン・オフ制御線BIT_CF[2]で制御される。

【0039】

また、CFBK_N4は、CINT内のCIUにおける容量変化量の1/4の変化量を実現し、図3におけるCIU[1]〜CIU[4]を備える。同様に、CFBK_N8は、CINT内のCIUにおける容量変化量の1/8の変化量を実現するため図3におけるCIU[1]〜CIU[8]を備え、CFBK_N16は、CINT内のCIUにおける容量変化量の1/16の変化量を実現するため図3におけるCIU[1]〜CIU[16]を備える。CFBK_N4,CFBK_N8,CFBK_N16内の各スイッチは、それぞれオン・オフ制御線BIT_CF[4],BIT_CF[8],BIT_CF[16]で制御される。

【0040】

これによって、例えば、CINT内のCIUにおける発振周波数の調整幅を10kHzとして、BIT_CF[16]によるオン・オフ制御によって0.625(=10/16)kHzの調整幅が実現でき、BIT_CF[8]によるオン・オフ制御によって1.25(=10/8)kHzの調整幅が実現できる。また、例えば、BIT_CF[16]によるオン・オフ制御とBIT_CF[8]によるオン・オフ制御を組み合わせることで、1.875(0.625+1.25)kHzの調整幅が実現できる。以降、同様にして、各BIT_CF([2],[4],[8],[16])を適宜組み合わせることで、10kHzの間を0.625kHz単位(16階調)で任意に調整することが可能になる。なお、ここでは、(1/24)を実現するCFBK_N16までの分数値用容量ブロックを設けたが、勿論、同様にして(1/2N)(Nは5以上の整数)対応の分数値用容量ブロックを設けることで、順次、分解能の向上が図れる。

【0041】

《容量バンク(分数値用)の構成(比較例)》

図21は、図3の分数値用容量ブロックの比較例を示すものであり、図21(a)はその構成例を示す回路図、図21(b)は、図21(a)において各スイッチをオンに制御した場合の等価回路図、図21(c)は、図21(a)において各スイッチをオフに制御した場合の等価回路図である。図21(a)に示すように、例えば、CINT内のCIUにおける容量変化量の分数を、単純に複数の容量素子の直列接続によって実現する方式が考えられる。図21(a)の例では、1/2の分数を実現するため、例えばOscPとスイッチ側のノードSWFDとの間に、OscP側から順に容量素子CFp2とCFp1が接続されている。

【0042】

当該方式において、図3の場合と同様にして、各スイッチがオンに駆動された際(図21(b)の際)の容量値Conと、各スイッチがオフに駆動された際(図21(c)の際)の容量値Coffとの変化量ΔCf2(=Con−Coff)を求めると、式(5)が得られる。式(5)において、CP1は、CFp1のスイッチ側のノードSWFDに存在する寄生容量CPp1の容量値であり、CP2は、CFp1とCFp2との間のノードに存在する寄生容量CPp2の容量値である。

【0043】

【数1】

【0044】

一方、CINT内のCIUにおける容量変化量は、前述した式(2)のΔCintで与えられる。そこで、ΔCf2=(1/2)・ΔCintとしてその解を求めると、式(6)が得られる。

【0045】

(4・CP1+3・CP2)C12+CP1・CP22=2・CP・C12 (6)

式(6)を満たす一つの解は、「CP1=CP/2」かつ「CP2=0」である。ただし、寄生容量をゼロにする後者の解は事実上不可能であり、前者は、配線とスイッチの寄生容量を含めてCP1を高精度にCP(すなわちCINT内のCIUの寄生容量)の1/2に設計することを意味し、非常に困難と言える。仮にスイッチのサイズにより調整できたとしてもデバイスばらつきや温度変動で変動してしまうため、高い歩留まりが求められる高周波信号処理等に適用することは困難である。上記以外にも解はあるものの、いずれもCP1およびCP2をCP以下に設計する必要があり、結局、当該容量ユニットとCINT内のCIUとの間の相対ばらつきの問題に帰結する。一方、図3の方式を用いると、CINT内のCIUと同じ構成のCIUを用いて分数容量が形成されるため、CINT内のCIUとの間で相対ばらつきが少なく、さらに各半導体チップ毎のデバイスばらつきもCINT内のCIUとほぼ均一に生じるため、高精度な分周容量が実現可能になる。

【0046】

《ディジタル制御発振回路の概略レイアウト構成》

図7は、本発明の実施の形態1によるディジタル制御発振装置において、それに含まれるディジタル制御発振回路の概略的なレイアウト構成例を示す平面図である。図7に示す各符号は、図1に示した各符号に対応している。図7に示すディジタル制御発振回路DCOは、略リング状に形成され、Y軸対称に配置されたメタル配線(LP,LM)を備えている。当該メタル配線は、その中点(中点タップ)に固定電圧(交流的な接地電源電圧)V3が印加され、当該中点タップを基準として一方の側でコイル素子LPを実現し、他方の側でコイル素子LMを実現する。当該リングの内側には、Y軸方向に向けて順に第1領域AR1、第2領域AR2、第3領域AR3が設けられる。

【0047】

AR2には、容量バンクCINT,CFARCが配置され、AR3には、ロジック回路LOGが配置される。LOGは、当該リング(LP,LM)の外側に配置されたロジック制御回路IOLを含めて図1のデコーダ回路DECを構成し、IOLからの制御に応じてCINT,CFRAC内の各単位容量ユニットを制御する。ここで、CINT,CFRACは、前述したように実質的に同一のレイアウトを持つ複数の単位容量ユニットCIUによって構成され、詳細は後述するが、その一部でCINTが構成され、他の一部でCFRACが構成される。Y軸方向において、CINT,CFRACの両側の一方にはLPから分岐してX軸方向に沿って延伸する配線が配置され、他方にはLMから分岐してX軸方向に沿って延伸する配線が配置される。前者の配線は発振出力ノードOscPとなり、後者の配線は発振出力ノードOscMとなる。

【0048】

AR1には、X軸方向においてアンプ回路AMPP,AMPMを挟んで両側に容量バンクCABSが分割して配置される。Z軸方向において、AMPP,AMPMおよびCABSの上層には、LPから分岐してX軸方向に沿って延伸する配線(すなわちOscP)と、LMから分岐してX軸方向に沿って延伸する配線(すなわちOscM)が配置され、AMPP,AMPM,CABSは、当該OscP,OscMに適宜接続される。ここで、AR1は、Y軸方向において当該リング(LP,LM)の略中間部分に配置され、これに伴いAMPP,AMPMは、当該リングの略中心部分に配置される。このようなAMPP,AMPMの配置によって、LC回路における共振周波数を1個に設定することが可能となり、発振周波数の高精度化や発振出力信号の高品質化等が図れる。

【0049】

すなわち、例えば、AMPP,AMPNを当該リング(LP,LM)の端部(例えば図7においてAR3を挟んでAR2と対向する領域等)に配置した場合を想定する。この場合、AMPP,AMPNMからLC回路側を見た場合に、CABSが最も大きな容量であるため、等価的に、LP,LMの一部(AMPP,AMPMからCABSまでの配線)を介してCABS,CINT,CFRACとLP,LMの他の部分に伴う第1のLC回路が見える。そのため、上述したLP,LMの一部とCABS,CINT,CFRACに伴う第2の直列LC回路がAMPP,AMPMから見え、これが不要な共振周波数を発生させる。この不要な共振周波数が必要な共振周波数よりも十分大きい場合は問題とならないが、不要な共振周波数は、AMPP,AMPMからCABSまでの距離が長いほど低くなる。したがってAMPP,AMPMとCABSはできるだけ近づける必要がある。図7のようなレイアウト構成例を用いると、AMPP,AMPMが当該リング(LP,LM)の略中心部分に配置されるため、このような遠近差の影響を緩和できる。

【0050】

《容量バンク(整数値用)のレイアウト概要》

図8は、図7のディジタル制御発振回路において、その容量バンク(整数値用)周りのレイアウト概要の一例を表す模式図である。図8に示す容量バンクCINTでは、簡略化して、8行×4列のマトリックス状に32個の単位容量ユニットCIUが配置されている。ただし、CINTは、実際には、例えば、32行×64列のマトリックスに伴う2048個のCIUを備える。図8において、発振出力ノードOscPは、行方向に沿って延伸する発振出力ノード(発振出力配線)OscPrと、そこから等間隔で分岐し、列方向に沿って並んで延伸する4本の発振出力ノード(発振出力配線)OscPc[0]〜OscPc[3]を含む。同様に、発振出力ノードOscMは、行方向に沿って延伸する発振出力ノード(発振出力配線)OscMrと、そこから等間隔で分岐し、列方向に沿って並んで延伸する4本の発振出力ノード(発振出力配線)OscMc[0]〜OscMc[3]を含む。

【0051】

OscPc[0]とOscMc[0]は互いに近接して配置され、以降同様にして、OscPc[3]とOscMc[3]も互いに近接して配置される。また、OscPrとOscMrは、32個のCIUを列方向で挟んで両側に配置される。OscPc[0],OscMc[0]の配線経路上には、1列目となる8個のCIUが順次配置され、当該各CIUは、OscPc[0],OscMc[0]に対して接続される。以降同様にして、OscPc[3],OscMc[3]の配線経路上には、4列目となる8個のCIUが順次配置され、当該各CIUは、OscPc[3],OscMc[3]に対して接続される。

【0052】

また、1列目となる8個のCIUの近傍には、列方向に沿って並んで延伸する複数本(ここでは4本)のオン・オフ制御線BIT_CI[0]〜BIT_CI[3]が配置される。2列目、3列目および4列目に対しても同様に、各列を構成する8個のCIUの近傍に、列方向に沿って並んで延伸する複数本(ここでは4本)のオン・オフ制御線が各列毎に配置される。1列目に対応するオン・オフ制御線は、ロジック回路LOG[0]によって駆動され、以降同様にして、2列目、3列目、4列目の対応するオン・オフ制御線は、それぞれロジック回路LOG[1],LOG[2],LOG[3]によって駆動される。ロジック回路LOG[0]〜LOG[3]は、ロジック制御回路IOLと共にデコーダ回路DECを構成する。DECは、CIUのマトリックス領域のいずれか一辺(ここではOscMr側の一辺)に沿って配置される。

【0053】

LOG[0]は、1列目に含まれる8個のCIUを対象に、BIT_CI[0]を用いて1個のCIUを制御し、BIT_CI[1]を用いて2個のCIUを制御し、BIT_CI[2]を用いて4個のCIUを制御し、BIT_CI[3]を用いて1個のCIUを制御する。具体的には、例えばBIT_CI[1]を用いて2個のCIU内に含まれる各スイッチ(図2のSWI1〜SWI3)のオン・オフを共通に制御する。したがって、例えば、BIT_CI[0]のみをオンレベルに駆動すれば、OscPc[0],OscMc[0]にそれぞれ1個の容量素子(図2のCIp,CIm)が付加され、BIT_CI[1]のみをオンレベルに駆動すれば、OscPc[0],OscMc[0]にそれぞれ2個の容量素子が付加される。更に、BIT_CI[0],BIT_CI[1]をオンレベルに駆動すれば、OscPc[0],OscMc[0]にそれぞれ3個の容量素子が付加される。以降、同様にしてBIT_CI[0]〜BIT_CI[3]のオンレベル・オフレベルを適宜組み合わせることで、OscPc[0],OscMc[0]に対して4個〜8個の容量素子を付加することが可能になる。

【0054】

LOG[2]〜LOG[3]に関しても同様であり、例えば、LOG[3]は、BIT_CI[0]〜BIT_CI[3]のオンレベル・オフレベルを適宜組み合わせることで、OscPc[3],OscMc[3]に対して0個〜8個の容量素子を適宜付加することが可能になる。また、ロジック制御回路IOLは、LOG[0]〜LOG[3]のいずれかを選択して、前述したBIT_CI[0]〜BIT_CI[3]のオンレベル・オフレベルの指示を与えると共に、LOG[0]〜LOG[3]のそれぞれに対して、BIT_CI[0]〜BIT_CI[3]全体をオンレベル又はオフレベルに駆動するための命令を与える。これによって、例えば、OscP,OscMに対してそれぞれ9個の容量素子を付加する場合には、LOG[0]においてBIT_CI[0]〜BIT_CI[3]全体をオンレベルに駆動させた状態で、LOG[1]を選択し、LOG[1]においてBIT_CI[0]のみを駆動させればよい。

【0055】

《容量バンク(分数値用)のレイアウト概要》

図9は、図7のディジタル制御発振回路において、その容量バンク(分数値用)のレイアウト概要の一例を表す模式図である。図9の例では、分数値用の容量バンクCFRACは、整数値用の容量バンクCINTと隣接して配置される。言い換えれば、図8に示したように、複数の単位容量ユニットがマトリックス状に配置され、その一部の領域によってCINTが構成され、他の一部の領域によってCFRACが構成される。これによって、図21等でも述べたように、CINT内のCIUとCFRAC内のCIUとの間で相対的なプロセスばらつきを低減でき、また、各半導体チップ毎のデバイスばらつきの影響を抑制できる。この観点で、CFRACは、必ずしも図9の例のようにCINTの端部に配置される必要はなく、適宜変更することが可能である。

【0056】

CFRACは、ここでは、34行×3列に配置されたCIUを用いて実現されている。ただし、1列目はダミーとして用いられ、また1行目と34行目もダミーとして用いられるため、実質的には、32行×2列となる。ダミーは、例えば、各CIUに対してその周辺のレイアウトパターン(パターン密度)を均一にするために設けられ、周辺パターンに依存して製造ばらつきが生じる事態を抑制するために設けられる。なお、前述したCINTに関しても同様であり、実際には端の行と端の列にダミーが設けられる。

【0057】

CFRACにおいて、2列目のCIUには、2行目〜9行目の8個のCIUを用いて図6の分数値用容量ブロックCFBK_N8が形成され、18行目〜33行目の16個のCIUを用いて図6の分数値用容量ブロックCFBK_N16が形成される。また、3列目のCIUには、2行目〜3行目の2個のCIUを用いて図6の分数値用容量ブロックCFBK_N2が形成され、30行目〜33行目の4個のCIUを用いて図6の分数値用容量ブロックCFBK_N4が形成される。なお、2列目および3列目において、残りの行に対応するCIUはダミーとなる。

【0058】

図10は、図9における分数値用容量ブロック(1/8用)周りのレイアウト概要の一例を示す模式図である。図10に示すように、例えば分数値用容量ブロックCFBK_N8は、同一列上に順次並んで配置された8個のCIUによって構成される。ここで、図10での1行目のCIUは、図3で述べた基準単位容量ユニット(図3のCIU[1])となり、2個の容量素子(図3のCFXp,CFXmに該当)の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、図10での2行目〜8行目のCIUでは、2個の容量素子の一方の一端が列方向に沿って延伸する配線GLNpに接続され、2個の容量素子の他方の一端が列方向に沿って延伸する配線GLNmに接続される。当該2本の配線GLNp,GLNmは、固定電圧(交流的な接地電源電圧)V6用の配線となる。

【0059】

また、図10での1行目〜8行目のCIUにおいて、2個の容量素子の一方(CFXp側)の他端は、列方向に沿って延伸する配線(ノードSWFD)に共通に接続され、2個の容量素子の他方(CFXm側)の他端も、列方向に沿って延伸する配線(ノードSWFS)に共通に接続される。1行目〜8行目のCIUに含まれるスイッチ(図3のSWF1〜SWF3に該当)は、列方向に沿って延伸するオン・オフ制御線BIT_CF[8]によって共通に制御される。当該BIT_CF[8]は、分数値用ロジック回路LOG_Fによって駆動される。LOG_Fは、例えば図7に示したロジック回路LOG内に配置され、BIT_CF[8]に加えて他のオン・オフ制御線BIT_CF([16],[2],[4])も駆動する。

【0060】

ここで、図10での1行目のCIU(図3の基準単位容量ユニットCIU[1])は、図9における2行目2列目のCIUに該当する。同様に、図9におけるCFBK_N2の基準単位容量ユニットも、2行目のCIUに該当する。また、図9におけるCFBK_N16の基準単位容量ユニットは、図9における33行目のCIUに該当し、同様に、図9におけるCFBK_N4の基準単位容量ユニットも33行目のCIUに該当する。このように各分数値用容量ブロックCFBKの基準単位容量ユニットをダミーを除いた端の行に配置することで、中間の行のダミー(例えば図9におけるCFBK_N8とCFBK_N16の間に位置する各ダミー)のノードをOscP,OscMでなく例えば図3のV6に接続することができるため、ダミーによる余分な寄生容量を低減できる。

【0061】

《単位容量ユニットの周りの詳細構成》

図11は、図8のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例ならびにデバイス断面構造例を示す平面図および断面図である。図12は、図10のレイアウト概要において、その各単位容量ユニット周りの詳細なレイアウト構成例を示す平面図である。図11には、整数値用の容量バンクCINTに含まれる単位容量ユニットCIUが示され、図12には、分数値用の容量バンクCFRACに含まれる単位容量ユニットCIUが示されている。

【0062】

まず、図11において、単位容量ユニットCIU内の各符号は、前述した図2の各符号に対応している。図2に示されない各符号において、M1,M2,M3,M4は、それぞれ第1、第2、第3、第4メタル配線層であり、CTは各メタル配線層間を適宜接続するコンタクト層であり、ISLは各メタル配線層を覆う絶縁膜である。また、図11に示す断面図(A−A’間断面およびB−B’間断面)では、メタル配線層の部分が抽出して示されているが、実際には、その下層(Z軸方向)に半導体基板が存在する。

【0063】

図11の平面図では、1個の単位容量ユニットCIUをX軸方向(行方向)で挟んだ両側に、Y軸方向(列方向)に沿って並んで延伸する複数本(ここでは簡易的に3本表示)のオン・オフ制御線BIT_CIが配置される。BIT_CIは、そのX側方向の片側(ここでは右側)に隣接して配置されたCIUを制御する。CIUは、A−A’間断面図に示されるように、X軸方向でスイッチSWI(ここではSWIの詳細構造例は省略)を挟んで一方側に容量素子CIpが形成され、他方側に容量素子CImが形成される。CIpは、M3で形成されたノードSWIDを備え、SWIDは、複数のCTおよびM1,M2を介してSWIの一端(具体的には図示しない半導体基板内のドレイン拡散層)に接続される。

【0064】

SWIDのZ軸方向における上層(M4)と下層(M2)には、それぞれ絶縁膜ISLを介して発振出力ノードOscPが形成される。当該M4,M2のOscPは、複数のCTおよびM3を介して接続される。これによって、図11の平面図に示すように、SWIDとOscP(M4)の重複部分で容量素子CIpの一部が形成され、SWIDとOscP(M2)の重複部分でCIpの他の一部が形成される。すなわち、ここでは、2個の容量素子の並列接続によってCIpを構成している。ただし、勿論、M4,M2のいずれか一方のみでOscPを形成することも可能である。このような容量素子CIpは、MIM容量における絶縁膜(I)の部分を通常のメタル配線層の層間絶縁膜(代表的にはシリコン酸化膜)を利用して形成する意味で、MOM容量と呼ばれる場合がある。

【0065】

また、図11の平面図およびA−A’間断面図おいて、CIUとX軸方向で隣接する箇所に(ここでは左側に)、M2によって形成された3本のオン・オフ制御線BIT_CIが配置される。ここで、BIT_CIは、A−A’間断面図から判るように、その周辺が前述したシールド部GSによって覆われている。すなわち、BIT_CIを基準に、Z軸方向の下層および上層はM1およびM4の配線(GS)で覆われ、X軸方向の左右は当該M1とM4間を接続する複数のCTおよびM2,M3の配線(GS)で覆われている。当該M2,M3の配線は、図11の平面図に示すように、Y軸方向においてある程度の長さを持ち、この長さは、OscP(M4),OscP(M2)のY軸方向の長さと同等となっている。これによって、CIU外に配置されたBIT_CIとOscPとの間がシールドされる。その結果、BIT_CIとOscPとの間の直接的なカップリング結合が低減され、例えばBIT_CIの駆動状態に応じてOscPのインピーダンスが不規則に変動するような事態を抑制でき、DNLの向上等が図れる。

【0066】

また、図11の平面図に示すように、この3本のBIT_CIの内のいずれか1本(ここでは真ん中)は、CTによってM3の配線に接続され、当該M3の配線がX軸方向において隣接するCIUに向けて延伸している。当該M3の配線は、CIU内で複数のCTおよびM2を介してM1の配線に接続され、当該M1の配線が、X軸方向に沿って延伸したのちスイッチSWI(NMOSトランジスタ)のゲートに接続される。ここで、当該M1の配線(すなわちBIT_CI)は、B−B’間断面図および平面図から判るように、Y軸方向においてはM1からなるシールド部GS(M1)で保護され、Z軸方向においてはM2からなるシールド部GS(M2)で保護されている。これによって、B−B’間断面図および平面図から判るように、CIU内に配置されたBIT_CIとOscP,OscMとの間がシールドされる。

【0067】

一方、図12において、単位容量ユニットCIU[1],CIU[2]内の各符号は、前述した図3の各符号に対応している。図3に示されない各符号は、前述した図11の場合と同様である。図12に示すレイアウトは、図11に示したCIUの構成例(平面図)をY軸方向に2個繋げ、一方をCIU[1]、他方をCIU[2]としたような構成例となっている。ただし、CINTとCFRACの違いに伴い、ノードSWID,SWISがSWFD,SWFSに変更され、スイッチSWIがSWFに変更され、オン・オフ制御線BIT_CIがBIT_CFに変更されている。なお、BIT_CFは、CIUを挟んだ一方側に3本配置されているが、図9の例の場合には2本でよく、例えば、残りの1本はダミー等とすればよい。

【0068】

ここで、CFRACでは、図12に示すように、CIU[1],CIU[2]のノードSWFDが、Y軸方向に沿って延伸する第3メタル配線層M3のメタル配線SWFMLで共通に接続され、同様にCIU[1],CIU[2]のノードSWFSも、M3のメタル配線で共通に接続される。一方、CINTにおいては、本来、このようなメタル配線SWFMLは不要である。ただし、SWFMLの存在によって、CINT内のCIUとCFRAC内のCIUとで、容量素子(図2のCIpと図4のCFXp)の容量値や寄生容量(図4のCPp)の容量値が異なり得る。そこで、本実施の形態1では、図11に示すように、CINT内のCIUにおいても、図12のSWFMLを反映したM3のダミーメタル配線DMが備わっている。これによって、CINT内のCIUとCFRAC内のCIUとは実質的に同一(略同一)のレイアウト構成を備えることになり、分数容量の使用に際し、高精度化が図れる。

【0069】

また、図11および図12に示した単位容量ユニットCIUの周りの構成は、前述したダミーメタル配線DMやオン・オフ制御線のシールド部GSの特徴に加えて、図11の平面図やA−A’間断面図から判るように、CIU外のBIT_CIとOscP(M2)の下層において広い領域にM1の配線が備わった点も特徴となっている。当該M1の配線は、シールド部GSとなるが、BIT_CIとOscPとの間のシールド機能に加えて、図示しない半導体基板からのノイズに対するシールド機能も兼ね備えている。これによって、発振出力信号における信号品質の向上が実現可能となり、結果的に、DNLの向上にも寄与し得る。

【0070】

なお、例えば図11のA−A’間断面図および平面図に示す容量素子CImの構造に関しては、前述した容量素子CIpの構造をY軸対称で折り返したような構造となるため、詳細な説明は省略する。また、例えば、図11では1個のCIU周りの構成を示したが、実際には、図8に示したように、図11のCIUがY軸方向において複数個(図8の例では8個)配置され、各CIU内のOscP,OscM同士が共通の配線(図8の例えばOscPc[0],OscMc[0]等)で接続される構成となる。この場合、当該共通の配線は、特に限定はされないが、図11においてM4の上層に位置する例えば第5メタル配線層(図示せず)で形成される。また、図8のOscPr,OscMrおよびこれに対応する図7のOscP,OscMは、特に限定はされないが、例えば第5メタル配線層の上層に位置する第6メタル配線層(図示せず)で図7のLP,LMと共に形成される。

【0071】

《ディジタルPLL回路の概略構成》

図13は、本発明の実施の形態1によるディジタル制御発振装置において、図1のディジタル制御発振回路を適用したディジタルPLL回路の概略構成例を示すブロック図である。図13に示すディジタルPLL回路(ディジタル制御発振装置)DPLLは、時間差検出回路(ディジタル位相比較部)TDC、ディジタルロウパスフィルタ(ディジタルループフィルタ)DLPFと、ディジタル制御発振回路DCO、マルチモジュラス周波数分周回路(分周部)MMD、シグマデルタ変調回路(又はデルタシグマ変調回路)SDMを備えている。このDCOに図1等の構成例が適用される。

【0072】

時間差検出回路TDCは、水晶発振回路等によって生成された基準発振周波数(例えば26MHz)を持つ基準発振信号REFと、マルチモジュラス周波数分周回路(分周部)MMDによって生成された分周発振信号FDIVとの位相差(時間差)を検出する。TDCは、例えば、複数段の単位遅延回路(CMOSインバータ回路)を含み、FDIVを単位遅延回路で順次遅延させ、各単位遅延回路の出力をREFに同期してラッチし、このラッチ結果によって位相差(時間差)を検出する。CMOS製造プロセスの微細化に伴い当該単位遅延回路の遅延量が小さくなるほど、位相差(時間差)検出結果の高精度化が図れる。

【0073】

ディジタルロウパスフィルタDLPFは、TDCからの位相比較結果となるディジタルコードCODE1を対象として、平均化処理を行う。DLPFは、代表的には、IIR(Infinite Impulse Response)フィルタや、FIR(Finite Impulse Response)フィルタや、これらの組合せ等である。DCOは、このDLPFの処理結果となるディジタルコードを受けて、当該ディジタルコードの値に応じた発振周波数を持つ発振出力信号PLLOUTを生成する。当該ディジタルコードは、図1における整数容量値制御信号W_INTや分数容量値制御信号W_FRACに該当する。なお、図示は省略しているが、実際には、カウンタ回路等を備えた周波数差検出回路等がTDCと共に備わっている。図1の自動バンド制御信号W_ABSは、当該周波数差検出回路等によって生成される。

【0074】

シグマデルタ変調部SDMは、分周比設定コードDAT−DIVNに基づいてマルチモジュラス周波数分周回路MMDに分周比を設定すると共に当該分周比を可変制御する。例えば、DAT−DIVNは、小数部分を含む分周比を表し、SDMは、MMDに対して、時系列的に異なる整数分周比を設定することで、平均的に小数部分を含んだ分周比を設定する。MMDは、SDMによって設定された分周比で発振出力信号PLLOUTを分周し、その結果を分周発振信号FDIVとしてTDCに帰還する。

【0075】

このような構成および動作において、DCOは、前述した分数値用の容量バンクCFRACを用いることで、TDCによって検出された位相差(時間差)をW_FRACを介して高精度にPLLOUTの発振周波数に反映させることができる。その結果、位相誤差が小さい高精度な発振出力信号が得られる。また、この際には分数容量を実現するためのシグマデルタ変調回路を用いないため(すなわち、図20のDPLLcにおけるSDDCOが不要となるため)、発振周波数遠方の雑音を低減することが可能になる。

【0076】

図14は、図6および図13の動作例を表す概念図である。図14において、横軸には整数コードが示され、縦軸には発振周波数が示されている。整数コードにおける「1」の変化量は、図13における整数容量値制御信号W_INTの1ビット分に対応する。図14に示すように、図13のDPLLにおけるDCOに図6のような分数値用の容量バンクCFRACを適用することで、整数コードの「1」の変化量に対応する発振周波数の変動量ΔFINTの間を更に16分割(ΔFINT/16)した状態で発振周波数の制御を行うことが可能になる。この際には、前述したように、CFRACによる分周容量を高精度に実現できることから、DNL(すなわち図14における傾き特性の線形性の程度)の向上等も図れる。

【0077】

《ディジタルPLL回路の検証結果》

図15は、図13のディジタルPLL回路を対象に行ったノイズ特性の検証結果の一例を示す図である。図15では、横軸は所定の発振出力周波数を基準としたオフセット周波数(Hz)を示し、縦軸はノイズ(dBm/Hz)を示している。また、ここでは、図13のディジタルPLL回路を用いた場合(本方式)と併せて、ディジタルPLL回路を開ループとした場合と、本方式を用いずにDCO用シグマデルタ変調回路を用いない場合(ΣΔ無)と、図20のようにDCO用シグマデルタ変調回路を用いた場合(ΣΔ有)とが示されている。

【0078】

図15に示すように、DCO用シグマデルタ変調回路を用いない場合(ΣΔ無)では、開ループ時に比べて量子化雑音により発振周波数近傍の雑音が悪化する。一方、DCO用シグマデルタ変調回路を用いた場合(ΣΔ有)には、近傍雑音は改善するものの発振周波数遠方の雑音が悪化してしまう。一方、本方式を用いることで、分数容量の高精度化(すなわち量子化雑音の低減)により発振周波数近傍の雑音が改善され、シグマデルタ変調回路を用いないことにより、発振周波数遠方の雑音も改善する。

【0079】

以上、本実施の形態1のディジタル制御発振装置を用いることで、代表的には、発振周波数遠方の雑音を低減することが可能になる。また、加えて、発振周波数近傍の雑音を低減することが可能になる。

【0080】

(実施の形態2)

《高周波信号処理装置の各種概略構成》

本実施の形態2では、実施の形態1で説明したようなディジタル制御発振装置を備えた各種無線通信システム(代表的には携帯電話機)用の高周波信号処理装置の各種構成例について説明する。

【0081】

図16は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示すブロック図である。図16に示す高周波信号処理装置RFIC1は、例えば、一つの半導体チップによって構成される。当該RFIC1は、時間差検出回路TDC、ディジタルロウパスフィルタDLPFと、ディジタル制御発振回路DCO、マルチモジュラス周波数分周回路MMD、シグマデルタ変調回路SDM、および合成回路ADD1,ADD2を備える。ここで、当該DCOに、実施の形態1で述べたような構成例が適用される。RFIC1内の各回路は、例えば、無線通信システムにおける送信回路の一部を構成する。

【0082】

図16のRFIC1は、図13で述べたディジタルPLL回路DPLLに対して、ADD1,ADD2が加わった構成となっている。以降、図7と重複する部分に関しては、詳細な説明は省略する。ADD1は、DLPFの出力と位相変調用コードDAT−PMとを合成し、その合成結果をディジタルコードとしてDCOに出力する。当該ディジタルコードは、整数容量値制御信号W_INTおよび分数容量値制御信号W_FRACに該当する。ADD2は、DAT−PMと分周比設定コードDAT−DIVNとを合成し、SDMに入力する。その結果、DCOからは、所定の発振周波数を基準にDAT−PMに応じた位相変調が加えられた発振出力信号PLLOUTが生成される。PLLOUTは、例えば図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。

【0083】

このように、DCOに対してADD1を介してDAT−PMに伴う位相変調を直接行うと共に、MMD(SDM)に対してADD2を介してDAT−PMに伴う位相変調を行う方式は、2ポイント変調方式と呼ばれる。仮に、MMD(SDM)に対する変調パスのみの場合、当該パスはロウパスフィルタ特性となり、そのループ帯域は帯域外雑音やスプリアスの観点から例えば数百kHz程度等に制限されるため、高域の送信データが欠落してしまう(すなわち送信データレートの高速化が困難となる)恐れがある。一方、DCOに対する変調パスのみの場合、当該パスはハイパスフィルタ特性となるため、低域の周波数成分が十分に得られず、また、ループ帯域外の制御となるためオープンループ制御に近い状態となり、変調精度が低下する恐れがある。そこで、2ポイント変調方式を用いると、このロウパスフィルタ特性とハイパスフィルタ特性が相互に補完され、広帯域での通信が実現可能となる。

【0084】

図16のRFIC1を用いると、前述した2ポイント変調方式による効果に加えて、本実施の形態のDCOによって発振周波数遠方および近傍の雑音を低減できるため、高精度又は高品質な発振出力信号PLLOUTを生成できる。その結果、図示しないアンテナを介してスペクトラムの劣化が少なく、高精度な変調精度(高いEVM(Error Vector Magnitude)特性)を持つ高周波信号が送出可能になる。また、DCO用のシグマデルタ変調回路が不要となるため、消費電力の低減等が図れる。なお、特に限定はされないが、当該RFIC1は、例えばGMSK(Gaussian filtered Minimum Shift Keying)変調が用いられるGSM(Global System for Mobile Communications)規格系の携帯電話システムや、OQPSK(offset quadrature phase shift keying)変調が用いられるZigBee(登録商標)システム等に適用できる。

【0085】

図17は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す他のブロック図である。図17に示す高周波信号処理装置RFIC2は、例えば、一つの半導体チップによって構成される。当該RFIC2は、送信回路として、ロウパスフィルタLPFT−I,LPFT−Q、可変増幅回路VGA−I,VGA−Q、送信用ミキサ回路MIXT−I,MIXT−Q、合成回路ADD3、可変ドライバ回路VDRV、送信用ディジタルPLL回路DPLL_TX、および分周回路DIVN−Tを備える。また、受信回路として、ロウノイズアンプ回路LNA、受信用ミキサ回路MIXR−I,MIXR−Q、プログラマブルゲイン回路PGA−I,PGA−Q、ロウパスフィルタLPFR−I,LPFR−Q、受信用ディジタルPLL回路DPLL_RX、および分周回路DIVN−Rを備える。ここで、当該DPLL_TX,DPLL_RXに、実施の形態1の図13で述べたような構成例が適用され、図13内のDCOに、実施の形態1で述べたような構成例が適用される。

【0086】

図17において、送信動作時には、直交信号となる送信ベースバンド信号TXIN−I,TXIN−QがLPFT−I,LPFT−Qを介して伝送され、VGA−I,VGA−Qで適宜増幅が行われたのちMIXT−I,MIXT−Qに入力される。MIXT−I,MIXT−Qは、DIVN−Tから出力されるローカル信号(キャリア信号、局部発振信号)を用いて、VGA−I,VGA−Qを介して出力される送信ベースバンド信号を所定の高周波信号にアップコンバート(周波数変換)する。この際に、DIVN−Tは、DPLL_TXから出力される発振出力信号を適宜分周し、加えて、90°位相が異なる2個のローカル信号を生成し、その一方をMIXT−Iに、他方をMIXT−Qに出力する。ADD3は、MIXT−Iの出力とMIXT−Qの出力をベクトル合成し、VDRVは、このベクトル合成された高周波信号を所定のゲインで増幅して、送信高周波信号TXOUTを生成する。TXOUTは、図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。

【0087】

図17において、受信動作時には、図示しないアンテナによって受信された受信高周波信号RXINがLNAに入力され、LNAによって増幅された高周波信号がMIXR−I,MIXR−Qに入力される。MIXR−I,MIXR−Qは、DIVN−Rから出力されるローカル信号(キャリア信号、局部発振信号)を用いて、LNAから出力される高周波信号を所定のベースバンド信号にダウンコンバート(周波数変換)する。この際に、DIVN−Rは、DPLL_RXから出力される発振出力信号を適宜分周し、加えて、90°位相が異なる2個のローカル信号を生成し、その一方をMIXR−Iに、他方をMIXR−Qに出力する。MIXR−I,MIXR−Qの出力信号は、PGA−I,PGA−Qで適宜増幅が行われたのち、LPFR−I,LPFR−Qを介して出力される。当該出力信号は直交信号である受信ベースバンド信号RXOUT−I,RXOUT−Qとなる。

【0088】

図17のRFIC2を用いると、例えば、送信動作時には、DPLL−TXに伴い高精度又は高品質なローカル信号を生成できるため、送信高周波信号における位相誤差の低減やスペクトラムの改善等が図れる。また、受信動作時には、DPLL−RXに伴い位相雑音が小さいローカル信号を生成できるため、BER(Bit Error Rate)の低減等が図れる。当該RFIC2は、様々な位相変調または加えて振幅変調を実現できるため、所謂2G(例えばGSM規格)、3G(例えばW−CDMA(Wideband Code Division Multiple Access規格)、3.9G(例えばLTE(Long Term Evolution)規格)といった様々な携帯電話システムに適用できる。

【0089】

例えば、3Gや3.9G等では、FDD方式が用いられるため、所定の送信周波数帯を持つTXOUTが所定の受信周波数帯を持つRXINに影響を及ぼさないようにする必要がある。前述したように、仮にDPLL_TXにDCO用シグマデルタ変調回路を適用した場合、TXOUTに発振周波数遠方の雑音が生じ、これが受信周波数帯に影響を及ぼす(例えば重畳する)恐れがあるため、これを抑制するためのSAWフィルタ等がTXOUTの先に必要とされる場合がある。一方、本実施の形態のDPLL_TXを用いると、このような遠方雑音が低減されるため、SAWフィルタ等が不要となり、無線通信システムの小型化や低コスト化等が図れる。なお、当該RFIC2は、勿論、携帯電話システムに限らず、無線LAN(Local Area Network)、Bluetooth(登録商標)、ZigBee(登録商標)システム等といった様々な無線通信システムに適用可能である。

【0090】

図18は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。図18に示す高周波信号処理装置RFIC3は、例えば、一つの半導体チップによって構成される。当該RFIC3は、PLL制御回路PLLCTL、ディジタル制御発振回路DCO、分周回路DIV1,DIV2、およびドライバ回路DRV1,DRV2を備える。ここで、当該DCOに、実施の形態1で述べたような構成例が適用される。RFIC3内の各回路は、例えば、無線通信システムにおける送信回路の一部を構成する。

【0091】

PLLCTLは、例えば、位相比較回路、ループフィルタ回路、分周回路等を含み、DCOからの発振出力信号に対して所定の分周比の分周信号を生成し、その分周信号の位相と基準発振信号REFとの位相とが一致するようにDCOの発振周波数を制御する。また、PLLCTLは、位相変調用コードDAT−PMが入力され、当該コードに基づいて変調を行う。具体的には、DCOに対して直接変調を行ったり、または図16で述べたような2ポイント変調を行う。例えば、変調指数が0.5のFSK(frequency shift keying)を行うことで、MSK(Minimum Shift Keying)変調が可能になることが知られており、これにガウスフィルタを組み合わせることで、GSM規格等で用いられるGMSK変調が可能となる。

【0092】

DIV1は、このようなDCOの発振出力信号を例えば1/2分周し、DRV1は、DIV1の出力を受けて送信高周波信号TXOUT1を出力する。TXOUT1は、図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。TXOUT1は、例えば、1850MHz〜1910MHzの送信周波数帯と1930MHz〜1990MHzの受信周波数帯を持つPCS(Personal Communications Service)規格や、1710MHz〜1785MHzの送信周波数帯と1805MHz〜1880MHzの受信周波数帯を持つDCS(Digital Cellular System)規格の信号である。なお、PCS規格やDCS規格は、GSM規格のハイバンド等とも呼ばれる。

【0093】

DIV2は、DIV1の出力信号を更に例えば1/2分周し、DRV2は、DIV2の出力を受けて送信高周波信号TXOUT2を出力する。TXOUT2は、図示しない電力増幅装置等によって増幅されたのちアンテナを介して送信される。TXOUT2は、例えば、824MHz〜849MHzの送信周波数帯と869MHz〜894MHzの受信周波数帯を持つGSM850規格や、880MHz〜915MHzの送信周波数帯と925MHz〜960MHzの受信周波数帯を持つGSM900規格の信号である。なお、DRV1とDRV2は、通信モードの設定に応じていずれか一方が活性化される。図18のRFIC3を用いると、本実施の形態のDCOに伴い高精度又は高品質な発振出力信号を生成できる。その結果、図示しないアンテナを介してスペクトラムの劣化が少なく、高精度な変調精度(高いEVM特性)を持つ高周波信号が送出可能になる。

【0094】

図19は、本発明の実施の形態2による高周波信号処理装置において、その概略的な構成例を示す更に他のブロック図である。図19に示す高周波信号処理装置RFIC4は、例えば、一つの半導体チップによって構成される。当該RFIC4は、図18のRFIC3に対して2個の振幅変調用ミキサ回路MIX−HA,MIX−LAが加わった構成となっている。これ以外の構成に関しては、図18と同様であるため詳細な説明は省略する。MIX−HAは、DRV1の入出力と並列に設けられ、DIV1の出力を振幅変調用コードDAT−AMで振幅変調し、TXOUT1として出力する。同様に、MIX−LAは、DRV2の入出力と並列に設けられ、DIV2の出力をDAT−AMで振幅変調し、TXOUT2として出力する。

【0095】

DRV1,MIX−HA,DRV2,MIX−LAは、いずれか1個が活性化される。DRV1が活性化された場合には、TXOUT1として前述したようなPCS規格やDCS規格の信号が出力され、DRV2が活性化された場合には、TXOUT2として前述したようなGSM850規格やGSM900規格の信号が出力される。一方、MIX−HAが活性化された場合には、TXOUT1としてPCS規格やDCS規格のEDGE(Enhanced Data rates for GSM Evolutions)モードの信号が出力され、MIX−LAが活性化された場合には、TXOUT2としてGSM850規格やGSM900規格のEDGEモードの信号が出力される。EDGEモードでは、包括線変動が生じないGMSK変調とは異なり包括線変動が生じる8PSK(Phase Shift Keying)変調等が用いられるため、MIX−HA,MIX−LAによる振幅制御が必要となる。

【0096】

以上のように、本実施の形態2による高周波信号処理装置を用いることで、発振周波数の設定精度に加えて、変調精度や復調精度の向上が図れるため、代表的には、送信信号・受信信号の信号品質を向上させることが可能になる。更に、発振周波数遠方の雑音を低減できることから、例えばFDD方式では、送信信号と受信信号の干渉等を抑制でき、TDD方式においても、例えば、ある送信チャネルが他の送信チャネルに影響を及ぼすような事態を抑制できる。その結果、送信回路におけるSAWフィルタ等が不要となり、無線通信システムの小型化や低コスト化が図れる。

【0097】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。例えば、ここでは、本実施の形態によるディジタル制御発振回路を無線通信システムに適用したが、場合によっては有線の通信システムに適用することも可能である。

【符号の説明】

【0098】

ADD 合成回路

AMPBK アンプ回路ブロック

AMPM,AMPP アンプ回路

AR 領域

BIT_CI,BIT_CF オン・オフ制御線(オン・オフ制御信号)

BITND オン・オフ制御ノード

CA,CI,CF,CFX 容量素子

CABS,CINT,CFRAC 容量バンク

CFBK 容量ブロック

CIU 単位容量ユニット

CODE ディジタルコード

COX ゲート絶縁膜

CP 寄生容量

CT コンタクト層

DAT−AM 振幅変調用コード

DAT−DIVN 分周比設定コード

DAT−PM 位相変調用コード

DCO ディジタル制御発振回路

DEC デコーダ回路

DF 拡散層

DIV,DIVN 分周回路

DLPF ディジタルロウパスフィルタ

DPLL ディジタルPLL回路

DRV ドライバ回路

FDIV 分周発振信号

GLN 配線

GND 接地電源電圧

GS シールド部

GT ゲート層

IOL ロジック制御回路

ISL 絶縁膜

LNA ロウノイズアンプ回路

LP,LM コイル素子

LPFT,LPFR ロウパスフィルタ

M メタル配線層

MIX 振幅変調用ミキサ回路

MIXR 受信用ミキサ回路

MIXT 送信用ミキサ回路

MMD マルチモジュラス周波数分周回路

OscP,OscM 発振出力ノード

PGA プログラマブルゲイン回路

PLLCTL PLL制御回路

PLLOUT 発振出力信号

REF 基準発振信号

RFIC 高周波信号処理装置

RXIN 受信高周波信号

SDDCO DCO用シグマデルタ変調回路

SDM シグマデルタ変調回路

SUB 半導体基板

SWA,SWI,SWF スイッチ

TDC 時間差検出回路

TXIN 送信ベースバンド信号

TXOUT 送信高周波信号

V 固定電圧

VDD 電源電圧

VDRV 可変ドライバ回路

VGA 可変増幅回路

W_ABS 自動バンド制御信号

W_FRAC 分数容量値制御信号

W_INT 整数容量値制御信号

【特許請求の範囲】

【請求項1】

相補の発振出力信号が出力される第1及び第2発振出力ノードと、

前記第1発振出力ノードと前記第2発振出力ノードの間に結合されるコイル素子と、

それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備える複数の容量ユニットと、

前記第1発振出力ノードと前記第2発振出力ノードの間に負性抵抗を生成する負性抵抗生成回路とを備え、

前記複数の容量ユニットの一部は複数の第1容量ユニットとして第1容量バンクを構成し、

前記複数の容量ユニットの他の一部は第2容量バンクを構成し、

前記複数の第1容量ユニットの前記第1ノードは前記第1発振出力ノードに、前記第2ノードは前記第2発振出力ノードにそれぞれ結合され、

前記第2容量バンクは、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロックを含み、

前記容量ブロックは、

前記N個の容量ユニットの1個となる第2容量ユニットと、

前記第2容量ユニット以外となる(N−1)個の第3容量ユニットとを備え、

前記第2容量ユニットの前記第1ノードは前記第1発振出力ノードに、前記第2ノードは前記第2発振出力ノードにそれぞれ結合され、

前記(N−1)個の第3容量ユニットにおける前記第1及び第2ノードは、交流的な接地電源電圧に結合され、

前記第2容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードと共通に結合され、

前記第2容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードと共通に結合され、

前記第2容量ユニット及び前記(N−1)個の第3容量ユニットにおける前記第1スイッチは、オン・オフが共通に制御されることを特徴とするディジタル制御発振装置。

【請求項2】

請求項1記載のディジタル制御発振装置において、

前記複数の容量ユニットのそれぞれは、さらに、

前記第1容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第2スイッチと、

前記第2容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第3スイッチとを備えることを特徴とするディジタル制御発振装置。

【請求項3】

請求項2記載のディジタル制御発振装置において、

前記第2容量バンクは、更に、前記容量ブロックを複数備え、

前記複数の容量ブロックのいずれか1個となる第1容量ブロックは、前記「N」の値が2のM乗(Mは1以上の整数)の構成を備え、

前記複数の容量ブロックの他のいずれか1個となる第2容量ブロックは、前記「N」の値が2のJ乗(Jは1以上の整数であり、Mとは異なる値)の構成を備えることを特徴とするディジタル制御発振装置。

【請求項4】

請求項3記載のディジタル制御発振装置において、さらに、

前記相補の発振出力信号を分周し、分周発振信号を出力する分周回路と、

予め入力された基準発振信号の位相と前記分周発振信号の位相を比較し、当該比較結果を第1ディジタルコードとして出力する位相差検出回路と、

前記第1ディジタルコードを対象に平均化処理を行い、第2ディジタルコードを出力するディジタルフィルタと、

前記分周回路に分周比を設定すると共に、当該分周比を時系列的に変化させるシグマデルタ変調回路とを備え、

前記複数の第1容量ユニット内の前記第1スイッチのそれぞれは、前記第2ディジタルコードに基づいて制御され、

前記第1容量ブロックにおける前記第2容量ユニットおよび前記(N−1)個の第3容量ユニット内の前記第1スイッチは、前記第2ディジタルコードに基づいて共通に制御され、

前記第2容量ブロックにおける前記第2容量ユニットおよび前記(N−1)個の第3容量ユニット内の前記第1スイッチは、前記第2ディジタルコードに基づいて共通に制御されることを特徴とするディジタル制御発振装置。

【請求項5】

略リング状に形成され、第1軸を基準に対称に配置され、中点が交流的に接地されることで中点を基準として一方の側に第1コイル素子を、他方の側に第2コイル素子をそれぞれ実現するコイル用メタル配線と、

前記コイル用メタル配線の前記第1コイル素子側から分岐し、前記第1軸と直交する第2軸に沿って延伸する第1発振出力ノード用メタル配線と、

前記コイル用メタル配線の前記第2コイル素子側から分岐し、前記第2軸に沿って延伸する第2発振出力ノード用メタル配線と、

前記略リング状の形状を持つ前記コイル用メタル配線のリング内に形成され、マトリックス状に配置される複数の容量ユニットを含む容量バンクと、

前記コイル用メタル配線の前記リング内に形成され、前記第1発振出力ノード用メタル配線と前記第2発振出力ノード用メタル配線との間に負性抵抗を生成する負性抵抗生成回路とを備え、

前記複数の容量ユニットは、それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備え、

前記容量バンクは、

前記複数の容量ユニットの一部となる複数の第1容量ユニットで構成され、前記複数の第1容量ユニットの前記第1ノードは前記第1発振出力ノード用メタル配線に、前記第2ノードは前記第2発振出力ノード用メタル配線にそれぞれ結合される第1容量バンクと、

前記複数の容量ユニットの他の一部で構成され、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロックを含む第2容量バンクとを備え、

前記容量ブロックは、

前記N個の容量ユニットの1個となる第2容量ユニットと、

前記第2容量ユニット以外となる(N−1)個の第3容量ユニットとを備え、

前記第2容量ユニットの前記第1ノードは前記第1発振出力ノード用メタル配線に、前記第2ノードは前記第2発振出力ノード用メタル配線にそれぞれ結合され、

前記(N−1)個の第3容量ユニットにおける前記第1及び第2ノードは、交流的な接地電源電圧に結合され、

前記第2容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードと第1メタル配線を用いて共通に結合され、

前記第2容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードと第2メタル配線を用いて共通に結合され、

前記第2容量ユニット及び前記(N−1)個の第3容量ユニットにおける前記第1スイッチは、オン・オフが共通に制御されることを特徴とするディジタル制御発振装置。

【請求項6】

請求項5記載のディジタル制御発振装置において、

前記容量ブロックは、前記マトリックス状に配置される前記複数の容量ユニットの中から、列方向又は行方向に連続するN個の容量ユニットによって構成されることを特徴とするディジタル制御発振装置。

【請求項7】

請求項6記載のディジタル制御発振装置において、

前記第1容量ユニット内の前記第1容量素子における前記第1スイッチ側の電極は、前記第1メタル配線の形状を反映した形状を備え、

前記第1容量ユニット内の前記第2容量素子における前記第1スイッチ側の電極は、前記第2メタル配線の形状を反映した形状を備えることを特徴とするディジタル制御発振装置。

【請求項8】

請求項7記載のディジタル制御発振装置において、

前記複数の容量ユニットのそれぞれは、さらに、

前記第1容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第2スイッチと、

前記第2容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第3スイッチとを備えることを特徴とするディジタル制御発振装置。

【請求項9】

請求項5記載のディジタル制御発振装置において、

前記第2容量バンクは、更に、前記容量ブロックを複数備え、

前記複数の容量ブロックのいずれか1個となる第1容量ブロックは、前記「N」の値が2のM乗(Mは1以上の整数)の構成を備え、

前記複数の容量ブロックの他のいずれか1個となる第2容量ブロックは、前記「N」の値が2のJ乗(Jは1以上の整数であり、Mとは異なる値)の構成を備えることを特徴とするディジタル制御発振装置。

【請求項10】

請求項5記載のディジタル制御発振装置において、

前記負性抵抗生成回路は、前記コイル用メタル配線の前記リング内で略中心部分に配置されることを特徴とするディジタル制御発振装置。

【請求項11】

第1ディジタル制御発振回路と、

前記第1ディジタル制御発振回路を用いてベースバンド信号のアップコンバートを行う周波数変換回路とを備え、

前記第1ディジタル制御発振回路は、

相補の発振出力信号が出力される第1及び第2発振出力ノードと、

前記第1発振出力ノードと前記第2発振出力ノードの間に結合されるコイル素子と、

それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備える複数の容量ユニットと、

前記第1発振出力ノードと前記第2発振出力ノードの間に負性抵抗を生成する負性抵抗生成回路とを備え、

前記複数の容量ユニットの一部は複数の第1容量ユニットとして第1容量バンクを構成し、

前記複数の容量ユニットの他の一部は第2容量バンクを構成し、

前記複数の第1容量ユニットの前記第1ノードは前記第1発振出力ノードに、前記第2ノードは前記第2発振出力ノードにそれぞれ結合され、

前記第2容量バンクは、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロックを含み、

前記容量ブロックは、

前記N個の容量ユニットの1個となる第2容量ユニットと、

前記第2容量ユニット以外となる(N−1)個の第3容量ユニットとを備え、

前記第2容量ユニットの前記第1ノードは前記第1発振出力ノードに、前記第2ノードは前記第2発振出力ノードにそれぞれ結合され、

前記(N−1)個の第3容量ユニットにおける前記第1及び第2ノードは、交流的な接地電源電圧に接続され、

前記第2容量ユニットにおける前記第1スイッチの前記第1ノード側のノードは、前記(N−1)個の第3容量ユニットにおける前記第1スイッチの前記第1ノード側のノードと共通に結合され、

前記第2容量ユニットにおける前記第1スイッチの前記第2ノード側のノードは、前記(N−1)個の第3容量ユニットにおける前記第1スイッチの前記第2ノード側のノードと共通に結合され、

前記第2容量ユニット及び前記(N−1)個の第3容量ユニットにおける前記第1スイッチは、オン・オフが共通に制御されることを特徴とする高周波信号処理装置。

【請求項12】

請求項11記載の高周波信号処理装置において、

前記複数の容量ユニットのそれぞれは、さらに、

前記第1容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第2スイッチと、

前記第2容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第3スイッチとを備えることを特徴とする高周波信号処理装置。

【請求項13】

請求項12記載の高周波信号処理装置において、

前記第2容量バンクは、更に、前記容量ブロックを複数備え、

前記複数の容量ブロックのいずれか1個となる第1容量ブロックは、前記「N」の値が2のM乗(Mは1以上の整数)の構成を備え、

前記複数の容量ブロックの他のいずれか1個となる第2容量ブロックは、前記「N」の値が2のJ乗(Jは1以上の整数であり、Mとは異なる値)の構成を備えることを特徴とする高周波信号処理装置。

【請求項1】

相補の発振出力信号が出力される第1及び第2発振出力ノードと、

前記第1発振出力ノードと前記第2発振出力ノードの間に結合されるコイル素子と、

それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備える複数の容量ユニットと、

前記第1発振出力ノードと前記第2発振出力ノードの間に負性抵抗を生成する負性抵抗生成回路とを備え、

前記複数の容量ユニットの一部は複数の第1容量ユニットとして第1容量バンクを構成し、

前記複数の容量ユニットの他の一部は第2容量バンクを構成し、

前記複数の第1容量ユニットの前記第1ノードは前記第1発振出力ノードに、前記第2ノードは前記第2発振出力ノードにそれぞれ結合され、

前記第2容量バンクは、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロックを含み、

前記容量ブロックは、

前記N個の容量ユニットの1個となる第2容量ユニットと、

前記第2容量ユニット以外となる(N−1)個の第3容量ユニットとを備え、

前記第2容量ユニットの前記第1ノードは前記第1発振出力ノードに、前記第2ノードは前記第2発振出力ノードにそれぞれ結合され、

前記(N−1)個の第3容量ユニットにおける前記第1及び第2ノードは、交流的な接地電源電圧に結合され、

前記第2容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードと共通に結合され、

前記第2容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードと共通に結合され、

前記第2容量ユニット及び前記(N−1)個の第3容量ユニットにおける前記第1スイッチは、オン・オフが共通に制御されることを特徴とするディジタル制御発振装置。

【請求項2】

請求項1記載のディジタル制御発振装置において、

前記複数の容量ユニットのそれぞれは、さらに、

前記第1容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第2スイッチと、

前記第2容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第3スイッチとを備えることを特徴とするディジタル制御発振装置。

【請求項3】

請求項2記載のディジタル制御発振装置において、

前記第2容量バンクは、更に、前記容量ブロックを複数備え、

前記複数の容量ブロックのいずれか1個となる第1容量ブロックは、前記「N」の値が2のM乗(Mは1以上の整数)の構成を備え、

前記複数の容量ブロックの他のいずれか1個となる第2容量ブロックは、前記「N」の値が2のJ乗(Jは1以上の整数であり、Mとは異なる値)の構成を備えることを特徴とするディジタル制御発振装置。

【請求項4】

請求項3記載のディジタル制御発振装置において、さらに、

前記相補の発振出力信号を分周し、分周発振信号を出力する分周回路と、

予め入力された基準発振信号の位相と前記分周発振信号の位相を比較し、当該比較結果を第1ディジタルコードとして出力する位相差検出回路と、

前記第1ディジタルコードを対象に平均化処理を行い、第2ディジタルコードを出力するディジタルフィルタと、

前記分周回路に分周比を設定すると共に、当該分周比を時系列的に変化させるシグマデルタ変調回路とを備え、

前記複数の第1容量ユニット内の前記第1スイッチのそれぞれは、前記第2ディジタルコードに基づいて制御され、

前記第1容量ブロックにおける前記第2容量ユニットおよび前記(N−1)個の第3容量ユニット内の前記第1スイッチは、前記第2ディジタルコードに基づいて共通に制御され、

前記第2容量ブロックにおける前記第2容量ユニットおよび前記(N−1)個の第3容量ユニット内の前記第1スイッチは、前記第2ディジタルコードに基づいて共通に制御されることを特徴とするディジタル制御発振装置。

【請求項5】

略リング状に形成され、第1軸を基準に対称に配置され、中点が交流的に接地されることで中点を基準として一方の側に第1コイル素子を、他方の側に第2コイル素子をそれぞれ実現するコイル用メタル配線と、

前記コイル用メタル配線の前記第1コイル素子側から分岐し、前記第1軸と直交する第2軸に沿って延伸する第1発振出力ノード用メタル配線と、

前記コイル用メタル配線の前記第2コイル素子側から分岐し、前記第2軸に沿って延伸する第2発振出力ノード用メタル配線と、

前記略リング状の形状を持つ前記コイル用メタル配線のリング内に形成され、マトリックス状に配置される複数の容量ユニットを含む容量バンクと、

前記コイル用メタル配線の前記リング内に形成され、前記第1発振出力ノード用メタル配線と前記第2発振出力ノード用メタル配線との間に負性抵抗を生成する負性抵抗生成回路とを備え、

前記複数の容量ユニットは、それぞれ、同一の回路構成および略同一のレイアウト構成を持ち、第1ノードと第2ノードとの間で順に直列に結合される第1容量素子、第1スイッチ、第2容量素子を備え、

前記容量バンクは、

前記複数の容量ユニットの一部となる複数の第1容量ユニットで構成され、前記複数の第1容量ユニットの前記第1ノードは前記第1発振出力ノード用メタル配線に、前記第2ノードは前記第2発振出力ノード用メタル配線にそれぞれ結合される第1容量バンクと、

前記複数の容量ユニットの他の一部で構成され、N個(Nは2以上の整数)の容量ユニットで構成される容量ブロックを含む第2容量バンクとを備え、

前記容量ブロックは、

前記N個の容量ユニットの1個となる第2容量ユニットと、

前記第2容量ユニット以外となる(N−1)個の第3容量ユニットとを備え、

前記第2容量ユニットの前記第1ノードは前記第1発振出力ノード用メタル配線に、前記第2ノードは前記第2発振出力ノード用メタル配線にそれぞれ結合され、

前記(N−1)個の第3容量ユニットにおける前記第1及び第2ノードは、交流的な接地電源電圧に結合され、

前記第2容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第1容量素子の前記第1スイッチ側のノードと第1メタル配線を用いて共通に結合され、

前記第2容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードは、前記(N−1)個の第3容量ユニットにおける前記第2容量素子の前記第1スイッチ側のノードと第2メタル配線を用いて共通に結合され、

前記第2容量ユニット及び前記(N−1)個の第3容量ユニットにおける前記第1スイッチは、オン・オフが共通に制御されることを特徴とするディジタル制御発振装置。

【請求項6】

請求項5記載のディジタル制御発振装置において、

前記容量ブロックは、前記マトリックス状に配置される前記複数の容量ユニットの中から、列方向又は行方向に連続するN個の容量ユニットによって構成されることを特徴とするディジタル制御発振装置。

【請求項7】

請求項6記載のディジタル制御発振装置において、

前記第1容量ユニット内の前記第1容量素子における前記第1スイッチ側の電極は、前記第1メタル配線の形状を反映した形状を備え、

前記第1容量ユニット内の前記第2容量素子における前記第1スイッチ側の電極は、前記第2メタル配線の形状を反映した形状を備えることを特徴とするディジタル制御発振装置。

【請求項8】

請求項7記載のディジタル制御発振装置において、

前記複数の容量ユニットのそれぞれは、さらに、

前記第1容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第2スイッチと、

前記第2容量素子の前記第1スイッチ側のノードと交流的な接地電源電圧との間に結合され、オン・オフが当該第1スイッチと共通に制御される第3スイッチとを備えることを特徴とするディジタル制御発振装置。

【請求項9】

請求項5記載のディジタル制御発振装置において、