ディスプレイドライバーとその動作方法、ホストの動作方法、イメージ処理システム、携帯用通信装置、及びアプリケーションホストプロセッサの動作方法

【課題】ディスプレイドライバーとその動作方法、ホストの動作方法、イメージ処理システム、携帯用通信装置、及びアプリケーションホストプロセッサの動作方法を提供する。

【解決手段】本発明のディスプレイドライバーの動作方法は、ホストから伝送された同期パケットに関連する同期信号の周期をカウントしてカウント値を生成する段階と、フレームメモリをバイパスして第1イメージデータをディスプレイに伝送するビデオモードからフレームメモリを通じて第2イメージデータをディスプレイに伝送する命令モードへの転換を指示するモード転換命令を、ホストから受信する段階と、同期信号の最後のパルスが生成された後、モード転換命令によって、カウント値を用いて同期信号の周期と同じ周期を有する内部同期信号を生成する段階と、を有し、同期信号の最後のパルスと内部同期信号の最初のパルスとの時間間隔は、同期信号の周期と同一である。

【解決手段】本発明のディスプレイドライバーの動作方法は、ホストから伝送された同期パケットに関連する同期信号の周期をカウントしてカウント値を生成する段階と、フレームメモリをバイパスして第1イメージデータをディスプレイに伝送するビデオモードからフレームメモリを通じて第2イメージデータをディスプレイに伝送する命令モードへの転換を指示するモード転換命令を、ホストから受信する段階と、同期信号の最後のパルスが生成された後、モード転換命令によって、カウント値を用いて同期信号の周期と同じ周期を有する内部同期信号を生成する段階と、を有し、同期信号の最後のパルスと内部同期信号の最初のパルスとの時間間隔は、同期信号の周期と同一である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ディスプレイドライバーに係り、より詳しくは、動作途中でモード転換命令によってビデオモードと命令モードとの間でモード転換ができるディスプレイドライバーとその動作方法、ディスプレイドライバーを制御するホストの動作方法、イメージ処理システム、携帯用通信装置、及びアプリケーションホストプロセッサの動作方法に関する。

【背景技術】

【0002】

映像解像度の増加に伴い、モバイルアプリケーションプロセッサとディスプレイドライバーIC(integrated circuit)との間のデータトラフィックが急速に増加している。これにより、モバイルアプリケーションプロセッサ及び/又はディスプレイドライバーICで消耗する電力も継続的に増加している。

【0003】

音声通話中心の既存の携帯電話は、マルチメディアデータ中心のスマートフォンに急速に代替されている。スマートフォンに具現されたディスプレイドライバーICは、静止映像信号又は動画信号のようなマルチメディアデータをディスプレイで表示するために頻繁に作動する。

【0004】

従って、スマートフォンのバッテリーの持続時間が減少する。バッテリーの持続時間は、一回の充電で使い続けることが可能なバッテリーの使用時間を意味する。これにより、静止映像信号と動画信号とを処理するスマートフォンのような移動通信装置のバッテリーの持続時間を延ばすことができる方法が必要である。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、上記従来の問題点に鑑みてなされたものであって、本発明の目的は、省力化のために、動作途中でモード転換命令によってビデオモードと命令モードとの間でモード転換ができ、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令によって、メモリを用いて静止映像信号をディスプレイに伝送するか、又はメモリを利用せずに動画信号をディスプレイに伝送するかを決定するディスプレイドライバーとその動作方法、ディスプレイドライバーを制御するホストの動作方法、イメージ映像信号処理システム、携帯用通信装置、及びアプリケーションホストプロセッサの動作方法を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するためになされた本発明の一態様によるディスプレイドライバーの動作方法は、ホストから伝送された同期パケットに関連する同期信号の周期をカウントしてカウント値を生成する段階と、フレームメモリをバイパスして第1イメージデータをディスプレイに伝送するビデオモードから前記フレームメモリを通じて第2イメージデータを前記ディスプレイに伝送する命令モードへの転換を指示するモード転換命令を、前記ホストから受信する段階と、前記同期信号の最後のパルスが生成された後、前記モード転換命令によって、前記カウント値を用いて前記同期信号の周期と同じ周期を有する内部同期信号を生成する段階と、を有し、前記最後のパルスと前記内部同期信号の最初のパルスとの時間間隔は、前記同期信号の周期と同一である。

【0007】

前記ディスプレイドライバーの動作方法は、前記時間間隔の間に、前記第1イメージデータを前記ディスプレイにバイパスすると同時に前記フレームメモリに書き込む段階を更に含む。

前記第1イメージデータのフレームレートは、前記第2イメージデータのフレームレートより大きい。

前記ディスプレイドライバーの動作方法は、前記同期信号の周期と前記内部同期信号の周期との差を計算する段階と、前記差を用いてティアリング効果制御信号の発生タイミングを調節し、該ティアリング効果制御信号を前記ホストに伝送する段階と、を更に含む。

【0008】

上記目的を達成するためになされた本発明の一態様によるディスプレイドライバーの動作を制御するホストの動作方法は、前記ディスプレイドライバーからティアリング効果制御信号と誤差情報とを受信する段階と、前記ティアリング効果制御信号と前記誤差情報とを用いて、前記ディスプレイドライバーで復元される同期信号に関連する同期パケットの発生タイミングを調節する段階と、を有する。

【0009】

前記誤差情報は、前記同期信号の周期と前記同期信号の周期を用いて前記ディスプレイドライバーで生成された内部同期信号の周期との差に対応する情報である。

【0010】

上記目的を達成するためになされた本発明の他の態様によるディスプレイドライバーの動作を制御するホストの動作方法は、前記ディスプレイドライバーから誤差情報を受信する段階と、前記誤差情報に基づいてティアリング効果制御信号の発生タイミングを制御するための制御値を前記ディスプレイドライバーに伝送する段階と、前記ディスプレイドライバーから、前記制御値によって前記発生タイミングが制御されたティアリング効果制御信号を受信する段階と、前記制御されたティアリング効果制御信号によって、前記ディスプレイドライバーで復元される同期信号に関連する同期パケットを生成する段階と、を有する。

【0011】

前記誤差情報は、前記同期信号の周期と前記同期信号の周期を用いて前記ディスプレイドライバーで生成された内部同期信号の周期との差に対応する情報である。

【0012】

上記目的を達成するためになされた本発明の一態様によるイメージ処理システムは、ディスプレイドライバーと、前記ディスプレイドライバーの動作を制御するホストと、を有し、前記ディスプレイドライバーは、前記ホストから伝送された同期パケットに関連する同期信号の周期をカウントしてカウント値を生成し、フレームメモリをバイパスして第1イメージデータをディスプレイに伝送するビデオモードから前記フレームメモリを通じて第2イメージデータを前記ディスプレイに伝送する命令モードへの転換を指示する第1モード転換命令を、前記ホストから受信し、前記同期信号の最後のパルスが生成された後、前記カウント値を用いて前記同期信号の周期と同じ周期を有する内部同期信号を生成し、前記最後のパルスと前記内部同期信号の最初のパルスとの時間間隔は、前記同期信号の周期と同一であり、前記ビデオモードから前記命令モードに転換された後、前記ホストは、新たな同期パケットを前記ディスプレイドライバーに伝送しない。

【0013】

前記ディスプレイドライバーは、前記同期信号の周期と前記内部同期信号の周期との差を計算し、前記命令モードから前記ビデオモードへの転換を指示する第2モード転換命令を前記ホストから受信した後、前記差を用いてティアリング効果制御信号の発生タイミングを調節し、該ティアリング効果制御信号を前記ホストに伝送し、前記ホストは、前記ティアリング効果制御信号によって新たな同期パケットを生成する。

【0014】

上記目的を達成するためになされた本発明の他の態様によるイメージ処理システムは、ディスプレイドライバーと、前記ディスプレイドライバーの動作を制御するホストと、を有し、前記ディスプレイドライバーは、フレームメモリを通じて第1イメージデータをディスプレイに伝送する命令モードから前記フレームメモリをバイパスして第2イメージデータを前記ディスプレイに伝送するビデオモードへの転換を指示するモード転換命令によって、ティアリング効果制御信号と誤差情報とを前記ホストに伝送し、前記ホストは、前記ティアリング効果制御信号と前記誤差情報とを用いて、前記ディスプレイドライバーで復元される同期信号に関連する同期パケットの発生タイミングを調節する。

【0015】

前記ホストは、前記命令モードの間に、前記ディスプレイで生成された内部同期信号の最後のパルスと前記同期信号の最初のパルスとの時間間隔が前記内部同期信号の周期と同一になるように、前記同期パケットの前記発生タイミングを調節する。

【0016】

上記目的を達成するためになされた本発明の更に他の態様によるイメージ処理システムは、ディスプレイドライバーと、前記ディスプレイドライバーの動作を制御するホストと、を有し、前記ディスプレイドライバーは、フレームメモリを使って第1イメージデータをディスプレイに伝送する命令モードから前記フレームメモリをバイパスして第2イメージデータを前記ディスプレイに伝送するビデオモードへの転換を指示するモード転換命令によって、誤差情報を前記ホストに伝送し、前記ホストは、前記誤差情報に基づいてティアリング効果制御信号の発生タイミングを制御するための制御値を前記ディスプレイドライバーに伝送し、前記ホストは、前記ディスプレイドライバーから前記制御値によって生成されたティアリング効果制御信号を受信し、該受信したティアリング効果制御信号によって前記ディスプレイドライバーで復元される同期信号に関連する同期パケットを生成する。

【0017】

上記目的を達成するためになされた本発明の一態様によるディスプレイドライバーは、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を含む前記映像信号を受信する受信器と、前記受信器から出力された前記モード転換命令に応答して、第1制御信号と第2制御信号とを生成する制御回路と、前記第1制御信号に応答して、前記受信器から出力された前記静止映像信号を、メモリを用いて出力する第1インターフェースと、前記第2制御信号に応答して、前記受信器から出力された前記動画信号を、前記メモリを利用せずに出力する第2インターフェースと、を備える。

【0018】

前記第1インターフェースは、前記第1制御信号に応答して、前記静止映像信号の伝送を制御する第1スイッチング回路と、前記モード転換命令によって、前記制御回路から出力された選択信号に応答して、前記第1スイッチング回路から伝送された前記静止映像信号と前記第2インターフェースから伝送された前記動画信号とのうちの何れか1つを前記メモリに伝送する選択回路と、を含む。

前記第1インターフェースは、MIPI(Mobile Industry Processor Interface)命令モードをサポートするインターフェース又はCPUインターフェースであり、前記第2インターフェースは、MIPIビデオモードをサポートするインターフェース又はRGBインターフェースである。

前記モード転換命令は、前記映像信号に含まれる垂直ブランキング区間に含まれる。

前記ディスプレイドライバーは、第1選択信号に応答して、前記メモリから出力された前記静止映像信号又は前記第2インターフェースから出力された前記動画信号を出力する第1選択回路と、前記第1選択回路から出力された映像信号を前記ディスプレイに伝送する出力回路と、を更に含み、前記制御回路は、前記モード転換命令に応答して、前記第1選択信号を生成する。

【0019】

上記目的を達成するためになされた本発明の一態様による携帯用通信装置は、ディスプレイと、前記ディスプレイに映像信号を伝送するためのディスプレイドライバーと、前記ディスプレイドライバーに、前記ディスプレイで表示される前記映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を含む前記映像信号を伝送するホストと、を有し、前記ディスプレイドライバーは、前記モード転換命令に応答して、第1制御信号と第2制御信号とを生成する制御回路と、前記第1制御信号によって、メモリを用いて前記静止映像信号を前記ディスプレイに伝送する第1インターフェースと、前記第2制御信号によって、前記メモリを利用せずに前記動画信号を前記ディスプレイに伝送する第2インターフェースと、を含む。

【0020】

前記ディスプレイドライバーは、第1選択信号に応答して、前記第1インターフェースの出力ポートと前記第2インターフェースの出力ポートとのうちの何れか1つから出力された前記映像信号を出力する第1選択回路と、前記第1選択回路から出力された映像信号を前記ディスプレイに伝送する出力回路と、を更に含み、前記第1インターフェースは、前記第1制御信号に応答して、前記静止映像信号を伝送する第1スイッチング回路と、第2選択信号に応答して、前記第1スイッチング回路から出力された前記静止映像信号と前記第2インターフェースから出力された前記動画信号とのうちの何れか1つを前記メモリに出力する第2選択回路と、スキャンスイッチング信号に応答して、前記メモリに保存された前記静止映像信号を前記第1選択回路に伝送するスキャンスイッチング回路と、を含み、前記第2インターフェースは、前記第2制御信号に応答して、前記動画信号を前記第1選択回路と前記第2選択回路とのうちの少なくとも1つに伝送する第2スイッチング回路を含み、前記制御回路は、前記モード転換命令に応答して、前記第1選択信号、前記第2選択信号、及び前記スキャンスイッチング信号を生成する。

前記ホストは、コーデックの実行によって前記映像信号が前記静止映像信号又は前記動画信号であるか否かを判断し、該判断結果によって前記モード転換命令を生成する。

前記ホストは、前記動画信号の次に前記静止映像信号が伝送されることを指示する前記モード転換命令を垂直ブランキング区間に前記ディスプレイドライバーに伝送した後、最初の静止映像信号を最初のティアリング効果制御信号の立下りエッジの前に前記ディスプレイドライバーに伝送する。

前記第2インターフェースは、前記第2制御信号によって、前記動画信号を前記ディスプレイに伝送すると同時に前記メモリに伝送し、前記第1インターフェースは、前記制御回路から出力されたスイッチング信号によって、前記メモリに保存された前記動画を前記ディスプレイドライバーに伝送する。

【0021】

上記目的を達成するためになされた本発明の他の態様によるディスプレイドライバーの動作方法は、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令に応答して、制御信号を生成する段階と、前記制御信号によって、メモリを経由して前記静止映像信号を前記ディスプレイに伝送する命令モードと前記メモリを経由せずに前記動画信号を前記ディスプレイに伝送するビデオモードとの間でスイッチングする段階と、を有する。

【0022】

前記モード転換命令は、前記映像信号の垂直ブランク区間に含まれる。

前記ビデオモードと前記命令モードとの間でスイッチングされる際、前記映像信号は、前記映像信号の少なくとも1フレームの間に前記ディスプレイに伝送されない段階を更に含む。

【0023】

上記目的を達成するためになされた本発明の一態様によるアプリケーションホストプロセッサの動作方法は、ディスプレイドライバーから出力されたティアリング効果制御信号をモニタリングする段階と、前記モニタリング結果によって、前記ディスプレイドライバーに伝送される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を前記映像信号の垂直ブランキング区間に伝送する段階と、を有する。

【0024】

前記アプリケーションホストプロセッサの動作方法は、前記モード転換命令を伝送した後、直ちに前記動画信号を前記ディスプレイドライバーに伝送する段階を更に含む。

前記モード転換命令は、前記垂直ブランキング区間の垂直フロントポーチ又は垂直バックポーチに伝送される。

前記アプリケーションホストプロセッサの動作方法は、前記モード転換命令を伝送した後の最初の静止映像信号を前記ティアリング効果制御信号の立下りエッジの前に伝送する段階を更に含む。

【発明の効果】

【0025】

本発明のディスプレイドライバーによれば、動作途中でモード転換命令によってビデオモードと命令モードとの間でモード転換を行うことができる。従って、ディスプレイドライバーで消耗する電力を効果的に減らすことができる。

また、本発明のディスプレイドライバーによれば、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令によって、メモリを用いて静止映像信号をディスプレイに伝送するか又はメモリを利用せずに動画信号をディスプレイに伝送するかを決定することができる。従って、ディスプレイドライバーで消耗する電力を減らすことができる。

【図面の簡単な説明】

【0026】

【図1】本発明の一実施形態による映像信号処理システムのブロック図である。

【図2】ホストからディスプレイドライバーに伝送されるパケットの一例を示す図である。

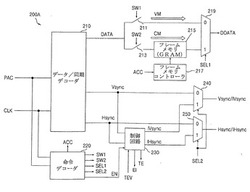

【図3】図1に示したディスプレイドライバーの一例を示すブロック図である。

【図4】図3に示したディスプレイドライバーの動作を説明するフローチャートである。

【図5】図3に示したディスプレイドライバーの動作を説明するタイミング図である。

【図6】図3に示した制御回路の一例を示すブロック図である。

【図7】本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するフローチャートである。

【図8】本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するタイミング図である。

【図9】図1に示したホストの一例を示す内部ブロック図である。

【図10】図9に示したホストの同期パケットの発生タイミングを制御する方法を説明するフローチャートである。

【図11】図9に示したホストのティアリング効果制御信号の発生タイミングを制御するための制御値を生成する方法を説明するフローチャートである。

【図12】本発明の他の実施形態による映像信号処理システムのブロック図である。

【図13】図12に示したディスプレイドライバーの一例を示すブロック図である。

【図14】図12に示したディスプレイドライバーの動作を説明するフローチャートである。

【図15】本発明の更に他の実施形態による映像信号処理システムのブロック図である。

【図16】図15に示したアプリケーションホストプロセッサの一例を示す概略的なブロック図である。

【図17】図16に示したアプリケーションホストプロセッサの動作を説明するフローチャートである。

【図18】図16に示したアプリケーションホストプロセッサから出力されるモード転換命令を含む映像信号及びクロック信号の波形図である。

【図19】図15に示したディスプレイドライバーの一例を示す概略的なブロック図である。

【図20】図19に示したディスプレイドライバーの動作モードによる映像信号経路の一例を示す図である。

【図21】図19に示したディスプレイドライバーの動作モードによるデータの流れの一例を示す図である。

【図22】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の一例を示すタイミング図である。

【図23】図19に示したディスプレイドライバーの動作モードによるデータの流れの変形例を示す図である。

【図24】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の変形例を示すタイミング図である。

【図25】図19に示したディスプレイドライバーの動作モードによる映像信号経路の他の例を示す図である。

【図26】図19に示したディスプレイドライバーの動作モードによるデータの流れの他の例を示す図である。

【図27】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の他の例を示すタイミング図である。

【図28】図19に示したディスプレイドライバーの動作モードによる映像信号経路の更に他の例を示す図である。

【図29】図19に示したディスプレイドライバーの動作モードによるデータの流れの更に他の例を示す図である。

【図30】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の更に他の例を示すタイミング図である。

【発明を実施するための形態】

【0027】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

【0028】

図1は、本発明の一実施形態による映像信号処理システムのブロック図であり、図2は、ホストからディスプレイドライバーに伝送されるパケットの一例を示す図である。図1を参照すると、映像信号処理システム10Aは、静止映像信号又は動画信号をディスプレイ300で表示する携帯電話、スマートフォン、タブレットPC(personal computer)、PDA(Personal Digital Assistant)、又はPMP(Portable Multimedia Player)のような移動型の装置、小型機器(handheld device)又は小型コンピュータを意味する。

【0029】

映像信号処理システム10Aは、アプリケーションホストプロセッサ(以下、‘ホスト’と称する)100、ディスプレイドライバーIC(DDI)200A、及びディスプレイ300を含む。

【0030】

一実施形態として、ホスト100は、ホスト100の内部に具現されたコーデックの実行によって、ディスプレイ300で表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を有する命令パケットCPを含むパケットPACをディスプレイドライバーIC200Aに伝送する。他の実施形態として、ホスト100は、ディスプレイ300で表示されるイメージデータのフレームレートによって、イメージデータを、フレームメモリをバイパスしてディスプレイ300に伝送するか、又はフレームメモリを通じてディスプレイ300に伝送するかを指示するモード転換命令を有する命令パケットCPを含むパケットPACをディスプレイドライバーIC200Aに伝送し得る。

【0031】

例えば、イメージデータのフレームレートが30fps(frames per second)より小さい場合、イメージデータはフレームメモリを通じてディスプレイ300に伝送され、それ以外の場合、イメージデータはフレームメモリをバイパスしてディスプレイ300に伝送される。

【0032】

図1及び図2を参照すると、クロック信号CLKによって、ホスト100からディスプレイドライバーIC200Aに伝送されるパケットPACは、垂直同期パケットVS、水平同期パケットHS、データストリームパケット(DS)、及び命令パケットCPを含む。ここで、パケットは、ビットの集合である。

【0033】

垂直同期パケットVSは、映像信号(又は、イメージデータ)を表示するために必要な垂直同期信号に関連する情報を含み、水平同期パケットHSは、映像信号を表示するために必要な水平同期信号に関連する情報を含む。従って、ディスプレイドライバーIC200Aは、垂直同期パケットVSから垂直同期信号を復元し、水平同期パケットHSから水平同期信号を復元する。この際、クロック信号CLKが、復元に使われる。

【0034】

データストリームパケットDSは、ディスプレイ300で表示される映像信号を含み、命令パケットCPは、ディスプレイドライバーIC200Aの動作及び/又はディスプレイ300の動作に関連する命令を含む。例えば、命令パケットCPは、モード転換命令を含む。

【0035】

ホスト100は、ディスプレイドライバーIC200Aから出力されたティアリング効果(tearing effect:TE)制御信号TEを受信し、該受信したTE制御信号TEによって、パケットPACの生成タイミング又は伝送タイミングを制御する。従って、パケットPACの生成タイミング又は伝送タイミングによって、垂直同期信号及び/又は水平同期信号の復元タイミングが制御される。ここで、TE制御信号TEは、ティアリング又はスクリーンティアリング(一画面に複数のフレームが表示されることで歪みやちらつきが見える現象)を防止するための制御信号である。

【0036】

例えば、垂直同期信号Vsyncの生成タイミングは、TE制御信号TEの生成タイミングによって決定される。また、TE制御信号TEの生成タイミングは、ホスト100によって設定された制御値TEVによって、ディスプレイドライバーIC200Aによって制御される。即ち、制御値TEVによって、TE制御信号TEの生成タイミング、垂直同期信号Vsyncの生成タイミング、及び/又は水平同期信号Hsyncの生成タイミングが制御される。一実施形態として、ホスト100は、TE制御信号TEと誤差情報EIとを用いて、パケットPACの生成タイミング又は伝送タイミングを制御する。他の実施形態として、ホスト100は、誤差情報EIを用いて制御値TEVを調節することができる。

【0037】

ディスプレイドライバーIC200Aは、ホスト100から出力されたパケットPACに含まれるデータストリームパケットDSを処理又は復元し、ホスト100から出力されたパケットPACの命令パケットCPに含まれるモード転換命令に応答して、処理又は復元されたデータDDATAを、フレームメモリを通じてディスプレイ300に伝送するか、又はフレームメモリをバイパスしてディスプレイ300に伝送するかを決定する。

【0038】

この際、ビデオモードVMで、ディスプレイドライバーIC200Aは、フレームメモリをバイパスしたデータDDATAと共に同期信号Syncをディスプレイ300に伝送する。また、命令モードCMで、ディスプレイドライバーIC200Aは、フレームメモリを通じて出力されたデータDDATAを内部同期信号ISyncと共にディスプレイ300に伝送する。

【0039】

ディスプレイ300は、同期信号Sync又は内部同期信号ISyncを用いて、ディスプレイドライバーIC200Aから出力された出力映像信号DDATAを表示する。例えば、ディスプレイ300は、LCD(Liquid CrystalDisplay)、LED(Light Emitting Diode)ディスプレイ、OLED(Organic LED)ディスプレイ、又はAMOLED(Active−Matrix OLED)ディスプレイとして具現可能である。

【0040】

図3は、図1に示したディスプレイドライバーの一例を示すブロック図であり、図4は、図3に示したディスプレイドライバーの動作を説明するフローチャートであり、図5は、図3に示したディスプレイドライバーの動作を説明するタイミング図である。図1〜図3を参照すると、ディスプレイドライバーIC200Aは、データ/同期デコーダ(data/synchronization decoder)210、第1スイッチ回路211、第2スイッチ回路213、フレームメモリ(GRAM)215、フレームメモリコントローラ217、第1選択回路219、命令デコーダ220、制御回路230、第2選択回路240、及び第3選択回路250を含む。

【0041】

クロック信号CLKに応答して、データ/同期デコーダ210は、パケットPACに含まれるデータストリームパケットDSから映像信号DATAを復元し、垂直同期パケットVSから垂直同期信号Vsyncを復元し、水平同期パケットHSから水平同期信号Hsyncを復元する。一実施形態として、データ/同期デコーダ210は、デシリアライザ(deserializer)として具現可能である。

【0042】

第1スイッチ回路211は、復元映像信号DATAを第1スイッチング信号SW1に応答して第1選択回路219に伝送する。第2スイッチ回路213は、復元映像信号DATAを第2スイッチング信号SW2に応答してフレームメモリ(GRAM)215に伝送する。一実施形態として、第1及び第2スイッチ回路211、213は、NMOSトランジスタで具現された少なくとも1つのスイッチを含む。他の実施形態として、第1及び第2スイッチ回路211、213は、バスコントローラの機能を行うことができる。

【0043】

例えば、第1スイッチ回路211は、フレームメモリ215を通じないで動画信号を処理するMIPI(Mobile Industry Processor Interface)ビデオモードをサポートするインターフェース又はRGBインターフェースである。

【0044】

第2スイッチ回路213は、静止映像信号を処理するために、フレームメモリ215を使うMIPI命令モードをサポートするインターフェース、CPU(Central Processing Unit)インターフェース又はMCU(Micro Controller Unit)インターフェースである。

【0045】

フレームメモリコントローラ217の制御によって、フレームメモリ(GRAM)215は、第2スイッチ回路213を通じて入力された復元映像信号DATAを受信して保存する。例えば、フレームメモリ215は、グラフィックメモリとして具現可能である。

【0046】

フレームメモリコントローラ217は、命令デコーダ220から出力されたアクセス制御信号ACCによって、フレームメモリ(GRAM)215のライト動作又はリード動作を制御する。一実施形態として、アクセス制御信号ACCは、ライト動作に関連する制御信号又はリード動作に関連する制御信号である。

【0047】

第1選択信号SEL1によって、第1選択回路219は、第1スイッチ回路211を通じて入力された復元映像信号DATA又はフレームメモリ(GRAM)215から出力された映像信号を出力映像信号DDATAとしてディスプレイ300に伝送する。例えば、第1選択信号SEL1が論理0又はローレベルであると、第1選択回路219は、第1スイッチ回路211を通じて入力された復元映像信号DATAを出力し、第1選択信号SEL1が論理1又はハイレベルであると、第1選択回路219は、フレームメモリ215から出力された映像信号を出力する。例えば、第1選択回路219は、マルチプレクサとして具現可能である。

【0048】

命令デコーダ220は、クロック信号CLKによって、パケットPACに含まれる命令パケットCPをデコーディングし、該デコーディング結果によって、アクセス制御信号ACC、複数のスイッチング信号SW1、SW2、複数の選択信号SEL1、SEL2、及びイネーブル信号ENを生成する。

【0049】

制御回路230は、TE制御信号TE及び/又はエラー情報EIをホスト100に出力する。

【0050】

一実施形態として、制御回路230は、パケットPACの生成タイミング又は出力タイミングを制御するために、TE制御信号TEとエラー情報EIとをホスト100に伝送する。他の実施形態として、制御回路230は、パケットPACの生成タイミング又は出力タイミングを制御するために、エラー情報EIのみをホスト100に伝送し得る。更に他の実施形態として、制御回路230は、パケットPACの生成タイミング又は出力タイミングを制御するために、制御値TEVによってTE制御信号TEの生成タイミングを制御し、その結果として生成されたTE制御信号TEをホスト100に伝送し得る。

【0051】

また、制御回路230は、イネーブル信号ENに応答して、垂直同期信号Vsyncの周期と同じ周期を有する内部垂直同期信号IVsyncを出力し、水平同期信号Hsyncの周期と同じ周期を有する内部水平同期信号IHsyncを出力する。

【0052】

第2選択信号SEL2によって、第2選択回路240は、ビデオモードVMの間に垂直同期信号Vsyncを、そして命令モードCMの間に内部垂直同期信号IVsyncを出力する。第2選択信号SEL2によって、第3選択回路250は、ビデオモードVMの間に水平同期信号Hsyncを、そして命令モードCMの間に内部水平同期信号IHsyncを出力する。

【0053】

例えば、第2選択信号SEL2が論理0又はローレベルであると、第2及び第3選択回路240、250は、ビデオモードVMを行うために、各同期信号Vsync、Hsyncを出力し、第2選択信号SEL2が論理1又はハイレベルであると、第2及び第3選択回路240、250は、命令モードCMを行うために、各内部同期信号IVsync、IHsyncを出力する。

【0054】

例示的に、命令パケットCPに含まれるモード転換命令が2ビットで具現される場合、モード転換命令によるディスプレイドライバーIC200Aの動作モードと各制御信号SW1、SW2、SEL1、及びSEL2の状態は、表1のようである。

【0055】

【表1】

【0056】

この際、オーバーラップモード(overlap mode)は、ビデオモードVMから命令モードCMへの転換を指示するモード転換命令(図5のMCC参照)によって、ディスプレイドライバーIC200Aが、前記命令モードCMを行う前の少なくとも1フレームの間に、ビデオモードVMで入力されたイメージデータをディスプレイ300にバイパスすると同時にフレームメモリ217に書き込む動作を意味する。

【0057】

ディスプレイドライバーIC200Aの動作モードが、モード転換命令によって、フレームメモリ215をバイパスして第1イメージデータをディスプレイ300に伝送するビデオモードVMから、フレームメモリ217を通じて第2イメージデータをディスプレイ300に伝送する命令モードCMに転換される手順を、図1〜図5を参照して説明すると、次の通りである。この際、第1イメージデータのフレームレートは、第2イメージデータのフレームレートより大きい。

【0058】

ビデオモードVMの間に、データ/同期デコーダ210は、ホスト100からパケットPACを受信し(ステップS10)、パケットPACに含まれる垂直同期パケットVSを用いて垂直同期信号Vsyncを復元し、パケットPACに含まれる水平同期パケットHSを用いて水平同期信号Hsyncを復元し、パケットPACに含まれるデータストリームDSからデータDATAを復元する(ステップS20)。

【0059】

命令デコーダ220は、パケットPACに含まれる命令パケットCPによって、ビデオモードを行うための複数の制御信号SW1、SW2、SEL1、及びSEL2を生成する。各制御信号SW1、SW2、SEL1、及びSEL2のレベルは、表1のようである。

【0060】

第1選択回路219は、第1スイッチ回路211を通じて入力された復元データDATAをディスプレイ300に伝送し、第2及び第3選択回路240、250は、各同期信号Vsync、Hsyncをディスプレイ300に伝送する(ステップS30)。

【0061】

第1区間INT1の間に、制御回路230は、垂直同期信号Vsyncの周期T1をカウントして第1カウント値を生成し、水平同期信号Hsyncの周期T2をカウントして第2カウント値を生成する(ステップS40)。

【0062】

ホスト100は、ビデオモードから命令モードへの転換を指示するモード転換命令MCCを有する命令パケット101をパケットPACに含めてディスプレイドライバーIC200Aに伝送する。ディスプレイドライバーIC200Aは、命令パケット101を受信する(ステップS50)。モード転換命令MCCは、モード転換の1フレーム前又は数フレーム前にディスプレイドライバーIC200Aに伝送される。

【0063】

命令デコーダ220は、命令パケット101に含まれるビット、例えば‘00’をデコーディングし、該デコーディング結果によって、複数の制御信号SW1、SW2、SEL1、及びSEL2を生成する。

【0064】

この際、オーバーラップ区間INT2の間に、復元データDATAは、第1スイッチ回路211と第1選択回路219とを通じてディスプレイ300にバイパスされると同時に、第2スイッチ回路213を通じてフレームメモリ215に書き込まれる。この際、復元データDATAと共に、各同期信号Vsync、Hsyncは、ディスプレイ300に伝送される。従って、ディスプレイ300は、各同期信号Vsync、Hsyncを用いて、復元データDATAを表示する。

【0065】

モード転換命令MCCを受信した後、制御回路230は、垂直同期信号Vsyncの最後のパルスLPを受信した後に第1カウント値を用いて、垂直同期信号Vsyncの周期T1と同じ周期T1を有する内部垂直同期信号IVsyncを生成する。また、制御回路230は、内部垂直同期信号IVsyncと第2カウント値とを用いて、水平同期信号の周期T2と同じ周期T2を有する内部水平同期信号IHsyncを生成する(ステップS60)。

【0066】

図5に示したように、垂直同期信号Vsyncの最後のパルスLPと内部垂直同期信号IVsyncの最初のパルスFPとの時間間隔T1は、垂直同期信号Vsyncの周期T1と同一である。即ち、ビデオモードから命令モードに転換時、ディスプレイドライバーIC200Aは、垂直同期信号Vsyncに連続する内部垂直同期信号IVsyncを発生するので、ディスプレイ300で発生する映像フリッカー現象を防止することができる。

【0067】

命令デコーダ220は、第2選択信号SEL2の発生時点を調節することによって、垂直同期信号Vsyncの最後のパルスLPと内部垂直同期信号IVsyncの最初のパルスFPとの時間間隔T1が垂直同期信号Vsyncの周期T1と同一になるように、第2選択回路240を制御する。

【0068】

第1〜第3選択回路219、240、及び250は、各選択信号SEL1及びSEL2によって、復元データDATAと各内部同期信号IVsync、IHsyncとをディスプレイ300に伝送する(ステップS70)。従って、第2区間INT3から、ディスプレイドライバーIC200Aは、命令モードを行う。この際、第2区間INT3から、ホスト100は、ホスト100で消耗する電力を減らすために、垂直同期パケットVSと水平同期パケットHSとをディスプレイドライバーIC200Aに伝送せず、データストリームパケットDSのみを伝送する。従って、ディスプレイドライバーIC200Aは、垂直同期信号Vsyncと水平同期信号Hsyncを生成しない。ディスプレイドライバーIC200Aは、復元データDATAを、フレームメモリ215を通じてディスプレイ300に伝送する。

【0069】

図6は、図3に示した制御回路の一例を示すブロック図である。図3、図5、及び図6を参照すると、制御回路230は、垂直同期信号周期カウンター231−1、内部垂直同期信号生成器231−2、水平同期信号周期カウンター232−1、内部水平同期信号生成器232−2、オシレーター233、誤差計算器234、TE制御信号生成器235、制御値レジスタ236、及び誤差情報レジスタ237を含む。

【0070】

垂直同期信号周期カウンター231−1は、クロック信号CLK1を用いて垂直同期信号Vsyncの周期T1をカウントし、第1カウント値CNT1を生成する。内部垂直同期信号生成器231−2は、第1カウント値CNT1とオシレーター233から出力されたオシレーション信号OSCを用いて、垂直同期信号Vsyncの周期T1と同じ周期T1を有する内部垂直同期信号IVsyncを生成する。

【0071】

水平同期信号周期カウンター232−1は、クロック信号CLK1を用いて水平同期信号Hsyncの周期T2をカウントし、第2カウント値CNT2を生成する。内部水平同期信号生成器232−2は、第2カウント値CNT2とオシレーター233から出力されたオシレーション信号OSCを用いて、水平同期信号Hsyncの周期T2と同じ周期T2を有する内部水平同期信号IHsyncを生成する。

【0072】

内部垂直及び水平同期信号生成器231−2、232−2は、イネーブル信号ENに応答して、各内部同期信号IVsync、IHsyncの生成タイミング又は出力タイミングを制御する。

【0073】

一実施形態として、垂直及び水平同期信号周期カウンター231−1、232−1は、各同期信号Vsync、Hsyncの最後のパルスを検出し、該検出結果によって、内部垂直及び水平同期信号生成器231−2、232−2の動作を制御する各制御信号を出力する。この場合、垂直及び水平同期信号周期カウンター231−1、232−1は、最後のパルス検出器の機能を行う。

【0074】

誤差計算器234は、垂直同期信号Vsyncの周期T1と内部垂直同期信号IVsyncの周期との差を計算して第1誤差値を生成し、水平同期信号Hsyncの周期T2と内部水平同期信号IHsyncの周期との差を計算して第2誤差値を生成し、第1誤差値と第2誤差値のそれぞれを誤差情報レジスタ237に保存する。例えば、誤差計算器234は、クロック信号に基づいて、第1誤差値と第2誤差値のそれぞれを計算する。

【0075】

誤差情報レジスタ237に保存された第1誤差値と第2誤差値のそれぞれは、ホスト100によってアクセス可能である。理論的には、垂直同期信号Vsyncの周期と同じ周期を有する内部垂直同期信号IVsyncを生成することができるが、実際の具現例では、垂直同期信号Vsyncの周期と内部垂直同期信号IVsyncの周期との間には誤差が発生することがある。

【0076】

同様に、水平同期信号Hsyncの周期と同じ周期を有する内部水平同期信号IHsyncを生成することができるが、実際の具現例では、水平同期信号Vsyncの周期と内部垂直同期信号IVsyncの周期との間には誤差が発生することがある。

【0077】

TE制御信号生成器235は、誤差計算器234から提供された第1誤差値によって、TE制御信号TEの生成タイミングを制御する。

【0078】

制御値レジスタ236は、ホスト100から出力された制御値TEVを保存する。この際、誤差計算器234は、制御値TEVを受信して解析し、該解析結果によって、TE制御信号生成器235の動作を制御する。従って、TE制御信号生成器235は、制御値TEVを用いてTE制御信号TEの発生タイミングを制御することができる。

【0079】

図7は、本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するフローチャートであり、図8は、本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するタイミング図である。

【0080】

ディスプレイドライバーIC200Aが、TE制御信号TEの発生時点を制御する方法とディスプレイドライバーIC200Aの動作モードが、モード転換命令(図2の103参照)によって、ビデオモードから命令モードに転換される手順を、図2、図3、図6、図7、及び図8を参照して説明すると、次の通りである。

【0081】

モード転換時点で、各内部同期信号IVsync、IHsyncから各同期信号Vsync、Hsyncへのハンドオーバーが正確に行われると、ディスプレイ300で映像フリッカーが発生しない。もし、第2TE制御信号TE2がホスト100に伝送されると、ホスト100は、第2TE制御信号TE2によって、垂直同期信号Vsyncに関連する垂直同期パケットVSを生成する。従って、垂直同期信号VsyncのパルスP2は、第1時点T1ではなく第2時点T2で生成される。即ち、垂直同期信号Vsyncが遅延時間TDほど遅延されて発生すると、ディスプレイ300で映像フリッカーが発生する。従って、第2TE制御信号TE2の生成タイミングを調節する必要がある。

【0082】

誤差計算器234は、垂直同期信号Vsyncの周期と内部垂直同期信号IVsyncの周期との差である第1誤差値を計算し、これを誤差情報レジスタ237に保存する(ステップS110)。誤差計算器234は、誤差情報レジスタ237に保存された第1誤差値によって、TE制御信号TEの生成タイミングを制御する制御信号をTE制御信号生成器235に伝送する(ステップS120)。

【0083】

TE制御信号生成器235は、制御信号によって生成された第1TE制御信号TE1をホスト100に伝送する(ステップS130)。ホスト100は、第1TE制御信号TE1によって、第1時点T1で生成された垂直同期信号VsyncのパルスP1に関連する垂直同期パケットVSを生成する。

【0084】

第1時点T1を基準に、内部垂直同期信号IVsyncから垂直同期信号Vsyncへのハンドオーバーが正確に行われるので、ディスプレイ300では、映像フリッカーが発生しない。即ち、垂直同期信号Vsyncの最初のパルスP1が、第2時点T2ではない第1時点T1で生成される。

【0085】

図9は、図1に示したホストの一例を示す内部ブロック図であり、図10は、図9に示したホストの同期パケット発生タイミングを制御する方法を説明するフローチャートである。図1、図9、及び図10を参照すると、一実施形態として、ホスト100は、制御ロジック110と同期パケット生成器120とを含む。他の実施形態として、ホスト100は、制御ロジック110と制御値調節ロジック130とを含み得る。更に他の実施形態として、ホスト100は、制御ロジック110、同期パケット生成器120、及び制御値調節ロジック130を含み得る。

【0086】

ディスプレイドライバーIC200Aの動作モードが、モード転換命令(図2の103参照)によって命令モードからビデオモードに転換される手順を、図1、図2、図8、図9、及び図10を参照して説明すると、次の通りである。

【0087】

上述したように、モード転換時点で各内部同期信号IVsync、IHsyncから各同期信号Vsync、Hsyncへのハンドオーバーが正確に行われると、ディスプレイ300では、映像フリッカーが発生しない。

【0088】

モード転換命令(図2の103参照)を含むパケットPACがディスプレイドライバーIC200Aに伝送された後、制御ロジック110は、ディスプレイドライバーIC200Aから出力されたTE制御信号TEと誤差情報EIとを受信し(ステップS210)、TE制御信号TEと誤差情報EIとを用いて、同期パケットの生成タイミングを調節するための制御信号を同期パケット生成器120に出力する。

【0089】

TE制御信号TEの立ち上りエッジによって、垂直同期信号Vsyncの最初のパルスFPの立ち上りエッジのタイミングが決定されるので、制御ロジック110は、TE制御信号TEと誤差情報EIとを用いて、第1時点T1で垂直同期信号Vsyncの最初のパルスP1の立ち上りエッジが生成されるように制御信号を同期パケット生成器120に出力する。従って、同期パケット生成器120は、制御信号に応答して、第1時点T1で垂直同期信号Vsyncの最初のパルスP1の立ち上りエッジが生成されるように垂直同期パケットVSを生成し、該生成された垂直同期パケットVSをディスプレイドライバーIC200Aに伝送する。

【0090】

即ち、同期パケット生成器120は、制御信号によって、各同期パケットVS、HSの生成タイミング又は出力タイミングを調節する(ステップS220)。これにより、同期パケット生成器120は、生成された各同期パケットVS、HSを含むパケットPACをディスプレイドライバーIC200Aに伝送する(ステップS230)。

【0091】

図11は、図9に示したホストのティアリング効果制御信号の発生タイミングを調節するための制御値を生成する方法を説明するフローチャートである。ディスプレイドライバーIC200Aの動作モードが、モード転換命令(図2の103参照)によって命令モードからビデオモードに転換される手順を、図1、図2、図8、図9、及び図11を参照して説明すると、次の通りである。

【0092】

モード転換時点で、各内部同期信号IVsync、IHsyncから各同期信号Vsync、Hsyncへのハンドオーバーが正確に行われると、ディスプレイ300では、映像フリッカーが発生しない。モード転換命令(図2の103参照)を含むパケットPACがディスプレイドライバーIC200Aに伝送された後、制御ロジック110は、ディスプレイドライバーIC200Aから出力された誤差情報EIを受信し(ステップS310)、誤差情報EIを制御値調節ロジック130に出力する。

【0093】

制御値調節ロジック130は、誤差情報EIに基づいて、TE制御信号の発生タイミングを制御するための制御値TEVを生成し(ステップS320)、該生成された制御値TEVをディスプレイドライバーIC200Aの制御値レジスタ236に伝送する(ステップS330)。従って、TE制御信号生成器235は、制御値レジスタ236に保存された制御値TEVによって、TE制御信号TEを生成することができる。

【0094】

図12は、本発明の他の実施形態による映像信号処理システムのブロック図である。映像信号処理システム10Bは、ホスト100、ディスプレイドライバーIC200B、及びディスプレイ300を含む。

【0095】

ホスト100は、データDATAと命令CMD、垂直同期信号Vsync、水平同期信号Hsync、及び制御値TEVをディスプレイドライバーIC200Bに伝送する。ディスプレイドライバーIC200Bは、TE制御信号TE及び/又は誤差情報EIをホスト100に伝送する。

【0096】

ディスプレイドライバーIC200Bは、動作モード、例えばビデオモードによって、データDATA、垂直同期信号Vsync、及び水平同期信号Hsyncをディスプレイ300に伝送する。また、ディスプレイドライバーIC200Bは、動作モード、例えば命令モードによって、データDATA、内部垂直同期信号IVsync、及び内部水平同期信号IHsyncをディスプレイ300に伝送する。

【0097】

図13は、図12に示したディスプレイドライバーの一例を示すブロック図である。

【0098】

図3と図13とを参照すると、データ/同期デコーダ210を除くと、図13に示したディスプレイドライバーIC200Bの構造と動作は、図3に示したディスプレイドライバーIC200Aの構造と動作と実質的に同一である。

【0099】

図14は、図12に示したディスプレイドライバーの動作を説明するフローチャートである。図2、図6、図12、図13、及び図14を参照すると、制御回路230は、各同期信号Vsync、Hsyncの周期をカウントし、各カウント値CNT1、CNT2を生成する(ステップS410)。

【0100】

命令デコーダ220は、モード転換命令、例えばディスプレイドライバーIC200Bの動作モードをビデオモードから命令モードに変換するためのモード転換命令を含む命令パケット101を受信する(ステップS420)。

【0101】

上述したように、制御回路230は、各カウント値CNT1、CNT2を用いて、各同期信号Vsync、Hsyncの周期と同じ周期を有する各内部同期信号IVsync、IHsyncを生成する(ステップS430)。命令モードで作動するディスプレイドライバーIC200Bは、データDATAと各内部同期信号IVsync、IHsyncとをディスプレイドライバー300に伝送する(ステップS440)。ビデオモードで作動するディスプレイドライバーIC200Bは、データDATAと各同期信号Vsync、Hsyncとをディスプレイドライバー300に伝送する。

【0102】

一実施形態として、制御値TEVと誤差情報EIは、ホスト100又はディスプレイドライバーIC200A、200Bに具現された不揮発性メモリに保存される。従って、ホスト100又はディスプレイドライバーIC200A、200Bの初期化動作時に、不揮発性メモリに保存された各情報TEV、EIは、制御値及び誤差情報レジスタ236、237にロードされる。他の実施形態として、制御値TEVと誤差情報EIは、リアルタイムで毎フレーム毎にアップデートされ得る。

【0103】

本発明によるディスプレイドライバーは、動作途中で、モード転換命令によってビデオモードと命令モードとの間でモード転換を行うことができる。従って、ディスプレイドライバーで消耗する電力を効果的に減らすことができる効果がある。

【0104】

図15は、本発明の更に他の実施形態による映像信号処理システムのブロック図である。図15を参照すると、映像信号処理システム10Cは、静止映像信号又は動画信号をディスプレイ3000で表示することができる携帯電話、スマートフォン、タブレットPC、PDA、又はPMPのような移動型の装置、小型機器又は小型コンピュータを意味する。

【0105】

映像信号処理システム10Cは、アプリケーションホストプロセッサ1000、ディスプレイドライバーIC2000、及びディスプレイ3000を含む。

【0106】

ホスト1000は、ホスト1000内に具現されたコーデックの実行によって、ディスプレイ3000で表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を含む映像信号DATAをディスプレイドライバーIC2000に伝送する。モード転換命令は、ディスプレイドライバーIC2000の動作モードを制御する制御信号である。

【0107】

モード転換命令を含む映像信号DATAは、クロック信号CLKに応答して、ディスプレイドライバーIC2000に伝送される。

【0108】

ホスト1000は、ディスプレイドライバーIC2000から出力されたTE制御信号TEを受信し、該受信したTE制御信号TEのレベルによって、映像信号DATAの伝送タイミングを制御する。ここで、TE制御信号TEは、ティアリング又はスクリーンティアリングを防止するための制御信号である。

【0109】

ディスプレイドライバーIC2000は、ホスト1000から出力されたモード転換命令によって、ディスプレイドライバーIC2000内に具現された静止映像信号を処理するインターフェースと動画信号を処理するインターフェースとのうちの何れか1つを選択し、ホスト1000から出力された映像信号DATA、例えば静止映像信号又は動画信号を、選択されたインターフェースを通じて出力映像信号DDATAとしてディスプレイ3000に伝送する。

【0110】

ディスプレイ3000は、ディスプレイドライバーIC2000から出力された出力映像信号DDATAを表示する。例えば、ディスプレイ3000は、LCD、LEDディスプレイ、OLEDディスプレイ、又はAMOLEDディスプレイとして具現可能である。

【0111】

図16は、図15に示したアプリケーションホストプロセッサの一例を示す概略的なブロック図である。図16に示した点線は、命令(instruction)実行経路を表わす。図16を参照すると、ホスト1000は、RF受信器1110、DRAM(Dynamic Random Access Memory)1114のような揮発性メモリ、NANDフラッシュメモリ1116のような不揮発性メモリ、フレームバッファ1118、コーデック1120、ディスプレイコントローラ1122、レジスタ1124を含むインターフェース1126、及びCPUコア1128を含む。

【0112】

ホスト1000の動作を全般的に制御するCPUコア1128は、DRAM1114、NANDフラッシュメモリ1116、フレームバッファ1118、コーデック1120、ディスプレイコントローラ1122、レジスタ1124、及びインターフェース1126の各構成要素の動作を制御し、実行コードCODEを実行する。

【0113】

ユーザが動画信号MIをディスプレイ3000から再生しようとする際、例えば、実行コードCODEによってコーデック1120が実行されると、CPUコア1128は、コーデック1120の実行を感知し、該感知結果によって、モード転換命令MCC[1:0]を生成し、該生成されたモード転換命令MCC[1:0]をレジスタ1124に伝送する。

【0114】

例えば、動画信号MIの再生に関連するイベントが発生すると、実行コードCODEのメイン関数内で、イベントに関連するイベント処理関数が呼び出され、イベント処理関数がコーデック1120を呼び出すと、CPUコア1128は、実行コードCODEの実行及び/又は呼び出しによって、ディスプレイ3000で表示される映像信号が動画信号MIであることを判断する。

【0115】

例えば、モード転換命令MCC[1:0]が2ビットである場合、ディスプレイドライバーIC2000の動作モードは、表2のようである。即ち、ディスプレイドライバーIC2000は、モード転換命令MCC[1:0]によって、静止映像信号を処理する命令モードと動画信号を処理するビデオモードとの間でスイッチング動作を行う。ここで、ブリッジモード(bridge mode)は、ディスプレイドライバーIC2000の動作モードが命令モードからビデオモードにスイッチングされる際に、内部スキャン動作によってフレームメモリ(GRAM)2204−3(図19参照)のダミー映像信号がディスプレイ3000に出力されることを防止するためのモードである。

【0116】

【表2】

【0117】

各モードによるディスプレイドライバーIC2000の動作は、後に関連図面を参照して詳しく説明する。

【0118】

また、ユーザが静止映像信号SIをディスプレイ3000で再生しようとする際、例えば実行コードCODEによってコーデック1120の実行が終了すると、又はコーデック1120が実行されない場合、CPUコア1128は、コーデック1120の実行の終了又はコーデック1120が実行されないことを感知し、該感知結果によって、モード転換命令MCC[1:0]を生成し、該生成されたモード転換命令MCC[1:0]をレジスタ1124に伝送する。

【0119】

例えば、静止映像信号SIをディスプレイ3000で表示するために、実行中であるコーデック1120が終了イベントによって終了し、コーデック1120を実行するために、呼び出されたイベント処理関数がメイン関数でリターンされると、CPUコア1128は、リターンを検出し、ディスプレイ3000で表示される映像信号が静止映像信号SIであることを判断する。

【0120】

実行コードの例は、次の通りである。

【0121】

【0122】

RF受信器1110は、インターネット又はDMB(Digital Multimedia Broadcasting)を通じて映像信号、例えば静止映像信号SI又は動画信号MIを受信し、該受信した映像信号をDRAM1114及び/又はNANDフラッシュメモリ1116に保存する。

【0123】

ホスト1000がブーティングされると、NANDフラッシュメモリ1116に保存された実行コードCODEはDRAM1114にロードされ、DRAM1114にロードされた実行コードCODEは順次に実行される。一実施形態として、NANDフラッシュメモリ1116に保存された実行コードCODEは、CPUコア1128の制御によって、リアルタイムでDRAM1114にロードされる。

【0124】

NANDフラッシュメモリ1116は、静止映像信号、動画信号、ゲームプログラム、開始プログラム、例えば実行コード及び/又はアプリケーションを保存する。例えば、NANDフラッシュメモリ1116に保存された静止映像信号、動画信号、ゲームプログラム、開始プログラム、例えば実行コード及び/又はアプリケーションは、CPUコア1128の制御によって、DRAM1114にロードされる。

【0125】

フレームバッファ1118は、DRAM1114から出力された静止映像信号SI又はコーデック120から出力された動画信号MIを受信して保存する。例えば、静止映像信号SIをディスプレイ3000で表示しようとする際に、DRAM1114に保存された静止映像信号SIは、直ちにフレームバッファ1118に伝送される。しかし、動画信号MIをディスプレイ3000で表示しようとする際に、DRAM1114に保存された動画信号MIは、コーデック1120によって処理された後、フレームバッファ1118に伝送される。

【0126】

コーデック1120は、データストリーム又は信号をエンコーディング及び/又はデコーディングするハードウェア又はコンピュータプログラムである。例えば、コーデック1120は、DRAM1114から出力された動画信号MIをデコーディングし、該デコードされた動画信号をフレームバッファ1118に伝送する。

【0127】

ディスプレイコントローラ1122は、フレームバッファ1118から出力された静止映像信号SI又は動画信号MIをインターフェース1126に伝送することを制御する。

【0128】

インターフェース1126は、クロック信号CLK、及び映像信号DATA、例えば静止映像信号又は動画信号をディスプレイドライバーIC2000に伝送する。

【0129】

ディスプレイコントローラ1122の制御によって、インターフェース1126は、静止映像信号を命令モードに適した静止映像信号に変換して出力し、動画信号をビデオモードに適した動画信号に変換して出力する。

【0130】

一実施形態として、インターフェース1126は、レジスタ1124に保存されたモード転換命令MCC[1:0]を参照して、静止映像信号を命令モードに適した静止映像信号に変換して出力し、動画信号をビデオモードに適した動画信号に変換して出力する。ここで、命令モードは、静止映像信号を処理するためのモードであり、ビデオモードは、動画信号を処理するためのモードである。

【0131】

インターフェース1126は、ディスプレイドライバーIC2000から伝送されたTE制御信号TEをCPUコア1128に伝送する。

【0132】

TE制御信号TEに応答して、CPUコア1128は、後述する図22、図24、図27、又は図30に示すように、モード転換命令MCC[1:0]の発生タイミング及び/又は映像信号DATAの伝送タイミングを制御するために、インターフェース1126の動作を制御する。

【0133】

図17は、図16に示したアプリケーションホストプロセッサの動作を説明するフローチャートであり、図18は、図16に示したアプリケーションホストプロセッサから出力されるモード転換命令を含む映像信号及びクロック信号の波形図である。

【0134】

ホスト1000の動作は、図15〜図18を参照して詳しく説明する。

【0135】

第1に、動画信号がディスプレイ3000で再生された後に終了する場合、即ち場合1CASE1を説明すると、動画信号MIをディスプレイ3000で再生するために、コーデック1120が実行されると(ステップS1011)、CPUコア1128は、コーデック1120の実行を感知し、該感知結果によって、ビデオモードに進入する(ステップS1012)。

【0136】

ホスト1000の動作モードがビデオモードに進入することを感知したCPUコア1128は、ディスプレイドライバーIC2000がビデオモードを行うように、モード転換命令MCC[1:0]=10を生成し、該生成されたモード転換命令MCC[1:0]=10をレジスタ1124に伝送する(ステップS1014)。ディスプレイコントローラ1122は、フレームバッファ1118から出力された動画信号MIをインターフェース1126に伝送する。この際、インターフェース1126は、レジスタ1124に保存されたモード転換命令MCC[1:0]=10を参照して、ビデオモードに適した動画信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1016)。

【0137】

図18に示したように、モード転換命令MCC[1:0]=10は、垂直同期信号Vsyncに含まれて映像信号DATAと共にディスプレイドライバーIC2000に伝送される。ディスプレイドライバーIC2000は、垂直同期信号Vsyncと動画信号MIとを各信号Vsync、MIのレベルとパケットの種類によって区別する。例えば、モード転換命令MCC[1:0]は、パケット形態で垂直同期信号Vsyncに含まれる。

【0138】

垂直同期信号Vsyncと動画信号MIとを含む映像信号DATAは、クロック信号CLKによってホスト1000からディスプレイドライバーIC2000に伝送される。

【0139】

従って、ディスプレイドライバーIC2000は、モード転換命令MCC[1:0]=10によって、メモリを有していないビデオモードを行う。メモリを有していないビデオモードについては、後に図19及び図20を参照して詳しく説明する。

【0140】

コーデック1120の実行が終了すると(ステップS1018)、ディスプレイ3000では、動画信号MIの再生を終了する(ステップS1028)。コーデック1120の実行が終了するまで(ステップS1018)、ホスト1000は、ビデオモードによる新たな動画信号をディスプレイドライバーIC2000に伝送する(ステップS1016)。

【0141】

第2に、静止映像信号SIがディスプレイ3000で再生された後に終了する場合、即ち場合2CASE2を説明すると、コーデック1120が実行されない場合(ステップS1011)、CPUコア1128は、コーデック1120が実行されないことを感知し、該感知結果によって、命令モードに進入する(ステップS1020)。ホスト1000の動作モードが命令モードに進入することを感知したCPUコア1128は、ディスプレイドライバーIC2000が命令モードを行うように、モード転換命令MCC[1:0]=00を生成し、該生成されたモード転換命令MCC[1:0]=00をレジスタ1124に伝送する(ステップS1022)。

【0142】

ディスプレイコントローラ1122は、フレームバッファ1118から出力された静止映像信号SIをインターフェース1126に伝送する。インターフェース1126は、レジスタ1124に保存されたモード転換命令MCC[1:0]=00を参照して、命令モードによる静止映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1024)。

【0143】

図18に示したように、モード転換命令MCC[1:0]=00は、垂直同期信号Vsyncにパケット形態で含まれてディスプレイドライバーIC2000に伝送される。この際、映像信号DATAは、垂直同期信号Vsyncと静止映像信号とを含む。命令モードで、ホスト1000は、フレームバッファ1118に新たな静止映像信号がアップデートされる度に、命令モードによる新たな静止映像信号をディスプレイドライバーIC2000に伝送する(ステップS1024)。コーデック1120が実行されずに静止映像信号の再生が終了すると(ステップS1026)、ディスプレイ3000では、静止映像信号の再生を終了する(ステップS1028)。

【0144】

第3に、動画信号MIがディスプレイ3000で再生された後に直ちに静止映像信号SIが再生される場合、即ち場合3CASE3を説明すると、動画信号MIがディスプレイ3000で表示される途中でコーデック1120の実行が終了すると(ステップS1018)、ホスト1000のCPUコア1128は、コーデック1120の実行が終了することを感知し、該感知結果によって、命令モードに進入する(ステップS1020)。

【0145】

ビデオモードから命令モードへのスイッチングは、後に図22、図24、図27、及び図30を参照して詳しく説明する。

【0146】

第4に、静止映像信号SIがディスプレイ3000で再生された後に直ちに動画信号MIが再生される場合、即ち場合4CASE4を説明すると、静止映像信号がディスプレイ3000で表示される途中でコーデック1120が実行されると(ステップS1026)、CPUコア1128は、コーデック1120の実行を感知し、該感知結果によって、ビデオモードに進入する(ステップS1012)。

【0147】

命令モードからビデオモードへのスイッチングは、後に図22、図24、図27、及び図30を参照して詳しく説明する。

【0148】

図19は、図15に示したディスプレイドライバーの一例を示す概略的なブロック図である。図19に示したディスプレイドライバーIC2000は、ホスト1000から出力された映像信号DATAに含まれるモード転換命令MCC[1:0]によって、表2に示した4つの動作モードのうちの何れか1つを行う。

【0149】

モード転換命令MCC[1:0]が‘00’である場合、行われる命令モードは、第1インターフェース2204に含まれる第1スイッチング回路2204−1、第2選択回路2204−2、フレームメモリ(GRAM)2204−3、及びスキャンスイッチング回路2204−4の各構成要素を用いて、静止映像信号SIをディスプレイ3000に伝送する動作モードである。この命令モードで、静止映像信号SIは、後述する図20、図21、又は図28に示した第1経路PATH1を通じてディスプレイ3000に伝送される。

【0150】

モード転換命令MCC[1:0]が‘01’である場合、行われるメモリを有するビデオモードは、第2インターフェース2206の第2スイッチング回路2206−1と第1インターフェース2204に含まれる各構成要素2204−2、2204−3、2204−4を用いて、動画信号をディスプレイ3000に伝送する動作モードである。

【0151】

メモリを有するビデオモードで、動画信号は、後述する図28に示した第4経路PATH4を通じてディスプレイ3000に伝送される。

【0152】

第1経路PATH1と第4経路PATH4には、フレームメモリ(GRAM)2204−3が含まれる。

【0153】

モード転換命令MCC[1:0]が‘10’である場合、行われるメモリを有していないビデオモードは、第2インターフェース2206の第2スイッチング回路2206−1を通じて、即ちフレームメモリ(GRAM)2204−3をバイパスして、動画信号をディスプレイ3000に伝送する動作モードである。

【0154】

メモリを有していないビデオモードで、動画信号は、後述する図20又は図25に示した第2経路PATH2を通じてディスプレイ3000に伝送される。

【0155】

モード転換命令MCC[1:0]が‘11’である場合、行われるブリッジモードは、一定時間の間に、第2インターフェース2206の第2スイッチング回路2206−1を通じて動画信号をディスプレイ3000に伝送すると同時に、動画信号を、各構成要素2206−1、2204−2を通じてフレームメモリ(GRAM)2204−3に書き込む動作モードである。

【0156】

図19を参照すると、ディスプレイドライバーIC2000は、受信器2202、第1インターフェース2204、第2インターフェース2206、制御回路2208、第1選択回路2210、出力回路2212、及びタイミングコントローラ2220を含む。ディスプレイドライバーIC2000は、オシレーター2218と電力回路2222とを更に含む。

【0157】

受信器2202は、ディスプレイ3000で表示される映像信号DATAが、静止映像信号SI又は動画信号MIであるか否かを指示するモード転換命令MCC[1:0]を含む映像信号DATAを受信する。この際、映像信号DATAは、クロック信号CLKに同期して伝送される。受信器2202は、映像信号DATAに含まれるモード転換命令MCC[1:0]を制御回路2208に伝送する。

【0158】

受信器2202は、直列に入力された命令モードによる映像信号DATA、即ち静止映像信号のフォーマットを第1インターフェース2204が処理することができる信号のフォーマットに変換し、該変換された静止映像信号SIを第1インターフェース2204に出力する。また、受信器2202は、直列に入力されたビデオモードによる映像信号DATA、即ち動画信号のフォーマットを第2インターフェース2206が処理することができる信号のフォーマットに変換し、該変換された動画信号MIを第2インターフェース2206に出力する。

【0159】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]に応答して、第1制御信号CTRL1と第2制御信号CTRL2とを生成し、第1制御信号CTRL1を第1インターフェース2204に伝送し、第2制御信号CTRL2を第2インターフェース2206に伝送する。制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]に応答して、第1インターフェース2204を制御する第1インターフェース制御信号CRTL1、MMC[0]、及びSWC_OFFを生成する。

【0160】

例えば、第1インターフェース2204は、静止映像信号を処理するために、メモリを使うMIPI命令モードをサポートするインターフェース、CPUインターフェース又はMCUインターフェースである。第2インターフェース2206は、メモリを使わずに動画信号を処理するMIPIビデオモードをサポートするインターフェース又はRGBインターフェースである。

【0161】

第1制御信号CTRL1に応答して、第1インターフェース2204は、受信器2202から出力された静止映像信号SIを、フレームメモリ(GRAM)2204−3を用いて出力する。

【0162】

第1インターフェース2204は、第1スイッチング回路2204−1、第2選択回路2204−2、フレームメモリ(GRAM)2204−3、及びスキャンスイッチング回路2204−4を含む。第1スイッチング回路2204−1は、第1制御信号CTRL1に応答して、静止映像信号SIを第2選択回路2204−2に伝送する。第1スイッチング回路2204−1は、静止映像信号SIが伝送されるバスを制御するロジック回路としての機能を行う。

【0163】

第2選択信号MMC[0]に応答して、第2選択回路2204−2は、第1スイッチング回路2204−1から出力された静止映像信号SIと第2インターフェース2206の第2スイッチング回路2206−1から出力された動画信号MIとのうちの1つをフレームメモリ(GRAM)2204−3に選択的に伝送する。例えば、第2選択信号MMC[0]が0である場合、第2選択回路2204−2は、第1スイッチング回路2204−1から出力された静止映像信号SIをフレームメモリ(GRAM)2204−3に伝送し、第2選択信号MMC[0]が1である場合、第2選択回路2204−2は、第2スイッチング回路2206−1から出力された動画信号MIをフレームメモリ(GRAM)2204−3に伝送する。

【0164】

グラフィックメモリとして具現可能なフレームメモリ(GRAM)2240−3は、第2選択回路2204−2から出力された映像信号を受信して保存する。フレームメモリ(GRAM)2240−3に対するアクセス動作、例えばライト動作とリード動作は、タイミングコントローラ2220によって制御される。

【0165】

モードに応じて、フレームメモリ(GRAM)2240−3に保存された静止映像信号又は動画信号は、スキャンスイッチング回路2204−4を通じて第1選択回路2210と出力回路2212とを通じてディスプレイ3000に伝送される。即ち、スキャンスイッチング回路2204−4は、制御回路2208から出力されたスキャンスイッチング信号SWC_OFFによって、フレームメモリ(GRAM)2240−3に保存された静止映像信号又は動画信号を第1選択回路2210に伝送する。

【0166】

第2インターフェース2206の第2スイッチング回路2206−1は、受信器2202から出力された動画信号MIを、第2制御信号CTRL2によって、第1選択回路2210と第1インターフェース2204の第2選択回路2204−2とのうちの少なくとも1つに出力する。

【0167】

第2スイッチング回路2206−1は、動画信号が伝送されるバスを制御するロジック回路としての機能を行う。

【0168】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]に応答して、第1選択信号MMC[1]、スキャンスイッチング信号SWC、及び第2選択信号MMC[0]を更に生成する。

【0169】

第1選択回路2210は、第1選択信号MMC[1]に応答して、第1インターフェース2204の出力ポート、即ちフレームメモリ(GRAM)2204−3とスキャンスイッチング回路2204−4から出力される静止映像信号と第2インターフェース2206の出力ポートから出力される動画信号とを選択的に出力回路2212に出力する。一実施形態として、各選択回路2204−2、2210は、マルチプレクサとして具現可能である。

【0170】

例えば、第1選択信号MMC[1]が0である場合、第1選択回路2210は、第1インターフェース2204から出力された映像信号を出力回路2212に伝送し、第1選択信号MMC[1]が1である場合、第1選択回路2210は、第2インターフェース2206から出力された動画信号を出力回路2212に伝送する。

【0171】

出力回路2212は、第1選択回路2210から出力された映像信号、例えば静止映像信号又は動画信号を処理し、該処理された映像信号DDATAをディスプレイ3000に伝送する。例えば、出力回路2212は、輝度調節回路2214とドライバーブロック2216とを含む。

【0172】

輝度調節回路2214は、アルゴリズムによって、ディスプレイ3000で表示される映像信号によってバックライトユニット(back light unit)の輝度(brightness)とガンマ曲線とを調節して映像信号の歪曲を除去する。輝度調節回路2214の動作は、制御回路2208から出力された制御信号によって制御される。

【0173】

ドライバーブロック2216は、輝度調節回路2214から出力された映像信号をディスプレイ3000に出力する。

【0174】

ドライバーブロック2216は、多数のソースドライバー(図示せず)を含み、多数のソースドライバーのそれぞれは、ディスプレイ3000の多数のデータライン(又は、ソースライン)のそれぞれに映像信号によるグレースケール電圧を供給する。一実施形態として、ドライバーブロック2216は、少なくとも1つのゲートドライバー(又は、スキャンドライバー:図示せず)を含む。ドライバーブロック2216は、タイミングコントローラ2220から出力された制御信号によって制御される。

【0175】

タイミングコントローラ2220は、制御回路2208から出力された制御信号によって、ドライバーブロック2216の動作を制御する。また、タイミングコントローラ2220は、制御回路2208から出力された制御信号によって、ティアリング又はスクリーンティアリングを防止するためにTE制御信号TEを生成し、該生成されたTE制御信号TEをホスト1000に伝送する。

【0176】

ホスト1000のCPUコア1128は、TE制御信号TEをモニターし、該モニター結果によって、ティアリング又はスクリーンティアリングを防止するために、後述する図24、図27、又は図30に示したように静止映像信号の伝送タイミング又は動画信号の伝送タイミングを制御する。

【0177】

また、タイミングコントローラ2220は、クロック信号CLK又はオシレーション信号OSCに応答して、パワー基準クロック信号BCLKを生成する。電力回路2222は、パワー基準クロック信号BCLKによって、ディスプレイドライバーIC2000のパワーを昇圧し、該昇圧されたパワーPWRを出力する。タイミングコントローラ2220は、動画信号の伝送に関連する内部垂直同期信号IVsyncを生成する。後述する図24、図27、又は図30に示したように、内部垂直同期信号IVsyncのパルス幅は、TE制御信号TEのパルス幅より小さい。

【0178】

オシレーター2218は、制御回路2208の制御によってオシレーション信号OSCを生成し、オシレーション信号OSCをタイミングコントローラ2220に伝送する。

【0179】

図20は、図19に示したディスプレイドライバーの動作モードによる映像信号経路の一例を示す図であり、図21は、図19に示したディスプレイドライバーの動作モードによるデータの流れの一例を示す図であり、図22は、図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の一例を示すタイミング図である。

【0180】

図19〜図22を参照すると、ディスプレイドライバーIC2000は、MIPI(Mobile Industry Processor Interface)標準によって映像信号DATAを処理する。

【0181】

従って、例示的に示した受信器2202は、MIPI標準によるMIPI D−PHY2202−1、CIL&DSI(control and interfacelogic:CIL)&display serial interface:DSI)2202−2、及びラッパ(wrapper)2202−3を含む。

【0182】

MIPI D−PHY2202−1とCIL&DSI2202−2は、ホスト1000から出力された映像信号DATAをラッパ2202−3に伝送し、ラッパ2202−3は、命令モードによる静止映像信号SIを第1インターフェース2204に適した信号に変換するか、又はビデオモードによる動画信号MIを第2インターフェース2206に適した信号に変換する。

【0183】

図19〜図22を参照して、静止映像信号、動画信号、及び静止映像信号が順次にディスプレイ3000で表示される手順を説明すると、次の通りである。

【0184】

ホスト1000がディスプレイドライバーIC2000に静止映像信号SIを伝送しようとする際(ステップS1101)、CPUコア1128は、コーデック1120が実行されないことを感知し、該感知結果によって、モード転換命令MCC[1:0]=00をディスプレイドライバーIC2000に伝送する(ステップS1102)。受信器2202は、モード転換命令MCC[1:0]=00を制御回路2208に伝送する。

【0185】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=00に応答して、第1インターフェース2204の第1スイッチング回路2204−1をイネーブルするための第1制御信号CTRL1、第2インターフェース2206の第2スイッチング回路2206−1をディセーブルするための第2制御信号CTRL2、第1スイッチング回路2204−1の出力信号を第2選択回路2204−2に伝送するための第2選択信号MMC[0]=0、フレームメモリ(GRAM)2204−3の出力信号を第1選択回路2210に伝送するためのスキャンスイッチング信号SWC_OFF、及び第1インターフェース2204の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=0を発生する(ステップS1103)。即ち、第1インターフェース2204が選択されることによって、第1経路PATH1が形成される。

【0186】

ホスト1000は、モード転換命令MCC[1:0]=00を出力した後、静止映像信号SIを出力する(ステップS1104)。従って、ホスト1000から出力された静止映像信号DATA=SIは、第1インターフェース2204又は第1経路PATH1を通じてディスプレイ3000に伝送されるので(ステップS1105)、ディスプレイ3000では、静止映像信号SIが表示される(ステップS1106)。

【0187】

モード転換命令MCC[1:0]=00によって定義された命令モードCOMMANDMODEの間(図22の1A参照)に、静止映像信号SIは、ディスプレイ3000で表示される。

【0188】

ホスト1000が動画信号をディスプレイドライバーIC2000に伝送しようとする際、コーデック1120が実行されると(ステップS1107)、CPUコア1128は、コーデック1120の実行によってモード転換命令MCC[1:0]=10を生成し、インターフェース1126は、モード転換命令MCC[1:0]=10を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1108)。

【0189】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=10に応答して、第1インターフェース2204の第1スイッチング回路2204−1をディセーブルするための第1制御信号CTRL1、第2インターフェース2206の第2スイッチング回路2206−1をイネーブルするための第2制御信号CTRL2、2A区間の間にフレームメモリ(GRAM)2204−3の出力信号を第1選択回路2210に伝送するためのスキャンスイッチング信号SWC_OFF、及び第2インターフェース2206の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=1を発生する(ステップS1109)。即ち、第2インターフェース2206が選択されることによって、第2経路PATH2が形成される。

【0190】

スキャンスイッチング回路2204−4は、スキャンスイッチング信号SWC_OFFが第1レベル、例えばローレベルである場合に、オンになり、スキャンスイッチング信号SWC_OFFが第2レベル、例えばハイレベルである場合に、オフになる。

【0191】

3A区間は、命令モードCOMMAND MODEからビデオモードVIDEO MODEへのスイッチング準備区間、即ちオーバーラップ区間(overlap interval)であり、出力回路2212は、タイミングコントローラ2220の制御によってディセーブルされる(ステップS1110)。従って、ディスプレイ3000は、出力回路2212がディセーブルされる直前の静止映像信号のフレームPFを保持する。

【0192】

1A区間から3A区間の間に、オシレーター2218は、制御回路2208の制御によってオシレーション信号OSCを発生する。オシレーション信号OSCは、ディスプレイ3000で表示されるフレームの周波数になる。

【0193】

一実施形態として、ディスプレイ3000がTFT−LCDとして具現される場合、TFT−LCDでフリッカーの発生を防止するために、TFT−LCDに供給される電圧の極性は、前のフレームの極性を保持する。

【0194】

3A区間を経た後、ディスプレイドライバーIC2000は、命令モードからビデオモードにスイッチングされる。即ち、4A区間の間に、ホスト1000は、動画信号DATA=MIをディスプレイドライバーIC2000に伝送し(ステップS1112)、ディスプレイドライバーIC2000は、第2インターフェース2206又は第2経路PATH2を用いて、ホスト1000から出力された動画信号MIをディスプレイ3000に伝送する。従って、ディスプレイ3000は、動画信号MIを、ドットクロック信号を用いて表示する(ステップS1114)。この際、オシレーター2218は、制御回路2208の制御によってオシレーション信号OSCを生成しない。

【0195】

ホスト1000が動画信号の次に静止映像信号をディスプレイ3000に伝送しようとする際、CPUコア1128は、コーデック1120の実行の終了を判断し(ステップS1115)、該判断結果によって、モード転換命令MCC[1:0]=00を生成してレジスタ1124に伝送する。インターフェース1126は、モード転換命令MCC[1:0]=00を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1116)。

【0196】

モード転換命令MCC[1:0]=00は、X時点で映像信号DATAに含まれて伝送され、Y時点、即ち垂直同期信号又は垂直ブランキング区間に含まれて伝送される。

【0197】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=00に応答して、第1インターフェース2204の第1スイッチング回路2204−1をイネーブルするための第1制御信号CTRL1、第2インターフェース2206の第2スイッチング回路2206−1をディセーブルするための第2制御信号CTRL2、第1スイッチング回路2204−1の出力信号を第2選択回路2204−2に伝送するための第2選択信号MMC[0]=0、フレームメモリ(GRAM)2204−3の出力信号を第1選択回路2210に伝送するためのスキャンスイッチング信号SWC_OFF、及び第1インターフェース2204の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=0を発生する(ステップS1117)。

【0198】

即ち、ディスプレイドライバーIC2000の動作モードは、ビデオモードから命令モードにスイッチングされる。第1インターフェース2204が選択されることによって、第1経路PATH1が形成される(ステップS1117)。

【0199】

ディスプレイドライバーIC2000の動作モードは、ビデオモードから命令モードにスイッチングされるが、ビデオモードでフレームメモリ(GRAM)2204−3はアクセスされないので、命令モードで入力された静止映像信号をフレームメモリ(GRAM)2204−3に書き込むための時間が必要である。

【0200】

従って、図22の5A区間の間に、即ちオーバーラップ区間の間に、出力回路2212のドライバーブロック2216は、タイミングコントローラ2220の制御によってディセーブルされる。従って、ディスプレイ3000は、出力回路2212がディセーブルされる直前にディスプレイされた動画信号PFを保持する(ステップS1118)。5A区間の間に、第1スイッチング回路2204−1を通じて伝送された静止映像信号は、フレームメモリ(GRAM)2204−4に書き込まれる(ステップS1119)。また、5A区間の間に、スキャンスイッチング信号SWC_OFFはハイレベルを保持するので、フレームメモリ(GRAM)2204−3に書き込まれた静止映像信号は出力されない。

【0201】

6A区間の間に、即ちビデオモードVIDEO MODEから命令モードCOMMAND MODEにスイッチングされた後、フレームメモリ(GRAM)2204−3に書き込まれた静止映像信号は、第1経路PATH1を通じてディスプレイ3000に伝送される(ステップS1120)。即ち、ディスプレイドライバーIC2000は、フレームメモリ(GRAM)2204−3に書き込まれた静止映像信号をスキャンして、該スキャンされた静止映像信号をディスプレイ3000に出力するので、静止映像信号SIは、ディスプレイ3000で表示される(ステップS1121)。

【0202】

図23は、図19に示したディスプレイドライバーの動作モードによるデータの流れの変形例を示す図であり、図24は、図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の変形例を示すタイミング図である。

【0203】

図19、図20、図23、及び図24を参照して、静止映像信号、動画信号、及び静止映像信号が順次にディスプレイ3000で表示される手順を説明すると、次の通りである。

【0204】

ホスト1000がディスプレイドライバーIC2000に静止映像信号SIを伝送しようとする際(ステップS1201)、CPUコア1128は、コーデック1120が実行されないことを感知し、該感知結果によって、モード転換命令MCC[1:0]=00をディスプレイドライバーIC2000に伝送する(ステップS1202)。受信器2202は、モード転換命令MCC[1:0]=00を制御回路2208に伝送する。

【0205】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=00に応答して、第1インターフェース2204の第1スイッチング回路2204−1をイネーブルするための第1制御信号CTRL1、第1スイッチング回路2204−1の出力信号を第2選択回路2204−2に伝送するための第2選択信号MMC[0]=0、フレームメモリ(GRAM)2204−3の出力信号を第1選択回路2210に伝送するためのスキャンスイッチング信号SWC_OFF、及び第1インターフェース2204の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=0を発生する(ステップS1203)。即ち、第1インターフェース2204が選択されることによって、第1経路PATH1が形成される。

【0206】

ホスト1000は、モード転換命令MCC[1:0]=00を伝送した後、静止映像信号SIを伝送する(ステップS1204)。従って、ホスト1000から出力された静止映像信号DATA=SIは、第1インターフェース2204又は第1経路PATH1を通じてディスプレイ3000に伝送されるので(ステップS1205)、ディスプレイ3000では、静止映像信号SIが表示される(ステップS1206)。

【0207】

モード転換命令MCC[1:0]=00によって定義された命令モードCOMMANDMODEの間(図24の1B参照)に、静止映像信号SIは、ディスプレイ3000で表示される。

【0208】

ホスト1000が動画信号をディスプレイドライバーIC2000に伝送しようとする際、コーデック1120が実行されると(ステップS1207)、CPUコア1128は、コーデック1120の実行によってモード転換命令MCC[1:0]=10を生成し、インターフェース1126は、モード転換命令MCC[1:0]=10を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1208)。

【0209】

この際、ディスプレイ3000での正常でない表示(abnormal display)を防止するために、CPUコア1128は、TE制御信号TEをモニターして、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直フロントポーチ(verticalfront porch:VFP)の間に、モード転換命令MCC[1:0]=10をディスプレイドライバーIC2000に伝送する(ステップS1208)。

【0210】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=10に応答して、第2インターフェース2206の第2スイッチング回路2206−1をイネーブルするための第2制御信号CTRL2を出力し、図24に示したタイミングによって、フレームメモリ(GRAM)2204−3の出力信号が第1選択回路2210に伝送されることを遮断するために、ハイレベルを有するスキャンスイッチング信号SWC_OFFを発生し、第2インターフェース2206の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=1を発生する(ステップS1209)。

【0211】

この際、第2選択信号MMC[0]は0である。即ち、第2インターフェース2206が選択されることによって、第2経路PATH2が形成される。

【0212】

ホスト1000は、モード転換命令MCC[1:0]=10を伝送した後、即座に動画信号(又は、動画ストリーム)を伝送する(ステップS1212)。従って、ディスプレイドライバーIC2000は、第2インターフェース2206又は第2経路PATH2を用いて動画信号MIをディスプレイ3000に伝送するので(ステップS1213)、動画信号MIがディスプレイ3000で表示される(ステップS1214)。

【0213】

垂直ブランキング区間の間に、ディスプレイドライバーIC2000は、動作モードを命令モードからビデオモードにスイッチングするので、ホスト1000とディスプレイドライバーIC2000のそれぞれは、ビデオモードで作動する。また、2B区間の間に、ホスト1000とディスプレイドライバーIC2000のそれぞれは、メモリを有していないビデオモードで作動する。

【0214】

ホスト1000が動画信号の次に静止映像信号をディスプレイ3000に伝送しようとする際、CPUコア1128は、コーデック1120の実行の終了を判断し(ステップS1215)、該判断結果によって、モード転換命令MCC[1:0]=00を生成してレジスタ1124に伝送する。インターフェース1126は、モード転換命令MCC[1:0]=00を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1216)。

【0215】

この際、ディスプレイ3000での正常でない表示を防止するために、CPUコア1128は、TE制御信号TEをモニターして、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直バックポーチ(vertical back porch:VBP)の間に、モード転換命令MCC[1:0]=10をディスプレイドライバーIC2000に伝送する(ステップS1216)。ポーチ区間は、垂直フロントポーチVFPと垂直バックポーチVBFとを含む。

【0216】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=00に応答して、第1インターフェース2204の第1スイッチング回路2204−1をイネーブルするための第1制御信号CTRL1、第1スイッチング回路2204−1の出力信号を第2選択回路2204−2に伝送するための第2選択信号MMC[0]=0、フレームメモリ(GRAM)2204−3の出力信号を第1選択回路2210に伝送するためのローレベルを有するスキャンスイッチング信号SWC_OFF、及び第1インターフェース2204の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=0を発生する(ステップS1217)。

【0217】

即ち、ディスプレイドライバーIC2000の動作モードは、ビデオモードから命令モードにスイッチングされる。第1インターフェース2204が選択されることによって、第1経路PATH1が選択される(ステップS1217)。

【0218】

ホスト1000は、モード転換命令MCC[1:0]=00を伝送した後、最初の静止映像信号、例えばフレームをTE制御信号TEの立下りエッジの前に伝送しなければならない(ステップS1218)。

【0219】

その理由は、静止映像信号をメモリ(GRAM)2204−3に書き込む動作が、フレームメモリ(GRAM)2204−3をスキャンする動作より先行しなければならないためである。即ち、ビデオモードから命令モードにスイッチングされることによってフレームメモリ(GRAM)2204−3からダミー映像信号が出力されることを防止するためである。ここで、スキャンとは、フレームメモリ(GRAM)2204−3に書き込まれた映像信号を読み出して、ディスプレイ3000に伝送する動作を意味する。

【0220】

静止映像信号がアップデートされる度に、静止映像信号は、フレームメモリ(GRAM)2204−3に書き込まれる。従って、ディスプレイドライバーIC2000は、第1インターフェース2204又は第1経路PATH1を通じて静止映像信号をディスプレイ3000に伝送し(ステップS1219)、静止映像信号は、ディスプレイ3000で表示される(ステップS1220)。

【0221】

図25は、図19に示したディスプレイドライバーの動作モードによる映像信号経路の他の例を示す図であり、図26は、図19に示したディスプレイドライバーの動作モードによるデータの流れの他の例を示す図であり、図27は、図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の他の例を示すタイミング図である。

【0222】

図19、図25、図26、及び図27を参照して、静止映像信号、動画信号、及び静止映像信号が順次にディスプレイ3000で表示される手順を説明すると、次の通りである。図26に示したS1201〜S1206は、図23に示したS1201〜S1206と実質的に同一である。

【0223】

静止映像信号SIがディスプレイ3000で表示された後、ホスト1000が動画信号をディスプレイドライバーIC2000に伝送しようとする際、コーデック1120が実行されると(ステップS1307)、CPUコア1128は、コーデック1120の実行によってモード転換命令MCC[1:0]=10を生成し、インターフェース1126は、レジスタ1124に保存されたモード転換命令MCC[1:0]=10を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1308)。

【0224】

この際、ディスプレイ3000での正常でない表示を防止するために、CPUコア1128は、TE制御信号TEをモニターして、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直フロントポーチVFPの間に、モード転換命令MCC[1:0]=10をディスプレイドライバーIC2000に伝送する(ステップS1308)。

【0225】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=10に応答して、第2インターフェース2206の第2スイッチング回路2206−1をイネーブルするための第2制御信号CTRL2を出力し、図27に示したタイミングによって、フレームメモリ(GRAM)2204−3の出力信号が第1選択回路2210に伝送されることを遮断するために、ハイレベルを有するスキャンスイッチング信号SWC_OFFを発生し、第2インターフェース2206の出力信号を出力回路2212に伝送するための第1選択信号MMC[1]=1を発生する(ステップS1309)。即ち、第2インターフェース2206が選択されることによって、第2経路PATH2が形成される。

【0226】

ホスト1000は、モード転換命令MCC[1:0]=10を伝送した後、即座に動画信号(又は、動画ストリーム)を伝送する(ステップS1312)。従って、ディスプレイドライバーIC2000は、第2インターフェース2206又は第2経路PATH2を用いて動画信号をディスプレイ3000に伝送するので(ステップS1313)、動画信号MIが、ディスプレイ3000で表示される(ステップS1314)。

【0227】

ホスト1000が動画信号の次に静止映像信号をディスプレイ3000に伝送しようとする際、CPUコア1128は、コーデック1120の実行の終了を判断し(ステップS1315)、該判断結果によって、モード転換命令MCC[1:0]=11を生成してレジスタ1124に伝送する。インターフェース1126は、モード転換命令MCC[1:0]=11を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1316)。

【0228】

この際、ディスプレイ3000での正常でない表示を防止するために、CPUコア1128は、TE制御信号TEをモニターして、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直バックポーチVBPの間に、モード転換命令MCC[1:0]=11をディスプレイドライバーIC2000に伝送する(ステップS1316)。

【0229】

制御回路2208は、受信器2202から出力されたモード転換命令MCC[1:0]=11に応答して、第2制御信号CTRL2、第2選択信号MMC[0]=1、ハイレベルを有するスキャンスイッチング信号SWC_OFF、及び第1選択信号MMC[1]=1を生成する。

【0230】

第2スイッチング回路2206−1は、ブリッジモードを行うために、第2制御信号CTRL2に応答して、動画信号MIを第1選択回路2210に伝送すると同時に第2選択回路2204−2に伝送する。第2選択回路2204−2は、第2選択信号MMC[0]=1によって、動画信号をフレームメモリ(GRAM)2204−3に伝送する。ブリッジモードで第3経路PATH3が形成される。即ち、モード転換命令MCC[1:0]=11に対応するブリッジモードで、ディスプレイドライバーIC2000は、第2インターフェース2206を用いて動画信号を第1選択回路2210に伝送すると同時に、第2選択回路2204−2を通じて動画信号をフレームメモリ(GRAM)2204−3に書き込む(ステップS1317)。

【0231】

図27に示したように、3C区間の間に、スキャンスイッチング回路2204−4は、ハイレベルを有するスキャンスイッチング信号SWC_OFFに応答して、オフ状態を保持する。

【0232】

第1選択信号MMC[1]=1に応答して、第1選択回路2210は、第2スイッチング回路2206−1から出力された動画信号を出力回路2212に伝送する。

【0233】

3C区間を経た後、ホスト1000は、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直フロントポーチVFPの間に、モード転換命令MCC[1:0]=00をディスプレイドライバーIC2000に伝送する(ステップS1318)。

【0234】

モード転換命令MCC[1:0]=00によって、第1インターフェース2204又は第1経路PATH1が選択された後(ステップS1319)、ホスト1000は、静止映像信号をディスプレイドライバーに伝送し(ステップS1320)、ディスプレイドライバーIC2000は、第1インターフェース2204に含まれるフレームメモリ(GRAM)2204−3を用いて、静止映像信号をディスプレイ3000に伝送する(ステップS1321)。従って、ディスプレイ3000で静止映像信号SIが表示される(ステップS1322)。

【0235】

図28は、図19に示したディスプレイドライバーの動作モードによる映像信号経路の更に他の例を示す図であり、図29は、図19に示したディスプレイドライバーの動作モードによるデータの流れの更に他の例を示す図であり、図30は、図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の更に他の例を示すタイミング図である。

【0236】

図19、図28、図29、及び図30を参照して、静止映像信号、動画信号、及び静止映像信号が順次にディスプレイ3000で表示される手順を説明すると、次の通りである。図29に示したS1201〜S1206は、図23に示したS1201〜S1206と実質的に同一である。

【0237】

静止映像信号SIがディスプレイ3000で表示された後、ホスト1000が動画信号をディスプレイドライバーIC2000に伝送しようとする際、コーデック1120が実行されると(ステップS1407)、CPUコア1128は、コーデック1120の実行によってモード転換命令MCC[1:0]=01を生成し、インターフェース1126は、モード転換命令MCC[1:0]=01を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1408)。

【0238】

この際、ディスプレイ3000での正常でない表示を防止するために、CPUコア1128は、TE制御信号TEをモニターして、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直フロントポーチVFPの間に、モード転換命令MCC[1:0]=01をディスプレイドライバーIC2000に伝送する(ステップS1408)。

【0239】

制御回路2208は、第4経路PATH4を形成するための第2制御信号CTRL2、第2選択信号MMC[0]=1、ローレベルを有するスキャンスイッチング信号SWC_OFF、及び第2選択信号(MMC[1]=0)を生成する(ステップS1409)。

【0240】

ホスト1000は、モード転換命令MCC[1:0]=01をディスプレイドライバーIC2000に伝送した後、即座に動画信号をディスプレイドライバーIC2000に伝送する(ステップS1410)。従って、ディスプレイドライバーIC2000は、第4経路PATH4を通じて動画信号をディスプレイに伝送する(ステップS1411)。動画信号MIが、ディスプレイ3000で表示される(ステップS1412)。

【0241】

ホスト1000が動画信号の次に静止映像信号をディスプレイ3000に伝送しようとする際、CPUコア1128は、コーデック1120の実行の終了を判断し(ステップS1413)、該判断結果によって、モード転換命令MCC[1:0]=00を生成してレジスタ1124に伝送する。インターフェース1126は、モード転換命令MCC[1:0]=00を含む映像信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1414)。

【0242】

この際、ディスプレイ3000での正常でない表示を防止するために、CPUコア1128は、TE制御信号TEをモニターして、垂直同期信号Vsyncの垂直ブランキング区間の間に、例えば垂直バックポーチVBPの間に、モード転換命令MCC[1:0]=00をディスプレイドライバーIC2000に伝送する(ステップS1414)。

【0243】

モード転換命令MCC[1:0]=00によって、ディスプレイドライバーIC2000は、第1インターフェース2204又は第1経路PATH1を選択する(ステップS1415)。ディスプレイドライバーIC2000は、ホスト1000から伝送された静止映像信号SIを受信し(ステップS1416)、第1インターフェース2204又は第1経路PATH1を通じて静止映像信号SIをディスプレイ3000に伝送する(ステップS1417)。従って、ディスプレイ3000では、静止映像信号SIが表示される(ステップS1418)。

【0244】

以上、図面を参照しながら本発明の実施形態を説明したが、本発明は、上述の実施形態に限定されるものではなく、本発明の技術思想から逸脱しない範囲内で多様に変更実施することが可能である。

【符号の説明】

【0245】

10、10A、10B、10C 映像信号処理システム

100 アプリケーションホストプロセッサ(ホスト)

101、103 命令パケット

110 制御ロジック

120 同期パケット生成器

130 制御値調節ロジック

200A、200B、2000 ディスプレイドライバーIC(DDI)

210 データ/同期デコーダ

211 第1スイッチ回路

213 第2スイッチ回路

215、2204−3 フレームメモリ(GRAM)

217 フレームメモリコントローラ

219、2210 第1選択回路

220 命令デコーダ

230、2208 制御回路

231−1 垂直同期信号同期カウンター

231−2 内部垂直同期信号生成器

232−1 水平同期信号同期カウンター

232−2 内部水平同期信号生成器

233、2218 オシレーター

234 誤差計算器

235 TE制御信号生成器

236 制御値レジスタ

237 誤差情報レジスタ

240、2204−2 第2選択回路

250 第3選択回路

300、2300、3000 ディスプレイ

1000 アプリケーションホストプロセッサ

1110 RF受信器

1114 DRAM

1116 NANDフラッシュメモリ

1118 フレームバッファ

1120 コーデック

1122 ディスプレイコントローラ

1124 レジスタ

1126 インターフェース

1128 CPUコア

2202 受信器

2202−1 MIPI D−PHY

2202−2 CIL&DSI

2202−3 ラッパ

2204 第1インターフェース

2204−1 第1スイッチング回路

2204−4 スキャンスイッチング回路

2206 第2インターフェース

2206−1 第2スイッチング回路

2212 出力回路

2214 輝度調節回路

2216 ドライバーブロック

2220 タイミングコントローラ

2222 電力回路

【技術分野】

【0001】

本発明は、ディスプレイドライバーに係り、より詳しくは、動作途中でモード転換命令によってビデオモードと命令モードとの間でモード転換ができるディスプレイドライバーとその動作方法、ディスプレイドライバーを制御するホストの動作方法、イメージ処理システム、携帯用通信装置、及びアプリケーションホストプロセッサの動作方法に関する。

【背景技術】

【0002】

映像解像度の増加に伴い、モバイルアプリケーションプロセッサとディスプレイドライバーIC(integrated circuit)との間のデータトラフィックが急速に増加している。これにより、モバイルアプリケーションプロセッサ及び/又はディスプレイドライバーICで消耗する電力も継続的に増加している。

【0003】

音声通話中心の既存の携帯電話は、マルチメディアデータ中心のスマートフォンに急速に代替されている。スマートフォンに具現されたディスプレイドライバーICは、静止映像信号又は動画信号のようなマルチメディアデータをディスプレイで表示するために頻繁に作動する。

【0004】

従って、スマートフォンのバッテリーの持続時間が減少する。バッテリーの持続時間は、一回の充電で使い続けることが可能なバッテリーの使用時間を意味する。これにより、静止映像信号と動画信号とを処理するスマートフォンのような移動通信装置のバッテリーの持続時間を延ばすことができる方法が必要である。

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、上記従来の問題点に鑑みてなされたものであって、本発明の目的は、省力化のために、動作途中でモード転換命令によってビデオモードと命令モードとの間でモード転換ができ、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令によって、メモリを用いて静止映像信号をディスプレイに伝送するか、又はメモリを利用せずに動画信号をディスプレイに伝送するかを決定するディスプレイドライバーとその動作方法、ディスプレイドライバーを制御するホストの動作方法、イメージ映像信号処理システム、携帯用通信装置、及びアプリケーションホストプロセッサの動作方法を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するためになされた本発明の一態様によるディスプレイドライバーの動作方法は、ホストから伝送された同期パケットに関連する同期信号の周期をカウントしてカウント値を生成する段階と、フレームメモリをバイパスして第1イメージデータをディスプレイに伝送するビデオモードから前記フレームメモリを通じて第2イメージデータを前記ディスプレイに伝送する命令モードへの転換を指示するモード転換命令を、前記ホストから受信する段階と、前記同期信号の最後のパルスが生成された後、前記モード転換命令によって、前記カウント値を用いて前記同期信号の周期と同じ周期を有する内部同期信号を生成する段階と、を有し、前記最後のパルスと前記内部同期信号の最初のパルスとの時間間隔は、前記同期信号の周期と同一である。

【0007】

前記ディスプレイドライバーの動作方法は、前記時間間隔の間に、前記第1イメージデータを前記ディスプレイにバイパスすると同時に前記フレームメモリに書き込む段階を更に含む。

前記第1イメージデータのフレームレートは、前記第2イメージデータのフレームレートより大きい。

前記ディスプレイドライバーの動作方法は、前記同期信号の周期と前記内部同期信号の周期との差を計算する段階と、前記差を用いてティアリング効果制御信号の発生タイミングを調節し、該ティアリング効果制御信号を前記ホストに伝送する段階と、を更に含む。

【0008】

上記目的を達成するためになされた本発明の一態様によるディスプレイドライバーの動作を制御するホストの動作方法は、前記ディスプレイドライバーからティアリング効果制御信号と誤差情報とを受信する段階と、前記ティアリング効果制御信号と前記誤差情報とを用いて、前記ディスプレイドライバーで復元される同期信号に関連する同期パケットの発生タイミングを調節する段階と、を有する。

【0009】

前記誤差情報は、前記同期信号の周期と前記同期信号の周期を用いて前記ディスプレイドライバーで生成された内部同期信号の周期との差に対応する情報である。

【0010】

上記目的を達成するためになされた本発明の他の態様によるディスプレイドライバーの動作を制御するホストの動作方法は、前記ディスプレイドライバーから誤差情報を受信する段階と、前記誤差情報に基づいてティアリング効果制御信号の発生タイミングを制御するための制御値を前記ディスプレイドライバーに伝送する段階と、前記ディスプレイドライバーから、前記制御値によって前記発生タイミングが制御されたティアリング効果制御信号を受信する段階と、前記制御されたティアリング効果制御信号によって、前記ディスプレイドライバーで復元される同期信号に関連する同期パケットを生成する段階と、を有する。

【0011】

前記誤差情報は、前記同期信号の周期と前記同期信号の周期を用いて前記ディスプレイドライバーで生成された内部同期信号の周期との差に対応する情報である。

【0012】

上記目的を達成するためになされた本発明の一態様によるイメージ処理システムは、ディスプレイドライバーと、前記ディスプレイドライバーの動作を制御するホストと、を有し、前記ディスプレイドライバーは、前記ホストから伝送された同期パケットに関連する同期信号の周期をカウントしてカウント値を生成し、フレームメモリをバイパスして第1イメージデータをディスプレイに伝送するビデオモードから前記フレームメモリを通じて第2イメージデータを前記ディスプレイに伝送する命令モードへの転換を指示する第1モード転換命令を、前記ホストから受信し、前記同期信号の最後のパルスが生成された後、前記カウント値を用いて前記同期信号の周期と同じ周期を有する内部同期信号を生成し、前記最後のパルスと前記内部同期信号の最初のパルスとの時間間隔は、前記同期信号の周期と同一であり、前記ビデオモードから前記命令モードに転換された後、前記ホストは、新たな同期パケットを前記ディスプレイドライバーに伝送しない。

【0013】

前記ディスプレイドライバーは、前記同期信号の周期と前記内部同期信号の周期との差を計算し、前記命令モードから前記ビデオモードへの転換を指示する第2モード転換命令を前記ホストから受信した後、前記差を用いてティアリング効果制御信号の発生タイミングを調節し、該ティアリング効果制御信号を前記ホストに伝送し、前記ホストは、前記ティアリング効果制御信号によって新たな同期パケットを生成する。

【0014】

上記目的を達成するためになされた本発明の他の態様によるイメージ処理システムは、ディスプレイドライバーと、前記ディスプレイドライバーの動作を制御するホストと、を有し、前記ディスプレイドライバーは、フレームメモリを通じて第1イメージデータをディスプレイに伝送する命令モードから前記フレームメモリをバイパスして第2イメージデータを前記ディスプレイに伝送するビデオモードへの転換を指示するモード転換命令によって、ティアリング効果制御信号と誤差情報とを前記ホストに伝送し、前記ホストは、前記ティアリング効果制御信号と前記誤差情報とを用いて、前記ディスプレイドライバーで復元される同期信号に関連する同期パケットの発生タイミングを調節する。

【0015】

前記ホストは、前記命令モードの間に、前記ディスプレイで生成された内部同期信号の最後のパルスと前記同期信号の最初のパルスとの時間間隔が前記内部同期信号の周期と同一になるように、前記同期パケットの前記発生タイミングを調節する。

【0016】

上記目的を達成するためになされた本発明の更に他の態様によるイメージ処理システムは、ディスプレイドライバーと、前記ディスプレイドライバーの動作を制御するホストと、を有し、前記ディスプレイドライバーは、フレームメモリを使って第1イメージデータをディスプレイに伝送する命令モードから前記フレームメモリをバイパスして第2イメージデータを前記ディスプレイに伝送するビデオモードへの転換を指示するモード転換命令によって、誤差情報を前記ホストに伝送し、前記ホストは、前記誤差情報に基づいてティアリング効果制御信号の発生タイミングを制御するための制御値を前記ディスプレイドライバーに伝送し、前記ホストは、前記ディスプレイドライバーから前記制御値によって生成されたティアリング効果制御信号を受信し、該受信したティアリング効果制御信号によって前記ディスプレイドライバーで復元される同期信号に関連する同期パケットを生成する。

【0017】

上記目的を達成するためになされた本発明の一態様によるディスプレイドライバーは、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を含む前記映像信号を受信する受信器と、前記受信器から出力された前記モード転換命令に応答して、第1制御信号と第2制御信号とを生成する制御回路と、前記第1制御信号に応答して、前記受信器から出力された前記静止映像信号を、メモリを用いて出力する第1インターフェースと、前記第2制御信号に応答して、前記受信器から出力された前記動画信号を、前記メモリを利用せずに出力する第2インターフェースと、を備える。

【0018】

前記第1インターフェースは、前記第1制御信号に応答して、前記静止映像信号の伝送を制御する第1スイッチング回路と、前記モード転換命令によって、前記制御回路から出力された選択信号に応答して、前記第1スイッチング回路から伝送された前記静止映像信号と前記第2インターフェースから伝送された前記動画信号とのうちの何れか1つを前記メモリに伝送する選択回路と、を含む。

前記第1インターフェースは、MIPI(Mobile Industry Processor Interface)命令モードをサポートするインターフェース又はCPUインターフェースであり、前記第2インターフェースは、MIPIビデオモードをサポートするインターフェース又はRGBインターフェースである。

前記モード転換命令は、前記映像信号に含まれる垂直ブランキング区間に含まれる。

前記ディスプレイドライバーは、第1選択信号に応答して、前記メモリから出力された前記静止映像信号又は前記第2インターフェースから出力された前記動画信号を出力する第1選択回路と、前記第1選択回路から出力された映像信号を前記ディスプレイに伝送する出力回路と、を更に含み、前記制御回路は、前記モード転換命令に応答して、前記第1選択信号を生成する。

【0019】

上記目的を達成するためになされた本発明の一態様による携帯用通信装置は、ディスプレイと、前記ディスプレイに映像信号を伝送するためのディスプレイドライバーと、前記ディスプレイドライバーに、前記ディスプレイで表示される前記映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を含む前記映像信号を伝送するホストと、を有し、前記ディスプレイドライバーは、前記モード転換命令に応答して、第1制御信号と第2制御信号とを生成する制御回路と、前記第1制御信号によって、メモリを用いて前記静止映像信号を前記ディスプレイに伝送する第1インターフェースと、前記第2制御信号によって、前記メモリを利用せずに前記動画信号を前記ディスプレイに伝送する第2インターフェースと、を含む。

【0020】

前記ディスプレイドライバーは、第1選択信号に応答して、前記第1インターフェースの出力ポートと前記第2インターフェースの出力ポートとのうちの何れか1つから出力された前記映像信号を出力する第1選択回路と、前記第1選択回路から出力された映像信号を前記ディスプレイに伝送する出力回路と、を更に含み、前記第1インターフェースは、前記第1制御信号に応答して、前記静止映像信号を伝送する第1スイッチング回路と、第2選択信号に応答して、前記第1スイッチング回路から出力された前記静止映像信号と前記第2インターフェースから出力された前記動画信号とのうちの何れか1つを前記メモリに出力する第2選択回路と、スキャンスイッチング信号に応答して、前記メモリに保存された前記静止映像信号を前記第1選択回路に伝送するスキャンスイッチング回路と、を含み、前記第2インターフェースは、前記第2制御信号に応答して、前記動画信号を前記第1選択回路と前記第2選択回路とのうちの少なくとも1つに伝送する第2スイッチング回路を含み、前記制御回路は、前記モード転換命令に応答して、前記第1選択信号、前記第2選択信号、及び前記スキャンスイッチング信号を生成する。

前記ホストは、コーデックの実行によって前記映像信号が前記静止映像信号又は前記動画信号であるか否かを判断し、該判断結果によって前記モード転換命令を生成する。

前記ホストは、前記動画信号の次に前記静止映像信号が伝送されることを指示する前記モード転換命令を垂直ブランキング区間に前記ディスプレイドライバーに伝送した後、最初の静止映像信号を最初のティアリング効果制御信号の立下りエッジの前に前記ディスプレイドライバーに伝送する。

前記第2インターフェースは、前記第2制御信号によって、前記動画信号を前記ディスプレイに伝送すると同時に前記メモリに伝送し、前記第1インターフェースは、前記制御回路から出力されたスイッチング信号によって、前記メモリに保存された前記動画を前記ディスプレイドライバーに伝送する。

【0021】

上記目的を達成するためになされた本発明の他の態様によるディスプレイドライバーの動作方法は、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令に応答して、制御信号を生成する段階と、前記制御信号によって、メモリを経由して前記静止映像信号を前記ディスプレイに伝送する命令モードと前記メモリを経由せずに前記動画信号を前記ディスプレイに伝送するビデオモードとの間でスイッチングする段階と、を有する。

【0022】

前記モード転換命令は、前記映像信号の垂直ブランク区間に含まれる。

前記ビデオモードと前記命令モードとの間でスイッチングされる際、前記映像信号は、前記映像信号の少なくとも1フレームの間に前記ディスプレイに伝送されない段階を更に含む。

【0023】

上記目的を達成するためになされた本発明の一態様によるアプリケーションホストプロセッサの動作方法は、ディスプレイドライバーから出力されたティアリング効果制御信号をモニタリングする段階と、前記モニタリング結果によって、前記ディスプレイドライバーに伝送される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を前記映像信号の垂直ブランキング区間に伝送する段階と、を有する。

【0024】

前記アプリケーションホストプロセッサの動作方法は、前記モード転換命令を伝送した後、直ちに前記動画信号を前記ディスプレイドライバーに伝送する段階を更に含む。

前記モード転換命令は、前記垂直ブランキング区間の垂直フロントポーチ又は垂直バックポーチに伝送される。

前記アプリケーションホストプロセッサの動作方法は、前記モード転換命令を伝送した後の最初の静止映像信号を前記ティアリング効果制御信号の立下りエッジの前に伝送する段階を更に含む。

【発明の効果】

【0025】

本発明のディスプレイドライバーによれば、動作途中でモード転換命令によってビデオモードと命令モードとの間でモード転換を行うことができる。従って、ディスプレイドライバーで消耗する電力を効果的に減らすことができる。

また、本発明のディスプレイドライバーによれば、ディスプレイで表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令によって、メモリを用いて静止映像信号をディスプレイに伝送するか又はメモリを利用せずに動画信号をディスプレイに伝送するかを決定することができる。従って、ディスプレイドライバーで消耗する電力を減らすことができる。

【図面の簡単な説明】

【0026】

【図1】本発明の一実施形態による映像信号処理システムのブロック図である。

【図2】ホストからディスプレイドライバーに伝送されるパケットの一例を示す図である。

【図3】図1に示したディスプレイドライバーの一例を示すブロック図である。

【図4】図3に示したディスプレイドライバーの動作を説明するフローチャートである。

【図5】図3に示したディスプレイドライバーの動作を説明するタイミング図である。

【図6】図3に示した制御回路の一例を示すブロック図である。

【図7】本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するフローチャートである。

【図8】本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するタイミング図である。

【図9】図1に示したホストの一例を示す内部ブロック図である。

【図10】図9に示したホストの同期パケットの発生タイミングを制御する方法を説明するフローチャートである。

【図11】図9に示したホストのティアリング効果制御信号の発生タイミングを制御するための制御値を生成する方法を説明するフローチャートである。

【図12】本発明の他の実施形態による映像信号処理システムのブロック図である。

【図13】図12に示したディスプレイドライバーの一例を示すブロック図である。

【図14】図12に示したディスプレイドライバーの動作を説明するフローチャートである。

【図15】本発明の更に他の実施形態による映像信号処理システムのブロック図である。

【図16】図15に示したアプリケーションホストプロセッサの一例を示す概略的なブロック図である。

【図17】図16に示したアプリケーションホストプロセッサの動作を説明するフローチャートである。

【図18】図16に示したアプリケーションホストプロセッサから出力されるモード転換命令を含む映像信号及びクロック信号の波形図である。

【図19】図15に示したディスプレイドライバーの一例を示す概略的なブロック図である。

【図20】図19に示したディスプレイドライバーの動作モードによる映像信号経路の一例を示す図である。

【図21】図19に示したディスプレイドライバーの動作モードによるデータの流れの一例を示す図である。

【図22】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の一例を示すタイミング図である。

【図23】図19に示したディスプレイドライバーの動作モードによるデータの流れの変形例を示す図である。

【図24】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の変形例を示すタイミング図である。

【図25】図19に示したディスプレイドライバーの動作モードによる映像信号経路の他の例を示す図である。

【図26】図19に示したディスプレイドライバーの動作モードによるデータの流れの他の例を示す図である。

【図27】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の他の例を示すタイミング図である。

【図28】図19に示したディスプレイドライバーの動作モードによる映像信号経路の更に他の例を示す図である。

【図29】図19に示したディスプレイドライバーの動作モードによるデータの流れの更に他の例を示す図である。

【図30】図19に示したディスプレイドライバーを含む図15の映像信号処理システムの信号の更に他の例を示すタイミング図である。

【発明を実施するための形態】

【0027】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

【0028】

図1は、本発明の一実施形態による映像信号処理システムのブロック図であり、図2は、ホストからディスプレイドライバーに伝送されるパケットの一例を示す図である。図1を参照すると、映像信号処理システム10Aは、静止映像信号又は動画信号をディスプレイ300で表示する携帯電話、スマートフォン、タブレットPC(personal computer)、PDA(Personal Digital Assistant)、又はPMP(Portable Multimedia Player)のような移動型の装置、小型機器(handheld device)又は小型コンピュータを意味する。

【0029】

映像信号処理システム10Aは、アプリケーションホストプロセッサ(以下、‘ホスト’と称する)100、ディスプレイドライバーIC(DDI)200A、及びディスプレイ300を含む。

【0030】

一実施形態として、ホスト100は、ホスト100の内部に具現されたコーデックの実行によって、ディスプレイ300で表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を有する命令パケットCPを含むパケットPACをディスプレイドライバーIC200Aに伝送する。他の実施形態として、ホスト100は、ディスプレイ300で表示されるイメージデータのフレームレートによって、イメージデータを、フレームメモリをバイパスしてディスプレイ300に伝送するか、又はフレームメモリを通じてディスプレイ300に伝送するかを指示するモード転換命令を有する命令パケットCPを含むパケットPACをディスプレイドライバーIC200Aに伝送し得る。

【0031】

例えば、イメージデータのフレームレートが30fps(frames per second)より小さい場合、イメージデータはフレームメモリを通じてディスプレイ300に伝送され、それ以外の場合、イメージデータはフレームメモリをバイパスしてディスプレイ300に伝送される。

【0032】

図1及び図2を参照すると、クロック信号CLKによって、ホスト100からディスプレイドライバーIC200Aに伝送されるパケットPACは、垂直同期パケットVS、水平同期パケットHS、データストリームパケット(DS)、及び命令パケットCPを含む。ここで、パケットは、ビットの集合である。

【0033】

垂直同期パケットVSは、映像信号(又は、イメージデータ)を表示するために必要な垂直同期信号に関連する情報を含み、水平同期パケットHSは、映像信号を表示するために必要な水平同期信号に関連する情報を含む。従って、ディスプレイドライバーIC200Aは、垂直同期パケットVSから垂直同期信号を復元し、水平同期パケットHSから水平同期信号を復元する。この際、クロック信号CLKが、復元に使われる。

【0034】

データストリームパケットDSは、ディスプレイ300で表示される映像信号を含み、命令パケットCPは、ディスプレイドライバーIC200Aの動作及び/又はディスプレイ300の動作に関連する命令を含む。例えば、命令パケットCPは、モード転換命令を含む。

【0035】

ホスト100は、ディスプレイドライバーIC200Aから出力されたティアリング効果(tearing effect:TE)制御信号TEを受信し、該受信したTE制御信号TEによって、パケットPACの生成タイミング又は伝送タイミングを制御する。従って、パケットPACの生成タイミング又は伝送タイミングによって、垂直同期信号及び/又は水平同期信号の復元タイミングが制御される。ここで、TE制御信号TEは、ティアリング又はスクリーンティアリング(一画面に複数のフレームが表示されることで歪みやちらつきが見える現象)を防止するための制御信号である。

【0036】

例えば、垂直同期信号Vsyncの生成タイミングは、TE制御信号TEの生成タイミングによって決定される。また、TE制御信号TEの生成タイミングは、ホスト100によって設定された制御値TEVによって、ディスプレイドライバーIC200Aによって制御される。即ち、制御値TEVによって、TE制御信号TEの生成タイミング、垂直同期信号Vsyncの生成タイミング、及び/又は水平同期信号Hsyncの生成タイミングが制御される。一実施形態として、ホスト100は、TE制御信号TEと誤差情報EIとを用いて、パケットPACの生成タイミング又は伝送タイミングを制御する。他の実施形態として、ホスト100は、誤差情報EIを用いて制御値TEVを調節することができる。

【0037】

ディスプレイドライバーIC200Aは、ホスト100から出力されたパケットPACに含まれるデータストリームパケットDSを処理又は復元し、ホスト100から出力されたパケットPACの命令パケットCPに含まれるモード転換命令に応答して、処理又は復元されたデータDDATAを、フレームメモリを通じてディスプレイ300に伝送するか、又はフレームメモリをバイパスしてディスプレイ300に伝送するかを決定する。

【0038】

この際、ビデオモードVMで、ディスプレイドライバーIC200Aは、フレームメモリをバイパスしたデータDDATAと共に同期信号Syncをディスプレイ300に伝送する。また、命令モードCMで、ディスプレイドライバーIC200Aは、フレームメモリを通じて出力されたデータDDATAを内部同期信号ISyncと共にディスプレイ300に伝送する。

【0039】

ディスプレイ300は、同期信号Sync又は内部同期信号ISyncを用いて、ディスプレイドライバーIC200Aから出力された出力映像信号DDATAを表示する。例えば、ディスプレイ300は、LCD(Liquid CrystalDisplay)、LED(Light Emitting Diode)ディスプレイ、OLED(Organic LED)ディスプレイ、又はAMOLED(Active−Matrix OLED)ディスプレイとして具現可能である。

【0040】

図3は、図1に示したディスプレイドライバーの一例を示すブロック図であり、図4は、図3に示したディスプレイドライバーの動作を説明するフローチャートであり、図5は、図3に示したディスプレイドライバーの動作を説明するタイミング図である。図1〜図3を参照すると、ディスプレイドライバーIC200Aは、データ/同期デコーダ(data/synchronization decoder)210、第1スイッチ回路211、第2スイッチ回路213、フレームメモリ(GRAM)215、フレームメモリコントローラ217、第1選択回路219、命令デコーダ220、制御回路230、第2選択回路240、及び第3選択回路250を含む。

【0041】

クロック信号CLKに応答して、データ/同期デコーダ210は、パケットPACに含まれるデータストリームパケットDSから映像信号DATAを復元し、垂直同期パケットVSから垂直同期信号Vsyncを復元し、水平同期パケットHSから水平同期信号Hsyncを復元する。一実施形態として、データ/同期デコーダ210は、デシリアライザ(deserializer)として具現可能である。

【0042】

第1スイッチ回路211は、復元映像信号DATAを第1スイッチング信号SW1に応答して第1選択回路219に伝送する。第2スイッチ回路213は、復元映像信号DATAを第2スイッチング信号SW2に応答してフレームメモリ(GRAM)215に伝送する。一実施形態として、第1及び第2スイッチ回路211、213は、NMOSトランジスタで具現された少なくとも1つのスイッチを含む。他の実施形態として、第1及び第2スイッチ回路211、213は、バスコントローラの機能を行うことができる。

【0043】

例えば、第1スイッチ回路211は、フレームメモリ215を通じないで動画信号を処理するMIPI(Mobile Industry Processor Interface)ビデオモードをサポートするインターフェース又はRGBインターフェースである。

【0044】

第2スイッチ回路213は、静止映像信号を処理するために、フレームメモリ215を使うMIPI命令モードをサポートするインターフェース、CPU(Central Processing Unit)インターフェース又はMCU(Micro Controller Unit)インターフェースである。

【0045】

フレームメモリコントローラ217の制御によって、フレームメモリ(GRAM)215は、第2スイッチ回路213を通じて入力された復元映像信号DATAを受信して保存する。例えば、フレームメモリ215は、グラフィックメモリとして具現可能である。

【0046】

フレームメモリコントローラ217は、命令デコーダ220から出力されたアクセス制御信号ACCによって、フレームメモリ(GRAM)215のライト動作又はリード動作を制御する。一実施形態として、アクセス制御信号ACCは、ライト動作に関連する制御信号又はリード動作に関連する制御信号である。

【0047】

第1選択信号SEL1によって、第1選択回路219は、第1スイッチ回路211を通じて入力された復元映像信号DATA又はフレームメモリ(GRAM)215から出力された映像信号を出力映像信号DDATAとしてディスプレイ300に伝送する。例えば、第1選択信号SEL1が論理0又はローレベルであると、第1選択回路219は、第1スイッチ回路211を通じて入力された復元映像信号DATAを出力し、第1選択信号SEL1が論理1又はハイレベルであると、第1選択回路219は、フレームメモリ215から出力された映像信号を出力する。例えば、第1選択回路219は、マルチプレクサとして具現可能である。

【0048】

命令デコーダ220は、クロック信号CLKによって、パケットPACに含まれる命令パケットCPをデコーディングし、該デコーディング結果によって、アクセス制御信号ACC、複数のスイッチング信号SW1、SW2、複数の選択信号SEL1、SEL2、及びイネーブル信号ENを生成する。

【0049】

制御回路230は、TE制御信号TE及び/又はエラー情報EIをホスト100に出力する。

【0050】

一実施形態として、制御回路230は、パケットPACの生成タイミング又は出力タイミングを制御するために、TE制御信号TEとエラー情報EIとをホスト100に伝送する。他の実施形態として、制御回路230は、パケットPACの生成タイミング又は出力タイミングを制御するために、エラー情報EIのみをホスト100に伝送し得る。更に他の実施形態として、制御回路230は、パケットPACの生成タイミング又は出力タイミングを制御するために、制御値TEVによってTE制御信号TEの生成タイミングを制御し、その結果として生成されたTE制御信号TEをホスト100に伝送し得る。

【0051】

また、制御回路230は、イネーブル信号ENに応答して、垂直同期信号Vsyncの周期と同じ周期を有する内部垂直同期信号IVsyncを出力し、水平同期信号Hsyncの周期と同じ周期を有する内部水平同期信号IHsyncを出力する。

【0052】

第2選択信号SEL2によって、第2選択回路240は、ビデオモードVMの間に垂直同期信号Vsyncを、そして命令モードCMの間に内部垂直同期信号IVsyncを出力する。第2選択信号SEL2によって、第3選択回路250は、ビデオモードVMの間に水平同期信号Hsyncを、そして命令モードCMの間に内部水平同期信号IHsyncを出力する。

【0053】

例えば、第2選択信号SEL2が論理0又はローレベルであると、第2及び第3選択回路240、250は、ビデオモードVMを行うために、各同期信号Vsync、Hsyncを出力し、第2選択信号SEL2が論理1又はハイレベルであると、第2及び第3選択回路240、250は、命令モードCMを行うために、各内部同期信号IVsync、IHsyncを出力する。

【0054】

例示的に、命令パケットCPに含まれるモード転換命令が2ビットで具現される場合、モード転換命令によるディスプレイドライバーIC200Aの動作モードと各制御信号SW1、SW2、SEL1、及びSEL2の状態は、表1のようである。

【0055】

【表1】

【0056】

この際、オーバーラップモード(overlap mode)は、ビデオモードVMから命令モードCMへの転換を指示するモード転換命令(図5のMCC参照)によって、ディスプレイドライバーIC200Aが、前記命令モードCMを行う前の少なくとも1フレームの間に、ビデオモードVMで入力されたイメージデータをディスプレイ300にバイパスすると同時にフレームメモリ217に書き込む動作を意味する。

【0057】

ディスプレイドライバーIC200Aの動作モードが、モード転換命令によって、フレームメモリ215をバイパスして第1イメージデータをディスプレイ300に伝送するビデオモードVMから、フレームメモリ217を通じて第2イメージデータをディスプレイ300に伝送する命令モードCMに転換される手順を、図1〜図5を参照して説明すると、次の通りである。この際、第1イメージデータのフレームレートは、第2イメージデータのフレームレートより大きい。

【0058】

ビデオモードVMの間に、データ/同期デコーダ210は、ホスト100からパケットPACを受信し(ステップS10)、パケットPACに含まれる垂直同期パケットVSを用いて垂直同期信号Vsyncを復元し、パケットPACに含まれる水平同期パケットHSを用いて水平同期信号Hsyncを復元し、パケットPACに含まれるデータストリームDSからデータDATAを復元する(ステップS20)。

【0059】

命令デコーダ220は、パケットPACに含まれる命令パケットCPによって、ビデオモードを行うための複数の制御信号SW1、SW2、SEL1、及びSEL2を生成する。各制御信号SW1、SW2、SEL1、及びSEL2のレベルは、表1のようである。

【0060】

第1選択回路219は、第1スイッチ回路211を通じて入力された復元データDATAをディスプレイ300に伝送し、第2及び第3選択回路240、250は、各同期信号Vsync、Hsyncをディスプレイ300に伝送する(ステップS30)。

【0061】

第1区間INT1の間に、制御回路230は、垂直同期信号Vsyncの周期T1をカウントして第1カウント値を生成し、水平同期信号Hsyncの周期T2をカウントして第2カウント値を生成する(ステップS40)。

【0062】

ホスト100は、ビデオモードから命令モードへの転換を指示するモード転換命令MCCを有する命令パケット101をパケットPACに含めてディスプレイドライバーIC200Aに伝送する。ディスプレイドライバーIC200Aは、命令パケット101を受信する(ステップS50)。モード転換命令MCCは、モード転換の1フレーム前又は数フレーム前にディスプレイドライバーIC200Aに伝送される。

【0063】

命令デコーダ220は、命令パケット101に含まれるビット、例えば‘00’をデコーディングし、該デコーディング結果によって、複数の制御信号SW1、SW2、SEL1、及びSEL2を生成する。

【0064】

この際、オーバーラップ区間INT2の間に、復元データDATAは、第1スイッチ回路211と第1選択回路219とを通じてディスプレイ300にバイパスされると同時に、第2スイッチ回路213を通じてフレームメモリ215に書き込まれる。この際、復元データDATAと共に、各同期信号Vsync、Hsyncは、ディスプレイ300に伝送される。従って、ディスプレイ300は、各同期信号Vsync、Hsyncを用いて、復元データDATAを表示する。

【0065】

モード転換命令MCCを受信した後、制御回路230は、垂直同期信号Vsyncの最後のパルスLPを受信した後に第1カウント値を用いて、垂直同期信号Vsyncの周期T1と同じ周期T1を有する内部垂直同期信号IVsyncを生成する。また、制御回路230は、内部垂直同期信号IVsyncと第2カウント値とを用いて、水平同期信号の周期T2と同じ周期T2を有する内部水平同期信号IHsyncを生成する(ステップS60)。

【0066】

図5に示したように、垂直同期信号Vsyncの最後のパルスLPと内部垂直同期信号IVsyncの最初のパルスFPとの時間間隔T1は、垂直同期信号Vsyncの周期T1と同一である。即ち、ビデオモードから命令モードに転換時、ディスプレイドライバーIC200Aは、垂直同期信号Vsyncに連続する内部垂直同期信号IVsyncを発生するので、ディスプレイ300で発生する映像フリッカー現象を防止することができる。

【0067】

命令デコーダ220は、第2選択信号SEL2の発生時点を調節することによって、垂直同期信号Vsyncの最後のパルスLPと内部垂直同期信号IVsyncの最初のパルスFPとの時間間隔T1が垂直同期信号Vsyncの周期T1と同一になるように、第2選択回路240を制御する。

【0068】

第1〜第3選択回路219、240、及び250は、各選択信号SEL1及びSEL2によって、復元データDATAと各内部同期信号IVsync、IHsyncとをディスプレイ300に伝送する(ステップS70)。従って、第2区間INT3から、ディスプレイドライバーIC200Aは、命令モードを行う。この際、第2区間INT3から、ホスト100は、ホスト100で消耗する電力を減らすために、垂直同期パケットVSと水平同期パケットHSとをディスプレイドライバーIC200Aに伝送せず、データストリームパケットDSのみを伝送する。従って、ディスプレイドライバーIC200Aは、垂直同期信号Vsyncと水平同期信号Hsyncを生成しない。ディスプレイドライバーIC200Aは、復元データDATAを、フレームメモリ215を通じてディスプレイ300に伝送する。

【0069】

図6は、図3に示した制御回路の一例を示すブロック図である。図3、図5、及び図6を参照すると、制御回路230は、垂直同期信号周期カウンター231−1、内部垂直同期信号生成器231−2、水平同期信号周期カウンター232−1、内部水平同期信号生成器232−2、オシレーター233、誤差計算器234、TE制御信号生成器235、制御値レジスタ236、及び誤差情報レジスタ237を含む。

【0070】

垂直同期信号周期カウンター231−1は、クロック信号CLK1を用いて垂直同期信号Vsyncの周期T1をカウントし、第1カウント値CNT1を生成する。内部垂直同期信号生成器231−2は、第1カウント値CNT1とオシレーター233から出力されたオシレーション信号OSCを用いて、垂直同期信号Vsyncの周期T1と同じ周期T1を有する内部垂直同期信号IVsyncを生成する。

【0071】

水平同期信号周期カウンター232−1は、クロック信号CLK1を用いて水平同期信号Hsyncの周期T2をカウントし、第2カウント値CNT2を生成する。内部水平同期信号生成器232−2は、第2カウント値CNT2とオシレーター233から出力されたオシレーション信号OSCを用いて、水平同期信号Hsyncの周期T2と同じ周期T2を有する内部水平同期信号IHsyncを生成する。

【0072】

内部垂直及び水平同期信号生成器231−2、232−2は、イネーブル信号ENに応答して、各内部同期信号IVsync、IHsyncの生成タイミング又は出力タイミングを制御する。

【0073】

一実施形態として、垂直及び水平同期信号周期カウンター231−1、232−1は、各同期信号Vsync、Hsyncの最後のパルスを検出し、該検出結果によって、内部垂直及び水平同期信号生成器231−2、232−2の動作を制御する各制御信号を出力する。この場合、垂直及び水平同期信号周期カウンター231−1、232−1は、最後のパルス検出器の機能を行う。

【0074】

誤差計算器234は、垂直同期信号Vsyncの周期T1と内部垂直同期信号IVsyncの周期との差を計算して第1誤差値を生成し、水平同期信号Hsyncの周期T2と内部水平同期信号IHsyncの周期との差を計算して第2誤差値を生成し、第1誤差値と第2誤差値のそれぞれを誤差情報レジスタ237に保存する。例えば、誤差計算器234は、クロック信号に基づいて、第1誤差値と第2誤差値のそれぞれを計算する。

【0075】

誤差情報レジスタ237に保存された第1誤差値と第2誤差値のそれぞれは、ホスト100によってアクセス可能である。理論的には、垂直同期信号Vsyncの周期と同じ周期を有する内部垂直同期信号IVsyncを生成することができるが、実際の具現例では、垂直同期信号Vsyncの周期と内部垂直同期信号IVsyncの周期との間には誤差が発生することがある。

【0076】

同様に、水平同期信号Hsyncの周期と同じ周期を有する内部水平同期信号IHsyncを生成することができるが、実際の具現例では、水平同期信号Vsyncの周期と内部垂直同期信号IVsyncの周期との間には誤差が発生することがある。

【0077】

TE制御信号生成器235は、誤差計算器234から提供された第1誤差値によって、TE制御信号TEの生成タイミングを制御する。

【0078】

制御値レジスタ236は、ホスト100から出力された制御値TEVを保存する。この際、誤差計算器234は、制御値TEVを受信して解析し、該解析結果によって、TE制御信号生成器235の動作を制御する。従って、TE制御信号生成器235は、制御値TEVを用いてTE制御信号TEの発生タイミングを制御することができる。

【0079】

図7は、本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するフローチャートであり、図8は、本発明の一実施形態によるティアリング効果制御信号の発生タイミングを制御する方法を説明するタイミング図である。

【0080】

ディスプレイドライバーIC200Aが、TE制御信号TEの発生時点を制御する方法とディスプレイドライバーIC200Aの動作モードが、モード転換命令(図2の103参照)によって、ビデオモードから命令モードに転換される手順を、図2、図3、図6、図7、及び図8を参照して説明すると、次の通りである。

【0081】

モード転換時点で、各内部同期信号IVsync、IHsyncから各同期信号Vsync、Hsyncへのハンドオーバーが正確に行われると、ディスプレイ300で映像フリッカーが発生しない。もし、第2TE制御信号TE2がホスト100に伝送されると、ホスト100は、第2TE制御信号TE2によって、垂直同期信号Vsyncに関連する垂直同期パケットVSを生成する。従って、垂直同期信号VsyncのパルスP2は、第1時点T1ではなく第2時点T2で生成される。即ち、垂直同期信号Vsyncが遅延時間TDほど遅延されて発生すると、ディスプレイ300で映像フリッカーが発生する。従って、第2TE制御信号TE2の生成タイミングを調節する必要がある。

【0082】

誤差計算器234は、垂直同期信号Vsyncの周期と内部垂直同期信号IVsyncの周期との差である第1誤差値を計算し、これを誤差情報レジスタ237に保存する(ステップS110)。誤差計算器234は、誤差情報レジスタ237に保存された第1誤差値によって、TE制御信号TEの生成タイミングを制御する制御信号をTE制御信号生成器235に伝送する(ステップS120)。

【0083】

TE制御信号生成器235は、制御信号によって生成された第1TE制御信号TE1をホスト100に伝送する(ステップS130)。ホスト100は、第1TE制御信号TE1によって、第1時点T1で生成された垂直同期信号VsyncのパルスP1に関連する垂直同期パケットVSを生成する。

【0084】

第1時点T1を基準に、内部垂直同期信号IVsyncから垂直同期信号Vsyncへのハンドオーバーが正確に行われるので、ディスプレイ300では、映像フリッカーが発生しない。即ち、垂直同期信号Vsyncの最初のパルスP1が、第2時点T2ではない第1時点T1で生成される。

【0085】

図9は、図1に示したホストの一例を示す内部ブロック図であり、図10は、図9に示したホストの同期パケット発生タイミングを制御する方法を説明するフローチャートである。図1、図9、及び図10を参照すると、一実施形態として、ホスト100は、制御ロジック110と同期パケット生成器120とを含む。他の実施形態として、ホスト100は、制御ロジック110と制御値調節ロジック130とを含み得る。更に他の実施形態として、ホスト100は、制御ロジック110、同期パケット生成器120、及び制御値調節ロジック130を含み得る。

【0086】

ディスプレイドライバーIC200Aの動作モードが、モード転換命令(図2の103参照)によって命令モードからビデオモードに転換される手順を、図1、図2、図8、図9、及び図10を参照して説明すると、次の通りである。

【0087】

上述したように、モード転換時点で各内部同期信号IVsync、IHsyncから各同期信号Vsync、Hsyncへのハンドオーバーが正確に行われると、ディスプレイ300では、映像フリッカーが発生しない。

【0088】

モード転換命令(図2の103参照)を含むパケットPACがディスプレイドライバーIC200Aに伝送された後、制御ロジック110は、ディスプレイドライバーIC200Aから出力されたTE制御信号TEと誤差情報EIとを受信し(ステップS210)、TE制御信号TEと誤差情報EIとを用いて、同期パケットの生成タイミングを調節するための制御信号を同期パケット生成器120に出力する。

【0089】

TE制御信号TEの立ち上りエッジによって、垂直同期信号Vsyncの最初のパルスFPの立ち上りエッジのタイミングが決定されるので、制御ロジック110は、TE制御信号TEと誤差情報EIとを用いて、第1時点T1で垂直同期信号Vsyncの最初のパルスP1の立ち上りエッジが生成されるように制御信号を同期パケット生成器120に出力する。従って、同期パケット生成器120は、制御信号に応答して、第1時点T1で垂直同期信号Vsyncの最初のパルスP1の立ち上りエッジが生成されるように垂直同期パケットVSを生成し、該生成された垂直同期パケットVSをディスプレイドライバーIC200Aに伝送する。

【0090】

即ち、同期パケット生成器120は、制御信号によって、各同期パケットVS、HSの生成タイミング又は出力タイミングを調節する(ステップS220)。これにより、同期パケット生成器120は、生成された各同期パケットVS、HSを含むパケットPACをディスプレイドライバーIC200Aに伝送する(ステップS230)。

【0091】

図11は、図9に示したホストのティアリング効果制御信号の発生タイミングを調節するための制御値を生成する方法を説明するフローチャートである。ディスプレイドライバーIC200Aの動作モードが、モード転換命令(図2の103参照)によって命令モードからビデオモードに転換される手順を、図1、図2、図8、図9、及び図11を参照して説明すると、次の通りである。

【0092】

モード転換時点で、各内部同期信号IVsync、IHsyncから各同期信号Vsync、Hsyncへのハンドオーバーが正確に行われると、ディスプレイ300では、映像フリッカーが発生しない。モード転換命令(図2の103参照)を含むパケットPACがディスプレイドライバーIC200Aに伝送された後、制御ロジック110は、ディスプレイドライバーIC200Aから出力された誤差情報EIを受信し(ステップS310)、誤差情報EIを制御値調節ロジック130に出力する。

【0093】

制御値調節ロジック130は、誤差情報EIに基づいて、TE制御信号の発生タイミングを制御するための制御値TEVを生成し(ステップS320)、該生成された制御値TEVをディスプレイドライバーIC200Aの制御値レジスタ236に伝送する(ステップS330)。従って、TE制御信号生成器235は、制御値レジスタ236に保存された制御値TEVによって、TE制御信号TEを生成することができる。

【0094】

図12は、本発明の他の実施形態による映像信号処理システムのブロック図である。映像信号処理システム10Bは、ホスト100、ディスプレイドライバーIC200B、及びディスプレイ300を含む。

【0095】

ホスト100は、データDATAと命令CMD、垂直同期信号Vsync、水平同期信号Hsync、及び制御値TEVをディスプレイドライバーIC200Bに伝送する。ディスプレイドライバーIC200Bは、TE制御信号TE及び/又は誤差情報EIをホスト100に伝送する。

【0096】

ディスプレイドライバーIC200Bは、動作モード、例えばビデオモードによって、データDATA、垂直同期信号Vsync、及び水平同期信号Hsyncをディスプレイ300に伝送する。また、ディスプレイドライバーIC200Bは、動作モード、例えば命令モードによって、データDATA、内部垂直同期信号IVsync、及び内部水平同期信号IHsyncをディスプレイ300に伝送する。

【0097】

図13は、図12に示したディスプレイドライバーの一例を示すブロック図である。

【0098】

図3と図13とを参照すると、データ/同期デコーダ210を除くと、図13に示したディスプレイドライバーIC200Bの構造と動作は、図3に示したディスプレイドライバーIC200Aの構造と動作と実質的に同一である。

【0099】

図14は、図12に示したディスプレイドライバーの動作を説明するフローチャートである。図2、図6、図12、図13、及び図14を参照すると、制御回路230は、各同期信号Vsync、Hsyncの周期をカウントし、各カウント値CNT1、CNT2を生成する(ステップS410)。

【0100】

命令デコーダ220は、モード転換命令、例えばディスプレイドライバーIC200Bの動作モードをビデオモードから命令モードに変換するためのモード転換命令を含む命令パケット101を受信する(ステップS420)。

【0101】

上述したように、制御回路230は、各カウント値CNT1、CNT2を用いて、各同期信号Vsync、Hsyncの周期と同じ周期を有する各内部同期信号IVsync、IHsyncを生成する(ステップS430)。命令モードで作動するディスプレイドライバーIC200Bは、データDATAと各内部同期信号IVsync、IHsyncとをディスプレイドライバー300に伝送する(ステップS440)。ビデオモードで作動するディスプレイドライバーIC200Bは、データDATAと各同期信号Vsync、Hsyncとをディスプレイドライバー300に伝送する。

【0102】

一実施形態として、制御値TEVと誤差情報EIは、ホスト100又はディスプレイドライバーIC200A、200Bに具現された不揮発性メモリに保存される。従って、ホスト100又はディスプレイドライバーIC200A、200Bの初期化動作時に、不揮発性メモリに保存された各情報TEV、EIは、制御値及び誤差情報レジスタ236、237にロードされる。他の実施形態として、制御値TEVと誤差情報EIは、リアルタイムで毎フレーム毎にアップデートされ得る。

【0103】

本発明によるディスプレイドライバーは、動作途中で、モード転換命令によってビデオモードと命令モードとの間でモード転換を行うことができる。従って、ディスプレイドライバーで消耗する電力を効果的に減らすことができる効果がある。

【0104】

図15は、本発明の更に他の実施形態による映像信号処理システムのブロック図である。図15を参照すると、映像信号処理システム10Cは、静止映像信号又は動画信号をディスプレイ3000で表示することができる携帯電話、スマートフォン、タブレットPC、PDA、又はPMPのような移動型の装置、小型機器又は小型コンピュータを意味する。

【0105】

映像信号処理システム10Cは、アプリケーションホストプロセッサ1000、ディスプレイドライバーIC2000、及びディスプレイ3000を含む。

【0106】

ホスト1000は、ホスト1000内に具現されたコーデックの実行によって、ディスプレイ3000で表示される映像信号が静止映像信号又は動画信号であるか否かを指示するモード転換命令を含む映像信号DATAをディスプレイドライバーIC2000に伝送する。モード転換命令は、ディスプレイドライバーIC2000の動作モードを制御する制御信号である。

【0107】

モード転換命令を含む映像信号DATAは、クロック信号CLKに応答して、ディスプレイドライバーIC2000に伝送される。

【0108】

ホスト1000は、ディスプレイドライバーIC2000から出力されたTE制御信号TEを受信し、該受信したTE制御信号TEのレベルによって、映像信号DATAの伝送タイミングを制御する。ここで、TE制御信号TEは、ティアリング又はスクリーンティアリングを防止するための制御信号である。

【0109】

ディスプレイドライバーIC2000は、ホスト1000から出力されたモード転換命令によって、ディスプレイドライバーIC2000内に具現された静止映像信号を処理するインターフェースと動画信号を処理するインターフェースとのうちの何れか1つを選択し、ホスト1000から出力された映像信号DATA、例えば静止映像信号又は動画信号を、選択されたインターフェースを通じて出力映像信号DDATAとしてディスプレイ3000に伝送する。

【0110】

ディスプレイ3000は、ディスプレイドライバーIC2000から出力された出力映像信号DDATAを表示する。例えば、ディスプレイ3000は、LCD、LEDディスプレイ、OLEDディスプレイ、又はAMOLEDディスプレイとして具現可能である。

【0111】

図16は、図15に示したアプリケーションホストプロセッサの一例を示す概略的なブロック図である。図16に示した点線は、命令(instruction)実行経路を表わす。図16を参照すると、ホスト1000は、RF受信器1110、DRAM(Dynamic Random Access Memory)1114のような揮発性メモリ、NANDフラッシュメモリ1116のような不揮発性メモリ、フレームバッファ1118、コーデック1120、ディスプレイコントローラ1122、レジスタ1124を含むインターフェース1126、及びCPUコア1128を含む。

【0112】

ホスト1000の動作を全般的に制御するCPUコア1128は、DRAM1114、NANDフラッシュメモリ1116、フレームバッファ1118、コーデック1120、ディスプレイコントローラ1122、レジスタ1124、及びインターフェース1126の各構成要素の動作を制御し、実行コードCODEを実行する。

【0113】

ユーザが動画信号MIをディスプレイ3000から再生しようとする際、例えば、実行コードCODEによってコーデック1120が実行されると、CPUコア1128は、コーデック1120の実行を感知し、該感知結果によって、モード転換命令MCC[1:0]を生成し、該生成されたモード転換命令MCC[1:0]をレジスタ1124に伝送する。

【0114】

例えば、動画信号MIの再生に関連するイベントが発生すると、実行コードCODEのメイン関数内で、イベントに関連するイベント処理関数が呼び出され、イベント処理関数がコーデック1120を呼び出すと、CPUコア1128は、実行コードCODEの実行及び/又は呼び出しによって、ディスプレイ3000で表示される映像信号が動画信号MIであることを判断する。

【0115】

例えば、モード転換命令MCC[1:0]が2ビットである場合、ディスプレイドライバーIC2000の動作モードは、表2のようである。即ち、ディスプレイドライバーIC2000は、モード転換命令MCC[1:0]によって、静止映像信号を処理する命令モードと動画信号を処理するビデオモードとの間でスイッチング動作を行う。ここで、ブリッジモード(bridge mode)は、ディスプレイドライバーIC2000の動作モードが命令モードからビデオモードにスイッチングされる際に、内部スキャン動作によってフレームメモリ(GRAM)2204−3(図19参照)のダミー映像信号がディスプレイ3000に出力されることを防止するためのモードである。

【0116】

【表2】

【0117】

各モードによるディスプレイドライバーIC2000の動作は、後に関連図面を参照して詳しく説明する。

【0118】

また、ユーザが静止映像信号SIをディスプレイ3000で再生しようとする際、例えば実行コードCODEによってコーデック1120の実行が終了すると、又はコーデック1120が実行されない場合、CPUコア1128は、コーデック1120の実行の終了又はコーデック1120が実行されないことを感知し、該感知結果によって、モード転換命令MCC[1:0]を生成し、該生成されたモード転換命令MCC[1:0]をレジスタ1124に伝送する。

【0119】

例えば、静止映像信号SIをディスプレイ3000で表示するために、実行中であるコーデック1120が終了イベントによって終了し、コーデック1120を実行するために、呼び出されたイベント処理関数がメイン関数でリターンされると、CPUコア1128は、リターンを検出し、ディスプレイ3000で表示される映像信号が静止映像信号SIであることを判断する。

【0120】

実行コードの例は、次の通りである。

【0121】

【0122】

RF受信器1110は、インターネット又はDMB(Digital Multimedia Broadcasting)を通じて映像信号、例えば静止映像信号SI又は動画信号MIを受信し、該受信した映像信号をDRAM1114及び/又はNANDフラッシュメモリ1116に保存する。

【0123】

ホスト1000がブーティングされると、NANDフラッシュメモリ1116に保存された実行コードCODEはDRAM1114にロードされ、DRAM1114にロードされた実行コードCODEは順次に実行される。一実施形態として、NANDフラッシュメモリ1116に保存された実行コードCODEは、CPUコア1128の制御によって、リアルタイムでDRAM1114にロードされる。

【0124】

NANDフラッシュメモリ1116は、静止映像信号、動画信号、ゲームプログラム、開始プログラム、例えば実行コード及び/又はアプリケーションを保存する。例えば、NANDフラッシュメモリ1116に保存された静止映像信号、動画信号、ゲームプログラム、開始プログラム、例えば実行コード及び/又はアプリケーションは、CPUコア1128の制御によって、DRAM1114にロードされる。

【0125】

フレームバッファ1118は、DRAM1114から出力された静止映像信号SI又はコーデック120から出力された動画信号MIを受信して保存する。例えば、静止映像信号SIをディスプレイ3000で表示しようとする際に、DRAM1114に保存された静止映像信号SIは、直ちにフレームバッファ1118に伝送される。しかし、動画信号MIをディスプレイ3000で表示しようとする際に、DRAM1114に保存された動画信号MIは、コーデック1120によって処理された後、フレームバッファ1118に伝送される。

【0126】

コーデック1120は、データストリーム又は信号をエンコーディング及び/又はデコーディングするハードウェア又はコンピュータプログラムである。例えば、コーデック1120は、DRAM1114から出力された動画信号MIをデコーディングし、該デコードされた動画信号をフレームバッファ1118に伝送する。

【0127】

ディスプレイコントローラ1122は、フレームバッファ1118から出力された静止映像信号SI又は動画信号MIをインターフェース1126に伝送することを制御する。

【0128】

インターフェース1126は、クロック信号CLK、及び映像信号DATA、例えば静止映像信号又は動画信号をディスプレイドライバーIC2000に伝送する。

【0129】

ディスプレイコントローラ1122の制御によって、インターフェース1126は、静止映像信号を命令モードに適した静止映像信号に変換して出力し、動画信号をビデオモードに適した動画信号に変換して出力する。

【0130】

一実施形態として、インターフェース1126は、レジスタ1124に保存されたモード転換命令MCC[1:0]を参照して、静止映像信号を命令モードに適した静止映像信号に変換して出力し、動画信号をビデオモードに適した動画信号に変換して出力する。ここで、命令モードは、静止映像信号を処理するためのモードであり、ビデオモードは、動画信号を処理するためのモードである。

【0131】

インターフェース1126は、ディスプレイドライバーIC2000から伝送されたTE制御信号TEをCPUコア1128に伝送する。

【0132】

TE制御信号TEに応答して、CPUコア1128は、後述する図22、図24、図27、又は図30に示すように、モード転換命令MCC[1:0]の発生タイミング及び/又は映像信号DATAの伝送タイミングを制御するために、インターフェース1126の動作を制御する。

【0133】

図17は、図16に示したアプリケーションホストプロセッサの動作を説明するフローチャートであり、図18は、図16に示したアプリケーションホストプロセッサから出力されるモード転換命令を含む映像信号及びクロック信号の波形図である。

【0134】

ホスト1000の動作は、図15〜図18を参照して詳しく説明する。

【0135】

第1に、動画信号がディスプレイ3000で再生された後に終了する場合、即ち場合1CASE1を説明すると、動画信号MIをディスプレイ3000で再生するために、コーデック1120が実行されると(ステップS1011)、CPUコア1128は、コーデック1120の実行を感知し、該感知結果によって、ビデオモードに進入する(ステップS1012)。

【0136】

ホスト1000の動作モードがビデオモードに進入することを感知したCPUコア1128は、ディスプレイドライバーIC2000がビデオモードを行うように、モード転換命令MCC[1:0]=10を生成し、該生成されたモード転換命令MCC[1:0]=10をレジスタ1124に伝送する(ステップS1014)。ディスプレイコントローラ1122は、フレームバッファ1118から出力された動画信号MIをインターフェース1126に伝送する。この際、インターフェース1126は、レジスタ1124に保存されたモード転換命令MCC[1:0]=10を参照して、ビデオモードに適した動画信号DATAをディスプレイドライバーIC2000に伝送する(ステップS1016)。

【0137】