デイジタル信号デスクランブル用デコーダアダプタ

【目的】 スクランブルの施されたディジタル信号伝送信号を受信機に前置されたデコーダアダプタで効率よくデスクランブルする。

【構成】 スクランブルの施された入力信号をデスクランブルし、アダプタの入力信号と同じ信号形式のスクランブルの解かれた出力信号を再構成して受信機に印加するデスクランブル用デコーダアダプタであって、プリデコーダ回路(1,2)によって誤り訂正符号の前までデコードされた信号と、デスクランブルのための擬似乱数信号(21)を誤り訂正符号化回路(13)によって符号化した信号とを、加算回路(23)によって加算したのち、ポストエンコーダ(12)で再びエンコードするよう構成している。

【構成】 スクランブルの施された入力信号をデスクランブルし、アダプタの入力信号と同じ信号形式のスクランブルの解かれた出力信号を再構成して受信機に印加するデスクランブル用デコーダアダプタであって、プリデコーダ回路(1,2)によって誤り訂正符号の前までデコードされた信号と、デスクランブルのための擬似乱数信号(21)を誤り訂正符号化回路(13)によって符号化した信号とを、加算回路(23)によって加算したのち、ポストエンコーダ(12)で再びエンコードするよう構成している。

【発明の詳細な説明】

【0001】

【産業上の利用分野】この発明は、衛星テレビジョン放送または高精細度テレビジョン放送などの受信機に接続し、ディジタル信号のスクランブルを解除するためのデスクランブル用デコーダアダプタであって、このアダプタの出力信号をこのアダプタの入力信号と同一の信号形式に再構成する機能を有するアダプタに係り、特にディジタル音声信号処理技術に関するものである。

【0002】

【従来の技術】日本における高精細度テレビジョン放送方式には、MUSE(Multiple Sub-Nyquist Sampling Encoding)伝送方式が採用されている。この方式は高精細度信号の故に拡大する伝送帯域を極力圧縮し、しかも受信側に高精細度情報をそこなうことなく伝送できる方式である。その映像は動き補正型サブサンプル時分割多重の帯域圧縮形態を有し、音声は映像信号の垂直帰線期間に時分割多重されたディジタル信号形態を有している。なお、MUSE方式の詳細については、文献、二宮他:MUSE方式の開発,NHK 技術研究,Vol. 39, No.2,pp. 18−53, 1987を参照されたい。

【0003】高精細度テレビジョン放送は、将来的にはスクランブルを施した有料放送として実施される可能性が高い。このため高精細度テレビジョン放送方式は、MUSE方式による伝送方式と併せて、スクランブル方式(有料方式)についても規格化されている。しかしながら、当初はスクランブルを施さない実験放送が行なわれているのみであったため、市販されているデコーダはデススクランブル機能を持っていないものである。将来スクランブルを施した有料放送が実施されたときに、こうしたデスクランブル機能を持たないデコーダもデスクランブル用のアダプタを付加して利用できることが望ましい。本発明のアダプタはかかる要望にそうためのものである。

【0004】さて高精細度テレビジョン放送の受信機に接続しスクランブルを解除するためのデスクランブル用デコーダアダプタであって、アダプタの出力信号をアダプタの入力信号と同じ信号形式に再構成する機能を有したデスクランブル用デコーダアダプタにおける、音声信号処理技術については、本願人が先に出願した特願平2−105216号「音声デスクランブル用デコーダアダプタ」がある。前記特願平に述べられており、本願発明にとっては従来技術となるアダプタの構成は、その明細書の第6図および第1図に示されている。これら従来技術の構成を、本願発明ではその図4および図5に整理のうえ再掲する。

【0005】図4図示の構成においては、アダプタへの入力信号は、まず同期・制御符号検出回路1、フレーム内デインタリーブ回路2、誤り訂正符号復号回路3によってプリデコードされる。つぎに、排他的論理和回路22で、擬似乱数信号発生回路21からの擬似乱数信号が加算されデスクランブルが行われる。さらに、誤り訂正符号化回路13、フレーム内インタリーブ回路12、同期・制御符号付加回路11によってポストエンコードされ、入力信号と同じ形式の出力信号が得られる。

【0006】この際、誤り訂正符号復号回路3では、訂正不可能な誤りが検出された場合、入力信号をそのまま出力している。また、同期・制御符号付加回路11では、正しい同期・制御符号を生成して付加する。

【0007】図5図示の構成においては、アダプタへの入力信号は、まず同期・制御符号検出回路1、フレーム内デインタリーブ回路2、誤り訂正符号復号回路3によってプリデコードされる。つぎに、排他的論理和回路22で、擬似乱数信号発生回路21からの擬似乱数信号が加算されデスクランブルが行われる。さらに、誤り訂正符号化回路13、フレーム内インタリーブ回路12、同期・制御符号付加回路11によってポストエンコードされる。

【0008】この際、誤り訂正符号復号回路3で訂正不可能な誤りを検出した場合、誤り信号発生回路31で擬似的な誤り信号を発生させ、排他的論理和回路23で信号に加算する。また、同期・制御符号付加回路11では、同期・制御符号検出回路1で抜き採られた同期・制御符号を再付加する。なお、遅延回路32および33は、擬似的な誤り信号あるいは同期・制御信号の付加のタイミングを合わせるためのものである。

【0009】なお、構成図面に「誤り訂正符号復号回路」とあるは「誤り検出訂正回路」とも称せられるべきもので、正味のディジタル情報例えば音声情報に付加されたパリディビットや冗長ビットを使用して伝送中のビット誤りを検出しこれを訂正する機能を有する回路で、この回路の出力からは誤り検出訂正されたディジタル情報が出力される。一方「誤り訂正符号化回路」とは正味のディジタル情報に誤り検出訂正用のパリティビットや冗長ビットを付加する機能を有する回路を意味するものである。

【0010】また、「フレーム内インタリーブ回路」、「フレーム内デインタリーブ回路」とあるは、衛星テレビジョン放送あるいは高精細度テレビジョン放送をこの場合の例として採用したために生じた回路ブロックで、ここでいうフレームとはテレビジョン映像信号のフレームとは別のもので、ディジタル音声信号の一つの処理単位を表わすものである。つまり、衛星テレビジョン放送では2048ビット分1ミリ秒、高精細度テレビジョン放送では1350ビット分1ミリ秒の単位を表す。伝送によりディジタル音声信号にまとまった誤りが生じても、その誤りを分散させてその影響を軽減させるため、また誤り訂正を効果的に行うため、ディジタル信号をフレーム内で並べ替えて伝送し受信側でこれを元に戻す技術を使用している。この並べ変え回路が「フレーム内インターリーブ回路」、元に戻す回路が「フレーム内デインタリーブ回路」であり、これを使用するかしないかは後に述べる本発明の本質には関係がない。さらに高精細度テレビジョン放送では、フレーム間に及ぶ信号の並べ替えも行っており、この場合には後述の「フレーム間インタリーブ回路」、「フレーム間デインタリーブ回路」が使用される。

【0011】説明のついでに述べれば、後述の構成図に出てくる「時間軸伸長回路」、「時間軸圧縮回路」、「3値2値変換回路」、「2値3値変換回路」などの回路ブロックも高精細度テレビジョン放送方式特有のもので、詳細な説明は省略するがこれらも使用するかしないかは本発明の本質には関係しない。

【0012】

【発明が解決しようとする課題】図4図示従来構成のアダプタにおいては、デスクランブル後に改めて誤り訂正符号化を行い、また同期・制御符号も誤りの無いものを再付加しているので、見かけ上出力信号には全く誤りを含まない、すなわち、この構成のデスクランブル用デコーダアダプタの出力に接続された受信機にとっては、常に誤りの無い信号を受信しているように見える。つまり、その受信機は、決して誤り処理機能を動作させることはない。

【0013】伝送路でビット誤りが生じているような場合において、誤り訂正符号復号回路で訂正不可能な誤りが検出されたとしても、その情報はそこで途切れ、出力に接続された受信機に伝わることはない。つまり、その受信機が、訂正不可能な誤りを検出したとき音声信号を補間する機能を備えていたとしても、その機能を発揮させることはできない。

【0014】このように、伝送路に誤りが生じる可能性がある場合には、上述のデスクランブル用デコーダアダプタを接続された受信機はその機能を十分発揮できない。

【0015】図5図示の従来構成のアダプタは、この問題点を解決する一技術を提供するものであるが、本願発明も同じくこの問題点を解決する別構成のアダプタを提供しようとするものである。

【0016】

【課題を解決するための手段】前述の問題点を解決するためのディジタル信号デスクランブル用デコーダアダプタの第1の発明はすなわち、誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、

【0017】前記入力信号を前記誤り訂正符号の復号を行う前の状態の信号にデコードするプリデコーダ回路と、前記誤り訂正符号の符号化を行った後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、2を法とする加算回路とを具備し、

【0018】前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするものである。

【0019】また、ディジタル信号デスクランブル用デコーダアダプタの第2の発明は、誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、

【0020】前記入力信号をフレーム内デインタリーブ処理を行う前の状態の信号にデコードするプリデコーダ回路と、フレーム内インタリーブ処理を行った後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、フレーム内インタリーブ回路と、2を法とする加算回路とを具備し、

【0021】前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化しさらにフレーム内インタリーブ処理した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするものである。

【0022】

【実施例】以下添付図面を参照し実施例により本発明を詳細に説明する。図1にデスクランブル用デコーダアダプタ第1の発明の基本的な構成例を示す。

【0023】図1の構成例において、入力信号はまず同期・制御符号検出回路1、フレーム内デインタリーブ回路2によってプリデコードされる。一方、擬似乱数信号発生回路21で発生された擬似乱数信号は、誤り訂正符号化回路13で予め符号化されたうえで、前記プリデコードされた信号に加算されデスクランブルが行われる。さらにフレーム内インタリーブ回路12によってポストエンコードされ出力信号となる。

【0024】ここで、同期・制御符号検出回路1は、同期の確立・制御符号のデコードを行いデスクランブル用デコーダアダプタの各回路を制御する働きをし、信号そのものはそのまま通過させる。また、フレーム内デインタリーブ回路2およびフレーム内インタリーブ回路12は、同期・制御符号を含めてフレームに属する全てのビットを処理の対象とする。従って、同期・制御符号は元のまま残っており、改めて付加する必要はない。

【0025】つぎに、図1図示構成における、デスクランブル動作を説明する。このとき送信側では、誤り訂正符号化前に擬似乱数信号加算方式によりスクランブルが施されていること、その誤り訂正符号は線形符号であることを仮定する。

【0026】スクランブルを施された信号の列を表わすベクトルsi は、スクランブルを施す前のクリアな信号ci 、スクランブルのための擬似乱数信号pi として、次のように表される。

si =ci + pi

【0027】このsi をエンコードしたものが、送出信号sとなる。誤り訂正符号の生成行列をG、フレーム内インタリーブによる置換を表わす行列をPとすれば送出信号sは次のように表される。

s=P・G・si =P・G・(ci + pi )

【0028】図1図示デスクランブル用デコーダアダプタの入力信号iは、この送出信号sに伝送誤りeが加算されたものとなる。

i=s+ e

【0029】デスクランブル用デコーダアダプタでは、フレーム内デインタリーブ回路2でプリエンコードしたのち、排他的論理和回路23で誤り訂正符号化回路13の出力pを加算して、さらにフレーム内インタリーブ回路12でポストエンコードして出力信号oを得る。

o=P・(P-1・i+ p)

【0030】上記pは、擬似乱数信号発生回路21で発生された前記pi と等しい信号が、誤り訂正符号化回路13で符号化されたものである。

p=G・pi

【0031】以上を整理すると、o=P・P-1・i+ P・p=i+ P・p=s+ e+ P・p=P・G・(ci + pi ) + e+ P・G・pi =P・G・ci + P・G・pi + e+ P・G・pi =P・G・ci + e

【0032】ここで、P・G・ci はスクランブルを施されていないクリアな信号をエンコードしたものに他ならない。従って、このデスクランブルアダプタの出力に接続された受信機は、伝送誤りの影響を含めて、クリアな信号を受信しているのと等価である。なお、式中大文字P,Gは行列表示を表わし、小文字si , p i , c i , s,p,i,o,eはベクトルを表わすものとする。

【0033】衛星テレビジョン放送または高精細度テレビジョン放送の音声デスクランブル用デコーダアダプタでは、ビットストリームの形式で入出力する場合、この図1の構成が用いられる。

【0034】高精細度テレビジョン放送の音声デスクランブル用デコーダアダプタで、MUSE信号形式で入出力する場合には、図2図示のような構成となる。図1の構成に、プリデコーダ部分としてMUSE信号から1.35MHz ビットストリーム信号に変換する部分を、ポストエンコーダ部分として1.35MHz ビットストリーム信号からMUSE信号に変換する部分を、それぞれ加えた構成である。

【0035】図2の構成において、回路ブロック4,5,6,7,8,1,2はそれぞれ音声信号分離回路、周波数変換回路、3値2値変換回路、時間軸伸長回路、フレーム間デインタリーブ回路、同期・制御符号検出回路、フレーム内デインタリーブ回路を表しここまでが本発明でいうプリデコーダ回路である。またブロック12,18, 17, 16, 15, 14はそれぞれフレーム内インタリーブ回路、フレーム間インタリーブ回路、時間軸圧縮回路、2値3値変換回路、周波数変換回路、音声信号多重回路を表し、ブロック12から14までが本発明でいうポストエンコーダ回路である。すなわち本発明ではプリデコーダ回路、ポストエンコーダ回路の中味は本発明を適用する伝送方式によって当然異なり、本発明の従来例と異なる主たる部分は図1にも示した図2の擬似乱数信号発生回路21、誤り訂正符号化回路13と加算回路23の部分で、この部分は図4の従来例ではブロック3, 21, 22, 13に図5R>5の従来例ではブロック3,21, 22, 13, 32, 23, 33に対応している。

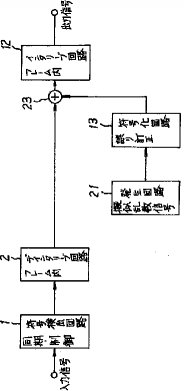

【0036】図3に、デスクランブル用デコーダアダプタ第2の発明の構成例を示す。

【0037】図3の構成においては、入力信号に、予めエンコードされた擬似乱数信号を加算し出力信号とする。予めエンコードされた擬似乱数信号とは、擬似乱数信号発生回路21で発生した擬似乱数信号を誤り訂正符号化回路13で符号化しフレーム内インタリーブ回路12でインタリーブして得られる信号である。

【0038】ここで、同期・制御符号検出回路1は、同期の確立・制御符号のデコードを行いデスクランブル用デコーダアダプタの各回路を制御する働きをし、信号そのものはそのまま通過させる。従って、同期・制御符号は元のまま残っており、改めて付加する必要はない。

【0039】以上本発明を実施例により詳細に説明してきたが、本発明はこれに限定されることなく、特許請求に記載した発明の要旨内で各種の変形変更の可能なことは明白であろう。すなわち本発明の実施例では入力信号としてディジタル音声を使用した場合について説明してきたが、これはディジタル信号として映像信号を使用した場合にも適用できるであろう。

【0040】

【発明の効果】図4に示された従来構成が、出力に接続された受信機の伝送誤り処理機能を発揮させることができなかったのに対し、図1図示構成によれば、前述のように入力信号に含まれる伝送誤りの情報は出力信号に伝搬するので、接続された受信機の伝送誤り処理機能をそのまま発揮させることができる。

【0041】この効果は、図3図示構成においても同様である。

【0042】図1の構成では、図4の構成に比較して誤り訂正符号復号回路および同期・制御符号付加回路の分だけ簡単化されている。また、図5の構成に比較して誤り訂正符号復号回路、同期・制御符号付加回路、誤り信号発生回路および2つの遅延回路の分だけ簡単化されている。

【0043】図3の構成では、図1の構成における簡単化に加え、さらにフレーム内デインタリーブ回路の分だけ簡単化することができる。

【図面の簡単な説明】

【図1】デスクランブル用デコーダアダプタ第1の発明の基本的な構成例を示す図。

【図2】本発明によるMUSE音声デスクランブル用デコーダアダプタの構成を示す図。

【図3】デスクランブル用デコーダアダプタ第2の発明の構成を示す図。

【図4】従来のデスクランブル用デコーダアダプタの構成を示す図。

【図5】従来のデスクランブル用デコーダの別の構成を示す図。

【符号の説明】

1 同期・制御符号検出回路

2 フレーム内デインタリーブ回路

3 誤り訂正符号復号回路

4 音声信号分離回路

5 周波数変換回路

6 3値2値変換回路

7 時間軸伸長回路

8 フレーム間デインタリーブ回路

11 同期・制御符号付加回路

12 フレーム内インタリーブ回路

13 誤り訂正符号化回路

14 音声信号多重回路

15 周波数変換回路

16 2値3値変換回路

17 時間軸圧縮回路

18 フレーム間インタリーブ回路

21 擬似乱数信号発生回路

22, 23, 24 加算回路

31 誤り信号発生回路

32, 33 遅延回路

【0001】

【産業上の利用分野】この発明は、衛星テレビジョン放送または高精細度テレビジョン放送などの受信機に接続し、ディジタル信号のスクランブルを解除するためのデスクランブル用デコーダアダプタであって、このアダプタの出力信号をこのアダプタの入力信号と同一の信号形式に再構成する機能を有するアダプタに係り、特にディジタル音声信号処理技術に関するものである。

【0002】

【従来の技術】日本における高精細度テレビジョン放送方式には、MUSE(Multiple Sub-Nyquist Sampling Encoding)伝送方式が採用されている。この方式は高精細度信号の故に拡大する伝送帯域を極力圧縮し、しかも受信側に高精細度情報をそこなうことなく伝送できる方式である。その映像は動き補正型サブサンプル時分割多重の帯域圧縮形態を有し、音声は映像信号の垂直帰線期間に時分割多重されたディジタル信号形態を有している。なお、MUSE方式の詳細については、文献、二宮他:MUSE方式の開発,NHK 技術研究,Vol. 39, No.2,pp. 18−53, 1987を参照されたい。

【0003】高精細度テレビジョン放送は、将来的にはスクランブルを施した有料放送として実施される可能性が高い。このため高精細度テレビジョン放送方式は、MUSE方式による伝送方式と併せて、スクランブル方式(有料方式)についても規格化されている。しかしながら、当初はスクランブルを施さない実験放送が行なわれているのみであったため、市販されているデコーダはデススクランブル機能を持っていないものである。将来スクランブルを施した有料放送が実施されたときに、こうしたデスクランブル機能を持たないデコーダもデスクランブル用のアダプタを付加して利用できることが望ましい。本発明のアダプタはかかる要望にそうためのものである。

【0004】さて高精細度テレビジョン放送の受信機に接続しスクランブルを解除するためのデスクランブル用デコーダアダプタであって、アダプタの出力信号をアダプタの入力信号と同じ信号形式に再構成する機能を有したデスクランブル用デコーダアダプタにおける、音声信号処理技術については、本願人が先に出願した特願平2−105216号「音声デスクランブル用デコーダアダプタ」がある。前記特願平に述べられており、本願発明にとっては従来技術となるアダプタの構成は、その明細書の第6図および第1図に示されている。これら従来技術の構成を、本願発明ではその図4および図5に整理のうえ再掲する。

【0005】図4図示の構成においては、アダプタへの入力信号は、まず同期・制御符号検出回路1、フレーム内デインタリーブ回路2、誤り訂正符号復号回路3によってプリデコードされる。つぎに、排他的論理和回路22で、擬似乱数信号発生回路21からの擬似乱数信号が加算されデスクランブルが行われる。さらに、誤り訂正符号化回路13、フレーム内インタリーブ回路12、同期・制御符号付加回路11によってポストエンコードされ、入力信号と同じ形式の出力信号が得られる。

【0006】この際、誤り訂正符号復号回路3では、訂正不可能な誤りが検出された場合、入力信号をそのまま出力している。また、同期・制御符号付加回路11では、正しい同期・制御符号を生成して付加する。

【0007】図5図示の構成においては、アダプタへの入力信号は、まず同期・制御符号検出回路1、フレーム内デインタリーブ回路2、誤り訂正符号復号回路3によってプリデコードされる。つぎに、排他的論理和回路22で、擬似乱数信号発生回路21からの擬似乱数信号が加算されデスクランブルが行われる。さらに、誤り訂正符号化回路13、フレーム内インタリーブ回路12、同期・制御符号付加回路11によってポストエンコードされる。

【0008】この際、誤り訂正符号復号回路3で訂正不可能な誤りを検出した場合、誤り信号発生回路31で擬似的な誤り信号を発生させ、排他的論理和回路23で信号に加算する。また、同期・制御符号付加回路11では、同期・制御符号検出回路1で抜き採られた同期・制御符号を再付加する。なお、遅延回路32および33は、擬似的な誤り信号あるいは同期・制御信号の付加のタイミングを合わせるためのものである。

【0009】なお、構成図面に「誤り訂正符号復号回路」とあるは「誤り検出訂正回路」とも称せられるべきもので、正味のディジタル情報例えば音声情報に付加されたパリディビットや冗長ビットを使用して伝送中のビット誤りを検出しこれを訂正する機能を有する回路で、この回路の出力からは誤り検出訂正されたディジタル情報が出力される。一方「誤り訂正符号化回路」とは正味のディジタル情報に誤り検出訂正用のパリティビットや冗長ビットを付加する機能を有する回路を意味するものである。

【0010】また、「フレーム内インタリーブ回路」、「フレーム内デインタリーブ回路」とあるは、衛星テレビジョン放送あるいは高精細度テレビジョン放送をこの場合の例として採用したために生じた回路ブロックで、ここでいうフレームとはテレビジョン映像信号のフレームとは別のもので、ディジタル音声信号の一つの処理単位を表わすものである。つまり、衛星テレビジョン放送では2048ビット分1ミリ秒、高精細度テレビジョン放送では1350ビット分1ミリ秒の単位を表す。伝送によりディジタル音声信号にまとまった誤りが生じても、その誤りを分散させてその影響を軽減させるため、また誤り訂正を効果的に行うため、ディジタル信号をフレーム内で並べ替えて伝送し受信側でこれを元に戻す技術を使用している。この並べ変え回路が「フレーム内インターリーブ回路」、元に戻す回路が「フレーム内デインタリーブ回路」であり、これを使用するかしないかは後に述べる本発明の本質には関係がない。さらに高精細度テレビジョン放送では、フレーム間に及ぶ信号の並べ替えも行っており、この場合には後述の「フレーム間インタリーブ回路」、「フレーム間デインタリーブ回路」が使用される。

【0011】説明のついでに述べれば、後述の構成図に出てくる「時間軸伸長回路」、「時間軸圧縮回路」、「3値2値変換回路」、「2値3値変換回路」などの回路ブロックも高精細度テレビジョン放送方式特有のもので、詳細な説明は省略するがこれらも使用するかしないかは本発明の本質には関係しない。

【0012】

【発明が解決しようとする課題】図4図示従来構成のアダプタにおいては、デスクランブル後に改めて誤り訂正符号化を行い、また同期・制御符号も誤りの無いものを再付加しているので、見かけ上出力信号には全く誤りを含まない、すなわち、この構成のデスクランブル用デコーダアダプタの出力に接続された受信機にとっては、常に誤りの無い信号を受信しているように見える。つまり、その受信機は、決して誤り処理機能を動作させることはない。

【0013】伝送路でビット誤りが生じているような場合において、誤り訂正符号復号回路で訂正不可能な誤りが検出されたとしても、その情報はそこで途切れ、出力に接続された受信機に伝わることはない。つまり、その受信機が、訂正不可能な誤りを検出したとき音声信号を補間する機能を備えていたとしても、その機能を発揮させることはできない。

【0014】このように、伝送路に誤りが生じる可能性がある場合には、上述のデスクランブル用デコーダアダプタを接続された受信機はその機能を十分発揮できない。

【0015】図5図示の従来構成のアダプタは、この問題点を解決する一技術を提供するものであるが、本願発明も同じくこの問題点を解決する別構成のアダプタを提供しようとするものである。

【0016】

【課題を解決するための手段】前述の問題点を解決するためのディジタル信号デスクランブル用デコーダアダプタの第1の発明はすなわち、誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、

【0017】前記入力信号を前記誤り訂正符号の復号を行う前の状態の信号にデコードするプリデコーダ回路と、前記誤り訂正符号の符号化を行った後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、2を法とする加算回路とを具備し、

【0018】前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするものである。

【0019】また、ディジタル信号デスクランブル用デコーダアダプタの第2の発明は、誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、

【0020】前記入力信号をフレーム内デインタリーブ処理を行う前の状態の信号にデコードするプリデコーダ回路と、フレーム内インタリーブ処理を行った後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、フレーム内インタリーブ回路と、2を法とする加算回路とを具備し、

【0021】前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化しさらにフレーム内インタリーブ処理した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするものである。

【0022】

【実施例】以下添付図面を参照し実施例により本発明を詳細に説明する。図1にデスクランブル用デコーダアダプタ第1の発明の基本的な構成例を示す。

【0023】図1の構成例において、入力信号はまず同期・制御符号検出回路1、フレーム内デインタリーブ回路2によってプリデコードされる。一方、擬似乱数信号発生回路21で発生された擬似乱数信号は、誤り訂正符号化回路13で予め符号化されたうえで、前記プリデコードされた信号に加算されデスクランブルが行われる。さらにフレーム内インタリーブ回路12によってポストエンコードされ出力信号となる。

【0024】ここで、同期・制御符号検出回路1は、同期の確立・制御符号のデコードを行いデスクランブル用デコーダアダプタの各回路を制御する働きをし、信号そのものはそのまま通過させる。また、フレーム内デインタリーブ回路2およびフレーム内インタリーブ回路12は、同期・制御符号を含めてフレームに属する全てのビットを処理の対象とする。従って、同期・制御符号は元のまま残っており、改めて付加する必要はない。

【0025】つぎに、図1図示構成における、デスクランブル動作を説明する。このとき送信側では、誤り訂正符号化前に擬似乱数信号加算方式によりスクランブルが施されていること、その誤り訂正符号は線形符号であることを仮定する。

【0026】スクランブルを施された信号の列を表わすベクトルsi は、スクランブルを施す前のクリアな信号ci 、スクランブルのための擬似乱数信号pi として、次のように表される。

si =ci + pi

【0027】このsi をエンコードしたものが、送出信号sとなる。誤り訂正符号の生成行列をG、フレーム内インタリーブによる置換を表わす行列をPとすれば送出信号sは次のように表される。

s=P・G・si =P・G・(ci + pi )

【0028】図1図示デスクランブル用デコーダアダプタの入力信号iは、この送出信号sに伝送誤りeが加算されたものとなる。

i=s+ e

【0029】デスクランブル用デコーダアダプタでは、フレーム内デインタリーブ回路2でプリエンコードしたのち、排他的論理和回路23で誤り訂正符号化回路13の出力pを加算して、さらにフレーム内インタリーブ回路12でポストエンコードして出力信号oを得る。

o=P・(P-1・i+ p)

【0030】上記pは、擬似乱数信号発生回路21で発生された前記pi と等しい信号が、誤り訂正符号化回路13で符号化されたものである。

p=G・pi

【0031】以上を整理すると、o=P・P-1・i+ P・p=i+ P・p=s+ e+ P・p=P・G・(ci + pi ) + e+ P・G・pi =P・G・ci + P・G・pi + e+ P・G・pi =P・G・ci + e

【0032】ここで、P・G・ci はスクランブルを施されていないクリアな信号をエンコードしたものに他ならない。従って、このデスクランブルアダプタの出力に接続された受信機は、伝送誤りの影響を含めて、クリアな信号を受信しているのと等価である。なお、式中大文字P,Gは行列表示を表わし、小文字si , p i , c i , s,p,i,o,eはベクトルを表わすものとする。

【0033】衛星テレビジョン放送または高精細度テレビジョン放送の音声デスクランブル用デコーダアダプタでは、ビットストリームの形式で入出力する場合、この図1の構成が用いられる。

【0034】高精細度テレビジョン放送の音声デスクランブル用デコーダアダプタで、MUSE信号形式で入出力する場合には、図2図示のような構成となる。図1の構成に、プリデコーダ部分としてMUSE信号から1.35MHz ビットストリーム信号に変換する部分を、ポストエンコーダ部分として1.35MHz ビットストリーム信号からMUSE信号に変換する部分を、それぞれ加えた構成である。

【0035】図2の構成において、回路ブロック4,5,6,7,8,1,2はそれぞれ音声信号分離回路、周波数変換回路、3値2値変換回路、時間軸伸長回路、フレーム間デインタリーブ回路、同期・制御符号検出回路、フレーム内デインタリーブ回路を表しここまでが本発明でいうプリデコーダ回路である。またブロック12,18, 17, 16, 15, 14はそれぞれフレーム内インタリーブ回路、フレーム間インタリーブ回路、時間軸圧縮回路、2値3値変換回路、周波数変換回路、音声信号多重回路を表し、ブロック12から14までが本発明でいうポストエンコーダ回路である。すなわち本発明ではプリデコーダ回路、ポストエンコーダ回路の中味は本発明を適用する伝送方式によって当然異なり、本発明の従来例と異なる主たる部分は図1にも示した図2の擬似乱数信号発生回路21、誤り訂正符号化回路13と加算回路23の部分で、この部分は図4の従来例ではブロック3, 21, 22, 13に図5R>5の従来例ではブロック3,21, 22, 13, 32, 23, 33に対応している。

【0036】図3に、デスクランブル用デコーダアダプタ第2の発明の構成例を示す。

【0037】図3の構成においては、入力信号に、予めエンコードされた擬似乱数信号を加算し出力信号とする。予めエンコードされた擬似乱数信号とは、擬似乱数信号発生回路21で発生した擬似乱数信号を誤り訂正符号化回路13で符号化しフレーム内インタリーブ回路12でインタリーブして得られる信号である。

【0038】ここで、同期・制御符号検出回路1は、同期の確立・制御符号のデコードを行いデスクランブル用デコーダアダプタの各回路を制御する働きをし、信号そのものはそのまま通過させる。従って、同期・制御符号は元のまま残っており、改めて付加する必要はない。

【0039】以上本発明を実施例により詳細に説明してきたが、本発明はこれに限定されることなく、特許請求に記載した発明の要旨内で各種の変形変更の可能なことは明白であろう。すなわち本発明の実施例では入力信号としてディジタル音声を使用した場合について説明してきたが、これはディジタル信号として映像信号を使用した場合にも適用できるであろう。

【0040】

【発明の効果】図4に示された従来構成が、出力に接続された受信機の伝送誤り処理機能を発揮させることができなかったのに対し、図1図示構成によれば、前述のように入力信号に含まれる伝送誤りの情報は出力信号に伝搬するので、接続された受信機の伝送誤り処理機能をそのまま発揮させることができる。

【0041】この効果は、図3図示構成においても同様である。

【0042】図1の構成では、図4の構成に比較して誤り訂正符号復号回路および同期・制御符号付加回路の分だけ簡単化されている。また、図5の構成に比較して誤り訂正符号復号回路、同期・制御符号付加回路、誤り信号発生回路および2つの遅延回路の分だけ簡単化されている。

【0043】図3の構成では、図1の構成における簡単化に加え、さらにフレーム内デインタリーブ回路の分だけ簡単化することができる。

【図面の簡単な説明】

【図1】デスクランブル用デコーダアダプタ第1の発明の基本的な構成例を示す図。

【図2】本発明によるMUSE音声デスクランブル用デコーダアダプタの構成を示す図。

【図3】デスクランブル用デコーダアダプタ第2の発明の構成を示す図。

【図4】従来のデスクランブル用デコーダアダプタの構成を示す図。

【図5】従来のデスクランブル用デコーダの別の構成を示す図。

【符号の説明】

1 同期・制御符号検出回路

2 フレーム内デインタリーブ回路

3 誤り訂正符号復号回路

4 音声信号分離回路

5 周波数変換回路

6 3値2値変換回路

7 時間軸伸長回路

8 フレーム間デインタリーブ回路

11 同期・制御符号付加回路

12 フレーム内インタリーブ回路

13 誤り訂正符号化回路

14 音声信号多重回路

15 周波数変換回路

16 2値3値変換回路

17 時間軸圧縮回路

18 フレーム間インタリーブ回路

21 擬似乱数信号発生回路

22, 23, 24 加算回路

31 誤り信号発生回路

32, 33 遅延回路

【特許請求の範囲】

【請求項1】 誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、前記入力信号を前記誤り訂正符号の復号を行う前の状態の信号にデコードするプリデコーダ回路と、前記誤り訂正符号の符号化を行った後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、2を法とする加算回路とを具備し、前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするディジタル信号デスクランブル用デコーダアダプタ。

【請求項2】 前記ディジタル信号伝送方式が、衛星テレビジョン放送または高精細度テレビジョン放送の音声伝送方式であることを特徴とする請求項1記載のデスクランブル用デコーダアダプタ。

【請求項3】 誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、前記入力信号をフレーム内デインタリーブ処理を行う前の状態の信号にデコードするプリデコーダ回路と、フレーム内インタリーブ処理を行なった後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、フレーム内インタリーブ回路と、2を法とする加算回路とを具備し、前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化しさらにフレーム内インタリーブ処理した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするディジタル信号デスクランブル用デコーダアダプタ。

【請求項1】 誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、前記入力信号を前記誤り訂正符号の復号を行う前の状態の信号にデコードするプリデコーダ回路と、前記誤り訂正符号の符号化を行った後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、2を法とする加算回路とを具備し、前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするディジタル信号デスクランブル用デコーダアダプタ。

【請求項2】 前記ディジタル信号伝送方式が、衛星テレビジョン放送または高精細度テレビジョン放送の音声伝送方式であることを特徴とする請求項1記載のデスクランブル用デコーダアダプタ。

【請求項3】 誤り訂正符号として線形符号を使用し、かつ、該誤り訂正符号による符号化前の信号に擬似乱数信号加算方式によりスクランブルを施す形式のディジタル信号伝送方式に使用され、スクランブルの施された入力信号をデスクランブルし、該入力信号と同じ信号形式のスクランブルの解かれた出力信号に再構成する機能を有したデスクランブル用デコーダアダプタにおいて、前記入力信号をフレーム内デインタリーブ処理を行う前の状態の信号にデコードするプリデコーダ回路と、フレーム内インタリーブ処理を行なった後の状態の信号を前記出力信号にエンコードするポストエンコーダ回路と、デスクランブルのための擬似乱数信号発生回路と、前記誤り訂正符号の誤り訂正符号化回路と、フレーム内インタリーブ回路と、2を法とする加算回路とを具備し、前記プリデコーダ回路によってデコードされた信号と、前記擬似乱数信号発生回路で発生した擬似乱数信号を前記誤り訂正符号化回路によって符号化しさらにフレーム内インタリーブ処理した信号とを、前記加算回路によって加算したのち、前記ポストエンコーダで再構成することを特徴とするディジタル信号デスクランブル用デコーダアダプタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開平5−56431

【公開日】平成5年(1993)3月5日

【国際特許分類】

【出願番号】特願平3−236921

【出願日】平成3年(1991)8月26日

【出願人】(000004352)日本放送協会 (2,206)

【公開日】平成5年(1993)3月5日

【国際特許分類】

【出願日】平成3年(1991)8月26日

【出願人】(000004352)日本放送協会 (2,206)

[ Back to top ]