デシメーションフィルタ

【課題】多くの演算装置を必要とせずに、フィルタ特性の優れたデシメーションフィルタを提供する。

【解決手段】第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、バッファメモリが出力したデータと係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、前段のバッファメモリが出力したデータを遅延して出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する2段目以降の演算ユニットとを備えたデシメーションフィルタ。

【解決手段】第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、バッファメモリが出力したデータと係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、前段のバッファメモリが出力したデータを遅延して出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する2段目以降の演算ユニットとを備えたデシメーションフィルタ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、必要とする演算装置の数が少なく、特性の優れたデシメーションフィルタに関する。

【背景技術】

【0002】

第1サンプリング周波数でサンプリングされたディジタル信号を、第1サンプリング周波数よりも低い第2サンプリング周波数のディジタル信号に変換する際に、デシメータ(間引き器:decimator)が用いられる。

【0003】

デシメータでは、入力データに対してフィルタリング処理を行なった後、データを間引く処理を行なう。フィルタリング処理は、第2サンプリング周波数にダウンサンプリングする際に、第2サンプリング周波数の1/2の周波数(ナイキスト周波数)よりも高い成分が含まれていると、エイリアシングと呼ばれる折り返し歪みが生じてしまうことから、周波数帯域をナイキスト周波数以下に制限するために行なうものである。このフィルタリング処理に用いるフィルタは、デシメーションフィルタと呼ばれる。

【0004】

例えば、特許文献1には、図5に示すような構成のデシメータ300が記載されている。本図において、デシメータ300は、第1サンプリング周波数の信号S1を入力し、バッファメモリ311に一時的に格納する。演算装置313は、タイミング制御回路314によるタイミング制御の下で、バッファメモリ311からデータを読み出し、係数メモリ312に格納されたフィルタ係数を用いた所定の演算を行なうことで帯域制限を施す。すなわち、バッファメモリ311、係数メモリ312、演算装置313、タイミング制御回路314でデシメーションフィルタ310を構成している。

【0005】

そして、デシメータ300は、デシメーションフィルタによって帯域制限が施されたデータをスイッチ回路320で第2サンプリング周波数にサブサンプリングすることで、第2サンプリング周波数の信号S2を出力する。デシメーションフィルタ310は、オーディオ帯の信号等の比較的低いサンプリング周波数に適している。

【0006】

また、特許文献2には、図6に示すような構成のデシメータ400が記載されている。本図において、デシメータ400は、デシメーションフィルタ410を構成するN段連結された係数メモリ411と演算装置412とを備えている。1段目の係数メモリ411には、フィルタ係数が格納されており、2段目以降の係数メモリ411は、シフトレジスタとなっている。また、演算装置412は、乗算器とアキュムレータと備えている。

【0007】

第1サンプリング周波数の信号S1を第2サンプリング周波数の信号S2に変換する場合、デシメーション比をDRとすると、それぞれの係数メモリ411からDR段ずつずれたフィルタ係数を読み出して、それぞれの演算装置412が所定の演算を行なうことで帯域制限を施す。そして、スイッチ回路420で第2サンプリング周波数にサブサンプリングすることで、第2サンプリング周波数の信号S2を出力する。デシメーションフィルタ410は、比較的高いサンプリング周波数に適している。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−219560号公報

【特許文献2】特開2008−124593号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

第1サンプリング周波数と第2サンプリング周波数との比であるデシメーション比が大きい場合には、複数個のデシメータを多段に接続することが行なわれている。例えば、2段のデシメータを接続する場合、図7に示すように、第1サンプリング周波数を、1段目の比較的高いサンプリング周波数に適したデシメータ400(図6)で中間のサンプリング周波数に落としてから、2段目の比較的低いサンプリング周波数に適したデシメータ300(図5)で第2サンプリング周波数に変換する。これにより、高速で動作させる必要のある1段目のデシメータ400のフィルタの特性の要求性能(カットオフ特性)を緩和し、2段目のデシメータ300で必要な帯域特性を実現することができる。

【0010】

しかしながら、2段目のデシメータ300で行なうべきデシメーション比が小さい場合には、必要な帯域特性を実現するための十分なフィルタ演算のタップ数を確保することができなくなる。

【0011】

例えば、第1サンプリング周波数を100MHzとし、1段目のデシメータでサンプリング周波数を1/4にデシメートする場合を想定する。この場合、2段目のデシメータには25MHzのサンプリング周波数が入力されることになる。

【0012】

2段目のデシメータに、比較的低いサンプリング周波数に適したデシメータ300を用いる構成とすると、例えば、2段目のデシメーション比が1:3で3サンプル毎にフィルタ演算を完了する必要がある場合、フィルタの動作クロック周波数が1段目と同じ100MHzであれば、12タップのフィルタ演算しか実現できない。このタップ数のフィルタ演算では、必要な帯域制限をかけることは極めて困難である。

【0013】

したがって、必要な帯域特性を実現するために、2段目にも比較的高いサンプリング周波数に適したデシメータ400を用いなければならないが、必要となる演算装置数が多くなってしまい、回路的な負担が大きくなり、消費電力も増大するという問題があった。

【0014】

そこで、本発明は、多くの演算装置を必要とせずに、フィルタ特性の優れたデシメーションフィルタを提供することを目的とする。

【課題を解決するための手段】

【0015】

上記課題を解決するため、本発明の第1の態様であるデシメーションフィルタは、第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、前段の演算ユニットのバッファメモリが出力したデータを遅延して出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とする。

【0016】

ここで、前記初段の演算ユニットのバッファメモリは、前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力する動作を繰り返すことができる。

【0017】

また、前記係数メモリは、前記フィルタ演算のタップ数分のフィルタ係数の後にデシメーション比×(演算ユニット段数−1)個のダミーデータDDを付加したものを前記フィルタ係数としてリングバッファ形式で出力することができる。

【0018】

また、前記2段目以降の演算ユニットのバッファメモリは、前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の演算ユニットのバッファメモリが出力したデータを、(デシメーション比×クロック比−デシメーション比)分遅延して出力することができる。

【0019】

また、前記係数バッファメモリは、前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を、(デシメーション比×クロック比)分遅延して出力することができる。

【0020】

上記課題を解決するため、本発明の第2の態様であるデシメーションフィルタは、第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、前記第1信号を入力し、段数に応じた遅延量で選択的に出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とする。

【0021】

ここで、前記各段の演算ユニットのバッファメモリは、前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力する動作を繰り返すことができる。

【0022】

いずれの態様においても、前記2段目以降の演算ユニットにおいて、前記係数バッファメモリに代えて、リングバッファ形式でフィルタ係数を出力する係数メモリを備え、前記演算装置は、自段のバッファメモリが出力したデータと自段の係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうようにしてもよい。

【0023】

さらに、第2の態様では、前記2段目以降の演算ユニットにおいて、前記係数バッファメモリを省き、前記演算装置は、自段のバッファメモリが出力したデータと前記初段の演算ユニットが備える係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうようにしてもよい。

【発明の効果】

【0024】

本発明によれば、多くの演算装置を必要とせずに、フィルタ特性の優れたデシメーションフィルタが提供される。

【図面の簡単な説明】

【0025】

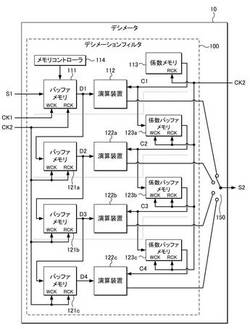

【図1】本実施形態に係るデシメータの構成を示すブロック図である。

【図2】デシメーションフィルタの動作について説明するタイミングチャートである。

【図3】デシメーション比毎のフィルタリング処理後のデータが順次生成されている様子を模式的に示した図である。

【図4】2段目以降のバッファメモリを初段のバッファメモリと並列に接続した場合の構成例を示すブロック図である。

【図5】従来のデシメータの第1の構成例を示すブロック図である。

【図6】従来のデシメータの第2の構成例を示すブロック図である。

【図7】2段のデシメータ

【発明を実施するための形態】

【0026】

本発明の実施の形態について図面を参照して説明する。図1は、本実施形態に係るデシメータの構成を示すブロック図である。本図に示すようにデシメータ10は、第1サンプリング周波数でサンプリングされたディジタル入力信号S1を入力し、第1サンプリング周波数よりも低い第2サンプリング周波数のディジタル信号S2に変換して出力する。また、デシメータ10には、第1サンプリング周波数のクロックCK1と、第1サンプリング周波数よりも十分高く、動作クロックとなるクロックCK2とが入力される。

【0027】

本実施形態では、クロックCK1とクロックCK2との比は、1:4(=4)であるとする。すなわち、第1サンプリング周波数が、例えば、25MHzであれば、動作クロックCK2は、100MHzとなる。以下では、クロックCK1とクロックCK2との比をクロック比CRと称する。

【0028】

デシメータ10は、帯域制限を行なうデシメーションフィルタ100と、第2サンプリング周波数にサブサンプリングして、信号S2として出力するスイッチ回路150とを備えている。

【0029】

デシメーションフィルタ100は、フィルタ演算を行なう多段の演算ユニットを備えて構成されている。初段の演算ユニットは、バッファメモリ111と演算装置112と係数メモリ113とメモリコントローラ114を備えており、2段目以降の演算ユニットは、バッファメモリ121、演算装置122、係数バッファメモリ123を備えている。

【0030】

本実施形態では、デシメーションフィルタ100は、4段の演算ユニットを備えているものとする。各演算ユニットの出力は、デシメーション比に応じてスイッチ回路150で切り替えられ、第2サンプリング周波数のディジタル信号S2として出力される。

【0031】

以下では、演算ユニットの段数をSNと称し、デシメーション比をDRと称し、フィルタ演算のタップ数をTNと称する。なお、図1中において2段目以降の演算ユニットの各ブロックの符号には、2段目について「a」、3段目について「b」、4段目について「c」の識別子を付しているが、特に区別する必要がない場合は、識別子を省略して説明する。

【0032】

初段の演算ユニットにおいて、バッファメモリ111には、入力信号S1と、クロックCK1と、クロックCK2とが入力される。バッファメモリ111は、クロックCK1に同期して入力された入力信号S1を一時的に格納した後、クロックCK2に同期して選択的にD1として出力する。このため、バッファメモリ111は、デュアルポートメモリを用いることが好ましい。以下では、入力信号S1をd0、d1、d2…で表わすものとする。

【0033】

バッファメモリ111が選択的に出力するデータD1は、メモリコントローラ114により制御される。なお、メモリコントローラ114は、バッファメモリ111に内蔵させてもよい。バッファメモリ111の出力D1は、初段の演算装置112に入力されるとともに、2段目の演算ユニットのバッファメモリ121aに入力される。

【0034】

メモリコントローラ114は、バッファメモリ111に対して以下のような制御を行なう。すなわち、入力信号S1として入力されるd0、d1、d2…に対して、まず、開始データsdとしてd0を設定し、開始データsdからタップ数TN+デシメーション比DR×(演算ユニット段数SN−1)個のデータをCK2に同期して連続的にデータD1として出力させる。このため、データD1の出力は、バッファメモリ111に、タップ数TN+デシメーション比DR×(演算ユニット段数SN−1)個分のデータが溜まってから開始することが望ましい。

【0035】

初段の演算ユニットでは、d0〜d38までしか使用しないが、次段以降の演算ユニットでd47まで使用するために、データD1としてd0〜d47まで連続的に出力する。

【0036】

その後は、開始データsdからデシメーション比DR×演算ユニット段数SN個番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdからタップ数TN+デシメーション比DR×(演算ユニット段数SN−1)個のデータをCK2に同期して連続的にデータD1として出力する動作を繰り返させる。これは、最後段まで順次フィルタ演算を行なった後に、初段に戻ってフィルタ演算を行なうためである。

【0037】

例えば、演算ユニット段数SNを4とし、デシメーション比DRを3、タップ数TNを39とした場合、図2に示すように、バッファメモリ111にd0からd47まで蓄積されるのを待ってから、まず、d0からd47までのデータをCK2に同期して連続的に出力する(時刻t0〜時刻t4)。

【0038】

そして、d0から12個番目のd12からd59までのデータをCK2に同期して連続的に出力する(時刻t4〜)。以降は、d24からd71、d36からd83…というようにバッファメモリ111からデータD1として出力させる。

【0039】

図1の説明に戻って、初段の演算ユニットにおいて、係数メモリ113には、フィルタ演算のためのフィルタ係数が格納される。ここで、格納されるフィルタ係数は、タップ数TN個のフィルタ係数の後にデシメーション比DR×(演算ユニット段数SN−1)個のダミーデータDDが付加されたものである。ダミーデータDDは、最後段のフィルタ演算を行なった後、初段に戻ったときのフィルタ係数開始位置を合わせるために用いるものであり、フィルタ演算には使用しないため、例えば、0とすることができる。ダミーデータDDが付加されたフィルタ係数は、リングバッファ形式で係数メモリ113に格納される。

【0040】

係数メモリ113に格納されたフィルタ係数は、クロックCK2に同期してフィルタ係数C1として読み出され、初段の演算装置112に入力されるとともに、2段目の係数バッファメモリ123aに入力される。

【0041】

本実施形態では、フィルタ演算のタップ数TNを39としているため、図2に示すように、係数メモリ113からは、フィルタ係数C1としてc0〜c38がクロックCK2に同期して順次出力され(時刻t0〜時刻t3)、その後、9個のダミーデータDDが出力されることになる(時刻t3〜時刻t4)。

【0042】

係数メモリ113は、リングバッファ形式でフィルタ係数を格納するため、以降は、フィルタ係数C1として、c0〜c38の出力と、9個のダミーデータDDの出力とが繰り返される(時刻t4〜)。

【0043】

図1の説明に戻って、初段の演算ユニットにおいて、演算装置112は、バッファメモリ111から出力されたデータD1と、係数メモリ113から出力されたフィルタ係数C1とを用いてフィルタ演算を行ない、演算結果をスイッチ回路150に出力する。

【0044】

本実施形態では、図2に示すように、時刻t0から時刻t3において、d0×c0+d1×c1+d2×c2…+d37×c37+d38×c38のフィルタ演算が行なわれ、d0〜d38に対するタップ数TN39のフィルタリング処理後のデータfD0が算出される。

【0045】

時刻t3から時刻t4は、ダミーデータDDであるため、フィルタ演算結果には影響を与えない。時刻t4からは、d12×c0+d13×c1+d14×c2…+d49×c37+d50×c38のフィルタ演算が行なわれ、d12〜d50に対するタップ数TN39のフィルタリング処理後のデータfD12が算出される。

【0046】

図1の説明に戻って、2段目以降の演算ユニットnにおいて、バッファメモリ121には、初段のバッファメモリ111あるいは前段のバッファメモリ121から読み出されたデータD(n−1)とクロックCK2とが入力される。バッファメモリ121は、クロックCK2に同期して入力されたデータD(n−1)を、一時的に格納した後、クロックCK2に同期して、データDnとして同段の演算装置122に出力するとともに、次段の演算ユニットのバッファメモリ121に出力する。

【0047】

バッファメモリ121は、例えば、FIFOメモリで構成することができる。バッファメモリ121の遅延量DBは、

遅延量DB=デシメーション比DR×クロック比CR−デシメーション比DR

と設定する。

【0048】

例えば、デシメーション比DRを3とした場合、クロック比CRが4であれば、バッファメモリ121の遅延量DBは、クロックCK2で3×4−3=9クロック分と定められる。また、デシメーション比DRを10とした場合、クロック比CRが8であれば、バッファメモリ121の遅延量DBは、10×8−10=70クロック分と定められる。

【0049】

本実施形態では、2段目以降のバッファメモリ121の遅延量DBは9となるため、図2に示すように2段目のバッファメモリ121aの出力D2は、初段のバッファメモリ121の出力D1から9クロック遅れて出力される(時刻t1)。

【0050】

図1の説明に戻って、2段目以降の演算ユニットnにおいて、係数バッファメモリ123は、初段の係数メモリ113あるいは前段の係数バッファメモリ123から読み出されたフィルタ係数C(n−1)とクロックCK2とが入力される。係数バッファメモリ123は、クロックCK2に同期して入力されたフィルタ係数C(n−1)を、一時的に格納した後、クロックCK2に同期して、フィルタ係数Cnとして同段の演算装置122に出力するとともに、次段の演算ユニットの係数バッファメモリ123に出力する。

【0051】

係数バッファメモリ123は、例えば、FIFOメモリで構成することができる。係数バッファメモリ123の遅延量DCは、

遅延量DC=デシメーション比DR×クロック比CR

と設定する。

【0052】

本実施形態では、2段目以降の係数バッファメモリ123の遅延量は、12となるため、図2に示すように2段目の係数バッファメモリ123aの出力C2は、1段目の係数メモリ113の出力C1から12クロック遅れて出力される(時刻t2)。

【0053】

図1の説明に戻って、2段目以降の演算ユニットnにおいて演算装置122は、バッファメモリ121から出力されたデータDnと、係数バッファメモリ123から出力されたフィルタ係数Cnとを用いてフィルタ演算を行ない、演算結果をスイッチ回路150に出力する。

【0054】

本実施形態では、2段目の演算装置122aは、図2に示すように、時刻t2から時刻t5において、d3×c0+d4×c1+d5×c2…+d40×c37+d41×c38のフィルタ演算が行なわれ、d3〜d41に対するタップ数TN39のフィルタリング処理後のデータfD3が算出される。時刻t1から時刻t2は、データD2としてd0、d1、d2が入力されるが、2段目の演算装置122aが時刻t2から演算を開始することで、フィルタ演算結果には影響を与えないようになっている。

【0055】

同様に、3段目の演算装置122bでは、d6〜d44に対するフィルタリング処理後のデータfD6が算出され、4段目の演算装置122cでは、d9〜d47に対するフィルタリング処理後のデータfD9が順次算出される。

【0056】

その後は、1段目の演算装置112で、d12〜d51に対するフィルタリング処理後のデータfD12が算出され、2段目の演算装置122aで、d15〜d54に対するフィルタリング処理後のデータfD15が算出されていく。図3(a)は、デシメーション比毎のフィルタリング処理後のデータが順次生成されている様子を模式的に示している。

【0057】

これらのフィルタリング処理後のデータfD0、fD3、fD6、fD9、fD12、fD15…を、スイッチ回路150が第2サンプリング周波数で順次出力することで、第1サンプリング周波数の入力信号S1が、デシメーション比DRが3である第2サンプリング周波数の信号S2に変換されることになる。

【0058】

このように、本実施形態のデシメーションフィルタ100では、バッファメモリと演算装置とを備えた演算ユニットを複数段連結し、デシメーション比の個数分入力データをずらしたフィルタ演算を行なうようにすることで、少ない演算装置で多くのタップ数のフィルタ演算を行なえるようにし、優れたフィルタ特性を得るようにしている。

【0059】

図1の例では、4個の演算装置で39タップのフィルタ演算を実現しており、少ない演算装置では、同条件で12タップ程度しか実現できなかった従来のデシメーションフィルタと比較して大幅にフィルタ特性が改善されている。もちろん、演算装置の数は4個に限られず、タップ数やデシメーション比等の条件によって2個で十分の場合もあれば、8個必要となる場合もあり得る。

【0060】

本実施形態のデシメーションフィルタ100では、演算ユニットを増やすことで、容易にフィルタ演算のタップ数を増やすことが可能であり、十分な帯域特性を有するデシメーションフィルタを、多量の演算装置を用いることなく実現することができ、回路コストや消費電力を削減することができる。

【0061】

また、タップ数やデシメーション比等に応じて複数備えた演算装置の一部を用いてデシメーションフィルタを構成してもよく、この場合、消費電力を一層削減することができる。なお、クロック比CRを高くすれば、演算ユニットの数をさらに少なくすることができる。

【0062】

なお、上述の例では、2段目以降のバッファメモリ221に、デシメーション比DRとクロック比CRとで定められる遅延量DBを与えていたが、これらのバッファメモリを初段のバッファメモリ111と並列に接続して、それぞれのバッファメモリから初段のバッファメモリ111と同様の読み出し出し順で、タイミングをずらしてそれぞれの演算装置にデータDnを出力するようにしてもよい。

【0063】

図4は、2段目以降のバッファメモリを初段のバッファメモリ111と並列に接続した場合の構成例を示すブロック図である。図1の構成と同じブロックについては同じ符号を付して、説明を省略する。

【0064】

本図に示すように、2段目以降のバッファメモリ221には、入力信号S1と、クロックCK1と、クロックCK2とが入力される。バッファメモリ221は、クロックCK1に同期して入力された入力信号S1を一時的に格納した後、クロックCK2に同期して選択的にD2、D3、D4として出力する。このため、バッファメモリ221は、デュアルポートメモリを用いることが好ましい。

【0065】

バッファメモリ111とバッファメモリ221とが選択的に出力するデータD1、D2、D3、D4は、メモリコントローラ214により制御される。

【0066】

メモリコントローラ214は、バッファメモリ221に対してバッファメモリ111と同じ読み出し出し順でデータD2を出力させるが、2段目のバッファメモリ221aは、初段のバッファメモリ111よりも、デシメーション比DR×クロック比CR−デシメーション比DRクロック分タイミングを遅らせる。

【0067】

3段目以降のバッファメモリ221についても、バッファメモリ111と同じ読み出し出し順でデータDnを出力させるが、前段のバッファメモリ221よりも、デシメーション比DR×クロック比CR−デシメーション比DRクロック分タイミングを遅らせる。このような制御を行なうことにより、図2に示したタイミングと同様のタイミングでデータDnを出力することができるようになる。

【0068】

さらに、図4に示した構成では、バッファメモリ111とバッファメモリ221は、次段以降で用いるデータを出力せずに、自段の演算ユニットで用いるデータのみを出力すればよいため、図3(b)に示すようなタイミングでフィルタ演算を行なうことができる。係数メモリ113のダミーデータDDも不要である。

【0069】

このとき、上述の例とは逆に、1段目のバッファメモリ111のデータ出力および2段目、3段目のバッファメモリ221の出力を、4段目のバッファメモリ221cのデータ出力タイミングに揃えるように遅らせるようにしてもよい。この場合、係数メモリc113から出力されるフィルタ係数Cnを同じタイミングで共通に使用することができるため、係数バッファメモリ123a、123b、123cを省くことができる。

【0070】

また、上述の例では、2段目以降の演算ユニットに、係数バッファメモリ123を備えさせ、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力するようにしていたが、係数バッファメモリ123に代えて、初段と同様の係数メモリ113を備えさせるようにしてもよい。

【0071】

この場合、図4に示したメモリコントローラ214がそれぞれの係数メモリ113に対して、図2あるいは図3(b)に示すようなタイミングで、各バッファメモリ111、121、221の出力データに対応するフィルタ係数Cnを出力するように制御すればよい。あるいは、出力を開始するフィルタ係数を各段の係数メモリ113毎にずらすようにしてもよい。

【符号の説明】

【0072】

10…デシメータ、100…デシメーションフィルタ、111…バッファメモリ、112…演算装置、113…係数メモリ、114…メモリコントローラ、121…バッファメモリ、122…演算装置、123…係数バッファメモリ、150…スイッチ回路、214…メモリコントローラ、221…バッファメモリ、300…デシメータ、310…デシメーションフィルタ、311…バッファメモリ、312…係数メモリ、313…演算装置、314…タイミング制御回路、320…スイッチ回路、400…デシメータ、410…デシメーションフィルタ、411…係数メモリ、412…演算装置、420…スイッチ回路

【技術分野】

【0001】

本発明は、必要とする演算装置の数が少なく、特性の優れたデシメーションフィルタに関する。

【背景技術】

【0002】

第1サンプリング周波数でサンプリングされたディジタル信号を、第1サンプリング周波数よりも低い第2サンプリング周波数のディジタル信号に変換する際に、デシメータ(間引き器:decimator)が用いられる。

【0003】

デシメータでは、入力データに対してフィルタリング処理を行なった後、データを間引く処理を行なう。フィルタリング処理は、第2サンプリング周波数にダウンサンプリングする際に、第2サンプリング周波数の1/2の周波数(ナイキスト周波数)よりも高い成分が含まれていると、エイリアシングと呼ばれる折り返し歪みが生じてしまうことから、周波数帯域をナイキスト周波数以下に制限するために行なうものである。このフィルタリング処理に用いるフィルタは、デシメーションフィルタと呼ばれる。

【0004】

例えば、特許文献1には、図5に示すような構成のデシメータ300が記載されている。本図において、デシメータ300は、第1サンプリング周波数の信号S1を入力し、バッファメモリ311に一時的に格納する。演算装置313は、タイミング制御回路314によるタイミング制御の下で、バッファメモリ311からデータを読み出し、係数メモリ312に格納されたフィルタ係数を用いた所定の演算を行なうことで帯域制限を施す。すなわち、バッファメモリ311、係数メモリ312、演算装置313、タイミング制御回路314でデシメーションフィルタ310を構成している。

【0005】

そして、デシメータ300は、デシメーションフィルタによって帯域制限が施されたデータをスイッチ回路320で第2サンプリング周波数にサブサンプリングすることで、第2サンプリング周波数の信号S2を出力する。デシメーションフィルタ310は、オーディオ帯の信号等の比較的低いサンプリング周波数に適している。

【0006】

また、特許文献2には、図6に示すような構成のデシメータ400が記載されている。本図において、デシメータ400は、デシメーションフィルタ410を構成するN段連結された係数メモリ411と演算装置412とを備えている。1段目の係数メモリ411には、フィルタ係数が格納されており、2段目以降の係数メモリ411は、シフトレジスタとなっている。また、演算装置412は、乗算器とアキュムレータと備えている。

【0007】

第1サンプリング周波数の信号S1を第2サンプリング周波数の信号S2に変換する場合、デシメーション比をDRとすると、それぞれの係数メモリ411からDR段ずつずれたフィルタ係数を読み出して、それぞれの演算装置412が所定の演算を行なうことで帯域制限を施す。そして、スイッチ回路420で第2サンプリング周波数にサブサンプリングすることで、第2サンプリング周波数の信号S2を出力する。デシメーションフィルタ410は、比較的高いサンプリング周波数に適している。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−219560号公報

【特許文献2】特開2008−124593号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

第1サンプリング周波数と第2サンプリング周波数との比であるデシメーション比が大きい場合には、複数個のデシメータを多段に接続することが行なわれている。例えば、2段のデシメータを接続する場合、図7に示すように、第1サンプリング周波数を、1段目の比較的高いサンプリング周波数に適したデシメータ400(図6)で中間のサンプリング周波数に落としてから、2段目の比較的低いサンプリング周波数に適したデシメータ300(図5)で第2サンプリング周波数に変換する。これにより、高速で動作させる必要のある1段目のデシメータ400のフィルタの特性の要求性能(カットオフ特性)を緩和し、2段目のデシメータ300で必要な帯域特性を実現することができる。

【0010】

しかしながら、2段目のデシメータ300で行なうべきデシメーション比が小さい場合には、必要な帯域特性を実現するための十分なフィルタ演算のタップ数を確保することができなくなる。

【0011】

例えば、第1サンプリング周波数を100MHzとし、1段目のデシメータでサンプリング周波数を1/4にデシメートする場合を想定する。この場合、2段目のデシメータには25MHzのサンプリング周波数が入力されることになる。

【0012】

2段目のデシメータに、比較的低いサンプリング周波数に適したデシメータ300を用いる構成とすると、例えば、2段目のデシメーション比が1:3で3サンプル毎にフィルタ演算を完了する必要がある場合、フィルタの動作クロック周波数が1段目と同じ100MHzであれば、12タップのフィルタ演算しか実現できない。このタップ数のフィルタ演算では、必要な帯域制限をかけることは極めて困難である。

【0013】

したがって、必要な帯域特性を実現するために、2段目にも比較的高いサンプリング周波数に適したデシメータ400を用いなければならないが、必要となる演算装置数が多くなってしまい、回路的な負担が大きくなり、消費電力も増大するという問題があった。

【0014】

そこで、本発明は、多くの演算装置を必要とせずに、フィルタ特性の優れたデシメーションフィルタを提供することを目的とする。

【課題を解決するための手段】

【0015】

上記課題を解決するため、本発明の第1の態様であるデシメーションフィルタは、第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、前段の演算ユニットのバッファメモリが出力したデータを遅延して出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とする。

【0016】

ここで、前記初段の演算ユニットのバッファメモリは、前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力する動作を繰り返すことができる。

【0017】

また、前記係数メモリは、前記フィルタ演算のタップ数分のフィルタ係数の後にデシメーション比×(演算ユニット段数−1)個のダミーデータDDを付加したものを前記フィルタ係数としてリングバッファ形式で出力することができる。

【0018】

また、前記2段目以降の演算ユニットのバッファメモリは、前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の演算ユニットのバッファメモリが出力したデータを、(デシメーション比×クロック比−デシメーション比)分遅延して出力することができる。

【0019】

また、前記係数バッファメモリは、前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を、(デシメーション比×クロック比)分遅延して出力することができる。

【0020】

上記課題を解決するため、本発明の第2の態様であるデシメーションフィルタは、第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、前記第1信号を入力し、段数に応じた遅延量で選択的に出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とする。

【0021】

ここで、前記各段の演算ユニットのバッファメモリは、前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力する動作を繰り返すことができる。

【0022】

いずれの態様においても、前記2段目以降の演算ユニットにおいて、前記係数バッファメモリに代えて、リングバッファ形式でフィルタ係数を出力する係数メモリを備え、前記演算装置は、自段のバッファメモリが出力したデータと自段の係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうようにしてもよい。

【0023】

さらに、第2の態様では、前記2段目以降の演算ユニットにおいて、前記係数バッファメモリを省き、前記演算装置は、自段のバッファメモリが出力したデータと前記初段の演算ユニットが備える係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうようにしてもよい。

【発明の効果】

【0024】

本発明によれば、多くの演算装置を必要とせずに、フィルタ特性の優れたデシメーションフィルタが提供される。

【図面の簡単な説明】

【0025】

【図1】本実施形態に係るデシメータの構成を示すブロック図である。

【図2】デシメーションフィルタの動作について説明するタイミングチャートである。

【図3】デシメーション比毎のフィルタリング処理後のデータが順次生成されている様子を模式的に示した図である。

【図4】2段目以降のバッファメモリを初段のバッファメモリと並列に接続した場合の構成例を示すブロック図である。

【図5】従来のデシメータの第1の構成例を示すブロック図である。

【図6】従来のデシメータの第2の構成例を示すブロック図である。

【図7】2段のデシメータ

【発明を実施するための形態】

【0026】

本発明の実施の形態について図面を参照して説明する。図1は、本実施形態に係るデシメータの構成を示すブロック図である。本図に示すようにデシメータ10は、第1サンプリング周波数でサンプリングされたディジタル入力信号S1を入力し、第1サンプリング周波数よりも低い第2サンプリング周波数のディジタル信号S2に変換して出力する。また、デシメータ10には、第1サンプリング周波数のクロックCK1と、第1サンプリング周波数よりも十分高く、動作クロックとなるクロックCK2とが入力される。

【0027】

本実施形態では、クロックCK1とクロックCK2との比は、1:4(=4)であるとする。すなわち、第1サンプリング周波数が、例えば、25MHzであれば、動作クロックCK2は、100MHzとなる。以下では、クロックCK1とクロックCK2との比をクロック比CRと称する。

【0028】

デシメータ10は、帯域制限を行なうデシメーションフィルタ100と、第2サンプリング周波数にサブサンプリングして、信号S2として出力するスイッチ回路150とを備えている。

【0029】

デシメーションフィルタ100は、フィルタ演算を行なう多段の演算ユニットを備えて構成されている。初段の演算ユニットは、バッファメモリ111と演算装置112と係数メモリ113とメモリコントローラ114を備えており、2段目以降の演算ユニットは、バッファメモリ121、演算装置122、係数バッファメモリ123を備えている。

【0030】

本実施形態では、デシメーションフィルタ100は、4段の演算ユニットを備えているものとする。各演算ユニットの出力は、デシメーション比に応じてスイッチ回路150で切り替えられ、第2サンプリング周波数のディジタル信号S2として出力される。

【0031】

以下では、演算ユニットの段数をSNと称し、デシメーション比をDRと称し、フィルタ演算のタップ数をTNと称する。なお、図1中において2段目以降の演算ユニットの各ブロックの符号には、2段目について「a」、3段目について「b」、4段目について「c」の識別子を付しているが、特に区別する必要がない場合は、識別子を省略して説明する。

【0032】

初段の演算ユニットにおいて、バッファメモリ111には、入力信号S1と、クロックCK1と、クロックCK2とが入力される。バッファメモリ111は、クロックCK1に同期して入力された入力信号S1を一時的に格納した後、クロックCK2に同期して選択的にD1として出力する。このため、バッファメモリ111は、デュアルポートメモリを用いることが好ましい。以下では、入力信号S1をd0、d1、d2…で表わすものとする。

【0033】

バッファメモリ111が選択的に出力するデータD1は、メモリコントローラ114により制御される。なお、メモリコントローラ114は、バッファメモリ111に内蔵させてもよい。バッファメモリ111の出力D1は、初段の演算装置112に入力されるとともに、2段目の演算ユニットのバッファメモリ121aに入力される。

【0034】

メモリコントローラ114は、バッファメモリ111に対して以下のような制御を行なう。すなわち、入力信号S1として入力されるd0、d1、d2…に対して、まず、開始データsdとしてd0を設定し、開始データsdからタップ数TN+デシメーション比DR×(演算ユニット段数SN−1)個のデータをCK2に同期して連続的にデータD1として出力させる。このため、データD1の出力は、バッファメモリ111に、タップ数TN+デシメーション比DR×(演算ユニット段数SN−1)個分のデータが溜まってから開始することが望ましい。

【0035】

初段の演算ユニットでは、d0〜d38までしか使用しないが、次段以降の演算ユニットでd47まで使用するために、データD1としてd0〜d47まで連続的に出力する。

【0036】

その後は、開始データsdからデシメーション比DR×演算ユニット段数SN個番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdからタップ数TN+デシメーション比DR×(演算ユニット段数SN−1)個のデータをCK2に同期して連続的にデータD1として出力する動作を繰り返させる。これは、最後段まで順次フィルタ演算を行なった後に、初段に戻ってフィルタ演算を行なうためである。

【0037】

例えば、演算ユニット段数SNを4とし、デシメーション比DRを3、タップ数TNを39とした場合、図2に示すように、バッファメモリ111にd0からd47まで蓄積されるのを待ってから、まず、d0からd47までのデータをCK2に同期して連続的に出力する(時刻t0〜時刻t4)。

【0038】

そして、d0から12個番目のd12からd59までのデータをCK2に同期して連続的に出力する(時刻t4〜)。以降は、d24からd71、d36からd83…というようにバッファメモリ111からデータD1として出力させる。

【0039】

図1の説明に戻って、初段の演算ユニットにおいて、係数メモリ113には、フィルタ演算のためのフィルタ係数が格納される。ここで、格納されるフィルタ係数は、タップ数TN個のフィルタ係数の後にデシメーション比DR×(演算ユニット段数SN−1)個のダミーデータDDが付加されたものである。ダミーデータDDは、最後段のフィルタ演算を行なった後、初段に戻ったときのフィルタ係数開始位置を合わせるために用いるものであり、フィルタ演算には使用しないため、例えば、0とすることができる。ダミーデータDDが付加されたフィルタ係数は、リングバッファ形式で係数メモリ113に格納される。

【0040】

係数メモリ113に格納されたフィルタ係数は、クロックCK2に同期してフィルタ係数C1として読み出され、初段の演算装置112に入力されるとともに、2段目の係数バッファメモリ123aに入力される。

【0041】

本実施形態では、フィルタ演算のタップ数TNを39としているため、図2に示すように、係数メモリ113からは、フィルタ係数C1としてc0〜c38がクロックCK2に同期して順次出力され(時刻t0〜時刻t3)、その後、9個のダミーデータDDが出力されることになる(時刻t3〜時刻t4)。

【0042】

係数メモリ113は、リングバッファ形式でフィルタ係数を格納するため、以降は、フィルタ係数C1として、c0〜c38の出力と、9個のダミーデータDDの出力とが繰り返される(時刻t4〜)。

【0043】

図1の説明に戻って、初段の演算ユニットにおいて、演算装置112は、バッファメモリ111から出力されたデータD1と、係数メモリ113から出力されたフィルタ係数C1とを用いてフィルタ演算を行ない、演算結果をスイッチ回路150に出力する。

【0044】

本実施形態では、図2に示すように、時刻t0から時刻t3において、d0×c0+d1×c1+d2×c2…+d37×c37+d38×c38のフィルタ演算が行なわれ、d0〜d38に対するタップ数TN39のフィルタリング処理後のデータfD0が算出される。

【0045】

時刻t3から時刻t4は、ダミーデータDDであるため、フィルタ演算結果には影響を与えない。時刻t4からは、d12×c0+d13×c1+d14×c2…+d49×c37+d50×c38のフィルタ演算が行なわれ、d12〜d50に対するタップ数TN39のフィルタリング処理後のデータfD12が算出される。

【0046】

図1の説明に戻って、2段目以降の演算ユニットnにおいて、バッファメモリ121には、初段のバッファメモリ111あるいは前段のバッファメモリ121から読み出されたデータD(n−1)とクロックCK2とが入力される。バッファメモリ121は、クロックCK2に同期して入力されたデータD(n−1)を、一時的に格納した後、クロックCK2に同期して、データDnとして同段の演算装置122に出力するとともに、次段の演算ユニットのバッファメモリ121に出力する。

【0047】

バッファメモリ121は、例えば、FIFOメモリで構成することができる。バッファメモリ121の遅延量DBは、

遅延量DB=デシメーション比DR×クロック比CR−デシメーション比DR

と設定する。

【0048】

例えば、デシメーション比DRを3とした場合、クロック比CRが4であれば、バッファメモリ121の遅延量DBは、クロックCK2で3×4−3=9クロック分と定められる。また、デシメーション比DRを10とした場合、クロック比CRが8であれば、バッファメモリ121の遅延量DBは、10×8−10=70クロック分と定められる。

【0049】

本実施形態では、2段目以降のバッファメモリ121の遅延量DBは9となるため、図2に示すように2段目のバッファメモリ121aの出力D2は、初段のバッファメモリ121の出力D1から9クロック遅れて出力される(時刻t1)。

【0050】

図1の説明に戻って、2段目以降の演算ユニットnにおいて、係数バッファメモリ123は、初段の係数メモリ113あるいは前段の係数バッファメモリ123から読み出されたフィルタ係数C(n−1)とクロックCK2とが入力される。係数バッファメモリ123は、クロックCK2に同期して入力されたフィルタ係数C(n−1)を、一時的に格納した後、クロックCK2に同期して、フィルタ係数Cnとして同段の演算装置122に出力するとともに、次段の演算ユニットの係数バッファメモリ123に出力する。

【0051】

係数バッファメモリ123は、例えば、FIFOメモリで構成することができる。係数バッファメモリ123の遅延量DCは、

遅延量DC=デシメーション比DR×クロック比CR

と設定する。

【0052】

本実施形態では、2段目以降の係数バッファメモリ123の遅延量は、12となるため、図2に示すように2段目の係数バッファメモリ123aの出力C2は、1段目の係数メモリ113の出力C1から12クロック遅れて出力される(時刻t2)。

【0053】

図1の説明に戻って、2段目以降の演算ユニットnにおいて演算装置122は、バッファメモリ121から出力されたデータDnと、係数バッファメモリ123から出力されたフィルタ係数Cnとを用いてフィルタ演算を行ない、演算結果をスイッチ回路150に出力する。

【0054】

本実施形態では、2段目の演算装置122aは、図2に示すように、時刻t2から時刻t5において、d3×c0+d4×c1+d5×c2…+d40×c37+d41×c38のフィルタ演算が行なわれ、d3〜d41に対するタップ数TN39のフィルタリング処理後のデータfD3が算出される。時刻t1から時刻t2は、データD2としてd0、d1、d2が入力されるが、2段目の演算装置122aが時刻t2から演算を開始することで、フィルタ演算結果には影響を与えないようになっている。

【0055】

同様に、3段目の演算装置122bでは、d6〜d44に対するフィルタリング処理後のデータfD6が算出され、4段目の演算装置122cでは、d9〜d47に対するフィルタリング処理後のデータfD9が順次算出される。

【0056】

その後は、1段目の演算装置112で、d12〜d51に対するフィルタリング処理後のデータfD12が算出され、2段目の演算装置122aで、d15〜d54に対するフィルタリング処理後のデータfD15が算出されていく。図3(a)は、デシメーション比毎のフィルタリング処理後のデータが順次生成されている様子を模式的に示している。

【0057】

これらのフィルタリング処理後のデータfD0、fD3、fD6、fD9、fD12、fD15…を、スイッチ回路150が第2サンプリング周波数で順次出力することで、第1サンプリング周波数の入力信号S1が、デシメーション比DRが3である第2サンプリング周波数の信号S2に変換されることになる。

【0058】

このように、本実施形態のデシメーションフィルタ100では、バッファメモリと演算装置とを備えた演算ユニットを複数段連結し、デシメーション比の個数分入力データをずらしたフィルタ演算を行なうようにすることで、少ない演算装置で多くのタップ数のフィルタ演算を行なえるようにし、優れたフィルタ特性を得るようにしている。

【0059】

図1の例では、4個の演算装置で39タップのフィルタ演算を実現しており、少ない演算装置では、同条件で12タップ程度しか実現できなかった従来のデシメーションフィルタと比較して大幅にフィルタ特性が改善されている。もちろん、演算装置の数は4個に限られず、タップ数やデシメーション比等の条件によって2個で十分の場合もあれば、8個必要となる場合もあり得る。

【0060】

本実施形態のデシメーションフィルタ100では、演算ユニットを増やすことで、容易にフィルタ演算のタップ数を増やすことが可能であり、十分な帯域特性を有するデシメーションフィルタを、多量の演算装置を用いることなく実現することができ、回路コストや消費電力を削減することができる。

【0061】

また、タップ数やデシメーション比等に応じて複数備えた演算装置の一部を用いてデシメーションフィルタを構成してもよく、この場合、消費電力を一層削減することができる。なお、クロック比CRを高くすれば、演算ユニットの数をさらに少なくすることができる。

【0062】

なお、上述の例では、2段目以降のバッファメモリ221に、デシメーション比DRとクロック比CRとで定められる遅延量DBを与えていたが、これらのバッファメモリを初段のバッファメモリ111と並列に接続して、それぞれのバッファメモリから初段のバッファメモリ111と同様の読み出し出し順で、タイミングをずらしてそれぞれの演算装置にデータDnを出力するようにしてもよい。

【0063】

図4は、2段目以降のバッファメモリを初段のバッファメモリ111と並列に接続した場合の構成例を示すブロック図である。図1の構成と同じブロックについては同じ符号を付して、説明を省略する。

【0064】

本図に示すように、2段目以降のバッファメモリ221には、入力信号S1と、クロックCK1と、クロックCK2とが入力される。バッファメモリ221は、クロックCK1に同期して入力された入力信号S1を一時的に格納した後、クロックCK2に同期して選択的にD2、D3、D4として出力する。このため、バッファメモリ221は、デュアルポートメモリを用いることが好ましい。

【0065】

バッファメモリ111とバッファメモリ221とが選択的に出力するデータD1、D2、D3、D4は、メモリコントローラ214により制御される。

【0066】

メモリコントローラ214は、バッファメモリ221に対してバッファメモリ111と同じ読み出し出し順でデータD2を出力させるが、2段目のバッファメモリ221aは、初段のバッファメモリ111よりも、デシメーション比DR×クロック比CR−デシメーション比DRクロック分タイミングを遅らせる。

【0067】

3段目以降のバッファメモリ221についても、バッファメモリ111と同じ読み出し出し順でデータDnを出力させるが、前段のバッファメモリ221よりも、デシメーション比DR×クロック比CR−デシメーション比DRクロック分タイミングを遅らせる。このような制御を行なうことにより、図2に示したタイミングと同様のタイミングでデータDnを出力することができるようになる。

【0068】

さらに、図4に示した構成では、バッファメモリ111とバッファメモリ221は、次段以降で用いるデータを出力せずに、自段の演算ユニットで用いるデータのみを出力すればよいため、図3(b)に示すようなタイミングでフィルタ演算を行なうことができる。係数メモリ113のダミーデータDDも不要である。

【0069】

このとき、上述の例とは逆に、1段目のバッファメモリ111のデータ出力および2段目、3段目のバッファメモリ221の出力を、4段目のバッファメモリ221cのデータ出力タイミングに揃えるように遅らせるようにしてもよい。この場合、係数メモリc113から出力されるフィルタ係数Cnを同じタイミングで共通に使用することができるため、係数バッファメモリ123a、123b、123cを省くことができる。

【0070】

また、上述の例では、2段目以降の演算ユニットに、係数バッファメモリ123を備えさせ、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力するようにしていたが、係数バッファメモリ123に代えて、初段と同様の係数メモリ113を備えさせるようにしてもよい。

【0071】

この場合、図4に示したメモリコントローラ214がそれぞれの係数メモリ113に対して、図2あるいは図3(b)に示すようなタイミングで、各バッファメモリ111、121、221の出力データに対応するフィルタ係数Cnを出力するように制御すればよい。あるいは、出力を開始するフィルタ係数を各段の係数メモリ113毎にずらすようにしてもよい。

【符号の説明】

【0072】

10…デシメータ、100…デシメーションフィルタ、111…バッファメモリ、112…演算装置、113…係数メモリ、114…メモリコントローラ、121…バッファメモリ、122…演算装置、123…係数バッファメモリ、150…スイッチ回路、214…メモリコントローラ、221…バッファメモリ、300…デシメータ、310…デシメーションフィルタ、311…バッファメモリ、312…係数メモリ、313…演算装置、314…タイミング制御回路、320…スイッチ回路、400…デシメータ、410…デシメーションフィルタ、411…係数メモリ、412…演算装置、420…スイッチ回路

【特許請求の範囲】

【請求項1】

第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、

前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、

前段の演算ユニットのバッファメモリが出力したデータを遅延して出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とするデシメーションフィルタ。

【請求項2】

前記初段の演算ユニットのバッファメモリは、

前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力する動作を繰り返すことを特徴とする請求項1に記載のデシメーションフィルタ。

【請求項3】

前記係数メモリは、

前記フィルタ演算のタップ数分のフィルタ係数の後にデシメーション比×(演算ユニット段数−1)個のダミーデータDDを付加したものを前記フィルタ係数としてリングバッファ形式で出力することを特徴とする請求項1または2に記載のデシメーションフィルタ。

【請求項4】

前記2段目以降の演算ユニットのバッファメモリは、

前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の演算ユニットのバッファメモリが出力したデータを、(デシメーション比×クロック比−デシメーション比)分遅延して出力することを特徴とする請求項1〜3のいずれか1項に記載のデシメーションフィルタ。

【請求項5】

前記係数バッファメモリは、

前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を、(デシメーション比×クロック比)分遅延して出力することを特徴とする請求項1〜4のいずれか1項に記載のデシメーションフィルタ。

【請求項6】

第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、

前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、

前記第1信号を入力し、段数に応じた遅延量で選択的に出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とするデシメーションフィルタ。

【請求項7】

前記各段の演算ユニットのバッファメモリは、

前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力する動作を繰り返すことを特徴とする請求項6に記載のデシメーションフィルタ。

【請求項8】

前記2段目以降の演算ユニットにおいて、

前記係数バッファメモリに代えて、リングバッファ形式でフィルタ係数を出力する係数メモリを備え、

前記演算装置は、自段のバッファメモリが出力したデータと自段の係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうことを特徴とする請求項1〜7のいずれか1項に記載のデシメーションフィルタ。

【請求項9】

前記2段目以降の演算ユニットにおいて、

前記係数バッファメモリを省き、

前記演算装置は、自段のバッファメモリが出力したデータと前記初段の演算ユニットが備える係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうことを特徴とする請求項6または7に記載のデシメーションフィルタ。

【請求項1】

第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、

前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、

前段の演算ユニットのバッファメモリが出力したデータを遅延して出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とするデシメーションフィルタ。

【請求項2】

前記初段の演算ユニットのバッファメモリは、

前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから前記フィルタ演算のタップ数+デシメーション比×(演算ユニット段数−1)個のデータを出力する動作を繰り返すことを特徴とする請求項1に記載のデシメーションフィルタ。

【請求項3】

前記係数メモリは、

前記フィルタ演算のタップ数分のフィルタ係数の後にデシメーション比×(演算ユニット段数−1)個のダミーデータDDを付加したものを前記フィルタ係数としてリングバッファ形式で出力することを特徴とする請求項1または2に記載のデシメーションフィルタ。

【請求項4】

前記2段目以降の演算ユニットのバッファメモリは、

前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の演算ユニットのバッファメモリが出力したデータを、(デシメーション比×クロック比−デシメーション比)分遅延して出力することを特徴とする請求項1〜3のいずれか1項に記載のデシメーションフィルタ。

【請求項5】

前記係数バッファメモリは、

前記第1サンプリング周波数と、前記バッファメモリの読み出しクロック周波数との比をクロック比と称した場合、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を、(デシメーション比×クロック比)分遅延して出力することを特徴とする請求項1〜4のいずれか1項に記載のデシメーションフィルタ。

【請求項6】

第1サンプリング周波数でサンプリングされた第1信号を、前記第1サンプリング周波数より低い第2サンプリング周波数の第2信号に変換するためのデシメーションフィルタであって、

前記第1信号を入力し、選択的に出力するバッファメモリと、リングバッファ形式でフィルタ係数を出力する係数メモリと、前記バッファメモリが出力したデータと前記係数メモリが出力したフィルタ係数とを用いてフィルタ演算を行なう演算装置とを有する初段の演算ユニットと、

前記第1信号を入力し、段数に応じた遅延量で選択的に出力するバッファメモリと、前段の係数メモリあるいは係数バッファメモリが出力したフィルタ係数を遅延して出力する係数バッファメモリと、自段のバッファメモリが出力したデータと自段の係数バッファメモリが出力したフィルタ係数を用いてフィルタ演算を行なう演算装置とを有する、1または複数個の2段目以降の演算ユニットとを備えたことを特徴とするデシメーションフィルタ。

【請求項7】

前記各段の演算ユニットのバッファメモリは、

前記第1信号として入力されるd0、d1、d2…に対して、開始データsdとしてd0を設定し、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力した後、(開始データsdからデシメーション比×演算ユニット段数)番目のデータに戻って、そのデータを開始データsdと設定して、開始データsdから少なくとも前記フィルタ演算のタップ数個のデータを出力する動作を繰り返すことを特徴とする請求項6に記載のデシメーションフィルタ。

【請求項8】

前記2段目以降の演算ユニットにおいて、

前記係数バッファメモリに代えて、リングバッファ形式でフィルタ係数を出力する係数メモリを備え、

前記演算装置は、自段のバッファメモリが出力したデータと自段の係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうことを特徴とする請求項1〜7のいずれか1項に記載のデシメーションフィルタ。

【請求項9】

前記2段目以降の演算ユニットにおいて、

前記係数バッファメモリを省き、

前記演算装置は、自段のバッファメモリが出力したデータと前記初段の演算ユニットが備える係数メモリが出力したフィルタ係数を用いてフィルタ演算を行なうことを特徴とする請求項6または7に記載のデシメーションフィルタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−227594(P2012−227594A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−91019(P2011−91019)

【出願日】平成23年4月15日(2011.4.15)

【出願人】(000006507)横河電機株式会社 (4,443)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月15日(2011.4.15)

【出願人】(000006507)横河電機株式会社 (4,443)

[ Back to top ]