デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デシリアライザに関する。

【背景技術】

【0002】

近年、ディスプレイ、カメラ、複写機、プリンタ、医療機器、通信機器などの様々な機器において大容量のデータが扱われるようになり、パラレルデータによるデータ転送方式が採用されるようになった。もっとも、パラレルデータによるデータ転送方式は、多ビットのデータをパラレルに処理するものであり、転送効率が向上する一方で、信号ラインを増やさなければならないといった制約もある。このため、一般的には、パラレルデータをシリアルデータに変換し、あるいはシリアルデータをパラレルデータに変換して送受信するSERDES(SERializer/DESerializer)が併用される。

【0003】

SERDESによるデータ転送方式には、クロックに関する方式として主に3つの方式がある。データとは別にクロックを併走させる「チャネルリンクSERDES」、クロックをシリアルデータに埋め込む「エンベデット・クロックSERDES」、8ビットのパラレルデータを10ビットのシリアルデータにコード変換する「8b10bSERDES」である。「8b10bSERDES」は、コード変換によって特定回数の信号遷移を保障することでクロックを復元する。

【0004】

上記した3つの方式の内、「エンベデット・クロックSERDES」および「8b10bSERDES」のデシリアライザは、クロックの復元同期を行うCDR(Clock Data Recovery)回路として、PLL(Phase Locked Loop)回路を用いている(例えば、図5の「PLL部」を参照)。また、PLL回路は、図6や図7に示すように、クロックを復元する。図5〜図7は、従来技術を説明するための図である。

【0005】

なお、従来、SERDESによるデータ転送方式に関連して、差動クロック位相の正負信号を調整する技術や、パラレルデータへの変換後に遅延量を調整する技術などが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−297404号公報

【特許文献2】特開2005−33701号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記した従来の技術では、クロックの同期のためにPLL回路を用いなければならず、実装上の制約が大きくなってしまうという課題があった。

【0008】

具体的には、例えば、装置が多数のSERDES回線を備えたとする。FPGA(Field Programmable Gate Array)などのASIC(Application Specific Integrated Circuit)内にデシリアライザを搭載しようとしても、PLL回路の数は有限であり、PLL回路が足りないといったリソース不足が発生する。すると、例えば図8に示すように、専用IC(Integrated Circuit)や専用LSI(Large Scale Integration)をSERDES回線の回線数に応じて搭載することになるが、消費電力が増大し、実装面積も増大してしまう。

【0009】

また、パラレルデータを受信する側となるASICにおいて、パラレルインタフェースを圧迫することにもなり、パラレルインタフェースの多い部品を採用するとなれば、コストにも影響がある。さらに、パラレルインタフェースのパターンがプリント板に多く配線されることになり、プリント板の配線層数も増大してしまう。なお、差動クロック位相の正負信号を調整する技術や遅延量を調整する技術は、上記した課題を解決するものではない。

【0010】

開示の技術は、上記に鑑みてなされたものであって、PLL回路を用いずにクロックを同期させることが可能なデシリアライザを提供することを目的とする。

【課題を解決するための手段】

【0011】

本願の開示するデシリアライザは、一つの態様において、入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する異位相データ生成部を備えたことを特徴とする。また、デシリアライザは、前記異位相データ生成部によって生成された複数のシリアルデータそれぞれの位相と、発振器によって発振されたクロックの位相とを比較する位相比較部を備えたことを特徴とする。また、デシリアライザは、前記位相比較部による比較結果に基づいて、前記発振器によって発振されたクロックとの同期に適したシリアルデータを選択するデータ選択部を備えたことを特徴とする。

【発明の効果】

【0012】

本願の開示するデシリアライザの一つの態様によれば、PLL回路を用いずにクロックを同期させることが可能になるという効果を奏する。

【図面の簡単な説明】

【0013】

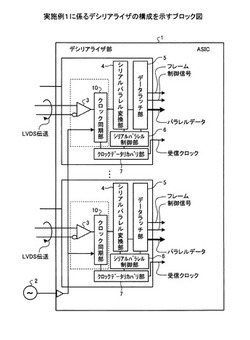

【図1】図1は、実施例1に係るデシリアライザの構成を示すブロック図である。

【図2】図2は、実施例1におけるクロック同期部の構成を示すブロック図である。

【図3】図3は、データ位相コントロール部を説明するための図である。

【図4】図4は、実施例1におけるデータ位相コントロール処理を示すフローチャートである。

【図5】図5は、従来技術を説明するための図である。

【図6】図6は、従来技術を説明するための図である。

【図7】図7は、従来技術を説明するための図である。

【図8】図8は、従来技術を説明するための図である。

【発明を実施するための形態】

【0014】

以下に、本願の開示するデシリアライザの実施例を図面に基づいて詳細に説明する。なお、本実施例により本発明が限定されるものではない。

【実施例1】

【0015】

[実施例1に係るデシリアライザの構成]

まず、図1〜図3を用いて、実施例1に係るデシリアライザの構成を説明する。図1は、実施例1に係るデシリアライザの構成を示すブロック図である。なお、実施例1においては、装置が多数のSERDES回線を備えた場合を説明するが、これに限られるものではなく、SERDES回線が単数である場合にも同様に適用することができる。

【0016】

実施例1に係るデシリアライザは、後述するように、PLL回路を用いずにクロックを同期させるものである。このため、実施例1におけるASICは、図1に示すように、クロック同期の機能を有するデシリアライザ部1をASIC内に搭載する。このように、ASIC内にデシリアライザ部1を搭載する場合には、専用ICや専用LSIをSERDES回線の回線数に応じて搭載する必要がなくなるので、消費電力や実装面積、インタフェース、コスト、プリント板の配線層数などの増大が解消される。もっとも、ASICの外部にLVDS(Low Voltage Differential Signaling)変換部3とクロック同期部10、ならびに発振器2を搭載する構成を採用することもできる。

【0017】

また、図8に示した従来技術のデシリアライザと比較すると明らかなように、実施例1におけるデシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。なお、実施例1における発振器2は、デシリアライザ部1に外付けされている。本図では、発振器2を外付けしているが、デシリアライザ部1内に搭載する構成を採用することもできる。

【0018】

以下、図1に示す各部の機能を説明する。

【0019】

発振器2は、クロック同期部10と接続され、クロックを発振する。

【0020】

LVDS変換部3は、シリアライザ側の伝送路とクロック同期部10と接続される。LVDS変換部3は、LVDSレベルに変換されたシリアルデータの入力を伝送路から受け付け、CMOS(Complementary Metal Oxide Semiconductor)レベルもしくはTTL(Transistor Transistor Logic)レベルに変換し、クロック同期部10に出力する。

【0021】

シリアルパラレル変換部4は、クロック同期部10とデータラッチ部5とシリアルパラレル制御部6と接続される。シリアルパラレル変換部4は、クロックと同期されたシリアルデータの入力をクロック同期部10から受け付け、シリアルデータと同期されたクロックの入力をシリアルパラレル制御部6から受け付ける。また、シリアルパラレル変換部4は、シリアルデータをクロックによってシフトレジスタにラッチし、シリアルパラレル制御部6の制御によってパラレルデータへ変換し、データラッチ部5に出力する。

【0022】

データラッチ部5は、シリアルパラレル変換部4とシリアルパラレル制御部6と接続され、パラレルデータの入力をシリアルパラレル変換部4から受け付け、シリアルパラレル制御部6からの制御によってパラレルデータをラッチし、出力する。

【0023】

シリアルパラレル制御部6は、クロックデータリカバリ部7とシリアルパラレル変換部4とデータラッチ部5と接続される。シリアルパラレル制御部6は、クロックデータリカバリ部7と合わせ、シリアルパラレル変換部4のシフトレジスタに展開されたデータから先頭データを確認し、パラレルデータに変換する制御をシリアルパラレル変換部4に対しておこなう。また、データラッチ部5に送られたパラレルデータのラッチタイミングを生成し、データラッチ部5に出力する。

【0024】

クロックデータリカバリ部7は、クロック同期部10とシリアルパラレル制御部6と接続される。クロックデータリカバリ部7は、シリアルパラレル制御部6経由で、シリアルパラレル変換部4のシフトレジスタにラッチされたデータより先頭データを見つけ出し、データの復号化を行う。

【0025】

クロック同期部10は、発振器2とLVDS変換部3とクロックデータリカバリ部7とシリアルパラレル変換部4と接続される。クロック同期部10は、CMOSレベルもしくはTTLレベルに変換されたシリアルデータの入力をLVDS変換部3から受け付ける。また、クロック同期部10は、クロックを発振器2から受け付け、シリアルデータと同期されたクロックをクロックデータリカバリ部7に出力するとともに、クロックと同期されたシリアルデータをシリアルパラレル変換部4に出力する。

【0026】

ここで、図2および図3を用いて、クロック同期部10の構成を詳細に説明する。図2は、実施例1におけるクロック同期部の構成を説明するための図であり、図3は、データ位相コントロール部を説明するための図である。

【0027】

図2に示すように、クロック同期部10は、シリアルデータ遅延部11と、1:8セレクタ部12と、データ位相コントロール部13と、1:2セレクタ部14と、D−FF(Delay−FlipFlop)部15とを備える。

【0028】

シリアルデータ遅延部11は、LVDS変換部3と1:8セレクタ部12とデータ位相コントロール部13と接続される。具体的には、シリアルデータ遅延部11は、CMOSレベルもしくはTTLレベルに変換されたシリアルデータの入力をLVDS変換部3から受け付け、シリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する。また、シリアルデータ遅延部11は、生成した複数のシリアルデータを1:8セレクタ部12とデータ位相コントロール部13とに出力する。

【0029】

具体的には、シリアルデータ遅延部11は、遅延させないシリアルデータをそのまま伝送する線と幾種類かの遅延線とによって、シリアルデータの1ビット分を例えば8分割し、位相の異なる8つのデータ(D0、D1、・・・、D7)を生成する。なお、実施例1においては、遅延線によってシリアルデータを段階的に遅延させる手法を説明したが、これに限られるものではなく、例えばバッファなどの半導体素子を用いることで遅延させてもよい。

【0030】

また、実施例1においては、分割比として8分割を例に説明する。これは、データの同期を取るために、データの送信周波数の8倍以上周波数でサンプリングを行って同期をとるという考え方から採用するものであるが、これに限られるものではなく、8分割よりも少ない分割比であっても、あるいは多い分割比であってもよい。少ない分割比である場合、例えば4分割である場合には、1/4位相分ずれない限り同期外れと判定されないため、精度は低下してしまう。一方、多い分割比である場合には、その分、精度は向上する。

【0031】

1:8セレクタ部12は、シリアルデータ遅延部11とデータ位相コントロール部13とD−FF部15と接続される。具体的には、1:8セレクタ部12は、位相の異なる8つのデータの入力をシリアルデータ遅延部11から受け付け、また、どの位相のシリアルデータを選択すべきであるかを指示する1:8セレクト信号の入力をデータ位相コントロール部13から受け付ける。また、1:8セレクタ部12は、1:8セレクト信号によって指示された位相のシリアルデータを選択し、D−FF部15に出力する。

【0032】

データ位相コントロール部13は、発振器2とシリアルデータ遅延部11と1:8セレクタ部12と1:2セレクタ部14と接続される。具体的には、データ位相コントロール部13は、クロックの入力を発振器2から受け付け、位相の異なる8つのシリアルデータの入力をシリアルデータ遅延部11から受け付ける。また、データ位相コントロール部13は、位相の異なる8つのシリアルデータの内、どの位相のシリアルデータを選択すべきであるかを指示する1:8セレクト信号を生成し、1:8セレクタ部12に出力する。また、データ位相コントロール部13は、正位相のクロックと正位相のクロックを反転させた逆位相のクロックとのどちらのクロックを選択すべきであるかを指示するクロックセレクト信号を生成し、1:2セレクタ部14に出力する。

【0033】

ここで、データ位相コントロール部13による処理について、図3を用いて説明する。まず、図3の(A)は、シリアルデータ遅延部11によって生成された位相の異なる8つのシリアルデータ(D0、D1、・・・、D7)を例示するものである。また、図3の(B)は、正位相のクロック(受信クロック)を点線で例示し、逆位相のクロック(反転クロック)を実線で例示するものである。

【0034】

ところで、データ位相コントロール部13は、シリアルデータ遅延部11によって生成された8つのシリアルデータそれぞれの位相と、受信クロックあるいは反転クロックそれぞれの位相とを比較し、比較結果に基づいて、クロックの同期に適したシリアルデータを選択する。この時、実施例1におけるデータ位相コントロール部13は、受信クロックあるいは反転クロックの位相がL(Low)からH(High)に変位するタイミングがシリアルデータの中心(1ビットの1/2τ程度)になるようなクロックとシリアルデータとの組合せを選択する。すなわち、データ位相コントロール部13は、どのシリアルデータのところで受信クロックあるいは反転クロックの立ち上がりが入ってくるかをみている。

【0035】

例えば、図3の(B)に示すクロックの場合、受信クロックあるいは反転クロックの位相がLからHに変位するタイミング(位相変化点)は、「2」および「6」である。

【0036】

また、(C)に示す組合せでは、反転クロックとシリアルデータD2との組合せを選択している。この組合せにおいては、図3の(C)に示すように、シリアルデータD2の中心あたりに反転クロックの位相変化点が位置している。また、(D)に示す組合せでは、受信クロックとシリアルデータD0との組合せを選択している。この組合せにおいては、図3の(D)に示すように、シリアルデータD0の中心あたりに受信クロックの位相変化点が位置している。

【0037】

なお、実施例1においては、受信クロックあるいは反転クロックの位相がLからHに変位するタイミングがシリアルデータの中心になるようなクロックとシリアルデータとの組合せを選択する手法を説明したが、これに限られるものではない。対象となるデバイスのSETUP/HOLDのタイミングに問題がなければ、必ずしも中心を選択する手法でなくてもよい。すなわち、D−FF部15が所定のシリアルデータを所定のクロックにてラッチし、クロック同期を行ってクロックに同期されたシリアルデータを出力するタイミングに十分なマージンを持てるのであれば、必ずしも中心を選択する手法でなくてもよいということになる。

【0038】

1:2セレクタ部14は、発振器2とD−FF部15と接続される。具体的には、1:2セレクタ部14は、クロックの入力を発振器2から受け付け、正位相のクロックと逆位相のクロックとを生成する。また、1:2セレクタ部14は、正位相のクロックと逆位相のクロックとのどちらのクロックを選択すべきであるかを指示するクロックセレクト信号の入力をデータ位相コントロール部13から受け付ける。また、1:2セレクタ部14は、クロックセレクト信号によって指示されたクロックを選択し、シリアルデータと同期されたクロック(同期クロック)としてクロックデータリカバリ部7に出力する。

【0039】

D−FF部15は、1:8セレクタ部12と1:2セレクタ部14とシリアルパラレル変換部4と接続される。具体的には、D−FF部15は、クロックとの同期に適したシリアルデータの入力を1:8セレクタ部12から受け付け、シリアルデータとの同期に適したクロックの入力を1:2セレクタ部14から受け付ける。また、D−FF部15は、受け付けたシリアルデータを、受け付けたクロックにてラッチし、クロック同期を行って、クロックに同期されたシリアルデータをシリアルパラレル変換部4に出力する。

【0040】

[実施例1におけるデータ位相コントロール部による処理手順]

さて、上記したデータ位相コントロール部13による処理は、ワイヤードロジックによるハードウェアとして実現してもよいし、CPU(Central Processing Unit)にて解析実行されるプログラムとして実行してもよい。図4を用いて、データ位相コントロール部13による処理がプログラムとして実行される場合について説明する。図4は、実施例1におけるデータ位相コントロール処理を示すフローチャートである。

【0041】

図4に示すように、データ位相コントロール部13は、発振器2から入力を受け付けたクロック(受信クロック)について、位相変化点を検出したか否かを判定している(ステップS101)。

【0042】

例えば、データ位相コントロール部13は、シリアルデータ遅延部11から受け付けた位相の異なる8つのデータのエッジを用い、位相変化点を検出する。例えば、データ位相コントロール部13は、シリアルデータD1のエッジでクロックを確認した場合に位相が「L」で、シリアルデータD2のエッジで確認した場合に「H」であれば、シリアルデータD1とシリアルデータD2との間に位相変化点を検出する。なお、データ位相コントロール部13は、受信クロックのみを用いて反転クロックの位相変化点も検出するので、「L」から「H」に変位する場合のみならず、「H」から「L」に変位する場合も検出する。

【0043】

位相変化点を検出していない場合には(ステップS101否定)、データ位相コントロール部13は、位相変化点を検出したか否かを判定する処理に戻る。一方、位相変化点を検出した場合には(ステップS101肯定)、データ位相コントロール部13は、受信クロックあるいは反転クロックの位相変化点がシリアルデータの中心になるようなシリアルデータおよびクロックの組合せを選択する(ステップS102)。

【0044】

そして、データ位相コントロール部13は、ステップS102において選択したシリアルデータおよびクロックの組合せについて、セレクト信号を生成し、1:8セレクタ部12に出力する(ステップS103)。具体的には、データ位相コントロール部13は、どの位相のシリアルデータを選択すべきであるかを指示する1:8セレクト信号を生成し、受信クロックと反転クロックとのどちらのクロックを選択すべきであるかを指示するクロックセレクト信号を生成する。データ位相コントロール部13は、シリアルデータに対して受信クロックの立ち下がり(「H」から「L」への変位)が最適な場合は反転クロックを選択するクロックセレクト信号を生成し、受信クロックの立ち上がり(「L」から「H」への変位)が最適な場合は、受信クロックを選択するクロックセレクト信号を生成する。

【0045】

ここで、実施例1においては、データ位相コントロール部13による処理がプログラムとして実行される場合を想定するので、データ位相コントロール部13は、一旦選択した組合せを維持し、同期外れや位相ずれを検出した場合にのみ、選択をやり直す。

【0046】

すなわち、データ位相コントロール部13は、同期外れおよび位相ずれを確認し(ステップS104)、同期外れを検出した場合には(ステップS105肯定)、ステップS101の処理に戻る。同期外れの検出について具体的に説明すると、SERDESの特性上、シリアルデータ内には、クロック復元のため規定数以内にデータレベルの変位が発生するはずである。このため、データ位相コントロール部13は、シリアルデータが規定数以上「H」のまま、あるいは「L」のまま連続して入力され、データレベルの変位がなかった場合に、同期外れを検出する。

【0047】

一方、検出していない場合には(ステップS105否定)、続いて、データ位相コントロール部13は、位相ずれを検出したか否かを判定する(ステップS106)。位相ずれの検出について具体的に説明すると、データ位相コントロール部13は、受信クロックの位相変化点とシリアルデータとの関係が変化した(崩れた)か否かで検出する。すなわち、データ位相コントロール部13は、位相の異なる8つのシリアルデータそれぞれのエッジでクロックを確認する。例えば、それまでシリアルデータD1とシリアルデータD2との間に位相変化点を検出していたのに、シリアルデータD2とシリアルデータD3との間で位相変化点を検出するようになった場合に、位相ずれを検出する。

【0048】

位相ずれを検出した場合には(ステップS106肯定)、データ位相コントロール部13は、位相補正のため、シリアルデータを選択し直し、1:8セレクト信号を生成し直して(ステップS107)、ステップS104に戻る。また、ステップS107において位相ずれを検出していない場合には(ステップS106否定)、データ位相コントロール部13は、ステップS104に戻る。

【0049】

なお、データ位相コントロール部13による処理がハードウェアとして実現される場合には、データ位相コントロール部13は、例えば、シリアルデータを受信するごとに、その都度、シリアルデータおよびクロックを選択し、セレクト信号を生成する。

【0050】

[実施例1の効果]

上記してきたように、実施例1に係るデシリアライザ部1によれば、クロック同期部10が、入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する。次に、クロック同期部10は、生成された複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

【0051】

このようなことから、実施例1によれば、PLL回路を用いずにクロックを同期させることが可能になる。すなわち、従来のデシリアライザは、データから抽出したクロックをPLL回路で復元する手法を用いていた。言い換えると、デシリアライザは、PLL回路を備えることが必須となっていた。この場合には、例えば、装置が多数のSERDES回線を備えると、FPGAなどのASIC内にデシリアライザを搭載しようとしても、PLL回路の数は有限であり、PLL回路が足りないといったリソース不足が発生していた。

【0052】

一方、実施例1によれば、デシリアライザは、データを段階的に遅延させて異位相データを複数生成し、それぞれを発振器のクロック位相と比較して、同期に適したデータを選択するので、PLL回路を用いる必要がない。この結果、例えば、装置が多数のSERDES回線を備えたとしても、PLL回路の数といった制約がなくなり、FPGAなどのASIC内にデシリアライザを搭載することが可能になる。

【0053】

また、デシリアライザがASIC内に搭載されると、ASICへのデータ入力はパラレルデータ入力ではなくシリアルデータ入力となる。この結果、専用ICや専用LSIをSERDES回線の回線数に応じて搭載する必要がなくなるので、消費電力や実装面積、インタフェース、コスト、プリント板の配線層数などの増大も解消される。

【0054】

また、実施例1におけるクロック同期部10は、クロックの位相として、発振器2によって発振された正位相のクロックと、正位相のクロックを反転させた逆位相のクロックとを用いる。例えば、正位相のクロックのみを用いる手法では、クロックの位相が合わない場合があり得るが、2種類のクロックを準備し、いずれかを選択する手法をとることで、より効率的にクロックを選択することが可能になる。

【実施例2】

【0055】

[他の実施例]

さて、これまで本発明の実施例1について説明してきたが、本発明は上述した実施例1以外にも、種々の異なる形態にて実施されてよいものである。

【0056】

具体的には、上記文書中や図面中で示した処理手順(図4など)、具体的名称(図1、図2など)、各種のデータやパラメータを含む情報については、特記する場合を除いて任意に変更することができる。また、図示した各装置の各構成要素は機能概念的なものであり、必ずしも物理的に図示(図1、図2など)の如く構成されていることを要しない。すなわち、各装置の分散・統合の具体的形態は図示のものに限られず、その全部または一部を、各種の負荷や使用状況などに応じて、任意の単位で機能的または物理的に分散・統合して構成することができる。

【0057】

以上の各実施例を含む実施形態に関し、さらに以下の付記を開示する。

【0058】

(付記1)入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する異位相データ生成部と、

前記異位相データ生成部によって生成された複数のシリアルデータそれぞれの位相と、発振器によって発振されたクロックの位相とを比較する位相比較部と、

前記位相比較部による比較結果に基づいて、前記発振器によって発振されたクロックとの同期に適したシリアルデータを選択するデータ選択部と

を備えたことを特徴とするデシリアライザ。

【0059】

(付記2)前記位相比較部は、前記クロックの位相として、前記発振器によって発振された正位相のクロックと、当該正位相のクロックを反転させた逆位相のクロックとを用いることを特徴とする付記1に記載のデシリアライザ。

【0060】

(付記3)前記異位相データ生成部は、遅延器もしくはバッファを用いることで、前記シリアルデータを段階的に遅延させることを特徴とする付記1または2に記載のデシリアライザ。

【0061】

(付記4)前記異位相データ生成部と前記位相比較部と前記データ選択部とが、ASIC内に搭載されることを特徴とする付記1〜3のいずれか一つに記載のデシリアライザ。

【0062】

(付記5)前記発振器が、前記デシリアライザに外付けされることを特徴とする付記1〜4のいずれか一つに記載のデシリアライザ。

【符号の説明】

【0063】

1 デシリアライザ部

2 発振器

3 LVDS変換部

4 シリアルパラレル変換部

5 データラッチ部

6 シリアルパラレル制御部

7 クロックデータリカバリ部

10 クロック同期部

11 シリアルデータ遅延部

12 1:8セレクタ部

13 データ位相コントロール部

14 1:2セレクタ部

15 D−FF部

【技術分野】

【0001】

本発明は、デシリアライザに関する。

【背景技術】

【0002】

近年、ディスプレイ、カメラ、複写機、プリンタ、医療機器、通信機器などの様々な機器において大容量のデータが扱われるようになり、パラレルデータによるデータ転送方式が採用されるようになった。もっとも、パラレルデータによるデータ転送方式は、多ビットのデータをパラレルに処理するものであり、転送効率が向上する一方で、信号ラインを増やさなければならないといった制約もある。このため、一般的には、パラレルデータをシリアルデータに変換し、あるいはシリアルデータをパラレルデータに変換して送受信するSERDES(SERializer/DESerializer)が併用される。

【0003】

SERDESによるデータ転送方式には、クロックに関する方式として主に3つの方式がある。データとは別にクロックを併走させる「チャネルリンクSERDES」、クロックをシリアルデータに埋め込む「エンベデット・クロックSERDES」、8ビットのパラレルデータを10ビットのシリアルデータにコード変換する「8b10bSERDES」である。「8b10bSERDES」は、コード変換によって特定回数の信号遷移を保障することでクロックを復元する。

【0004】

上記した3つの方式の内、「エンベデット・クロックSERDES」および「8b10bSERDES」のデシリアライザは、クロックの復元同期を行うCDR(Clock Data Recovery)回路として、PLL(Phase Locked Loop)回路を用いている(例えば、図5の「PLL部」を参照)。また、PLL回路は、図6や図7に示すように、クロックを復元する。図5〜図7は、従来技術を説明するための図である。

【0005】

なお、従来、SERDESによるデータ転送方式に関連して、差動クロック位相の正負信号を調整する技術や、パラレルデータへの変換後に遅延量を調整する技術などが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−297404号公報

【特許文献2】特開2005−33701号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記した従来の技術では、クロックの同期のためにPLL回路を用いなければならず、実装上の制約が大きくなってしまうという課題があった。

【0008】

具体的には、例えば、装置が多数のSERDES回線を備えたとする。FPGA(Field Programmable Gate Array)などのASIC(Application Specific Integrated Circuit)内にデシリアライザを搭載しようとしても、PLL回路の数は有限であり、PLL回路が足りないといったリソース不足が発生する。すると、例えば図8に示すように、専用IC(Integrated Circuit)や専用LSI(Large Scale Integration)をSERDES回線の回線数に応じて搭載することになるが、消費電力が増大し、実装面積も増大してしまう。

【0009】

また、パラレルデータを受信する側となるASICにおいて、パラレルインタフェースを圧迫することにもなり、パラレルインタフェースの多い部品を採用するとなれば、コストにも影響がある。さらに、パラレルインタフェースのパターンがプリント板に多く配線されることになり、プリント板の配線層数も増大してしまう。なお、差動クロック位相の正負信号を調整する技術や遅延量を調整する技術は、上記した課題を解決するものではない。

【0010】

開示の技術は、上記に鑑みてなされたものであって、PLL回路を用いずにクロックを同期させることが可能なデシリアライザを提供することを目的とする。

【課題を解決するための手段】

【0011】

本願の開示するデシリアライザは、一つの態様において、入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する異位相データ生成部を備えたことを特徴とする。また、デシリアライザは、前記異位相データ生成部によって生成された複数のシリアルデータそれぞれの位相と、発振器によって発振されたクロックの位相とを比較する位相比較部を備えたことを特徴とする。また、デシリアライザは、前記位相比較部による比較結果に基づいて、前記発振器によって発振されたクロックとの同期に適したシリアルデータを選択するデータ選択部を備えたことを特徴とする。

【発明の効果】

【0012】

本願の開示するデシリアライザの一つの態様によれば、PLL回路を用いずにクロックを同期させることが可能になるという効果を奏する。

【図面の簡単な説明】

【0013】

【図1】図1は、実施例1に係るデシリアライザの構成を示すブロック図である。

【図2】図2は、実施例1におけるクロック同期部の構成を示すブロック図である。

【図3】図3は、データ位相コントロール部を説明するための図である。

【図4】図4は、実施例1におけるデータ位相コントロール処理を示すフローチャートである。

【図5】図5は、従来技術を説明するための図である。

【図6】図6は、従来技術を説明するための図である。

【図7】図7は、従来技術を説明するための図である。

【図8】図8は、従来技術を説明するための図である。

【発明を実施するための形態】

【0014】

以下に、本願の開示するデシリアライザの実施例を図面に基づいて詳細に説明する。なお、本実施例により本発明が限定されるものではない。

【実施例1】

【0015】

[実施例1に係るデシリアライザの構成]

まず、図1〜図3を用いて、実施例1に係るデシリアライザの構成を説明する。図1は、実施例1に係るデシリアライザの構成を示すブロック図である。なお、実施例1においては、装置が多数のSERDES回線を備えた場合を説明するが、これに限られるものではなく、SERDES回線が単数である場合にも同様に適用することができる。

【0016】

実施例1に係るデシリアライザは、後述するように、PLL回路を用いずにクロックを同期させるものである。このため、実施例1におけるASICは、図1に示すように、クロック同期の機能を有するデシリアライザ部1をASIC内に搭載する。このように、ASIC内にデシリアライザ部1を搭載する場合には、専用ICや専用LSIをSERDES回線の回線数に応じて搭載する必要がなくなるので、消費電力や実装面積、インタフェース、コスト、プリント板の配線層数などの増大が解消される。もっとも、ASICの外部にLVDS(Low Voltage Differential Signaling)変換部3とクロック同期部10、ならびに発振器2を搭載する構成を採用することもできる。

【0017】

また、図8に示した従来技術のデシリアライザと比較すると明らかなように、実施例1におけるデシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。なお、実施例1における発振器2は、デシリアライザ部1に外付けされている。本図では、発振器2を外付けしているが、デシリアライザ部1内に搭載する構成を採用することもできる。

【0018】

以下、図1に示す各部の機能を説明する。

【0019】

発振器2は、クロック同期部10と接続され、クロックを発振する。

【0020】

LVDS変換部3は、シリアライザ側の伝送路とクロック同期部10と接続される。LVDS変換部3は、LVDSレベルに変換されたシリアルデータの入力を伝送路から受け付け、CMOS(Complementary Metal Oxide Semiconductor)レベルもしくはTTL(Transistor Transistor Logic)レベルに変換し、クロック同期部10に出力する。

【0021】

シリアルパラレル変換部4は、クロック同期部10とデータラッチ部5とシリアルパラレル制御部6と接続される。シリアルパラレル変換部4は、クロックと同期されたシリアルデータの入力をクロック同期部10から受け付け、シリアルデータと同期されたクロックの入力をシリアルパラレル制御部6から受け付ける。また、シリアルパラレル変換部4は、シリアルデータをクロックによってシフトレジスタにラッチし、シリアルパラレル制御部6の制御によってパラレルデータへ変換し、データラッチ部5に出力する。

【0022】

データラッチ部5は、シリアルパラレル変換部4とシリアルパラレル制御部6と接続され、パラレルデータの入力をシリアルパラレル変換部4から受け付け、シリアルパラレル制御部6からの制御によってパラレルデータをラッチし、出力する。

【0023】

シリアルパラレル制御部6は、クロックデータリカバリ部7とシリアルパラレル変換部4とデータラッチ部5と接続される。シリアルパラレル制御部6は、クロックデータリカバリ部7と合わせ、シリアルパラレル変換部4のシフトレジスタに展開されたデータから先頭データを確認し、パラレルデータに変換する制御をシリアルパラレル変換部4に対しておこなう。また、データラッチ部5に送られたパラレルデータのラッチタイミングを生成し、データラッチ部5に出力する。

【0024】

クロックデータリカバリ部7は、クロック同期部10とシリアルパラレル制御部6と接続される。クロックデータリカバリ部7は、シリアルパラレル制御部6経由で、シリアルパラレル変換部4のシフトレジスタにラッチされたデータより先頭データを見つけ出し、データの復号化を行う。

【0025】

クロック同期部10は、発振器2とLVDS変換部3とクロックデータリカバリ部7とシリアルパラレル変換部4と接続される。クロック同期部10は、CMOSレベルもしくはTTLレベルに変換されたシリアルデータの入力をLVDS変換部3から受け付ける。また、クロック同期部10は、クロックを発振器2から受け付け、シリアルデータと同期されたクロックをクロックデータリカバリ部7に出力するとともに、クロックと同期されたシリアルデータをシリアルパラレル変換部4に出力する。

【0026】

ここで、図2および図3を用いて、クロック同期部10の構成を詳細に説明する。図2は、実施例1におけるクロック同期部の構成を説明するための図であり、図3は、データ位相コントロール部を説明するための図である。

【0027】

図2に示すように、クロック同期部10は、シリアルデータ遅延部11と、1:8セレクタ部12と、データ位相コントロール部13と、1:2セレクタ部14と、D−FF(Delay−FlipFlop)部15とを備える。

【0028】

シリアルデータ遅延部11は、LVDS変換部3と1:8セレクタ部12とデータ位相コントロール部13と接続される。具体的には、シリアルデータ遅延部11は、CMOSレベルもしくはTTLレベルに変換されたシリアルデータの入力をLVDS変換部3から受け付け、シリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する。また、シリアルデータ遅延部11は、生成した複数のシリアルデータを1:8セレクタ部12とデータ位相コントロール部13とに出力する。

【0029】

具体的には、シリアルデータ遅延部11は、遅延させないシリアルデータをそのまま伝送する線と幾種類かの遅延線とによって、シリアルデータの1ビット分を例えば8分割し、位相の異なる8つのデータ(D0、D1、・・・、D7)を生成する。なお、実施例1においては、遅延線によってシリアルデータを段階的に遅延させる手法を説明したが、これに限られるものではなく、例えばバッファなどの半導体素子を用いることで遅延させてもよい。

【0030】

また、実施例1においては、分割比として8分割を例に説明する。これは、データの同期を取るために、データの送信周波数の8倍以上周波数でサンプリングを行って同期をとるという考え方から採用するものであるが、これに限られるものではなく、8分割よりも少ない分割比であっても、あるいは多い分割比であってもよい。少ない分割比である場合、例えば4分割である場合には、1/4位相分ずれない限り同期外れと判定されないため、精度は低下してしまう。一方、多い分割比である場合には、その分、精度は向上する。

【0031】

1:8セレクタ部12は、シリアルデータ遅延部11とデータ位相コントロール部13とD−FF部15と接続される。具体的には、1:8セレクタ部12は、位相の異なる8つのデータの入力をシリアルデータ遅延部11から受け付け、また、どの位相のシリアルデータを選択すべきであるかを指示する1:8セレクト信号の入力をデータ位相コントロール部13から受け付ける。また、1:8セレクタ部12は、1:8セレクト信号によって指示された位相のシリアルデータを選択し、D−FF部15に出力する。

【0032】

データ位相コントロール部13は、発振器2とシリアルデータ遅延部11と1:8セレクタ部12と1:2セレクタ部14と接続される。具体的には、データ位相コントロール部13は、クロックの入力を発振器2から受け付け、位相の異なる8つのシリアルデータの入力をシリアルデータ遅延部11から受け付ける。また、データ位相コントロール部13は、位相の異なる8つのシリアルデータの内、どの位相のシリアルデータを選択すべきであるかを指示する1:8セレクト信号を生成し、1:8セレクタ部12に出力する。また、データ位相コントロール部13は、正位相のクロックと正位相のクロックを反転させた逆位相のクロックとのどちらのクロックを選択すべきであるかを指示するクロックセレクト信号を生成し、1:2セレクタ部14に出力する。

【0033】

ここで、データ位相コントロール部13による処理について、図3を用いて説明する。まず、図3の(A)は、シリアルデータ遅延部11によって生成された位相の異なる8つのシリアルデータ(D0、D1、・・・、D7)を例示するものである。また、図3の(B)は、正位相のクロック(受信クロック)を点線で例示し、逆位相のクロック(反転クロック)を実線で例示するものである。

【0034】

ところで、データ位相コントロール部13は、シリアルデータ遅延部11によって生成された8つのシリアルデータそれぞれの位相と、受信クロックあるいは反転クロックそれぞれの位相とを比較し、比較結果に基づいて、クロックの同期に適したシリアルデータを選択する。この時、実施例1におけるデータ位相コントロール部13は、受信クロックあるいは反転クロックの位相がL(Low)からH(High)に変位するタイミングがシリアルデータの中心(1ビットの1/2τ程度)になるようなクロックとシリアルデータとの組合せを選択する。すなわち、データ位相コントロール部13は、どのシリアルデータのところで受信クロックあるいは反転クロックの立ち上がりが入ってくるかをみている。

【0035】

例えば、図3の(B)に示すクロックの場合、受信クロックあるいは反転クロックの位相がLからHに変位するタイミング(位相変化点)は、「2」および「6」である。

【0036】

また、(C)に示す組合せでは、反転クロックとシリアルデータD2との組合せを選択している。この組合せにおいては、図3の(C)に示すように、シリアルデータD2の中心あたりに反転クロックの位相変化点が位置している。また、(D)に示す組合せでは、受信クロックとシリアルデータD0との組合せを選択している。この組合せにおいては、図3の(D)に示すように、シリアルデータD0の中心あたりに受信クロックの位相変化点が位置している。

【0037】

なお、実施例1においては、受信クロックあるいは反転クロックの位相がLからHに変位するタイミングがシリアルデータの中心になるようなクロックとシリアルデータとの組合せを選択する手法を説明したが、これに限られるものではない。対象となるデバイスのSETUP/HOLDのタイミングに問題がなければ、必ずしも中心を選択する手法でなくてもよい。すなわち、D−FF部15が所定のシリアルデータを所定のクロックにてラッチし、クロック同期を行ってクロックに同期されたシリアルデータを出力するタイミングに十分なマージンを持てるのであれば、必ずしも中心を選択する手法でなくてもよいということになる。

【0038】

1:2セレクタ部14は、発振器2とD−FF部15と接続される。具体的には、1:2セレクタ部14は、クロックの入力を発振器2から受け付け、正位相のクロックと逆位相のクロックとを生成する。また、1:2セレクタ部14は、正位相のクロックと逆位相のクロックとのどちらのクロックを選択すべきであるかを指示するクロックセレクト信号の入力をデータ位相コントロール部13から受け付ける。また、1:2セレクタ部14は、クロックセレクト信号によって指示されたクロックを選択し、シリアルデータと同期されたクロック(同期クロック)としてクロックデータリカバリ部7に出力する。

【0039】

D−FF部15は、1:8セレクタ部12と1:2セレクタ部14とシリアルパラレル変換部4と接続される。具体的には、D−FF部15は、クロックとの同期に適したシリアルデータの入力を1:8セレクタ部12から受け付け、シリアルデータとの同期に適したクロックの入力を1:2セレクタ部14から受け付ける。また、D−FF部15は、受け付けたシリアルデータを、受け付けたクロックにてラッチし、クロック同期を行って、クロックに同期されたシリアルデータをシリアルパラレル変換部4に出力する。

【0040】

[実施例1におけるデータ位相コントロール部による処理手順]

さて、上記したデータ位相コントロール部13による処理は、ワイヤードロジックによるハードウェアとして実現してもよいし、CPU(Central Processing Unit)にて解析実行されるプログラムとして実行してもよい。図4を用いて、データ位相コントロール部13による処理がプログラムとして実行される場合について説明する。図4は、実施例1におけるデータ位相コントロール処理を示すフローチャートである。

【0041】

図4に示すように、データ位相コントロール部13は、発振器2から入力を受け付けたクロック(受信クロック)について、位相変化点を検出したか否かを判定している(ステップS101)。

【0042】

例えば、データ位相コントロール部13は、シリアルデータ遅延部11から受け付けた位相の異なる8つのデータのエッジを用い、位相変化点を検出する。例えば、データ位相コントロール部13は、シリアルデータD1のエッジでクロックを確認した場合に位相が「L」で、シリアルデータD2のエッジで確認した場合に「H」であれば、シリアルデータD1とシリアルデータD2との間に位相変化点を検出する。なお、データ位相コントロール部13は、受信クロックのみを用いて反転クロックの位相変化点も検出するので、「L」から「H」に変位する場合のみならず、「H」から「L」に変位する場合も検出する。

【0043】

位相変化点を検出していない場合には(ステップS101否定)、データ位相コントロール部13は、位相変化点を検出したか否かを判定する処理に戻る。一方、位相変化点を検出した場合には(ステップS101肯定)、データ位相コントロール部13は、受信クロックあるいは反転クロックの位相変化点がシリアルデータの中心になるようなシリアルデータおよびクロックの組合せを選択する(ステップS102)。

【0044】

そして、データ位相コントロール部13は、ステップS102において選択したシリアルデータおよびクロックの組合せについて、セレクト信号を生成し、1:8セレクタ部12に出力する(ステップS103)。具体的には、データ位相コントロール部13は、どの位相のシリアルデータを選択すべきであるかを指示する1:8セレクト信号を生成し、受信クロックと反転クロックとのどちらのクロックを選択すべきであるかを指示するクロックセレクト信号を生成する。データ位相コントロール部13は、シリアルデータに対して受信クロックの立ち下がり(「H」から「L」への変位)が最適な場合は反転クロックを選択するクロックセレクト信号を生成し、受信クロックの立ち上がり(「L」から「H」への変位)が最適な場合は、受信クロックを選択するクロックセレクト信号を生成する。

【0045】

ここで、実施例1においては、データ位相コントロール部13による処理がプログラムとして実行される場合を想定するので、データ位相コントロール部13は、一旦選択した組合せを維持し、同期外れや位相ずれを検出した場合にのみ、選択をやり直す。

【0046】

すなわち、データ位相コントロール部13は、同期外れおよび位相ずれを確認し(ステップS104)、同期外れを検出した場合には(ステップS105肯定)、ステップS101の処理に戻る。同期外れの検出について具体的に説明すると、SERDESの特性上、シリアルデータ内には、クロック復元のため規定数以内にデータレベルの変位が発生するはずである。このため、データ位相コントロール部13は、シリアルデータが規定数以上「H」のまま、あるいは「L」のまま連続して入力され、データレベルの変位がなかった場合に、同期外れを検出する。

【0047】

一方、検出していない場合には(ステップS105否定)、続いて、データ位相コントロール部13は、位相ずれを検出したか否かを判定する(ステップS106)。位相ずれの検出について具体的に説明すると、データ位相コントロール部13は、受信クロックの位相変化点とシリアルデータとの関係が変化した(崩れた)か否かで検出する。すなわち、データ位相コントロール部13は、位相の異なる8つのシリアルデータそれぞれのエッジでクロックを確認する。例えば、それまでシリアルデータD1とシリアルデータD2との間に位相変化点を検出していたのに、シリアルデータD2とシリアルデータD3との間で位相変化点を検出するようになった場合に、位相ずれを検出する。

【0048】

位相ずれを検出した場合には(ステップS106肯定)、データ位相コントロール部13は、位相補正のため、シリアルデータを選択し直し、1:8セレクト信号を生成し直して(ステップS107)、ステップS104に戻る。また、ステップS107において位相ずれを検出していない場合には(ステップS106否定)、データ位相コントロール部13は、ステップS104に戻る。

【0049】

なお、データ位相コントロール部13による処理がハードウェアとして実現される場合には、データ位相コントロール部13は、例えば、シリアルデータを受信するごとに、その都度、シリアルデータおよびクロックを選択し、セレクト信号を生成する。

【0050】

[実施例1の効果]

上記してきたように、実施例1に係るデシリアライザ部1によれば、クロック同期部10が、入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する。次に、クロック同期部10は、生成された複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

【0051】

このようなことから、実施例1によれば、PLL回路を用いずにクロックを同期させることが可能になる。すなわち、従来のデシリアライザは、データから抽出したクロックをPLL回路で復元する手法を用いていた。言い換えると、デシリアライザは、PLL回路を備えることが必須となっていた。この場合には、例えば、装置が多数のSERDES回線を備えると、FPGAなどのASIC内にデシリアライザを搭載しようとしても、PLL回路の数は有限であり、PLL回路が足りないといったリソース不足が発生していた。

【0052】

一方、実施例1によれば、デシリアライザは、データを段階的に遅延させて異位相データを複数生成し、それぞれを発振器のクロック位相と比較して、同期に適したデータを選択するので、PLL回路を用いる必要がない。この結果、例えば、装置が多数のSERDES回線を備えたとしても、PLL回路の数といった制約がなくなり、FPGAなどのASIC内にデシリアライザを搭載することが可能になる。

【0053】

また、デシリアライザがASIC内に搭載されると、ASICへのデータ入力はパラレルデータ入力ではなくシリアルデータ入力となる。この結果、専用ICや専用LSIをSERDES回線の回線数に応じて搭載する必要がなくなるので、消費電力や実装面積、インタフェース、コスト、プリント板の配線層数などの増大も解消される。

【0054】

また、実施例1におけるクロック同期部10は、クロックの位相として、発振器2によって発振された正位相のクロックと、正位相のクロックを反転させた逆位相のクロックとを用いる。例えば、正位相のクロックのみを用いる手法では、クロックの位相が合わない場合があり得るが、2種類のクロックを準備し、いずれかを選択する手法をとることで、より効率的にクロックを選択することが可能になる。

【実施例2】

【0055】

[他の実施例]

さて、これまで本発明の実施例1について説明してきたが、本発明は上述した実施例1以外にも、種々の異なる形態にて実施されてよいものである。

【0056】

具体的には、上記文書中や図面中で示した処理手順(図4など)、具体的名称(図1、図2など)、各種のデータやパラメータを含む情報については、特記する場合を除いて任意に変更することができる。また、図示した各装置の各構成要素は機能概念的なものであり、必ずしも物理的に図示(図1、図2など)の如く構成されていることを要しない。すなわち、各装置の分散・統合の具体的形態は図示のものに限られず、その全部または一部を、各種の負荷や使用状況などに応じて、任意の単位で機能的または物理的に分散・統合して構成することができる。

【0057】

以上の各実施例を含む実施形態に関し、さらに以下の付記を開示する。

【0058】

(付記1)入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する異位相データ生成部と、

前記異位相データ生成部によって生成された複数のシリアルデータそれぞれの位相と、発振器によって発振されたクロックの位相とを比較する位相比較部と、

前記位相比較部による比較結果に基づいて、前記発振器によって発振されたクロックとの同期に適したシリアルデータを選択するデータ選択部と

を備えたことを特徴とするデシリアライザ。

【0059】

(付記2)前記位相比較部は、前記クロックの位相として、前記発振器によって発振された正位相のクロックと、当該正位相のクロックを反転させた逆位相のクロックとを用いることを特徴とする付記1に記載のデシリアライザ。

【0060】

(付記3)前記異位相データ生成部は、遅延器もしくはバッファを用いることで、前記シリアルデータを段階的に遅延させることを特徴とする付記1または2に記載のデシリアライザ。

【0061】

(付記4)前記異位相データ生成部と前記位相比較部と前記データ選択部とが、ASIC内に搭載されることを特徴とする付記1〜3のいずれか一つに記載のデシリアライザ。

【0062】

(付記5)前記発振器が、前記デシリアライザに外付けされることを特徴とする付記1〜4のいずれか一つに記載のデシリアライザ。

【符号の説明】

【0063】

1 デシリアライザ部

2 発振器

3 LVDS変換部

4 シリアルパラレル変換部

5 データラッチ部

6 シリアルパラレル制御部

7 クロックデータリカバリ部

10 クロック同期部

11 シリアルデータ遅延部

12 1:8セレクタ部

13 データ位相コントロール部

14 1:2セレクタ部

15 D−FF部

【特許請求の範囲】

【請求項1】

入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する異位相データ生成部と、

前記異位相データ生成部によって生成された複数のシリアルデータそれぞれの位相と、発振器によって発振されたクロックの位相とを比較する位相比較部と、

前記位相比較部による比較結果に基づいて、前記発振器によって発振されたクロックとの同期に適したシリアルデータを選択するデータ選択部と

を備えたことを特徴とするデシリアライザ。

【請求項2】

前記位相比較部は、前記クロックの位相として、前記発振器によって発振された正位相のクロックと、当該正位相のクロックを反転させた逆位相のクロックとを用いることを特徴とする請求項1に記載のデシリアライザ。

【請求項3】

前記異位相データ生成部は、遅延器もしくはバッファを用いることで、前記シリアルデータを段階的に遅延させることを特徴とする請求項1または2に記載のデシリアライザ。

【請求項1】

入力されたシリアルデータを段階的に遅延させることで異なる位相のシリアルデータを複数生成する異位相データ生成部と、

前記異位相データ生成部によって生成された複数のシリアルデータそれぞれの位相と、発振器によって発振されたクロックの位相とを比較する位相比較部と、

前記位相比較部による比較結果に基づいて、前記発振器によって発振されたクロックとの同期に適したシリアルデータを選択するデータ選択部と

を備えたことを特徴とするデシリアライザ。

【請求項2】

前記位相比較部は、前記クロックの位相として、前記発振器によって発振された正位相のクロックと、当該正位相のクロックを反転させた逆位相のクロックとを用いることを特徴とする請求項1に記載のデシリアライザ。

【請求項3】

前記異位相データ生成部は、遅延器もしくはバッファを用いることで、前記シリアルデータを段階的に遅延させることを特徴とする請求項1または2に記載のデシリアライザ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−268406(P2010−268406A)

【公開日】平成22年11月25日(2010.11.25)

【国際特許分類】

【出願番号】特願2009−120317(P2009−120317)

【出願日】平成21年5月18日(2009.5.18)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成22年11月25日(2010.11.25)

【国際特許分類】

【出願日】平成21年5月18日(2009.5.18)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]