デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、位相同期ループ回路に関し、特に、デスキュー(De−Skew)用のADPLL(All Digital Phase Locked Loop)等に適用して好適なデジタル位相同期ループ回路に関する。

【背景技術】

【0002】

近年、特定用途向けIC(ASIC:Application Specific Integrated Circuits)等の半導体集積回路装置においてクロック生成回路として組み込まれるアナログPLL(Phase Locked Loop)(PLLマクロ)は、内部フィルタを抵抗や容量といったアナログ素子を用いて構成することによる面積の増加や、電源電圧の低下(低電圧化)による特性の劣化など、様々な問題に直面している。そこで、アナログPLLの素子をすべてデジタル構成に置き換えた全デジタルPLL(ADPLL)の開発が盛んに進められている。

【0003】

図14に、逓倍用のアナログPLL(APLL)の典型的な構成の一例を示す。図14に示すように、このPLLは、FREF端子に入力されるリファレンスクロック(基準クロック)信号FREFをM分周する前段分周器(MDIV)31と、前段分周器(MDIV)31の出力信号FRと帰還分周器(NDIV)32の出力信号FDを入力し位相・周波数を比較する位相周波数比較器(PFD)33と、位相周波数比較器(PFD)33での位相比較結果UP/DNに応じて容量を充電・放電する電流を制御し位相差に対応した電圧を蓄積するチャージポンプ(CP)34と、チャージポンプ(CP)34の電圧を平滑化させる低域通過フィルタよりなるアナログフィルタ(FIL)35と、アナログフィルタ(FIL)35の出力電圧を制御電圧として入力し該制御電圧に対応した周波数の発振クロックを出力する電圧制御発振器(VCO)36と、電圧制御発振器(VCO)36の出力クロック信号FOをP分周した信号FOUTを出力する後段分周器(PDIV)37と、電圧制御発振器(VCO)36の出力クロック信号FOをN分周した信号FDを出力する帰還分周器(NDIV)32と、を備え、リファレンスクロック信号FREFをM分周した信号FR(周波数:FREF/M)と、電圧制御発振器(VCO)36の出力クロック信号FO(周波数:FOUT×P)をN分周した信号FD(周波数:(FOUT×P)/N)の位相、周波数が一致するように制御される。

【0004】

FREF/M=(FOUT×P)/N ・・・(1)

【0005】

なお、FREF、FR、FD、FO、FOUT等は、リファレンスクロック信号、M分周したリファレンスクロック信号、FOUTをN分周したフィードバッククロック信号、発振クロック信号、DOをP分周した出力クロック信号の各信号を表しているが、各信号の周波数を表すものとする。

【0006】

上式(1)より、逓倍用アナログPLLは次式(2)の周波数FOUTを出力する。

FOUT=FREF×N/(M×P) ・・・(2)

【0007】

したがって、トータルの逓倍値はFOUT/FREFより、次式(3)で与えられる。

【0008】

N/(M×P) ・・・(3)

【0009】

逓倍用アナログPLLは、PLL回路内に帰還経路(フィードバックパス)を有し、逓倍されたクロック(周波数FOUT)を出力する。

【0010】

一方、De−skew用アナログPLLでは、PLL回路外部に帰還経路(フィードバックパス)を備え、リファレンスクロック信号と、帰還クロック信号(フィードバッククロック)の位相を合わせる。

【0011】

図15に、De−skew用アナログPLLの典型的な構成の一例を示す。このDe−skew用アナログPLLはチップ間やマクロ間の入出信号の位相合わせに使われるマクロである。このため、PLL30の外部の帰還経路(フィードバックパス)にCTS(Clock Tree Synthesis)41が配置される。CTS41には、クロック分配システムにおいて末端間でのスキューを解消するようにバッファ(CTSバッファ)が挿入される。リファレンスクロック信号FREFをM分周した信号FRと、CTS41の末端から出力される信号FBAKをN分周した信号FDの位相、周波数が一致するように帰還制御される。

【0012】

FREF/M=FOUT/N ・・・(4)

【0013】

De−Skew用アナログPLLは、次式(5)で表される周波数FOUTを出力する。

【0014】

FOUT=FREF×N/M ・・・(5)

【0015】

したがって、トータルの逓倍値は、

N/M

である。

【0016】

図16は、図15に示したDe−Skew用アナログPLL30の適用例の一例を模式的に示す図である(図16は本願発明者が作図したものである)。図16に示すように、De−Skew用PLL30(図16のDe−Skew用アナログPLL30と等しい)は、例えば、異なるクロックドメイン間やチップ間でのデータのやり取りを行なう際に用いられる。CTS41、42の末端同士の位相を調整し、同期をとることで、データのやり取りが可能となる。図16に示した例では、De−Skew用PLL30のFREF端子に入力されるクロックが200MHZで動作するユーザロジック43に入力され、De−Skew用PLL30のFOUT端子からの出力クロックがCTS41を介して400MHZで動作するユーザロジック44に入力されるとともに、端子FBAKに入力され、De−Skew用PLL30において、FREFとFBAKの2つの信号の立ち上がりエッジの位相が揃うように制御される。

【0017】

上記したDe−Skew用PLL30に、ADPLLの構成を適用する場合、以下に説明するように、問題があることが明らかとなった(本願発明者等の分析による)。以下では、この問題を説明するための前提として、はじめにADPLLを説明する。

【0018】

図17は、特許文献1に開示されたADPLLの構成を示す図である。図18は、図17を簡略化して示した図である(非特許文献1のFig.1参照)。図18に示すように、リファレンスクロック信号FREFは、TDC(time−to−digital converter)1に入力されるとともに、DCO(Digitally−Controlled−Oscillator)の出力CKVをクロック端子に入力するフリップフロップ(FF)2のデータ端子に入力される。FF2は、CKVの立ち上がりエッジに応答して、FREFをサンプルし、タイミング調整されたFREF(Retimed FREF)をCKR(Retimed FREF)として出力する。CKRは、TDC1の測定結果をラッチするラッチ回路(Latch)とアキュムレータ(Reference Phase Accumulator)3に入力される。アキュムレータ3では、CKRのエッジが入力されるごとに、逓倍設定値をアキュムレート(累算)する。

【0019】

図18において、TDC1(図17の201に対応)は、リファレンスクロック信号FREFのタイミングでのFREFの位相と出力クロックCKVの位相の差分をデジタルデータにて出力する。この位相差分は、TDC1内の遅延素子の個数に対応する。

【0020】

図24に、図17に示したTDC201の構成例を示す。このTDCは、DCOの出力CKVとリファレンスクロックFREFを入力し、CKVの立ち上がりエッジとFREFの立ち上がりエッジの位相差TDC_RISEと、CKVの立ち下りエッジとFREFの立ち上がりエッジの位相差TDC_FALLを出力する。図24に示すように、TCD1は、L個の遅延素子と、L個のFFと、エッジ検出器を備えている。

【0021】

図25は、図24のTDCのタイミング動作を示す図であり、L=10としている。TDCにおいて、DCOの出力CKVをL個の遅延素子で徐々に遅延させた信号D(0)〜D(L−1)を、時刻T1にリファレンスクロック信号FREFの立ち上がりエッジで一斉にサンプリングし、10ビットのサンプリングデータQ[0:9]として例えば“0011110000”を得る。サンプリングデータQ[0:9]の0から1に値が変化する箇所と1から0に値が変化する箇所を検出することで、遅延した出力クロックCKVの立ち上がりエッジと立ち下りエッジとの間隔を、遅延素子の段数で表すことができる。この場合、1から0へ変化する箇所Q[6]が立ち上がりエッジの情報となり(Q[2−5]が1であり、Q[6]で0となる)、1から0に変化する箇所Q[2]が立ち下りエッジの情報となり(Q[6−9]、Q[0−1]が1であり、Q[2]で1となる)、それぞれ、デジタルデータTDC_RISE、TDC_FALLとして出力される。すなわち、TDCによって出力クロックCKVの立ち上がりエッジはFREFの立ち上がりエッジに対してTDC内の遅延素子6段分進んでおり、出力クロックCKVの立ち下がりエッジはFREFの立ち上がりエッジに対してTDC内の遅延素子2段分進んでいることが測定される。

【0022】

図18、図17のADPLLにおいて、TDC1(TDC201)は、最大CKV信号1周期分の時間が測定できればよい。TDC1(TDC201)の出力は、DCO周期正規化回路(DCO Period Normalization)5に入力され、TDC1で測定れた遅延素子の個数に対応した位相差を、CKVの1周期に対する割合(小数部分)に正規化される。

【0023】

アキュムレータ(Oscillator Phase Accumulator)4では、CKVのエッジ回数(例えば立ち上がりエッジ)をアキュムレート(累算)し、サンプラ8でCKRのタイミング(例えば立ち上がりエッジのタイミング)ごとにアキュムレート値を出力する。上記動作によって、CKRのタイミングごとに、アキュムレータ3によるFREFのアキュムレート値、アキュムレータ4によるCKVのアキュムレート値、及び、FREFとCKVの間の位相差(TDC1によって測定される)のデータが得られる。

【0024】

アキュムレータ3、4のアキュムレート値の差分(RR[k]−Rv[k])は、DCOの出力クロック信号CKVの1サイクル以上の位相差を、整数で表した成分(何クロックサイクル分に対応するかを示す)である。一方、TDC1で得られる位相差ε[k]は、DCOの出力クロック信号CKVの1サイクル以内の位相差であり、小数の扱いとなる。なお、RR[k]、Rv[k]、ε[k](k=1、2、・・・・)は、時間離散信号(サンプリングクロックCKRでサンプリングされた信号)であることを表しており、振幅も離散値(デジタル信号)である。

【0025】

得られたデータは、位相誤差検出回路(Phase detector)6にて、次式(6)により、デジタル演算処理にて位相誤差データφE[k]が出力される。

【0026】

φE[k]=RR[k]−Rv[k]+ε[k] ・・・(6)

【0027】

ただし、φE[k]は、位相差(位相誤差データ)、

RR[k]は、FREFのアキュムレート値、

Rv[k]は、サンプラ8の出力(CKVのアキュムレート値)、

ε[k]は、CKV1クロック以内の位相差データ

である。

【0028】

この位相誤差データφE[k]を、デジタルフィルタ(Loop Filter)へ入力して平滑化し、DCOのゲインの正規化(DCO gain normalization)を行った複数ビットのデジタル信号d[k]がCKRのタイミングでDCOに入力される。DCOは、LC共振回路からなり、並列接続されたバリキャップダイオードをデジタル信号d[k]の各ビットの論理1、0の電圧で制御することで容量を可変させ、LC共振周波数を可変させる。最終的には、位相誤差データφE[k]が0になるようにDCOの発振周波数が調整される(ロック状態となる)。

【0029】

図19(A)は、図18における、アキュムレータ4の出力Rv[i]と出力クロックCKVの対応を示す図である(非特許文献1のFig.5参照)。図19(B)は、アキュムレータ3の出力RR[k]とクロックCKRの対応を示す図である。いずれもmodulo 16であり、累算結果は0〜15の値をとる。非特許文献1のFig.5では、φE=3が例示されているが、図19では、φE=0(位相誤差=0)としている。

【0030】

図19(A)に示すように、アキュムレータ4の出力Rv[i]は、出力クロックCVKの1パルスにつき1つずつmodulo 16で増加する。なお、Rv[i](i=1、2、・・・)も時間離散信号を表しているが、CKVのタイミングで更新されるサンプル値データである。サンプラ8ではアキュムレータ4の出力Rv[i]をCKRのタイミングでサンプリングし、サンプリングした信号Rv[k]が位相誤差検出回路(Phase detector)6に入力される。CKVの1周期内に収まるFREFとCKVの位相差ε[k](CKRのタイミングでサンプリングされる)も、位相誤差検出回路(Phase detector)6での位相比較に使用される。

【0031】

図19(B)に示すように、周波数設定コマンドによりアキュムレータ3に対してFCW(Fequency Command Word)=10とセットされた場合、アキュムレータ3の出力RR[k]は、CKR1パルスにつき、10ずつ、modulo 16で増加する。

【0032】

図18に示したADPLLにおいて、CKRのタイミングで比較演算(φE[k]=RR[k]−Rv[k]+ε[k])が行われ、差分φE[k]が0となるように動作する。最終的な位相比較特性(入力位相差(CKV数)と出力デジタルコード)は、図20に示すようなものとなる(本願発明者等による)。位相差のCKV1クロックサイクル以内の小数部は、TDC1内の遅延素子の時間分解能によって設定される。

【0033】

ADPLLにおいて、アキュムレータではなく、カウンタによって整数差分を測定する構成も知られている(例えば特許文献2参照)。図21に、特許文献2に開示されたADPLLの構成を示す(特許文献2の図4)。図21に示すように、PFD(Phase Frequency Detector)+TDCは、遅延線401、制御ロジック回路402、サンプラ403、カウンタ404、加算器405、オフセットコントロール回路406を備えている。分周器DIVは、プリスケーラ407、プログラムカウンタ408、スワローカウンタ409を備えている。DLFはデジタルフィルタ(ループフィルタ)、DCO(Digitally−Controlled−Oscillator)は、図18と同様の構成とされる。

【0034】

図21の回路においては、図18のように、信号FREF、CKVの位相差の整数部分を、2つのアキュムレータ3、4の値の差分としてではなく、カウンタ404のカウント値で求めている。カウンタ404は、リファレンス信号VREFを、分周器DIVのプリスケーラ407の出力VPRE(1GHz)でサンプルするサンプラ403の出力を受けて、VPREのカウントをスタートさせ、分周器DIVのプログラムカウンタ408の出力VDIV(26MHz)を受けてプリスケーラ407の出力VPREのカウント動作をストップする。この構成は、カウンタ404を用いることとTDCの特性改善から、VREFとVDIVが位相差を持った状態でロックする。

【先行技術文献】

【特許文献】

【0035】

【特許文献1】特開2002−076886号公報

【特許文献2】特開2009−268047号公報

【非特許文献】

【0036】

【非特許文献1】Robert Bogdan Staszewski and Poras T. Balsara, "Phase-Domain All-Digital Phase-Locked Loop", IEEE TRANSACTION ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, PP.159-163, VOL.52, NO.3, MARCH 2005

【発明の概要】

【発明が解決しようとする課題】

【0037】

以下に関連技術の分析を与える。

【0038】

上記したADPLLを、De−Skew用PLLに適用する場合、以下のような問題がある。

【0039】

図22は、図18の構成を用いたDe−Skew用PLLの構成を示す図である。なお、図22は、課題の説明のために、本発明者等によって作成されたものである。

【0040】

一般的にDe−Skew用PLLの後段分周器(PDIV)は1〜16分周程度の分周が可能となっている。CTS(Clock Tree Synthesis)の末端(Leaf)の出力であるFBAKは、DCOの出力クロック信号CKVの1〜16分周の信号が入力されることになる。図22において、後段分周器(PDIV)の分周値が1であれば、図18の回路と変わらない動作となるので問題はないが、後段分周器(PDIV)の分周値が1よりも大の場合、問題が発生する。

【0041】

図22において、アキュムレータ(Oscillator Phase Accumulator)4には、DCOの出力クロック信号CKVではなく、DCOの出力クロック信号CKVを後段分周器(PDIV)でP分周した信号FOUTを、帰還路のCTSに入力し、CTSの末端の出力信号が、PLLのFBAK端子に入力される。

【0042】

図18の構成では、アキュムレータ4は、DCOの出力クロックCKV(2.4GHZ)のエッジごとに、累算(アキュムレート)していたが、図22において、FBAK端子に入力される信号(帰還路のCTSの末端から出力される信号は、後段分周器(PDIV)にてDCOの出力CKVをP分周したタイミングでしか、そのエッジ(立ち上がりエッジ)は発生しない。したがって、図22において、図18と同じ処理を行うのであれば、アキュムレータ4は、FBAKのエッジの入力に応答して、1の代わりに、P値(分周値)を累算する必要ある。このため、アキュムレータ4の回路構成が大規模化することになる。

【0043】

さらに、問題となるのがTDC1である。図18の構成では、TDC1は、出力クロックCKVの1周期以内で位相差を測定するため、CKVの1周期を測定できる長さに対応した個数の遅延素子、ラッチ回路(フリップフロップ)を備えるだけで十分である。これに対して、図22の構成においては、DCOの出力クロック信号CKVのP(Pは例えば1〜16の整数)周期の期間内での位相差を測定するために、TDC1の遅延素子数、ラッチ回路(フリップフロップ)は、分周値が1のときの最大16倍必要とされ、TDCの回路面積が増大し、大きなデメリットになる。

【0044】

図23は、図22の構成における入力位相(FREFとFBAKの位相差)と出力デジタルコード(Phase Detector5の出力)の位相比較特性を示す図である。図23と、図20を比較すると、図20では、TDCは、CKV1周期分の長さを所定の遅延分解能で測定しているが、図23では、TDCは、CKVP周期分を、所定分解能で測定することが必要とされ、図22のTDCにおける遅延素子列の長さ、ラッチ回路(フリップフロップ)の数はP倍となる。

【0045】

より詳細には、図22において、後段分周器(PDIV)を4分周(P=4)に設定した場合、FBAKを累算するアキュムレータ4では、CKVの4倍の周期(4分周)でしかアキュムレートすることができないため、CKV4クロック分以内の位相差は、全てTDC1で測定しなければならない。同様に、後段分周器PDIVの分周数が16分周(P=16)に設定されていると、TDC1においてCKV16クロック分を測定する必要がある。それ以上の分周設定が可能であれば、TDC1においてその分を測定するだけの長さの遅延素子列、ラッチ回路群が必要となる。

【0046】

よって、このADPLLの構成では、De−Skew用のPLLの構成を採ることは困難であり、実質的に不可能である。

【0047】

また、図21に示した構成も、De−Skew用PLLとしては使用することはできない。図21に示すように、オフセットを与えるオフセットコントロール回路406で、位相誤差データに一定のオフセット値を与えるため、ロック時は、その位相データ分、差分をもってVREFとVDIVがロック状態となる。このオフセットの機能がないとしても、前述したADPLLと同じく、カウンタ404により計数される位相差の整数部は、分周後のクロックでしか動作しない。したがって、分周クロックの1周期分の時間を補間するために、TDCの測定時間を延ばす必要がある。このため、前述と同じ理由で、図21の構成も、De−Skew用PLLとしての使用には不適である。

【0048】

上記した通り、関連技術の構成は、De−Skew用PLLを構成する場合、アキュムレータ、カウンタ及びTDCに、後段分周器(PDIV)の信号が入力されるため、TDCでの位相差の測定範囲を、DCOの出力CKVをP分周する後段分周器(PDIV)の分周値に合わせて拡張することが必要とされ、回路規模の増大等を招く。

【0049】

そこで本発明の目的は、TDCの回路規模を拡張することなく、デスキュー用途に用いることが可能であるデジタル位相同期ループ回路を提供することにある。

【課題を解決するための手段】

【0050】

本発明の概要を以下に説明する。なお、各要素に付した括弧内の符号は本発明の理解を容易化するためのものであり、本発明を制限するために解釈すべきものでないことは勿論である。

【0051】

本発明によれば、入力された第1のクロック信号(FR)と第2のクロック信号(FD)のうち位相が進んでいる方のクロック信号の有効エッジ(立ち上がりエッジ)と、位相が遅れている方のクロック信号の有効エッジ(立ち上がりエッジ)の間(時間期間)に、第3のクロック信号(FO)の有効エッジ(立ち上がりエッジ)がいくつあるかを計数するカウンタ(17)と、前記第1のクロック信号(FR)と前記第3のクロック信号(FO)の有効エッジの位相差を前記第3のクロック信号(FO)の1サイクルよりも短時間の時間分解能で測定する第1の位相差検出回路(13)と、前記第2のクロック信号(FD)と前記第3のクロック信号(FO)の有効エッジの位相差を前記第3のクロック信号(FO)の1サイクルよりも短時間の時間分解能で測定する第2の位相差検出回路(14)と、前記第1のクロック信号と前記第2のクロック信号のうちどちらが位相が進んでいるかを判定する判定器(15)と、前記カウンタ(17)の出力、前記第1、第2の位相差検出回路(13、14)の出力、及び、前記判定器(15)の出力を元に、前記第1のクロック信号と前記第2のクロック信号の位相誤差を演算する位相誤差演算器(16)と、前記位相誤差に対応したデジタル信号に基づき発振周波数を可変させ前記第3のクロック信号を出力するデジタル制御発振器(19)と、を備え、前記第2のクロック信号(FD)は前記第3のクロック信号(FO)を分周した信号(FBAK)から生成される構成としたデジタル位相同期ループ回路が提供される。

【0052】

本発明に係るデジタル位相同期ループにおいては、リファレンスクロック信号を入力して分周する第1の分周器(11)と、

入力されたデジタル信号に応じて発振周波数を可変させるデジタル制御発振器(19)と、

前記デジタル制御発振器(19)の出力信号(FO)を入力して分周し出力クロック信号(FOUT)を出力する第2の分周器(20)と、

前記第2の分周器(20)の出力クロック信号(FOUT)を帰還させた信号(FBAK)を入力して分周する第3の分周器(12)と、

前記第1の分周器(11)の出力信号(FR)と前記デジタル制御発振器(19)の出力信号(FO)を入力し、前記第1の分周器(11)の出力信号(FR)に対する前記デジタル制御発振器(19)の出力信号(FO)の位相差を、前記デジタル制御発振器(19)の出力信号(FO)の1周期以下の範囲で、且つ、前記デジタル制御発振器(19)の出力信号(FO)の1周期よりも短い時間分解能で、測定する第1の位相差検出回路(13)と、

前記第3の分周器(12)の出力信号(FD)と前記デジタル制御発振器(19)の出力信号(FO)を入力し、前記第3の分周器(12)の出力信号(FD)に対する前記デジタル制御発振器(FO)の出力信号の位相差を、前記デジタル制御発振器(19)の出力信号(FO)の1周期以下の範囲で、且つ、前記デジタル制御発振器(19)の出力信号(FO)の1周期よりも短い時間分解能で、測定する第2の位相差検出回路(14)と、

前記第1の分周器(11)及び第3の分周器(12)の出力信号(FR、FD)を入力し、前記第1の分周器(11)の出力信号(FR)に対して前記第3の分周器(12)の出力信号(FD)の位相が進んでいるか遅れているかを判別し判別結果(SEL)を出力する判定器(156)と、

前記第1の分周器の出力信号(RF)と前記第3の分周器の出力信号(FD)のうち位相が進んでいる一方の出力信号のエッジと、位相が遅れている他方の出力信号のエッジで規定される時間期間における、前記デジタル制御発振器(19)の出力信号(FO)をカウント値を提供するカウンタ(17)と、

前記カウンタ(17)のカウント値と、前記第1及び第2の位相差検出回路(13、14)の出力と、前記判定器(15)での判定結果を入力し、前記第1の分周器(11)の出力信号(FR)と前記第3の分周器(12)の出力信号(FD)の位相誤差(PERR)を演算する位相誤差演算器(16)と、

前記位相誤差演算器(16)で演算された位相誤差(PERR)を入力しフィルタ処理したデジタル信号を前記デジタル制御発振器(19)に出力するデジタルフィルタ(18)と、を備えた構成としてもよい。

【0053】

本発明においては、前記デジタル制御発振器(19)の出力信号(FO)の1周期を測定する第3の位相差検出回路(21)を備え、前記位相誤差演算器(16)は、前記第3の位相差検出回路(21)の出力信号(TRO)を入力し、前記第1及び第2の位相差検出回路(13、14)における位相差の測定結果を、前記第3の位相差検出回路(21)で測定した前記デジタル制御発振器(19)の出力信号(FO)の1周期で正規化する構成としてもよい。

【発明の効果】

【0054】

本発明によれば、TDCでの位相差の測定範囲を拡張することなく、DCOの出力を分周する後段分周器の分周値を設定可能としている。

【図面の簡単な説明】

【0055】

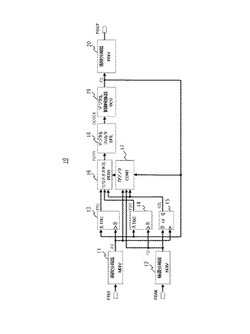

【図1】本発明の一実施形態の構成を示す図である。

【図2】本発明の一実施形態における位相演算を説明する図である。

【図3】本発明の別の実施形態の構成を示す図である。

【図4】本発明の一実施例におけるカウンタを説明する図である。

【図5】サンプリング時のエラーを説明する図である。

【図6】本発明の一実施例におけるサンプリング例を説明する図である。

【図7】本発明の一実施例におけるサンプリング例を説明する図である。

【図8】図4のカウンタが理想カウンタの場合を説明する図である。

【図9】図4のカウンタが有限なカウンタの場合を説明する図である。

【図10】理想カウンタの場合の位相誤差検出特性を示す図である。

【図11】有限なカウンタの場合の位相誤差検出特性を示す図である。

【図12】有限なカウンタの場合の巻き戻りによる位相誤差検出特性を示す図である。

【図13】本発明の一実施例による位相誤差検出特性を示す図である。

【図14】逓倍用アナログPLLの典型的な構成の一例を示す図である。

【図15】Deskew用アナログPLLの典型的な構成の一例を示す図である。

【図16】Deskew用アナログPLLの使用例を示す図である。

【図17】特許文献1(特開2002−076886号公報)のADPLLの構成を示す図である。

【図18】図17の構成を模式的に示す図である。

【図19】(A)、(B)は図18の動作を説明する図である。

【図20】特許文献1(特開2002−076886号公報)のADPLLの位相比較特性を示す図である。

【図21】特許文献2のADPLLの構成を示す図である。

【図22】特許文献1(特開2002−076886号公報)のADPLLをDe−skew化した構成を示す図である。

【図23】図21の構成における位相比較特性を示す図である。

【図24】図17のTDCの構成を示す図である。

【図25】図24のTDCのタイミング動作を示す図である。

【図26】図1のTDC13、14の構成を示す図である。

【図27】図3のTDC21の構成を示す図である。

【図28】図27のTDCのタイミング動作を示す図である。

【発明を実施するための形態】

【0056】

本発明の好ましい態様について説明する。図1は、本発明の好ましい態様の一つをなす実施形態を示す図である。図1を参照すると、このデジタルPLL10は、端子FREFからリファレンスクロック信号FREFを入力してM分周する前段分周器(MDIV)11と、端子FBAKからフィードバッククロック信号FBAKを入力してN分周する帰還分周器(NDIV)12と、第1のTDC(Time−to−Digital−Converter)13と、第2のTDC14と、フリップフロップ(FF)15と、位相誤差演算器(PERR)16と、カウンタ(CONT)17と、デジタルフィルタ(DFIL)18と、デジタル制御発振器(DCO)19と、DCO19の出力クロック信号FOをP分周する後段分周器(PDIV)20を備えている。DCO19の出力クロック信号FOはカウンタ17及び第1、第2のTDC13、14に入力される。なお、特に制限されないが、以下では、信号が入力又は出力される端子を、信号名と同一の端子名で指示するものとする。

【0057】

図1のデジタルPLL10においては、前段分周器(MDIV)11の出力信号FRと、DCO19の出力クロック信号FOの位相が一致するように動作するが、第2のTDC14をさらに備え、帰還分周器(NDIV)12の出力信号FDと、DCO19の出力クロック信号FOの位相差も測定する。

【0058】

本発明の一実施形態において、図16に示したようなDe−skew用PLL30として用いる場合、後段分周器(PDIV)20の出力信号FOUTは、PLL外部のCTS41(図16参照)を介して、端子FBAKに帰還入力される。すなわち、図1において、後段分周器(PDIV)20の出力端子FOUTと、帰還分周器(NDIV)12の入力端子FBAK間に、図15に示すように、CTS(不図示)が挿入される。なお、特に制限されないが、以下では、TDC、カウンタ等において、信号の立ち上がりエッジを、有効エッジとする。第1、第2のTDC13、14において、入力される信号の立ち上がりエッジの位相差を測定し、フリップフロップ(FF)15はクロック端子に入力される信号の立ち上がりでデータ端子の信号をサンプルし、カウンタ17は、カウントイネーブル状態のとき、FOの立ち上がりでカウントアップ動作するものとする。

【0059】

第1のTDC13は、DCO19の出力クロック信号FOと、リファレンスクロック信号FREFを前段分周器(MDIV)11でM分周した信号FRとを端子A、Bにそれぞれ入力し、FOの立ち上がりエッジとFRの立ち上がりエッジの位相差(遅延)を、第1のTDC13内の遅延素子単位に換算した位相差情報TROを出力する。すなわち、FOの立ち上がりエッジがFRの立ち上がりエッジよりも第1のTDC13の遅延素子何段分の遅延に相等するか、又は、遅延素子段数をFO1周期単位に換算した値をTROとして出力する。

【0060】

第2のTDC14は、DCO19の出力クロック信号FOと、フィードバッククロック信号FBAKを帰還分周器(NDIV)12でN分周した信号FDを端子A、Bに入力し、FOの立ち上がりエッジとFDの立ち上がりエッジの位相差を、第2のTDC14内の遅延素子単位に換算した値を位相差情報TDOを出力する。すなわち、FDの立ち上がりエッジがFRの立ち上がりエッジよりも第2のTDC14の遅延素子何段分の遅延に相等するか、又は遅延素子段数をFO1周期単位に換算した値を、TROとして出力する。第1、第2のTDC13、14は、遅延測定範囲(遅延素子段数)、精度(遅延素子1個の遅延時間)等に関して同一構成としてもよい。

【0061】

FF15は、帰還分周器(NDIV)12の分周信号FDをデータ端子(D)に入力し、前段分周器(MDIV)11の出力信号FRをクロック端子に入力しFRの立ち上がりエッジでFDをサンプルした値を出力端子Qから出力信号SELとして出力する。SELは、FRの立ち上がりエッジに対してFDの立ち上がりエッジの位相が遅れていれば、Low、FRの立ち上がりエッジに対してFDの立ち上がりエッジの位相が進んでいれば、Highとなる。なお、FF15のデータ端子とクロック端子に入力されるFDとFRを入れ替えてもよい。この場合、FRとFDの位相の進み、遅れに対するFF15の出力信号SELの論理は反転するが、カウンタ17、位相誤差演算器16で反転した論理を考慮することで対応可能である。

【0062】

カウンタ17は、FF15の出力信号SELに応じて、FRとFDの一方をスタート信号、他方をエンド信号とし、その間、DCO19の出力クロックFOのカウントを行う。例えばFF15の出力信号SELがLow(論理0)の場合、FRの立ち上がりエッジに対してFDの立ち上がりエッジの位相が遅れているため、カウンタ17は、信号FR(の立ち上がりエッジ)をスタート信号とし、信号FD(の立ち上がりエッジ)をエンド信号として用い、スタート信号とエンド信号の間の時間期間におけるFOの立ち上がりエッジの数をカウントする。

【0063】

FF15の出力信号SELがHigh(論理1)の場合、FDの立ち上がりエッジに対してFRの立ち上がりエッジの位相が遅れているため、カウンタ17は、FD(の立ち上がりエッジ)をスタート信号とし、FR(の立ち上がりエッジ)をエンド信号として用い、スタート信号とエンド信号の間の時間期間におけるFOの立ち上がりエッジ数をカウントする。

【0064】

カウンタ17でFRとFDの位相差の整数部分(FOの立ち上がりエッジの数)を求め、第1、第2のTDC13、14では、FOを仲介にして、それぞれ(FO−FR)、(FO−FD)の小数部分の位相差を、FOの1周期以下の小数の精度(TDCの遅延素子単位)で測定する。

【0065】

第1、第2のTDC13、14でそれぞれ測定された(FO−FR)(=TRO)と、(FO−FD)(=TDO)から、例えば

TRO−TDO=(FO−FR)−(FO−FD)=FD−FR ・・・(7)

より、FRとFDの位相差の小数部分(FO1周期未満の遅延値)がTDCの遅延素子段数として求められる。

【0066】

第1、第2のTDC13、14の出力信号TRO、TDO(小数値)、FF15の出力信号SEL、カウンタ17のカウント値(整数値)は、位相誤差演算器16に入力される。

【0067】

位相誤差演算器16では、FRとFDの位相誤差PERRを、カウンタ17のカウント値(整数値)と、TRO、TDOの差分から位相誤差を求める。FRの立ち上がりエッジがFDの立ち上がりエッジよりも時間的に進んでいる場合(SEL=Low)、位相誤差PERRは、例えば次式(8)によって求めることができる。

【0068】

PERR=カウント値−TRO+TDO ・・・(8)

【0069】

FDの立ち上がりエッジがFRの立ち上がりエッジよりも進んでいる場合(SEL=High)、位相誤差PERRは、例えば次式(9)によって求めることができる。

【0070】

PERR=カウント値−TDO+TRO ・・・(9)

【0071】

デジタルフィルタ18は、位相差PERRを平滑化する低域通過フィルタ(FIR(有限インパルスレスポンスフィルタ))として構成され、フィルタ演算結果のデジタル信号DCODEを出力する。

【0072】

DCO19は、デジタル信号DCODEに基づき、論理1、0の信号に基づき複数のバラクタダイオードの容量が可変させLC共振周波数を可変させる。

【0073】

図1の第1、第2のTDC13、14は、図26に示すような、基本的なTDCを用いることができる。なお、図26に示した構成は、図24に示したTDCの構成と基本的に同一である。

【0074】

図26において、TDCは、端子AとBにそれぞれ入力される信号の立ち上がりエッジの位相差を測定する。端子Aに入力された信号は、複数段の単位遅延素子(バッファ)211からなる遅延素子列で遅延される。遅延素子列の各段の信号を、各段に対応して設けられたFF212のデータ端子に入力し、端子Bに入力される信号を複数のFF212のクロック端子に共通に入力する。各FF212では、データ端子の信号をクロック端子に共通に入力される信号の立ち上がりエッジでサンプルする。各FF212の出力と隣(後段)のFF212の出力をインバータ214で反転した信号を入力するAND回路213を備えている。AND回路213はFF212の出力が“1”、隣(後段)のFF212の出力が“0”、したがってインバータ214の出力が“1”のとき、“1”を出力し、それ以外は“0”を出力する検出回路として機能する(AND回路213は図24のエッジ検出回路を構成し、複数のFF212のサンプルのうち1つ前のFFの出力が1、当該FFの出力が0となるFFを検出する)。複数のAND回路213の出力をパラレルビットにバス化し、バイナリ化デコーダ215でデコードする。バイナリ化デコーダ215の出力OUTには、端子AとBにそれぞれ入力される信号の立ち上がりエッジの位相差に応じたバッファ211の段数がデジタルデータとして出力される。

【0075】

図26の動作の一例として、例えば端子Bに入力される信号が、端子Aに入力された信号の立ち上がりエッジからバッファ1段分相等の遅延時間、遅延して立ち上がる場合、端子Bから各FF212のクロック端子に共通入力される信号の立ち上がり時点で、端子Aに入力された信号(Highレベル)はすでにバッファ1段分伝播しており、1段目のバッファ211の出力は“1”であるが、2段目以降のバッファ211の出力は全て“0”である。したがって、1段目のFF212に出力1と2段目のFF212の出力0の反転を受けるAND回路213の出力は“1”となり、残りの全てのAND回路213の出力は“0”となり、端子AとBの信号の位相差が、バッファ1段分の遅延に相当していることがわかる。なお、図26のTDCでは、端子Aに入力される信号を遅延素子列で遅延させることで、端子Aに入力される信号の立ち上がりエッジが端子Bに入力される信号の立ち上がりエッジよりも位相が進んでいる場合の2つの信号の位相差を検出しているが、端子Aに入力される信号の立ち上がりエッジが端子Bに入力される信号の立ち上がりエッジよりも時間的に遅れている場合には、端子Aに入力される信号の1周期(サイクル)前の立ち上がりエッジと端子Bに入力される信号の立ち上がりエッジの位相差が検出され、端子Aに入力される信号の1周期から当該位相差を差し引いた値が、端子Aに入力される信号の位相の遅れとなる。

【0076】

なお、第1、第2のTDC13、14は、図24に示したTDCにおいて、出力信号としてTDC_RISEを用いるようにしてもよいことは勿論である。

【0077】

次に図2を参照して、図1に示した実施形態の動作原理を説明する。図2に示すように、本実施形態においては、FOとFRの立ち上がりエッジの位相差、FOとFDの立ち上がりエッジの位相差を、それぞれ、第1、第2のTDC13、14で測定することで、FRとFDの位相差を測定する。

【0078】

図2に示す例では、FRの立ち上がりエッジに対して、FDの立ち上がりエッジの位相が遅れているため、カウンタ17は、FRのHighパルスの立ち上がりエッジを、カウント・スタート信号(例えばカウントイネーブル(許可)にセット)、FDのHighパルスの立ち上がりエッジをカウント・エンド信号(カウントディスエーブル(不許可)にセット)として用い、その間のFOの立ち上がりエッジの数をカウントする。図2の場合、カウンタ17でカウントされるFOの立ち上がりエッジの数は「3」となる。

【0079】

第1のTDC13において、端子Aに入力されるFOの立ち上がりエッジの方が端子Bに入力されるFRの立ち上がりエッジよりも位相が進んでおり、第1のTDC13においてFOとFRの位相差として

TRO=FO−FR=0.2

が測定される。なお、TRO=0.2は、第1のTDC13内の単位遅延素子段数をFOの1周期分に換算した結果である。例えばFOの1周期が第1のTDC13内の単位遅延素子段数で10段である場合、FOはFRよりも、単位遅延素子で2段分相等、位相が進んでいることに対応する。

【0080】

また、第2のTDC14では、端子Aに入力されるFOの立ち上がりエッジが端子Bに入力されるFDの立ち上がりエッジよりも位相が進んでおり、第2のTDC14において、FOとFDの位相差として、

TDO=FO−FD=0.4

が測定される(なお、TDO=0.4は第2のTDC14内の遅延素子段数をFOの1周期分に換算した結果である)。

【0081】

図2の例では、FRの立ち上がりエッジが、FDの立ち上がりエッジよりも位相が進んでおり(時間的に先にHighに立ち上がる)、FF15の出力SEL=0となり、位相誤差演算器16では、上式(8)より、FRとFDの位相差PERRを以下で求める。

【0082】

PERR=カウント値−TRO+TDO

=3−0.2+0.4

=3.2

【0083】

本発明の一実施形態において、第1、第2のTDC13、14は、FOの1周期分の測定時間に対応していればよい。すなわち、後段分周器(PDIV)20のP分周の設定がいくつであっても、第1、第2のTDC13、14おける測定時間を拡張することは不要とされ、FRとFDの立ち上がりエッジの位相差が0(立ち上がりエッジのタイミングが一致する)となるように、PLLをロックさせることが可能となる。ただし、前段分周器(MDIV)11と、帰還分周器(NDIV)12での遅延の合わせこみは必要である。なお、この遅延の調整は、図14のアナログPLLにおける前段分周器(MDIV)31と帰還分周器(NDIV)32においても必要である。

【0084】

本発明の一実施形態において、FRの立ち上がりエッジを基準に、FOとFRの位相差を測定する第1のTDC13と、FDの立ち上がりエッジを基準にFOとFDの位相差を測定する第2のTDC14を備えており、第1、第2のTDC13、14における位相差の測定範囲は、いずれもFO1周期分でよい。

【0085】

本発明の一実施形態においては、前述した関連技術のように、TDCにおいて、FOのP周期分(分周値Pは例えば16)の長さに及ぶ測定は不要とされ、遅延素子段数、ラッチ回路の個数の増大を抑止し、省面積のDe−Skew用ADPLLの構成を可能としている。

【0086】

また、本発明の一実施形態においては、FOの1周期内は、TDCで測定された位相差(小数部分)を用い、整数部分は、FOの1周期でカウントされるため、入力位相差(FRとFDの位相差)と、位相誤差演算器16の出力デジタルコードの対応(位相比較特性)は図20と等しいものとなる。ただし、図1の構成を実回路として実現する場合、改善すべき点が幾つか存在する。以下に、いくかの改善点を実施例として説明する。

【0087】

<TDCレプリカ>

はじめに図1の構成にTDCレプリカを追加した実施例を説明する。TDCでの測定結果の正規化処理、すなわち遅延素子の段数情報の位相差をDCOの出力信号FO1周期に対する割合に変換する処理を行う際に、FO1周期に相等するTDC内の遅延素子の段数を測定する必要がある。本発明の一実施例では、FOの1周期を測定するTDCを別途用意している。

【0088】

図3は、本実施例の構成を示す図である。図3において、図1に示した前記実施形態の構成と同一又は同等の要素には同一の参照符号が付されている。以下では、同一又は同等の要素の説明は省略する。

【0089】

図3において、図1の前記実施形態に追加されたTDCレプリカ21は、DCO19の出力クロック信号FOを入力し、FO1周期の測定結果TREP(FO1周期をTDCの遅延素子段数に換算した値)を出力する。位相誤差演算器16では、例えば、第1、第2のTDC13、14の出力(遅延素子の段数で表される)を、TDCレプリカ21からのTREP(FOの1周期相等の遅延段数)を用いて正規化し、0と1の間の小数とする。

【0090】

図3のTDCレプリカ21は、図1のTDC13、14の構成例として説明した図26のTDCにおいて、A端子とB端子にFOを共通に入力することで、FO1周期に相等する遅延素子段数を測定することができる。あるいは、FOのデューティが50%の場合、図24のTDCの出力TDC_FALLとTDC_RISEからHighパルスのパルス幅を求め、これを2倍することで1周期を求めてもよい。

【0091】

図27にTDCレプリカ21の構成の別の例を示す。図27の基本構成は図26と同一であるが、FOの一周期の測定結果を移動平均(平滑化)する移動平均回路を備え、移動平均した結果をFO周期信号TREPとして出力する。図27を参照すると、図26と同様に、m+1個のフリップフロップ(FF1〜FFm+1)と、m+1個の遅延素子(BO1、BO2、・・・BOm+1)と、各フリップフロップ(FF1〜FFm)と、その右隣のフリップフロップ(FF2〜FFm+1)の反転信号のANDをとるAND回路(AND1〜ANDm)と、AND回路(AND1〜ANDm)の出力FOW[m−1]〜FOW[0]をバス化したmビット信号FOW[m−1:0]を入力するバイナリ化エンコーダ301と、バイナリ化エンコーダ301の出力FOW_BINの移動平均をとり、TREPとして出力する移動平均回路302を備えている。

【0092】

図28は、図27のTDCレプリカ21の動作の一例を示すタイミング図である。FOの1周期を遅延素子の段数として検出し、その値を元に、FO周期信号TREPを生成する。FOの立ち上がりエッジから次のサイクルの立ち上がりエッジの遅延を測定している。時刻t1でFOがHighに立ち上がり、時刻t2で、FOから遅延してFO1がHighに立ち上がり、同様にしてFO2〜FOmがそれぞれ前段の出力から所定の遅延をもってHighに立ち上がり、時刻t3でFOm+1がHighに立ち上がる。FOの立ち上がりエッジに対してHighレベルの遅延クロックFOk〜FOm−1(0<k<m−1)がフリップフロップFFk〜FFm−1のデータ端子に入力され、フリップフロップFFk〜FFm−1の出力であるサンプリング信号FOPk〜FOPm−1が時刻t1でHighに立ち上がる。サンプリング信号FOPmはLowであるため、AND回路ANDm−1の出力が「1」となり、エッジ抽出信号FOW[1]だけが時刻t1でHighとなる。その他のAND回路はいずれか一方の入力端子が0であるため出力はLowである。バイナリ化エンコーダ301は、エッジ検出信号FOW[m−1:0]に応じてデジタルデータFOW_BINを出力する。図28の例の場合、FOW_BINは、遅延素子の(m−FOW_BIN)段分が、DCO19の出力クロックFOの1周期にあたるとして、「m−1」がデジタルデータFOW_BINとして出力される。FOをクロックとして入力する移動平均回路302によって、所定数のFOW_BINが平均化され(平滑化され)、平均化した値がFO周期信号TREPとして出力される。かかる構成によれば、DCO19の出力信号FOのジッタ、ノイズ等によって、FOW_BINの値がずれることがあってもそのずれを平均化することで吸収し、より正確なクロックFOの1周期の測定が可能である。

【0093】

<カウンタ構成>

次に、本発明の別の実施例として、カウンタの変更と同期非同期の処理について説明する。実際の回路(実回路)において、PLLのロック時は、FRの立ち上がりエッジとFDの立ち上がりエッジは近傍にあることがほとんどである。

【0094】

図1の実施形態においては、FF15でFRとFDの遅れ進みを判断し、カウンタ17のスタート/エンドをFR/FDで制御している。FR/FDのいずれの信号でカウンタ17におけるFOのカウント動作のスタート/ストップを行うかは、FF15の出力SELで選択され、FRの立ち上がりエッジがFDの立ち上がりエッジよりも位相が進んでいれば、FRをカウンタ17のスタート、FDをエンドとする制御を行う。この制御は、FRとFDのエッジ(立ち上がりエッジ)が近傍にある場合、実現は困難となる。また、カウンタ17自身も、ロック近傍では、0や1しか値を取らない(ロック状態では、FDとFRの位相差の整数部分に対応するカウント値は0又は1の近辺で揺動する)。このため、リセットの解除や、カウント動作の高速動作が必要とされる。しかしながら、その実現はかなり困難と思料されることから、FR/FDをカウンタ17のスタート/エンドを制御する制御信号として用いる構成ではなく、図4に示すように、常にカウント動作しているカウンタ(CONT)17のカウンタ値を、FRとFDでサンプリングする構成としてもよい。

【0095】

すなわち、図4において、カウンタ17は、FOを常時カウントしており、FRとFDのそれぞれのパルスの立ち上がりエッジで、カウント値をサンプリング(ラッチ)し、時間的に前後2点でサンプルしたカウント値の差分から、FRとFDの位相差(整数部分、FOのエッジが何個あるか)を求める。カウンタ17ではFOの例えば立ち上がりエッジのタイミングでカウント値を変化させ、FOと非同期のFRやFDの立ち上がりエッジでカウンタ17のカウント値をサンプリング(ラッチ)する。したがって、FOとFR、FDは非同期(エッジは近い位置にあるが、同期関係ではない)であるため、FR、FDのサンプリングのタイミングが、FOのカウント値が遷移するタイミングと重なる可能性がある。

【0096】

例えば図5に例示したように、カウント値の変化時(図5のTdx)と、FR/FDによるカウント値のサンプリングのタイミングが重なる場合(図5のXで示す位置のタイミング)、正しいデータを取り込むことはできない。Tdataはカウンタ17における1データ期間であり、FOの1周期に対応する。

【0097】

この不具合を回避するために、FRやFDを、

Tdx<Tdsa<2×Tdsa<Tdata ・・・(10)

を満たす遅延時間Tdsa、2×Tdsaだけ、遅延させた信号を生成し、これらの遅延信号で、カウンタ17のカウント値をサンプルし、サンプルした値から、正しい値を判定する。

【0098】

図6に示す例では、FRをそれぞれTdsa、2×Tdsa遅延させた遅延信号FR1、FR2を作成し、FR、FR1、FR3の三つの信号の各立ち上がりエッジでカウンタ17のカウント値をサンプリングする。FRによるサンプル値はX(NG)であるが、FR1、FR2ではBを取り込み、TDCでの状態(位相差)と併せて判定する。この場合、FRによりサンプルしたカウント値としてBが用いられる。

【0099】

図6の例は、図4のカウンタ17のカウント値がバイナリデータ(バイナリカウンタ)である。バイナリデータの場合、桁上がりが発生すると、遷移時間は長く、エラーデータをサンプリングする可能性も高くなる。この懸念は、バイナリカウンタをグレイコード・カウンタに変更することで解消される。

【0100】

グレイコード(Gray code)では、ある値から隣接する値に変更する際に常に1ビット移しか変化しない。図6において、カウント値のXの箇所をサンプリングしても、その前又は後のカウント値を捕獲(キャプチュア)することができる。このため、サンプリングポイントは2点で済む。

【0101】

図7において、FRではA、FRからTdsa遅延したFR1では、Bをサンプリングした場合、TDC13の状態(FOとFRの位相の進み遅れ)を併せて判断する(位相誤差演算回路16で判断される)。この場合、Bが用いられる。

【0102】

FOをカウントするカウンタ17として、グレイコード・カウンタを用い、図4に示すように、常時動作するカウンタ17のカウント値を、FRとFDでFOとサンプリングする構成において、カウンタ17は常に動き続けるために、カウンタのフルビットまでカウントすると、オートクリアして0から、再度、カウントアップを開始する。FRとFDのサンプリングのタイミングが、オートクリアを間に挟む場合、カウンタ17により測定される整数部(integer part)の位相誤差が間違った値となる可能性がある。

【0103】

すなわち、図8に示すように、カウンタ値が無限の理想カウンタの場合、FRとFDによるカウンタ17のカウント値をサンプリングした値の差分によって、FRとFDの位相差の整数部分を検出することが可能である。

【0104】

位相誤差の整数部分=FDのカウンタ値−FRのカウンタ値 ・・・(11)

(ただし、位相誤差が正の場合、遅れ、負の場合、進みに対応する。)

【0105】

図8の(1)の場合、

FDのカウンタ値(=258)−FRのカウンタ値(=6)

=258−6

=252(遅れ)

【0106】

図8の(2)の場合、

FDのカウンタ値(=250)−FRのカウンタ値(=578)

=250−578

=−328(進み)

【0107】

しかしながら、カウンタ値が有限の場合(例えば8ビット:0〜255)、図10に示すように、

(1)の場合、

FDのカウンタ値=258は、

258 modulo 256=2(258−256=2)

となり、

FDのカウンタ値(=2)−FRのカウンタ値(=6)

=2−6

=−4(進み)

となる。

【0108】

(2)の場合、578は、

578 modulo 256=66

となり、

FDのカウンタ値(=250)−FRのカウンタ値(=578)

=250−66

=184(遅れ)

となる。

【0109】

図10は、カウンタ17として、理想カウンタ(無限カウンタ)を用いた場合の位相誤差検出特性を示す。横軸は位相差(FRとFDの位相差)、縦軸は位相誤差カウンタ値(カウンタ17のカウント値)である。位相差が大、あるいは小(負に大)となるにしたがって位相誤差カウンタ値も大あるいは小(負に大)となり、一定の勾配を有する。

【0110】

図11に、図4のカウンタ17として有限カウンタを用いた場合の位相誤差検出特性を示す。有限カウンタの場合、測定できる位相差は、理論上、カウンタの最大値±Maxまでとなる。それ以上、以下では再度、0に巻き戻る。

【0111】

図12の実線は、図11の特性と同一であるが、状態によっては、破線で示す特性を辿る場合がある。これは、FRとFDの位相差分を算出する際に、FRとFDのエッジの比較を行うべきエッジのカウント値間で、カウンタ17に0への巻き戻りが発生する場合である。

【0112】

FDのカウンタ値−FRのカウンタ値

=258−6

=252

となるべきところ、FRとFDのエッジの間にカウンタが0となり、

FDのカウンタ値−FRのカウンタ値

=2−6

=−4

に写像される。

【0113】

この場合、本来の位相差、遅れ/進み情報のいずれも誤った情報をとり得ることになる。そこで、本実施例では、FRとFDの位相差±の判定だけでなく、図1のFF15の出力信号SELを用いて、FRとFDの位相の遅れ/進みの判定を行い、位相誤差カウンタ値が正値であるべきところ、負値である状態や、負値であるべきところ、正値であるという状態を、再度、写像し直す。SEL信号(FDの立ち上がりエッジがFRの立ち上がりエッジよりも位相が進んでいるとき(位相差が+のとき)、論理1、遅れているとき、論理0)によるFR/FDの位相の遅れ/進みの情報をもとに、図13に示すように、位相誤差カウンタ値の極性が異なる場合、SEL信号の値を、位相誤差カウンタ値に反映させる。位相誤差(位相誤差カウンタ値)の符号がSEL信号と等しい場合、位相誤差(位相誤差カウンタ値)をそのまま出力し、位相誤差(位相誤差カウンタ値)の符号ビットがSEL信号と異なる場合、SEL信号に符号ビットを合わせる。

【0114】

あるいは、位相誤差カウンタ値の符号がBang―Bang特性(位相差が+の領域で正値、位相差が−の領域で負値をとる特性)の極性と異なる場合、さらに写像して元に戻す。

【0115】

FDのカウンタ値−FRのカウンタ値

=2−6

=−4

の場合、

Bang―Bang特性の極性が正であるため、

−4+256=252

に写像して元に戻す。

【0116】

この結果、図13の破線で示す特性は実線で示す本来の特性となる。なお、図13に示す例では、カウンタは−255(バイナリ表現:00000001)から−1(バイナリ表現:11111111)、0〜+255(バイナリ表現:11111111)の値をとる。

【0117】

以上の改善を行なった実施例が最終的にインプリメント(実装)可能な回路構成となり、De−Skew用ADPLLとして実現可能な構成となる。

【0118】

本実施例により、逓倍PLL(SSCG(Spread Spectrum Clock Generator))は勿論のこと、De−Skew用ADPLLを構成することができる。

【0119】

上記したように、本実施形態によれば、また、TDC13、14を備えたことで(すなわち、TDC14を1つ追加することで)、FOを仲介してそれぞれの位相差を測定し、その後、演算にて最終的に求めたいFR−FDの位相差を求める構成としたことで、TDCの位相差の測定時間を増加させることなく、De−Skew用ADPLLを構成することができる。

【0120】

なお、上記実施形態では、TDC13、14においてFOとFR、FOとFDの立ち上がりエッジの位相差を例を説明したが、信号のエッジとしては立ち上がりエッジで限定されるものでなく、立ち下りエッジを用いる構成としてもよい。

【0121】

なお、上記の特許文献1、2、非特許文献1の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0122】

1 TDC

2 FF

3 アキュムレータ

4 アキュムレータ

5 正規化回路(DCO period normalization)

6 位相検出器

8 サンプラ

10、30 ADPLL

11、31 前段分周器

12、32 帰還分周器

13 TDC

14 TDC

15 FF

16 位相誤差演算器

17 カウンタ

18 デジタルフィルタ

19 デジタル制御発振器

20、37 後段分周器

21 TDCレプリカ

33 位相周波数比較器

34 チャージポンプ

35 アナログフィルタ

36 電圧制御発振器

41、42 CTS

43、44 ユーザロジック

102 アキュムレータ

106 波形成型器

110 FREF

112 CKR

118 インクリメンタ

120 ラッチ

116 FCW

201 TDC

211 バッファ(遅延素子)

212 フリップフロップ

213 AND回路

214 インバータ

215 バイナリ化デコーダ

301 バイナリ化エンコーダ

302 移動平均回路

401 Delay Line

402 Control Logic

403 Sampler

405 加算器

404 Counter

406 Offset Control

407 Prescaler

408 Program Counter

409 Swallow Counter

【技術分野】

【0001】

本発明は、位相同期ループ回路に関し、特に、デスキュー(De−Skew)用のADPLL(All Digital Phase Locked Loop)等に適用して好適なデジタル位相同期ループ回路に関する。

【背景技術】

【0002】

近年、特定用途向けIC(ASIC:Application Specific Integrated Circuits)等の半導体集積回路装置においてクロック生成回路として組み込まれるアナログPLL(Phase Locked Loop)(PLLマクロ)は、内部フィルタを抵抗や容量といったアナログ素子を用いて構成することによる面積の増加や、電源電圧の低下(低電圧化)による特性の劣化など、様々な問題に直面している。そこで、アナログPLLの素子をすべてデジタル構成に置き換えた全デジタルPLL(ADPLL)の開発が盛んに進められている。

【0003】

図14に、逓倍用のアナログPLL(APLL)の典型的な構成の一例を示す。図14に示すように、このPLLは、FREF端子に入力されるリファレンスクロック(基準クロック)信号FREFをM分周する前段分周器(MDIV)31と、前段分周器(MDIV)31の出力信号FRと帰還分周器(NDIV)32の出力信号FDを入力し位相・周波数を比較する位相周波数比較器(PFD)33と、位相周波数比較器(PFD)33での位相比較結果UP/DNに応じて容量を充電・放電する電流を制御し位相差に対応した電圧を蓄積するチャージポンプ(CP)34と、チャージポンプ(CP)34の電圧を平滑化させる低域通過フィルタよりなるアナログフィルタ(FIL)35と、アナログフィルタ(FIL)35の出力電圧を制御電圧として入力し該制御電圧に対応した周波数の発振クロックを出力する電圧制御発振器(VCO)36と、電圧制御発振器(VCO)36の出力クロック信号FOをP分周した信号FOUTを出力する後段分周器(PDIV)37と、電圧制御発振器(VCO)36の出力クロック信号FOをN分周した信号FDを出力する帰還分周器(NDIV)32と、を備え、リファレンスクロック信号FREFをM分周した信号FR(周波数:FREF/M)と、電圧制御発振器(VCO)36の出力クロック信号FO(周波数:FOUT×P)をN分周した信号FD(周波数:(FOUT×P)/N)の位相、周波数が一致するように制御される。

【0004】

FREF/M=(FOUT×P)/N ・・・(1)

【0005】

なお、FREF、FR、FD、FO、FOUT等は、リファレンスクロック信号、M分周したリファレンスクロック信号、FOUTをN分周したフィードバッククロック信号、発振クロック信号、DOをP分周した出力クロック信号の各信号を表しているが、各信号の周波数を表すものとする。

【0006】

上式(1)より、逓倍用アナログPLLは次式(2)の周波数FOUTを出力する。

FOUT=FREF×N/(M×P) ・・・(2)

【0007】

したがって、トータルの逓倍値はFOUT/FREFより、次式(3)で与えられる。

【0008】

N/(M×P) ・・・(3)

【0009】

逓倍用アナログPLLは、PLL回路内に帰還経路(フィードバックパス)を有し、逓倍されたクロック(周波数FOUT)を出力する。

【0010】

一方、De−skew用アナログPLLでは、PLL回路外部に帰還経路(フィードバックパス)を備え、リファレンスクロック信号と、帰還クロック信号(フィードバッククロック)の位相を合わせる。

【0011】

図15に、De−skew用アナログPLLの典型的な構成の一例を示す。このDe−skew用アナログPLLはチップ間やマクロ間の入出信号の位相合わせに使われるマクロである。このため、PLL30の外部の帰還経路(フィードバックパス)にCTS(Clock Tree Synthesis)41が配置される。CTS41には、クロック分配システムにおいて末端間でのスキューを解消するようにバッファ(CTSバッファ)が挿入される。リファレンスクロック信号FREFをM分周した信号FRと、CTS41の末端から出力される信号FBAKをN分周した信号FDの位相、周波数が一致するように帰還制御される。

【0012】

FREF/M=FOUT/N ・・・(4)

【0013】

De−Skew用アナログPLLは、次式(5)で表される周波数FOUTを出力する。

【0014】

FOUT=FREF×N/M ・・・(5)

【0015】

したがって、トータルの逓倍値は、

N/M

である。

【0016】

図16は、図15に示したDe−Skew用アナログPLL30の適用例の一例を模式的に示す図である(図16は本願発明者が作図したものである)。図16に示すように、De−Skew用PLL30(図16のDe−Skew用アナログPLL30と等しい)は、例えば、異なるクロックドメイン間やチップ間でのデータのやり取りを行なう際に用いられる。CTS41、42の末端同士の位相を調整し、同期をとることで、データのやり取りが可能となる。図16に示した例では、De−Skew用PLL30のFREF端子に入力されるクロックが200MHZで動作するユーザロジック43に入力され、De−Skew用PLL30のFOUT端子からの出力クロックがCTS41を介して400MHZで動作するユーザロジック44に入力されるとともに、端子FBAKに入力され、De−Skew用PLL30において、FREFとFBAKの2つの信号の立ち上がりエッジの位相が揃うように制御される。

【0017】

上記したDe−Skew用PLL30に、ADPLLの構成を適用する場合、以下に説明するように、問題があることが明らかとなった(本願発明者等の分析による)。以下では、この問題を説明するための前提として、はじめにADPLLを説明する。

【0018】

図17は、特許文献1に開示されたADPLLの構成を示す図である。図18は、図17を簡略化して示した図である(非特許文献1のFig.1参照)。図18に示すように、リファレンスクロック信号FREFは、TDC(time−to−digital converter)1に入力されるとともに、DCO(Digitally−Controlled−Oscillator)の出力CKVをクロック端子に入力するフリップフロップ(FF)2のデータ端子に入力される。FF2は、CKVの立ち上がりエッジに応答して、FREFをサンプルし、タイミング調整されたFREF(Retimed FREF)をCKR(Retimed FREF)として出力する。CKRは、TDC1の測定結果をラッチするラッチ回路(Latch)とアキュムレータ(Reference Phase Accumulator)3に入力される。アキュムレータ3では、CKRのエッジが入力されるごとに、逓倍設定値をアキュムレート(累算)する。

【0019】

図18において、TDC1(図17の201に対応)は、リファレンスクロック信号FREFのタイミングでのFREFの位相と出力クロックCKVの位相の差分をデジタルデータにて出力する。この位相差分は、TDC1内の遅延素子の個数に対応する。

【0020】

図24に、図17に示したTDC201の構成例を示す。このTDCは、DCOの出力CKVとリファレンスクロックFREFを入力し、CKVの立ち上がりエッジとFREFの立ち上がりエッジの位相差TDC_RISEと、CKVの立ち下りエッジとFREFの立ち上がりエッジの位相差TDC_FALLを出力する。図24に示すように、TCD1は、L個の遅延素子と、L個のFFと、エッジ検出器を備えている。

【0021】

図25は、図24のTDCのタイミング動作を示す図であり、L=10としている。TDCにおいて、DCOの出力CKVをL個の遅延素子で徐々に遅延させた信号D(0)〜D(L−1)を、時刻T1にリファレンスクロック信号FREFの立ち上がりエッジで一斉にサンプリングし、10ビットのサンプリングデータQ[0:9]として例えば“0011110000”を得る。サンプリングデータQ[0:9]の0から1に値が変化する箇所と1から0に値が変化する箇所を検出することで、遅延した出力クロックCKVの立ち上がりエッジと立ち下りエッジとの間隔を、遅延素子の段数で表すことができる。この場合、1から0へ変化する箇所Q[6]が立ち上がりエッジの情報となり(Q[2−5]が1であり、Q[6]で0となる)、1から0に変化する箇所Q[2]が立ち下りエッジの情報となり(Q[6−9]、Q[0−1]が1であり、Q[2]で1となる)、それぞれ、デジタルデータTDC_RISE、TDC_FALLとして出力される。すなわち、TDCによって出力クロックCKVの立ち上がりエッジはFREFの立ち上がりエッジに対してTDC内の遅延素子6段分進んでおり、出力クロックCKVの立ち下がりエッジはFREFの立ち上がりエッジに対してTDC内の遅延素子2段分進んでいることが測定される。

【0022】

図18、図17のADPLLにおいて、TDC1(TDC201)は、最大CKV信号1周期分の時間が測定できればよい。TDC1(TDC201)の出力は、DCO周期正規化回路(DCO Period Normalization)5に入力され、TDC1で測定れた遅延素子の個数に対応した位相差を、CKVの1周期に対する割合(小数部分)に正規化される。

【0023】

アキュムレータ(Oscillator Phase Accumulator)4では、CKVのエッジ回数(例えば立ち上がりエッジ)をアキュムレート(累算)し、サンプラ8でCKRのタイミング(例えば立ち上がりエッジのタイミング)ごとにアキュムレート値を出力する。上記動作によって、CKRのタイミングごとに、アキュムレータ3によるFREFのアキュムレート値、アキュムレータ4によるCKVのアキュムレート値、及び、FREFとCKVの間の位相差(TDC1によって測定される)のデータが得られる。

【0024】

アキュムレータ3、4のアキュムレート値の差分(RR[k]−Rv[k])は、DCOの出力クロック信号CKVの1サイクル以上の位相差を、整数で表した成分(何クロックサイクル分に対応するかを示す)である。一方、TDC1で得られる位相差ε[k]は、DCOの出力クロック信号CKVの1サイクル以内の位相差であり、小数の扱いとなる。なお、RR[k]、Rv[k]、ε[k](k=1、2、・・・・)は、時間離散信号(サンプリングクロックCKRでサンプリングされた信号)であることを表しており、振幅も離散値(デジタル信号)である。

【0025】

得られたデータは、位相誤差検出回路(Phase detector)6にて、次式(6)により、デジタル演算処理にて位相誤差データφE[k]が出力される。

【0026】

φE[k]=RR[k]−Rv[k]+ε[k] ・・・(6)

【0027】

ただし、φE[k]は、位相差(位相誤差データ)、

RR[k]は、FREFのアキュムレート値、

Rv[k]は、サンプラ8の出力(CKVのアキュムレート値)、

ε[k]は、CKV1クロック以内の位相差データ

である。

【0028】

この位相誤差データφE[k]を、デジタルフィルタ(Loop Filter)へ入力して平滑化し、DCOのゲインの正規化(DCO gain normalization)を行った複数ビットのデジタル信号d[k]がCKRのタイミングでDCOに入力される。DCOは、LC共振回路からなり、並列接続されたバリキャップダイオードをデジタル信号d[k]の各ビットの論理1、0の電圧で制御することで容量を可変させ、LC共振周波数を可変させる。最終的には、位相誤差データφE[k]が0になるようにDCOの発振周波数が調整される(ロック状態となる)。

【0029】

図19(A)は、図18における、アキュムレータ4の出力Rv[i]と出力クロックCKVの対応を示す図である(非特許文献1のFig.5参照)。図19(B)は、アキュムレータ3の出力RR[k]とクロックCKRの対応を示す図である。いずれもmodulo 16であり、累算結果は0〜15の値をとる。非特許文献1のFig.5では、φE=3が例示されているが、図19では、φE=0(位相誤差=0)としている。

【0030】

図19(A)に示すように、アキュムレータ4の出力Rv[i]は、出力クロックCVKの1パルスにつき1つずつmodulo 16で増加する。なお、Rv[i](i=1、2、・・・)も時間離散信号を表しているが、CKVのタイミングで更新されるサンプル値データである。サンプラ8ではアキュムレータ4の出力Rv[i]をCKRのタイミングでサンプリングし、サンプリングした信号Rv[k]が位相誤差検出回路(Phase detector)6に入力される。CKVの1周期内に収まるFREFとCKVの位相差ε[k](CKRのタイミングでサンプリングされる)も、位相誤差検出回路(Phase detector)6での位相比較に使用される。

【0031】

図19(B)に示すように、周波数設定コマンドによりアキュムレータ3に対してFCW(Fequency Command Word)=10とセットされた場合、アキュムレータ3の出力RR[k]は、CKR1パルスにつき、10ずつ、modulo 16で増加する。

【0032】

図18に示したADPLLにおいて、CKRのタイミングで比較演算(φE[k]=RR[k]−Rv[k]+ε[k])が行われ、差分φE[k]が0となるように動作する。最終的な位相比較特性(入力位相差(CKV数)と出力デジタルコード)は、図20に示すようなものとなる(本願発明者等による)。位相差のCKV1クロックサイクル以内の小数部は、TDC1内の遅延素子の時間分解能によって設定される。

【0033】

ADPLLにおいて、アキュムレータではなく、カウンタによって整数差分を測定する構成も知られている(例えば特許文献2参照)。図21に、特許文献2に開示されたADPLLの構成を示す(特許文献2の図4)。図21に示すように、PFD(Phase Frequency Detector)+TDCは、遅延線401、制御ロジック回路402、サンプラ403、カウンタ404、加算器405、オフセットコントロール回路406を備えている。分周器DIVは、プリスケーラ407、プログラムカウンタ408、スワローカウンタ409を備えている。DLFはデジタルフィルタ(ループフィルタ)、DCO(Digitally−Controlled−Oscillator)は、図18と同様の構成とされる。

【0034】

図21の回路においては、図18のように、信号FREF、CKVの位相差の整数部分を、2つのアキュムレータ3、4の値の差分としてではなく、カウンタ404のカウント値で求めている。カウンタ404は、リファレンス信号VREFを、分周器DIVのプリスケーラ407の出力VPRE(1GHz)でサンプルするサンプラ403の出力を受けて、VPREのカウントをスタートさせ、分周器DIVのプログラムカウンタ408の出力VDIV(26MHz)を受けてプリスケーラ407の出力VPREのカウント動作をストップする。この構成は、カウンタ404を用いることとTDCの特性改善から、VREFとVDIVが位相差を持った状態でロックする。

【先行技術文献】

【特許文献】

【0035】

【特許文献1】特開2002−076886号公報

【特許文献2】特開2009−268047号公報

【非特許文献】

【0036】

【非特許文献1】Robert Bogdan Staszewski and Poras T. Balsara, "Phase-Domain All-Digital Phase-Locked Loop", IEEE TRANSACTION ON CIRCUITS AND SYSTEMS-II: EXPRESS BRIEFS, PP.159-163, VOL.52, NO.3, MARCH 2005

【発明の概要】

【発明が解決しようとする課題】

【0037】

以下に関連技術の分析を与える。

【0038】

上記したADPLLを、De−Skew用PLLに適用する場合、以下のような問題がある。

【0039】

図22は、図18の構成を用いたDe−Skew用PLLの構成を示す図である。なお、図22は、課題の説明のために、本発明者等によって作成されたものである。

【0040】

一般的にDe−Skew用PLLの後段分周器(PDIV)は1〜16分周程度の分周が可能となっている。CTS(Clock Tree Synthesis)の末端(Leaf)の出力であるFBAKは、DCOの出力クロック信号CKVの1〜16分周の信号が入力されることになる。図22において、後段分周器(PDIV)の分周値が1であれば、図18の回路と変わらない動作となるので問題はないが、後段分周器(PDIV)の分周値が1よりも大の場合、問題が発生する。

【0041】

図22において、アキュムレータ(Oscillator Phase Accumulator)4には、DCOの出力クロック信号CKVではなく、DCOの出力クロック信号CKVを後段分周器(PDIV)でP分周した信号FOUTを、帰還路のCTSに入力し、CTSの末端の出力信号が、PLLのFBAK端子に入力される。

【0042】

図18の構成では、アキュムレータ4は、DCOの出力クロックCKV(2.4GHZ)のエッジごとに、累算(アキュムレート)していたが、図22において、FBAK端子に入力される信号(帰還路のCTSの末端から出力される信号は、後段分周器(PDIV)にてDCOの出力CKVをP分周したタイミングでしか、そのエッジ(立ち上がりエッジ)は発生しない。したがって、図22において、図18と同じ処理を行うのであれば、アキュムレータ4は、FBAKのエッジの入力に応答して、1の代わりに、P値(分周値)を累算する必要ある。このため、アキュムレータ4の回路構成が大規模化することになる。

【0043】

さらに、問題となるのがTDC1である。図18の構成では、TDC1は、出力クロックCKVの1周期以内で位相差を測定するため、CKVの1周期を測定できる長さに対応した個数の遅延素子、ラッチ回路(フリップフロップ)を備えるだけで十分である。これに対して、図22の構成においては、DCOの出力クロック信号CKVのP(Pは例えば1〜16の整数)周期の期間内での位相差を測定するために、TDC1の遅延素子数、ラッチ回路(フリップフロップ)は、分周値が1のときの最大16倍必要とされ、TDCの回路面積が増大し、大きなデメリットになる。

【0044】

図23は、図22の構成における入力位相(FREFとFBAKの位相差)と出力デジタルコード(Phase Detector5の出力)の位相比較特性を示す図である。図23と、図20を比較すると、図20では、TDCは、CKV1周期分の長さを所定の遅延分解能で測定しているが、図23では、TDCは、CKVP周期分を、所定分解能で測定することが必要とされ、図22のTDCにおける遅延素子列の長さ、ラッチ回路(フリップフロップ)の数はP倍となる。

【0045】

より詳細には、図22において、後段分周器(PDIV)を4分周(P=4)に設定した場合、FBAKを累算するアキュムレータ4では、CKVの4倍の周期(4分周)でしかアキュムレートすることができないため、CKV4クロック分以内の位相差は、全てTDC1で測定しなければならない。同様に、後段分周器PDIVの分周数が16分周(P=16)に設定されていると、TDC1においてCKV16クロック分を測定する必要がある。それ以上の分周設定が可能であれば、TDC1においてその分を測定するだけの長さの遅延素子列、ラッチ回路群が必要となる。

【0046】

よって、このADPLLの構成では、De−Skew用のPLLの構成を採ることは困難であり、実質的に不可能である。

【0047】

また、図21に示した構成も、De−Skew用PLLとしては使用することはできない。図21に示すように、オフセットを与えるオフセットコントロール回路406で、位相誤差データに一定のオフセット値を与えるため、ロック時は、その位相データ分、差分をもってVREFとVDIVがロック状態となる。このオフセットの機能がないとしても、前述したADPLLと同じく、カウンタ404により計数される位相差の整数部は、分周後のクロックでしか動作しない。したがって、分周クロックの1周期分の時間を補間するために、TDCの測定時間を延ばす必要がある。このため、前述と同じ理由で、図21の構成も、De−Skew用PLLとしての使用には不適である。

【0048】

上記した通り、関連技術の構成は、De−Skew用PLLを構成する場合、アキュムレータ、カウンタ及びTDCに、後段分周器(PDIV)の信号が入力されるため、TDCでの位相差の測定範囲を、DCOの出力CKVをP分周する後段分周器(PDIV)の分周値に合わせて拡張することが必要とされ、回路規模の増大等を招く。

【0049】

そこで本発明の目的は、TDCの回路規模を拡張することなく、デスキュー用途に用いることが可能であるデジタル位相同期ループ回路を提供することにある。

【課題を解決するための手段】

【0050】

本発明の概要を以下に説明する。なお、各要素に付した括弧内の符号は本発明の理解を容易化するためのものであり、本発明を制限するために解釈すべきものでないことは勿論である。

【0051】

本発明によれば、入力された第1のクロック信号(FR)と第2のクロック信号(FD)のうち位相が進んでいる方のクロック信号の有効エッジ(立ち上がりエッジ)と、位相が遅れている方のクロック信号の有効エッジ(立ち上がりエッジ)の間(時間期間)に、第3のクロック信号(FO)の有効エッジ(立ち上がりエッジ)がいくつあるかを計数するカウンタ(17)と、前記第1のクロック信号(FR)と前記第3のクロック信号(FO)の有効エッジの位相差を前記第3のクロック信号(FO)の1サイクルよりも短時間の時間分解能で測定する第1の位相差検出回路(13)と、前記第2のクロック信号(FD)と前記第3のクロック信号(FO)の有効エッジの位相差を前記第3のクロック信号(FO)の1サイクルよりも短時間の時間分解能で測定する第2の位相差検出回路(14)と、前記第1のクロック信号と前記第2のクロック信号のうちどちらが位相が進んでいるかを判定する判定器(15)と、前記カウンタ(17)の出力、前記第1、第2の位相差検出回路(13、14)の出力、及び、前記判定器(15)の出力を元に、前記第1のクロック信号と前記第2のクロック信号の位相誤差を演算する位相誤差演算器(16)と、前記位相誤差に対応したデジタル信号に基づき発振周波数を可変させ前記第3のクロック信号を出力するデジタル制御発振器(19)と、を備え、前記第2のクロック信号(FD)は前記第3のクロック信号(FO)を分周した信号(FBAK)から生成される構成としたデジタル位相同期ループ回路が提供される。

【0052】

本発明に係るデジタル位相同期ループにおいては、リファレンスクロック信号を入力して分周する第1の分周器(11)と、

入力されたデジタル信号に応じて発振周波数を可変させるデジタル制御発振器(19)と、

前記デジタル制御発振器(19)の出力信号(FO)を入力して分周し出力クロック信号(FOUT)を出力する第2の分周器(20)と、

前記第2の分周器(20)の出力クロック信号(FOUT)を帰還させた信号(FBAK)を入力して分周する第3の分周器(12)と、

前記第1の分周器(11)の出力信号(FR)と前記デジタル制御発振器(19)の出力信号(FO)を入力し、前記第1の分周器(11)の出力信号(FR)に対する前記デジタル制御発振器(19)の出力信号(FO)の位相差を、前記デジタル制御発振器(19)の出力信号(FO)の1周期以下の範囲で、且つ、前記デジタル制御発振器(19)の出力信号(FO)の1周期よりも短い時間分解能で、測定する第1の位相差検出回路(13)と、

前記第3の分周器(12)の出力信号(FD)と前記デジタル制御発振器(19)の出力信号(FO)を入力し、前記第3の分周器(12)の出力信号(FD)に対する前記デジタル制御発振器(FO)の出力信号の位相差を、前記デジタル制御発振器(19)の出力信号(FO)の1周期以下の範囲で、且つ、前記デジタル制御発振器(19)の出力信号(FO)の1周期よりも短い時間分解能で、測定する第2の位相差検出回路(14)と、

前記第1の分周器(11)及び第3の分周器(12)の出力信号(FR、FD)を入力し、前記第1の分周器(11)の出力信号(FR)に対して前記第3の分周器(12)の出力信号(FD)の位相が進んでいるか遅れているかを判別し判別結果(SEL)を出力する判定器(156)と、

前記第1の分周器の出力信号(RF)と前記第3の分周器の出力信号(FD)のうち位相が進んでいる一方の出力信号のエッジと、位相が遅れている他方の出力信号のエッジで規定される時間期間における、前記デジタル制御発振器(19)の出力信号(FO)をカウント値を提供するカウンタ(17)と、

前記カウンタ(17)のカウント値と、前記第1及び第2の位相差検出回路(13、14)の出力と、前記判定器(15)での判定結果を入力し、前記第1の分周器(11)の出力信号(FR)と前記第3の分周器(12)の出力信号(FD)の位相誤差(PERR)を演算する位相誤差演算器(16)と、

前記位相誤差演算器(16)で演算された位相誤差(PERR)を入力しフィルタ処理したデジタル信号を前記デジタル制御発振器(19)に出力するデジタルフィルタ(18)と、を備えた構成としてもよい。

【0053】

本発明においては、前記デジタル制御発振器(19)の出力信号(FO)の1周期を測定する第3の位相差検出回路(21)を備え、前記位相誤差演算器(16)は、前記第3の位相差検出回路(21)の出力信号(TRO)を入力し、前記第1及び第2の位相差検出回路(13、14)における位相差の測定結果を、前記第3の位相差検出回路(21)で測定した前記デジタル制御発振器(19)の出力信号(FO)の1周期で正規化する構成としてもよい。

【発明の効果】

【0054】

本発明によれば、TDCでの位相差の測定範囲を拡張することなく、DCOの出力を分周する後段分周器の分周値を設定可能としている。

【図面の簡単な説明】

【0055】

【図1】本発明の一実施形態の構成を示す図である。

【図2】本発明の一実施形態における位相演算を説明する図である。

【図3】本発明の別の実施形態の構成を示す図である。

【図4】本発明の一実施例におけるカウンタを説明する図である。

【図5】サンプリング時のエラーを説明する図である。

【図6】本発明の一実施例におけるサンプリング例を説明する図である。

【図7】本発明の一実施例におけるサンプリング例を説明する図である。

【図8】図4のカウンタが理想カウンタの場合を説明する図である。

【図9】図4のカウンタが有限なカウンタの場合を説明する図である。

【図10】理想カウンタの場合の位相誤差検出特性を示す図である。

【図11】有限なカウンタの場合の位相誤差検出特性を示す図である。

【図12】有限なカウンタの場合の巻き戻りによる位相誤差検出特性を示す図である。

【図13】本発明の一実施例による位相誤差検出特性を示す図である。

【図14】逓倍用アナログPLLの典型的な構成の一例を示す図である。

【図15】Deskew用アナログPLLの典型的な構成の一例を示す図である。

【図16】Deskew用アナログPLLの使用例を示す図である。

【図17】特許文献1(特開2002−076886号公報)のADPLLの構成を示す図である。

【図18】図17の構成を模式的に示す図である。

【図19】(A)、(B)は図18の動作を説明する図である。

【図20】特許文献1(特開2002−076886号公報)のADPLLの位相比較特性を示す図である。

【図21】特許文献2のADPLLの構成を示す図である。

【図22】特許文献1(特開2002−076886号公報)のADPLLをDe−skew化した構成を示す図である。

【図23】図21の構成における位相比較特性を示す図である。

【図24】図17のTDCの構成を示す図である。

【図25】図24のTDCのタイミング動作を示す図である。

【図26】図1のTDC13、14の構成を示す図である。

【図27】図3のTDC21の構成を示す図である。

【図28】図27のTDCのタイミング動作を示す図である。

【発明を実施するための形態】

【0056】

本発明の好ましい態様について説明する。図1は、本発明の好ましい態様の一つをなす実施形態を示す図である。図1を参照すると、このデジタルPLL10は、端子FREFからリファレンスクロック信号FREFを入力してM分周する前段分周器(MDIV)11と、端子FBAKからフィードバッククロック信号FBAKを入力してN分周する帰還分周器(NDIV)12と、第1のTDC(Time−to−Digital−Converter)13と、第2のTDC14と、フリップフロップ(FF)15と、位相誤差演算器(PERR)16と、カウンタ(CONT)17と、デジタルフィルタ(DFIL)18と、デジタル制御発振器(DCO)19と、DCO19の出力クロック信号FOをP分周する後段分周器(PDIV)20を備えている。DCO19の出力クロック信号FOはカウンタ17及び第1、第2のTDC13、14に入力される。なお、特に制限されないが、以下では、信号が入力又は出力される端子を、信号名と同一の端子名で指示するものとする。

【0057】

図1のデジタルPLL10においては、前段分周器(MDIV)11の出力信号FRと、DCO19の出力クロック信号FOの位相が一致するように動作するが、第2のTDC14をさらに備え、帰還分周器(NDIV)12の出力信号FDと、DCO19の出力クロック信号FOの位相差も測定する。

【0058】

本発明の一実施形態において、図16に示したようなDe−skew用PLL30として用いる場合、後段分周器(PDIV)20の出力信号FOUTは、PLL外部のCTS41(図16参照)を介して、端子FBAKに帰還入力される。すなわち、図1において、後段分周器(PDIV)20の出力端子FOUTと、帰還分周器(NDIV)12の入力端子FBAK間に、図15に示すように、CTS(不図示)が挿入される。なお、特に制限されないが、以下では、TDC、カウンタ等において、信号の立ち上がりエッジを、有効エッジとする。第1、第2のTDC13、14において、入力される信号の立ち上がりエッジの位相差を測定し、フリップフロップ(FF)15はクロック端子に入力される信号の立ち上がりでデータ端子の信号をサンプルし、カウンタ17は、カウントイネーブル状態のとき、FOの立ち上がりでカウントアップ動作するものとする。

【0059】

第1のTDC13は、DCO19の出力クロック信号FOと、リファレンスクロック信号FREFを前段分周器(MDIV)11でM分周した信号FRとを端子A、Bにそれぞれ入力し、FOの立ち上がりエッジとFRの立ち上がりエッジの位相差(遅延)を、第1のTDC13内の遅延素子単位に換算した位相差情報TROを出力する。すなわち、FOの立ち上がりエッジがFRの立ち上がりエッジよりも第1のTDC13の遅延素子何段分の遅延に相等するか、又は、遅延素子段数をFO1周期単位に換算した値をTROとして出力する。

【0060】

第2のTDC14は、DCO19の出力クロック信号FOと、フィードバッククロック信号FBAKを帰還分周器(NDIV)12でN分周した信号FDを端子A、Bに入力し、FOの立ち上がりエッジとFDの立ち上がりエッジの位相差を、第2のTDC14内の遅延素子単位に換算した値を位相差情報TDOを出力する。すなわち、FDの立ち上がりエッジがFRの立ち上がりエッジよりも第2のTDC14の遅延素子何段分の遅延に相等するか、又は遅延素子段数をFO1周期単位に換算した値を、TROとして出力する。第1、第2のTDC13、14は、遅延測定範囲(遅延素子段数)、精度(遅延素子1個の遅延時間)等に関して同一構成としてもよい。

【0061】

FF15は、帰還分周器(NDIV)12の分周信号FDをデータ端子(D)に入力し、前段分周器(MDIV)11の出力信号FRをクロック端子に入力しFRの立ち上がりエッジでFDをサンプルした値を出力端子Qから出力信号SELとして出力する。SELは、FRの立ち上がりエッジに対してFDの立ち上がりエッジの位相が遅れていれば、Low、FRの立ち上がりエッジに対してFDの立ち上がりエッジの位相が進んでいれば、Highとなる。なお、FF15のデータ端子とクロック端子に入力されるFDとFRを入れ替えてもよい。この場合、FRとFDの位相の進み、遅れに対するFF15の出力信号SELの論理は反転するが、カウンタ17、位相誤差演算器16で反転した論理を考慮することで対応可能である。

【0062】

カウンタ17は、FF15の出力信号SELに応じて、FRとFDの一方をスタート信号、他方をエンド信号とし、その間、DCO19の出力クロックFOのカウントを行う。例えばFF15の出力信号SELがLow(論理0)の場合、FRの立ち上がりエッジに対してFDの立ち上がりエッジの位相が遅れているため、カウンタ17は、信号FR(の立ち上がりエッジ)をスタート信号とし、信号FD(の立ち上がりエッジ)をエンド信号として用い、スタート信号とエンド信号の間の時間期間におけるFOの立ち上がりエッジの数をカウントする。

【0063】

FF15の出力信号SELがHigh(論理1)の場合、FDの立ち上がりエッジに対してFRの立ち上がりエッジの位相が遅れているため、カウンタ17は、FD(の立ち上がりエッジ)をスタート信号とし、FR(の立ち上がりエッジ)をエンド信号として用い、スタート信号とエンド信号の間の時間期間におけるFOの立ち上がりエッジ数をカウントする。

【0064】

カウンタ17でFRとFDの位相差の整数部分(FOの立ち上がりエッジの数)を求め、第1、第2のTDC13、14では、FOを仲介にして、それぞれ(FO−FR)、(FO−FD)の小数部分の位相差を、FOの1周期以下の小数の精度(TDCの遅延素子単位)で測定する。

【0065】

第1、第2のTDC13、14でそれぞれ測定された(FO−FR)(=TRO)と、(FO−FD)(=TDO)から、例えば

TRO−TDO=(FO−FR)−(FO−FD)=FD−FR ・・・(7)

より、FRとFDの位相差の小数部分(FO1周期未満の遅延値)がTDCの遅延素子段数として求められる。

【0066】

第1、第2のTDC13、14の出力信号TRO、TDO(小数値)、FF15の出力信号SEL、カウンタ17のカウント値(整数値)は、位相誤差演算器16に入力される。

【0067】

位相誤差演算器16では、FRとFDの位相誤差PERRを、カウンタ17のカウント値(整数値)と、TRO、TDOの差分から位相誤差を求める。FRの立ち上がりエッジがFDの立ち上がりエッジよりも時間的に進んでいる場合(SEL=Low)、位相誤差PERRは、例えば次式(8)によって求めることができる。

【0068】

PERR=カウント値−TRO+TDO ・・・(8)

【0069】

FDの立ち上がりエッジがFRの立ち上がりエッジよりも進んでいる場合(SEL=High)、位相誤差PERRは、例えば次式(9)によって求めることができる。

【0070】

PERR=カウント値−TDO+TRO ・・・(9)

【0071】

デジタルフィルタ18は、位相差PERRを平滑化する低域通過フィルタ(FIR(有限インパルスレスポンスフィルタ))として構成され、フィルタ演算結果のデジタル信号DCODEを出力する。

【0072】

DCO19は、デジタル信号DCODEに基づき、論理1、0の信号に基づき複数のバラクタダイオードの容量が可変させLC共振周波数を可変させる。

【0073】

図1の第1、第2のTDC13、14は、図26に示すような、基本的なTDCを用いることができる。なお、図26に示した構成は、図24に示したTDCの構成と基本的に同一である。

【0074】

図26において、TDCは、端子AとBにそれぞれ入力される信号の立ち上がりエッジの位相差を測定する。端子Aに入力された信号は、複数段の単位遅延素子(バッファ)211からなる遅延素子列で遅延される。遅延素子列の各段の信号を、各段に対応して設けられたFF212のデータ端子に入力し、端子Bに入力される信号を複数のFF212のクロック端子に共通に入力する。各FF212では、データ端子の信号をクロック端子に共通に入力される信号の立ち上がりエッジでサンプルする。各FF212の出力と隣(後段)のFF212の出力をインバータ214で反転した信号を入力するAND回路213を備えている。AND回路213はFF212の出力が“1”、隣(後段)のFF212の出力が“0”、したがってインバータ214の出力が“1”のとき、“1”を出力し、それ以外は“0”を出力する検出回路として機能する(AND回路213は図24のエッジ検出回路を構成し、複数のFF212のサンプルのうち1つ前のFFの出力が1、当該FFの出力が0となるFFを検出する)。複数のAND回路213の出力をパラレルビットにバス化し、バイナリ化デコーダ215でデコードする。バイナリ化デコーダ215の出力OUTには、端子AとBにそれぞれ入力される信号の立ち上がりエッジの位相差に応じたバッファ211の段数がデジタルデータとして出力される。

【0075】

図26の動作の一例として、例えば端子Bに入力される信号が、端子Aに入力された信号の立ち上がりエッジからバッファ1段分相等の遅延時間、遅延して立ち上がる場合、端子Bから各FF212のクロック端子に共通入力される信号の立ち上がり時点で、端子Aに入力された信号(Highレベル)はすでにバッファ1段分伝播しており、1段目のバッファ211の出力は“1”であるが、2段目以降のバッファ211の出力は全て“0”である。したがって、1段目のFF212に出力1と2段目のFF212の出力0の反転を受けるAND回路213の出力は“1”となり、残りの全てのAND回路213の出力は“0”となり、端子AとBの信号の位相差が、バッファ1段分の遅延に相当していることがわかる。なお、図26のTDCでは、端子Aに入力される信号を遅延素子列で遅延させることで、端子Aに入力される信号の立ち上がりエッジが端子Bに入力される信号の立ち上がりエッジよりも位相が進んでいる場合の2つの信号の位相差を検出しているが、端子Aに入力される信号の立ち上がりエッジが端子Bに入力される信号の立ち上がりエッジよりも時間的に遅れている場合には、端子Aに入力される信号の1周期(サイクル)前の立ち上がりエッジと端子Bに入力される信号の立ち上がりエッジの位相差が検出され、端子Aに入力される信号の1周期から当該位相差を差し引いた値が、端子Aに入力される信号の位相の遅れとなる。

【0076】

なお、第1、第2のTDC13、14は、図24に示したTDCにおいて、出力信号としてTDC_RISEを用いるようにしてもよいことは勿論である。

【0077】

次に図2を参照して、図1に示した実施形態の動作原理を説明する。図2に示すように、本実施形態においては、FOとFRの立ち上がりエッジの位相差、FOとFDの立ち上がりエッジの位相差を、それぞれ、第1、第2のTDC13、14で測定することで、FRとFDの位相差を測定する。

【0078】

図2に示す例では、FRの立ち上がりエッジに対して、FDの立ち上がりエッジの位相が遅れているため、カウンタ17は、FRのHighパルスの立ち上がりエッジを、カウント・スタート信号(例えばカウントイネーブル(許可)にセット)、FDのHighパルスの立ち上がりエッジをカウント・エンド信号(カウントディスエーブル(不許可)にセット)として用い、その間のFOの立ち上がりエッジの数をカウントする。図2の場合、カウンタ17でカウントされるFOの立ち上がりエッジの数は「3」となる。

【0079】

第1のTDC13において、端子Aに入力されるFOの立ち上がりエッジの方が端子Bに入力されるFRの立ち上がりエッジよりも位相が進んでおり、第1のTDC13においてFOとFRの位相差として

TRO=FO−FR=0.2

が測定される。なお、TRO=0.2は、第1のTDC13内の単位遅延素子段数をFOの1周期分に換算した結果である。例えばFOの1周期が第1のTDC13内の単位遅延素子段数で10段である場合、FOはFRよりも、単位遅延素子で2段分相等、位相が進んでいることに対応する。

【0080】

また、第2のTDC14では、端子Aに入力されるFOの立ち上がりエッジが端子Bに入力されるFDの立ち上がりエッジよりも位相が進んでおり、第2のTDC14において、FOとFDの位相差として、

TDO=FO−FD=0.4

が測定される(なお、TDO=0.4は第2のTDC14内の遅延素子段数をFOの1周期分に換算した結果である)。

【0081】

図2の例では、FRの立ち上がりエッジが、FDの立ち上がりエッジよりも位相が進んでおり(時間的に先にHighに立ち上がる)、FF15の出力SEL=0となり、位相誤差演算器16では、上式(8)より、FRとFDの位相差PERRを以下で求める。

【0082】

PERR=カウント値−TRO+TDO

=3−0.2+0.4

=3.2

【0083】

本発明の一実施形態において、第1、第2のTDC13、14は、FOの1周期分の測定時間に対応していればよい。すなわち、後段分周器(PDIV)20のP分周の設定がいくつであっても、第1、第2のTDC13、14おける測定時間を拡張することは不要とされ、FRとFDの立ち上がりエッジの位相差が0(立ち上がりエッジのタイミングが一致する)となるように、PLLをロックさせることが可能となる。ただし、前段分周器(MDIV)11と、帰還分周器(NDIV)12での遅延の合わせこみは必要である。なお、この遅延の調整は、図14のアナログPLLにおける前段分周器(MDIV)31と帰還分周器(NDIV)32においても必要である。

【0084】

本発明の一実施形態において、FRの立ち上がりエッジを基準に、FOとFRの位相差を測定する第1のTDC13と、FDの立ち上がりエッジを基準にFOとFDの位相差を測定する第2のTDC14を備えており、第1、第2のTDC13、14における位相差の測定範囲は、いずれもFO1周期分でよい。

【0085】

本発明の一実施形態においては、前述した関連技術のように、TDCにおいて、FOのP周期分(分周値Pは例えば16)の長さに及ぶ測定は不要とされ、遅延素子段数、ラッチ回路の個数の増大を抑止し、省面積のDe−Skew用ADPLLの構成を可能としている。

【0086】

また、本発明の一実施形態においては、FOの1周期内は、TDCで測定された位相差(小数部分)を用い、整数部分は、FOの1周期でカウントされるため、入力位相差(FRとFDの位相差)と、位相誤差演算器16の出力デジタルコードの対応(位相比較特性)は図20と等しいものとなる。ただし、図1の構成を実回路として実現する場合、改善すべき点が幾つか存在する。以下に、いくかの改善点を実施例として説明する。

【0087】

<TDCレプリカ>

はじめに図1の構成にTDCレプリカを追加した実施例を説明する。TDCでの測定結果の正規化処理、すなわち遅延素子の段数情報の位相差をDCOの出力信号FO1周期に対する割合に変換する処理を行う際に、FO1周期に相等するTDC内の遅延素子の段数を測定する必要がある。本発明の一実施例では、FOの1周期を測定するTDCを別途用意している。

【0088】

図3は、本実施例の構成を示す図である。図3において、図1に示した前記実施形態の構成と同一又は同等の要素には同一の参照符号が付されている。以下では、同一又は同等の要素の説明は省略する。

【0089】

図3において、図1の前記実施形態に追加されたTDCレプリカ21は、DCO19の出力クロック信号FOを入力し、FO1周期の測定結果TREP(FO1周期をTDCの遅延素子段数に換算した値)を出力する。位相誤差演算器16では、例えば、第1、第2のTDC13、14の出力(遅延素子の段数で表される)を、TDCレプリカ21からのTREP(FOの1周期相等の遅延段数)を用いて正規化し、0と1の間の小数とする。

【0090】

図3のTDCレプリカ21は、図1のTDC13、14の構成例として説明した図26のTDCにおいて、A端子とB端子にFOを共通に入力することで、FO1周期に相等する遅延素子段数を測定することができる。あるいは、FOのデューティが50%の場合、図24のTDCの出力TDC_FALLとTDC_RISEからHighパルスのパルス幅を求め、これを2倍することで1周期を求めてもよい。

【0091】

図27にTDCレプリカ21の構成の別の例を示す。図27の基本構成は図26と同一であるが、FOの一周期の測定結果を移動平均(平滑化)する移動平均回路を備え、移動平均した結果をFO周期信号TREPとして出力する。図27を参照すると、図26と同様に、m+1個のフリップフロップ(FF1〜FFm+1)と、m+1個の遅延素子(BO1、BO2、・・・BOm+1)と、各フリップフロップ(FF1〜FFm)と、その右隣のフリップフロップ(FF2〜FFm+1)の反転信号のANDをとるAND回路(AND1〜ANDm)と、AND回路(AND1〜ANDm)の出力FOW[m−1]〜FOW[0]をバス化したmビット信号FOW[m−1:0]を入力するバイナリ化エンコーダ301と、バイナリ化エンコーダ301の出力FOW_BINの移動平均をとり、TREPとして出力する移動平均回路302を備えている。

【0092】

図28は、図27のTDCレプリカ21の動作の一例を示すタイミング図である。FOの1周期を遅延素子の段数として検出し、その値を元に、FO周期信号TREPを生成する。FOの立ち上がりエッジから次のサイクルの立ち上がりエッジの遅延を測定している。時刻t1でFOがHighに立ち上がり、時刻t2で、FOから遅延してFO1がHighに立ち上がり、同様にしてFO2〜FOmがそれぞれ前段の出力から所定の遅延をもってHighに立ち上がり、時刻t3でFOm+1がHighに立ち上がる。FOの立ち上がりエッジに対してHighレベルの遅延クロックFOk〜FOm−1(0<k<m−1)がフリップフロップFFk〜FFm−1のデータ端子に入力され、フリップフロップFFk〜FFm−1の出力であるサンプリング信号FOPk〜FOPm−1が時刻t1でHighに立ち上がる。サンプリング信号FOPmはLowであるため、AND回路ANDm−1の出力が「1」となり、エッジ抽出信号FOW[1]だけが時刻t1でHighとなる。その他のAND回路はいずれか一方の入力端子が0であるため出力はLowである。バイナリ化エンコーダ301は、エッジ検出信号FOW[m−1:0]に応じてデジタルデータFOW_BINを出力する。図28の例の場合、FOW_BINは、遅延素子の(m−FOW_BIN)段分が、DCO19の出力クロックFOの1周期にあたるとして、「m−1」がデジタルデータFOW_BINとして出力される。FOをクロックとして入力する移動平均回路302によって、所定数のFOW_BINが平均化され(平滑化され)、平均化した値がFO周期信号TREPとして出力される。かかる構成によれば、DCO19の出力信号FOのジッタ、ノイズ等によって、FOW_BINの値がずれることがあってもそのずれを平均化することで吸収し、より正確なクロックFOの1周期の測定が可能である。

【0093】

<カウンタ構成>

次に、本発明の別の実施例として、カウンタの変更と同期非同期の処理について説明する。実際の回路(実回路)において、PLLのロック時は、FRの立ち上がりエッジとFDの立ち上がりエッジは近傍にあることがほとんどである。

【0094】

図1の実施形態においては、FF15でFRとFDの遅れ進みを判断し、カウンタ17のスタート/エンドをFR/FDで制御している。FR/FDのいずれの信号でカウンタ17におけるFOのカウント動作のスタート/ストップを行うかは、FF15の出力SELで選択され、FRの立ち上がりエッジがFDの立ち上がりエッジよりも位相が進んでいれば、FRをカウンタ17のスタート、FDをエンドとする制御を行う。この制御は、FRとFDのエッジ(立ち上がりエッジ)が近傍にある場合、実現は困難となる。また、カウンタ17自身も、ロック近傍では、0や1しか値を取らない(ロック状態では、FDとFRの位相差の整数部分に対応するカウント値は0又は1の近辺で揺動する)。このため、リセットの解除や、カウント動作の高速動作が必要とされる。しかしながら、その実現はかなり困難と思料されることから、FR/FDをカウンタ17のスタート/エンドを制御する制御信号として用いる構成ではなく、図4に示すように、常にカウント動作しているカウンタ(CONT)17のカウンタ値を、FRとFDでサンプリングする構成としてもよい。

【0095】

すなわち、図4において、カウンタ17は、FOを常時カウントしており、FRとFDのそれぞれのパルスの立ち上がりエッジで、カウント値をサンプリング(ラッチ)し、時間的に前後2点でサンプルしたカウント値の差分から、FRとFDの位相差(整数部分、FOのエッジが何個あるか)を求める。カウンタ17ではFOの例えば立ち上がりエッジのタイミングでカウント値を変化させ、FOと非同期のFRやFDの立ち上がりエッジでカウンタ17のカウント値をサンプリング(ラッチ)する。したがって、FOとFR、FDは非同期(エッジは近い位置にあるが、同期関係ではない)であるため、FR、FDのサンプリングのタイミングが、FOのカウント値が遷移するタイミングと重なる可能性がある。

【0096】

例えば図5に例示したように、カウント値の変化時(図5のTdx)と、FR/FDによるカウント値のサンプリングのタイミングが重なる場合(図5のXで示す位置のタイミング)、正しいデータを取り込むことはできない。Tdataはカウンタ17における1データ期間であり、FOの1周期に対応する。

【0097】

この不具合を回避するために、FRやFDを、

Tdx<Tdsa<2×Tdsa<Tdata ・・・(10)

を満たす遅延時間Tdsa、2×Tdsaだけ、遅延させた信号を生成し、これらの遅延信号で、カウンタ17のカウント値をサンプルし、サンプルした値から、正しい値を判定する。

【0098】

図6に示す例では、FRをそれぞれTdsa、2×Tdsa遅延させた遅延信号FR1、FR2を作成し、FR、FR1、FR3の三つの信号の各立ち上がりエッジでカウンタ17のカウント値をサンプリングする。FRによるサンプル値はX(NG)であるが、FR1、FR2ではBを取り込み、TDCでの状態(位相差)と併せて判定する。この場合、FRによりサンプルしたカウント値としてBが用いられる。

【0099】

図6の例は、図4のカウンタ17のカウント値がバイナリデータ(バイナリカウンタ)である。バイナリデータの場合、桁上がりが発生すると、遷移時間は長く、エラーデータをサンプリングする可能性も高くなる。この懸念は、バイナリカウンタをグレイコード・カウンタに変更することで解消される。

【0100】

グレイコード(Gray code)では、ある値から隣接する値に変更する際に常に1ビット移しか変化しない。図6において、カウント値のXの箇所をサンプリングしても、その前又は後のカウント値を捕獲(キャプチュア)することができる。このため、サンプリングポイントは2点で済む。

【0101】

図7において、FRではA、FRからTdsa遅延したFR1では、Bをサンプリングした場合、TDC13の状態(FOとFRの位相の進み遅れ)を併せて判断する(位相誤差演算回路16で判断される)。この場合、Bが用いられる。

【0102】

FOをカウントするカウンタ17として、グレイコード・カウンタを用い、図4に示すように、常時動作するカウンタ17のカウント値を、FRとFDでFOとサンプリングする構成において、カウンタ17は常に動き続けるために、カウンタのフルビットまでカウントすると、オートクリアして0から、再度、カウントアップを開始する。FRとFDのサンプリングのタイミングが、オートクリアを間に挟む場合、カウンタ17により測定される整数部(integer part)の位相誤差が間違った値となる可能性がある。

【0103】

すなわち、図8に示すように、カウンタ値が無限の理想カウンタの場合、FRとFDによるカウンタ17のカウント値をサンプリングした値の差分によって、FRとFDの位相差の整数部分を検出することが可能である。

【0104】

位相誤差の整数部分=FDのカウンタ値−FRのカウンタ値 ・・・(11)

(ただし、位相誤差が正の場合、遅れ、負の場合、進みに対応する。)

【0105】

図8の(1)の場合、

FDのカウンタ値(=258)−FRのカウンタ値(=6)

=258−6

=252(遅れ)

【0106】

図8の(2)の場合、

FDのカウンタ値(=250)−FRのカウンタ値(=578)

=250−578

=−328(進み)

【0107】

しかしながら、カウンタ値が有限の場合(例えば8ビット:0〜255)、図10に示すように、

(1)の場合、

FDのカウンタ値=258は、

258 modulo 256=2(258−256=2)

となり、

FDのカウンタ値(=2)−FRのカウンタ値(=6)

=2−6

=−4(進み)

となる。

【0108】

(2)の場合、578は、

578 modulo 256=66

となり、

FDのカウンタ値(=250)−FRのカウンタ値(=578)

=250−66

=184(遅れ)

となる。

【0109】

図10は、カウンタ17として、理想カウンタ(無限カウンタ)を用いた場合の位相誤差検出特性を示す。横軸は位相差(FRとFDの位相差)、縦軸は位相誤差カウンタ値(カウンタ17のカウント値)である。位相差が大、あるいは小(負に大)となるにしたがって位相誤差カウンタ値も大あるいは小(負に大)となり、一定の勾配を有する。

【0110】

図11に、図4のカウンタ17として有限カウンタを用いた場合の位相誤差検出特性を示す。有限カウンタの場合、測定できる位相差は、理論上、カウンタの最大値±Maxまでとなる。それ以上、以下では再度、0に巻き戻る。

【0111】

図12の実線は、図11の特性と同一であるが、状態によっては、破線で示す特性を辿る場合がある。これは、FRとFDの位相差分を算出する際に、FRとFDのエッジの比較を行うべきエッジのカウント値間で、カウンタ17に0への巻き戻りが発生する場合である。

【0112】

FDのカウンタ値−FRのカウンタ値

=258−6

=252

となるべきところ、FRとFDのエッジの間にカウンタが0となり、

FDのカウンタ値−FRのカウンタ値

=2−6

=−4

に写像される。

【0113】

この場合、本来の位相差、遅れ/進み情報のいずれも誤った情報をとり得ることになる。そこで、本実施例では、FRとFDの位相差±の判定だけでなく、図1のFF15の出力信号SELを用いて、FRとFDの位相の遅れ/進みの判定を行い、位相誤差カウンタ値が正値であるべきところ、負値である状態や、負値であるべきところ、正値であるという状態を、再度、写像し直す。SEL信号(FDの立ち上がりエッジがFRの立ち上がりエッジよりも位相が進んでいるとき(位相差が+のとき)、論理1、遅れているとき、論理0)によるFR/FDの位相の遅れ/進みの情報をもとに、図13に示すように、位相誤差カウンタ値の極性が異なる場合、SEL信号の値を、位相誤差カウンタ値に反映させる。位相誤差(位相誤差カウンタ値)の符号がSEL信号と等しい場合、位相誤差(位相誤差カウンタ値)をそのまま出力し、位相誤差(位相誤差カウンタ値)の符号ビットがSEL信号と異なる場合、SEL信号に符号ビットを合わせる。

【0114】

あるいは、位相誤差カウンタ値の符号がBang―Bang特性(位相差が+の領域で正値、位相差が−の領域で負値をとる特性)の極性と異なる場合、さらに写像して元に戻す。

【0115】

FDのカウンタ値−FRのカウンタ値

=2−6

=−4

の場合、

Bang―Bang特性の極性が正であるため、

−4+256=252

に写像して元に戻す。

【0116】

この結果、図13の破線で示す特性は実線で示す本来の特性となる。なお、図13に示す例では、カウンタは−255(バイナリ表現:00000001)から−1(バイナリ表現:11111111)、0〜+255(バイナリ表現:11111111)の値をとる。

【0117】

以上の改善を行なった実施例が最終的にインプリメント(実装)可能な回路構成となり、De−Skew用ADPLLとして実現可能な構成となる。

【0118】

本実施例により、逓倍PLL(SSCG(Spread Spectrum Clock Generator))は勿論のこと、De−Skew用ADPLLを構成することができる。

【0119】

上記したように、本実施形態によれば、また、TDC13、14を備えたことで(すなわち、TDC14を1つ追加することで)、FOを仲介してそれぞれの位相差を測定し、その後、演算にて最終的に求めたいFR−FDの位相差を求める構成としたことで、TDCの位相差の測定時間を増加させることなく、De−Skew用ADPLLを構成することができる。

【0120】

なお、上記実施形態では、TDC13、14においてFOとFR、FOとFDの立ち上がりエッジの位相差を例を説明したが、信号のエッジとしては立ち上がりエッジで限定されるものでなく、立ち下りエッジを用いる構成としてもよい。

【0121】

なお、上記の特許文献1、2、非特許文献1の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0122】

1 TDC

2 FF

3 アキュムレータ

4 アキュムレータ

5 正規化回路(DCO period normalization)

6 位相検出器

8 サンプラ

10、30 ADPLL

11、31 前段分周器

12、32 帰還分周器

13 TDC

14 TDC

15 FF

16 位相誤差演算器

17 カウンタ

18 デジタルフィルタ

19 デジタル制御発振器

20、37 後段分周器

21 TDCレプリカ

33 位相周波数比較器

34 チャージポンプ

35 アナログフィルタ

36 電圧制御発振器

41、42 CTS

43、44 ユーザロジック

102 アキュムレータ

106 波形成型器

110 FREF

112 CKR

118 インクリメンタ

120 ラッチ

116 FCW

201 TDC

211 バッファ(遅延素子)

212 フリップフロップ

213 AND回路

214 インバータ

215 バイナリ化デコーダ

301 バイナリ化エンコーダ

302 移動平均回路

401 Delay Line

402 Control Logic

403 Sampler

405 加算器

404 Counter

406 Offset Control

407 Prescaler

408 Program Counter

409 Swallow Counter

【特許請求の範囲】

【請求項1】

入力された第1のクロック信号と第2のクロック信号のうち位相が進んでいる方のクロック信号と、位相が遅れている方のクロック信号の間の時間期間に、第3のクロック信号の有効エッジがいくつあるかを計数するカウンタと、

前記第1のクロック信号と前記第3のクロック信号の位相差を、前記第3のクロック信号の1サイクルよりも短時間の時間分解能で測定する第1の位相差検出回路と、

前記第2のクロック信号と前記第3のクロック信号の位相差を、前記第3のクロック信号の1サイクルよりも短時間の時間分解能で測定する第2の位相差検出回路と、

前記第1のクロック信号と前記第2のクロック信号のうちどちらが位相が進んでいるかを判定する判定器と、

前記カウンタの出力、前記第1、第2の位相差検出回路の出力、及び、前記判定器の出力を元に、前記第1のクロック信号と前記第2のクロック信号の位相誤差を演算する位相誤差演算器と、

前記位相誤差を平滑化するデジタルフィルタと、

前記デジタルフィルタで平滑化された位相誤差に基づき発振周波数を可変させ前記第3のクロック信号を出力するデジタル制御発振器と、

を備え、

前記第2のクロック信号は、前記第3のクロック信号を分周した信号から生成される、ことを特徴とするデジタル位相同期ループ回路。

【請求項2】

リファレンスクロック信号を入力して分周し前記第1のクロック信号を出力する第1の分周器と、

前記第3のクロック信号を入力して分周し出力クロック信号を出力する第2の分周器と、

前記第2の分周器の出力クロック信号を帰還させた信号を入力して分周し前記第2のクロック信号を出力する第3の分周器と、

を備え、

前記第1の位相差検出回路は、

前記第1の分周器から出力される前記第1のクロック信号と、前記第3のクロック信号とを入力し、前記第1のクロック信号と前記第3のクロック信号の有効エッジの間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定し、

前記第2の位相差検出回路は、

前記第3の分周器から出力される前記第2のクロック信号と、前記第3のクロック信号とを入力し、前記第2のクロック信号と前記第3のクロック信号の有効エッジの間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定し、

前記判定器は、

前記第1分周器からの前記第1のクロック信号と前記第3の分周器からの前記第2のクロック信号のうちの一方をクロック端子、他方をデータ端子に入力し、前記第1のクロック信号の有効エッジに対して前記第2のクロックの有効エッジの位相が進んでいるか遅れているかを判別して出力するフリップフロップを備え、

前記カウンタは、

前記第1のクロック信号と前記第2のクロック信号のうち位相が進んでいる一方のクロック信号の有効エッジと、位相が遅れている他方のクロック信号の有効エッジで規定される時間範囲内での、前記第3のクロック信号の有効エッジのカウント値を提供する、ことを特徴とする請求項1記載のデジタル位相同期ループ回路。

【請求項3】

リファレンスクロック信号を入力して分周し第1のクロック信号を出力する第1の分周器と、

入力されたデジタル信号に応じて発振周波数が可変させ第3のクロック信号を出力するデジタル制御発振器と、

前記デジタル制御発振器からの前記第3のクロック信号を入力して分周し出力クロック信号を出力する第2の分周器と、

前記第2の分周器から出力される出力クロック信号を帰還させた信号を入力して分周し第2のクロック信号を出力する第3の分周器と、

前記第1の分周器からの前記第1のクロック信号と、前記デジタル制御発振器からの前記第3のクロック信号とを入力し、前記第1のクロック信号の有効エッジと前記第3のクロック信号の有効エッジ間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定する第1の位相差検出回路と、

前記第3の分周器からの前記第2のクロック信号と、前記デジタル制御発振器からの前記第3のクロック信号とを入力し、前記第2のクロック信号の有効エッジと前記第3のクロック信号の有効エッジ間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定する第2の位相差検出回路と、

前記第1分周器からの前記第1のクロック信号と前記第3の分周器からの前記第2のクロック信号のうちの一方をクロック端子、他方をデータ端子に入力し、前記第1のクロック信号の有効エッジに対して前記第2のクロックの有効エッジの位相が進んでいるか遅れているかを判別して出力するフリップフロップからなる判定器と、

前記第1分周器からの前記第1のクロック信号と、前記第3分周器からの前記第2のクロック信号と、前記デジタル制御発振器からの前記第3のクロック信号とを入力し、前記第1のクロック信号と前記第2のクロック信号のうち位相が進んでいる一方のクロック信号の有効エッジと、位相が遅れている他方のクロック信号の有効エッジで規定される時間期間内での、前記第3のクロック信号の有効エッジのカウント値を提供するカウンタと、

前記カウンタでのカウント値と、前記第1及び第2の位相差検出回路の出力と、前記判定器での判定結果とを入力し、前記第1のクロック信号と前記第2のクロック信号の有効エッジ間の位相差を演算する位相誤差演算器と、

前記位相誤差演算器で演算された位相差を入力しフィルタ処理したデジタル信号を前記デジタル制御発振器に出力するデジタルフィルタと、

を備えている、ことを特徴とするデジタル位相同期ループ回路。

【請求項4】

前記カウンタは、前記判定器の判定結果に基づき、前記第1のクロック信号と前記第2のクロック信号のうち位相が先行する一方のクロック信号により、前記第3のクロック信号のカウント動作を開始し、

前記第1のクロック信号と前記第2のクロック信号のうち位相が遅れた他方のクロック信号により、前記デジタル制御発振器からの前記第3のクロック信号のカウント動作を停止する、ことを特徴とする請求項3記載のデジタル位相同期ループ回路。

【請求項5】

前記カウンタは、前記第3のクロック信号をカウントし、

前記第1のクロック信号と前記第2のクロック信号のうち位相が進んでいる一方のクロック信号の有効エッジで、前記カウンタのカウント値をラッチし、

前記第1のクロック信号と前記第2のクロック信号のうち位相が遅れた他方のクロック信号の有効エッジで、前記カウンタのカウント値をラッチし、

前記位相が進んでいる一方のクロック信号のエッジでサンプリングしたカウント値と、前記位相が遅れている他方のクロック信号のエッジでサンプリングしたカウント値との差分をとり、前記差分を、前記位相が進んでいる一方のクロック信号のエッジと、前記位相が遅れている他方のクロック信号のエッジで規定される時間期間内での、前記第3のクロック信号の有効エッジのカウント値とする、ことを特徴とする請求項3記載のデジタル位相同期ループ回路。

【請求項6】

前記第1のクロック信号と前記第2のクロック信号の少なくとも1つについて前記クロック信号を予め定められた時間遅延させた少なくとも1つの遅延信号を生成し、

前記カウンタにおいて、前記第1のクロック信号と前記第2のクロック信号の少なくとも1つについて前記遅延信号で前記カウンタのカウント値をサンプリングする、ことを特徴とする請求項5記載のデジタル位相同期ループ回路。

【請求項7】

前記位相誤差演算器は、前記クロック信号と前記遅延信号によって前記カウンタのカウント値をサンプリングした複数のカウント値と、前記第1位相差検出回路又は前記第2の位相差検出回路の位相差から1つのカウント値を選択する、ことを特徴とする請求項5又は6記載のデジタル位相同期ループ回路。

【請求項8】

前記カウンタが、カウント値をグレイコードで出力するカウンタである、ことを特徴とする請求項5乃至7のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項9】

前記カウンタは、前記デジタル制御発振器からの前記第3のクロック信号を常時カウントし、カウント値が最大値に達すると再びカウント値0からカウントを行い、

前記第1のクロック信号に対して前記第2のクロック信号の位相が進んでいるか遅れているかの判別結果に基づき、前記位相が進んでいる一方のクロック信号の有効エッジでラッチしたカウント値と、前記位相が遅れている他方のクロック信号の有効エッジでラッチしたカウント値との間に、前記カウンタのカウント値の0への巻き戻りが存在する場合に対応して、前記差分を補正する、ことを特徴とする請求項5乃至8のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項10】

前記デジタル制御発振器からの前記第3のクロック信号の1周期を測定する第3の位相差検出回路を備え、

前記位相誤差演算器は、前記第3の位相差検出回路の出力信号を入力し、前記第1及び第2の位相差検出回路における位相差の測定結果を、前記第3の位相差検出回路で測定した前記デジタル制御発振器からの前記第3のクロック信号の1周期で正規化する、ことを特徴とする請求項2乃至9のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項11】

前記第1、第2の位相差検出回路は、各々、

第1、第2の端子を有し、

前記第1の端子に入力された第1の信号を遅延させる、カスケード接続された複数段の第1の遅延素子と、

前記第1の信号を、前記第2の端子に入力された第2の信号の有効エッジでサンプルする第1のフリップフロップと、

前記複数の第1の遅延素子の出力を、前記第1のフリップフロップと共通に前記第2の信号のエッジでサンプルする複数段の第2のフリップフロップと、

前記第1のフリップフロップの出力と、初段の前記第2のフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する第1の検出回路と、

2段目以降の前記複数の第2のフリップフロップの隣接する二つのフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する複数の第2の検出回路と、

前記第1の検出回路と、前記複数の第2の検出回路と検出結果を受け、前記位相差を2進符号にエンコードする回路と、

を備えていることを特徴とする請求項1記載のデジタル位相同期ループ回路。

【請求項12】

前記第3の位相差検出回路は、前記デジタル制御発振器からの前記第3のクロック信号を共通に入力する第1、第2の端子を有し、

前記第1の端子に入力された第1の信号を遅延させる、カスケード接続された複数の第1の遅延素子と、

前記第1の信号を、前記第2の端子に入力された第2の信号の有効エッジでサンプルする第1のフリップフロップと、

前記複数の第1の遅延素子の出力を、前記第1のフリップフロップと共通に前記第2の信号のエッジでサンプルする複数段の第2のフリップフロップと、

前記第1のフリップフロップの出力と、初段の前記第2のフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する第1の検出回路と、

2段目以降の前記複数の第2のフリップフロップの隣接する二つのフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する複数の第2の検出回路と、

前記第1の検出回路と、前記複数の第2の検出回路と検出結果を受け、前記位相差を2進符号にエンコードする回路と、

前記エンコード結果を予め定められた個数移動平均をとった結果を1周期として出力する回路と、

を備えている、ことを特徴とする請求項10記載のデジタル位相同期ループ回路。

【請求項13】

前記第2の分周器からの出力クロック信号が、帰還路のクロックツリーシンセシスバッファに入力され、前記クロックツリーシンセシスバッファの出力が前記第3の分周器に入力される、ことを特徴とする請求項1乃至13のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項14】

請求項1乃至13のいずれか1項記載の前記デジタル位相同期ループ回路を備えた半導体装置。

【請求項1】

入力された第1のクロック信号と第2のクロック信号のうち位相が進んでいる方のクロック信号と、位相が遅れている方のクロック信号の間の時間期間に、第3のクロック信号の有効エッジがいくつあるかを計数するカウンタと、

前記第1のクロック信号と前記第3のクロック信号の位相差を、前記第3のクロック信号の1サイクルよりも短時間の時間分解能で測定する第1の位相差検出回路と、

前記第2のクロック信号と前記第3のクロック信号の位相差を、前記第3のクロック信号の1サイクルよりも短時間の時間分解能で測定する第2の位相差検出回路と、

前記第1のクロック信号と前記第2のクロック信号のうちどちらが位相が進んでいるかを判定する判定器と、

前記カウンタの出力、前記第1、第2の位相差検出回路の出力、及び、前記判定器の出力を元に、前記第1のクロック信号と前記第2のクロック信号の位相誤差を演算する位相誤差演算器と、

前記位相誤差を平滑化するデジタルフィルタと、

前記デジタルフィルタで平滑化された位相誤差に基づき発振周波数を可変させ前記第3のクロック信号を出力するデジタル制御発振器と、

を備え、

前記第2のクロック信号は、前記第3のクロック信号を分周した信号から生成される、ことを特徴とするデジタル位相同期ループ回路。

【請求項2】

リファレンスクロック信号を入力して分周し前記第1のクロック信号を出力する第1の分周器と、

前記第3のクロック信号を入力して分周し出力クロック信号を出力する第2の分周器と、

前記第2の分周器の出力クロック信号を帰還させた信号を入力して分周し前記第2のクロック信号を出力する第3の分周器と、

を備え、

前記第1の位相差検出回路は、

前記第1の分周器から出力される前記第1のクロック信号と、前記第3のクロック信号とを入力し、前記第1のクロック信号と前記第3のクロック信号の有効エッジの間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定し、

前記第2の位相差検出回路は、

前記第3の分周器から出力される前記第2のクロック信号と、前記第3のクロック信号とを入力し、前記第2のクロック信号と前記第3のクロック信号の有効エッジの間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定し、

前記判定器は、

前記第1分周器からの前記第1のクロック信号と前記第3の分周器からの前記第2のクロック信号のうちの一方をクロック端子、他方をデータ端子に入力し、前記第1のクロック信号の有効エッジに対して前記第2のクロックの有効エッジの位相が進んでいるか遅れているかを判別して出力するフリップフロップを備え、

前記カウンタは、

前記第1のクロック信号と前記第2のクロック信号のうち位相が進んでいる一方のクロック信号の有効エッジと、位相が遅れている他方のクロック信号の有効エッジで規定される時間範囲内での、前記第3のクロック信号の有効エッジのカウント値を提供する、ことを特徴とする請求項1記載のデジタル位相同期ループ回路。

【請求項3】

リファレンスクロック信号を入力して分周し第1のクロック信号を出力する第1の分周器と、

入力されたデジタル信号に応じて発振周波数が可変させ第3のクロック信号を出力するデジタル制御発振器と、

前記デジタル制御発振器からの前記第3のクロック信号を入力して分周し出力クロック信号を出力する第2の分周器と、

前記第2の分周器から出力される出力クロック信号を帰還させた信号を入力して分周し第2のクロック信号を出力する第3の分周器と、

前記第1の分周器からの前記第1のクロック信号と、前記デジタル制御発振器からの前記第3のクロック信号とを入力し、前記第1のクロック信号の有効エッジと前記第3のクロック信号の有効エッジ間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定する第1の位相差検出回路と、

前記第3の分周器からの前記第2のクロック信号と、前記デジタル制御発振器からの前記第3のクロック信号とを入力し、前記第2のクロック信号の有効エッジと前記第3のクロック信号の有効エッジ間の位相差を、前記第3のクロック信号の1周期よりも短い時間分解能で、且つ、前記第3のクロック信号の1周期以下の測定範囲で測定する第2の位相差検出回路と、

前記第1分周器からの前記第1のクロック信号と前記第3の分周器からの前記第2のクロック信号のうちの一方をクロック端子、他方をデータ端子に入力し、前記第1のクロック信号の有効エッジに対して前記第2のクロックの有効エッジの位相が進んでいるか遅れているかを判別して出力するフリップフロップからなる判定器と、

前記第1分周器からの前記第1のクロック信号と、前記第3分周器からの前記第2のクロック信号と、前記デジタル制御発振器からの前記第3のクロック信号とを入力し、前記第1のクロック信号と前記第2のクロック信号のうち位相が進んでいる一方のクロック信号の有効エッジと、位相が遅れている他方のクロック信号の有効エッジで規定される時間期間内での、前記第3のクロック信号の有効エッジのカウント値を提供するカウンタと、

前記カウンタでのカウント値と、前記第1及び第2の位相差検出回路の出力と、前記判定器での判定結果とを入力し、前記第1のクロック信号と前記第2のクロック信号の有効エッジ間の位相差を演算する位相誤差演算器と、

前記位相誤差演算器で演算された位相差を入力しフィルタ処理したデジタル信号を前記デジタル制御発振器に出力するデジタルフィルタと、

を備えている、ことを特徴とするデジタル位相同期ループ回路。

【請求項4】

前記カウンタは、前記判定器の判定結果に基づき、前記第1のクロック信号と前記第2のクロック信号のうち位相が先行する一方のクロック信号により、前記第3のクロック信号のカウント動作を開始し、

前記第1のクロック信号と前記第2のクロック信号のうち位相が遅れた他方のクロック信号により、前記デジタル制御発振器からの前記第3のクロック信号のカウント動作を停止する、ことを特徴とする請求項3記載のデジタル位相同期ループ回路。

【請求項5】

前記カウンタは、前記第3のクロック信号をカウントし、

前記第1のクロック信号と前記第2のクロック信号のうち位相が進んでいる一方のクロック信号の有効エッジで、前記カウンタのカウント値をラッチし、

前記第1のクロック信号と前記第2のクロック信号のうち位相が遅れた他方のクロック信号の有効エッジで、前記カウンタのカウント値をラッチし、

前記位相が進んでいる一方のクロック信号のエッジでサンプリングしたカウント値と、前記位相が遅れている他方のクロック信号のエッジでサンプリングしたカウント値との差分をとり、前記差分を、前記位相が進んでいる一方のクロック信号のエッジと、前記位相が遅れている他方のクロック信号のエッジで規定される時間期間内での、前記第3のクロック信号の有効エッジのカウント値とする、ことを特徴とする請求項3記載のデジタル位相同期ループ回路。

【請求項6】

前記第1のクロック信号と前記第2のクロック信号の少なくとも1つについて前記クロック信号を予め定められた時間遅延させた少なくとも1つの遅延信号を生成し、

前記カウンタにおいて、前記第1のクロック信号と前記第2のクロック信号の少なくとも1つについて前記遅延信号で前記カウンタのカウント値をサンプリングする、ことを特徴とする請求項5記載のデジタル位相同期ループ回路。

【請求項7】

前記位相誤差演算器は、前記クロック信号と前記遅延信号によって前記カウンタのカウント値をサンプリングした複数のカウント値と、前記第1位相差検出回路又は前記第2の位相差検出回路の位相差から1つのカウント値を選択する、ことを特徴とする請求項5又は6記載のデジタル位相同期ループ回路。

【請求項8】

前記カウンタが、カウント値をグレイコードで出力するカウンタである、ことを特徴とする請求項5乃至7のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項9】

前記カウンタは、前記デジタル制御発振器からの前記第3のクロック信号を常時カウントし、カウント値が最大値に達すると再びカウント値0からカウントを行い、

前記第1のクロック信号に対して前記第2のクロック信号の位相が進んでいるか遅れているかの判別結果に基づき、前記位相が進んでいる一方のクロック信号の有効エッジでラッチしたカウント値と、前記位相が遅れている他方のクロック信号の有効エッジでラッチしたカウント値との間に、前記カウンタのカウント値の0への巻き戻りが存在する場合に対応して、前記差分を補正する、ことを特徴とする請求項5乃至8のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項10】

前記デジタル制御発振器からの前記第3のクロック信号の1周期を測定する第3の位相差検出回路を備え、

前記位相誤差演算器は、前記第3の位相差検出回路の出力信号を入力し、前記第1及び第2の位相差検出回路における位相差の測定結果を、前記第3の位相差検出回路で測定した前記デジタル制御発振器からの前記第3のクロック信号の1周期で正規化する、ことを特徴とする請求項2乃至9のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項11】

前記第1、第2の位相差検出回路は、各々、

第1、第2の端子を有し、

前記第1の端子に入力された第1の信号を遅延させる、カスケード接続された複数段の第1の遅延素子と、

前記第1の信号を、前記第2の端子に入力された第2の信号の有効エッジでサンプルする第1のフリップフロップと、

前記複数の第1の遅延素子の出力を、前記第1のフリップフロップと共通に前記第2の信号のエッジでサンプルする複数段の第2のフリップフロップと、

前記第1のフリップフロップの出力と、初段の前記第2のフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する第1の検出回路と、

2段目以降の前記複数の第2のフリップフロップの隣接する二つのフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する複数の第2の検出回路と、

前記第1の検出回路と、前記複数の第2の検出回路と検出結果を受け、前記位相差を2進符号にエンコードする回路と、

を備えていることを特徴とする請求項1記載のデジタル位相同期ループ回路。

【請求項12】

前記第3の位相差検出回路は、前記デジタル制御発振器からの前記第3のクロック信号を共通に入力する第1、第2の端子を有し、

前記第1の端子に入力された第1の信号を遅延させる、カスケード接続された複数の第1の遅延素子と、

前記第1の信号を、前記第2の端子に入力された第2の信号の有効エッジでサンプルする第1のフリップフロップと、

前記複数の第1の遅延素子の出力を、前記第1のフリップフロップと共通に前記第2の信号のエッジでサンプルする複数段の第2のフリップフロップと、

前記第1のフリップフロップの出力と、初段の前記第2のフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する第1の検出回路と、

2段目以降の前記複数の第2のフリップフロップの隣接する二つのフリップフロップの出力が予め定められた値の組み合わせであるか否かを検出する複数の第2の検出回路と、

前記第1の検出回路と、前記複数の第2の検出回路と検出結果を受け、前記位相差を2進符号にエンコードする回路と、

前記エンコード結果を予め定められた個数移動平均をとった結果を1周期として出力する回路と、

を備えている、ことを特徴とする請求項10記載のデジタル位相同期ループ回路。

【請求項13】

前記第2の分周器からの出力クロック信号が、帰還路のクロックツリーシンセシスバッファに入力され、前記クロックツリーシンセシスバッファの出力が前記第3の分周器に入力される、ことを特徴とする請求項1乃至13のいずれか1項に記載のデジタル位相同期ループ回路。

【請求項14】

請求項1乃至13のいずれか1項記載の前記デジタル位相同期ループ回路を備えた半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【公開番号】特開2012−49659(P2012−49659A)

【公開日】平成24年3月8日(2012.3.8)

【国際特許分類】

【出願番号】特願2010−187929(P2010−187929)

【出願日】平成22年8月25日(2010.8.25)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年3月8日(2012.3.8)

【国際特許分類】

【出願日】平成22年8月25日(2010.8.25)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]