デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、位相同期して所定の周波数信号を出力するデジタル位相同期回路および物理量検出センサに関する。

【背景技術】

【0002】

一般に、物理量検出センサの処理回路は、アナログ回路をデジタル回路に置き換えると、微細な半導体製造プロセスを用いて製造できるためICチップを小型化できコストを削減できる。また、入力したアナログ信号を早い段階でデジタル信号処理系に変換できればその効果はより大きい。

【0003】

特許文献1はアナログPLLを採用した技術の一例を示しており、図18は、この特許文献1の技術を適用したPLL回路のブロック構成を示している。PLL回路1は、波形整形回路2を通じて入力される入力信号に基づいて出力信号を出力するもので、電圧制御発振器(VCO)3および発振制御回路4を備えている。

【0004】

ここで、発振制御回路4は、制御電圧を生成するローパスフィルタ(LPF)5と、電圧制御発振器3の発振信号を分周して分周信号を生成する分周器(DIV)6と、入力信号と分周信号の位相差に基づいて充電信号または放電信号を出力する位相検出回路(PFD)7と、充電信号または放電信号に応じてローパスフィルタ5の制御電圧を増加または減少させるチャージポンプ(CP)8とを含んで構成されている。このようなブロック構成のアナログ回路の入力信号をAD変換し、アナログ回路をデジタル化すると、位相検出回路の位相比較結果にデジタル離散化による位相誤差が発生するため、正確な位相同期ができないという問題を生じる。この構成で位相誤差をなくすため高精度化しようとすると、サンプリング数を増やして高速サンプリングする必要がある。

【0005】

また、本願に関連したデジタル位相同期回路は特許文献2〜4にも開示されている。特許文献2記載の技術思想では、入力信号が非周期的な信号であり、非周期的に生じるゼロクロスの度に位相比較、周波数比較を行わなければならず、周波数比較器、ローパスフィルタに加えて、周波数比較器をスイッチによってオンオフ制御を行う回路を備える必要があるため、処理が複雑で回路サイズが大きい。

【0006】

また、特許文献3記載の技術思想では、デジタル位相同期回路において、時間軸離散的な時間点にのみ振幅値を有する入力信号におけるゼロクロス点を挟む2時間点の入力信号の振幅比を求めてゼロクロスを推定し、時間差に応じた位相量信号を出力している。

【0007】

しかしながら、この技術思想においても、入力信号はゼロクロス推定で位相を算出するも、比較信号はカウントのみによって位相を算出するため、高精度化のためにはカウントするクロックを高速にする必要があるとともに、ゼロクロス点を推定しカウンタのリセット信号などでち密なタイミングに反映する必要があるためタイミング設計が難しい。また、特許文献4記載の技術思想では、位相同期回路において、ゼロクロス点前後の離散入力信号を用いた数値演算処理により、サンプル点に対するゼロクロス点の位相を算出し、クロックの位相を制御している。しかしながら、簡単な構成で正確な位相同期を行うことができる構成が望まれている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2009−281888号公報

【特許文献2】特開平10−107623号公報

【特許文献3】特開昭55−115737号公報

【特許文献4】特開平06−119720号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、上記事情に鑑みてなされたもので、その目的は、簡単な構成で正確な位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供することにある。

【課題を解決するための手段】

【0010】

請求項1記載の発明によれば、次のように作用する。位相補正部はAD変換器のサンプリング値のゼロクロス前後の値を線形近似しゼロクロスタイミングの位相補正値を算出する。他方、クロック生成部はAD変換器のサンプリング値の符号情報に応じて符号クロックを生成し、位相比較部がクロック生成部の符号クロックと分周部の分周クロックとの位相差を算出する。すると、AD変換器のサンプリング値の符号が切替わるタイミングと分周部の分周クロックのタイミングの位相差を検出できる。

【0011】

調整出力部には、この位相比較部の位相差を位相補正部の位相補正値で補正した値が与えられるため、調整出力部はこの値に応じた調整量を制御発振部の入力調整値として出力し、制御発振部はこの調整量に応じてN逓倍周波数信号を発振出力できる。

【0012】

したがって、位相比較部、加減算部、調整出力部、制御発振部および分周部によるフィードバックループは、クロック生成部が生成した符号クロックの位相を位相補正部の位相補正値により補正しているため、位相を正確に同期することができ、制御発振部は位相同期した安定的なN逓倍周波数信号を発振出力できる。主に位相補正部、位相比較部により位相同期を図っているため、正確な位相同期処理を実現できる。

【0013】

また、アップダウンカウンタがクロック生成部の符号クロックによるカウント開始タイミングから一方向にカウントを開始し、分周部の分周クロックによるカウント転換タイミングにて逆方向にカウントを逆転し、クロック生成部の符号クロックによるカウント終了タイミングにて得られたカウント値を出力し、このカウント値を位相算出値とする。これにより、符号クロックと分周クロックの位相差を簡単な構成で算出できる。

【0014】

請求項2記載の発明によれば、アップダウンカウンタが、クロック生成部の符号クロックの立上りタイミングから所定の基準クロックに応じてダウンカウントし、当該ダウンカウントされてから分周部の分周クロックによる立下りタイミングを受け付けると当該立下りタイミングから基準クロックに応じてアップカウントする。そして、位相比較部は、クロック生成部の符号クロックの立上りタイミングにてアップダウンカウンタによるアップカウントを終了し、得られたカウント値を位相算出値として出力する。これにより、符号クロックと分周クロックの位相差を簡単な構成で算出できる。

【0015】

請求項3記載の発明に示すように、アップダウンカウンタが2つの同じカウンタを組み合わせてダウンカウントおよびアップカウントすると良い。

請求項4記載の発明によれば、位相補正部の第1減算器が遅延サンプリング値x(n−1)(立上りゼロクロス時は負数)を、AD変換器の現サンプリング値x(n)(立上りゼロクロス時は正数)から減算すると、減算値x(n)−x(n−1)を算出できる。そして、第1除算器がAD変換部の現サンプリング値x(n)を第1減算器の減算値(x(n)−x(n−1))によって除算すると、x(n)/(x(n)−x(n−1))を算出できる。この値は、AD変換部のゼロクロス前後のサンプリング値の振幅比分に相当する値となり、現サンプリングタイミングおよび遅延サンプリングタイミング間の時間に対する現サンプリングタイミングからゼロクロスタイミングの時間の比に対応する。

【0016】

位相比較部のアップダウンカウンタのダウンカウント増加分はアップカウント減少分となり、逆にダウンカウント減少分はアップカウント増加分となるため、位相比較部で得られた位相差に相当するカウント値はカウントクロックの2倍のカウント値となる。

【0017】

したがって、第1乗算器が、サンプリング周期に相当するカウントクロックのカウント値を−2倍した値を第1除算器の除算値x(n)/(x(n)−x(n−1))と乗算すれば、位相比較部と位相補正部のカウント値増減度をマッチさせた位相値を算出できる。したがって、加減算部が位相比較部によって算出した位相算出値に位相補正部によって算出した位相補正値を加減算して出力することでゼロクロスタイミングに応じた位相値を正確に出力できる。

【0018】

請求項5記載の発明によれば、位相補正部の第1減算器、第1除算器、第1乗算器は、その少なくとも何れか一つが演算許可/停止の切換機能を有しているため、第1減算器、第1除算器、第1乗算器の少なくとも一つを演算停止でき、演算停止中の消費電力を低減できる。

【0019】

請求項6記載の発明によれば、固定値設定器は、演算停止対象となる演算器の入力を固定値に設定するため、例えば演算器を構成するトランジスタがオンオフしたときに生じるスイッチング損失を低減でき、演算停止中における消費電力を低減できる。

【0020】

請求項7記載の発明によれば、第1減算器、第1除算器および第1乗算器がクロックに同期してデータを保持する構成であるとき、第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止すると良い。この場合、例えばクロックによって動作するトランジスタのオンオフ時のスイッチング損失を低減でき、演算停止中における消費電力を低減できる。

【0021】

請求項8記載の発明によれば、ゼロクロス検出部はAD変換器のサンプリング値がゼロクロスしたタイミングを検出するが、ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて、位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する期間を設定する。

【0022】

請求項9記載の発明によれば、クロック生成部の符号クロックを用いて位相補正部の第

1減算器、第1除算器および第1乗算器の何れか少なくとも何れか一つの演算を停止する期間を設定する。

【0023】

請求項10記載の発明によれば、位相補正部の第2加算器が、第2遅延器の遅延サンプリング値|x(n−1)|(x(n−1)は立上りゼロクロス時に負数)と絶対値演算器の演算値|x(n)|(x(n)は立上りゼロクロス時に正数)とを加算し、第2除算器が絶対値演算器の演算値|x(n)|を第2加算器の加算値(|x(n)|+|x(n−1)|)によって除算すると|x(n)|/(|x(n)|+|x(n−1)|)を算出できる。したがって、請求項4記載の発明と同様に、第2乗算器が、サンプリング周期に相当するカウントクロックのカウント値を−2倍した値を第2除算器の除算値|x(n)|/(|x(n)|+|x(n−1)|)と乗算すれば、位相比較部と位相補正部のカウント値増減度をマッチさせた位相値を算出でき、同様にゼロクロスタイミングに応じた位相値を正確に出力できる。

【0024】

請求項11記載の発明によれば、位相補正部の第2減算器、第2除算器、第2乗算器は、その少なくとも何れか一つが演算許可/演算停止の切換機能を有しているため、第2減算器、第2除算器、第2乗算器は演算停止することができ、演算停止中の消費電力を低減できる。

【0025】

請求項12記載の発明によれば、固定値設定器は、演算停止対象となる演算器の入力を固定値に設定するため、例えば演算器を構成するトランジスタがオンオフしたときに生じるスイッチング損失を低減でき、演算停止中の消費電力を低減できる。

【0026】

請求項13記載の発明によれば、第2減算器、第2除算器および第2乗算器がクロックに同期してデータを保持する構成であるとき、第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止すると良い。この場合、例えばクロックによって動作するトランジスタのオンオフ時のスイッチング損失を低減でき、演算停止中の消費電力を低減できる。

【0027】

請求項14記載の発明によれば、ゼロクロス検出部はAD変換器のサンプリング値がゼロクロスしたタイミングを検出するが、ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて、位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する期間を設定する。

【0028】

請求項15記載の発明によれば、クロック生成部の符号クロックを用いて位相補正部の第2減算器、第2除算器および第2乗算器の何れか少なくとも何れか一つの演算を停止する期間を設定する。

【0029】

請求項16記載の発明のように、AGC、信号検出部、請求項1ないし15の何れかに記載のデジタル位相同期回路を備えた物理量検出センサに適用すると良い。

【図面の簡単な説明】

【0030】

【図1】本発明の第1実施形態における振動型角速度センサの電気的構成を示すブロック図

【図2】位相同期回路のハードウェア構成図

【図3】位相補正部のハードウェア構成図

【図4】位相補正値の説明図

【図5】符号情報と符号クロックとの対応関係を示す図

【図6】位相比較部のハードウェア構成図

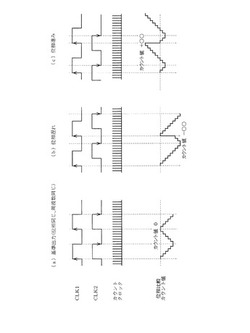

【図7】位相比較部の位相比較カウント値の説明図((a)は基準出力、(b)は位相遅れ、(c)は位相進み)

【図8】位相比較部の位相比較カウント値の説明図((a)は基準出力、(b)は周波数高、(c)は周波数低)

【図9】本発明の第2実施形態を示す図3相当図

【図10】本発明の第3実施形態を示す図6相当図

【図11】本発明の第4実施形態を示す図6相当図

【図12】本発明の第5実施形態を示す図6相当図

【図13】本発明の第6実施形態を示す説明図((a)は図3相当図、(b)(c)はデータマスク回路の構成例)

【図14】動作を概略的に示すタイミングチャート

【図15】本発明の第7実施形態を示す図3相当図

【図16】動作を概略的に示すタイミングチャート

【図17】本発明の第8実施形態を示す図9相当図

【図18】従来例を示す図2相当図

【発明を実施するための形態】

【0031】

(第1実施形態)

以下、本発明の物理量検出センサを振動型角速度センサに適用した第1実施形態について図面を参照しながら説明する。車両内では、舵角、車輪速、加速度の各センサの情報から、各車輪の駆動トルク、ブレーキ力を適切に制御することにより車両のスピンやドリフトを抑制する。したがって、振動型角速度センサ10は、車両性能を向上させる上で重要なセンサとなる。

【0032】

図1は、振動型角速度センサの電気的なブロック構成を示している。振動型角速度センサ10は、特に車両用のヨーレートセンサとして用いられるもので、振動子11、信号検出回路12、位相同期回路13、タイミング生成部13a、AGC14、角速度検出部15を接続して構成される。振動子11は、AGC14から駆動信号が与えられることにより基準方向に振動する。この振動した振動子11に角速度Ωが加わると、基準方向と直交する検出方向にコリオリ力が働く。例えば、質量mの物体が角速度ベクトルΩで回転する平面上を速度ベクトルvで移動すると、その物体に発生するコリオリ力Fcは、

Fc = 2mv×Ω(×は外積を示す) …(1)

で表される。信号検出回路12は、基準方向の振動信号を波形整形する回路を示している。振動子11には電極が構成されており、信号検出回路12は、基準方向に振動した振動子11の電極の容量変化をCV変換回路により電圧値として検出することで基準方向の振動信号(以下モニタ信号)を検出し、フィルタ、アンプなどを通じて出力する。

【0033】

デジタル位相同期回路(以下、位相同期回路と称す)13は、所謂デジタルPLL(Phase Locked Loop)回路であり、入力信号と出力信号との位相差を検出し同期した周波数信号を発振出力する。この位相同期回路13の詳細構成は後述する。タイミング生成部13aは、駆動タイミング信号、サンプリングクロック、カウントクロック等のセンサ回路の動作に要するタイミング信号を生成する。AGC(Auto Gain Control)14は、信号検出回路12の出力信号振幅を基に、振動子11の基準方向の振動が所望の振動状態で一定となるように、タイミング生成部13aの駆動タイミング信号の振幅を制御した駆動信号を振動子11に印加する。

【0034】

角速度検出部15は、振動子11に生じたコリオリ力に応じた角速度振動信号について、信号検出回路12と同等の処理で電圧値として検出し、同期検波回路、LPF(Low Pass Filter)を用いて角速度振動成分のみを抽出し、角速度情報(センサ信号)として出力する。

【0035】

振動子11には固有振動数が存在し、角速度振動信号を効率良く検出するためには、振動子11に適切な周波数の駆動信号を印加すると良く、位相同期回路13を用いて駆動信号を適切な周波数および位相に制御すると良い。

【0036】

図2は、位相同期回路の電気的構成の概略的なブロック図を示している。本実施形態では、全ての構成要素をデジタルブロックで構成した実施形態を示す。

位相同期回路13は、AD変換器16、位相補正部17、クロック生成部18、位相比較部19、加減算部としての加算器20、調整出力部としてのループフィルタ21、制御発振部としてのDCO(Digital Controlled Oscillator)22、分周部としての分周器23を接続して構成されている。この位相同期回路13は、AD変換器16によりモニタ信号をサンプリングしたサンプリング値に応じてPLL出力クロックをAGC14に出力する。

【0037】

AD変換器16は、与えられたサンプリングクロックに応じてモニタ信号をサンプルホールドし、位相補正部17およびクロック生成部18の入力デジタル値とする。位相補正部17は、サンプリング値がゼロクロスする前後のサンプリング値に応じて、ゼロクロスタイミングの位相を補正する位相補正値を出力する。この位相補正部17の具体構成例を図3に示している。

【0038】

図3に示すように、位相補正部17は、遅延器(第1遅延器に相当)24、減算器(第1減算器に相当)25、除算器(第1除算器に相当)26、乗算器(第1乗算器に相当)27、サンプルホールド回路28、および立上りゼロクロス検出回路29を組み合わせたハードウェアにより構成されている。位相補正部17は、ゼロクロス前後のAD変換器16のサンプリング値を線形近似することでゼロクロスタイミングの位相値を算出する。

【0039】

遅延器24は、AD変換器16のサンプリング値x(n)を1サンプリングクロック分遅延し、減算器25に出力する。減算器25は、AD変換器16の現サンプリング値x(n)から1サンプリングクロック分遅延した遅延サンプリング値x(n−1)を減算(すなわち、x(n)−(−|x(n−1)|))し、除算器26に出力する。

【0040】

除算器26は、現サンプリング値x(n)を減算器25で減算した結果x(n)−x(n−1)で除算し、乗算器27に出力する。乗算器27は、定数(サンプリング周期に相当するカウントクロックのカウント値を−2倍した値)に除算器26の除算値x(n)/(x(n)−x(n−1))を乗算し、サンプルホールド回路28に与える。サンプルホールド回路28は、乗算器27の乗算値を立上りゼロクロス検出回路29で検出されたタイミングでサンプルホールドする。

【0041】

図4は、位相補正部17の動作説明図を示している。図4には、例えばモニタ信号のアナログ値の最大周波数(最小周期)を8サンプリング(1桁数サンプリング)する例を示している。なお、サンプリングクロックはカウントクロックに同期するもので、サンプリングクロック周期は、カウントクロック周期の数十〜数百倍の時間に設定されている。

【0042】

ゼロクロスタイミング前後のサンプリング値を、それぞれx(n−1),x(n)とすると、これらのx(n−1)とx(n)の振幅比は、x(n−1)のAD変換タイミングからゼロクロスするまでの時間T1と、ゼロクロスタイミングからx(n)のAD変換タイミングまでの時間T2との比とほぼ同一となる。したがって、AD変換器16のサンプリング間隔にx(n)/(x(n)−x(n−1))を乗算することで時間T2に相当する時間を算出できる。

【0043】

立上りゼロクロス検出回路29は、現サンプリング値x(n)が正数で且つ遅延サンプリング値x(n−1)が負数となるタイミングにおいてサンプルホールド回路28にサンプリングパルスを出力し、サンプルホールド回路28は、このタイミングでx(n)/(x(n)−x(n−1))×定数(サンプリング周期に相当するカウントクロックのカウント数×(−2))を取得する。

【0044】

ここで、(−2)のうち「−1」は図4のサンプリングポイントAより時間を遡ることを示しており、「2」とはシステムに依存した係数値を示している。この定数は、クロック生成部18および位相比較部19のカウントクロックの位相比較カウント値のカウント方式(後述参照)に合わせて設定されている。

【0045】

さて、位相補正部17による補正方法を適用すると、サンプリングポイント間を線形近似した場合のゼロクロスタイミングを算出でき、例えば正弦波のゼロクロス付近を線形近似可能な場合に近似して求めることができる。本実施形態では、クロック生成部18、位相比較部19、および加算器20を設けることで、AD変換器16のサンプリング数が少なくても正確なゼロクロスタイミングを簡単に導出できるようにしている。以下、図2を参照しながら説明を行う。

【0046】

クロック生成部18は、モニタ信号のAD変換器16のサンプリング値の符号情報を2値化して位相比較部19に出力するもので、例えば、AD変換器16のサンプリング値が0以上の「+」のときには「H」レベル、0未満の「−」のときには「L」レベルを出力する。これにより符号クロックCLK1が生成される。図5は、AD変換器16のサンプリング値の符号情報と符号クロックCLK1の信号波形の関係を示している。この符号クロックCLK1の立上りタイミングは離散化に応じた誤差が生じている。

【0047】

正確な位相比較を行うためには、AD変換器16のサンプリング周波数をより高速にする必要がある。高速サンプリングを防ぎながら正確な位相比較を行うため、前述した位相補正部17が設けられると共に、さらに、後述の位相比較部19、加算器20が構成されている。

【0048】

図2に示すように、位相比較部19には、符号クロックCLK1と、DCO22のPLL出力クロックを分周器23にて分周した分周クロックCLK2とが与えられている。DCO22は、符号クロックCLK1をN逓倍したPLL出力クロックをN逓倍周波数信号として発振出力し、分周器23は、PLL出力クロックをN分周し分周クロックCLK2として位相比較部19に出力する。

【0049】

図6は、位相比較部19のハードウェア構成を示している。位相比較部19は、アップ/ダウン選択回路30、セレクタ31、加算器32、サンプルホールド回路33、立上りエッジ検出回路34、および、サンプルホールド回路35を備える。カウントクロックは、アップ/ダウン選択回路30、セレクタ31、サンプルホールド回路33、および、立上りエッジ検出回路34に与えられている。

【0050】

アップ/ダウン選択回路30は、符号クロックCLK1および分周クロックCLK2を入力し、カウントクロックの入力タイミングにおいて選択信号を切替出力する。このアップ/ダウン選択回路30は、カウントクロックの立上りタイミングにおいて符号クロックCLK1が立ち上がったか否かを判定し、符号クロックCLK1の立上りエッジを検出すると、セレクタ31に「−1」を選択するための選択信号を出力する。

【0051】

また、アップ/ダウン選択回路30は、カウントクロックの立上りタイミングにおいて分周クロックCLK2が立ち下がったか否かを判定し、分周クロックCLK2の立下りを検出すると、セレクタ31に「+1」を選択するための選択信号を出力する。

【0052】

セレクタ31は、選択信号に応じて「−1」または「+1」を出力し、加算器32はサンプルホールド回路33にてホールドされた出力値にセレクタ31の出力値(「−1」または「+1」)を加算して出力し、サンプルホールド回路33は、この出力値を次回のカウントクロックの立上りタイミングでサンプリングホールドする。

【0053】

したがって、アップ/ダウン選択回路30は、符号クロックCLK1の変化に応じて所定の一方向(本実施形態の場合、減少方向)にカウントする方向を変化させ、分周クロックCLK2の変化(カウント転換タイミング)にて一方向とは逆方向(本実施形態の場合、増加方向)にカウントする方向を転換させている。

【0054】

そして、加算器32およびサンプルホールド回路33は、セレクタ31の増加値(「1」)または減少値(「−1」)をカウントクロックの立上りタイミングにて加算する。すなわち、セレクタ31、加算器32およびサンプルホールド回路33は、アップダウンカウンタ36として動作するものであり、そのカウント値を位相比較カウント値としてサンプルホールド回路35に出力する。

【0055】

立上りエッジ検出回路34は、符号クロックCLK1の立上りエッジをカウントクロックの立上りタイミングにて検出し、サンプルホールド回路35のサンプルタイミングとして出力する。サンプルホールド回路35は、立上りエッジ検出回路34が検出した符号クロックCLK1の立上りエッジのタイミングにて位相比較カウント値をサンプルホールドし位相値として出力する。

【0056】

図7(a)〜図7(c)は、それぞれ、周波数および位相が同期した場合、位相遅れを生じた場合、位相進みが生じた場合の各クロックと位相比較カウント値の関係を示している。また、図8(a)〜図8(c)は、それぞれ、周波数および位相が同期した場合、分周クロックCLK2の周波数が高い場合、分周クロックCLK2の周波数が低い場合、についての各クロックと位相比較カウント値の関係を示している。

【0057】

これらの図7(a)〜図7(c)、図8(a)〜図8(c)に示すように、符号クロックCLK1が立ち上がると、アップダウンカウンタ36は、ダウンカウントを開始し、カウントクロックを受け付ける度にダウンカウントする。そして、分周クロックCLK2の立下りエッジを検出するとカウントを停止し、その後、カウントクロックを受け付ける度にアップカウントし、符号クロックCLK1が再度立ち上がると、サンプルホールド回路35が位相比較カウント値を位相値としてサンプルホールド出力し、出力がカウントクリアされる。

【0058】

したがって、図7(a)または図8(a)に示すように、符号クロックCLK1と分周クロックCLK2とが同一周波数、同一位相となるときには、位相比較カウント値が例えば0を基準出力した時点でサンプルホールド回路35がサンプルホールドし位相値として出力する。

【0059】

また、図7(b)に示すように、分周クロックCLK2の位相が符号クロックCLK1に比較して遅れた場合には、ダウンカウント数が基準出力よりも多くなり、逆にアップカウント数が基準出力より少なくなり、基準出力より少ない値(例えば負の値)を位相比較カウント値として出力した時点でサンプルホールド回路35がサンプルホールドし位相値として出力する。

【0060】

このとき、最終的に得られる位相値は、ダウンカウントの増加数にアップカウントの減少数を加えたカウント数となるため、実際の位相遅れに相当するカウントクロック数の2倍カウントされることになる。図7(b)に示す模式的な例では、分周クロックCLK2は符号クロックCLK1に「3」カウント遅れており位相値は「−6」となる。

【0061】

逆に、図7(c)に示すように、分周クロックCLK2の位相が符号クロックCLK1に比較して進む場合には、ダウンカウント数が基準出力よりも少なくなり、逆にアップカウント数が基準出力より多くなるため、位相比較カウント値として基準出力より多い値(例えば正の値)を出力した時点でサンプルホールド回路35がサンプルホールドし位相値として出力する。

【0062】

前述と同様に、最終的に得られる位相値は、ダウンカウントの減少数にアップカウントの増加数を加えたカウント数となるため、実際の位相進みに相当するカウントクロック数の2倍カウントされることになる。図7(c)に示す模式的な例では、分周クロックCLK2は符号クロックCLK1に「3」カウント進んでおり位相値は「+6」となる。

【0063】

同様に、図8(b)に示すように、分周クロックCLK2の周波数が符号クロックCLK1に比較して高い場合には、ダウンカウント数が基準出力より少なくなり、逆にアップカウント数が基準出力より多くなるため、位相値として基準出力より多い値(例えば正の値)を出力する。

【0064】

このとき、出力される位相値は、ダウンカウントの減少数にアップカウントの増加数を加えたカウント数となるため、実際の周波数偏差に相当するカウントクロック数の2倍カウントされることになる。図8(b)に示す模式的な例では、分周クロックCLK2は符号クロックCLK1の2倍の周波数となっており、カウントクロック数は「3」カウント進んでおり位相値は「+6」となる。

【0065】

さらに、図8(c)に示すように、分周クロックCLK2の周波数が符号クロックCLK1に比較して低い場合には、ダウンカウント数が基準出力より多くなり、逆にアップカウント数が基準出力より少なくなるため、位相値として負の値を出力する。

【0066】

このとき出力される位相値は、ダウンカウントの増加数にアップカウントの減少数を加えたカウント数となるため、実際の周波数偏差に相当するカウントクロック数の2倍カウントされることになる。図8(c)の例では、分周クロックCLK2は符号クロックCLK1の1/2の周波数となっており、カウントクロック数は「3」カウント遅れており位相値は「−6」となる。

【0067】

位相比較部19の位相比較カウント値がカウントクロックの2倍のカウントをしており、前述した時間T2に対応した位相補正部17による位相補正値をカウントクロックに対応づけて2倍のカウントを行っている。したがって、前述では「2」というアップダウンカウントシステムに依存した係数値を採用して構成している。

【0068】

<第1実施形態のまとめ>

位相補正部17は、AD変換器16のサンプリング値のゼロクロス前後の値を線形近似しゼロクロスタイミングの位相補正値を算出し、他方では、クロック生成部18がAD変換器16のサンプリング値の符号情報に応じて符号クロックを生成し、位相比較部19がクロック生成部18の符号クロックCLK1と分周器23の分周クロックCLK2の位相差を算出する。これにより、AD変換器16の入力サンプリング値の符号が切替わるタイミングと分周器23の分周クロックのタイミングとの位相差を検出できる。

【0069】

ループフィルタ21には、この位相比較部19の位相差を位相補正部17の位相補正値で補正した値が与えられるため、ループフィルタ21はこの出力値に応じた調整量をDCO22に出力し、DCO22はこの調整量に応じてN逓倍周波数信号を発振出力できる。

【0070】

したがって、位相比較部19、加算器20、ループフィルタ21、DCO22および分周器23によるフィードバックループは、クロック生成部18が生成した符号クロックCLK1の位相を位相補正部17の位相補正値により補正しているため、位相同期することができ、DCO22は位相同期した安定的なN逓倍周波数信号を発振出力できる。したがって、主に位相補正部17、位相比較部19を構成して位相同期を図っているため正確な位相同期を実現できる。

【0071】

アップダウンカウンタ36は、クロック生成部18の符号クロックCLK1によるカウント開始タイミングから一方向にカウントを開始し、分周器23の分周クロックCLK2によるカウント転換タイミングにて逆方向にカウントを逆転し、クロック生成部18の符号クロックCLK1によるカウント終了タイミングにて得られたカウント値を位相算出値として出力する。これにより、符号クロックCLK1と分周クロックCLK2の位相差を簡単な構成で算出できる。

【0072】

具体的には、アップダウンカウンタ36が、クロック生成部18の符号クロックCLK1の立上りタイミングからカウントクロックに応じてダウンカウントし、アップダウンカウンタ36は、ダウンカウントされてから分周器23の分周クロックCLK2による立下りタイミングを受け付けると当該立下りタイミングからカウントクロックに応じてアップカウントする。そして、位相比較部19は、クロック生成部18の符号クロックCLK1の立上りタイミングにてアップカウンタによるカウントを終了し得られたカウント値を位相算出値として出力する。これにより、符号クロックCLK1と分周クロックCLK2の位相差を簡単な構成で算出できる。

【0073】

位相補正部17の減算器(加減算器)25が遅延サンプリング値とAD変換器16の現サンプリング値とを減算すると、x(n)−x(n−1)を算出できる。そして、除算器26がAD変換器16の現サンプリング値を減算器(加減算器)25の加減算値により除算すると、x(n)/(x(n)−x(n−1))を算出できる。

【0074】

位相比較部19のアップダウンカウンタ36のダウンカウント増加分はアップカウント減少分となり、逆にダウンカウント減少分はアップカウント増加分となるため、位相比較部19で得られた位相差に相当するカウント値はカウントクロックの2倍のカウント値となる。

【0075】

したがって、乗算器27が、サンプリング周期に相当するカウンタクロックのカウント値を−2倍した値を除算器26の除算値と乗算すれば、位相比較部19と位相補正部17のカウント値のカウント値増減度をマッチさせて算出でき、位相比較部19により算出した位相算出値に位相補正部17により算出した位相補正値を加算して出力することでゼロクロスタイミングに応じた位相値を正確に出力できる。

【0076】

以上の作用により、低速サンプリングで離散化による位相誤差が発生しても正確な位相同期が可能となる。また、位相補正精度は、AD変換器16の分解能により決定されるため、適切なAD分解能に設定することでカウントクロックの高速化を最低限に抑えることができる。

【0077】

特許文献2記載の技術思想では、周波数比較器、ローパスフィルタに加えて、周波数比較器をスイッチによってオンオフ制御を行う回路を具備するため、処理が複雑となり回路サイズが大きくなってしまう。本実施形態では、周波数比較器をスイッチでオンオフする回路を設ける必要がなくなり、より簡単で小型化できる。また、高速なクロックが不要となるため、位相補正部17、位相比較部19を小型化、低消費電力化することができる。

【0078】

また、位相補正部17で算出した位相補正値をち密なタイミング操作(例えば回路のセット、リセット等)ではなく、デジタル値の加算のみで行うことができるため、回路設計が簡単になる。

【0079】

(第2実施形態)

図9は、本発明の第2実施形態を示すもので、前述実施形態と異なるところは、位相補正部の構成を変更したところにある。前述実施形態と同一部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0080】

図9は、位相補正部の変形例を示している。位相補正部37は、絶対値演算器38、遅延器(第2遅延器に相当)39、加算器(第2加算器に相当)40、除算器(第2除算器に相当)41、乗算器(第2乗算器に相当)42などを組み合わせて構成され、図示しないサンプリングホールド回路を介して位相補正値を出力する。AD変換器16によるモニタ信号のサンプリング値は、絶対値演算器38に入力される。

【0081】

絶対値演算器38はサンプリング値の絶対値を演算し、遅延器39、加算器40、除算器41に演算値を出力する。遅延器39は、絶対値演算器38の演算値を1サンプリングクロック分遅延して加算器40に出力する。加算器40は、遅延サンプリング値の絶対値|x(n−1)|と現サンプリング値の絶対値|x(n)|とを加算し除算器41に出力する。除算器41は、現サンプリング値の絶対値|x(n)|を加算器40の加算値|x(n)|+|x(n−1)|で除算し、乗算器42に出力する。乗算器42は、除算器41の除算値|x(n)|/(|x(n)|+|x(n−1)|)と定数(サンプリング周期に相当するカウントクロックのカウント値を−2倍した値)を乗算した値を位相補正値として出力する。すると、|x(n)|/(|x(n)|+|x(n−1)|)×定数(サンプリング周期に相当するカウントクロックのカウント数×(−2))を演算できる。

【0082】

この場合、クロック生成部18が出力したゼロクロスタイミング直後の符号クロックCLK1の立上りタイミング(「L」→「H」)でサンプリングして位相補正値として出力すれば、前述実施形態と同様に位相補正部17の位相補正値を適切に取得できる。

【0083】

(第3実施形態)

図10は、本発明の第3実施形態を示すもので、前述実施形態と異なるところは、位相比較部のアップダウンカウンタの構成を変更したところにある。

【0084】

図10は、第1実施形態の位相比較部19に代わる位相比較部43の電気的構成を示している。図10に示すアップダウンカウンタ44は第1実施形態のアップダウンカウンタ36に代えて構成されている。アップダウンカウンタ44は、アップ/ダウン選択回路30からアップカウント、ダウンカウントの選択信号を入力すると、アップカウンタ、ダウンカウンタの機能を切替え、入力するカウントクロックのパルスに応じてアップカウントまたはダウンカウントし、位相比較カウント値としてサンプルホールド回路35に出力する。

【0085】

このアップダウンカウンタ44は、例えばJKフリップフロップなどのフリップフロップを連結して構成されている。このように位相比較部43が構成されていたとしても前述実施形態と同様の作用効果が得られる。

【0086】

(第4実施形態)

図11は、本発明の第4実施形態を示すもので、前述実施形態と異なるところは、位相比較部のアップダウンカウンタについて、2つのアップカウンタを組み合わせて構成したところにある。前述実施形態と同一部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0087】

図11は位相比較部45の電気的構成を示している。位相比較部45は、前述実施形態のアップ/ダウン選択回路30に代わるカウンタ選択回路46を備える。また、アップダウンカウンタ36または44に代わるアップダウンカウンタ47を備える。

【0088】

カウンタ選択回路46は、符号クロックCLK1の立上りエッジを受け付けると有効/無効切替信号(イネーブル信号)として「H」レベルを出力し、分周クロックCLK2の立下りエッジを受け付けると有効/無効切替信号(イネーブル信号)として「L」レベルをアップダウンカウンタ47に出力するように構成されている。

【0089】

アップダウンカウンタ47は、2つのアップカウンタ48aおよび48bを備える。アップカウンタ48aは、加算器50aによりサンプルホールド回路51aの出力に「+1」を加算し、再度サンプルホールド回路51aに入力する。このアップカウンタ48aは、カウントクロックをクロック端子に入力し、当該カウントクロックのパルスに応じてアップカウントする。

【0090】

一方のアップカウンタ48aのサンプルホールド回路51aにはイネーブル端子ENが設けられており、このイネーブル端子ENにはカウンタ選択回路46が出力する有効/無効切替信号(イネーブル信号)が入力されている。

【0091】

他方、アップカウンタ48bは、加算器50bによりサンプルホールド回路51bの出力に「+1」を加算し、再度サンプルホールド回路51bに入力するように構成される。このアップカウンタ48bは、カウントクロックをクロック端子に入力し、当該カウントクロックのパルスに応じてアップカウントする。

【0092】

他方のアップカウンタ48bのサンプルホールド回路51bにもイネーブル端子ENが設けられており、このイネーブル端子ENにはカウンタ選択回路46が出力する有効/無効切替信号(イネーブル信号)が反転ゲート49を介して入力されている。

【0093】

すなわち、2つのアップカウンタ48aおよび48bは、カウンタ選択回路46が出力する有効/無効切替信号(イネーブル信号)に応じて何れか一方が動作する。これらのアップカウンタ48aおよび48bの出力は減算器52に与えられている。この減算器52はアップカウンタ48bの出力値からアップカウンタ48aの出力値を減算し、位相比較カウント値としてサンプルホールド回路35に出力する。サンプルホールド回路35は、立上りエッジ検出回路34の出力パルスに応じてサンプルホールドし位相値として出力する。

【0094】

したがって、2つのアップカウンタ48a、48bを切替え、それぞれアップカウンタ、ダウンカウンタとして機能させることで前述実施形態と同様の動作を実現できる。本実施形態のように、位相比較部45のアップダウンカウンタ47が2つのアップカウンタ48aおよび48bを備えて構成されていたとしても前述実施形態と同様の作用効果が得られる。

【0095】

(第5実施形態)

図12は、本発明の第5実施形態を示すもので、前述の第4実施形態と異なるところは、2つのアップカウンタを別構成したところにある。

図12は、第4実施形態の位相比較部45に代わる位相比較部53の電気的構成を示している。図12に示すアップダウンカウンタ54は第4実施形態のアップダウンカウンタ47に代えて構成されている。アップダウンカウンタ54は、反転ゲート49および減算器52と共に、2つのアップカウンタ55aおよび55bを備える。すなわち、第4実施形態のアップカウンタ48aおよびアップカウンタ48bに代えて、本実施形態では、アップカウンタ55aおよび55bを具備する。

【0096】

アップカウンタ55aおよび55bは、それぞれ例えばJKフリップフロップなどのフリップフロップを連結して構成されている。位相比較部53がこのように構成されていても前述実施形態と同様の作用効果が得られる。

【0097】

(第6実施形態)

図13(a)〜図13(c)および図14は、本発明の第6実施形態を示すもので、第1実施形態と異なるところは、位相補正部の減算器25(第1減算器に相当)および除算器26(第1除算器に相当)が演算許可/演算停止の切換可能に構成されているところにある。特に、減算器25および除算器26が、立上りゼロクロス検出回路29が検出する立上りゼロクロス検出信号の無効期間(ロウ期間)にて演算停止するところを特徴としている。前述実施形態と同一または類似部分については同一符号または類似符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0098】

図13(a)は、図3に代わる位相補正部のブロック構成を概略的に示している。この図13(a)に示すように、位相補正部17に代わる位相補正部17aは、遅延器24、減算器25、除算器26、乗算器27、サンプルホールド回路28、立上りゼロクロス検出回路29と共に、固定値設定器としてデータマスク回路56〜58を追加して組み合わせたハードウェアにより構成されている。

【0099】

前述実施形態で説明したように、位相補正部17aは、ゼロクロス前後のAD変換器16のサンプリング値を線形近似することでゼロクロスタイミングの位相値を算出するが、このゼロクロス前後のAD変換器16のサンプリング値を取得し位相値を算出する間以外の期間は演算機能が不要となるため、データマスク回路56〜58を設けることで減算器25および除算器26の演算機能を停止させている。

【0100】

データマスク回路56〜58のそれぞれの構成例を図13(b)または図13(c)に示している。データマスク回路56〜58は、図13(b)に示すようにANDゲート59によって構成しても良いし、図13(c)に示すようにNOTゲート60およびORゲート61を組み合わせて構成しても良い。

【0101】

図13(b)に示す回路例を適用したとき、立上りゼロクロス検出回路29の出力がハイのときには入力データをそのまま出力するが、立上りゼロクロス検出回路29の出力がロウであるときには、データマスク回路56〜58の出力を「ロウ」に固定(マスク)できる。

【0102】

図13(c)に示す回路例を適用したとき、立上りゼロクロス検出回路29の出力がハイのときには入力データをそのまま出力するが、立上りゼロクロス検出回路29の出力がロウであるときには、データマスク回路56〜58の出力を「ハイ」に固定(マスク)できる。

【0103】

したがって、図14のタイミングチャートに示すように、モニタ信号のサンプリング値が負から正になったときには、符号情報が負から正に切換わり、立上りゼロクロス検出回路29の出力が「ハイ」となるため、データマスク回路56〜58は、入力データをマスクすることなく、減算器25および除算器26にそれぞれ入力データを与える。

【0104】

しかし、それ以外の期間(立上りゼロクロス検出回路29の出力のロウ期間)では、データマスク回路56〜58は入力データをマスクすることになるため、データマスク回路56〜58は減算器25および除算器26にそれぞれ固定値を与える。

【0105】

減算器25および除算器26は、それぞれ複数のスイッチング素子を組み合わせて構成され、これらの演算器は多数のスイッチング素子をオンオフ切換えすることで演算処理しているが、演算処理するとスイッチング損失が増加する。

【0106】

したがって、減算器25、除算器26に固定値が与えられている間は、スイッチング素子をオンオフ切換えすることがなくなるためスイッチング損失も発生しない(図14の低消費電力期間参照)。これにより、低消費電力期間において、減算器25および除算器26が演算処理することがなくなり消費電力を低減できる。

【0107】

図14に示すように、減算器25および除算器26は、モニタ信号の一周期に一回演算処理するのみであるため消費電力を低減できる。

(第7実施形態)

図15および図16は、本発明の第7実施形態を示すもので、第1実施形態と異なるところは、位相補正部の減算器25(第1減算器に相当)および除算器26(第1除算器に相当)が演算停止対象とされており、演算許可/演算停止の切換可能に構成されているところにある。特に、減算器25および除算器26が、クロック生成部18が生成する符号クロックCLK1のロウ期間(符号情報の負期間)にて演算停止するところを特徴としている。前述実施形態と同一または類似部分については同一符号または類似符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0108】

図15は、図3に代わる位相補正部のブロック構成を概略的に示している。前述実施形態と同様に、位相補正部17aにはデータマスク回路56〜58が設けられており、これらのデータマスク回路56〜58には、クロック生成部18が生成した符号クロックCLK1がマスク信号として与えられている。

【0109】

図16のタイミングチャートに示すように、クロック生成部18が符号クロックCLK1をハイ出力している間、各データマスク回路56〜58は入力データをそのまま減算器25および除算器26に与える。しかし、クロック生成部18が符号クロックCLK1をロウ出力している間は、各データマスク回路56〜58は入力データをマスクして固定値を減算器25および除算器26に与える。したがって、減算器25および除算器26に固定値が与えられている間、前述実施形態と同様に消費電力を低減できる。

【0110】

(第8実施形態)

図17は、本発明の第8実施形態を示すもので、前述実施形態と異なるところは、第2実施形態で説明した加算器40(第2加算器に相当)および除算器41(第2除算器に相当)を演算停止対象とし、第6実施形態または第7実施形態の特徴を適用したところにある。前述実施形態と同一または類似部分については同一または類似の符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0111】

図17は、図9に代わる位相補正部のブロック構成を概略的に示している。この図17に示すように、位相補正部37に代わる位相補正部37aは、絶対値演算器38、遅延器39、加算器40、除算器41、乗算器42と共に、固定値設定器としてデータマスク回路62〜64を追加して組み合わせたハードウェアにより構成され、図示しないサンプリングホールド回路を介して位相補正値を出力する。

【0112】

データマスク回路62〜64は、それぞれ、前述実施形態で説明したデータマスク回路56〜58と同様の回路で構成されており、これらのデータマスク回路62〜64は、低消費電力制御信号に応じた入力データをマスクし、加算器40および除算器41に出力する。

【0113】

この「低消費電力制御信号」は、第6実施形態に示したように、立上りゼロクロス検出回路29の出力であっても良いし、第7実施形態に示したように、クロック生成部18の符号クロックCLK1の出力であっても良い。

【0114】

すなわち、第6実施形態で説明したように、立上りゼロクロス検出回路29の立上りゼロクロス検出信号がハイ期間のとき、データマスク回路62〜64が入力データをそのまま加算器40および除算器41に出力し、ゼロクロス検出信号がロウ期間のとき、データマスク回路62〜64が入力データをマスクして固定値を加算器40および除算器41に出力する。この場合、前述説明と同様に低消費電力化を図ることができる。

【0115】

また、第7実施形態で説明したように、クロック生成部18の符号クロックCLK1の出力がハイ期間のとき、データマスク回路62〜64が入力データをそのまま加算器40および除算器41に出力し、符号クロックCLK1の出力がロウ期間のとき、データマスク回路62〜64が入力データをマスクして固定値を加算器40および除算器41に出力する。この場合も同様に低消費電力化を図ることができる。

【0116】

(他の実施形態)

本発明は、前記した実施形態に限定されるものではなく、例えば、以下に示す変形または拡張が可能である。

振動型角速度センサ10としては、セラミック音叉型、シリコン音叉型、容量式等の何れに適用しても良い。

アップダウンカウンタ36、44、47、54は、それぞれダウンカウントしてからカウント転換タイミングにてアップカウントを開始する形態を示したが、アップカウントしてからカウント転換タイミングにてダウンカウントを開始する形態に適用しても良い。

【0117】

前述実施形態では、位相同期回路13は全ての構成要素をデジタルブロックにより構成した実施形態を示したが、一部アナログブロックで構成しても良い。例えば、ループフィルタ21をアナログローパスフィルタにしても良く、DCO22をVCO(Voltage Controlled Oscillator)としても良い。このような場合、D/A変換器、A/D変換器などを別途挿入して構成しても良い。

【0118】

第6実施形態、第7実施形態では、減算器25および除算器26が演算停止対象として構成され演算許可/演算停止の切換可能に構成された実施形態を示したが、何れか一方のみが切換えできるように構成されていても良く、また、その他の演算器(例えば乗算器27など)が演算停止機能を備えていても良い。同様に、第8実施形態では、加算器40および除算器41が演算許可/演算停止の切換可能に構成されている実施形態を示したが、何れか一方のみで切換えできるように構成されていても良く、また、その他の演算器(例えば乗算器42など)が演算停止機能を備えていても良い。

【0119】

また、特に第1実施形態において、減算器25、除算器26、乗算器27がクロックに同期してデータを保持する構成であるとき、減算器25、除算器26、乗算器27の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止するようにしても良い。

【0120】

前述実施形態の特に第2実施形態でも同様に、加算器40、除算器41、乗算器42がクロックに同期してデータを保持する構成であるとき、加算器40、除算器41、乗算器42の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止するようにしても良い。このような場合、演算器の動作クロックによって動作するトランジスタのオンオフ時スイッチング損失を低減でき、演算停止中における消費電力を低減できる。

【符号の説明】

【0121】

図面中、10は振動型角速度センサ(物理量検出センサ)、11は振動子、12は信号検出回路(信号検出部)、13は位相同期回路、13aはタイミング生成部、14はAGC、15は角速度検出部、16はAD変換器、17、37は位相補正部、18はクロック生成部、19、43、45、53は位相比較部、20は加算器(加減算部)、21はループフィルタ(調整出力部)、22はDCO(制御発振部)、23は分周器(分周部)、24は遅延器(第1遅延器)、25は減算器(第1減算器)、26は除算器(第1除算器)、27は乗算器(第1乗算器)、36、44、47、54はアップダウンカウンタ、38は絶対値演算器、39は遅延器(第2遅延器)、40は加算器(第2加算器)、41は除算器(第2除算器)、42は乗算器(第2乗算器)、48a、48b、55a、55bはアップカウンタ、56〜58、62〜64はデータマスク回路(固定値設定器)を示す。

【技術分野】

【0001】

本発明は、位相同期して所定の周波数信号を出力するデジタル位相同期回路および物理量検出センサに関する。

【背景技術】

【0002】

一般に、物理量検出センサの処理回路は、アナログ回路をデジタル回路に置き換えると、微細な半導体製造プロセスを用いて製造できるためICチップを小型化できコストを削減できる。また、入力したアナログ信号を早い段階でデジタル信号処理系に変換できればその効果はより大きい。

【0003】

特許文献1はアナログPLLを採用した技術の一例を示しており、図18は、この特許文献1の技術を適用したPLL回路のブロック構成を示している。PLL回路1は、波形整形回路2を通じて入力される入力信号に基づいて出力信号を出力するもので、電圧制御発振器(VCO)3および発振制御回路4を備えている。

【0004】

ここで、発振制御回路4は、制御電圧を生成するローパスフィルタ(LPF)5と、電圧制御発振器3の発振信号を分周して分周信号を生成する分周器(DIV)6と、入力信号と分周信号の位相差に基づいて充電信号または放電信号を出力する位相検出回路(PFD)7と、充電信号または放電信号に応じてローパスフィルタ5の制御電圧を増加または減少させるチャージポンプ(CP)8とを含んで構成されている。このようなブロック構成のアナログ回路の入力信号をAD変換し、アナログ回路をデジタル化すると、位相検出回路の位相比較結果にデジタル離散化による位相誤差が発生するため、正確な位相同期ができないという問題を生じる。この構成で位相誤差をなくすため高精度化しようとすると、サンプリング数を増やして高速サンプリングする必要がある。

【0005】

また、本願に関連したデジタル位相同期回路は特許文献2〜4にも開示されている。特許文献2記載の技術思想では、入力信号が非周期的な信号であり、非周期的に生じるゼロクロスの度に位相比較、周波数比較を行わなければならず、周波数比較器、ローパスフィルタに加えて、周波数比較器をスイッチによってオンオフ制御を行う回路を備える必要があるため、処理が複雑で回路サイズが大きい。

【0006】

また、特許文献3記載の技術思想では、デジタル位相同期回路において、時間軸離散的な時間点にのみ振幅値を有する入力信号におけるゼロクロス点を挟む2時間点の入力信号の振幅比を求めてゼロクロスを推定し、時間差に応じた位相量信号を出力している。

【0007】

しかしながら、この技術思想においても、入力信号はゼロクロス推定で位相を算出するも、比較信号はカウントのみによって位相を算出するため、高精度化のためにはカウントするクロックを高速にする必要があるとともに、ゼロクロス点を推定しカウンタのリセット信号などでち密なタイミングに反映する必要があるためタイミング設計が難しい。また、特許文献4記載の技術思想では、位相同期回路において、ゼロクロス点前後の離散入力信号を用いた数値演算処理により、サンプル点に対するゼロクロス点の位相を算出し、クロックの位相を制御している。しかしながら、簡単な構成で正確な位相同期を行うことができる構成が望まれている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2009−281888号公報

【特許文献2】特開平10−107623号公報

【特許文献3】特開昭55−115737号公報

【特許文献4】特開平06−119720号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

本発明は、上記事情に鑑みてなされたもので、その目的は、簡単な構成で正確な位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供することにある。

【課題を解決するための手段】

【0010】

請求項1記載の発明によれば、次のように作用する。位相補正部はAD変換器のサンプリング値のゼロクロス前後の値を線形近似しゼロクロスタイミングの位相補正値を算出する。他方、クロック生成部はAD変換器のサンプリング値の符号情報に応じて符号クロックを生成し、位相比較部がクロック生成部の符号クロックと分周部の分周クロックとの位相差を算出する。すると、AD変換器のサンプリング値の符号が切替わるタイミングと分周部の分周クロックのタイミングの位相差を検出できる。

【0011】

調整出力部には、この位相比較部の位相差を位相補正部の位相補正値で補正した値が与えられるため、調整出力部はこの値に応じた調整量を制御発振部の入力調整値として出力し、制御発振部はこの調整量に応じてN逓倍周波数信号を発振出力できる。

【0012】

したがって、位相比較部、加減算部、調整出力部、制御発振部および分周部によるフィードバックループは、クロック生成部が生成した符号クロックの位相を位相補正部の位相補正値により補正しているため、位相を正確に同期することができ、制御発振部は位相同期した安定的なN逓倍周波数信号を発振出力できる。主に位相補正部、位相比較部により位相同期を図っているため、正確な位相同期処理を実現できる。

【0013】

また、アップダウンカウンタがクロック生成部の符号クロックによるカウント開始タイミングから一方向にカウントを開始し、分周部の分周クロックによるカウント転換タイミングにて逆方向にカウントを逆転し、クロック生成部の符号クロックによるカウント終了タイミングにて得られたカウント値を出力し、このカウント値を位相算出値とする。これにより、符号クロックと分周クロックの位相差を簡単な構成で算出できる。

【0014】

請求項2記載の発明によれば、アップダウンカウンタが、クロック生成部の符号クロックの立上りタイミングから所定の基準クロックに応じてダウンカウントし、当該ダウンカウントされてから分周部の分周クロックによる立下りタイミングを受け付けると当該立下りタイミングから基準クロックに応じてアップカウントする。そして、位相比較部は、クロック生成部の符号クロックの立上りタイミングにてアップダウンカウンタによるアップカウントを終了し、得られたカウント値を位相算出値として出力する。これにより、符号クロックと分周クロックの位相差を簡単な構成で算出できる。

【0015】

請求項3記載の発明に示すように、アップダウンカウンタが2つの同じカウンタを組み合わせてダウンカウントおよびアップカウントすると良い。

請求項4記載の発明によれば、位相補正部の第1減算器が遅延サンプリング値x(n−1)(立上りゼロクロス時は負数)を、AD変換器の現サンプリング値x(n)(立上りゼロクロス時は正数)から減算すると、減算値x(n)−x(n−1)を算出できる。そして、第1除算器がAD変換部の現サンプリング値x(n)を第1減算器の減算値(x(n)−x(n−1))によって除算すると、x(n)/(x(n)−x(n−1))を算出できる。この値は、AD変換部のゼロクロス前後のサンプリング値の振幅比分に相当する値となり、現サンプリングタイミングおよび遅延サンプリングタイミング間の時間に対する現サンプリングタイミングからゼロクロスタイミングの時間の比に対応する。

【0016】

位相比較部のアップダウンカウンタのダウンカウント増加分はアップカウント減少分となり、逆にダウンカウント減少分はアップカウント増加分となるため、位相比較部で得られた位相差に相当するカウント値はカウントクロックの2倍のカウント値となる。

【0017】

したがって、第1乗算器が、サンプリング周期に相当するカウントクロックのカウント値を−2倍した値を第1除算器の除算値x(n)/(x(n)−x(n−1))と乗算すれば、位相比較部と位相補正部のカウント値増減度をマッチさせた位相値を算出できる。したがって、加減算部が位相比較部によって算出した位相算出値に位相補正部によって算出した位相補正値を加減算して出力することでゼロクロスタイミングに応じた位相値を正確に出力できる。

【0018】

請求項5記載の発明によれば、位相補正部の第1減算器、第1除算器、第1乗算器は、その少なくとも何れか一つが演算許可/停止の切換機能を有しているため、第1減算器、第1除算器、第1乗算器の少なくとも一つを演算停止でき、演算停止中の消費電力を低減できる。

【0019】

請求項6記載の発明によれば、固定値設定器は、演算停止対象となる演算器の入力を固定値に設定するため、例えば演算器を構成するトランジスタがオンオフしたときに生じるスイッチング損失を低減でき、演算停止中における消費電力を低減できる。

【0020】

請求項7記載の発明によれば、第1減算器、第1除算器および第1乗算器がクロックに同期してデータを保持する構成であるとき、第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止すると良い。この場合、例えばクロックによって動作するトランジスタのオンオフ時のスイッチング損失を低減でき、演算停止中における消費電力を低減できる。

【0021】

請求項8記載の発明によれば、ゼロクロス検出部はAD変換器のサンプリング値がゼロクロスしたタイミングを検出するが、ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて、位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する期間を設定する。

【0022】

請求項9記載の発明によれば、クロック生成部の符号クロックを用いて位相補正部の第

1減算器、第1除算器および第1乗算器の何れか少なくとも何れか一つの演算を停止する期間を設定する。

【0023】

請求項10記載の発明によれば、位相補正部の第2加算器が、第2遅延器の遅延サンプリング値|x(n−1)|(x(n−1)は立上りゼロクロス時に負数)と絶対値演算器の演算値|x(n)|(x(n)は立上りゼロクロス時に正数)とを加算し、第2除算器が絶対値演算器の演算値|x(n)|を第2加算器の加算値(|x(n)|+|x(n−1)|)によって除算すると|x(n)|/(|x(n)|+|x(n−1)|)を算出できる。したがって、請求項4記載の発明と同様に、第2乗算器が、サンプリング周期に相当するカウントクロックのカウント値を−2倍した値を第2除算器の除算値|x(n)|/(|x(n)|+|x(n−1)|)と乗算すれば、位相比較部と位相補正部のカウント値増減度をマッチさせた位相値を算出でき、同様にゼロクロスタイミングに応じた位相値を正確に出力できる。

【0024】

請求項11記載の発明によれば、位相補正部の第2減算器、第2除算器、第2乗算器は、その少なくとも何れか一つが演算許可/演算停止の切換機能を有しているため、第2減算器、第2除算器、第2乗算器は演算停止することができ、演算停止中の消費電力を低減できる。

【0025】

請求項12記載の発明によれば、固定値設定器は、演算停止対象となる演算器の入力を固定値に設定するため、例えば演算器を構成するトランジスタがオンオフしたときに生じるスイッチング損失を低減でき、演算停止中の消費電力を低減できる。

【0026】

請求項13記載の発明によれば、第2減算器、第2除算器および第2乗算器がクロックに同期してデータを保持する構成であるとき、第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止すると良い。この場合、例えばクロックによって動作するトランジスタのオンオフ時のスイッチング損失を低減でき、演算停止中の消費電力を低減できる。

【0027】

請求項14記載の発明によれば、ゼロクロス検出部はAD変換器のサンプリング値がゼロクロスしたタイミングを検出するが、ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて、位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する期間を設定する。

【0028】

請求項15記載の発明によれば、クロック生成部の符号クロックを用いて位相補正部の第2減算器、第2除算器および第2乗算器の何れか少なくとも何れか一つの演算を停止する期間を設定する。

【0029】

請求項16記載の発明のように、AGC、信号検出部、請求項1ないし15の何れかに記載のデジタル位相同期回路を備えた物理量検出センサに適用すると良い。

【図面の簡単な説明】

【0030】

【図1】本発明の第1実施形態における振動型角速度センサの電気的構成を示すブロック図

【図2】位相同期回路のハードウェア構成図

【図3】位相補正部のハードウェア構成図

【図4】位相補正値の説明図

【図5】符号情報と符号クロックとの対応関係を示す図

【図6】位相比較部のハードウェア構成図

【図7】位相比較部の位相比較カウント値の説明図((a)は基準出力、(b)は位相遅れ、(c)は位相進み)

【図8】位相比較部の位相比較カウント値の説明図((a)は基準出力、(b)は周波数高、(c)は周波数低)

【図9】本発明の第2実施形態を示す図3相当図

【図10】本発明の第3実施形態を示す図6相当図

【図11】本発明の第4実施形態を示す図6相当図

【図12】本発明の第5実施形態を示す図6相当図

【図13】本発明の第6実施形態を示す説明図((a)は図3相当図、(b)(c)はデータマスク回路の構成例)

【図14】動作を概略的に示すタイミングチャート

【図15】本発明の第7実施形態を示す図3相当図

【図16】動作を概略的に示すタイミングチャート

【図17】本発明の第8実施形態を示す図9相当図

【図18】従来例を示す図2相当図

【発明を実施するための形態】

【0031】

(第1実施形態)

以下、本発明の物理量検出センサを振動型角速度センサに適用した第1実施形態について図面を参照しながら説明する。車両内では、舵角、車輪速、加速度の各センサの情報から、各車輪の駆動トルク、ブレーキ力を適切に制御することにより車両のスピンやドリフトを抑制する。したがって、振動型角速度センサ10は、車両性能を向上させる上で重要なセンサとなる。

【0032】

図1は、振動型角速度センサの電気的なブロック構成を示している。振動型角速度センサ10は、特に車両用のヨーレートセンサとして用いられるもので、振動子11、信号検出回路12、位相同期回路13、タイミング生成部13a、AGC14、角速度検出部15を接続して構成される。振動子11は、AGC14から駆動信号が与えられることにより基準方向に振動する。この振動した振動子11に角速度Ωが加わると、基準方向と直交する検出方向にコリオリ力が働く。例えば、質量mの物体が角速度ベクトルΩで回転する平面上を速度ベクトルvで移動すると、その物体に発生するコリオリ力Fcは、

Fc = 2mv×Ω(×は外積を示す) …(1)

で表される。信号検出回路12は、基準方向の振動信号を波形整形する回路を示している。振動子11には電極が構成されており、信号検出回路12は、基準方向に振動した振動子11の電極の容量変化をCV変換回路により電圧値として検出することで基準方向の振動信号(以下モニタ信号)を検出し、フィルタ、アンプなどを通じて出力する。

【0033】

デジタル位相同期回路(以下、位相同期回路と称す)13は、所謂デジタルPLL(Phase Locked Loop)回路であり、入力信号と出力信号との位相差を検出し同期した周波数信号を発振出力する。この位相同期回路13の詳細構成は後述する。タイミング生成部13aは、駆動タイミング信号、サンプリングクロック、カウントクロック等のセンサ回路の動作に要するタイミング信号を生成する。AGC(Auto Gain Control)14は、信号検出回路12の出力信号振幅を基に、振動子11の基準方向の振動が所望の振動状態で一定となるように、タイミング生成部13aの駆動タイミング信号の振幅を制御した駆動信号を振動子11に印加する。

【0034】

角速度検出部15は、振動子11に生じたコリオリ力に応じた角速度振動信号について、信号検出回路12と同等の処理で電圧値として検出し、同期検波回路、LPF(Low Pass Filter)を用いて角速度振動成分のみを抽出し、角速度情報(センサ信号)として出力する。

【0035】

振動子11には固有振動数が存在し、角速度振動信号を効率良く検出するためには、振動子11に適切な周波数の駆動信号を印加すると良く、位相同期回路13を用いて駆動信号を適切な周波数および位相に制御すると良い。

【0036】

図2は、位相同期回路の電気的構成の概略的なブロック図を示している。本実施形態では、全ての構成要素をデジタルブロックで構成した実施形態を示す。

位相同期回路13は、AD変換器16、位相補正部17、クロック生成部18、位相比較部19、加減算部としての加算器20、調整出力部としてのループフィルタ21、制御発振部としてのDCO(Digital Controlled Oscillator)22、分周部としての分周器23を接続して構成されている。この位相同期回路13は、AD変換器16によりモニタ信号をサンプリングしたサンプリング値に応じてPLL出力クロックをAGC14に出力する。

【0037】

AD変換器16は、与えられたサンプリングクロックに応じてモニタ信号をサンプルホールドし、位相補正部17およびクロック生成部18の入力デジタル値とする。位相補正部17は、サンプリング値がゼロクロスする前後のサンプリング値に応じて、ゼロクロスタイミングの位相を補正する位相補正値を出力する。この位相補正部17の具体構成例を図3に示している。

【0038】

図3に示すように、位相補正部17は、遅延器(第1遅延器に相当)24、減算器(第1減算器に相当)25、除算器(第1除算器に相当)26、乗算器(第1乗算器に相当)27、サンプルホールド回路28、および立上りゼロクロス検出回路29を組み合わせたハードウェアにより構成されている。位相補正部17は、ゼロクロス前後のAD変換器16のサンプリング値を線形近似することでゼロクロスタイミングの位相値を算出する。

【0039】

遅延器24は、AD変換器16のサンプリング値x(n)を1サンプリングクロック分遅延し、減算器25に出力する。減算器25は、AD変換器16の現サンプリング値x(n)から1サンプリングクロック分遅延した遅延サンプリング値x(n−1)を減算(すなわち、x(n)−(−|x(n−1)|))し、除算器26に出力する。

【0040】

除算器26は、現サンプリング値x(n)を減算器25で減算した結果x(n)−x(n−1)で除算し、乗算器27に出力する。乗算器27は、定数(サンプリング周期に相当するカウントクロックのカウント値を−2倍した値)に除算器26の除算値x(n)/(x(n)−x(n−1))を乗算し、サンプルホールド回路28に与える。サンプルホールド回路28は、乗算器27の乗算値を立上りゼロクロス検出回路29で検出されたタイミングでサンプルホールドする。

【0041】

図4は、位相補正部17の動作説明図を示している。図4には、例えばモニタ信号のアナログ値の最大周波数(最小周期)を8サンプリング(1桁数サンプリング)する例を示している。なお、サンプリングクロックはカウントクロックに同期するもので、サンプリングクロック周期は、カウントクロック周期の数十〜数百倍の時間に設定されている。

【0042】

ゼロクロスタイミング前後のサンプリング値を、それぞれx(n−1),x(n)とすると、これらのx(n−1)とx(n)の振幅比は、x(n−1)のAD変換タイミングからゼロクロスするまでの時間T1と、ゼロクロスタイミングからx(n)のAD変換タイミングまでの時間T2との比とほぼ同一となる。したがって、AD変換器16のサンプリング間隔にx(n)/(x(n)−x(n−1))を乗算することで時間T2に相当する時間を算出できる。

【0043】

立上りゼロクロス検出回路29は、現サンプリング値x(n)が正数で且つ遅延サンプリング値x(n−1)が負数となるタイミングにおいてサンプルホールド回路28にサンプリングパルスを出力し、サンプルホールド回路28は、このタイミングでx(n)/(x(n)−x(n−1))×定数(サンプリング周期に相当するカウントクロックのカウント数×(−2))を取得する。

【0044】

ここで、(−2)のうち「−1」は図4のサンプリングポイントAより時間を遡ることを示しており、「2」とはシステムに依存した係数値を示している。この定数は、クロック生成部18および位相比較部19のカウントクロックの位相比較カウント値のカウント方式(後述参照)に合わせて設定されている。

【0045】

さて、位相補正部17による補正方法を適用すると、サンプリングポイント間を線形近似した場合のゼロクロスタイミングを算出でき、例えば正弦波のゼロクロス付近を線形近似可能な場合に近似して求めることができる。本実施形態では、クロック生成部18、位相比較部19、および加算器20を設けることで、AD変換器16のサンプリング数が少なくても正確なゼロクロスタイミングを簡単に導出できるようにしている。以下、図2を参照しながら説明を行う。

【0046】

クロック生成部18は、モニタ信号のAD変換器16のサンプリング値の符号情報を2値化して位相比較部19に出力するもので、例えば、AD変換器16のサンプリング値が0以上の「+」のときには「H」レベル、0未満の「−」のときには「L」レベルを出力する。これにより符号クロックCLK1が生成される。図5は、AD変換器16のサンプリング値の符号情報と符号クロックCLK1の信号波形の関係を示している。この符号クロックCLK1の立上りタイミングは離散化に応じた誤差が生じている。

【0047】

正確な位相比較を行うためには、AD変換器16のサンプリング周波数をより高速にする必要がある。高速サンプリングを防ぎながら正確な位相比較を行うため、前述した位相補正部17が設けられると共に、さらに、後述の位相比較部19、加算器20が構成されている。

【0048】

図2に示すように、位相比較部19には、符号クロックCLK1と、DCO22のPLL出力クロックを分周器23にて分周した分周クロックCLK2とが与えられている。DCO22は、符号クロックCLK1をN逓倍したPLL出力クロックをN逓倍周波数信号として発振出力し、分周器23は、PLL出力クロックをN分周し分周クロックCLK2として位相比較部19に出力する。

【0049】

図6は、位相比較部19のハードウェア構成を示している。位相比較部19は、アップ/ダウン選択回路30、セレクタ31、加算器32、サンプルホールド回路33、立上りエッジ検出回路34、および、サンプルホールド回路35を備える。カウントクロックは、アップ/ダウン選択回路30、セレクタ31、サンプルホールド回路33、および、立上りエッジ検出回路34に与えられている。

【0050】

アップ/ダウン選択回路30は、符号クロックCLK1および分周クロックCLK2を入力し、カウントクロックの入力タイミングにおいて選択信号を切替出力する。このアップ/ダウン選択回路30は、カウントクロックの立上りタイミングにおいて符号クロックCLK1が立ち上がったか否かを判定し、符号クロックCLK1の立上りエッジを検出すると、セレクタ31に「−1」を選択するための選択信号を出力する。

【0051】

また、アップ/ダウン選択回路30は、カウントクロックの立上りタイミングにおいて分周クロックCLK2が立ち下がったか否かを判定し、分周クロックCLK2の立下りを検出すると、セレクタ31に「+1」を選択するための選択信号を出力する。

【0052】

セレクタ31は、選択信号に応じて「−1」または「+1」を出力し、加算器32はサンプルホールド回路33にてホールドされた出力値にセレクタ31の出力値(「−1」または「+1」)を加算して出力し、サンプルホールド回路33は、この出力値を次回のカウントクロックの立上りタイミングでサンプリングホールドする。

【0053】

したがって、アップ/ダウン選択回路30は、符号クロックCLK1の変化に応じて所定の一方向(本実施形態の場合、減少方向)にカウントする方向を変化させ、分周クロックCLK2の変化(カウント転換タイミング)にて一方向とは逆方向(本実施形態の場合、増加方向)にカウントする方向を転換させている。

【0054】

そして、加算器32およびサンプルホールド回路33は、セレクタ31の増加値(「1」)または減少値(「−1」)をカウントクロックの立上りタイミングにて加算する。すなわち、セレクタ31、加算器32およびサンプルホールド回路33は、アップダウンカウンタ36として動作するものであり、そのカウント値を位相比較カウント値としてサンプルホールド回路35に出力する。

【0055】

立上りエッジ検出回路34は、符号クロックCLK1の立上りエッジをカウントクロックの立上りタイミングにて検出し、サンプルホールド回路35のサンプルタイミングとして出力する。サンプルホールド回路35は、立上りエッジ検出回路34が検出した符号クロックCLK1の立上りエッジのタイミングにて位相比較カウント値をサンプルホールドし位相値として出力する。

【0056】

図7(a)〜図7(c)は、それぞれ、周波数および位相が同期した場合、位相遅れを生じた場合、位相進みが生じた場合の各クロックと位相比較カウント値の関係を示している。また、図8(a)〜図8(c)は、それぞれ、周波数および位相が同期した場合、分周クロックCLK2の周波数が高い場合、分周クロックCLK2の周波数が低い場合、についての各クロックと位相比較カウント値の関係を示している。

【0057】

これらの図7(a)〜図7(c)、図8(a)〜図8(c)に示すように、符号クロックCLK1が立ち上がると、アップダウンカウンタ36は、ダウンカウントを開始し、カウントクロックを受け付ける度にダウンカウントする。そして、分周クロックCLK2の立下りエッジを検出するとカウントを停止し、その後、カウントクロックを受け付ける度にアップカウントし、符号クロックCLK1が再度立ち上がると、サンプルホールド回路35が位相比較カウント値を位相値としてサンプルホールド出力し、出力がカウントクリアされる。

【0058】

したがって、図7(a)または図8(a)に示すように、符号クロックCLK1と分周クロックCLK2とが同一周波数、同一位相となるときには、位相比較カウント値が例えば0を基準出力した時点でサンプルホールド回路35がサンプルホールドし位相値として出力する。

【0059】

また、図7(b)に示すように、分周クロックCLK2の位相が符号クロックCLK1に比較して遅れた場合には、ダウンカウント数が基準出力よりも多くなり、逆にアップカウント数が基準出力より少なくなり、基準出力より少ない値(例えば負の値)を位相比較カウント値として出力した時点でサンプルホールド回路35がサンプルホールドし位相値として出力する。

【0060】

このとき、最終的に得られる位相値は、ダウンカウントの増加数にアップカウントの減少数を加えたカウント数となるため、実際の位相遅れに相当するカウントクロック数の2倍カウントされることになる。図7(b)に示す模式的な例では、分周クロックCLK2は符号クロックCLK1に「3」カウント遅れており位相値は「−6」となる。

【0061】

逆に、図7(c)に示すように、分周クロックCLK2の位相が符号クロックCLK1に比較して進む場合には、ダウンカウント数が基準出力よりも少なくなり、逆にアップカウント数が基準出力より多くなるため、位相比較カウント値として基準出力より多い値(例えば正の値)を出力した時点でサンプルホールド回路35がサンプルホールドし位相値として出力する。

【0062】

前述と同様に、最終的に得られる位相値は、ダウンカウントの減少数にアップカウントの増加数を加えたカウント数となるため、実際の位相進みに相当するカウントクロック数の2倍カウントされることになる。図7(c)に示す模式的な例では、分周クロックCLK2は符号クロックCLK1に「3」カウント進んでおり位相値は「+6」となる。

【0063】

同様に、図8(b)に示すように、分周クロックCLK2の周波数が符号クロックCLK1に比較して高い場合には、ダウンカウント数が基準出力より少なくなり、逆にアップカウント数が基準出力より多くなるため、位相値として基準出力より多い値(例えば正の値)を出力する。

【0064】

このとき、出力される位相値は、ダウンカウントの減少数にアップカウントの増加数を加えたカウント数となるため、実際の周波数偏差に相当するカウントクロック数の2倍カウントされることになる。図8(b)に示す模式的な例では、分周クロックCLK2は符号クロックCLK1の2倍の周波数となっており、カウントクロック数は「3」カウント進んでおり位相値は「+6」となる。

【0065】

さらに、図8(c)に示すように、分周クロックCLK2の周波数が符号クロックCLK1に比較して低い場合には、ダウンカウント数が基準出力より多くなり、逆にアップカウント数が基準出力より少なくなるため、位相値として負の値を出力する。

【0066】

このとき出力される位相値は、ダウンカウントの増加数にアップカウントの減少数を加えたカウント数となるため、実際の周波数偏差に相当するカウントクロック数の2倍カウントされることになる。図8(c)の例では、分周クロックCLK2は符号クロックCLK1の1/2の周波数となっており、カウントクロック数は「3」カウント遅れており位相値は「−6」となる。

【0067】

位相比較部19の位相比較カウント値がカウントクロックの2倍のカウントをしており、前述した時間T2に対応した位相補正部17による位相補正値をカウントクロックに対応づけて2倍のカウントを行っている。したがって、前述では「2」というアップダウンカウントシステムに依存した係数値を採用して構成している。

【0068】

<第1実施形態のまとめ>

位相補正部17は、AD変換器16のサンプリング値のゼロクロス前後の値を線形近似しゼロクロスタイミングの位相補正値を算出し、他方では、クロック生成部18がAD変換器16のサンプリング値の符号情報に応じて符号クロックを生成し、位相比較部19がクロック生成部18の符号クロックCLK1と分周器23の分周クロックCLK2の位相差を算出する。これにより、AD変換器16の入力サンプリング値の符号が切替わるタイミングと分周器23の分周クロックのタイミングとの位相差を検出できる。

【0069】

ループフィルタ21には、この位相比較部19の位相差を位相補正部17の位相補正値で補正した値が与えられるため、ループフィルタ21はこの出力値に応じた調整量をDCO22に出力し、DCO22はこの調整量に応じてN逓倍周波数信号を発振出力できる。

【0070】

したがって、位相比較部19、加算器20、ループフィルタ21、DCO22および分周器23によるフィードバックループは、クロック生成部18が生成した符号クロックCLK1の位相を位相補正部17の位相補正値により補正しているため、位相同期することができ、DCO22は位相同期した安定的なN逓倍周波数信号を発振出力できる。したがって、主に位相補正部17、位相比較部19を構成して位相同期を図っているため正確な位相同期を実現できる。

【0071】

アップダウンカウンタ36は、クロック生成部18の符号クロックCLK1によるカウント開始タイミングから一方向にカウントを開始し、分周器23の分周クロックCLK2によるカウント転換タイミングにて逆方向にカウントを逆転し、クロック生成部18の符号クロックCLK1によるカウント終了タイミングにて得られたカウント値を位相算出値として出力する。これにより、符号クロックCLK1と分周クロックCLK2の位相差を簡単な構成で算出できる。

【0072】

具体的には、アップダウンカウンタ36が、クロック生成部18の符号クロックCLK1の立上りタイミングからカウントクロックに応じてダウンカウントし、アップダウンカウンタ36は、ダウンカウントされてから分周器23の分周クロックCLK2による立下りタイミングを受け付けると当該立下りタイミングからカウントクロックに応じてアップカウントする。そして、位相比較部19は、クロック生成部18の符号クロックCLK1の立上りタイミングにてアップカウンタによるカウントを終了し得られたカウント値を位相算出値として出力する。これにより、符号クロックCLK1と分周クロックCLK2の位相差を簡単な構成で算出できる。

【0073】

位相補正部17の減算器(加減算器)25が遅延サンプリング値とAD変換器16の現サンプリング値とを減算すると、x(n)−x(n−1)を算出できる。そして、除算器26がAD変換器16の現サンプリング値を減算器(加減算器)25の加減算値により除算すると、x(n)/(x(n)−x(n−1))を算出できる。

【0074】

位相比較部19のアップダウンカウンタ36のダウンカウント増加分はアップカウント減少分となり、逆にダウンカウント減少分はアップカウント増加分となるため、位相比較部19で得られた位相差に相当するカウント値はカウントクロックの2倍のカウント値となる。

【0075】

したがって、乗算器27が、サンプリング周期に相当するカウンタクロックのカウント値を−2倍した値を除算器26の除算値と乗算すれば、位相比較部19と位相補正部17のカウント値のカウント値増減度をマッチさせて算出でき、位相比較部19により算出した位相算出値に位相補正部17により算出した位相補正値を加算して出力することでゼロクロスタイミングに応じた位相値を正確に出力できる。

【0076】

以上の作用により、低速サンプリングで離散化による位相誤差が発生しても正確な位相同期が可能となる。また、位相補正精度は、AD変換器16の分解能により決定されるため、適切なAD分解能に設定することでカウントクロックの高速化を最低限に抑えることができる。

【0077】

特許文献2記載の技術思想では、周波数比較器、ローパスフィルタに加えて、周波数比較器をスイッチによってオンオフ制御を行う回路を具備するため、処理が複雑となり回路サイズが大きくなってしまう。本実施形態では、周波数比較器をスイッチでオンオフする回路を設ける必要がなくなり、より簡単で小型化できる。また、高速なクロックが不要となるため、位相補正部17、位相比較部19を小型化、低消費電力化することができる。

【0078】

また、位相補正部17で算出した位相補正値をち密なタイミング操作(例えば回路のセット、リセット等)ではなく、デジタル値の加算のみで行うことができるため、回路設計が簡単になる。

【0079】

(第2実施形態)

図9は、本発明の第2実施形態を示すもので、前述実施形態と異なるところは、位相補正部の構成を変更したところにある。前述実施形態と同一部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0080】

図9は、位相補正部の変形例を示している。位相補正部37は、絶対値演算器38、遅延器(第2遅延器に相当)39、加算器(第2加算器に相当)40、除算器(第2除算器に相当)41、乗算器(第2乗算器に相当)42などを組み合わせて構成され、図示しないサンプリングホールド回路を介して位相補正値を出力する。AD変換器16によるモニタ信号のサンプリング値は、絶対値演算器38に入力される。

【0081】

絶対値演算器38はサンプリング値の絶対値を演算し、遅延器39、加算器40、除算器41に演算値を出力する。遅延器39は、絶対値演算器38の演算値を1サンプリングクロック分遅延して加算器40に出力する。加算器40は、遅延サンプリング値の絶対値|x(n−1)|と現サンプリング値の絶対値|x(n)|とを加算し除算器41に出力する。除算器41は、現サンプリング値の絶対値|x(n)|を加算器40の加算値|x(n)|+|x(n−1)|で除算し、乗算器42に出力する。乗算器42は、除算器41の除算値|x(n)|/(|x(n)|+|x(n−1)|)と定数(サンプリング周期に相当するカウントクロックのカウント値を−2倍した値)を乗算した値を位相補正値として出力する。すると、|x(n)|/(|x(n)|+|x(n−1)|)×定数(サンプリング周期に相当するカウントクロックのカウント数×(−2))を演算できる。

【0082】

この場合、クロック生成部18が出力したゼロクロスタイミング直後の符号クロックCLK1の立上りタイミング(「L」→「H」)でサンプリングして位相補正値として出力すれば、前述実施形態と同様に位相補正部17の位相補正値を適切に取得できる。

【0083】

(第3実施形態)

図10は、本発明の第3実施形態を示すもので、前述実施形態と異なるところは、位相比較部のアップダウンカウンタの構成を変更したところにある。

【0084】

図10は、第1実施形態の位相比較部19に代わる位相比較部43の電気的構成を示している。図10に示すアップダウンカウンタ44は第1実施形態のアップダウンカウンタ36に代えて構成されている。アップダウンカウンタ44は、アップ/ダウン選択回路30からアップカウント、ダウンカウントの選択信号を入力すると、アップカウンタ、ダウンカウンタの機能を切替え、入力するカウントクロックのパルスに応じてアップカウントまたはダウンカウントし、位相比較カウント値としてサンプルホールド回路35に出力する。

【0085】

このアップダウンカウンタ44は、例えばJKフリップフロップなどのフリップフロップを連結して構成されている。このように位相比較部43が構成されていたとしても前述実施形態と同様の作用効果が得られる。

【0086】

(第4実施形態)

図11は、本発明の第4実施形態を示すもので、前述実施形態と異なるところは、位相比較部のアップダウンカウンタについて、2つのアップカウンタを組み合わせて構成したところにある。前述実施形態と同一部分については同一符号を付して説明を省略し、以下、異なる部分について説明する。

【0087】

図11は位相比較部45の電気的構成を示している。位相比較部45は、前述実施形態のアップ/ダウン選択回路30に代わるカウンタ選択回路46を備える。また、アップダウンカウンタ36または44に代わるアップダウンカウンタ47を備える。

【0088】

カウンタ選択回路46は、符号クロックCLK1の立上りエッジを受け付けると有効/無効切替信号(イネーブル信号)として「H」レベルを出力し、分周クロックCLK2の立下りエッジを受け付けると有効/無効切替信号(イネーブル信号)として「L」レベルをアップダウンカウンタ47に出力するように構成されている。

【0089】

アップダウンカウンタ47は、2つのアップカウンタ48aおよび48bを備える。アップカウンタ48aは、加算器50aによりサンプルホールド回路51aの出力に「+1」を加算し、再度サンプルホールド回路51aに入力する。このアップカウンタ48aは、カウントクロックをクロック端子に入力し、当該カウントクロックのパルスに応じてアップカウントする。

【0090】

一方のアップカウンタ48aのサンプルホールド回路51aにはイネーブル端子ENが設けられており、このイネーブル端子ENにはカウンタ選択回路46が出力する有効/無効切替信号(イネーブル信号)が入力されている。

【0091】

他方、アップカウンタ48bは、加算器50bによりサンプルホールド回路51bの出力に「+1」を加算し、再度サンプルホールド回路51bに入力するように構成される。このアップカウンタ48bは、カウントクロックをクロック端子に入力し、当該カウントクロックのパルスに応じてアップカウントする。

【0092】

他方のアップカウンタ48bのサンプルホールド回路51bにもイネーブル端子ENが設けられており、このイネーブル端子ENにはカウンタ選択回路46が出力する有効/無効切替信号(イネーブル信号)が反転ゲート49を介して入力されている。

【0093】

すなわち、2つのアップカウンタ48aおよび48bは、カウンタ選択回路46が出力する有効/無効切替信号(イネーブル信号)に応じて何れか一方が動作する。これらのアップカウンタ48aおよび48bの出力は減算器52に与えられている。この減算器52はアップカウンタ48bの出力値からアップカウンタ48aの出力値を減算し、位相比較カウント値としてサンプルホールド回路35に出力する。サンプルホールド回路35は、立上りエッジ検出回路34の出力パルスに応じてサンプルホールドし位相値として出力する。

【0094】

したがって、2つのアップカウンタ48a、48bを切替え、それぞれアップカウンタ、ダウンカウンタとして機能させることで前述実施形態と同様の動作を実現できる。本実施形態のように、位相比較部45のアップダウンカウンタ47が2つのアップカウンタ48aおよび48bを備えて構成されていたとしても前述実施形態と同様の作用効果が得られる。

【0095】

(第5実施形態)

図12は、本発明の第5実施形態を示すもので、前述の第4実施形態と異なるところは、2つのアップカウンタを別構成したところにある。

図12は、第4実施形態の位相比較部45に代わる位相比較部53の電気的構成を示している。図12に示すアップダウンカウンタ54は第4実施形態のアップダウンカウンタ47に代えて構成されている。アップダウンカウンタ54は、反転ゲート49および減算器52と共に、2つのアップカウンタ55aおよび55bを備える。すなわち、第4実施形態のアップカウンタ48aおよびアップカウンタ48bに代えて、本実施形態では、アップカウンタ55aおよび55bを具備する。

【0096】

アップカウンタ55aおよび55bは、それぞれ例えばJKフリップフロップなどのフリップフロップを連結して構成されている。位相比較部53がこのように構成されていても前述実施形態と同様の作用効果が得られる。

【0097】

(第6実施形態)

図13(a)〜図13(c)および図14は、本発明の第6実施形態を示すもので、第1実施形態と異なるところは、位相補正部の減算器25(第1減算器に相当)および除算器26(第1除算器に相当)が演算許可/演算停止の切換可能に構成されているところにある。特に、減算器25および除算器26が、立上りゼロクロス検出回路29が検出する立上りゼロクロス検出信号の無効期間(ロウ期間)にて演算停止するところを特徴としている。前述実施形態と同一または類似部分については同一符号または類似符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0098】

図13(a)は、図3に代わる位相補正部のブロック構成を概略的に示している。この図13(a)に示すように、位相補正部17に代わる位相補正部17aは、遅延器24、減算器25、除算器26、乗算器27、サンプルホールド回路28、立上りゼロクロス検出回路29と共に、固定値設定器としてデータマスク回路56〜58を追加して組み合わせたハードウェアにより構成されている。

【0099】

前述実施形態で説明したように、位相補正部17aは、ゼロクロス前後のAD変換器16のサンプリング値を線形近似することでゼロクロスタイミングの位相値を算出するが、このゼロクロス前後のAD変換器16のサンプリング値を取得し位相値を算出する間以外の期間は演算機能が不要となるため、データマスク回路56〜58を設けることで減算器25および除算器26の演算機能を停止させている。

【0100】

データマスク回路56〜58のそれぞれの構成例を図13(b)または図13(c)に示している。データマスク回路56〜58は、図13(b)に示すようにANDゲート59によって構成しても良いし、図13(c)に示すようにNOTゲート60およびORゲート61を組み合わせて構成しても良い。

【0101】

図13(b)に示す回路例を適用したとき、立上りゼロクロス検出回路29の出力がハイのときには入力データをそのまま出力するが、立上りゼロクロス検出回路29の出力がロウであるときには、データマスク回路56〜58の出力を「ロウ」に固定(マスク)できる。

【0102】

図13(c)に示す回路例を適用したとき、立上りゼロクロス検出回路29の出力がハイのときには入力データをそのまま出力するが、立上りゼロクロス検出回路29の出力がロウであるときには、データマスク回路56〜58の出力を「ハイ」に固定(マスク)できる。

【0103】

したがって、図14のタイミングチャートに示すように、モニタ信号のサンプリング値が負から正になったときには、符号情報が負から正に切換わり、立上りゼロクロス検出回路29の出力が「ハイ」となるため、データマスク回路56〜58は、入力データをマスクすることなく、減算器25および除算器26にそれぞれ入力データを与える。

【0104】

しかし、それ以外の期間(立上りゼロクロス検出回路29の出力のロウ期間)では、データマスク回路56〜58は入力データをマスクすることになるため、データマスク回路56〜58は減算器25および除算器26にそれぞれ固定値を与える。

【0105】

減算器25および除算器26は、それぞれ複数のスイッチング素子を組み合わせて構成され、これらの演算器は多数のスイッチング素子をオンオフ切換えすることで演算処理しているが、演算処理するとスイッチング損失が増加する。

【0106】

したがって、減算器25、除算器26に固定値が与えられている間は、スイッチング素子をオンオフ切換えすることがなくなるためスイッチング損失も発生しない(図14の低消費電力期間参照)。これにより、低消費電力期間において、減算器25および除算器26が演算処理することがなくなり消費電力を低減できる。

【0107】

図14に示すように、減算器25および除算器26は、モニタ信号の一周期に一回演算処理するのみであるため消費電力を低減できる。

(第7実施形態)

図15および図16は、本発明の第7実施形態を示すもので、第1実施形態と異なるところは、位相補正部の減算器25(第1減算器に相当)および除算器26(第1除算器に相当)が演算停止対象とされており、演算許可/演算停止の切換可能に構成されているところにある。特に、減算器25および除算器26が、クロック生成部18が生成する符号クロックCLK1のロウ期間(符号情報の負期間)にて演算停止するところを特徴としている。前述実施形態と同一または類似部分については同一符号または類似符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0108】

図15は、図3に代わる位相補正部のブロック構成を概略的に示している。前述実施形態と同様に、位相補正部17aにはデータマスク回路56〜58が設けられており、これらのデータマスク回路56〜58には、クロック生成部18が生成した符号クロックCLK1がマスク信号として与えられている。

【0109】

図16のタイミングチャートに示すように、クロック生成部18が符号クロックCLK1をハイ出力している間、各データマスク回路56〜58は入力データをそのまま減算器25および除算器26に与える。しかし、クロック生成部18が符号クロックCLK1をロウ出力している間は、各データマスク回路56〜58は入力データをマスクして固定値を減算器25および除算器26に与える。したがって、減算器25および除算器26に固定値が与えられている間、前述実施形態と同様に消費電力を低減できる。

【0110】

(第8実施形態)

図17は、本発明の第8実施形態を示すもので、前述実施形態と異なるところは、第2実施形態で説明した加算器40(第2加算器に相当)および除算器41(第2除算器に相当)を演算停止対象とし、第6実施形態または第7実施形態の特徴を適用したところにある。前述実施形態と同一または類似部分については同一または類似の符号を付して説明を省略し、以下、異なる部分について説明を行う。

【0111】

図17は、図9に代わる位相補正部のブロック構成を概略的に示している。この図17に示すように、位相補正部37に代わる位相補正部37aは、絶対値演算器38、遅延器39、加算器40、除算器41、乗算器42と共に、固定値設定器としてデータマスク回路62〜64を追加して組み合わせたハードウェアにより構成され、図示しないサンプリングホールド回路を介して位相補正値を出力する。

【0112】

データマスク回路62〜64は、それぞれ、前述実施形態で説明したデータマスク回路56〜58と同様の回路で構成されており、これらのデータマスク回路62〜64は、低消費電力制御信号に応じた入力データをマスクし、加算器40および除算器41に出力する。

【0113】

この「低消費電力制御信号」は、第6実施形態に示したように、立上りゼロクロス検出回路29の出力であっても良いし、第7実施形態に示したように、クロック生成部18の符号クロックCLK1の出力であっても良い。

【0114】

すなわち、第6実施形態で説明したように、立上りゼロクロス検出回路29の立上りゼロクロス検出信号がハイ期間のとき、データマスク回路62〜64が入力データをそのまま加算器40および除算器41に出力し、ゼロクロス検出信号がロウ期間のとき、データマスク回路62〜64が入力データをマスクして固定値を加算器40および除算器41に出力する。この場合、前述説明と同様に低消費電力化を図ることができる。

【0115】

また、第7実施形態で説明したように、クロック生成部18の符号クロックCLK1の出力がハイ期間のとき、データマスク回路62〜64が入力データをそのまま加算器40および除算器41に出力し、符号クロックCLK1の出力がロウ期間のとき、データマスク回路62〜64が入力データをマスクして固定値を加算器40および除算器41に出力する。この場合も同様に低消費電力化を図ることができる。

【0116】

(他の実施形態)

本発明は、前記した実施形態に限定されるものではなく、例えば、以下に示す変形または拡張が可能である。

振動型角速度センサ10としては、セラミック音叉型、シリコン音叉型、容量式等の何れに適用しても良い。

アップダウンカウンタ36、44、47、54は、それぞれダウンカウントしてからカウント転換タイミングにてアップカウントを開始する形態を示したが、アップカウントしてからカウント転換タイミングにてダウンカウントを開始する形態に適用しても良い。

【0117】

前述実施形態では、位相同期回路13は全ての構成要素をデジタルブロックにより構成した実施形態を示したが、一部アナログブロックで構成しても良い。例えば、ループフィルタ21をアナログローパスフィルタにしても良く、DCO22をVCO(Voltage Controlled Oscillator)としても良い。このような場合、D/A変換器、A/D変換器などを別途挿入して構成しても良い。

【0118】

第6実施形態、第7実施形態では、減算器25および除算器26が演算停止対象として構成され演算許可/演算停止の切換可能に構成された実施形態を示したが、何れか一方のみが切換えできるように構成されていても良く、また、その他の演算器(例えば乗算器27など)が演算停止機能を備えていても良い。同様に、第8実施形態では、加算器40および除算器41が演算許可/演算停止の切換可能に構成されている実施形態を示したが、何れか一方のみで切換えできるように構成されていても良く、また、その他の演算器(例えば乗算器42など)が演算停止機能を備えていても良い。

【0119】

また、特に第1実施形態において、減算器25、除算器26、乗算器27がクロックに同期してデータを保持する構成であるとき、減算器25、除算器26、乗算器27の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止するようにしても良い。

【0120】

前述実施形態の特に第2実施形態でも同様に、加算器40、除算器41、乗算器42がクロックに同期してデータを保持する構成であるとき、加算器40、除算器41、乗算器42の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止するようにしても良い。このような場合、演算器の動作クロックによって動作するトランジスタのオンオフ時スイッチング損失を低減でき、演算停止中における消費電力を低減できる。

【符号の説明】

【0121】

図面中、10は振動型角速度センサ(物理量検出センサ)、11は振動子、12は信号検出回路(信号検出部)、13は位相同期回路、13aはタイミング生成部、14はAGC、15は角速度検出部、16はAD変換器、17、37は位相補正部、18はクロック生成部、19、43、45、53は位相比較部、20は加算器(加減算部)、21はループフィルタ(調整出力部)、22はDCO(制御発振部)、23は分周器(分周部)、24は遅延器(第1遅延器)、25は減算器(第1減算器)、26は除算器(第1除算器)、27は乗算器(第1乗算器)、36、44、47、54はアップダウンカウンタ、38は絶対値演算器、39は遅延器(第2遅延器)、40は加算器(第2加算器)、41は除算器(第2除算器)、42は乗算器(第2乗算器)、48a、48b、55a、55bはアップカウンタ、56〜58、62〜64はデータマスク回路(固定値設定器)を示す。

【特許請求の範囲】

【請求項1】

入力調整値に応じて調整したN逓倍周波数信号を発振出力する制御発振部と、

前記制御発振部のN逓倍周波数信号をN分周した分周クロックを出力する分周部と、

AD変換器のサンプリング値のゼロクロス前後のデジタル値を線形近似しゼロクロスタイミングの位相補正値を算出する位相補正部と、

前記AD変換器のサンプリング値の符号情報に応じて符号クロックを生成するクロック生成部と、

前記クロック生成部の符号クロックと前記分周部の分周クロックとの位相差を算出する位相比較部と、

前記位相比較部の位相算出値に前記位相補正部の位相補正値を加減算する加減算部と、

前記加減算部の出力値に応じた調整量を前記制御発振部の入力調整値として出力する調整出力部と、を備え、

前記位相比較部は、

前記クロック生成部の符号クロックによるカウント開始タイミングから一方向にカウントクロックによるカウントを開始し、前記分周部の分周クロックによるカウント転換タイミングにて前記一方向とは逆方向にカウントクロックによるカウントを逆転し、前記クロック生成部の符号クロックによるカウント終了タイミングまでカウントするアップダウンカウンタを備え、

前記クロック生成部の符号クロックと前記分周部の分周クロックの位相差を算出するときには、前記アップダウンカウンタによってカウント終了タイミングで得られたカウント値を前記位相算出値として出力することを特徴とするデジタル位相同期回路。

【請求項2】

前記位相比較部は、

前記クロック生成部の符号クロックと前記分周部の分周クロックとの周波数および位相が互いに同一となるときのカウント値を基準出力する構成であり、

前記アップダウンカウンタは、前記クロック生成部の符号クロックの立上りタイミングから所定のカウントクロックに応じてダウンカウントし、当該ダウンカウントされてから前記分周部の分周クロックによる立下りタイミングを受け付けると当該立下りタイミングから前記カウントクロックに応じてアップカウントすることを特徴とする請求項1記載のデジタル位相同期回路。

【請求項3】

前記アップダウンカウンタは、2つの同じカウンタを組み合わせてカウントすることを特徴とする請求項1または2記載のデジタル位相同期回路。

【請求項4】

前記位相補正部は、

アナログ値をサンプリングした前記AD変換器のサンプリング値を1サンプリングクロック分遅延させる第1遅延器と、

前記第1遅延部の遅延サンプリング値を前記AD変換器の現サンプリング値から減算する第1減算器と、

前記AD変換部の現サンプリング値を前記第1減算器の減算値により除算する第1除算器と、

前記AD変換器のサンプリング周期に相当する前記カウントクロックのカウント値を−2倍した定数値を前記第1除算部の除算値と乗算する第1乗算器とを備えたことを特徴とする請求項1ないし3の何れかに記載のデジタル位相同期回路。

【請求項5】

前記位相補正部の第1減算器、第1除算器および第1乗算器は、その少なくとも何れか一つが演算許可/演算停止の切換機能を有することを特徴とする請求項4記載のデジタル位相同期回路。

【請求項6】

前記位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止するときに、演算停止対象となる演算器の入力を固定値に設定する固定値設定器を備えたことを特徴とする請求項5記載のデジタル位相同期回路。

【請求項7】

前記位相補正部の第1減算器、第1除算器および第1乗算器がクロックに同期してデータを保持する構成であるときには、

前記第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止することを特徴とする請求項5または6記載のデジタル位相同期回路。

【請求項8】

AD変換器のサンプリング値がゼロクロスしたタイミングを検出するゼロクロス検出部を備え、

前記ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて前記位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項5ないし7の何れかに記載のデジタル位相同期回路。

【請求項9】

前記クロック生成部の符号クロックを用いて前記位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項5ないし7の何れかに記載のデジタル位相同期回路。

【請求項10】

前記位相補正部は、

アナログ値をサンプリングした前記AD変換器のサンプリング値の絶対値を演算する絶対値演算器と、

前記絶対値演算器の演算値を1サンプリングクロック分遅延させる第2遅延器と、

前記第2遅延器の遅延サンプリング値と前記絶対値演算器の演算値とを加算する第2加算器と、

前記絶対値演算器の演算値を前記第2加算器の加算値により除算する第2除算器と、

前記AD変換器のサンプリング周期に相当する前記カウントクロックのカウント値を−2倍した定数値を前記第2除算部の除算値と乗算する第2乗算器とを備えたことを特徴とする請求項1ないし3の何れかに記載のデジタル位相同期回路。

【請求項11】

前記位相補正部の第2減算器、第2除算器、第2乗算器は、その少なくとも何れか一つが演算許可/演算停止の切換機能を有することを特徴とする請求項10記載のデジタル位相同期回路。

【請求項12】

前記位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止するときに、演算停止対象となる演算器の入力を固定値に設定する固定値設定器を備えたことを特徴とする請求項11記載のデジタル位相同期回路。

【請求項13】

前記位相補正部の第2減算器、第2除算器および第2乗算器がクロックに同期してデータを保持するデータ保持回路であるときには、

前記第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の入力クロックを停止することを特徴とする請求項11または12記載のデジタル位相同期回路。

【請求項14】

AD変換器のサンプリング値がゼロクロスしたタイミングを検出するゼロクロス検出部を備え、

前記ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて前記位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項11ないし13の何れかに記載のデジタル位相同期回路。

【請求項15】

前記クロック生成部の符号クロックを用いて前記位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項11ないし13の何れかに記載のデジタル位相同期回路。

【請求項16】

駆動信号が与えられることにより基準方向に振動する振動子を備え当該振動子に与えられる物理量に応じてセンサ信号を出力する角速度検出部を具備する物理量検出センサであって、

入力信号の振幅を一定となるように制御し前記振動子に駆動信号を印加するAGCと、

前記基準方向の振動信号を検出する信号検出部と、

前記信号検出部の検出信号を入力しこの入力信号を位相同期して前記駆動信号出力部の入力信号として出力する請求項1ないし15の何れかに記載のデジタル位相同期回路と、を備えたことを特徴とする物理量検出センサ。

【請求項1】

入力調整値に応じて調整したN逓倍周波数信号を発振出力する制御発振部と、

前記制御発振部のN逓倍周波数信号をN分周した分周クロックを出力する分周部と、

AD変換器のサンプリング値のゼロクロス前後のデジタル値を線形近似しゼロクロスタイミングの位相補正値を算出する位相補正部と、

前記AD変換器のサンプリング値の符号情報に応じて符号クロックを生成するクロック生成部と、

前記クロック生成部の符号クロックと前記分周部の分周クロックとの位相差を算出する位相比較部と、

前記位相比較部の位相算出値に前記位相補正部の位相補正値を加減算する加減算部と、

前記加減算部の出力値に応じた調整量を前記制御発振部の入力調整値として出力する調整出力部と、を備え、

前記位相比較部は、

前記クロック生成部の符号クロックによるカウント開始タイミングから一方向にカウントクロックによるカウントを開始し、前記分周部の分周クロックによるカウント転換タイミングにて前記一方向とは逆方向にカウントクロックによるカウントを逆転し、前記クロック生成部の符号クロックによるカウント終了タイミングまでカウントするアップダウンカウンタを備え、

前記クロック生成部の符号クロックと前記分周部の分周クロックの位相差を算出するときには、前記アップダウンカウンタによってカウント終了タイミングで得られたカウント値を前記位相算出値として出力することを特徴とするデジタル位相同期回路。

【請求項2】

前記位相比較部は、

前記クロック生成部の符号クロックと前記分周部の分周クロックとの周波数および位相が互いに同一となるときのカウント値を基準出力する構成であり、

前記アップダウンカウンタは、前記クロック生成部の符号クロックの立上りタイミングから所定のカウントクロックに応じてダウンカウントし、当該ダウンカウントされてから前記分周部の分周クロックによる立下りタイミングを受け付けると当該立下りタイミングから前記カウントクロックに応じてアップカウントすることを特徴とする請求項1記載のデジタル位相同期回路。

【請求項3】

前記アップダウンカウンタは、2つの同じカウンタを組み合わせてカウントすることを特徴とする請求項1または2記載のデジタル位相同期回路。

【請求項4】

前記位相補正部は、

アナログ値をサンプリングした前記AD変換器のサンプリング値を1サンプリングクロック分遅延させる第1遅延器と、

前記第1遅延部の遅延サンプリング値を前記AD変換器の現サンプリング値から減算する第1減算器と、

前記AD変換部の現サンプリング値を前記第1減算器の減算値により除算する第1除算器と、

前記AD変換器のサンプリング周期に相当する前記カウントクロックのカウント値を−2倍した定数値を前記第1除算部の除算値と乗算する第1乗算器とを備えたことを特徴とする請求項1ないし3の何れかに記載のデジタル位相同期回路。

【請求項5】

前記位相補正部の第1減算器、第1除算器および第1乗算器は、その少なくとも何れか一つが演算許可/演算停止の切換機能を有することを特徴とする請求項4記載のデジタル位相同期回路。

【請求項6】

前記位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止するときに、演算停止対象となる演算器の入力を固定値に設定する固定値設定器を備えたことを特徴とする請求項5記載のデジタル位相同期回路。

【請求項7】

前記位相補正部の第1減算器、第1除算器および第1乗算器がクロックに同期してデータを保持する構成であるときには、

前記第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の動作クロックを停止することを特徴とする請求項5または6記載のデジタル位相同期回路。

【請求項8】

AD変換器のサンプリング値がゼロクロスしたタイミングを検出するゼロクロス検出部を備え、

前記ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて前記位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項5ないし7の何れかに記載のデジタル位相同期回路。

【請求項9】

前記クロック生成部の符号クロックを用いて前記位相補正部の第1減算器、第1除算器および第1乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項5ないし7の何れかに記載のデジタル位相同期回路。

【請求項10】

前記位相補正部は、

アナログ値をサンプリングした前記AD変換器のサンプリング値の絶対値を演算する絶対値演算器と、

前記絶対値演算器の演算値を1サンプリングクロック分遅延させる第2遅延器と、

前記第2遅延器の遅延サンプリング値と前記絶対値演算器の演算値とを加算する第2加算器と、

前記絶対値演算器の演算値を前記第2加算器の加算値により除算する第2除算器と、

前記AD変換器のサンプリング周期に相当する前記カウントクロックのカウント値を−2倍した定数値を前記第2除算部の除算値と乗算する第2乗算器とを備えたことを特徴とする請求項1ないし3の何れかに記載のデジタル位相同期回路。

【請求項11】

前記位相補正部の第2減算器、第2除算器、第2乗算器は、その少なくとも何れか一つが演算許可/演算停止の切換機能を有することを特徴とする請求項10記載のデジタル位相同期回路。

【請求項12】

前記位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止するときに、演算停止対象となる演算器の入力を固定値に設定する固定値設定器を備えたことを特徴とする請求項11記載のデジタル位相同期回路。

【請求項13】

前記位相補正部の第2減算器、第2除算器および第2乗算器がクロックに同期してデータを保持するデータ保持回路であるときには、

前記第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する間、演算停止対象となる演算器の入力クロックを停止することを特徴とする請求項11または12記載のデジタル位相同期回路。

【請求項14】

AD変換器のサンプリング値がゼロクロスしたタイミングを検出するゼロクロス検出部を備え、

前記ゼロクロス検出部により検出されたゼロクロスタイミングの信号を用いて前記位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項11ないし13の何れかに記載のデジタル位相同期回路。

【請求項15】

前記クロック生成部の符号クロックを用いて前記位相補正部の第2減算器、第2除算器および第2乗算器の少なくとも何れか一つの演算を停止する期間を設定することを特徴とする請求項11ないし13の何れかに記載のデジタル位相同期回路。

【請求項16】

駆動信号が与えられることにより基準方向に振動する振動子を備え当該振動子に与えられる物理量に応じてセンサ信号を出力する角速度検出部を具備する物理量検出センサであって、

入力信号の振幅を一定となるように制御し前記振動子に駆動信号を印加するAGCと、

前記基準方向の振動信号を検出する信号検出部と、

前記信号検出部の検出信号を入力しこの入力信号を位相同期して前記駆動信号出力部の入力信号として出力する請求項1ないし15の何れかに記載のデジタル位相同期回路と、を備えたことを特徴とする物理量検出センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−217121(P2012−217121A)

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願番号】特願2011−182640(P2011−182640)

【出願日】平成23年8月24日(2011.8.24)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願日】平成23年8月24日(2011.8.24)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]