デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は位相周波数検出器に係り、より詳細にはデジタル位相周波数検出器、このデジタル位相周波数検出器を含むデジタル位相固定ループ及びデジタル位相周波数検出方法に関する。

【背景技術】

【0002】

位相固定ループ(phase locked loop;PLL)は固定された位相及び周波数を有する出力信号を得るために使用される。従来、アナログ回路で具現されたアナログ位相固定ループが使用されてきたが、半導体技術の発達によってトランジスタの速度が増加し、供給電圧が低下したことから、アナログ位相固定ループでは外部ノイズに敏感で精密度が落ちるという問題があった。従って、最近では外部ノイズに敏感でなく精密度が確保できるデジタル回路で具現されたデジタル位相固定ループが使用されている。デジタル位相固定ループは入力信号と出力信号の位相及び周波数差を検出するデジタル位相周波数検出器(phase frequency detector;PFD)を含み、このデジタル位相周波数検出器の性能によってデジタル位相固定ループの性能を決定することができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−154270号公報

【特許文献2】米国特許7,728,675号明細書

【特許文献3】米国特許出願公開2008/0136535号明細書

【特許文献4】米国特許7,595,699号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一目的は、小型化及び高速化に適合し、基準信号とフィードバック入力信号との間の位相及び周波数差を精密に検出できるデジタル位相周波数検出器を提供することにある。

【0005】

本発明の他の目的は、小型化及び高速化に適合し、基準信号とフィードバック入力信号の間の位相及び周波数差を精密に検出できるデジタル位相周波数検出方法を提供することにある。

本発明のまた他の目的は前記デジタル位相周波数検出器を含み、出力信号の固定時間を減少させることのできるデジタル位相固定ループを提供することにある。

【課題を解決するための手段】

【0006】

前記一目的を達成するために、本発明の一実施形態に係るデジタル位相周波数検出器は検出部、位相比較部、及びリセット部を含む。前記検出部は基準信号及びフィードバック入力信号のエッジを検出して、基準エッジ信号及びフィードバックエッジ信号を発生する。前記リセット部は前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記検出部を初期化させるリセット信号を発生する。前記位相比較部は、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生する。前記位相比較部は第1フリップフロップ、第2フリップフロップ及びラッチブロックを含む。前記第1フリップフロップは前記基準エッジ信号を受信するデータ入力端及び前記フィードバックエッジ信号を受信するクロック入力端を具備し、第1比較信号を出力する。前記第2フリップフロップは前記フィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備し、第2比較信号を出力する。前記ラッチブロックは前記第1比較信号及び前記第2比較信号をラッチして前記第1位相比較信号及び前記第2位相比較信号を発生する。

【0007】

一実施形態において、前記第1位相比較信号及び前記第2位相比較信号は互いに相補的に活性化し、前記第1位相比較信号は前記フィードバック入力信号の位相が前記基準信号の位相より遅れる場合に活性化し、前記第2位相比較信号は前記フィードバック入力信号の位相が前記基準信号の位相より進む場合に活性化することができる。

【0008】

前記第1位相比較信号は前記フィードバックエッジ信号が活性化する時点に前記基準エッジ信号の論理レベルに対応するように同期化し、前記第2位相比較信号は前記基準エッジ信号が活性化する時点での前記フィードバックエッジ信号の論理レベルに対応するように同期化できる。前記リセット信号は前記基準エッジ信号及び前記フィードバックエッジ信号が、全部活性化した場合に活性化し、前記基準エッジ信号及び前記フィードバックエッジ信号は前記リセット信号が活性化した場合に非活性化することができる。

【0009】

前記検出部は第3フリップフロップ及び第4フリップフロップを含むことができる。前記第3フリップフロップは前記基準信号の上昇エッジ及び下降エッジのうちの1つに応答して活性化し、前記リセット信号に応答して非活性化される前記基準エッジ信号を発生することができる。前記第4フリップフロップは前記フィードバック入力信号の上昇エッジ及び下降エッジのうちの1つに応答して活性化し、前記リセット信号に応答して非活性化される前記フィードバックエッジ信号を発生することができる。

【0010】

前記リセット部は少なくとも1つの論理素子を含むことができる。前記少なくとも1つの論理素子は前記基準エッジ信号、前記フィードバックエッジ信号、及び検出イネイブル信号に対して論理演算を実行して前記リセット信号を発生することができる。

【0011】

一実施形態において、前記デジタル位相周波数検出器は、同期化部をさらに含むことができる。前記同期化部は前記基準信号及び前記フィードバック入力信号のうちの1つに基づいて前記第1位相比較信号及び前記第2位相比較信号を同期化して、第1位相比較出力信号及び第2位相比較出力信号を発生することができる。

【0012】

前記同期化部は第3フリップフロップ及び第4フリップフロップを含むことができる。前記第3フリップフロップは前記基準信号及び前記フィードバック入力信号のうちの1つを受信するクロック入力端及び前記第1位相比較信号を受信するデータ入力端を具備し、前記第1位相比較出力信号を出力することができる。前記第4フリップフロップは前記基準信号及び前記フィードバック入力信号のうちの1つを受信するクロック入力端及び前記第2位相比較信号を受信するデータ入力端を具備し、前記第2位相比較出力信号を出力 することができる。

【0013】

前記一目的を達成するために、本発明の他の実施形態に係るデジタル位相周波数検出器は基準信号生成部、位相比較信号生成部及び利得調節部を含む。前記基準信号生成部は入力信号に基づいてリード基準信号、基準信号及びラグ基準信号を発生する。前記位相比較信号生成部は前記基準信号及びフィードバック入力信号に基づいて基準エッジ信号及びフィードバックエッジ信号を発生し、前記基準信号と前記フィードバック入力信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生する。前記利得調節部は前記リード基準信号、前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記基準信号と前記フィードバック入力信号の位相差が予め決まっていた位相差より大きいか否かを示す高利得信号を発生する。

【0014】

前記リード基準信号は前記基準信号と同じ波形を有し、前記基準信号より進んだ位相を有し、前記ラグ基準信号は前記基準信号と同じ波形を有し、前記基準信号より遅れた位相を有することができる。前記高利得信号は前記フィードバック入力信号の位相が前記リード基準信号の位相より進んだり、または、前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れる場合に活性化することができる。

【0015】

前記利得調節部は、リード検出部、ラグ検出部及び高利得信号生成部を含むことができる。前記リード検出部は、前記リード基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記リード基準信号の位相より進んでいるのかどうかを示すハイリード信号を発生できる。前記ラグ検出部は前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れているのかどうかを示すハイラグ信号を発生することができる。前記高利得信号生成部は前記ハイリード信号及び前記ハイラグ信号に基づいて前記高利得信号を発生できる。

【0016】

前記リード検出部はリード検出ブロック、論理演算ブロック及びリード出力ブロックを含むことができる。前記リード検出ブロックは前記リード基準信号のエッジを検出してリードエッジ信号を発生することができる。前記論理演算ブロックは前記リードエッジ信号、前記基準エッジ信号及び前記フィードバックエッジ信号に対し論理演算を実行してリード信号を発生することができる。前記リード出力ブロックは前記リードエッジ信号に基づいて前記リード信号を同期化して前記ハイリード信号を発生することができる。

【0017】

前記ラグ検出部は、ラグ検出ブロック、論理演算ブロック及びラグ出力ブロックを含むことができる。前記ラグ検出ブロックは前記ラグ基準信号のエッジを検出してラグエッジ信号を発生することができる。前記論理演算ブロックは前記ラグエッジ信号、前記基準エッジ信号及び前記フィードバックエッジ信号に対し論理演算を実行してラグ信号を発生することができる。前記ラグ出力ブロックは前記ラグエッジ信号に基づいて前記ラグ信号を同期化して前記ハイラグ信号を発生することができる。

【0018】

前記利得調節部は利得同期化部をさらに含むことができる。前記利得同期化部は前記基準信号及び前記フィードバック入力信号のうちの1つに基づいて前記高利得信号を同期化して高利得出力信号を発生することができる。

【0019】

一実施形態において、前記リード基準信号は第1〜第n(ただ、nは2以上の自然数)リード基準信号を含み、前記ラグ基準信号は第1〜第nラグ基準信号を含むことができる。前記第1〜第nリード基準信号は、nが増加するほど前記基準信号より、予め設定された値だけ進んだ位相を各々有することができる。前記第1〜第nラグ基準信号はnが増加するほど前記基準信号より前記予め設定された値だけ遅れた位相を各々有することができる。

【0020】

前記利得調節部は第1〜第nリード検出部、第1〜第nラグ検出部及び第1〜第n高利得信号生成部を含むことができる。前記第1〜第nリード検出部は、前記第1〜第nリード基準信号のうちの1つ、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号が前記第1〜第nリード基準信号のうち、対応するリード基準信号より進んだ位相を有するか否かを示す第1〜第nハイリード信号を各々発生することができる。前記第1〜第nラグ検出部は前記第1〜第nラグ基準信号のうちの1つ、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号が、前記第1〜第nラグ基準信号のうち、対応するラグ基準信号より遅れた位相を有するか否かを示す第1〜第nハイラグ信号を各々発生することができる。前記第1〜第n高利得信号生成部は前記第1〜第nハイリード 信号のうちの1つ及び対応する前記第1〜第nハイラグ信号のうちの1つに基づいて第1〜第n高利得信号を各々発生することができる。

【0021】

前記位相比較信号生成部は、前記基準信号及び前記フィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生し、前記フィードバックエッジ信号に基づいて前記基準エッジ信号を同期化して前記第1位相比較信号を発生し、前記基準エッジ信号に基づいて前記フィードバックエッジ信号を同期化して前記第2位相比較信号を発生することができる。

【0022】

前記デジタル位相周波数検出器は、利得選択部をさらに含むことができる。前記利得選択部は前記第1位相比較信号及び前記第2位相比較信号のうちの1つと前記高利得信号に基づいて、前記高利得信号が非活性化された場合に第1デジタル値を有して前記高利得信号が活性化した場合に前記第1デジタル値より大きい第2デジタル値を有する選択利得信号を発生することができる。

【0023】

前記他の目的を達成するために、本発明の一実施形態に係るデジタル位相周波数検出方法では、入力信号に基づいてリード基準信号、基準信号及びラグ基準信号を発生し、前記基準信号及びフィードバック入力信号に基づいて基準エッジ信号及びフィードバックエッジ信号を発生し、前記リード基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記リード基準信号の位相より先んじるのかどうかを示すハイリード信号を発生し、前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れているのかどうかを示すハイラグ信号を発生し、前記ハイリード信号及び前記ハイラグ信号に基づいて前記フィードバック入力信号が単位利得または、前記単位利得より大きい調整利得に基づいて補正されるのかどうかを示す高利得信号を発生する。

【0024】

前記高利得信号は前記フィードバック入力信号の位相が前記リード基準信号の位相より進んでいたり前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れている場合に活性化することができる。この場合前記デジタル位相周波数検出方法では前記高利得信号が活性化した場合に前記調整利得に対応して前記高利得信号が非活性化された場合に前記単位利得に対応する選択利得信号をさらに発生することができる。

【0025】

前記また他の目的を達成するために、本発明の一実施形態に係るデジタル位相固定ループはデジタル位相周波数検出器、デジタルループフィルタ、デジタル制御発振器及び分周器を含む。前記デジタル位相周波数検出器は基準信号及びフィードバック入力信号に基づいて前記基準信号と前記フィードバック入力信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生する。前記デジタルループフィルタは前記第1位相比較信号及び前記第2位相比較信号のうちの1つに基づいて出力信号の位相及び周波数を調節するためのデジタル制御信号を発生する。前記デジタル制御発振器は前記デジタル制御信号に対応する位相及び周波数を有する前記出力信号を発生する。前記分周器は前記出力信号を分周して前記フィードバック入力信号を発生する。前記デジタル位相周波数検出器は検出部、リセット部、第1フリップフロップ、第2フリップフロップ及びラッチ部を含む。前記検出部は前記基準信号及び前記フィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。前記リセット部は前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記検出部を初期化させるリセット信号を発生する。前記第1フリップフロップは前記基準エッジ信号を受信するデータ入力端及び前記フィードバックエッジ信号を受信するクロック入力端を具備し、第1比較信号を出力する。前記第2フリップフロップは前記フィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備し、第2比較信号を出力する。前記ラッチ部は前記第1比較信号及び前記第2比較信号をラッチして前記第1位相比較信号及び前記第2位相比較信号を発生する。

【0026】

前記また他の目的を達成するために、本発明の他の実施形態に係るデジタル位相固定ループはデジタル位相周波数検出器、デジタルループフィルタ、デジタル制御発振器及び分周器を含む。前記デジタル位相周波数検出器は入力信号に基づいてリード基準信号、基準信号及びラグ基準信号を発生し、前記基準信号及びフィードバック入力信号に基づいて基準エッジ信号及びフィードバックエッジ信号を発生し、前記基準信号と前記フィードバック入力信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生し、前記リード基準信号、前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記基準信号と前記フィードバック入力信号との位相差が予め決まった位相差より大きいのか否かを示す高利得信号を発生する。前記デジタルループフィルタは前記第1位相比較信号及び前記第2位相比較信号のうちの1つと前記高利得信号に基づいて出力信号の位相及び周波数を調節するためのデジタル制御信号を発生する。前記デジタル制御発振器は前記デジタル制御信号に対応する位相及び周波数を有する前記出力信号を発生する。前記分周器は前記出力信号を分周して前記フィードバック入力信号を発生する。

【0027】

前記出力信号の初期傾きは前記出力信号の最終傾きより大きいこともある。

【0028】

一実施形態において、前記デジタル位相固定ループは自動周波数調節器をさらに含むことができる。前記自動周波数調節器は前記基準信号及び前記フィードバック入力信号に基づいて前記出力信号の初期周波数を調節するための自動デジタル制御信号を発生することができる。

【0029】

前記一目的を達成するために、本発明のまた他の実施形態に係るデジタル位相固定ループを制御するデジタル位相周波数検出器は、位相比較信号生成部、利得調節部及び利得選択部を含む。前記位相比較信号生成部は前記デジタル位相固定ループの基準信号及びフィードバック信号に応答して、前記基準信号と前記フィードバック信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生する。前記利得調節部はリード基準信号及びラグ基準信号に応答して、前記基準信号と前記フィードバック入力信号との位相差が予め決まった位相差より大きいのか否かを示す高利得信号を発生する。前記利得選択部は前記第1位相比較信号及び前記第2位相比較信号のうちの1つと前記高利得信号に基づいて、選択利得信号を発生する。前記選択利得信号は前記高利得信号が非活性化された場合に第1デジタル値を有し、前記高利得信号が活性化した場合に前記第1デジタル値より大きい第2デジタル値を有する。前記第1デジタル値及び前記第2デジタル値により、前記デジタル位相固定ループの出力信号及び前記フィードバック信号の位相調節と周波数調節を制御する。

【発明の効果】

【0030】

前記のような本発明の実施形態に係るデジタル位相周波数検出器は、フィードバックエッジ信号に基づいて基準エッジ信号を同期化して第1位相比較信号を発生し、基準エッジ信号に基づいてフィードバックエッジ信号を同期化して第2位相比較信号を発生することによって、小型化及び高速化に適合し、基準信号とフィードバック入力信号との間の位相及び周波数差を精密に検出することができる。また、基準信号とフィードバック入力信号の位相差が予め決まった位相差より大きいのか否かを示す高利得信号をさらに発生することによって、前記デジタル位相周波数検出器を含むデジタル位相固定ループのフィードバック利得を効率的に調節することができる。

【0031】

また、本発明の実施形態に係るデジタル位相周波数検出器を含むデジタル位相固定ループは構造が簡単で、向上した動作速度を有して、出力信号を効果的に固定させることができる。特にジッタまたは、位相ノイズには影響を及ぼさずに出力信号の固定時間のみを減少させることができる。

【図面の簡単な説明】

【0032】

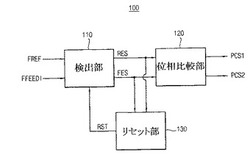

【図1】本発明の一実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図2】図1のデジタル位相周波数検出器に含まれる位相比較部の一例を示すブロック図。

【図3】図1のデジタル位相周波数検出器に含まれる検出部の一例を示すブロック図。

【図4】図1のデジタル位相周波数検出器に含まれるリセット部の一例を示すブロック図。

【図5】図1のデジタル位相周波数検出器の動作を示すタイミング図。

【図6】図1のデジタル位相周波数検出器の動作を示すタイミング図。

【図7】本発明の他の実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図8】図7のデジタル位相周波数検出器に含まれる同期化部の一例を示すブロック図。

【図9】本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャート。

【図10】本発明のまた他の実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図11】図10のデジタル位相周波数検出器から発生する基準信号の一例を示す図。

【図12】図10のデジタル位相周波数検出器に含まれる基準信号生成部の一例を示すブロック図。

【図13】図10のデジタル位相周波数検出器に含まれる利得調節部の一例を示すブロック図。

【図14】図13の利得調節部の具体的な例を示すブロック図。

【図15】図10のデジタル位相周波数検出器の動作を示すタイミング図。

【図16】図10のデジタル位相周波数検出器の動作を示すタイミング図。

【図17】図10のデジタル位相周波数検出器に含まれる利得調節部の他の例を示すブロック図。

【図18】図17の利得調節部に含まれる利得同期化部の一例を示すブロック図。

【図19】図10のデジタル位相周波数検出器から発生する基準信号の他の例を示す図面。

【図20】図10のデジタル位相周波数検出器に含まれる基準信号生成部の他の例を示すブロック図。

【図21】図10のデジタル位相周波数検出器に含まれる利得調節部のまた他の例を示すブロック図。

【図22】本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャート。

【図23】本発明のまた他の実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図24】図23のデジタル位相周波数検出器に含まれる利得選択部の一例を示すブロック図。

【図25】本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャート。

【図26】本発明の一実施形態に係るデジタル位相固定ループを示すブロック図。

【図27】本発明の一実施形態に係るデジタル位相固定方法を示すフローチャート。

【図28】本発明の他の実施形態に係るデジタル位相固定ループを示すブロック図。

【図29】本発明の他の実施形態に係るデジタル位相固定方法を示すフローチャート。

【図30】本発明のまた他の実施形態に係るデジタル位相固定ループを示すブロック図。

【図31】本発明の実施形態に係るデジタル位相固定ループの動作を示すグラフ。

【図32】本発明の実施形態に係るデジタル位相固定ループを含む集積回路を示すブロック図。

【図33】本発明の実施形態に係るデジタル位相固定ループを含む送信機を示すブロック図。

【図34】本発明の実施形態に係るデジタル位相固定ループを含むメモリ装置を示すブロック図。

【図35】図34のメモリ装置を含むシステムを示すブロック図。

【発明を実施するための最良の形態】

【0033】

本明細書に開示されている本発明の実施形態に対して、特定の構造的ないし機能的説明は、単に本発明の実施形態を説明するための目的で例示されたものであり、本発明の実施形態は多様な形態で実施することができ、本明細書に説明された実施形態に限定されるものではない。

【0034】

本発明は多様な変更を加えることができ、種々の形態を有することができるが、特定の実施形態を図面に例示して本明細書に詳細に説明する。しかし、これは本発明を特定の開示形態に限定しようとするものではなく、本発明の思想及び技術範囲に含まれるすべての変更、均等物ないし代替物を含むと理解すべきである。

【0035】

本明細書において、第1、第2等の用語は多様な構成要素を説明するのに使用することができるが、これらの構成要素がこのような用語によって限定されてはならない。これらの用語は一つの構成要素を他の構成要素から区別する目的で使われる。例えば、本発明の権利範囲から逸脱せずに第1構成要素は第2構成要素と命名することができ、同様に第2構成要素も第1構成要素と命名することができる。

【0036】

ある構成要素が他の構成要素に「連結されて」いる、または「接続されて」いると言及されている場合には、その他の構成要素に直接的に連結されていたり、接続されていることも意味するが、中間に他の構成要素が存在する場合も含むと理解すべきである。一方、ある構成要素が他の構成要素に「直接連結されて」いる、または「直接接続されて」いると言及されている場合には、中間に他の構成要素が存在しないと理解すべきである。構成要素の間の関係を説明する他の表現、すなわち「〜間に」と「すぐに〜間に」または「〜に隣接する」と「〜に直接隣接する」等も同様に解釈すべきである。

【0037】

本明細書で使用した用語は単に特定の実施形態を説明するために使用したもので、本発明を限定するものではない。単数の表現は文脈上明白に異ならない限り、複数の表現をも含む。本明細書で、「含む」または「有する」等の用語は明細書上に記載された特徴、数字、段階、動作、構成要素、部品または、これを組み合わせたものが存在するということを示すものであって、一つまたはそれ以上の他の特徴や数字、段階、動作、構成要素、部品または、これを組み合わせたものなどの存在または、付加の可能性を、予め排除するわけではない。

【0038】

また、別に定義しない限り、技術的或いは科学的用語を含み、本明細書中において使用される全ての用語は本発明が属する技術分野で通常の知識を有する者であれば、一般的に理解するのと同一の意味を有する。一般的に使用される辞書において定義する用語と同じ用語は関連技術の文脈上に有する意味と一致する意味を有するものと理解すべきで、本明細書において明白に定義しない限り、理想的或いは形式的な意味として解釈してはならない。

【0039】

一方、ある実施形態が別に実現可能な場合に特定ブロック内に明記された機能または、動作がフローチャートに明記された順序と違う場合もある。例えば、連続する2つのブロックが実際には実質的に同時に実行する事もでき、関連した機能または、動作によっては前記ブロックが逆に遂行されることも可能である。

【0040】

以下、添付図面を参照して、本発明の望ましい実施形態をより詳細に説明する。図面上の同一構成要素に対しては同一参照符号を使用し、同一構成要素に対しての重複した説明は省略する。

【0041】

図1は本発明の一実施形態に係るデジタル位相周波数検出器(phase frequency detector;PFD)を示すブロック図である。

図1を参照すれば、デジタル位相周波数検出器100は検出部110、位相比較部120及びリセット部130を含む。

【0042】

デジタル位相周波数検出器100はデジタル位相固定ループ(phase locked loop;PLL)内に含まれ、デジタル位相固定ループの入力信号と出力信号との位相及び周波数差を検出することによって、デジタル位相固定ループが出力信号の位相及び周波数を調節し、固定された位相及び周波数を有する出力信号を発生するようにする。

【0043】

検出部110は基準信号FREF及びフィードバック入力信号FFEEDIのエッジを検出して基準エッジ信号RES及びフィードバックエッジ信号FESを発生する。即ち、検出部110は基準信号FREFのエッジを検出して基準エッジ信号RESを発生し、フィードバック入力信号FFEEDIのエッジを検出してフィードバックエッジ信号FESを発生する。

【0044】

基準信号FREFはデジタル位相固定ループの入力信号に対応し、フィードバック入力信号FFEEDIはデジタル位相固定ループの出力信号に対応することができる。例えば、基準信号FREFはデジタル位相固定ループの入力信号と実質的に同一であるか、または、デジタル位相固定ループの入力信号を遅延して発生させることができる。フィードバック入力信号FFEEDIはデジタル位相固定ループの出力信号と実質的に同一であるか、または、デジタル位相固定ループの出力信号を分周して発生させることができる。基準信号FREFはクリスタル(crystal)等を利用して生成され、固定された周波数を有するので、基準信号FREFの周波数はフィードバック入力信号FFEEDIの周波数に対する基準周波数として使用される。

【0045】

一実施形態において、基準エッジ信号RESは基準信号FREFの上昇エッジ及び下降エッジのうちの1つに応答して活性化し、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIの上昇エッジ及び下降エッジのうちの1つに応答して活性化できる。例えば、基準エッジ信号RESが基準信号FREFの上昇エッジに応答して活性化する場合に、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIの上昇エッジに応答して活性化できる。また、基準エッジ信号RES及びフィードバックエッジ信号FESはリセット信号RSTに応答して非活性化できる。

【0046】

ここで、「活性化」とは各信号が第1論理レベルから第2論理レベルに遷移されることを示し、「非活性化」とは各信号が第2論理レベルから第1論理レベルに遷移されることを示す。例えば、第1論理レベルは論理ローレベルで第2論理レベルは論理ハイレベルとすることができる。

【0047】

位相比較部120は基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する。例えば、位相比較部120はフィードバックエッジ信号FESに基づいて基準エッジ信号RESを同期化して第1位相比較信号PCS1を発生し、基準エッジ信号RESに基づいてフィードバックエッジ信号FESを同期化して第2位相比較信号PCS2を発生することができる。第1位相比較信号PCS1及び第2位相比較信号PCS2は基準信号FREFとフィードバック入力信号FFEEDIとの位相及び周波数の差を示すことができる。例えば、第1位相比較信号PCS1はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れるのか(lag)の有無を示し、第2位相比較信号PCS2はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進むのか(lead)の有無を示すことができる。

【0048】

第1位相比較信号PCS1及び第2位相比較信号PCS2は互いに相補的に活性化できる。即ち、第1位相比較信号PCS1及び第2位相比較信号PCS2は互いに相補的な論理レベルを有することができる。例えば、第1位相比較信号PCS1はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れる場合に活性化し、第2位相比較信号PCS2はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進んでいる場合に活性化することができる。本発明の一実施形態に係るデジタル位相周波数検出器100は基準信号FREFとフィードバック入力信号FFEEDIとの位相及び周波数差を検出してバイナリコード(binary code)で出力するバンバン(Bang-Bang)デジタル位相周波数検出器の形態で具現できる。

【0049】

図2は図1のデジタル位相周波数検出器に含まれる位相比較部の一例を示すブロック図である。

図2を参照すれば、位相比較部120は第1フリップフロップ122、第2フリップフロップ124及びラッチブロック126を含む。

【0050】

第1フリップフロップ122は基準エッジ信号RESを受信するデータ入力端及びフィードバックエッジ信号FESを受信するクロック入力端を具備し、第1比較信号CS1を出力する。第1比較信号CS1はフィードバックエッジ信号FESが活性化する時点に基準エッジ信号RESの論理レベルに対応するように同期化できる。即ち、第1フリップフロップ122はフィードバックエッジ信号FESが活性化する時点で基準エッジ信号RESの論理レベルをサンプリングして第1比較信号CS1の論理レベルを決定できる。

【0051】

第2フリップフロップ124はフィードバックエッジ信号FESを受信するデータ入力端及び基準エッジ信号RESを受信するクロック入力端を具備し、第2比較信号CS2を出力する。第2比較信号CS2は基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルに対応するように同期化できる。即ち、第2フリップフロップ124は基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルをサンプリングして第2比較信号CS2の論理レベルを決定できる。

【0052】

第1フリップフロップ122及び第2フリップフロップ124のリセット入力端は検出イネーブル信号PDENを受信することができる。検出イネーブル信号PDENはデジタル位相周波数検出器100が位相及び周波数検出動作を遂行する間は活性化し、位相及び周波数検出動作が終了してデジタル位相固定ループの出力信号の位相及び周波数が固定(lock)された場合に非活性化することができる。

【0053】

ラッチブロック126は第1比較信号CS1及び第2比較信号CS2をラッチして、互いに相補的な論理レベルを有する第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する。ラッチブロック126はSRラッチの形態で具現でき、第1NANDゲート126a及び第2NANDゲート126bを含むことができる。第1NANDゲート126aは第1比較信号CS1の反転信号及び第2位相比較信号PCS2に対して、NAND演算を実行して、第1位相比較信号PCS1を発生させる。第2NANDゲート126bは第2比較信号CS2の反転信号及び第1位相比較信号PCS1に対しNAND演算を実行して第2位相比較信号PCS2を発生させる。

【0054】

一実施形態において、第1比較信号CS1及び第2比較信号CS2のうちの1つのみを活性化した場合に、第1位相比較信号PCS1及び第2位相比較信号PCS2は、第1比較信号CS1及び第2比較信号CS2に各々対応する論理レベルを有することができる。即ち、第1位相比較信号PCS1及び第2位相比較信号PCS2各々は、第1比較信号CS1及び第2比較信号CS2と実質的に同一とすることができ、第1位相比較信号PCS1はフィードバックエッジ信号FESが活性化する時点で基準エッジ信号RESの論理レベルに対応するように同期化され、第2位相比較信号PCS2は基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルに対応するように同期化できる。言い換えれば、位相比較部120はフィードバックエッジ信号FESが活性化する時点で基準エッジ信号RESの論理レベルをサンプリングして第1位相比較信号PCS1の論理レベルを決定し、基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルをサンプリングして第2位相比較信号PCS2の論理レベルを決定できる。

【0055】

他の実施形態で、第1比較信号CS1及び第2比較信号CS2が全部非活性化された場合に、第1位相比較信号PCS1及び第2位相比較信号PCS2は、以前周期の第1位相比較信号PCS1及び第2位相比較信号PCS2に各々対応する論理レベルを有することができる。

【0056】

再び、図1を参照すれば、リセット部130は基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて検出部110を初期化させるリセット信号RSTを発生する。一実施形態において、リセット信号RSTは、基準エッジ信号RES及びフィードバックエッジ信号FESが全部活性化した場合に活性化できる。この場合、リセット信号RSTは一定の遅延時間が経過した以後に活性化することができる。即ち、リセット部130は非同期的(asynchronous)で動作することができる。リセット信号RSTが活性化した場合に、検出部110は基準信号FREF及びフィードバック入力信号FFEEDIの次の周期のエッジを検出できるように基準エッジ信号RES及びフィードバックエッジ信号FESを非活性化させることができる。このようなリセット部130の非同期的な動作を介して、デジタル位相周波数検出器100は位相検出動作時に実質的に無限の動作範囲(infinite dynamic range)を有することができ、同時に周波数検出動作も実行できる。

【0057】

上述した通り、本発明の一実施形態に係るデジタル位相周波数検出器100はデータ入力端とクロック入力端に基準エッジ信号RES及びフィードバック入力信号FESが互いに変わって入力される第1フリップフロップ122及び第2フリップフロップ124を具備する位相比較部120を含んで具現される。即ち、本発明の一実施形態に係るデジタル位相周波数検出器100は、フィードバックエッジ信号FESに基づいて基準エッジ信号RESを同期化して第1位相比較信号PCS1を発生し、基準エッジ信号RESに基づいてフィードバックエッジ信号FESを同期化して第2位相比較信号PCS2を発生することによって、簡単な構造で具現でき、向上した動作速度を有し、基準信号FREFとフィードバック入力信号FFEEDIとの間の位相及び周波数差を精密に検出することができる。

【0058】

一方、基準信号の位相とフィードバック入力信号の位相とが非常に近接した場合に、従来のデジタル位相周波数検出器は基準信号とフィードバック入力信号との位相差を検出できないこともある。即ち、従来のデジタル位相周波数検出器で、第1位相比較信号PCS1及び第2位相比較信号PCS2が全部非活性化される準安定状態(metastable state)が発生する。本発明の一実施形態に係るデジタル位相周波数検出器100は、ラッチブロック126を具備する位相比較部120を含み、基準信号FREFの位相とフィードバック入力信号FFEEDIの位相とが非常に近接した場合にも互いに相補的な論理レベルを各々有する第1位相比較信号PCS1及び第2位相比較信号PCS2を発生することによって、位相及び周波数検出動作の正確度及び安定度を向上させることができる。

【0059】

図3は図1のデジタル位相周波数検出器に含まれる検出部の一例を示すブロック図である。

図3を参照すれば、検出部110は第3フリップフロップ112及び第4フリップフロップ114を含むことができる。

【0060】

第3フリップフロップ112は基準信号FREFの上昇エッジ及び下降エッジのうちの1つに応答して活性化し、リセット信号RSTに応答して非活性化される基準エッジ信号RESを発生することができる。第4フリップフロップ114はフィードバック入力信号FFEEDIの上昇エッジ及び下降エッジのうちの1つに応答して活性化し、リセット信号RSTに応答して非活性化されるフィードバックエッジ信号FESを発生することができる。第3フリップフロップ112及び第4フリップフロップ114は、Dフリップフロップであることができる。

【0061】

一実施形態において、第3フリップフロップ112及び第4フリップフロップ114のデータ入力端は論理ハイレベルを有するように電源電圧と各々接続することができる。他の実施形態において、第3フリップフロップ112及び第4フリップフロップ114のデータ入力端は論理ローレベルを有するように接地電圧と各々接続することができる。図示はしていないが、第3フリップフロップ112及び第4フリップフロップ114のデータ入力端が接地電圧と接続する場合に、第3フリップフロップ112及び第4フリップフロップ114のデータ出力端にはインバータを各々接続することができる。

【0062】

第3フリップフロップ112及び第4フリップフロップ114のクロック入力端は、基準信号FREF及びフィードバック入力信号FFEEDIを各々受信することができる。第3フリップフロップ112及び第4フリップフロップ114のリセット入力端は、リセット信号RSTを各々受信することができる。第3フリップフロップ112及び第4フリップフロップ114の出力端は、基準エッジ信号RES及びフィードバックエッジ信号FESを各々出力することができる。一方、図示はしていないが、第3フリップフロップ112及び第4フリップフロップ114は、さらに基準エッジ信号RESの反転信号及びフィードバックエッジ信号FESの反転信号を各々出力する反転出力端を含むことができる。

【0063】

図4は図1のデジタル位相周波数検出器に含まれるリセット部の一例を示すブロック図である。

図4を参照すれば、リセット部130は少なくとも1つの論理素子を含むことができ、この少なくとも1つの論理素子はNANDゲート132、136及びインバータ134a、134b、138を含むことができる。

【0064】

少なくとも1つの論理素子132、134a、134b、136、138は、基準エッジ信号RES、フィードバックエッジ信号FES、及び検出イネイブル信号PDENに対して論理演算を実行して、リセット信号RSTを発生することができる。第1NANDゲート132は基準エッジ信号RES及びフィードバックエッジ信号FESに対しNAND演算を実行できる。第1インバータ134a及び第2インバータ134bは、入力と出力が相互接続され、第1NANDゲート132の出力信号を演算して内部信号ISを出力することができる。第2NANDゲート136は内部信号IS及び検出イネイブル信号PDENに対して、NAND演算を実行できる。第3インバータ138は第2NANDゲート138の出力信号を反転してリセット信号RSTを出力できる。

【0065】

図5及び図6は図1のデジタル位相周波数検出器の動作を示すタイミング図である。

図5はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れる場合のデジタル位相周波数検出器100の動作を示し、図6はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進む場合のデジタル位相周波数検出器100の動作を示す。図5及び図6において、デジタル位相周波数検出器100は信号FREF、FFEEDI、RES、FES、RSTの上昇エッジに応答して動作し、信号RES、FES、RST、PCS1、PCS2は、論理ローレベルから論理ハイレベルに遷移することによって活性化されることが図示される。一方、第1比較信号CS1及び第2比較信号CS2は、第1位相比較信号PCS1及び第2位相比較信号PCS2と各々実質的に同じ論理レベルを有するので詳細な説明は省略する。

【0066】

以下においては、図5及び図6を参照して本発明の一実施形態に係るデジタル位相周波数検出器100の動作を詳細に説明する。

【0067】

図1及び図5を参照すれば、時刻t1で、基準信号FREFの論理レベルが論理ローレベルから論理ハイレベルに遷移する。検出部110は基準信号FREFの上昇エッジに応答して基準エッジ信号RESを活性化させる。時間t2で、フィードバック入力信号FFEEDIの論理レベルが論理ローレベルから論理ハイレベルに遷移する。検出部110はフィードバック入力信号FFEEDIの上昇エッジに応答してフィードバックエッジ信号FESを活性化させる。

【0068】

時刻t1で、位相比較部120は基準エッジ信号RESの上昇エッジに応答してフィードバックエッジ信号FESの論理レベルに対応するように第2位相比較信号PCS2の論理レベルを決定する。フィードバックエッジ信号FESの論理レベルは論理ローレベルであるので、第2位相比較信号PCS2は論理ローレベルを維持する。時刻t2で、位相比較部120はフィードバックエッジ信号FESの上昇エッジに応答して基準エッジ信号RESの論理レベルに対応するように第1位相比較信号PCS1の論理レベルを決定する。基準エッジ信号RESの論理レベルは論理ハイレベルであるので、第1位相比較信号PCS1は論理ローレベルから論理ハイレベルに遷移する。即ち、第1位相比較信号PCS1は論理ハイレベルを有し、第2位相比較信号PCS2は論理ローレベルを有することによって、フィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れることになる。

【0069】

一方、リセット部130は基準エッジ信号RES及びフィードバックエッジ信号FESに応答して非同期的にリセット信号RSTを活性化させる。即ち、リセット部130は基準エッジ信号RES及びフィードバックエッジ信号FESが全部活性化した時刻t2から一定の遅延時間が経過した時刻t3で、リセット信号RSTを活性化させる。リセット信号RSTが活性化することによって、検出部110は基準エッジ信号RES及びフィードバックエッジ信号FESを非活性化させる。基準エッジ信号RES及びフィードバックエッジ信号FESが非活性化された時刻t3から一定の遅延時間が経過した時刻t4で、リセット部130はリセット信号RSTを非活性化させる。

【0070】

図1及び図6を参照すれば、時刻t5で、フィードバック入力信号FFEEDIの論理レベルが論理ローレベルから論理ハイレベルに遷移し、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIの上昇エッジに応答して活性化する。時刻t6で、基準信号FREFの論理レベルが論理ローレベルから論理ハイレベルに遷移し、基準エッジ信号RESは基準信号FREFの上昇エッジに応答して活性化する。

【0071】

時刻t5で、フィードバックエッジ信号FESの上昇エッジに応答して基準エッジ信号RESの論理レベルに対応するように第1位相比較信号PCS1の論理レベルが決定される。基準エッジ信号RESの論理レベルは、論理ローレベルであるので、第1位相比較信号PCS1は論理ローレベルを維持する。時刻t6で、基準エッジ信号RESの上昇エッジに応答してフィードバックエッジ信号FESの論理レベルに対応するように第2位相比較信号PCS2の論理レベルが決定される。フィードバックエッジ信号FESの論理レベルは論理ハイレベルであるので、第2位相比較信号PCS2は論理ローレベルから論理ハイレベルに遷移する。即ち、第2位相比較信号PCS2は論理ハイレベルを有し、第1位相比較信号PCS1は論理ローレベルを有することによって、フィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進むことになる。

【0072】

一方、基準エッジ信号RES及びフィードバックエッジ信号FESが全部活性化した時刻t6から一定の遅延時間が経過した時刻t7で、リセット信号RSTが活性化する。リセット信号RSTが活性化することによって、基準エッジ信号RES及びフィードバックエッジ信号FESが非活性化される。基準エッジ信号RES及びフィードバックエッジ信号FESが非活性化された時刻t7から一定の遅延時間が経過した時刻t8で、リセット信号RSTが非活性化される。

【0073】

図7は本発明の他の実施形態に係るデジタル位相周波数検出器を示すブロック図である。

図7を参照すれば、デジタル位相周波数検出器200は検出部210、位相比較部220及びリセット部230を含み、同期化部240をさらに含むことができる。

【0074】

同期化部240をさらに含むことを除けば、図7のデジタル位相周波数検出器200は図1のデジタル位相周波数検出器100と実質的に同じ構成とすることができる。即ち、検出部210、位相比較部220及びリセット部230は図1の検出部110、位相比較部120及びリセット部130と各々同じ構成とすることができ、それに対する重複する説明は省略する。

【0075】

同期化部240は基準信号FREF及びフィードバック入力信号FFEEDIのうちの1つに基づいて第1位相比較信号PCS1及び第2位相比較信号PCS2を同期化して第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2を発生することができる。即ち、第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2は、一定周期を各々有することができる。第1位相比較出力信号OPCS1は第1位相比較信号PCS1に対応し、第2位相比較出力信号OPCS2は第2位相比較信号PCS2に対応することができる。

【0076】

図5及び図6を参照して説明したように、第1位相比較信号PCS1の論理レベルが決定される時点と第2位相比較信号PCS2の論理レベルが決定される時点とが相異なるようにすることができる。即ち、第1位相比較信号PCS1及び第2位相比較信号PCS2は互いに同期化しないこともある。

【0077】

上述した通り、本発明の他の実施形態に係るデジタル位相周波数検出器200は、フィードバック入力信号FFEEDIまたは、基準信号FREFのエッジに同期して、一定周期を各々有する第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2を発生することによって、位相及び周波数検出動作の正確度及び安定度を向上させることができる。

【0078】

図8は図7のデジタル位相周波数検出器に含まれる同期化部の一例を示すブロック図である。

図8を参照すれば、同期化部240は第3フリップフロップ242及び第4フリップフロップ244を含むことができる。

【0079】

上述した通り、同期化部240は基準信号FREF及びフィードバック入力信号FFEEDIのうちの1つに基づいて第1位相比較信号PCS1及び第2位相比較信号PCS2を各々同期化して、第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2を発生することができる。第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2は、基準信号FREFの上昇及び下降エッジ、フィードバック入力信号FFEEDIの上昇及び下降エッジのうちの1つに同期化できる。図8では同期化部240がフィードバック入力信号FFEEDIに基づいて同期化動作を実行することを示す。

【0080】

第3フリップフロップ242はフィードバック入力信号FFEEDIに基づいて第1位相比較信号PCS1を同期化して第1位相比較出力信号OPCS1を発生し、第4フリップフロップ244はフィードバック入力信号FFEEDIに基づいて第2位相比較信号PCS2を同期化し、第2位相比較出力信号OPCS2を発生することができる。第3フリップフロップ242及び第4フリップフロップ244のリセット入力端は検出イネイブル信号PDENを受信することができる。一方、図示はしていないが、第3フリップフロップ242及び第4フリップフロップ244のクロック入力端は、フィードバック入力信号FFEEDIの代わりに基準信号FREFを受信でき、第3フリップフロップ242及び第4フリップフロップ244は基準信号FREFに同期化された第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2を出力することができる。

【0081】

図9は本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャートである。

図1、図7及び図9を参照すれば、本発明の実施形態に係るデジタル位相周波数検出方法では、基準信号FREF及びフィードバック入力信号FFEEDIのエッジを各々検出して基準エッジ信号RES及びフィードバックエッジ信号FESを発生する(段階S110)。例えば、基準信号FREF及びフィードバック入力信号FFEEDIの上昇エッジ及び下降エッジのうちの1つを各々検出できる。

【0082】

フィードバックエッジ信号FESに基づいて基準エッジ信号RESを同期化して第1位相比較信号PCS1を発生し、基準エッジ信号RESに基づいてフィードバックエッジ信号FESを同期化して第2位相比較信号PCS2を発生する(段階S120)。第1位相比較信号PCS1及び第2位相比較信号PCS2は、基準信号FREFとフィードバック入力信号FFEEDIの位相差を示すことができ、互いに相補的に活性化することができる。

【0083】

一実施形態において、デジタル位相周波数検出方法は基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて、リセット信号RSTを発生する段階をさらに含むことができる。他の実施形態において、デジタル位相周波数検出方法は第1位相比較信号PCS1及び第2位相比較信号PCS2に基づいて相補的な論理レベルを有し、一定周期を各々有する第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2を発生する段階をさらに含むことができる。

【0084】

このように、本発明の実施形態に係るデジタル位相周波数検出方法では基準エッジ信号RES及びフィードバックエッジ信号FESを相互同期化して、第1位相比較信号PCS1及び第2位相比較信号PCS2を発生することによって、デジタル位相周波数検出方法を利用するデジタル位相周波数検出器100、200を小型化、高速化及び高性能化させることができる。

【0085】

図10は本発明のまた他の実施形態に係るデジタル位相周波数検出器を示すブロック図である。

図10を参照すれば、デジタル位相周波数検出器300は、基準信号生成部360、位相比較信号生成部301及び利得調節部350を含む。

【0086】

基準信号生成部360は入力信号FINに基づいてリード基準信号EFREF、基準信号FREF及びラグ基準信号LFREFを発生する。

【0087】

図11は図10のデジタル位相周波数検出器から発生する基準信号の一例を示す図である。

図11を参照すれば、リード基準信号EFREFは基準信号FREFと同じ波形を有し、基準信号FREFより△Pの位相差だけ進んだ位相を有している。ラグ基準信号LFREFは基準信号FREFと同じ波形を有し、基準信号FREFより△Pの位相差だけ遅れた位相を有している。例えば、△Pは約0度〜180度の間の値を有することができる。

【0088】

一実施形態において、基準信号生成部360は入力信号FINより遅れたり、入力信号FINと実質的に同じ位相を有するリード基準信号EFREFを発生し、リード基準信号EFREFを△Pだけ遅延させて基準信号FREFを発生し、基準信号FREFを△Pだけ遅延させてラグ基準信号LFREFを発生することができる。

【0089】

一方、図11において、UGは単位利得を示し、HGは単位利得より大きい調整利得を示す。後述するように、デジタル位相周波数検出器300を含むデジタル位相固定ループでは基準信号FREFとフィードバック入力信号FFEEDIとの位相差によりフィードバック入力信号FFEEDIの位相を単位利得UG或いは調整利得HGだけ移動させて基準信号FREFと出力信号との周波数差、及び/または、位相差を補償することができる。例えば、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差ΔPより小さい場合、即ち、フィードバック入力信号FFEEDIのエッジが区間Bに含まれる場合に、デジタル位相固定ループはフィードバック入力信号FFEEDIとの位相を単位利得UGだけ移動させることができる。基準信号FREFとフィードバック入力信号FFEEDIとの位相差が、予め決まった位相差ΔPより大きい場合、即ち、フィードバック入力信号FFEEDIのエッジが区間Aまたは区間Cに含まれる場合に、デジタル位相固定ループはフィードバック入力信号FFEEDIの位相を調整利得HGだけ移動させることができる。

【0090】

再び、図10を参照すれば、位相比較信号生成部301は基準信号FREF及びフィードバック入力信号FFEEDIに基づいて基準エッジ信号RES及びフィードバックエッジ信号FESを発生し、基準信号FREFとフィードバック入力信号FFEEDIとの位相差を示す第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する。基準エッジ信号RESは基準信号FREFのエッジを検出した場合に活性化し、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIのエッジを検出した場合に活性化することができる。第1位相比較信号PCS1及び第2位相比較信号PCS2は互いに相補的に活性化でき、第1位相比較信号PCS1はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れる場合に活性化し、第2位相比較信号PCS2はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進む場合に活性化することができる。

【0091】

一実施形態において、位相比較信号生成部301は図1のデジタル位相周波数検出器100と実質的に同じ構成とすることができる。即ち、検出部310、位相比較部320及びリセット部330は、図1の検出部110、位相比較部120及びリセット部130と各々同じ構成とすることができ、それに対する重複する説明は省略する。一方、図示はしていないが、位相比較信号生成部301は、図7及び図8を参照して上述したのと同じ同期化部240をさらに含むことができる。

【0092】

利得調節部350は、リード基準信号EFREF、ラグ基準信号LFREF、基準エッジ信号RES、及びフィードバックエッジ信号FESに基づいて基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差より大きいのか否かを示す高利得信号HGSを発生できる。即ち、高利得信号HGSはフィードバック入力信号FFEEDIが単位利得(図11のUG)に基づいて補正されるのかまたは、単位利得より大きい調整利得(図11のHG)に基づいて補正されるのかどうかを示すことができる。

【0093】

一実施形態において、高利得信号HGSは基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差より大きい場合に活性化することができる。例えば、高利得信号HGSは、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進んだり(即ち、フィードバック入力信号FFEEDIのエッジが図11の区間Aに含まれる場合)、フィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れる場合(即ち、フィードバック入力信号FFEEDIのエッジが図11の区間Cに含まれる場合)に活性化できる。

【0094】

一実施形態において、位相比較信号生成部301は基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてリセット信号RSTを発生でき、利得調節部350はリセット信号RSTをさらに受信できる。

【0095】

一実施形態において、リード基準信号EFREFは基準信号FREFより順次に進んだ位相を各々有する複数のリード基準信号を含み、ラグ基準信号LFREFは基準信号FREFより順次に遅れた位相を各々有する複数のラグ基準信号を含むことができる。この場合、利得調節部350は基準信号FREFとフィードバック入力信号FFEEDIとの位相差をより細部的に示すことができる複数の高利得信号を生成することができる。前記複数のリード基準信号、複数のラグ基準信号及びこれに対応するデジタル位相周波数検出器の構成に対しては図21〜図23を参照して後述する。

【0096】

従来のデジタル位相固定ループでは入力信号と出力信号との周波数差及び位相差を補正する際に、一定のフィードバック利得を適用した。従って、入力信号と出力信号との周波数差または位相差が大きい場合に、出力信号の位相及び周波数を固定するのに必要とされる出力信号の固定時間(lock time)が増加するという問題があった。

【0097】

上述した通り、本発明のまた他の実施形態に係るデジタル位相周波数検出器300はリード基準信号EFREF、ラグ基準信号LFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて高利得信号HGSをさらに発生し、高利得信号HGSが活性化した場合にデジタル位相周波数検出器300を含むデジタル位相固定ループのフィードバック利得を効率的に調節することができる。従って、デジタル位相周波数検出器300を含むデジタル位相固定ループの出力信号の固定時間(lock time)を効果的に減少させることができる。また、デジタル位相周波数検出器300に含まれる利得調節部350はデジタル位相固定ループの出力信号の位相及び周波数が固定された以後の正常状態(steady state)では動作を実行しないので、デジタル位相固定ループのジッタ(jitter)または、位相ノイズ(phase noise)には影響を及ぼさず、出力信号の固定時間のみを減少させることができる。

【0098】

図12は図10のデジタル位相周波数検出器に含まれる基準信号生成部の一例を示すブロック図である。

図12を参照すれば、基準信号生成部360aは3つのディレーセルDCを含むことができる。これら3つのディレーセルDCは直列接続され、入力信号FINを順次に遅延させて、リード基準信号EFREF、基準信号FREF及びラグ基準信号LFREFを順次に発生することができる。即ち、最も前段のディレーセルは入力信号FINを遅延させてリード基準信号EFREFを発生し、第2段のディレーセルはリード基準信号EFREFを遅延させて基準信号FREFを発生し、最後段のディレーセルは基準信号FREFを遅延させてラグ基準信号LFREFを発生することができる。

【0099】

図13は図10のデジタル位相周波数検出器に含まれる利得調節部の一例を示すブロック図である。

図13を参照すれば、利得調節部350aはリード検出部352、ラグ検出部354及び高利得信号生成部356を含むことができる。

【0100】

リード検出部352はリード基準信号EFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてフィードバック入力信号FFEEDIがリード基準信号EFREFより進んだ位相を有するのか否かを示すハイリード信号HLEADを発生することができる。ハイリード信号HLEADは、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進んでいる場合に活性化することができる。

【0101】

ラグ検出部354はラグ基準信号LFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてフィードバック入力信号FFEEDIがラグ基準信号LFREFより遅れた位相を有するか否かを示すハイラグ信号HLAGを発生することができる。ハイラグ信号HLAGはフィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れた場合に活性化できる。リード検出部352及びラグ検出部354は、リセット信号RSTをさらに受信することができる。

【0102】

高利得信号生成部356はハイリード信号HLEAD及びハイラグ信号HLAGに基づいて高利得信号HGSを発生できる。一実施形態において、高利得信号生成部356はハイリード信号HLEAD及びハイラグ信号HLAGに対して論理演算を実行する少なくとも1つの論理素子を含んで具現できる。

【0103】

図14は図13の利得調節部の具体的な例を示すブロック図である。

図14を参照すれば、利得調節部350aはリード検出部352、ラグ検出部354及び高利得信号生成部356を含み、リード検出部352はリード検出ブロック3521、論理演算ブロック3522及びリード出力ブロック3523を含むことができる。

【0104】

リード検出ブロック3521はリード基準信号EFREFのエッジを検出してリードエッジ信号EESを発生することができる。リードエッジ信号EESは、リード基準信号EFREFの上昇エッジ及び下降エッジのうちの1つに応答して活性化でき、リセット信号RSTに応答して非活性化できる。

【0105】

リード検出ブロック3521は第1フリップフロップFFLE1を含んで具現できる。第1フリップフロップFFLE1は、Dフリップフロップとすることができ、電源電圧が印加されるデータ入力端、リード基準信号EFREFが印加されるクロック入力端、リセット信号RSTが印加されるリセット入力端、リードエッジ信号EESが出力される出力端及びリードエッジ信号EESの反転信号EESbが出力される反転出力端を含むことができる。

【0106】

論理演算ブロック3522はリードエッジ信号EES、基準エッジ信号RES及びフィードバックエッジ信号FESに対して論理演算を実行してリード信号VEを発生することができる。この論理演算はAND演算であることができる。即ち、論理演算ブロック3522はANDゲートANDLEを含んで具現できる。

【0107】

一実施形態において、論理演算ブロック3522はリードエッジ信号EESの反転信号EESb、基準エッジ信号RESの反転信号RESb及びフィードバックエッジ信号FESに対してAND演算を実行してリード信号VEを発生することができる。この場合、リード信号VEはフィードバックエッジ信号FESが活性化してリードエッジ信号EES及び基準エッジ信号RESが非活性化された場合に活性化することができる。実施形態に従って、基準エッジ信号RESの反転信号RESbは、図3の検出部110に含まれた第3フリップフロップ112の反転出力端(図示せず)で提供される事もでき、第3フリップフロップ112の出力端の基準エッジ信号RESを反転して提供することもできる。

【0108】

リード出力ブロック3523はリードエッジ信号EESに基づいてリード信号VEを同期化してハイリード信号HLEADを発生することができる。ハイリード信号HLEADはリードエッジ信号EESが活性化する時点でリード信号VEの論理レベルに対応するように同期化できる。即ち、リード出力ブロック3523は、リードエッジ信号EESが活性化する時点でリード信号VEの論理レベルをサンプリングしてハイリード信号HLEADの論理レベルを決定できる。

【0109】

リード出力ブロック3523は第2フリップフロップFFLE2を含んで具現できる。第2フリップフロップFFLE2は、Dフリップフロップとすることができ、リード信号VEが印加されるデータ入力端、リードエッジ信号EESが印加されるクロック入力端、検出イネイブル信号PDENが印加されるリセット入力端及びハイリード信号HLEADが出力される出力端を含むことができる。

【0110】

ラグ検出部354はラグ検出ブロック3541、論理演算ブロック3542及びラグ出力ブロック3543を含むことができる。ラグ検出部354は、リード検出部352と類似の構成を有することができる。

【0111】

ラグ検出ブロック3541はラグ基準信号LFREFのエッジを検出してラグエッジ信号LESを発生することができる。ラグエッジ信号LESは、ラグ基準信号LFREFの上昇エッジ及び下降エッジのうちの1つに応答して活性化でき、リセット信号RSTに応答して非活性化できる。ラグ検出ブロック3541は第1フリップフロップFFLA1を含んで具現できる。

【0112】

論理演算ブロック3542はラグエッジ信号LES、基準エッジ信号RES及びフィードバックエッジ信号FESに対して論理演算を実行しラグ信号VLを発生できる。論理演算ブロック3542はANDゲートANDLAを含んで具現され、ラグエッジ信号LESの反転信号LESb、基準エッジ信号RES及びフィードバックエッジ信号FESの反転信号FESbに対してAND演算を実行してラグ信号VLを発生することができる。この場合、ラグ信号VLは基準エッジ信号RESが活性化し、ラグエッジ信号LES及びフィードバックエッジ信号FESが非活性化された場合に活性化することができる。実施形態に従って、フィードバックエッジ信号FESの反転信号FESbは図3の検出部110に含まれた第4フリップフロップ114の反転出力端(図示せず)に提供することもでき、第4フリップフロップ114の出力端のフィードバックエッジ信号FESを反転して提供することもできる。

【0113】

ラグ出力ブロック3543はラグエッジ信号LESに基づいてラグ信号VLを同期化してハイラグ信号HLAGを発生することができる。ラグ出力ブロック3543は第2フリップフロップFFLA2を含んで具現できる。

【0114】

高利得信号生成部356はORゲートを含んで具現できる。このORゲートはハイリード信号HLEAD及びハイラグ信号HLAGに対してOR演算を実行して高利得信号HGSを発生することができる。上述した通り、高利得信号HGSはハイリード信号HLEAD及びハイラグ信号HLAGのうちの1つが活性化した場合に活性化することができる。

【0115】

図15及び図16は図10のデジタル位相周波数検出器の動作を示すタイミング図である。

図15はフィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れる場合のデジタル位相周波数検出器300の動作を示し、図16はフィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進む場合のデジタル位相周波数検出器300の動作を示す。図15及び図16において、デジタル位相周波数検出器300は信号FREF、LFREF、EFREF、FFEEDI、RES、FES、LES、EES、RSTの上昇エッジに応答して動作し、信号RES、FES、LES、EES、RST、VL、VE、HLAG、HLEADは論理ローレベルから論理ハイレベルに遷移することによって活性化することを示している。

【0116】

以下では図15及び図16を参照して本発明のまた他の実施形態に係るデジタル位相周波数検出器300の動作を詳細に説明する。

【0117】

図10、図14及び図15を参照すれば、時刻taで、基準信号FREFの論理レベルが論理ローレベルから論理ハイレベルに遷移される。検出部310は基準信号FREFの上昇エッジに応答して基準エッジ信号RESを活性化させる。時刻tbで、ラグ基準信号LFREFの論理レベルが論理ローレベルから論理ハイレベルに遷移される。ラグ検出ブロック3541はラグ基準信号LFREFの上昇エッジに応答してラグエッジ信号LESを活性化させる。時刻tcで、フィードバック入力信号FFEEDIの論理レベルが論理ローレベルから論理ハイレベルに遷移される。検出部310はフィードバック入力信号FFEEDIの上昇エッジに応答してフィードバックエッジ信号FESを活性化させる。即ち、時刻ta、tb及びtcで基準信号FREF、ラグ基準信号LFREF及びフィードバック入力信号FFEEDIの第1周期が各々始まる。

【0118】

時刻taで、基準エッジ信号RESが活性化してラグエッジ信号LES及びフィードバックエッジ信号FESが非活性化されるので、論理演算ブロック3542はラグ信号VLを活性化させる。時刻tbで、ラグエッジ信号LESが活性化するので、論理演算ブロック3542はラグ信号VLを非活性化させる。また、ラグ出力ブロック3543はラグエッジ信号LESの上昇エッジに応答してラグ信号VLの論理レベルに対応するようにしラグ信号HLAGの論理レベルを決定する。ラグ信号VLの論理レベルは論理ハイレベルであるので、ハイラグ信号HLAGは論理ローレベルから論理ハイレベルに遷移する。即ち、フィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れる。

【0119】

一方、リセット部330は基準エッジ信号RES及びフィードバックエッジ信号FESが全部活性化した時刻tcから一定の遅延時間が経過した時刻tdでリセット信号RSTを活性化させる。リセット信号RSTが活性化することによって、検出部310は基準エッジ信号RES及びフィードバックエッジ信号FESを非活性化させ、ラグ検出ブロック3541はラグエッジ信号LESを非活性化させる。基準エッジ信号RES及びフィードバックエッジ信号FESが非活性化された時刻tdから一定の遅延時間が経過した時刻teで、リセット部330はリセット信号RSTを非活性化させる。

【0120】

時刻tfで基準エッジ信号RESが活性化し、時刻tgでフィードバックエッジ信号FESが活性化し、時刻tiでラグエッジ信号LESが活性化する。即ち、時刻tf、tg及びtiで基準信号FREF、フィードバック入力信号FFEEDI及びラグ基準信号LFREFの第2周期が各々始まる。ハイラグ信号HLAGが活性化することによって高利得信号HGSが活性化され、図27〜図29を参照して後述する通り、高利得信号HGSに基づいてフィードバック入力信号FFEEDIの位相が調整されたので、デジタル位相周波数検出器300は第1周期とは違うように動作することができる。

【0121】

時刻tfで、基準エッジ信号RESが活性化してラグエッジ信号LES及びフィードバックエッジ信号FESが非活性化されるので、ラグ信号VLは活性化する。時刻tgで、フィードバックエッジ信号FESが活性化するので、ラグ信号VLは非活性化される。時刻tgから一定の遅延時間が経過した時刻thで、リセット信号RSTが活性化する。リセット信号RSTが活性化することによって、基準エッジ信号RES及びフィードバックエッジ信号FESは非活性化され、ラグエッジ信号LESを非活性化状態に維持する。時刻tiで、ラグ信号VLの論理レベルは、論理ローレベルであるので、ハイラグ信号HLAGはラグエッジ信号LESの上昇エッジに応答して論理ハイレベルから論理ローレベルに遷移する。即ち、フィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅くないことを示す。時刻thから一定の遅延時間が経過した時刻tiで、リセット信号RSTは非活性化される。

【0122】

本発明のまた他の実施形態に係るデジタル位相周波数検出器300で、フィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れた場合に基準エッジ信号RES、フィードバックエッジ信号FES及びラグエッジ信号LESの論理レベルは一連の特定の組み合わせを有することができる。例えば、フィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れた第1周期の場合に、信号(RES、FES、LES)の論理レベルは、000、100、101、111、000の順に変更することができる。

【0123】

一方、図示はしていないが、図5を参照して上述した通り、第1位相比較信号PCS1は、時刻tcで活性化し、第2位相比較信号PCS2は非活性化状態を維持することができる。

【0124】

図10、図14及び図16を参照すれば、時刻tkで、フィードバック入力信号FFEEDIの論理レベルが論理ローレベルから論理ハイレベルに遷移され、フィードバックエッジ信号FESが活性化する。時刻tlで、リード基準信号EFREFの論理レベルが論理ローレベルから論理ハイレベルに遷移される。リード検出ブロック3521はリード基準信号EFREFの上昇エッジに応答してリードエッジ信号EESを活性化させる。時刻tmで、基準信号FREFの論理レベルが論理ローレベルから論理ハイレベルに遷移され、基準エッジ信号RESが活性化する。即ち、時刻tk、tl及びtmでフィードバック入力信号FFEEDI、リード基準信号EFREF及び基準信号FREFの第3周期が各々始まる。

【0125】

時刻tkで、フィードバックエッジ信号FESが活性化され、リードエッジ信号EES及び基準エッジ信号RESが非活性化されるので、論理演算ブロック3522はリード信号VEを活性化させる。時刻tlで、リードエッジ信号EESが活性化するので、論理演算ブロック3522はリード信号VEを非活性化させる。また、リード出力ブロック3523はリードエッジ信号EESの上昇エッジに応答してリード信号VEの論理レベルに対応するようにハイリード信号HLEADの論理レベルを決定する。リード信号VEの論理レベルは論理ハイレベルであるので、ハイリード信号HLEADは論理ローレベルから論理ハイレベルに遷移する。即ち、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進むことになる。

【0126】

時刻tmから一定の遅延時間が経過した時刻tnでリセット信号RSTが活性化する。リセット信号RSTが活性化することによって、検出部310は基準エッジ信号RES及びフィードバックエッジ信号FESを非活性化させ、リード検出ブロック3521はリードエッジ信号EESを非活性化させる。時刻tnから一定の遅延時間が経過した時刻toで、リセット信号RSTは非活性化される。

【0127】

時刻tpでリードエッジ信号EESが活性化し、時刻tqでフィードバックエッジ信号FESが活性化し、時刻trで、基準エッジ信号RESが活性化する。即ち、時刻tp、tq及びtrでリード基準信号EFREF、フィードバック入力信号FFEEDI及び基準信号FREFの第4周期が各々始まる。活性化した高利得信号HGSに基づいてフィードバック入力信号FFEEDIの位相が調整されるので、デジタル位相周波数検出器300は前記第3周期とは違うように動作することができる。

【0128】

第4周期では基準エッジ信号RESが活性化するが、ラグエッジ信号RES及びフィードバックエッジ信号FESが非活性化される区間が存在しないので、リード信号VEは活性化しない。時刻tpで、リード信号VEの論理レベルは論理ローレベルであるので、ハイリード信号HLEADはリードエッジ信号EESの上昇エッジに応答して論理ハイレベルから論理ローレベルに遷移する。即ち、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進んでいない。時刻trから一定の遅延時間が経過した時刻tsで、リセット信号RSTが活性化する。リセット信号RSTが活性化することによって、リードエッジ信号EES、基準エッジ信号RES及びフィードバックエッジ信号FESは非活性化される。時刻tsから一定の遅延時間が経過した時刻ttで、リセット信号RSTは非活性化される。

【0129】

本発明のまた他の実施形態に係るデジタル位相周波数検出器300で、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進む場合にリードエッジ信号EES、基準エッジ信号RES及びフィードバックエッジ信号FESの論理レベルは、一連の特定の組み合わせを有することができる。例えば、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進む第3周期の場合に、信号(EES、RES、FES)の論理レベルは、000、001、101、111、000の順に変更することができる。

【0130】

一方、図示はしていないが、図6を参照して上述した通り、第2位相比較信号PCS2は時刻tmで活性化し、第1位相比較信号PCS1は非活性化状態を維持することができる。

【0131】

図17は図10のデジタル位相周波数検出器に含まれる利得調節部の他の例を示すブロック図である。

【0132】

図17を参照すれば、利得調節部350bはリード検出部352、ラグ検出部354及び高利得信号生成部356を含み、利得同期化部358をさらに含むことができる。

【0133】

利得同期化部358をさらに含むのを除けば、図17の利得調節部350bは図13の利得調節部350aと実質的に同じ構成とすることができる。従って、リード検出部352、ラグ検出部354及び高利得信号生成部356に対する重複する説明は省略する。

【0134】

利得同期化部358は基準信号FREF及びフィードバック入力信号FFEEDIのうちの1つに基づいて高利得信号HGSを同期化して高利得出力信号OHGSを発生することができる。例えば、利得同期化部358はフィードバック入力信号FFEEDI或いは基準信号FREFの上昇または下降エッジに同期化して高利得出力信号OHGSを出力することができる。

【0135】

図10のデジタル位相周波数検出器300が図7及び図8を参照して上述したのと同じ同期化部240をさらに含む場合に、デジタル位相周波数検出器300は基準信号FREF及びフィードバック入力信号FFEEDIのうちの1つに同期化された第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2を出力することができる。これに対応するように図10のデジタル位相周波数検出器300に含まれる利得調節部350は図17に図示されたのと同じ構造とすることができ、デジタル位相周波数検出器300は基準信号FREF及びフィードバック入力信号FFEEDIのうちの1つに同期化された高利得出力信号OHGSを出力することができる。従って、位相及び周波数検出動作の正確度及び安定度を向上させることができる。

【0136】

図18は図17の利得調節部に含まれる利得同期化部の一例を示すブロック図である。

図18を参照すれば、利得同期化部358はフリップフロップを含んで具現することができる。図18では利得同期化部358がフィードバック入力信号FFEEDIに基づいて同期化動作を実行することが図示される。フリップフロップはフィードバック入力信号FFEEDIに基づいて高利得信号HGSを同期化し、高利得出力信号OHGSを発生することができる。フリップフロップのリセット入力端は検出イネイブル信号PDENを受信することができる。一方、図示はしていないが、フリップフロップのクロック入力端は、フィードバック入力信号FFEEDIの代わりに基準信号FREFを受信でき、フリップフロップは基準信号FREFに同期化された高利得出力信号OHGSを出力することができる。

【0137】

図19は図10のデジタル位相周波数検出器から発生する基準信号の他の例を示す図である。

図19を参照すれば、リード基準信号EFREFは基準信号FREFより進んだ位相を有する第1リード基準信号EFREF1〜第nリード基準信号EFREFn(ただ、nは2以上の自然数)を含むことができる。ラグ基準信号LFREFは、基準信号FREFより遅れた位相を有する第1ラグ基準信号LFREF1〜第nラグ基準信号LFREFnを含むことができる。

【0138】

一実施形態において、第1リード基準信号EFREF1〜第nリード基準信号EFREFnは、基準信号FREFと同じ波形を各々有して、nが増加するほど基準信号FREFより、予め設定された値だけ進んだ位相を各々有することができる。例えば、第1リード基準信号EFREF1は、基準信号FREFより△Pnだけ進んだ位相を有し、第2リード基準信号EFREF2は第1リード基準信号EFREF1より△Pnだけ進んだ位相を有することができる。これと同様に、第1ラグ基準信号LFREFn〜第nラグ基準信号LFREFnは、基準信号FREFと同じ波形を各々有し、nが増加するほど基準信号FREFより予め設定された値だけ遅れた位相を各々有することができる。第nリード基準信号EFREFnと基準信号FREFとは、約0度〜180度の間の位相差を有することができる。即ち、n×△Pnは約0度〜180度の間の値を有することができる。

【0139】

一実施形態において、第1リード基準信号EFREF1〜第nリード基準信号EFREFn、基準信号FREF、及び第1ラグ基準信号LFREF1〜第nラグ基準信号LFREFnは、入力信号FINに基づいて発生できる。例えば、入力信号を順次に△Pnだけ遅延させて第nリード基準信号EFREFnから第nラグ基準信号LFREFnまで順次に発生させることができる。

【0140】

図20は図10のデジタル位相周波数検出器に含まれる基準信号生成部の他の例を示すブロック図である。

図20を参照すれば、基準信号生成部360bは、複数個のディレーセルDCを含むことができる。例えば、基準信号生成部360bが、n個のリード基準信号(EFREF1,EFREF2,…,EFREFn)、基準信号FREF、及びn個のラグ基準信号(LFREF1,LFREF2,…,LFREFn)を生成する場合に、基準信号生成部360bは、2n+1個のディレーセルDCを含むことができる。これら複数個のディレーセルDCは直列接続され、入力信号FINを順次に遅延させて第nリード基準信号EFREFnから第nラグ基準信号LFREFnまで順次に発生させることができる。

【0141】

図21は図10のデジタル位相周波数検出器に含まれる利得調節部のまた他の例を示すブロック図である。

図21を参照すれば、利得調節部350cは、第1〜第nリード検出部(352a,352b,…,352n)、第1〜第nラグ検出部(354a,354b,…,354n)及び第1〜第n高利得信号生成部(356a,356b,…,356n)を含むことができる。

【0142】

第1リード検出部352a〜第nリード検出部352nは、第1リード基準信号EFREF1〜第nリード基準信号EFREFnのうちの1つ、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてフィードバック入力信号FFEEDIが、第1リード基準信号EFREF1〜第nリード基準信号EFREFnのうち、対応するリード基準信号より進んだ位相を有するのか否かを示す第1HLEAD1〜第nハイリード信号HLEADnを各々発生することができる。例えば、第1リード検出部352aは第1リード基準信号EFREF1、基準エッジ信号RES、及びフィードバックエッジ信号FESに基づいてフィードバック入力信号FFEEDIが第1リード基準信号EFREF1より進んだ位相を有するか否かを示す第1ハイリード信号HLEAD1を発生することができる。

【0143】

第1ラグ検出部354a〜第nラグ検出部354nは、第1ラグ基準信号LFREF1〜第nラグ基準信号LFREFnのうちのいずれか1つ、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてフィードバック入力信号FFEEDIが第1ラグ基準信号LFREF1〜第nラグ基準信号LFREFnより遅れた位相を有するか否かを示す第1ハイラグ信号HLAG1〜第nハイラグ信号HLAGnを各々発生することができる。例えば、第1ラグ検出部354aは第1ラグ基準信号LFREF1、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてフィードバック入力信号FFEEDIが第1ラグ基準信号LFREF1より遅れた位相を有するか否かを示す第1ハイラグ信号HLAG1を発生することができる。

【0144】

第1高利得信号生成部356a〜第n高利得信号生成部356nは、第1ハイリード信号HLEAD1〜第nハイリード信号HLEADnのうちのいずれか1つ及び対応する第1ハイラグ信号HLAG1〜第nハイラグ信号HLAGnのうちの1つに基づいて第1高利得信号HGS1〜第n高利得信号HGSnを各々発生することができる。例えば、第1高利得信号生成部356aは第1ハイリード信号HLEAD1及び第1ハイラグ信号HLAG1に基づいて第1高利得信号HGS1を発生することができる。

【0145】

第1高利得信号HGS1〜第n高利得信号HGSnは、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった範囲より大きい時、各々活性化することができる。例えば、第1高利得信号HGS1は、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が△Pnより大きい場合に、即ち、フィードバック入力信号FFEEDIの位相が第1リード基準信号EFREF1の位相より進んだり、または、第1ラグ基準信号LFREF1の位相より遅れる場合に活性化することができる。第2高利得信号HGS2は、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が2×ΔPnより大きい場合に、即ち、フィードバック入力信号FFEEDIの位相が第2リード基準信号EFREF2の位相より進んだり第2ラグ基準信号LFREF2の位相より遅れる場合に活性化することができる。

【0146】

一実施形態において、第1リード検出部352a〜第nリード検出部352nは、図14のリード検出部352と類似の構成を各々有することができ、第1ラグ検出部354a〜第nラグ検出部354nは、図14のラグ検出部354と類似の構成を各々有することができ、第1高利得信号生成部356a〜第n高利得信号生成部356nは、図14の高利得信号生成部356と類似の構成を各々有することができる。

【0147】

上述した通り、本発明のまた他の実施形態に係るデジタル位相周波数検出器300は、複数の高利得信号(HGS1,…,HGSn)を生成することによって、デジタル位相周波数検出器300を含むデジタル位相固定ループのフィードバック利得を精密に調節することができ、デジタル位相固定ループの出力信号の固定時間を減少させることができる。

【0148】

図22は本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャートである。

【0149】

図10及び図22を参照すれば、本発明の実施形態に係るデジタル位相周波数検出方法では、基準信号FREF及びフィードバック入力信号FFEEDIのエッジを各々検出して基準エッジ信号RES及びフィードバックエッジ信号FESを発生し(段階S210)、フィードバックエッジ信号FESに基づいて基準エッジ信号RESを同期化して第1位相比較信号PCS1を発生し、基準エッジ信号RESに基づいてフィードバックエッジ信号FESを同期化して第2位相比較信号PCS2を発生する(段階S220)。前記段階S210及びS220は各々図9の段階S110及びS120と実質的に同一であることもある。

【0150】

リード基準信号EFREF、ラグ基準信号LFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて高利得信号HGSを発生する(段階S230)。高利得信号HGSは、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差より大きいか否かを示すことができる。

【0151】

一実施形態において、デジタル位相周波数検出方法は入力信号FINに基づいてリード基準信号EFREF、基準信号FREF及びラグ基準信号LFREFを発生する段階をさらに含むことができる。他の実施形態において、デジタル位相周波数検出方法は基準信号FREF及びフィードバック入力信号FFEEDIのうちの1つに基づいて高利得信号HGSを同期化して高利得出力信号OHGSを発生する段階をさらに含むことができる。

【0152】

これと共に、本発明の実施形態に係るデジタル位相周波数検出方法ではリード基準信号EFREF及びラグ基準信号LFREFに基づいて高利得信号HGSをさらに発生することによって、デジタル位相周波数検出方法を利用するデジタル位相周波数検出器300を含むデジタル位相固定ループの出力信号の固定時間を減少させることができる。

【0153】

図23は本発明のまた他の実施形態に係るデジタル位相周波数検出器を示すブロック図である。

図23を参照すれば、デジタル位相周波数検出器400は基準信号生成部460、位相比較信号生成部401及び利得調節部450を含み、利得選択部470をさらに含むことができる。

【0154】

利得選択部470をさらに含むことを除けば、図23のデジタル位相周波数検出器400は、図10のデジタル位相周波数検出器300と実質的に同じ構成とすることができる。即ち、基準信号生成部460、位相比較信号生成部401及び利得調節部450は、図10の基準信号生成部360、位相比較信号生成部301及び利得調節部350と各々同じ構成とすることができ、それに対する重複する説明は省略する。

【0155】

利得選択部470は第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つと高利得信号HGSとに基づいて選択利得信号SGSを発生することができる。選択利得信号SGSは基準信号FREFとフィードバック入力信号FFEEDIとの位相差に対応するデジタル形態の値を有することができる。

【0156】

一実施形態において、選択利得信号SGSは、高利得信号HGSが活性化した場合に相対的に大きいデジタル値を有し、高利得信号HGSが非活性化された場合に相対的に小さいデジタル値を有することができる。例えば、第1位相比較信号PCS1が非活性化された場合、即ち、フィードバック入力信号FFEEDIの位相が基準信号FREFより進む場合を仮定すれば、利得選択部470は高利得信号HGSが非活性化された場合に第1デジタル値を有する選択利得信号SGSを出力し、高利得信号HGSが活性化した場合に第2デジタル値を有する選択利得信号SGSを出力することができる。第1デジタル値は一般的にフィードバック入力信号FFEEDIの位相を遅延させるための単位利得に対応でき、第2デジタル値はフィードバック入力信号FFEEDIの位相を相対的にさらに多く遅延させるための、単位利得より大きい調整利得に対応することができる。第2デジタル値は第1デジタル値と符号が同じであり、第1デジタル値より大きさが大きいこともある。

【0157】

一実施形態において、第2デジタル値は第1デジタル値より予め決まった利得増加比だけ大きいこともある。即ち、第1デジタル値と第2デジタル値は一定の比率を有することができ、下記の式(1)を満足することができる。

【0158】

【数1】

式(1)で、GRは予め決まった利得増加比を示し、UGは高利得信号HGSが非活性化された場合にフィードバック入力信号FFEEDIの位相を調節するための第1デジタル値の大きさ(即ち、単位利得の大きさ)を示し、HGは高利得信号HGSが活性化した場合にフィードバック入力信号FFEEDIの位相を調節するための第2デジタル値の大きさ(即ち、調整利得の大きさ)を示す。また、例えば、予め決まった利得増加比は約2〜8の間の値を有することができる。予め決まった利得増加比が2より小さければデジタル位相固定ループの出力信号の固定時間がほとんど減少されず、予め決まった利得増加比が8より大きければ出力信号の位相及び周波数を精密に調節しにくいこともある。

【0159】

図24は図23のデジタル位相周波数検出器に含まれる利得選択部の一例を示すブロック図である。

図24を参照すれば、利得選択部470はマルチプレクサを含んで具現できる。このマルチプレクサは第1位相比較信号PCS1及び高利得信号HGSに基づいて複数のデジタル値(HE、LE、LL、HL)のうちの1つを選択して選択利得信号SGSとして出力することができる。

【0160】

一実施形態において、マルチプレクサは第1位相比較信号PCS1が非活性化された場合にフィードバック入力信号FFEEDIの位相を遅延させるためのデジタル値を選択し、第1位相比較信号PCS1が活性化した場合にフィードバック入力信号FFEEDIの位相を操り上げるためのデジタル値を選択することができる。また、マルチプレクサは高利得信号HGSが非活性化された場合にフィードバック入力信号FFEEDIの位相を相対的に少なく調節するためのデジタル値(即ち、前記単位利得に対応するデジタル値)を選択し、高利得信号HGSが活性化した場合にフィードバック入力信号FFEEDIの位相を相対的に多く調節するためのデジタル値(即ち、前記調整利得に対応するデジタル値)を選択することができる。

【0161】

一実施形態において、複数のデジタル値(HE、LE、LL、HL)各々はフィードバック入力信号FFEEDIの位相を調節するためのフィードバック利得に対応することができる。第1デジタル値HEは、フィードバック入力信号FFEEDIの位相を相対的に多く遅延させるための第1調整利得に対応し、第2デジタル値LEは、フィードバック入力信号FFEEDIの位相を相対的に少なく遅延させるための第1単位利得に対応することができる。第3デジタル値LLは、フィードバック入力信号FFEEDIの位相を相対的に少なく進めるための第2単位利得に対応し、第4デジタル値HLは、フィードバック入力信号FFEEDIの位相を相対的に多く進めるための第2調整利得に対応することができる。例えば、第1〜第4デジタル値(HE、LE、LL、HL)は、各々「−8」、「−1」、「+1」及び「+8」に対応することができる。この場合、予め決まった利得増加比は8と設定され、デジタル位相固定ループはフィードバック入力信号FFEEDIの位相を遅延させるために記デジタル位相固定ループ内のデジタルループフィルタから発生するデジタル制御信号DCONの値を減少させ、フィードバック入力信号FFEEDIの位相を進めるためにデジタル制御信号DCONの値を増加させることができる。

【0162】

一実施形態において、マルチプレクサは第1位相比較信号PCS1が非活性化された場合に第1デジタル値HE及び第2デジタル値LEのうちの1つを選択でき、第1位相比較信号PCS1が活性化した場合に第3デジタル値LL及び第4デジタル値HLのうちの1つを選択することができる。また、マルチプレクサは高利得信号HGSが非活性化された場合に第2デジタル値LE及び第3デジタル値LLのうちの1つを選択でき、高利得信号HGSが活性化した場合に第1デジタル値HE及び第4デジタル値HLのうちの1つを選択することができる。例えば、第1位相比較信号PCS1及び高利得信号HGSが全部活性化した場合に、マルチプレクサは第4デジタル値HLを選択して選択利得信号SGSとして出力することができる。即ち、第1〜第4デジタル値(HE、LE、LL、HL)が各々「−8」、「−1」、「+1」及び「+8」に対応する場合に、第1位相比較信号PCS1は選択利得信号SGSの符号を決めて高利得信号HGSは選択利得信号SGSの大きさを決定することができる。

【0163】

図24では第1位相比較信号PCS1が選択信号として使われることを図示したが、第2位相比較信号PCS2が選択信号として使われることもできる。また、図24では利得選択部470が4つのデジタル値(HE、LE、LL、HL)のうちのいずれか1つを選択して出力することを図示したが、実施形態に従って、高利得信号HGSは図21を参照して上述した通り、第1〜第n高利得信号を含むことができ、この場合利得選択部470は第1位相比較信号PCS1及び第1〜第n高利得信号に基づいて、2(n+1)個のデジタル値のうち、いずれか1つを選択して出力することができる。

【0164】

図25は本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャートである。

図23及び図25を参照すれば、本発明の実施形態に係るデジタル位相周波数検出方法では、入力信号FINに基づいてリード基準信号EFREF、基準信号FREF及びラグ基準信号LFREFを発生する(段階S215)。リード基準信号EFREFは基準信号FREFより進んだ位相を有し、ラグ基準信号LFREFは基準信号FREFより遅れた位相を有することができる。

【0165】

基準信号FREF及びフィードバック入力信号FFEEDIに基づいて基準エッジ信号RES及びフィードバックエッジ信号FESを発生する(段階S225)。例えば、基準信号FREFのエッジを検出して基準エッジ信号RESを発生し、フィードバック入力信号FFEEDIのエッジを検出してフィードバックエッジ信号FESを発生することができる。

【0166】

リード基準信号EFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてハイリード信号を発生し(段階S235)、ラグ基準信号LFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいてハイラグ信号を発生する(段階S245)。ハイリード信号はフィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進んでいるのかどうかを示し、ハイラグ信号はフィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れているのか否かを示す。

【0167】

ハイリード信号及びハイラグ信号に基づいて高利得信号HGSを発生する(段階S255)。高利得信号HGSはフィードバック入力信号FFEEDIが単位利得に基づいて補正されるか、または、単位利得より大きい調整利得に基づいて補正されるか否か、即ち、フィードバック入力信号FFEEDIが単位利得だけ補正されるか、または、調整利得だけ補正されるか否かを示す。

【0168】

一実施形態において、高利得信号HGSは、フィードバック入力信号FFEEDIの位相がリード基準信号EFREFの位相より進んだりフィードバック入力信号FFEEDIの位相がラグ基準信号LFREFの位相より遅れる場合に活性化し、高利得信号HGSに基づいて選択利得信号SGSを発生することができる(段階S265)。選択利得信号SGSは高利得信号HGSが活性化した場合に調整利得に対応して高利得信号HGSが非活性化された場合に単位利得に対応することができる。

【0169】

一実施形態において、デジタル位相周波数検出方法は基準信号FREF及びフィードバック入力信号FFEEDIに基づいて第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する段階をさらに含むことができる。

【0170】

図26は本発明の一実施形態に係るデジタル位相固定ループを示すブロック図である。

図26を参照すれば、デジタル位相固定ループ500はデジタル位相周波数検出器510、デジタルループフィルタ(digital loop filter;DLF)520、デジタル制御発振器(digitally controlled oscillator;DCO)530及び分周器540を含む。

【0171】

デジタル位相周波数検出器510は、基準信号FREF及びフィードバック入力信号FFEEDIに基づいて基準信号FREFとフィードバック入力信号FFEEDIとの位相差を示す第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する。例えば、デジタル位相周波数検出器510は、基準信号FREF及びフィードバック入力信号FFEEDIのエッジを各々検出して基準エッジ信号及びフィードバックエッジ信号を発生し、このフィードバックエッジ信号に基づいて基準エッジ信号を同期化して第1位相比較信号PCS1を発生し、基準エッジ信号に基づいてフィードバックエッジ信号を同期化して第2位相比較信号PCS2を発生することができる。

【0172】

デジタル位相周波数検出器510は、図1及び図7のデジタル位相周波数検出器(100、200)のうちの1つでありうる。即ち、デジタル位相周波数検出器510は、検出部、位相比較部及びリセット部を含み、同期化部をさらに含むことができる。デジタル位相周波数検出器510が、図7のデジタル位相周波数検出器200とともに同期化部240をさらに含む場合に、図26に図示された第1位相比較信号PCS1及び第2位相比較信号PCS2は、図7の第1位相比較出力信号OPCS1及び第2位相比較出力信号OPCS2に各々対応することができる。

【0173】

検出部は、基準信号FREF及びフィードバック入力信号FFEEDIのエッジを検出して、基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいて検出部を初期化させるリセット信号を発生する。位相比較部は基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備して、第1比較信号を出力する第1フリップフロップ、フィードバックエッジ信号を受信するデータ入力端及び基準エッジ信号を受信するクロック入力端を具備し、第2比較信号を出力する第2フリップフロップ及び第1比較信号及び第2比較信号をラッチして、第1位相比較信号PCS1及び第2位相比較信号PCS2を発生するラッチ部を含んで具現する。

【0174】

デジタルループフィルタ520は、第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つに基づいて出力信号FOUTの位相及び周波数を調節するためのデジタル制御信号DCONを発生する。即ち、デジタルループフィルタ520は、基準信号FREF及びフィードバック入力信号FFEEDIの位相差及び周波数差に該当する誤差値がデジタル位相同期ループ500で許容する基準誤差値より大きい場合に、出力信号FOUTを制御するためのデジタル形態の制御信号DCONをデジタル制御発振器530で出力する。一実施形態において、デジタルループフィルタ520は、第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つに対応するデジタル値を選択し、選択されたデジタル値を累積してデジタル制御信号DCONを発生することができ、マルチプレクサ及び累積器(accumulator)を含んで具現できる。

【0175】

デジタル制御発振器530はデジタル制御信号DCONに対応する位相及び周波数を有する出力信号FOUTを発生する。分周器540は出力信号FOUTを分周してフィードバック入力信号FFEEDIを発生する。分周器540はフィードバック入力信号FFEEDIをデジタル位相周波数検出器510に提供することによって、基準信号FREF及びフィードバック入力信号FFEEDIの位相及び周波数が一致する時まで繰り返して位相及び周波数検出動作を実行させることができる。

【0176】

一実施形態において、デジタル位相固定ループ500は、オール−デジタル位相固定ループ(all−digital PLL;ADPLL)形態で具現できる。即ち、デジタル制御発振器530を除いたデジタル位相固定ループ500に含まれる大部分の構成要素はデジタルロジックを利用して具現され、工程、電圧及び温度変化による影響を相対的に減少させることができ、位相固定ループを相対的に効率的に設計することができる。

【0177】

上述した通り、本発明の一実施形態に係るデジタル位相固定ループ500は、図1及び図7のデジタル位相周波数検出器(100、200)のうちの1つを含んで具現されることによって、簡単な構造で具現されることができ、向上した動作速度を有して、基準信号FREFとフィードバック入力信号FFEEDIとの間の位相及び周波数差を精密に検出して出力信号FOUTを効果的に固定させることができる。

【0178】

図27は本発明の一実施形態に係るデジタル位相固定方法を示すフローチャートである。

図1、図26及び図27を参照すれば、本発明の一実施形態に係るデジタル位相固定方法では、基準信号FREF及びフィードバック入力信号FFEEDIのエッジを各々検出して基準エッジ信号RES及びフィードバックエッジ信号FESを発生し、フィードバックエッジ信号FES及び基準エッジ信号RESを各々同期化して第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する(段階S310)。段階S310は図9を参照して説明した本発明の実施形態に係るデジタル位相周波数検出方法と実質的に同一でありうる。

【0179】

第1位相比較信号PCS1及び第2位相比較信号PCS2に基づいてデジタル制御信号DCONを発生する(段階S320)。デジタル制御信号DCONは出力信号FOUTの位相及び周波数を調節するためのデジタル形態の制御信号でありうる。

【0180】

デジタル制御信号DCONに対応する位相及び周波数を有する出力信号FOUTを発生し(段階S330)、出力信号FOUTを分周してフィードバック入力信号FFEEDIを発生する(段階S340)。また、基準信号FREF及びフィードバック入力信号FFEEDIの位相及び周波数が一致するかを判断する(段階S350)。位相及び周波数が同じである場合にデジタル位相固定方法を終了して、同一でない場合に段階S310〜S340を繰り返して実行する。

【0181】

図28は本発明の他の実施形態に係るデジタル位相固定ループを示すブロック図である。

図28を参照すれば、デジタル位相固定ループ600は、デジタル位相周波数検出器610、デジタルループフィルタ620、デジタル制御発振器630及び分周器640を含む。

【0182】

デジタル位相周波数検出器610が高利得信号HGSをさらに生成することを除けば、図28のデジタル位相固定ループ600は、図26のデジタル位相固定ループ500と実質的に同じ構成とすることができる。即ち、デジタル制御発振器630及び分周器640は、図26のデジタル制御発振器530及び分周器540と各々同じ構成とすることができ、それに対して重複する説明は省略する。

【0183】

デジタル位相周波数検出器610は入力信号FINに基づいてリード基準信号EFREF、基準信号FREF及びラグ基準信号LFREFを発生し、基準信号FREF及びフィードバック入力信号FFEEDIに基づいて基準エッジ信号RES及びフィードバックエッジ信号FESを発生し、基準信号FREFとフィードバック入力信号FFEEDIとの位相差を示す第1位相比較信号PCS1及び第2位相比較信号PCS2を発生し、リード基準信号EFREF、ラグ基準信号LFREF、基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差より大きいか否かを示す高利得信号HGSを発生する。

【0184】

一実施形態において、デジタル位相周波数検出器610は、図10のデジタル位相周波数検出器300でありうる。即ち、デジタル位相周波数検出器610は基準信号生成部602、位相比較信号生成部604及び利得調節部606を含むことができる。基準信号生成部602、位相比較信号生成部604及び利得調節部606は、図10の基準信号生成部360、位相比較信号生成部301及び利得調節部350と各々同じ構成とすることができ、それに対する重複する説明は省略するようにする。

【0185】

他の実施形態において、デジタル位相周波数検出器610は、図23のデジタル位相周波数検出器400でありうる。即ち、デジタル位相周波数検出器610は選択利得信号を発生する利得選択部をさらに含むことができる。

【0186】

デジタルループフィルタ620は、第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つと高利得信号HGSとに基づいて、出力信号FOUTの位相及び周波数を調節するためのデジタル制御信号DCONを発生する。

【0187】

一実施形態において、デジタル位相周波数検出器610が図10のデジタル位相周波数検出器300の場合に、デジタルループフィルタ620は第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つと高利得信号HGSに対応するデジタル値を選択し、この選択されたデジタル値を累積してデジタル制御信号DCONを発生できる。この場合デジタルループフィルタ620は、高利得信号HGSに基づいてフィードバック利得を調節することができる。即ち、デジタルループフィルタ620は、高利得信号HGSが活性化した場合にフィードバック利得を増加させて出力信号FOUTの位相及び周波数を相対的に大幅で調節することができる。

【0188】

他の実施形態において、デジタル位相周波数検出器610が図23のデジタル位相周波数検出器400の場合に、デジタルループフィルタ620は選択利得信号SGSを累積してデジタル制御信号DCONを発生することができる。

【0189】

上述した通り、本発明の他の実施形態に係るデジタル位相固定ループ600は、図10及び図23のデジタル位相周波数検出器(300、400)のうちの1つを含んで具現されることによって、ジッタまたは、位相ノイズには影響を及ぼさずに出力信号FOUTの固定時間のみを効果的に減少させることができる。

【0190】

図29は本発明の他の実施形態に係るデジタル位相固定方法を示すフローチャートである。

図28及び図29を参照すれば、本発明の他の実施形態に係るデジタル位相固定方法では、基準信号FREFとフィードバック入力信号FFEEDIとの位相差を示す第1位相比較信号PCS1及び第2位相比較信号PCS2を発生し、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差より大きいか否かを示す高利得信号HGSを発生する(段階S410)。段階S410は、図22を参照して説明された本発明の実施形態に係るデジタル位相周波数検出方法と実質的に同一であることもできる。

【0191】

第1位相比較信号PCS1、第2位相比較信号PCS2及び高利得信号HGSに基づいてデジタル制御信号DCONを発生する(段階S420)。例えば、第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つと高利得信号HGSとに基づいて複数のデジタル値のうちの1つを選択して選択利得信号SGSを発生し、選択利得信号SGSに基づいてデジタル制御信号DCONを発生することができる。この場合、第1位相比較信号PCS1及び第2位相比較信号PCS2のうちの1つに基づいて選択利得信号SGSの符号が決定されて高利得信号HGSに基づいて選択利得信号SGSの大きさを決定することができる。

【0192】

デジタル制御信号DCONに対応する位相及び周波数を有する出力信号FOUTを発生し(段階S430)、出力信号FOUTを分周してフィードバック入力信号FFEEDIを発生する(段階S440)。また、基準信号FREF及びフィードバック入力信号FFEEDIの位相及び周波数が一致するかを判断する(段階S450)。位相及び周波数が同じ場合にデジタル位相固定方法を終了し、同一ではない場合に段階S410〜S440を繰り返して実行する。

【0193】

図30は本発明のまた他の実施形態に係るデジタル位相固定ループを示すブロック図である。

図30を参照すれば、デジタル位相固定ループ700はデジタル位相周波数検出器710、デジタルループフィルタ720、デジタル制御発振器730及び分周器740を含み、自動周波数調節器(automatic frequency controller;AFC)750をさらに含むことができる。

【0194】

自動周波数調節器750をさらに含むことを除けば、図30のデジタル位相固定ループ700は、図28のデジタル位相固定ループ600と実質的に同じ構成とすることができる。即ち、基準信号生成部702、位相比較信号生成部704及び利得調節部706を含むデジタル位相周波数検出器710、デジタルループフィルタ720及び分周器740は、図28のデジタル位相周波数検出器610、デジタルループフィルタ620及び分周器640と各々同じ構成とすることができ、それに対する重複する説明は省略する。

【0195】

自動周波数調節器750は基準信号FREF及びフィードバック入力信号FFEEDIに基づいて出力信号FOUTの初期周波数を調節するための自動デジタル制御信号DCONAを発生することができる。一実施形態において、自動周波数調節器750は基準信号FREF及びフィードバック入力信号FFEEDIのクロックの個数をカウントするカウンタ及びカウント回数を比較する比較器などを含んで具現され、基準信号FREF及びフィードバック入力信号FFEEDIの比較時点を制御するためにダイナミックバイナリブランチ(dynamic binary branch)のような技法を使うことができる。

【0196】

デジタル制御発振器730は自動デジタル制御信号DCONA及びデジタル制御信号DCONに基づいて出力信号FOUTの位相及び周波数を調節することができる。例えば、デジタル位相固定ループ700の位相及び周波数調節動作はコース(coarse)モード及びファイン(fine)モードに区分され、デジタル制御発振器730は、コースモードで概略的な周波数調節動作を実行して自動デジタル制御信号DCONAに対応する周波数を有する出力信号FOUTを発生し、ファインモードで精密な位相及び周波数調節動作を実行してデジタル制御信号DCONに対応する位相及び周波数を有する出力信号FOUTを発生することができる。

【0197】

上述した通り、本発明のまた他の実施形態に係るデジタル位相固定ループ700は、出力信号FOUTの初期周波数を調節するための自動デジタル制御信号DCONAを発生する自動周波数調節器750をさらに含んで具現することによって、出力信号FOUTの固定時間を効果的に減少させることができる。

【0198】

図31は本発明の実施形態に係るデジタル位相固定ループの動作を示すグラフである。図31は位相及び周波数調節動作が実行されることによるデジタル位相固定ループの出力信号の周波数の変化を示す。図31において、CASE Aは従来のデジタル位相固定ループの出力信号を示し、CASE Bは図28のデジタル位相固定ループ600の出力信号を示し、CASE Cは図30のデジタル位相固定ループ700の出力信号を示す。

【0199】

図31を参照すれば、CASE Aで図示されるように、従来のデジタル位相固定ループは常に一定のフィードバック利得、即ち、単位利得を適用して位相及び周波数調節動作を実行する。即ち、従来のデジタル位相固定ループは、周波数キャプチャ区間(時間T0〜TA1)で出力信号の周波数を単位利得だけ増加させ、位相キャプチャ区間(時間TA1〜TA2)で出力信号の周波数を単位利得だけ増加または減少させ、位相固定区間(時間TA2以後)で出力信号の位相及び周波数を固定させる。図31のCASE Aで、従来のデジタル位相固定ループで適用される単位利得は1と示す。従来のデジタル位相固定ループは出力信号の初期周波数と目標周波数(TARGET)との差が大きい場合に出力信号の固定時間が長いという問題があった。

【0200】

図28及び図31を参照すれば、CASE Bで図示するように、本発明の他の実施形態に係るデジタル位相固定ループ600は基準信号FREFとフィードバック入力信号FFEEDIとの位相差により互いに異なるフィードバック利得を適用して位相及び周波数調節動作を実行する。即ち、デジタル位相固定ループ600は周波数キャプチャ区間(時間T0〜TB1)で出力信号の周波数を単位利得より大きい調整利得だけ増加させ、位相キャプチャ区間(時間TB1〜TB3)の第1区間(時間TB1〜TB2)で出力信号の周波数を調整利得だけ減少させる。デジタル位相固定ループ600は位相キャプチャ区間(時間TB1〜TB3)の第2区間(時間TB2〜TB3)で出力信号の周波数を単位利得だけ増加または、減少させて、出力信号の位相及び周波数を精密に調節し、位相固定区間(時間TB3以後)で出力信号の位相及び周波数を固定させる。図31のCASE Bで、単位利得は1と示し調整利得はnと示す。上述した通りnは2〜8の間の整数でありうる。

【0201】

デジタル位相固定ループ600から発生する出力信号の初期傾きは、出力信号の最終傾きより大きいこともある。例えば、周波数キャプチャ区間(時間T0〜TB1)及び位相キャプチャ区間の第1区間(時間TB1〜TB2)では、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が相対的に大きいから高利得信号HGSが活性化して相対的に大きい調整利得が適用され、従って、出力信号の傾きが相対的に大きい。位相キャプチャ(PHASE CAPTURE)区間の第2区間(時間TB2〜TB3)では、基準信号FREFとフィードバック入力信号FFEEDIとの位相差が相対的に小さいから高利得信号HGSが非活性化されて相対的に小さい単位利得を適用することができ、従って、出力信号の傾きが相対的に小さい。

【0202】

本発明の他の実施形態に係るデジタル位相固定ループ600は基準信号FREFとフィードバック入力信号FFEEDIとの位相差が予め決まった位相差より大きい場合(時間T0〜TB2)には調整利得を適用して位相及び周波数調節動作を実行し、予め決まった位相差より小さい場合(時間TB2〜TB3)には単位利得を適用して位相及び周波数調節動作を実行する。従って、デジタル位相固定ループ600は出力信号の固定時間を効果的に減少させることができる。

【0203】

図30及び図31を参照すれば、CASE Cで図示するように、本発明のまた他の実施形態に係るデジタル位相固定ループ700は自動周波数調節器750を利用して出力信号の初期周波数を調節することを除けば図28のデジタル位相固定ループ600と実質的に同じ動作を実行する。即ち、デジタル位相固定ループ700は周波数キャプチャ区間(時間T0〜TC2)の第1区間(時間T0〜TC1)で自動周波数調節器750を利用して出力信号の初期周波数を概略的に調節し、周波数キャプチャ区間(時間T0〜TC2)の第2区間(時間TC1〜TC2)で出力信号の周波数を調整利得だけ増加させ、位相キャプチャ区間(時間TC2〜TC4)の第1区間(時間TC2〜TC3)で出力信号の周波数を調整利得だけ減少させる。デジタル位相固定ループ700は、位相キャプチャ区間(時間TC2〜TC4)の第2区間(時間TC3〜TC4)で出力信号の周波数を単位利得だけ増加または減少させて、出力信号の位相及び周波数を精密に調節し、位相固定区間(時間TC4以後)で出力信号の位相及び周波数を固定させる。

【0204】

本発明のまた他の実施形態に係るデジタル位相固定ループ700は自動周波数調節器750を含み、デジタル位相周波数検出器710が高利得信号HGSを発生し、デジタルループフィルタ720が高利得信号HGSに基づいてフィードバック利得を調節することによって、ジッタまたは位相ノイズには影響を及ぼさずに出力信号FOUTの固定時間のみを効果的に減少させることができる。

【0205】

一実施形態において、周波数キャプチャ区間の所要時間は下記の式(2)を満足する。

【0206】

【数2】

式(2)で、GRは予め決まった利得増加比(即ち、n)を示し、T1は従来のデジタル位相固定ループの周波数キャプチャ区間の所要時間(即ち、T0〜TA1)を示し、T2はデジタル位相固定ループ600の周波数キャプチャ区間の所要時間(即ち、T0〜TB1)を示す。デジタル位相固定ループ700の周波数キャプチャ区間の所要時間(即ち、T0〜TC2)は自動周波数調節器750の構造及び設計によりさらに減少させることができる。

【0207】

図32は本発明の実施形態に係るデジタル位相固定ループを含む集積回路を示すブロック図である。

図32を参照すれば、集積回路800はデジタル位相固定ループ810及び内部回路820を含む。

【0208】

デジタル位相固定ループ810は、基準信号FREF及び入力信号FINのうちの1つに基づいて固定された位相及び周波数を有する出力信号FOUTを発生する。上述した通り、基準信号FREFは入力信号FINと同一または、入力信号FINを遅延させて発生することができる。デジタル位相固定ループ810は、図26、図28及び図30のデジタル位相固定ループ(500、600、700)のうちの1つでありうる。

【0209】

内部回路820は、出力信号FOUTに基づいて予め決まった動作を実行する。即ち、出力信号FOUTは内部回路820を駆動させるクロック信号として使うことができる。内部回路820は検出回路、制御回路、駆動回路、増幅回路、変換回路、フューズ回路などのような任意の回路のうち、少なくとも1つを含んで具現することができる。

【0210】

一実施形態において、集積回路800は、モバイルSoC(mobile system on chip)、AP(application processor) SoC、マルチメディア(multimedia) SoCなどのような多様な形態のSoC、スマートカード、DTV(digital TV)、プリンタ、ビデオカメラ、イメージ装置などのような多様なアプリケーションに適用できる。

【0211】

図33は本発明の実施形態に係るデジタル位相固定ループを含む送信機を示すブロック図である。

図33を参照すれば、送信機900はデータ処理回路910、周波数合成器920及び増幅器930を含む。送信機900は例えばポーラー送信機(polar transmitter)の形態で具現できる。

【0212】

データ処理回路910は同相信号(I)と直交信号(Q)で構成される基底帯域データ(BASEBAND)を処理して振幅信号Aと位相信号Pとに分離する。一実施形態において、データ処理回路910は、CORDIC(Coordinate Rotational Digital Computer)で具現され、座標系上でI信号軸とQ信号軸に対する座標成分と表示された基底帯域データ(BASEBAND)を位相成分(即ち、位相信号P)と振幅成分(即ち、振幅信号A)に変換することができる。

【0213】

周波数合成器920は基準信号FREF及び入力信号FINのうちの1つと位相信号Pとに基づいて出力信号FOUTを生成する。即ち、周波数合成器920は位相信号Pに基づいて基準信号FREF及び入力信号FINのうちの1つから出力信号FOUTを生成する。一実施形態において、周波数合成器920は基準信号FREF及び入力信号FINのうちの1つと位相信号Pとを合算する加算器及び合算された信号に基づいて出力信号FOUTを生成するデジタル位相固定ループを含んで具現できる。デジタル位相固定ループは図26、図28及び図30のデジタル位相固定ループ(500、600、700)のうちの1つでありうる。

【0214】

増幅器930は出力信号FOUTと振幅信号Aとを合成して送信信号TSを出力する。即ち、増幅器930は出力信号FOUTを受信して振幅信号Aに符合する出力レベルを有する伝送信号TS、即ち、搬送波を出力する。

【0215】

図34は本発明の実施形態に係るデジタル位相固定ループを含むメモリ装置を示すブロック図である。

図34を参照すれば、メモリ装置1000は、デジタル位相固定ループ1010、メモリコア1020、及びデータ出力バッファ1030を含む。

【0216】

メモリ装置1000は、例えば、動的ランダムアクセスメモリ(Dynamic Random Access Memory;DRAM)、静的ランダムアクセスメモリ(Static Random Access Memory;SRAM)などのような揮発性メモリ装置及びEPROM(Erasable Programmable Read−Only Memory)、EEPROM(Electrically Erasable Programmable Read−Only Memory)及びフラッシュメモリ装置(flash memory device)などのような非揮発性メモリ装置のうちの1つとすることができ、特にDDR SDRAMまたはGDDR SDRAMでありうる。

【0217】

デジタル位相固定ループ1010は、基準信号FREF及び入力信号FINのうちの1つに基づいて固定された位相及び周波数を有する出力信号FOUTを発生する。出力信号FOUTはメモリ装置1000を駆動させるクロック信号として使うことができる。デジタル位相固定ループ1010は、図26、図28及び図30のデジタル位相固定ループ(500、600、700)のうちの1つでありうる。

【0218】

メモリコア1020は出力信号FOUT、即ち、クロック信号に基づいて動作することができる。メモリコア1020は、データ入力バッファ(図示せず)から提供された記入データを保存し、読み出しデータDATAを生成してデータ出力バッファ1030に提供する。図示はしていないが、メモリコア1020は、データを保存する複数のメモリセルを含むメモリセルアレイ、アドレス信号に基づいてメモリセルアレイのワードライン及びビットラインを選択するローデコーダ及びコラムデコーダ、及び選択されたメモリセルに保存されたデータを感知して読み出しデータDATAを生成する感知増幅器を含むことができる。

【0219】

データ出力バッファ1030は、出力信号FOUT、即ち、クロック信号に応答して読み出しデータDATAを出力データDOUTとして出力する。出力データDOUTはクロック信号に同期して出力され、例えば、メモリコントローラのような外部装置に提供することができる。

【0220】

図35は図34のメモリ装置を含むシステムを示すブロック図である。

図35を参照すれば、システム1100はプロセッサ1110、メモリ装置1120、ユーザインターフェース1130、保存装置1140、入出力装置1150及び電源装置1160を含むことができる。

【0221】

プロセッサ1110は特定計算または、タスク(task)を実行できる。実施形態に従って、プロセッサ1110は、マイクロプロセッサ(microprocessor)、中央処理装置(Central Processing Unit;CPU)でありうる。プロセッサ1110はアドレスバス(address bus)、制御バス(control bus)及びデータバス(data bus)を介してメモリ装置1120、ユーザインターフェース1130、保存装置1140及び入出力装置1150に接続されて通信を実行できる。実施形態に従って、プロセッサ1110は周辺構成要素相互接続(Peripheral Component Interconnect;PCI)バスのような拡張バスにも接続することができる。

【0222】

一方、プロセッサ1110はシングルコア(single core)または、マルチコア(multi core)の形態で具現することができる。例えば、ARMコアプロセッサは約1GHz未満のシステムクロックを利用して動作する場合に、シングルコアの形態で具現することができ、約1GHz以上のシステムクロックを利用して高速で動作する次世代プロセッサの場合にマルチコアの形態で具現することができる。また、前記のような次世代ARMコアプロセッサはAXI(Advanced extensible Interface)バスを介して周辺装置と通信を実行できる。

【0223】

メモリ装置1120はシステム1100の動作に必要なデータを保存でき、図34のメモリ装置1000でありうる。即ち、メモリ装置1120は、図26、図28及び図30のデジタル位相固定ループ(500、600、700)のうちの1つを含んで具現することができる。

【0224】

ユーザインターフェース1130は、使用者がシステム1100を動作させるのに必要な多様な手段を含むことができる。保存装置1140はソリッドステートドライブ(solid state drive)、ハードディスクドライブ(hard disk drive)及びCD−ROMなどを含むことができる。入出力装置1150は、キーボード、キーパッド、マウスなどと同じ入力手段及びプリンタ、ディスプレイなどのような出力手段を含むことができる。電源装置1160は、システム1100の動作に必要な動作電圧を供給することができる。

【0225】

図示はしていないが、システム1100はビデオカード、サウンドカード、メモリカード、USB装置などと通信したり、または、他の電子機器と通信できるポート(port)をさらに含むことができる。また、システム1100はベースバンドチップセット(baseband chipset)、応用チップセット(application chip set)及びイメージセンサなどをさらに含むことができる。一方、システム1100は任意のコンピューティングシステムと解釈されなければならない。

【産業上の利用可能性】

【0226】

本発明は位相及び周波数が固定された出力信号(例えば、クロック信号)を必要とする任意の集積回路、送信機、及び半導体装置などとこれを含む電子機器及び電子システムに有用に利用することができる。特に本発明はモバイルSoC(mobile system on chip)、AP(application processor) SoC、マルチメディア(multimedia) SoC、スマートカード、DTV(digital TV)、プリンタ、ビデオカメラ、イメージ装置などと同じ多様なアプリケーションに適用することができる。

【0227】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【符号の説明】

【0228】

110: 検出部

120: 位相比較部

130: リセット部

122: 第1フリップフロップ

124: 第2フリップフロップ

126: ラッチブロック

【技術分野】

【0001】

本発明は位相周波数検出器に係り、より詳細にはデジタル位相周波数検出器、このデジタル位相周波数検出器を含むデジタル位相固定ループ及びデジタル位相周波数検出方法に関する。

【背景技術】

【0002】

位相固定ループ(phase locked loop;PLL)は固定された位相及び周波数を有する出力信号を得るために使用される。従来、アナログ回路で具現されたアナログ位相固定ループが使用されてきたが、半導体技術の発達によってトランジスタの速度が増加し、供給電圧が低下したことから、アナログ位相固定ループでは外部ノイズに敏感で精密度が落ちるという問題があった。従って、最近では外部ノイズに敏感でなく精密度が確保できるデジタル回路で具現されたデジタル位相固定ループが使用されている。デジタル位相固定ループは入力信号と出力信号の位相及び周波数差を検出するデジタル位相周波数検出器(phase frequency detector;PFD)を含み、このデジタル位相周波数検出器の性能によってデジタル位相固定ループの性能を決定することができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−154270号公報

【特許文献2】米国特許7,728,675号明細書

【特許文献3】米国特許出願公開2008/0136535号明細書

【特許文献4】米国特許7,595,699号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の一目的は、小型化及び高速化に適合し、基準信号とフィードバック入力信号との間の位相及び周波数差を精密に検出できるデジタル位相周波数検出器を提供することにある。

【0005】

本発明の他の目的は、小型化及び高速化に適合し、基準信号とフィードバック入力信号の間の位相及び周波数差を精密に検出できるデジタル位相周波数検出方法を提供することにある。

本発明のまた他の目的は前記デジタル位相周波数検出器を含み、出力信号の固定時間を減少させることのできるデジタル位相固定ループを提供することにある。

【課題を解決するための手段】

【0006】

前記一目的を達成するために、本発明の一実施形態に係るデジタル位相周波数検出器は検出部、位相比較部、及びリセット部を含む。前記検出部は基準信号及びフィードバック入力信号のエッジを検出して、基準エッジ信号及びフィードバックエッジ信号を発生する。前記リセット部は前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記検出部を初期化させるリセット信号を発生する。前記位相比較部は、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生する。前記位相比較部は第1フリップフロップ、第2フリップフロップ及びラッチブロックを含む。前記第1フリップフロップは前記基準エッジ信号を受信するデータ入力端及び前記フィードバックエッジ信号を受信するクロック入力端を具備し、第1比較信号を出力する。前記第2フリップフロップは前記フィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備し、第2比較信号を出力する。前記ラッチブロックは前記第1比較信号及び前記第2比較信号をラッチして前記第1位相比較信号及び前記第2位相比較信号を発生する。

【0007】

一実施形態において、前記第1位相比較信号及び前記第2位相比較信号は互いに相補的に活性化し、前記第1位相比較信号は前記フィードバック入力信号の位相が前記基準信号の位相より遅れる場合に活性化し、前記第2位相比較信号は前記フィードバック入力信号の位相が前記基準信号の位相より進む場合に活性化することができる。

【0008】

前記第1位相比較信号は前記フィードバックエッジ信号が活性化する時点に前記基準エッジ信号の論理レベルに対応するように同期化し、前記第2位相比較信号は前記基準エッジ信号が活性化する時点での前記フィードバックエッジ信号の論理レベルに対応するように同期化できる。前記リセット信号は前記基準エッジ信号及び前記フィードバックエッジ信号が、全部活性化した場合に活性化し、前記基準エッジ信号及び前記フィードバックエッジ信号は前記リセット信号が活性化した場合に非活性化することができる。

【0009】

前記検出部は第3フリップフロップ及び第4フリップフロップを含むことができる。前記第3フリップフロップは前記基準信号の上昇エッジ及び下降エッジのうちの1つに応答して活性化し、前記リセット信号に応答して非活性化される前記基準エッジ信号を発生することができる。前記第4フリップフロップは前記フィードバック入力信号の上昇エッジ及び下降エッジのうちの1つに応答して活性化し、前記リセット信号に応答して非活性化される前記フィードバックエッジ信号を発生することができる。

【0010】

前記リセット部は少なくとも1つの論理素子を含むことができる。前記少なくとも1つの論理素子は前記基準エッジ信号、前記フィードバックエッジ信号、及び検出イネイブル信号に対して論理演算を実行して前記リセット信号を発生することができる。

【0011】

一実施形態において、前記デジタル位相周波数検出器は、同期化部をさらに含むことができる。前記同期化部は前記基準信号及び前記フィードバック入力信号のうちの1つに基づいて前記第1位相比較信号及び前記第2位相比較信号を同期化して、第1位相比較出力信号及び第2位相比較出力信号を発生することができる。

【0012】

前記同期化部は第3フリップフロップ及び第4フリップフロップを含むことができる。前記第3フリップフロップは前記基準信号及び前記フィードバック入力信号のうちの1つを受信するクロック入力端及び前記第1位相比較信号を受信するデータ入力端を具備し、前記第1位相比較出力信号を出力することができる。前記第4フリップフロップは前記基準信号及び前記フィードバック入力信号のうちの1つを受信するクロック入力端及び前記第2位相比較信号を受信するデータ入力端を具備し、前記第2位相比較出力信号を出力 することができる。

【0013】

前記一目的を達成するために、本発明の他の実施形態に係るデジタル位相周波数検出器は基準信号生成部、位相比較信号生成部及び利得調節部を含む。前記基準信号生成部は入力信号に基づいてリード基準信号、基準信号及びラグ基準信号を発生する。前記位相比較信号生成部は前記基準信号及びフィードバック入力信号に基づいて基準エッジ信号及びフィードバックエッジ信号を発生し、前記基準信号と前記フィードバック入力信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生する。前記利得調節部は前記リード基準信号、前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記基準信号と前記フィードバック入力信号の位相差が予め決まっていた位相差より大きいか否かを示す高利得信号を発生する。

【0014】

前記リード基準信号は前記基準信号と同じ波形を有し、前記基準信号より進んだ位相を有し、前記ラグ基準信号は前記基準信号と同じ波形を有し、前記基準信号より遅れた位相を有することができる。前記高利得信号は前記フィードバック入力信号の位相が前記リード基準信号の位相より進んだり、または、前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れる場合に活性化することができる。

【0015】

前記利得調節部は、リード検出部、ラグ検出部及び高利得信号生成部を含むことができる。前記リード検出部は、前記リード基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記リード基準信号の位相より進んでいるのかどうかを示すハイリード信号を発生できる。前記ラグ検出部は前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れているのかどうかを示すハイラグ信号を発生することができる。前記高利得信号生成部は前記ハイリード信号及び前記ハイラグ信号に基づいて前記高利得信号を発生できる。

【0016】

前記リード検出部はリード検出ブロック、論理演算ブロック及びリード出力ブロックを含むことができる。前記リード検出ブロックは前記リード基準信号のエッジを検出してリードエッジ信号を発生することができる。前記論理演算ブロックは前記リードエッジ信号、前記基準エッジ信号及び前記フィードバックエッジ信号に対し論理演算を実行してリード信号を発生することができる。前記リード出力ブロックは前記リードエッジ信号に基づいて前記リード信号を同期化して前記ハイリード信号を発生することができる。

【0017】

前記ラグ検出部は、ラグ検出ブロック、論理演算ブロック及びラグ出力ブロックを含むことができる。前記ラグ検出ブロックは前記ラグ基準信号のエッジを検出してラグエッジ信号を発生することができる。前記論理演算ブロックは前記ラグエッジ信号、前記基準エッジ信号及び前記フィードバックエッジ信号に対し論理演算を実行してラグ信号を発生することができる。前記ラグ出力ブロックは前記ラグエッジ信号に基づいて前記ラグ信号を同期化して前記ハイラグ信号を発生することができる。

【0018】

前記利得調節部は利得同期化部をさらに含むことができる。前記利得同期化部は前記基準信号及び前記フィードバック入力信号のうちの1つに基づいて前記高利得信号を同期化して高利得出力信号を発生することができる。

【0019】

一実施形態において、前記リード基準信号は第1〜第n(ただ、nは2以上の自然数)リード基準信号を含み、前記ラグ基準信号は第1〜第nラグ基準信号を含むことができる。前記第1〜第nリード基準信号は、nが増加するほど前記基準信号より、予め設定された値だけ進んだ位相を各々有することができる。前記第1〜第nラグ基準信号はnが増加するほど前記基準信号より前記予め設定された値だけ遅れた位相を各々有することができる。

【0020】

前記利得調節部は第1〜第nリード検出部、第1〜第nラグ検出部及び第1〜第n高利得信号生成部を含むことができる。前記第1〜第nリード検出部は、前記第1〜第nリード基準信号のうちの1つ、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号が前記第1〜第nリード基準信号のうち、対応するリード基準信号より進んだ位相を有するか否かを示す第1〜第nハイリード信号を各々発生することができる。前記第1〜第nラグ検出部は前記第1〜第nラグ基準信号のうちの1つ、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号が、前記第1〜第nラグ基準信号のうち、対応するラグ基準信号より遅れた位相を有するか否かを示す第1〜第nハイラグ信号を各々発生することができる。前記第1〜第n高利得信号生成部は前記第1〜第nハイリード 信号のうちの1つ及び対応する前記第1〜第nハイラグ信号のうちの1つに基づいて第1〜第n高利得信号を各々発生することができる。

【0021】

前記位相比較信号生成部は、前記基準信号及び前記フィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生し、前記フィードバックエッジ信号に基づいて前記基準エッジ信号を同期化して前記第1位相比較信号を発生し、前記基準エッジ信号に基づいて前記フィードバックエッジ信号を同期化して前記第2位相比較信号を発生することができる。

【0022】

前記デジタル位相周波数検出器は、利得選択部をさらに含むことができる。前記利得選択部は前記第1位相比較信号及び前記第2位相比較信号のうちの1つと前記高利得信号に基づいて、前記高利得信号が非活性化された場合に第1デジタル値を有して前記高利得信号が活性化した場合に前記第1デジタル値より大きい第2デジタル値を有する選択利得信号を発生することができる。

【0023】

前記他の目的を達成するために、本発明の一実施形態に係るデジタル位相周波数検出方法では、入力信号に基づいてリード基準信号、基準信号及びラグ基準信号を発生し、前記基準信号及びフィードバック入力信号に基づいて基準エッジ信号及びフィードバックエッジ信号を発生し、前記リード基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記リード基準信号の位相より先んじるのかどうかを示すハイリード信号を発生し、前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れているのかどうかを示すハイラグ信号を発生し、前記ハイリード信号及び前記ハイラグ信号に基づいて前記フィードバック入力信号が単位利得または、前記単位利得より大きい調整利得に基づいて補正されるのかどうかを示す高利得信号を発生する。

【0024】

前記高利得信号は前記フィードバック入力信号の位相が前記リード基準信号の位相より進んでいたり前記フィードバック入力信号の位相が前記ラグ基準信号の位相より遅れている場合に活性化することができる。この場合前記デジタル位相周波数検出方法では前記高利得信号が活性化した場合に前記調整利得に対応して前記高利得信号が非活性化された場合に前記単位利得に対応する選択利得信号をさらに発生することができる。

【0025】

前記また他の目的を達成するために、本発明の一実施形態に係るデジタル位相固定ループはデジタル位相周波数検出器、デジタルループフィルタ、デジタル制御発振器及び分周器を含む。前記デジタル位相周波数検出器は基準信号及びフィードバック入力信号に基づいて前記基準信号と前記フィードバック入力信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生する。前記デジタルループフィルタは前記第1位相比較信号及び前記第2位相比較信号のうちの1つに基づいて出力信号の位相及び周波数を調節するためのデジタル制御信号を発生する。前記デジタル制御発振器は前記デジタル制御信号に対応する位相及び周波数を有する前記出力信号を発生する。前記分周器は前記出力信号を分周して前記フィードバック入力信号を発生する。前記デジタル位相周波数検出器は検出部、リセット部、第1フリップフロップ、第2フリップフロップ及びラッチ部を含む。前記検出部は前記基準信号及び前記フィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。前記リセット部は前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記検出部を初期化させるリセット信号を発生する。前記第1フリップフロップは前記基準エッジ信号を受信するデータ入力端及び前記フィードバックエッジ信号を受信するクロック入力端を具備し、第1比較信号を出力する。前記第2フリップフロップは前記フィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備し、第2比較信号を出力する。前記ラッチ部は前記第1比較信号及び前記第2比較信号をラッチして前記第1位相比較信号及び前記第2位相比較信号を発生する。

【0026】

前記また他の目的を達成するために、本発明の他の実施形態に係るデジタル位相固定ループはデジタル位相周波数検出器、デジタルループフィルタ、デジタル制御発振器及び分周器を含む。前記デジタル位相周波数検出器は入力信号に基づいてリード基準信号、基準信号及びラグ基準信号を発生し、前記基準信号及びフィードバック入力信号に基づいて基準エッジ信号及びフィードバックエッジ信号を発生し、前記基準信号と前記フィードバック入力信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生し、前記リード基準信号、前記ラグ基準信号、前記基準エッジ信号及び前記フィードバックエッジ信号に基づいて前記基準信号と前記フィードバック入力信号との位相差が予め決まった位相差より大きいのか否かを示す高利得信号を発生する。前記デジタルループフィルタは前記第1位相比較信号及び前記第2位相比較信号のうちの1つと前記高利得信号に基づいて出力信号の位相及び周波数を調節するためのデジタル制御信号を発生する。前記デジタル制御発振器は前記デジタル制御信号に対応する位相及び周波数を有する前記出力信号を発生する。前記分周器は前記出力信号を分周して前記フィードバック入力信号を発生する。

【0027】

前記出力信号の初期傾きは前記出力信号の最終傾きより大きいこともある。

【0028】

一実施形態において、前記デジタル位相固定ループは自動周波数調節器をさらに含むことができる。前記自動周波数調節器は前記基準信号及び前記フィードバック入力信号に基づいて前記出力信号の初期周波数を調節するための自動デジタル制御信号を発生することができる。

【0029】

前記一目的を達成するために、本発明のまた他の実施形態に係るデジタル位相固定ループを制御するデジタル位相周波数検出器は、位相比較信号生成部、利得調節部及び利得選択部を含む。前記位相比較信号生成部は前記デジタル位相固定ループの基準信号及びフィードバック信号に応答して、前記基準信号と前記フィードバック信号との位相差を示す第1位相比較信号及び第2位相比較信号を発生する。前記利得調節部はリード基準信号及びラグ基準信号に応答して、前記基準信号と前記フィードバック入力信号との位相差が予め決まった位相差より大きいのか否かを示す高利得信号を発生する。前記利得選択部は前記第1位相比較信号及び前記第2位相比較信号のうちの1つと前記高利得信号に基づいて、選択利得信号を発生する。前記選択利得信号は前記高利得信号が非活性化された場合に第1デジタル値を有し、前記高利得信号が活性化した場合に前記第1デジタル値より大きい第2デジタル値を有する。前記第1デジタル値及び前記第2デジタル値により、前記デジタル位相固定ループの出力信号及び前記フィードバック信号の位相調節と周波数調節を制御する。

【発明の効果】

【0030】

前記のような本発明の実施形態に係るデジタル位相周波数検出器は、フィードバックエッジ信号に基づいて基準エッジ信号を同期化して第1位相比較信号を発生し、基準エッジ信号に基づいてフィードバックエッジ信号を同期化して第2位相比較信号を発生することによって、小型化及び高速化に適合し、基準信号とフィードバック入力信号との間の位相及び周波数差を精密に検出することができる。また、基準信号とフィードバック入力信号の位相差が予め決まった位相差より大きいのか否かを示す高利得信号をさらに発生することによって、前記デジタル位相周波数検出器を含むデジタル位相固定ループのフィードバック利得を効率的に調節することができる。

【0031】

また、本発明の実施形態に係るデジタル位相周波数検出器を含むデジタル位相固定ループは構造が簡単で、向上した動作速度を有して、出力信号を効果的に固定させることができる。特にジッタまたは、位相ノイズには影響を及ぼさずに出力信号の固定時間のみを減少させることができる。

【図面の簡単な説明】

【0032】

【図1】本発明の一実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図2】図1のデジタル位相周波数検出器に含まれる位相比較部の一例を示すブロック図。

【図3】図1のデジタル位相周波数検出器に含まれる検出部の一例を示すブロック図。

【図4】図1のデジタル位相周波数検出器に含まれるリセット部の一例を示すブロック図。

【図5】図1のデジタル位相周波数検出器の動作を示すタイミング図。

【図6】図1のデジタル位相周波数検出器の動作を示すタイミング図。

【図7】本発明の他の実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図8】図7のデジタル位相周波数検出器に含まれる同期化部の一例を示すブロック図。

【図9】本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャート。

【図10】本発明のまた他の実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図11】図10のデジタル位相周波数検出器から発生する基準信号の一例を示す図。

【図12】図10のデジタル位相周波数検出器に含まれる基準信号生成部の一例を示すブロック図。

【図13】図10のデジタル位相周波数検出器に含まれる利得調節部の一例を示すブロック図。

【図14】図13の利得調節部の具体的な例を示すブロック図。

【図15】図10のデジタル位相周波数検出器の動作を示すタイミング図。

【図16】図10のデジタル位相周波数検出器の動作を示すタイミング図。

【図17】図10のデジタル位相周波数検出器に含まれる利得調節部の他の例を示すブロック図。

【図18】図17の利得調節部に含まれる利得同期化部の一例を示すブロック図。

【図19】図10のデジタル位相周波数検出器から発生する基準信号の他の例を示す図面。

【図20】図10のデジタル位相周波数検出器に含まれる基準信号生成部の他の例を示すブロック図。

【図21】図10のデジタル位相周波数検出器に含まれる利得調節部のまた他の例を示すブロック図。

【図22】本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャート。

【図23】本発明のまた他の実施形態に係るデジタル位相周波数検出器を示すブロック図。

【図24】図23のデジタル位相周波数検出器に含まれる利得選択部の一例を示すブロック図。

【図25】本発明の実施形態に係るデジタル位相周波数検出方法を示すフローチャート。

【図26】本発明の一実施形態に係るデジタル位相固定ループを示すブロック図。

【図27】本発明の一実施形態に係るデジタル位相固定方法を示すフローチャート。

【図28】本発明の他の実施形態に係るデジタル位相固定ループを示すブロック図。

【図29】本発明の他の実施形態に係るデジタル位相固定方法を示すフローチャート。

【図30】本発明のまた他の実施形態に係るデジタル位相固定ループを示すブロック図。

【図31】本発明の実施形態に係るデジタル位相固定ループの動作を示すグラフ。

【図32】本発明の実施形態に係るデジタル位相固定ループを含む集積回路を示すブロック図。

【図33】本発明の実施形態に係るデジタル位相固定ループを含む送信機を示すブロック図。

【図34】本発明の実施形態に係るデジタル位相固定ループを含むメモリ装置を示すブロック図。

【図35】図34のメモリ装置を含むシステムを示すブロック図。

【発明を実施するための最良の形態】

【0033】

本明細書に開示されている本発明の実施形態に対して、特定の構造的ないし機能的説明は、単に本発明の実施形態を説明するための目的で例示されたものであり、本発明の実施形態は多様な形態で実施することができ、本明細書に説明された実施形態に限定されるものではない。

【0034】

本発明は多様な変更を加えることができ、種々の形態を有することができるが、特定の実施形態を図面に例示して本明細書に詳細に説明する。しかし、これは本発明を特定の開示形態に限定しようとするものではなく、本発明の思想及び技術範囲に含まれるすべての変更、均等物ないし代替物を含むと理解すべきである。

【0035】

本明細書において、第1、第2等の用語は多様な構成要素を説明するのに使用することができるが、これらの構成要素がこのような用語によって限定されてはならない。これらの用語は一つの構成要素を他の構成要素から区別する目的で使われる。例えば、本発明の権利範囲から逸脱せずに第1構成要素は第2構成要素と命名することができ、同様に第2構成要素も第1構成要素と命名することができる。

【0036】

ある構成要素が他の構成要素に「連結されて」いる、または「接続されて」いると言及されている場合には、その他の構成要素に直接的に連結されていたり、接続されていることも意味するが、中間に他の構成要素が存在する場合も含むと理解すべきである。一方、ある構成要素が他の構成要素に「直接連結されて」いる、または「直接接続されて」いると言及されている場合には、中間に他の構成要素が存在しないと理解すべきである。構成要素の間の関係を説明する他の表現、すなわち「〜間に」と「すぐに〜間に」または「〜に隣接する」と「〜に直接隣接する」等も同様に解釈すべきである。

【0037】

本明細書で使用した用語は単に特定の実施形態を説明するために使用したもので、本発明を限定するものではない。単数の表現は文脈上明白に異ならない限り、複数の表現をも含む。本明細書で、「含む」または「有する」等の用語は明細書上に記載された特徴、数字、段階、動作、構成要素、部品または、これを組み合わせたものが存在するということを示すものであって、一つまたはそれ以上の他の特徴や数字、段階、動作、構成要素、部品または、これを組み合わせたものなどの存在または、付加の可能性を、予め排除するわけではない。

【0038】

また、別に定義しない限り、技術的或いは科学的用語を含み、本明細書中において使用される全ての用語は本発明が属する技術分野で通常の知識を有する者であれば、一般的に理解するのと同一の意味を有する。一般的に使用される辞書において定義する用語と同じ用語は関連技術の文脈上に有する意味と一致する意味を有するものと理解すべきで、本明細書において明白に定義しない限り、理想的或いは形式的な意味として解釈してはならない。

【0039】

一方、ある実施形態が別に実現可能な場合に特定ブロック内に明記された機能または、動作がフローチャートに明記された順序と違う場合もある。例えば、連続する2つのブロックが実際には実質的に同時に実行する事もでき、関連した機能または、動作によっては前記ブロックが逆に遂行されることも可能である。

【0040】

以下、添付図面を参照して、本発明の望ましい実施形態をより詳細に説明する。図面上の同一構成要素に対しては同一参照符号を使用し、同一構成要素に対しての重複した説明は省略する。

【0041】

図1は本発明の一実施形態に係るデジタル位相周波数検出器(phase frequency detector;PFD)を示すブロック図である。

図1を参照すれば、デジタル位相周波数検出器100は検出部110、位相比較部120及びリセット部130を含む。

【0042】

デジタル位相周波数検出器100はデジタル位相固定ループ(phase locked loop;PLL)内に含まれ、デジタル位相固定ループの入力信号と出力信号との位相及び周波数差を検出することによって、デジタル位相固定ループが出力信号の位相及び周波数を調節し、固定された位相及び周波数を有する出力信号を発生するようにする。

【0043】

検出部110は基準信号FREF及びフィードバック入力信号FFEEDIのエッジを検出して基準エッジ信号RES及びフィードバックエッジ信号FESを発生する。即ち、検出部110は基準信号FREFのエッジを検出して基準エッジ信号RESを発生し、フィードバック入力信号FFEEDIのエッジを検出してフィードバックエッジ信号FESを発生する。

【0044】

基準信号FREFはデジタル位相固定ループの入力信号に対応し、フィードバック入力信号FFEEDIはデジタル位相固定ループの出力信号に対応することができる。例えば、基準信号FREFはデジタル位相固定ループの入力信号と実質的に同一であるか、または、デジタル位相固定ループの入力信号を遅延して発生させることができる。フィードバック入力信号FFEEDIはデジタル位相固定ループの出力信号と実質的に同一であるか、または、デジタル位相固定ループの出力信号を分周して発生させることができる。基準信号FREFはクリスタル(crystal)等を利用して生成され、固定された周波数を有するので、基準信号FREFの周波数はフィードバック入力信号FFEEDIの周波数に対する基準周波数として使用される。

【0045】

一実施形態において、基準エッジ信号RESは基準信号FREFの上昇エッジ及び下降エッジのうちの1つに応答して活性化し、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIの上昇エッジ及び下降エッジのうちの1つに応答して活性化できる。例えば、基準エッジ信号RESが基準信号FREFの上昇エッジに応答して活性化する場合に、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIの上昇エッジに応答して活性化できる。また、基準エッジ信号RES及びフィードバックエッジ信号FESはリセット信号RSTに応答して非活性化できる。

【0046】

ここで、「活性化」とは各信号が第1論理レベルから第2論理レベルに遷移されることを示し、「非活性化」とは各信号が第2論理レベルから第1論理レベルに遷移されることを示す。例えば、第1論理レベルは論理ローレベルで第2論理レベルは論理ハイレベルとすることができる。

【0047】

位相比較部120は基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する。例えば、位相比較部120はフィードバックエッジ信号FESに基づいて基準エッジ信号RESを同期化して第1位相比較信号PCS1を発生し、基準エッジ信号RESに基づいてフィードバックエッジ信号FESを同期化して第2位相比較信号PCS2を発生することができる。第1位相比較信号PCS1及び第2位相比較信号PCS2は基準信号FREFとフィードバック入力信号FFEEDIとの位相及び周波数の差を示すことができる。例えば、第1位相比較信号PCS1はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れるのか(lag)の有無を示し、第2位相比較信号PCS2はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進むのか(lead)の有無を示すことができる。

【0048】

第1位相比較信号PCS1及び第2位相比較信号PCS2は互いに相補的に活性化できる。即ち、第1位相比較信号PCS1及び第2位相比較信号PCS2は互いに相補的な論理レベルを有することができる。例えば、第1位相比較信号PCS1はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れる場合に活性化し、第2位相比較信号PCS2はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進んでいる場合に活性化することができる。本発明の一実施形態に係るデジタル位相周波数検出器100は基準信号FREFとフィードバック入力信号FFEEDIとの位相及び周波数差を検出してバイナリコード(binary code)で出力するバンバン(Bang-Bang)デジタル位相周波数検出器の形態で具現できる。

【0049】

図2は図1のデジタル位相周波数検出器に含まれる位相比較部の一例を示すブロック図である。

図2を参照すれば、位相比較部120は第1フリップフロップ122、第2フリップフロップ124及びラッチブロック126を含む。

【0050】

第1フリップフロップ122は基準エッジ信号RESを受信するデータ入力端及びフィードバックエッジ信号FESを受信するクロック入力端を具備し、第1比較信号CS1を出力する。第1比較信号CS1はフィードバックエッジ信号FESが活性化する時点に基準エッジ信号RESの論理レベルに対応するように同期化できる。即ち、第1フリップフロップ122はフィードバックエッジ信号FESが活性化する時点で基準エッジ信号RESの論理レベルをサンプリングして第1比較信号CS1の論理レベルを決定できる。

【0051】

第2フリップフロップ124はフィードバックエッジ信号FESを受信するデータ入力端及び基準エッジ信号RESを受信するクロック入力端を具備し、第2比較信号CS2を出力する。第2比較信号CS2は基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルに対応するように同期化できる。即ち、第2フリップフロップ124は基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルをサンプリングして第2比較信号CS2の論理レベルを決定できる。

【0052】

第1フリップフロップ122及び第2フリップフロップ124のリセット入力端は検出イネーブル信号PDENを受信することができる。検出イネーブル信号PDENはデジタル位相周波数検出器100が位相及び周波数検出動作を遂行する間は活性化し、位相及び周波数検出動作が終了してデジタル位相固定ループの出力信号の位相及び周波数が固定(lock)された場合に非活性化することができる。

【0053】

ラッチブロック126は第1比較信号CS1及び第2比較信号CS2をラッチして、互いに相補的な論理レベルを有する第1位相比較信号PCS1及び第2位相比較信号PCS2を発生する。ラッチブロック126はSRラッチの形態で具現でき、第1NANDゲート126a及び第2NANDゲート126bを含むことができる。第1NANDゲート126aは第1比較信号CS1の反転信号及び第2位相比較信号PCS2に対して、NAND演算を実行して、第1位相比較信号PCS1を発生させる。第2NANDゲート126bは第2比較信号CS2の反転信号及び第1位相比較信号PCS1に対しNAND演算を実行して第2位相比較信号PCS2を発生させる。

【0054】

一実施形態において、第1比較信号CS1及び第2比較信号CS2のうちの1つのみを活性化した場合に、第1位相比較信号PCS1及び第2位相比較信号PCS2は、第1比較信号CS1及び第2比較信号CS2に各々対応する論理レベルを有することができる。即ち、第1位相比較信号PCS1及び第2位相比較信号PCS2各々は、第1比較信号CS1及び第2比較信号CS2と実質的に同一とすることができ、第1位相比較信号PCS1はフィードバックエッジ信号FESが活性化する時点で基準エッジ信号RESの論理レベルに対応するように同期化され、第2位相比較信号PCS2は基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルに対応するように同期化できる。言い換えれば、位相比較部120はフィードバックエッジ信号FESが活性化する時点で基準エッジ信号RESの論理レベルをサンプリングして第1位相比較信号PCS1の論理レベルを決定し、基準エッジ信号RESが活性化する時点でフィードバックエッジ信号FESの論理レベルをサンプリングして第2位相比較信号PCS2の論理レベルを決定できる。

【0055】

他の実施形態で、第1比較信号CS1及び第2比較信号CS2が全部非活性化された場合に、第1位相比較信号PCS1及び第2位相比較信号PCS2は、以前周期の第1位相比較信号PCS1及び第2位相比較信号PCS2に各々対応する論理レベルを有することができる。

【0056】

再び、図1を参照すれば、リセット部130は基準エッジ信号RES及びフィードバックエッジ信号FESに基づいて検出部110を初期化させるリセット信号RSTを発生する。一実施形態において、リセット信号RSTは、基準エッジ信号RES及びフィードバックエッジ信号FESが全部活性化した場合に活性化できる。この場合、リセット信号RSTは一定の遅延時間が経過した以後に活性化することができる。即ち、リセット部130は非同期的(asynchronous)で動作することができる。リセット信号RSTが活性化した場合に、検出部110は基準信号FREF及びフィードバック入力信号FFEEDIの次の周期のエッジを検出できるように基準エッジ信号RES及びフィードバックエッジ信号FESを非活性化させることができる。このようなリセット部130の非同期的な動作を介して、デジタル位相周波数検出器100は位相検出動作時に実質的に無限の動作範囲(infinite dynamic range)を有することができ、同時に周波数検出動作も実行できる。

【0057】

上述した通り、本発明の一実施形態に係るデジタル位相周波数検出器100はデータ入力端とクロック入力端に基準エッジ信号RES及びフィードバック入力信号FESが互いに変わって入力される第1フリップフロップ122及び第2フリップフロップ124を具備する位相比較部120を含んで具現される。即ち、本発明の一実施形態に係るデジタル位相周波数検出器100は、フィードバックエッジ信号FESに基づいて基準エッジ信号RESを同期化して第1位相比較信号PCS1を発生し、基準エッジ信号RESに基づいてフィードバックエッジ信号FESを同期化して第2位相比較信号PCS2を発生することによって、簡単な構造で具現でき、向上した動作速度を有し、基準信号FREFとフィードバック入力信号FFEEDIとの間の位相及び周波数差を精密に検出することができる。

【0058】

一方、基準信号の位相とフィードバック入力信号の位相とが非常に近接した場合に、従来のデジタル位相周波数検出器は基準信号とフィードバック入力信号との位相差を検出できないこともある。即ち、従来のデジタル位相周波数検出器で、第1位相比較信号PCS1及び第2位相比較信号PCS2が全部非活性化される準安定状態(metastable state)が発生する。本発明の一実施形態に係るデジタル位相周波数検出器100は、ラッチブロック126を具備する位相比較部120を含み、基準信号FREFの位相とフィードバック入力信号FFEEDIの位相とが非常に近接した場合にも互いに相補的な論理レベルを各々有する第1位相比較信号PCS1及び第2位相比較信号PCS2を発生することによって、位相及び周波数検出動作の正確度及び安定度を向上させることができる。

【0059】

図3は図1のデジタル位相周波数検出器に含まれる検出部の一例を示すブロック図である。

図3を参照すれば、検出部110は第3フリップフロップ112及び第4フリップフロップ114を含むことができる。

【0060】

第3フリップフロップ112は基準信号FREFの上昇エッジ及び下降エッジのうちの1つに応答して活性化し、リセット信号RSTに応答して非活性化される基準エッジ信号RESを発生することができる。第4フリップフロップ114はフィードバック入力信号FFEEDIの上昇エッジ及び下降エッジのうちの1つに応答して活性化し、リセット信号RSTに応答して非活性化されるフィードバックエッジ信号FESを発生することができる。第3フリップフロップ112及び第4フリップフロップ114は、Dフリップフロップであることができる。

【0061】

一実施形態において、第3フリップフロップ112及び第4フリップフロップ114のデータ入力端は論理ハイレベルを有するように電源電圧と各々接続することができる。他の実施形態において、第3フリップフロップ112及び第4フリップフロップ114のデータ入力端は論理ローレベルを有するように接地電圧と各々接続することができる。図示はしていないが、第3フリップフロップ112及び第4フリップフロップ114のデータ入力端が接地電圧と接続する場合に、第3フリップフロップ112及び第4フリップフロップ114のデータ出力端にはインバータを各々接続することができる。

【0062】

第3フリップフロップ112及び第4フリップフロップ114のクロック入力端は、基準信号FREF及びフィードバック入力信号FFEEDIを各々受信することができる。第3フリップフロップ112及び第4フリップフロップ114のリセット入力端は、リセット信号RSTを各々受信することができる。第3フリップフロップ112及び第4フリップフロップ114の出力端は、基準エッジ信号RES及びフィードバックエッジ信号FESを各々出力することができる。一方、図示はしていないが、第3フリップフロップ112及び第4フリップフロップ114は、さらに基準エッジ信号RESの反転信号及びフィードバックエッジ信号FESの反転信号を各々出力する反転出力端を含むことができる。

【0063】

図4は図1のデジタル位相周波数検出器に含まれるリセット部の一例を示すブロック図である。

図4を参照すれば、リセット部130は少なくとも1つの論理素子を含むことができ、この少なくとも1つの論理素子はNANDゲート132、136及びインバータ134a、134b、138を含むことができる。

【0064】

少なくとも1つの論理素子132、134a、134b、136、138は、基準エッジ信号RES、フィードバックエッジ信号FES、及び検出イネイブル信号PDENに対して論理演算を実行して、リセット信号RSTを発生することができる。第1NANDゲート132は基準エッジ信号RES及びフィードバックエッジ信号FESに対しNAND演算を実行できる。第1インバータ134a及び第2インバータ134bは、入力と出力が相互接続され、第1NANDゲート132の出力信号を演算して内部信号ISを出力することができる。第2NANDゲート136は内部信号IS及び検出イネイブル信号PDENに対して、NAND演算を実行できる。第3インバータ138は第2NANDゲート138の出力信号を反転してリセット信号RSTを出力できる。

【0065】

図5及び図6は図1のデジタル位相周波数検出器の動作を示すタイミング図である。

図5はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れる場合のデジタル位相周波数検出器100の動作を示し、図6はフィードバック入力信号FFEEDIの位相が基準信号FREFの位相より進む場合のデジタル位相周波数検出器100の動作を示す。図5及び図6において、デジタル位相周波数検出器100は信号FREF、FFEEDI、RES、FES、RSTの上昇エッジに応答して動作し、信号RES、FES、RST、PCS1、PCS2は、論理ローレベルから論理ハイレベルに遷移することによって活性化されることが図示される。一方、第1比較信号CS1及び第2比較信号CS2は、第1位相比較信号PCS1及び第2位相比較信号PCS2と各々実質的に同じ論理レベルを有するので詳細な説明は省略する。

【0066】

以下においては、図5及び図6を参照して本発明の一実施形態に係るデジタル位相周波数検出器100の動作を詳細に説明する。

【0067】

図1及び図5を参照すれば、時刻t1で、基準信号FREFの論理レベルが論理ローレベルから論理ハイレベルに遷移する。検出部110は基準信号FREFの上昇エッジに応答して基準エッジ信号RESを活性化させる。時間t2で、フィードバック入力信号FFEEDIの論理レベルが論理ローレベルから論理ハイレベルに遷移する。検出部110はフィードバック入力信号FFEEDIの上昇エッジに応答してフィードバックエッジ信号FESを活性化させる。

【0068】

時刻t1で、位相比較部120は基準エッジ信号RESの上昇エッジに応答してフィードバックエッジ信号FESの論理レベルに対応するように第2位相比較信号PCS2の論理レベルを決定する。フィードバックエッジ信号FESの論理レベルは論理ローレベルであるので、第2位相比較信号PCS2は論理ローレベルを維持する。時刻t2で、位相比較部120はフィードバックエッジ信号FESの上昇エッジに応答して基準エッジ信号RESの論理レベルに対応するように第1位相比較信号PCS1の論理レベルを決定する。基準エッジ信号RESの論理レベルは論理ハイレベルであるので、第1位相比較信号PCS1は論理ローレベルから論理ハイレベルに遷移する。即ち、第1位相比較信号PCS1は論理ハイレベルを有し、第2位相比較信号PCS2は論理ローレベルを有することによって、フィードバック入力信号FFEEDIの位相が基準信号FREFの位相より遅れることになる。

【0069】

一方、リセット部130は基準エッジ信号RES及びフィードバックエッジ信号FESに応答して非同期的にリセット信号RSTを活性化させる。即ち、リセット部130は基準エッジ信号RES及びフィードバックエッジ信号FESが全部活性化した時刻t2から一定の遅延時間が経過した時刻t3で、リセット信号RSTを活性化させる。リセット信号RSTが活性化することによって、検出部110は基準エッジ信号RES及びフィードバックエッジ信号FESを非活性化させる。基準エッジ信号RES及びフィードバックエッジ信号FESが非活性化された時刻t3から一定の遅延時間が経過した時刻t4で、リセット部130はリセット信号RSTを非活性化させる。

【0070】

図1及び図6を参照すれば、時刻t5で、フィードバック入力信号FFEEDIの論理レベルが論理ローレベルから論理ハイレベルに遷移し、フィードバックエッジ信号FESはフィードバック入力信号FFEEDIの上昇エッジに応答して活性化する。時刻t6で、基準信号FREFの論理レベルが論理ローレベルから論理ハイレベルに遷移し、基準エッジ信号RESは基準信号FREFの上昇エッジに応答して活性化する。

【0071】