デジタル位相比較器及びデジタル位相同期回路

【課題】デジタル位相比較器の時間分解能を向上させつつ回路面積及び消費電力の増大を抑制する。

【解決手段】一実施形態によれば、デジタル位相比較器は、基準信号Refを初段から入力し、各段で遅延を与える遅延器列200を含む。デジタル位相比較器は、基準信号Refに応じてN相入力信号(Nは2以上の整数)のうちの信号CKV0をサンプルするサンプラ100−0と、遅延器列200の初段の出力信号に応じてN相入力信号のうち信号CKV0に比べて2π/Nだけ位相の遅れた信号CKV1をサンプルするサンプラとを含む、サンプラ群100を含む。デジタル位相比較器は、サンプラ群100のサンプル信号に基づいて、基準信号Refと信号CKV0との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路300を含む。

【解決手段】一実施形態によれば、デジタル位相比較器は、基準信号Refを初段から入力し、各段で遅延を与える遅延器列200を含む。デジタル位相比較器は、基準信号Refに応じてN相入力信号(Nは2以上の整数)のうちの信号CKV0をサンプルするサンプラ100−0と、遅延器列200の初段の出力信号に応じてN相入力信号のうち信号CKV0に比べて2π/Nだけ位相の遅れた信号CKV1をサンプルするサンプラとを含む、サンプラ群100を含む。デジタル位相比較器は、サンプラ群100のサンプル信号に基づいて、基準信号Refと信号CKV0との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路300を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、デジタル位相比較器に関する。

【背景技術】

【0002】

携帯電話機などに使用される無線通信技術では、搬送周波数帯からベースバンドへの周波数変換(ダウンコンバート)及び逆方向の周波数変換(アップコンバート)が行われる。係る周波数変換には、局部発振器が生成する局部発振信号が利用される。局部発振器は、例えばデジタル位相同期回路(DPLL;Digital Phase Locked Loop)によって実現できる。DPLLは、典型的には、デジタルコードによって発振信号の周波数が離散的に制御されるデジタル制御発振器(DCO)、発振信号を分周する分周器、(分周された)発振信号と基準信号との間の位相差を表すデジタル信号を出力するデジタル位相比較器などを含む。

【0003】

デジタル位相比較器は、通常、複数の遅延器をカスケード接続した遅延器列と、遅延器列の各段の出力信号を夫々入力する複数のサンプラとを含む。遅延器列には発振信号が入力され、複数のサンプラのクロック端子には基準信号が入力される。複数のサンプラの出力信号を解析することにより、発振信号と基準信号との間の位相差を表すデジタル信号が得られる。係る通常のデジタル位相比較器の時間分解能は、遅延器列の各段において生じる遅延時間に一致する。

【0004】

また、デジタル位相比較器の時間分解能を向上させる技術として、VDL(Vernier Delay Line)が提案されている。VDLに基づくデジタル位相比較器は、基準信号のための遅延器列を更に含む。この遅延器列には基準信号が入力され、この遅延器列の各段の出力信号が各サンプラのクロック端子に供給される。VDLに基づくデジタル位相比較器の時間分解能は、両遅延器列の一段において生じる遅延時間の差分に一致する。尚、両遅延器列の一段において生じる遅延時間は相違するように設計される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7,304,510号明細書

【非特許文献】

【0006】

【非特許文献1】P. Dudek et al, "A High-Resolution CMOS Time-to-Digital Converter Utilizing a Vernier Delay Line," IEEE J. Solid-State Circuits, vol.35, No.2, pp.240-247, Feb. 2000.

【発明の概要】

【発明が解決しようとする課題】

【0007】

前述の通常のデジタル位相比較器は、遅延器列の一段において生じる遅延時間よりも細かく位相差を検出することができない。一方、VDLに基づくデジタル位相比較器は、基準信号のための遅延器列を必要とする。遅延器列の追加は、回路面積及び消費電力の増大を招く。

【0008】

実施形態は、デジタル位相比較器の時間分解能を向上させつつ回路面積及び消費電力の増大を抑制することを目的とする。

【課題を解決するための手段】

【0009】

一実施形態によれば、デジタル位相比較器は、基準信号を初段から入力し、各段で遅延を与える遅延器列を含む。デジタル位相比較器は、基準信号に応じてN相入力信号(Nは2以上の整数)のうちの第1の信号をサンプルする第1のサンプラと、遅延器列の初段の出力信号に応じてN相入力信号のうち第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群を含む。デジタル位相比較器は、サンプラ群のサンプル信号に基づいて、基準信号と第1の信号との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路を含む。

【0010】

別の実施形態によれば、デジタル位相比較器は、基準信号をトリガとして利用するL相(Lは2以上の整数)リングオシレータを含む。デジタル位相比較器は、リングオシレータのL相発振信号のうち最も位相の進んだ信号に応じてN相入力信号(NはLの約数)のうちの第1の信号をサンプルする第1のサンプラと、L相発振信号のうち第2番目に位相の進んだ信号に応じてN相入力信号のうち第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群を含む。デジタル位相比較器は、サンプラ群のサンプル信号に基づいて、基準信号と第1の信号との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路を含む。

【0011】

別の実施形態によれば、デジタル位相比較器は、基準信号とN相入力信号(Nは2以上の整数)のうちの第1の信号との間のエッジの時間差を、N相入力信号における隣接相間の時間差に相当する第1の時間分解能によって量子化し、第1の量子化値を得る第1の時間−デジタル変換器を含む。デジタル位相比較器は、基準信号とN相入力信号のうち第1の信号に比べて2π・K/Nだけ(Kは0以上M未満の整数、MはNの整数倍)位相の遅れた第2の信号との間のエッジの時間差を、N相入力信号における隣接相間の時間差よりも小さい第2の時間分解能によって量子化し、第2の量子化値を得る第2の時間−デジタル変換器を含む。第2の時間−デジタル変換器は、環状接続されたM段の遅延器を含み、基準信号を第(K+1)段から入力し、各段で遅延を与える遅延器列を含む。第2の時間−デジタル変換器は、遅延器列の第(K+1)段の出力信号に応じて第2の信号をサンプルする第1のサンプラと、遅延器列の第(K+1)段の次段の出力信号に応じてN相入力信号のうち第2の信号に比べて2π/Nだけ位相の遅れた第3の信号をサンプルする第2のサンプラとを含む、第1のサンプラ群を含む。第2の時間−デジタル変換器は、第1のサンプラ群のサンプル信号に基づいて、第2の信号と基準信号との間のエッジの時間差を検出し、第2の量子化値を得る検出回路とを含む。

【図面の簡単な説明】

【0012】

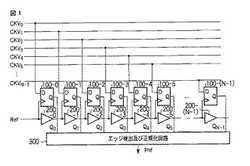

【図1】第1の実施形態に係るデジタル位相比較器を例示するブロック図。

【図2】第2の実施形態に係るデジタル位相比較器を例示するブロック図。

【図3】第3の実施形態に係るデジタル位相比較器を例示するブロック図。

【図4A】図3のデジタル位相比較器による入力信号と基準信号との間のエッジの時間差検出の説明図。

【図4B】図3のデジタル位相比較器による入力信号と基準信号との間のエッジの時間差検出の説明図。

【図5】第4の実施形態に係るデジタル位相比較器を例示するブロック図。

【図6】図5のリングオシレータにおける各段の出力信号の電圧変化を例示するタイミングチャート。

【図7】第5の実施形態に係るデジタル位相比較器を例示するブロック図。

【図8】第6の実施形態に係るデジタル位相比較器を例示するブロック図。

【図9】第7の実施形態に係るデジタル位相比較器を例示するブロック図。

【図10】第8の実施形態に係るTDCを例示するブロック図。

【図11A】図10のFTDCによる入力信号と基準信号との間のエッジの時間差検出の説明図。

【図11B】図10のFTDCによる入力信号と基準信号との間のエッジの時間差検出の説明図。

【図12】第8の実施形態に係るTDCを含むデジタル位相比較器を例示するブロック図。

【図13】図12の位相予測器の動作の説明図。

【図14】第9の実施形態に係るTDCの一部を例示するブロック図。

【図15】第9の実施形態に係るTDCを含むデジタル位相比較器を例示するブロック図。

【図16】第10の実施形態に係るデジタル位相同期回路を例示するブロック図。

【図17】第11の実施形態に係る通信装置を例示するブロック図。

【発明を実施するための形態】

【0013】

以下、図面を参照して、実施形態について説明する。尚、各実施形態において、説明済みの他の実施形態と同一または類似の要素には同一または類似の符号を付し、重複する説明を基本的に省略する。

【0014】

また、以降の説明において、立ち上がりエッジの検出は、立ち下がりエッジの検出に適宜読み替えることができる。一方、立ち下がりエッジの検出もまた、立ち上がりエッジの検出に適宜読み替えることができる。

【0015】

(第1の実施形態)

図1に示されるように、第1の実施形態に係るデジタル位相比較器は、N個(Nは2以上の整数)のサンプラ100−0,100−1,・・・,100−(N−1)と、N個の遅延器200−0,200−1,・・・,200−(N−1)と、エッジ検出及び正規化回路300とを含む。尚、本実施形態において、サンプラ100−0,100−1,・・・,100−(N−1)をまとめてサンプラ群100と称することもある。

【0016】

図1のデジタル位相比較器には、N相の入力信号CKV0,CKV1,・・・,CKVN−1と、基準信号Refとが入力される。図1のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態において、入力信号の相数=遅延器及びサンプラの数であるが、両者は相違してもよい。

【0017】

N相の入力信号CKV0,CKV1,・・・,CKVN−1は、順番に略2π/Nずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0以上N−2以下の任意の整数である)は、入力信号CKVjよりも略2π/Nだけ位相が遅れている。2π/Nの位相差は、Tv/Nの時間差に相当する。TvはN相の入力信号CKV0,CKV1,・・・,CKVN−1の周期(即ち、周波数の逆数)を表す。

【0018】

N個の遅延器200−0,200−1,・・・,200−(N−1)は、カスケード接続されて遅延器列を形成する。遅延器列の初段(遅延器200−0)には、基準信号Refが入力され、各段において略t2の遅延が夫々与えられる。例えば、遅延器200−(N−2)の出力信号は基準信号Refに比べて略(N−1)・t2だけ遅れている。尚、t2及びTv/Nは相違するように設計されるが、両者の大小関係は問われない。

【0019】

サンプラ100−0,100−1,・・・,100−(N−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ100−0のクロック端子には基準信号Refが供給され、サンプラ100−0のD端子には入力信号CKV0が供給される。サンプラ100−0は、クロック信号に応じて入力信号CKV0をサンプルし、Q端子からエッジ検出及び正規化回路300へ出力する。サンプラ100−(i+1)のクロック端子には遅延器200−iからの出力信号が供給され、サンプラ100−(i+1)のD端子には入力信号CKVi+1が供給される。ここで、iは0以上N−2以下の任意の整数である。サンプラ100−(i+1)は、クロック信号に応じて入力信号CKVi+1をサンプルし、Q端子からエッジ検出及び正規化回路300へ出力する。

【0020】

エッジ検出及び正規化回路300は、サンプラ群100からの入力信号系列Q0,Q1,・・・,QN−1に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。具体的には、エッジ検出及び正規化回路300は、入力信号系列において「1」から「0」に(或いは、「0」から「1」に)遷移する位置を解析することにより、時間差td0を検出する。

【0021】

エッジ検出及び正規化回路300は、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。例えば、エッジ検出及び正規化回路300は、入力信号系列Q0,Q1,・・・,QN−1に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち下がりエッジとの間の時間差td’0を更に検出する。エッジ検出及び正規化回路300は、入力信号系列において「0」から「1」に(または「1」から「0」に)遷移する位置を解析することにより、時間差td’0を検出する。時間差td’0と時間差td0との間の差分は、Tv/2に相当するので、これを2倍すれば周期Tvを導出できる。エッジ検出及び正規化回路300は、検出した時間差td0を周期Tvで除算(正規化)することにより、時間差td0を位相差に変換する。エッジ検出及び正規化回路300は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0022】

前述のように、サンプラ群100は、t2ずつ遅れたクロック信号に従ってTv/Nずつ遅れた入力信号をサンプルする。即ち、図1のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図1のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/Nと基準信号Refの単位遅延t2との間の差分に一致する。

【0023】

以上説明したように、第1の実施形態に係るデジタル位相比較器は、多相入力信号における信号間の位相差を遅延として利用することにより、入力信号のための遅延器列を必要とせずにVDLと同様の動作を実現する。従って、本実施形態に係るデジタル位相比較器によれば、VDLと同様の高い時間分解能を達成しつつ、入力信号のための遅延器列に相当する回路面積及び消費電力を節約できる。

【0024】

(第2の実施形態)

図2に示されるように、第2の実施形態に係るデジタル位相比較器は、8個のサンプラ110−0,110−1,・・・,110−7と、8個の遅延器210−0,210−1,・・・,210−7と、エッジ検出及び正規化回路310とを含む。

【0025】

図2のデジタル位相比較器には、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図2のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数=遅延器及びサンプラの数=「8」に設計されているが、これらをN(但し、本実施形態において入力信号の相数は偶数)に一般化しても勿論よい。更に、本実施形態において、入力信号の相数=遅延器及びサンプラの数であるが、これらは相違してもよい。

【0026】

8相の入力信号CKV0,CKV1,・・・,CKV7は、順番に略π/4ずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0以上6以下の任意の整数である)は、入力信号CKVjよりも略π/4だけ位相が遅れている。π/4の位相差は、Tv/8の時間差に相当する。Tvは8相の入力信号CKV0,CKV1,・・・,CKV7の周期を表す。更に、入力信号CKVj+4(または、入力信号CKVj−4)は、入力信号CKVjの逆相信号に相当する。尚、入力信号の相数をNに一般化する場合には、入力信号CKVjの逆相信号は入力信号CKVj+N/2(または、入力信号CKVj−N/2)である。

【0027】

遅延器210−0,210−1,・・・,210−7は、カスケード接続されて遅延器列を形成する。遅延器列の初段(遅延器210−0)には、基準信号Refが入力され、各段において略t2の遅延が夫々与えられる。例えば、遅延器210−6の出力信号は基準信号Refに比べて略7・t2だけ遅れている。尚、t2及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0028】

サンプラ110−0,110−1,・・・,110−7は、典型的には、差動構成のDフリップフロップまたは類似の素子である。サンプラ110−0のクロック端子には基準信号Refが供給され、サンプラ110−0のD端子には入力信号CKV0が供給され、サンプラ110−0のDb端子には入力信号CKV4が供給される。サンプラ110−0は、クロック信号に応じて入力信号CKV0及び入力信号CKV4(即ち、入力信号CKV0の逆相信号)の差動信号をサンプルし、Q端子からエッジ検出及び正規化回路310へ出力する。サンプラ110−(i+1)のクロック端子には遅延器210−iからの出力信号が供給され、サンプラ110−(i+1)のD端子には入力信号CKVi+1が供給され、サンプラ110−(i+1)のDb端子には入力信号CKVi+5(またはCKVi−3)が供給される。ここで、iは0以上6以下の任意の整数である。サンプラ100−(i+1)は、クロック信号に応じて入力信号CKVi+1及び入力信号CKVi+5(またはCKVi−3)の差動信号をサンプルし、Q端子からエッジ検出及び正規化回路310へ出力する。

【0029】

エッジ検出及び正規化回路310は、エッジ検出及び正規化回路300と同様に、サンプラ群110からの入力信号系列Q0,Q1,・・・,Q7に基づいて、時間差td0を検出する。更に、エッジ検出及び正規化回路310は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路310は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0030】

前述のように、サンプラ群110は、t2ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号(の差動信号)をサンプルする。即ち、図2のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図2のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延t2との間の差分に一致する。

【0031】

以上説明したように、第2の実施形態に係るデジタル位相比較器は、第1の実施形態に係るデジタル位相比較器において差動入力信号をサンプルする構成に相当する。従って、本実施形態に係るデジタル位相比較器によれば、第1の実施形態と同様の効果を得ることができると共に、差動構成による様々な利点(コモンモード除去効果など)も得ることができる。

【0032】

(第3の実施形態)

図3に示されるように、第3の実施形態に係るデジタル位相比較器は、N+M個(Nは2以上の整数、Mは1以上の整数)のサンプラ120−0,120−1,・・・,120−(N+M−1)と、N+M個の遅延器220−0,220−1,・・・,220−(N+M−1)と、エッジ検出及び正規化回路320とを含む。尚、本実施形態において、サンプラ120−0,120−1,・・・,120−(N+M−1)をまとめてサンプラ群120と称することもある。

【0033】

図3のデジタル位相比較器には、N相の入力信号CKV0,CKV1,・・・,CKVN−1と、基準信号Refとが入力される。図3のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。

【0034】

遅延器220−0,220−1,・・・,220−(N+M−1)は、カスケード接続されて遅延器列を形成する。遅延器列の初段(遅延器220−0)には、基準信号Refが入力され、各段において略t2の遅延が夫々与えられる。例えば、遅延器220−(N+M−2)の出力信号は基準信号Refに比べて略(N+M−1)・t2だけ遅れている。尚、t2及びTv/Nは相違するように設計されるが、両者の大小関係は問われない。

【0035】

サンプラ120−0,120−1,・・・,120−(N+M−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ120−0のクロック端子には基準信号Refが供給され、サンプラ120−0のD端子には入力信号CKV0が供給される。サンプラ120−0は、クロック信号に応じて入力信号CKV0をサンプルし、Q端子からエッジ検出及び正規化回路320へ出力する。

【0036】

サンプラ120−(i+1)のクロック端子には遅延器220−iからの出力信号が供給され、サンプラ120−(i+1)のD端子には入力信号CKVi+1が供給される。ここで、iは0以上(N+M−2)以下の整数である。

【0037】

但し、i+1≧Nである場合には、i+1の値は入力信号の相数を超過する。そこで、例えばサンプラ120−NのD端子には入力信号CKV0が供給される。以降、i+1=Nから2Nまで、サンプラ120−(i+1)のD端子には入力信号CKV(i+1)−Nが供給される。一般化するならば、サンプラ120−(i+1)のD端子には、入力信号CKV(i+1)modNが入力される。「xmody」は、「xのyを法とする剰余」を意味する。

【0038】

尚、例えば、入力信号CKV0は、サンプラ120−(N−1)のD端子に供給される入力信号CKVN−1に比べてTv/Nだけ遅れているとみなすことができる。故に、i+1≧Nの場合にも、サンプラのD端子に供給される入力信号が略Tv/Nずつ遅れているという関係は維持される。

【0039】

サンプラ120−(i+1)は、クロック信号に応じて入力信号CKV(i+1)modNをサンプルし、Q端子からエッジ検出及び正規化回路320へ出力する。尚、Nが偶数である場合には、サンプラ群120は、差動入力信号をサンプルしてもよい。

【0040】

エッジ検出及び正規化回路320は、エッジ検出及び正規化回路300と同様に、サンプラ群120からの入力信号系列Q0,Q1,・・・,QN+M−1に基づいて、時間差td0を検出する。更に、エッジ検出及び正規化回路320は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路320は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0041】

例えば、N=8とした場合の入力信号CKV0と基準信号Refとの間の時間差検出は、例えば図4Aまたは図4Bに示すように実現される。図4AはTv/8<t2の場合に対応し、図4BはTv/8>t2の場合に対応する。以降、便宜的に、サンプラ120−(i+1)のクロック端子に供給される遅延基準信号Refi+1との間の立ち上がりエッジと、その直前における入力信号CKV(i+1)modNの立ち上がりエッジとの間の時間差をtdi+1で表す。

【0042】

図4Aの例では、時間差tdi+1=td0−i(Tv/8−t2)である。時間差tdi+1が正値から負値に遷移する位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「1」から「0」に遷移する位置)を検出すれば、時間差td0を(Tv/8−t2)によって量子化した値を得ることができる。更に、時間差tdi+1がTv/2(または−Tv/2)を下回る位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「0」から「1」に遷移する位置)を検出すれば、時間差td’0を(Tv/8−t2)によって量子化した値を得ることができる。

【0043】

図4Bの例では、時間差tdi+1=td0+i(t2−Tv/8)である。時間差tdi+1が周期Tvを上回る位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「0」から「1」に遷移する位置)を検出すれば、(Tv−td0)を(t2−Tv/8)によって量子化した値を得ることができる。従って、係る量子化値をTvから減算することにより、時間差td0を(t2−Tv/8)によって量子化した値を得ることができる。更に、時間差tdi+1がTv/2(または3Tv/2)を上回る位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「1」から「0」に遷移する位置)を検出すれば、(Tv−td’0)を(Tv/8−t2)によって量子化した値を得ることができる。従って、係る量子化値をTvから減算することにより、時間差td’0を(t2−Tv/8)によって量子化した値を得ることができる。

【0044】

前述のように、サンプラ群120は、t2ずつ遅れたクロック信号に従ってTv/Nずつ遅れた入力信号をサンプルする。即ち、図3のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図3のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/Nと基準信号Refの単位遅延t2との間の差分に一致する。

【0045】

以上説明したように、第3の実施形態に係るデジタル位相比較器は、入力信号の相数を超える数のサンプラを許容する。従って、本実施形態に係るデジタル位相比較器によれば、より大きな(最大で時間分解能の(N+M)倍の)時間差を検出することができる。

【0046】

(第4の実施形態)

図5に示されるように、第4の実施形態に係るデジタル位相比較器は、7個のサンプラ130−0,130−1,・・・,130−6と、7個の遅延器230−0,230−1,・・・230−6と、エッジ検出及び正規化回路330とを含む。尚、本実施形態において、サンプラ130−0,130−1,・・・,130−6をまとめてサンプラ群130と称することもある。

【0047】

図5のデジタル位相比較器には、7相の入力信号CKV0,CKV1,・・・,CKV6と、基準信号Refとが入力される。図5のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数=遅延器及びサンプラの数=「7」に設計されているが、これらをN(但し、本実施形態において遅延器及びサンプラの数は奇数)に一般化しても勿論よい。更に、本実施形態において、入力信号の相数=遅延器及びサンプラの数であるが、これらは相違してもよい。

【0048】

7相の入力信号CKV0,CKV1,・・・,CKV6は、順番に略2π/7ずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0以上5以下の任意の整数である)は、入力信号CKVjよりも略2π/7だけ位相が遅れている。2π/7の位相差は、Tv/7の時間差に相当する。Tvは7相の入力信号CKV0,CKV1,・・・,CKV6の周期を表す。

【0049】

遅延器230−0,230−1,・・・,230−6は、典型的には単相インバータである。これらは、環状接続され、(7相)リングオシレータとして機能する。以降の説明では、遅延器230−0,230−1,・・・,230−6をまとめてリングオシレータ230と称することもある。

【0050】

リングオシレータ230は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器230−0から順番に発振し始める。遅延器230−(i+1)は、遅延器230−iからの入力信号を反転させて出力する。ここで、iは0以上5以下の任意の整数である。更に、信号には遅延器230−(i+1)の通過によって略TR/14の遅延が与えられる。TRはリングオシレータ230の発振周期を表す。即ち、遅延器230−(i+1)の出力信号Ri+1は、その入力信号Riに比べて略4TR/7だけ遅延する。図6は、リングオシレータ230における各段の出力信号の電圧変化を例示する。図6から明らかなように、リングオシレータ230における各段の出力信号は、R0→R2→R4→R6→R1→R3→R5の順序でTR/7ずつ遅れている。尚、TR/7及びTv/7は相違するように設計されるが、両者の大小関係は問われない。

【0051】

リングオシレータ230の発振周期は、図示しないカウンタによってカウントされる。そして、例えば、第t番目(tは1以上の所定数)の発振周期の完了時に、リングオシレータ230の発振は停止される。故に、サンプラ群130は、合計7×t点のサンプリングを行うことができる。即ち、リングオシレータ230は7×t個の遅延器であるとみなすことができるし、サンプラ群130は7×t個のサンプラであるとみなすことができる。また、第t回目の発振周期の完了を待たずに、エッジ検出及び正規化回路330が所望の時間差td0(及びtd’0)を検出したことを条件に、リングオシレータの発振が停止されてもよい。

【0052】

サンプラ130−0,130−1,・・・,130−6は、遅延器230−0,230−1,・・・,230−6の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ130−0,130−1,・・・,130−6がサンプルする信号は、クロック信号の遅延順によって決まる。即ち、最も遅延の小さいクロック信号R0を利用するサンプラ130−0は、最も遅延の小さい入力信号CKV0をサンプルする。一方、最も遅延の大きいクロック信号R5を利用するサンプラ130−5は、最も遅延の大きい入力信号CKV6をサンプルする。サンプラ群130は、サンプル信号をエッジ検出及び正規化回路330へ入力する。

【0053】

エッジ検出及び正規化回路330は、サンプラ群130からの入力信号系列Q0,Q1,・・・,Q6に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。具体的には、入力信号系列Q0,Q1,・・・,Q6を、遅延順に従ってQ0→Q2→Q4→Q6→Q1→Q3→Q5の順序にソートすれば、エッジ検出及び正規化回路300と同様の手法が適用できる。尚、tが2以上であるならば、エッジ検出及び正規化回路330は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路330は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路330は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0054】

前述のように、サンプラ群130は、TR/7ずつ遅れたクロック信号に従ってTv/7ずつ遅れた入力信号をサンプルする。即ち、図5のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図5のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/7と基準信号Refの単位遅延TR/7との間の差分に一致する。

【0055】

以上説明したように、第4の実施形態に係るデジタル位相比較器は、リングオシレータを最大t周期に亘って発振させることにより遅延クロック信号を生成する。従って、本実施形態に係るデジタル位相比較器によれば、リングオシレータの相数×t個のサンプラ及び遅延器を用意する場合と同様の効果を得ることができる。

【0056】

(第5の実施形態)

図7に示されるように、第5の実施形態に係るデジタル位相比較器は、9個のサンプラ140−0,140−1,・・・,140−8と、9個の遅延器240−0,240−1,・・・,240−8と、エッジ検出及び正規化回路340とを含む。尚、本実施形態において、サンプラ140−0,140−1,・・・,140−8をまとめてサンプラ群140と称することもある。

【0057】

図7のデジタル位相比較器には、3相の入力信号CKV0,CKV1,CKV2と、基準信号Refとが入力される。図7のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数×3=遅延器及びサンプラの数=「9」に設計されているが、入力信号の相数をNに一般化し、遅延器及びサンプラの数をNの奇数倍に一般化しても勿論よい。

【0058】

3相の入力信号CKV0,CKV1,CKV2は、順番に略2π/3ずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0または1である)は、入力信号CKVjよりも略2π/3だけ位相が遅れている。2π/3の位相差は、Tv/3の時間差に相当する。Tvは3相の入力信号CKV0,CKV1,CKV2の周期を表す。

【0059】

遅延器240−0,240−1,・・・,240−8は、典型的には単相インバータである。これらは、環状接続され、9相リングオシレータとして機能する。以降の説明では、遅延器240−0,240−1,・・・,240−8をまとめてリングオシレータ240と称することもある。

【0060】

リングオシレータ240は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器240−0から順番に発振し始める。遅延器240−(i+1)は、遅延器240−iからの入力信号を反転させて出力する。ここで、iは0以上7以下の整数である。更に、信号には遅延器240−(i+1)の通過によって略TR/18の遅延が与えられる。TRはリングオシレータ240の発振周期を表す。即ち、遅延器240−(i+1)の出力信号Ri+1は、その入力信号Riに比べて略5TR/9だけ遅延する。従って、リングオシレータ240における各段の出力信号は、R0→R2→R4→R6→R8→R1→R3→R5→R7の順序でTR/9ずつ遅れている。尚、TR/9及びTv/3は相違するように設計されるが、両者の大小関係は問われない。

【0061】

リングオシレータ240もまた、リングオシレータ230と同様に、最大t周期に亘って発振する。故に、サンプラ140群は、合計9×t点のサンプリングを行うことができる。即ち、リングオシレータ240は9×t個の遅延器であるとみなすことができるし、サンプラ140群は9×t個のサンプラであるとみなすことができる。

【0062】

サンプラ140−0,140−1,・・・,140−8は、遅延器240−0,240−1,・・・,240−8の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ140−0,140−1,・・・,140−8がサンプルする信号は、クロック信号の遅延順によって決まる。即ち、最も遅延の小さいクロック信号R0を利用するサンプラ140−0は、最も遅延の小さい入力信号CKV0をサンプルする。2番目に遅延の小さいクロック信号R2を利用するサンプラ140−2は、2番目に遅延の小さい入力信号CKV1をサンプルする。

【0063】

本実施形態では、入力信号の相数がサンプラの数に比べて小さい。しかしながら、入力信号はCKV0→CKV1→CKV2→CKV0・・・の順序で遅延しているので、この順序によってサンプラ140−0,140−1,・・・,140−8がサンプルする信号を決定できる。例えば、第4番目に遅延の小さいクロック信号R6を利用するサンプラ140−6は、第4番目に遅延の小さい入力信号CKV0をサンプルする。サンプラ群140は、サンプル信号をエッジ検出及び正規化回路340へ入力する。

【0064】

エッジ検出及び正規化回路340は、サンプラ群140からの入力信号系列Q0,Q1,・・・,Q8に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。具体的には、入力信号系列Q0,Q1,・・・,Q8を、遅延順に従ってQ0→Q2→Q4→Q6→Q8→Q1→Q3→Q5→Q7の順序にソートすれば、エッジ検出及び正規化回路300と同様の手法が適用できる。尚、tが2以上であるならば、エッジ検出及び正規化回路340は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路340は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路330は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0065】

前述のように、サンプラ140群は、TR/9ずつ遅れたクロック信号に従ってTv/3ずつ遅れた入力信号をサンプルする。即ち、図7のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図7のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/3と基準信号Refの単位遅延TR/9との間の差分に一致する。

【0066】

以上説明したように、第5の実施形態に係るデジタル位相比較器は、入力信号の相数に比べて多くのサンプラ及び遅延器を利用する。従って、本実施形態に係るデジタル位相比較器によれば、サンプラ及び遅延器を入力信号の周波数に比べて低速に(低い周波数で)動作させることができる。

【0067】

(第6の実施形態)

図8に示されるように、第6の実施形態に係るデジタル位相比較器は、8個のサンプラ150−0,150−1,・・・,150−7と、4個の遅延器250−0,250−1,・・・250−3と、エッジ検出及び正規化回路350とを含む。尚、本実施形態において、サンプラ150−0,150−1,・・・,150−7をまとめてサンプラ群150と称することもある。

【0068】

図8のデジタル位相比較器には、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図8のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数=遅延器の数×2=サンプラの数=「8」に設計されているが、これらをNに一般化しても勿論よい。更に、本実施形態において、入力信号の相数=遅延器の数×2=サンプラの数であるが、入力信号の相数と遅延器の数×2及びサンプラの数とは相違してもよい。

【0069】

4個の遅延器250−0,250−1,・・・,250−3は、典型的には差動増幅器である。これらは、環状接続され、(8相)差動リングオシレータとして機能する。以降の説明では、4個の遅延器250−0,250−1,・・・,250−3をまとめて差動リングオシレータ250と称することもある。

【0070】

差動リングオシレータ250は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器250−0から順番に発振し始める。遅延器250−(i+1)は、遅延器250−iからの差動入力信号Ri及びRi+4に略TR/8の遅延を与え、差動出力信号Ri+1及びRi+5を次段に供給する。ここで、iは0以上2以下の整数である。TRは差動リングオシレータ250の発振周期を表す。即ち、遅延器250−(i+1)の差動出力信号Ri+1及びRi+5は、その差動入力信号Ri及びRi+4に比べて略TR/8だけ遅延する。従って、差動リングオシレータ250における各段の出力信号は、R0→R1→,・・・,→R7の順序でTR/8ずつ遅れている。尚、TR/8及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0071】

差動リングオシレータ250もまた、リングオシレータ230と同様に、最大t周期に亘って発振する。故に、サンプラ群150は、合計8×t点のサンプリングを行うことができる。即ち、差動リングオシレータ250は8×t個の遅延器であるとみなすことができるし、サンプラ群150は8×t個のサンプラであるとみなすことができる。

【0072】

サンプラ150−0,150−1,・・・,150−7は、遅延器250−0,250−1,・・・,250−3の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ150−hは、Rhをクロック信号として利用し、入力信号CKVhをサンプルする。本実施形態において、hは0以上7以下の整数である。サンプラ群150は、サンプル信号をエッジ検出及び正規化回路350へ入力する。尚、サンプラ群150は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出及び正規化回路350は、エッジ検出及び正規化回路300と同様に、サンプラ群150からの入力信号系列Q0,Q1,・・・,Q7に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。尚、tが2以上であるならば、エッジ検出及び正規化回路350は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路350は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路350は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0073】

前述のように、サンプラ群150は、TR/8ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号をサンプルする。即ち、図8のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図8のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延TR/8との間の差分に一致する。

【0074】

以上説明したように、第6の実施形態に係るデジタル位相比較器は、差動リングオシレータを最大t周期に亘って発振させることにより遅延クロック信号を生成する。従って、本実施形態に係るデジタル位相比較器によれば、差動リングオシレータの相数×t個のサンプラ及び遅延器を用意する場合と同様の効果を得ることができる。

【0075】

(第7の実施形態)

図9に示されるように、第7の実施形態に係るデジタル位相比較器は、16個のサンプラ160−0,160−1,・・・,160−15と、8個の遅延器260−0,260−1,・・・,260−7と、エッジ検出及び正規化回路360とを含む。尚、本実施形態において、サンプラ160−0,160−1,・・・,160−15をまとめてサンプラ群160と称することもある。

【0076】

図9のデジタル位相比較器には、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図9のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数×2=遅延器の数×2=サンプラの数=「16」に設計されているが、入力信号の相数をNに一般化し、遅延器の数×2及びサンプラの数をN/2の整数倍に一般化しても勿論よい。

【0077】

遅延器260−0,260−1,・・・,260−7は、典型的には差動増幅器である。これらは、環状接続され、(16相)差動リングオシレータとして機能する。以降の説明では、遅延器260−0,260−1,・・・,260−7をまとめて差動リングオシレータ260と称することもある。

【0078】

差動リングオシレータ260は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器260−0から順番に発振し始める。遅延器260−(i+1)は、遅延器260−iからの差動入力信号Ri及びRi+8に略TR/16の遅延を与え、差動出力信号Ri+1及びRi+9を次段に供給する。ここで、iは0以上6以下の整数である。TRは差動リングオシレータ260の発振周期を表す。即ち、遅延器260−(i+1)の差動出力信号Ri+1及びRi+9は、その差動入力信号Ri及びRi+8に比べて略TR/16だけ遅延する。即ち、差動リングオシレータ260における各段の出力信号は、R0→R1→,・・・,→R15の順序でTR/16ずつ遅れている。尚、TR/16及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0079】

差動リングオシレータ260もまた、リングオシレータ230と同様に、最大t周期に亘って発振する。故に、サンプラ群160は、合計16×t点のサンプリングを行うことができる。即ち、差動リングオシレータ260は16×t個の遅延器であるとみなすことができるし、サンプラ群160は16×t個のサンプラであるとみなすことができる。

【0080】

サンプラ160−0,160−1,・・・,160−15は、遅延器260−0,260−1,・・・,260−8の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ160−hは、Rhをクロック信号として利用し、入力信号CKVhをサンプルする。本実施形態においてhは、0以上15以下の整数である。

【0081】

本実施形態では、入力信号の相数が、サンプラの数及び遅延器の数×2に比べて小さい。しかしながら、入力信号はCKV0→CKV1→,・・・,→CKV7→CKV0・・・の順序で遅延しているので、この順序によってサンプラ160−0,160−1,・・・,160−15がサンプルする信号を決定できる。例えば、第9番目に遅延の小さいクロック信号R8を利用するサンプラ160−8は、第9番目に遅延の小さい入力信号CKV0をサンプルする。一般化するならば、サンプラ160−hは、入力信号CKVhmod8をサンプルする。サンプラ群160は、サンプル信号をエッジ検出及び正規化回路360へ入力する。尚、サンプラ群160は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出及び正規化回路360は、エッジ検出及び正規化回路300と同様に、サンプラ群160からの入力信号系列Q0,Q1,・・・,Q15に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。尚、tが2以上であるならば、エッジ検出及び正規化回路360は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路360は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路360は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0082】

前述のように、サンプラ群160は、TR/16ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号をサンプルする。即ち、図9のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図9のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延TR/16との間の差分に一致する。

【0083】

以上説明したように、第7の実施形態に係るデジタル位相比較器は、入力信号の相数に比べて多くのサンプラと、サンプラの半数の遅延器を含む差動リングオシレータとを利用する。従って、本実施形態に係るデジタル位相比較器によれば、サンプラ及び遅延器を入力信号の周波数に比べて低速に(低い周波数で)動作させることができる。

【0084】

(第8の実施形態)

第8の実施形態は、デジタル位相比較器に含まれる時間−デジタル変換器(TDC)に関する。一般に、TDCは、入力信号と基準信号との間のエッジの時間差をデジタル値に変換する。図10に示されるように、本実施形態に係るTDCは、時間分解能が相対的に粗いCTDC410と、時間分解能が相対的に細かいFTDC440とを含む。図10のTDCには、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図10のTDCは、任意の入力信号(例えば、CKV0)と基準信号Refとの間の時間差を表すデジタル信号DTriseCと、当該任意の入力信号と同一または異なる位相の入力信号と基準信号Refとの間の時間差を表すデジタル信号DTriseFとを出力する。

【0085】

CTDC410は、8個のサンプラ420−0,420−1,・・・,420−7と、エッジ検出回路430とを含む。尚、本実施形態では、簡単化のために、入力信号の相数=サンプラ420の数=「8」に設計されているが、両者をNに一般化しても勿論よい。更に、本実施形態において、入力信号の相数=サンプラ420の数であるが、両者は相違してもよい。

【0086】

サンプラ420−0,420−1,・・・,420−7は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ420−0,420−1,・・・,420−7のクロック端子には基準信号Refが共通に供給され、サンプラ420−0,420−1,・・・,420−7のD端子には入力信号CKV0,CKV1,・・・,CKV7が夫々供給される。即ち、サンプラ420−0,420−1,・・・,420−7は、基準信号Refに応じて入力信号CKV0,CKV1,・・・,CKV7を夫々サンプルし、Q端子からエッジ検出回路430へ出力する。尚、サンプラ420−0,420−1,・・・,420−7は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出回路430は、サンプラ420−0,420−1,・・・,420−7からの入力信号系列Qc0,Qc1,・・・,Qc7に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差を検出し、検出した時間差を表すデジタル信号DTriseCを出力する。具体的には、エッジ検出回路430は、エッジ検出及び正規化回路300と同様に時間差を検出すればよい。CTDC410の時間分解能は、Tv/8に一致する。

【0087】

FTDC440は、M個のサンプラ450−0,450−1,・・・,450−(M−1)と、M個の遅延器460−0,460−1,・・・,460−(M−1)と、エッジ検出回路470とを含む。本実施形態において、Mは8の整数倍である。尚、入力信号の相数をNに一般化するならば、MはNの整数倍である。また、本実施形態において、サンプラ450−0,450−1,・・・,450−(M−1)をまとめてサンプラ群450と称することもある。

【0088】

M個の遅延器460−0,460−1,・・・,460−(M−1)は、典型的には、セレクタである。M個の遅延器460−0,460−1,・・・,460−(M−1)は、選択制御信号S0,S1,・・・,SM−1に夫々従って、2入力信号の一方を選択し、選択信号に略t2の遅延を与えて次段に供給する。以降の説明では、簡単化のために、遅延器460−mは、選択制御信号Smが「0」であれば前段の出力信号Rm−1(但し、m=0であればRM−1)を選択し、選択制御信号Smが「1」であれば基準信号Refを選択することにする。本実施形態において、mは0以上M−1以下の任意の整数である。

【0089】

選択制御信号S0,S1,・・・,SM−1のうち1つは「1」に設定され、残りのM−1個は「0」に設定される。以降の説明では、SK=1とする(Kは、0以上M−1以下の整数である)。即ち、遅延器460−(M−1)の出力信号RM−1は、遅延器460−Kの出力信号RKに比べて略(M−K−1)・t2だけ遅れている。尚、以降の説明において、基準信号Refと、遅延器460−Kの出力信号RKとの間の時間差は簡単化のために無視する。また、遅延器460−(K−1)の出力信号RK−1(但し、K=0であれば、遅延器460−(M−1)の出力信号RM−1)は、遅延器460−Kの出力信号RKに比べて略(M−1)・t2だけ遅れている。尚、t2及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0090】

サンプラ450−0,450−1,・・・,450−(M−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ450−mのクロック端子には遅延器460−mの出力信号Rmが供給される。サンプラ450−mのD端子には入力信号CKVmmod8が供給される。即ち、サンプラ450−mは、遅延器460−mの出力信号Rmに応じて入力信号CKVmmod8をサンプルし、Q端子からエッジ検出回路470へ出力する。尚、サンプラ群450は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出回路470は、サンプラ群450からの入力信号系列Qf0,Qf1,・・・,Qf(M−1)に基づいて、基準信号Refの立ち上がりエッジと、その直前における所定の入力信号の立ち上がりエッジとの間の時間差を検出し、検出した時間差を表すデジタル信号DTriseFを出力する。所定の入力信号とは、入力信号CKV0からK・Tv/8だけ遅れた信号であり、換言すれば、サンプラ450−Kがサンプルする入力信号CKVKmod8である。

【0091】

K=1である場合の時間差検出を図11Aに例示し、K=3である場合の時間差検出を図11Bに例示する。尚、図11A及び図11Bの例では、いずれもTv/8>t2である。

【0092】

図11Aの例では、エッジ検出回路470は、入力信号系列において「1」から「0」に遷移する位置(R10とR11との間)を解析することにより、時間差td0を検出する。この時間差td0は、入力信号CKV0の立ち上がりエッジと基準信号Refの立ち上がりエッジとの間の時間差を表す。

【0093】

図11Bの例では、エッジ検出回路470は、入力信号系列において「1」から「0」に遷移する位置(R5とR6との間)を解析することにより、時間差td3を検出する。この時間差td3は、入力信号CKV3の立ち上がりエッジと基準信号Refの立ち上がりエッジとの間の時間差を表す。

【0094】

図11A及び図11Bから明らかなように、Kの値次第で、エッジ検出回路470が検出する時間差は異なる。即ち、Kに適切な値が与えられれば、エッジ検出回路470が時間差tdKを検出するために必要な入力信号系列の数を抑えることができる。換言すれば、エッジ検出回路470は、時間差td0の大きさに関わらず、より小さい時間差tdKを検出すればよい。故に、図10のTDCによれば時間差td0を検出する構成に比べて時間差検出に必要な遅延器460及びサンプラ450の数を抑えることができる。尚、時間差td0と時間差tdKとの間の差分K・Tv/8は既知の値なので、時間差tdKに差分K・Tv/8を加算すれば時間差td0を復元できる。

【0095】

前述のように、サンプラ群450は、t2ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号をサンプルする。即ち、図10のTDCは、VDLと同様の動作を実現する。故に、図10のTDCの時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延t2との間の差分に一致する。

【0096】

本実施形態に係るTDCを含むデジタル位相比較器を図12に例示する。図12のデジタル位相比較器は、本実施形態に係るTDC400と、乗算器501と、位相予測器502と、周期計算回路503と、乗算器504と、補正器510とを含む。

【0097】

乗算器501は、CTDC410の時間分解能(=Tv/N)によって入力信号の周期Tvを量子化した値TvC(=N)の逆数を、CTDC410の出力信号DTriseCに乗算する。即ち、乗算器501は、CTDC410の出力信号DTriseCに入力信号の相数の逆数を乗算し、時間差を位相差に変換する。尚、本実施形態では、入力信号の相数=「8」の場合を例示しているが、入力信号の相数=Nに一般化できる。乗算器501の出力信号PHfCは、外部(例えば、図示しないデジタル位相同期回路中の他の要素)に出力される。更に、乗算器501の出力信号PHfCは、位相予測器502にも入力される。

【0098】

位相予測器502は、乗算器501の出力信号PHfCと、外部からの周波数設定コードFCWとに基づいて、基準信号Refの次の周期における入力信号(例えば、CKV0)の位相を予測する。位相予測器502は、予測結果に応じてSK=1を与えるKの値を決定する。

【0099】

一例として、図12のデジタル位相比較器を含む図示しないデジタル位相同期回路がロックしていると仮定する。係る条件下では、図13に示されるように、入力信号の位相が基準信号Refの周期Tref毎にFCWだけ増加する。即ち、位相予測器502は、乗算器501の出力信号PHfC及び周波数設定コードFCWの和の小数部を取り出すことにより、基準信号Refの次の周期における入力信号の位相を予測できる。

【0100】

FTDC440の出力信号DTriseFが表す位相差を時間差に変換するためには、FTDC440の時間分解能(=|Tv/N−t2|)によって入力信号の周期Tvを量子化した値TvFが必要となる。しかしながら、FTDC440の入力範囲は狭いので、量子化値TvFを直接導出することはできない。

【0101】

そこで、周期計算回路503は、以下のように量子化値TvFを計算する。FDCT440の出力信号DTriseFは時間差tdKをFDCT440の時間分解能によって量子化した値を表し、CDTC410の出力信号DTriseCは時間差td0をCDTC410の時間分解能によって量子化した値を表す。ここで、DTriseCからKを減算した値は、DTriseFを同じ値を表す。即ち、DTriseF/(DTriseC−K)は、CTDC410による量子化値をFTDC440による量子化値に変換するための比率に相当する。この比率をTvC(=N)に乗算すれば、TvF(=N・DTriseF/(DTriseC−K))を導出できる。周期計算回路503は、TvFの逆数を乗算器504に入力する。乗算器504は、FTDC440の出力信号DTriseFに周期計算回路503からのTvFの逆数を乗算し、時間差を位相差に変換する。乗算器504は、位相差を表す信号PHfF0を補正器510に入力する。

【0102】

信号PHfF0は、CKVKmod8と基準信号Refとの間の位相差を表している。補正器510は、信号PHfF0を補正し、CKV0と基準信号Refとの間の位相差を表す信号PHfFを出力する。補正器510は、加算器511と乗算器512とを含む。乗算器512は、位相予測器502からのKに入力信号の相数の逆数を乗算し、入力信号CKV0と入力信号CKVKmod8との間の位相シフト量を計算する。加算器511は、乗算器512による乗算結果を信号PHfF0に加算し、CKV0と基準信号Refとの間の位相差を復元する。

【0103】

以上説明したように、第8の実施形態に係るTDCは、入力信号の1つを選択し、選択した入力信号と基準信号との間のエッジの時間差を検出する。従って、本実施形態に係るTDCによれば、基準信号との位相差の小さい入力信号を選択することで時間差検出に必要な遅延器及びサンプラの数を抑えることができる。

【0104】

(第9の実施形態)

第9の実施形態に係るTDCは、図10のTDCにおけるFTDC440を、図14に示されるFTDC640に置き換えた構成に相当する。FTDC640は、M個のサンプラ450−0,450−1,・・・,450−(M−1)と、M個のサンプラ680−0,680−1,・・・,680−(M−1)と、M個の遅延器460−0,460−1,・・・,460−(M−1)と、エッジ検出回路670とを含む。尚、本実施形態において、サンプラ450−0,450−1,・・・,450−(M−1)をまとめて第1のサンプラ群450と称することもあれば、サンプラ680−0,680−1,・・・,680−(M−1)をまとめて第2のサンプラ群680と称することもある。

【0105】

サンプラ680−0,680−1,・・・,680−(M−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ680−mのクロック端子には遅延器460−mの出力信号Rmが供給される。サンプラ680−mのD端子には入力信号CKV(m+1)mod8が供給される。即ち、サンプラ680−mは、サンプラ450−mと共通のクロック信号に従って、サンプラ450−mよりも1相だけ遅れた入力信号をサンプルし、Q端子からエッジ検出回路670へ出力する。尚、第2のサンプラ群680は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出回路670は、エッジ検出回路470と同様に、第1のサンプラ群450からの入力信号系列Qf0,Qf1,・・・,Qf(M−1)に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKVKmod8の立ち上がりエッジとの間の時間差tdKを検出し、検出した時間差tdKを表すデジタル信号DTriseFを出力する。

【0106】

更に、エッジ検出回路670は、第2のサンプラ群680からの入力信号系列Q’f0,Q’f1,・・・,Q’f(M−1)とに基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV(K+1)mod8の立ち上がりエッジとの間の時間差tdK+1を検出する。そして、エッジ検出回路670は、時間差tdK+1と時間差tdKとの間の差分を表すデジタル信号DivNTvを出力する。デジタル信号DivNTvは、入力信号CKVKmod8及び入力信号CKV(K+1)mod8の立ち上がりエッジの時間差を、FTDC640の時間分解能(|Tv/8−t2|)によって量子化した値である。即ち、デジタル信号DivNTvに入力信号の相数(この例では、「8」)を乗算すれば、TvFを導出できる。

【0107】

本実施形態に係るTDCを含むデジタル位相比較器を図15に例示する。図15のデジタル位相比較器は、本実施形態に係るTDC600と、乗算器501と、位相予測器502と、乗算器721と、逆数変換器722と、乗算器504と、補正器510とを含む。

【0108】

乗算器721は、FTDC640の出力信号DiVNTvに入力信号の相数を乗算し、TvFを導出する。逆数変換器722は、乗算器からのTvFの逆数を乗算器504に供給する。

【0109】

以上説明したように、第9の実施形態に係るTDCは、入力信号における隣接相間の時間差をFTDCの時間分解能によって量子化した値を更に検出する。従って、本実施形態に係るTDCによれば、入力信号の周期をFTDCの時間分解能によって量子化した値を容易に(除算処理を必要とせずに)導出できる。

【0110】

(第10の実施形態)

図16に示されるように、第10の実施形態に係るデジタル位相同期回路は、前述の各実施形態に係るデジタル位相比較器500を含む。より具体的には、図16のデジタル位相同期回路は、デジタル位相比較器500、デジタル制御発振器801、分周器802、カウンタ803、加算器804、微分器805、比較器806、積分器807、ループフィルタ808、利得正規化器809、デルタシグマ変調器810を含む。

【0111】

デジタル制御発振器801は、利得正規化回路809及びデルタシグマ変調器810によって発振信号の周波数が離散的に制御される。デジタル制御発振器801の発振信号は出力信号として取り出されると共に、分周器802に入力される。

【0112】

分周器802は、デジタル制御発振器801からの差動発振信号を4分周し、8相信号CKV0,・・・,CKV7を得る。8相信号CKV0,・・・,CKV7は、デジタル位相比較器500に入力される。更に、8相信号CKV0,・・・,CKV7のうちの任意の1つ(例えば、CKV0)はカウンタ803にも入力される。

【0113】

デジタル位相比較器500は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。カウンタ803は、基準信号Refをクロックとして利用し、入力信号(例えば、CKV0)の周期数をカウントする。

【0114】

加算器804は、カウンタ803の出力信号と、デジタル位相比較器500の出力信号とを加算し、入力信号CKV0の位相情報を得る。尚、カウンタ803の出力信号は入力信号CKV0の位相情報の整数部を表し、デジタル位相比較器500の出力信号は入力信号CKV0の位相情報の小数部を表す。

【0115】

微分器805は、加算器804からの入力信号CKV0の位相情報を微分し、入力信号CKV0の周波数情報を得る。比較器806は、所望の周波数設定コードFCWと、微分器805からの入力信号CKV0の周波数情報とを比較し、入力信号CKV0の周波数誤差情報を検出する。

【0116】

積分器806は、比較器806からの入力信号CKV0の周波数誤差情報を積分し、入力信号CKV0の位相誤差情報を得る。ループフィルタ808は、積分器806からの位相誤差情報をフィルタリングする。

【0117】

利得正規化回路809は、ループフィルタ808の出力信号に基づいてループ利得を調整するための利得調整信号を生成する。デルタシグマ変調器810は、利得調整信号の下位ビットにデルタシグマ変調を行い、デジタル制御発振器801の制御信号を生成する。

【0118】

以上説明したように、第10の実施形態に係るデジタル位相同期回路は、前述の各実施形態に係るデジタル位相比較器を含む。従って、本実施形態に係るデジタル位相同期回路によれば、前述の各実施形態と同様の効果が得られる。

【0119】

尚、図16のデジタル位相同期回路は例示であり、本実施形態に係るデジタル位相同期回路は図16に示されていない要素を含んでもよいし、図16に示された要素の一部を含まなくてもよい。

【0120】

(第11の実施形態)

図17に示されるように、第11の実施形態に係る通信装置は、第10の実施形態に係るデジタル位相同期回路800を含む。より具体的には、図17の通信装置は、デジタル位相同期回路800、アンテナ901、スイッチ902、LNA903、ミキサ904、ABB(アナログベースバンド回路)905、ADC(アナログ−デジタル変換器)906、デジタル信号処理部910、DAC(デジタル−アナログ変換器)911、ABB912、ミキサ913及びPA(電力増幅器)914を含む。

【0121】

アンテナ901によって受信された搬送周波数帯の受信信号は、スイッチ902を介してLNA903に供給される。LNA903は、入力信号の信号レベルを増幅し、ミキサ904に供給する。ミキサ904は、デジタル位相同期回路800(即ち、局部発振器)によって生成された局部発振信号を、LNA903の出力信号に乗算し、ベースバンド受信信号を得る(ダウンコンバート)。

【0122】

ABB905は、ミキサ904からのベースバンド受信信号にフィルタリング処理などの各種ベースバンド処理を行い、ADC906に入力する。ADC906は、ABB905の出力信号をデジタルドメインに変換し、デジタル信号処理部910に入力する。デジタル信号処理部910は、受信データ及び送信データに対する各種処理を行う。

【0123】

DAC911は、デジタル信号処理部910からの入力信号をアナログドメインに変換し、ABB912に入力する。ABB912は、DAC911からのアナログ信号に増幅、フィルタリング処理などの各種ベースバンド処理を行い、ミキサ913に入力する。

【0124】

ミキサ913は、デジタル位相同期回路800によって生成された局部発振信号を、ABB912の出力信号に乗算し、搬送周波数帯の送信信号を得る(アップコンバート)。PA914は、ミキサ913からの搬送周波数帯の送信信号の電力を増幅し、スイッチ902を介してアンテナ901に供給する。アンテナ901は、供給された送信信号を空間に放射する。

【0125】

尚、図17の通信装置は例示であり、本実施形態に係る通信装置は図17に示されていない要素を含んでもよいし、図17に示された要素の一部を含まなくてもよい。また、図17の通信装置は、送信及び受信の両方が可能である。しかしながら、第10の実施形態に係るデジタル位相同期回路は、送信を専ら行う通信装置(即ち、送信機)及び受信を専ら行う通信装置(即ち、受信機)のいずれにも適用可能である。

【0126】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0127】

100,110,120,130,140,150,160・・・サンプラ

200,210,220,230,240,250,260・・・遅延器

300,310,320,330,340,350,360・・・エッジ検出及び正規化回路

400,600・・・TDC

410・・・CTDC

420・・・サンプラ

430・・・エッジ検出回路

440,640・・・FTDC

450・・・サンプラ

460・・・遅延器

470,670・・・エッジ検出回路

500・・・デジタル位相比較器

501・・・乗算器

502・・・位相予測器

503・・・周期計算回路

504・・・乗算器

510・・・補正器

511・・・乗算器

512・・・乗算器

680・・・サンプラ

721・・・乗算器

722・・・逆数変換器

800・・・デジタル位相同期回路

801・・・デジタル制御発振器

802・・・分周器

803・・・カウンタ

804・・・加算器

805・・・微分器

806・・・比較器

807・・・積分器

808・・・ループフィルタ

809・・・利得正規化器

810・・・デルタシグマ変調器

901・・・アンテナ

902・・・スイッチ

903・・・LNA

904・・・ミキサ

905・・・アナログベースバンド回路

906・・・ADC

910・・・デジタル信号処理部

911・・・DAC

912・・・アナログベースバンド回路

913・・・ミキサ

914・・・PA

【技術分野】

【0001】

本発明の実施形態は、デジタル位相比較器に関する。

【背景技術】

【0002】

携帯電話機などに使用される無線通信技術では、搬送周波数帯からベースバンドへの周波数変換(ダウンコンバート)及び逆方向の周波数変換(アップコンバート)が行われる。係る周波数変換には、局部発振器が生成する局部発振信号が利用される。局部発振器は、例えばデジタル位相同期回路(DPLL;Digital Phase Locked Loop)によって実現できる。DPLLは、典型的には、デジタルコードによって発振信号の周波数が離散的に制御されるデジタル制御発振器(DCO)、発振信号を分周する分周器、(分周された)発振信号と基準信号との間の位相差を表すデジタル信号を出力するデジタル位相比較器などを含む。

【0003】

デジタル位相比較器は、通常、複数の遅延器をカスケード接続した遅延器列と、遅延器列の各段の出力信号を夫々入力する複数のサンプラとを含む。遅延器列には発振信号が入力され、複数のサンプラのクロック端子には基準信号が入力される。複数のサンプラの出力信号を解析することにより、発振信号と基準信号との間の位相差を表すデジタル信号が得られる。係る通常のデジタル位相比較器の時間分解能は、遅延器列の各段において生じる遅延時間に一致する。

【0004】

また、デジタル位相比較器の時間分解能を向上させる技術として、VDL(Vernier Delay Line)が提案されている。VDLに基づくデジタル位相比較器は、基準信号のための遅延器列を更に含む。この遅延器列には基準信号が入力され、この遅延器列の各段の出力信号が各サンプラのクロック端子に供給される。VDLに基づくデジタル位相比較器の時間分解能は、両遅延器列の一段において生じる遅延時間の差分に一致する。尚、両遅延器列の一段において生じる遅延時間は相違するように設計される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7,304,510号明細書

【非特許文献】

【0006】

【非特許文献1】P. Dudek et al, "A High-Resolution CMOS Time-to-Digital Converter Utilizing a Vernier Delay Line," IEEE J. Solid-State Circuits, vol.35, No.2, pp.240-247, Feb. 2000.

【発明の概要】

【発明が解決しようとする課題】

【0007】

前述の通常のデジタル位相比較器は、遅延器列の一段において生じる遅延時間よりも細かく位相差を検出することができない。一方、VDLに基づくデジタル位相比較器は、基準信号のための遅延器列を必要とする。遅延器列の追加は、回路面積及び消費電力の増大を招く。

【0008】

実施形態は、デジタル位相比較器の時間分解能を向上させつつ回路面積及び消費電力の増大を抑制することを目的とする。

【課題を解決するための手段】

【0009】

一実施形態によれば、デジタル位相比較器は、基準信号を初段から入力し、各段で遅延を与える遅延器列を含む。デジタル位相比較器は、基準信号に応じてN相入力信号(Nは2以上の整数)のうちの第1の信号をサンプルする第1のサンプラと、遅延器列の初段の出力信号に応じてN相入力信号のうち第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群を含む。デジタル位相比較器は、サンプラ群のサンプル信号に基づいて、基準信号と第1の信号との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路を含む。

【0010】

別の実施形態によれば、デジタル位相比較器は、基準信号をトリガとして利用するL相(Lは2以上の整数)リングオシレータを含む。デジタル位相比較器は、リングオシレータのL相発振信号のうち最も位相の進んだ信号に応じてN相入力信号(NはLの約数)のうちの第1の信号をサンプルする第1のサンプラと、L相発振信号のうち第2番目に位相の進んだ信号に応じてN相入力信号のうち第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群を含む。デジタル位相比較器は、サンプラ群のサンプル信号に基づいて、基準信号と第1の信号との間のエッジの時間差を検出し、時間差を位相差に変換する検出回路を含む。

【0011】

別の実施形態によれば、デジタル位相比較器は、基準信号とN相入力信号(Nは2以上の整数)のうちの第1の信号との間のエッジの時間差を、N相入力信号における隣接相間の時間差に相当する第1の時間分解能によって量子化し、第1の量子化値を得る第1の時間−デジタル変換器を含む。デジタル位相比較器は、基準信号とN相入力信号のうち第1の信号に比べて2π・K/Nだけ(Kは0以上M未満の整数、MはNの整数倍)位相の遅れた第2の信号との間のエッジの時間差を、N相入力信号における隣接相間の時間差よりも小さい第2の時間分解能によって量子化し、第2の量子化値を得る第2の時間−デジタル変換器を含む。第2の時間−デジタル変換器は、環状接続されたM段の遅延器を含み、基準信号を第(K+1)段から入力し、各段で遅延を与える遅延器列を含む。第2の時間−デジタル変換器は、遅延器列の第(K+1)段の出力信号に応じて第2の信号をサンプルする第1のサンプラと、遅延器列の第(K+1)段の次段の出力信号に応じてN相入力信号のうち第2の信号に比べて2π/Nだけ位相の遅れた第3の信号をサンプルする第2のサンプラとを含む、第1のサンプラ群を含む。第2の時間−デジタル変換器は、第1のサンプラ群のサンプル信号に基づいて、第2の信号と基準信号との間のエッジの時間差を検出し、第2の量子化値を得る検出回路とを含む。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に係るデジタル位相比較器を例示するブロック図。

【図2】第2の実施形態に係るデジタル位相比較器を例示するブロック図。

【図3】第3の実施形態に係るデジタル位相比較器を例示するブロック図。

【図4A】図3のデジタル位相比較器による入力信号と基準信号との間のエッジの時間差検出の説明図。

【図4B】図3のデジタル位相比較器による入力信号と基準信号との間のエッジの時間差検出の説明図。

【図5】第4の実施形態に係るデジタル位相比較器を例示するブロック図。

【図6】図5のリングオシレータにおける各段の出力信号の電圧変化を例示するタイミングチャート。

【図7】第5の実施形態に係るデジタル位相比較器を例示するブロック図。

【図8】第6の実施形態に係るデジタル位相比較器を例示するブロック図。

【図9】第7の実施形態に係るデジタル位相比較器を例示するブロック図。

【図10】第8の実施形態に係るTDCを例示するブロック図。

【図11A】図10のFTDCによる入力信号と基準信号との間のエッジの時間差検出の説明図。

【図11B】図10のFTDCによる入力信号と基準信号との間のエッジの時間差検出の説明図。

【図12】第8の実施形態に係るTDCを含むデジタル位相比較器を例示するブロック図。

【図13】図12の位相予測器の動作の説明図。

【図14】第9の実施形態に係るTDCの一部を例示するブロック図。

【図15】第9の実施形態に係るTDCを含むデジタル位相比較器を例示するブロック図。

【図16】第10の実施形態に係るデジタル位相同期回路を例示するブロック図。

【図17】第11の実施形態に係る通信装置を例示するブロック図。

【発明を実施するための形態】

【0013】

以下、図面を参照して、実施形態について説明する。尚、各実施形態において、説明済みの他の実施形態と同一または類似の要素には同一または類似の符号を付し、重複する説明を基本的に省略する。

【0014】

また、以降の説明において、立ち上がりエッジの検出は、立ち下がりエッジの検出に適宜読み替えることができる。一方、立ち下がりエッジの検出もまた、立ち上がりエッジの検出に適宜読み替えることができる。

【0015】

(第1の実施形態)

図1に示されるように、第1の実施形態に係るデジタル位相比較器は、N個(Nは2以上の整数)のサンプラ100−0,100−1,・・・,100−(N−1)と、N個の遅延器200−0,200−1,・・・,200−(N−1)と、エッジ検出及び正規化回路300とを含む。尚、本実施形態において、サンプラ100−0,100−1,・・・,100−(N−1)をまとめてサンプラ群100と称することもある。

【0016】

図1のデジタル位相比較器には、N相の入力信号CKV0,CKV1,・・・,CKVN−1と、基準信号Refとが入力される。図1のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態において、入力信号の相数=遅延器及びサンプラの数であるが、両者は相違してもよい。

【0017】

N相の入力信号CKV0,CKV1,・・・,CKVN−1は、順番に略2π/Nずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0以上N−2以下の任意の整数である)は、入力信号CKVjよりも略2π/Nだけ位相が遅れている。2π/Nの位相差は、Tv/Nの時間差に相当する。TvはN相の入力信号CKV0,CKV1,・・・,CKVN−1の周期(即ち、周波数の逆数)を表す。

【0018】

N個の遅延器200−0,200−1,・・・,200−(N−1)は、カスケード接続されて遅延器列を形成する。遅延器列の初段(遅延器200−0)には、基準信号Refが入力され、各段において略t2の遅延が夫々与えられる。例えば、遅延器200−(N−2)の出力信号は基準信号Refに比べて略(N−1)・t2だけ遅れている。尚、t2及びTv/Nは相違するように設計されるが、両者の大小関係は問われない。

【0019】

サンプラ100−0,100−1,・・・,100−(N−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ100−0のクロック端子には基準信号Refが供給され、サンプラ100−0のD端子には入力信号CKV0が供給される。サンプラ100−0は、クロック信号に応じて入力信号CKV0をサンプルし、Q端子からエッジ検出及び正規化回路300へ出力する。サンプラ100−(i+1)のクロック端子には遅延器200−iからの出力信号が供給され、サンプラ100−(i+1)のD端子には入力信号CKVi+1が供給される。ここで、iは0以上N−2以下の任意の整数である。サンプラ100−(i+1)は、クロック信号に応じて入力信号CKVi+1をサンプルし、Q端子からエッジ検出及び正規化回路300へ出力する。

【0020】

エッジ検出及び正規化回路300は、サンプラ群100からの入力信号系列Q0,Q1,・・・,QN−1に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。具体的には、エッジ検出及び正規化回路300は、入力信号系列において「1」から「0」に(或いは、「0」から「1」に)遷移する位置を解析することにより、時間差td0を検出する。

【0021】

エッジ検出及び正規化回路300は、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。例えば、エッジ検出及び正規化回路300は、入力信号系列Q0,Q1,・・・,QN−1に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち下がりエッジとの間の時間差td’0を更に検出する。エッジ検出及び正規化回路300は、入力信号系列において「0」から「1」に(または「1」から「0」に)遷移する位置を解析することにより、時間差td’0を検出する。時間差td’0と時間差td0との間の差分は、Tv/2に相当するので、これを2倍すれば周期Tvを導出できる。エッジ検出及び正規化回路300は、検出した時間差td0を周期Tvで除算(正規化)することにより、時間差td0を位相差に変換する。エッジ検出及び正規化回路300は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0022】

前述のように、サンプラ群100は、t2ずつ遅れたクロック信号に従ってTv/Nずつ遅れた入力信号をサンプルする。即ち、図1のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図1のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/Nと基準信号Refの単位遅延t2との間の差分に一致する。

【0023】

以上説明したように、第1の実施形態に係るデジタル位相比較器は、多相入力信号における信号間の位相差を遅延として利用することにより、入力信号のための遅延器列を必要とせずにVDLと同様の動作を実現する。従って、本実施形態に係るデジタル位相比較器によれば、VDLと同様の高い時間分解能を達成しつつ、入力信号のための遅延器列に相当する回路面積及び消費電力を節約できる。

【0024】

(第2の実施形態)

図2に示されるように、第2の実施形態に係るデジタル位相比較器は、8個のサンプラ110−0,110−1,・・・,110−7と、8個の遅延器210−0,210−1,・・・,210−7と、エッジ検出及び正規化回路310とを含む。

【0025】

図2のデジタル位相比較器には、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図2のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数=遅延器及びサンプラの数=「8」に設計されているが、これらをN(但し、本実施形態において入力信号の相数は偶数)に一般化しても勿論よい。更に、本実施形態において、入力信号の相数=遅延器及びサンプラの数であるが、これらは相違してもよい。

【0026】

8相の入力信号CKV0,CKV1,・・・,CKV7は、順番に略π/4ずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0以上6以下の任意の整数である)は、入力信号CKVjよりも略π/4だけ位相が遅れている。π/4の位相差は、Tv/8の時間差に相当する。Tvは8相の入力信号CKV0,CKV1,・・・,CKV7の周期を表す。更に、入力信号CKVj+4(または、入力信号CKVj−4)は、入力信号CKVjの逆相信号に相当する。尚、入力信号の相数をNに一般化する場合には、入力信号CKVjの逆相信号は入力信号CKVj+N/2(または、入力信号CKVj−N/2)である。

【0027】

遅延器210−0,210−1,・・・,210−7は、カスケード接続されて遅延器列を形成する。遅延器列の初段(遅延器210−0)には、基準信号Refが入力され、各段において略t2の遅延が夫々与えられる。例えば、遅延器210−6の出力信号は基準信号Refに比べて略7・t2だけ遅れている。尚、t2及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0028】

サンプラ110−0,110−1,・・・,110−7は、典型的には、差動構成のDフリップフロップまたは類似の素子である。サンプラ110−0のクロック端子には基準信号Refが供給され、サンプラ110−0のD端子には入力信号CKV0が供給され、サンプラ110−0のDb端子には入力信号CKV4が供給される。サンプラ110−0は、クロック信号に応じて入力信号CKV0及び入力信号CKV4(即ち、入力信号CKV0の逆相信号)の差動信号をサンプルし、Q端子からエッジ検出及び正規化回路310へ出力する。サンプラ110−(i+1)のクロック端子には遅延器210−iからの出力信号が供給され、サンプラ110−(i+1)のD端子には入力信号CKVi+1が供給され、サンプラ110−(i+1)のDb端子には入力信号CKVi+5(またはCKVi−3)が供給される。ここで、iは0以上6以下の任意の整数である。サンプラ100−(i+1)は、クロック信号に応じて入力信号CKVi+1及び入力信号CKVi+5(またはCKVi−3)の差動信号をサンプルし、Q端子からエッジ検出及び正規化回路310へ出力する。

【0029】

エッジ検出及び正規化回路310は、エッジ検出及び正規化回路300と同様に、サンプラ群110からの入力信号系列Q0,Q1,・・・,Q7に基づいて、時間差td0を検出する。更に、エッジ検出及び正規化回路310は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路310は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0030】

前述のように、サンプラ群110は、t2ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号(の差動信号)をサンプルする。即ち、図2のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図2のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延t2との間の差分に一致する。

【0031】

以上説明したように、第2の実施形態に係るデジタル位相比較器は、第1の実施形態に係るデジタル位相比較器において差動入力信号をサンプルする構成に相当する。従って、本実施形態に係るデジタル位相比較器によれば、第1の実施形態と同様の効果を得ることができると共に、差動構成による様々な利点(コモンモード除去効果など)も得ることができる。

【0032】

(第3の実施形態)

図3に示されるように、第3の実施形態に係るデジタル位相比較器は、N+M個(Nは2以上の整数、Mは1以上の整数)のサンプラ120−0,120−1,・・・,120−(N+M−1)と、N+M個の遅延器220−0,220−1,・・・,220−(N+M−1)と、エッジ検出及び正規化回路320とを含む。尚、本実施形態において、サンプラ120−0,120−1,・・・,120−(N+M−1)をまとめてサンプラ群120と称することもある。

【0033】

図3のデジタル位相比較器には、N相の入力信号CKV0,CKV1,・・・,CKVN−1と、基準信号Refとが入力される。図3のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。

【0034】

遅延器220−0,220−1,・・・,220−(N+M−1)は、カスケード接続されて遅延器列を形成する。遅延器列の初段(遅延器220−0)には、基準信号Refが入力され、各段において略t2の遅延が夫々与えられる。例えば、遅延器220−(N+M−2)の出力信号は基準信号Refに比べて略(N+M−1)・t2だけ遅れている。尚、t2及びTv/Nは相違するように設計されるが、両者の大小関係は問われない。

【0035】

サンプラ120−0,120−1,・・・,120−(N+M−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ120−0のクロック端子には基準信号Refが供給され、サンプラ120−0のD端子には入力信号CKV0が供給される。サンプラ120−0は、クロック信号に応じて入力信号CKV0をサンプルし、Q端子からエッジ検出及び正規化回路320へ出力する。

【0036】

サンプラ120−(i+1)のクロック端子には遅延器220−iからの出力信号が供給され、サンプラ120−(i+1)のD端子には入力信号CKVi+1が供給される。ここで、iは0以上(N+M−2)以下の整数である。

【0037】

但し、i+1≧Nである場合には、i+1の値は入力信号の相数を超過する。そこで、例えばサンプラ120−NのD端子には入力信号CKV0が供給される。以降、i+1=Nから2Nまで、サンプラ120−(i+1)のD端子には入力信号CKV(i+1)−Nが供給される。一般化するならば、サンプラ120−(i+1)のD端子には、入力信号CKV(i+1)modNが入力される。「xmody」は、「xのyを法とする剰余」を意味する。

【0038】

尚、例えば、入力信号CKV0は、サンプラ120−(N−1)のD端子に供給される入力信号CKVN−1に比べてTv/Nだけ遅れているとみなすことができる。故に、i+1≧Nの場合にも、サンプラのD端子に供給される入力信号が略Tv/Nずつ遅れているという関係は維持される。

【0039】

サンプラ120−(i+1)は、クロック信号に応じて入力信号CKV(i+1)modNをサンプルし、Q端子からエッジ検出及び正規化回路320へ出力する。尚、Nが偶数である場合には、サンプラ群120は、差動入力信号をサンプルしてもよい。

【0040】

エッジ検出及び正規化回路320は、エッジ検出及び正規化回路300と同様に、サンプラ群120からの入力信号系列Q0,Q1,・・・,QN+M−1に基づいて、時間差td0を検出する。更に、エッジ検出及び正規化回路320は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路320は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0041】

例えば、N=8とした場合の入力信号CKV0と基準信号Refとの間の時間差検出は、例えば図4Aまたは図4Bに示すように実現される。図4AはTv/8<t2の場合に対応し、図4BはTv/8>t2の場合に対応する。以降、便宜的に、サンプラ120−(i+1)のクロック端子に供給される遅延基準信号Refi+1との間の立ち上がりエッジと、その直前における入力信号CKV(i+1)modNの立ち上がりエッジとの間の時間差をtdi+1で表す。

【0042】

図4Aの例では、時間差tdi+1=td0−i(Tv/8−t2)である。時間差tdi+1が正値から負値に遷移する位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「1」から「0」に遷移する位置)を検出すれば、時間差td0を(Tv/8−t2)によって量子化した値を得ることができる。更に、時間差tdi+1がTv/2(または−Tv/2)を下回る位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「0」から「1」に遷移する位置)を検出すれば、時間差td’0を(Tv/8−t2)によって量子化した値を得ることができる。

【0043】

図4Bの例では、時間差tdi+1=td0+i(t2−Tv/8)である。時間差tdi+1が周期Tvを上回る位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「0」から「1」に遷移する位置)を検出すれば、(Tv−td0)を(t2−Tv/8)によって量子化した値を得ることができる。従って、係る量子化値をTvから減算することにより、時間差td0を(t2−Tv/8)によって量子化した値を得ることができる。更に、時間差tdi+1がTv/2(または3Tv/2)を上回る位置(即ち、入力信号系列Q0,Q1,・・・,QN+M−1が「1」から「0」に遷移する位置)を検出すれば、(Tv−td’0)を(Tv/8−t2)によって量子化した値を得ることができる。従って、係る量子化値をTvから減算することにより、時間差td’0を(t2−Tv/8)によって量子化した値を得ることができる。

【0044】

前述のように、サンプラ群120は、t2ずつ遅れたクロック信号に従ってTv/Nずつ遅れた入力信号をサンプルする。即ち、図3のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図3のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/Nと基準信号Refの単位遅延t2との間の差分に一致する。

【0045】

以上説明したように、第3の実施形態に係るデジタル位相比較器は、入力信号の相数を超える数のサンプラを許容する。従って、本実施形態に係るデジタル位相比較器によれば、より大きな(最大で時間分解能の(N+M)倍の)時間差を検出することができる。

【0046】

(第4の実施形態)

図5に示されるように、第4の実施形態に係るデジタル位相比較器は、7個のサンプラ130−0,130−1,・・・,130−6と、7個の遅延器230−0,230−1,・・・230−6と、エッジ検出及び正規化回路330とを含む。尚、本実施形態において、サンプラ130−0,130−1,・・・,130−6をまとめてサンプラ群130と称することもある。

【0047】

図5のデジタル位相比較器には、7相の入力信号CKV0,CKV1,・・・,CKV6と、基準信号Refとが入力される。図5のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数=遅延器及びサンプラの数=「7」に設計されているが、これらをN(但し、本実施形態において遅延器及びサンプラの数は奇数)に一般化しても勿論よい。更に、本実施形態において、入力信号の相数=遅延器及びサンプラの数であるが、これらは相違してもよい。

【0048】

7相の入力信号CKV0,CKV1,・・・,CKV6は、順番に略2π/7ずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0以上5以下の任意の整数である)は、入力信号CKVjよりも略2π/7だけ位相が遅れている。2π/7の位相差は、Tv/7の時間差に相当する。Tvは7相の入力信号CKV0,CKV1,・・・,CKV6の周期を表す。

【0049】

遅延器230−0,230−1,・・・,230−6は、典型的には単相インバータである。これらは、環状接続され、(7相)リングオシレータとして機能する。以降の説明では、遅延器230−0,230−1,・・・,230−6をまとめてリングオシレータ230と称することもある。

【0050】

リングオシレータ230は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器230−0から順番に発振し始める。遅延器230−(i+1)は、遅延器230−iからの入力信号を反転させて出力する。ここで、iは0以上5以下の任意の整数である。更に、信号には遅延器230−(i+1)の通過によって略TR/14の遅延が与えられる。TRはリングオシレータ230の発振周期を表す。即ち、遅延器230−(i+1)の出力信号Ri+1は、その入力信号Riに比べて略4TR/7だけ遅延する。図6は、リングオシレータ230における各段の出力信号の電圧変化を例示する。図6から明らかなように、リングオシレータ230における各段の出力信号は、R0→R2→R4→R6→R1→R3→R5の順序でTR/7ずつ遅れている。尚、TR/7及びTv/7は相違するように設計されるが、両者の大小関係は問われない。

【0051】

リングオシレータ230の発振周期は、図示しないカウンタによってカウントされる。そして、例えば、第t番目(tは1以上の所定数)の発振周期の完了時に、リングオシレータ230の発振は停止される。故に、サンプラ群130は、合計7×t点のサンプリングを行うことができる。即ち、リングオシレータ230は7×t個の遅延器であるとみなすことができるし、サンプラ群130は7×t個のサンプラであるとみなすことができる。また、第t回目の発振周期の完了を待たずに、エッジ検出及び正規化回路330が所望の時間差td0(及びtd’0)を検出したことを条件に、リングオシレータの発振が停止されてもよい。

【0052】

サンプラ130−0,130−1,・・・,130−6は、遅延器230−0,230−1,・・・,230−6の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ130−0,130−1,・・・,130−6がサンプルする信号は、クロック信号の遅延順によって決まる。即ち、最も遅延の小さいクロック信号R0を利用するサンプラ130−0は、最も遅延の小さい入力信号CKV0をサンプルする。一方、最も遅延の大きいクロック信号R5を利用するサンプラ130−5は、最も遅延の大きい入力信号CKV6をサンプルする。サンプラ群130は、サンプル信号をエッジ検出及び正規化回路330へ入力する。

【0053】

エッジ検出及び正規化回路330は、サンプラ群130からの入力信号系列Q0,Q1,・・・,Q6に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。具体的には、入力信号系列Q0,Q1,・・・,Q6を、遅延順に従ってQ0→Q2→Q4→Q6→Q1→Q3→Q5の順序にソートすれば、エッジ検出及び正規化回路300と同様の手法が適用できる。尚、tが2以上であるならば、エッジ検出及び正規化回路330は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路330は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路330は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0054】

前述のように、サンプラ群130は、TR/7ずつ遅れたクロック信号に従ってTv/7ずつ遅れた入力信号をサンプルする。即ち、図5のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図5のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/7と基準信号Refの単位遅延TR/7との間の差分に一致する。

【0055】

以上説明したように、第4の実施形態に係るデジタル位相比較器は、リングオシレータを最大t周期に亘って発振させることにより遅延クロック信号を生成する。従って、本実施形態に係るデジタル位相比較器によれば、リングオシレータの相数×t個のサンプラ及び遅延器を用意する場合と同様の効果を得ることができる。

【0056】

(第5の実施形態)

図7に示されるように、第5の実施形態に係るデジタル位相比較器は、9個のサンプラ140−0,140−1,・・・,140−8と、9個の遅延器240−0,240−1,・・・,240−8と、エッジ検出及び正規化回路340とを含む。尚、本実施形態において、サンプラ140−0,140−1,・・・,140−8をまとめてサンプラ群140と称することもある。

【0057】

図7のデジタル位相比較器には、3相の入力信号CKV0,CKV1,CKV2と、基準信号Refとが入力される。図7のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数×3=遅延器及びサンプラの数=「9」に設計されているが、入力信号の相数をNに一般化し、遅延器及びサンプラの数をNの奇数倍に一般化しても勿論よい。

【0058】

3相の入力信号CKV0,CKV1,CKV2は、順番に略2π/3ずつ位相が遅れている。例えば、入力信号CKVj+1(ここで、jは0または1である)は、入力信号CKVjよりも略2π/3だけ位相が遅れている。2π/3の位相差は、Tv/3の時間差に相当する。Tvは3相の入力信号CKV0,CKV1,CKV2の周期を表す。

【0059】

遅延器240−0,240−1,・・・,240−8は、典型的には単相インバータである。これらは、環状接続され、9相リングオシレータとして機能する。以降の説明では、遅延器240−0,240−1,・・・,240−8をまとめてリングオシレータ240と称することもある。

【0060】

リングオシレータ240は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器240−0から順番に発振し始める。遅延器240−(i+1)は、遅延器240−iからの入力信号を反転させて出力する。ここで、iは0以上7以下の整数である。更に、信号には遅延器240−(i+1)の通過によって略TR/18の遅延が与えられる。TRはリングオシレータ240の発振周期を表す。即ち、遅延器240−(i+1)の出力信号Ri+1は、その入力信号Riに比べて略5TR/9だけ遅延する。従って、リングオシレータ240における各段の出力信号は、R0→R2→R4→R6→R8→R1→R3→R5→R7の順序でTR/9ずつ遅れている。尚、TR/9及びTv/3は相違するように設計されるが、両者の大小関係は問われない。

【0061】

リングオシレータ240もまた、リングオシレータ230と同様に、最大t周期に亘って発振する。故に、サンプラ140群は、合計9×t点のサンプリングを行うことができる。即ち、リングオシレータ240は9×t個の遅延器であるとみなすことができるし、サンプラ140群は9×t個のサンプラであるとみなすことができる。

【0062】

サンプラ140−0,140−1,・・・,140−8は、遅延器240−0,240−1,・・・,240−8の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ140−0,140−1,・・・,140−8がサンプルする信号は、クロック信号の遅延順によって決まる。即ち、最も遅延の小さいクロック信号R0を利用するサンプラ140−0は、最も遅延の小さい入力信号CKV0をサンプルする。2番目に遅延の小さいクロック信号R2を利用するサンプラ140−2は、2番目に遅延の小さい入力信号CKV1をサンプルする。

【0063】

本実施形態では、入力信号の相数がサンプラの数に比べて小さい。しかしながら、入力信号はCKV0→CKV1→CKV2→CKV0・・・の順序で遅延しているので、この順序によってサンプラ140−0,140−1,・・・,140−8がサンプルする信号を決定できる。例えば、第4番目に遅延の小さいクロック信号R6を利用するサンプラ140−6は、第4番目に遅延の小さい入力信号CKV0をサンプルする。サンプラ群140は、サンプル信号をエッジ検出及び正規化回路340へ入力する。

【0064】

エッジ検出及び正規化回路340は、サンプラ群140からの入力信号系列Q0,Q1,・・・,Q8に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。具体的には、入力信号系列Q0,Q1,・・・,Q8を、遅延順に従ってQ0→Q2→Q4→Q6→Q8→Q1→Q3→Q5→Q7の順序にソートすれば、エッジ検出及び正規化回路300と同様の手法が適用できる。尚、tが2以上であるならば、エッジ検出及び正規化回路340は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路340は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路330は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0065】

前述のように、サンプラ140群は、TR/9ずつ遅れたクロック信号に従ってTv/3ずつ遅れた入力信号をサンプルする。即ち、図7のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図7のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/3と基準信号Refの単位遅延TR/9との間の差分に一致する。

【0066】

以上説明したように、第5の実施形態に係るデジタル位相比較器は、入力信号の相数に比べて多くのサンプラ及び遅延器を利用する。従って、本実施形態に係るデジタル位相比較器によれば、サンプラ及び遅延器を入力信号の周波数に比べて低速に(低い周波数で)動作させることができる。

【0067】

(第6の実施形態)

図8に示されるように、第6の実施形態に係るデジタル位相比較器は、8個のサンプラ150−0,150−1,・・・,150−7と、4個の遅延器250−0,250−1,・・・250−3と、エッジ検出及び正規化回路350とを含む。尚、本実施形態において、サンプラ150−0,150−1,・・・,150−7をまとめてサンプラ群150と称することもある。

【0068】

図8のデジタル位相比較器には、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図8のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数=遅延器の数×2=サンプラの数=「8」に設計されているが、これらをNに一般化しても勿論よい。更に、本実施形態において、入力信号の相数=遅延器の数×2=サンプラの数であるが、入力信号の相数と遅延器の数×2及びサンプラの数とは相違してもよい。

【0069】

4個の遅延器250−0,250−1,・・・,250−3は、典型的には差動増幅器である。これらは、環状接続され、(8相)差動リングオシレータとして機能する。以降の説明では、4個の遅延器250−0,250−1,・・・,250−3をまとめて差動リングオシレータ250と称することもある。

【0070】

差動リングオシレータ250は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器250−0から順番に発振し始める。遅延器250−(i+1)は、遅延器250−iからの差動入力信号Ri及びRi+4に略TR/8の遅延を与え、差動出力信号Ri+1及びRi+5を次段に供給する。ここで、iは0以上2以下の整数である。TRは差動リングオシレータ250の発振周期を表す。即ち、遅延器250−(i+1)の差動出力信号Ri+1及びRi+5は、その差動入力信号Ri及びRi+4に比べて略TR/8だけ遅延する。従って、差動リングオシレータ250における各段の出力信号は、R0→R1→,・・・,→R7の順序でTR/8ずつ遅れている。尚、TR/8及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0071】

差動リングオシレータ250もまた、リングオシレータ230と同様に、最大t周期に亘って発振する。故に、サンプラ群150は、合計8×t点のサンプリングを行うことができる。即ち、差動リングオシレータ250は8×t個の遅延器であるとみなすことができるし、サンプラ群150は8×t個のサンプラであるとみなすことができる。

【0072】

サンプラ150−0,150−1,・・・,150−7は、遅延器250−0,250−1,・・・,250−3の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ150−hは、Rhをクロック信号として利用し、入力信号CKVhをサンプルする。本実施形態において、hは0以上7以下の整数である。サンプラ群150は、サンプル信号をエッジ検出及び正規化回路350へ入力する。尚、サンプラ群150は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出及び正規化回路350は、エッジ検出及び正規化回路300と同様に、サンプラ群150からの入力信号系列Q0,Q1,・・・,Q7に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。尚、tが2以上であるならば、エッジ検出及び正規化回路350は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路350は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路350は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0073】

前述のように、サンプラ群150は、TR/8ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号をサンプルする。即ち、図8のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図8のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延TR/8との間の差分に一致する。

【0074】

以上説明したように、第6の実施形態に係るデジタル位相比較器は、差動リングオシレータを最大t周期に亘って発振させることにより遅延クロック信号を生成する。従って、本実施形態に係るデジタル位相比較器によれば、差動リングオシレータの相数×t個のサンプラ及び遅延器を用意する場合と同様の効果を得ることができる。

【0075】

(第7の実施形態)

図9に示されるように、第7の実施形態に係るデジタル位相比較器は、16個のサンプラ160−0,160−1,・・・,160−15と、8個の遅延器260−0,260−1,・・・,260−7と、エッジ検出及び正規化回路360とを含む。尚、本実施形態において、サンプラ160−0,160−1,・・・,160−15をまとめてサンプラ群160と称することもある。

【0076】

図9のデジタル位相比較器には、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図9のデジタル位相比較器は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。尚、本実施形態では、簡単化のために、入力信号の相数×2=遅延器の数×2=サンプラの数=「16」に設計されているが、入力信号の相数をNに一般化し、遅延器の数×2及びサンプラの数をN/2の整数倍に一般化しても勿論よい。

【0077】

遅延器260−0,260−1,・・・,260−7は、典型的には差動増幅器である。これらは、環状接続され、(16相)差動リングオシレータとして機能する。以降の説明では、遅延器260−0,260−1,・・・,260−7をまとめて差動リングオシレータ260と称することもある。

【0078】

差動リングオシレータ260は、基準信号Refをトリガとして利用する。即ち、基準信号RefがLow(「0」)からHigh(「1」)に遷移すると、遅延器260−0から順番に発振し始める。遅延器260−(i+1)は、遅延器260−iからの差動入力信号Ri及びRi+8に略TR/16の遅延を与え、差動出力信号Ri+1及びRi+9を次段に供給する。ここで、iは0以上6以下の整数である。TRは差動リングオシレータ260の発振周期を表す。即ち、遅延器260−(i+1)の差動出力信号Ri+1及びRi+9は、その差動入力信号Ri及びRi+8に比べて略TR/16だけ遅延する。即ち、差動リングオシレータ260における各段の出力信号は、R0→R1→,・・・,→R15の順序でTR/16ずつ遅れている。尚、TR/16及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0079】

差動リングオシレータ260もまた、リングオシレータ230と同様に、最大t周期に亘って発振する。故に、サンプラ群160は、合計16×t点のサンプリングを行うことができる。即ち、差動リングオシレータ260は16×t個の遅延器であるとみなすことができるし、サンプラ群160は16×t個のサンプラであるとみなすことができる。

【0080】

サンプラ160−0,160−1,・・・,160−15は、遅延器260−0,260−1,・・・,260−8の出力信号を夫々クロック信号として利用し、入力信号をサンプルする。サンプラ160−hは、Rhをクロック信号として利用し、入力信号CKVhをサンプルする。本実施形態においてhは、0以上15以下の整数である。

【0081】

本実施形態では、入力信号の相数が、サンプラの数及び遅延器の数×2に比べて小さい。しかしながら、入力信号はCKV0→CKV1→,・・・,→CKV7→CKV0・・・の順序で遅延しているので、この順序によってサンプラ160−0,160−1,・・・,160−15がサンプルする信号を決定できる。例えば、第9番目に遅延の小さいクロック信号R8を利用するサンプラ160−8は、第9番目に遅延の小さい入力信号CKV0をサンプルする。一般化するならば、サンプラ160−hは、入力信号CKVhmod8をサンプルする。サンプラ群160は、サンプル信号をエッジ検出及び正規化回路360へ入力する。尚、サンプラ群160は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出及び正規化回路360は、エッジ検出及び正規化回路300と同様に、サンプラ群160からの入力信号系列Q0,Q1,・・・,Q15に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差td0を検出する。尚、tが2以上であるならば、エッジ検出及び正規化回路360は、第1番目の発振周期における入力信号系列から順にエッジ検出を行えばよい。更に、エッジ検出及び正規化回路360は、エッジ検出及び正規化回路300と同様に、検出した時間差td0を位相差に正規化してデジタル信号Phfを得る。エッジ検出及び正規化回路360は、基準信号Refの周期毎にデジタル信号Phfを出力する。

【0082】

前述のように、サンプラ群160は、TR/16ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号をサンプルする。即ち、図9のデジタル位相比較器は、VDLと同様の動作を実現する。故に、図9のデジタル位相比較器の時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延TR/16との間の差分に一致する。

【0083】

以上説明したように、第7の実施形態に係るデジタル位相比較器は、入力信号の相数に比べて多くのサンプラと、サンプラの半数の遅延器を含む差動リングオシレータとを利用する。従って、本実施形態に係るデジタル位相比較器によれば、サンプラ及び遅延器を入力信号の周波数に比べて低速に(低い周波数で)動作させることができる。

【0084】

(第8の実施形態)

第8の実施形態は、デジタル位相比較器に含まれる時間−デジタル変換器(TDC)に関する。一般に、TDCは、入力信号と基準信号との間のエッジの時間差をデジタル値に変換する。図10に示されるように、本実施形態に係るTDCは、時間分解能が相対的に粗いCTDC410と、時間分解能が相対的に細かいFTDC440とを含む。図10のTDCには、8相の入力信号CKV0,CKV1,・・・,CKV7と、基準信号Refとが入力される。図10のTDCは、任意の入力信号(例えば、CKV0)と基準信号Refとの間の時間差を表すデジタル信号DTriseCと、当該任意の入力信号と同一または異なる位相の入力信号と基準信号Refとの間の時間差を表すデジタル信号DTriseFとを出力する。

【0085】

CTDC410は、8個のサンプラ420−0,420−1,・・・,420−7と、エッジ検出回路430とを含む。尚、本実施形態では、簡単化のために、入力信号の相数=サンプラ420の数=「8」に設計されているが、両者をNに一般化しても勿論よい。更に、本実施形態において、入力信号の相数=サンプラ420の数であるが、両者は相違してもよい。

【0086】

サンプラ420−0,420−1,・・・,420−7は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ420−0,420−1,・・・,420−7のクロック端子には基準信号Refが共通に供給され、サンプラ420−0,420−1,・・・,420−7のD端子には入力信号CKV0,CKV1,・・・,CKV7が夫々供給される。即ち、サンプラ420−0,420−1,・・・,420−7は、基準信号Refに応じて入力信号CKV0,CKV1,・・・,CKV7を夫々サンプルし、Q端子からエッジ検出回路430へ出力する。尚、サンプラ420−0,420−1,・・・,420−7は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出回路430は、サンプラ420−0,420−1,・・・,420−7からの入力信号系列Qc0,Qc1,・・・,Qc7に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV0の立ち上がりエッジとの間の時間差を検出し、検出した時間差を表すデジタル信号DTriseCを出力する。具体的には、エッジ検出回路430は、エッジ検出及び正規化回路300と同様に時間差を検出すればよい。CTDC410の時間分解能は、Tv/8に一致する。

【0087】

FTDC440は、M個のサンプラ450−0,450−1,・・・,450−(M−1)と、M個の遅延器460−0,460−1,・・・,460−(M−1)と、エッジ検出回路470とを含む。本実施形態において、Mは8の整数倍である。尚、入力信号の相数をNに一般化するならば、MはNの整数倍である。また、本実施形態において、サンプラ450−0,450−1,・・・,450−(M−1)をまとめてサンプラ群450と称することもある。

【0088】

M個の遅延器460−0,460−1,・・・,460−(M−1)は、典型的には、セレクタである。M個の遅延器460−0,460−1,・・・,460−(M−1)は、選択制御信号S0,S1,・・・,SM−1に夫々従って、2入力信号の一方を選択し、選択信号に略t2の遅延を与えて次段に供給する。以降の説明では、簡単化のために、遅延器460−mは、選択制御信号Smが「0」であれば前段の出力信号Rm−1(但し、m=0であればRM−1)を選択し、選択制御信号Smが「1」であれば基準信号Refを選択することにする。本実施形態において、mは0以上M−1以下の任意の整数である。

【0089】

選択制御信号S0,S1,・・・,SM−1のうち1つは「1」に設定され、残りのM−1個は「0」に設定される。以降の説明では、SK=1とする(Kは、0以上M−1以下の整数である)。即ち、遅延器460−(M−1)の出力信号RM−1は、遅延器460−Kの出力信号RKに比べて略(M−K−1)・t2だけ遅れている。尚、以降の説明において、基準信号Refと、遅延器460−Kの出力信号RKとの間の時間差は簡単化のために無視する。また、遅延器460−(K−1)の出力信号RK−1(但し、K=0であれば、遅延器460−(M−1)の出力信号RM−1)は、遅延器460−Kの出力信号RKに比べて略(M−1)・t2だけ遅れている。尚、t2及びTv/8は相違するように設計されるが、両者の大小関係は問われない。

【0090】

サンプラ450−0,450−1,・・・,450−(M−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ450−mのクロック端子には遅延器460−mの出力信号Rmが供給される。サンプラ450−mのD端子には入力信号CKVmmod8が供給される。即ち、サンプラ450−mは、遅延器460−mの出力信号Rmに応じて入力信号CKVmmod8をサンプルし、Q端子からエッジ検出回路470へ出力する。尚、サンプラ群450は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出回路470は、サンプラ群450からの入力信号系列Qf0,Qf1,・・・,Qf(M−1)に基づいて、基準信号Refの立ち上がりエッジと、その直前における所定の入力信号の立ち上がりエッジとの間の時間差を検出し、検出した時間差を表すデジタル信号DTriseFを出力する。所定の入力信号とは、入力信号CKV0からK・Tv/8だけ遅れた信号であり、換言すれば、サンプラ450−Kがサンプルする入力信号CKVKmod8である。

【0091】

K=1である場合の時間差検出を図11Aに例示し、K=3である場合の時間差検出を図11Bに例示する。尚、図11A及び図11Bの例では、いずれもTv/8>t2である。

【0092】

図11Aの例では、エッジ検出回路470は、入力信号系列において「1」から「0」に遷移する位置(R10とR11との間)を解析することにより、時間差td0を検出する。この時間差td0は、入力信号CKV0の立ち上がりエッジと基準信号Refの立ち上がりエッジとの間の時間差を表す。

【0093】

図11Bの例では、エッジ検出回路470は、入力信号系列において「1」から「0」に遷移する位置(R5とR6との間)を解析することにより、時間差td3を検出する。この時間差td3は、入力信号CKV3の立ち上がりエッジと基準信号Refの立ち上がりエッジとの間の時間差を表す。

【0094】

図11A及び図11Bから明らかなように、Kの値次第で、エッジ検出回路470が検出する時間差は異なる。即ち、Kに適切な値が与えられれば、エッジ検出回路470が時間差tdKを検出するために必要な入力信号系列の数を抑えることができる。換言すれば、エッジ検出回路470は、時間差td0の大きさに関わらず、より小さい時間差tdKを検出すればよい。故に、図10のTDCによれば時間差td0を検出する構成に比べて時間差検出に必要な遅延器460及びサンプラ450の数を抑えることができる。尚、時間差td0と時間差tdKとの間の差分K・Tv/8は既知の値なので、時間差tdKに差分K・Tv/8を加算すれば時間差td0を復元できる。

【0095】

前述のように、サンプラ群450は、t2ずつ遅れたクロック信号に従ってTv/8ずつ遅れた入力信号をサンプルする。即ち、図10のTDCは、VDLと同様の動作を実現する。故に、図10のTDCの時間分解能は、入力信号の単位遅延Tv/8と基準信号Refの単位遅延t2との間の差分に一致する。

【0096】

本実施形態に係るTDCを含むデジタル位相比較器を図12に例示する。図12のデジタル位相比較器は、本実施形態に係るTDC400と、乗算器501と、位相予測器502と、周期計算回路503と、乗算器504と、補正器510とを含む。

【0097】

乗算器501は、CTDC410の時間分解能(=Tv/N)によって入力信号の周期Tvを量子化した値TvC(=N)の逆数を、CTDC410の出力信号DTriseCに乗算する。即ち、乗算器501は、CTDC410の出力信号DTriseCに入力信号の相数の逆数を乗算し、時間差を位相差に変換する。尚、本実施形態では、入力信号の相数=「8」の場合を例示しているが、入力信号の相数=Nに一般化できる。乗算器501の出力信号PHfCは、外部(例えば、図示しないデジタル位相同期回路中の他の要素)に出力される。更に、乗算器501の出力信号PHfCは、位相予測器502にも入力される。

【0098】

位相予測器502は、乗算器501の出力信号PHfCと、外部からの周波数設定コードFCWとに基づいて、基準信号Refの次の周期における入力信号(例えば、CKV0)の位相を予測する。位相予測器502は、予測結果に応じてSK=1を与えるKの値を決定する。

【0099】

一例として、図12のデジタル位相比較器を含む図示しないデジタル位相同期回路がロックしていると仮定する。係る条件下では、図13に示されるように、入力信号の位相が基準信号Refの周期Tref毎にFCWだけ増加する。即ち、位相予測器502は、乗算器501の出力信号PHfC及び周波数設定コードFCWの和の小数部を取り出すことにより、基準信号Refの次の周期における入力信号の位相を予測できる。

【0100】

FTDC440の出力信号DTriseFが表す位相差を時間差に変換するためには、FTDC440の時間分解能(=|Tv/N−t2|)によって入力信号の周期Tvを量子化した値TvFが必要となる。しかしながら、FTDC440の入力範囲は狭いので、量子化値TvFを直接導出することはできない。

【0101】

そこで、周期計算回路503は、以下のように量子化値TvFを計算する。FDCT440の出力信号DTriseFは時間差tdKをFDCT440の時間分解能によって量子化した値を表し、CDTC410の出力信号DTriseCは時間差td0をCDTC410の時間分解能によって量子化した値を表す。ここで、DTriseCからKを減算した値は、DTriseFを同じ値を表す。即ち、DTriseF/(DTriseC−K)は、CTDC410による量子化値をFTDC440による量子化値に変換するための比率に相当する。この比率をTvC(=N)に乗算すれば、TvF(=N・DTriseF/(DTriseC−K))を導出できる。周期計算回路503は、TvFの逆数を乗算器504に入力する。乗算器504は、FTDC440の出力信号DTriseFに周期計算回路503からのTvFの逆数を乗算し、時間差を位相差に変換する。乗算器504は、位相差を表す信号PHfF0を補正器510に入力する。

【0102】

信号PHfF0は、CKVKmod8と基準信号Refとの間の位相差を表している。補正器510は、信号PHfF0を補正し、CKV0と基準信号Refとの間の位相差を表す信号PHfFを出力する。補正器510は、加算器511と乗算器512とを含む。乗算器512は、位相予測器502からのKに入力信号の相数の逆数を乗算し、入力信号CKV0と入力信号CKVKmod8との間の位相シフト量を計算する。加算器511は、乗算器512による乗算結果を信号PHfF0に加算し、CKV0と基準信号Refとの間の位相差を復元する。

【0103】

以上説明したように、第8の実施形態に係るTDCは、入力信号の1つを選択し、選択した入力信号と基準信号との間のエッジの時間差を検出する。従って、本実施形態に係るTDCによれば、基準信号との位相差の小さい入力信号を選択することで時間差検出に必要な遅延器及びサンプラの数を抑えることができる。

【0104】

(第9の実施形態)

第9の実施形態に係るTDCは、図10のTDCにおけるFTDC440を、図14に示されるFTDC640に置き換えた構成に相当する。FTDC640は、M個のサンプラ450−0,450−1,・・・,450−(M−1)と、M個のサンプラ680−0,680−1,・・・,680−(M−1)と、M個の遅延器460−0,460−1,・・・,460−(M−1)と、エッジ検出回路670とを含む。尚、本実施形態において、サンプラ450−0,450−1,・・・,450−(M−1)をまとめて第1のサンプラ群450と称することもあれば、サンプラ680−0,680−1,・・・,680−(M−1)をまとめて第2のサンプラ群680と称することもある。

【0105】

サンプラ680−0,680−1,・・・,680−(M−1)は、典型的には、Dフリップフロップまたは類似の素子である。サンプラ680−mのクロック端子には遅延器460−mの出力信号Rmが供給される。サンプラ680−mのD端子には入力信号CKV(m+1)mod8が供給される。即ち、サンプラ680−mは、サンプラ450−mと共通のクロック信号に従って、サンプラ450−mよりも1相だけ遅れた入力信号をサンプルし、Q端子からエッジ検出回路670へ出力する。尚、第2のサンプラ群680は、差動入力信号をサンプルしてもよいし、差動クロック信号によって駆動されてもよい

エッジ検出回路670は、エッジ検出回路470と同様に、第1のサンプラ群450からの入力信号系列Qf0,Qf1,・・・,Qf(M−1)に基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKVKmod8の立ち上がりエッジとの間の時間差tdKを検出し、検出した時間差tdKを表すデジタル信号DTriseFを出力する。

【0106】

更に、エッジ検出回路670は、第2のサンプラ群680からの入力信号系列Q’f0,Q’f1,・・・,Q’f(M−1)とに基づいて、基準信号Refの立ち上がりエッジと、その直前における入力信号CKV(K+1)mod8の立ち上がりエッジとの間の時間差tdK+1を検出する。そして、エッジ検出回路670は、時間差tdK+1と時間差tdKとの間の差分を表すデジタル信号DivNTvを出力する。デジタル信号DivNTvは、入力信号CKVKmod8及び入力信号CKV(K+1)mod8の立ち上がりエッジの時間差を、FTDC640の時間分解能(|Tv/8−t2|)によって量子化した値である。即ち、デジタル信号DivNTvに入力信号の相数(この例では、「8」)を乗算すれば、TvFを導出できる。

【0107】

本実施形態に係るTDCを含むデジタル位相比較器を図15に例示する。図15のデジタル位相比較器は、本実施形態に係るTDC600と、乗算器501と、位相予測器502と、乗算器721と、逆数変換器722と、乗算器504と、補正器510とを含む。

【0108】

乗算器721は、FTDC640の出力信号DiVNTvに入力信号の相数を乗算し、TvFを導出する。逆数変換器722は、乗算器からのTvFの逆数を乗算器504に供給する。

【0109】

以上説明したように、第9の実施形態に係るTDCは、入力信号における隣接相間の時間差をFTDCの時間分解能によって量子化した値を更に検出する。従って、本実施形態に係るTDCによれば、入力信号の周期をFTDCの時間分解能によって量子化した値を容易に(除算処理を必要とせずに)導出できる。

【0110】

(第10の実施形態)

図16に示されるように、第10の実施形態に係るデジタル位相同期回路は、前述の各実施形態に係るデジタル位相比較器500を含む。より具体的には、図16のデジタル位相同期回路は、デジタル位相比較器500、デジタル制御発振器801、分周器802、カウンタ803、加算器804、微分器805、比較器806、積分器807、ループフィルタ808、利得正規化器809、デルタシグマ変調器810を含む。

【0111】

デジタル制御発振器801は、利得正規化回路809及びデルタシグマ変調器810によって発振信号の周波数が離散的に制御される。デジタル制御発振器801の発振信号は出力信号として取り出されると共に、分周器802に入力される。

【0112】

分周器802は、デジタル制御発振器801からの差動発振信号を4分周し、8相信号CKV0,・・・,CKV7を得る。8相信号CKV0,・・・,CKV7は、デジタル位相比較器500に入力される。更に、8相信号CKV0,・・・,CKV7のうちの任意の1つ(例えば、CKV0)はカウンタ803にも入力される。

【0113】

デジタル位相比較器500は、任意の入力信号(例えば、CKV0)と、基準信号Refとの間の位相差を表すデジタル信号Phfを出力する。カウンタ803は、基準信号Refをクロックとして利用し、入力信号(例えば、CKV0)の周期数をカウントする。

【0114】

加算器804は、カウンタ803の出力信号と、デジタル位相比較器500の出力信号とを加算し、入力信号CKV0の位相情報を得る。尚、カウンタ803の出力信号は入力信号CKV0の位相情報の整数部を表し、デジタル位相比較器500の出力信号は入力信号CKV0の位相情報の小数部を表す。

【0115】

微分器805は、加算器804からの入力信号CKV0の位相情報を微分し、入力信号CKV0の周波数情報を得る。比較器806は、所望の周波数設定コードFCWと、微分器805からの入力信号CKV0の周波数情報とを比較し、入力信号CKV0の周波数誤差情報を検出する。

【0116】

積分器806は、比較器806からの入力信号CKV0の周波数誤差情報を積分し、入力信号CKV0の位相誤差情報を得る。ループフィルタ808は、積分器806からの位相誤差情報をフィルタリングする。

【0117】

利得正規化回路809は、ループフィルタ808の出力信号に基づいてループ利得を調整するための利得調整信号を生成する。デルタシグマ変調器810は、利得調整信号の下位ビットにデルタシグマ変調を行い、デジタル制御発振器801の制御信号を生成する。

【0118】

以上説明したように、第10の実施形態に係るデジタル位相同期回路は、前述の各実施形態に係るデジタル位相比較器を含む。従って、本実施形態に係るデジタル位相同期回路によれば、前述の各実施形態と同様の効果が得られる。

【0119】

尚、図16のデジタル位相同期回路は例示であり、本実施形態に係るデジタル位相同期回路は図16に示されていない要素を含んでもよいし、図16に示された要素の一部を含まなくてもよい。

【0120】

(第11の実施形態)

図17に示されるように、第11の実施形態に係る通信装置は、第10の実施形態に係るデジタル位相同期回路800を含む。より具体的には、図17の通信装置は、デジタル位相同期回路800、アンテナ901、スイッチ902、LNA903、ミキサ904、ABB(アナログベースバンド回路)905、ADC(アナログ−デジタル変換器)906、デジタル信号処理部910、DAC(デジタル−アナログ変換器)911、ABB912、ミキサ913及びPA(電力増幅器)914を含む。

【0121】

アンテナ901によって受信された搬送周波数帯の受信信号は、スイッチ902を介してLNA903に供給される。LNA903は、入力信号の信号レベルを増幅し、ミキサ904に供給する。ミキサ904は、デジタル位相同期回路800(即ち、局部発振器)によって生成された局部発振信号を、LNA903の出力信号に乗算し、ベースバンド受信信号を得る(ダウンコンバート)。

【0122】

ABB905は、ミキサ904からのベースバンド受信信号にフィルタリング処理などの各種ベースバンド処理を行い、ADC906に入力する。ADC906は、ABB905の出力信号をデジタルドメインに変換し、デジタル信号処理部910に入力する。デジタル信号処理部910は、受信データ及び送信データに対する各種処理を行う。

【0123】

DAC911は、デジタル信号処理部910からの入力信号をアナログドメインに変換し、ABB912に入力する。ABB912は、DAC911からのアナログ信号に増幅、フィルタリング処理などの各種ベースバンド処理を行い、ミキサ913に入力する。

【0124】

ミキサ913は、デジタル位相同期回路800によって生成された局部発振信号を、ABB912の出力信号に乗算し、搬送周波数帯の送信信号を得る(アップコンバート)。PA914は、ミキサ913からの搬送周波数帯の送信信号の電力を増幅し、スイッチ902を介してアンテナ901に供給する。アンテナ901は、供給された送信信号を空間に放射する。

【0125】

尚、図17の通信装置は例示であり、本実施形態に係る通信装置は図17に示されていない要素を含んでもよいし、図17に示された要素の一部を含まなくてもよい。また、図17の通信装置は、送信及び受信の両方が可能である。しかしながら、第10の実施形態に係るデジタル位相同期回路は、送信を専ら行う通信装置(即ち、送信機)及び受信を専ら行う通信装置(即ち、受信機)のいずれにも適用可能である。

【0126】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0127】

100,110,120,130,140,150,160・・・サンプラ

200,210,220,230,240,250,260・・・遅延器

300,310,320,330,340,350,360・・・エッジ検出及び正規化回路

400,600・・・TDC

410・・・CTDC

420・・・サンプラ

430・・・エッジ検出回路

440,640・・・FTDC

450・・・サンプラ

460・・・遅延器

470,670・・・エッジ検出回路

500・・・デジタル位相比較器

501・・・乗算器

502・・・位相予測器

503・・・周期計算回路

504・・・乗算器

510・・・補正器

511・・・乗算器

512・・・乗算器

680・・・サンプラ

721・・・乗算器

722・・・逆数変換器

800・・・デジタル位相同期回路

801・・・デジタル制御発振器

802・・・分周器

803・・・カウンタ

804・・・加算器

805・・・微分器

806・・・比較器

807・・・積分器

808・・・ループフィルタ

809・・・利得正規化器

810・・・デルタシグマ変調器

901・・・アンテナ

902・・・スイッチ

903・・・LNA

904・・・ミキサ

905・・・アナログベースバンド回路

906・・・ADC

910・・・デジタル信号処理部

911・・・DAC

912・・・アナログベースバンド回路

913・・・ミキサ

914・・・PA

【特許請求の範囲】

【請求項1】

基準信号を初段から入力し、各段で遅延を与える遅延器列と、

前記基準信号に応じてN相入力信号(Nは2以上の整数)のうちの第1の信号をサンプルする第1のサンプラと、前記遅延器列の初段の出力信号に応じて前記N相入力信号のうち前記第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群と、

前記サンプラ群のサンプル信号に基づいて、前記基準信号と前記第1の信号との間のエッジの時間差を検出し、前記時間差を位相差に変換する検出回路と

を具備する、デジタル位相比較器。

【請求項2】

Nは偶数であり、

前記第1のサンプラは、前記基準信号に応じて、前記第1の信号と前記N相入力信号のうち前記第1の信号の逆相信号との第1の差動信号をサンプルし、

前記第2のサンプラは、前記遅延器列の初段の出力信号に応じて、前記第2の信号と前記N相入力信号のうち前記第2の信号の逆相信号との第2の差動信号をサンプルする、

請求項1のデジタル位相比較器。

【請求項3】

前記遅延器列は、少なくともN個の遅延器を含み、

前記サンプラ群は、前記遅延器列の第N段の出力信号に応じて前記第1の信号をサンプルする第3のサンプラを含み、

前記サンプラ群に含まれるサンプラの総数は、Nよりも大きい、

請求項1のデジタル位相比較器。

【請求項4】

基準信号をトリガとして利用するL相(Lは2以上の整数)リングオシレータと、

前記リングオシレータのL相発振信号のうち最も位相の進んだ信号に応じてN相入力信号(NはLの約数)のうちの第1の信号をサンプルする第1のサンプラと、前記L相発振信号のうち第2番目に位相の進んだ信号に応じて前記N相入力信号のうち前記第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群と、

前記サンプラ群のサンプル信号に基づいて、前記基準信号と前記第1の信号との間のエッジの時間差を検出し、前記時間差を位相差に変換する検出回路と

を具備する、デジタル位相比較器。

【請求項5】

LはNよりも大きく、

前記サンプラ群は、前記リングオシレータのL相出力信号のうち第(N+1)番目に位相の進んだ信号に応じて前記第1の信号をサンプルする第3のサンプラを含み、

前記サンプラ群に含まれるサンプラの総数は、Nよりも大きい、

請求項4のデジタル位相比較器。

【請求項6】

基準信号とN相入力信号(Nは2以上の整数)のうちの第1の信号との間のエッジの時間差を、前記N相入力信号における隣接相間の時間差に相当する第1の時間分解能によって量子化し、第1の量子化値を得る第1の時間−デジタル変換器と、

前記基準信号と前記N相入力信号のうち前記第1の信号に比べて2π・K/Nだけ(Kは0以上M未満の整数、MはNの整数倍)位相の遅れた第2の信号との間のエッジの時間差を、前記N相入力信号における隣接相間の時間差よりも小さい第2の時間分解能によって量子化し、第2の量子化値を得る第2の時間−デジタル変換器と

を具備し、

前記第2の時間−デジタル変換器は、

環状接続されたM段の遅延器を含み、前記基準信号を第(K+1)段から入力し、各段で遅延を与える遅延器列と、

前記遅延器列の第(K+1)段の出力信号に応じて前記第2の信号をサンプルする第1のサンプラと、前記遅延器列の第(K+1)段の次段の出力信号に応じて前記N相入力信号のうち前記第2の信号に比べて2π/Nだけ位相の遅れた第3の信号をサンプルする第2のサンプラとを含む、第1のサンプラ群と、

前記第1のサンプラ群のサンプル信号に基づいて、前記第2の信号と前記基準信号との間のエッジの時間差を検出し、前記第2の量子化値を得る検出回路と

を含む、デジタル位相比較器。

【請求項7】

前記N相入力信号の所望の周波数を設定する周波数設定コードと前記第1の量子化値とに基づいて、前記基準信号の次の周期における前記第1の信号の位相を予測し、予測結果に応じてKの値を決定する位相予測器を更に具備する、請求項6のデジタル位相比較器。

【請求項8】

前記第1の量子化値からKを減算し、減算結果によって前記第2の量子化値を除算し、除算結果を前記N相入力信号の周期を前記第1の時間分解能で量子化した値に乗算して、前記N相入力信号の周期を前記第2の時間分解能で量子化した値を計算する計算回路を更に具備する、請求項6のデジタル位相比較器。

【請求項9】

前記遅延器列の第(K+1)段の出力信号に応じて前記第3の信号をサンプルする第3のサンプラと、前記遅延器列の第(K+1)段の次段の出力信号に応じて前記N相入力信号のうち前記第3の信号に比べて2π/Nだけ位相の遅れた第4の信号をサンプルする第4のサンプラとを含む、第2のサンプラ群を更に具備し、

前記検出回路は、更に、前記第2のサンプラ群のサンプル信号に基づいて、前記第4の信号と前記基準信号との間のエッジの時間差を検出し、前記第2の信号及び前記第3の信号のエッジの時間差を前記第2の時間分解能によって量子化した第3の量子化値を得る、

請求項6のデジタル位相比較器。

【請求項10】

発振信号の周波数が離散的に制御されるデジタル制御発振器と、

前記発振信号を分周し、前記N相入力信号を得る分周器と、

請求項1のデジタル位相比較器と、

前記位相差に基づいて前記発振信号と所望信号との間の位相誤差を推定し、前記デジタル制御発振器を制御する制御回路と

を具備する、デジタル位相同期回路。

【請求項1】

基準信号を初段から入力し、各段で遅延を与える遅延器列と、

前記基準信号に応じてN相入力信号(Nは2以上の整数)のうちの第1の信号をサンプルする第1のサンプラと、前記遅延器列の初段の出力信号に応じて前記N相入力信号のうち前記第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群と、

前記サンプラ群のサンプル信号に基づいて、前記基準信号と前記第1の信号との間のエッジの時間差を検出し、前記時間差を位相差に変換する検出回路と

を具備する、デジタル位相比較器。

【請求項2】

Nは偶数であり、

前記第1のサンプラは、前記基準信号に応じて、前記第1の信号と前記N相入力信号のうち前記第1の信号の逆相信号との第1の差動信号をサンプルし、

前記第2のサンプラは、前記遅延器列の初段の出力信号に応じて、前記第2の信号と前記N相入力信号のうち前記第2の信号の逆相信号との第2の差動信号をサンプルする、

請求項1のデジタル位相比較器。

【請求項3】

前記遅延器列は、少なくともN個の遅延器を含み、

前記サンプラ群は、前記遅延器列の第N段の出力信号に応じて前記第1の信号をサンプルする第3のサンプラを含み、

前記サンプラ群に含まれるサンプラの総数は、Nよりも大きい、

請求項1のデジタル位相比較器。

【請求項4】

基準信号をトリガとして利用するL相(Lは2以上の整数)リングオシレータと、

前記リングオシレータのL相発振信号のうち最も位相の進んだ信号に応じてN相入力信号(NはLの約数)のうちの第1の信号をサンプルする第1のサンプラと、前記L相発振信号のうち第2番目に位相の進んだ信号に応じて前記N相入力信号のうち前記第1の信号に比べて2π/Nだけ位相の遅れた第2の信号をサンプルする第2のサンプラとを含む、サンプラ群と、

前記サンプラ群のサンプル信号に基づいて、前記基準信号と前記第1の信号との間のエッジの時間差を検出し、前記時間差を位相差に変換する検出回路と

を具備する、デジタル位相比較器。

【請求項5】

LはNよりも大きく、

前記サンプラ群は、前記リングオシレータのL相出力信号のうち第(N+1)番目に位相の進んだ信号に応じて前記第1の信号をサンプルする第3のサンプラを含み、

前記サンプラ群に含まれるサンプラの総数は、Nよりも大きい、

請求項4のデジタル位相比較器。

【請求項6】

基準信号とN相入力信号(Nは2以上の整数)のうちの第1の信号との間のエッジの時間差を、前記N相入力信号における隣接相間の時間差に相当する第1の時間分解能によって量子化し、第1の量子化値を得る第1の時間−デジタル変換器と、

前記基準信号と前記N相入力信号のうち前記第1の信号に比べて2π・K/Nだけ(Kは0以上M未満の整数、MはNの整数倍)位相の遅れた第2の信号との間のエッジの時間差を、前記N相入力信号における隣接相間の時間差よりも小さい第2の時間分解能によって量子化し、第2の量子化値を得る第2の時間−デジタル変換器と

を具備し、

前記第2の時間−デジタル変換器は、

環状接続されたM段の遅延器を含み、前記基準信号を第(K+1)段から入力し、各段で遅延を与える遅延器列と、

前記遅延器列の第(K+1)段の出力信号に応じて前記第2の信号をサンプルする第1のサンプラと、前記遅延器列の第(K+1)段の次段の出力信号に応じて前記N相入力信号のうち前記第2の信号に比べて2π/Nだけ位相の遅れた第3の信号をサンプルする第2のサンプラとを含む、第1のサンプラ群と、

前記第1のサンプラ群のサンプル信号に基づいて、前記第2の信号と前記基準信号との間のエッジの時間差を検出し、前記第2の量子化値を得る検出回路と

を含む、デジタル位相比較器。

【請求項7】

前記N相入力信号の所望の周波数を設定する周波数設定コードと前記第1の量子化値とに基づいて、前記基準信号の次の周期における前記第1の信号の位相を予測し、予測結果に応じてKの値を決定する位相予測器を更に具備する、請求項6のデジタル位相比較器。

【請求項8】

前記第1の量子化値からKを減算し、減算結果によって前記第2の量子化値を除算し、除算結果を前記N相入力信号の周期を前記第1の時間分解能で量子化した値に乗算して、前記N相入力信号の周期を前記第2の時間分解能で量子化した値を計算する計算回路を更に具備する、請求項6のデジタル位相比較器。

【請求項9】

前記遅延器列の第(K+1)段の出力信号に応じて前記第3の信号をサンプルする第3のサンプラと、前記遅延器列の第(K+1)段の次段の出力信号に応じて前記N相入力信号のうち前記第3の信号に比べて2π/Nだけ位相の遅れた第4の信号をサンプルする第4のサンプラとを含む、第2のサンプラ群を更に具備し、

前記検出回路は、更に、前記第2のサンプラ群のサンプル信号に基づいて、前記第4の信号と前記基準信号との間のエッジの時間差を検出し、前記第2の信号及び前記第3の信号のエッジの時間差を前記第2の時間分解能によって量子化した第3の量子化値を得る、

請求項6のデジタル位相比較器。

【請求項10】

発振信号の周波数が離散的に制御されるデジタル制御発振器と、

前記発振信号を分周し、前記N相入力信号を得る分周器と、

請求項1のデジタル位相比較器と、

前記位相差に基づいて前記発振信号と所望信号との間の位相誤差を推定し、前記デジタル制御発振器を制御する制御回路と

を具備する、デジタル位相同期回路。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−70087(P2012−70087A)

【公開日】平成24年4月5日(2012.4.5)

【国際特許分類】

【出願番号】特願2010−211273(P2010−211273)

【出願日】平成22年9月21日(2010.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年4月5日(2012.4.5)

【国際特許分類】

【出願日】平成22年9月21日(2010.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]