デジタル制御装置の設計方法および設計装置

【課題】マルチレートデジタル制御装置を簡易な構成で設計する。

【解決手段】本発明にかかるデジタル制御装置の設計方法は、低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得ステップと、前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換ステップと、を含む。記変換ステップでは、前記高レート補償器のインパルス応答を求めてFIR形フィルタに変換した後に、ポリフェーズ分解を施す、ことも好ましい。

【解決手段】本発明にかかるデジタル制御装置の設計方法は、低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得ステップと、前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換ステップと、を含む。記変換ステップでは、前記高レート補償器のインパルス応答を求めてFIR形フィルタに変換した後に、ポリフェーズ分解を施す、ことも好ましい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マルチレートデジタル制御装置の設計方法および設計装置に関する。

【背景技術】

【0002】

デジタル制御装置の設計にあたり、観測信号のサンプリングレートに対して制御信号のサンプリングレートを数倍に設定するマルチレート制御方式が提案されている。例えば、特許文献1,2は、マルチレート制御方式にてハードディスクのアーム位置の制御を行う方式を提案している。これらは、離散化されたナイキスト周波数よりも高い周波数領域での外乱抑圧制御を実現するために考案された方式である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−296906号公報

【特許文献2】特開2007−4910号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1,2による方式は、図3(a)に示すように、低レートで動作する補償器101と高レートで動作する補償器103を組み合わせて制御装置が実現される。これにより所望の特性を実現することが可能となるが、動作速度の異なる二つのデジタルフィルタを実現する必要があるため、実装の観点から考えると効率的とは言い難い。

【0005】

本発明は、実装面で効率的なマルチレートデジタル制御装置を設計するための技術を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記の課題を解決するために、本発明にかかるデジタル制御装置の設計方法は、

低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得ステップと、

前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換ステップと、

を含む。

【0007】

このように、高レート補償器のポリフェーズ分解に対してノーブル恒等変換を適用することで、レート変換器と高レート補償器とを、その特性を保ったまま順序を入れ替えることができる。これにより、高レート補償器がレート変換器の前段に配置されることになり、二つの低レート補償器でのみ動作すれば良くなり、実装が簡単になる。また、単位時間中にフィルタリングすべきサンプル数も減少するため、処理負荷も軽減する。

【0008】

本発明において、前記変換ステップでは、前記高レート補償器のインパルス応答を求めてFIR形フィルタに変換した後に、ポリフェーズ分解を施す、ことも好ましい。

【0009】

一般的に補償器の伝達関数は極を持つIIR形であるため、単純に伝達関数を基にポリフェーズ分解できない場合がある。このような場合でも一旦高レート補償器のインパルス応答を求めてFIR形フィルタに変換することで、ポリフェーズ分解を行えるようになる。

【0010】

また、本発明において、前記低レート補償器と前記第2の低レート補償器を合成して一つの低レート補償器を得る合成工程をさらに含む、ことも好ましい。

【0011】

これにより実装がより簡略化される。なお、低レート補償器と第2の低レート補償器はサンプルレートが同じであるため、合成は容易である。

【0012】

なお、本発明は、上記処理の少なくとも一部を有するデジタル制御装置の設計方法として捉えることができる。また、本発明は、上記処理をコンピュータにおいて実行するためのプログラムとして捉えることもできる。また、本発明は上記処理を実行するための設計装置として捉えることもできる。上記手段および処理の各々は可能な限り互いに組み合わせて本発明を構成することができる。

【発明の効果】

【0013】

本発明によれば、実装面で効率的なマルチレートデジタル制御装置を設計することができる。

【図面の簡単な説明】

【0014】

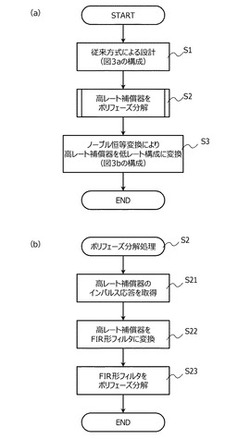

【図1】本発明にかかるマルチレート制御装置の設計方法の流れを示すフローチャート。

【図2】高レート構成を低レート構成に変換する方法を説明する図。

【図3】従来方式および本発明により設計されるマルチレート制御装置の構成を示す図。

【発明を実施するための形態】

【0015】

以下に図面を参照して、この発明の好適な実施の形態を例示的に詳しく説明する。なお、以下の処理はCPU、RAMなどの主記憶装置、HDDやDVD−ROMなどの補助記憶装置、キーボード等の入力装置、液晶ディスプレイなどの表示装置を備えるコンピュータが、アプリケーションプログラムを実行することによって実現される。一台のコンピュータによって全ての処理が実行される必要はなく、ネットワークを介して接続された複数のコンピュータから構成されるシステムによって上記処理が実行されても良い。また、全ての処理をソフトウェアによって実現する必要はなく、一部または全部の処理を専用のハードウェアによって実現してもかまわない。

【0016】

図1は本発明の設計方法の流れを示すフローチャートである。図1(a)は基本的な設計方法の流れを示している。ステップS1では、特許文献1,2などに記載された従来方式によって、ハードディスクのアーム位置制御装置(マルチレートデジタル制御装置)の設計を行う。具体的には、例えば、制御対象の周波数特性や外乱周波数特性の実測値を、それぞれ最適な最小二乗近似が得られるようにフィルタリングを施した上で、必要な伝達関数モデルで最小二乗近似する。そして、この近似モデルにH∞制御理論の可解条件を満たす伝達関数を付加し、さらに設計パラメタとなる伝達関数を付加し、このモデルに関して、制御系にとってクリティカルとなる周波数帯域でのH∞ノルムを規定値に一致されるようにコンピュータで自動的に調整する。

【0017】

このような設計により、図3(a)に示すような構成のマルチレートデジタル制御装置が得られる。すなわち、低レートで動作する低レート補償器101と低レート補償器の出力を高レートに変換するレート変換器102と、高レートで動作する高レート補償器102とから構成されるマルチレートデジタル制御装置の構成が得られる。

【0018】

なお、ステップS1では、このような構成のデジタル制御装置を得ることが目的である

ので、上記で説明した以外の設計手法によってデジタル制御装置の構成を得てもかまわない。また、既に作成されているデジタル制御装置の構成情報を、たとえば、HDL(ハードウェア記述言語)などの形式として取得するようにしてもかまわない。

【0019】

ステップS2では、高レート補償器103をポリフェーズ分解する。ここでは、例としてレート変換器102が2倍のレート変換を行う場合を例として説明する。高レート変換器103の伝達関数をH(z)とすると、以下のようにポリフェーズ分解できる。

H(z)=E1(z2)+z−1E2(z2)

これを表したのが図2(a)(b)である。

【0020】

ステップS3では、上記のポリフェーズ分解に対して、ノーブル恒等変換を用いて高レート補償器を変換して、低レート構成(図2(c))にする。ノーブル恒等変換とは、伝達関数H(z)のフィルタの後にL倍のレート変換器を接続した構造と、L倍のレート変換器の後に伝達関数H(zL)のフィルタを接続した構造が機能的に等価であり、互いに置換できるという変換原理である。図2(b)のポリフェーズ分解に対してノーブル恒等変換を適用することで、図2(c)に示す低レート構成にする。これにより、レート変換器と高レート補償器の処理順序を入れ替えた図3(b)に示すようなデジタル制御装置が得られる。

【0021】

なお、ここでは2倍のレート変換を行う場合を例に説明したが、L分割のポリフェーズ分解は、

H(z)=Σk=0, L-1Ei(zL)z−k

として与えられるので、これにノーブル恒等変換を施すことで、L倍のレート変換を行うデジタル制御装置も低レート構成に変換することができる。

【0022】

なお、高レート補償器103が極を持つIIR形である場合には、単純に伝達関数をポリフェーズ分解することはできない。このような場合には、上記ステップS2におけるポリフェーズ分解処理を、図1(b)に示す方法で行う。すなわち、まず、高レート補償器103のインパルス応答を求める(ステップS21)。インパルス応答を基に高レート補償器103を近似的にFIR形フィルタに変換する(S22)。FIR形フィルタに対してはポリフェーズ分解が行えるので、FIR形フィルタに対してポリフェーズ分解する(S23)。このようにすることで、高レート補償器がIIR形フィルタの場合であっても、低レート構成を得ることができる。

【0023】

また、上記のようにして得た低レート構成(図3(b))において、低レート補償器1と低レート補償器2を合成して実装しても良い。例えば、低レート補償器1と低レート補償器2のフィードフォワード演算を合成して一括で実行し、低レート補償器1のフィードバック演算を後段で実行しても特性は同じである。また、サンプルレートが同じであるため、合成は容易である。

【0024】

上記の例では、ハードディスクのアーム位置制御装置を例に説明したが、観測信号のサンプリングレートよりも制御信号のサンプリングレートが高いマルチレート制御装置一般に本発明の設計方法は適用可能である。本発明は、例えば、電気自動車などで用いられるインホイールモータの制御装置に対して適用することができる。この例では角速度をフィードバックする方式であるが、このような制御装置における補償器の設計にも本発明を適用することができる。

【符号の説明】

【0025】

10 マルチレート制御装置

1,2,101 低レート補償器

3,102 レート変換器

103 高レート補償器

【技術分野】

【0001】

本発明は、マルチレートデジタル制御装置の設計方法および設計装置に関する。

【背景技術】

【0002】

デジタル制御装置の設計にあたり、観測信号のサンプリングレートに対して制御信号のサンプリングレートを数倍に設定するマルチレート制御方式が提案されている。例えば、特許文献1,2は、マルチレート制御方式にてハードディスクのアーム位置の制御を行う方式を提案している。これらは、離散化されたナイキスト周波数よりも高い周波数領域での外乱抑圧制御を実現するために考案された方式である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−296906号公報

【特許文献2】特開2007−4910号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1,2による方式は、図3(a)に示すように、低レートで動作する補償器101と高レートで動作する補償器103を組み合わせて制御装置が実現される。これにより所望の特性を実現することが可能となるが、動作速度の異なる二つのデジタルフィルタを実現する必要があるため、実装の観点から考えると効率的とは言い難い。

【0005】

本発明は、実装面で効率的なマルチレートデジタル制御装置を設計するための技術を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記の課題を解決するために、本発明にかかるデジタル制御装置の設計方法は、

低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得ステップと、

前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換ステップと、

を含む。

【0007】

このように、高レート補償器のポリフェーズ分解に対してノーブル恒等変換を適用することで、レート変換器と高レート補償器とを、その特性を保ったまま順序を入れ替えることができる。これにより、高レート補償器がレート変換器の前段に配置されることになり、二つの低レート補償器でのみ動作すれば良くなり、実装が簡単になる。また、単位時間中にフィルタリングすべきサンプル数も減少するため、処理負荷も軽減する。

【0008】

本発明において、前記変換ステップでは、前記高レート補償器のインパルス応答を求めてFIR形フィルタに変換した後に、ポリフェーズ分解を施す、ことも好ましい。

【0009】

一般的に補償器の伝達関数は極を持つIIR形であるため、単純に伝達関数を基にポリフェーズ分解できない場合がある。このような場合でも一旦高レート補償器のインパルス応答を求めてFIR形フィルタに変換することで、ポリフェーズ分解を行えるようになる。

【0010】

また、本発明において、前記低レート補償器と前記第2の低レート補償器を合成して一つの低レート補償器を得る合成工程をさらに含む、ことも好ましい。

【0011】

これにより実装がより簡略化される。なお、低レート補償器と第2の低レート補償器はサンプルレートが同じであるため、合成は容易である。

【0012】

なお、本発明は、上記処理の少なくとも一部を有するデジタル制御装置の設計方法として捉えることができる。また、本発明は、上記処理をコンピュータにおいて実行するためのプログラムとして捉えることもできる。また、本発明は上記処理を実行するための設計装置として捉えることもできる。上記手段および処理の各々は可能な限り互いに組み合わせて本発明を構成することができる。

【発明の効果】

【0013】

本発明によれば、実装面で効率的なマルチレートデジタル制御装置を設計することができる。

【図面の簡単な説明】

【0014】

【図1】本発明にかかるマルチレート制御装置の設計方法の流れを示すフローチャート。

【図2】高レート構成を低レート構成に変換する方法を説明する図。

【図3】従来方式および本発明により設計されるマルチレート制御装置の構成を示す図。

【発明を実施するための形態】

【0015】

以下に図面を参照して、この発明の好適な実施の形態を例示的に詳しく説明する。なお、以下の処理はCPU、RAMなどの主記憶装置、HDDやDVD−ROMなどの補助記憶装置、キーボード等の入力装置、液晶ディスプレイなどの表示装置を備えるコンピュータが、アプリケーションプログラムを実行することによって実現される。一台のコンピュータによって全ての処理が実行される必要はなく、ネットワークを介して接続された複数のコンピュータから構成されるシステムによって上記処理が実行されても良い。また、全ての処理をソフトウェアによって実現する必要はなく、一部または全部の処理を専用のハードウェアによって実現してもかまわない。

【0016】

図1は本発明の設計方法の流れを示すフローチャートである。図1(a)は基本的な設計方法の流れを示している。ステップS1では、特許文献1,2などに記載された従来方式によって、ハードディスクのアーム位置制御装置(マルチレートデジタル制御装置)の設計を行う。具体的には、例えば、制御対象の周波数特性や外乱周波数特性の実測値を、それぞれ最適な最小二乗近似が得られるようにフィルタリングを施した上で、必要な伝達関数モデルで最小二乗近似する。そして、この近似モデルにH∞制御理論の可解条件を満たす伝達関数を付加し、さらに設計パラメタとなる伝達関数を付加し、このモデルに関して、制御系にとってクリティカルとなる周波数帯域でのH∞ノルムを規定値に一致されるようにコンピュータで自動的に調整する。

【0017】

このような設計により、図3(a)に示すような構成のマルチレートデジタル制御装置が得られる。すなわち、低レートで動作する低レート補償器101と低レート補償器の出力を高レートに変換するレート変換器102と、高レートで動作する高レート補償器102とから構成されるマルチレートデジタル制御装置の構成が得られる。

【0018】

なお、ステップS1では、このような構成のデジタル制御装置を得ることが目的である

ので、上記で説明した以外の設計手法によってデジタル制御装置の構成を得てもかまわない。また、既に作成されているデジタル制御装置の構成情報を、たとえば、HDL(ハードウェア記述言語)などの形式として取得するようにしてもかまわない。

【0019】

ステップS2では、高レート補償器103をポリフェーズ分解する。ここでは、例としてレート変換器102が2倍のレート変換を行う場合を例として説明する。高レート変換器103の伝達関数をH(z)とすると、以下のようにポリフェーズ分解できる。

H(z)=E1(z2)+z−1E2(z2)

これを表したのが図2(a)(b)である。

【0020】

ステップS3では、上記のポリフェーズ分解に対して、ノーブル恒等変換を用いて高レート補償器を変換して、低レート構成(図2(c))にする。ノーブル恒等変換とは、伝達関数H(z)のフィルタの後にL倍のレート変換器を接続した構造と、L倍のレート変換器の後に伝達関数H(zL)のフィルタを接続した構造が機能的に等価であり、互いに置換できるという変換原理である。図2(b)のポリフェーズ分解に対してノーブル恒等変換を適用することで、図2(c)に示す低レート構成にする。これにより、レート変換器と高レート補償器の処理順序を入れ替えた図3(b)に示すようなデジタル制御装置が得られる。

【0021】

なお、ここでは2倍のレート変換を行う場合を例に説明したが、L分割のポリフェーズ分解は、

H(z)=Σk=0, L-1Ei(zL)z−k

として与えられるので、これにノーブル恒等変換を施すことで、L倍のレート変換を行うデジタル制御装置も低レート構成に変換することができる。

【0022】

なお、高レート補償器103が極を持つIIR形である場合には、単純に伝達関数をポリフェーズ分解することはできない。このような場合には、上記ステップS2におけるポリフェーズ分解処理を、図1(b)に示す方法で行う。すなわち、まず、高レート補償器103のインパルス応答を求める(ステップS21)。インパルス応答を基に高レート補償器103を近似的にFIR形フィルタに変換する(S22)。FIR形フィルタに対してはポリフェーズ分解が行えるので、FIR形フィルタに対してポリフェーズ分解する(S23)。このようにすることで、高レート補償器がIIR形フィルタの場合であっても、低レート構成を得ることができる。

【0023】

また、上記のようにして得た低レート構成(図3(b))において、低レート補償器1と低レート補償器2を合成して実装しても良い。例えば、低レート補償器1と低レート補償器2のフィードフォワード演算を合成して一括で実行し、低レート補償器1のフィードバック演算を後段で実行しても特性は同じである。また、サンプルレートが同じであるため、合成は容易である。

【0024】

上記の例では、ハードディスクのアーム位置制御装置を例に説明したが、観測信号のサンプリングレートよりも制御信号のサンプリングレートが高いマルチレート制御装置一般に本発明の設計方法は適用可能である。本発明は、例えば、電気自動車などで用いられるインホイールモータの制御装置に対して適用することができる。この例では角速度をフィードバックする方式であるが、このような制御装置における補償器の設計にも本発明を適用することができる。

【符号の説明】

【0025】

10 マルチレート制御装置

1,2,101 低レート補償器

3,102 レート変換器

103 高レート補償器

【特許請求の範囲】

【請求項1】

低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得ステップと、

前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換ステップと、

を含むデジタル制御装置の設計方法。

【請求項2】

前記変換ステップでは、前記高レート補償器のインパルス応答を求めてFIR型フィルタに変換した後に、ポリフェーズ分解を施す、

請求項1に記載のデジタル制御装置の設計方法。

【請求項3】

前記低レート補償器と前記第2の低レート補償器を合成して一つの低レート補償器を得る合成ステップをさらに含む、

請求項1または2に記載のデジタル制御装置の設計方法。

【請求項4】

低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得手段と、

前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換手段と、

を備える、デジタル制御装置の設計装置。

【請求項5】

前記変換手段は、前記高レート補償器のインパルス応答を求めてFIR型フィルタに変換した後に、ポリフェーズ分解を施す、

請求項4に記載のデジタル制御装置の設計装置。

【請求項6】

前記低レート補償器と前記第2の低レート補償器を合成して一つの低レート補償器を得る合成手段をさらに備える

請求項4または5に記載のデジタル制御装置の設計装置。

【請求項1】

低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得ステップと、

前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換ステップと、

を含むデジタル制御装置の設計方法。

【請求項2】

前記変換ステップでは、前記高レート補償器のインパルス応答を求めてFIR型フィルタに変換した後に、ポリフェーズ分解を施す、

請求項1に記載のデジタル制御装置の設計方法。

【請求項3】

前記低レート補償器と前記第2の低レート補償器を合成して一つの低レート補償器を得る合成ステップをさらに含む、

請求項1または2に記載のデジタル制御装置の設計方法。

【請求項4】

低レートで動作する低レート補償器と、前記低レート補償器の出力を高レートに変換するレート変換器と、高レートで動作する高レート補償器とを得る取得手段と、

前記高レート補償器をポリフェーズ分解し、該ポリフェーズ分解に対してノーブル恒等変換を用いて、第2の低レート補償器とレート変換器から構成される低レート構成に変換する変換手段と、

を備える、デジタル制御装置の設計装置。

【請求項5】

前記変換手段は、前記高レート補償器のインパルス応答を求めてFIR型フィルタに変換した後に、ポリフェーズ分解を施す、

請求項4に記載のデジタル制御装置の設計装置。

【請求項6】

前記低レート補償器と前記第2の低レート補償器を合成して一つの低レート補償器を得る合成手段をさらに備える

請求項4または5に記載のデジタル制御装置の設計装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−128590(P2012−128590A)

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願番号】特願2010−278522(P2010−278522)

【出願日】平成22年12月14日(2010.12.14)

【出願人】(502087460)株式会社トヨタIT開発センター (232)

【Fターム(参考)】

【公開日】平成24年7月5日(2012.7.5)

【国際特許分類】

【出願日】平成22年12月14日(2010.12.14)

【出願人】(502087460)株式会社トヨタIT開発センター (232)

【Fターム(参考)】

[ Back to top ]