デジタルAGC回路およびそれを用いた角速度センサ

【課題】本発明は、ゲイン算出等の演算において、乗算器を必要としない小型のデジタルAGC回路を提供することを目的とするものである。

【解決手段】本発明のデジタルAGC回路は、少なくとも2つのレベルの電荷量を出力するDA変換手段43と、このDA変換手段43から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段44と、この積分手段44から出力される積分値を所定の値と比較する比較手段45と、この比較手段45の出力に応じて前記DA変換手段43の出力を切り替えるDA切替手段46とにより構成してなるΣΔ変調器61と、振幅検出手段71と、ゲイン算出手段72と、置換演算手段73と、デジタルフィルタ48と、PLL回路91を有するタイミング制御手段93とで構成したものである。

【解決手段】本発明のデジタルAGC回路は、少なくとも2つのレベルの電荷量を出力するDA変換手段43と、このDA変換手段43から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段44と、この積分手段44から出力される積分値を所定の値と比較する比較手段45と、この比較手段45の出力に応じて前記DA変換手段43の出力を切り替えるDA切替手段46とにより構成してなるΣΔ変調器61と、振幅検出手段71と、ゲイン算出手段72と、置換演算手段73と、デジタルフィルタ48と、PLL回路91を有するタイミング制御手段93とで構成したものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、特にセンサデバイスにおけるセンサ素子の振動制御に用いられるデジタルAGC回路およびそれを用いた角速度センサに関するものである。

【背景技術】

【0002】

従来のこの種のデジタルAGC回路について、以下、図面を参照しながら説明する。

【0003】

図9は従来のデジタルAGC回路を示したものである。

【0004】

図9において、1はゲイン算出手段で、このゲイン算出手段1はメモリ2と乗算器4と加減算器5とで構成され、アナログの入力信号をA/D変換してデジタル化した入力信号Xに対するゲインGを決定する。次に、出力信号Zは、制御信号SEL1,SEL2でレジスタBからの現在設定されているゲインGと入力信号Xをセレクタ8,9で選択し、乗算器4でかけ算して求めるものである。

【0005】

なお、この出願の発明に関する先行技術文献情報としては、例えば、特許文献1が知られている。

【特許文献1】特開平7−336174号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上記した従来の構成においては、ゲイン算出等の演算において乗算器4をデジタルAGC回路もしくはその周辺回路において使用しているため、この乗算器4がその入出力ビット数および動作速度が増加するほど大きな回路となってしまうという課題を有していた。

【0007】

本発明は上記従来の課題を解決するもので、ゲイン算出等の演算において、乗算器を必要としない小型のAGC回路およびそれを用いた角速度センサを提供することを目的とするものである。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明は以下の構成を有するものである。

【0009】

本発明の請求項1に記載の発明は、少なくとも2つのレベルの電荷量を出力するDA変換手段と、このDA変換手段から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段と、この積分手段から出力される積分値を所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段と、デジタルフィルタと、PLL回路を有するタイミング制御手段とで構成したもので、この構成によれば、デジタルAGC回路を振幅検出手段と、ゲイン算出手段と、置換演算手段とで構成しているため、デジタルAGC回路への入力信号を逓倍してタイミング信号を生成するタイミング制御手段より出力される信号により動作するΣΔ変調器から出力される低ビットのパルス密度変調信号が置換演算手段によって振幅検出手段およびゲイン算出手段において算出されたゲインと置換演算されることになり、これにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号に変換可能な小型で低コストのデジタルAGC回路を提供することができるという作用効果を有するものである。

【0010】

本発明の請求項2に記載の発明は、特に、ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けたもので、この構成によれば、振幅検出手段から出力される振幅情報を元に、任意のゲイン特性を有するゲインをビットシフト演算手段と加算演算手段のみで乗算器を使用することなく算出可能となるため、小型で低コストのデジタルAGC回路を提供することができるという作用効果を有するものである。

【0011】

本発明の請求項3に記載の発明は、特に、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としたもので、この構成によれば、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としているため、EEPROMなどのROMに格納されたデータをもとにゲイン算出手段で算出するAGCゲイン特性、デジタルフィルタのフィルタ特性を変更することが可能となり、これにより、AGCしたい対象が変化してもROM値の変更のみで対応可能なデジタルAGC回路を提供することができるという作用効果を有するものである。

【0012】

本発明の請求項4に記載の発明は、特に、振幅検出回路にデジタルフィルタとピークホールド手段とを設けたもので、この構成によれば、振幅検出回路にデジタルフィルタとピークホールド手段とを設けているため、ΣΔ変調器から出力される低ビットのパルス密度変調信号をデジタルフィルタにより高調波ノイズを除去してマルチビット化し、そしてタイミング制御手段より出力されるタイミング信号を元にピークホールド手段によって入力信号の振幅を検出することになり、この場合、入力信号と非同期のクロックを用いてサンプリングする場合よりも、タイミング制御手段はPLL回路を有しているため、入力信号がピークになるタイミングで正確にサンプリングでき、これにより、安定して入力された信号の振幅情報を取得できることになるため、AGC特性が安定するという作用効果を有するものである。

【0013】

請求項5に記載の発明は、特に、デジタルフィルタをビットシフト演算手段で構成したもので、この構成によれば、デジタルフィルタをビットシフト演算手段で構成しているため、乗算器を用いることなく高精度のゲインコントロールが可能で、かつ低ノイズのデジタルAGC回路を提供することができるという作用効果を有するものである。

【0014】

本発明の請求項6に記載の発明は、駆動電極と、センス電極と、モニタ電極とを有するセンサ素子と、このセンサ素子を所定の振幅で振動駆動させるドライブ回路と、前記センサ素子におけるセンス電極から出力される信号を角速度出力信号に変換するセンス回路とを備え、前記ドライブ回路を、少なくとも2つのレベルの電荷量を出力するDA変換手段と、前記センサ素子におけるモニタ電極から出力される信号とDA変換手段とから出力される電荷を積分し、その積分値を保持する積分回路と、この積分回路から出力される積分値を少なくとも1つの所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ型変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段を備えたデジタルAGC回路と、デジタルフィルタと、PLL回路を有するタイミング制御手段と、駆動回路とで構成したもので、この構成によれば、デジタルAGC回路を振幅検出手段と、ゲイン算出手段と、置換演算手段とで構成しているため、デジタルAGC回路への入力信号を逓倍してタイミング信号を生成するタイミング制御手段より出力される信号により動作するモニタ電極から出力される信号がΣΔ型変調器から出力される低ビットのパルス密度変調信号が置換演算手段によって振幅検出手段およびゲイン算出手段において算出されたゲインと置換演算されることになり、これにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号が駆動回路から出力されるため、小型で低コストの角速度センサが得られるという作用効果を有するものである。

【0015】

本発明の請求項7に記載の発明は、特に、ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けたもので、この構成によれば、ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けているため、振幅検出手段から出力される振幅情報を基に、任意のゲイン特性を有するゲインをビットシフト演算手段と加算演算手段のみで乗算器を使用することなく算出することができるという作用効果を有するものである。

【0016】

本発明の請求項8に記載の発明は、特に、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としたもので、この構成によれば、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としているため、EEPROMなどのROMに格納されたデータをもとにゲイン算出手段で算出するAGCゲイン特性、デジタルフィルタのフィルタ特性を変更できることになり、これにより、用いるセンサ素子の特性やセンサの用途に応じてROMへ書き込む値を適宜変更できる角速度センサを提供することができるという作用効果を有するものである。

【0017】

本発明の請求項9に記載の発明は、特に、振幅検出回路にデジタルフィルタとピークホールド手段とを設けたもので、この構成によれば、振幅検出回路にデジタルフィルタとピークホールド手段とを設けているため、ΣΔ変調器から出力される低ビットのパルス密度変調信号を、デジタルフィルタにより高調波ノイズを除去してマルチビット化し、そしてタイミング制御手段より出力されるタイミング信号を元にピークホールド手段によって入力信号の振幅を検出することになり、この場合、入力信号と非同期のクロックを用いてサンプリングする場合よりも、タイミング制御手段はPLL回路を有しているため、正確に入力信号がピークになるタイミングでサンプリングでき、これにより、安定して入力された信号の振幅情報を取得できるという作用効果を有するものである。

【0018】

本発明の請求項10に記載の発明は、特に、デジタルフィルタをビットシフト演算手段で構成したもので、この構成によれば、デジタルフィルタをビットシフト演算手段で構成しているため、乗算器を用いることなく高精度のゲインコントロールが可能で、かつ低ノイズの角速度センサを提供することができるという作用効果を有するものである。

【発明の効果】

【0019】

以上のように本発明のデジタルAGC回路は、少なくとも2つのレベルの電荷量を出力するDA変換手段と、このDA変換手段から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段と、この積分手段から出力される積分値を所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段と、デジタルフィルタと、PLL回路を有するタイミング制御手段とで構成したもので、デジタルAGC回路を振幅検出手段と、ゲイン算出手段と、置換演算手段とで構成しているため、デジタルAGC回路への入力信号を逓倍してタイミング信号を生成するタイミング制御手段より出力される信号により動作するΣΔ変調器から出力される低ビットのパルス密度変調信号が置換演算手段によって振幅検出手段およびゲイン算出手段において算出されたゲインと置換演算されることになり、これにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号に変換可能な小型で低コストのデジタルAGC回路を提供することができるという優れた効果を奏するものである。

【発明を実施するための最良の形態】

【0020】

(実施の形態1)

以下、本発明の実施の形態1におけるデジタルAGC回路およびそれを用いた角速度センサについて、図面を参照しながら説明する。

【0021】

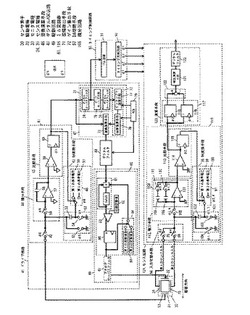

図1は本発明の実施の形態1におけるデジタルAGC回路を用いた角速度センサの回路図である。

【0022】

図1において、30はセンサ素子で、このセンサ素子30は振動体31と、この振動体31を振動させるための圧電体を有する駆動電極32と、振動状態に応じて電荷を発生する圧電体を有するモニタ電極33と、前記センサ素子30に角速度が印加されると電荷を発生する圧電体を有する一対のセンス電極とを設けている。また、前記センサ素子30における一対のセンス電極は、第1のセンス電極34と、この第1のセンス電極34と逆極性の電荷を発生する第2のセンス電極35とで構成されている。41はドライブ回路で、このドライブ回路41は入力切替手段42と、DA変換手段43、積分手段44、比較手段45、DA切替手段46、デジタルAGC回路47、デジタルフィルタ48および駆動回路49とで構成されている。また、前記ドライブ回路41における入力切替手段42は、振動体31におけるモニタ電極33と接続され、第6のタイミングΦ6で動作するアナログスイッチで構成されている。そしてまた、前記ドライブ回路41におけるDA切替手段46は、第1の基準電圧50および第2の基準電圧51を有し、そしてこの第1の基準電圧50と第2の基準電圧51を第6のタイミングΦ6で所定の信号により切り替えている。さらに、前記ドライブ回路41にはDA出力手段52を設けており、このDA出力手段52は前記DA切替手段46の出力信号が入力されるコンデンサ53と、このコンデンサ53の両端に接続され、かつ前記第5のタイミングΦ5で動作してコンデンサ53の電荷を放電するSW54,55により構成されている。そして、前記DA切替手段46とDA出力手段52とでDA変換手段43を構成し、かつこのDA変換手段43は第5のタイミングΦ5で前記コンデンサ53の電荷を放電し、さらに前記第6のタイミングΦ6で前記DA切替手段46が出力する基準電圧に応じた電荷を入出力するものである。56はSWで、このSW56には前記入力切替手段42とDA変換手段43の出力が入力され、前記第6のタイミングΦ6で出力するものである。

【0023】

44は積分手段で、この積分手段44には前記SW56の出力が入力されるもので、演算増幅器57と、この演算増幅器57の帰還に接続されるコンデンサ58とにより構成されている。そして、第6のタイミングΦ6で、前記積分手段44への入力信号がコンデンサ58により積分される。45は比較手段で、この比較手段45には前記積分手段44が出力する積分信号が入力され、そしてこの積分信号と所定の値とを比較する比較器59と、この比較器59が出力する1ビットデジタル信号が入力されるD型フリップフロップ60とにより構成されている。また、前記D型フリップフロップ60は前記第5のタイミングΦ5の開始時に前記1ビットデジタル信号をラッチしてラッチ信号を出力するものであり、このラッチ信号は、前記DA変換手段43のDA切替手段46に入力されて、第1の基準電圧50と第2の基準電圧51とを切り替えるものである。そして、前記入力切替手段42、DA変換手段43、積分手段44および比較手段45によりΣΔ変調器61を構成している。

【0024】

また、前記ΣΔ変調器61の出力するパルス密度変調信号はデジタルAGC回路47に入力され、かつこのデジタルAGC回路47は振幅検出手段71、ゲイン算出手段72、置換演算手段73により構成される。そして前記振幅検出手段71は、前記ΣΔ変調器61の出力するパルス密度変調信号が入力され高周波ノイズを除去してマルチビット信号を出力するデジタルローパスフィルタ74と、このデジタルローパスフィルタ74の出力するマルチビット信号が入力されこれをピークホールドして出力するピークホールド手段75と、前記ピークホールド手段75の出力する振幅情報が入力されてこれを平滑し振幅情報を出力するデジタルローパスフィルタ76により構成される。さらに前記振幅検出手段71の出力する振幅情報は前記ゲイン算出手段72に入力され、かつこのゲイン算出手段72はビットシフト演算手段77と加算演算手段78とで構成される。また、前記ゲイン算出手段72では入力された振幅情報に対して、所定係数値のビットシフト演算と所定係数値の加算演算を行い、ゲイン情報を算出する。ここで前記ビットシフト演算手段77および加算演算手段78で用いられる係数値はROM79より読み出されて供給される。そして、前記ゲイン算出手段72の出力するゲイン情報と、前記ΣΔ変調器61の出力するパルス密度変調信号が前記置換演算手段73に入力されて置換演算されることにより、ゲインコントロールされたマルチビットのパルス密度変調信号として前記デジタルAGC回路47より出力されることとなる。さらにこの前記デジタルAGC回路47より出力されるゲインコントロールされたマルチビットのパルス密度変調信号は前記デジタルフィルタ48に入力される。

【0025】

ここで前記デジタルフィルタ48の構成例を図2に示す。また前記デジタルフィルタ48の演算処理に用いられる係数値は前記ROM79より読み出されて供給される構成となっている。前記デジタルフィルタ48によりΣΔ変調されたことによる高周波ノイズを除去し、そしてセンサ素子30の共振周波数のみを抽出してノイズ成分を除去したマルチビット信号は前記駆動回路49に入力される。

【0026】

前記駆動回路49は、2値を保持しているデジタル値出力手段80と、デジタルフィルタ48からの出力信号と前記デジタル値出力手段80の出力を加算し積分する加積分演算手段81と、この加積分演算手段81からの出力を比較定数値82と比較する値比較手段83と、この値比較手段83の出力に応じて前記デジタル値出力手段80の出力するデジタル値を切り替える値切り替え手段84と、値比較手段83の出力を所定タイミングでラッチするフリップフロップ85とにより構成されるデジタルΣΔ変調器86を有している。前記デジタルΣΔ変調器86により前記デジタルフィルタ48が出力するマルチビット信号は1ビットのパルス密度変調信号に変調されて出力され、かつこのパルス密度変調信号はアナログローパスフィルタ87に入力され、さらにセンサ素子30を駆動するのに有害な周波数成分はフィルタリングされて、センサ素子30に出力される。以上の構成により前記振動体31の振動が一定振幅となるように調整するものである。

【0027】

91はPLL回路で、このPLL回路91はモニタ電極33が出力するモニタ信号を元とした信号を逓倍し、位相ノイズを時間的に積分し低減して出力するものであり、前記ドライブ回路41におけるデジタルローパスフィルタ74が出力する信号が入力されることになる。92はタイミング生成回路で、このタイミング生成回路92は前記PLL回路91から出力されるモニタ信号を逓倍したタイミング信号を前記ドライブ回路41に供給するとともに、このタイミング信号をもとに、モニタ信号の2周期間を第1のタイミングΦ1、第2のタイミングΦ2、第3のタイミングΦ3、第4のタイミングΦ4に分割してこのタイミング信号を生成して出力するものである。そして、前記PLL回路91とタイミング生成回路92とでタイミング制御回路93を構成している。94は入力切替手段で、この入力切替手段94は前記センサ素子30における第1のセンス電極34と接続され前記第2のタイミングΦ2で動作するアナログスイッチ95(以下、SWと記す)と、第2のセンス電極35と接続され前記第4のタイミングΦ4で動作するアナログスイッチ96とで構成されている。この構成により、入力切替手段94は、第1のセンス電極34または第2のセンス電極35からの入力信号を第2のタイミングΦ2または第4のタイミングΦ4で切り替えて出力することになる。97はDA切替手段で、このDA切替手段97は、第1の基準電圧99および第2の基準電圧100を有し、そしてこの第1の基準電圧99と第2の基準電圧100を所定の信号により切り替えるものである。101はDA出力手段で、このDA出力手段101は前記DA切替手段97の出力信号が入力されるコンデンサ102と、このコンデンサ102の両端に接続され、かつ前記第1のタイミングΦ1と第3のタイミングΦ3で動作してコンデンサ102の電荷を放電するSW103,104とにより構成されている。そして、前記DA切替手段97とDA出力手段101とでDA変換手段98を構成し、かつこのDA変換手段98は第1のタイミングΦ1と第3のタイミングΦ3で前記コンデンサ102の電荷を放電し、さらに前記第2のタイミングΦ2と第4のタイミングΦ4で前記DA切替手段97が出力する基準電圧に応じた電荷を入出力するものである。

【0028】

105はSWで、このSW105には前記入力切替手段94とDA変換手段98の出力が入力され、前記第2のタイミングΦ2と第4のタイミングΦ4で出力するものである。106は積分回路で、この積分回路106には前記SW105の出力が入力されるもので、演算増幅器107と、この演算増幅器107の帰還に並列に接続される一対のコンデンサ108,109と、このコンデンサ109に接続される一対のSW110,111とにより構成されている。また、SW110は第1のタイミングΦ1と第2のタイミングΦ2で動作し、前記積分回路106への入力信号がコンデンサ108に積分されて積分値が保持されることになる。そしてまた、SW111は前記第3のタイミングΦ3と第4のタイミングΦ4で動作し、前記積分回路106への入力信号がコンデンサ109に積分されて積分値が保持されることになる。113は比較手段で、この比較手段113には積分手段112が出力する積分信号が入力され、そしてこの積分信号と所定の値とを比較する比較器114と、この比較器114が出力する1ビットデジタル信号が入力されるD型フリップフロップ115とで構成されている。また、前記D型フリップフロップ115は前記第2のタイミングΦ2と第4のタイミングΦ4の開始時に前記1ビットデジタル信号をラッチしてラッチ信号を出力するものであり、このラッチ信号は、前記DA変換手段98のDA切替手段97に入力されて第1の基準電圧99と第2の基準電圧100とを切り替えるものである。そして、前記入力切替手段94、DA変換手段98、積分手段112および比較手段113によりΣΔ変調器116を構成している。

【0029】

またこのΣΔ変調器116は上記構成により、前記センサ素子30における一対のセンス電極34,35より出力される電荷をΣΔ変調し、1ビットデジタル信号に変換して出力するものである。

【0030】

117はラッチ回路で、このラッチ回路117には前記ΣΔ変調器116の比較手段113における比較器114より出力される1ビットデジタル信号が入力され、かつ前記1ビットデジタル信号をラッチする一対のD型フリップフロップ119により構成されている。また、D型フリップフロップ118は第2のタイミングΦ2で前記1ビットデジタル信号をラッチするものであり、かつD型フリップフロップ119は第4のタイミングΦ4で前記1ビットデジタル信号をラッチするものである。120は差分演算手段で、この差分演算手段120には前記ラッチ回路117における一対のD型フリップフロップ119がラッチして出力する一対の1ビットデジタル信号が入力され、そしてこの一対の1ビットデジタル信号の差を演算する1ビット差分演算を置換処理により実現するものである。つまり、差分演算手段120に入力される一対の1ビットデジタル信号が、“00”“01”“10”“11”である時、それぞれ“0”“−1”“1”“0”と置き換えて出力する構成となっている。121は補正演算手段で、この補正演算手段121には前記差分演算手段120が出力する1ビット差分信号が入力され、この1ビット差分信号と所定の補正情報との補正演算を置換処理により実現するものである。つまり、上記したように補正演算手段121に入力される1ビット差分信号が“0”“1”“−1”であり、例えば、補正情報が“5”である場合にはそれぞれ“0”“5”“−5”と置き換えて出力する構成となっている。122はデジタルフィルタで、このデジタルフィルタ122には前記補正演算手段121より出力されるデジタル差分信号が入力され、ノイズ成分を除去するフィルタリング処理を行うものである。そして、前記ラッチ回路117、差分演算手段120、補正演算手段121およびデジタルフィルタ122により演算手段123を構成している。また、この演算手段123は、第2、第4のタイミングで一対の1ビットデジタル信号をラッチして、差分演算、補正演算、フィルタリング処理を行い、マルチビット信号を出力することになる。そしてまた、前記タイミング制御回路93とΣΔ変調器116および演算手段123によりセンス回路124を構成している。

【0031】

以上のように構成された本発明の実施の形態1における角速度センサについて、次にその動作を説明する。

【0032】

前記センサ素子30の駆動電極32に駆動信号を加えると、前記振動体31が共振し、モニタ電極33に電荷が発生する。このモニタ電極33に発生した電荷をドライブ回路41におけるΣΔ変調器61に入力し、パルス密度変調信号へと変換する。そしてこのΣΔ変調器61の出力するパルス密度変調信号をデジタルAGC回路47へ入力し、このデジタルAGC回路47がもつ振幅検出手段71によりモニタ電極33より発生した信号の振幅情報を取得し、この振幅情報をゲイン算出手段72に入力してゲイン情報を演算により取得する。ゲイン算出手段72の出力するゲイン情報と前記ΣΔ変調器61の出力するパルス密度変調信号が置換演算手段73に入力されて、前記振動体31の振動が一定振幅となるようゲインコントロールされたマルチビットのパルス密度変調信号が出力される。このゲインコントロールされたマルチビットのパルス密度変調信号をデジタルフィルタ48に入力し、前記振動体31の共振周波数のみを抽出したノイズ成分が除去されたマルチビット信号を出力する。そしてこのデジタルフィルタ48の出力するマルチビット信号を駆動回路49に入力し、さらにこの駆動回路49を構成するデジタルΣΔ変調器86およびアナログフィルタ87より駆動信号がセンサ素子30における駆動電極32へ出力され、前記振動体31の振動が一定振幅となるように調整するものである。この場合におけるΣΔ変調器61、デジタルAGC回路47、デジタルフィルタ48、駆動回路49の動作を以下に説明する。

【0033】

ΣΔ変調器61はタイミング制御回路93より出力されるモニタ信号に同期したタイミングである第1のタイミングΦ5、第2のタイミングΦ6を繰り返すことによって動作するもので、第1のタイミングΦ5ではセンサ素子30におけるモニタ電極33から出力される信号がΣΔ変調されて1ビットデジタル信号に変換される。

【0034】

上記した2つのタイミングでの動作をひとつずつ説明する。まず、第1のタイミングΦ5では、積分手段44におけるコンデンサ58に保持されている積分値を比較する前記比較手段45の比較器59より出力される1ビットデジタル信号が、第1のタイミングΦ5の立ち上がり時にD型フリップフロップ60にラッチされ、このラッチ信号が前記DA変換手段43のDA切替手段46に入力される。また、DA出力手段52におけるSW54とSW55がONになって、コンデンサ53に保持されている電荷が放電される。

【0035】

次に第2のタイミングΦ6では、前記DA切替手段46に入力されたラッチ信号に応じて基準電圧50,51が切り替えられてコンデンサ53に入力され、かつDA変換手段43より切り替えられた基準電圧に応じた電荷が出力される。また、入力SW42がONになり、前記センサ素子30のモニタ電極33より発生する電荷が入力される。さらに、積分手段44におけるSW56がONになり、前記入力SW42とDA変換手段43から出力される電荷が積分手段44に入力される。これにより第2のタイミングΦ6では、積分手段44におけるコンデンサ58に、図3(a)の斜線部で示される電荷量とDA変換手段43より出力される電荷量の総和が積分されて保持されることになる。

【0036】

上記した第1のタイミングΦ5および第2のタイミングΦ6での以上の動作によりセンサ素子30のモニタ電極33から出力される電荷がΣΔ変調され、第1のタイミングΦ5の信号の立ち上がり時に1ビットデジタル信号として出力されることになる。

【0037】

次にデジタルAGC回路47について動作を説明する。前記ΣΔ変調器61の出力するパルス密度変調信号が前記振幅検出手段71の有するデジタルローパスフィルタ74に入力されて高周波ノイズを除去し、図4(a)で示されるマルチビット信号へと変換される。このマルチビット信号がピークホールド手段75へ入力され、図4(b)で示されるピーク信号へと変換される。さらに、正のピークだけでなく負のピークも検出しその差分をとることでさらに精度が向上する。この時、ΣΔ変調器61によるモニタ電極35より出力されるモニタ信号のサンプリングが、このモニタ信号を逓倍した信号により行われているため、正確にピークのポイントを検出でき、そしてこれを基にAGC制御が行われるため、低ノイズで高精度のAGC制御が実現でき、これにより、このデジタルAGC回路47を用いて低ノイズで高精度の角速度センサを提供することができるという効果を有することになる。このようにピークホールド手段75によりピークホールドされた信号が、デジタルローパスフィルタ76に入力されて平滑されることにより、ノイズが除去された前記モニタ電極33の出力する信号の振幅に応じた振幅情報を得ることができる。次に振幅検出手段71の出力する振幅情報がゲイン算出手段72へと入力され、ゲイン情報が算出される。ここで、センサ素子30の振動振幅を一定に制御するためのAGCゲイン特性が図5で示される場合、(数1)に示すように、ビットシフト演算および加算演算を行うことにより、現在必要なゲイン情報を算出することができる。

【0038】

【数1】

【0039】

このとき、“+c”は定数値“B”の加算処理であり、“A*x”の演算は“A”を“−1.25”としたい場合には、(数2)に示すように表記し直すことが可能であるため、ビットシフト演算および加算演算と±は符合ビットの反転のみで(数2)の演算を行うことが可能となる。

【0040】

【数2】

【0041】

このように、ゲイン算出手段72の有するビットシフト演算手段77と加算演算手段78により、センサ素子30の振動振幅を一定に制御するためのAGCゲイン情報が算出される。このとき、傾き“A”、切片“B”を固定ではなくROM79より読み出された値により決定する構成とし、決定された値によりビットシフト演算手段77でのシフト量および加算演算手段78で加算される切片“B”の値を変更することによって、AGCゲイン特性を容易に変化させることが可能となる。これにより、センサ素子の特性やセンサが用いられる用途に応じてAGCゲイン特性をROM値の書き換えのみで変更可能な角速度センサを提供することができるという効果が得られるものである。

【0042】

次にゲイン算出手段72から出力されるゲイン情報“G”と、前記ΣΔ変調器61が出力するパルス密度変調信号が前記置換演算手段73に入力される。ここで、前記ΣΔ変調器61が出力するパルス密度変調信号は“1”もしくは“−1”の1bit信号であるため、これをゲイン情報“G”と置換、すなわち“−1”⇒“−G”、“1”⇒“G”と置き換えることにより、乗算器を用いること無しに、“入力信号×G”の演算を実現することが可能となる。よって、前記置換演算手段73によりゲインの演算がなされる。ここで、ΣΔ変調器61は1bitのΣΔ変調器として説明しているが、複数bit出力のΣΔ変調器であったとしてもΣΔ変調器の出力は例えば2bitであれば“00,01,611”の4値に限定でき、“00,01,611”⇒“−G,−G/2,G/2,G”と置き換えることによって、上記と同様の構成により“入力信号×G”が実現可能となるものである。以上のようにデジタルAGC回路47からセンサ素子30の振動振幅を一定に制御するためにゲインコントロールされたマルチビットのパルス密度変調信号が出力されることになるため、デジタルAGC回路47を乗算器を用いることなしに低コストで、かつ高精度にデジタル回路により実現できるという効果が得られるものである。

【0043】

次に前記デジタルAGC回路47から出力されるゲインコントロールされたマルチビットのパルス密度変調信号が入力されるデジタルフィルタ48について動作を説明する。ここで図2は前記デジタルフィルタ48の構成例である。図2の141はIIRフィルタで一般的なIIRの構成を示しており、142〜146はこのフィルタの特性を決定するゲイン演算部であり、147,148は加算演算部、149,150は遅延部である。ここで、フィルタの特性を決定するゲイン演算部142〜146のゲイン係数を例えば{a0,a1,a2,b0,b1}={1,81.71475,−0.75}としたい場合、(数3)に示すように表記し直すことが可能であり、これらのゲイン計算はゲイン算出手段において説明した通り、ビットシフト演算により演算可能である。

【0044】

【数3】

【0045】

また、151〜153はビットシフト演算部であり、これらの値を(数4)で示すように演算を行うことにより、最初にc0を+7ビットシフト(×128)として演算した後にc2において−7ビットシフト(1/128)することによって、ビットシフト演算による丸め誤差等の演算誤差を低減することが可能となる。

【0046】

【数4】

【0047】

以上の構成/動作により、ビットシフト演算と加算演算のみによって演算精度を確保した上でフィルタ演算を行うことが可能な低コストのデジタルフィルタを得ることが可能であるという効果を有するものである。また、上記ビットシフトによるゲイン計算はFIR等他のフィルタ形式でも利用可能であり、図2のIIRのフィルタ構成を係数を変えて縦続接続することによって、必要なフィルタ特性を実現することが可能となるものである。さらに、センサ素子30を所定の共振周波数のみで振動させるにあたっては、バンドパスフィルタ特性を持つことが望ましい。よって、前記デジタルAGC回路47から出力されるパルス密度変調信号がデジタルフィルタ48に入力され、ノイズ成分がフィルタリングされゲインコントロールされたマルチビット信号が出力されることになる。

【0048】

さらに、ビットシフト演算部154を追加で設けた場合の動作について説明する。まず、デジタルAGC回路47におけるゲイン情報“G”を例えば、“128±128”の“0〜256”の値とし、ゲイン係数{d2}={1/128}={1/2^7}の−7ビットシフト(1/128)として置換演算およびビットシフトを行うことにより、デジタルAGC回路47およびデジタルフィルタ48により“1/128”の分解能で0倍から2倍までの可変ゲインを演算精度を確保したまま実現することが可能となる。さらにこのゲイン分解能およびゲイン幅は、ゲイン情報“G”の取り得る値とゲイン係数{d2}のビットシフト量を必要な量だけ確保するだけで、任意に設定可能である。

【0049】

以上のように構成/動作させることにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号およびマルチビット信号に変換可能な小型・低コストで、かつ低ノイズでそのAGC特性およびフィルタ特性が容易に可変なデジタルAGC回路およびデジタルフィルタが得られるという効果を有するものである。また、上記ビットシフト演算でのビットシフト量をROM79に格納されたデータにより決定する構成とすることにより、センサ素子の特性やセンサが用いられる用途に応じてフィルタ特性をROM79に格納する値を書き換えるだけで変更可能な角速度センサを提供することができるという効果が得られるものである。

【0050】

次に駆動回路49の動作を説明する。デジタルΣΔ変調器86の加積分演算手段81に前記デジタルフィルタ48から出力されるマルチビット信号と、所定の2値を保持しているデジタル値出力手段80のどちらかの値を出力する値切り替え手段84より出力される定数値が加積分演算手段81へと入力され、加算して積分される。この加積分演算手段81から出力される積分値が比較定数値82と値比較手段83により比較されて比較結果が出力される。そして、この比較結果がフリップフロップ85により所定のタイミングでラッチされて出力される。このフリップフロップ85の出力により値切り替え手段84より出力される定数値が切り替えられることになる。この時、加積分演算手段81の出力値が比較定数値82より小さい場合には、デジタル値出力手段80の2値のうちの大きい方の値が、逆の場合には小さい方の値が選択されて出力されるように動作する。この動作を繰り返すことによりフリップフロップ85より、前記デジタルフィルタ48が出力するマルチビット信号が、1ビットのパルス密度変調信号に変調されて出力されることになる。ここで、デジタルΣΔ変調器86に入力される信号が例えば、10bit(=±9bit)である場合は、比較定数値82を“0”デジタル値出力手段80の2値を“511”“−511”以上とすることが望ましい。

【0051】

以上の構成により、センサ素子30のモニタ電極33より出力された信号が、ΣΔ変調器61によりパルス密度変調信号に変換され、デジタルAGC回路47によりセンサ素子30の振動を一定に制御するよう所定のAGCゲイン特性で振幅調整され、さらにデジタルフィルタ48によりノイズが除去されてマルチビット化される。この振幅調整されたマルチビット信号がデジタルΣΔ変調器86によりΣΔ変調されて1bitのパルス密度変調信号に変換され、この信号がセンサ素子30における駆動電極32に出力される。この時、1bitのパルス密度変調信号はモニタ電極33より出力された信号の周波数成分をデジタルAGC回路47により振幅調整されて含んでいることとなり、この信号がセンサ素子30に出力されることによって、前記振動体31の振動が所定の共振周波数において一定振幅で振動することになる。このような駆動回路49を構成することにより、高精度DA変換器を用いることなく大半をデジタル回路で実現することができるため、低コストで、かつ高精度の角速度センサを提供することができるという効果が得られるものである。

【0052】

なお、ΣΔ変調ではオーバーサンプリングを行い、その量子化ノイズが高域にノイズジェーピングされるため、高周波成分のノイズ成分を含むが、センサ素子30の応答がそのような高周波に応答できないため、パルス密度変調信号のサンプリング周波数でなく、オーバーサンプリングされた所定の周波数成分で振動することになる。また、センサ素子30の高周波での応答ゲインが高くて、このような高周波成分のノイズが問題になる場合には、デジタルΣΔ変調器86の出力信号のうち問題となる周波数成分を低減するよう設定されたアナログフィルタ87を追加することによって、さらに低ノイズで、高精度のドライブ回路41を実現することが可能となるものである。

【0053】

さらに、タイミング制御回路93に、図6(a)に示される正弦波信号が入力され、前記PLL回路91で逓倍した信号をもとにタイミング生成回路92により図6(b)で示される第1のタイミングΦ1、第2のタイミングΦ2、第3のタイミングΦ3、第4のタイミングΦ4を形成する。そして、このタイミング信号が前記ΣΔ変調器116および演算手段123に、SWの切替およびラッチ回路のラッチタイミングとして入力される。また、位相器で位相を90度シフトさせた前記正弦波信号を所定の基準電圧(図示せず)と比較する電圧コンパレータ(図示せず)に入力し、そしてその出力をロジック回路(図示せず)に入力するようにした場合でも、前記タイミング信号Φ1、Φ2、Φ3、Φ4を形成することは可能であるが、この場合、正弦波信号の電圧ノイズおよび温度変化や電源変動による電圧ノイズが位相ノイズとして表れることになる。この位相ノイズは、入力信号や積分切替手段を切り替えるタイミングノイズとして信号処理の精度に悪影響を与える要因となるが、前記PLL回路91を用いて時間的に積分され位相ノイズが低減されたタイミング信号とすることにより、切替タイミングノイズを低減し信号処理の精度を高めることができるものである。そして、前記センサ素子30が図1に図示している駆動方向に速度Vで屈曲振動している状態において、前記振動体31の長手方向の中心軸周りにセンサ素子30が角速度ωで回転すると、このセンサ素子30にF=2mV×ωのコリオリ力が発生する。このコリオリ力により前記センサ素子30が有する一対のセンス電極34,35に、図6(c)および図6(d)に示すように電荷が発生する。そしてこのセンス電極34,35に発生する電荷はコリオリ力により発生するため、前記モニタ電極33に発生する信号より位相が50度進んでいる。そしてまた、前記一対のセンス電極34,35に発生した出力信号は図6(c)および図6(d)に示す通り、正極性信号と負極性信号の関係にある。

【0054】

この場合におけるΣΔ変調器116の動作を以下に説明する。このΣΔ変調器116は第1のタイミングΦ1、第2のタイミングΦ2、第3のタイミングΦ3および第4のタイミングΦ4を繰り返すことによって動作するもので、第1のタイミングΦ1および第2のタイミングΦ2ではセンサ素子30における第1のセンス電極34から出力される正極性信号がΣΔ変調されて1ビットデジタル信号に変換され、また第3のタイミングΦ3および第4のタイミングΦ4では第2のセンス電極35から出力される負極性信号がΣΔ変調されて1ビットデジタル信号に変換される。

【0055】

上記した4つのタイミングでの動作をひとつずつ説明する。まず第1のタイミングΦ1では、積分手段112におけるコンデンサ108と接続されているSW110がONになり、このコンデンサ108に保持されている積分値が比較手段113における比較器114に入力され比較結果が1ビットデジタル信号として出力される。また、DA変換手段98におけるSW103と104がONになりコンデンサ102に保持されている電荷が放電される。

【0056】

次に第2のタイミングΦ2では、前記比較手段113の比較器114より出力される1ビットデジタル信号が第2のタイミングΦ2の立ち上がり時にD型フリップフロップ115にラッチされ、このラッチ信号が前記DA変換手段98のDA切替手段97に入力される。この入力されたラッチ信号に応じて基準電圧が第1の基準電圧99または第2の基準電圧100に切り替えられてコンデンサ102に入力され、DA変化手段98より切り替えられた基準電圧に応じた電荷が出力される。それとともに、入力切替手段94ではSW95がONになり、前記センサ素子30の第1のセンス電極34より発生する電荷が出力される。さらに、積分手段112におけるSW105がONになり、前記入力切替手段94とDA変換手段98から出力される電荷が積分回路106に入力される。これにより第2のタイミングΦ2では、積分回路106におけるコンデンサ108に、図6(c)の斜線部で示される電荷量とDA変換手段98より出力される電荷量の総和が積分されて保持されることになる。

【0057】

上記した第1のタイミングΦ1および第2のタイミングΦ2での以上の動作によりセンサ素子30のセンス電極34から出力される振幅値の半分に相当する電荷量がΣΔ変調されることになる。

【0058】

また、第1のタイミングΦ1および第2のタイミングΦ2での動作と同様に、第3のタイミングΦ3および第4のタイミングΦ4では、センサ素子30の第2のセンス電極35から出力される振幅値の半分に相当する電荷量がΣΔ変調され、1ビッデジタル信号に変換されて出力されることになる。以上の動作により、センサ素子30における一対のセンス電極34,35から出力される電荷の振幅値の半分に相当する電荷量が一つのΣΔ変調器116によりΣΔ変調されて一対の1ビットデジタル信号として上記タイミングで出力されることになる。

【0059】

そしてまた、センサ素子30における第1のセンス電極34および第2のセンス電極35から出力される電荷は、角速度によるコリオリ力で発生する、モニタ電極33に発生する信号より位相が90度進んだセンス信号だけでなく、モニタ信号と同相の不要信号があるため、センサ素子30における第1のセンス電極34および第2のセンス電極35からセンス信号と不要信号の合成信号が出力される場合について説明する。角速度によるコリオリ力で発生するセンス信号は、図6(c)(d)で示され、そして上記で説明した通り、第2のタイミングΦ2と第4のタイミングΦ4で、積分回路106により図6(c)(d)の斜線部で示される電荷量、つまり、振幅値の半分に相当する電荷量が積分されることになる。さらに、第1のセンス電極34および第2のセンス電極35より発生する不要信号は図6(e)(f)で示され、そして前記センス信号と同様に第2のタイミングΦ2と第4のタイミングΦ4で、図6(e)(f)の斜線部で示される電荷量、つまり、不要信号の振幅の最大値から最小値までの区間の電荷量が積分されている。これは、振幅の中央値を基準に積分するとキャンセルされて“0”の電荷量となるものである。つまり、第2のタイミングΦ2と第4のタイミングΦ4での積分手段112の動作により、不要信号がキャンセルされてセンス信号の振幅に応じた電荷量が積分される、いわゆる同期検波処理が一対の入力信号のそれぞれに対し実施されることになる。よって、上記不要信号のない場合の動作の説明と同様に、前記ΣΔ変調器116からは同期検波処理された信号がΣΔ変調され、1ビットデジタル信号に変換されて出力されることになる。

【0060】

次に、演算手段123について、その動作を説明する。まず、第2のタイミングΦ2で、前記ΣΔ変調器116の比較手段113における比較器114より出力される1ビットデジタル信号が、ラッチ回路117のD型フリップフロップ118にラッチされる。また、第4のタイミングΦ4で、前記ΣΔ変調器116の比較手段113における比較器114より出力される1ビットデジタル信号が、ラッチ回路117のD型フリップフロップ118,119にラッチされる。

【0061】

この一対のD型フリップフロップ118,119にラッチされた一対の1ビットデジタル信号は、上記で説明した通り、センサ素子30における一対のセンス電極34,35より出力された信号の不要信号を除いた振幅値の半分に相当する電荷量をそれぞれΣΔ変調によりデジタル値に変換したものである。次に、前記ラッチ回路117が出力する一対の1ビットデジタル信号が1ビット差分演算手段120に入力され、この一対の1ビットデジタル信号の差が演算されて1ビット差分信号が出力される。ここで、第1のタイミングΦ1での1ビット差分信号は、一つ前の周期における第2のタイミングΦ2、第4のタイミングΦ4でラッチされた1ビットデジタル信号の差であり、この1ビット差分信号は、図6(c)(d)で示されるセンサ素子30における一対のセンス電極34,35より出力される信号の不要信号を除いた振幅値を表す信号となる。次に、1ビット差分演算手段120が出力する1ビット差分信号が補正演算手段121に入力され、この1ビット差分信号と所定の補正情報との補正演算が置換処理により行われる。この補正演算は、上記したように、1ビット差分信号が“0”“1”“−1”の3値に限られることを利用して、例えば所定の補正情報が“5”である場合に、補正演算手段に入力される1ビット差分信号“0”“1”“−1”を、それぞれ“0”“5”“−5”と置換処理することにより乗算を実現して信号の補正が可能となるものである。

【0062】

(実施の形態2)

以下、本発明の実施の形態2におけるデジタルAGC回路を用いた角速度センサについて、図面を参照しながら説明する。

【0063】

図7は本発明の実施の形態2におけるデジタルAGC回路を用いた角速度センサの回路図である。なお、本発明の実施の形態2においては、上記した本発明の実施の形態1と同様の構成を有するものについては、同一番号を付しており、その説明は省略する。

【0064】

駆動回路49はDA変換器131により構成される。この時、図8(a)で示されるような信号が前記ドライブ回路41におけるΣΔ変調器61へ入力され、図8(b)で示される1bitのパルス密度変調信号へと変換される。そしてこの1bitのパルス密度変調信号が前記デジタルAGC回路47へ入力されて任意のAGCゲイン特性によりゲインコントロールされた図8(c)で示されるような±G[LSB]のマルチビットのパルス密度変調信号に変換され、このマルチビットのパルス密度変調信号が直接前記DA変換器131に入力され、前記DA変換器131よりパルス密度変調信号が図8(d)で示されるようなG[LSB]の値に応じた振幅電圧の駆動信号として出力され、前記センサ素子30におけるモニタ電極33へと入力されることになる。この駆動信号はモニタ電極33より出力された信号の所定の周波数成分をデジタルAGCにより振幅調整されて含んでいることになり、この信号がセンサ素子30に出力されることによって、前記振動体31の振動が所定の共振周波数において一定振幅で振動するよう制御されることになる。以上のように、ΣΔ変調器61、デジタルAGC回路47、DA変換器131という少ない回路点数によりドライブ回路が構成でき、これにより、小型で、かつ低コストの角速度センサを提供することができるという効果が得られるものである。さらに、振動させたい所定の周波数以外でセンサ素子の応答ゲインが高い不要な周波数成分やΣΔ変調による高周波ノイズを除去するように周波数特性が設定されたデジタルフィルタ48もしくはアナログフィルタ87を追加することにより、さらに高精度で、かつ低ノイズのドライブ回路を有する角速度センサを提供することができるという効果が得られるものである。

【産業上の利用可能性】

【0065】

本発明のデジタルAGC回路およびそれを用いた角速度センサは、ゲイン算出等の演算において、乗算器を必要としない小型のAGC回路およびそれを用いた角速度センサを提供することができるという効果を有するものであり、特に、センサデバイスにおけるセンサ素子の振動制御に用いられるデジタルAGC回路とそれを用いた角速度センサとして有用なものである。

【図面の簡単な説明】

【0066】

【図1】本発明の実施の形態1におけるデジタルAGC回路を用いた角速度センサの回路図

【図2】同角速度センサのドライブ回路におけるデジタルフィルタの回路図

【図3】(a)〜(c)ΣΔ変調器の動作状態を示す図

【図4】(a)、(b)デジタルAGC回路の動作状態を示す図

【図5】本発明の実施の形態1におけるAGC回路のAGCゲイン特性を示す図

【図6】(a)〜(f)同デジタルAGC回路を用いた角速度センサの動作状態を示す図

【図7】本発明の実施の形態2におけるデジタルAGC回路を用いた角速度センサの回路図

【図8】(a)〜(d)同角速度センサの動作状態を示す図

【図9】従来のΣΔ型AD変換器の回路図

【符号の説明】

【0067】

30 センサ素子

32 駆動電極

33 モニタ電極

34,35 センス電極

41 ドライブ回路

43,98 DA変換手段

44 積分手段

45 比較手段

46 置換演算手段

47 デジタルAGC回路

48 デジタルフィルタ

49 駆動回路

61,116 ΣΔ変調器

71 振幅検出手段

72 ゲイン算出手段

73 置換演算手段

75 ピークホールド手段

77 ビットシフト演算手段

79 ROM

91 PLL回路

93 タイミング制御手段

97 DA切替手段

106 積分回路

113 比較手段

124 センス回路

154 ビットシフト演算手段

【技術分野】

【0001】

本発明は、特にセンサデバイスにおけるセンサ素子の振動制御に用いられるデジタルAGC回路およびそれを用いた角速度センサに関するものである。

【背景技術】

【0002】

従来のこの種のデジタルAGC回路について、以下、図面を参照しながら説明する。

【0003】

図9は従来のデジタルAGC回路を示したものである。

【0004】

図9において、1はゲイン算出手段で、このゲイン算出手段1はメモリ2と乗算器4と加減算器5とで構成され、アナログの入力信号をA/D変換してデジタル化した入力信号Xに対するゲインGを決定する。次に、出力信号Zは、制御信号SEL1,SEL2でレジスタBからの現在設定されているゲインGと入力信号Xをセレクタ8,9で選択し、乗算器4でかけ算して求めるものである。

【0005】

なお、この出願の発明に関する先行技術文献情報としては、例えば、特許文献1が知られている。

【特許文献1】特開平7−336174号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上記した従来の構成においては、ゲイン算出等の演算において乗算器4をデジタルAGC回路もしくはその周辺回路において使用しているため、この乗算器4がその入出力ビット数および動作速度が増加するほど大きな回路となってしまうという課題を有していた。

【0007】

本発明は上記従来の課題を解決するもので、ゲイン算出等の演算において、乗算器を必要としない小型のAGC回路およびそれを用いた角速度センサを提供することを目的とするものである。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明は以下の構成を有するものである。

【0009】

本発明の請求項1に記載の発明は、少なくとも2つのレベルの電荷量を出力するDA変換手段と、このDA変換手段から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段と、この積分手段から出力される積分値を所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段と、デジタルフィルタと、PLL回路を有するタイミング制御手段とで構成したもので、この構成によれば、デジタルAGC回路を振幅検出手段と、ゲイン算出手段と、置換演算手段とで構成しているため、デジタルAGC回路への入力信号を逓倍してタイミング信号を生成するタイミング制御手段より出力される信号により動作するΣΔ変調器から出力される低ビットのパルス密度変調信号が置換演算手段によって振幅検出手段およびゲイン算出手段において算出されたゲインと置換演算されることになり、これにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号に変換可能な小型で低コストのデジタルAGC回路を提供することができるという作用効果を有するものである。

【0010】

本発明の請求項2に記載の発明は、特に、ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けたもので、この構成によれば、振幅検出手段から出力される振幅情報を元に、任意のゲイン特性を有するゲインをビットシフト演算手段と加算演算手段のみで乗算器を使用することなく算出可能となるため、小型で低コストのデジタルAGC回路を提供することができるという作用効果を有するものである。

【0011】

本発明の請求項3に記載の発明は、特に、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としたもので、この構成によれば、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としているため、EEPROMなどのROMに格納されたデータをもとにゲイン算出手段で算出するAGCゲイン特性、デジタルフィルタのフィルタ特性を変更することが可能となり、これにより、AGCしたい対象が変化してもROM値の変更のみで対応可能なデジタルAGC回路を提供することができるという作用効果を有するものである。

【0012】

本発明の請求項4に記載の発明は、特に、振幅検出回路にデジタルフィルタとピークホールド手段とを設けたもので、この構成によれば、振幅検出回路にデジタルフィルタとピークホールド手段とを設けているため、ΣΔ変調器から出力される低ビットのパルス密度変調信号をデジタルフィルタにより高調波ノイズを除去してマルチビット化し、そしてタイミング制御手段より出力されるタイミング信号を元にピークホールド手段によって入力信号の振幅を検出することになり、この場合、入力信号と非同期のクロックを用いてサンプリングする場合よりも、タイミング制御手段はPLL回路を有しているため、入力信号がピークになるタイミングで正確にサンプリングでき、これにより、安定して入力された信号の振幅情報を取得できることになるため、AGC特性が安定するという作用効果を有するものである。

【0013】

請求項5に記載の発明は、特に、デジタルフィルタをビットシフト演算手段で構成したもので、この構成によれば、デジタルフィルタをビットシフト演算手段で構成しているため、乗算器を用いることなく高精度のゲインコントロールが可能で、かつ低ノイズのデジタルAGC回路を提供することができるという作用効果を有するものである。

【0014】

本発明の請求項6に記載の発明は、駆動電極と、センス電極と、モニタ電極とを有するセンサ素子と、このセンサ素子を所定の振幅で振動駆動させるドライブ回路と、前記センサ素子におけるセンス電極から出力される信号を角速度出力信号に変換するセンス回路とを備え、前記ドライブ回路を、少なくとも2つのレベルの電荷量を出力するDA変換手段と、前記センサ素子におけるモニタ電極から出力される信号とDA変換手段とから出力される電荷を積分し、その積分値を保持する積分回路と、この積分回路から出力される積分値を少なくとも1つの所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ型変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段を備えたデジタルAGC回路と、デジタルフィルタと、PLL回路を有するタイミング制御手段と、駆動回路とで構成したもので、この構成によれば、デジタルAGC回路を振幅検出手段と、ゲイン算出手段と、置換演算手段とで構成しているため、デジタルAGC回路への入力信号を逓倍してタイミング信号を生成するタイミング制御手段より出力される信号により動作するモニタ電極から出力される信号がΣΔ型変調器から出力される低ビットのパルス密度変調信号が置換演算手段によって振幅検出手段およびゲイン算出手段において算出されたゲインと置換演算されることになり、これにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号が駆動回路から出力されるため、小型で低コストの角速度センサが得られるという作用効果を有するものである。

【0015】

本発明の請求項7に記載の発明は、特に、ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けたもので、この構成によれば、ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けているため、振幅検出手段から出力される振幅情報を基に、任意のゲイン特性を有するゲインをビットシフト演算手段と加算演算手段のみで乗算器を使用することなく算出することができるという作用効果を有するものである。

【0016】

本発明の請求項8に記載の発明は、特に、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としたもので、この構成によれば、ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成としているため、EEPROMなどのROMに格納されたデータをもとにゲイン算出手段で算出するAGCゲイン特性、デジタルフィルタのフィルタ特性を変更できることになり、これにより、用いるセンサ素子の特性やセンサの用途に応じてROMへ書き込む値を適宜変更できる角速度センサを提供することができるという作用効果を有するものである。

【0017】

本発明の請求項9に記載の発明は、特に、振幅検出回路にデジタルフィルタとピークホールド手段とを設けたもので、この構成によれば、振幅検出回路にデジタルフィルタとピークホールド手段とを設けているため、ΣΔ変調器から出力される低ビットのパルス密度変調信号を、デジタルフィルタにより高調波ノイズを除去してマルチビット化し、そしてタイミング制御手段より出力されるタイミング信号を元にピークホールド手段によって入力信号の振幅を検出することになり、この場合、入力信号と非同期のクロックを用いてサンプリングする場合よりも、タイミング制御手段はPLL回路を有しているため、正確に入力信号がピークになるタイミングでサンプリングでき、これにより、安定して入力された信号の振幅情報を取得できるという作用効果を有するものである。

【0018】

本発明の請求項10に記載の発明は、特に、デジタルフィルタをビットシフト演算手段で構成したもので、この構成によれば、デジタルフィルタをビットシフト演算手段で構成しているため、乗算器を用いることなく高精度のゲインコントロールが可能で、かつ低ノイズの角速度センサを提供することができるという作用効果を有するものである。

【発明の効果】

【0019】

以上のように本発明のデジタルAGC回路は、少なくとも2つのレベルの電荷量を出力するDA変換手段と、このDA変換手段から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段と、この積分手段から出力される積分値を所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段と、デジタルフィルタと、PLL回路を有するタイミング制御手段とで構成したもので、デジタルAGC回路を振幅検出手段と、ゲイン算出手段と、置換演算手段とで構成しているため、デジタルAGC回路への入力信号を逓倍してタイミング信号を生成するタイミング制御手段より出力される信号により動作するΣΔ変調器から出力される低ビットのパルス密度変調信号が置換演算手段によって振幅検出手段およびゲイン算出手段において算出されたゲインと置換演算されることになり、これにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号に変換可能な小型で低コストのデジタルAGC回路を提供することができるという優れた効果を奏するものである。

【発明を実施するための最良の形態】

【0020】

(実施の形態1)

以下、本発明の実施の形態1におけるデジタルAGC回路およびそれを用いた角速度センサについて、図面を参照しながら説明する。

【0021】

図1は本発明の実施の形態1におけるデジタルAGC回路を用いた角速度センサの回路図である。

【0022】

図1において、30はセンサ素子で、このセンサ素子30は振動体31と、この振動体31を振動させるための圧電体を有する駆動電極32と、振動状態に応じて電荷を発生する圧電体を有するモニタ電極33と、前記センサ素子30に角速度が印加されると電荷を発生する圧電体を有する一対のセンス電極とを設けている。また、前記センサ素子30における一対のセンス電極は、第1のセンス電極34と、この第1のセンス電極34と逆極性の電荷を発生する第2のセンス電極35とで構成されている。41はドライブ回路で、このドライブ回路41は入力切替手段42と、DA変換手段43、積分手段44、比較手段45、DA切替手段46、デジタルAGC回路47、デジタルフィルタ48および駆動回路49とで構成されている。また、前記ドライブ回路41における入力切替手段42は、振動体31におけるモニタ電極33と接続され、第6のタイミングΦ6で動作するアナログスイッチで構成されている。そしてまた、前記ドライブ回路41におけるDA切替手段46は、第1の基準電圧50および第2の基準電圧51を有し、そしてこの第1の基準電圧50と第2の基準電圧51を第6のタイミングΦ6で所定の信号により切り替えている。さらに、前記ドライブ回路41にはDA出力手段52を設けており、このDA出力手段52は前記DA切替手段46の出力信号が入力されるコンデンサ53と、このコンデンサ53の両端に接続され、かつ前記第5のタイミングΦ5で動作してコンデンサ53の電荷を放電するSW54,55により構成されている。そして、前記DA切替手段46とDA出力手段52とでDA変換手段43を構成し、かつこのDA変換手段43は第5のタイミングΦ5で前記コンデンサ53の電荷を放電し、さらに前記第6のタイミングΦ6で前記DA切替手段46が出力する基準電圧に応じた電荷を入出力するものである。56はSWで、このSW56には前記入力切替手段42とDA変換手段43の出力が入力され、前記第6のタイミングΦ6で出力するものである。

【0023】

44は積分手段で、この積分手段44には前記SW56の出力が入力されるもので、演算増幅器57と、この演算増幅器57の帰還に接続されるコンデンサ58とにより構成されている。そして、第6のタイミングΦ6で、前記積分手段44への入力信号がコンデンサ58により積分される。45は比較手段で、この比較手段45には前記積分手段44が出力する積分信号が入力され、そしてこの積分信号と所定の値とを比較する比較器59と、この比較器59が出力する1ビットデジタル信号が入力されるD型フリップフロップ60とにより構成されている。また、前記D型フリップフロップ60は前記第5のタイミングΦ5の開始時に前記1ビットデジタル信号をラッチしてラッチ信号を出力するものであり、このラッチ信号は、前記DA変換手段43のDA切替手段46に入力されて、第1の基準電圧50と第2の基準電圧51とを切り替えるものである。そして、前記入力切替手段42、DA変換手段43、積分手段44および比較手段45によりΣΔ変調器61を構成している。

【0024】

また、前記ΣΔ変調器61の出力するパルス密度変調信号はデジタルAGC回路47に入力され、かつこのデジタルAGC回路47は振幅検出手段71、ゲイン算出手段72、置換演算手段73により構成される。そして前記振幅検出手段71は、前記ΣΔ変調器61の出力するパルス密度変調信号が入力され高周波ノイズを除去してマルチビット信号を出力するデジタルローパスフィルタ74と、このデジタルローパスフィルタ74の出力するマルチビット信号が入力されこれをピークホールドして出力するピークホールド手段75と、前記ピークホールド手段75の出力する振幅情報が入力されてこれを平滑し振幅情報を出力するデジタルローパスフィルタ76により構成される。さらに前記振幅検出手段71の出力する振幅情報は前記ゲイン算出手段72に入力され、かつこのゲイン算出手段72はビットシフト演算手段77と加算演算手段78とで構成される。また、前記ゲイン算出手段72では入力された振幅情報に対して、所定係数値のビットシフト演算と所定係数値の加算演算を行い、ゲイン情報を算出する。ここで前記ビットシフト演算手段77および加算演算手段78で用いられる係数値はROM79より読み出されて供給される。そして、前記ゲイン算出手段72の出力するゲイン情報と、前記ΣΔ変調器61の出力するパルス密度変調信号が前記置換演算手段73に入力されて置換演算されることにより、ゲインコントロールされたマルチビットのパルス密度変調信号として前記デジタルAGC回路47より出力されることとなる。さらにこの前記デジタルAGC回路47より出力されるゲインコントロールされたマルチビットのパルス密度変調信号は前記デジタルフィルタ48に入力される。

【0025】

ここで前記デジタルフィルタ48の構成例を図2に示す。また前記デジタルフィルタ48の演算処理に用いられる係数値は前記ROM79より読み出されて供給される構成となっている。前記デジタルフィルタ48によりΣΔ変調されたことによる高周波ノイズを除去し、そしてセンサ素子30の共振周波数のみを抽出してノイズ成分を除去したマルチビット信号は前記駆動回路49に入力される。

【0026】

前記駆動回路49は、2値を保持しているデジタル値出力手段80と、デジタルフィルタ48からの出力信号と前記デジタル値出力手段80の出力を加算し積分する加積分演算手段81と、この加積分演算手段81からの出力を比較定数値82と比較する値比較手段83と、この値比較手段83の出力に応じて前記デジタル値出力手段80の出力するデジタル値を切り替える値切り替え手段84と、値比較手段83の出力を所定タイミングでラッチするフリップフロップ85とにより構成されるデジタルΣΔ変調器86を有している。前記デジタルΣΔ変調器86により前記デジタルフィルタ48が出力するマルチビット信号は1ビットのパルス密度変調信号に変調されて出力され、かつこのパルス密度変調信号はアナログローパスフィルタ87に入力され、さらにセンサ素子30を駆動するのに有害な周波数成分はフィルタリングされて、センサ素子30に出力される。以上の構成により前記振動体31の振動が一定振幅となるように調整するものである。

【0027】

91はPLL回路で、このPLL回路91はモニタ電極33が出力するモニタ信号を元とした信号を逓倍し、位相ノイズを時間的に積分し低減して出力するものであり、前記ドライブ回路41におけるデジタルローパスフィルタ74が出力する信号が入力されることになる。92はタイミング生成回路で、このタイミング生成回路92は前記PLL回路91から出力されるモニタ信号を逓倍したタイミング信号を前記ドライブ回路41に供給するとともに、このタイミング信号をもとに、モニタ信号の2周期間を第1のタイミングΦ1、第2のタイミングΦ2、第3のタイミングΦ3、第4のタイミングΦ4に分割してこのタイミング信号を生成して出力するものである。そして、前記PLL回路91とタイミング生成回路92とでタイミング制御回路93を構成している。94は入力切替手段で、この入力切替手段94は前記センサ素子30における第1のセンス電極34と接続され前記第2のタイミングΦ2で動作するアナログスイッチ95(以下、SWと記す)と、第2のセンス電極35と接続され前記第4のタイミングΦ4で動作するアナログスイッチ96とで構成されている。この構成により、入力切替手段94は、第1のセンス電極34または第2のセンス電極35からの入力信号を第2のタイミングΦ2または第4のタイミングΦ4で切り替えて出力することになる。97はDA切替手段で、このDA切替手段97は、第1の基準電圧99および第2の基準電圧100を有し、そしてこの第1の基準電圧99と第2の基準電圧100を所定の信号により切り替えるものである。101はDA出力手段で、このDA出力手段101は前記DA切替手段97の出力信号が入力されるコンデンサ102と、このコンデンサ102の両端に接続され、かつ前記第1のタイミングΦ1と第3のタイミングΦ3で動作してコンデンサ102の電荷を放電するSW103,104とにより構成されている。そして、前記DA切替手段97とDA出力手段101とでDA変換手段98を構成し、かつこのDA変換手段98は第1のタイミングΦ1と第3のタイミングΦ3で前記コンデンサ102の電荷を放電し、さらに前記第2のタイミングΦ2と第4のタイミングΦ4で前記DA切替手段97が出力する基準電圧に応じた電荷を入出力するものである。

【0028】

105はSWで、このSW105には前記入力切替手段94とDA変換手段98の出力が入力され、前記第2のタイミングΦ2と第4のタイミングΦ4で出力するものである。106は積分回路で、この積分回路106には前記SW105の出力が入力されるもので、演算増幅器107と、この演算増幅器107の帰還に並列に接続される一対のコンデンサ108,109と、このコンデンサ109に接続される一対のSW110,111とにより構成されている。また、SW110は第1のタイミングΦ1と第2のタイミングΦ2で動作し、前記積分回路106への入力信号がコンデンサ108に積分されて積分値が保持されることになる。そしてまた、SW111は前記第3のタイミングΦ3と第4のタイミングΦ4で動作し、前記積分回路106への入力信号がコンデンサ109に積分されて積分値が保持されることになる。113は比較手段で、この比較手段113には積分手段112が出力する積分信号が入力され、そしてこの積分信号と所定の値とを比較する比較器114と、この比較器114が出力する1ビットデジタル信号が入力されるD型フリップフロップ115とで構成されている。また、前記D型フリップフロップ115は前記第2のタイミングΦ2と第4のタイミングΦ4の開始時に前記1ビットデジタル信号をラッチしてラッチ信号を出力するものであり、このラッチ信号は、前記DA変換手段98のDA切替手段97に入力されて第1の基準電圧99と第2の基準電圧100とを切り替えるものである。そして、前記入力切替手段94、DA変換手段98、積分手段112および比較手段113によりΣΔ変調器116を構成している。

【0029】

またこのΣΔ変調器116は上記構成により、前記センサ素子30における一対のセンス電極34,35より出力される電荷をΣΔ変調し、1ビットデジタル信号に変換して出力するものである。

【0030】

117はラッチ回路で、このラッチ回路117には前記ΣΔ変調器116の比較手段113における比較器114より出力される1ビットデジタル信号が入力され、かつ前記1ビットデジタル信号をラッチする一対のD型フリップフロップ119により構成されている。また、D型フリップフロップ118は第2のタイミングΦ2で前記1ビットデジタル信号をラッチするものであり、かつD型フリップフロップ119は第4のタイミングΦ4で前記1ビットデジタル信号をラッチするものである。120は差分演算手段で、この差分演算手段120には前記ラッチ回路117における一対のD型フリップフロップ119がラッチして出力する一対の1ビットデジタル信号が入力され、そしてこの一対の1ビットデジタル信号の差を演算する1ビット差分演算を置換処理により実現するものである。つまり、差分演算手段120に入力される一対の1ビットデジタル信号が、“00”“01”“10”“11”である時、それぞれ“0”“−1”“1”“0”と置き換えて出力する構成となっている。121は補正演算手段で、この補正演算手段121には前記差分演算手段120が出力する1ビット差分信号が入力され、この1ビット差分信号と所定の補正情報との補正演算を置換処理により実現するものである。つまり、上記したように補正演算手段121に入力される1ビット差分信号が“0”“1”“−1”であり、例えば、補正情報が“5”である場合にはそれぞれ“0”“5”“−5”と置き換えて出力する構成となっている。122はデジタルフィルタで、このデジタルフィルタ122には前記補正演算手段121より出力されるデジタル差分信号が入力され、ノイズ成分を除去するフィルタリング処理を行うものである。そして、前記ラッチ回路117、差分演算手段120、補正演算手段121およびデジタルフィルタ122により演算手段123を構成している。また、この演算手段123は、第2、第4のタイミングで一対の1ビットデジタル信号をラッチして、差分演算、補正演算、フィルタリング処理を行い、マルチビット信号を出力することになる。そしてまた、前記タイミング制御回路93とΣΔ変調器116および演算手段123によりセンス回路124を構成している。

【0031】

以上のように構成された本発明の実施の形態1における角速度センサについて、次にその動作を説明する。

【0032】

前記センサ素子30の駆動電極32に駆動信号を加えると、前記振動体31が共振し、モニタ電極33に電荷が発生する。このモニタ電極33に発生した電荷をドライブ回路41におけるΣΔ変調器61に入力し、パルス密度変調信号へと変換する。そしてこのΣΔ変調器61の出力するパルス密度変調信号をデジタルAGC回路47へ入力し、このデジタルAGC回路47がもつ振幅検出手段71によりモニタ電極33より発生した信号の振幅情報を取得し、この振幅情報をゲイン算出手段72に入力してゲイン情報を演算により取得する。ゲイン算出手段72の出力するゲイン情報と前記ΣΔ変調器61の出力するパルス密度変調信号が置換演算手段73に入力されて、前記振動体31の振動が一定振幅となるようゲインコントロールされたマルチビットのパルス密度変調信号が出力される。このゲインコントロールされたマルチビットのパルス密度変調信号をデジタルフィルタ48に入力し、前記振動体31の共振周波数のみを抽出したノイズ成分が除去されたマルチビット信号を出力する。そしてこのデジタルフィルタ48の出力するマルチビット信号を駆動回路49に入力し、さらにこの駆動回路49を構成するデジタルΣΔ変調器86およびアナログフィルタ87より駆動信号がセンサ素子30における駆動電極32へ出力され、前記振動体31の振動が一定振幅となるように調整するものである。この場合におけるΣΔ変調器61、デジタルAGC回路47、デジタルフィルタ48、駆動回路49の動作を以下に説明する。

【0033】

ΣΔ変調器61はタイミング制御回路93より出力されるモニタ信号に同期したタイミングである第1のタイミングΦ5、第2のタイミングΦ6を繰り返すことによって動作するもので、第1のタイミングΦ5ではセンサ素子30におけるモニタ電極33から出力される信号がΣΔ変調されて1ビットデジタル信号に変換される。

【0034】

上記した2つのタイミングでの動作をひとつずつ説明する。まず、第1のタイミングΦ5では、積分手段44におけるコンデンサ58に保持されている積分値を比較する前記比較手段45の比較器59より出力される1ビットデジタル信号が、第1のタイミングΦ5の立ち上がり時にD型フリップフロップ60にラッチされ、このラッチ信号が前記DA変換手段43のDA切替手段46に入力される。また、DA出力手段52におけるSW54とSW55がONになって、コンデンサ53に保持されている電荷が放電される。

【0035】

次に第2のタイミングΦ6では、前記DA切替手段46に入力されたラッチ信号に応じて基準電圧50,51が切り替えられてコンデンサ53に入力され、かつDA変換手段43より切り替えられた基準電圧に応じた電荷が出力される。また、入力SW42がONになり、前記センサ素子30のモニタ電極33より発生する電荷が入力される。さらに、積分手段44におけるSW56がONになり、前記入力SW42とDA変換手段43から出力される電荷が積分手段44に入力される。これにより第2のタイミングΦ6では、積分手段44におけるコンデンサ58に、図3(a)の斜線部で示される電荷量とDA変換手段43より出力される電荷量の総和が積分されて保持されることになる。

【0036】

上記した第1のタイミングΦ5および第2のタイミングΦ6での以上の動作によりセンサ素子30のモニタ電極33から出力される電荷がΣΔ変調され、第1のタイミングΦ5の信号の立ち上がり時に1ビットデジタル信号として出力されることになる。

【0037】

次にデジタルAGC回路47について動作を説明する。前記ΣΔ変調器61の出力するパルス密度変調信号が前記振幅検出手段71の有するデジタルローパスフィルタ74に入力されて高周波ノイズを除去し、図4(a)で示されるマルチビット信号へと変換される。このマルチビット信号がピークホールド手段75へ入力され、図4(b)で示されるピーク信号へと変換される。さらに、正のピークだけでなく負のピークも検出しその差分をとることでさらに精度が向上する。この時、ΣΔ変調器61によるモニタ電極35より出力されるモニタ信号のサンプリングが、このモニタ信号を逓倍した信号により行われているため、正確にピークのポイントを検出でき、そしてこれを基にAGC制御が行われるため、低ノイズで高精度のAGC制御が実現でき、これにより、このデジタルAGC回路47を用いて低ノイズで高精度の角速度センサを提供することができるという効果を有することになる。このようにピークホールド手段75によりピークホールドされた信号が、デジタルローパスフィルタ76に入力されて平滑されることにより、ノイズが除去された前記モニタ電極33の出力する信号の振幅に応じた振幅情報を得ることができる。次に振幅検出手段71の出力する振幅情報がゲイン算出手段72へと入力され、ゲイン情報が算出される。ここで、センサ素子30の振動振幅を一定に制御するためのAGCゲイン特性が図5で示される場合、(数1)に示すように、ビットシフト演算および加算演算を行うことにより、現在必要なゲイン情報を算出することができる。

【0038】

【数1】

【0039】

このとき、“+c”は定数値“B”の加算処理であり、“A*x”の演算は“A”を“−1.25”としたい場合には、(数2)に示すように表記し直すことが可能であるため、ビットシフト演算および加算演算と±は符合ビットの反転のみで(数2)の演算を行うことが可能となる。

【0040】

【数2】

【0041】

このように、ゲイン算出手段72の有するビットシフト演算手段77と加算演算手段78により、センサ素子30の振動振幅を一定に制御するためのAGCゲイン情報が算出される。このとき、傾き“A”、切片“B”を固定ではなくROM79より読み出された値により決定する構成とし、決定された値によりビットシフト演算手段77でのシフト量および加算演算手段78で加算される切片“B”の値を変更することによって、AGCゲイン特性を容易に変化させることが可能となる。これにより、センサ素子の特性やセンサが用いられる用途に応じてAGCゲイン特性をROM値の書き換えのみで変更可能な角速度センサを提供することができるという効果が得られるものである。

【0042】

次にゲイン算出手段72から出力されるゲイン情報“G”と、前記ΣΔ変調器61が出力するパルス密度変調信号が前記置換演算手段73に入力される。ここで、前記ΣΔ変調器61が出力するパルス密度変調信号は“1”もしくは“−1”の1bit信号であるため、これをゲイン情報“G”と置換、すなわち“−1”⇒“−G”、“1”⇒“G”と置き換えることにより、乗算器を用いること無しに、“入力信号×G”の演算を実現することが可能となる。よって、前記置換演算手段73によりゲインの演算がなされる。ここで、ΣΔ変調器61は1bitのΣΔ変調器として説明しているが、複数bit出力のΣΔ変調器であったとしてもΣΔ変調器の出力は例えば2bitであれば“00,01,611”の4値に限定でき、“00,01,611”⇒“−G,−G/2,G/2,G”と置き換えることによって、上記と同様の構成により“入力信号×G”が実現可能となるものである。以上のようにデジタルAGC回路47からセンサ素子30の振動振幅を一定に制御するためにゲインコントロールされたマルチビットのパルス密度変調信号が出力されることになるため、デジタルAGC回路47を乗算器を用いることなしに低コストで、かつ高精度にデジタル回路により実現できるという効果が得られるものである。

【0043】

次に前記デジタルAGC回路47から出力されるゲインコントロールされたマルチビットのパルス密度変調信号が入力されるデジタルフィルタ48について動作を説明する。ここで図2は前記デジタルフィルタ48の構成例である。図2の141はIIRフィルタで一般的なIIRの構成を示しており、142〜146はこのフィルタの特性を決定するゲイン演算部であり、147,148は加算演算部、149,150は遅延部である。ここで、フィルタの特性を決定するゲイン演算部142〜146のゲイン係数を例えば{a0,a1,a2,b0,b1}={1,81.71475,−0.75}としたい場合、(数3)に示すように表記し直すことが可能であり、これらのゲイン計算はゲイン算出手段において説明した通り、ビットシフト演算により演算可能である。

【0044】

【数3】

【0045】

また、151〜153はビットシフト演算部であり、これらの値を(数4)で示すように演算を行うことにより、最初にc0を+7ビットシフト(×128)として演算した後にc2において−7ビットシフト(1/128)することによって、ビットシフト演算による丸め誤差等の演算誤差を低減することが可能となる。

【0046】

【数4】

【0047】

以上の構成/動作により、ビットシフト演算と加算演算のみによって演算精度を確保した上でフィルタ演算を行うことが可能な低コストのデジタルフィルタを得ることが可能であるという効果を有するものである。また、上記ビットシフトによるゲイン計算はFIR等他のフィルタ形式でも利用可能であり、図2のIIRのフィルタ構成を係数を変えて縦続接続することによって、必要なフィルタ特性を実現することが可能となるものである。さらに、センサ素子30を所定の共振周波数のみで振動させるにあたっては、バンドパスフィルタ特性を持つことが望ましい。よって、前記デジタルAGC回路47から出力されるパルス密度変調信号がデジタルフィルタ48に入力され、ノイズ成分がフィルタリングされゲインコントロールされたマルチビット信号が出力されることになる。

【0048】

さらに、ビットシフト演算部154を追加で設けた場合の動作について説明する。まず、デジタルAGC回路47におけるゲイン情報“G”を例えば、“128±128”の“0〜256”の値とし、ゲイン係数{d2}={1/128}={1/2^7}の−7ビットシフト(1/128)として置換演算およびビットシフトを行うことにより、デジタルAGC回路47およびデジタルフィルタ48により“1/128”の分解能で0倍から2倍までの可変ゲインを演算精度を確保したまま実現することが可能となる。さらにこのゲイン分解能およびゲイン幅は、ゲイン情報“G”の取り得る値とゲイン係数{d2}のビットシフト量を必要な量だけ確保するだけで、任意に設定可能である。

【0049】

以上のように構成/動作させることにより、乗算器を用いることなくゲインコントロールされたマルチビットのパルス密度変調信号およびマルチビット信号に変換可能な小型・低コストで、かつ低ノイズでそのAGC特性およびフィルタ特性が容易に可変なデジタルAGC回路およびデジタルフィルタが得られるという効果を有するものである。また、上記ビットシフト演算でのビットシフト量をROM79に格納されたデータにより決定する構成とすることにより、センサ素子の特性やセンサが用いられる用途に応じてフィルタ特性をROM79に格納する値を書き換えるだけで変更可能な角速度センサを提供することができるという効果が得られるものである。

【0050】

次に駆動回路49の動作を説明する。デジタルΣΔ変調器86の加積分演算手段81に前記デジタルフィルタ48から出力されるマルチビット信号と、所定の2値を保持しているデジタル値出力手段80のどちらかの値を出力する値切り替え手段84より出力される定数値が加積分演算手段81へと入力され、加算して積分される。この加積分演算手段81から出力される積分値が比較定数値82と値比較手段83により比較されて比較結果が出力される。そして、この比較結果がフリップフロップ85により所定のタイミングでラッチされて出力される。このフリップフロップ85の出力により値切り替え手段84より出力される定数値が切り替えられることになる。この時、加積分演算手段81の出力値が比較定数値82より小さい場合には、デジタル値出力手段80の2値のうちの大きい方の値が、逆の場合には小さい方の値が選択されて出力されるように動作する。この動作を繰り返すことによりフリップフロップ85より、前記デジタルフィルタ48が出力するマルチビット信号が、1ビットのパルス密度変調信号に変調されて出力されることになる。ここで、デジタルΣΔ変調器86に入力される信号が例えば、10bit(=±9bit)である場合は、比較定数値82を“0”デジタル値出力手段80の2値を“511”“−511”以上とすることが望ましい。

【0051】

以上の構成により、センサ素子30のモニタ電極33より出力された信号が、ΣΔ変調器61によりパルス密度変調信号に変換され、デジタルAGC回路47によりセンサ素子30の振動を一定に制御するよう所定のAGCゲイン特性で振幅調整され、さらにデジタルフィルタ48によりノイズが除去されてマルチビット化される。この振幅調整されたマルチビット信号がデジタルΣΔ変調器86によりΣΔ変調されて1bitのパルス密度変調信号に変換され、この信号がセンサ素子30における駆動電極32に出力される。この時、1bitのパルス密度変調信号はモニタ電極33より出力された信号の周波数成分をデジタルAGC回路47により振幅調整されて含んでいることとなり、この信号がセンサ素子30に出力されることによって、前記振動体31の振動が所定の共振周波数において一定振幅で振動することになる。このような駆動回路49を構成することにより、高精度DA変換器を用いることなく大半をデジタル回路で実現することができるため、低コストで、かつ高精度の角速度センサを提供することができるという効果が得られるものである。

【0052】

なお、ΣΔ変調ではオーバーサンプリングを行い、その量子化ノイズが高域にノイズジェーピングされるため、高周波成分のノイズ成分を含むが、センサ素子30の応答がそのような高周波に応答できないため、パルス密度変調信号のサンプリング周波数でなく、オーバーサンプリングされた所定の周波数成分で振動することになる。また、センサ素子30の高周波での応答ゲインが高くて、このような高周波成分のノイズが問題になる場合には、デジタルΣΔ変調器86の出力信号のうち問題となる周波数成分を低減するよう設定されたアナログフィルタ87を追加することによって、さらに低ノイズで、高精度のドライブ回路41を実現することが可能となるものである。

【0053】

さらに、タイミング制御回路93に、図6(a)に示される正弦波信号が入力され、前記PLL回路91で逓倍した信号をもとにタイミング生成回路92により図6(b)で示される第1のタイミングΦ1、第2のタイミングΦ2、第3のタイミングΦ3、第4のタイミングΦ4を形成する。そして、このタイミング信号が前記ΣΔ変調器116および演算手段123に、SWの切替およびラッチ回路のラッチタイミングとして入力される。また、位相器で位相を90度シフトさせた前記正弦波信号を所定の基準電圧(図示せず)と比較する電圧コンパレータ(図示せず)に入力し、そしてその出力をロジック回路(図示せず)に入力するようにした場合でも、前記タイミング信号Φ1、Φ2、Φ3、Φ4を形成することは可能であるが、この場合、正弦波信号の電圧ノイズおよび温度変化や電源変動による電圧ノイズが位相ノイズとして表れることになる。この位相ノイズは、入力信号や積分切替手段を切り替えるタイミングノイズとして信号処理の精度に悪影響を与える要因となるが、前記PLL回路91を用いて時間的に積分され位相ノイズが低減されたタイミング信号とすることにより、切替タイミングノイズを低減し信号処理の精度を高めることができるものである。そして、前記センサ素子30が図1に図示している駆動方向に速度Vで屈曲振動している状態において、前記振動体31の長手方向の中心軸周りにセンサ素子30が角速度ωで回転すると、このセンサ素子30にF=2mV×ωのコリオリ力が発生する。このコリオリ力により前記センサ素子30が有する一対のセンス電極34,35に、図6(c)および図6(d)に示すように電荷が発生する。そしてこのセンス電極34,35に発生する電荷はコリオリ力により発生するため、前記モニタ電極33に発生する信号より位相が50度進んでいる。そしてまた、前記一対のセンス電極34,35に発生した出力信号は図6(c)および図6(d)に示す通り、正極性信号と負極性信号の関係にある。

【0054】

この場合におけるΣΔ変調器116の動作を以下に説明する。このΣΔ変調器116は第1のタイミングΦ1、第2のタイミングΦ2、第3のタイミングΦ3および第4のタイミングΦ4を繰り返すことによって動作するもので、第1のタイミングΦ1および第2のタイミングΦ2ではセンサ素子30における第1のセンス電極34から出力される正極性信号がΣΔ変調されて1ビットデジタル信号に変換され、また第3のタイミングΦ3および第4のタイミングΦ4では第2のセンス電極35から出力される負極性信号がΣΔ変調されて1ビットデジタル信号に変換される。

【0055】

上記した4つのタイミングでの動作をひとつずつ説明する。まず第1のタイミングΦ1では、積分手段112におけるコンデンサ108と接続されているSW110がONになり、このコンデンサ108に保持されている積分値が比較手段113における比較器114に入力され比較結果が1ビットデジタル信号として出力される。また、DA変換手段98におけるSW103と104がONになりコンデンサ102に保持されている電荷が放電される。

【0056】

次に第2のタイミングΦ2では、前記比較手段113の比較器114より出力される1ビットデジタル信号が第2のタイミングΦ2の立ち上がり時にD型フリップフロップ115にラッチされ、このラッチ信号が前記DA変換手段98のDA切替手段97に入力される。この入力されたラッチ信号に応じて基準電圧が第1の基準電圧99または第2の基準電圧100に切り替えられてコンデンサ102に入力され、DA変化手段98より切り替えられた基準電圧に応じた電荷が出力される。それとともに、入力切替手段94ではSW95がONになり、前記センサ素子30の第1のセンス電極34より発生する電荷が出力される。さらに、積分手段112におけるSW105がONになり、前記入力切替手段94とDA変換手段98から出力される電荷が積分回路106に入力される。これにより第2のタイミングΦ2では、積分回路106におけるコンデンサ108に、図6(c)の斜線部で示される電荷量とDA変換手段98より出力される電荷量の総和が積分されて保持されることになる。

【0057】

上記した第1のタイミングΦ1および第2のタイミングΦ2での以上の動作によりセンサ素子30のセンス電極34から出力される振幅値の半分に相当する電荷量がΣΔ変調されることになる。

【0058】

また、第1のタイミングΦ1および第2のタイミングΦ2での動作と同様に、第3のタイミングΦ3および第4のタイミングΦ4では、センサ素子30の第2のセンス電極35から出力される振幅値の半分に相当する電荷量がΣΔ変調され、1ビッデジタル信号に変換されて出力されることになる。以上の動作により、センサ素子30における一対のセンス電極34,35から出力される電荷の振幅値の半分に相当する電荷量が一つのΣΔ変調器116によりΣΔ変調されて一対の1ビットデジタル信号として上記タイミングで出力されることになる。

【0059】

そしてまた、センサ素子30における第1のセンス電極34および第2のセンス電極35から出力される電荷は、角速度によるコリオリ力で発生する、モニタ電極33に発生する信号より位相が90度進んだセンス信号だけでなく、モニタ信号と同相の不要信号があるため、センサ素子30における第1のセンス電極34および第2のセンス電極35からセンス信号と不要信号の合成信号が出力される場合について説明する。角速度によるコリオリ力で発生するセンス信号は、図6(c)(d)で示され、そして上記で説明した通り、第2のタイミングΦ2と第4のタイミングΦ4で、積分回路106により図6(c)(d)の斜線部で示される電荷量、つまり、振幅値の半分に相当する電荷量が積分されることになる。さらに、第1のセンス電極34および第2のセンス電極35より発生する不要信号は図6(e)(f)で示され、そして前記センス信号と同様に第2のタイミングΦ2と第4のタイミングΦ4で、図6(e)(f)の斜線部で示される電荷量、つまり、不要信号の振幅の最大値から最小値までの区間の電荷量が積分されている。これは、振幅の中央値を基準に積分するとキャンセルされて“0”の電荷量となるものである。つまり、第2のタイミングΦ2と第4のタイミングΦ4での積分手段112の動作により、不要信号がキャンセルされてセンス信号の振幅に応じた電荷量が積分される、いわゆる同期検波処理が一対の入力信号のそれぞれに対し実施されることになる。よって、上記不要信号のない場合の動作の説明と同様に、前記ΣΔ変調器116からは同期検波処理された信号がΣΔ変調され、1ビットデジタル信号に変換されて出力されることになる。

【0060】

次に、演算手段123について、その動作を説明する。まず、第2のタイミングΦ2で、前記ΣΔ変調器116の比較手段113における比較器114より出力される1ビットデジタル信号が、ラッチ回路117のD型フリップフロップ118にラッチされる。また、第4のタイミングΦ4で、前記ΣΔ変調器116の比較手段113における比較器114より出力される1ビットデジタル信号が、ラッチ回路117のD型フリップフロップ118,119にラッチされる。

【0061】

この一対のD型フリップフロップ118,119にラッチされた一対の1ビットデジタル信号は、上記で説明した通り、センサ素子30における一対のセンス電極34,35より出力された信号の不要信号を除いた振幅値の半分に相当する電荷量をそれぞれΣΔ変調によりデジタル値に変換したものである。次に、前記ラッチ回路117が出力する一対の1ビットデジタル信号が1ビット差分演算手段120に入力され、この一対の1ビットデジタル信号の差が演算されて1ビット差分信号が出力される。ここで、第1のタイミングΦ1での1ビット差分信号は、一つ前の周期における第2のタイミングΦ2、第4のタイミングΦ4でラッチされた1ビットデジタル信号の差であり、この1ビット差分信号は、図6(c)(d)で示されるセンサ素子30における一対のセンス電極34,35より出力される信号の不要信号を除いた振幅値を表す信号となる。次に、1ビット差分演算手段120が出力する1ビット差分信号が補正演算手段121に入力され、この1ビット差分信号と所定の補正情報との補正演算が置換処理により行われる。この補正演算は、上記したように、1ビット差分信号が“0”“1”“−1”の3値に限られることを利用して、例えば所定の補正情報が“5”である場合に、補正演算手段に入力される1ビット差分信号“0”“1”“−1”を、それぞれ“0”“5”“−5”と置換処理することにより乗算を実現して信号の補正が可能となるものである。

【0062】

(実施の形態2)

以下、本発明の実施の形態2におけるデジタルAGC回路を用いた角速度センサについて、図面を参照しながら説明する。

【0063】

図7は本発明の実施の形態2におけるデジタルAGC回路を用いた角速度センサの回路図である。なお、本発明の実施の形態2においては、上記した本発明の実施の形態1と同様の構成を有するものについては、同一番号を付しており、その説明は省略する。

【0064】

駆動回路49はDA変換器131により構成される。この時、図8(a)で示されるような信号が前記ドライブ回路41におけるΣΔ変調器61へ入力され、図8(b)で示される1bitのパルス密度変調信号へと変換される。そしてこの1bitのパルス密度変調信号が前記デジタルAGC回路47へ入力されて任意のAGCゲイン特性によりゲインコントロールされた図8(c)で示されるような±G[LSB]のマルチビットのパルス密度変調信号に変換され、このマルチビットのパルス密度変調信号が直接前記DA変換器131に入力され、前記DA変換器131よりパルス密度変調信号が図8(d)で示されるようなG[LSB]の値に応じた振幅電圧の駆動信号として出力され、前記センサ素子30におけるモニタ電極33へと入力されることになる。この駆動信号はモニタ電極33より出力された信号の所定の周波数成分をデジタルAGCにより振幅調整されて含んでいることになり、この信号がセンサ素子30に出力されることによって、前記振動体31の振動が所定の共振周波数において一定振幅で振動するよう制御されることになる。以上のように、ΣΔ変調器61、デジタルAGC回路47、DA変換器131という少ない回路点数によりドライブ回路が構成でき、これにより、小型で、かつ低コストの角速度センサを提供することができるという効果が得られるものである。さらに、振動させたい所定の周波数以外でセンサ素子の応答ゲインが高い不要な周波数成分やΣΔ変調による高周波ノイズを除去するように周波数特性が設定されたデジタルフィルタ48もしくはアナログフィルタ87を追加することにより、さらに高精度で、かつ低ノイズのドライブ回路を有する角速度センサを提供することができるという効果が得られるものである。

【産業上の利用可能性】

【0065】

本発明のデジタルAGC回路およびそれを用いた角速度センサは、ゲイン算出等の演算において、乗算器を必要としない小型のAGC回路およびそれを用いた角速度センサを提供することができるという効果を有するものであり、特に、センサデバイスにおけるセンサ素子の振動制御に用いられるデジタルAGC回路とそれを用いた角速度センサとして有用なものである。

【図面の簡単な説明】

【0066】

【図1】本発明の実施の形態1におけるデジタルAGC回路を用いた角速度センサの回路図

【図2】同角速度センサのドライブ回路におけるデジタルフィルタの回路図

【図3】(a)〜(c)ΣΔ変調器の動作状態を示す図

【図4】(a)、(b)デジタルAGC回路の動作状態を示す図

【図5】本発明の実施の形態1におけるAGC回路のAGCゲイン特性を示す図

【図6】(a)〜(f)同デジタルAGC回路を用いた角速度センサの動作状態を示す図

【図7】本発明の実施の形態2におけるデジタルAGC回路を用いた角速度センサの回路図

【図8】(a)〜(d)同角速度センサの動作状態を示す図

【図9】従来のΣΔ型AD変換器の回路図

【符号の説明】

【0067】

30 センサ素子

32 駆動電極

33 モニタ電極

34,35 センス電極

41 ドライブ回路

43,98 DA変換手段

44 積分手段

45 比較手段

46 置換演算手段

47 デジタルAGC回路

48 デジタルフィルタ

49 駆動回路

61,116 ΣΔ変調器

71 振幅検出手段

72 ゲイン算出手段

73 置換演算手段

75 ピークホールド手段

77 ビットシフト演算手段

79 ROM

91 PLL回路

93 タイミング制御手段

97 DA切替手段

106 積分回路

113 比較手段

124 センス回路

154 ビットシフト演算手段

【特許請求の範囲】

【請求項1】

少なくとも2つのレベルの電荷量を出力するDA変換手段と、このDA変換手段から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段と、この積分手段から出力される積分値を所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段と、デジタルフィルタと、PLL回路を有するタイミング制御手段とで構成したデジタルAGC回路。

【請求項2】

ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けた請求項1記載のデジタルAGC回路。

【請求項3】

ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成とした請求項1記載のデジタルAGC回路。

【請求項4】

振幅検出手段にデジタルフィルタとピークホールド手段とを設けた請求項1記載のデジタルAGC回路。

【請求項5】

デジタルフィルタをビットシフト演算手段で構成した請求項1記載のデジタルAGC回路。

【請求項6】

駆動電極と、センス電極と、モニタ電極とを有するセンサ素子と、このセンサ素子を所定の振幅で振動駆動させるドライブ回路と、前記センサ素子におけるセンス電極から出力される信号を角速度出力信号に変換するセンス回路とを備え、前記ドライブ回路を、少なくとも2つのレベルの電荷量を出力するDA変換手段と、前記センサ素子におけるモニタ電極から出力される信号とDA変換手段とから出力される電荷を積分し、その積分値を保持する積分回路と、この積分回路から出力される積分値を少なくとも1つの所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ型変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段を備えたデジタルAGC回路と、デジタルフィルタと、PLL回路を有するタイミング制御手段と、駆動回路とで構成した角速度センサ。

【請求項7】

ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けた請求項6記載の角速度センサ。

【請求項8】

ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成とした請求項6記載の角速度センサ。

【請求項9】

振幅検出手段にデジタルフィルタピークホールド手段とを設けた請求項6記載の角速度センサ。

【請求項10】

デジタルフィルタをビットシフト演算手段で構成した請求項6記載の角速度センサ。

【請求項1】

少なくとも2つのレベルの電荷量を出力するDA変換手段と、このDA変換手段から出力される信号と外部から入力される信号とを加算・積分しその積分値を保持する積分手段と、この積分手段から出力される積分値を所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段と、デジタルフィルタと、PLL回路を有するタイミング制御手段とで構成したデジタルAGC回路。

【請求項2】

ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けた請求項1記載のデジタルAGC回路。

【請求項3】

ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成とした請求項1記載のデジタルAGC回路。

【請求項4】

振幅検出手段にデジタルフィルタとピークホールド手段とを設けた請求項1記載のデジタルAGC回路。

【請求項5】

デジタルフィルタをビットシフト演算手段で構成した請求項1記載のデジタルAGC回路。

【請求項6】

駆動電極と、センス電極と、モニタ電極とを有するセンサ素子と、このセンサ素子を所定の振幅で振動駆動させるドライブ回路と、前記センサ素子におけるセンス電極から出力される信号を角速度出力信号に変換するセンス回路とを備え、前記ドライブ回路を、少なくとも2つのレベルの電荷量を出力するDA変換手段と、前記センサ素子におけるモニタ電極から出力される信号とDA変換手段とから出力される電荷を積分し、その積分値を保持する積分回路と、この積分回路から出力される積分値を少なくとも1つの所定の値と比較する比較手段と、この比較手段の出力に応じて前記DA変換手段の出力を切り替えるDA切替手段とにより構成してなるΣΔ型変調器と、振幅検出手段と、ゲイン算出手段と、置換演算手段を備えたデジタルAGC回路と、デジタルフィルタと、PLL回路を有するタイミング制御手段と、駆動回路とで構成した角速度センサ。

【請求項7】

ゲイン算出手段にビットシフト演算手段と加算演算手段とを設けた請求項6記載の角速度センサ。

【請求項8】

ROMに格納されたデータをゲイン算出手段および/またはデジタルフィルタに入力する構成とした請求項6記載の角速度センサ。

【請求項9】

振幅検出手段にデジタルフィルタピークホールド手段とを設けた請求項6記載の角速度センサ。

【請求項10】

デジタルフィルタをビットシフト演算手段で構成した請求項6記載の角速度センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2009−194798(P2009−194798A)

【公開日】平成21年8月27日(2009.8.27)

【国際特許分類】

【出願番号】特願2008−35595(P2008−35595)

【出願日】平成20年2月18日(2008.2.18)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成21年8月27日(2009.8.27)

【国際特許分類】

【出願日】平成20年2月18日(2008.2.18)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]