デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本願開示は、一般に電子回路に関し、詳しくはデジタルPLL回路に関する。

【背景技術】

【0002】

デジタルPLL(Phase Locked Loop)回路は、デジタル位相比較器、デジタルループフィルタ、DA変換器、電圧制御発振器、分周器、及び位相カウントクロック生成器を含む。デジタル位相比較器は、位相カウントクロック生成器から位相カウントクロックを受け取ると共に、外部クロック源からのマスタクロック(基準クロック)と分周器からのスレーブクロック(分周クロック)とを受け取る。デジタル位相比較器は、マスタクロックとスレーブクロックとの位相差を、位相カウントクロックのパルス数として計数する。位相差を示すカウント値がデジタルループフィルタにより時間平均化され、平均化後のカウント値がDA変換器によりアナログ電圧に変換される。電圧制御発振器が、このアナログ電圧に応じた周波数のクロック信号を発振する。この発振クロック信号が分周器により所定の分周比で分周され、得られた分周クロック信号が、デジタル位相比較器にスレーブクロックとして印加される。このフィードバック制御により、マスタクロックとスレーブクロックとの周波数が等しく且つ位相が所定の位相関係となるように、電圧制御発振器の発振クロック信号が制御される。

【0003】

デジタル位相比較器は、マスタクロックのパルスとそれに後続するスレーブクロックのパルスとの時間差を、位相カウントクロックのパルス数として計数することにより、位相差を検出する。このような位相差検出では、パルス同士の対応関係をパルス間の距離に関わらずに検知するのではなく、1サイクル内でパルス同士を対応させるので、検出される位相差は常に−πから+πの範囲の値となる。位相差が増加して+πより大きくなると、反対側の端である−π側に位相差が現れる。また逆に位相差が減少して−πより小さくなると、反対側の端である+π側に位相差が現れる。

【0004】

このように−πから+πの範囲の上端と下端との間で位相差が急激に遷移すると、PLL回路がスレーブクロックをマスタクロックに位相合わせする動作(引き込み動作)が遅くなる。即ち、フィードバック制御による収束対象の位相差が、引き込み動作の間振動するために、引き込み時間が長くなってしまう。この現象は、サイクルスリップと呼ばれ、高速引き込みが要求されるシステムでは問題となってしまう。

【0005】

理想PLLでは、引き込み時間は、固有周波数とダンピングファクタ(制動係数)で決まる。固有周波数が高く、ダンピンクファクタが小さい方が、引き込みが速い。また、サイクルスリップも発生しにくい。従来技術では、これらのパラメータを引き込み時とロック時で切り替えることで、上述の問題を回避している。しかしながら、固有周波数を高く(或いはダンピングファクタを小さく)するとループの安定性が悪くなり、発振してしまう可能性があるので、これらのパラメータでの調整には限界がある。また、パラメータを切り替えるということで、回路規模が増大することになる。更には、サイクルスリップが発生するようなケースでは、単純な計算では引き込み時間を見積むことができず、シミュレータによる解析が必要になるという問題もある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−343724号公報

【特許文献2】特表2006−518151号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

以上を鑑みると、位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供することが望まれる。

【課題を解決するための手段】

【0008】

デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器と、前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正する補正部と、前記補正部の出力する前記位相値に応じて前記スレーブクロックを生成するスレーブクロック生成部とを含むことを特徴とする。

【0009】

デジタルPLL回路におけるクロック生成方法は、マスタクロックとスレーブクロックとの位相差を検出することにより、長さが2πの範囲内の値をとる位相差検出値を求め、前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正し、前記位相値に応じて前記スレーブクロックを生成する各段階を含むことを特徴とする。

【発明の効果】

【0010】

本願開示の少なくとも1つの実施例によれば、位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供することができる。

【図面の簡単な説明】

【0011】

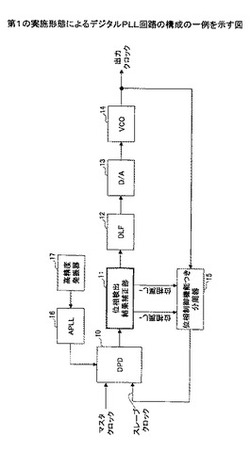

【図1】第1の実施形態によるデジタルPLL回路の構成の一例を示す図である。

【図2】デジタル位相比較器の構成の一例を示す図である。

【図3】図2に示すデジタル位相比較器の動作の一例を示す図である。

【図4】位相検出結果補正部の構成の一例を示す図である。

【図5】位相検出結果補正部の動作シーケンスを示す図である。

【図6】位相制御機能付き分周器の構成の一例を示す図である。

【図7】位相制御機能付き分周器の動作の一例を模式的に示す図である。

【図8】位相戻し動作の一例を模式的に示す図である。

【図9】位相検出結果補正部による補正計算を模式的に示す図である。

【図10】位相戻し動作の別の一例を模式的に示す図である。

【図11】図1に示すデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。

【図12】比較のために従来のデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。

【図13】第2の実施形態によるデジタルPLL回路の構成の一例を示す図である。

【図14】位相検出結果補正部の構成の一例を示す図である。

【図15】図1又は図13に示すデジタルPLL回路を適用したシステムの構成の一例を示す図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

【0013】

図1は、第1の実施形態によるデジタルPLL回路の構成の一例を示す図である。図1に示すデジタルPLL回路は、デジタル位相比較器(DPD)10、位相検出結果補正部11、デジタルループフィルタ(DLF)12、DA変換器(D/A)13、電圧制御発振器(VCO)14、及び位相制御機能付き分周器15を含む。デジタルPLL回路は更に、位相カウントクロック生成器として、アナログPLL(APLL)16及び高精度発振器17を含む。アナログPLL16は、高精度発振器17の発振信号を逓倍することにより、高精度で高周波の位相カウント用のクロック信号を生成する。なお図1及び以降の図において、各ボックスで示される各機能ブロックと他の機能ブロックとの境界は、基本的には機能的な境界を示すものであり、物理的な位置の分離、電気的な信号の分離、制御論理的な分離等に対応するとは限らない。ハードウェアの場合、各機能ブロックは、他のブロックと物理的にある程度分離された1つのハードウェアモジュールであってもよいし、或いは他のブロックと物理的に一体となったハードウェアモジュール中の1つの機能を示したものであってもよい。

【0014】

デジタル位相比較器10は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力する。具体的には、デジタル位相比較器10は、アナログPLL16から位相カウントクロックを受け取ると共に、外部クロック源からのマスタクロック(基準クロック)と位相制御機能付き分周器15からのスレーブクロック(分周クロック)とを受け取る。デジタル位相比較器10は、マスタクロックとスレーブクロックとの位相差を、位相カウントクロックのパルス数として計数して、計数結果を位相差検出値として出力する。この位相差検出値は、例えば0〜2πの範囲内の位相差を示すデジタル値であってよい。範囲の下限と上限は、任意であってよく、0〜2πの範囲の代りに例えば−π〜+πの範囲であると考えてもよい。これは、位相ゼロの基準点を何処にとるか、或いは、範囲の左端と右端を何処にとるかの違いであり、本質的な問題ではない。

【0015】

位相検出結果補正部11は、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を上記の範囲に限定されない位相値に補正する。デジタルループフィルタ12、DA変換器13、電圧制御発振器14、及び位相制御機能付き分周器15は、スレーブクロックを生成するスレーブクロック生成部として機能する。このスレーブクロック生成部は、位相検出結果補正部11の出力する補正後の位相値に応じて、スレーブクロックを生成する。具体的には、補正後の位相値がデジタルループフィルタ12により時間平均化され、平均化後のカウント値がDA変換器13によりアナログ電圧に変換される。電圧制御発振器14が、このアナログ電圧に応じた周波数のクロック信号を発振する。この発振クロック信号が位相制御機能付き分周器15により所定の分周比で分周され、得られた分周クロック信号が、デジタル位相比較器10にスレーブクロックとして印加される。このフィードバック制御により、マスタクロックとスレーブクロックとの周波数が等しく且つ位相が所定の位相関係となるように、電圧制御発振器14の発振クロック信号が制御される。

【0016】

図2は、デジタル位相比較器10の構成の一例を示す図である。図2に示すデジタル位相比較器10は、立ち上がりエッジ検出器21、立ち上がりエッジ検出器22、カウンタ23、レジスタ24、及び減算器25を含む。立ち上がりエッジ検出器21は、マスタクロック(基準クロック)REF_CLKの立ち上がりエッジを検出すると、その出力をアサートする。立ち上がりエッジ検出器22は、スレーブクロック(フィードバッククロック)FB_CLKの立ち上がりエッジを検出すると、その出力をアサートする。カウンタ23は、位相カウントクロックDPD_CLKの各パルスに同期して1ずつカウントアップし、立ち上がりエッジ検出器21の出力のアサートによりゼロにリセットされる。レジスタ24は、立ち上がりエッジ検出器22の出力のアサートに応答して、カウンタ23の出力カウント値を取り込み保持する。減算器25は、レジスタ24に格納されるカウント値から、収束位相の位相カウント値を減算することにより、位相比較結果(位相差検出値)を出力する。

【0017】

図3は、図2に示すデジタル位相比較器10の動作の一例を示す図である。カウンタ23により、マスタクロックREF_CLKのパルス27の立ち上がりエッジから、それに後続するスレーブクロックFB_CLKのパルス28の立ち上がりエッジまでの期間、位相カウントクロックDPD_CLKのパルス数を計数する。そのようにして計数されるパルス数が図3にCountとして示される。この計数値Countは、パルス27の立ち上がりエッジからパルス28の立ち上がりエッジ迄の期間長Tに相当する。この計数結果に基づいて、デジタル位相比較器10は、位相差検出値としてCount−π_Countを出力する。ここでπ_Countは、収束位相の位相カウント値である。例えば、0から2πの範囲の中心位置(位相πの位置)、即ちマスタクロックREF_CLKの隣接する2つのパルスのちょうど中間の位置に、スレーブクロックFB_CLKのパルスを収束させたい場合、π_Countは位相πに相当するカウント値となる。この場合、デジタルPLL回路による引き込み動作が完了して安定状態となると、位相差検出値Count−π_Countはゼロ近傍の値となる。

【0018】

図4は、位相検出結果補正部11の構成の一例を示す図である。図4に示す位相検出結果補正部11は、閾値比較部31、カウント値レジスタ32、加算器33、及び積算器34を含む。閾値比較部31は、デジタル位相比較器10からの位相差検出値と閾値とを比較する。この位相差検出値と閾値とを比較した結果は、第1の状態、第2の状態、又は第3の状態をとる。閾値としては、0〜2πの範囲内で、この範囲の中心より位相が小さい側に位置する第1の閾値と、範囲の中心より位相が大きい側に位置する第2の閾値とを含む。第1の状態は、位相差検出値が第1の閾値よりも小さくなった状態、即ち0〜2πの範囲内で0側の端に近づいた状態である。第2の状態は、位相差検出値が第2の閾値よりも大きくなった状態、即ち0〜2πの範囲内で2π側の端に近づいた状態である。第3の状態は、位相差検出値が第1の閾値以上で且つ第2の閾値以下の状態、即ち0〜2πの範囲内で両端に近くない位置に位相差検出値が存在する状態である。

【0019】

カウント値レジスタ32は、カウント値を格納するとともに、閾値比較部31からの指示に応じてカウント値を1増減する機能を有する。閾値比較部31が上記第1の状態を検出すると、図4の「位相戻し+」がアサートされ、カウント値レジスタ32のカウント値が1減少する。閾値比較部31が上記第2の状態を検出すると、図4の「位相戻し−」がアサートされ、カウント値レジスタ32のカウント値が1増加する。閾値比較部31が上記第3の状態を検出すると、「位相戻し+」及び「位相戻し−」のいずれもアサートされず、カウント値レジスタ32のカウント値はそのまま同一の値に保持される。積算器34は、カウント値レジスタ32のカウント値に所定の位相量(位相戻し量)を積算した値を求める。こうして求めた値を、加算器33が、位相検出結果補正部11からの位相検出値に加算することにより補正後の位相値を求める。

【0020】

図5は、位相検出結果補正部11の動作シーケンスを示す図である。ステップS1で、位相検出結果補正部11から位相検出結果(位相差検出値)を取得する。ステップS2で、位相検出結果が上限閾値(上記第2の閾値)より大きいか否かを判定する。上限閾値より大きい場合には、ステップS3で、位相戻し(−方向)のトリガを発生する(図1及び図4に示す「位相戻し−」をアサートする)。更に、ステップS4で、カウント値レジスタ32のカウント値COUNTを+1する。

【0021】

更に、ステップS5で、位相検出結果が下限閾値(上記第1の閾値)より小さいか否かを判定する。下限閾値より小さい場合には、ステップS6で、位相戻し(+方向)のトリガを発生する(図1及び図4に示す「位相戻し+」をアサートする)。更に、ステップS7で、カウント値レジスタ32のカウント値COUNTを−1する。

【0022】

最後にステップS8で、位相戻し量をCOUNT倍した値を位相検出結果補正部11からの位相検出結果に加算する。この結果得られた補正後の位相値が、スレーブクロック生成部によるループフィルタ処理に供給される。

【0023】

位相検出結果補正部11は、位相差検出値が第1の閾値よりも小さくなると、「位相戻し+」をアサートすることにより、スレーブクロック生成部の位相制御機能付き分周器15に指示してスレーブクロックの位相を変化させ、位相差検出値を大きくする。位相検出結果補正部11は、位相差検出値が第2の閾値よりも大きくなると、「位相戻し−」をアサートすることにより、スレーブクロック生成部の位相制御機能付き分周器15に指示してスレーブクロックの位相を変化させ、位相差検出値を小さくする。

【0024】

図6は、位相制御機能付き分周器15の構成の一例を示す図である。図6に示す位相制御機能付き分周器15は、制御ロジック41、カウンタ42、一致検出器43、及びフリップフロップ44を含む。カウンタ42は、電圧制御発振器14が発振する被分周クロック信号の各パルスに同期してカウントアップする。一致検出器43は、カウンタ42の出力するカウント値と分周設定値とが一致すると、その出力をアサートする。カウンタ42は、一致検出器43の出力のアサートに応答して、次の被分周クロック信号のパルスのタイミングでゼロにリセットされる。例えば分周設定値が3である場合、カウント値が3になると、カウンタ42は次のタイミングでリセットされてカウント値が0に戻る。フリップフロップ44は、被分周クロック信号を同期信号として、一致検出器43の出力をラッチする。従って、カウント値と分周設定値とが一致して一致検出器43の出力が1にアサートされると、次の被分周クロック信号のパルスに同期してフリップフロップ44が1にセットされる。この結果、被分周クロックの1サイクルの間、分周クロック出力としてHIGHパルスが出力される。例えば分周設定値が3である場合、被分周クロックの4サイクルに一度、分周クロックのパルスが出力されることになり、周波数を1/4にする分周動作が実現される。

【0025】

制御ロジック41は、位相検出結果補正部11からの「位相戻し+」がアサートされると、次のマスタクロックREF_CLKの立ち上がりエッジで、リロード信号1をアサートする。このリロード信号1のアサートに応答して、カウンタ42はリロード値1をリロードして、カウント値がリロード値1に設定される。制御ロジック41は、位相検出結果補正部11からの「位相戻し−」がアサートされると、次のマスタクロックREF_CLKの立ち上がりエッジで、リロード信号2をアサートする。このリロード信号2のアサートに応答して、カウンタ42はリロード値2をリロードして、カウント値がリロード値2に設定される。

【0026】

図7は、位相制御機能付き分周器15の動作の一例を模式的に示す図である。VCO出力(被分周クロック信号)の各パルスに同期して、カウンタ42のカウント値が0から3まで増加し、リセットされて0に戻る動作を繰り返す。従って、分周後クロックは1/4の周波数に分周した信号となる。ここでRとして示すタイミングで、カウンタ42にカウント値“2”がリロードされ、その後は2からのカウントアップを続行する。従って、リロードを実行しなければパルス46が分周後クロックとして出力されたところ、リロードを実行した結果、パルス47が分周後クロックとして出力され、位相が所定の位相量戻る(シフトする)ことになる。

【0027】

図8は、位相戻し動作の一例を模式的に示す図である。図8では、ゼロ位相をマスタクロックREF_CLKのパルス間の中間点に設定し、−π〜+πの位相範囲でスレーブクロックFB_CLKのパルスが移動していく様子を示している。タイミングt0において、位相制御機能付き分周器15により、スレーブクロックFB_CLKのパルス51が図示の位相位置に出力される。次のサイクルのタイミングt1において、スレーブクロックFB_CLKのパルス52が図示の位相位置に出力される。パルス51からパルス52でパルス位置が右に移動するのは、マスタクロックREF_CLKの周波数に対してスレーブクロックFB_CLKの周波数が低いためである。同様にして、t1の次のサイクルのタイミングt2において、スレーブクロックFB_CLKのパルス53が図示の位相位置に出力され、更にt2の次のサイクルのタイミングt3において、スレーブクロックFB_CLKのパルス54が図示の位相位置に出力される。このとき、パルス54に対して検出された位相差検出値が第2の閾値よりも大きくなる、即ちパルス54の位相位置が第2の閾値の位置よりも右側となるので、位相検出結果補正部11から位相制御機能付き分周器15に対して「位相戻し−」をアサートする。

【0028】

「位相戻し−」のアサート(位相検出結果補正部11からの負の位相方向への位相戻し指示)に応答して、位相制御機能付き分周器15は、内部状態(カウント値)を再設定(リロード)することにより、パルス54の位置がパルス54’の位置まで戻される。なおこのパルス54’は実際に出力されるスレーブクロックFB_CLKのパルスではなく、カウンタのリロードにより、前回のパルス54の位置(カウント値が0に相当する位置)が−π〜+πの位相範囲の何処に存在することになるかを示したものである。その後、t3の次のサイクルのタイミングt4において、スレーブクロックFB_CLKのパルス55が図示の位相位置に出力される。リロードを実行しなければパルス56がスレーブクロックFB_CLKとして出力されたところ、リロードを実行した結果、パルス55がスレーブクロックFB_CLKとして出力され、位相が所定の位相量戻る(シフトする)ことになる。

【0029】

図8の下半分には、横軸に位相、縦軸に−π〜+πの範囲制限により折り返される位相値を示すグラフにおいて、上記説明したt1〜t4の各タイミングでのスレーブクロックFB_CLKのパルスの位相位置(即ち位相差検出値)を示している。各タイミングt1,t2,t3,t4で検出される位相差検出値は、図中の黒丸で示す位相位置のものとなる。タイミングt3’に示す位相位置は、実際に出力されるスレーブクロックのパルスの位相位置を示すものではなく、カウンタのリロードにより、タイミングt3のパルスの位置が−π〜+πの位相範囲の何処に存在することになるかを示したものである。タイミングt4での位相差検出値は、リロードを実行しなければ位相位置58となるところ、リロードを実行した結果、位相位置57となり、位相が所定の位相量戻る(シフトする)ことになる。ここでリロードにより戻る位相量をPdOffsetとして示し、タイミングt4での位相差検出値をPdOut_t4として示してある。位相戻り量PdOffsetは、スレーブクロックの周波数がマスタクロックの周波数と略等しい場合には、リロード値に応じた略固定の既知の値であると考えてよい。なお、第1の閾値と第2の閾値とは、不要な位相戻しが実行されないように、−π〜+πの位相範囲の端に十分に近い位置に設定されることが望ましい。但し、閾値と端との間の区間が狭すぎて、パルスが一度もその区間内で検出されることなく飛び越してしまうことがないように、第1の閾値と第2の閾値とを適切な値に設定することが好ましい。

【0030】

図9は、位相検出結果補正部11による補正計算を模式的に示す図である。図9において、横軸は位相を示し、縦軸は0〜2πの範囲制限により折り返される位相値を示す。図8で説明したタイミングt4での位相差検出値PdOut_t4は、位相位置57にある。この位相位置57の位相差検出値(位相検出結果補正部11の出力値)に、位相戻り量PdOffsetを加算することにより、位相位置59にある補正後の位相値が計算される。この補正後の位相値に基づいて、スレーブクロック生成部がスレーブクロックを生成する。従って、デジタルPLL回路は、0〜2πの範囲制限による折り返しによる影響を受けることなく、高速な引き込み動作を実行できる。

【0031】

図10は、位相戻し動作の別の一例を模式的に示す図である。図10には、ゼロ位相をマスタクロックREF_CLKのパルス間の中間点に設定し、−π〜+πの位相範囲でスレーブクロックFB_CLKのパルスが移動していく様子を示している。各タイミングでのパルス波形の右側には、図4に示す位相検出結果補正部11のカウント値レジスタ32に格納されるカウント値(図5に示すCOUNT)の値を示す。上側から下側に向かい時間が進行するにつれて、スレーブクロックFB_CLKのパルスは、その位相が増大する方向に最初は移動している。スレーブクロックFB_CLKのパルス61が第2の閾値よりも右側に位置するようになると、位相戻し動作が実行され、パルス位置が−π〜+πの位相範囲の中心あたりに戻される。この負の方向への位相戻し動作に伴い、カウント値が0から1に増加する。なおこの例では、パルス位置を−π〜+πの位相範囲の中心あたりに戻す構成となっているが、パルスを戻す位置は特定の位置に限定されるものではない。パルス61が第2の閾値よりも右側に位置するということは、スレーブクロックFB_CLKの現在の状態が位相値の増大する方向に設定されていることを意味するので、例えば−πに近い位置までパルスを戻すような構成としてもよい。

【0032】

その後、時間が進行するにつれて、スレーブクロックFB_CLKの状態が変化し、位相が減少する方向にパルス位置が移動し始める。スレーブクロックFB_CLKのパルス62が第1の閾値よりも右側に位置するようになると、位相戻し動作が実行され、パルス位置が−π〜+πの位相範囲の中心あたりに戻される。この正の方向への位相戻し動作に伴い、カウント値が1から0に減少する。なおこの例では、パルス位置を−π〜+πの位相範囲の中心あたりに戻す構成となっているが、パルスを戻す位置は特定の位置に限定されるものではない。パルス61が第1の閾値よりも左側に位置するということは、スレーブクロックFB_CLKの現在の状態が位相値の減少する方向に設定されていることを意味するので、例えば+πに近い位置までパルスを戻すような構成としてもよい。

【0033】

図11は、図1に示すデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。図11(a)において、横軸は時間を示し、縦軸はマスタクロックとスレーブクロックとの位相差を示す。図11(b)において、横軸は時間を示し、縦軸は周波数偏差を示す。図11(b)に示すシミュレーション入力73は、マスタクロックとスレーブクロックとに周波数差が無い状態から、マスタクロックの周波数がステップ関数的に6ppmだけ変動したことを示す。このマスタクロックの周波数変動に応答して、図11(a)に示す位相差変化71が発生する。位相差変化71が示すように、最初に位相差が2πを超えてしまっても、その後は安定した状態で徐々に位相差が減少していき最終的に0に収束している。即ち、位相差が2πを超えてもサイクルスリップが発生することなく、安定的に位相差が収束している。これに伴い図11(b)において、スレーブクロックの周波数変化72が示すように、スレーブクロックの周波数がマスタクロックの周波数に安定的に追従している。

【0034】

図12は、比較のために従来のデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。図12(a)において、横軸は時間を示し、縦軸はマスタクロックとスレーブクロックとの位相差を示す。図12(b)において、横軸は時間を示し、縦軸は周波数偏差を示す。シミュレーション入力は、図11(b)に示すものと同一であり、マスタクロックとスレーブクロックとに周波数差が無い状態から、マスタクロックの周波数がステップ関数的に6ppmだけ変動するものである。このマスタクロックの周波数変動に応答して、図12(a)に示す位相差変化74が発生する。位相差変化74が示すように、位相差が2πを超えるためにサイクルスリップが発生して長い期間振動した後に、徐々に位相差が減少して最終的に0に収束している。位相差変化71は図11(a)に示すものと同一の波形であり、比較のために位相差変化74と重ねて示してある。また図12(b)において、スレーブクロックの周波数変化75が示すように、サイクルスリップが発生して長い期間振動した後に、マスタクロックに追従している。周波数変化72は図11(b)に示すものと同一の波形であり、比較のために周波数変化75と重ねて示してある。このように、図1に示すデジタルPLL回路では、位相差検出値を補正して値の範囲が制限されない位相値を算出し、この補正後の位相値に基づいてスレーブクロックを生成することにより、安定した引き込み動作を実現できる。即ち、0〜2πの範囲制限により位相値が折り返されることにより発生する振動を抑制し、安定した引き込み動作を実現することができる。

【0035】

図13は、第2の実施形態によるデジタルPLL回路の構成の一例を示す図である。図13において、図1と同一の構成要素は同一又は対応する番号で参照し、その説明は適宜省略する。図13に示すデジタルPLL回路は、デジタル位相比較器(DPD)10、位相検出結果補正部81、デジタルループフィルタ(DLF)12、DA変換器(D/A)13、電圧制御発振器(VCO)14、及び分周器85を含む。デジタルPLL回路は更に、位相カウントクロック生成器として、アナログPLL(APLL)16及び高精度発振器17を含む。図13においては、位相検出結果補正部81及び分周器85が、図1の位相検出結果補正部11及び位相制御機能付き分周器15の代りに設けられている。

【0036】

図1の場合と同様に、デジタル位相比較器10が出力する位相差検出値は、例えば0〜2πの範囲内の位相差を示すデジタル値であってよい。範囲の下限と上限は、任意であってよく、0〜2πの範囲の代りに例えば−π〜+πの範囲であると考えてもよい。

【0037】

位相検出結果補正部81は、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を上記の範囲に限定されない位相値に補正する。デジタルループフィルタ12、DA変換器13、電圧制御発振器14、及び分周器85は、スレーブクロックを生成するスレーブクロック生成部として機能する。このスレーブクロック生成部は、位相検出結果補正部81の出力する補正後の位相値に応じて、スレーブクロックを生成する。具体的には、補正後の位相値がデジタルループフィルタ12により時間平均化され、平均化後のカウント値がDA変換器13によりアナログ電圧に変換される。電圧制御発振器14が、このアナログ電圧に応じた周波数のクロック信号を発振する。この発振クロック信号が分周器85により所定の分周比で分周され、得られた分周クロック信号が、デジタル位相比較器10にスレーブクロックとして印加される。このフィードバック制御により、マスタクロックとスレーブクロックとの周波数が等しく且つ位相が所定の位相関係となるように、電圧制御発振器14の発振クロック信号が制御される。

【0038】

図14は、位相検出結果補正部81の構成の一例を示す図である。位相検出結果補正部81は、レジスタ91及び92、比較器93乃至96、AND回路97及び98、セレクタ99、レジスタ100、加算器101、積算器102、及び加算器103を含む。比較器93乃至96は、位相差検出値と閾値とを比較する。位相差検出値と閾値とを比較した結果は第1の状態、第2の状態、又は第3の状態をとる。位相検出結果補正部81は、第1の状態を検出すると、レジスタ100に格納されるカウント値を1減らし、第2の状態を検出するとカウント値を1増やし、第3の状態を検出するとカウント値をそのまま保持する。位相検出結果補正部81の積算器102は、カウント値に所定の位相量(πカウント値)を積算した値を求める。位相検出結果補正部81の加算器103は、デジタル位相比較器10からの位相検出値に、積算器102が求めた値を加算することにより、補正後の位相値を求める。

【0039】

比較器93乃至96に比較対象として印加される閾値は、0〜2πの範囲内で、範囲の中心より位相が小さい側に位置する第1の閾値(下限閾値)と、範囲の中心より位相が大きい側に位置する第2の閾値(上限閾値)とを含む。上記第1の状態は、位相差検出値が第1の閾値よりも小さくなった直後に、第2の閾値よりも大きくなったことが検出された状態である。上記第2の状態は、位相差検出値が第2の閾値よりも大きくなった直後に、第1の閾値よりも小さくなったことが検出された状態である。具体的には、比較器93は、レジスタ91に格納されるある検出タイミングでの位相差検出値と第2の閾値とを比較し、位相差検出値が第2の閾値よりも大きくなると出力をアサートする。比較器94は、次の検出タイミングでの位相差検出値と第1の閾値とを比較し、位相差検出値が第1の閾値よりも小さくなると出力をアサートする。AND回路97は、ある検出タイミングで検出された位相差検出値が第2の閾値よりも大きくなり且つ次の検出タイミングで検出された位相差検出値が第1の閾値よりも小さくなると、出力をアサートする(第2の状態を検出する)。同様に、比較器96は、レジスタ92に格納されるある検出タイミングでの位相差検出値と第1の閾値とを比較し、位相差検出値が第1の閾値よりも小さくなると出力をアサートする。比較器95は、次の検出タイミングでの位相差検出値と第2の閾値とを比較し、位相差検出値が第2の閾値よりも大きくなると出力をアサートする。AND回路98は、ある検出タイミングで検出された位相差検出値が第1の閾値よりも小さくなり且つ次の検出タイミングで検出された位相差検出値が第2の閾値よりも大きくなると、出力をアサートする(第1の状態を検出する)。

【0040】

セレクタ99は、AND回路97の出力のアサート状態(第2の状態)に応答して、+1を選択して出力する。更にセレクタ99は、AND回路98の出力のアサート状態(第1の状態)に応答して、−1を選択して出力する。第1の状態も第2の状態も検出されない場合(第3の状態の場合)に、セレクタ99は、0を選択して出力する。セレクタ99の出力は、加算器101によりレジスタ100の格納値(カウント値)に加算される。加算結果は、レジスタ100に更新後のカウント値として格納される。積算器102は、レジスタ100のカウント値と所定の位相量(位相量πに相当するカウント値)とを積算して、積算結果を加算器103に供給する。加算器103は、デジタル位相比較器10からの位相差検出値と積算結果とを加算することにより、補正後の位相値を求める。

【0041】

図1に示す第1の実施形態のデジタルPLL回路では、位相差検出値が位相範囲の端に近づくと、位相差検出値を端から遠ざけるように位相戻し動作が実行される。またこの位相戻し動作に伴い、所定の位相量を位相差検出値に加算することで、補正後の位相値を求めている。それに対し図13に示す第2の実施形態のデジタルPLL回路では、位相差検出値が位相範囲の端を通過したこと、即ち位相差検出値が位相範囲の端を超えたことを検出すると、所定の位相量を位相差検出値に加算することで、補正後の位相値を求めている。位相差検出値が位相範囲の端を通過すると、位相値の折り返しにより逆側の端に位相差検出値が遷移することになるので、所定の位相量を位相差検出値に加算することにより、適切な補正結果を得ることができる。

【0042】

図15は、図1又は図13に示すデジタルPLL回路を適用したシステムの構成の一例を示す図である。図15に示すシステムは、A/Dコンバータ111及びデジタルPLL回路112を含む。A/Dコンバータ111は、アナログ映像信号を受け取り、アナログ映像信号をデジタル映像信号に変換する。この信号変換の際に、A/Dコンバータ111は、アナログ映像信号のアナログ電圧を所定のサンプリングクロックに同期してサンプリングしてホールドし、ホールドされたアナログ電圧を並列或いは逐次処理によりデジタル値に変換する。デジタルPLL回路112は、複合同期信号等を基準クロック(マスタクロック)として、基準クロックに同期したサンプリングクロックを生成する。デジタルPLL回路112は、図1又は図13に示すデジタルPLL回路であり、位相差検出値の範囲制限に影響を受けることなく、高速に引き込み動作を実行することができる。

【0043】

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

【符号の説明】

【0044】

10 デジタル位相比較器(DPD)

11 位相検出結果補正部

12 デジタルループフィルタ(DLF)

13 DA変換器(D/A)

14 電圧制御発振器(VCO)

15 位相制御機能付き分周器

16 アナログPLL(APLL)

17 高精度発振器

81 位相検出結果補正部

85 分周器

【技術分野】

【0001】

本願開示は、一般に電子回路に関し、詳しくはデジタルPLL回路に関する。

【背景技術】

【0002】

デジタルPLL(Phase Locked Loop)回路は、デジタル位相比較器、デジタルループフィルタ、DA変換器、電圧制御発振器、分周器、及び位相カウントクロック生成器を含む。デジタル位相比較器は、位相カウントクロック生成器から位相カウントクロックを受け取ると共に、外部クロック源からのマスタクロック(基準クロック)と分周器からのスレーブクロック(分周クロック)とを受け取る。デジタル位相比較器は、マスタクロックとスレーブクロックとの位相差を、位相カウントクロックのパルス数として計数する。位相差を示すカウント値がデジタルループフィルタにより時間平均化され、平均化後のカウント値がDA変換器によりアナログ電圧に変換される。電圧制御発振器が、このアナログ電圧に応じた周波数のクロック信号を発振する。この発振クロック信号が分周器により所定の分周比で分周され、得られた分周クロック信号が、デジタル位相比較器にスレーブクロックとして印加される。このフィードバック制御により、マスタクロックとスレーブクロックとの周波数が等しく且つ位相が所定の位相関係となるように、電圧制御発振器の発振クロック信号が制御される。

【0003】

デジタル位相比較器は、マスタクロックのパルスとそれに後続するスレーブクロックのパルスとの時間差を、位相カウントクロックのパルス数として計数することにより、位相差を検出する。このような位相差検出では、パルス同士の対応関係をパルス間の距離に関わらずに検知するのではなく、1サイクル内でパルス同士を対応させるので、検出される位相差は常に−πから+πの範囲の値となる。位相差が増加して+πより大きくなると、反対側の端である−π側に位相差が現れる。また逆に位相差が減少して−πより小さくなると、反対側の端である+π側に位相差が現れる。

【0004】

このように−πから+πの範囲の上端と下端との間で位相差が急激に遷移すると、PLL回路がスレーブクロックをマスタクロックに位相合わせする動作(引き込み動作)が遅くなる。即ち、フィードバック制御による収束対象の位相差が、引き込み動作の間振動するために、引き込み時間が長くなってしまう。この現象は、サイクルスリップと呼ばれ、高速引き込みが要求されるシステムでは問題となってしまう。

【0005】

理想PLLでは、引き込み時間は、固有周波数とダンピングファクタ(制動係数)で決まる。固有周波数が高く、ダンピンクファクタが小さい方が、引き込みが速い。また、サイクルスリップも発生しにくい。従来技術では、これらのパラメータを引き込み時とロック時で切り替えることで、上述の問題を回避している。しかしながら、固有周波数を高く(或いはダンピングファクタを小さく)するとループの安定性が悪くなり、発振してしまう可能性があるので、これらのパラメータでの調整には限界がある。また、パラメータを切り替えるということで、回路規模が増大することになる。更には、サイクルスリップが発生するようなケースでは、単純な計算では引き込み時間を見積むことができず、シミュレータによる解析が必要になるという問題もある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2004−343724号公報

【特許文献2】特表2006−518151号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

以上を鑑みると、位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供することが望まれる。

【課題を解決するための手段】

【0008】

デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器と、前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正する補正部と、前記補正部の出力する前記位相値に応じて前記スレーブクロックを生成するスレーブクロック生成部とを含むことを特徴とする。

【0009】

デジタルPLL回路におけるクロック生成方法は、マスタクロックとスレーブクロックとの位相差を検出することにより、長さが2πの範囲内の値をとる位相差検出値を求め、前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正し、前記位相値に応じて前記スレーブクロックを生成する各段階を含むことを特徴とする。

【発明の効果】

【0010】

本願開示の少なくとも1つの実施例によれば、位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供することができる。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態によるデジタルPLL回路の構成の一例を示す図である。

【図2】デジタル位相比較器の構成の一例を示す図である。

【図3】図2に示すデジタル位相比較器の動作の一例を示す図である。

【図4】位相検出結果補正部の構成の一例を示す図である。

【図5】位相検出結果補正部の動作シーケンスを示す図である。

【図6】位相制御機能付き分周器の構成の一例を示す図である。

【図7】位相制御機能付き分周器の動作の一例を模式的に示す図である。

【図8】位相戻し動作の一例を模式的に示す図である。

【図9】位相検出結果補正部による補正計算を模式的に示す図である。

【図10】位相戻し動作の別の一例を模式的に示す図である。

【図11】図1に示すデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。

【図12】比較のために従来のデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。

【図13】第2の実施形態によるデジタルPLL回路の構成の一例を示す図である。

【図14】位相検出結果補正部の構成の一例を示す図である。

【図15】図1又は図13に示すデジタルPLL回路を適用したシステムの構成の一例を示す図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

【0013】

図1は、第1の実施形態によるデジタルPLL回路の構成の一例を示す図である。図1に示すデジタルPLL回路は、デジタル位相比較器(DPD)10、位相検出結果補正部11、デジタルループフィルタ(DLF)12、DA変換器(D/A)13、電圧制御発振器(VCO)14、及び位相制御機能付き分周器15を含む。デジタルPLL回路は更に、位相カウントクロック生成器として、アナログPLL(APLL)16及び高精度発振器17を含む。アナログPLL16は、高精度発振器17の発振信号を逓倍することにより、高精度で高周波の位相カウント用のクロック信号を生成する。なお図1及び以降の図において、各ボックスで示される各機能ブロックと他の機能ブロックとの境界は、基本的には機能的な境界を示すものであり、物理的な位置の分離、電気的な信号の分離、制御論理的な分離等に対応するとは限らない。ハードウェアの場合、各機能ブロックは、他のブロックと物理的にある程度分離された1つのハードウェアモジュールであってもよいし、或いは他のブロックと物理的に一体となったハードウェアモジュール中の1つの機能を示したものであってもよい。

【0014】

デジタル位相比較器10は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力する。具体的には、デジタル位相比較器10は、アナログPLL16から位相カウントクロックを受け取ると共に、外部クロック源からのマスタクロック(基準クロック)と位相制御機能付き分周器15からのスレーブクロック(分周クロック)とを受け取る。デジタル位相比較器10は、マスタクロックとスレーブクロックとの位相差を、位相カウントクロックのパルス数として計数して、計数結果を位相差検出値として出力する。この位相差検出値は、例えば0〜2πの範囲内の位相差を示すデジタル値であってよい。範囲の下限と上限は、任意であってよく、0〜2πの範囲の代りに例えば−π〜+πの範囲であると考えてもよい。これは、位相ゼロの基準点を何処にとるか、或いは、範囲の左端と右端を何処にとるかの違いであり、本質的な問題ではない。

【0015】

位相検出結果補正部11は、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を上記の範囲に限定されない位相値に補正する。デジタルループフィルタ12、DA変換器13、電圧制御発振器14、及び位相制御機能付き分周器15は、スレーブクロックを生成するスレーブクロック生成部として機能する。このスレーブクロック生成部は、位相検出結果補正部11の出力する補正後の位相値に応じて、スレーブクロックを生成する。具体的には、補正後の位相値がデジタルループフィルタ12により時間平均化され、平均化後のカウント値がDA変換器13によりアナログ電圧に変換される。電圧制御発振器14が、このアナログ電圧に応じた周波数のクロック信号を発振する。この発振クロック信号が位相制御機能付き分周器15により所定の分周比で分周され、得られた分周クロック信号が、デジタル位相比較器10にスレーブクロックとして印加される。このフィードバック制御により、マスタクロックとスレーブクロックとの周波数が等しく且つ位相が所定の位相関係となるように、電圧制御発振器14の発振クロック信号が制御される。

【0016】

図2は、デジタル位相比較器10の構成の一例を示す図である。図2に示すデジタル位相比較器10は、立ち上がりエッジ検出器21、立ち上がりエッジ検出器22、カウンタ23、レジスタ24、及び減算器25を含む。立ち上がりエッジ検出器21は、マスタクロック(基準クロック)REF_CLKの立ち上がりエッジを検出すると、その出力をアサートする。立ち上がりエッジ検出器22は、スレーブクロック(フィードバッククロック)FB_CLKの立ち上がりエッジを検出すると、その出力をアサートする。カウンタ23は、位相カウントクロックDPD_CLKの各パルスに同期して1ずつカウントアップし、立ち上がりエッジ検出器21の出力のアサートによりゼロにリセットされる。レジスタ24は、立ち上がりエッジ検出器22の出力のアサートに応答して、カウンタ23の出力カウント値を取り込み保持する。減算器25は、レジスタ24に格納されるカウント値から、収束位相の位相カウント値を減算することにより、位相比較結果(位相差検出値)を出力する。

【0017】

図3は、図2に示すデジタル位相比較器10の動作の一例を示す図である。カウンタ23により、マスタクロックREF_CLKのパルス27の立ち上がりエッジから、それに後続するスレーブクロックFB_CLKのパルス28の立ち上がりエッジまでの期間、位相カウントクロックDPD_CLKのパルス数を計数する。そのようにして計数されるパルス数が図3にCountとして示される。この計数値Countは、パルス27の立ち上がりエッジからパルス28の立ち上がりエッジ迄の期間長Tに相当する。この計数結果に基づいて、デジタル位相比較器10は、位相差検出値としてCount−π_Countを出力する。ここでπ_Countは、収束位相の位相カウント値である。例えば、0から2πの範囲の中心位置(位相πの位置)、即ちマスタクロックREF_CLKの隣接する2つのパルスのちょうど中間の位置に、スレーブクロックFB_CLKのパルスを収束させたい場合、π_Countは位相πに相当するカウント値となる。この場合、デジタルPLL回路による引き込み動作が完了して安定状態となると、位相差検出値Count−π_Countはゼロ近傍の値となる。

【0018】

図4は、位相検出結果補正部11の構成の一例を示す図である。図4に示す位相検出結果補正部11は、閾値比較部31、カウント値レジスタ32、加算器33、及び積算器34を含む。閾値比較部31は、デジタル位相比較器10からの位相差検出値と閾値とを比較する。この位相差検出値と閾値とを比較した結果は、第1の状態、第2の状態、又は第3の状態をとる。閾値としては、0〜2πの範囲内で、この範囲の中心より位相が小さい側に位置する第1の閾値と、範囲の中心より位相が大きい側に位置する第2の閾値とを含む。第1の状態は、位相差検出値が第1の閾値よりも小さくなった状態、即ち0〜2πの範囲内で0側の端に近づいた状態である。第2の状態は、位相差検出値が第2の閾値よりも大きくなった状態、即ち0〜2πの範囲内で2π側の端に近づいた状態である。第3の状態は、位相差検出値が第1の閾値以上で且つ第2の閾値以下の状態、即ち0〜2πの範囲内で両端に近くない位置に位相差検出値が存在する状態である。

【0019】

カウント値レジスタ32は、カウント値を格納するとともに、閾値比較部31からの指示に応じてカウント値を1増減する機能を有する。閾値比較部31が上記第1の状態を検出すると、図4の「位相戻し+」がアサートされ、カウント値レジスタ32のカウント値が1減少する。閾値比較部31が上記第2の状態を検出すると、図4の「位相戻し−」がアサートされ、カウント値レジスタ32のカウント値が1増加する。閾値比較部31が上記第3の状態を検出すると、「位相戻し+」及び「位相戻し−」のいずれもアサートされず、カウント値レジスタ32のカウント値はそのまま同一の値に保持される。積算器34は、カウント値レジスタ32のカウント値に所定の位相量(位相戻し量)を積算した値を求める。こうして求めた値を、加算器33が、位相検出結果補正部11からの位相検出値に加算することにより補正後の位相値を求める。

【0020】

図5は、位相検出結果補正部11の動作シーケンスを示す図である。ステップS1で、位相検出結果補正部11から位相検出結果(位相差検出値)を取得する。ステップS2で、位相検出結果が上限閾値(上記第2の閾値)より大きいか否かを判定する。上限閾値より大きい場合には、ステップS3で、位相戻し(−方向)のトリガを発生する(図1及び図4に示す「位相戻し−」をアサートする)。更に、ステップS4で、カウント値レジスタ32のカウント値COUNTを+1する。

【0021】

更に、ステップS5で、位相検出結果が下限閾値(上記第1の閾値)より小さいか否かを判定する。下限閾値より小さい場合には、ステップS6で、位相戻し(+方向)のトリガを発生する(図1及び図4に示す「位相戻し+」をアサートする)。更に、ステップS7で、カウント値レジスタ32のカウント値COUNTを−1する。

【0022】

最後にステップS8で、位相戻し量をCOUNT倍した値を位相検出結果補正部11からの位相検出結果に加算する。この結果得られた補正後の位相値が、スレーブクロック生成部によるループフィルタ処理に供給される。

【0023】

位相検出結果補正部11は、位相差検出値が第1の閾値よりも小さくなると、「位相戻し+」をアサートすることにより、スレーブクロック生成部の位相制御機能付き分周器15に指示してスレーブクロックの位相を変化させ、位相差検出値を大きくする。位相検出結果補正部11は、位相差検出値が第2の閾値よりも大きくなると、「位相戻し−」をアサートすることにより、スレーブクロック生成部の位相制御機能付き分周器15に指示してスレーブクロックの位相を変化させ、位相差検出値を小さくする。

【0024】

図6は、位相制御機能付き分周器15の構成の一例を示す図である。図6に示す位相制御機能付き分周器15は、制御ロジック41、カウンタ42、一致検出器43、及びフリップフロップ44を含む。カウンタ42は、電圧制御発振器14が発振する被分周クロック信号の各パルスに同期してカウントアップする。一致検出器43は、カウンタ42の出力するカウント値と分周設定値とが一致すると、その出力をアサートする。カウンタ42は、一致検出器43の出力のアサートに応答して、次の被分周クロック信号のパルスのタイミングでゼロにリセットされる。例えば分周設定値が3である場合、カウント値が3になると、カウンタ42は次のタイミングでリセットされてカウント値が0に戻る。フリップフロップ44は、被分周クロック信号を同期信号として、一致検出器43の出力をラッチする。従って、カウント値と分周設定値とが一致して一致検出器43の出力が1にアサートされると、次の被分周クロック信号のパルスに同期してフリップフロップ44が1にセットされる。この結果、被分周クロックの1サイクルの間、分周クロック出力としてHIGHパルスが出力される。例えば分周設定値が3である場合、被分周クロックの4サイクルに一度、分周クロックのパルスが出力されることになり、周波数を1/4にする分周動作が実現される。

【0025】

制御ロジック41は、位相検出結果補正部11からの「位相戻し+」がアサートされると、次のマスタクロックREF_CLKの立ち上がりエッジで、リロード信号1をアサートする。このリロード信号1のアサートに応答して、カウンタ42はリロード値1をリロードして、カウント値がリロード値1に設定される。制御ロジック41は、位相検出結果補正部11からの「位相戻し−」がアサートされると、次のマスタクロックREF_CLKの立ち上がりエッジで、リロード信号2をアサートする。このリロード信号2のアサートに応答して、カウンタ42はリロード値2をリロードして、カウント値がリロード値2に設定される。

【0026】

図7は、位相制御機能付き分周器15の動作の一例を模式的に示す図である。VCO出力(被分周クロック信号)の各パルスに同期して、カウンタ42のカウント値が0から3まで増加し、リセットされて0に戻る動作を繰り返す。従って、分周後クロックは1/4の周波数に分周した信号となる。ここでRとして示すタイミングで、カウンタ42にカウント値“2”がリロードされ、その後は2からのカウントアップを続行する。従って、リロードを実行しなければパルス46が分周後クロックとして出力されたところ、リロードを実行した結果、パルス47が分周後クロックとして出力され、位相が所定の位相量戻る(シフトする)ことになる。

【0027】

図8は、位相戻し動作の一例を模式的に示す図である。図8では、ゼロ位相をマスタクロックREF_CLKのパルス間の中間点に設定し、−π〜+πの位相範囲でスレーブクロックFB_CLKのパルスが移動していく様子を示している。タイミングt0において、位相制御機能付き分周器15により、スレーブクロックFB_CLKのパルス51が図示の位相位置に出力される。次のサイクルのタイミングt1において、スレーブクロックFB_CLKのパルス52が図示の位相位置に出力される。パルス51からパルス52でパルス位置が右に移動するのは、マスタクロックREF_CLKの周波数に対してスレーブクロックFB_CLKの周波数が低いためである。同様にして、t1の次のサイクルのタイミングt2において、スレーブクロックFB_CLKのパルス53が図示の位相位置に出力され、更にt2の次のサイクルのタイミングt3において、スレーブクロックFB_CLKのパルス54が図示の位相位置に出力される。このとき、パルス54に対して検出された位相差検出値が第2の閾値よりも大きくなる、即ちパルス54の位相位置が第2の閾値の位置よりも右側となるので、位相検出結果補正部11から位相制御機能付き分周器15に対して「位相戻し−」をアサートする。

【0028】

「位相戻し−」のアサート(位相検出結果補正部11からの負の位相方向への位相戻し指示)に応答して、位相制御機能付き分周器15は、内部状態(カウント値)を再設定(リロード)することにより、パルス54の位置がパルス54’の位置まで戻される。なおこのパルス54’は実際に出力されるスレーブクロックFB_CLKのパルスではなく、カウンタのリロードにより、前回のパルス54の位置(カウント値が0に相当する位置)が−π〜+πの位相範囲の何処に存在することになるかを示したものである。その後、t3の次のサイクルのタイミングt4において、スレーブクロックFB_CLKのパルス55が図示の位相位置に出力される。リロードを実行しなければパルス56がスレーブクロックFB_CLKとして出力されたところ、リロードを実行した結果、パルス55がスレーブクロックFB_CLKとして出力され、位相が所定の位相量戻る(シフトする)ことになる。

【0029】

図8の下半分には、横軸に位相、縦軸に−π〜+πの範囲制限により折り返される位相値を示すグラフにおいて、上記説明したt1〜t4の各タイミングでのスレーブクロックFB_CLKのパルスの位相位置(即ち位相差検出値)を示している。各タイミングt1,t2,t3,t4で検出される位相差検出値は、図中の黒丸で示す位相位置のものとなる。タイミングt3’に示す位相位置は、実際に出力されるスレーブクロックのパルスの位相位置を示すものではなく、カウンタのリロードにより、タイミングt3のパルスの位置が−π〜+πの位相範囲の何処に存在することになるかを示したものである。タイミングt4での位相差検出値は、リロードを実行しなければ位相位置58となるところ、リロードを実行した結果、位相位置57となり、位相が所定の位相量戻る(シフトする)ことになる。ここでリロードにより戻る位相量をPdOffsetとして示し、タイミングt4での位相差検出値をPdOut_t4として示してある。位相戻り量PdOffsetは、スレーブクロックの周波数がマスタクロックの周波数と略等しい場合には、リロード値に応じた略固定の既知の値であると考えてよい。なお、第1の閾値と第2の閾値とは、不要な位相戻しが実行されないように、−π〜+πの位相範囲の端に十分に近い位置に設定されることが望ましい。但し、閾値と端との間の区間が狭すぎて、パルスが一度もその区間内で検出されることなく飛び越してしまうことがないように、第1の閾値と第2の閾値とを適切な値に設定することが好ましい。

【0030】

図9は、位相検出結果補正部11による補正計算を模式的に示す図である。図9において、横軸は位相を示し、縦軸は0〜2πの範囲制限により折り返される位相値を示す。図8で説明したタイミングt4での位相差検出値PdOut_t4は、位相位置57にある。この位相位置57の位相差検出値(位相検出結果補正部11の出力値)に、位相戻り量PdOffsetを加算することにより、位相位置59にある補正後の位相値が計算される。この補正後の位相値に基づいて、スレーブクロック生成部がスレーブクロックを生成する。従って、デジタルPLL回路は、0〜2πの範囲制限による折り返しによる影響を受けることなく、高速な引き込み動作を実行できる。

【0031】

図10は、位相戻し動作の別の一例を模式的に示す図である。図10には、ゼロ位相をマスタクロックREF_CLKのパルス間の中間点に設定し、−π〜+πの位相範囲でスレーブクロックFB_CLKのパルスが移動していく様子を示している。各タイミングでのパルス波形の右側には、図4に示す位相検出結果補正部11のカウント値レジスタ32に格納されるカウント値(図5に示すCOUNT)の値を示す。上側から下側に向かい時間が進行するにつれて、スレーブクロックFB_CLKのパルスは、その位相が増大する方向に最初は移動している。スレーブクロックFB_CLKのパルス61が第2の閾値よりも右側に位置するようになると、位相戻し動作が実行され、パルス位置が−π〜+πの位相範囲の中心あたりに戻される。この負の方向への位相戻し動作に伴い、カウント値が0から1に増加する。なおこの例では、パルス位置を−π〜+πの位相範囲の中心あたりに戻す構成となっているが、パルスを戻す位置は特定の位置に限定されるものではない。パルス61が第2の閾値よりも右側に位置するということは、スレーブクロックFB_CLKの現在の状態が位相値の増大する方向に設定されていることを意味するので、例えば−πに近い位置までパルスを戻すような構成としてもよい。

【0032】

その後、時間が進行するにつれて、スレーブクロックFB_CLKの状態が変化し、位相が減少する方向にパルス位置が移動し始める。スレーブクロックFB_CLKのパルス62が第1の閾値よりも右側に位置するようになると、位相戻し動作が実行され、パルス位置が−π〜+πの位相範囲の中心あたりに戻される。この正の方向への位相戻し動作に伴い、カウント値が1から0に減少する。なおこの例では、パルス位置を−π〜+πの位相範囲の中心あたりに戻す構成となっているが、パルスを戻す位置は特定の位置に限定されるものではない。パルス61が第1の閾値よりも左側に位置するということは、スレーブクロックFB_CLKの現在の状態が位相値の減少する方向に設定されていることを意味するので、例えば+πに近い位置までパルスを戻すような構成としてもよい。

【0033】

図11は、図1に示すデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。図11(a)において、横軸は時間を示し、縦軸はマスタクロックとスレーブクロックとの位相差を示す。図11(b)において、横軸は時間を示し、縦軸は周波数偏差を示す。図11(b)に示すシミュレーション入力73は、マスタクロックとスレーブクロックとに周波数差が無い状態から、マスタクロックの周波数がステップ関数的に6ppmだけ変動したことを示す。このマスタクロックの周波数変動に応答して、図11(a)に示す位相差変化71が発生する。位相差変化71が示すように、最初に位相差が2πを超えてしまっても、その後は安定した状態で徐々に位相差が減少していき最終的に0に収束している。即ち、位相差が2πを超えてもサイクルスリップが発生することなく、安定的に位相差が収束している。これに伴い図11(b)において、スレーブクロックの周波数変化72が示すように、スレーブクロックの周波数がマスタクロックの周波数に安定的に追従している。

【0034】

図12は、比較のために従来のデジタルPLL回路の引き込み動作のシミュレーション結果を示す図である。図12(a)において、横軸は時間を示し、縦軸はマスタクロックとスレーブクロックとの位相差を示す。図12(b)において、横軸は時間を示し、縦軸は周波数偏差を示す。シミュレーション入力は、図11(b)に示すものと同一であり、マスタクロックとスレーブクロックとに周波数差が無い状態から、マスタクロックの周波数がステップ関数的に6ppmだけ変動するものである。このマスタクロックの周波数変動に応答して、図12(a)に示す位相差変化74が発生する。位相差変化74が示すように、位相差が2πを超えるためにサイクルスリップが発生して長い期間振動した後に、徐々に位相差が減少して最終的に0に収束している。位相差変化71は図11(a)に示すものと同一の波形であり、比較のために位相差変化74と重ねて示してある。また図12(b)において、スレーブクロックの周波数変化75が示すように、サイクルスリップが発生して長い期間振動した後に、マスタクロックに追従している。周波数変化72は図11(b)に示すものと同一の波形であり、比較のために周波数変化75と重ねて示してある。このように、図1に示すデジタルPLL回路では、位相差検出値を補正して値の範囲が制限されない位相値を算出し、この補正後の位相値に基づいてスレーブクロックを生成することにより、安定した引き込み動作を実現できる。即ち、0〜2πの範囲制限により位相値が折り返されることにより発生する振動を抑制し、安定した引き込み動作を実現することができる。

【0035】

図13は、第2の実施形態によるデジタルPLL回路の構成の一例を示す図である。図13において、図1と同一の構成要素は同一又は対応する番号で参照し、その説明は適宜省略する。図13に示すデジタルPLL回路は、デジタル位相比較器(DPD)10、位相検出結果補正部81、デジタルループフィルタ(DLF)12、DA変換器(D/A)13、電圧制御発振器(VCO)14、及び分周器85を含む。デジタルPLL回路は更に、位相カウントクロック生成器として、アナログPLL(APLL)16及び高精度発振器17を含む。図13においては、位相検出結果補正部81及び分周器85が、図1の位相検出結果補正部11及び位相制御機能付き分周器15の代りに設けられている。

【0036】

図1の場合と同様に、デジタル位相比較器10が出力する位相差検出値は、例えば0〜2πの範囲内の位相差を示すデジタル値であってよい。範囲の下限と上限は、任意であってよく、0〜2πの範囲の代りに例えば−π〜+πの範囲であると考えてもよい。

【0037】

位相検出結果補正部81は、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を上記の範囲に限定されない位相値に補正する。デジタルループフィルタ12、DA変換器13、電圧制御発振器14、及び分周器85は、スレーブクロックを生成するスレーブクロック生成部として機能する。このスレーブクロック生成部は、位相検出結果補正部81の出力する補正後の位相値に応じて、スレーブクロックを生成する。具体的には、補正後の位相値がデジタルループフィルタ12により時間平均化され、平均化後のカウント値がDA変換器13によりアナログ電圧に変換される。電圧制御発振器14が、このアナログ電圧に応じた周波数のクロック信号を発振する。この発振クロック信号が分周器85により所定の分周比で分周され、得られた分周クロック信号が、デジタル位相比較器10にスレーブクロックとして印加される。このフィードバック制御により、マスタクロックとスレーブクロックとの周波数が等しく且つ位相が所定の位相関係となるように、電圧制御発振器14の発振クロック信号が制御される。

【0038】

図14は、位相検出結果補正部81の構成の一例を示す図である。位相検出結果補正部81は、レジスタ91及び92、比較器93乃至96、AND回路97及び98、セレクタ99、レジスタ100、加算器101、積算器102、及び加算器103を含む。比較器93乃至96は、位相差検出値と閾値とを比較する。位相差検出値と閾値とを比較した結果は第1の状態、第2の状態、又は第3の状態をとる。位相検出結果補正部81は、第1の状態を検出すると、レジスタ100に格納されるカウント値を1減らし、第2の状態を検出するとカウント値を1増やし、第3の状態を検出するとカウント値をそのまま保持する。位相検出結果補正部81の積算器102は、カウント値に所定の位相量(πカウント値)を積算した値を求める。位相検出結果補正部81の加算器103は、デジタル位相比較器10からの位相検出値に、積算器102が求めた値を加算することにより、補正後の位相値を求める。

【0039】

比較器93乃至96に比較対象として印加される閾値は、0〜2πの範囲内で、範囲の中心より位相が小さい側に位置する第1の閾値(下限閾値)と、範囲の中心より位相が大きい側に位置する第2の閾値(上限閾値)とを含む。上記第1の状態は、位相差検出値が第1の閾値よりも小さくなった直後に、第2の閾値よりも大きくなったことが検出された状態である。上記第2の状態は、位相差検出値が第2の閾値よりも大きくなった直後に、第1の閾値よりも小さくなったことが検出された状態である。具体的には、比較器93は、レジスタ91に格納されるある検出タイミングでの位相差検出値と第2の閾値とを比較し、位相差検出値が第2の閾値よりも大きくなると出力をアサートする。比較器94は、次の検出タイミングでの位相差検出値と第1の閾値とを比較し、位相差検出値が第1の閾値よりも小さくなると出力をアサートする。AND回路97は、ある検出タイミングで検出された位相差検出値が第2の閾値よりも大きくなり且つ次の検出タイミングで検出された位相差検出値が第1の閾値よりも小さくなると、出力をアサートする(第2の状態を検出する)。同様に、比較器96は、レジスタ92に格納されるある検出タイミングでの位相差検出値と第1の閾値とを比較し、位相差検出値が第1の閾値よりも小さくなると出力をアサートする。比較器95は、次の検出タイミングでの位相差検出値と第2の閾値とを比較し、位相差検出値が第2の閾値よりも大きくなると出力をアサートする。AND回路98は、ある検出タイミングで検出された位相差検出値が第1の閾値よりも小さくなり且つ次の検出タイミングで検出された位相差検出値が第2の閾値よりも大きくなると、出力をアサートする(第1の状態を検出する)。

【0040】

セレクタ99は、AND回路97の出力のアサート状態(第2の状態)に応答して、+1を選択して出力する。更にセレクタ99は、AND回路98の出力のアサート状態(第1の状態)に応答して、−1を選択して出力する。第1の状態も第2の状態も検出されない場合(第3の状態の場合)に、セレクタ99は、0を選択して出力する。セレクタ99の出力は、加算器101によりレジスタ100の格納値(カウント値)に加算される。加算結果は、レジスタ100に更新後のカウント値として格納される。積算器102は、レジスタ100のカウント値と所定の位相量(位相量πに相当するカウント値)とを積算して、積算結果を加算器103に供給する。加算器103は、デジタル位相比較器10からの位相差検出値と積算結果とを加算することにより、補正後の位相値を求める。

【0041】

図1に示す第1の実施形態のデジタルPLL回路では、位相差検出値が位相範囲の端に近づくと、位相差検出値を端から遠ざけるように位相戻し動作が実行される。またこの位相戻し動作に伴い、所定の位相量を位相差検出値に加算することで、補正後の位相値を求めている。それに対し図13に示す第2の実施形態のデジタルPLL回路では、位相差検出値が位相範囲の端を通過したこと、即ち位相差検出値が位相範囲の端を超えたことを検出すると、所定の位相量を位相差検出値に加算することで、補正後の位相値を求めている。位相差検出値が位相範囲の端を通過すると、位相値の折り返しにより逆側の端に位相差検出値が遷移することになるので、所定の位相量を位相差検出値に加算することにより、適切な補正結果を得ることができる。

【0042】

図15は、図1又は図13に示すデジタルPLL回路を適用したシステムの構成の一例を示す図である。図15に示すシステムは、A/Dコンバータ111及びデジタルPLL回路112を含む。A/Dコンバータ111は、アナログ映像信号を受け取り、アナログ映像信号をデジタル映像信号に変換する。この信号変換の際に、A/Dコンバータ111は、アナログ映像信号のアナログ電圧を所定のサンプリングクロックに同期してサンプリングしてホールドし、ホールドされたアナログ電圧を並列或いは逐次処理によりデジタル値に変換する。デジタルPLL回路112は、複合同期信号等を基準クロック(マスタクロック)として、基準クロックに同期したサンプリングクロックを生成する。デジタルPLL回路112は、図1又は図13に示すデジタルPLL回路であり、位相差検出値の範囲制限に影響を受けることなく、高速に引き込み動作を実行することができる。

【0043】

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

【符号の説明】

【0044】

10 デジタル位相比較器(DPD)

11 位相検出結果補正部

12 デジタルループフィルタ(DLF)

13 DA変換器(D/A)

14 電圧制御発振器(VCO)

15 位相制御機能付き分周器

16 アナログPLL(APLL)

17 高精度発振器

81 位相検出結果補正部

85 分周器

【特許請求の範囲】

【請求項1】

マスタクロックとスレーブクロックとの位相差を検出し、所定の範囲内の位相差検出値を出力するデジタル位相比較器と、

前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正する補正部と、

前記補正部の出力する前記位相値に応じて前記スレーブクロックを生成するスレーブクロック生成部と

を含むことを特徴とするデジタルPLL回路。

【請求項2】

前記位相差検出値と閾値とを比較した結果は第1の状態、第2の状態、又は第3の状態をとり、前記補正部は、前記第1の状態を検出するとカウント値を1減らし、前記第2の状態を検出すると前記カウント値を1増やし、前記第3の状態を検出すると前記カウント値をそのまま保持し、前記カウント値に所定の位相量を積算した値を前記位相検出値に加算することにより前記位相値を求めることを特徴とする請求項1記載のデジタルPLL回路。

【請求項3】

前記閾値は、前記範囲内で、前記範囲の中心より位相が小さい側に位置する第1の閾値と前記範囲の中心より位相が大きい側に位置する第2の閾値とを含み、前記第1の状態は、前記位相差検出値が前記第1の閾値よりも小さくなった時又は直後に発生する状態であり、前記第2の状態は、前記位相差検出値が前記第2の閾値よりも大きくなった時又は直後に発生する状態であることを特徴とする請求項2記載のデジタルPLL回路。

【請求項4】

前記補正部は、前記位相差検出値が前記第1の閾値よりも小さくなると前記第1の状態を検出するとともに、前記スレーブクロック生成部に指示して前記スレーブクロックの位相を変化させることにより前記位相差検出値を大きくし、前記位相差検出値が前記第2の閾値よりも大きくなると前記第2の状態を検出するとともに、前記スレーブクロック生成部に指示して前記スレーブクロックの位相を変化させることにより前記位相差検出値を小さくすることを特徴とする請求項3記載のデジタルPLL回路。

【請求項5】

前記スレーブクロック生成部は、

前記位相値に応じた周波数のクロックを発振する電圧制御発振器と、

前記電圧制御発振器が発振する前記クロックを分周する分周器と

を含み、前記補正部からの前記指示に応答して前記分周器は内部状態を再設定することを特徴とする請求項4記載のデジタルPLL回路。

【請求項6】

前記補正部は、ある検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなると前記第1の状態を検出し、ある検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなると前記第2の状態を検出することを特徴とする請求項3記載のデジタルPLL回路。

【請求項7】

マスタクロックとスレーブクロックとの位相差を検出することにより、所定の範囲内の位相差検出値を求め、

前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正し、

前記位相値に応じて前記スレーブクロックを生成する

各段階を含むことを特徴とするデジタルPLL回路におけるクロック生成方法。

【請求項8】

前記補正する段階は、

前記位相差検出値と閾値とを比較した結果が第1の状態、第2の状態、又は第3の状態をとり、前記第1の状態が発生するとカウント値を1減らし、前記第2の状態が発生すると前記カウント値を1増やし、前記第3の状態が発生すると前記カウント値をそのまま保持し、

前記カウント値に所定の位相量を積算した値を前記位相検出値に加算することにより前記位相値を求める

各段階を含むことを特徴とする請求項7記載のクロック生成方法。

【請求項9】

前記閾値は、前記範囲内で、前記範囲の中心より位相が小さい側に位置する第1の閾値と前記範囲の中心より位相が大きい側に位置する第2の閾値とを含み、前記第1の状態は、前記位相差検出値が前記第1の閾値よりも小さくなった時又は直後に発生する状態であり、前記第2の状態は、前記位相差検出値が前記第2の閾値よりも大きくなった時又は直後に発生する状態であることを特徴とする請求項8記載のクロック生成方法。

【請求項10】

前記位相差検出値が前記第1の閾値よりも小さくなると前記第1の状態を検出するとともに、前記スレーブクロックの位相を変化させることにより前記位相差検出値を大きくし、

前記位相差検出値が前記第2の閾値よりも大きくなると前記第2の状態を検出するとともに、前記スレーブクロックの位相を変化させることにより前記位相差検出値を小さくする

各段階を更に含むことを特徴とする請求項9記載のクロック生成方法。

【請求項11】

ある検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなると前記第1の状態を検出し、

ある検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなると前記第2の状態を検出する

各段階を更に含むことを特徴とする請求項9記載のクロック生成方法。

【請求項1】

マスタクロックとスレーブクロックとの位相差を検出し、所定の範囲内の位相差検出値を出力するデジタル位相比較器と、

前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正する補正部と、

前記補正部の出力する前記位相値に応じて前記スレーブクロックを生成するスレーブクロック生成部と

を含むことを特徴とするデジタルPLL回路。

【請求項2】

前記位相差検出値と閾値とを比較した結果は第1の状態、第2の状態、又は第3の状態をとり、前記補正部は、前記第1の状態を検出するとカウント値を1減らし、前記第2の状態を検出すると前記カウント値を1増やし、前記第3の状態を検出すると前記カウント値をそのまま保持し、前記カウント値に所定の位相量を積算した値を前記位相検出値に加算することにより前記位相値を求めることを特徴とする請求項1記載のデジタルPLL回路。

【請求項3】

前記閾値は、前記範囲内で、前記範囲の中心より位相が小さい側に位置する第1の閾値と前記範囲の中心より位相が大きい側に位置する第2の閾値とを含み、前記第1の状態は、前記位相差検出値が前記第1の閾値よりも小さくなった時又は直後に発生する状態であり、前記第2の状態は、前記位相差検出値が前記第2の閾値よりも大きくなった時又は直後に発生する状態であることを特徴とする請求項2記載のデジタルPLL回路。

【請求項4】

前記補正部は、前記位相差検出値が前記第1の閾値よりも小さくなると前記第1の状態を検出するとともに、前記スレーブクロック生成部に指示して前記スレーブクロックの位相を変化させることにより前記位相差検出値を大きくし、前記位相差検出値が前記第2の閾値よりも大きくなると前記第2の状態を検出するとともに、前記スレーブクロック生成部に指示して前記スレーブクロックの位相を変化させることにより前記位相差検出値を小さくすることを特徴とする請求項3記載のデジタルPLL回路。

【請求項5】

前記スレーブクロック生成部は、

前記位相値に応じた周波数のクロックを発振する電圧制御発振器と、

前記電圧制御発振器が発振する前記クロックを分周する分周器と

を含み、前記補正部からの前記指示に応答して前記分周器は内部状態を再設定することを特徴とする請求項4記載のデジタルPLL回路。

【請求項6】

前記補正部は、ある検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなると前記第1の状態を検出し、ある検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなると前記第2の状態を検出することを特徴とする請求項3記載のデジタルPLL回路。

【請求項7】

マスタクロックとスレーブクロックとの位相差を検出することにより、所定の範囲内の位相差検出値を求め、

前記位相差検出値と閾値とを比較した結果に応じて、前記位相差検出値を前記範囲に限定されない位相値に補正し、

前記位相値に応じて前記スレーブクロックを生成する

各段階を含むことを特徴とするデジタルPLL回路におけるクロック生成方法。

【請求項8】

前記補正する段階は、

前記位相差検出値と閾値とを比較した結果が第1の状態、第2の状態、又は第3の状態をとり、前記第1の状態が発生するとカウント値を1減らし、前記第2の状態が発生すると前記カウント値を1増やし、前記第3の状態が発生すると前記カウント値をそのまま保持し、

前記カウント値に所定の位相量を積算した値を前記位相検出値に加算することにより前記位相値を求める

各段階を含むことを特徴とする請求項7記載のクロック生成方法。

【請求項9】

前記閾値は、前記範囲内で、前記範囲の中心より位相が小さい側に位置する第1の閾値と前記範囲の中心より位相が大きい側に位置する第2の閾値とを含み、前記第1の状態は、前記位相差検出値が前記第1の閾値よりも小さくなった時又は直後に発生する状態であり、前記第2の状態は、前記位相差検出値が前記第2の閾値よりも大きくなった時又は直後に発生する状態であることを特徴とする請求項8記載のクロック生成方法。

【請求項10】

前記位相差検出値が前記第1の閾値よりも小さくなると前記第1の状態を検出するとともに、前記スレーブクロックの位相を変化させることにより前記位相差検出値を大きくし、

前記位相差検出値が前記第2の閾値よりも大きくなると前記第2の状態を検出するとともに、前記スレーブクロックの位相を変化させることにより前記位相差検出値を小さくする

各段階を更に含むことを特徴とする請求項9記載のクロック生成方法。

【請求項11】

ある検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなると前記第1の状態を検出し、

ある検出タイミングで検出された前記位相差検出値が前記第2の閾値よりも大きくなり且つ次の検出タイミングで検出された前記位相差検出値が前記第1の閾値よりも小さくなると前記第2の状態を検出する

各段階を更に含むことを特徴とする請求項9記載のクロック生成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−199815(P2012−199815A)

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願番号】特願2011−63109(P2011−63109)

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成24年10月18日(2012.10.18)

【国際特許分類】

【出願日】平成23年3月22日(2011.3.22)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]