デバッグ回路

【課題】LSI出力PINを増やすことなく解析データをリアルタイムで採取することができるようにする。

【解決手段】デバッグ回路1は、LSI論理回路50の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持回路10と、LSI論理回路50内の論理回路状態信号がモード保持回路10出力の条件と一致したときパタン一致信号とパタン種別信号を送出するパタン検出回路20と、パタン一致信号を受けるとパタン種別信号に毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路50から出力される解析データをつけたユーザ定義メッセージトランザクションを作成するトランザクション生成回路30と、通常トランザクションとユーザ定義メッセージトランザクションとを選択しLSI70からトランザクション出力として出力するトランザクション選択回路40とを含む。

【解決手段】デバッグ回路1は、LSI論理回路50の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持回路10と、LSI論理回路50内の論理回路状態信号がモード保持回路10出力の条件と一致したときパタン一致信号とパタン種別信号を送出するパタン検出回路20と、パタン一致信号を受けるとパタン種別信号に毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路50から出力される解析データをつけたユーザ定義メッセージトランザクションを作成するトランザクション生成回路30と、通常トランザクションとユーザ定義メッセージトランザクションとを選択しLSI70からトランザクション出力として出力するトランザクション選択回路40とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はデバッグ回路に関し、特に、LSIの動作不具合時のデバッグを行うデバッグ回路に関するものである。

【背景技術】

【0002】

従来のデバッグ回路では、LSI(Large Scale Integration)内部論理の解析データを得るために、LSIに解析データ採取用の出力を設けデータを採取していた。

また、他の従来のデバッグ回路では、LSI(Large Scale Integration)の内部の特定タイミングでLSI内部情報データを解析する必要がある場合、通常のLSI出力信号の論理では期待するデータが得られないため、LSI内部の動作不具合の解析を行うために、LSI内部に解析データを保持する保持レジスタまたはラッチを内蔵し、解析データを格納し、解析データをシリアルデータに変換して出力することで、少ない外部ピンでLSI内部の複数の信号を観測可能としていた。例えば、LSI内動作不具合の原因解明に有効と考えられる複数の内部信号を、タイミング生成ブロックから出力された信号でラッチし、シリアルデータに変換して出力ブロックに出力することで、少ない外部ピンでLSI内部の複数の信号を観測可能としていた(例えば特許文献1参照)。

また、内部タイミング信号の選択を行うデータを書き込みできるI/Oレジスタと、I/Oレジスタのデータをデコードして内部タイミング信号を選択する選択信号を生成するデコーダと、論理回路の内部タイミング信号を選択信号に従って選択する選択回路群とを有し、内部タイミング信号をデバッグ用外部出力端子群から直接観測することで、LSIの動作不具合のデバッグを行うようにしたものがあった(例えば、特許文献2参照)。

【特許文献1】特開2005−091310号公報

【特許文献2】特開2000−259441号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、従来のデバッグ回路においては、次のような課題があった。

第1の課題は、シリアルデータでデバッグデータを採取するため、ハードウェア動作中にリアルタイムで解析データを採取できないということである。

第2の課題は、デバッグデータ専用外部端子を設けるため、LSIのPINが増加してしまうことである。

本発明はこのような状況に鑑みてなされたものであり、LSIの内部動作解析のため、LSI内部情報を採取するデバッグ回路において、LSI内部動作解析に必要なタイミングの内部データをハードウェア動作中にリアルタイムかつLSIのPINを増やすことなく採取可能とする機能を提供することを目的とする。

【課題を解決するための手段】

【0004】

請求項1に記載のデバッグ回路は、LSI動作解析データを採取するデバッグ回路であって、ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取手段を備えることを特徴とする。

また、ユーザ定義メッセージトランザクションと通常トランザクションの競合多発のケースでユーザ定義メッセージトランザクションロストを防ぐため、トランザクションバッファを備えるようにすることができる。

請求項3に記載のデバッグ回路は、LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持手段と、前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出手段と、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成手段と、通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択手段とを備えることを特徴とする。

請求項4に記載のデバッグ方法は、LSI動作解析データを採取するデバッグ方法であって、ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップを備えることを特徴とする。

請求項5に記載のデバッグ方法は、LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップとを備えることを特徴とする。

請求項6に記載のデバッグプログラムは、LSI動作解析データを採取するデバッグ回路を制御するデバッグプログラムであって、ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップをコンピュータに実行させることを特徴とする。

請求項7に記載のデバッグプログラムは、LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップとをコンピュータに実行させることを特徴とする。

【発明の効果】

【0005】

本発明のデバッグ回路によれば、以下に記載するような効果を奏する。

第1の効果は、モード保持回路からのデータ採取条件情報を含むモード信号とLSI論理回路の論理回路動作状態信号をパタン検出回路20で比較し、一致したタイミングでユーザ定義メッセージトランザクションに解析データを付加するので、ハードウェア動作中に必要とするタイミングの解析データをリアルタイムで採取できることである。

第2の効果は、解析データが付加されたユーザ定義メッセージトランザクションと通常トランザクションとでLSI出力PINを共用しているのでデバッグ用にLSI出力PINを増やさずに解析データを採取できることである。

【発明を実施するための最良の形態】

【0006】

本発明の概要について説明する。本発明の一実施の形態としてのデバッグ回路1は、ユーザ定義メッセージトランザクションを使用し、解析用デバッグデータをユーザ定義メッセージトランザクション内に付加してLSI70の外へ出力することにより、LSI内部動作解析データをハードウェア動作中にリアルタイムかつLSI70のPINを増やすことなく採取することを特徴としている。

【0007】

本実施の形態で述べるユーザ定義メッセージトランザクションは、通常のトランザクションと異なり、メッセージデータのみ付加されたトランザクションであり、通常動作では使用されない。通常の受信回路論理では、ユーザ定義メッセージトランザクションを受信した場合、使用されず破棄される。

【0008】

デバッグ回路1は、LSI論理回路50の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持手段(図1のモード保持回路10)と、LSI論理回路50内の論理回路状態信号がモード保持回路10出力の条件と一致したときパタン一致信号とパタン種別信号を送出するパタン検出手段(パタン検出回路20)と、パタン一致信号を受けるとパタン種別信号に毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路50から出力される解析データをつけたユーザ定義メッセージトランザクションを作成するトランザクション生成手段(トランザクション生成回路30)と、通常トランザクションとユーザ定義メッセージトランザクションとを選択しLSI70からトランザクション出力として出力するトランザクション選択手段(トランザクション選択回路40)とを含む。

【0009】

図1において、モード保持回路10にLSI論理回路50動作中にデータ採取するタイミングと採取するデータの選択条件が設定される。パタン検出回路20はLSI論理回路50内の論理回路状態信号とモード保持回路10出力を入力し、LSI論理回路50内の論理回路状態信号がモード保持回路10出力の条件と一致したとき、トランザクション生成回路30にパタン一致信号とパタン種別信号を送出する。

【0010】

トランザクション生成回路30は、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路50から出力される解析データをつけたユーザ定義メッセージトランザクションを作成する。

【0011】

ユーザ定義メッセージトランザクションが作成されると、トランザクション選択回路40は、通常トランザクションとユーザ定義メッセージトランザクションから出力トランザクションを選択し、トランザクション出力とする。

【0012】

このようにして本実施の形態では、トランザクション内に解析データを付加したユーザ定義メッセージトランザクションを、LSI70の通常トランザクション出力パスを共用して出力するので、ハードウェアが通常動作中にLSI70内部の解析データをリアルタイムに採取することができる。

【0013】

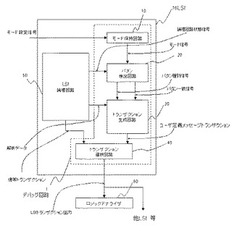

以下、本発明の一実施の形態としてのデバッグ回路1について詳細に説明する。図1を参照すると、デバッグ回路1は、LSI論理回路50およびロジックアナライザ60にそれぞれ接続されており、モード保持回路10、パタン検出回路20、トランザクション生成回路30、トランザクション選択回路40、LSI論理回路50を含んで構成される。

【0014】

モード保持回路10には、モード設定信号が入力されるようになっている。LSI論理回路50は、パタン検出回路20に対して論理回路状態信号を供給し、トランザクション生成回路30に対して解析データを供給し、トランザクション選択回路40に対して通常トランザクションを供給するようになっている。モード保持回路10は、モード信号をパタン検出回路20に供給し、パタン検出回路20は、パタン種別信号およびパタン一致信号をトランザクション生成回路30にそれぞれ供給し、トランザクション生成回路30は、ユーザ定義トランザクションをトランザクション選択回路40に供給するようになっている。トランザクション選択回路40は、LSIトランザクション出力をロジックアナライザ60およびその他のLSI等に供給するようになっている。

【0015】

モード保持回路10はモード設定信号により、LSI論理回路50から出力される解析データを採取するタイミング情報と解析データ採取条件を保持する。パタン検出回路20は、LSI論理回路50から出力される論理回路状態信号とモード保持回路10の出力を入力し、LSI論理回路50からの論理状態信号がモード保持回路10からの条件と一致するか否かをチェックし、一致する場合はパタン種別信号とパタン一致信号をトランザクション生成回路30に送出する。

【0016】

トランザクション生成回路30は、パタン検出回路20から送出されたパタン一致信号を受けたとき、パタン検出回路20から送出されるパタン種別信号に応じてユーザ定義メッセージトランザクションヘッダとパタン種別信号毎に異なる補助コードを作成し、LSI論理回路50から送出される解析データをヘッダの後に付加したユーザ定義メッセージトランザクションを作成する。

【0017】

トランザクション選択回路40は、トランザクション生成回路30から供給されるユーザ定義メッセージトランザクションとLSI論理回路50から供給される通常トランザクションを選択し、LSIトランザクション出力とする。LSIトランザクション出力はロジックアナライザ60に送出される。

【0018】

ロジックアナライザ60では、トランザクションヘッダがユーザ定義メッセージトランザクションである場合、入力データをロジックアナライザ60内のメモリ等に記録する。ロジックアナライザ60に記録されたデータを解析することにより、ハードウェア動作中のLSI内論理回路動作を解析することができる。ここでは、解析データを記録する装置をロジックアナライザ60としたが、この他の記録装置でも良く、特にロジックアナライザ60に限定しない。

【0019】

次に、図1に示したデバッグ回路1の動作について、図2のトランザクション発生タイミング例と、図3のユーザ定義メッセージトランザクションフォーマットを参照して説明する。

【0020】

図2に示したトランザクション発生タイミング例のように、時刻nから時刻(n+7+m)の間で、時刻(n+7)でモード信号保持回路10の条件とLSI論理回路50の論理動作が一致した場合についての動作を図1、図2、図3を参照して説明する。

【0021】

図1において、採取したいデータのタイミングとデータ種別などの情報を含むモード設定信号がモード信号保持回路10に設定される。モード設定信号によりLSI論理回路50からの解析データを採取するタイミング情報と解析データ採取条件が保持される。

【0022】

パタン検出回路20は、LSI論理回路50の論理状態信号とモード保持回路10の出力を入力し、LSI論理回路50からの論理状態信号がモード保持回路10からの条件と一致するか否かを比較して判定し、一致する場合はパタン種別信号とパタン一致信号をトランザクション生成回路30に送出する。

【0023】

図2の例では、時刻nから時刻(n+6)まではモード保持回路10から出力されるモード信号を受けたパタン検出回路20は、LSI論理回路50からの論理回路状態信号とデータ採取タイミング条件とを比較し、論理回路状態信号がデータ採取タイミング条件に一致しないため、パタン一致信号を出力しない。

【0024】

時刻(n+7)でLSI論理回路50から出力される論理回路状態信号とモード信号が一致するため、パタン検出回路20はトランザクション生成回路30に対してパタン一致信号と一致したモード信号をパタン種別信号として送出する。トランザクション生成回路30では、パタン一致信号を受けるとユーザ定義メッセージトランザクションのヘッダを作成する。

【0025】

図3に示したように、ユーザ定義メッセージトランザクションのヘッダ情報には、補助コードフィールドにパタン種別信号が埋め込まれる。これによって、ユーザ定義メッセージトランザクションがどのようなモード設定で発生したかを解析時に判別できる。

【0026】

トランザクション生成回路30では、図3に示したように、解析データとして(m−1)ワードのデータを採取する。解析データのワード数はパタン種別信号により変更可能である。トランザクション生成回路30は、LSI論理回路50から出力される(m−1)ワードの解析データを受け、図3に示したような、mワードのユーザ定義メッセージトランザクションを作成する。

【0027】

ユーザ定義メッセージトランザクションは、時刻(n+7)でトランザクション選択回路40に送出され、時刻(n+7)から時刻(n+7+m)の間、トランザクション選択回路40で選択され、LSIトランザクション出力としてLSI70の外に出力され、ロジックアナライザ60に入力される。

【0028】

時刻(n+7+m)においてパタン検出回路20によってパタン一致が検出されないので、トランザクション選択回路40では、図2の通常トランザクション(n+8)を選択し、LSIトランザクション出力としてLSI70の外に出力する。

【0029】

図2の例では、通常トランザクションとユーザ定義メッセージトランザクションのタイミングは競合しないが、競合するケースが発生した場合、トランザクション選択回路40は通常トランザクションを優先して選択し、性能低下が生じないようにする。

【0030】

このように、通常トランザクションとユーザ定義メッセージトランザクションは競合するケースがあるため、ユーザ定義メッセージトランザクションはLSI70の外に出力されるまで、トランザクション生成回路30で保持される。

【0031】

ロジックアナライザ60では、トランザクションヘッダがユーザ定義メッセージトランザクションである場合、データをロジックアナライザ60のメモリ等に記録する。

【0032】

次に、本発明の他の実施の形態について説明する。図4は、本発明の他の実施の形態の構成例を示しており、その基本的構成は図1に示した実施の形態の場合と同様であるが、図4の実施の形態では、ユーザ定義メッセージトランザクションと通常トランザクションが競合するケースについてさらに工夫している。

【0033】

図4に示した実施の形態において、トランザクションバッファ80は、トランザクション生成回路30で作成したユーザ定義メッセージトランザクションを複数保持する。モード保持回路10は、モード設定信号によりLSI論理回路50からの解析データを採取するタイミング情報と解析データ採取条件を保持する。

【0034】

パタン検出回路20は、LSI論理回路50から出力される論理状態信号とモード保持回路10の出力を入力し、LSI論理回路50からの論理状態信号がモード保持回路10からの条件と一致するか否かをチェックし、一致する場合はパタン種別信号とパタン一致信号をトランザクション生成回路30に送出する。

【0035】

トランザクション生成回路30はパタン検出回路20からパタン一致信号を受けたとき、パタン検出回路20から送出されるパタン種別信号に応じてユーザ定義メッセージトランザクションヘッダとパタン種別信号毎に存在する補助コードを作成し、LSI論理回路50から送出される解析データをヘッダの後に付加したユーザ定義メッセージトランザクションを作成する。

【0036】

トランザクションバッファ80は、トランザクション生成回路30で作成されたユーザ定義メッセージトランザクションを保持する。トランザクション選択回路40は、トランザクションバッファ80から供給されるユーザ定義メッセージトランザクションとLSI論理回路50から出力される通常トランザクションを選択し、LSIトランザクション出力とする。

【0037】

LSIトランザクション出力は、ロジックアナライザ60に送出される。ロジックアナライザ60では、トランザクションヘッダがユーザ定義メッセージトランザクションである場合、データをロジックアナライザ60内のメモリ等に記録する。ロジックアナライザ60に記録されたデータを解析することにより、ハードウェア動作中のLSI内論理回路動作を解析することができる。

【0038】

ここでは、解析データを記録する装置をロジックアナライザ60としたが、この他の記録装置でも良く、特にロジックアナライザ60に限定しない。

【0039】

このように、図4に示した実施の形態では、ユーザ定義メッセージトランザクションをトランザクションバッファ80で複数保持することができるので、ユーザ定義メッセージトランザクションが複数生成されたとき、通常トランザクションとトランザクション選択回路40での競合が多発したときにユーザ定義メッセージトランザクションをロストすることなくLSI70より出力できるという効果が得られる。

【0040】

以上説明したように、本実施の形態においては、以下に記載するような効果を奏する。

第1の効果は、モード保持回路10からのデータ採取条件情報を含むモード信号とLSI論理回路50の論理回路状態信号をパタン検出回路20で比較し、一致したタイミングでユーザ定義メッセージトランザクションに解析データを付加するので、ハードウェア動作中に必要とするタイミングの解析データをリアルタイムで採取できることである。

第2の効果は、解析データが付加されたユーザ定義メッセージトランザクションと通常トランザクションとでLSI出力PINを共用しているので、デバッグ用にLSI出力PINを増やさずに解析データを採取できることである。

【0041】

なお、上記実施の形態の構成及び動作は例であって、本発明の趣旨を逸脱しない範囲で適宜変更することができることは言うまでもない。

【産業上の利用可能性】

【0042】

本発明はLSIの内部動作解析のため、LSI内部情報を採取するデバッグ回路に適用できる。特に解析に必要なタイミングの内部データをハードウェア動作中にリアルタイムかつLSIのPINを増やすことなく採取する必要がある場合に効果的に適用できる。

【図面の簡単な説明】

【0043】

【図1】本発明のデバッグ回路の一実施の形態の構成例を示すブロック図である。

【図2】トランザクション発生タイミング例を示す図である。

【図3】ユーザ定義メッセージトランザクションフォーマット例を示す図である。

【図4】本発明のデバッグ回路の他の実施の形態の構成例を示すブロック図である。

【符号の説明】

【0044】

1 デバッグ回路

10 モード保持回路

20 パタン検出回路

30 トランザクション生成回路

40 トランザクション選択回路

50 LSI論理回路

60 ロジックアナライザ

70 LSI

80 トランザクションバッファ

【技術分野】

【0001】

本発明はデバッグ回路に関し、特に、LSIの動作不具合時のデバッグを行うデバッグ回路に関するものである。

【背景技術】

【0002】

従来のデバッグ回路では、LSI(Large Scale Integration)内部論理の解析データを得るために、LSIに解析データ採取用の出力を設けデータを採取していた。

また、他の従来のデバッグ回路では、LSI(Large Scale Integration)の内部の特定タイミングでLSI内部情報データを解析する必要がある場合、通常のLSI出力信号の論理では期待するデータが得られないため、LSI内部の動作不具合の解析を行うために、LSI内部に解析データを保持する保持レジスタまたはラッチを内蔵し、解析データを格納し、解析データをシリアルデータに変換して出力することで、少ない外部ピンでLSI内部の複数の信号を観測可能としていた。例えば、LSI内動作不具合の原因解明に有効と考えられる複数の内部信号を、タイミング生成ブロックから出力された信号でラッチし、シリアルデータに変換して出力ブロックに出力することで、少ない外部ピンでLSI内部の複数の信号を観測可能としていた(例えば特許文献1参照)。

また、内部タイミング信号の選択を行うデータを書き込みできるI/Oレジスタと、I/Oレジスタのデータをデコードして内部タイミング信号を選択する選択信号を生成するデコーダと、論理回路の内部タイミング信号を選択信号に従って選択する選択回路群とを有し、内部タイミング信号をデバッグ用外部出力端子群から直接観測することで、LSIの動作不具合のデバッグを行うようにしたものがあった(例えば、特許文献2参照)。

【特許文献1】特開2005−091310号公報

【特許文献2】特開2000−259441号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、従来のデバッグ回路においては、次のような課題があった。

第1の課題は、シリアルデータでデバッグデータを採取するため、ハードウェア動作中にリアルタイムで解析データを採取できないということである。

第2の課題は、デバッグデータ専用外部端子を設けるため、LSIのPINが増加してしまうことである。

本発明はこのような状況に鑑みてなされたものであり、LSIの内部動作解析のため、LSI内部情報を採取するデバッグ回路において、LSI内部動作解析に必要なタイミングの内部データをハードウェア動作中にリアルタイムかつLSIのPINを増やすことなく採取可能とする機能を提供することを目的とする。

【課題を解決するための手段】

【0004】

請求項1に記載のデバッグ回路は、LSI動作解析データを採取するデバッグ回路であって、ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取手段を備えることを特徴とする。

また、ユーザ定義メッセージトランザクションと通常トランザクションの競合多発のケースでユーザ定義メッセージトランザクションロストを防ぐため、トランザクションバッファを備えるようにすることができる。

請求項3に記載のデバッグ回路は、LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持手段と、前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出手段と、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成手段と、通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択手段とを備えることを特徴とする。

請求項4に記載のデバッグ方法は、LSI動作解析データを採取するデバッグ方法であって、ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップを備えることを特徴とする。

請求項5に記載のデバッグ方法は、LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップとを備えることを特徴とする。

請求項6に記載のデバッグプログラムは、LSI動作解析データを採取するデバッグ回路を制御するデバッグプログラムであって、ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップをコンピュータに実行させることを特徴とする。

請求項7に記載のデバッグプログラムは、LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップとをコンピュータに実行させることを特徴とする。

【発明の効果】

【0005】

本発明のデバッグ回路によれば、以下に記載するような効果を奏する。

第1の効果は、モード保持回路からのデータ採取条件情報を含むモード信号とLSI論理回路の論理回路動作状態信号をパタン検出回路20で比較し、一致したタイミングでユーザ定義メッセージトランザクションに解析データを付加するので、ハードウェア動作中に必要とするタイミングの解析データをリアルタイムで採取できることである。

第2の効果は、解析データが付加されたユーザ定義メッセージトランザクションと通常トランザクションとでLSI出力PINを共用しているのでデバッグ用にLSI出力PINを増やさずに解析データを採取できることである。

【発明を実施するための最良の形態】

【0006】

本発明の概要について説明する。本発明の一実施の形態としてのデバッグ回路1は、ユーザ定義メッセージトランザクションを使用し、解析用デバッグデータをユーザ定義メッセージトランザクション内に付加してLSI70の外へ出力することにより、LSI内部動作解析データをハードウェア動作中にリアルタイムかつLSI70のPINを増やすことなく採取することを特徴としている。

【0007】

本実施の形態で述べるユーザ定義メッセージトランザクションは、通常のトランザクションと異なり、メッセージデータのみ付加されたトランザクションであり、通常動作では使用されない。通常の受信回路論理では、ユーザ定義メッセージトランザクションを受信した場合、使用されず破棄される。

【0008】

デバッグ回路1は、LSI論理回路50の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持手段(図1のモード保持回路10)と、LSI論理回路50内の論理回路状態信号がモード保持回路10出力の条件と一致したときパタン一致信号とパタン種別信号を送出するパタン検出手段(パタン検出回路20)と、パタン一致信号を受けるとパタン種別信号に毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路50から出力される解析データをつけたユーザ定義メッセージトランザクションを作成するトランザクション生成手段(トランザクション生成回路30)と、通常トランザクションとユーザ定義メッセージトランザクションとを選択しLSI70からトランザクション出力として出力するトランザクション選択手段(トランザクション選択回路40)とを含む。

【0009】

図1において、モード保持回路10にLSI論理回路50動作中にデータ採取するタイミングと採取するデータの選択条件が設定される。パタン検出回路20はLSI論理回路50内の論理回路状態信号とモード保持回路10出力を入力し、LSI論理回路50内の論理回路状態信号がモード保持回路10出力の条件と一致したとき、トランザクション生成回路30にパタン一致信号とパタン種別信号を送出する。

【0010】

トランザクション生成回路30は、パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路50から出力される解析データをつけたユーザ定義メッセージトランザクションを作成する。

【0011】

ユーザ定義メッセージトランザクションが作成されると、トランザクション選択回路40は、通常トランザクションとユーザ定義メッセージトランザクションから出力トランザクションを選択し、トランザクション出力とする。

【0012】

このようにして本実施の形態では、トランザクション内に解析データを付加したユーザ定義メッセージトランザクションを、LSI70の通常トランザクション出力パスを共用して出力するので、ハードウェアが通常動作中にLSI70内部の解析データをリアルタイムに採取することができる。

【0013】

以下、本発明の一実施の形態としてのデバッグ回路1について詳細に説明する。図1を参照すると、デバッグ回路1は、LSI論理回路50およびロジックアナライザ60にそれぞれ接続されており、モード保持回路10、パタン検出回路20、トランザクション生成回路30、トランザクション選択回路40、LSI論理回路50を含んで構成される。

【0014】

モード保持回路10には、モード設定信号が入力されるようになっている。LSI論理回路50は、パタン検出回路20に対して論理回路状態信号を供給し、トランザクション生成回路30に対して解析データを供給し、トランザクション選択回路40に対して通常トランザクションを供給するようになっている。モード保持回路10は、モード信号をパタン検出回路20に供給し、パタン検出回路20は、パタン種別信号およびパタン一致信号をトランザクション生成回路30にそれぞれ供給し、トランザクション生成回路30は、ユーザ定義トランザクションをトランザクション選択回路40に供給するようになっている。トランザクション選択回路40は、LSIトランザクション出力をロジックアナライザ60およびその他のLSI等に供給するようになっている。

【0015】

モード保持回路10はモード設定信号により、LSI論理回路50から出力される解析データを採取するタイミング情報と解析データ採取条件を保持する。パタン検出回路20は、LSI論理回路50から出力される論理回路状態信号とモード保持回路10の出力を入力し、LSI論理回路50からの論理状態信号がモード保持回路10からの条件と一致するか否かをチェックし、一致する場合はパタン種別信号とパタン一致信号をトランザクション生成回路30に送出する。

【0016】

トランザクション生成回路30は、パタン検出回路20から送出されたパタン一致信号を受けたとき、パタン検出回路20から送出されるパタン種別信号に応じてユーザ定義メッセージトランザクションヘッダとパタン種別信号毎に異なる補助コードを作成し、LSI論理回路50から送出される解析データをヘッダの後に付加したユーザ定義メッセージトランザクションを作成する。

【0017】

トランザクション選択回路40は、トランザクション生成回路30から供給されるユーザ定義メッセージトランザクションとLSI論理回路50から供給される通常トランザクションを選択し、LSIトランザクション出力とする。LSIトランザクション出力はロジックアナライザ60に送出される。

【0018】

ロジックアナライザ60では、トランザクションヘッダがユーザ定義メッセージトランザクションである場合、入力データをロジックアナライザ60内のメモリ等に記録する。ロジックアナライザ60に記録されたデータを解析することにより、ハードウェア動作中のLSI内論理回路動作を解析することができる。ここでは、解析データを記録する装置をロジックアナライザ60としたが、この他の記録装置でも良く、特にロジックアナライザ60に限定しない。

【0019】

次に、図1に示したデバッグ回路1の動作について、図2のトランザクション発生タイミング例と、図3のユーザ定義メッセージトランザクションフォーマットを参照して説明する。

【0020】

図2に示したトランザクション発生タイミング例のように、時刻nから時刻(n+7+m)の間で、時刻(n+7)でモード信号保持回路10の条件とLSI論理回路50の論理動作が一致した場合についての動作を図1、図2、図3を参照して説明する。

【0021】

図1において、採取したいデータのタイミングとデータ種別などの情報を含むモード設定信号がモード信号保持回路10に設定される。モード設定信号によりLSI論理回路50からの解析データを採取するタイミング情報と解析データ採取条件が保持される。

【0022】

パタン検出回路20は、LSI論理回路50の論理状態信号とモード保持回路10の出力を入力し、LSI論理回路50からの論理状態信号がモード保持回路10からの条件と一致するか否かを比較して判定し、一致する場合はパタン種別信号とパタン一致信号をトランザクション生成回路30に送出する。

【0023】

図2の例では、時刻nから時刻(n+6)まではモード保持回路10から出力されるモード信号を受けたパタン検出回路20は、LSI論理回路50からの論理回路状態信号とデータ採取タイミング条件とを比較し、論理回路状態信号がデータ採取タイミング条件に一致しないため、パタン一致信号を出力しない。

【0024】

時刻(n+7)でLSI論理回路50から出力される論理回路状態信号とモード信号が一致するため、パタン検出回路20はトランザクション生成回路30に対してパタン一致信号と一致したモード信号をパタン種別信号として送出する。トランザクション生成回路30では、パタン一致信号を受けるとユーザ定義メッセージトランザクションのヘッダを作成する。

【0025】

図3に示したように、ユーザ定義メッセージトランザクションのヘッダ情報には、補助コードフィールドにパタン種別信号が埋め込まれる。これによって、ユーザ定義メッセージトランザクションがどのようなモード設定で発生したかを解析時に判別できる。

【0026】

トランザクション生成回路30では、図3に示したように、解析データとして(m−1)ワードのデータを採取する。解析データのワード数はパタン種別信号により変更可能である。トランザクション生成回路30は、LSI論理回路50から出力される(m−1)ワードの解析データを受け、図3に示したような、mワードのユーザ定義メッセージトランザクションを作成する。

【0027】

ユーザ定義メッセージトランザクションは、時刻(n+7)でトランザクション選択回路40に送出され、時刻(n+7)から時刻(n+7+m)の間、トランザクション選択回路40で選択され、LSIトランザクション出力としてLSI70の外に出力され、ロジックアナライザ60に入力される。

【0028】

時刻(n+7+m)においてパタン検出回路20によってパタン一致が検出されないので、トランザクション選択回路40では、図2の通常トランザクション(n+8)を選択し、LSIトランザクション出力としてLSI70の外に出力する。

【0029】

図2の例では、通常トランザクションとユーザ定義メッセージトランザクションのタイミングは競合しないが、競合するケースが発生した場合、トランザクション選択回路40は通常トランザクションを優先して選択し、性能低下が生じないようにする。

【0030】

このように、通常トランザクションとユーザ定義メッセージトランザクションは競合するケースがあるため、ユーザ定義メッセージトランザクションはLSI70の外に出力されるまで、トランザクション生成回路30で保持される。

【0031】

ロジックアナライザ60では、トランザクションヘッダがユーザ定義メッセージトランザクションである場合、データをロジックアナライザ60のメモリ等に記録する。

【0032】

次に、本発明の他の実施の形態について説明する。図4は、本発明の他の実施の形態の構成例を示しており、その基本的構成は図1に示した実施の形態の場合と同様であるが、図4の実施の形態では、ユーザ定義メッセージトランザクションと通常トランザクションが競合するケースについてさらに工夫している。

【0033】

図4に示した実施の形態において、トランザクションバッファ80は、トランザクション生成回路30で作成したユーザ定義メッセージトランザクションを複数保持する。モード保持回路10は、モード設定信号によりLSI論理回路50からの解析データを採取するタイミング情報と解析データ採取条件を保持する。

【0034】

パタン検出回路20は、LSI論理回路50から出力される論理状態信号とモード保持回路10の出力を入力し、LSI論理回路50からの論理状態信号がモード保持回路10からの条件と一致するか否かをチェックし、一致する場合はパタン種別信号とパタン一致信号をトランザクション生成回路30に送出する。

【0035】

トランザクション生成回路30はパタン検出回路20からパタン一致信号を受けたとき、パタン検出回路20から送出されるパタン種別信号に応じてユーザ定義メッセージトランザクションヘッダとパタン種別信号毎に存在する補助コードを作成し、LSI論理回路50から送出される解析データをヘッダの後に付加したユーザ定義メッセージトランザクションを作成する。

【0036】

トランザクションバッファ80は、トランザクション生成回路30で作成されたユーザ定義メッセージトランザクションを保持する。トランザクション選択回路40は、トランザクションバッファ80から供給されるユーザ定義メッセージトランザクションとLSI論理回路50から出力される通常トランザクションを選択し、LSIトランザクション出力とする。

【0037】

LSIトランザクション出力は、ロジックアナライザ60に送出される。ロジックアナライザ60では、トランザクションヘッダがユーザ定義メッセージトランザクションである場合、データをロジックアナライザ60内のメモリ等に記録する。ロジックアナライザ60に記録されたデータを解析することにより、ハードウェア動作中のLSI内論理回路動作を解析することができる。

【0038】

ここでは、解析データを記録する装置をロジックアナライザ60としたが、この他の記録装置でも良く、特にロジックアナライザ60に限定しない。

【0039】

このように、図4に示した実施の形態では、ユーザ定義メッセージトランザクションをトランザクションバッファ80で複数保持することができるので、ユーザ定義メッセージトランザクションが複数生成されたとき、通常トランザクションとトランザクション選択回路40での競合が多発したときにユーザ定義メッセージトランザクションをロストすることなくLSI70より出力できるという効果が得られる。

【0040】

以上説明したように、本実施の形態においては、以下に記載するような効果を奏する。

第1の効果は、モード保持回路10からのデータ採取条件情報を含むモード信号とLSI論理回路50の論理回路状態信号をパタン検出回路20で比較し、一致したタイミングでユーザ定義メッセージトランザクションに解析データを付加するので、ハードウェア動作中に必要とするタイミングの解析データをリアルタイムで採取できることである。

第2の効果は、解析データが付加されたユーザ定義メッセージトランザクションと通常トランザクションとでLSI出力PINを共用しているので、デバッグ用にLSI出力PINを増やさずに解析データを採取できることである。

【0041】

なお、上記実施の形態の構成及び動作は例であって、本発明の趣旨を逸脱しない範囲で適宜変更することができることは言うまでもない。

【産業上の利用可能性】

【0042】

本発明はLSIの内部動作解析のため、LSI内部情報を採取するデバッグ回路に適用できる。特に解析に必要なタイミングの内部データをハードウェア動作中にリアルタイムかつLSIのPINを増やすことなく採取する必要がある場合に効果的に適用できる。

【図面の簡単な説明】

【0043】

【図1】本発明のデバッグ回路の一実施の形態の構成例を示すブロック図である。

【図2】トランザクション発生タイミング例を示す図である。

【図3】ユーザ定義メッセージトランザクションフォーマット例を示す図である。

【図4】本発明のデバッグ回路の他の実施の形態の構成例を示すブロック図である。

【符号の説明】

【0044】

1 デバッグ回路

10 モード保持回路

20 パタン検出回路

30 トランザクション生成回路

40 トランザクション選択回路

50 LSI論理回路

60 ロジックアナライザ

70 LSI

80 トランザクションバッファ

【特許請求の範囲】

【請求項1】

LSI動作解析データを採取するデバッグ回路であって、

ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取手段を備える

ことを特徴とするデバッグ回路。

【請求項2】

ユーザ定義メッセージトランザクションと通常トランザクションの競合多発のケースでユーザ定義メッセージトランザクションロストを防ぐため、トランザクションバッファを備える

ことを特徴とする請求項1に記載のデバッグ回路。

【請求項3】

LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持手段と、

前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出手段と、

パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成手段と、

通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択手段と

を備えることを特徴とするデバッグ回路。

【請求項4】

LSI動作解析データを採取するデバッグ方法であって、

ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップを備える

ことを特徴とするデバッグ方法。

【請求項5】

LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、

前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、

パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、

通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップと

を備えることを特徴とするデバッグ方法。

【請求項6】

LSI動作解析データを採取するデバッグ回路を制御するデバッグプログラムであって、

ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップをコンピュータに実行させる

ことを特徴とするデバッグプログラム。

【請求項7】

LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、

前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、

パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、

通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップと

をコンピュータに実行させることを特徴とするデバッグプログラム。

【請求項1】

LSI動作解析データを採取するデバッグ回路であって、

ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取手段を備える

ことを特徴とするデバッグ回路。

【請求項2】

ユーザ定義メッセージトランザクションと通常トランザクションの競合多発のケースでユーザ定義メッセージトランザクションロストを防ぐため、トランザクションバッファを備える

ことを特徴とする請求項1に記載のデバッグ回路。

【請求項3】

LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持手段と、

前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出手段と、

パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成手段と、

通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択手段と

を備えることを特徴とするデバッグ回路。

【請求項4】

LSI動作解析データを採取するデバッグ方法であって、

ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップを備える

ことを特徴とするデバッグ方法。

【請求項5】

LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、

前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、

パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、

通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップと

を備えることを特徴とするデバッグ方法。

【請求項6】

LSI動作解析データを採取するデバッグ回路を制御するデバッグプログラムであって、

ユーザ定義メッセージトランザクションにデバッグデータを付加して通常トランザクション出力パスとLSIの出力を共用して解析データを採取する採取ステップをコンピュータに実行させる

ことを特徴とするデバッグプログラム。

【請求項7】

LSI論理回路の動作中にデータ採取するタイミングと採取するデータの選択条件を保持するモード保持ステップと、

前記LSI論理回路内の論理回路状態信号がモード保持回路出力の条件と一致したとき、パタン一致信号とパタン種別信号を送出するパタン検出ステップと、

パタン一致信号を受けるとパタン種別信号毎に異なる補助コードを持ったトランザクションヘッダを作成し、ヘッダの後にLSI論理回路から出力される解析データを付加したユーザ定義メッセージトランザクションを作成するトランザクション生成ステップと、

通常トランザクションと前記ユーザ定義メッセージトランザクションとを選択し、LSIからトランザクション出力として出力するトランザクション選択ステップと

をコンピュータに実行させることを特徴とするデバッグプログラム。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2007−212327(P2007−212327A)

【公開日】平成19年8月23日(2007.8.23)

【国際特許分類】

【出願番号】特願2006−33421(P2006−33421)

【出願日】平成18年2月10日(2006.2.10)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成19年8月23日(2007.8.23)

【国際特許分類】

【出願日】平成18年2月10日(2006.2.10)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]