デュアルゲート半導体装置の製造方法およびその構造

【課題】2つのゲート配線間の接続を容易に、かつ低抵抗で行えるデュアルゲート半導体装置を提供する。

【解決手段】半導体基板を準備する工程と、半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、第1および第2の電極の上部を層間絶縁層から露出させる工程と、第2の電極の第1ゲート金属膜を選択的に除去する工程と、第1および第2の電極を覆うように、層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する工程と、第2ゲート金属膜とゲート配線膜をパターニングして、第1ゲート電極と第2ゲート電極とを形成するとともに、第1ゲート電極と第2ゲート電極とをゲート配線膜で接続する工程とを含む。

【解決手段】半導体基板を準備する工程と、半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、第1および第2の電極の上部を層間絶縁層から露出させる工程と、第2の電極の第1ゲート金属膜を選択的に除去する工程と、第1および第2の電極を覆うように、層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する工程と、第2ゲート金属膜とゲート配線膜をパターニングして、第1ゲート電極と第2ゲート電極とを形成するとともに、第1ゲート電極と第2ゲート電極とをゲート配線膜で接続する工程とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デュアルゲート半導体装置の製造方法およびその構造に関し、特に、CMOSFET半導体装置の製造方法およびその構造に関する。

【背景技術】

【0002】

近年、CMOSFET等のデュアルゲート半導体装置では、半導体装置の微細化に伴い、空乏層の形成を防止するためにメタルゲート電極が用いられる。メタルゲート電極の形成工程では、p型FETとn型FETのように、異なる材料からなるメタルゲート電極をそれぞれエッチング加工で形成することは困難である。このため、第1の金属材料で双方のゲート電極を形成し層間絶縁層に埋め込んだ後、一方のゲート電極を選択的に除去して、代わりに第2の金属材料を埋め込む製造方法が用いられている(例えば、特許文献1参照)。

【特許文献1】特開2002−289700号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、CMOSFET等のデュアルゲート半導体装置では、第1の金属材料からなるゲート配線と、第2の金属材料からなるゲート配線とを接続する必要があるが、微細ゲート配線では接続のための位置合わせが困難となり、断線が発生しやすく、製造歩留まりが低下するという問題があった。

また、ゲート配線が、金属ゲート電極膜とその上に形成される低抵抗の金属ゲート配線膜からなる場合、ゲート配線の接続が金属ゲート電極膜を挟むため、接続部分が高抵抗化して、半導体装置の特性が悪くなるという問題もあった。

【0004】

そこで、本発明は、デュアルゲート半導体装置において、2つのゲート配線間の接続を容易に、かつ低抵抗で行えるデュアルゲート半導体装置の製造方法およびその構造の提供を目的とする。

【課題を解決するための手段】

【0005】

本発明は、第1導電型FETと第2導電型FETとを含むデュアルゲート半導体装置の製造方法であって、半導体基板を準備する工程と、半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、第1および第2の電極の上部を層間絶縁層から露出させる工程と、第2の電極の第1ゲート金属膜を選択的に除去する選択除去工程と、第1および第2の電極を覆うように、層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する堆積工程と、第2ゲート金属膜とゲート配線膜をパターニングして、ゲート絶縁膜上に第1ゲート金属膜、第2ゲート金属膜、およびゲート配線膜が順次積層された第1ゲート電極と、ゲート絶縁膜上に第2ゲート金属膜とゲート配線膜が順次積層された第2ゲート電極とを形成するとともに、第1ゲート電極と第2ゲート電極とをゲート配線膜で接続する工程とを含むことを特徴とするデュアルゲート半導体装置の製造方法である。

【0006】

また、本発明は、導電型の異なる2つのFETを含むデュアルゲート半導体装置であって、半導体基板と、半導体基板上に設けられた、ゲート絶縁膜上に順次積層された第1ゲート金属膜、第2ゲート金属膜、およびゲート配線膜を含む第1導電型FETの第1ゲート電極と、ゲート絶縁膜上に順次積層された第2ゲート金属膜およびゲート配線膜を含む第2導電型FETの第2ゲート電極と、を有し、第1ゲート電極と第2ゲート電極とが、これらの電極で共通するゲート配線膜により電気的に接続されたことを特徴とするデュアルゲート半導体装置でもある。

【発明の効果】

【0007】

本発明にかかる半導体装置の製造方法では、製造歩留まりが良好で、かつ特性の良好なデュアルゲート半導体装置の提供が可能となる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

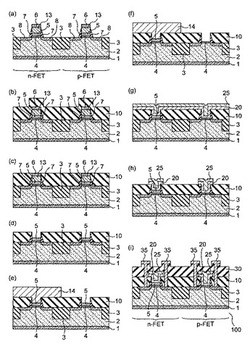

図1は、全体が100で表される、本実施の形態1にかかるCMOSFET半導体装置の製造工程の断面図である。かかる製造工程は、以下の1〜9の工程を含む。

【0009】

工程1:図1(a)に示すように、シリコン基板1を準備する。シリコン基板1の上には、シリコン層2を形成する。シリコン層2には、酸化シリコン等の素子分離領域3により電気的に分離されたn−FET領域とp−FET領域が形成される。これらの領域には、例えば、HfSiON等のHigh−k(高誘電体)材料からなるゲート絶縁膜4、TaSiNからなる第1ゲート金属膜5、Wからなる金属ゲート配線膜13、SiNからなるハードマスク6を形成する。第1ゲート金属膜5には、TaSiNのみでなく、TaC、TaN、TiSiN、TiNといった金属膜を用いても良い。これらは、ハードマスク6を用いたRIE等で同時に形成できる。続いて、例えばSiO2からなるサイドウオール7を形成する。更に、ハードマスク6等をマスクに用いたイオン注入と、熱処理による注入イオンの活性化を行い、ソース/ドレイン領域8を形成する。

【0010】

工程2:図1(b)に示すように、PMD(Pre-Metal Dielectric)層10を例えばCVD法で形成する。

【0011】

工程3:図1(c)に示すように、例えばCMP法を用いてPMD層10を平坦化する。かかる工程で、PMD層10に埋め込まれたハードマスク6が露出する。

【0012】

工程4:図1(d)に示すように、RIEやウエットエッチングを用いて、ハードマスク6を選択的に除去する。続いて、金属ゲート配線膜13を選択的に除去する。金属ゲート配線膜13の除去は、例えば、60℃の過酸化水素水を用いたウエットエッチングで行う。

【0013】

工程5:図1(e)に示すように、アモルファスシリコン層14を全面に形成した後、エッチングにより、n−FET領域のみにアモルファスシリコン層14を残す。

【0014】

工程6:図1(f)に示すように、アモルファスシリコン層14をマスクに用いて、p−FET領域の第1ゲート金属膜5を選択的に除去する。第1ゲート金属膜5の除去は、例えば、約60〜80℃のアンモニア過酸化水素混合水(APM)を用いたウエットエッチングで行う。

【0015】

工程7:図1(g)に示すように、n−FET領域のアモルファスシリコン層14を、過酸化水素水を用いたウエットエッチングで除去する。続いて、例えばTiNからなる第2ゲート金属膜5、Wからなる金属ゲート配線膜25を全面に形成する。かかる工程で、n−FET領域の第1ゲート金属膜5と、p−FET領域の第2ゲート金属膜20とが接続される。

【0016】

第2ゲート金属膜5には、TiN、TiAlN、TaN、TaAlN、Ru、Ir、Pt、Ni、Co、W、WN、Mo、MoN、NiSi(好適にはNixSiのxは1以上)、およびPtSi(好適にはPtxSiのxは1以上)からなる群から選択される材料を主成分とする材料を選択することが好ましい。以下の実施の形態2、3でも同様である。

【0017】

また、以下の工程8以降は、シリコン基板1の温度が500℃以下で行われることが好ましい。

【0018】

工程8:図1(h)に示すように、エッチングマスク(図示せず)を用いて、第2ゲート金属膜20、金属ゲート配線膜25をエッチングする。この工程は、CMPプロセスを用いてPMD層10まで平坦化することで、電極をパターニングしても良い。

【0019】

工程9:図1(i)に示すように、例えばSiO2からなる層間絶縁層30を形成し、ソース/ドレイン領域からの引き出し配線35を形成することにより、CMOSFET半導体装置100が完成する。

【0020】

図2は、CMOSFET半導体装置100の概略図であり、(a)に上面図、(b)に(a)のII−II方向に見た場合の断面図を示す。図2中、図1と同一符号は同一又は相当箇所を示す。

【0021】

上述のように、工程7(図1(g))により、n−FET領域のゲート電極とp−FET領域のゲート電極とは、Wからなる金属ゲート配線膜25により接続される。このため、従来のように、n−FET領域のゲート配線層とp−FET領域のゲート配線層とを接続する必要がなく、接続不良による歩留まりの低下を防止できる。

また、第1ゲート金属膜5や第2ゲート金属膜20を間に挟むことなく低抵抗の金属ゲート配線膜25で接続されるため、接続箇所の高抵抗化による性能の低下も防止できる。

【0022】

実施の形態2.

図3は、全体が200で表される、本実施の形態2にかかるCMOSFET半導体装置の製造工程の断面図である。図3中、図1と同一符号は同一又は相当箇所を示す。かかる製造工程は、以下の1〜9の工程を含む。

【0023】

工程1:図3(a)に示すように、実施の形態1の工程1と略同様の工程で、n−FET領域、p−FET領域に、例えば、HfSiON等のHigh−k材料からなるゲート絶縁膜4、TaSiNからなる第1ゲート金属膜5、アモルファスシリコン(マスク用シリコン)膜15、SiNからなるハードマスク6を形成する。第1ゲート金属膜5には、TaSiNのみでなく、TaC、TaN、TiSiN、TiNといった金属膜を用いても良い。続いて、例えばSiO2からなるサイドウオール7を形成した後、イオン注入によりソース/ドレイン領域8を形成する。

ここでは、Wからなる金属ゲート配線膜13に代えてアモルファスシリコン膜15が形成されている点を除き、図1(a)と同じ構造となっている。なお、アモルファスシリコン膜15に代えて、ポリシリコン膜を用いても構わない。

【0024】

工程2:図3(b)に示すように、PMD層10を例えばCVD法で形成する。

【0025】

工程3:図3(c)に示すように、例えばCMP法を用いてPMD層10を平坦化し、ハードマスク6を露出させる。工程2、3は、実施の形態1の工程2、3と同様である。

【0026】

工程4:図3(d)に示すように、RIEやウエットエッチングを用いて、n−FET領域およびp−FET領域のハードマスク10を選択的に除去する。続いて、例えばレジストマスク(図示せず)でn−FET領域を覆って、p−FET領域のアモルファスシリコン膜15を、例えばRIEで選択的に除去する。

【0027】

工程5:図3(e)に示すように、p−FET領域の第1ゲート金属膜5を、例えば、60〜80℃のアンモニア/過酸化水素混合水を用いたウエットエッチングで、選択的に除去する。

【0028】

工程6:図3(f)に示すように、n−FET領域のアモルファスシリコン膜15を、例えば、60℃の水酸化アンモニウム溶液を用いて、ウエットエッチングで除去する。

【0029】

工程7:図3(g)に示すように、例えばTiNからなる第2ゲート金属膜5、Wからなる金属ゲート配線膜25を全面に形成する。かかる工程で、n−FET領域の第1ゲート金属膜5と、p−FET領域の第2ゲート金属膜20とが接続される。

【0030】

工程8:図3(h)に示すように、エッチングマスク(図示せず)を用いて、第2ゲート金属膜20、金属ゲート配線膜25をエッチングする。この工程は、CMPプロセスを用いてPMD層10まで平坦化することで、電極をパターニングしても良い。

【0031】

工程9:図3(i)に示すように、例えばSiO2からなる層間絶縁層30を形成し、ソース/ドレイン領域からの引き出し配線35を形成することにより、CMOSFET半導体装置200が完成する。

【0032】

本実施の形態2にかかる製造方法では、第1ゲート金属膜5の上に形成したアモルファスシリコン膜15が、工程4、5でエッチング用マスクとして機能する。このため、実施の形態1の工程5(図1(e))のように、ポリシリコン層15のエッチングマスクを別途形成する工程が省略できる。

【0033】

実施の形態3.

図4は、全体が300で表される、本実施の形態3にかかるCMOSFET半導体装置の製造工程の断面図である。図4中、図1と同一符号は同一又は相当箇所を示す。かかる製造工程は、以下の1〜9の工程を含む。

【0034】

工程1:図4(a)に示すように、実施の形態2の工程1と略同様の工程で、n−FET領域、p−FET領域に、例えば、HfSiON等のHigh−k材料からなるゲート絶縁膜4、TaSiNからなる第1ゲート金属膜5、アモルファスシリコン膜15、およびSiNからなるハードマスク6を形成する。第1ゲート金属膜5には、TaSiNのみでなく、TaC、TaN、TiSiN、TiNといった金属膜を用いても良い。続いて、例えばSiO2からなるサイドウオール7を形成した後、イオン注入によりソース/ドレイン領域8を形成する。アモルファスシリコン膜15に代えて、ポリシリコン膜を用いても構わない。

【0035】

工程2:図4(b)に示すように、PMD層10を例えばCVD法で形成する。

【0036】

工程3:図4(c)に示すように、例えばCMP法を用いてPMD層10を平坦化し、ハードマスク6を露出させる。工程2、3は、実施の形態1の工程2、3と同様である。

【0037】

工程4:図4(d)に示すように、RIEやウエットエッチングを用いて、n−FET領域およびp−FET領域のハードマスク10を選択的に除去する。続いて、例えばレジストマスク(図示せず)でn−FET領域を覆って、p−FET領域のアモルファスシリコン膜15を、例えばRIEで選択的に除去する。

【0038】

工程5:図4(e)に示すように、p−FET領域の第1ゲート金属膜5を、例えば、60〜80℃のアンモニア/過酸化水素混合水を用いたウエットエッチングで、選択的に除去する。

【0039】

工程6:図4(f)に示すように、n−FET領域のアモルファスシリコン膜15を、例えば、60℃の水酸化アンモニウム溶液を用いて、ウエットエッチングで除去する。

【0040】

工程7:図4(g)に示すように、ポリシリコン膜を全面に形成した後、RIE等を用いたパターニングで、後にゲート電極となるポリシリコン膜40を形成する。ポリシリコン膜のパターニングは、工程9で行っても構わない。

【0041】

工程8:図4(h)に示すように、例えば蒸着法により、全面にニッケル層45を形成する。ニッケル層45の膜厚は、ポリシリコン膜40の膜厚より厚く、2倍程度が好ましい。

【0042】

工程9:図4(i)に示すように、400℃程度に加熱し、ポリシリコン膜40をニッケル層45中のニッケルと反応させ、ニッケルシリサイド(NixSi:xは好適には1以上)膜41(FUSI電極)とする。続いて、エッチングマスク(図示せず)を用いて、ニッケル層45をパターニングする。

【0043】

工程10:図4(j)に示すように、例えばSiO2からなる層間絶縁層30を形成し、ソース/ドレイン電極35を形成することにより、CMOSFET半導体装置300が完成する。

【0044】

かかる製造方法では、工程7以降の工程に、従来のFUSIゲート作製工程を適用することができ、プロセス条件等の設定が容易に行える。

【0045】

また、CMOSFET半導体装置300では、ニッケルシリサイド(NixSi)膜41のニッケル含有量によりFETの閾値を変化させることができ、ニッケル含有量が多いほど閾値が小さくなる。例えば、Ni/Siの組成比を2〜3程度にすることにより、ニッケルシリサイド膜4の実効仕事関数が約4.8eVとなり、閾値を−0.4Vとすることができる。

【0046】

なお、実施の形態1〜3では、MOSFETを例に述べたが、ゲート絶縁膜が酸化膜以外の絶縁膜からなるMISFETにも適用することができる。また、砒化ガリウムや炭化シリコンのような、シリコン以外の半導体材料にも適用することができる。

【0047】

また、ソース/ドレイン領域8の表面を例えばニッケルシリサイド化したり、ソース/ドレイン領域8にエクステンション領域を設けるなど、一般的なCMOSFETに用いられる構造を適宜適用しても構わない。

【図面の簡単な説明】

【0048】

【図1】本発明の実施の形態1にかかるCMOSFET半導体装置の製造工程の断面図である。

【図2】本発明の実施の形態1にかかるCMOSFET半導体装置のゲート電極部分の概略図である。

【図3】本発明の実施の形態2にかかるCMOSFET半導体装置の製造工程の断面図である。

【図4】本発明の実施の形態3にかかるCMOSFET半導体装置の製造工程の断面図である。

【符号の説明】

【0049】

1 シリコン基板、2 シリコン層、3 素子分離領域、4 ゲート絶縁膜、5 第1ゲート金属膜、6 ハードマスク、7 サイドウオール、8 ソース/ドレイン領域、10 PMD層、14 アモルファスシリコン層、20 第2ゲート金属膜、25 金属ゲート配線膜、30 層間絶縁層、100 CMOSFET半導体装置。

【技術分野】

【0001】

本発明は、デュアルゲート半導体装置の製造方法およびその構造に関し、特に、CMOSFET半導体装置の製造方法およびその構造に関する。

【背景技術】

【0002】

近年、CMOSFET等のデュアルゲート半導体装置では、半導体装置の微細化に伴い、空乏層の形成を防止するためにメタルゲート電極が用いられる。メタルゲート電極の形成工程では、p型FETとn型FETのように、異なる材料からなるメタルゲート電極をそれぞれエッチング加工で形成することは困難である。このため、第1の金属材料で双方のゲート電極を形成し層間絶縁層に埋め込んだ後、一方のゲート電極を選択的に除去して、代わりに第2の金属材料を埋め込む製造方法が用いられている(例えば、特許文献1参照)。

【特許文献1】特開2002−289700号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、CMOSFET等のデュアルゲート半導体装置では、第1の金属材料からなるゲート配線と、第2の金属材料からなるゲート配線とを接続する必要があるが、微細ゲート配線では接続のための位置合わせが困難となり、断線が発生しやすく、製造歩留まりが低下するという問題があった。

また、ゲート配線が、金属ゲート電極膜とその上に形成される低抵抗の金属ゲート配線膜からなる場合、ゲート配線の接続が金属ゲート電極膜を挟むため、接続部分が高抵抗化して、半導体装置の特性が悪くなるという問題もあった。

【0004】

そこで、本発明は、デュアルゲート半導体装置において、2つのゲート配線間の接続を容易に、かつ低抵抗で行えるデュアルゲート半導体装置の製造方法およびその構造の提供を目的とする。

【課題を解決するための手段】

【0005】

本発明は、第1導電型FETと第2導電型FETとを含むデュアルゲート半導体装置の製造方法であって、半導体基板を準備する工程と、半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、第1および第2の電極の上部を層間絶縁層から露出させる工程と、第2の電極の第1ゲート金属膜を選択的に除去する選択除去工程と、第1および第2の電極を覆うように、層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する堆積工程と、第2ゲート金属膜とゲート配線膜をパターニングして、ゲート絶縁膜上に第1ゲート金属膜、第2ゲート金属膜、およびゲート配線膜が順次積層された第1ゲート電極と、ゲート絶縁膜上に第2ゲート金属膜とゲート配線膜が順次積層された第2ゲート電極とを形成するとともに、第1ゲート電極と第2ゲート電極とをゲート配線膜で接続する工程とを含むことを特徴とするデュアルゲート半導体装置の製造方法である。

【0006】

また、本発明は、導電型の異なる2つのFETを含むデュアルゲート半導体装置であって、半導体基板と、半導体基板上に設けられた、ゲート絶縁膜上に順次積層された第1ゲート金属膜、第2ゲート金属膜、およびゲート配線膜を含む第1導電型FETの第1ゲート電極と、ゲート絶縁膜上に順次積層された第2ゲート金属膜およびゲート配線膜を含む第2導電型FETの第2ゲート電極と、を有し、第1ゲート電極と第2ゲート電極とが、これらの電極で共通するゲート配線膜により電気的に接続されたことを特徴とするデュアルゲート半導体装置でもある。

【発明の効果】

【0007】

本発明にかかる半導体装置の製造方法では、製造歩留まりが良好で、かつ特性の良好なデュアルゲート半導体装置の提供が可能となる。

【発明を実施するための最良の形態】

【0008】

実施の形態1.

図1は、全体が100で表される、本実施の形態1にかかるCMOSFET半導体装置の製造工程の断面図である。かかる製造工程は、以下の1〜9の工程を含む。

【0009】

工程1:図1(a)に示すように、シリコン基板1を準備する。シリコン基板1の上には、シリコン層2を形成する。シリコン層2には、酸化シリコン等の素子分離領域3により電気的に分離されたn−FET領域とp−FET領域が形成される。これらの領域には、例えば、HfSiON等のHigh−k(高誘電体)材料からなるゲート絶縁膜4、TaSiNからなる第1ゲート金属膜5、Wからなる金属ゲート配線膜13、SiNからなるハードマスク6を形成する。第1ゲート金属膜5には、TaSiNのみでなく、TaC、TaN、TiSiN、TiNといった金属膜を用いても良い。これらは、ハードマスク6を用いたRIE等で同時に形成できる。続いて、例えばSiO2からなるサイドウオール7を形成する。更に、ハードマスク6等をマスクに用いたイオン注入と、熱処理による注入イオンの活性化を行い、ソース/ドレイン領域8を形成する。

【0010】

工程2:図1(b)に示すように、PMD(Pre-Metal Dielectric)層10を例えばCVD法で形成する。

【0011】

工程3:図1(c)に示すように、例えばCMP法を用いてPMD層10を平坦化する。かかる工程で、PMD層10に埋め込まれたハードマスク6が露出する。

【0012】

工程4:図1(d)に示すように、RIEやウエットエッチングを用いて、ハードマスク6を選択的に除去する。続いて、金属ゲート配線膜13を選択的に除去する。金属ゲート配線膜13の除去は、例えば、60℃の過酸化水素水を用いたウエットエッチングで行う。

【0013】

工程5:図1(e)に示すように、アモルファスシリコン層14を全面に形成した後、エッチングにより、n−FET領域のみにアモルファスシリコン層14を残す。

【0014】

工程6:図1(f)に示すように、アモルファスシリコン層14をマスクに用いて、p−FET領域の第1ゲート金属膜5を選択的に除去する。第1ゲート金属膜5の除去は、例えば、約60〜80℃のアンモニア過酸化水素混合水(APM)を用いたウエットエッチングで行う。

【0015】

工程7:図1(g)に示すように、n−FET領域のアモルファスシリコン層14を、過酸化水素水を用いたウエットエッチングで除去する。続いて、例えばTiNからなる第2ゲート金属膜5、Wからなる金属ゲート配線膜25を全面に形成する。かかる工程で、n−FET領域の第1ゲート金属膜5と、p−FET領域の第2ゲート金属膜20とが接続される。

【0016】

第2ゲート金属膜5には、TiN、TiAlN、TaN、TaAlN、Ru、Ir、Pt、Ni、Co、W、WN、Mo、MoN、NiSi(好適にはNixSiのxは1以上)、およびPtSi(好適にはPtxSiのxは1以上)からなる群から選択される材料を主成分とする材料を選択することが好ましい。以下の実施の形態2、3でも同様である。

【0017】

また、以下の工程8以降は、シリコン基板1の温度が500℃以下で行われることが好ましい。

【0018】

工程8:図1(h)に示すように、エッチングマスク(図示せず)を用いて、第2ゲート金属膜20、金属ゲート配線膜25をエッチングする。この工程は、CMPプロセスを用いてPMD層10まで平坦化することで、電極をパターニングしても良い。

【0019】

工程9:図1(i)に示すように、例えばSiO2からなる層間絶縁層30を形成し、ソース/ドレイン領域からの引き出し配線35を形成することにより、CMOSFET半導体装置100が完成する。

【0020】

図2は、CMOSFET半導体装置100の概略図であり、(a)に上面図、(b)に(a)のII−II方向に見た場合の断面図を示す。図2中、図1と同一符号は同一又は相当箇所を示す。

【0021】

上述のように、工程7(図1(g))により、n−FET領域のゲート電極とp−FET領域のゲート電極とは、Wからなる金属ゲート配線膜25により接続される。このため、従来のように、n−FET領域のゲート配線層とp−FET領域のゲート配線層とを接続する必要がなく、接続不良による歩留まりの低下を防止できる。

また、第1ゲート金属膜5や第2ゲート金属膜20を間に挟むことなく低抵抗の金属ゲート配線膜25で接続されるため、接続箇所の高抵抗化による性能の低下も防止できる。

【0022】

実施の形態2.

図3は、全体が200で表される、本実施の形態2にかかるCMOSFET半導体装置の製造工程の断面図である。図3中、図1と同一符号は同一又は相当箇所を示す。かかる製造工程は、以下の1〜9の工程を含む。

【0023】

工程1:図3(a)に示すように、実施の形態1の工程1と略同様の工程で、n−FET領域、p−FET領域に、例えば、HfSiON等のHigh−k材料からなるゲート絶縁膜4、TaSiNからなる第1ゲート金属膜5、アモルファスシリコン(マスク用シリコン)膜15、SiNからなるハードマスク6を形成する。第1ゲート金属膜5には、TaSiNのみでなく、TaC、TaN、TiSiN、TiNといった金属膜を用いても良い。続いて、例えばSiO2からなるサイドウオール7を形成した後、イオン注入によりソース/ドレイン領域8を形成する。

ここでは、Wからなる金属ゲート配線膜13に代えてアモルファスシリコン膜15が形成されている点を除き、図1(a)と同じ構造となっている。なお、アモルファスシリコン膜15に代えて、ポリシリコン膜を用いても構わない。

【0024】

工程2:図3(b)に示すように、PMD層10を例えばCVD法で形成する。

【0025】

工程3:図3(c)に示すように、例えばCMP法を用いてPMD層10を平坦化し、ハードマスク6を露出させる。工程2、3は、実施の形態1の工程2、3と同様である。

【0026】

工程4:図3(d)に示すように、RIEやウエットエッチングを用いて、n−FET領域およびp−FET領域のハードマスク10を選択的に除去する。続いて、例えばレジストマスク(図示せず)でn−FET領域を覆って、p−FET領域のアモルファスシリコン膜15を、例えばRIEで選択的に除去する。

【0027】

工程5:図3(e)に示すように、p−FET領域の第1ゲート金属膜5を、例えば、60〜80℃のアンモニア/過酸化水素混合水を用いたウエットエッチングで、選択的に除去する。

【0028】

工程6:図3(f)に示すように、n−FET領域のアモルファスシリコン膜15を、例えば、60℃の水酸化アンモニウム溶液を用いて、ウエットエッチングで除去する。

【0029】

工程7:図3(g)に示すように、例えばTiNからなる第2ゲート金属膜5、Wからなる金属ゲート配線膜25を全面に形成する。かかる工程で、n−FET領域の第1ゲート金属膜5と、p−FET領域の第2ゲート金属膜20とが接続される。

【0030】

工程8:図3(h)に示すように、エッチングマスク(図示せず)を用いて、第2ゲート金属膜20、金属ゲート配線膜25をエッチングする。この工程は、CMPプロセスを用いてPMD層10まで平坦化することで、電極をパターニングしても良い。

【0031】

工程9:図3(i)に示すように、例えばSiO2からなる層間絶縁層30を形成し、ソース/ドレイン領域からの引き出し配線35を形成することにより、CMOSFET半導体装置200が完成する。

【0032】

本実施の形態2にかかる製造方法では、第1ゲート金属膜5の上に形成したアモルファスシリコン膜15が、工程4、5でエッチング用マスクとして機能する。このため、実施の形態1の工程5(図1(e))のように、ポリシリコン層15のエッチングマスクを別途形成する工程が省略できる。

【0033】

実施の形態3.

図4は、全体が300で表される、本実施の形態3にかかるCMOSFET半導体装置の製造工程の断面図である。図4中、図1と同一符号は同一又は相当箇所を示す。かかる製造工程は、以下の1〜9の工程を含む。

【0034】

工程1:図4(a)に示すように、実施の形態2の工程1と略同様の工程で、n−FET領域、p−FET領域に、例えば、HfSiON等のHigh−k材料からなるゲート絶縁膜4、TaSiNからなる第1ゲート金属膜5、アモルファスシリコン膜15、およびSiNからなるハードマスク6を形成する。第1ゲート金属膜5には、TaSiNのみでなく、TaC、TaN、TiSiN、TiNといった金属膜を用いても良い。続いて、例えばSiO2からなるサイドウオール7を形成した後、イオン注入によりソース/ドレイン領域8を形成する。アモルファスシリコン膜15に代えて、ポリシリコン膜を用いても構わない。

【0035】

工程2:図4(b)に示すように、PMD層10を例えばCVD法で形成する。

【0036】

工程3:図4(c)に示すように、例えばCMP法を用いてPMD層10を平坦化し、ハードマスク6を露出させる。工程2、3は、実施の形態1の工程2、3と同様である。

【0037】

工程4:図4(d)に示すように、RIEやウエットエッチングを用いて、n−FET領域およびp−FET領域のハードマスク10を選択的に除去する。続いて、例えばレジストマスク(図示せず)でn−FET領域を覆って、p−FET領域のアモルファスシリコン膜15を、例えばRIEで選択的に除去する。

【0038】

工程5:図4(e)に示すように、p−FET領域の第1ゲート金属膜5を、例えば、60〜80℃のアンモニア/過酸化水素混合水を用いたウエットエッチングで、選択的に除去する。

【0039】

工程6:図4(f)に示すように、n−FET領域のアモルファスシリコン膜15を、例えば、60℃の水酸化アンモニウム溶液を用いて、ウエットエッチングで除去する。

【0040】

工程7:図4(g)に示すように、ポリシリコン膜を全面に形成した後、RIE等を用いたパターニングで、後にゲート電極となるポリシリコン膜40を形成する。ポリシリコン膜のパターニングは、工程9で行っても構わない。

【0041】

工程8:図4(h)に示すように、例えば蒸着法により、全面にニッケル層45を形成する。ニッケル層45の膜厚は、ポリシリコン膜40の膜厚より厚く、2倍程度が好ましい。

【0042】

工程9:図4(i)に示すように、400℃程度に加熱し、ポリシリコン膜40をニッケル層45中のニッケルと反応させ、ニッケルシリサイド(NixSi:xは好適には1以上)膜41(FUSI電極)とする。続いて、エッチングマスク(図示せず)を用いて、ニッケル層45をパターニングする。

【0043】

工程10:図4(j)に示すように、例えばSiO2からなる層間絶縁層30を形成し、ソース/ドレイン電極35を形成することにより、CMOSFET半導体装置300が完成する。

【0044】

かかる製造方法では、工程7以降の工程に、従来のFUSIゲート作製工程を適用することができ、プロセス条件等の設定が容易に行える。

【0045】

また、CMOSFET半導体装置300では、ニッケルシリサイド(NixSi)膜41のニッケル含有量によりFETの閾値を変化させることができ、ニッケル含有量が多いほど閾値が小さくなる。例えば、Ni/Siの組成比を2〜3程度にすることにより、ニッケルシリサイド膜4の実効仕事関数が約4.8eVとなり、閾値を−0.4Vとすることができる。

【0046】

なお、実施の形態1〜3では、MOSFETを例に述べたが、ゲート絶縁膜が酸化膜以外の絶縁膜からなるMISFETにも適用することができる。また、砒化ガリウムや炭化シリコンのような、シリコン以外の半導体材料にも適用することができる。

【0047】

また、ソース/ドレイン領域8の表面を例えばニッケルシリサイド化したり、ソース/ドレイン領域8にエクステンション領域を設けるなど、一般的なCMOSFETに用いられる構造を適宜適用しても構わない。

【図面の簡単な説明】

【0048】

【図1】本発明の実施の形態1にかかるCMOSFET半導体装置の製造工程の断面図である。

【図2】本発明の実施の形態1にかかるCMOSFET半導体装置のゲート電極部分の概略図である。

【図3】本発明の実施の形態2にかかるCMOSFET半導体装置の製造工程の断面図である。

【図4】本発明の実施の形態3にかかるCMOSFET半導体装置の製造工程の断面図である。

【符号の説明】

【0049】

1 シリコン基板、2 シリコン層、3 素子分離領域、4 ゲート絶縁膜、5 第1ゲート金属膜、6 ハードマスク、7 サイドウオール、8 ソース/ドレイン領域、10 PMD層、14 アモルファスシリコン層、20 第2ゲート金属膜、25 金属ゲート配線膜、30 層間絶縁層、100 CMOSFET半導体装置。

【特許請求の範囲】

【請求項1】

第1導電型FETと第2導電型FETとを含むデュアルゲート半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、

該第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、

該第1および第2の電極の上部を該層間絶縁層から露出させる工程と、

該第2の電極の該第1ゲート金属膜を選択的に除去する選択除去工程と、

該第1および第2の電極を覆うように、該層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する堆積工程と、

該第2ゲート金属膜と該ゲート配線膜をパターニングして、該ゲート絶縁膜上に該第1ゲート金属膜、該第2ゲート金属膜、および該ゲート配線膜が順次積層された第1ゲート電極と、該ゲート絶縁膜上に第2ゲート金属膜と該ゲート配線膜が順次積層された第2ゲート電極とを形成するとともに、該第1ゲート電極と該第2ゲート電極とを該ゲート配線膜で接続する工程とを含むことを特徴とするデュアルゲート半導体装置の製造方法。

【請求項2】

第1導電型FETと第2導電型FETとを含むデュアルゲート半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、

該第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、

該第1および第2の電極の上部を該層間絶縁層から露出させる工程と、

該第2の電極の該第1ゲート金属膜を選択的に除去する選択除去工程と、

該第1および第2の電極を覆うように、該層間絶縁層上に、シリコン膜を堆積する堆積工程と、

該シリコン膜を覆うようにニッケル層を形成する工程と、

熱処理により該シリコン膜をニッケルシリサイド膜にする工程と、

少なくとも該ニッケル層をパターニングして、該ゲート絶縁膜上に該第1ゲート金属膜、該ニッケルシリサイド膜、および該ニッケル層が順次積層された第1ゲート電極と、該ゲート絶縁膜上に該ニッケルシリサイド膜および該ニッケル層が順次積層された第2ゲート電極とを形成するとともに、該第1ゲート電極と該第2ゲート電極とを該ニッケル層で接続する工程とを含むことを特徴とするデュアルゲート半導体装置の製造方法。

【請求項3】

上記堆積工程後に、上記シリコン膜をパターニングする工程を含むことを特徴とする請求項2に記載のデュアルゲート半導体装置の製造方法。

【請求項4】

上記第1および第2の電極が、上記半導体基板上に順次積層された、ゲート絶縁膜、第1ゲート金属膜、およびマスク用シリコン膜からなり、

上記選択除去工程が、該マスク用シリコン膜で該第1の電極を保護しながら、該第2の電極の該第1ゲート金属膜を選択的に除去する工程であることを特徴とする請求項1〜3のいずれかに記載のデュアルゲート半導体装置の製造方法。

【請求項5】

上記堆積工程後に行われる工程は、上記半導体基板の温度が500℃以下で行われる工程であることを特徴とする請求項1〜4のいずれかに記載のデュアルゲート半導体装置の製造方法。

【請求項6】

上記第1ゲート金属膜が、TaSiN、TaC、TaN、TiSiN、またはTiNからなることを特徴とする請求項1〜4のいずれかに記載のデュアルゲート半導体装置の製造方法。

【請求項7】

上記第2ゲート金属膜が、TiN、TiAlN、TaN、TaAlN、Ru、Ir、Pt、Ni、Co、W、WN、Mo、MoN、NiSi、およびPtSiからなる群から選択される材料を主成分とすることを特徴とする請求項1または4に記載のデュアルゲート半導体装置の製造方法。

【請求項8】

導電型の異なる2つのFETを含むデュアルゲート半導体装置であって、

半導体基板と、

該半導体基板上に設けられた、ゲート絶縁膜上に順次積層された第1ゲート金属膜、第2ゲート金属膜、およびゲート配線膜を含む第1導電型FETの第1ゲート電極と、該ゲート絶縁膜上に順次積層された第2ゲート金属膜および該ゲート配線膜を含む第2導電型FETの第2ゲート電極と、を有し、

該第1ゲート電極と該第2ゲート電極とが、これらの電極で共通する該ゲート配線膜により電気的に接続されたことを特徴とするデュアルゲート半導体装置。

【請求項9】

更に、上記第1ゲート電極と上記第2ゲート電極とが、これらの電極で共通する上記第2ゲート金属膜により電気的に接続されたことを特徴とする請求項8に記載のデュアルゲート半導体装置。

【請求項10】

上記第1ゲート金属膜が、TaSiN、TaC、TaN、TiSiN、またはTiNからなることを特徴とする請求項8または9に記載のデュアルゲート半導体装置。

【請求項11】

上記第2ゲート金属膜が、TiN、TiAlN、TaN、TaAlN、Ru、Ir、Pt、Ni、Co、W、WN、Mo、MoN、NiSi、およびPtSiからなる群から選択される材料を主成分とすることを特徴とする請求項8または9に記載のデュアルゲート半導体装置。

【請求項1】

第1導電型FETと第2導電型FETとを含むデュアルゲート半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、

該第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、

該第1および第2の電極の上部を該層間絶縁層から露出させる工程と、

該第2の電極の該第1ゲート金属膜を選択的に除去する選択除去工程と、

該第1および第2の電極を覆うように、該層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する堆積工程と、

該第2ゲート金属膜と該ゲート配線膜をパターニングして、該ゲート絶縁膜上に該第1ゲート金属膜、該第2ゲート金属膜、および該ゲート配線膜が順次積層された第1ゲート電極と、該ゲート絶縁膜上に第2ゲート金属膜と該ゲート配線膜が順次積層された第2ゲート電極とを形成するとともに、該第1ゲート電極と該第2ゲート電極とを該ゲート配線膜で接続する工程とを含むことを特徴とするデュアルゲート半導体装置の製造方法。

【請求項2】

第1導電型FETと第2導電型FETとを含むデュアルゲート半導体装置の製造方法であって、

半導体基板を準備する工程と、

該半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、

該第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、

該第1および第2の電極の上部を該層間絶縁層から露出させる工程と、

該第2の電極の該第1ゲート金属膜を選択的に除去する選択除去工程と、

該第1および第2の電極を覆うように、該層間絶縁層上に、シリコン膜を堆積する堆積工程と、

該シリコン膜を覆うようにニッケル層を形成する工程と、

熱処理により該シリコン膜をニッケルシリサイド膜にする工程と、

少なくとも該ニッケル層をパターニングして、該ゲート絶縁膜上に該第1ゲート金属膜、該ニッケルシリサイド膜、および該ニッケル層が順次積層された第1ゲート電極と、該ゲート絶縁膜上に該ニッケルシリサイド膜および該ニッケル層が順次積層された第2ゲート電極とを形成するとともに、該第1ゲート電極と該第2ゲート電極とを該ニッケル層で接続する工程とを含むことを特徴とするデュアルゲート半導体装置の製造方法。

【請求項3】

上記堆積工程後に、上記シリコン膜をパターニングする工程を含むことを特徴とする請求項2に記載のデュアルゲート半導体装置の製造方法。

【請求項4】

上記第1および第2の電極が、上記半導体基板上に順次積層された、ゲート絶縁膜、第1ゲート金属膜、およびマスク用シリコン膜からなり、

上記選択除去工程が、該マスク用シリコン膜で該第1の電極を保護しながら、該第2の電極の該第1ゲート金属膜を選択的に除去する工程であることを特徴とする請求項1〜3のいずれかに記載のデュアルゲート半導体装置の製造方法。

【請求項5】

上記堆積工程後に行われる工程は、上記半導体基板の温度が500℃以下で行われる工程であることを特徴とする請求項1〜4のいずれかに記載のデュアルゲート半導体装置の製造方法。

【請求項6】

上記第1ゲート金属膜が、TaSiN、TaC、TaN、TiSiN、またはTiNからなることを特徴とする請求項1〜4のいずれかに記載のデュアルゲート半導体装置の製造方法。

【請求項7】

上記第2ゲート金属膜が、TiN、TiAlN、TaN、TaAlN、Ru、Ir、Pt、Ni、Co、W、WN、Mo、MoN、NiSi、およびPtSiからなる群から選択される材料を主成分とすることを特徴とする請求項1または4に記載のデュアルゲート半導体装置の製造方法。

【請求項8】

導電型の異なる2つのFETを含むデュアルゲート半導体装置であって、

半導体基板と、

該半導体基板上に設けられた、ゲート絶縁膜上に順次積層された第1ゲート金属膜、第2ゲート金属膜、およびゲート配線膜を含む第1導電型FETの第1ゲート電極と、該ゲート絶縁膜上に順次積層された第2ゲート金属膜および該ゲート配線膜を含む第2導電型FETの第2ゲート電極と、を有し、

該第1ゲート電極と該第2ゲート電極とが、これらの電極で共通する該ゲート配線膜により電気的に接続されたことを特徴とするデュアルゲート半導体装置。

【請求項9】

更に、上記第1ゲート電極と上記第2ゲート電極とが、これらの電極で共通する上記第2ゲート金属膜により電気的に接続されたことを特徴とする請求項8に記載のデュアルゲート半導体装置。

【請求項10】

上記第1ゲート金属膜が、TaSiN、TaC、TaN、TiSiN、またはTiNからなることを特徴とする請求項8または9に記載のデュアルゲート半導体装置。

【請求項11】

上記第2ゲート金属膜が、TiN、TiAlN、TaN、TaAlN、Ru、Ir、Pt、Ni、Co、W、WN、Mo、MoN、NiSi、およびPtSiからなる群から選択される材料を主成分とすることを特徴とする請求項8または9に記載のデュアルゲート半導体装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2009−164527(P2009−164527A)

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願番号】特願2008−3140(P2008−3140)

【出願日】平成20年1月10日(2008.1.10)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願日】平成20年1月10日(2008.1.10)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]