デュアル近接スイッチ、および制御方法、遊技球の通過方向検出システム、遊技機、並びにプログラム

【課題】不正や異常を適切に検出して、遊技球を適切に計数させる。

【解決手段】正常通過判定部162は、デュアル近接スイッチ101の近接スイッチ161−1,161−2の検出結果に基づいて、正常な検出順序で検出されているか否かに基づいて、遊技球の正常通過を判定し、判定結果を正常通過判定信号として出力する。異常判定部163は、デュアル近接スイッチ101の近接スイッチ161−1,161−2の検出結果に基づいて、異常な検出順序で検出されているか否かを示す、異常検出信号を出力する。出力合成部153は、正常通過判定信号、および異常検出信号に基づいて、3種類の電圧からなる検出信号を出力する。本発明は、遊技機に適用することができる。

【解決手段】正常通過判定部162は、デュアル近接スイッチ101の近接スイッチ161−1,161−2の検出結果に基づいて、正常な検出順序で検出されているか否かに基づいて、遊技球の正常通過を判定し、判定結果を正常通過判定信号として出力する。異常判定部163は、デュアル近接スイッチ101の近接スイッチ161−1,161−2の検出結果に基づいて、異常な検出順序で検出されているか否かを示す、異常検出信号を出力する。出力合成部153は、正常通過判定信号、および異常検出信号に基づいて、3種類の電圧からなる検出信号を出力する。本発明は、遊技機に適用することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デュアル近接スイッチ、および制御方法、遊技球の通過方向検出システム、遊技機、並びにプログラムに関し、特に、不正を抑制しつつ、適切に遊技球の通過を検出できるようにしたデュアル近接スイッチ、および制御方法、遊技球の通過方向検出システム、遊技機、並びにプログラムに関する。

【背景技術】

【0002】

これまでの遊技球を用いた遊技機および計数機おける、遊技球を検出する直流2線式スイッチに対する不正行為を防止する構成としては、直流2線式スイッチとインタフェース回路間の断線異常、短絡異常、または電源電圧の低下異常といった不正行為との因果関係が知られている異常を検出し、報知するものが提案されている(特許文献1参照)。

【0003】

ところが、昨今においては、これまでの不正行為に加え、遊技球が直流2線式スイッチを通過している際に、強力な低周波近傍電磁界を照射し、カウント数を増やす不正行為や、セルと呼ばれる道具を用いて、直流2線式スイッチの検出部に検出媒体を往復させて、遊技球のカウント数を増やす、リフティングと呼ばれる新たな不正行為が確認されている。

【0004】

これらの新たな不正行為は、従来のインタフェース回路では対策できず、対策には従来のインタフェース回路とは異なる信号処理(特許文献2乃至4参照)が必要となっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第4332797号公報

【特許文献2】特許第2817021号公報

【特許文献3】特開2001−054618号公報

【特許文献4】特開2001−129214号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した特許文献2乃至4の技術だけでは、断線異常、短絡異常、または電源低下の異常を検出できない。従って、これまでの構成により、断線異常、短絡異常、または電源低下の異常を検出しつつ、新たな不正行為を対策するためには、新たに対策する不正行為の種類だけ、CPU(Central Processing Unit)のポート数を増やしてセンサ数を増やし、処理する信号数を増やす必要があるため、処理に係る装置規模とソフトウェアによる処理負荷を増大させてしまう恐れがあった。

【0007】

また、リフティングによる不正での異常が解消された際に、直ちに復帰できないことや、低周波近傍電磁界のような外乱によりセンサ出力が同時に立ち上がった際、不正を検出できないといった誤動作を生じることがあった。

【0008】

本発明はこのような状況に鑑みてなされたものであり、特に、断線異常、短絡異常、および電源異常といった異常に加えて、必要に応じて低周波近傍電磁界やリフティングによる不正行為への対策を必要に応じて適正に実現しつつ、信号処理負担を低減できるようにするものである。

【課題を解決するための手段】

【0009】

本発明の一側面のデュアル近接スイッチは、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含む。

【0010】

前記正常通過判定手段、および前記異常判定手段には、それぞれ少なくとも1個の保持回路を含ませるようにすることができ、前記正常通過判定手段、および前記異常判定手段には、前記保持回路の動作に基づいて、それぞれ前記正常通過検出信号、および前記異常検出信号を出力させるようにすることができ、前記第1の近接スイッチ、および前記第2の近接スイッチが、所定の検出状況となった場合、前記保持回路をリセットするリセット手段をさらに含ませるようにすることができる。

【0011】

前記リセット手段には、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない状態の場合、前記保持回路をリセット、または、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない期間全域において、前記保持回路をクリアさせるようにすることができる。

【0012】

前記異常検出信号が出力された場合、前記正常通過検出信号を、正常でないことを示す所定の状態に固定して出力する出力信号固定手段をさらに含ませるようにすることができる。

【0013】

前記正常通過検出信号が検出された場合、第1の電圧値を出力し、前記正常通過検出信号、および、異常検出信号が検出されない場合、第2の電圧値を出力し、前記異常検出信号が検出された場合、第3の電圧値を出力する出力合成手段をさらに含ませるようにすることができる。

【0014】

前記第1乃至3の電圧値は、いずれも接地電位より高く、電源電位よりも低い中間電位とすることができ、いずれも異なる電位とすることができる。

【0015】

請求項1乃至4のいずれかに記載の1個のデュアル近接スイッチを含ませるようにすることができ、前記制御回路には、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を受け付けるようにさせることができる。

【0016】

本発明の遊技球の通過方向検出システムには、請求項1乃至6のいずれかに記載の1個のデュアル近接スイッチと、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を信号処理して、前記制御回路に供給するインタフェース回路とを含ませるようにすることができ、前記制御回路には、前記インタフェース回路から伝送される前記正常通過検出信号、および前記異常検出信号の信号処理結果を受け付けるようにさせることができる。

【0017】

本発明の遊技球の通過方向検出システムには、請求項5または6のいずれかに記載のデュアル近接スイッチと、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を信号処理して、前記制御回路に供給するインタフェース回路と、前記制御回路を含ませるようにすることができ、前記第3の所定の電圧値には、前記第1の電圧値、および前記第2の電圧値のいずれか低い電位の電圧値より低く、かつ、接地電位よりも高く設定されるようにすることができ、前記インタフェース回路には、前記正常通過検出信号の状態を比較判定する第1の比較回路と、前記異常検出信号の状態を比較判定する第2の比較回路とを含ませるようにすることができる。

【0018】

本発明の遊技球の通過方向検出システムにおける前記インタフェース回路には、短絡事故を検出する短絡事故検出手段と、前記断線事故を検出する断線事故検出手段と、前記電源異常を検出する電源異常検出手段とのうち、少なくとも1つをさらに含ませるようにすることができる。

【0019】

本発明の遊技機には、請求項1乃至6のいずれかに記載の1個のデュアル近接スイッチ、または、請求項7乃至9のいずれかに記載の遊技球の通過方向検出システムのうち、いずれか1個を含ませるようにすることができる。

【0020】

本発明の一側面のデュアル近接スイッチの制御方法は、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含むデュアル近接スイッチの制御方法であって、前記正常通過判定手段における、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定ステップと、前記異常判定手段における、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定ステップとを含む。

【0021】

本発明の一側面のプログラムは、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含むデュアル近接スイッチを制御するコンピュータに、前記正常通過判定手段における、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定ステップと、前記異常判定手段における、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定ステップとを含む処理を実行させる。

【0022】

本発明の一側面のデュアル近接スイッチにおいては、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチが含まれ、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果が後続の制御回路に伝達され、前記第1の近接スイッチにより先に通過の検出が開始され、かつ、遅れて前記第2の近接スイッチにより通過の検出が開始される検出順序であるか否かが判定され、その判定結果が、前記第1の近接スイッチによる先に通過の検出が開始され、かつ、遅れて前記第2の近接スイッチによる通過の検出が開始される検出順序である場合、1個の正常通過検出信号が出力され、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かが判定され、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号が出力される。

【0023】

すなわち、本発明の一側面のデュアル近接スイッチにおける、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチとは、例えば、遊技球の通過方向と共に通過を検出する遊技機に設けられる近接スイッチであり、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段とは、例えば、正常通過判定部であり、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とは、異常判定部である。

【0024】

すなわち、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、正常通過検出部により、1個の正常通過検出信号が出力されるので、正常に遊技球が通過したことが、制御回路に通知され、遊技球数の計数が可能となる。また、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、異常判定部より異常検出信号が出力されることになるので、第1の近接スイッチ、および第2の近接スイッチに対してリフティングによる不正がなされたか、または、低周波近傍電磁界による不正がなされたことが通知される。

【0025】

結果として、デュアル近接スイッチから直接、低周波近傍電磁界やリフティングによる不正の有無を示す異常検出信号と、遊技球の通過を検出する正常通過検出信号とを供給することができるので、後段の信号処理を容易なものとしつつ、不正を抑制しつつ適正に遊技球の通過を検出することが可能になる。

【発明の効果】

【0026】

本発明によれば、後段の信号処理を容易なものとしつつ、不正や異常を適切に検出して、遊技球を適切に計数することが可能となる。

【図面の簡単な説明】

【0027】

【図1】デュアル近接スイッチの構成例を説明する図である。

【図2】図1のデュアル近接スイッチの動作を説明する図である。

【図3】デュアル近接スイッチに用いられる本発明を適用したインタフェースシステムを説明する図である。

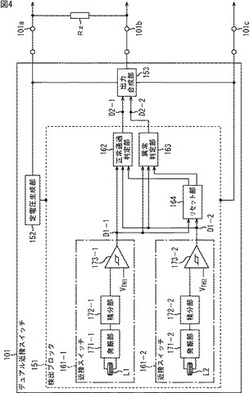

【図4】図3のデュアル近接スイッチの構成例を説明する図である。

【図5】図4の正常通過判定部、異常判定部、およびリセット部の回路構成例を説明する図である。

【図6】図3のインタフェース回路の構成例を説明する図である。

【図7】図3のデュアル近接スイッチの検出処理を説明するフローチャートである。

【図8】正常通過時における図3のデュアル近接スイッチの検出処理を説明する図である。

【図9】順序異常時における図3のデュアル近接スイッチの検出処理を説明する図である。

【図10】低周波近傍電磁界到来時における図3のデュアル近接スイッチの検出処理を説明する図である。

【図11】断線状態における図3のデュアル近接スイッチの検出処理を説明する図である。

【図12】短絡状態における図3のデュアル近接スイッチの検出処理を説明する図である。

【図13】図3のI/F回路における信号処理を説明するフローチャートである。

【図14】図3のCPUにおける計数処理を説明するフローチャートである。

【図15】図3のCPUにおける計数処理を説明する図である。

【図16】図3のCPUにおける計数処理を説明する図である。

【図17】図3のCPUにおける計数処理を説明する図である。

【図18】その他のインタフェースシステムを説明する図である。

【図19】図18のI/F回路の構成例を説明する図である。

【図20】正常通過時における図19のI/F回路による動作を説明する図である。

【図21】順序異常時における図19のI/F回路による動作を説明する図である。

【図22】低周波近傍電磁界到来時における図19のI/F回路による動作を説明する図である。

【図23】断線状態における図19のI/F回路による動作を説明する図である。

【図24】短絡状態における図19のI/F回路による動作を説明する図である。

【図25】図18のCPUにおける計数処理を説明するフローチャートである。

【図26】さらにその他のデュアル近接スイッチの構成例を示す図である。

【図27】図26のデュアル近接スイッチの出力合成部における出力合成処理を説明するフローチャートである。

【図28】正常通過時における図26のデュアル近接スイッチの出力合成部における出力合成処理を説明する図である。

【図29】順序異常時における図26のデュアル近接スイッチの出力合成部における出力合成処理を説明する図である。

【図30】低周波近傍電磁界到来時における図26のデュアル近接スイッチの出力合成部における出力合成処理を説明する図である。

【図31】汎用のパーソナルコンピュータを説明する図である。

【発明を実施するための形態】

【0028】

以下に本発明の実施の形態を説明するが、本発明の構成要件と、発明の詳細な説明に記載の実施の形態との対応関係を例示すると、次のようになる。この記載は、本発明をサポートする実施の形態が、発明の詳細な説明に記載されていることを確認するためのものである。従って、発明の詳細な説明中には記載されているが、本発明の構成要件に対応する実施の形態として、ここには記載されていない実施の形態があったとしても、そのことは、その実施の形態が、その構成要件に対応するものではないことを意味するものではない。逆に、実施の形態が構成要件に対応するものとしてここに記載されていたとしても、そのことは、その実施の形態が、その構成要件以外の構成要件には対応しないものであることを意味するものでもない。

【0029】

すなわち、本発明の一側面のデュアル近接スイッチ(例えば、図4のデュアル近接スイッチ101)は、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチ(例えば、図4の近接スイッチ161−1,161−2)を含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段(例えば、図4の正常通過判定部162)と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段(例えば、図4の異常判定部163)とを含む。

【0030】

前記正常通過判定手段、および前記異常判定手段には、それぞれ少なくとも1個の保持回路(例えば、図5のフリップフロップ回路FF1乃至FF4)を含ませるようにすることができ、前記正常通過判定手段、および前記異常判定手段には、前記保持回路の動作に基づいて、それぞれ前記正常通過検出信号、および前記異常検出信号を出力させるようにすることができ、前記第1の近接スイッチ、および前記第2の近接スイッチが、所定の検出状況となった場合、前記保持回路をリセットするリセット手段(例えば、図4のリセット部164)をさらに含ませるようにすることができる。

【0031】

前記リセット手段(例えば、図4のリセット部164)には、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない状態の場合、前記保持回路をリセット、または、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない期間全域において、前記保持回路をクリアさせるようにすることができる。

【0032】

前記異常検出信号が出力された場合、前記正常通過検出信号を、正常でないことを示す所定の状態に固定して出力する出力信号固定手段(例えば、図26の出力信号固定部302)をさらに含ませるようにすることができる。

【0033】

前記正常通過検出信号が検出された場合、第1の電圧値を出力し、前記正常通過検出信号、および、異常検出信号が検出されない場合、第2の電圧値を出力し、前記異常検出信号が検出された場合、第3の電圧値を出力する出力合成手段(例えば、図4の出力合成部153)をさらに含ませるようにすることができる。

【0034】

本発明の遊技球の通過方向検出システムには、請求項5または6のいずれかに記載のデュアル近接スイッチと、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を信号処理して、前記制御回路に供給するインタフェース回路と、前記制御回路を含ませるようにすることができ、前記第3の所定の電圧値には、前記第1の電圧値、および前記第2の電圧値のいずれか低い電位の電圧値より低く、かつ、接地電位よりも高く設定されるようにすることができ、前記インタフェース回路には、前記正常通過検出信号の状態を比較判定する第1の比較回路(例えば、図19の比較部221)と、前記異常検出信号の状態を比較判定する第2の比較回路(例えば、図19の比較部261)とを含ませるようにすることができる。

【0035】

本発明の遊技球の通過方向検出システムにおける前記インタフェース回路には、短絡事故を検出する短絡事故検出手段(例えば、図6の短絡検知部223)と、前記断線事故を検出する断線事故検出手段(例えば、図6の断線検知部222)と、前記電源異常を検出する電源異常検出手段(例えば、図6の電源監視部202)とのうち、少なくとも1つをさらに含ませるようにすることができる。

【0036】

本発明の一側面のデュアル近接スイッチの制御方法は、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含むデュアル近接スイッチの制御方法であって、前記正常通過判定手段における、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定ステップ(例えば、図7のステップS16)と、前記異常判定手段における、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定ステップ(例えば、図7のステップS18)とを含む。

【0037】

以下、本発明を実施するための形態(以下、実施の形態という)について説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態(デュアル近接スイッチにおいて正常通過検出信号と異常検出信号を出力する構成例)

2.第2の実施の形態(インタフェース回路のその他の構成例)

3.第3の実施の形態(デュアル近接スイッチのその他の構成例)

【0038】

<1.第1の実施の形態>

[本発明を適用したデュアル近接スイッチの一実施の形態の構成例]

図1は、本発明を適用したインタフェース回路に遊技球の検出信号を供給するデュアル近接スイッチの構成例を示す断面図を示している。

【0039】

図1のデュアル近接スイッチ1においては、遊技球と略同径の貫通孔21が設けられており、遊技球P1乃至P3は、遊技球P1,P2,P3の順序で、図中の矢印で示される順方向に貫通孔21の入口側11から出口側12に向けて通過するように構成されている。尚、遊技球P1乃至P3について、特に区別する必要がない場合、単に遊技球Pと称するものとし、その他の複数存在する構成についても同様に称するものとする。

【0040】

また、貫通口21には、貫通口21と同軸に、入口側11から出口側12に向かって順に検出コイルL1,L2が設けられている。検出コイルL1,L2は貫通口21と同軸で、かつ貫通口21の外周部に巻回されてる。

【0041】

2つの検出コイルL1およびL2は、例えば、遊技球Pの直径(例えば、11mm)の1/4の間隔をおいて配置されている。尚、この間隔は、遊技球Pの直径の1/4に限るものではなく、検出コイルL1およびL2が、同一の遊技球の検出の開始タイミング、および終了タイミングが異なるようにできて、かつ、同時に検出している状態を含むようにできる間隔であれば、別の間隔であってもよいものである。

【0042】

このように、デュアル近接スイッチ1においては、貫通孔21の入口側11における検出コイルL1を含む第1の近接スイッチと、出口側12の検出コイルL2を含む第2の近接スイッチとの2系統の近接スイッチが内蔵されている。

【0043】

[デュアル近接スイッチの動作]

後述する本発明の遊技球を計数するインタフェースシステムは、遊技球P1乃至P3が貫通孔21を通過することにより、出力される第1の近接スイッチの検出信号S1と第2の近接スイッチの検出信号S2のタイミングを比較することで、1個の遊技球が正規の順方向に通過したか否かを判別し、順方向に通過した場合にのみ計数する。

【0044】

例えば、上述したように、2つの検出コイルL1およびL2が、遊技球Pの直径(例えば、11mm)の1/4の距離だけ離して配置される場合、遊技球P1乃至P3が順次、図1の矢印で示される順方向に貫通孔21を通過すると、第1の近接スイッチの検出信号S1と、第2の近接スイッチの検出信号S2は、図2の波形図で示されるように検出されることになる。図2においては、上段に検出信号S1の波形が示されており、下段に検出信号S2の波形が示されており、いずれも横軸が時間方向である。

【0045】

すなわち、図2の波形図で示されるように、検出信号S1は、時刻TP1において、Low信号からHi信号に立上り、時刻TP3においてHi信号からLow信号に立下がっている。同様に、検出信号S2は、時刻TP2において、Hi信号に立上り、時刻TP4において、Low信号に立下がっている。

【0046】

このように、デュアル近接スイッチ1は、例えば、遊技球Pが順方向に通過するとき、図2で示されるような、検出信号S1,S2に基づいた出力信号を、後述するI/F回路102(図3)に対して順次出力する。

【0047】

[本発明を適用したデュアル近接スイッチを用いたインタフェースシステムの構成例]

次に、図3を参照して、本発明を適用したデュアル近接スイッチを用いたインタフェースシステムの構成例について説明する。

【0048】

インタフェースシステムは、デュアル近接スイッチ101−1乃至101−7、電源VS、インタフェース(I/F)回路102、電源Vcc、CPU103、発報部104、および計数部105を備えている。すなわち、本発明のインタフェースシステムは、例えば、遊技機、または計数機内における遊技球の計数に係る処理を担うものである。

【0049】

デュアル近接スイッチ101(101−1乃至101−7)は、図1,図2を参照して説明したものとは異なるものであり、図4,図5を参照して詳細は後述するが、電源VSより電力供給を受けて、遊技球の通過を検出し、検出結果として、上述した2種類の検出信号S1,S2に基づいた出力信号をI/F回路102に出力する。

【0050】

インタフェース(I/F)回路102は、デュアル近接スイッチ101からの出力信号を受け付けて、所定の信号処理を施して、CPU103に供給する。

【0051】

I/F回路102は、I/F入力部111、および端子VS,A1乃至A7,GND,Vcc,Y1乃至Y7,Eを備えている。端子VSは、デュアル近接スイッチ101に供給する電源VSの電圧を監視する機能を含む。

【0052】

端子A1乃至A7は、デュアル近接スイッチ101からの出力信号を受け付ける。端子GNDは、接地端子である。

【0053】

端子Y1乃至Y7は、それぞれデュアル近接スイッチ101の出力信号に基づいた遊技球の通過が検出されているか否か、または異常を検出しているか否かを示す処理出力信号をCPU103に供給する。端子Eは、デュアル近接スイッチ101の検出信号に基づいた、デュアル近接スイッチ101の動作異常および不正異常の有無を示す異常検出信号を出力する。

【0054】

尚、I/F回路102の詳細な構成は、図6を参照して、後述するものとする。

【0055】

CPU103は、インタフェースシステムの全体の動作を管理する。CPU103は、カウント部121、異常判定部122、特定部123、異常種別判定部124、タイマ125、および発報出力部126を備えている。

【0056】

カウント部121は、端子Y1乃至Y7の処理出力信号に基づいて、遊技球の通過を認識し、遊技球数をカウントする信号を計数部105に供給する。計数部105は、この信号に基づいて遊技球数をカウントする。

【0057】

異常判定部122は、端子Eからの異常検出信号に基づいて、デュアル近接スイッチ101−1乃至101−7の異常の有無を判定する。特定部123は、端子Y1乃至Y7からの処理出力信号、または端子Eからの異常検出信号に基づいて、いずれのデュアル近接スイッチ101において遊技球の通過が検出されたか、または、異常が発生したのかを特定する。異常種別判定部124は、端子Eからの異常検出信号と、タイマ125により計時される時間に基づいて、デュアル近接スイッチ101に発生した異常の種別を判定する。発報出力部126は、異常が検出された場合、いずれのデュアル近接スイッチ101において、発生した異常の種別を示す情報を発報部104に出力し、発報させる。

【0058】

[デュアル近接スイッチ101の構成例]

次に、図4を参照して、デュアル近接スイッチ101の構成例について説明する。

【0059】

デュアル近接スイッチ101は、検出ブロック151、定電圧生成部152、および出力合成部153を備えている。

【0060】

検出ブロック151は、図1におけるデュアル近接スイッチ1と同一機能の近接スイッチ161−1,161−2に加えて、正常通過判定部162、異常判定部163、およびリセット部164を備えており、定電圧生成部152より電力供給を受けて、端子101cを介して接地電位GNDに接続されている。検出ブロック151は、遊技球が正常に通過しているか否かを示す正常通過検出信号、および異常が検出されているか否かを示す異常検出信号を出力する。より詳細には、近接スイッチ161−1,161−2は、いずれも同一の構成であり、それぞれ検出コイルL1,L2、発振部171−1,171−2、積分部172−1,172−2、および比較部173−1,173−2を備えている。検出コイルL1,L2は、図1を参照して説明した検出コイルL1,L2と同一のものである。

【0061】

発振部171−1,171−2は、それぞれ検出コイルL1,L2の遊技球の通過に伴って、発振信号を生成し、積分部172−1,172−2に供給する。積分部172−1,172−2は、それぞれ発振信号を積分して比較部173−1,173−2に出力する。比較部173−1,173−2は、積分部172−1,172−2より供給されてくる波形に基づいて、それぞれ所定の閾値VTH1,VTH2とを比較する。そして、比較部173−1,173−2は、閾値VTH1,VTH2よりも高い場合、Lowレベルの、高くない場合、Hiレベルの弁別信号からなる検出信号D1−1,D1−2を正常通過判定部162、異常判定部163、およびリセット部164に出力する。尚、この検出信号D1−1,D1−2は、それぞれ図2を参照して説明した、検出信号S1,S2と同一のものである。

【0062】

正常通過判定部162は、検出信号D1−1,D1−2の波形に基づいて、遊技球が正常に通過したか否かを判定し、判定結果に対応するHiの信号、またはLowの信号からなる正常通過判定信号D2−1を出力合成部153に出力する。正常通過判定部162は、リセット部164より供給されてくるリセット信号により正常通過判定信号を遊技球の通過が非検出の状態にリセットする。

【0063】

異常判定部163は、検出信号D1−1,D1−2の波形に基づいて、異常が発生したか否かを判定し、判定結果に対応するHiの信号、またはLowの信号からなる異常判定信号D2−2を出力合成部153に出力する。異常判定部163は、リセット部164より供給されてくるリセット信号により異常判定信号を異常が非検出の状態にリセットする。

【0064】

リセット部164は、検出信号D1−1,D1−2が、いずれも遊技球の通過を非検出の状態のとき、リセット信号を発生し、正常通過判定部162および異常判定部163に供給し、それぞれ正常通過判定信号D2−1、および異常判定信号D2−2を非検出の状態にリセットする。

【0065】

定電圧生成部152は、端子101aを介して電源VSより供給されてくる電力に基づいて、所定の電圧を維持して、検出ブロック151に電力を供給する。

【0066】

出力合成部153は、端子101aを介して電源VSから電力供給を受けて、検出ブロック151より供給されてくる正常通過判定信号D2−1、および異常判定部D2−2に基づいて、出力検出信号を生成して、出力端子101bよりI/F回路102に供給する。また、出力合成部153は、端子101cを介して接地電位GNDに接続されている。

【0067】

尚、端子101a、および端子101b間には、調整抵抗として、抵抗Rzが設けられている。

【0068】

[正常通過判定部162、異常判定部163、およびリセット部164の回路構成例]

次に、図5を参照して、正常通過判定部162、異常判定部163、リセット部164、および出力合成部153の回路構成例について説明する。

【0069】

正常通過判定部162は、フリップフロップ回路FF1,FF2、インバータI11、およびアンド回路AND1乃至3により構成されている。異常判定部163は、オア回路OR1乃至3、およびフリップフロップ回路FF3,FF4により構成されている。

【0070】

正常通過判定部162のフリップフロップ回路FF1の入力端子D1には、近接スイッチ161−1からの検出信号が入力される。クロック端子CLK1には、近接スイッチ161−2からの検出信号が入力される。プリセット端子PR1には、リセット部164のインバータI21の出力信号が入力される。クリア端子CLR1は、電源Vccに接続されている。正出力端子Q1は、クロック端子CLK1にHiの信号が供給されるタイミングで、入力端子D1に入力されている信号をアンド回路AND2の入力端子に出力する。負出力端子Q’1は、クロック端子CLK1にHiの信号が供給されるタイミングで、入力端子D1に入力されている信号を反転出力に変換して、オア回路OR1の入力端子に出力する。尚、図5においては、負出力端子には、符号Qの上部にバーで表記されているが、本明細書の記載においては、バーに代えて「’」を用いるものとする。

【0071】

また、正常通過判定部162のフリップフロップ回路FF2の入力端子D2には、近接スイッチ161−2からの検出信号が入力される。クロック端子CLK2には、近接スイッチ161−1からの弁別信号が入力される。プリセット端子PR2は、電源Vccに接続されている。クリア端子CLR2には、リセット部164のインバータI21の出力信号が入力される。正出力端子Q2は、クロック端子CLK2にHiの信号が供給されるタイミングで、入力端子D2に入力されている信号をオア回路OR1の入力端子に出力する。負出力端子Q’2は、クロック端子CLK2にHiの信号が供給されるタイミングで、入力端子D2に入力されている信号を反転信号に変換して、アンド回路AND2の入力端子に出力する。

【0072】

異常判定部163のインバータI1は、近接スイッチ161−1からの検出信号を、反転信号に変換して、フリップフロップ回路FF3の入力端子D3、およびフリップフロップ回路FF4のクロック端子CLK4に入力する。また、インバータI2は、近接スイッチ161−2からの検出信号を、反転信号に変換して、フリップフロップ回路FF3のクロック端子CLK3、およびフリップフロップ回路FF4の入力端子D4に入力する。

【0073】

フリップフロップ回路FF3のプリセット端子PR3には、リセット部164のインバータI21の出力信号が入力される。クリア端子CLR3は、電源Vccに接続されている。負出力端子Q’3は、クロック端子CLK3にLowの信号が供給されたタイミングで、入力端子D3に入力されている信号を反転信号に変換して、オア回路OR2の入力端子に出力する。

【0074】

また、異常判定部163のフリップフロップ回路FF4のクリア端子CLR4には、リセット部164のインバータI21の出力信号が入力される。プリセット端子PR4は、電源Vccに接続されている。正出力端子Q4は、クロック端子CLK4にLowの信号が供給されたタイミングで、入力端子D4に入力されている信号をオア回路OR2の入力端子に出力する。

【0075】

正常通過判定部162のインバータI11は、オア回路OR3より出力される信号を、反転信号に変換してアンド回路AND1の入力端子に出力する。アンド回路AND1は、インバータI11の出力信号と、近接スイッチ161−2の検出信号とを比較し、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をアンド回路AND3の入力端子に出力する。アンド回路AND2は、フリップフロップ回路FF1の正出力端子Q1の出力信号と、フリップフロップ回路FF2の負出力端子Q’2の出力信号とを比較して、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をアンド回路AND3の入力端子に出力する。アンド回路AND3は、アンド回路AND1,AND2の出力信号を比較し、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号を正常通過判定信号D2−1として出力合成部153に出力する。

【0076】

オア回路OR1は、フリップフロップ回路FF1の負出力端子Q’1の出力信号と、フリップフロップ回路FF2の正出力端子Q2の出力信号とを比較して、いずれかがHiである場合、Hiの信号を、それ以外の場合、Lowの信号をオア回路OR3の入力端子に出力する。オア回路OR2は、フリップフロップ回路FF3の負出力端子Q’3の出力信号と、フリップフロップ回路FF4の正出力端子Q4の出力信号とを比較して、いずれかがHiである場合、Hiの信号を、それ以外の場合、Lowの信号をオア回路OR3の入力端子に出力する。オア回路OR3は、オア回路OR1,OR2の出力信号を比較して、いずれかがHiである場合、Hiの信号を、それ以外の場合、Lowの信号を異常検出信号D2−2として出力合成部153に出力する。

【0077】

リセット部164のインバータI22,I23は、近接スイッチ161−1,161−2の検出信号を反転信号に変換してアンド回路AND12に出力する。アンド回路AND12は、インバータI22,I23の出力信号を比較して、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をアンド回路AND11の入力端子に出力する。アンド回路AND11は、オア回路OR3の出力信号と、アンド回路AND12の出力信号とを比較して、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をインバータI21に出力する。インバータI21は、アンド回路AND11の出力信号を反転信号に変換して、フリップフロップ回路FF1,FF3のプリセット端子PR1,PR3、およびフリップフロップ回路FF2,FF4のクリア端子CLR2,CLR4に出力する。

【0078】

すなわち、図2の波形図で示されるように、遊技球が順方向で通過すれば、近接スイッチ161−1の検出信号である比較部173−1の弁別信号が立ち上がるタイミングでは、近接スイッチ161−2の検出信号である比較部173−2の弁別信号はLowの信号であり、逆に、近接スイッチ161−2の検出信号である比較部173−2の弁別信号が立ち上がるタイミングでは、近接スイッチ161−1の検出信号である比較部173−1の弁別信号はHiの信号となるため、フリップフロップ回路FF1の正出力端子Q1からはHiの信号が出力され続け、フリップフロップ回路FF2の負出力端子Q’2からはHiの信号が出力され続けることになる。

【0079】

同様に、近接スイッチ161−1の検出信号である比較部173−1の弁別信号が立ち下がるタイミングでは、近接スイッチ161−2の検出信号である比較部173−2の弁別信号はHiの信号であり、逆に、近接スイッチ161−2の検出信号である比較部173−2の弁別信号が立ち下がるタイミングでは、近接スイッチ161−1の検出信号である比較部173−1の弁別信号はLowの信号となるため、フリップフロップ回路FF3の負出力端子Q’3からはLowの信号が出力され続け、フリップフロップ回路FF4の正出力端子Q4からはLowの信号が出力され続けることになる。

【0080】

結果として、順方向に遊技球が通過している状態であれば、アンド回路AND2は、常にHiの信号を出力し続けるので、オア回路OR3から異常検出信号であるHiの信号が供給されて、インバータI11がLowの信号を出力をしていない限り、近接スイッチ161−2の検出信号である比較部173−2の弁別信号の出力波形が、アンド回路AND3より出力される。また、上述した比較部173−1,173−2の立上りおよび立下りの条件が満たされない場合、オア回路OR1,OR2のいずれかがHiの信号となるため、オア回路OR3は、Hiの信号の異常検出信号を出力することになる。

【0081】

フリップフロップ回路FF1乃至FF4は、一旦、異常があったものと判定される信号を記憶すると、その状態が維持されてしまうため、プリセット、またはクリア操作がない限り異常検出信号が出力され続け、遊技球の通過が非検出の状態が維持されてしまう。しかしながら、近接スイッチ161−1,161−2の検出信号である比較部173−1,173−2からの弁別信号がいずれも非検出状態になると、リセット部164のインバータI22,I23からはいずれもHiの信号が出力される。また、オア回路OR3は、異常検出信号であるHiの信号を出力し続けているため、アンド回路AND11は、Hiの信号を出力する。これにより、インバータI21は、Lowの信号をリセット信号として、フリップフロップ回路FF1,FF3のプリセット端子PR1,PR3、およびフリップフロップ回路FF2,FF4のクリア端子CLR2,CLR4に出力する。結果として、比較部173−1,173−2からの弁別信号がいずれも非検出状態になれば、フリップフロップ回路FF1乃至FF4がプリセット、またはクリアされることにより、異常検出信号の出力が停止されて、通常の状態にリセットされる。

【0082】

出力合成部153は、第1電位発生部181、第2電位発生部182、および第3電位発生部183より構成されている。第1電位発生部181は、トランジスタTR11,TR12、および抵抗R11より構成されている。トランジスタTR11のコレクタが出力端子101b、ダイオードD1のアノード、およびツェナーダイオードZDのカソードに接続されており、エミッタが抵抗R11の一方の端部、およびトランジスタTR12のベースに接続されている。また、トランジスタTR11のベースは、トランジスタTR12のコレクタ、および抵抗Raを介して端子101aに接続されている。トランジスタTR12のベースは、トランジスタTR11のエミッタ、および抵抗R11の一方の端部に接続され、エミッタは端子101cを介して接地電位GNDに接続されており、コレクタは、トランジスタTR11のベース、および抵抗Raを介して端子101aに接続されている。抵抗R11は、一方の端部がトランジスタTR11のエミッタ、およびトランジスタTR12のベースに接続され、他方の端部が端子101cに接続されている。

【0083】

すなわち、第1電位発生部181においては、トランジスタTR11が常にオンの状態となるため、抵抗R11により調整された第1電位V1が端子101bより出力される。尚、この第1電位V1は、後述する高位反転電圧である。

【0084】

第2電位発生部182は、インバータI51、トランジスタTR21、ツェナーダイオードZD、および抵抗R21より構成されている。インバータI51は、検出ブロック151における正常通過判定部162からの正常通過判定信号D2−1を反転出力に変換してトランジスタTR21のベース、および抵抗R21の一方の端部に出力する。トランジスタTR21のベースは、正常通過判定部162のアンド回路AND3の出力端子、および抵抗R21の一方の端部に接続され、エミッタは、抵抗R21の他方の端部、および接地電位GNDに接続され、コレクタは、ツェナーダイオードZDのアノードに接続されている。ツェナーダイオードZDのアノードは、トランジスタTR21のコレクタに接続されており、カソードは、ダイオードD1のアノード、トランジスタTR11のコレクタ、および端子101bに接続されている。

【0085】

すなわち、第1電位発生部181は、正常通過判定信号D2−1がHiの信号であるとき、インバータI51からの反転出力によりトランジスタTR21がオフとなり、ツェナーダイオードZDのツェナー電位ZDによる電圧降下がなくなるため、端子101bより第1電位発生部181に定電流が生成され、抵抗Rzの調整により第1電位V1が出力される。一方、第2電位発生部182は、正常通過判定信号D2−1がLowの信号であるとき、インバータI51からの反転出力によりトランジスタTR21がオンとなり、ツェナーダイオードZDのツェナー電位ZDにより決定される第2電位V2が端子101bより出力される。尚、この第2電位V2が、後述する低位反転電圧である。

【0086】

第3電位発生部183は、ダイオードD1,D2、トランジスタTR31、および抵抗R31より構成されている。トランジスタTR31は、コレクタがダイオードD2のカソードに接続され、エミッタが接地電位GND、および抵抗R31の他方の端部と接続され、ベースが抵抗R31の一方の端部、およびオア回路OR3の出力端子に接続されている。抵抗R31は、一方の端部がトランジスタTR31のベース、およびオア回路OR3の出力端子に接続されており、他方の端部がトランジスタTR31のエミッタおよび接地電位GNDに接続されている。ダイオードD1,D2は、カスケードに接続されており、D2のカソードは、トランジスタTR31のコレクタに接続され、ダイオードD1のアノードは、ツェナーダイオードZDのカソード、トランジスタTR11のコレクタ、およびベース、トランジスタTR12のコレクタ、および端子101cに接続されている。

【0087】

すなわち、第3電位発生部183は、異常が検出されたことを示す異常検出信号が供給されるとトランジスタTR31がオンの状態となる。この結果、第1電位発生部181、および第2電位発生部182の動作とは無関係にダイオードD1,D2による電圧降下が発生し、第1電位V1よりダイオードD1,D2分の電圧降下により第2電位V2よりも低い、第3電位V3が端子101bより出力される。

【0088】

[I/F回路102の構成例]

次に、図6を参照して、I/F回路102の構成例について説明する。尚、図6においては、1個のデュアル近接スイッチ101−1の接続に必要とされる構成例のみが示されており、端子VS,A1乃至A7,GND,Vcc,Y1乃至Y7,Eのみが示され、その他の構成については、省略して示されている。

【0089】

I/F入力部111には、入力処理部201−1乃至201−7、電源監視部202、異常検知処理部203,225、およびトランジスタTR41が設けられている。入力処理部201は、端子A1より供給されてくる検出信号に基づいて、遊技球の通過の有無を検出する信号を出力すると共に、断線事故、および短絡事故を判定して、断線事故、および短絡事故が発生していると判定した場合、異常検出信号を発生する。尚、端子A2乃至A7については、入力処理部201−1と同一のものが接続される。また、以降、端子A1に供給されてくる出力検出信号を出力検出信号A1とも称する。

【0090】

電源監視部202は、電源VSの電圧と、所定の閾値とを比較して、電源VSの電圧が所定の閾値よりも低位となり、異常低下したと判定する場合、電源異常の発生を検知して、異常が発生したことを異常検知処理部203,225に供給する。

【0091】

入力処理部201は、比較部221、断線検知部222、短絡検知部223、順序異常検知部224、および異常検知処理部225を備えている。

【0092】

断線検知部222は、出力検出信号A1の電位がHiの状態となった電位よりも高位の断線検知閾値電圧とを比較し、これを超えたとき断線事故を検知し、対応する異常検出信号を発生して異常検知処理部203,225に通知する。

【0093】

短絡検知部223は、出力検出信号A1の電位がLowの状態となった電位よりも低位の短絡検知閾値電圧とを比較し、これを下回ったとき短絡事故を検知し、対応する異常検出信号を発生して異常検知処理部203,225に通知する。

【0094】

順序異常検知部224は、出力検出信号A1の電位がLowの状態となった電位よりも低位であって、短絡検知閾値電圧よりも高位の順序異常閾値電圧とを比較し、短絡検知閾値電圧を上回って、かつ、順序異常閾値電圧を下回ったとき順序異常を検知し、対応する異常検出信号を発生して異常検知処理部203,225に通知する。

【0095】

異常検知処理部225は、電源監視部202、断線検知部222、短絡検知部223および順序異常検知部224のいずれかから異常が検知されたことを示す信号が供給されると、動作の異常を示すHiの信号からなる異常検出信号を後段のトランジスタTR52のベースに供給し、それ以外のときLowの信号を出力する。

【0096】

比較部221は、Hiとなる弁別信号を出力するとき、所定の電位より低位であって、かつ、出力検出信号A1がLowとなったときの電位よりも高位となる低位反転閾値VTH3Lと、出力検出信号A1の電位とを比較し、出力検出信号A1の電位が低位反転閾値よりも低位に変化したときLowの弁別信号を後段のトランジスタTR51のベースに出力する。比較部221は、Lowとなる弁別信号を出力するとき、所定の電位より高位であって、かつ、出力検出信号A1がHiとなったときの電位よりも低位となる高位反転閾値VTH3Hと、出力検出信号A1の電位とを比較し、出力検出信号A1の電位が高位反転閾値よりも高位に変化したときHiの弁別信号を後段のトランジスタTR51のベースに出力する。

【0097】

すなわち、比較部221は、出力検出信号A1が、高位反転閾値よりも高位になると、弁別信号としてHiの信号を出力すると共に、閾値を低位反転閾値に変更し、逆に、出力検出信号A1が、低位反転閾値よりも低位になると、弁別信号としてLowの信号を出力すると共に、閾値を高位反転閾値に変更する動作を繰り返す。

【0098】

トランジスタTR51は、ベースが、比較部221の出力端子に接続されており、エミッタが接地電位に接続されており、コレクタが端子Y1、およびトランジスタTR52のコレクタに接続されている。

【0099】

トランジスタTR52は、ベースが、異常検知処理部225の出力端子に接続されており、エミッタが接地電位に接続されており、コレクタが端子Y1、およびトランジスタTR51のコレクタに接続されている。

【0100】

異常検知処理部203は、電源監視部202、並びに、入力処理部201−1乃至201−7の全ての断線検知部222、短絡検知部223、および順序異常検知部224からの異常検出信号を受け付けて、異常を検出したとき異常検出信号を後段のトランジスタTR41のベースに出力する。トランジスタTR41は、ベースが、異常検知処理部203の出力端子に接続されており、エミッタが接地電位に接続されており、コレクタが端子Eに接続されている。

【0101】

尚、電源監視部202、断線検知部222、短絡検知部223、および比較部221の詳細な構成については、本出願人が出願している特開2005−318358を参照されたい。

【0102】

[デュアル近接スイッチによる検出処理]

次に、図7のフローチャートを参照して、遊技球の正常通過と異常を検出する処理について説明する。ただし、図7のフローチャートにおける処理の説明は、各種の動作状態における回路の動作を説明するものである。このため、図7のフローチャートにおいては、判断処理ステップにおける主体は存在せず、単に区別すべき条件のみが記述されている。

【0103】

すなわち、ステップS11において、電源に断線が発生しておらず、ステップS12において、短絡状態でもなく、ステップS13において、電源電圧の異常低下もない場合、処理は、ステップS14に進む。

【0104】

ステップS14において、例えば、図8の最上段で示されるように、近接スイッチ161−1の検出信号D1−1が、時刻T1において、立ち上がっているような場合、遊技球の通過が検出されているものとみなされ、処理は、ステップS15に進む。

【0105】

ステップS15において、例えば、遊技球が順方向に通過するとき、近接スイッチ161−1,161−2の検出信号D1−1,D1−2が、図8の最上段、および2段目で示されるような関係となる。すなわち、検出信号D1−1に対応した弁別信号が、立ち上がる時刻T1,T5においては、検出信号D1−2は、Low信号である。また、検出信号D1−2が、立ち上がる時刻T2,T6においては、検出信号D1−1は、Hiの信号である。さらに、検出信号D1−1が、立ち下がる時刻T3,T7においては、検出信号D1−2は、Hi信号である。また、検出信号D1−2が、立ち下がる時刻T4,T8においては、検出信号D1−1は、Lowの信号である。

【0106】

尚、図8乃至図12においては、最上段が近接スイッチ161−1より供給されてくる検出信号D1−1を、2段目が近接スイッチ161−2より供給されてくる検出信号D1−2を、3段目が正常通過判定部162より出力される正常通過判定信号D2−1を、4段目が異常判定部163より出力される異常検出信号D2−2を、5段目が、出力合成部153より出力され、端子A1に入力される出力検出信号A1を、6段目が端子Y1からの出力信号を、7段目が端子Eから出力される信号をそれぞれ示している。また、5段目に示される閾値は、閾値Vth−cが、断線事故の有無を判別する閾値であり、閾値Vth−Hiが、比較部221における弁別信号がLowの信号であるときの高位反転閾値であり、閾値Vth−Lowが、弁別信号がHiの信号であるときの低位反転閾値であり、閾値Vth−tが、順序異常の有無を判別する閾値であり、閾値Vth−sが、短絡事故の有無を判別する閾値である。

【0107】

ステップS16において、出力合成部153は、I/F回路102の端子A1に対して遊技球の正常な通過が検出されたことを示す第1電位V1となる出力信号を供給する。すなわち、この場合、正常通過判定部162は、図8の3段目で示されるように、2段目で示される近接スイッチ161−2からの出力信号と同様の正常通過判定信号を出力合成部153に供給する。また、異常判定部163は、異常を検出しないので、図8の4段目で示されるようにLowの信号の状態が維持される。この結果、出力合成部153における第2電位発生部182のトランジスタTR21がオフの状態となり、ツェナーダイオードZDによる効果がなくなると共に、第3電位発生部183のトランジスタTR31がオフの状態であるので、第1電位発生部181により発生される第1電位V1がそのまま端子101bより出力されて、図8の5段目における時刻T2乃至T4、およびT6乃至T8で示されるように、第1電位V1の波形が出力される。

【0108】

一方、ステップS14において、遊技球の通過が検出されていない場合、すなわち、近接スイッチ161−1,161−2より供給されてくる検出信号がいずれもLowの信号である場合、ステップS17において、出力合成部153は、I/F回路102の端子A1に対して遊技球の異常がない状態で遊技球の通過が検出されていないことを示す第2電位V2となる出力信号を供給する。すなわち、出力合成部153における第2電位発生部182のトランジスタTR21がオンの状態となり、ツェナーダイオードZDによる効果が生じると共に、第3電位発生部182のトランジスタTR31がオフの状態であるので、ツェナー電位分がそのまま第2電位V2として端子101bより出力されて、図8の5段目における時刻T4乃至T6で示されるように、第2電位V2の波形が出力される。

【0109】

また、ステップS15において、例えば、図9で示されるような波形が、異常判定部163に供給されてくる場合、遊技球が図1で示される順方向に通過していないと判定されて、処理は、ステップS18に進む。すなわち、図9の時刻T11で示されるように、近接スイッチ161−2の検出信号D1−2が立ち上がるとき、近接スイッチ161−1の検出信号D1−1が、Hiの信号であるべきであるところが、Low信号となっており、順方向に通過することを示さない波形となっている。図9の最上段、および2段目の波形は、遊技球が逆方向に移動した場合に検出される波形である。すなわち、リフティングなどの不正行為がなされることにより、このように逆方向に遊技球が移動するような波形が得られた場合、上述したように順方向に移動するときに発生する波形の条件を満たさないため、順方向に移動していないことが検出される。

【0110】

ステップS18において、出力合成部153は、I/F回路102の端子A1に対して遊技球の異常が検出されていることを示す第3電位V3となる出力信号を供給する。すなわち、出力合成部153における第3電位発生部183のトランジスタTR31がオンの状態となるため、第2電位発生部182の動作状態に関わらず、ダイオードD1,D2の順方向電位がそのまま第3電位V3として端子101bより出力されて、図9の5段目における時刻T11乃至T12,T13乃至T14で示されるように、第3電位V3の波形が出力される。

【0111】

ステップS19において、近接スイッチ161−1,161−2のそれぞれより供給されてくる検出信号D1−1,D1−2がいずれも遊技球の通過を示さないLowの信号であるか否かが判定されて、いずれもLowの信号となるまで、同様の処理を繰り返す。そして、ステップS19において、例えば、図9の時刻T12乃至T13においては、いずれの弁別信号もLowの信号となるので、この場合、ステップS20において、リセット部164は、異常判定部163に対してリセット信号を発生し供給する。この処理により、図9の4段目の時刻T12乃至T13で示されるように、異常判定部191は、異常合成部192に対しての異常検出信号の発生を停止して、異常の検出を示さない第2電位V2からなる波形を出力する。

【0112】

以上のように、遊技球が順方向に通過しているか否かが検出されることにより、リフティングなどの不正行為がなされる場合、逆方向の遊技球の通過が検出されると、異常を示す第3電位V3の出力を発生される。結果として、リフティングなどの不正行為があっても異常が発生したことを認識することが可能になる。

【0113】

尚、ステップS15において、例えば、低周波近傍電磁界が一定の周期でオンまたはオフして発生した場合、近接スイッチ161−1,161−2のそれぞれより供給されてくる検出信号D1−1,D1−2は、図10の最上段および2段目で示されるような波形となる。すなわち、コイルL1,L2の発信周波数は通常同一ではないため、図10で示されるように、コイルL1の周波数に対応するように低周波近傍電磁界が発生されていた場合、コイルL1のみ、すなわち、近接スイッチ161−1の検出信号D1−1のみが影響を受ける。しかしながら、コイルL2には影響せず、近接スイッチ161−2の検出信号D1−2には影響がない。すなわち、低周波近傍電磁界が発生しても、いずれか一方の検出信号に影響が出ても他方の検出信号に影響しない。

【0114】

このような条件の下、上述した順方向へ通過条件に照らして波形を分析すると、図10で示されるように、時刻T21においては、近接スイッチ161−2の検出信号D1−2が立ち上がるとき、近接スイッチ161−1の検出信号D1−1はHiであるので、この時刻においては、異常は検出されない。このため、異常判定部163からは、異常検出信号が出力されない。また、時刻T22においても、近接スイッチ161−1の検出信号D1−1の立下りのタイミングにおいて、近接スイッチ161−2の検出信号D1−2はHiの信号であるので、異常判定部163からは異常検出信号が出力されない。

【0115】

ところが、時刻T23において、近接スイッチ161−1の検出信号D1−1の立ち上がりのタイミングにおいては、近接スイッチ161−2の検出信号D1−2がHiであるので、正規の順方向に遊技球が通過するときの条件を満たさない状態となるため、異常判定部163は、異常検出信号を出力する。このため、出力合成部153からは順序異常を示す第3電位V3からなる出力信号が出力される。

【0116】

結果として、低周波近傍電磁界が発生されても、順序異常を示す信号が検出信号D1−1,D1−2が共にLowの信号となるまで発生されることとなる。

【0117】

一方、ステップS11において、例えば、図11の5段目における時刻T31で示されるように、デュアル近接スイッチ101において断線事故が発生すると、ステップS22において、端子A1の信号は、閾値Vth−cよりも高い電源電圧VSとなる。

【0118】

また、ステップS12において、電源異常が検出された場合、およびステップS13において、短絡事故が検出された場合、例えば、図12の5段目における時刻T41で示されるように、デュアル近接スイッチ101において短絡事故が発生すると、ステップS21において、端子A1の信号は、閾値Vth−sよりも低い接地電位となる。

【0119】

以上のように、デュアル近接スイッチ101は、動作状態に応じて、5種類の出力検出信号A1を出力する。すなわち、デュアル近接スイッチ101は、断線事故時においては、電源電圧VSを、遊技球の正常通過検出時においては、第1電位V1を、遊技球の通過非検出時においては、第2電位V2を、順序異常検出時には、第3電位V3を、短絡事故または電源Vsの異常低下時には、接地電位をそれぞれ出力する。そして、デュアル近接スイッチ101は、順序異常検出後においても、異常検が発生していることを示す出力検出信号を出力し続けるのではなく、通過非検出の状態になると、リセット部164により通常の状態に復帰する。

【0120】

[図6のI/F回路102による信号処理]

次に、図13のフローチャートを参照して、図6のI/F回路102による信号処理について説明する。

【0121】

ステップS41において、異常検知処理部225は、断線検知部222より異常検出信号が供給されてきたか否かを判定する。断線検知部222より異常検出信号が供給されてきていない場合、処理は、ステップS42に進む。

【0122】

ステップS42において、異常検知処理部225は、電源監視部202より電源VSの異常低下の検出による異常検出信号が供給されてきたか否かを判定する。ステップS42において、電源VSの異常低下の検出により異常検出信号がない場合、処理は、ステップS43に進む。

【0123】

ステップS43において、異常検知処理部225は、短絡検知部223より異常検出信号が供給されてきたか否かを判定する。短絡検知部223より異常検出信号が供給されてきていない場合、処理は、ステップS44に進む。

【0124】

すなわち、ステップS41乃至S43の処理により、断線事故、電源異常、および短絡事故のいずれもが発生していないと判定された場合、ステップS44において、異常検知処理部225は、いずれも、動作に異常がないことを示すLowの信号をトランジスタTR52に出力する。この結果、トランジスタTR52は、オフの状態となるため、比較部221の弁別結果に対応したトランジスタTR51のコレクタ出力が端子Y1を介して、CPU103に対して供給される。

【0125】

ステップS45において、順序異常検知部224は、端子A1を介して供給される検出信号が、遊技球の通過を示す第1電位V1の信号として供給されたか否かを判定する。例えば、図8の最上段で示されるように、端子A1より供給されてきた検出信号が、時刻T2において、立ち上がっているような場合、遊技球の通過が検出されているものとみなされ、処理は、ステップS46に進む。

【0126】

ステップS46において、順序異常検知部224は、端子A1を介して供給されてくるデュアル近接スイッチの検出信号に基づいて、遊技球が順方向に通過しているか否かを判定する。すなわち、例えば、遊技球が順方向に通過するとき、端子A1を介して供給されてくるデュアル近接スイッチの検出信号は、図8の5段目で示されるように、第1電位V1であるので、順序異常検知部224は、端子A1の信号が第1電位V1であるか否かに基づいて、順序異常が発生しているか否かを判定する。

【0127】

ステップS46において、例えば、端子A1の信号が第1電位V1であり、順序異常が発生していない場合、ステップS47において、順序異常検知部224は、異常検知処理部225に対して遊技球の検出順序の異常がないことを示す信号を供給する。すなわち、この場合、異常検知処理部203には、異常検知処理部225のいずれからも異常検出信号が供給されないため、図8の7段目で示されるように、異常検知処理部203は、端子Eを介して、異常が検出されていないことを示すLowの信号をCPU103に出力する。

【0128】

ステップS48において、トランジスタTR52は、異常検知処理部225から異常検出信号によりオフの状態であるため、図8の6段目の時刻T2乃至T4,T6乃至T8で示されるように、比較部221より供給されてくる弁別信号に基づいた遊技球を検出していることを示すHiの信号を弁別信号として、端子Y1よりCPU103に出力する。

【0129】

一方、ステップS45において、端子A1を介して供給される検出信号が、遊技球の通過を示す第1電位V1の信号ではなく、遊技球の通過が検出されていない場合、すなわち、デュアル近接スイッチ101より端子A1を介して供給されてくる検出信号が図8の5段目で示されるように第2電位V2である場合、ステップS49において、順序異常判定部224は、順序異常を検出していないことを示す信号を異常検知処理部203,225に供給する。この場合も、異常検知処理部203には、異常検知処理部225のいずれからも異常検出信号が供給されてこないので、異常検知処理部203は、端子Eを介してCPU103に対して異常が検出されていないLowの信号を供給する。

【0130】

ステップS50において、トランジスタTR52は、異常検知処理部225より異常が検出されたことを示す信号が供給されてこないので、オフの状態のままであり、比較部221より供給されてくる弁別信号、すなわち、遊技球の通過が検出されていない第2電位V2に基づいて、トランジスタTR51がオンの状態であるので、例えば、図8の時刻T4乃至T6で示されるように、端子Y1を介して遊技球が非検出であることを示すLowの信号をCPU103に出力する。

【0131】

また、ステップS46において、例えば、図9の5段目における時刻T11乃至T12,T13乃至T14で示されるような第3電位V3の波形が端子A1を介して順序異常検知部224に供給されてくる場合、遊技球が図1で示される順方向に通過していないと判定されて、処理は、ステップS51に進む。

【0132】

ステップS51において、順序異常判定部224は、遊技球の通過方向が異常であると判定したため、異常が発生したことを示す異常検出信号を異常検知処理部203,225に供給する。異常検知処理部203は、順序異常判定部224より異常検出信号が供給されてくるため、トランジスタTR41のベースにLowの信号を供給してオフにさせ、端子Eを介して、図9の7段目における時刻T11乃至T12,T13乃至T14で示されるように、異常が検出されたことを示すHiの信号からなる異常検出信号をCPU103に供給する。

【0133】

ステップS52において、異常検知処理部225は、順序異常判定部224からの異常検出信号に基づいて、比較部221より供給されてくる弁別信号の状態とは無関係に、遊技球の通過を検出していないことを示すLowの信号からなる出力信号を、端子Y1を介してCPU103に出力する。

【0134】

以上のように、遊技球が順方向に通過しているか否かが検出されることにより、リフティングなどの不正行為がなされる場合、逆方向の遊技球の通過が検出されても、端子Eより異常検出信号が発生されると共に、端子Y1からは比較部221からの弁別信号の有無に関わらず、遊技球の通過を示さない非検出の信号が出力信号としてCPU103に供給される。結果として、リフティングなどの不正行為があっても異常が発生したことを認識することが可能になると共に、不正行為により遊技球が不正にカウントさせないようにすることが可能となる。

【0135】

尚、ステップS46において、例えば、低周波近傍電磁界が一定の周期でオンまたはオフして発生した場合、デュアル近接スイッチ101より供給される波形は、図10の5段目の時刻T23乃至T24,T25乃至T26で示されるように、第3電位V3からなる波形となる。

【0136】

すなわち、順序異常判定部224には、時刻T21乃至T23において、順序異常検出閾値電圧Vth−tより低位で、かつ、短絡検知閾値電圧Vth−sよりも高位の第3電位V3が供給されないことになるため、順序異常が検出されない。このため、順序異常判定部203からは、トランジスタTR41、および端子Eより異常検出信号が出力されない。また、比較部221からの弁別信号はHiの信号となるため、遊技球が通過したことを示す出力信号が端子Y1より出力される。

【0137】

ところが、時刻T23において、順序異常判定部224には、時刻T23において、順序異常検出閾値電圧Vth−tより低位で、かつ、短絡検知閾値電圧Vth−sよりも高位の第3電位V3が供給されることになるため、順序異常が検出される。このため、順序異常判定部203は、異常検出信号を異常検知処理部203,225に供給する。異常検知処理部203は、トランジスタTR41をオフにして、端子Eからは異常検出信号が出力される。このとき、比較部221は、遊技球の通過を検出しないので、端子Y1からは遊技球が通過していないことを示す非検出信号であるLowの信号からなる出力信号が出力される。

【0138】

結果として、低周波近傍電磁界が発生されても、端子Eより異常検出信号D1−1,D1−2が共にLowの信号となるまで発生されることとなるため、遊技球の不正な計数がなされても、その異常の発生を認識することが可能となる。

【0139】

一方、ステップS41において、例えば、図11の5段目における時刻T31で示されるように、端子A1より供給されてくる出力検出信号が、断線事故の有無を判定する閾値Vth−cよりも高い電圧であり、断線を検知した場合、ステップS53において、断線検知部222は、断線による異常を検出したことを示す異常検出信号を異常検知処理部203,225に供給する。このため、異常検知処理部203,225は、断線検知部222からの異常検出信号に基づいて、異常検出信号の供給を受けたと判定し、処理は、ステップS53に進む。

【0140】

ステップS54において、異常検知処理部203は、異常が検出されたことを示す異常検出信号を、トランジスタTR41に出力する。このため、トランジスタTR41は、図11の7段目における時刻T31以降で示されるように、端子Eを介して、動作に異常が発生したことを示す信号をCPU103に供給する。

【0141】

ステップS55において、トランジスタTR52は、図11の5段目における時刻T31以降で示されるように、異常検知処理部225からの異常検出信号に基づいて、比較部221からの弁別信号に関わらず、遊技球の通過が検出されていないことを示す非検出を示すLowの出力信号を端子Y1より出力する。

【0142】

また、ステップS42において、電源異常が検出された場合、およびステップS43において、短絡事故が検出された場合のいずれもステップS53乃至S55の処理となる。

【0143】

すなわち、遊技球の通過が検出されている検出の状態であって、動作状態が正常の場合、端子Ynより出力される出力信号は、遊技球の検出を示すHiの信号となり、端子Eより出力される信号は、動作の異常が検出されていないことを示すLowの信号となる。

【0144】

さらに、遊技球の通過が検出されていない非検出の状態であって、動作状態が正常の場合、端子Ynより出力される出力信号は、遊技球の非検出を示すLowの信号となり、端子Eより出力される信号は、動作の異常が検出されていないことを示すLowの信号となる。

【0145】

また、断線事故、短絡事故、電源異常、または順序異常の場合、端子Ynより出力される出力信号は、遊技球の非検出を示すLowの信号となり、端子Eより出力される信号は、動作の異常が検出されていることを示すHiの信号となる。

【0146】

このように、遊技球の通過が検出されるのは、断線事故、短絡事故、電源異常、または順序異常のない場合にのみに限られるため、仮に、断線事故、短絡事故、電源異常、または順序異常といった動作の異常を意図的に発生させて不正行為を誘発させようとしても、その際には遊技球の通過は非検出の状態に維持されるため、不正行為を抑制させることが可能になる。

【0147】

[図3のCPU103による計数処理]

次に、図14のフローチャートを参照して、図3のCPU103による計数処理について説明する。

【0148】

ステップS111において、異常判定部122は、端子Eより異常の発生を検出したことを示すHiの信号からなる異常検出信号が検出されたか否かを判定する。ステップS111において、例えば、異常検出信号が供給されてきた場合、処理は、ステップS112に進む。

【0149】

ステップS112において、異常種別判定部124は、タイマ125を制御して、端子Eより供給されてくるHiの信号が、1個の遊技球の通過が検出された場合に弁別信号がHiの信号となる時間TAに対して十分長い時間TCよりも長い時間だけHiの状態となっているか否かを判定する。

【0150】

すなわち、例えば、図15の最上段における時刻T101以降で示されるように、端子A1に入力される検出信号が断線事故が発生したか否かが判定される閾値Vth−cよりも高い状態となると、断線事故の状態が解消されるまで、図15の4段目で示されるように、端子Eは異常検出信号であるHiの信号の状態が継続される。これは、断線事故にのみならず、短絡事故、順序異常、および電源異常においても同様の傾向となる。

【0151】

従って、ステップS112において、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAに対して十分に長い時間TCより長い時間だけHiの状態となった場合、ステップS117において、断線事故、短絡事故、順序異常、または電源異常のいずれかであるものとみなし、異常種別判定部124は、その旨を発報出力部126に発報情報として通知する。

【0152】

ステップS115において、特定部123は、異常が発生しているデュアル近接スイッチ101に接続されているI/F回路102を特定するための情報を発報出力部126に通知する。これにより、発報出力部126は、発報部104を制御して、発生している異常の種別と、その発生している位置の情報とを含めた発報情報を出力させる。

【0153】

また、ステップS112において、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAに対して十分に長い時間TCより長い時間だけHiの状態となっていない場合、処理は、ステップS113に進む。

【0154】

ステップS113において、異常種別判定部124は、タイマ125を制御して、端子E2に供給されてくる異常検出信号がHiの状態となっている時間が、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAよりも短いか否かを判定する。ステップS113において、端子E2に供給されてくる異常検出信号がHiの状態となっている時間が、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAよりも短い場合、処理は、ステップS114に進む。

【0155】

ステップS114において、異常種別判定部124は、低周波近傍電磁界が発生することにより人為的な不正により生じている異常であることを発生している異常の種別であるものとして発報出力部126に通知する。

【0156】

すなわち、端子A1に供給される信号が、図16の最上段で示されるように、低周波近傍電磁界が発生することにより周波数の高い矩形波となっている場合、2段目で示されるように、時刻T111においては、近接スイッチ161−1の検出信号D1−1が立ち上がるタイミングにおいて、近接スイッチ161−2の検出信号D1−2がLowの信号であるため、遊技球が順方向に通過していないものとみなされている。このため、この時刻T111乃至T112は、4段目で示されるように、端子Eからは異常検出信号が出力され続ける。しかしながら、時刻T113において、近接スイッチ161−2の検出信号D1−2の立ち上がりのタイミングにおいて、近接スイッチ161−1の検出信号D1−1がHiの信号となっているため、図16の3段目で示されるように、一旦は正規の順方向に通過しているものとみなされるが、時刻T114の近接スイッチ161−1の検出信号D1−1の立下りのタイミングにおいて、近接スイッチ161−2の検出信号D1−2がLowの信号となっている。このため、図16の4段目で示されるように、時刻T114より異常検出信号がHiの信号となる。そして、近接スイッチ161−1,161−2の検出信号D1−1,D1−2もLowの信号となる時刻T115において、端子Eの異常検出信号がリセット部164のリセット信号によりLowの信号にリセットされる。従って、低周波近傍電磁界が発生されることにより、端子Eが異常検出信号を発生する最長時間は、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAとなる。従って、異常検出信号としてHiの信号となっている時間が、これより時間TAより短い、例えば、図16で示される時間Taなどの場合、低周波近傍電磁界による異常であるものと判定される。

【0157】

一方、ステップS113において、端子Eに供給されてくる異常検出信号がHiの状態となっている時間が、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAよりも長い(かつ時間TCよりも短い)場合、処理は、ステップS116に進む。

【0158】

ステップS116において、異常種別判定部124は、遊技球が逆方向に通過されている状態が検出されている異常、すなわち、リフティングによる人為的な不正により生じている異常(逆方向に遊技球が通過しているかのうように検出される異常)であることを発生している異常の種別であるものとして発報出力部126に通知する。

【0159】

すなわち、例えば、遊技球が逆方向に通過する場合、図17の最上段、および2段目で示されるように、端子A1,A2の上に凸となる波形のタイミングが、正規の順方向に対して前後が逆になる(図10参照)。このため、図19の4段目における時刻T121乃至T122において、端子E2よりHiの信号が出力される。時刻T121乃至T122の時間TBは、1個の遊技球が通過する際に弁別信号がHiの信号状態となる時間TAよりも長い(かつ時間TCよりも短い)ので、この場合、遊技球が逆方向に通過するように検出されるリフティングにより異常であることが認識される。

【0160】

尚、ステップS111において、端子Eに異常検出信号が供給されてこない場合、処理は、ステップS118に進む。

【0161】

ステップS118において、カウント部121は、端子Y1乃至Y7の遊技球の通過の検出を示すHiの信号が供給されてきたか否かを判定する。ステップS118において、いずれかでHiの信号が検出された場合、ステップS119において、特定部123は、Hiの信号を検出した端子Y1乃至Y7のいずれかにより遊技球の通過を検出したデュアル近接スイッチ101を特定する。

【0162】

ステップS120において、カウント部121は、遊技球の通過を検出したHiの信号に基づいて、特定部123により特定されたデュアル近接スイッチ101について通過した遊技球の球数を計数し、処理は、ステップS111に戻る。

【0163】

以上の処理により、端子Eの異常検出信号の発生している時間の長さから、発生している異常の種別を特定すると共に、異常が発生しているデュアル近接スイッチの位置を特定して異常を発報することが可能となる。

【0164】

<2.第2の実施の形態>

[インタフェース回路のその他の構成例]

以上においては、インタフェース回路102は、1基のデュアル近接スイッチ101に対して、遊技球の通過検出を示す信号を出力する端子Yn(n=1,2,・・・7)、および全てのデュアル近接スイッチ101におけるエラーの有無を示す信号を出力する端子Eとを設ける例について説明してきたが、例えば、順序異常を識別するための端子をさらに設けるようにしてもよい。

【0165】

図18は、1基のデュアル近接スイッチ101に対して、遊技球の通過検出を示す信号を出力する端子Yn、および全てのデュアル近接スイッチ101におけるエラーの有無を示す信号を出力する端子Eに加えて、さらに、順序異常を識別する信号を出力する端子を設けるようにしたインタフェースシステムの構成例を示している。尚、図18のインタフェースシステムにおいては、図3のインタフェースシステムにおける構成と同様の機能を備えた構成には、同一の名称、および同一の符号を付しており、その説明は、適宜省略するものとする。

【0166】

すなわち、図18のインタフェースシステムにおいて、図3のインタフェースシステムと異なる構成は、I/F回路102に代えて、I/F回路102’を設けた点である。I/F回路102’は、1基のデュアル近接スイッチ101に対して、遊技球の通過検出を示す信号を出力する端子Yn−1、および全てのデュアル近接スイッチ101におけるエラーの有無を示す信号を出力する端子Eに加えて、さらに、順序異常のみを別途示す信号を出力する端子Yn−2を備えている。この関係上、I/F回路102により対応可能なデュアル近接スイッチ101の数量がほぼ半分になるため、デュアル近接スイッチ101−1乃至101−3のみとなっている。また、CPU103に代えて、CPU103’が設けられている。CPU103’は、CPU103と異なる手法により計数処理を実行する。尚、この計数手法については、図25を参照して、詳細を後述する。

【0167】

[図18のI/F回路102’の構成例]

次に、図19を参照して、図18のI/F回路102’の構成例について説明する。尚、図18のI/F回路102’において、図6のI/F回路102と同様の機能を備えた構成については、同一の名称、および同一の符号を付しており、その説明は、適宜省略するものとする。

【0168】

すなわち、図19のI/F回路102’において、図6のI/F回路102’と異なるのは、入力処理部201における、順序異常検知部224に代えて、順序異常検知部251を設けたことにより、正常通過を出力する端子Y1−1と順序異常を出力する端子Y1−2とを個別にした点である。順序異常検知部251は、比較部261、抵抗R201,R202、およびトランジスタTR201,TR202を備えている。比較部261は、デュアル近接スイッチ101の検出信号である端子A1の信号と、所定の閾値電圧VH4とを比較し、比較結果を抵抗R101,R102を介してトランジスタTR201,TR202のベースに供給する。尚、所定の閾値電圧VH4とは、上述した順序異常を示す第3電位V3を検出するためのものであり、具体的には、図22での閾値Vth−tであり、端子A1が第3電位V3状態となったときにはHiの信号を出力する。

【0169】

トランジスタTR201,TR202は、ベースがそれぞれ抵抗R201,R202を介して、比較部261の出力端子に接続されており、コレクタがそれぞれ端子Y1−1,Y1−2に接続されており、エミッタが接地電位に接続されている。

【0170】

すなわち、トランジスタTR201,TR202は、比較部261の出力信号に基づいて、オン、またはオフに動作する。これにより、順序異常判定部251は、順序異常が検出されたとき、端子Y1−1より非検出信号のLowの信号を出力させ、端子Y1−2より異常を示すHiの信号を出力させる。逆に、順序異常が発生されないとき、端子Y1−1より比較部221の弁別信号を出力させ、端子Y1−2より正常であることを示すLowの信号を出力させる。

【0171】

より具体的には、例えば、異常の検出がなく、遊技球が正常に通過する場合、図20の7段目で示されるように、端子Y1−2の出力はLowの信号となる。尚、図20乃至図24においては、7段目を除き、いずれも図8乃至図12における波形と同様である。ただし、6段目は、端子Y1−1の波形であるが、端子Y1−1の波形は、端子Y1と同様である。

【0172】

また、順序異常が発生した場合、図21の7段目における時刻T11乃至T12,T13乃至T14で示されるように、順序異常を示すHiの信号が端子Y1−2より出力される。

【0173】

さらに、低周波近傍電磁界の到来が検出された場合、図22の7段目における時刻T23乃至T24,T25乃至T26で示されるように、順序異常を示すHiの信号が端子Y1−2より出力される。

【0174】

さらに、断線事故が発生した場合、図23の5段目の時刻T31で示されるように、端子A1の信号が、閾値Vth−cを上回る電位となるため、比較部261は、Lowの信号を出力するが、断線検知部222が、異常検知処理部225へ異常を示すHiの信号を出力するため、トランジスタTR52がオンの状態となる。このため、端子Y1−1は非検出を示すLowの信号を出力するが、端子Y1−2は、正常を示すLowの信号を出力する。また、断線検知部222の異常は、異常検知処理部203へも出力されるため、端子Eは、異常を示すHiの信号を出力する。

【0175】

また、短絡事故が発生した場合、図24の5段目における時刻T41で示されるように、端子A1は0Vととなる。このとき、比較部261の比較電位Vth―tを下回るため、端子Y1−2は、異常を示すHiの信号を出力する。しかしながら、短絡検知閾値Vth−sも下回るため端子Eも同様に異常を示すHiの信号を出力する。

【0176】

[図18のCPU103’の計数処理]

次に、図25のフローチャートを参照して、図18のCPU103’における計数処理について説明する。

【0177】

ステップS171において、異常判定部122’は、端子Eおよび端子Yn−2より供給されてくる信号が共に正常を示すLowの信号からなる検出信号であるか否かを判定する。ステップS171において、例えば、端子Eおよび端子Yn−2より供給されてくる信号が共に正常を示すLowの信号ではない検出信号である場合、ステップS172において、異常判定部122’は、端子Eおよび端子Yn−2より供給されてくる信号が共に異常の発生を示すHiの信号からなる異常検出信号であるか否かを判定する。ステップS172において、例えば、端子Eおよび端子Yn−2の両方の端子において、異常の発生を示すHiの信号が検出された場合、処理は、ステップS173に進む。

【0178】

ステップS173において、異常種別判定部124’は、端子Eおよび端子Yn−2の両方から異常検出信号が供給されているので、発生している異常が、短絡事故、または電源異常のいずれかであるものとみなし、その旨の発報情報を発報出力部126に通知する。

【0179】

ステップS177において、特定部123は、いずれのI/F回路102であるかを特定し、その旨を発報情報として発報出力部126に供給する。これにより、発報出力部126は、特定部123により特定されたI/F回路102の位置の情報と共に、発生した異常の種別を示す発報情報に基づいて、発報部104を制御して、発報させる。

【0180】

一方、ステップS172において、端子Eおよび端子Yn−2のいずれにおいてもHiの信号からなる異常検出信号が供給されてきていない場合、ステップS174において、異常判定部122’は、端子Yn−2より供給されてくる信号のみが異常の発生を示すHiの信号からなる異常検出信号であるか否かを判定する。ステップS174において、例えば、端子Yn−2からのみ異常の発生を示すHiの信号が検出された場合、処理は、ステップS175に進む。

【0181】

テップS175において、異常種別判定部124は、端子Yn−2からの異常検出信号の供給を受けることになるので、発生している異常が、リフティング、または低周波近傍電磁界のいずれかであるものとみなし、その旨の発報情報を発報出力部126に通知する。この場合、ステップS177においては、特定部123は、端子Yn−2から、いずれのデュアル近接スイッチ101であるかを特定し、その旨を発報情報として発報出力部126に供給する。これにより、発報出力部126は、特定部123により特定されたデュアル近接スイッチ101の位置の情報と共に、発生した異常の種別を示す発報情報に基づいて、発報部104を制御して、発報させる。

【0182】

また、ステップS174において、例えば、端子Yn−2から異常の発生を示すHiの信号が検出されない場合、処理は、ステップS176に進む。

【0183】

ステップS176において、異常種別判定部124’は、端子Eのみから異常検出信号が供給されているので、発生している異常が、断線異常であるものとみなし、その旨の発報情報を発報出力部126に通知する。

【0184】

また、ステップS171において、例えば、端子Eおよび端子Yn−2より供給されてくる信号が共に正常を示すLowの信号からなる検出信号である場合、処理は、ステップS178に進む。

【0185】

尚、ステップS178乃至S180の処理については、図14を参照して説明したステップS118乃至S120の処理と同様であるので、その説明は省略するものとする。

【0186】

以上の処理によれば、端子E,Yn−2により発生される異常検出信号の有無のパターンにより、検出された異常の種別と共に、その位置を特定して発報させることが可能となる。尚、以上においては、端子E,Yn−2のそれぞれの異常検出信号のパターンにより発生した異常の種別を判定させる例について説明してきたが、端子E,Yn−2の少なくともいずれか一方において異常検出信号が供給されてきた場合、異常が検出されたことだけを発報させるようにしてもよい。

【0187】

また、図14のフローチャートを参照して説明した計数処理でもよい。ただし、この場合、端子Yn−2の信号が不要となる。

【0188】

<3.第3の実施の形態>

[デュアル近接スイッチのその他の構成例]

以上においては、インタフェースシステムにおいて、デュアル近接スイッチ101、I/F回路102、およびCPU103より構成される例について説明してきたが、例えば、デュアル近接スイッチ101からの出力される信号を調整することにより、I/F回路102を省略するようにしてもよい。

【0189】

図26は、I/F回路102を省略するようにしたインタフェースシステムの構成例を示している。尚、図26において、図3のインタフェースシステムにおける構成と同一の機能を備えた構成については、同一の名称、および同一の符号を付しており、その説明は適宜省略するものとする。

【0190】

すなわち、図26のインタフェースシステムにおいて、図3のインタフェースシステムと異なるのは、デュアル近接スイッチ101に代えて、デュアル近接スイッチ101’を備えた点である。

【0191】

デュアル近接スイッチ101’は、基本的にデュアル近接スイッチ101と同様であるが、出力合成部153に代えて、出力合成部153’を設けている。出力合成部153’は、正常通過判定信号出力部301、出力信号固定部302、および異常判定信号出力部303を備えている。

【0192】

正常通過判定信号出力部301は、出力信号固定部302により制御されており、出力信号固定部302より正常通過判定信号D2−1を固定するように指示されるとき、Lowの信号からなる正常通過判定信号を端子101xより出力する。一方、正常通過判定信号出力部301は、出力信号固定部302により制御されており、出力信号固定部302より出力信号を固定するように指示されないとき、正常通過判定部162の正常通過判定信号D2−1を端子101xよりそのまま出力する。

【0193】

出力信号固定部302は、異常判定部163より供給されてくる異常判定信号D2−2を異常判定信号出力部303に供給し、端子101yよりCPU103に出力させる。また、このとき、出力信号固定部302は、正常通過判定信号出力部301の出力信号をLowの信号に固定させる。

【0194】

[出力合成処理]

次に、図27のフローチャートを参照して、出力合成部153’における出力合成処理について説明する。

【0195】

ステップS201において、出力信号固定部302は、異常判定部163より異常が検出されたことを示す異常判定信号が供給されてきたか否かを判定する。ステップS201において、例えば、図28の最上段、および2段目で示されるように、近接スイッチ161−1,161−2の検出信号D1−1,D1−2が、それぞれ時刻T301乃至T302、T302乃至T303において正常な順序で検出される場合、4段目で示されるように、異常判定部163からは異常を示す異常判定信号が供給されてこないことになるため、このような場合、処理は、ステップS202に進む。

【0196】

ステップS202において、正常通過判定信号出力部301は、出力信号固定部302からの指示がないので、図28の3,5段目で示されるように、正常通過判定部162からの正常通過判定信号を、そのまま端子101yよりCPU103に出力し、処理は、ステップS201に戻る。すなわち、この場合、図28の6段目で示されるように、端子101yから異常が発生していないことを示すLowの信号からなる異常検出信号が出力される。

【0197】

一方、ステップS201において、例えば、図29の最上段、および2段目で示されるように、近接スイッチ161−1,161−2の検出信号D1−1,D1−2が、それぞれ時刻T311乃至T312、T312乃至T313において異常な順序で検出される場合、4段目で示されるように、異常判定部163からは異常を示す異常判定信号が供給されてくことになるので、このような場合、処理は、ステップS203に進む。

【0198】

ステップS203において、出力信号固定部302は、正常通過判定信号出力部301に対してLowの信号に固定した正常通過判定信号を出力するように指示する。このため、正常通過判定信号出力部301は、出力信号固定部302からの指示に基づいて、図29の3,5段目で示されるように、通過非検出を示すLowの信号を端子101yよりCPU103に出力する。

【0199】

ステップS204において、出力信号固定部302は、異常判定信号を異常を示すHiの信号として出力するように、異常判定信号出力部303を制御する。この結果、図29の6段目で示されるように、端子101yから異常が発生していることを示すHiの信号からなる異常を示す異常判定信号が出力される。

【0200】

尚、低周波近傍電磁界が到来するような場合、図30の4段目で示されるように、時刻T331乃至T333においては、異常判定部163より異常が検出されていることを示す異常判定信号D2−2が供給される。このため、図27におけるステップS201,S202における処理となり、図30の2,5,6段目で示されるように、端子101xからは遊技球の正常な通過を検出するHiの信号が出力され、端子102yからは異常が検出されていないことを示すLowの信号からなる異常判定信号がCPU103に出力される。

【0201】

一方、時刻T333乃至T334,T335乃至T336においては、4段目で示されるように、異常が検出されたことを示す異常判定信号D2−2が供給される。このため、6段目で示されるように、異常が検出されていることを示すHiの信号からなる異常判定信号が端子101yからCPU103に供給する。

【0202】

尚、この場合、端子101x,101yをそれぞれ図3の端子Yn,Eと同様に扱うものとし、CPU103における計数処理は、図14と同様の処理とすることで、I/F回路102を省略することが可能となる。このような構成により、I/F回路102に係る製造コストや設置の手間を低減することが可能となる。

【0203】

以上の如く、本発明によれば、断線異常、短絡異常、および電源異常といった異常に加えて、必要に応じて低周波近傍電磁界やリフティングによる不正行為への対策に係る制御装置側での負荷を低減することが可能となる。また、デュアル近接スイッチ内部において、近接スイッチ161−1,161−2がいずれも非検出となるだけで出力信号がリセットされるため、制御装置側からのリセット信号に基づいてリセットする構成と比べて、擬似的にリセット信号が発生されることでリセットされてしまうといった不正を抑制することが可能となる。さらに、出力合成処理により、I/F回路を省略することにより、装置コスト、および設置の手間を低減することが可能となる。

【0204】

ところで、上述した一連の処理は、ハードウェアにより実行させることもできるが、ソフトウェアにより実行させることもできる。一連の処理をソフトウェアにより実行させる場合には、そのソフトウェアを構成するプログラムが、専用のハードウェアに組み込まれているコンピュータ、または、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータなどに、記録媒体からインストールされる。

【0205】

図31は、汎用のパーソナルコンピュータの構成例を示している。このパーソナルコンピュータは、CPU(Central Processing Unit)1001を内蔵している。CPU1001にはバス1004を介して、入出力インタ-フェイス1005が接続されている。バス1004には、ROM(Read Only Memory)1002およびRAM(Random Access Memory)1003が接続されている。

【0206】

入出力インタ-フェイス1005には、ユーザが操作コマンドを入力するキーボード、マウスなどの入力デバイスよりなる入力部1006、処理操作画面や処理結果の画像を表示デバイスに出力する出力部1007、プログラムや各種データを格納するハードディスクドライブなどよりなる記憶部1008、LAN(Local Area Network)アダプタなどよりなり、インターネットに代表されるネットワークを介した通信処理を実行する通信部1009が接続されている。また、磁気ディスク(フレキシブルディスクを含む)、光ディスク(CD-ROM(Compact Disc-Read Only Memory)、DVD(Digital Versatile Disc)を含む)、光磁気ディスク(MD(Mini Disc)を含む)、もしくは半導体メモリなどのリムーバブルメディア1011に対してデータを読み書きするドライブ1010が接続されている。

【0207】

CPU1001は、ROM1002に記憶されているプログラム、または磁気ディスク、光ディスク、光磁気ディスク、もしくは半導体メモリ等のリムーバブルメディア1011から読み出されて記憶部1008にインストールされ、記憶部1008からRAM1003にロードされたプログラムに従って各種の処理を実行する。RAM1003にはまた、CPU1001が各種の処理を実行する上において必要なデータなども適宜記憶される。

【0208】

尚、本明細書において、記録媒体に記録されるプログラムを記述するステップは、記載された順序に沿って時系列的に行われる処理は、もちろん、必ずしも時系列的に処理されなくとも、並列的あるいは個別に実行される処理を含むものである。

【0209】

また、本明細書において、システムとは、複数の装置により構成される装置全体を表すものである。

【符号の説明】

【0210】

101,101−1,101−2 デュアル近接スイッチ

102,102’ I/F回路

103,103’ CPU

105 発報部

106 計数部

111 I/F入力部

121 カウント部

122 異常判定部

123 特定部

124 異常種別判定部

125 タイマ

126 発報出力部

【技術分野】

【0001】

本発明は、デュアル近接スイッチ、および制御方法、遊技球の通過方向検出システム、遊技機、並びにプログラムに関し、特に、不正を抑制しつつ、適切に遊技球の通過を検出できるようにしたデュアル近接スイッチ、および制御方法、遊技球の通過方向検出システム、遊技機、並びにプログラムに関する。

【背景技術】

【0002】

これまでの遊技球を用いた遊技機および計数機おける、遊技球を検出する直流2線式スイッチに対する不正行為を防止する構成としては、直流2線式スイッチとインタフェース回路間の断線異常、短絡異常、または電源電圧の低下異常といった不正行為との因果関係が知られている異常を検出し、報知するものが提案されている(特許文献1参照)。

【0003】

ところが、昨今においては、これまでの不正行為に加え、遊技球が直流2線式スイッチを通過している際に、強力な低周波近傍電磁界を照射し、カウント数を増やす不正行為や、セルと呼ばれる道具を用いて、直流2線式スイッチの検出部に検出媒体を往復させて、遊技球のカウント数を増やす、リフティングと呼ばれる新たな不正行為が確認されている。

【0004】

これらの新たな不正行為は、従来のインタフェース回路では対策できず、対策には従来のインタフェース回路とは異なる信号処理(特許文献2乃至4参照)が必要となっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第4332797号公報

【特許文献2】特許第2817021号公報

【特許文献3】特開2001−054618号公報

【特許文献4】特開2001−129214号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上述した特許文献2乃至4の技術だけでは、断線異常、短絡異常、または電源低下の異常を検出できない。従って、これまでの構成により、断線異常、短絡異常、または電源低下の異常を検出しつつ、新たな不正行為を対策するためには、新たに対策する不正行為の種類だけ、CPU(Central Processing Unit)のポート数を増やしてセンサ数を増やし、処理する信号数を増やす必要があるため、処理に係る装置規模とソフトウェアによる処理負荷を増大させてしまう恐れがあった。

【0007】

また、リフティングによる不正での異常が解消された際に、直ちに復帰できないことや、低周波近傍電磁界のような外乱によりセンサ出力が同時に立ち上がった際、不正を検出できないといった誤動作を生じることがあった。

【0008】

本発明はこのような状況に鑑みてなされたものであり、特に、断線異常、短絡異常、および電源異常といった異常に加えて、必要に応じて低周波近傍電磁界やリフティングによる不正行為への対策を必要に応じて適正に実現しつつ、信号処理負担を低減できるようにするものである。

【課題を解決するための手段】

【0009】

本発明の一側面のデュアル近接スイッチは、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含む。

【0010】

前記正常通過判定手段、および前記異常判定手段には、それぞれ少なくとも1個の保持回路を含ませるようにすることができ、前記正常通過判定手段、および前記異常判定手段には、前記保持回路の動作に基づいて、それぞれ前記正常通過検出信号、および前記異常検出信号を出力させるようにすることができ、前記第1の近接スイッチ、および前記第2の近接スイッチが、所定の検出状況となった場合、前記保持回路をリセットするリセット手段をさらに含ませるようにすることができる。

【0011】

前記リセット手段には、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない状態の場合、前記保持回路をリセット、または、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない期間全域において、前記保持回路をクリアさせるようにすることができる。

【0012】

前記異常検出信号が出力された場合、前記正常通過検出信号を、正常でないことを示す所定の状態に固定して出力する出力信号固定手段をさらに含ませるようにすることができる。

【0013】

前記正常通過検出信号が検出された場合、第1の電圧値を出力し、前記正常通過検出信号、および、異常検出信号が検出されない場合、第2の電圧値を出力し、前記異常検出信号が検出された場合、第3の電圧値を出力する出力合成手段をさらに含ませるようにすることができる。

【0014】

前記第1乃至3の電圧値は、いずれも接地電位より高く、電源電位よりも低い中間電位とすることができ、いずれも異なる電位とすることができる。

【0015】

請求項1乃至4のいずれかに記載の1個のデュアル近接スイッチを含ませるようにすることができ、前記制御回路には、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を受け付けるようにさせることができる。

【0016】

本発明の遊技球の通過方向検出システムには、請求項1乃至6のいずれかに記載の1個のデュアル近接スイッチと、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を信号処理して、前記制御回路に供給するインタフェース回路とを含ませるようにすることができ、前記制御回路には、前記インタフェース回路から伝送される前記正常通過検出信号、および前記異常検出信号の信号処理結果を受け付けるようにさせることができる。

【0017】

本発明の遊技球の通過方向検出システムには、請求項5または6のいずれかに記載のデュアル近接スイッチと、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を信号処理して、前記制御回路に供給するインタフェース回路と、前記制御回路を含ませるようにすることができ、前記第3の所定の電圧値には、前記第1の電圧値、および前記第2の電圧値のいずれか低い電位の電圧値より低く、かつ、接地電位よりも高く設定されるようにすることができ、前記インタフェース回路には、前記正常通過検出信号の状態を比較判定する第1の比較回路と、前記異常検出信号の状態を比較判定する第2の比較回路とを含ませるようにすることができる。

【0018】

本発明の遊技球の通過方向検出システムにおける前記インタフェース回路には、短絡事故を検出する短絡事故検出手段と、前記断線事故を検出する断線事故検出手段と、前記電源異常を検出する電源異常検出手段とのうち、少なくとも1つをさらに含ませるようにすることができる。

【0019】

本発明の遊技機には、請求項1乃至6のいずれかに記載の1個のデュアル近接スイッチ、または、請求項7乃至9のいずれかに記載の遊技球の通過方向検出システムのうち、いずれか1個を含ませるようにすることができる。

【0020】

本発明の一側面のデュアル近接スイッチの制御方法は、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含むデュアル近接スイッチの制御方法であって、前記正常通過判定手段における、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定ステップと、前記異常判定手段における、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定ステップとを含む。

【0021】

本発明の一側面のプログラムは、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含むデュアル近接スイッチを制御するコンピュータに、前記正常通過判定手段における、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定ステップと、前記異常判定手段における、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定ステップとを含む処理を実行させる。

【0022】

本発明の一側面のデュアル近接スイッチにおいては、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチが含まれ、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果が後続の制御回路に伝達され、前記第1の近接スイッチにより先に通過の検出が開始され、かつ、遅れて前記第2の近接スイッチにより通過の検出が開始される検出順序であるか否かが判定され、その判定結果が、前記第1の近接スイッチによる先に通過の検出が開始され、かつ、遅れて前記第2の近接スイッチによる通過の検出が開始される検出順序である場合、1個の正常通過検出信号が出力され、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かが判定され、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号が出力される。

【0023】

すなわち、本発明の一側面のデュアル近接スイッチにおける、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチとは、例えば、遊技球の通過方向と共に通過を検出する遊技機に設けられる近接スイッチであり、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段とは、例えば、正常通過判定部であり、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とは、異常判定部である。

【0024】

すなわち、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、正常通過検出部により、1個の正常通過検出信号が出力されるので、正常に遊技球が通過したことが、制御回路に通知され、遊技球数の計数が可能となる。また、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、異常判定部より異常検出信号が出力されることになるので、第1の近接スイッチ、および第2の近接スイッチに対してリフティングによる不正がなされたか、または、低周波近傍電磁界による不正がなされたことが通知される。

【0025】

結果として、デュアル近接スイッチから直接、低周波近傍電磁界やリフティングによる不正の有無を示す異常検出信号と、遊技球の通過を検出する正常通過検出信号とを供給することができるので、後段の信号処理を容易なものとしつつ、不正を抑制しつつ適正に遊技球の通過を検出することが可能になる。

【発明の効果】

【0026】

本発明によれば、後段の信号処理を容易なものとしつつ、不正や異常を適切に検出して、遊技球を適切に計数することが可能となる。

【図面の簡単な説明】

【0027】

【図1】デュアル近接スイッチの構成例を説明する図である。

【図2】図1のデュアル近接スイッチの動作を説明する図である。

【図3】デュアル近接スイッチに用いられる本発明を適用したインタフェースシステムを説明する図である。

【図4】図3のデュアル近接スイッチの構成例を説明する図である。

【図5】図4の正常通過判定部、異常判定部、およびリセット部の回路構成例を説明する図である。

【図6】図3のインタフェース回路の構成例を説明する図である。

【図7】図3のデュアル近接スイッチの検出処理を説明するフローチャートである。

【図8】正常通過時における図3のデュアル近接スイッチの検出処理を説明する図である。

【図9】順序異常時における図3のデュアル近接スイッチの検出処理を説明する図である。

【図10】低周波近傍電磁界到来時における図3のデュアル近接スイッチの検出処理を説明する図である。

【図11】断線状態における図3のデュアル近接スイッチの検出処理を説明する図である。

【図12】短絡状態における図3のデュアル近接スイッチの検出処理を説明する図である。

【図13】図3のI/F回路における信号処理を説明するフローチャートである。

【図14】図3のCPUにおける計数処理を説明するフローチャートである。

【図15】図3のCPUにおける計数処理を説明する図である。

【図16】図3のCPUにおける計数処理を説明する図である。

【図17】図3のCPUにおける計数処理を説明する図である。

【図18】その他のインタフェースシステムを説明する図である。

【図19】図18のI/F回路の構成例を説明する図である。

【図20】正常通過時における図19のI/F回路による動作を説明する図である。

【図21】順序異常時における図19のI/F回路による動作を説明する図である。

【図22】低周波近傍電磁界到来時における図19のI/F回路による動作を説明する図である。

【図23】断線状態における図19のI/F回路による動作を説明する図である。

【図24】短絡状態における図19のI/F回路による動作を説明する図である。

【図25】図18のCPUにおける計数処理を説明するフローチャートである。

【図26】さらにその他のデュアル近接スイッチの構成例を示す図である。

【図27】図26のデュアル近接スイッチの出力合成部における出力合成処理を説明するフローチャートである。

【図28】正常通過時における図26のデュアル近接スイッチの出力合成部における出力合成処理を説明する図である。

【図29】順序異常時における図26のデュアル近接スイッチの出力合成部における出力合成処理を説明する図である。

【図30】低周波近傍電磁界到来時における図26のデュアル近接スイッチの出力合成部における出力合成処理を説明する図である。

【図31】汎用のパーソナルコンピュータを説明する図である。

【発明を実施するための形態】

【0028】

以下に本発明の実施の形態を説明するが、本発明の構成要件と、発明の詳細な説明に記載の実施の形態との対応関係を例示すると、次のようになる。この記載は、本発明をサポートする実施の形態が、発明の詳細な説明に記載されていることを確認するためのものである。従って、発明の詳細な説明中には記載されているが、本発明の構成要件に対応する実施の形態として、ここには記載されていない実施の形態があったとしても、そのことは、その実施の形態が、その構成要件に対応するものではないことを意味するものではない。逆に、実施の形態が構成要件に対応するものとしてここに記載されていたとしても、そのことは、その実施の形態が、その構成要件以外の構成要件には対応しないものであることを意味するものでもない。

【0029】

すなわち、本発明の一側面のデュアル近接スイッチ(例えば、図4のデュアル近接スイッチ101)は、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチ(例えば、図4の近接スイッチ161−1,161−2)を含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段(例えば、図4の正常通過判定部162)と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段(例えば、図4の異常判定部163)とを含む。

【0030】

前記正常通過判定手段、および前記異常判定手段には、それぞれ少なくとも1個の保持回路(例えば、図5のフリップフロップ回路FF1乃至FF4)を含ませるようにすることができ、前記正常通過判定手段、および前記異常判定手段には、前記保持回路の動作に基づいて、それぞれ前記正常通過検出信号、および前記異常検出信号を出力させるようにすることができ、前記第1の近接スイッチ、および前記第2の近接スイッチが、所定の検出状況となった場合、前記保持回路をリセットするリセット手段(例えば、図4のリセット部164)をさらに含ませるようにすることができる。

【0031】

前記リセット手段(例えば、図4のリセット部164)には、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない状態の場合、前記保持回路をリセット、または、前記第1の近接スイッチ、および前記第2の近接スイッチが、いずれも同時に前記遊技球の通過を検出しない期間全域において、前記保持回路をクリアさせるようにすることができる。

【0032】

前記異常検出信号が出力された場合、前記正常通過検出信号を、正常でないことを示す所定の状態に固定して出力する出力信号固定手段(例えば、図26の出力信号固定部302)をさらに含ませるようにすることができる。

【0033】

前記正常通過検出信号が検出された場合、第1の電圧値を出力し、前記正常通過検出信号、および、異常検出信号が検出されない場合、第2の電圧値を出力し、前記異常検出信号が検出された場合、第3の電圧値を出力する出力合成手段(例えば、図4の出力合成部153)をさらに含ませるようにすることができる。

【0034】

本発明の遊技球の通過方向検出システムには、請求項5または6のいずれかに記載のデュアル近接スイッチと、前記デュアル近接スイッチから伝送される前記正常通過検出信号、および前記異常検出信号を信号処理して、前記制御回路に供給するインタフェース回路と、前記制御回路を含ませるようにすることができ、前記第3の所定の電圧値には、前記第1の電圧値、および前記第2の電圧値のいずれか低い電位の電圧値より低く、かつ、接地電位よりも高く設定されるようにすることができ、前記インタフェース回路には、前記正常通過検出信号の状態を比較判定する第1の比較回路(例えば、図19の比較部221)と、前記異常検出信号の状態を比較判定する第2の比較回路(例えば、図19の比較部261)とを含ませるようにすることができる。

【0035】

本発明の遊技球の通過方向検出システムにおける前記インタフェース回路には、短絡事故を検出する短絡事故検出手段(例えば、図6の短絡検知部223)と、前記断線事故を検出する断線事故検出手段(例えば、図6の断線検知部222)と、前記電源異常を検出する電源異常検出手段(例えば、図6の電源監視部202)とのうち、少なくとも1つをさらに含ませるようにすることができる。

【0036】

本発明の一側面のデュアル近接スイッチの制御方法は、それぞれの検出領域が同一軸上に配置され、同一の遊技球を同時に検出できる期間を含み、かつ、同一の前記遊技球の検出開始、および検出終了のタイミングが異なるように構成されている、第1の近接スイッチ、および第2の近接スイッチを含み、前記第1の近接スイッチ、および前記第2の近接スイッチの検出結果に基づいて、前記遊技球の通過を検出し、前記遊技球の通過を示す検出結果を後続の制御回路に伝達するデュアル近接スイッチであって、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定手段と、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定手段とを含むデュアル近接スイッチの制御方法であって、前記正常通過判定手段における、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序であるか否かを判定し、その判定結果が、前記第1の近接スイッチが先に通過の検出を開始し、かつ、遅れて前記第2の近接スイッチが通過の検出を開始する検出順序である場合、1個の正常通過検出信号を出力する正常通過判定ステップ(例えば、図7のステップS16)と、前記異常判定手段における、前記検出順序と異なる検出順序であるか否か、または、前記同一の遊技球を同時に検出できる期間が存在するか否かを判定し、前記検出順序と異なる検出順序の場合、または、前記同一の遊技球を同時に検出できる期間が存在しなかった場合、最低1個の異常検出信号を出力する異常判定ステップ(例えば、図7のステップS18)とを含む。

【0037】

以下、本発明を実施するための形態(以下、実施の形態という)について説明する。なお、説明は以下の順序で行う。

1.第1の実施の形態(デュアル近接スイッチにおいて正常通過検出信号と異常検出信号を出力する構成例)

2.第2の実施の形態(インタフェース回路のその他の構成例)

3.第3の実施の形態(デュアル近接スイッチのその他の構成例)

【0038】

<1.第1の実施の形態>

[本発明を適用したデュアル近接スイッチの一実施の形態の構成例]

図1は、本発明を適用したインタフェース回路に遊技球の検出信号を供給するデュアル近接スイッチの構成例を示す断面図を示している。

【0039】

図1のデュアル近接スイッチ1においては、遊技球と略同径の貫通孔21が設けられており、遊技球P1乃至P3は、遊技球P1,P2,P3の順序で、図中の矢印で示される順方向に貫通孔21の入口側11から出口側12に向けて通過するように構成されている。尚、遊技球P1乃至P3について、特に区別する必要がない場合、単に遊技球Pと称するものとし、その他の複数存在する構成についても同様に称するものとする。

【0040】

また、貫通口21には、貫通口21と同軸に、入口側11から出口側12に向かって順に検出コイルL1,L2が設けられている。検出コイルL1,L2は貫通口21と同軸で、かつ貫通口21の外周部に巻回されてる。

【0041】

2つの検出コイルL1およびL2は、例えば、遊技球Pの直径(例えば、11mm)の1/4の間隔をおいて配置されている。尚、この間隔は、遊技球Pの直径の1/4に限るものではなく、検出コイルL1およびL2が、同一の遊技球の検出の開始タイミング、および終了タイミングが異なるようにできて、かつ、同時に検出している状態を含むようにできる間隔であれば、別の間隔であってもよいものである。

【0042】

このように、デュアル近接スイッチ1においては、貫通孔21の入口側11における検出コイルL1を含む第1の近接スイッチと、出口側12の検出コイルL2を含む第2の近接スイッチとの2系統の近接スイッチが内蔵されている。

【0043】

[デュアル近接スイッチの動作]

後述する本発明の遊技球を計数するインタフェースシステムは、遊技球P1乃至P3が貫通孔21を通過することにより、出力される第1の近接スイッチの検出信号S1と第2の近接スイッチの検出信号S2のタイミングを比較することで、1個の遊技球が正規の順方向に通過したか否かを判別し、順方向に通過した場合にのみ計数する。

【0044】

例えば、上述したように、2つの検出コイルL1およびL2が、遊技球Pの直径(例えば、11mm)の1/4の距離だけ離して配置される場合、遊技球P1乃至P3が順次、図1の矢印で示される順方向に貫通孔21を通過すると、第1の近接スイッチの検出信号S1と、第2の近接スイッチの検出信号S2は、図2の波形図で示されるように検出されることになる。図2においては、上段に検出信号S1の波形が示されており、下段に検出信号S2の波形が示されており、いずれも横軸が時間方向である。

【0045】

すなわち、図2の波形図で示されるように、検出信号S1は、時刻TP1において、Low信号からHi信号に立上り、時刻TP3においてHi信号からLow信号に立下がっている。同様に、検出信号S2は、時刻TP2において、Hi信号に立上り、時刻TP4において、Low信号に立下がっている。

【0046】

このように、デュアル近接スイッチ1は、例えば、遊技球Pが順方向に通過するとき、図2で示されるような、検出信号S1,S2に基づいた出力信号を、後述するI/F回路102(図3)に対して順次出力する。

【0047】

[本発明を適用したデュアル近接スイッチを用いたインタフェースシステムの構成例]

次に、図3を参照して、本発明を適用したデュアル近接スイッチを用いたインタフェースシステムの構成例について説明する。

【0048】

インタフェースシステムは、デュアル近接スイッチ101−1乃至101−7、電源VS、インタフェース(I/F)回路102、電源Vcc、CPU103、発報部104、および計数部105を備えている。すなわち、本発明のインタフェースシステムは、例えば、遊技機、または計数機内における遊技球の計数に係る処理を担うものである。

【0049】

デュアル近接スイッチ101(101−1乃至101−7)は、図1,図2を参照して説明したものとは異なるものであり、図4,図5を参照して詳細は後述するが、電源VSより電力供給を受けて、遊技球の通過を検出し、検出結果として、上述した2種類の検出信号S1,S2に基づいた出力信号をI/F回路102に出力する。

【0050】

インタフェース(I/F)回路102は、デュアル近接スイッチ101からの出力信号を受け付けて、所定の信号処理を施して、CPU103に供給する。

【0051】

I/F回路102は、I/F入力部111、および端子VS,A1乃至A7,GND,Vcc,Y1乃至Y7,Eを備えている。端子VSは、デュアル近接スイッチ101に供給する電源VSの電圧を監視する機能を含む。

【0052】

端子A1乃至A7は、デュアル近接スイッチ101からの出力信号を受け付ける。端子GNDは、接地端子である。

【0053】

端子Y1乃至Y7は、それぞれデュアル近接スイッチ101の出力信号に基づいた遊技球の通過が検出されているか否か、または異常を検出しているか否かを示す処理出力信号をCPU103に供給する。端子Eは、デュアル近接スイッチ101の検出信号に基づいた、デュアル近接スイッチ101の動作異常および不正異常の有無を示す異常検出信号を出力する。

【0054】

尚、I/F回路102の詳細な構成は、図6を参照して、後述するものとする。

【0055】

CPU103は、インタフェースシステムの全体の動作を管理する。CPU103は、カウント部121、異常判定部122、特定部123、異常種別判定部124、タイマ125、および発報出力部126を備えている。

【0056】

カウント部121は、端子Y1乃至Y7の処理出力信号に基づいて、遊技球の通過を認識し、遊技球数をカウントする信号を計数部105に供給する。計数部105は、この信号に基づいて遊技球数をカウントする。

【0057】

異常判定部122は、端子Eからの異常検出信号に基づいて、デュアル近接スイッチ101−1乃至101−7の異常の有無を判定する。特定部123は、端子Y1乃至Y7からの処理出力信号、または端子Eからの異常検出信号に基づいて、いずれのデュアル近接スイッチ101において遊技球の通過が検出されたか、または、異常が発生したのかを特定する。異常種別判定部124は、端子Eからの異常検出信号と、タイマ125により計時される時間に基づいて、デュアル近接スイッチ101に発生した異常の種別を判定する。発報出力部126は、異常が検出された場合、いずれのデュアル近接スイッチ101において、発生した異常の種別を示す情報を発報部104に出力し、発報させる。

【0058】

[デュアル近接スイッチ101の構成例]

次に、図4を参照して、デュアル近接スイッチ101の構成例について説明する。

【0059】

デュアル近接スイッチ101は、検出ブロック151、定電圧生成部152、および出力合成部153を備えている。

【0060】

検出ブロック151は、図1におけるデュアル近接スイッチ1と同一機能の近接スイッチ161−1,161−2に加えて、正常通過判定部162、異常判定部163、およびリセット部164を備えており、定電圧生成部152より電力供給を受けて、端子101cを介して接地電位GNDに接続されている。検出ブロック151は、遊技球が正常に通過しているか否かを示す正常通過検出信号、および異常が検出されているか否かを示す異常検出信号を出力する。より詳細には、近接スイッチ161−1,161−2は、いずれも同一の構成であり、それぞれ検出コイルL1,L2、発振部171−1,171−2、積分部172−1,172−2、および比較部173−1,173−2を備えている。検出コイルL1,L2は、図1を参照して説明した検出コイルL1,L2と同一のものである。

【0061】

発振部171−1,171−2は、それぞれ検出コイルL1,L2の遊技球の通過に伴って、発振信号を生成し、積分部172−1,172−2に供給する。積分部172−1,172−2は、それぞれ発振信号を積分して比較部173−1,173−2に出力する。比較部173−1,173−2は、積分部172−1,172−2より供給されてくる波形に基づいて、それぞれ所定の閾値VTH1,VTH2とを比較する。そして、比較部173−1,173−2は、閾値VTH1,VTH2よりも高い場合、Lowレベルの、高くない場合、Hiレベルの弁別信号からなる検出信号D1−1,D1−2を正常通過判定部162、異常判定部163、およびリセット部164に出力する。尚、この検出信号D1−1,D1−2は、それぞれ図2を参照して説明した、検出信号S1,S2と同一のものである。

【0062】

正常通過判定部162は、検出信号D1−1,D1−2の波形に基づいて、遊技球が正常に通過したか否かを判定し、判定結果に対応するHiの信号、またはLowの信号からなる正常通過判定信号D2−1を出力合成部153に出力する。正常通過判定部162は、リセット部164より供給されてくるリセット信号により正常通過判定信号を遊技球の通過が非検出の状態にリセットする。

【0063】

異常判定部163は、検出信号D1−1,D1−2の波形に基づいて、異常が発生したか否かを判定し、判定結果に対応するHiの信号、またはLowの信号からなる異常判定信号D2−2を出力合成部153に出力する。異常判定部163は、リセット部164より供給されてくるリセット信号により異常判定信号を異常が非検出の状態にリセットする。

【0064】

リセット部164は、検出信号D1−1,D1−2が、いずれも遊技球の通過を非検出の状態のとき、リセット信号を発生し、正常通過判定部162および異常判定部163に供給し、それぞれ正常通過判定信号D2−1、および異常判定信号D2−2を非検出の状態にリセットする。

【0065】

定電圧生成部152は、端子101aを介して電源VSより供給されてくる電力に基づいて、所定の電圧を維持して、検出ブロック151に電力を供給する。

【0066】

出力合成部153は、端子101aを介して電源VSから電力供給を受けて、検出ブロック151より供給されてくる正常通過判定信号D2−1、および異常判定部D2−2に基づいて、出力検出信号を生成して、出力端子101bよりI/F回路102に供給する。また、出力合成部153は、端子101cを介して接地電位GNDに接続されている。

【0067】

尚、端子101a、および端子101b間には、調整抵抗として、抵抗Rzが設けられている。

【0068】

[正常通過判定部162、異常判定部163、およびリセット部164の回路構成例]

次に、図5を参照して、正常通過判定部162、異常判定部163、リセット部164、および出力合成部153の回路構成例について説明する。

【0069】

正常通過判定部162は、フリップフロップ回路FF1,FF2、インバータI11、およびアンド回路AND1乃至3により構成されている。異常判定部163は、オア回路OR1乃至3、およびフリップフロップ回路FF3,FF4により構成されている。

【0070】

正常通過判定部162のフリップフロップ回路FF1の入力端子D1には、近接スイッチ161−1からの検出信号が入力される。クロック端子CLK1には、近接スイッチ161−2からの検出信号が入力される。プリセット端子PR1には、リセット部164のインバータI21の出力信号が入力される。クリア端子CLR1は、電源Vccに接続されている。正出力端子Q1は、クロック端子CLK1にHiの信号が供給されるタイミングで、入力端子D1に入力されている信号をアンド回路AND2の入力端子に出力する。負出力端子Q’1は、クロック端子CLK1にHiの信号が供給されるタイミングで、入力端子D1に入力されている信号を反転出力に変換して、オア回路OR1の入力端子に出力する。尚、図5においては、負出力端子には、符号Qの上部にバーで表記されているが、本明細書の記載においては、バーに代えて「’」を用いるものとする。

【0071】

また、正常通過判定部162のフリップフロップ回路FF2の入力端子D2には、近接スイッチ161−2からの検出信号が入力される。クロック端子CLK2には、近接スイッチ161−1からの弁別信号が入力される。プリセット端子PR2は、電源Vccに接続されている。クリア端子CLR2には、リセット部164のインバータI21の出力信号が入力される。正出力端子Q2は、クロック端子CLK2にHiの信号が供給されるタイミングで、入力端子D2に入力されている信号をオア回路OR1の入力端子に出力する。負出力端子Q’2は、クロック端子CLK2にHiの信号が供給されるタイミングで、入力端子D2に入力されている信号を反転信号に変換して、アンド回路AND2の入力端子に出力する。

【0072】

異常判定部163のインバータI1は、近接スイッチ161−1からの検出信号を、反転信号に変換して、フリップフロップ回路FF3の入力端子D3、およびフリップフロップ回路FF4のクロック端子CLK4に入力する。また、インバータI2は、近接スイッチ161−2からの検出信号を、反転信号に変換して、フリップフロップ回路FF3のクロック端子CLK3、およびフリップフロップ回路FF4の入力端子D4に入力する。

【0073】

フリップフロップ回路FF3のプリセット端子PR3には、リセット部164のインバータI21の出力信号が入力される。クリア端子CLR3は、電源Vccに接続されている。負出力端子Q’3は、クロック端子CLK3にLowの信号が供給されたタイミングで、入力端子D3に入力されている信号を反転信号に変換して、オア回路OR2の入力端子に出力する。

【0074】

また、異常判定部163のフリップフロップ回路FF4のクリア端子CLR4には、リセット部164のインバータI21の出力信号が入力される。プリセット端子PR4は、電源Vccに接続されている。正出力端子Q4は、クロック端子CLK4にLowの信号が供給されたタイミングで、入力端子D4に入力されている信号をオア回路OR2の入力端子に出力する。

【0075】

正常通過判定部162のインバータI11は、オア回路OR3より出力される信号を、反転信号に変換してアンド回路AND1の入力端子に出力する。アンド回路AND1は、インバータI11の出力信号と、近接スイッチ161−2の検出信号とを比較し、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をアンド回路AND3の入力端子に出力する。アンド回路AND2は、フリップフロップ回路FF1の正出力端子Q1の出力信号と、フリップフロップ回路FF2の負出力端子Q’2の出力信号とを比較して、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をアンド回路AND3の入力端子に出力する。アンド回路AND3は、アンド回路AND1,AND2の出力信号を比較し、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号を正常通過判定信号D2−1として出力合成部153に出力する。

【0076】

オア回路OR1は、フリップフロップ回路FF1の負出力端子Q’1の出力信号と、フリップフロップ回路FF2の正出力端子Q2の出力信号とを比較して、いずれかがHiである場合、Hiの信号を、それ以外の場合、Lowの信号をオア回路OR3の入力端子に出力する。オア回路OR2は、フリップフロップ回路FF3の負出力端子Q’3の出力信号と、フリップフロップ回路FF4の正出力端子Q4の出力信号とを比較して、いずれかがHiである場合、Hiの信号を、それ以外の場合、Lowの信号をオア回路OR3の入力端子に出力する。オア回路OR3は、オア回路OR1,OR2の出力信号を比較して、いずれかがHiである場合、Hiの信号を、それ以外の場合、Lowの信号を異常検出信号D2−2として出力合成部153に出力する。

【0077】

リセット部164のインバータI22,I23は、近接スイッチ161−1,161−2の検出信号を反転信号に変換してアンド回路AND12に出力する。アンド回路AND12は、インバータI22,I23の出力信号を比較して、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をアンド回路AND11の入力端子に出力する。アンド回路AND11は、オア回路OR3の出力信号と、アンド回路AND12の出力信号とを比較して、いずれもHiである場合のみHiの信号を、それ以外の場合、Lowの信号をインバータI21に出力する。インバータI21は、アンド回路AND11の出力信号を反転信号に変換して、フリップフロップ回路FF1,FF3のプリセット端子PR1,PR3、およびフリップフロップ回路FF2,FF4のクリア端子CLR2,CLR4に出力する。

【0078】

すなわち、図2の波形図で示されるように、遊技球が順方向で通過すれば、近接スイッチ161−1の検出信号である比較部173−1の弁別信号が立ち上がるタイミングでは、近接スイッチ161−2の検出信号である比較部173−2の弁別信号はLowの信号であり、逆に、近接スイッチ161−2の検出信号である比較部173−2の弁別信号が立ち上がるタイミングでは、近接スイッチ161−1の検出信号である比較部173−1の弁別信号はHiの信号となるため、フリップフロップ回路FF1の正出力端子Q1からはHiの信号が出力され続け、フリップフロップ回路FF2の負出力端子Q’2からはHiの信号が出力され続けることになる。

【0079】

同様に、近接スイッチ161−1の検出信号である比較部173−1の弁別信号が立ち下がるタイミングでは、近接スイッチ161−2の検出信号である比較部173−2の弁別信号はHiの信号であり、逆に、近接スイッチ161−2の検出信号である比較部173−2の弁別信号が立ち下がるタイミングでは、近接スイッチ161−1の検出信号である比較部173−1の弁別信号はLowの信号となるため、フリップフロップ回路FF3の負出力端子Q’3からはLowの信号が出力され続け、フリップフロップ回路FF4の正出力端子Q4からはLowの信号が出力され続けることになる。

【0080】

結果として、順方向に遊技球が通過している状態であれば、アンド回路AND2は、常にHiの信号を出力し続けるので、オア回路OR3から異常検出信号であるHiの信号が供給されて、インバータI11がLowの信号を出力をしていない限り、近接スイッチ161−2の検出信号である比較部173−2の弁別信号の出力波形が、アンド回路AND3より出力される。また、上述した比較部173−1,173−2の立上りおよび立下りの条件が満たされない場合、オア回路OR1,OR2のいずれかがHiの信号となるため、オア回路OR3は、Hiの信号の異常検出信号を出力することになる。

【0081】

フリップフロップ回路FF1乃至FF4は、一旦、異常があったものと判定される信号を記憶すると、その状態が維持されてしまうため、プリセット、またはクリア操作がない限り異常検出信号が出力され続け、遊技球の通過が非検出の状態が維持されてしまう。しかしながら、近接スイッチ161−1,161−2の検出信号である比較部173−1,173−2からの弁別信号がいずれも非検出状態になると、リセット部164のインバータI22,I23からはいずれもHiの信号が出力される。また、オア回路OR3は、異常検出信号であるHiの信号を出力し続けているため、アンド回路AND11は、Hiの信号を出力する。これにより、インバータI21は、Lowの信号をリセット信号として、フリップフロップ回路FF1,FF3のプリセット端子PR1,PR3、およびフリップフロップ回路FF2,FF4のクリア端子CLR2,CLR4に出力する。結果として、比較部173−1,173−2からの弁別信号がいずれも非検出状態になれば、フリップフロップ回路FF1乃至FF4がプリセット、またはクリアされることにより、異常検出信号の出力が停止されて、通常の状態にリセットされる。

【0082】

出力合成部153は、第1電位発生部181、第2電位発生部182、および第3電位発生部183より構成されている。第1電位発生部181は、トランジスタTR11,TR12、および抵抗R11より構成されている。トランジスタTR11のコレクタが出力端子101b、ダイオードD1のアノード、およびツェナーダイオードZDのカソードに接続されており、エミッタが抵抗R11の一方の端部、およびトランジスタTR12のベースに接続されている。また、トランジスタTR11のベースは、トランジスタTR12のコレクタ、および抵抗Raを介して端子101aに接続されている。トランジスタTR12のベースは、トランジスタTR11のエミッタ、および抵抗R11の一方の端部に接続され、エミッタは端子101cを介して接地電位GNDに接続されており、コレクタは、トランジスタTR11のベース、および抵抗Raを介して端子101aに接続されている。抵抗R11は、一方の端部がトランジスタTR11のエミッタ、およびトランジスタTR12のベースに接続され、他方の端部が端子101cに接続されている。

【0083】

すなわち、第1電位発生部181においては、トランジスタTR11が常にオンの状態となるため、抵抗R11により調整された第1電位V1が端子101bより出力される。尚、この第1電位V1は、後述する高位反転電圧である。

【0084】

第2電位発生部182は、インバータI51、トランジスタTR21、ツェナーダイオードZD、および抵抗R21より構成されている。インバータI51は、検出ブロック151における正常通過判定部162からの正常通過判定信号D2−1を反転出力に変換してトランジスタTR21のベース、および抵抗R21の一方の端部に出力する。トランジスタTR21のベースは、正常通過判定部162のアンド回路AND3の出力端子、および抵抗R21の一方の端部に接続され、エミッタは、抵抗R21の他方の端部、および接地電位GNDに接続され、コレクタは、ツェナーダイオードZDのアノードに接続されている。ツェナーダイオードZDのアノードは、トランジスタTR21のコレクタに接続されており、カソードは、ダイオードD1のアノード、トランジスタTR11のコレクタ、および端子101bに接続されている。

【0085】

すなわち、第1電位発生部181は、正常通過判定信号D2−1がHiの信号であるとき、インバータI51からの反転出力によりトランジスタTR21がオフとなり、ツェナーダイオードZDのツェナー電位ZDによる電圧降下がなくなるため、端子101bより第1電位発生部181に定電流が生成され、抵抗Rzの調整により第1電位V1が出力される。一方、第2電位発生部182は、正常通過判定信号D2−1がLowの信号であるとき、インバータI51からの反転出力によりトランジスタTR21がオンとなり、ツェナーダイオードZDのツェナー電位ZDにより決定される第2電位V2が端子101bより出力される。尚、この第2電位V2が、後述する低位反転電圧である。

【0086】

第3電位発生部183は、ダイオードD1,D2、トランジスタTR31、および抵抗R31より構成されている。トランジスタTR31は、コレクタがダイオードD2のカソードに接続され、エミッタが接地電位GND、および抵抗R31の他方の端部と接続され、ベースが抵抗R31の一方の端部、およびオア回路OR3の出力端子に接続されている。抵抗R31は、一方の端部がトランジスタTR31のベース、およびオア回路OR3の出力端子に接続されており、他方の端部がトランジスタTR31のエミッタおよび接地電位GNDに接続されている。ダイオードD1,D2は、カスケードに接続されており、D2のカソードは、トランジスタTR31のコレクタに接続され、ダイオードD1のアノードは、ツェナーダイオードZDのカソード、トランジスタTR11のコレクタ、およびベース、トランジスタTR12のコレクタ、および端子101cに接続されている。

【0087】

すなわち、第3電位発生部183は、異常が検出されたことを示す異常検出信号が供給されるとトランジスタTR31がオンの状態となる。この結果、第1電位発生部181、および第2電位発生部182の動作とは無関係にダイオードD1,D2による電圧降下が発生し、第1電位V1よりダイオードD1,D2分の電圧降下により第2電位V2よりも低い、第3電位V3が端子101bより出力される。

【0088】

[I/F回路102の構成例]

次に、図6を参照して、I/F回路102の構成例について説明する。尚、図6においては、1個のデュアル近接スイッチ101−1の接続に必要とされる構成例のみが示されており、端子VS,A1乃至A7,GND,Vcc,Y1乃至Y7,Eのみが示され、その他の構成については、省略して示されている。

【0089】

I/F入力部111には、入力処理部201−1乃至201−7、電源監視部202、異常検知処理部203,225、およびトランジスタTR41が設けられている。入力処理部201は、端子A1より供給されてくる検出信号に基づいて、遊技球の通過の有無を検出する信号を出力すると共に、断線事故、および短絡事故を判定して、断線事故、および短絡事故が発生していると判定した場合、異常検出信号を発生する。尚、端子A2乃至A7については、入力処理部201−1と同一のものが接続される。また、以降、端子A1に供給されてくる出力検出信号を出力検出信号A1とも称する。

【0090】

電源監視部202は、電源VSの電圧と、所定の閾値とを比較して、電源VSの電圧が所定の閾値よりも低位となり、異常低下したと判定する場合、電源異常の発生を検知して、異常が発生したことを異常検知処理部203,225に供給する。

【0091】

入力処理部201は、比較部221、断線検知部222、短絡検知部223、順序異常検知部224、および異常検知処理部225を備えている。

【0092】

断線検知部222は、出力検出信号A1の電位がHiの状態となった電位よりも高位の断線検知閾値電圧とを比較し、これを超えたとき断線事故を検知し、対応する異常検出信号を発生して異常検知処理部203,225に通知する。

【0093】

短絡検知部223は、出力検出信号A1の電位がLowの状態となった電位よりも低位の短絡検知閾値電圧とを比較し、これを下回ったとき短絡事故を検知し、対応する異常検出信号を発生して異常検知処理部203,225に通知する。

【0094】

順序異常検知部224は、出力検出信号A1の電位がLowの状態となった電位よりも低位であって、短絡検知閾値電圧よりも高位の順序異常閾値電圧とを比較し、短絡検知閾値電圧を上回って、かつ、順序異常閾値電圧を下回ったとき順序異常を検知し、対応する異常検出信号を発生して異常検知処理部203,225に通知する。

【0095】

異常検知処理部225は、電源監視部202、断線検知部222、短絡検知部223および順序異常検知部224のいずれかから異常が検知されたことを示す信号が供給されると、動作の異常を示すHiの信号からなる異常検出信号を後段のトランジスタTR52のベースに供給し、それ以外のときLowの信号を出力する。

【0096】

比較部221は、Hiとなる弁別信号を出力するとき、所定の電位より低位であって、かつ、出力検出信号A1がLowとなったときの電位よりも高位となる低位反転閾値VTH3Lと、出力検出信号A1の電位とを比較し、出力検出信号A1の電位が低位反転閾値よりも低位に変化したときLowの弁別信号を後段のトランジスタTR51のベースに出力する。比較部221は、Lowとなる弁別信号を出力するとき、所定の電位より高位であって、かつ、出力検出信号A1がHiとなったときの電位よりも低位となる高位反転閾値VTH3Hと、出力検出信号A1の電位とを比較し、出力検出信号A1の電位が高位反転閾値よりも高位に変化したときHiの弁別信号を後段のトランジスタTR51のベースに出力する。

【0097】

すなわち、比較部221は、出力検出信号A1が、高位反転閾値よりも高位になると、弁別信号としてHiの信号を出力すると共に、閾値を低位反転閾値に変更し、逆に、出力検出信号A1が、低位反転閾値よりも低位になると、弁別信号としてLowの信号を出力すると共に、閾値を高位反転閾値に変更する動作を繰り返す。

【0098】

トランジスタTR51は、ベースが、比較部221の出力端子に接続されており、エミッタが接地電位に接続されており、コレクタが端子Y1、およびトランジスタTR52のコレクタに接続されている。

【0099】

トランジスタTR52は、ベースが、異常検知処理部225の出力端子に接続されており、エミッタが接地電位に接続されており、コレクタが端子Y1、およびトランジスタTR51のコレクタに接続されている。

【0100】

異常検知処理部203は、電源監視部202、並びに、入力処理部201−1乃至201−7の全ての断線検知部222、短絡検知部223、および順序異常検知部224からの異常検出信号を受け付けて、異常を検出したとき異常検出信号を後段のトランジスタTR41のベースに出力する。トランジスタTR41は、ベースが、異常検知処理部203の出力端子に接続されており、エミッタが接地電位に接続されており、コレクタが端子Eに接続されている。

【0101】

尚、電源監視部202、断線検知部222、短絡検知部223、および比較部221の詳細な構成については、本出願人が出願している特開2005−318358を参照されたい。

【0102】

[デュアル近接スイッチによる検出処理]

次に、図7のフローチャートを参照して、遊技球の正常通過と異常を検出する処理について説明する。ただし、図7のフローチャートにおける処理の説明は、各種の動作状態における回路の動作を説明するものである。このため、図7のフローチャートにおいては、判断処理ステップにおける主体は存在せず、単に区別すべき条件のみが記述されている。

【0103】

すなわち、ステップS11において、電源に断線が発生しておらず、ステップS12において、短絡状態でもなく、ステップS13において、電源電圧の異常低下もない場合、処理は、ステップS14に進む。

【0104】

ステップS14において、例えば、図8の最上段で示されるように、近接スイッチ161−1の検出信号D1−1が、時刻T1において、立ち上がっているような場合、遊技球の通過が検出されているものとみなされ、処理は、ステップS15に進む。

【0105】

ステップS15において、例えば、遊技球が順方向に通過するとき、近接スイッチ161−1,161−2の検出信号D1−1,D1−2が、図8の最上段、および2段目で示されるような関係となる。すなわち、検出信号D1−1に対応した弁別信号が、立ち上がる時刻T1,T5においては、検出信号D1−2は、Low信号である。また、検出信号D1−2が、立ち上がる時刻T2,T6においては、検出信号D1−1は、Hiの信号である。さらに、検出信号D1−1が、立ち下がる時刻T3,T7においては、検出信号D1−2は、Hi信号である。また、検出信号D1−2が、立ち下がる時刻T4,T8においては、検出信号D1−1は、Lowの信号である。

【0106】

尚、図8乃至図12においては、最上段が近接スイッチ161−1より供給されてくる検出信号D1−1を、2段目が近接スイッチ161−2より供給されてくる検出信号D1−2を、3段目が正常通過判定部162より出力される正常通過判定信号D2−1を、4段目が異常判定部163より出力される異常検出信号D2−2を、5段目が、出力合成部153より出力され、端子A1に入力される出力検出信号A1を、6段目が端子Y1からの出力信号を、7段目が端子Eから出力される信号をそれぞれ示している。また、5段目に示される閾値は、閾値Vth−cが、断線事故の有無を判別する閾値であり、閾値Vth−Hiが、比較部221における弁別信号がLowの信号であるときの高位反転閾値であり、閾値Vth−Lowが、弁別信号がHiの信号であるときの低位反転閾値であり、閾値Vth−tが、順序異常の有無を判別する閾値であり、閾値Vth−sが、短絡事故の有無を判別する閾値である。

【0107】

ステップS16において、出力合成部153は、I/F回路102の端子A1に対して遊技球の正常な通過が検出されたことを示す第1電位V1となる出力信号を供給する。すなわち、この場合、正常通過判定部162は、図8の3段目で示されるように、2段目で示される近接スイッチ161−2からの出力信号と同様の正常通過判定信号を出力合成部153に供給する。また、異常判定部163は、異常を検出しないので、図8の4段目で示されるようにLowの信号の状態が維持される。この結果、出力合成部153における第2電位発生部182のトランジスタTR21がオフの状態となり、ツェナーダイオードZDによる効果がなくなると共に、第3電位発生部183のトランジスタTR31がオフの状態であるので、第1電位発生部181により発生される第1電位V1がそのまま端子101bより出力されて、図8の5段目における時刻T2乃至T4、およびT6乃至T8で示されるように、第1電位V1の波形が出力される。

【0108】

一方、ステップS14において、遊技球の通過が検出されていない場合、すなわち、近接スイッチ161−1,161−2より供給されてくる検出信号がいずれもLowの信号である場合、ステップS17において、出力合成部153は、I/F回路102の端子A1に対して遊技球の異常がない状態で遊技球の通過が検出されていないことを示す第2電位V2となる出力信号を供給する。すなわち、出力合成部153における第2電位発生部182のトランジスタTR21がオンの状態となり、ツェナーダイオードZDによる効果が生じると共に、第3電位発生部182のトランジスタTR31がオフの状態であるので、ツェナー電位分がそのまま第2電位V2として端子101bより出力されて、図8の5段目における時刻T4乃至T6で示されるように、第2電位V2の波形が出力される。

【0109】

また、ステップS15において、例えば、図9で示されるような波形が、異常判定部163に供給されてくる場合、遊技球が図1で示される順方向に通過していないと判定されて、処理は、ステップS18に進む。すなわち、図9の時刻T11で示されるように、近接スイッチ161−2の検出信号D1−2が立ち上がるとき、近接スイッチ161−1の検出信号D1−1が、Hiの信号であるべきであるところが、Low信号となっており、順方向に通過することを示さない波形となっている。図9の最上段、および2段目の波形は、遊技球が逆方向に移動した場合に検出される波形である。すなわち、リフティングなどの不正行為がなされることにより、このように逆方向に遊技球が移動するような波形が得られた場合、上述したように順方向に移動するときに発生する波形の条件を満たさないため、順方向に移動していないことが検出される。

【0110】

ステップS18において、出力合成部153は、I/F回路102の端子A1に対して遊技球の異常が検出されていることを示す第3電位V3となる出力信号を供給する。すなわち、出力合成部153における第3電位発生部183のトランジスタTR31がオンの状態となるため、第2電位発生部182の動作状態に関わらず、ダイオードD1,D2の順方向電位がそのまま第3電位V3として端子101bより出力されて、図9の5段目における時刻T11乃至T12,T13乃至T14で示されるように、第3電位V3の波形が出力される。

【0111】

ステップS19において、近接スイッチ161−1,161−2のそれぞれより供給されてくる検出信号D1−1,D1−2がいずれも遊技球の通過を示さないLowの信号であるか否かが判定されて、いずれもLowの信号となるまで、同様の処理を繰り返す。そして、ステップS19において、例えば、図9の時刻T12乃至T13においては、いずれの弁別信号もLowの信号となるので、この場合、ステップS20において、リセット部164は、異常判定部163に対してリセット信号を発生し供給する。この処理により、図9の4段目の時刻T12乃至T13で示されるように、異常判定部191は、異常合成部192に対しての異常検出信号の発生を停止して、異常の検出を示さない第2電位V2からなる波形を出力する。

【0112】

以上のように、遊技球が順方向に通過しているか否かが検出されることにより、リフティングなどの不正行為がなされる場合、逆方向の遊技球の通過が検出されると、異常を示す第3電位V3の出力を発生される。結果として、リフティングなどの不正行為があっても異常が発生したことを認識することが可能になる。

【0113】

尚、ステップS15において、例えば、低周波近傍電磁界が一定の周期でオンまたはオフして発生した場合、近接スイッチ161−1,161−2のそれぞれより供給されてくる検出信号D1−1,D1−2は、図10の最上段および2段目で示されるような波形となる。すなわち、コイルL1,L2の発信周波数は通常同一ではないため、図10で示されるように、コイルL1の周波数に対応するように低周波近傍電磁界が発生されていた場合、コイルL1のみ、すなわち、近接スイッチ161−1の検出信号D1−1のみが影響を受ける。しかしながら、コイルL2には影響せず、近接スイッチ161−2の検出信号D1−2には影響がない。すなわち、低周波近傍電磁界が発生しても、いずれか一方の検出信号に影響が出ても他方の検出信号に影響しない。

【0114】

このような条件の下、上述した順方向へ通過条件に照らして波形を分析すると、図10で示されるように、時刻T21においては、近接スイッチ161−2の検出信号D1−2が立ち上がるとき、近接スイッチ161−1の検出信号D1−1はHiであるので、この時刻においては、異常は検出されない。このため、異常判定部163からは、異常検出信号が出力されない。また、時刻T22においても、近接スイッチ161−1の検出信号D1−1の立下りのタイミングにおいて、近接スイッチ161−2の検出信号D1−2はHiの信号であるので、異常判定部163からは異常検出信号が出力されない。

【0115】

ところが、時刻T23において、近接スイッチ161−1の検出信号D1−1の立ち上がりのタイミングにおいては、近接スイッチ161−2の検出信号D1−2がHiであるので、正規の順方向に遊技球が通過するときの条件を満たさない状態となるため、異常判定部163は、異常検出信号を出力する。このため、出力合成部153からは順序異常を示す第3電位V3からなる出力信号が出力される。

【0116】

結果として、低周波近傍電磁界が発生されても、順序異常を示す信号が検出信号D1−1,D1−2が共にLowの信号となるまで発生されることとなる。

【0117】

一方、ステップS11において、例えば、図11の5段目における時刻T31で示されるように、デュアル近接スイッチ101において断線事故が発生すると、ステップS22において、端子A1の信号は、閾値Vth−cよりも高い電源電圧VSとなる。

【0118】

また、ステップS12において、電源異常が検出された場合、およびステップS13において、短絡事故が検出された場合、例えば、図12の5段目における時刻T41で示されるように、デュアル近接スイッチ101において短絡事故が発生すると、ステップS21において、端子A1の信号は、閾値Vth−sよりも低い接地電位となる。

【0119】

以上のように、デュアル近接スイッチ101は、動作状態に応じて、5種類の出力検出信号A1を出力する。すなわち、デュアル近接スイッチ101は、断線事故時においては、電源電圧VSを、遊技球の正常通過検出時においては、第1電位V1を、遊技球の通過非検出時においては、第2電位V2を、順序異常検出時には、第3電位V3を、短絡事故または電源Vsの異常低下時には、接地電位をそれぞれ出力する。そして、デュアル近接スイッチ101は、順序異常検出後においても、異常検が発生していることを示す出力検出信号を出力し続けるのではなく、通過非検出の状態になると、リセット部164により通常の状態に復帰する。

【0120】

[図6のI/F回路102による信号処理]

次に、図13のフローチャートを参照して、図6のI/F回路102による信号処理について説明する。

【0121】

ステップS41において、異常検知処理部225は、断線検知部222より異常検出信号が供給されてきたか否かを判定する。断線検知部222より異常検出信号が供給されてきていない場合、処理は、ステップS42に進む。

【0122】

ステップS42において、異常検知処理部225は、電源監視部202より電源VSの異常低下の検出による異常検出信号が供給されてきたか否かを判定する。ステップS42において、電源VSの異常低下の検出により異常検出信号がない場合、処理は、ステップS43に進む。

【0123】

ステップS43において、異常検知処理部225は、短絡検知部223より異常検出信号が供給されてきたか否かを判定する。短絡検知部223より異常検出信号が供給されてきていない場合、処理は、ステップS44に進む。

【0124】

すなわち、ステップS41乃至S43の処理により、断線事故、電源異常、および短絡事故のいずれもが発生していないと判定された場合、ステップS44において、異常検知処理部225は、いずれも、動作に異常がないことを示すLowの信号をトランジスタTR52に出力する。この結果、トランジスタTR52は、オフの状態となるため、比較部221の弁別結果に対応したトランジスタTR51のコレクタ出力が端子Y1を介して、CPU103に対して供給される。

【0125】

ステップS45において、順序異常検知部224は、端子A1を介して供給される検出信号が、遊技球の通過を示す第1電位V1の信号として供給されたか否かを判定する。例えば、図8の最上段で示されるように、端子A1より供給されてきた検出信号が、時刻T2において、立ち上がっているような場合、遊技球の通過が検出されているものとみなされ、処理は、ステップS46に進む。

【0126】

ステップS46において、順序異常検知部224は、端子A1を介して供給されてくるデュアル近接スイッチの検出信号に基づいて、遊技球が順方向に通過しているか否かを判定する。すなわち、例えば、遊技球が順方向に通過するとき、端子A1を介して供給されてくるデュアル近接スイッチの検出信号は、図8の5段目で示されるように、第1電位V1であるので、順序異常検知部224は、端子A1の信号が第1電位V1であるか否かに基づいて、順序異常が発生しているか否かを判定する。

【0127】