デュプレクサ

【課題】アイソレーション特性を維持しつつ、ダブルモード型フィルタの入出力グランドインダクタンス及び共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを提供する。

【解決手段】送信フィルタ3と、受信フィルタ2と、第一の基板11と、第一の基板11上にパターン形成されたダイアタッチ層5と、第二の基板12と、第一の基板11と第二の基板12との間に位置する内層6を有するパッケージ基板1と、受信フィルタ2の一部を構成するダブルモード型フィルタと、ダイアタッチ層5の一部を構成する前記ダブルモード型フィルタの入力及び出力グランドを共通のグランドとする共通グランド端子と、内層6の一部を構成する前記ダブルモード型フィルタの入力側のグランド端子と、前記入力側のグランド端子とは分離して形成された内層6の一部を構成する前記ダブルモード型フィルタの出力側のグランド端子と、を有するデュプレクサ。

【解決手段】送信フィルタ3と、受信フィルタ2と、第一の基板11と、第一の基板11上にパターン形成されたダイアタッチ層5と、第二の基板12と、第一の基板11と第二の基板12との間に位置する内層6を有するパッケージ基板1と、受信フィルタ2の一部を構成するダブルモード型フィルタと、ダイアタッチ層5の一部を構成する前記ダブルモード型フィルタの入力及び出力グランドを共通のグランドとする共通グランド端子と、内層6の一部を構成する前記ダブルモード型フィルタの入力側のグランド端子と、前記入力側のグランド端子とは分離して形成された内層6の一部を構成する前記ダブルモード型フィルタの出力側のグランド端子と、を有するデュプレクサ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、携帯電話などの無線装置に使用されるデュプレクサに関する。

【背景技術】

【0002】

近年、移動体通信システムの発展に伴って携帯電話、携帯情報端末等が急速に普及してきた。携帯電話ではマルチバンド・マルチモード化が急速に進展しつつあるのに加え、無線LAN、Bluetooth(登録商標)、GPSといった付属の無線インターフェイスの搭載も進む方向にあり、携帯電話内のRF回路部への小型化、集積化の要求も強い。こうした状況の中、アンテナ共用器等として用いられ、RF回路部における主要部品の1つであるデュプレクサへの小型化、高性能化の要求が強くなっている。

【0003】

デュプレクサは、アンテナ共用器、分波器として用いられ、周波数の異なる送信信号と受信信号をインピーダンスの相違を利用して分離する。送信信号、受信信号がそれぞれ一つの場合、デュプレクサは、送信用フィルタと受信用フィルタとをそれぞれ一つ具備する。三つ以上のフィルタを共有することも可能であり、例えば三つの場合はトリプレクサと呼ばれることがあるが、本願においてはこれらを纏めてデュプレクサと呼ぶことにする。そして、これらのフィルタには一端子対共振器がよく使用される。共振器としては、従来広く使用されてきたサイズの大きい誘電体共振器に替わり、最近は特許文献1に記載のように、小型の圧電薄膜共振器(FBAR:Film Bulk Acoustic Wave)或いは弾性表面波(SAW:Surface

Acoustic Wave)共振器がよく使用される。

【0004】

弾性表面波共振器は、圧電基板上に入力端子と出力端子とに接続された櫛歯状電極指(IDT:Interdigital Transducer)と、必要に応じてIDTの両側に配置される反射器とから構成される。IDTおよび反射器は例えばアルミニウム(Al)等の金属で形成される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−271230号公報

【特許文献2】特開2005−318307号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述のような背景から、デュプレクサの小型化に伴い、送信端子から受信端子への信号漏れが大きくなり、アイソレーション特性の劣化につながっている。さらに、カスタム部品としてのさらなる高性能化の要求を満たすためには、デュプレクサ内の各種電極パターンを独立に調節できるなどの設計自由度の高いデュプレクサが求められる。

【0007】

特許文献1に開示される技術においては、受信フィルタのグランドパターンが、他のパターンから分離されているため、アイソレーション特性を向上することができる。また、特許文献2に開示される技術においては、ダイアタッチ層でフィルタの入出力グランドパターンを分離して、バランス出力型フィルタのバランス特性の改善を図ると共にグランドインダクタンスを小さくしている。

【0008】

しかしながら、これらの技術を組み合わせても、アイソレーション特性を維持しつつ、ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び入出力が共通する共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを得ることができなかった。

【0009】

本発明は、上記課題に鑑みなされたものであり、アイソレーション特性を維持しつつ、ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明は、アンテナ端子と送信端子との間に接続された送信フィルタと、前記アンテナ端子と受信端子との間に配置される受信フィルタと、第一の基板と、前記第一の基板上にパターン形成されたダイアタッチ層と、第二の基板と、前記第一の基板と前記第二の基板との間に位置する内層を有するパッケージ基板と、前記受信フィルタの一部を構成するダブルモード型フィルタと、前記ダイアタッチ層の一部を構成する前記ダブルモード型フィルタの入力グランド及び出力グランドを共通のグランドとする共通グランド端子と、前記内層の一部を構成する前記ダブルモード型フィルタの入力側のグランド端子と、前記入力側のグランド端子とは分離して形成された前記内層の一部を構成する前記ダブルモード型フィルタの出力側のグランド端子と、を有するデュプレクサである。本発明によれば、アイソレーション特性を維持しつつ、前記ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び共通グランドインダクタンスをそれぞれ独立に調節することができる。

【0011】

上記構成において、前記内層における前記ダブルモード型フィルタの入力グランドと出力グランドは、スリットにより分離されている構成とすることができる。

【0012】

上記構成において、前記ダブルモード型フィルタは並列に複数に分割されている構成とすることができる。かかる構成によれば、耐電圧が高く、より高周波帯域となっても挿入損失の低いフィルタを構成要素としたデュプレクサを得ることができる。

【0013】

上記構成において、前記ダブルモード型フィルタは、前記スリットと少なくとも一部が重なる位置に配置されている構成とすることができる。かかる構成によれば、受信フィルタ上のグランドパッド配置の設計自由度が広くなり、前記ダブルモード型フィルタの入出力グランドのインダクタンスを適正値にする為のチップレイアウトの調整が容易になる。

【0014】

上記構成において、前記受信フィルタは、複数のグランド端子に接続するためのバンプを有し、前記グランド端子に接続するためのバンプは、前記入力グランドパターン又は前記出力グランドパターンの少なくとも一部と重なっており、前記グランド端子に接続するためのバンプは、前記スリットとは重なっていない構成とすることができる。かかる構成によれば、パッケージ基板のコプラナリティ(平坦性)の悪化を防ぐことができる。

【0015】

上記構成において、前記第一の基板上の外周部に形成されたシールリング部を有し、前記シールリング部は、前記送信フィルタのグランド又は/及び前記受信フィルタのグランドと共通のグランドとなっている構成とすることができる。かかる構成によれば、電磁的な遮蔽効果が得られ、使用時に他の電子部品等による外部影響を受けにくくなることができる。

【0016】

上記構成において、前記第一の基板上の外周部に形成されたシールリング部を有し、前記シールリング部は、前記送信フィルタのグランド及び前記受信フィルタのグランドから電気的に独立している構成とすることができる。かかる構成によれば、グランドのレベルが低い場合に容量結合等による特性の劣化を防ぐとことができる。

【0017】

上記構成において、前記受信フィルタは、平衡出力とする構成とすることができる。かかる構成によれば、1入力2出力の受信フィルタを備えたデュプレクサを得られる。

【0018】

上記構成において、前記受信フィルタは、直列共振器と並列共振器を備えたラダー型フィルタを有し、前記ダイアタッチ層における前記並列共振器のグランドと前記ダブルモード型フィルタのグランドは分離しているかかる構成によれば、受信フィルタにラダー型フィルタを含めた場合において、並列共振器のグランドインダクタンスも独立して調整することができる。

【発明の効果】

【0019】

本発明によれば、アイソレーション特性を維持しつつ、ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び入出力が共通する共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを得ることができる。

【図面の簡単な説明】

【0020】

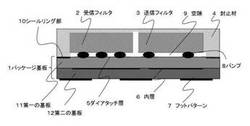

【図1】本発明の実施例1に係るデュプレクサの断面図。

【図2】実施例1に係るデュプレクサのパッケージ基板の各層のパターンを説明するための図。

【図3】実施例1に係るデュプレクサに用いられる受信フィルタ及び送信フィルタを説明するための図。

【図4】実施例1に係る受信フィルタ2に含まれるDMSを示す図。

【図5】実施例1に係るデュプレクサの等価回路を示す図。

【図6】実施例1に係るデュプレクサのスリットとダブルモード型フィルタの重なりを示す図。

【図7】本発明の実施例2に係るデュプレクサの特徴を説明するための図。

【図8】実施例2に係るデュプレクサの特性を示す図。

【発明を実施するための形態】

【実施例1】

【0021】

実施例1に係るデュプレクサの断面構造を図1に示す。かかる断面は、後述する図6におけるA−A‘断面に相当する。図1に示すように、実施例1によるデュプレクサは、パッケージ基板1上に受信フィルタ2と送信フィルタ3がフリップチップ方式によりバンプ8を介して実装され、封止材4により封止された構成を基本構成とする。受信フィルタ2と送信フィルタ3は一つのチップで構成されても良いし、複数のチップから構成されてもよい。より詳細には、パッケージ基板1は、第一の基板11及び第二の基板12からなり、第一の基板11のフィルタ実装面にはダイアタッチ層5の電極パターンならびにシールリング部10が形成され、第一の基板11と第二の基板12の間には内層6の電極パターンが形成され、さらに、第二の基板12の裏面には外部接続用のフットパターン7が形成されている。第一の基板11及び第二の基板12は、アルミナセラミクス、ガラスセラミクス、或いは樹脂などから形成されている。本実施例では第一の基板の厚みは100μm、第二の基板の厚みは51μmである。また、デュプレクサのサイズは、2.0mm×1.6mm角で、厚みは0.58mmである。本実施例では、パッケージ基板1は二層の基板により構成されているが、より複雑な電気回路を構成する必要がある場合には、三層以上の基板から構成してもよい。ダイアタッチ層5、内層6及びフットパターン7は、銅或いはアルミニウムなどの導電性部材により形成され、図示は省略するが、第一の基板11及び第二の基板12をそれぞれ貫通して選択的に配設された複数のビアにより接続され、電気的に導通可能としている。かかる導電層パターンが形成された第一の基板11及び第二の基板12は積層され、一体化され、パッケージ基板1が構成される。ダイアタッチ層5の上には、例えば半田などにより形成された複数のバンプ8を介して受信フィルタ2及び送信フィルタ3がフリップチップ実装され、フィルタとパッケージ基板1と電気的に接続されている。受信フィルタ2及び送信フィルタ3は、IDTなどにより形成された共振子などの機能素子が励振できる空間を確保するために、パッケージ基板1との間に空隙9を形成するように封止材4により封止されている。シールリング部10は、ダイアタッチ層と同層に、ダイアタッチ層を囲むように形成されている。後述する図2(A)において、シールリング部10は、切れ目無く完全にダイアタッチ層5を囲む構成を示しているが、切欠きが形成されていてもよいし、点線状や一点鎖線状にシールリング部10を形成してもよい。シールリング部10は、例えば金属などからできている。封止材4は、例えば樹脂や金属などからできている。封止材4が樹脂からできている場合には、シールリング10は形成しないことが好ましい。

【0022】

図2(A)〜(C)は、実施例1に係るデュプレクサのパッケージ基板の各層のパターンを説明するための図である。各層のパターンは、各基板を挟んで積層され、重畳する関係にある。このため、図2(B)に示す内層6、ならびに図2(C)に示すフットパターン7は、図2(A)に示すダイアタッチ層5側から透視した状態のパターンを示している。なお、図2(A)に示す要素には、その符号にAを含み、図2(B)に示す要素には、その符号にBを含み、図2(C)に示す要素には、その符号にCを含むことがある。図2(A)に示すように、第一の基板11の表面(上面)にはダイアタッチ層5とシールリング部10が形成されている。ダイアタッチ層5には、アンテナ端子111A、受信フィルタ2の並列共振器グランド端子112A、送信フィルタ3の並列共振器グランド端子113A、受信端子21A、送信端子31Aが形成されている。さらに、ダブルモード型フィルタのグランド端子114Aが形成されている。実施例1においては、ダブルモード型フィルタとして、ダブルモード型SAWフィルタ(以下、DMSという。)を用いた例を示している。受信フィルタ2の並列共振器グランド端子112AとDMSのグランド端子114Aは分離して形成される。DMSの入力のグランド及び出力グランドは、共通グランド端子114Aで、電気的に同電位として形成され、すなわち、連続したパターンで形成され、共通のグランドとなっている。ここで、DMSの入力グランド及び出力グランドがダイアタッチ層5で共通のグランドである旨は、図5において114Aで示されている。114Aと112Aは、ダイアタッチ層5において分離して形成されている。これにより、並列共振器のグランドとDMSの入出力の共通グランドのグランドインダクタンスを、それぞれ独立に調節することが可能となる。

【0023】

図2(B)に示すように、第一の基板11と第二の基板12の間に位置して形成される内層6には、アンテナ端子111B、送信フィルタ3の並列共振器グランド端子113B、DMSの入力側グランド端子114Bin、DMSの出力側グランド端子114Bout、受信端子21B、送信端子31Bが形成されている。ここで、ダイアタッチ層5における受信フィルタ2の並列共振器のグランド端子112Aは、第一の基板11を貫通するビアを通じて、内層6のDMSの入力側グランド端子114Binと導通し、両者のグランドは内層6で共通して形成されているが、分離して形成してもよい。ここで、図5を参照すると、DMSの入力グランド、出力グランドは、それぞれ図5に示す114Bin、114Boutを指し、114Binと112は、上記の説明の通り、内層6において共通に形成されている。DMSの入力側グランド端子114Binと出力側グランド端114Boutは、これら端子の配列方向に対して略直交するように形成されたスリット115Bにより分離して形成されている。これにより、後述する外部接続用フットパターン7のアンテナ端子111Cからの受信信号が、容量結合により内層のDMSのグランドパターンを伝わって、受信端子21B等に漏れることによるアイソレーション特性の劣化を防ぐことができる。特に、本実施例のように第二の基板12が第一の基板11に比べて薄い場合、ダイアタッチ層5及びシールリング部10に起因する容量結合よりも内層6のパターンによる容量結合のアイソレーション特性の劣化の方が深刻であるため、DMSの内層6の入出力グランドを分離する効果は大きい。なお、本実施例における上記配列方向のスリットの幅は、75μmである。また、スリットのパターンは、DMSの入力グランドパターンと出力グランドパターンを分離するものであればよく、例えば、斜めに形成したり、ジグザグ状や、波形のような形状に構成したり、幅が変化する構成など、種種の形状を採用できる。

【0024】

グランドの経路、すなわち電流の流れの多くは最短経路を取ろうとするため、ダイアタッチ層5で共通となっていても、電流の多くは、グランド端子に接続されたバンプから最も近いビアに流れ込む。よって、DMSの入出力のグランド端子のそれぞれのバンプの近くにビアを配置しておくことにより、電流の多くは近くのビアに流れ込み、その下層である内層6のパターンを分離しておくことで、入出力それぞれのグランドインダクタンスを調整することができる。また、電流の多くは最短経路を取るが、ダイアタッチ層5で共通となっていることにより一部の電流は入出力から遠いビアにも流れ込むため、その一部の電流が、共通グランドインダクタンスとなる。あとは通常の設計手法によりビアの配置乃至パターンレイアウト等の調整をすることにより所望のグランドインダクタンスを得ることができる。図7は、ダイアタッチ層5と内層6を接続するビア102の実施例1における配置を示している。図7の構成は後述する説明により明らかとなるが、DMSのグランドパターン114A、114Bin、114Boutにおいて、その領域内における各バンプパッド108から近くに位置するビア102に流れる電流が、それぞれ入出力のグランドインダクタンス成分の殆どを構成し、遠くに位置するビア102に流れる電流が、共通グランド114Aのグランドインダクタンス成分の殆どを構成する。よって、DMSの入出力のグランドをダイアタッチ層5において共通とし、内層6において分離する構成によれば、アンテナと受信端子の間のアイソレーションを確保しつつ、DMSの入出力のグランド及び共通グランドのインダクタンスをそれぞれ独立に調節することが可能となる。

【0025】

図2(C)に示すように、第二の基板12の表面(下面)には、フットパターン7として、アンテナ端子111C、受信端子21C、送信端子31C、ならびにグランド端子71、711、712が形成されている。ここで、受信フィルタ2を平衡出力とする場合には、第一の受信端子21Cに加え、711又は712が第二の受信端子として使用される。送信端子31Cとのアイソレーション特性を高めるためには、712よりも送信端子31Cとの間の距離が長い711を第二の受信端子として用いることが望ましい。

【0026】

図3は、実施例1に係るデュプレクサに用いられる受信フィルタ2及び送信フィルタ3を説明するための図である。図3は、弾性表面波共振器からなる機能素子の配置形態を、フィルタチップの背面から(機能素子が形成される側と反対側から)透視した図となっている。また、図5は、実施例1に係るデュプレクサの等価回路図である。図3と図5においては、双方、同じ構成要素には同じ符号を付している。以下、図3と図5を参照しつつ実施例1に係るデュプレクサの構造及び回路構成について説明する。受信フィルタ2は、並列に複数(本実施例では、2つ)に分割されたDMSと、DMSとアンテナ端子111との間に接続された複数の直列共振器SRと複数の並列共振器PRから構成されるラダー型フィルタと、DMSと受信端子21との間に接続された共振器Rから構成されている。アンテナ端子111から入力された信号のうち所望の通過帯域の信号が受信端子21から出力されるように設計されている。DMSを並列に複数分割することにより、耐電圧が高く、より高周波帯域となっても挿入損失の低いフィルタを得られるが、複数に分割されないDMSを用いてもよい。並列共振器PRは、グランド端子112を介して接地されている。DMSの入力グランド端子と出力グランド端子は、それぞれグランド端子114を介して接地される。すなわち、DMSの入力側のグランド端子114inは、3個のバンプを介してグランド端子114Aに接続され、また、出力側のグランド端子114outは2個のバンプを介してグランド端子114Aに接続されている。そして、かかるグランド端子114Aは、ビア102を介して接続された内層6においてグランド端子114Bin及び114Boutに分割されて延在している。

【0027】

図4は、実施例1に係る受信フィルタ2に含まれるDMSを示す図である。リチウムタンタレートの単結晶板などからなる圧電基板(図示せず)上に形成された一対の反射器の間に三つのIDTを備える2つのDMSが、並列接続されている。複数に分割して並列接続することにより、耐電圧が向上し、より高周波帯域に用いても挿入損失の悪化を防止することができる。このようなDMSは、図4に示すように、3つのIDTを挟む2つの反射器REFの間に形成された周波数f1の1次のモードと周波数f3の3次のモードとを使い、図8に示す受信帯域のような、周波数f1とf3による二重共振現象により形成される通過帯域を有する通過帯域特性を実現する。図4(B)は図4(A)に示す構造における、一方のDMSの弾性表面波のエネルギー分布を模式的に表している。

【0028】

図3に示す送信フィルタ3は、送信端子31とアンテナ端子111との間に接続された複数の直列共振器SRと複数の並列共振器PRにより構成されるラダー型フィルタから構成されている。並列共振器PRはグランド端子113を介して接地されている。送信端子31から入力された信号のうち所望の通過帯域の信号がアンテナ端子111から出力されるように設計されている。

【0029】

受信フィルタ2及び送信フィルタ3を構成する弾性表面波共振器は、それぞれIDTの両端に反射器REFを配置している。これにより、弾性表面波の漏れを防ぎ、損失の低減等を図っている。また、並列共振器PRはそれぞれグランド端子112、113を介して接地されている。また、受信フィルタ2におけるDMSの入力側及び出力側もそれぞれグランド端子114in、114outを介して接地されている。なお、ラダー型フィルタは一つの直列共振器と一つの並列共振器から構成される一段のラダー型フィルタであってもよい。受信フィルタ2及び送信フィルタ3は、圧電基板上にスパッタリング法または蒸着法などの成膜技術、ならびにフォトリソグラフィー法などのパターニング技術を適用して、金属層からなるIDT、反射電極、配線を形成することにより形成されている。当該金属層は、例えばアルミニウム(Al)を主体として形成され、例えば銅(Cu)を含んでもよい。また、送信フィルタ3にはFBARを用いてラダー型フィルタを構成してもよい。FBARはその特性上、より高周波帯域において用いられる場合に有利である。FBARは下部電極、窒化アルミニウムなどからなる圧電膜、及び上部電極がこの順に積層され、これらが重なり合う領域が振動することにより共振器として作用する。当該重なり合う領域が振動するため、一般には支持基板との間に空間を確保する必要があるが、音響ミラーにより振動を閉じ込める手法を適用してもよい。

【0030】

図6は、実施例1に係るデュプレクサのスリット115BとDMSの重なりを示す図である。受信フィルタ2、送信フィルタ3、ダイアタッチ層5及び内層6の各構成要素の位置関係の理解を助けるために、図3に対し、図2(A)に示したダイアタッチ層5及び図2(B)に示した内層6を重ねて、透視図としている。斜線でハッチングされた領域が内層6のパターンを、複数の点(ドット)で示された領域がダイアタッチ層5及びシールリング部10のパターンをそれぞれ示している。パッケージ基板1を上方(フィルタをフリップチップ実装する側)から透視した場合に、上記ハッチング領域と上記複数の点(ドット)で示された領域が重なっている領域が、ダイアタッチ層5及びシールリング部10と内層6とが第一の基板を介して重畳している領域を示している。受信フィルタ2チップの機能素子と内層6の重畳関係をみると、DMSの少なくとも一部が内層6のスリット115Bと重なっている構成であることがわかる。一般に、グランドインダクタンスの設計上、グランドインダクタンスを大きくすることは、種種の手法により容易であるが、小さくすることは困難である。よって、特にグランドインダクタンスを大きくしたい場合を除いては、設計上、グランドインダクタンスは最小の状態であることが望ましい。DMSの少なくとも一部が内層6のスリット115Bと重なっている構成によれば、最小限の配線により、グランドインダクタンスの無用な増大を防止し、フィルタチップの配線設計上のスペース効率が向上することができ、フィルタチップ上のグランドパッド配置の設計自由度が広くなり、DMSの入出力グランドのインダクタンスを適正値にする為のチップレイアウトの調整が容易になる。以下に、図6及び図7を参照しつつ、その理由を説明する。

【0031】

図7は、図6からフィルタ及びバンプを省略し、内層6とシールリング部10を導通させるビア101と、内層6とダイアタッチ層を導通させる複数のビア102と、バンプパッド108をそれぞれ示している。なお、本実施例においては、内層6とシールリング部10を導通させるビア101の直径は60μm、内層6とダイアタッチ層を導通させる複数のビア102の直径はそれぞれ75μmである。また、フィルタをフリップチップ実装する際のバンプとダイアタッチ層5の接続領域をバンプパッド108として示している。図7におけるその他の構成は図6と同様である。ここで、グランドの経路(電流の流れ)は最短経路を取る傾向にあるため、DMSの入力グランドと出力グランドを内層6において分離し且つグランドインダクタンスの無用な増大を防止するためには、受信フィルタのDMSの入力側グランド端子114in及び出力側グランド端子114outとダイアタッチ層5とが導通される位置は、それぞれ内層6の入力側グランド端子114Bin及び出力側グランド端子114Boutの真上となるように配置する必要がある。

【0032】

逆に、DMSがスリットと重ならない位置に配置されると、受信フィルタ2チップ上において、DMSからDMSの入力又は出力グランド端子までの配線は、DMSの入力側グランド端子114in及び出力側グランド端子114outを内層6の入力側グランド端子114Bin及び出力側グランド端子114Boutの真上となるように配置するために、少なくともスリットを超えるための長さの配線が必要となることにより、グランドインダクタンスの増大を招来する。あるいは、ダイアタッチ層5から内層6のグランド端子114Bin又は114Boutに接続する際の距離が偏ることにより、最短経路側(114Bin又は114Bout)には電流が集中することにより、他の経路(114Bout又は114Bin)にはその距離が長いことにより、グランドインダクタンスの増大を招来する。よって、DMSがスリットと重ならない位置に配置されると、スペースの効率悪化及び無用なグランド配線によるグランドインダクタンスの増大を招来することになる。

【0033】

以上の理由により、DMSの少なくとも一部が内層6のスリット115Bと重なっている構成によれば、最小限の長さの配線により、グランドインダクタンスの無用な増大を防止し、フィルタチップの配線設計上のスペース効率が向上することができ、フィルタチップ上のグランドパッド配置の設計自由度が広くなり、DMSの入出力グランドのインダクタンスを適正値にする為のチップレイアウトの調整が容易になる。また、本実施例においては、スリット115Bの長手方向と並列分割したDMSの配置方向が同じ方向である。このように同じ方向に設計することで、スペース効率がさらに向上する。

【0034】

図6を参照すると、図3に示した端子21、31、111、112、113、114in、114outが、それぞれ図2(A)に示されたダイアタッチ層5のパターン21A、31A、111A、112A、113A、114Aに対応して、バンプ8を介して電気的に導通している構成となっていることが理解できる。また、受信フィルタ2のバンプ8は、内層6のパターンと、少なくとも一部が重なるように配置されている。本実施例において、アンテナ端子111を接続するためのバンプ8以外は、重なっている。これにより、パッケージ基板の積層ずれによって変動する層間結合容量などのばらつきを抑えることができ、特性変動を最小限に抑えることができるとともに、コプラナリティを向上することができる。さらに、グランド端子を接続するためのバンプ8は、内層6のグランドパターンの少なくとも一部と重なっているが、スリット115Bとは重なっていない。本実施例においては、全てのグランド端子を接続するためのバンプ8が、内層6のグランドパターンと重なっている。特に、DMSの入出力のグランド端子を接続するためのバンプ8は、複数あり、密集して配置される。本実施例では、DMSの入力のグランド端子を接続するためのバンプが3個、DMSの出力のグランド端子を接続するためのバンプが2個ある。また、コプラナリティの悪化を招来するビアは、グランドを強化するために、ダイアタッチ層5と内層6の間に複数配置する場合が多いこと、に鑑みれば、DMSの入出力のグランド端子を接続するためのバンプ8は、全てダイアタッチ層5と内層6が重なる領域に配置して、コプラナリティの悪化を防止することが望ましい。

【実施例2】

【0035】

実施例2に係るデュプレクサにおいては、図7に示すように、機能素子を取り囲むシールリング部10と、内層6パターンの入力側グランド端子114Binとが、ビア101により電気的に導通している。かかる構成によれば、シールリング部10により電磁的な遮蔽効果が得られ、使用時に他の電子部品等による外部影響を受けにくくすることができる。さらに、封止材4の材料をはんだ等の導電性材料を用いることによって、遮蔽効果はさらに大きくなる。図7にはシールリング部10と受信フィルタ2のグランドが電気的に導通した例を示しているが、送信フィルタ3のグランドのみとシールリング部10を導通させてもよいし、送受信両方のフィルタのグランドと導通させてもよい。その他の構成は実施例1に係るデュプレクサと同様の構成であるので説明を省略する。

【0036】

図8は、実施例2に係るデュプレクサの特性を示す図である。送信帯域は1850〜1910MHzであり、受信帯域は1930〜1990MHzに設定されている。内層6における受信フィルタ2のDMSの入出力グランドが共通している場合(分離前)と内層6における受信フィルタ2のDMSの入力側グランド端子114Binと出力側グランド端子114Boutが分離して形成されている場合(分離後)とで、アイソレーション特性が向上していることがわかる。

【符号の説明】

【0037】

1 パッケージ基板

2 受信フィルタ

3 送信フィルタ

4 封止材

5 ダイアタッチ層

6 内層

7 フットパターン

9 空隙

10 シールリング部

11 第一の基板

12 第二の基板

21 受信端子

31 送信端子

71 グランド端子

101、102 ビア

111 アンテナ端子

112 受信フィルタ2の並列共振器グランド端子

113 送信フィルタ3の並列共振器グランド端子

114 DMSのグランド端子

115B スリット

【技術分野】

【0001】

本発明は、携帯電話などの無線装置に使用されるデュプレクサに関する。

【背景技術】

【0002】

近年、移動体通信システムの発展に伴って携帯電話、携帯情報端末等が急速に普及してきた。携帯電話ではマルチバンド・マルチモード化が急速に進展しつつあるのに加え、無線LAN、Bluetooth(登録商標)、GPSといった付属の無線インターフェイスの搭載も進む方向にあり、携帯電話内のRF回路部への小型化、集積化の要求も強い。こうした状況の中、アンテナ共用器等として用いられ、RF回路部における主要部品の1つであるデュプレクサへの小型化、高性能化の要求が強くなっている。

【0003】

デュプレクサは、アンテナ共用器、分波器として用いられ、周波数の異なる送信信号と受信信号をインピーダンスの相違を利用して分離する。送信信号、受信信号がそれぞれ一つの場合、デュプレクサは、送信用フィルタと受信用フィルタとをそれぞれ一つ具備する。三つ以上のフィルタを共有することも可能であり、例えば三つの場合はトリプレクサと呼ばれることがあるが、本願においてはこれらを纏めてデュプレクサと呼ぶことにする。そして、これらのフィルタには一端子対共振器がよく使用される。共振器としては、従来広く使用されてきたサイズの大きい誘電体共振器に替わり、最近は特許文献1に記載のように、小型の圧電薄膜共振器(FBAR:Film Bulk Acoustic Wave)或いは弾性表面波(SAW:Surface

Acoustic Wave)共振器がよく使用される。

【0004】

弾性表面波共振器は、圧電基板上に入力端子と出力端子とに接続された櫛歯状電極指(IDT:Interdigital Transducer)と、必要に応じてIDTの両側に配置される反射器とから構成される。IDTおよび反射器は例えばアルミニウム(Al)等の金属で形成される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−271230号公報

【特許文献2】特開2005−318307号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述のような背景から、デュプレクサの小型化に伴い、送信端子から受信端子への信号漏れが大きくなり、アイソレーション特性の劣化につながっている。さらに、カスタム部品としてのさらなる高性能化の要求を満たすためには、デュプレクサ内の各種電極パターンを独立に調節できるなどの設計自由度の高いデュプレクサが求められる。

【0007】

特許文献1に開示される技術においては、受信フィルタのグランドパターンが、他のパターンから分離されているため、アイソレーション特性を向上することができる。また、特許文献2に開示される技術においては、ダイアタッチ層でフィルタの入出力グランドパターンを分離して、バランス出力型フィルタのバランス特性の改善を図ると共にグランドインダクタンスを小さくしている。

【0008】

しかしながら、これらの技術を組み合わせても、アイソレーション特性を維持しつつ、ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び入出力が共通する共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを得ることができなかった。

【0009】

本発明は、上記課題に鑑みなされたものであり、アイソレーション特性を維持しつつ、ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明は、アンテナ端子と送信端子との間に接続された送信フィルタと、前記アンテナ端子と受信端子との間に配置される受信フィルタと、第一の基板と、前記第一の基板上にパターン形成されたダイアタッチ層と、第二の基板と、前記第一の基板と前記第二の基板との間に位置する内層を有するパッケージ基板と、前記受信フィルタの一部を構成するダブルモード型フィルタと、前記ダイアタッチ層の一部を構成する前記ダブルモード型フィルタの入力グランド及び出力グランドを共通のグランドとする共通グランド端子と、前記内層の一部を構成する前記ダブルモード型フィルタの入力側のグランド端子と、前記入力側のグランド端子とは分離して形成された前記内層の一部を構成する前記ダブルモード型フィルタの出力側のグランド端子と、を有するデュプレクサである。本発明によれば、アイソレーション特性を維持しつつ、前記ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び共通グランドインダクタンスをそれぞれ独立に調節することができる。

【0011】

上記構成において、前記内層における前記ダブルモード型フィルタの入力グランドと出力グランドは、スリットにより分離されている構成とすることができる。

【0012】

上記構成において、前記ダブルモード型フィルタは並列に複数に分割されている構成とすることができる。かかる構成によれば、耐電圧が高く、より高周波帯域となっても挿入損失の低いフィルタを構成要素としたデュプレクサを得ることができる。

【0013】

上記構成において、前記ダブルモード型フィルタは、前記スリットと少なくとも一部が重なる位置に配置されている構成とすることができる。かかる構成によれば、受信フィルタ上のグランドパッド配置の設計自由度が広くなり、前記ダブルモード型フィルタの入出力グランドのインダクタンスを適正値にする為のチップレイアウトの調整が容易になる。

【0014】

上記構成において、前記受信フィルタは、複数のグランド端子に接続するためのバンプを有し、前記グランド端子に接続するためのバンプは、前記入力グランドパターン又は前記出力グランドパターンの少なくとも一部と重なっており、前記グランド端子に接続するためのバンプは、前記スリットとは重なっていない構成とすることができる。かかる構成によれば、パッケージ基板のコプラナリティ(平坦性)の悪化を防ぐことができる。

【0015】

上記構成において、前記第一の基板上の外周部に形成されたシールリング部を有し、前記シールリング部は、前記送信フィルタのグランド又は/及び前記受信フィルタのグランドと共通のグランドとなっている構成とすることができる。かかる構成によれば、電磁的な遮蔽効果が得られ、使用時に他の電子部品等による外部影響を受けにくくなることができる。

【0016】

上記構成において、前記第一の基板上の外周部に形成されたシールリング部を有し、前記シールリング部は、前記送信フィルタのグランド及び前記受信フィルタのグランドから電気的に独立している構成とすることができる。かかる構成によれば、グランドのレベルが低い場合に容量結合等による特性の劣化を防ぐとことができる。

【0017】

上記構成において、前記受信フィルタは、平衡出力とする構成とすることができる。かかる構成によれば、1入力2出力の受信フィルタを備えたデュプレクサを得られる。

【0018】

上記構成において、前記受信フィルタは、直列共振器と並列共振器を備えたラダー型フィルタを有し、前記ダイアタッチ層における前記並列共振器のグランドと前記ダブルモード型フィルタのグランドは分離しているかかる構成によれば、受信フィルタにラダー型フィルタを含めた場合において、並列共振器のグランドインダクタンスも独立して調整することができる。

【発明の効果】

【0019】

本発明によれば、アイソレーション特性を維持しつつ、ダブルモード型フィルタの入力グランドインダクタンス、出力グランドインダクタンス、及び入出力が共通する共通グランドインダクタンスをそれぞれ独立に調節することができるデュプレクサを得ることができる。

【図面の簡単な説明】

【0020】

【図1】本発明の実施例1に係るデュプレクサの断面図。

【図2】実施例1に係るデュプレクサのパッケージ基板の各層のパターンを説明するための図。

【図3】実施例1に係るデュプレクサに用いられる受信フィルタ及び送信フィルタを説明するための図。

【図4】実施例1に係る受信フィルタ2に含まれるDMSを示す図。

【図5】実施例1に係るデュプレクサの等価回路を示す図。

【図6】実施例1に係るデュプレクサのスリットとダブルモード型フィルタの重なりを示す図。

【図7】本発明の実施例2に係るデュプレクサの特徴を説明するための図。

【図8】実施例2に係るデュプレクサの特性を示す図。

【発明を実施するための形態】

【実施例1】

【0021】

実施例1に係るデュプレクサの断面構造を図1に示す。かかる断面は、後述する図6におけるA−A‘断面に相当する。図1に示すように、実施例1によるデュプレクサは、パッケージ基板1上に受信フィルタ2と送信フィルタ3がフリップチップ方式によりバンプ8を介して実装され、封止材4により封止された構成を基本構成とする。受信フィルタ2と送信フィルタ3は一つのチップで構成されても良いし、複数のチップから構成されてもよい。より詳細には、パッケージ基板1は、第一の基板11及び第二の基板12からなり、第一の基板11のフィルタ実装面にはダイアタッチ層5の電極パターンならびにシールリング部10が形成され、第一の基板11と第二の基板12の間には内層6の電極パターンが形成され、さらに、第二の基板12の裏面には外部接続用のフットパターン7が形成されている。第一の基板11及び第二の基板12は、アルミナセラミクス、ガラスセラミクス、或いは樹脂などから形成されている。本実施例では第一の基板の厚みは100μm、第二の基板の厚みは51μmである。また、デュプレクサのサイズは、2.0mm×1.6mm角で、厚みは0.58mmである。本実施例では、パッケージ基板1は二層の基板により構成されているが、より複雑な電気回路を構成する必要がある場合には、三層以上の基板から構成してもよい。ダイアタッチ層5、内層6及びフットパターン7は、銅或いはアルミニウムなどの導電性部材により形成され、図示は省略するが、第一の基板11及び第二の基板12をそれぞれ貫通して選択的に配設された複数のビアにより接続され、電気的に導通可能としている。かかる導電層パターンが形成された第一の基板11及び第二の基板12は積層され、一体化され、パッケージ基板1が構成される。ダイアタッチ層5の上には、例えば半田などにより形成された複数のバンプ8を介して受信フィルタ2及び送信フィルタ3がフリップチップ実装され、フィルタとパッケージ基板1と電気的に接続されている。受信フィルタ2及び送信フィルタ3は、IDTなどにより形成された共振子などの機能素子が励振できる空間を確保するために、パッケージ基板1との間に空隙9を形成するように封止材4により封止されている。シールリング部10は、ダイアタッチ層と同層に、ダイアタッチ層を囲むように形成されている。後述する図2(A)において、シールリング部10は、切れ目無く完全にダイアタッチ層5を囲む構成を示しているが、切欠きが形成されていてもよいし、点線状や一点鎖線状にシールリング部10を形成してもよい。シールリング部10は、例えば金属などからできている。封止材4は、例えば樹脂や金属などからできている。封止材4が樹脂からできている場合には、シールリング10は形成しないことが好ましい。

【0022】

図2(A)〜(C)は、実施例1に係るデュプレクサのパッケージ基板の各層のパターンを説明するための図である。各層のパターンは、各基板を挟んで積層され、重畳する関係にある。このため、図2(B)に示す内層6、ならびに図2(C)に示すフットパターン7は、図2(A)に示すダイアタッチ層5側から透視した状態のパターンを示している。なお、図2(A)に示す要素には、その符号にAを含み、図2(B)に示す要素には、その符号にBを含み、図2(C)に示す要素には、その符号にCを含むことがある。図2(A)に示すように、第一の基板11の表面(上面)にはダイアタッチ層5とシールリング部10が形成されている。ダイアタッチ層5には、アンテナ端子111A、受信フィルタ2の並列共振器グランド端子112A、送信フィルタ3の並列共振器グランド端子113A、受信端子21A、送信端子31Aが形成されている。さらに、ダブルモード型フィルタのグランド端子114Aが形成されている。実施例1においては、ダブルモード型フィルタとして、ダブルモード型SAWフィルタ(以下、DMSという。)を用いた例を示している。受信フィルタ2の並列共振器グランド端子112AとDMSのグランド端子114Aは分離して形成される。DMSの入力のグランド及び出力グランドは、共通グランド端子114Aで、電気的に同電位として形成され、すなわち、連続したパターンで形成され、共通のグランドとなっている。ここで、DMSの入力グランド及び出力グランドがダイアタッチ層5で共通のグランドである旨は、図5において114Aで示されている。114Aと112Aは、ダイアタッチ層5において分離して形成されている。これにより、並列共振器のグランドとDMSの入出力の共通グランドのグランドインダクタンスを、それぞれ独立に調節することが可能となる。

【0023】

図2(B)に示すように、第一の基板11と第二の基板12の間に位置して形成される内層6には、アンテナ端子111B、送信フィルタ3の並列共振器グランド端子113B、DMSの入力側グランド端子114Bin、DMSの出力側グランド端子114Bout、受信端子21B、送信端子31Bが形成されている。ここで、ダイアタッチ層5における受信フィルタ2の並列共振器のグランド端子112Aは、第一の基板11を貫通するビアを通じて、内層6のDMSの入力側グランド端子114Binと導通し、両者のグランドは内層6で共通して形成されているが、分離して形成してもよい。ここで、図5を参照すると、DMSの入力グランド、出力グランドは、それぞれ図5に示す114Bin、114Boutを指し、114Binと112は、上記の説明の通り、内層6において共通に形成されている。DMSの入力側グランド端子114Binと出力側グランド端114Boutは、これら端子の配列方向に対して略直交するように形成されたスリット115Bにより分離して形成されている。これにより、後述する外部接続用フットパターン7のアンテナ端子111Cからの受信信号が、容量結合により内層のDMSのグランドパターンを伝わって、受信端子21B等に漏れることによるアイソレーション特性の劣化を防ぐことができる。特に、本実施例のように第二の基板12が第一の基板11に比べて薄い場合、ダイアタッチ層5及びシールリング部10に起因する容量結合よりも内層6のパターンによる容量結合のアイソレーション特性の劣化の方が深刻であるため、DMSの内層6の入出力グランドを分離する効果は大きい。なお、本実施例における上記配列方向のスリットの幅は、75μmである。また、スリットのパターンは、DMSの入力グランドパターンと出力グランドパターンを分離するものであればよく、例えば、斜めに形成したり、ジグザグ状や、波形のような形状に構成したり、幅が変化する構成など、種種の形状を採用できる。

【0024】

グランドの経路、すなわち電流の流れの多くは最短経路を取ろうとするため、ダイアタッチ層5で共通となっていても、電流の多くは、グランド端子に接続されたバンプから最も近いビアに流れ込む。よって、DMSの入出力のグランド端子のそれぞれのバンプの近くにビアを配置しておくことにより、電流の多くは近くのビアに流れ込み、その下層である内層6のパターンを分離しておくことで、入出力それぞれのグランドインダクタンスを調整することができる。また、電流の多くは最短経路を取るが、ダイアタッチ層5で共通となっていることにより一部の電流は入出力から遠いビアにも流れ込むため、その一部の電流が、共通グランドインダクタンスとなる。あとは通常の設計手法によりビアの配置乃至パターンレイアウト等の調整をすることにより所望のグランドインダクタンスを得ることができる。図7は、ダイアタッチ層5と内層6を接続するビア102の実施例1における配置を示している。図7の構成は後述する説明により明らかとなるが、DMSのグランドパターン114A、114Bin、114Boutにおいて、その領域内における各バンプパッド108から近くに位置するビア102に流れる電流が、それぞれ入出力のグランドインダクタンス成分の殆どを構成し、遠くに位置するビア102に流れる電流が、共通グランド114Aのグランドインダクタンス成分の殆どを構成する。よって、DMSの入出力のグランドをダイアタッチ層5において共通とし、内層6において分離する構成によれば、アンテナと受信端子の間のアイソレーションを確保しつつ、DMSの入出力のグランド及び共通グランドのインダクタンスをそれぞれ独立に調節することが可能となる。

【0025】

図2(C)に示すように、第二の基板12の表面(下面)には、フットパターン7として、アンテナ端子111C、受信端子21C、送信端子31C、ならびにグランド端子71、711、712が形成されている。ここで、受信フィルタ2を平衡出力とする場合には、第一の受信端子21Cに加え、711又は712が第二の受信端子として使用される。送信端子31Cとのアイソレーション特性を高めるためには、712よりも送信端子31Cとの間の距離が長い711を第二の受信端子として用いることが望ましい。

【0026】

図3は、実施例1に係るデュプレクサに用いられる受信フィルタ2及び送信フィルタ3を説明するための図である。図3は、弾性表面波共振器からなる機能素子の配置形態を、フィルタチップの背面から(機能素子が形成される側と反対側から)透視した図となっている。また、図5は、実施例1に係るデュプレクサの等価回路図である。図3と図5においては、双方、同じ構成要素には同じ符号を付している。以下、図3と図5を参照しつつ実施例1に係るデュプレクサの構造及び回路構成について説明する。受信フィルタ2は、並列に複数(本実施例では、2つ)に分割されたDMSと、DMSとアンテナ端子111との間に接続された複数の直列共振器SRと複数の並列共振器PRから構成されるラダー型フィルタと、DMSと受信端子21との間に接続された共振器Rから構成されている。アンテナ端子111から入力された信号のうち所望の通過帯域の信号が受信端子21から出力されるように設計されている。DMSを並列に複数分割することにより、耐電圧が高く、より高周波帯域となっても挿入損失の低いフィルタを得られるが、複数に分割されないDMSを用いてもよい。並列共振器PRは、グランド端子112を介して接地されている。DMSの入力グランド端子と出力グランド端子は、それぞれグランド端子114を介して接地される。すなわち、DMSの入力側のグランド端子114inは、3個のバンプを介してグランド端子114Aに接続され、また、出力側のグランド端子114outは2個のバンプを介してグランド端子114Aに接続されている。そして、かかるグランド端子114Aは、ビア102を介して接続された内層6においてグランド端子114Bin及び114Boutに分割されて延在している。

【0027】

図4は、実施例1に係る受信フィルタ2に含まれるDMSを示す図である。リチウムタンタレートの単結晶板などからなる圧電基板(図示せず)上に形成された一対の反射器の間に三つのIDTを備える2つのDMSが、並列接続されている。複数に分割して並列接続することにより、耐電圧が向上し、より高周波帯域に用いても挿入損失の悪化を防止することができる。このようなDMSは、図4に示すように、3つのIDTを挟む2つの反射器REFの間に形成された周波数f1の1次のモードと周波数f3の3次のモードとを使い、図8に示す受信帯域のような、周波数f1とf3による二重共振現象により形成される通過帯域を有する通過帯域特性を実現する。図4(B)は図4(A)に示す構造における、一方のDMSの弾性表面波のエネルギー分布を模式的に表している。

【0028】

図3に示す送信フィルタ3は、送信端子31とアンテナ端子111との間に接続された複数の直列共振器SRと複数の並列共振器PRにより構成されるラダー型フィルタから構成されている。並列共振器PRはグランド端子113を介して接地されている。送信端子31から入力された信号のうち所望の通過帯域の信号がアンテナ端子111から出力されるように設計されている。

【0029】

受信フィルタ2及び送信フィルタ3を構成する弾性表面波共振器は、それぞれIDTの両端に反射器REFを配置している。これにより、弾性表面波の漏れを防ぎ、損失の低減等を図っている。また、並列共振器PRはそれぞれグランド端子112、113を介して接地されている。また、受信フィルタ2におけるDMSの入力側及び出力側もそれぞれグランド端子114in、114outを介して接地されている。なお、ラダー型フィルタは一つの直列共振器と一つの並列共振器から構成される一段のラダー型フィルタであってもよい。受信フィルタ2及び送信フィルタ3は、圧電基板上にスパッタリング法または蒸着法などの成膜技術、ならびにフォトリソグラフィー法などのパターニング技術を適用して、金属層からなるIDT、反射電極、配線を形成することにより形成されている。当該金属層は、例えばアルミニウム(Al)を主体として形成され、例えば銅(Cu)を含んでもよい。また、送信フィルタ3にはFBARを用いてラダー型フィルタを構成してもよい。FBARはその特性上、より高周波帯域において用いられる場合に有利である。FBARは下部電極、窒化アルミニウムなどからなる圧電膜、及び上部電極がこの順に積層され、これらが重なり合う領域が振動することにより共振器として作用する。当該重なり合う領域が振動するため、一般には支持基板との間に空間を確保する必要があるが、音響ミラーにより振動を閉じ込める手法を適用してもよい。

【0030】

図6は、実施例1に係るデュプレクサのスリット115BとDMSの重なりを示す図である。受信フィルタ2、送信フィルタ3、ダイアタッチ層5及び内層6の各構成要素の位置関係の理解を助けるために、図3に対し、図2(A)に示したダイアタッチ層5及び図2(B)に示した内層6を重ねて、透視図としている。斜線でハッチングされた領域が内層6のパターンを、複数の点(ドット)で示された領域がダイアタッチ層5及びシールリング部10のパターンをそれぞれ示している。パッケージ基板1を上方(フィルタをフリップチップ実装する側)から透視した場合に、上記ハッチング領域と上記複数の点(ドット)で示された領域が重なっている領域が、ダイアタッチ層5及びシールリング部10と内層6とが第一の基板を介して重畳している領域を示している。受信フィルタ2チップの機能素子と内層6の重畳関係をみると、DMSの少なくとも一部が内層6のスリット115Bと重なっている構成であることがわかる。一般に、グランドインダクタンスの設計上、グランドインダクタンスを大きくすることは、種種の手法により容易であるが、小さくすることは困難である。よって、特にグランドインダクタンスを大きくしたい場合を除いては、設計上、グランドインダクタンスは最小の状態であることが望ましい。DMSの少なくとも一部が内層6のスリット115Bと重なっている構成によれば、最小限の配線により、グランドインダクタンスの無用な増大を防止し、フィルタチップの配線設計上のスペース効率が向上することができ、フィルタチップ上のグランドパッド配置の設計自由度が広くなり、DMSの入出力グランドのインダクタンスを適正値にする為のチップレイアウトの調整が容易になる。以下に、図6及び図7を参照しつつ、その理由を説明する。

【0031】

図7は、図6からフィルタ及びバンプを省略し、内層6とシールリング部10を導通させるビア101と、内層6とダイアタッチ層を導通させる複数のビア102と、バンプパッド108をそれぞれ示している。なお、本実施例においては、内層6とシールリング部10を導通させるビア101の直径は60μm、内層6とダイアタッチ層を導通させる複数のビア102の直径はそれぞれ75μmである。また、フィルタをフリップチップ実装する際のバンプとダイアタッチ層5の接続領域をバンプパッド108として示している。図7におけるその他の構成は図6と同様である。ここで、グランドの経路(電流の流れ)は最短経路を取る傾向にあるため、DMSの入力グランドと出力グランドを内層6において分離し且つグランドインダクタンスの無用な増大を防止するためには、受信フィルタのDMSの入力側グランド端子114in及び出力側グランド端子114outとダイアタッチ層5とが導通される位置は、それぞれ内層6の入力側グランド端子114Bin及び出力側グランド端子114Boutの真上となるように配置する必要がある。

【0032】

逆に、DMSがスリットと重ならない位置に配置されると、受信フィルタ2チップ上において、DMSからDMSの入力又は出力グランド端子までの配線は、DMSの入力側グランド端子114in及び出力側グランド端子114outを内層6の入力側グランド端子114Bin及び出力側グランド端子114Boutの真上となるように配置するために、少なくともスリットを超えるための長さの配線が必要となることにより、グランドインダクタンスの増大を招来する。あるいは、ダイアタッチ層5から内層6のグランド端子114Bin又は114Boutに接続する際の距離が偏ることにより、最短経路側(114Bin又は114Bout)には電流が集中することにより、他の経路(114Bout又は114Bin)にはその距離が長いことにより、グランドインダクタンスの増大を招来する。よって、DMSがスリットと重ならない位置に配置されると、スペースの効率悪化及び無用なグランド配線によるグランドインダクタンスの増大を招来することになる。

【0033】

以上の理由により、DMSの少なくとも一部が内層6のスリット115Bと重なっている構成によれば、最小限の長さの配線により、グランドインダクタンスの無用な増大を防止し、フィルタチップの配線設計上のスペース効率が向上することができ、フィルタチップ上のグランドパッド配置の設計自由度が広くなり、DMSの入出力グランドのインダクタンスを適正値にする為のチップレイアウトの調整が容易になる。また、本実施例においては、スリット115Bの長手方向と並列分割したDMSの配置方向が同じ方向である。このように同じ方向に設計することで、スペース効率がさらに向上する。

【0034】

図6を参照すると、図3に示した端子21、31、111、112、113、114in、114outが、それぞれ図2(A)に示されたダイアタッチ層5のパターン21A、31A、111A、112A、113A、114Aに対応して、バンプ8を介して電気的に導通している構成となっていることが理解できる。また、受信フィルタ2のバンプ8は、内層6のパターンと、少なくとも一部が重なるように配置されている。本実施例において、アンテナ端子111を接続するためのバンプ8以外は、重なっている。これにより、パッケージ基板の積層ずれによって変動する層間結合容量などのばらつきを抑えることができ、特性変動を最小限に抑えることができるとともに、コプラナリティを向上することができる。さらに、グランド端子を接続するためのバンプ8は、内層6のグランドパターンの少なくとも一部と重なっているが、スリット115Bとは重なっていない。本実施例においては、全てのグランド端子を接続するためのバンプ8が、内層6のグランドパターンと重なっている。特に、DMSの入出力のグランド端子を接続するためのバンプ8は、複数あり、密集して配置される。本実施例では、DMSの入力のグランド端子を接続するためのバンプが3個、DMSの出力のグランド端子を接続するためのバンプが2個ある。また、コプラナリティの悪化を招来するビアは、グランドを強化するために、ダイアタッチ層5と内層6の間に複数配置する場合が多いこと、に鑑みれば、DMSの入出力のグランド端子を接続するためのバンプ8は、全てダイアタッチ層5と内層6が重なる領域に配置して、コプラナリティの悪化を防止することが望ましい。

【実施例2】

【0035】

実施例2に係るデュプレクサにおいては、図7に示すように、機能素子を取り囲むシールリング部10と、内層6パターンの入力側グランド端子114Binとが、ビア101により電気的に導通している。かかる構成によれば、シールリング部10により電磁的な遮蔽効果が得られ、使用時に他の電子部品等による外部影響を受けにくくすることができる。さらに、封止材4の材料をはんだ等の導電性材料を用いることによって、遮蔽効果はさらに大きくなる。図7にはシールリング部10と受信フィルタ2のグランドが電気的に導通した例を示しているが、送信フィルタ3のグランドのみとシールリング部10を導通させてもよいし、送受信両方のフィルタのグランドと導通させてもよい。その他の構成は実施例1に係るデュプレクサと同様の構成であるので説明を省略する。

【0036】

図8は、実施例2に係るデュプレクサの特性を示す図である。送信帯域は1850〜1910MHzであり、受信帯域は1930〜1990MHzに設定されている。内層6における受信フィルタ2のDMSの入出力グランドが共通している場合(分離前)と内層6における受信フィルタ2のDMSの入力側グランド端子114Binと出力側グランド端子114Boutが分離して形成されている場合(分離後)とで、アイソレーション特性が向上していることがわかる。

【符号の説明】

【0037】

1 パッケージ基板

2 受信フィルタ

3 送信フィルタ

4 封止材

5 ダイアタッチ層

6 内層

7 フットパターン

9 空隙

10 シールリング部

11 第一の基板

12 第二の基板

21 受信端子

31 送信端子

71 グランド端子

101、102 ビア

111 アンテナ端子

112 受信フィルタ2の並列共振器グランド端子

113 送信フィルタ3の並列共振器グランド端子

114 DMSのグランド端子

115B スリット

【特許請求の範囲】

【請求項1】

アンテナ端子と送信端子との間に接続された送信フィルタと、

前記アンテナ端子と受信端子との間に配置される受信フィルタと、

第一の基板と、前記第一の基板上にパターン形成されたダイアタッチ層と、第二の基板と、前記第一の基板と前記第二の基板との間に位置する内層を有するパッケージ基板と、

前記受信フィルタの一部を構成するダブルモード型フィルタと、

前記ダイアタッチ層の一部を構成する前記ダブルモード型フィルタの入力グランド及び出力グランドを共通のグランドとする共通グランド端子と、

前記内層の一部を構成する前記ダブルモード型フィルタの入力側のグランド端子と、

前記入力側のグランド端子とは分離して形成された前記内層の一部を構成する前記ダブルモード型フィルタの出力側のグランド端子と、を有するデュプレクサ。

【請求項2】

前記内層における前記ダブルモード型フィルタの入力グランドと出力グランドは、スリットにより分離されている、請求項1に記載のデュプレクサ。

【請求項3】

前記ダブルモード型フィルタは、並列に複数に分割されていることを特徴とする請求項1又は2に記載のデュプレクサ。

【請求項4】

前記ダブルモード型フィルタは、前記スリットと少なくとも一部が重なる位置に配置されていることを特徴とする請求項1〜3いずれか1項に記載のデュプレクサ。

【請求項5】

前記受信フィルタは、複数のグランド端子に接続するためのバンプを有し、前記グランド端子に接続するためのバンプは、前記入力グランドパターン又は前記出力グランドパターンの少なくとも一部と重なっており、

前記グランド端子に接続するためのバンプは、前記スリットとは重なっていないことを特徴とする請求項1〜4いずれか1項に記載のデュプレクサ。

【請求項6】

前記第一の基板上の外周部に形成されたシールリング部を有し、

前記シールリング部は、前記送信フィルタのグランド又は/及び前記受信フィルタのグランドと共通のグランドとなっていることを特徴とする請求項1〜5いずれか1項に記載のデュプレクサ。

【請求項7】

前記第一の基板上の外周部に形成されたシールリング部を有し、

前記シールリング部は、前記送信フィルタのグランド及び前記受信フィルタのグランドから電気的に独立していることを特徴とする請求項1〜5いずれか1項に記載のデュプレクサ。

【請求項8】

前記受信フィルタは、平衡出力となっていることを特徴とする請求項1〜7いずれか1項に記載のデュプレクサ。

【請求項9】

前記受信フィルタは、直列共振器と並列共振器を備えたラダー型フィルタを有し、前記ダイアタッチ層における前記並列共振器のグランドと前記ダブルモード型フィルタのグランドは分離していることを特徴とする請求項1〜8いずれか1項に記載のデュプレクサ。

【請求項1】

アンテナ端子と送信端子との間に接続された送信フィルタと、

前記アンテナ端子と受信端子との間に配置される受信フィルタと、

第一の基板と、前記第一の基板上にパターン形成されたダイアタッチ層と、第二の基板と、前記第一の基板と前記第二の基板との間に位置する内層を有するパッケージ基板と、

前記受信フィルタの一部を構成するダブルモード型フィルタと、

前記ダイアタッチ層の一部を構成する前記ダブルモード型フィルタの入力グランド及び出力グランドを共通のグランドとする共通グランド端子と、

前記内層の一部を構成する前記ダブルモード型フィルタの入力側のグランド端子と、

前記入力側のグランド端子とは分離して形成された前記内層の一部を構成する前記ダブルモード型フィルタの出力側のグランド端子と、を有するデュプレクサ。

【請求項2】

前記内層における前記ダブルモード型フィルタの入力グランドと出力グランドは、スリットにより分離されている、請求項1に記載のデュプレクサ。

【請求項3】

前記ダブルモード型フィルタは、並列に複数に分割されていることを特徴とする請求項1又は2に記載のデュプレクサ。

【請求項4】

前記ダブルモード型フィルタは、前記スリットと少なくとも一部が重なる位置に配置されていることを特徴とする請求項1〜3いずれか1項に記載のデュプレクサ。

【請求項5】

前記受信フィルタは、複数のグランド端子に接続するためのバンプを有し、前記グランド端子に接続するためのバンプは、前記入力グランドパターン又は前記出力グランドパターンの少なくとも一部と重なっており、

前記グランド端子に接続するためのバンプは、前記スリットとは重なっていないことを特徴とする請求項1〜4いずれか1項に記載のデュプレクサ。

【請求項6】

前記第一の基板上の外周部に形成されたシールリング部を有し、

前記シールリング部は、前記送信フィルタのグランド又は/及び前記受信フィルタのグランドと共通のグランドとなっていることを特徴とする請求項1〜5いずれか1項に記載のデュプレクサ。

【請求項7】

前記第一の基板上の外周部に形成されたシールリング部を有し、

前記シールリング部は、前記送信フィルタのグランド及び前記受信フィルタのグランドから電気的に独立していることを特徴とする請求項1〜5いずれか1項に記載のデュプレクサ。

【請求項8】

前記受信フィルタは、平衡出力となっていることを特徴とする請求項1〜7いずれか1項に記載のデュプレクサ。

【請求項9】

前記受信フィルタは、直列共振器と並列共振器を備えたラダー型フィルタを有し、前記ダイアタッチ層における前記並列共振器のグランドと前記ダブルモード型フィルタのグランドは分離していることを特徴とする請求項1〜8いずれか1項に記載のデュプレクサ。

【図4】

【図1】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図1】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−81118(P2013−81118A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−220700(P2011−220700)

【出願日】平成23年10月5日(2011.10.5)

【出願人】(000204284)太陽誘電株式会社 (964)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月5日(2011.10.5)

【出願人】(000204284)太陽誘電株式会社 (964)

【Fターム(参考)】

[ Back to top ]