デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デューティ感知回路およびこれを備えるデューティ補正回路に関するもので、詳しくは、デューティの歪曲した程度を一度で正確に測定可能にする技術に関するものである。

【背景技術】

【0002】

半導体メモリー装置のようにクロックに基づいて動作する半導体装置において、クロックのデューティ(duty)が正確に制御されることは大変重要である。クロックのデューティが50%というのは、1つのクロック信号において、「ハイ」レベル区間と「ロー」レベル区間の長さ(時間的大きさ)が同じであるということを意味する。

【0003】

半導体メモリー装置の場合、クロックの立ち上がりエッジ(rising edge)および立ち下がりエッジ(falling edge)に正確に同期されデータが入・出力されなければならない。このような半導体装置においてクロックのデューティが正確に50%とならなければ、立ち上がりエッジと立ち下がりエッジとの間のタイミングがずれてしまい、データが正確なタイミングで入・出力されない。したがって半導体メモリー装置ではクロックのデューティを正確に50%に合わせるためにデューティ補正回路(DCC:Duty Cycle Correcter)が使用される。

【0004】

既存のデューティ補正回路は、クロックのデューティの補正において多くの短所を有している。

【0005】

第一に、既存のデューティ補正回路は、クロックのハイパルス幅(ハイレベルである時間)とローパルス幅(ローレベルである時間)とを比較してアップ・ダウン信号等を生成し、アップ・ダウン信号によってデューティ比を少しずつ補正する方法を使用する。このようなデューティ補正回路は幾度もの比較動作を終えて初めてデューティの補正が完了するため、ロッキングタイム(補正に要する時間)が長くなるという問題がある。

【0006】

第二に、デジタル方式のデューティ補正回路は、デューティ感知回路自体のオフセットによって、正確なデューティ比を測定するのが難しいという問題がある。

【0007】

第三に、デューティ補正対象クロックの周波数範囲が限定されているという問題、すなわちデューティ補正可能な入力クロックの周波数範囲に制限があるという問題がある。

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明は、前記した従来技術の問題点を解決するために提案されたものであり、その目的は、デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供することにある。

【課題を解決するための手段】

【0009】

前記した目的を達成するための本発明に係るデューティ補正回路は、デューティ調節コードに応答して入力クロックのデューティを調節した出力クロックを生成するデューティ調節部と、前記出力クロックのハイパルス幅とローパルス幅との差異を測定してその差異値を出力するデューティ感知部と、前記差異値を累積して前記デューティ調節コードを生成する累積部とを備える。

【0010】

また、前記した目的を達成するための本発明に係るデューティ感知回路は、クロックのハイパルス幅を測定してハイパルスコードを生成し、前記クロックのローパルス幅を測定してローパルスコードを生成する測定部と、前記ハイパルスコードと前記ローパルスコードとを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号を生成する比較部と、前記ハイパルスコードおよび前記ローパルスコードのうち、大きい方の値から小さい方の値を減算して差異値コードを生成する減算部とを備える。

【発明の効果】

【0011】

本発明のデューティ補正回路は、ハイパルス幅およびローパルス幅を測定し、測定された値の差異を利用して直ちにデューティを補正する。したがって、1サイクルの動作だけでデューティ比が補正されるため、従来に比べてロッキングタイムを顕著に減少させることができる。

【0012】

また、同一の構成によって、ハイパルス幅およびローパルス幅を測定し、測定された値が差異値のみを利用するため、ハイパルス幅を測定するときに発生するオフセット、およびローパルス幅を測定するときに発生するオフセットが除去されるという長所がある。

【図面の簡単な説明】

【0013】

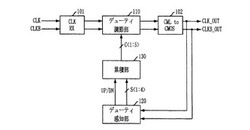

【図1】本発明に係るデューティ補正回路の一実施形態の構成図である。

【図2】図1のデューティ感知部120の一実施形態の構成図である。

【図3】図2の測定部210の一実施形態の構成図である。

【図4】図3の遅延部332の一実施形態の構成図である。

【図5A】図3に図示された測定部210でハイパルスコードH<1:4>が生成される過程を表した図である。

【図5B】測定部210でローパルスコードL<1:4>が生成される過程を表した図である。

【図6】図1の累積部130の一実施形態の図である。

【図7】図1のデューティ調節部110の一実施形態の図である。

【図8】デューティ調節部110によりデューティが調節されるのを図示した図である。

【図9】本発明によるデューティ補正回路の全体動作を表した図である。

【図10】図3に図示された測定部210に初期値調節部1000が追加されたことを図示した図である。

【図11】図10の遅延部1020の一実施形態の図である。

【発明を実施するための形態】

【0014】

以下、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施することができるように詳細に説明するため本発明の最も好ましい実施形態を、添付図を参照して説明する。

【0015】

図1は、本発明に係るデューティ補正回路の一実施形態の構成を示すブロック図である。

【0016】

本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、差異値S<1:4>を累積してデューティ調節コードC<1:5>を生成する累積部130とを備えて構成される。なお、デューティ補正回路に必須の構成ではないが、図1には、クロックの入力を受ける入力端を表すCLKRX101と、CMLレベルのクロックをCMOSレベルに変化させるシフター(shifter)を表すCMLtoCMOS102とを示している。

【0017】

デューティ感知部120は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅を測定して、その差異値S<1:4>(4ビット)を出力する。ハイパルス幅とローパルス幅との差異値S<1:4>は、現在のクロックのデューティが歪曲している程度を表す。また、デューティ感知部120は、ハイパルス幅がローパルス幅よりも大きいのか、または、ローパルス幅がハイパルス幅よりも大きいのかを表すアップ・ダウン信号UP/DNを出力するが、アップ・ダウン信号UP/DNは、クロックのデューティがどの方向に歪曲したのかを表わす信号となる。

【0018】

従来のデューティ感知部は、デューティが歪曲した方向を表わす情報だけを生成し、デューティがどれほど歪曲したのかを表す情報を生成しなかった。したがってデューティが歪曲した方向に応じて少しずつデューティを調節するほかなく、これに伴ってデューティ補正回路は幾度ものサイクル(cycle)の間、動作しなければならなかった。しかし本発明のデューティ感知部は、デューティが歪曲した方向UP/DNだけでなく、デューティが歪曲した程度に関する情報S<1:4>も生成する。したがってデューティ補正回路は、1サイクルの動作のみでデューティを正確に補正できるようになる。

【0019】

累積部130は、デューティ感知部120から出力される差異値S<1:4>を累積してデューティ調節コードC<1:5>(5ビット)を生成する。ここでの累積とは差異値S<1:4>を加算または減算することを意味するが、加算するのか減算するのかの可否はアップ・ダウン信号UP/DN(図2参照)によって決定される。すでにデューティ感知部120からはクロックのデューティを補正するために必要な十分な情報が出力されているため、1サイクルの動作のみでデューティの完全な調節が可能である。しかしクロックのデューティを調節した後もいろいろな要因によってデューティが再び歪曲する場合が発生し得る。累積部130は、デューティの補正後に再びデューティが歪曲した場合に備えるために具備される。

【0020】

例えば、最初にクロックのデューティが+5の分だけ(+はハイパルス幅がローパルス幅より大きいことを意味し、5は差の程度を意味する)歪曲したとすれば、クロックのデューティを+5の分だけ調節すればデューティは完全に補正される。しかしデューティ補正後にデューティが+2の分だけさらに歪曲したとすれば、既存の+5にさらに+2を足してデューティ調節コードC<1:5>の値を+7にしなければならない。累積部130は、このような役割を担当することになる。

【0021】

デューティ調節部110は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節して出力する。デューティ調節コードC<1:5>は、クロックがどの方向に歪曲したのか、およびどれだけ歪曲したのかに関する情報を含んでいるため、このようなデューティ調節コードC<1:5>を利用して入力クロックCLK、CLKBのデューティを調節し、出力クロックCLK_OUT、CLKB_OUTを生成することが可能である。

【0022】

上記したように、図1のCLKRX101は、クロックの入力を受ける入力端を表し、CMLtoCMOS102は、CMLレベルのクロックをCMOSレベルに変化させるシフター(shifter)を表す。下記の詳細の実施形態において、本発明のデューティ調節部110が、CML(Current Mode Logic)レベルでスイングするクロックのデューティを調節することを例示するために、そのための構成を図1に図示したが、デューティ調節部110が、CMOSレベルでスイングする(変化する)クロックのデューティを調節する場合には、CLKRX101、CMLtoCMOS102は不要である。デューティ調節部110が、CMOSレベルでスイングするクロックのデューティを調節するのか、CMLレベルでスイングするクロックのデューティを調節するのかは、状況に応じて変更可能な選択的な問題に過ぎないため、このようなレベルを変換するための構成は、デューティ補正回路に必須の構成ではない。

【0023】

図2は、図1のデューティ感知部120の一実施形態の構成を示すブロック図である。

【0024】

図2に図示されたように、デューティ感知部120は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅を測定してハイパルスコードH<1:4>を生成し、出力クロックCLK_OUT、CLKB_OUTのローパルス幅を測定してローパルスコードL<1:4>を生成する測定部210と、ハイパルスコードH<1:4>とローパルスコードL<1:4>とを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号UP/DNを生成する比較部220と、ハイパルスコードH<1:4>とローパルスコードL<1:4>とのうち、大きい値から小さい値を減算して差異値コードS<1:4>を生成する減算部230とを備え構成される。

【0025】

測定部210は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅を測定してハイパルスコードH<1:4>およびローパルスコードL<1:4>を生成する。測定部210でのハイパルス幅の測定およびローパルス幅の測定は順次成されるが、SEL信号が「ハイ」レベルである間にはハイパルス幅の測定が成され、SEL信号が「ロー」レベルである間にはローパルス幅の測定が成される。したがって測定部210の出力信号は、まずハイパルスコードH<1:4>が出力され、その後からローパルスコードL<1:4>が出力される。

【0026】

測定部210の出力端にあるラッチ211、212は、ハイパルスコードH<1:4>およびローパルスコードL<1:4>を各々一旦保存するために具備される。図2では、ラッチ211、212を測定部210とは別の構成要素として図示したが、ラッチ211、212を測定部210内に具備されるように構成することもできる。ラッチ211、212は、単にハイパルスコードH<1:4>およびローパルスコードL<1:4>を保存する役割だけを担うが、デューティ感知部210内の構成要素のタイミングチューニング(タイミングを揃えること)等を適切に行える場合には、ラッチ211、212を無くしてデューティ感知部210を構成することもできる。ラッチ211に入力されるUPDATE1信号、UPDATE2信号は、ラッチ211、212がハイパルスコードH<1:4>およびローパルスコードL<1:4>の入力を受ける時点(タイミング)を決定するための信号である。

【0027】

比較部220は、ハイパルスコードH<1:4>とローパルスコードL<1:4>とを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号UP/DNを生成する。比較部220に入力されるUPDATE3信号は、ハイパルスコードH<1:4>およびローパルスコードL<1:4>が比較部220に入力される時点を決定するための信号である。

【0028】

減算部230は、ハイパルスコードH<1:4>のコード値とローパルスコードL<1:4>のコード値との差異、すなわちハイパルス幅とローパルス幅との差異を求める役割を担う。減算部230は、アップ・ダウン信号UP/DNを利用してハイパルスコードH<1:4>およびローパルスコードL<1:4>のうち、どちらのコードがより大きいのかを判断して大きい値から小さい値を減算し差異値コードS<1:4>を生成する。減算部230に入力されるUPDATE4信号は、減算部230にハイパルスコードH<1:4>およびローパルスコードL<1:4>が入力される時点を決定するための信号である。

【0029】

図3は、図2の測定部210の一実施形態の構成を示すブロック図である。

【0030】

測定部210は、出力クロックCLK_OUT、CLKB_OUT(CLK_OUTが正クロック、CLKB_OUTが負クロック)を第1経路IN1、第2経路IN2に伝達する経路選択部310と、第1経路IN1および第2経路IN2に伝達されたクロックの入力を受けてハイパルス幅またはローパルス幅を測定するための直列に接続された複数の選択遅延端)320〜350を備え構成される。

【0031】

経路選択部310は、SEL信号が「ハイ」レベルである間は、正クロックCLK_OUTを第1経路IN1に伝達し、負クロックCLKB_OUTを第2経路IN2に伝達する。そして選択信号SELが「ロー」レベルである間には負クロックCLKB_OUTを第1経路IN1に伝達し、正クロックCLK_OUTを第2経路IN2に伝達する。SEL信号が「ハイ」レベルである区間は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅が測定される区間であり、SEL信号が「ロー」レベルである区間は、出力クロックCLK_OUT、CLKB_OUTのローパルス幅が測定される区間である。

【0032】

選択遅延端320〜350の各々は、第1経路IN1のクロックと第2経路IN2のクロックとの位相を比較する位相比較部(PD)321、331、341、351と、位相比較部321、331、341、351の比較結果Q<4>、Q<3>、Q<2>、Q<1>に応じて第1経路IN1のクロックまたは第2経路IN2のクロックを遅延させる遅延部322、332、342を備え構成される。

【0033】

位相比較部321、331、341、351は、第1経路IN1に伝達されたクロックの立ち上がりエッジ(rising edge)が、第2経路IN2に伝達されたクロックの立ち上がりエッジより先んじる場合には「1」の値を出力し、その反対の場合には「0」の値を出力する。遅延部322、332、342は、位相比較部321、331、341の比較結果Q<4>、Q<3>、Q<2>が「1」の場合には第1経路IN1のクロックを遅延させ、位相比較部321、331、341の比較結果Q<4>、Q<3>、Q<2>が「0」の場合には第2経路IN2のクロックを遅延させる。それぞれの遅延部322、332、342の遅延値は40PS(Pico Second)、20PS、10PSのようにバイナリウェイト(binary weight)を有するように設計される。

【0034】

第1経路IN1に正クロックCLK_OUTが入力され、第2経路IN2に負クロックCLKB_OUTが入力された場合、位相比較部321、331、341、351の出力値Q<4>、Q<3>、Q<2>、Q<1>は、ハイパルスコードH<1:4>となる(Q<1:4>=H<1:4>)。そして第1経路IN1に負クロックCLKB_OUTが入力され、第2経路IN2に正クロックCLK_OUTが入力される場合に位相比較部321、331、341、351の出力値Q<4>、Q<3>、Q<2>、Q<1>はローパルスコードL<1:4>となる(Q<1:4>=L<1:4>)。

【0035】

図3を参照すれば、最終端の選択遅延端350には遅延部が省略されていることが分かるが、これは、これ以上後端の選択遅延端が存在しないために遅延部を省略して構成したものである。

【0036】

初期遅延部311は、第1経路IN1に伝達されたクロックを一定時間遅延させ、ハイパルスコードH<1:4>およびローパルスコードL<1:4>の測定が速く成され得るようにするため具備されたものであり、本発明の必須の構成要素には該当しない。測定されたハイパルスコードH<1:4>およびローパルスコードL<1:4>は、初期遅延部311の遅延値の分だけ誤差を有するようになりはするが、本発明においてデューティの感知のために重要な値はハイパルスコードH<1:4>およびローパルスコードL<1:4>自体ではなく、2つのコードの差異値であるため、このような誤差は問題とならない。

【0037】

本発明は同一の選択遅延端320、330、340、350を利用して出力クロックCLK_OUT、CLKB_OUTのハイパルスコードH<1:4>およびローパルスコードL<1:4>を測定し、測定されたハイパルスコードH<1:4>とローパルスコードL<1:4>との差異を利用してデューティを感知する。したがって製造工程上、選択遅延端320、330、340、350にオフセット(offset)が発生したとしてもハイパルスコードH<1:4>とローパルスコードL<1:4>との差異を求める過程においてこのようなオフセットの影響が除去されるという長所がある。

【0038】

図3では、経路選択部310を利用して正クロックCLK_OUTおよび負クロックCLKB_OUTの経路を変え、同一の選択遅延端320、330、340、350を介して、ハイパルスコードH<1:4>およびローパルスコードL<1:4>を生成するが、経路選択部310なしで、ハイパルスコードH<1:4>を測定するための選択遅延端と、ローパルスコードL<1:4>を測定するための選択遅延端とを、それぞれ別に具備するよう設計することも可能である。

【0039】

図4は、図3の遅延部332の一実施形態の構成を示す回路図である。

【0040】

遅延部332は、位相比較部331の出力値Q<3>に応じてオン・オフされるパスゲートPG1〜PG8と遅延手段410、420とを備え構成される。

【0041】

位相比較部331の出力値Q<3>が「1」の値を有すれば、第1経路IN1のクロックは遅延手段420を介してOUT1に出力され、第2経路IN2のクロックは遅延手段410を介してOUT2に出力される。したがって第1経路IN1のクロックが第2経路IN2のクロックより20PSだけ遅延される。

【0042】

位相比較部331の出力値Q<3>が「0」の値を有すれば、第1経路IN1のクロックは遅延手段410を介してOUT1に出力され、第2経路IN2のクロックは遅延手段420を介してOUT2に出力される。したがって第2経路IN2のクロックが第1経路IN1のクロックより20PSだけ遅延されることになる。図4において、遅延手段420の下方に記載された「1+20PS」は、第2経路IN2の遅延時間が第1経路IN1の遅延時間(遅延手段410の下方に記載された「1」で表されている)よりも20PSだけ長いことを意味する。

【0043】

本発明で重要なのは、遅延手段410と遅延手段420間の遅延値の差異であるため、遅延手段420が、遅延手段410よりも、予め設定された値(例えば、上記した20PS)だけの遅延値をさらに有するように設計する。このような遅延手段410、420を設計する方法が無数に多いこと、及び、任意に設計・選択可能なことは、当業者にとっては当然のことである。

【0044】

図5Aは、図3に図示された測定部210でハイパルスコードH<1:4>が生成される過程を表した図であり、図5Bは、測定部210でローパルスコードL<1:4>が生成される過程を表す図である。

【0045】

図5Aは、第1経路IN1に正クロックCLK_OUTが入力され、第2経路IN2に負クロックCLKB_OUTが入力され、ハイパルスコードH<1:4>が測定される過程を図示するものである。

【0046】

まず、正クロックCLK_OUTは、初期遅延部311の遅延値の分だけ遅延される(1STEP)。その結果、初期遅延部311によって正クロックCLK_OUTは遅延されたが、依然として正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジより先んじている。したがって位相比較部321の出力値Q<4>は「1」となり、これに伴い遅延部322は、正クロックCLK_OUTを負クロックCLKB_OUTより40PSだけさらに遅延させる(2STEP)。これで正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジより遅延する。したがって位相比較部331の出力値Q<3>は「0」となり、遅延部332は、負クロックCLKB_OUTを正クロックCLK_OUTより20PSだけさらに遅延させる(3STEP、図5Aには便宜上、正クロックが20PSだけ先んじるものとして表現する)。その結果、正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジよりさらに先んじることになる。したがって位相比較部341の出力値Q<2>は「1」となり、遅延部342は、正クロックCLK_OUTを10PSの分だけさらに遅延させる(4STEP)。依然として正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジより先んじている。したがって位相比較部351の出力値Q<1>は「1」になる。位相比較部321、331、341、351の出力値(Q<1:4>)は、ハイパルスコードH<1:4>となるため、ハイパルスコードH<1:4>は「1011」(右端が最下位ビットであるH<1>、左端が最上位ビットであるH<4>)の値を有するようになる。

【0047】

図5Bは、第1経路IN1に負クロックCLKB_OUTが入力され、第2経路IN2に正クロックCLK_OUTが入力され、ローパルスコードL<1:4>が測定される過程を図示したものである。

【0048】

まず、負クロックCLKB_OUTは、初期遅延部311の遅延値の分だけ遅延される(1STEP)。その結果、初期遅延部311によって負クロックCLKB_OUTは遅延されたが、依然として負クロックCLKB_OUTの立ち上がりエッジは正クロックCLK_OUTの立ち上がりエッジより先んじている。したがって位相比較部321の出力値Q<4>は「1」となり、これに伴い遅延部322は、負クロックCLKB_OUTを正クロックCLK_OUTより40PSだけさらに遅延させる(2STEP)。これで負クロックCLKB_OUTの立ち上がりエッジは、正クロックCLK_OUTの立ち上がりエッジより遅れる。したがって位相比較部331の出力値Q<3>は、「0」となり、遅延部332は、正クロックCLK_OUTを負クロックCLKB_OUTより20PSだけさらに遅延させる(3STEP、図5Bには便宜上、負クロックが20PSだけ先んじるものとして表現する)。その結果、依然として負クロックCLKB_OUTの立ち上がりエッジは正クロックCLK_OUTの立ち上がりエッジより遅れている。したがって位相比較部341の出力値Q<2>は「0」となり、遅延部342は、正クロックCLK_OUTを負クロックCLKB_OUTより10PSだけさらに遅延させる(4STEP、図5Bには便宜上、負クロックが10PSだけ先んじるものしてと表現する)。これで負クロックCLKB_OUTの立ち上がりエッジは、正クロックCLK_OUTの立ち上がりエッジより先んじることになる。したがって位相比較部351の出力値Q<1>は「1」となる。位相比較部321、331、341、351の出力値(Q<1:4>)は、ローパルスコードL<1:4>になるため、ローパルスコード(L<1:4>)は「1001」(右端が最下位ビットであるL<1>、左端が最上位ビットであるL<4>)の値を有するようになる。

【0049】

図6は、図1の累積部130の一実施形態の構成を示すブロック図である。

【0050】

累積部130は、デューティ調節コードC<1:5>を保存するラッチ部620と、ラッチ部620に保存されたデューティ調節コードC<1:5>にアップ・ダウン信号UP/DNに応じて差異値S<1:4>を加算または減算する演算部610とを備え構成される。

【0051】

ラッチ部620は、デューティ調節部110がデューティ調節をしないようにする値をデューティ調節コードC<1:5>の初期値として保存している。本実施形態では、その初期値を「10000」とする(初期値は「10000」以外の値であってもよい)。次にラッチ部620は、演算部610の演算結果値である出力をデューティ調節コードC<1:5>として保存していくことになる。図6のUPDATE5信号は、演算部610の演算結果がラッチ部620に保存される時点を決定する信号に該当する。

【0052】

演算部610は、ラッチ部620に保存されていたデューティ調節コードC<1:5>値に差異値コードS<1:4>を加算または減算する役割をする。アップ・ダウン信号UP/DNが「ハイ」値を有する場合、ラッチ部620に保存されていたデューティ調節コードC<1:5>値に差異値コードS<1:4>が加算され、アップ・ダウン信号UP/DNが「ロー」値を有する場合には、ラッチ部620に保存されていた値から差異値コードS<1:4>を減算することになる。

【0053】

例えば、デューティ調節コードC<1:5>が「10000」であり、アップ・ダウン信号UP/DNが「ハイ」レベル、差異値コードS<1:4>が「0011」で入力されると、デューティ調節コードC<1:5>(演算部610の出力と同じ)は、「10011」となる。また、デューティ調節コードC<1:5>が「10000」であり、アップ・ダウン信号UP/DNが「ロー」レベル、差異値コード(S<1:4>)が「0011」で入力されると、デューティ調節コードC<1:5>(演算部610の出力と同じ)は「01101」となる。即ち、最下位ビットを揃えて演算が行われる。

【0054】

図7は、図1のデューティ調節部110の一実施形態を示す回路図である。

【0055】

デューティ調節部110は、入力クロックCLK、CLKBのうちの正クロック(RX_OUT、CLKINが出力されるものである)のレベルを調節する正クロック調節部710と、負クロック(RX_OUTB、CLKINBが出力されるものである)のレベルを調節する負クロック調節部730とを備えて構成される。

【0056】

正クロック調節部710は、バイナリウェイトを有するトランジスタ711〜714を利用して正クロックRX_OUTのレベルを調節することによってデューティを補正する。正クロック調節部710は、デューティ調節コードC<1:5>の最上位ビットC<5>が「1」の値を有する時に動作する。デューティ調節コードC<1:5>の最上位ビットC<5>が「1」の値を有するということは、ハイパルスコードH<1:4>値がローパルスコードL<1:4>値より大きいということを意味するため、正クロックRX_OUTのレベルを低くする必要がある。

【0057】

デューティ調節コードC<1:5>の最上位ビットC<5>が「1」の場合、NANDゲート715〜718の出力端に接続したインバータ(719〜722)の出力値は、各々のデューティ調節コードC<1:4>の値に応じて決定される。最上位ビットC<5>を除外したデューティ調節コードC<1:4>の値は、ハイパルス幅がローパルス幅よりどれくらい大きいのかを表す値であるため、デューティ調節コードC<1:4>の値に応じてトランジスタ711〜714をターンオンさせることになり、その結果、正クロックRX_OUTのレベルはデューティ調節コードC<1:4>の値に比例して低くなる。これはハイパルス幅が、デューティ調節コードC<1:4>の値に比例して狭くなることを意味することになる。

【0058】

負クロック調節部730は、バイナリウェイトを有するトランジスタ731〜734を利用して負クロックRX_OUTBのレベルを調節することによってデューティを補正する。負クロック調節部730は、デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の値を有するときに動作する。デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の値を有するということは、ローパルスコードL<1:4>値がハイパルスコードH<1:4>値より大きいということを意味するため、デューティの補正のためには負クロックRX_OUTBのレベルを低くする必要がある。

【0059】

デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の場合、NORゲート735〜738の出力値は、各々のデューティ調節コードC<1:4>の値と反対の値(各ビットを反転させた値)を有するようになる。これはデューティ調節コードC<1:5>の初期値の「10000」と現在のデューティ調節コードC<1:5>値との差異に比例するようにトランジスタ731〜734がターンオンされることを意味する。すなわち、ローパルス幅がハイパルス幅よりどれくらい大きいのかに比例してトランジスタ731〜734がターンオンされ、ローパルス幅を減らすことになる。

【0060】

デューティ調節部110の動作を簡単に整理すれば、デューティ調節部110は、デューティ調節コードC<1:5>が初期値「10000」より大きくなった場合は、大きくなった分だけ正クロックRX_OUTのレベルを低くし、デューティ調節コードC<1:5>が初期値「10000」より小さくなった場合は、小さくなった分だけ負クロックRX_OUTBのレベルを低くし、クロックのデューティを調節することになる。

【0061】

バイアス電圧BIASの入力を受けるトランジスタ723〜726、739〜742は各々のノードに流れる電流が過度に多くなることを防止する役割を担う。

【0062】

図8は、デューティ調節部110によってデューティが調節されることを図示したグラフである。横軸は時間であり、縦軸は例えば電圧である。

【0063】

図8には、デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の場合、すなわち負クロック調節部730が動作する場合における負クロックRX_OUTBのレベルの変化を、近接する16本の曲線で図示した。図8を参照すれば、デューティ調節コードC<1:4>に応じて負クロックRX_OUTBのレベルが低くなる程度が異なることを確認することができる。

【0064】

正クロックRX_OUTの立ち上がりエッジと負クロックRX_OUTBの立ち下がりエッジとが交差する地点(横軸の値を意味する。以下同じ)から、正クロックRX_OUTの立ち下がりエッジと負クロックRX_OUTBの立ち上がりエッジとが交差する地点までがクロックのハイパルス幅を表している。また、正クロックRX_OUTの立ち下がりエッジと負クロックRX_OUTBの立ち上がりエッジとが交差する地点から、正クロックRX_OUTの立ち上がりエッジと負クロックRX_OUTBの立ち下がりエッジとが交差する地点までがクロックのローパルス幅を表している。

【0065】

図9は、本発明に係るデューティ補正回路の全体的な動作を示すタイミングチャートである。

【0066】

まず、SEL信号が「ハイ」値を有する間、経路選択部310は、出力クロックの正クロックCLK_OUTを第1経路IN1に伝達し、出力クロックの負クロックCLKB_OUTを第2経路IN2に伝達する。したがって測定部210では、ハイパルス幅が測定される。ハイパルスコードH<1:4>の生成が完了した以後にUPDATE1信号がイネーブルされ(ハイレベルになる。以下同じ)、ラッチ211にハイパルスコードH<1:4>が保存される。以下、測定されたハイパルスコードH<1:4>の値は、「1011」であると仮定して説明することにする。

【0067】

次にSEL信号が「ロー」値を有するようになれば、経路選択部310は、出力クロックの負クロックCLKB_OUTを第1経路IN1に伝達し、出力クロックの正クロックCLK_OUTを第2経路IN2に伝達する。したがって測定部210ではローパルス幅が測定される。ローパルスコードL<1:4>の生成が完了した以後にUPDATE2信号がイネーブルされ、ラッチ212にローパルスコードL<1:4>が保存される。以下、測定されたローパルスコードL<1:4>の値は「1001」であると仮定して説明することにする。

【0068】

次にUPDATE3信号がイネーブルされ、比較部220に、ハイパルスコードH<1:4>として「1011」が入力され、ローパルスコードL<1:4>として「1001」が入力される。ハイパルスコードH<1:4>である「1011」がローパルスコードL<1:4>である「1001」より大きい値を有するため、比較部220は、アップ・ダウン信号UP/DNのレベルを「ハイ」で出力することになる。

【0069】

これでUPDATE4信号がイネーブルされ、減算部230に、ハイパルスコードH<1:4>である「1011」、ローパルスコードL<1:4>である「1001」、およびアップ・ダウン信号UP/DNが入力される。アップ・ダウン信号UP/DNが「ハイ」レベルであるため、減算部230は、ハイパルスコードH<1:4>である「1011」からローパルスコードL<1:4>である「1001」を減算し、差異値コードS<1:4>として「0010」を生成することになる。

【0070】

累積部130の演算部610は、ラッチ部620に保存されたデューティ調節コードC<1:5>の初期値「10000」に差異値コード(S<1:4>、ここでは「0010」)を加算する。そしてUPDATE5信号がイネーブルされ、演算部610の演算結果、即ち「10010」が新たなデューティ調節コードC<1:5>としてラッチ部620に保存されることになる。

【0071】

デューティ調節コードC<1:5>が「10010」であり、最上位ビットC<5>が「1」であるため、デューティ調節部110の正クロック調節部710が動作することになり、正クロック調節部710は、デューティ調節コードC<1:4>である「0010」の値に比例して正クロックRX_OUTのレベルを低くし、デューティを補正する。

【0072】

選択信号SELおよびアップデート信号UPDATE1〜5は、図9に図示された通り順次に活性化するように生成するが、このような信号を生成する手段は、本発明が属する技術分野で通常の知識を有する者ならば容易に実現することができるため、これに対するこれ以上の説明は省略する。

【0073】

図10は、図3に図示された測定部210に初期値調節部1000が追加されたことを図示したブロック図である。初期値遅延部311は省略されている。

【0074】

クロックCLK_OUT、CLKB_OUTの周波数が変われば、クロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅もこれに伴い変わることになる。したがって、クロックCLK_OUT、CLKB_OUTの周波数の変化に応じて測定部210がクロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅を正しく測定できない場合が発生し得る。

【0075】

例えば、測定された結果、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が「1111」になった場合を考えてみよう。ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値「1111」になったとすれば、これはハイパルス幅またはローパルス幅が測定部210の測定可能な範囲を外れたものと考えることができる。これとは反対にハイパルスコードH<1:4>またはローパルスコードL<1:4>が最小値「0000」になった時も、ハイパルス幅またはローパルス幅が測定部210の測定可能な範囲を外れたものと考えることができる。

【0076】

図10の測定部210は、このような場合に備えるため、図3の測定部210に初期値調節部1000をさらに備える。

【0077】

初期値調節部1000は、ラッチ211、212に保存されたハイパルスコードH<1:4>およびローパルスコードL<1:4>の入力を受け、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値「1111」または最小値「0000」の場合、第1経路IN1または第2経路IN2の初期遅延値を変更させる。

【0078】

ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値である「1111」になったということは、初期遅延部311の遅延値が正確な測定のために必要な値より小さいということができる。したがって、このような場合には第1経路IN1の遅延値を増やすことが必要になる。また、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最小値である「0000」になったということは、初期遅延部311の遅延値が正確な測定のために必要な値より大きいということができる。したがってこのような場合には第2経路IN2の遅延値を増やすことが必要になる。

【0079】

初期値調節部1000は、デコーダ部1010と遅延部1020とを備え構成され得る。デコーダ部1010は、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値になった場合には、RANGE<1>信号を「ロー」レベルに活性化させる。また、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最小値になった場合には、RANGE<2>信号を「ロー」レベルに活性化させる。

【0080】

遅延部1020は、RANGE<1>信号が「ロー」に活性化すれば第1経路IN1の遅延値を増やし、RANGE<2>信号が「ロー」に活性化すれば第2経路IN2の遅延値を増やすことで、ハイパルスコードH<1:4>およびローパルスコードL<1:4>が正しく生成されるようにする。

【0081】

図10に図示されたように、測定部210に初期値調節部1000が具備されるように構成する場合には、測定部210が測定可能なハイパルス幅およびローパルス幅の範囲を変更することが可能であるため、多様な周波数のクロックが入力されたとしても、正確な動作が保障されるという長所がある。

【0082】

図11は、図10の遅延部1020の一実施形態を示す回路図である。

【0083】

図11に図示された遅延部1020は、下記表1のようにRANGE<1>信号およびRANGE<2>信号が活性化されるようにデコードする。表1には、RANGE<1>信号およびRANGE<2>信号が活性化する条件だけを示したが、表1に示されていないコードH<1:4>、L<1:4>の組合せの場合、RANGE<1>信号およびRANGE<2>信号は、共に非活性化状態(即ちハイレベル)を維持する。

【0084】

【表1】

【0085】

表1において、×は任意の値、即ち「0」または「1」のどちらの値であってもよいことを表す。

【0086】

RANGE<1>信号は、ハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち、少なくとも一方が最大値「1111」であり、且つ、最大値である一方が他方のコード値と小さい差異(00××以下の差異)を示すときに活性化する。ハイパルスコードH<1:4>値およびローパルスコードL<1:4>値が最大値である場合も、この条件に当てはまる。単純にハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち一方が最大値でさえすれば、他方の値に依らずにRANGE<1>信号が活性化するようにすることもできるが、2つのコードH<1:4>値およびL<1:4>値が大きい差異を示すということは、測定されたコードH<1:4>値およびL<1:4>値に大きな異常がないということも意味し得るため、上記のようにデコードがされるようにした。さらには、2つのコードH<1:4>値およびL<1:4>値が共にほとんど最大値に近い値になった場合には、コードH<1:4>値およびL<1:4>値が誤っている可能性が高いためである。

【0087】

RANGE<2>信号は、ハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち、一方が最小値「0000」であり、且つ、最小値である一方が他方のコード値と小さい差異(00××以下の差異)を示すときに活性化する。単純にハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち一方が最小値でさえすれば、他方の値に依らずにRANGE<2>が活性化するようにデコーダ部1020を構成しなかった理由は、RANGE<1>について上記した理由と同様である。

【0088】

本発明は、上記したように、好ましい実施形態によって具体的に記述されたが、上記した実施形態は、本発明を説明するためのものであり、本発明を制限するためのものではない。また、本発明の技術分野の通常の専門家ならば、本発明の技術的範囲内で多様な実施形態が可能であることを知ることができるであろう。

【符号の説明】

【0089】

110 デューティ調節部

101 CLKRX

102 CMLtoCMOS

120 デューティ感知部

130 累積部

210 測定部

211、212 ラッチ

220 比較部

230 減算部

310 経路選択部

311 初期遅延部

320〜350 選択遅延端

321、331、341、351 位相比較部(PD)

322、332、342 遅延部

410、420 遅延手段

610 演算部

620 ラッチ部

710 正クロック調節部

730 負クロック調節部

1000 初期値調節部

1010 デコーダ部

1020 遅延部

IN1 第1経路

IN2 第2経路

CLK、CLKB 入力クロック

CLK_OUT、CLKB_OUT 出力クロック

C<1:5> デューティ調節コード

H<1:4> ハイパルスコード

L<1:4> ローパルスコード

S<1:4> 差異値

PG1〜PG8 パスゲート

SEL 選択信号

UP/DN アップ・ダウン信号

UPDATE1〜5 アップデート信号

【技術分野】

【0001】

本発明は、デューティ感知回路およびこれを備えるデューティ補正回路に関するもので、詳しくは、デューティの歪曲した程度を一度で正確に測定可能にする技術に関するものである。

【背景技術】

【0002】

半導体メモリー装置のようにクロックに基づいて動作する半導体装置において、クロックのデューティ(duty)が正確に制御されることは大変重要である。クロックのデューティが50%というのは、1つのクロック信号において、「ハイ」レベル区間と「ロー」レベル区間の長さ(時間的大きさ)が同じであるということを意味する。

【0003】

半導体メモリー装置の場合、クロックの立ち上がりエッジ(rising edge)および立ち下がりエッジ(falling edge)に正確に同期されデータが入・出力されなければならない。このような半導体装置においてクロックのデューティが正確に50%とならなければ、立ち上がりエッジと立ち下がりエッジとの間のタイミングがずれてしまい、データが正確なタイミングで入・出力されない。したがって半導体メモリー装置ではクロックのデューティを正確に50%に合わせるためにデューティ補正回路(DCC:Duty Cycle Correcter)が使用される。

【0004】

既存のデューティ補正回路は、クロックのデューティの補正において多くの短所を有している。

【0005】

第一に、既存のデューティ補正回路は、クロックのハイパルス幅(ハイレベルである時間)とローパルス幅(ローレベルである時間)とを比較してアップ・ダウン信号等を生成し、アップ・ダウン信号によってデューティ比を少しずつ補正する方法を使用する。このようなデューティ補正回路は幾度もの比較動作を終えて初めてデューティの補正が完了するため、ロッキングタイム(補正に要する時間)が長くなるという問題がある。

【0006】

第二に、デジタル方式のデューティ補正回路は、デューティ感知回路自体のオフセットによって、正確なデューティ比を測定するのが難しいという問題がある。

【0007】

第三に、デューティ補正対象クロックの周波数範囲が限定されているという問題、すなわちデューティ補正可能な入力クロックの周波数範囲に制限があるという問題がある。

【発明の開示】

【発明が解決しようとする課題】

【0008】

本発明は、前記した従来技術の問題点を解決するために提案されたものであり、その目的は、デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供することにある。

【課題を解決するための手段】

【0009】

前記した目的を達成するための本発明に係るデューティ補正回路は、デューティ調節コードに応答して入力クロックのデューティを調節した出力クロックを生成するデューティ調節部と、前記出力クロックのハイパルス幅とローパルス幅との差異を測定してその差異値を出力するデューティ感知部と、前記差異値を累積して前記デューティ調節コードを生成する累積部とを備える。

【0010】

また、前記した目的を達成するための本発明に係るデューティ感知回路は、クロックのハイパルス幅を測定してハイパルスコードを生成し、前記クロックのローパルス幅を測定してローパルスコードを生成する測定部と、前記ハイパルスコードと前記ローパルスコードとを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号を生成する比較部と、前記ハイパルスコードおよび前記ローパルスコードのうち、大きい方の値から小さい方の値を減算して差異値コードを生成する減算部とを備える。

【発明の効果】

【0011】

本発明のデューティ補正回路は、ハイパルス幅およびローパルス幅を測定し、測定された値の差異を利用して直ちにデューティを補正する。したがって、1サイクルの動作だけでデューティ比が補正されるため、従来に比べてロッキングタイムを顕著に減少させることができる。

【0012】

また、同一の構成によって、ハイパルス幅およびローパルス幅を測定し、測定された値が差異値のみを利用するため、ハイパルス幅を測定するときに発生するオフセット、およびローパルス幅を測定するときに発生するオフセットが除去されるという長所がある。

【図面の簡単な説明】

【0013】

【図1】本発明に係るデューティ補正回路の一実施形態の構成図である。

【図2】図1のデューティ感知部120の一実施形態の構成図である。

【図3】図2の測定部210の一実施形態の構成図である。

【図4】図3の遅延部332の一実施形態の構成図である。

【図5A】図3に図示された測定部210でハイパルスコードH<1:4>が生成される過程を表した図である。

【図5B】測定部210でローパルスコードL<1:4>が生成される過程を表した図である。

【図6】図1の累積部130の一実施形態の図である。

【図7】図1のデューティ調節部110の一実施形態の図である。

【図8】デューティ調節部110によりデューティが調節されるのを図示した図である。

【図9】本発明によるデューティ補正回路の全体動作を表した図である。

【図10】図3に図示された測定部210に初期値調節部1000が追加されたことを図示した図である。

【図11】図10の遅延部1020の一実施形態の図である。

【発明を実施するための形態】

【0014】

以下、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施することができるように詳細に説明するため本発明の最も好ましい実施形態を、添付図を参照して説明する。

【0015】

図1は、本発明に係るデューティ補正回路の一実施形態の構成を示すブロック図である。

【0016】

本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、差異値S<1:4>を累積してデューティ調節コードC<1:5>を生成する累積部130とを備えて構成される。なお、デューティ補正回路に必須の構成ではないが、図1には、クロックの入力を受ける入力端を表すCLKRX101と、CMLレベルのクロックをCMOSレベルに変化させるシフター(shifter)を表すCMLtoCMOS102とを示している。

【0017】

デューティ感知部120は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅を測定して、その差異値S<1:4>(4ビット)を出力する。ハイパルス幅とローパルス幅との差異値S<1:4>は、現在のクロックのデューティが歪曲している程度を表す。また、デューティ感知部120は、ハイパルス幅がローパルス幅よりも大きいのか、または、ローパルス幅がハイパルス幅よりも大きいのかを表すアップ・ダウン信号UP/DNを出力するが、アップ・ダウン信号UP/DNは、クロックのデューティがどの方向に歪曲したのかを表わす信号となる。

【0018】

従来のデューティ感知部は、デューティが歪曲した方向を表わす情報だけを生成し、デューティがどれほど歪曲したのかを表す情報を生成しなかった。したがってデューティが歪曲した方向に応じて少しずつデューティを調節するほかなく、これに伴ってデューティ補正回路は幾度ものサイクル(cycle)の間、動作しなければならなかった。しかし本発明のデューティ感知部は、デューティが歪曲した方向UP/DNだけでなく、デューティが歪曲した程度に関する情報S<1:4>も生成する。したがってデューティ補正回路は、1サイクルの動作のみでデューティを正確に補正できるようになる。

【0019】

累積部130は、デューティ感知部120から出力される差異値S<1:4>を累積してデューティ調節コードC<1:5>(5ビット)を生成する。ここでの累積とは差異値S<1:4>を加算または減算することを意味するが、加算するのか減算するのかの可否はアップ・ダウン信号UP/DN(図2参照)によって決定される。すでにデューティ感知部120からはクロックのデューティを補正するために必要な十分な情報が出力されているため、1サイクルの動作のみでデューティの完全な調節が可能である。しかしクロックのデューティを調節した後もいろいろな要因によってデューティが再び歪曲する場合が発生し得る。累積部130は、デューティの補正後に再びデューティが歪曲した場合に備えるために具備される。

【0020】

例えば、最初にクロックのデューティが+5の分だけ(+はハイパルス幅がローパルス幅より大きいことを意味し、5は差の程度を意味する)歪曲したとすれば、クロックのデューティを+5の分だけ調節すればデューティは完全に補正される。しかしデューティ補正後にデューティが+2の分だけさらに歪曲したとすれば、既存の+5にさらに+2を足してデューティ調節コードC<1:5>の値を+7にしなければならない。累積部130は、このような役割を担当することになる。

【0021】

デューティ調節部110は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節して出力する。デューティ調節コードC<1:5>は、クロックがどの方向に歪曲したのか、およびどれだけ歪曲したのかに関する情報を含んでいるため、このようなデューティ調節コードC<1:5>を利用して入力クロックCLK、CLKBのデューティを調節し、出力クロックCLK_OUT、CLKB_OUTを生成することが可能である。

【0022】

上記したように、図1のCLKRX101は、クロックの入力を受ける入力端を表し、CMLtoCMOS102は、CMLレベルのクロックをCMOSレベルに変化させるシフター(shifter)を表す。下記の詳細の実施形態において、本発明のデューティ調節部110が、CML(Current Mode Logic)レベルでスイングするクロックのデューティを調節することを例示するために、そのための構成を図1に図示したが、デューティ調節部110が、CMOSレベルでスイングする(変化する)クロックのデューティを調節する場合には、CLKRX101、CMLtoCMOS102は不要である。デューティ調節部110が、CMOSレベルでスイングするクロックのデューティを調節するのか、CMLレベルでスイングするクロックのデューティを調節するのかは、状況に応じて変更可能な選択的な問題に過ぎないため、このようなレベルを変換するための構成は、デューティ補正回路に必須の構成ではない。

【0023】

図2は、図1のデューティ感知部120の一実施形態の構成を示すブロック図である。

【0024】

図2に図示されたように、デューティ感知部120は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅を測定してハイパルスコードH<1:4>を生成し、出力クロックCLK_OUT、CLKB_OUTのローパルス幅を測定してローパルスコードL<1:4>を生成する測定部210と、ハイパルスコードH<1:4>とローパルスコードL<1:4>とを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号UP/DNを生成する比較部220と、ハイパルスコードH<1:4>とローパルスコードL<1:4>とのうち、大きい値から小さい値を減算して差異値コードS<1:4>を生成する減算部230とを備え構成される。

【0025】

測定部210は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅を測定してハイパルスコードH<1:4>およびローパルスコードL<1:4>を生成する。測定部210でのハイパルス幅の測定およびローパルス幅の測定は順次成されるが、SEL信号が「ハイ」レベルである間にはハイパルス幅の測定が成され、SEL信号が「ロー」レベルである間にはローパルス幅の測定が成される。したがって測定部210の出力信号は、まずハイパルスコードH<1:4>が出力され、その後からローパルスコードL<1:4>が出力される。

【0026】

測定部210の出力端にあるラッチ211、212は、ハイパルスコードH<1:4>およびローパルスコードL<1:4>を各々一旦保存するために具備される。図2では、ラッチ211、212を測定部210とは別の構成要素として図示したが、ラッチ211、212を測定部210内に具備されるように構成することもできる。ラッチ211、212は、単にハイパルスコードH<1:4>およびローパルスコードL<1:4>を保存する役割だけを担うが、デューティ感知部210内の構成要素のタイミングチューニング(タイミングを揃えること)等を適切に行える場合には、ラッチ211、212を無くしてデューティ感知部210を構成することもできる。ラッチ211に入力されるUPDATE1信号、UPDATE2信号は、ラッチ211、212がハイパルスコードH<1:4>およびローパルスコードL<1:4>の入力を受ける時点(タイミング)を決定するための信号である。

【0027】

比較部220は、ハイパルスコードH<1:4>とローパルスコードL<1:4>とを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号UP/DNを生成する。比較部220に入力されるUPDATE3信号は、ハイパルスコードH<1:4>およびローパルスコードL<1:4>が比較部220に入力される時点を決定するための信号である。

【0028】

減算部230は、ハイパルスコードH<1:4>のコード値とローパルスコードL<1:4>のコード値との差異、すなわちハイパルス幅とローパルス幅との差異を求める役割を担う。減算部230は、アップ・ダウン信号UP/DNを利用してハイパルスコードH<1:4>およびローパルスコードL<1:4>のうち、どちらのコードがより大きいのかを判断して大きい値から小さい値を減算し差異値コードS<1:4>を生成する。減算部230に入力されるUPDATE4信号は、減算部230にハイパルスコードH<1:4>およびローパルスコードL<1:4>が入力される時点を決定するための信号である。

【0029】

図3は、図2の測定部210の一実施形態の構成を示すブロック図である。

【0030】

測定部210は、出力クロックCLK_OUT、CLKB_OUT(CLK_OUTが正クロック、CLKB_OUTが負クロック)を第1経路IN1、第2経路IN2に伝達する経路選択部310と、第1経路IN1および第2経路IN2に伝達されたクロックの入力を受けてハイパルス幅またはローパルス幅を測定するための直列に接続された複数の選択遅延端)320〜350を備え構成される。

【0031】

経路選択部310は、SEL信号が「ハイ」レベルである間は、正クロックCLK_OUTを第1経路IN1に伝達し、負クロックCLKB_OUTを第2経路IN2に伝達する。そして選択信号SELが「ロー」レベルである間には負クロックCLKB_OUTを第1経路IN1に伝達し、正クロックCLK_OUTを第2経路IN2に伝達する。SEL信号が「ハイ」レベルである区間は、出力クロックCLK_OUT、CLKB_OUTのハイパルス幅が測定される区間であり、SEL信号が「ロー」レベルである区間は、出力クロックCLK_OUT、CLKB_OUTのローパルス幅が測定される区間である。

【0032】

選択遅延端320〜350の各々は、第1経路IN1のクロックと第2経路IN2のクロックとの位相を比較する位相比較部(PD)321、331、341、351と、位相比較部321、331、341、351の比較結果Q<4>、Q<3>、Q<2>、Q<1>に応じて第1経路IN1のクロックまたは第2経路IN2のクロックを遅延させる遅延部322、332、342を備え構成される。

【0033】

位相比較部321、331、341、351は、第1経路IN1に伝達されたクロックの立ち上がりエッジ(rising edge)が、第2経路IN2に伝達されたクロックの立ち上がりエッジより先んじる場合には「1」の値を出力し、その反対の場合には「0」の値を出力する。遅延部322、332、342は、位相比較部321、331、341の比較結果Q<4>、Q<3>、Q<2>が「1」の場合には第1経路IN1のクロックを遅延させ、位相比較部321、331、341の比較結果Q<4>、Q<3>、Q<2>が「0」の場合には第2経路IN2のクロックを遅延させる。それぞれの遅延部322、332、342の遅延値は40PS(Pico Second)、20PS、10PSのようにバイナリウェイト(binary weight)を有するように設計される。

【0034】

第1経路IN1に正クロックCLK_OUTが入力され、第2経路IN2に負クロックCLKB_OUTが入力された場合、位相比較部321、331、341、351の出力値Q<4>、Q<3>、Q<2>、Q<1>は、ハイパルスコードH<1:4>となる(Q<1:4>=H<1:4>)。そして第1経路IN1に負クロックCLKB_OUTが入力され、第2経路IN2に正クロックCLK_OUTが入力される場合に位相比較部321、331、341、351の出力値Q<4>、Q<3>、Q<2>、Q<1>はローパルスコードL<1:4>となる(Q<1:4>=L<1:4>)。

【0035】

図3を参照すれば、最終端の選択遅延端350には遅延部が省略されていることが分かるが、これは、これ以上後端の選択遅延端が存在しないために遅延部を省略して構成したものである。

【0036】

初期遅延部311は、第1経路IN1に伝達されたクロックを一定時間遅延させ、ハイパルスコードH<1:4>およびローパルスコードL<1:4>の測定が速く成され得るようにするため具備されたものであり、本発明の必須の構成要素には該当しない。測定されたハイパルスコードH<1:4>およびローパルスコードL<1:4>は、初期遅延部311の遅延値の分だけ誤差を有するようになりはするが、本発明においてデューティの感知のために重要な値はハイパルスコードH<1:4>およびローパルスコードL<1:4>自体ではなく、2つのコードの差異値であるため、このような誤差は問題とならない。

【0037】

本発明は同一の選択遅延端320、330、340、350を利用して出力クロックCLK_OUT、CLKB_OUTのハイパルスコードH<1:4>およびローパルスコードL<1:4>を測定し、測定されたハイパルスコードH<1:4>とローパルスコードL<1:4>との差異を利用してデューティを感知する。したがって製造工程上、選択遅延端320、330、340、350にオフセット(offset)が発生したとしてもハイパルスコードH<1:4>とローパルスコードL<1:4>との差異を求める過程においてこのようなオフセットの影響が除去されるという長所がある。

【0038】

図3では、経路選択部310を利用して正クロックCLK_OUTおよび負クロックCLKB_OUTの経路を変え、同一の選択遅延端320、330、340、350を介して、ハイパルスコードH<1:4>およびローパルスコードL<1:4>を生成するが、経路選択部310なしで、ハイパルスコードH<1:4>を測定するための選択遅延端と、ローパルスコードL<1:4>を測定するための選択遅延端とを、それぞれ別に具備するよう設計することも可能である。

【0039】

図4は、図3の遅延部332の一実施形態の構成を示す回路図である。

【0040】

遅延部332は、位相比較部331の出力値Q<3>に応じてオン・オフされるパスゲートPG1〜PG8と遅延手段410、420とを備え構成される。

【0041】

位相比較部331の出力値Q<3>が「1」の値を有すれば、第1経路IN1のクロックは遅延手段420を介してOUT1に出力され、第2経路IN2のクロックは遅延手段410を介してOUT2に出力される。したがって第1経路IN1のクロックが第2経路IN2のクロックより20PSだけ遅延される。

【0042】

位相比較部331の出力値Q<3>が「0」の値を有すれば、第1経路IN1のクロックは遅延手段410を介してOUT1に出力され、第2経路IN2のクロックは遅延手段420を介してOUT2に出力される。したがって第2経路IN2のクロックが第1経路IN1のクロックより20PSだけ遅延されることになる。図4において、遅延手段420の下方に記載された「1+20PS」は、第2経路IN2の遅延時間が第1経路IN1の遅延時間(遅延手段410の下方に記載された「1」で表されている)よりも20PSだけ長いことを意味する。

【0043】

本発明で重要なのは、遅延手段410と遅延手段420間の遅延値の差異であるため、遅延手段420が、遅延手段410よりも、予め設定された値(例えば、上記した20PS)だけの遅延値をさらに有するように設計する。このような遅延手段410、420を設計する方法が無数に多いこと、及び、任意に設計・選択可能なことは、当業者にとっては当然のことである。

【0044】

図5Aは、図3に図示された測定部210でハイパルスコードH<1:4>が生成される過程を表した図であり、図5Bは、測定部210でローパルスコードL<1:4>が生成される過程を表す図である。

【0045】

図5Aは、第1経路IN1に正クロックCLK_OUTが入力され、第2経路IN2に負クロックCLKB_OUTが入力され、ハイパルスコードH<1:4>が測定される過程を図示するものである。

【0046】

まず、正クロックCLK_OUTは、初期遅延部311の遅延値の分だけ遅延される(1STEP)。その結果、初期遅延部311によって正クロックCLK_OUTは遅延されたが、依然として正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジより先んじている。したがって位相比較部321の出力値Q<4>は「1」となり、これに伴い遅延部322は、正クロックCLK_OUTを負クロックCLKB_OUTより40PSだけさらに遅延させる(2STEP)。これで正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジより遅延する。したがって位相比較部331の出力値Q<3>は「0」となり、遅延部332は、負クロックCLKB_OUTを正クロックCLK_OUTより20PSだけさらに遅延させる(3STEP、図5Aには便宜上、正クロックが20PSだけ先んじるものとして表現する)。その結果、正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジよりさらに先んじることになる。したがって位相比較部341の出力値Q<2>は「1」となり、遅延部342は、正クロックCLK_OUTを10PSの分だけさらに遅延させる(4STEP)。依然として正クロックCLK_OUTの立ち上がりエッジは負クロックCLKB_OUTの立ち上がりエッジより先んじている。したがって位相比較部351の出力値Q<1>は「1」になる。位相比較部321、331、341、351の出力値(Q<1:4>)は、ハイパルスコードH<1:4>となるため、ハイパルスコードH<1:4>は「1011」(右端が最下位ビットであるH<1>、左端が最上位ビットであるH<4>)の値を有するようになる。

【0047】

図5Bは、第1経路IN1に負クロックCLKB_OUTが入力され、第2経路IN2に正クロックCLK_OUTが入力され、ローパルスコードL<1:4>が測定される過程を図示したものである。

【0048】

まず、負クロックCLKB_OUTは、初期遅延部311の遅延値の分だけ遅延される(1STEP)。その結果、初期遅延部311によって負クロックCLKB_OUTは遅延されたが、依然として負クロックCLKB_OUTの立ち上がりエッジは正クロックCLK_OUTの立ち上がりエッジより先んじている。したがって位相比較部321の出力値Q<4>は「1」となり、これに伴い遅延部322は、負クロックCLKB_OUTを正クロックCLK_OUTより40PSだけさらに遅延させる(2STEP)。これで負クロックCLKB_OUTの立ち上がりエッジは、正クロックCLK_OUTの立ち上がりエッジより遅れる。したがって位相比較部331の出力値Q<3>は、「0」となり、遅延部332は、正クロックCLK_OUTを負クロックCLKB_OUTより20PSだけさらに遅延させる(3STEP、図5Bには便宜上、負クロックが20PSだけ先んじるものとして表現する)。その結果、依然として負クロックCLKB_OUTの立ち上がりエッジは正クロックCLK_OUTの立ち上がりエッジより遅れている。したがって位相比較部341の出力値Q<2>は「0」となり、遅延部342は、正クロックCLK_OUTを負クロックCLKB_OUTより10PSだけさらに遅延させる(4STEP、図5Bには便宜上、負クロックが10PSだけ先んじるものしてと表現する)。これで負クロックCLKB_OUTの立ち上がりエッジは、正クロックCLK_OUTの立ち上がりエッジより先んじることになる。したがって位相比較部351の出力値Q<1>は「1」となる。位相比較部321、331、341、351の出力値(Q<1:4>)は、ローパルスコードL<1:4>になるため、ローパルスコード(L<1:4>)は「1001」(右端が最下位ビットであるL<1>、左端が最上位ビットであるL<4>)の値を有するようになる。

【0049】

図6は、図1の累積部130の一実施形態の構成を示すブロック図である。

【0050】

累積部130は、デューティ調節コードC<1:5>を保存するラッチ部620と、ラッチ部620に保存されたデューティ調節コードC<1:5>にアップ・ダウン信号UP/DNに応じて差異値S<1:4>を加算または減算する演算部610とを備え構成される。

【0051】

ラッチ部620は、デューティ調節部110がデューティ調節をしないようにする値をデューティ調節コードC<1:5>の初期値として保存している。本実施形態では、その初期値を「10000」とする(初期値は「10000」以外の値であってもよい)。次にラッチ部620は、演算部610の演算結果値である出力をデューティ調節コードC<1:5>として保存していくことになる。図6のUPDATE5信号は、演算部610の演算結果がラッチ部620に保存される時点を決定する信号に該当する。

【0052】

演算部610は、ラッチ部620に保存されていたデューティ調節コードC<1:5>値に差異値コードS<1:4>を加算または減算する役割をする。アップ・ダウン信号UP/DNが「ハイ」値を有する場合、ラッチ部620に保存されていたデューティ調節コードC<1:5>値に差異値コードS<1:4>が加算され、アップ・ダウン信号UP/DNが「ロー」値を有する場合には、ラッチ部620に保存されていた値から差異値コードS<1:4>を減算することになる。

【0053】

例えば、デューティ調節コードC<1:5>が「10000」であり、アップ・ダウン信号UP/DNが「ハイ」レベル、差異値コードS<1:4>が「0011」で入力されると、デューティ調節コードC<1:5>(演算部610の出力と同じ)は、「10011」となる。また、デューティ調節コードC<1:5>が「10000」であり、アップ・ダウン信号UP/DNが「ロー」レベル、差異値コード(S<1:4>)が「0011」で入力されると、デューティ調節コードC<1:5>(演算部610の出力と同じ)は「01101」となる。即ち、最下位ビットを揃えて演算が行われる。

【0054】

図7は、図1のデューティ調節部110の一実施形態を示す回路図である。

【0055】

デューティ調節部110は、入力クロックCLK、CLKBのうちの正クロック(RX_OUT、CLKINが出力されるものである)のレベルを調節する正クロック調節部710と、負クロック(RX_OUTB、CLKINBが出力されるものである)のレベルを調節する負クロック調節部730とを備えて構成される。

【0056】

正クロック調節部710は、バイナリウェイトを有するトランジスタ711〜714を利用して正クロックRX_OUTのレベルを調節することによってデューティを補正する。正クロック調節部710は、デューティ調節コードC<1:5>の最上位ビットC<5>が「1」の値を有する時に動作する。デューティ調節コードC<1:5>の最上位ビットC<5>が「1」の値を有するということは、ハイパルスコードH<1:4>値がローパルスコードL<1:4>値より大きいということを意味するため、正クロックRX_OUTのレベルを低くする必要がある。

【0057】

デューティ調節コードC<1:5>の最上位ビットC<5>が「1」の場合、NANDゲート715〜718の出力端に接続したインバータ(719〜722)の出力値は、各々のデューティ調節コードC<1:4>の値に応じて決定される。最上位ビットC<5>を除外したデューティ調節コードC<1:4>の値は、ハイパルス幅がローパルス幅よりどれくらい大きいのかを表す値であるため、デューティ調節コードC<1:4>の値に応じてトランジスタ711〜714をターンオンさせることになり、その結果、正クロックRX_OUTのレベルはデューティ調節コードC<1:4>の値に比例して低くなる。これはハイパルス幅が、デューティ調節コードC<1:4>の値に比例して狭くなることを意味することになる。

【0058】

負クロック調節部730は、バイナリウェイトを有するトランジスタ731〜734を利用して負クロックRX_OUTBのレベルを調節することによってデューティを補正する。負クロック調節部730は、デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の値を有するときに動作する。デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の値を有するということは、ローパルスコードL<1:4>値がハイパルスコードH<1:4>値より大きいということを意味するため、デューティの補正のためには負クロックRX_OUTBのレベルを低くする必要がある。

【0059】

デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の場合、NORゲート735〜738の出力値は、各々のデューティ調節コードC<1:4>の値と反対の値(各ビットを反転させた値)を有するようになる。これはデューティ調節コードC<1:5>の初期値の「10000」と現在のデューティ調節コードC<1:5>値との差異に比例するようにトランジスタ731〜734がターンオンされることを意味する。すなわち、ローパルス幅がハイパルス幅よりどれくらい大きいのかに比例してトランジスタ731〜734がターンオンされ、ローパルス幅を減らすことになる。

【0060】

デューティ調節部110の動作を簡単に整理すれば、デューティ調節部110は、デューティ調節コードC<1:5>が初期値「10000」より大きくなった場合は、大きくなった分だけ正クロックRX_OUTのレベルを低くし、デューティ調節コードC<1:5>が初期値「10000」より小さくなった場合は、小さくなった分だけ負クロックRX_OUTBのレベルを低くし、クロックのデューティを調節することになる。

【0061】

バイアス電圧BIASの入力を受けるトランジスタ723〜726、739〜742は各々のノードに流れる電流が過度に多くなることを防止する役割を担う。

【0062】

図8は、デューティ調節部110によってデューティが調節されることを図示したグラフである。横軸は時間であり、縦軸は例えば電圧である。

【0063】

図8には、デューティ調節コードC<1:5>の最上位ビットC<5>が「0」の場合、すなわち負クロック調節部730が動作する場合における負クロックRX_OUTBのレベルの変化を、近接する16本の曲線で図示した。図8を参照すれば、デューティ調節コードC<1:4>に応じて負クロックRX_OUTBのレベルが低くなる程度が異なることを確認することができる。

【0064】

正クロックRX_OUTの立ち上がりエッジと負クロックRX_OUTBの立ち下がりエッジとが交差する地点(横軸の値を意味する。以下同じ)から、正クロックRX_OUTの立ち下がりエッジと負クロックRX_OUTBの立ち上がりエッジとが交差する地点までがクロックのハイパルス幅を表している。また、正クロックRX_OUTの立ち下がりエッジと負クロックRX_OUTBの立ち上がりエッジとが交差する地点から、正クロックRX_OUTの立ち上がりエッジと負クロックRX_OUTBの立ち下がりエッジとが交差する地点までがクロックのローパルス幅を表している。

【0065】

図9は、本発明に係るデューティ補正回路の全体的な動作を示すタイミングチャートである。

【0066】

まず、SEL信号が「ハイ」値を有する間、経路選択部310は、出力クロックの正クロックCLK_OUTを第1経路IN1に伝達し、出力クロックの負クロックCLKB_OUTを第2経路IN2に伝達する。したがって測定部210では、ハイパルス幅が測定される。ハイパルスコードH<1:4>の生成が完了した以後にUPDATE1信号がイネーブルされ(ハイレベルになる。以下同じ)、ラッチ211にハイパルスコードH<1:4>が保存される。以下、測定されたハイパルスコードH<1:4>の値は、「1011」であると仮定して説明することにする。

【0067】

次にSEL信号が「ロー」値を有するようになれば、経路選択部310は、出力クロックの負クロックCLKB_OUTを第1経路IN1に伝達し、出力クロックの正クロックCLK_OUTを第2経路IN2に伝達する。したがって測定部210ではローパルス幅が測定される。ローパルスコードL<1:4>の生成が完了した以後にUPDATE2信号がイネーブルされ、ラッチ212にローパルスコードL<1:4>が保存される。以下、測定されたローパルスコードL<1:4>の値は「1001」であると仮定して説明することにする。

【0068】

次にUPDATE3信号がイネーブルされ、比較部220に、ハイパルスコードH<1:4>として「1011」が入力され、ローパルスコードL<1:4>として「1001」が入力される。ハイパルスコードH<1:4>である「1011」がローパルスコードL<1:4>である「1001」より大きい値を有するため、比較部220は、アップ・ダウン信号UP/DNのレベルを「ハイ」で出力することになる。

【0069】

これでUPDATE4信号がイネーブルされ、減算部230に、ハイパルスコードH<1:4>である「1011」、ローパルスコードL<1:4>である「1001」、およびアップ・ダウン信号UP/DNが入力される。アップ・ダウン信号UP/DNが「ハイ」レベルであるため、減算部230は、ハイパルスコードH<1:4>である「1011」からローパルスコードL<1:4>である「1001」を減算し、差異値コードS<1:4>として「0010」を生成することになる。

【0070】

累積部130の演算部610は、ラッチ部620に保存されたデューティ調節コードC<1:5>の初期値「10000」に差異値コード(S<1:4>、ここでは「0010」)を加算する。そしてUPDATE5信号がイネーブルされ、演算部610の演算結果、即ち「10010」が新たなデューティ調節コードC<1:5>としてラッチ部620に保存されることになる。

【0071】

デューティ調節コードC<1:5>が「10010」であり、最上位ビットC<5>が「1」であるため、デューティ調節部110の正クロック調節部710が動作することになり、正クロック調節部710は、デューティ調節コードC<1:4>である「0010」の値に比例して正クロックRX_OUTのレベルを低くし、デューティを補正する。

【0072】

選択信号SELおよびアップデート信号UPDATE1〜5は、図9に図示された通り順次に活性化するように生成するが、このような信号を生成する手段は、本発明が属する技術分野で通常の知識を有する者ならば容易に実現することができるため、これに対するこれ以上の説明は省略する。

【0073】

図10は、図3に図示された測定部210に初期値調節部1000が追加されたことを図示したブロック図である。初期値遅延部311は省略されている。

【0074】

クロックCLK_OUT、CLKB_OUTの周波数が変われば、クロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅もこれに伴い変わることになる。したがって、クロックCLK_OUT、CLKB_OUTの周波数の変化に応じて測定部210がクロックCLK_OUT、CLKB_OUTのハイパルス幅およびローパルス幅を正しく測定できない場合が発生し得る。

【0075】

例えば、測定された結果、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が「1111」になった場合を考えてみよう。ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値「1111」になったとすれば、これはハイパルス幅またはローパルス幅が測定部210の測定可能な範囲を外れたものと考えることができる。これとは反対にハイパルスコードH<1:4>またはローパルスコードL<1:4>が最小値「0000」になった時も、ハイパルス幅またはローパルス幅が測定部210の測定可能な範囲を外れたものと考えることができる。

【0076】

図10の測定部210は、このような場合に備えるため、図3の測定部210に初期値調節部1000をさらに備える。

【0077】

初期値調節部1000は、ラッチ211、212に保存されたハイパルスコードH<1:4>およびローパルスコードL<1:4>の入力を受け、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値「1111」または最小値「0000」の場合、第1経路IN1または第2経路IN2の初期遅延値を変更させる。

【0078】

ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値である「1111」になったということは、初期遅延部311の遅延値が正確な測定のために必要な値より小さいということができる。したがって、このような場合には第1経路IN1の遅延値を増やすことが必要になる。また、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最小値である「0000」になったということは、初期遅延部311の遅延値が正確な測定のために必要な値より大きいということができる。したがってこのような場合には第2経路IN2の遅延値を増やすことが必要になる。

【0079】

初期値調節部1000は、デコーダ部1010と遅延部1020とを備え構成され得る。デコーダ部1010は、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最大値になった場合には、RANGE<1>信号を「ロー」レベルに活性化させる。また、ハイパルスコードH<1:4>またはローパルスコードL<1:4>が最小値になった場合には、RANGE<2>信号を「ロー」レベルに活性化させる。

【0080】

遅延部1020は、RANGE<1>信号が「ロー」に活性化すれば第1経路IN1の遅延値を増やし、RANGE<2>信号が「ロー」に活性化すれば第2経路IN2の遅延値を増やすことで、ハイパルスコードH<1:4>およびローパルスコードL<1:4>が正しく生成されるようにする。

【0081】

図10に図示されたように、測定部210に初期値調節部1000が具備されるように構成する場合には、測定部210が測定可能なハイパルス幅およびローパルス幅の範囲を変更することが可能であるため、多様な周波数のクロックが入力されたとしても、正確な動作が保障されるという長所がある。

【0082】

図11は、図10の遅延部1020の一実施形態を示す回路図である。

【0083】

図11に図示された遅延部1020は、下記表1のようにRANGE<1>信号およびRANGE<2>信号が活性化されるようにデコードする。表1には、RANGE<1>信号およびRANGE<2>信号が活性化する条件だけを示したが、表1に示されていないコードH<1:4>、L<1:4>の組合せの場合、RANGE<1>信号およびRANGE<2>信号は、共に非活性化状態(即ちハイレベル)を維持する。

【0084】

【表1】

【0085】

表1において、×は任意の値、即ち「0」または「1」のどちらの値であってもよいことを表す。

【0086】

RANGE<1>信号は、ハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち、少なくとも一方が最大値「1111」であり、且つ、最大値である一方が他方のコード値と小さい差異(00××以下の差異)を示すときに活性化する。ハイパルスコードH<1:4>値およびローパルスコードL<1:4>値が最大値である場合も、この条件に当てはまる。単純にハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち一方が最大値でさえすれば、他方の値に依らずにRANGE<1>信号が活性化するようにすることもできるが、2つのコードH<1:4>値およびL<1:4>値が大きい差異を示すということは、測定されたコードH<1:4>値およびL<1:4>値に大きな異常がないということも意味し得るため、上記のようにデコードがされるようにした。さらには、2つのコードH<1:4>値およびL<1:4>値が共にほとんど最大値に近い値になった場合には、コードH<1:4>値およびL<1:4>値が誤っている可能性が高いためである。

【0087】

RANGE<2>信号は、ハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち、一方が最小値「0000」であり、且つ、最小値である一方が他方のコード値と小さい差異(00××以下の差異)を示すときに活性化する。単純にハイパルスコードH<1:4>値またはローパルスコードL<1:4>値のうち一方が最小値でさえすれば、他方の値に依らずにRANGE<2>が活性化するようにデコーダ部1020を構成しなかった理由は、RANGE<1>について上記した理由と同様である。

【0088】

本発明は、上記したように、好ましい実施形態によって具体的に記述されたが、上記した実施形態は、本発明を説明するためのものであり、本発明を制限するためのものではない。また、本発明の技術分野の通常の専門家ならば、本発明の技術的範囲内で多様な実施形態が可能であることを知ることができるであろう。

【符号の説明】

【0089】

110 デューティ調節部

101 CLKRX

102 CMLtoCMOS

120 デューティ感知部

130 累積部

210 測定部

211、212 ラッチ

220 比較部

230 減算部

310 経路選択部

311 初期遅延部

320〜350 選択遅延端

321、331、341、351 位相比較部(PD)

322、332、342 遅延部

410、420 遅延手段

610 演算部

620 ラッチ部

710 正クロック調節部

730 負クロック調節部

1000 初期値調節部

1010 デコーダ部

1020 遅延部

IN1 第1経路

IN2 第2経路

CLK、CLKB 入力クロック

CLK_OUT、CLKB_OUT 出力クロック

C<1:5> デューティ調節コード

H<1:4> ハイパルスコード

L<1:4> ローパルスコード

S<1:4> 差異値

PG1〜PG8 パスゲート

SEL 選択信号

UP/DN アップ・ダウン信号

UPDATE1〜5 アップデート信号

【特許請求の範囲】

【請求項1】

デューティ調節コードに応答して入力クロックのデューティを調節した出力クロックを生成するデューティ調節部と、

前記出力クロックのハイパルス幅とローパルス幅との差異を測定してその差異値を出力するデューティ感知部と、

前記差異値を累積して前記デューティ調節コードを生成する累積部とを備えるデューティ補正回路。

【請求項2】

前記デューティ感知部が、

前記差異値と共に、前記ハイパルス幅および前記ローパルス幅のうち、どちらが大きいのかを表すアップ・ダウン信号を出力することを特徴とする請求項1に記載のデューティ補正回路。

【請求項3】

前記累積部が、

前記アップ・ダウン信号に応じて前記差異値を既存のデューティ調節コードに加算または減算することを特徴とする請求項2に記載のデューティ補正回路。

【請求項4】

前記デューティ感知部が、

前記出力クロックのハイパルス幅を測定してハイパルスコードを生成し、前記出力クロックのローパルス幅を測定してローパルスコードを生成する測定部と、

前記ハイパルスコードと前記ローパルスコードとを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号を生成する比較部と、

前記ハイパルスコードおよび前記ローパルスコードのうち、大きい方の値から小さい方の値を減算して前記差異値を生成する減算部とを備えることを特徴とする請求項1に記載のデューティ補正回路。

【請求項5】

前記測定部が、

前記出力クロックの正クロックおよび前記出力クロックの負クロックの入力を受けて前記ハイパルス幅または前記ローパルス幅を測定するための直列に接続した複数の選択遅延端を備え、

複数の前記選択遅延端の各々が、

前記正クロックと前記負クロックとの位相を比較する位相比較部と、

前記位相比較部の比較結果に応じて前記正クロックまたは前記負クロックを遅延させる遅延部とを備えることを特徴とする請求項4に記載のデューティ補正回路。

【請求項6】

前記測定部での前記ハイパルス幅の測定と前記ローパルス幅の測定とが、順次に成され、

複数の前記遅延選択端では、

ハイパルス幅を測定する時およびローパルス幅を測定する時に、前記正クロックと前記負クロックとが互いに異なる経路に伝達されることを特徴とする請求項5に記載のデューティ補正回路。

【請求項7】

各々の前記位相比較部から出力される前記比較結果が、前記ハイパルスコードまたは前記ローパルスコードになることを特徴とする請求項6に記載のデューティ補正回路。

【請求項8】

前記累積部が、

前記デューティ調節コードを保存するラッチ部と、

該ラッチ部に保存された前記デューティ調節コードに、前記アップ・ダウン信号に応じて前記差異値を加算または減算する演算部とを備えることを特徴とする請求項4に記載のデューティ補正回路。

【請求項9】

前記デューティ調節部が、

前記デューティ調節コードに応答して前記クロックの全体的なレベルを調節することによってデューティを補正することを特徴とする請求項1に記載のデューティ補正回路。

【請求項10】

クロックのハイパルス幅を測定してハイパルスコードを生成し、前記クロックのローパルス幅を測定してローパルスコードを生成する測定部と、

前記ハイパルスコードと前記ローパルスコードとを比較してどちらのコードがより大きいのかを表すアップ・ダウン信号を生成する比較部と、

前記ハイパルスコードおよび前記ローパルスコードのうち、大きい方の値から小さい方の値を減算して差異値コードを生成する減算部とを備えることを特徴とするデューティ感知回路。

【請求項11】

前記測定部が、

前記クロックの正クロックおよび前記クロックの負クロックを第1経路および第2経路に伝達する経路選択部と、

前記第1経路および前記第2経路に伝達されたクロックの入力を受けて前記ハイパルス幅または前記ローパルス幅を測定するための直列に接続した複数の選択遅延端とを備え、

複数の前記選択遅延端の各々が、

前記第1経路のクロックおよび前記第2経路のクロックの位相を比較する位相比較部と、

前記位相比較部の比較結果に応じて前記第1経路のクロックまたは前記第2経路のクロックを遅延させる遅延部とを備えることを特徴とする請求項10に記載のデューティ感知回路。

【請求項12】

前記測定部での前記ハイパルス幅の測定および前記ローパルス幅の測定が順次に成され、

前記ハイパルス幅を測定する時および前記ローパルス幅を測定する時に、前記正クロックと前記負クロックとは、前記第1経路および前記第2経路のうちの互いに異なる経路に伝達されることを特徴とする請求項11に記載のデューティ感知回路。

【請求項13】

前記経路選択部の後端には、

前記ハイパルスコードおよび前記ローパスコードのうち、少なくともいずれか一方が最大値または最小値を有する場合、前記第1経路または前記第2経路の初期遅延値を調節する初期値調節部をさらに備えることを特徴とする請求項12に記載のデューティ感知回路。

【請求項14】

前記経路選択部の後端には、

前記ハイパルスコードおよび前記ローパスコードのうち、少なくともいずれか一方が最大値または最小値を有し、且つ、前記ハイパルスコードの値と前記ローパスコードの値との差違が所定の値以下である場合、前記第1経路または前記第2経路の初期遅延値を調節する初期値調節部をさらに備えることを特徴とする請求項12に記載のデューティ感知回路。

【請求項1】

デューティ調節コードに応答して入力クロックのデューティを調節した出力クロックを生成するデューティ調節部と、

前記出力クロックのハイパルス幅とローパルス幅との差異を測定してその差異値を出力するデューティ感知部と、

前記差異値を累積して前記デューティ調節コードを生成する累積部とを備えるデューティ補正回路。

【請求項2】

前記デューティ感知部が、

前記差異値と共に、前記ハイパルス幅および前記ローパルス幅のうち、どちらが大きいのかを表すアップ・ダウン信号を出力することを特徴とする請求項1に記載のデューティ補正回路。

【請求項3】

前記累積部が、

前記アップ・ダウン信号に応じて前記差異値を既存のデューティ調節コードに加算または減算することを特徴とする請求項2に記載のデューティ補正回路。

【請求項4】

前記デューティ感知部が、

前記出力クロックのハイパルス幅を測定してハイパルスコードを生成し、前記出力クロックのローパルス幅を測定してローパルスコードを生成する測定部と、

前記ハイパルスコードと前記ローパルスコードとを比較して、どちらのコードがより大きいのかを表すアップ・ダウン信号を生成する比較部と、

前記ハイパルスコードおよび前記ローパルスコードのうち、大きい方の値から小さい方の値を減算して前記差異値を生成する減算部とを備えることを特徴とする請求項1に記載のデューティ補正回路。

【請求項5】

前記測定部が、

前記出力クロックの正クロックおよび前記出力クロックの負クロックの入力を受けて前記ハイパルス幅または前記ローパルス幅を測定するための直列に接続した複数の選択遅延端を備え、

複数の前記選択遅延端の各々が、

前記正クロックと前記負クロックとの位相を比較する位相比較部と、

前記位相比較部の比較結果に応じて前記正クロックまたは前記負クロックを遅延させる遅延部とを備えることを特徴とする請求項4に記載のデューティ補正回路。

【請求項6】

前記測定部での前記ハイパルス幅の測定と前記ローパルス幅の測定とが、順次に成され、

複数の前記遅延選択端では、

ハイパルス幅を測定する時およびローパルス幅を測定する時に、前記正クロックと前記負クロックとが互いに異なる経路に伝達されることを特徴とする請求項5に記載のデューティ補正回路。

【請求項7】

各々の前記位相比較部から出力される前記比較結果が、前記ハイパルスコードまたは前記ローパルスコードになることを特徴とする請求項6に記載のデューティ補正回路。

【請求項8】

前記累積部が、

前記デューティ調節コードを保存するラッチ部と、

該ラッチ部に保存された前記デューティ調節コードに、前記アップ・ダウン信号に応じて前記差異値を加算または減算する演算部とを備えることを特徴とする請求項4に記載のデューティ補正回路。

【請求項9】

前記デューティ調節部が、

前記デューティ調節コードに応答して前記クロックの全体的なレベルを調節することによってデューティを補正することを特徴とする請求項1に記載のデューティ補正回路。

【請求項10】

クロックのハイパルス幅を測定してハイパルスコードを生成し、前記クロックのローパルス幅を測定してローパルスコードを生成する測定部と、

前記ハイパルスコードと前記ローパルスコードとを比較してどちらのコードがより大きいのかを表すアップ・ダウン信号を生成する比較部と、

前記ハイパルスコードおよび前記ローパルスコードのうち、大きい方の値から小さい方の値を減算して差異値コードを生成する減算部とを備えることを特徴とするデューティ感知回路。

【請求項11】

前記測定部が、

前記クロックの正クロックおよび前記クロックの負クロックを第1経路および第2経路に伝達する経路選択部と、

前記第1経路および前記第2経路に伝達されたクロックの入力を受けて前記ハイパルス幅または前記ローパルス幅を測定するための直列に接続した複数の選択遅延端とを備え、

複数の前記選択遅延端の各々が、

前記第1経路のクロックおよび前記第2経路のクロックの位相を比較する位相比較部と、

前記位相比較部の比較結果に応じて前記第1経路のクロックまたは前記第2経路のクロックを遅延させる遅延部とを備えることを特徴とする請求項10に記載のデューティ感知回路。

【請求項12】

前記測定部での前記ハイパルス幅の測定および前記ローパルス幅の測定が順次に成され、

前記ハイパルス幅を測定する時および前記ローパルス幅を測定する時に、前記正クロックと前記負クロックとは、前記第1経路および前記第2経路のうちの互いに異なる経路に伝達されることを特徴とする請求項11に記載のデューティ感知回路。

【請求項13】

前記経路選択部の後端には、

前記ハイパルスコードおよび前記ローパスコードのうち、少なくともいずれか一方が最大値または最小値を有する場合、前記第1経路または前記第2経路の初期遅延値を調節する初期値調節部をさらに備えることを特徴とする請求項12に記載のデューティ感知回路。

【請求項14】

前記経路選択部の後端には、

前記ハイパルスコードおよび前記ローパスコードのうち、少なくともいずれか一方が最大値または最小値を有し、且つ、前記ハイパルスコードの値と前記ローパスコードの値との差違が所定の値以下である場合、前記第1経路または前記第2経路の初期遅延値を調節する初期値調節部をさらに備えることを特徴とする請求項12に記載のデューティ感知回路。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−114875(P2010−114875A)

【公開日】平成22年5月20日(2010.5.20)

【国際特許分類】

【出願番号】特願2009−108143(P2009−108143)

【出願日】平成21年4月27日(2009.4.27)

【出願人】(591024111)株式会社ハイニックスセミコンダクター (1,189)

【氏名又は名称原語表記】HYNIX SEMICONDUCTOR INC.

【住所又は居所原語表記】San 136−1,Ami−Ri,Bubal−Eup,Ichon−Shi,Kyoungki−Do,Korea

【Fターム(参考)】

【公開日】平成22年5月20日(2010.5.20)

【国際特許分類】

【出願日】平成21年4月27日(2009.4.27)

【出願人】(591024111)株式会社ハイニックスセミコンダクター (1,189)

【氏名又は名称原語表記】HYNIX SEMICONDUCTOR INC.

【住所又は居所原語表記】San 136−1,Ami−Ri,Bubal−Eup,Ichon−Shi,Kyoungki−Do,Korea

【Fターム(参考)】

[ Back to top ]