デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路及びシリアライザに関する。

【背景技術】

【0002】

近年の通信システムでは、差動の高速シリアル通信は一般的なものとなっている。シリアル通信では、パラレルデータを高速な差動クロックで同期させてシリアル化する。

【0003】

ところで近年では、クロックの高速化及びデバイスの微細化によって、同一のチップ内部のトランジスタの性能のばらつきも無視できなくなっている。この同一チップ内のトランジスタの性能のばらつきによって、本来差動の関係であるはずのクロックもデューティやエッジ位置が異なることが問題視されている。動作の基準となるクロックのデューティのばらつきは、シリアルデータの決定論的なジッタとなるためである。

【0004】

決定論的なジッタを抑制する方法として、例えば特許文献1には、データパターンによって生じる出力回路の消費電流差を埋めることで消費電流を常に一定に保つ方法で、電源変動起因のジッタを減らすことが記載されている。

【0005】

また特許文献2には、差動信号間に生じた位相差を補正する方法として、位相の検出方法についてCPUで制御することが記載されている。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら特許文献1記載の発明では、クロックのデューティ及び位相ばらつきによるジッタを抑制することはできない。また特許文献2記載の発明では、デューティのばらつきについての補正がないため、デューティのばらつきが引き起こすジッタについては抑制ができない。

【0007】

本発明は、上記事情を鑑みてこれを解決すべくなされたものであり、クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明は、上記目的を達成すべく、以下の如き構成を採用した。

【0009】

本発明は、正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路において、前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、前記立ち下がり時間調整部から出力された前記負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有する。

【0010】

本発明は、正クロック信号と負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路と接続されており、前記正クロック出力信号及び負クロック出力信号に同期してパラレルデータをシリアルデータとするシリアライザであって、前記デューティ補正付位相調整回路は、前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、前記立ち下がり時間調整部から出力された負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有する。

【0011】

本発明は、正クロック信号及び負クロック信号に同期してパラレルデータをシリアルデータとするシリアライザであって、前記正クロック信号及び前記負クロック信号に同期して前記パラレルデータを前記シリアルデータとするシリアライズ手段と、前記シリアライズ手段により正クロック信号に同期した正シリアルデータと、前記負クロック信号に同期した負シリアルデータと、を入力とし、前記正シリアルデータと前記負シリアルデータのデューティ及び位相を調整して正シリアル出力データと負シリアル出力データとを出力するデューティ補正付位相調整回路と、を有し、前記デューティ補正付位相調整回路は、前記正シリアル出力データの平均電圧値を検出する平均電圧検出部と、参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、前記正シリアルデータが入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正シリアルデータのデューティを変化させるデューティ調整部と、前記正シリアル出力データの立ち上がり時間を検出する正の立ち上がり検出部と、前記正シリアル出力データの立ち下がり時間を検出する正の立ち下がり検出部と、前記負シリアル出力データの立ち上がり時間を検出する負の立ち上がり検出部と、前記負シリアル出力データの立ち下がり時間を検出する負の立ち下がり検出部と、前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、前記正の位相差信号に応じて前記負シリアルデータの立ち下がり時間を変化させる立ち下がり時間調整部と、前記立ち下がり時間調整部から出力された負シリアルデータの立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負シリアル出力データとする立ち上がり時間調整部と、を有する。

【発明の効果】

【0012】

本発明によれば、クロックのばらつきが引き起こすジッタを抑制することができる。

【図面の簡単な説明】

【0013】

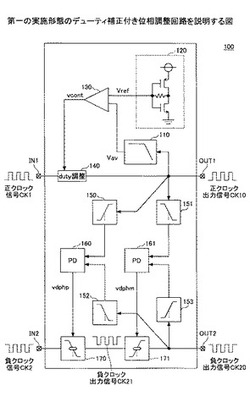

【図1】第一の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図2】第一の実施形態のデューティ補正付き位相調整回路の機能構成を説明する図である。

【図3】第一の実施形態のデューティ調整機能部の動作を説明するフローチャートである。

【図4】デューティ調整部による調整を説明する図である。

【図5】第一の実施形態の立ち下がり時間機能部を説明するフローチャートである。

【図6】第一の実施形態の立ち上がり時間機能部を説明するフローチャートである。

【図7】第一の実施形態において立ち下がり時間調整部と立ち上がり時間調整部の配置が逆であるデューティ補正付き位相調整回路を示す図である。

【図8】第二の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図9】第二の実施形態における遅延回路の役割を説明する図である。

【図10】第三の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図11】第四の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図12】第四の実施形態のデューティ調整機能部の動作を説明するフローチャートである。

【図13】第四の実施形態の立ち下がり時間調整機能部を説明するフローチャートである。

【図14】第四の実施形態の立ち上がり時間調整機能部を説明するフローチャートである。

【図15】第五の実施形態のシリアライザを説明する図である。

【図16】正クロック出力信号と負クロック出力信号に同期してパラレルデータをシリアライズする様子を示す図である。

【図17】デューティにばらつきのあるクロックでシリアライズした場合を説明する図である。

【図18】クロックのエッジにばらつきがあるクロックでシリアライズした場合を説明する図である。

【図19】第六の実施形態のシリアライザを説明する図である。

【図20】第六の実施形態のシリアライザ及びデューティ補正付き位相調整回路の動作を説明するフローチャートである。

【図21】第七の実施形態の通信システムを示す図である。

【発明を実施するための形態】

【0014】

本発明は、差動クロックまたは差動のシリアルデータのデューティを最適に制御しながら、差動の位相差を調整する。

(第一の実施形態)

以下に図面を参照して本発明の第一の実施形態について説明する。図1は、第一の実施形態のデューティ補正付き位相調整回路を説明する図である。

【0015】

本実施形態のデューティ補正付き位相調整回路100は、正クロック信号CK1が入力される入力端子IN1と、負クロック信号CK2が入力される入力端子IN2とを有する。またデューティ補正付き位相調整回路100は、正クロック出力信号CK10が出力される出力端子OUT1と、負クロック出力信号CK20が出力される出力端子OUT2と、を有する。

【0016】

本実施形態において、正クロック信号CK1と負クロック信号CK2は、ハイレベル(以下、Hレベル)とローレベル(以下、Lレベル)の2値の電圧レベルが一定の周期で遷移する信号である。本実施形態のデューティ補正付き位相調整回路100は、正クロック信号CK1と負クロック信号CK2のデューティと位相を調整する機能を有し、位相とデューティが調整された正クロック出力信号CK10と負クロック出力信号CK20とを出力する。

【0017】

本実施形態のデューティ補正付き位相調整回路100は、平均電圧検出部110、参照電圧生成部120、比較器130、デューティ調整部140、正の立ち上がり検出部150、正の立ち下がり検出部151、負の立ち下がり検出部152、負の立ち上がり検出部153、正の位相検出部160、負の位相検出部161、立ち下がり時間調整部170、立ち上がり時間調整部171を有する。

【0018】

平均電圧検出部110は、正クロック信号CK1の平均値電圧Vavを検出する。比較器130は、参照電圧生成部120により生成された参照電圧Vrefと、平均値電圧Vavとを比較し、比較結果に応じた制御信号Vcntを出力する。デューティ調整部140は、制御信号Vcntによって正クロック出力信号CK10のデューティを調整する。

【0019】

正の立ち上がり検出部150は、正クロック出力信号CK10がLレベルからHレベルに遷移する時間を正の立ち上がり時間として検出し、正の立ち下がり検出部151は、正クロック出力信号CK10がHレベルからLレベルに遷移する時間を正の立ち下がり時間として検出する。

【0020】

負の立ち下がり検出部152は、負クロック出力信号CK20がHレベルからLレベルに遷移する時間を負の立ち下がり時間として検出し、負の立ち上がり検出部153は負クロック出力信号CK20がLレベルからHレベルに遷移する時間を負の立ち上がり時間として検出する。

【0021】

正の位相検出部160は、正の立ち上り検出部150で検出された正の立ち上り時間と、負の立ち下り検出部152で検出された負の立ち下り時間の差に応じた正の位相差信号vdphpを出力する。負の位相検出部161は、正の立ち下り検出部151で検出された正の立ち下り時間と、負の立ち上り検出部153で検出された負の立ち上り時間を比較し、比較結果に応じた負の位相差信号vdphmを出力する。

【0022】

立ち下がり時間調整部170は、負のクロック信号CK2が入力され、正の位相差信号vdphpに応じて負クロック出力信号CK20のHレベルからLレベルに遷移する時間を変化させて出力する。

【0023】

立ち上がり時間調整部171は、負クロック信号CK2が入力され負の位相差信号vdphmに応じて負クロック出力信号CK20がLレベルからHレベルに遷移する時間を変化させて出力する。

【0024】

以下に図2を参照して本実施形態のデューティ補正付き位相調整回路100の機能構成を説明する。図2は、第一の実施形態のデューティ補正付き位相調整回路の機能構成を説明する図である。

【0025】

本実施形態のデューティ補正付き位相調整回路100は、デューティ調整機能部200と、立ち下がり時間調整機能部300と、立ち上がり時間調整機能部400と、を有する。

【0026】

デューティ調整機能部200は、正クロック信号CK1のクロックデューティを適切な値にする。本実施形態のデューティ調整機能部200は、平均電圧検出部110、参照電圧生成部120、比較器130、デューティ調整部140で構成されている。

【0027】

立ち下がり時間調整機能部300は、負クロック出力信号CK20の立ち下り時間を正クロック出力信号CK10の立ち上り時間と等しくする制御を行う。本実施形態の立ち下がり時間調整機能部300は、正の立ち上がり検出部150、負の立ち下がり検出部152、正の位相検出部160、立ち下がり時間調整部170で構成されている。

【0028】

立ち上がり時間調整機能部400は、負クロック出力信号CK20の立ち上り時間を正クロック出力信号CK10の立ち下り時間と等しくする制御を行う。本実施形態の立ち上がり時間調整機能部400は、正の立ち下がり検出部151、負の立ち上がり検出部153、負の位相検出部161、立ち上がり時間調整部171で構成されている。

【0029】

以下に図3を参照して本実施形態のデューティ調整機能部200の動作について説明する。図3は、第一の実施形態のデューティ調整機能部の動作を説明するフローチャートである。尚図3では、正クロック出力信号CK10のデューティが50%ではないと仮定した場合を示している。

【0030】

本実施形態のデューティ調整機能部200において、正クロック出力信号CK10が平均電圧検出部110に取り込まれ、平均電圧Vavが検出される(ステップS301)。尚本実施形態の平均電圧検出部110は、正クロック出力信号CK10に対して十分低いカットオフ周波数を持つローパスフィルタ回路等により実現されても良い。

【0031】

続いてデューティ調整機能部200は、比較器130で参照電圧Vrefと平均電圧Vavとを比較し(ステップS302)、参照電圧Vrefと平均電圧Vavとが等しいか否かを判断する(ステップS303)。

【0032】

ステップS303において、参照電圧Vrefと平均電圧Vavとが等しい場合、デューティ調整機能部200は処理を終了する。

【0033】

ステップS303において参照電圧Vrefと平均電圧Vavとが等しくなく、参照電圧Vref>平均電圧Vavであった場合(ステップS304)、デューティ調整機能部200はデューティ調整部140により正クロック出力信号CK10のディーティを上げ(ステップS305)、ステップS302へ戻る。

【0034】

ステップS304において参照電圧Vref>平均電圧Vavでない場合、デューティ調整部140により正クロック出力信号CK10のディーティを下げ(ステップS306)、ステップS302へ戻る。

【0035】

尚本実施形態のデューティ調整部140は、例えば、電流値を変更できるインバータを連ねる等して、電流値を調整することによって実現されても良く、必ずしもCPU(Central Processing Unit)等を用いたデジタル制御が必要となるわけではない。また本実施形態の参照電圧Vrefは、正クロック出力信号CK10が入力されるドライバの閾値に等しくなるような値に設定されることが好ましい。図1に示す本実施形態では正クロック出力信号CK10が入力されるドライバはインバータとして示される。

【0036】

以下に図4を参照して、正クロック出力信号CK10のデューティが50より大きい場合におけるデューティ調整部140の調整方法について説明する。図4は、デューティ調整部による調整を説明する図である。図4(A)は、デューティが50%より大きい場合に平均電圧検出部110により検出される平均電圧を説明する図である。図4(B)

は、デューティ調整部140によるデューティの調整を示す図である。図4(C)はデューティ調整後の正クロック出力信号CK10を説明する図である。

【0037】

図4(A)に示すように、正クロック出力信号CK10のデューティが50%より大きい場合、平均電圧Vavは、(Hレベル電圧−Lレベル電圧)/2よりも高い値となる。本実施形態では、参照電圧Vrefを(Hレベル電圧−Lレベル電圧)/2としているため、この場合は平均電圧Vavと参照電圧Vrefとを比較すると、参照電圧Vref<平均電圧Vavとなる。

【0038】

以下に図4(B)を参照して本実施形態のデューティ調整部140の構成を説明する。本実施形態のデューティ調整部140は、入力端子IN1、出力端子OUT1、PチャネルトランジスタM1、M2、nチャネルトランジスタM3、M4、電流源141、142を有する。

【0039】

トランジスタM1のソースは電流源141を介して電源ラインと接続されており、トランジスタM1のドレインがトランジスタM3のドレインと接続されている。トランジスタM3のソースは接地されている。トランジスタM1のゲートとトランジスタM3のゲートは入力端子IN1と接続されており、正クロック信号CK1が入力される。トランジスタM1のドレインとトランジスタM3のドレインとの接続点は、トランジスタM2のゲートとトランジスタM4のゲートと接続されている。

【0040】

トランジスタM2のソースは電源ラインと接続されており、トランジスタM2のドレインがトランジスタM4のドレインと接続されている。トランジスタM4のソースは電流源142を介して接地されている。トランジスタM1のドレインとトランジスタM3のドレインとの接続点は、出力端子OUT1と接続されており、正クロック出力信号CK10を出力する。

【0041】

本実施形態のデューティ調整部140では、平均電圧Vavが参照電圧より高い場合、正クロック出力信号CK10のデューティを下げる。具体的にはデューティ調整部140は、電流源141、142を制御してトランジスタM1とトランジスタM3に流れる電流値を制御前より大きくし、トランジスタM2とトランジスタM4に流れる電流値を制御前より小さくする。尚トランジスタM1〜M4に流れる電流値は比較器130から出力される制御信号Vcntによって制御される。本実施形態のデューティ調整部140では、例えば電流値の制御を指示する制御信号Vcntを受ける度に、所定の値ずつ電流値を変化させ、平均電圧Vavと参照電圧Vrefとが等しくなるようにしても良い。

【0042】

本実施形態ではこの制御により、図4(C)に示すように、正クロック出力信号CK10の立ち上がりが遅くなり、立ち下がりが早くなり、デューティが50%になるように改善される。

【0043】

また図4では、デューティが50%より大きいの場合を説明したが、デューティが50%より小さい場合も同様の制御を行うことができる。デューティが50%より小さい場合、平均電圧Vavは参照電圧Vrefより小さい値となる。よってデューティ調整部140は、正クロック出力信号CK10の立ち上がりを早くし、立ち下がりを遅くするようにすれば良い。

【0044】

次に、図5、図6を参照して本実施形態の立ち下がり時間調整機能部300と、立ち上がり時間調整機能部400の動作について説明する。

【0045】

図5は、第一の実施形態の立ち下がり時間機能部を説明するフローチャートである。本実施形態の立ち下がり時間調整機能部300において、正の立ち上がり検出部150は正クロック出力信号CK10の立ち上がり時間を検出し、負の立ち下がり検出部152は負クロック出力信号CK20の立ち下がり時間を検出する(ステップS501)。続いて正の位相検出部160は、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間との差分値を正の位相差信号vdphpとして立ち下がり時間調整部170へ出力する(ステップS502)。

【0046】

立ち下がり時間調整部170は、位相差信号vdphpに基づき、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しいか否かを判断する(ステップS503)。ステップS503で両者が等しい場合、立ち下がり時間調整部170は処理を終了する。

【0047】

ステップS503において両者が等しくない場合、立ち下がり時間調整部170は、負クロック出力信号CK20がHレベルからLレベルへ遷移する時間、すなわち負クロック出力信号CK20の立ち下がり時間を変化させる(ステップS504)。本実施形態では、立ち下がり時間調整部170は、位相差信号vdphpに基づき正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しくなるまで、負クロック出力信号CK20の立ち下がり時間を調整する。そして立ち下がり時間調整部170は、ステップS501へ戻る。

【0048】

図6は、第一の実施形態の立ち上がり時間機能部を説明するフローチャートである。本実施形態の立ち上がり時間調整機能部400において、正の立ち下がり検出部151は正クロック出力信号CK10の立ち下がり時間を検出し、負の立ち上がり検出部153は負クロック出力信号CK20の立ち上がり時間を検出する(ステップS601)。続いて負の位相検出部161は、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間との差分値を負の位相差信号vdphmとして立ち上がり時間調整部171へ出力する(ステップS602)。

【0049】

立ち上がり時間調整部171は、位相差信号vdphmに基づき、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間とが等しいか否かを判断する(ステップS603)。ステップS603で両者が等しい場合、立ち上がり時間調整部171は処理を終了する。

【0050】

ステップS603において両者が等しくない場合、立ち上がり時間調整部171は、負クロック出力信号CK20がLレベルからHレベルへ遷移する時間、すなわち負クロック出力信号CK20の立ち上がり時間を変化させる(ステップS604)。本実施形態では、立ち上がり時間調整部171は、位相差信号vdphmに基づき正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間とが等しくなるまで、負クロック出力信号CK20の立ち上がり時間を調整する。そして立ち上がり時間調整部171は、ステップS601へ戻る。

【0051】

以上に説明したように、本実施形態では、デューティ調整機能部200により、正クロック出力信号CK10のデューティが50%となるように制御される。また本実施形態では、立ち下がり時間調整機能部300により、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しくなるように調整する。さらに本実施形態では、立ち上がり時間調整機能部400により、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間とが等しくなるように調整する。すなわち本実施形態では、正クロック出力信号CK10と負クロック出力信号CK20の位相が等しくなるように調整する。

【0052】

したがって本実施形態では、差動クロックである正クロック出力信号CK10と負クロック出力信号CK20のデューティを最適に制御しながら、差動クロックの位相差を調整することができ、クロックのばらつきが引き起こすジッタを抑制することができる。

【0053】

尚本実施形態では、立ち下がり時間調整部170を入力端子IN2側に配置し、立ち上がり時間調整部171を出力端子OUT2側に配置したが、両者の配置はこれに限定されない。例えば立ち下がり時間調整部170と立ち上がり時間調整部171とは配置が逆であっても良い。

【0054】

図7は、第一の実施形態において立ち下がり時間調整部と立ち上がり時間調整部の配置が逆であるデューティ補正付き位相調整回路を示す図である。

【0055】

図7に示すデューティ補正付き位相調整回路100Aでは、立ち上がり時間調整部171が入力端子IN2側に配置されており、正の位相検出部160から出力される位相差信号が入力される。また立ち下がり時間調整部170が出力端子OUT2側に配置されており、負の位相検出部161から出力される位相差信号が入力される。

【0056】

デューティ補正付き位相調整回路100Aは、上記構成でもデューティ補正付き位相調整回路100と同様の効果を奏することができる。

【0057】

(第二の実施形態)

以下に図面を参照して本発明の第二の実施形態について説明する。本発明の第二の実施形態は、遅延回路が設けられた点が第一の実施形態と相違する。以下の本発明の第二の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0058】

図8は、第二の実施形態のデューティ補正付き位相調整回路を説明する図である。本実施形態のデューティ補正付き位相調整回路100Bは、デューティ調整部140の出力側に遅延回路180を有する。デューティ調整部140から出力された正クロック出力信号CK10は、遅延回路180を介して出力端子OUT1から出力される。

【0059】

以下に図9を参照して遅延回路180を設けた場合と遅延回路180を設けていない場合との違いを説明する。図9は、第二の実施形態における遅延回路の役割を説明する図である。

【0060】

遅延回路180を有していない場合、入力端子IN1から正クロック信号CK1がデューティ調整部140に入力され、正クロック出力信号CK10として出力されるまでに、デューティ調整部140において時間差t1[s]が生じる。

【0061】

これに対し、入力端子IN2から負クロック信号CK2が立ち下がり時間調整部170に入力され、負クロック出力信号CK21として出力されるまでに時間差t2[s]が生じる。さらに負クロック出力信号CK21が立ち上がり時間調整部171に入力され、負クロック出力信号CK20として出力されるまでに時間差t3[s]が生じる。

【0062】

すなわち負クロック出力信号CK2は、出力端子OUT2から出力されるまでにt2+t3[s]の時間差が生じる。

【0063】

本実施形態の遅延回路180は、正クロック出力信号CK10を出力する際に生じる時間t1[s]と、負クロック出力信号CK20を出力する際に生じる時間差t2+t3[s]とが、デューティ調整機能部200、立ち下がり時間調整機能部300、立ち上がり時間調整機能部400の制御により調整できない場合を考慮したものである。

【0064】

本実施形態では、遅延回路180により、デューティ調整部140から出力された正クロック出力信号CK10をt4[s]遅延させる。本実施形態の遅延回路180では、正クロック信号CK1がデューティ調整部140に入力されてから、正クロック出力信号CK10が出力端子OUT1から出力されるまでの時間差t1+t4[s]が、時間差t2+t3[s]と同じになるように設定することが好ましい。

【0065】

このように遅延回路180を設けることで、クロックのばらつきが引き起こすジッタを抑制することができる。

【0066】

(第三の実施形態)

以下に図面を参照して本発明の第三の実施形態について説明する。本発明の第三の実施形態は、分周器が設けられた点が第一の実施形態と相違する。以下の本発明の第三の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0067】

図10は、第三の実施形態のデューティ補正付き位相調整回路を説明する図である。

【0068】

本実施形態のデューティ補正付き位相調整回路100Cはデューティ調整部140から出力された正クロック出力信号CK10を分周する分周器190、191と、立ち上がり時間調整部171から出力された負クロック出力信号CK20を分周する分周器192、193を有する。

【0069】

本実施形態の分周器190〜193は、何れも同様の構成を有するものである。本実施形態では、分周器190で分周された正クロック出力信号CK10は、正の立ち上がり検出部150へ供給される。また分周器191で分周された正クロック出力信号CK10は、正の立ち下がり検出部151へ供給される。

【0070】

また本実施形態では、分周器192で分周された負クロック出力信号CK20が負の立ち下がり検出部152に供給され、分周器193で分周された負クロック出力信号CK20が負の立ち上がり検出部153に供給される。

【0071】

したがって本実施形態では、正の位相検出部160は、分周された正クロック出力信号CK10の立ち上がり時間と立ち下がり時間とを比較することになる。また負の位相検出部161は、分周された負クロック出力信号CK10の立ち下がり時間と立ち上がり時間とを比較することになる。よって本実施形態では、正の位相検出部160と負の位相検出部161とにおいて、比較時間が長くなる。このため本実施形態では、正の位相検出部160と負の位相検出部161の動作速度は分周しない場合と比べて遅くても良くなる。

【0072】

(第四の実施形態)

以下に図面を参照して本発明の第四の実施形態について説明する。本発明の第四の実施形態は、位相検出部の出力側にDAC(Digital to Analog Converter)が設けられた点が第一の実施形態と相違する。以下の本発明の第四の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0073】

図11は、第四の実施形態のデューティ補正付き位相調整回路を説明する図である。本実施形態のデューティ補正付き位相調整回路100Dは、キャリブレーション信号が入力される端子INCと、DAC195、196、197を有する。

【0074】

DAC195には比較器130の出力が供給される。DAC195の出力は、デューティ調整部140に供給される。DAC196には正の位相検出部160の出力が供給される。DAC196の出力は、立ち下がり時間調整部170に供給される。DAC197には負の位相検出部161の出力が供給される。DAC197の出力は、立ち上がり時間調整部171に供給される。

【0075】

DAC195〜197は、キャリブレーション信号に応じて、出力する値を保持している。キャリブレーション信号とは、正クロック出力信号CK10及び負クロック出力信号CK20に同期したシリアルデータのレベルを合わせるために入力される信号である。キャリブレーション信号の周波数は、予め設定された複数種類の周波数の中から選択された周波数である。

【0076】

以下に図12ないし図14を参照して本実施形態のデューティ調整機能部の動作について説明する。図12は、第四の実施形態のデューティ調整機能部の動作を説明するフローチャートである。

【0077】

図12において、キャリブレーション信号がオンになると、デューティ調整機能部は動作を開始する。

【0078】

図12のステップS1201の処理とステップS1202の処理は、図3のステップS301の処理とステップS302の処理とそれぞれ同様であるから説明を省略する。

【0079】

続いて本実施形態では、参照電圧Vrefと平均電圧Vavとが等しいか否か又は参照電圧Vrefと平均電圧Vavの大小関係が逆転したか否かを判断する(ステップS1203)。

【0080】

ステップS1203において、参照電圧Vrefと平均電圧Vavとが等しいか、又は参照電圧Vrefと平均電圧Vavの大小関係が逆転した場合、本実施形態におけるデューティ調整の処理は終了し、キャリブレーション信号がオフされる。

【0081】

ステップS1203において、参照電圧Vrefと平均電圧Vavとが等しくないか、又は参照電圧Vrefと平均電圧Vavの大小関係が逆転していない場合、参照電圧Vref>平均電圧Vavであるか否かを判断する(ステップS1204)。

【0082】

ステップS1204において参照電圧Vref>平均電圧Vavである場合、DAC195は、正クロック出力信号CK10のデューティを上げる方に1LSB(Least Significant Bit)動かし(ステップS1205)、ステップS1202へ戻る。

【0083】

ステップS1204において参照電圧Vref>平均電圧Vavでない場合、DAC195は、正クロック出力信号CK10のデューティを下げる方に1LSB(動かし(ステップS1206)、ステップS1202へ戻る。尚DAC195は比較器130の出力信号に応じて動作する。

【0084】

次に図13、図14を参照して本実施形態における立ち下がり時間調整機能部及び立ち上がり時間調整機能部の動作を説明する。

【0085】

図13は、第四の実施形態の立ち下がり時間調整機能部を説明するフローチャートである。

【0086】

本実施形態において、キャリブレーション信号がオンになると、正の立ち上がり検出部150は正クロック出力信号CK10の立ち上がり時間を検出し、負の立ち下がり検出部152は負クロック出力信号CK20の立ち下がり時間を検出する(ステップS1301)。

【0087】

続いて正の位相検出部160は、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間との差分値を正の位相差信号vdphpとして出力し、DAC196の出力を正の位相差を少なくする方に1LSB動かす(ステップS1302)。

【0088】

立ち下がり時間調整部170は、DAC196から出力される位相差信号vdphpに基づき、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しいか又は両者の大小関係が逆転したか否かを判断する(ステップS1303)。ステップS1303で両者が等しい又は大小関係が逆転した場合、キャリブレーション信号がオフされ、立ち下がり時間調整部170は処理を終了する。ステップS1303で両者が等しくない又は大小関係が逆転しない場合、ステップS1301へ戻る。

【0089】

図14は、第四の実施形態の立ち上がり時間調整機能部を説明するフローチャートである。

【0090】

本実施形態において、キャリブレーション信号がオンになると、正の立ち下がり検出部151は正クロック出力信号CK10の立ち下がり時間を検出し、負の立ち上がり検出部153は負クロック出力信号CK20の立ち上がり時間を検出する(ステップS1401)。

【0091】

続いて負の位相検出部161は、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間との差分値を負の位相差信号vdphmとして出力し、DAC197の出力を正の位相差を少なくする方に1LSB動かす(ステップS1402)。

【0092】

立ち上がり時間調整部171は、DAC197から出力される位相差信号vdphmに基づき、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しいか又は両者の大小関係が逆転したか否かを判断する(ステップS1403)。ステップS1403で両者が等しい又は大小関係が逆転した場合、キャリブレーション信号はオフされ、立ち上がり時間調整部171は処理を終了する。ステップS1403で両者が等しくない又は大小関係が逆転しない場合、ステップS1401へ戻る。

【0093】

本実施形態では、以上の制御により、第一の実施形態と同等の効果を得ることができる。

【0094】

(第五の実施形態)

以下に図面を参照して本発明の第五の実施形態について説明する。本発明の第五の実施形態は、4ビットのパラレルデータをシリアルデータに変換するシリアライザに第一ないし第四の実施形態のデューティ補正付き位相調整回路の何れかを適用した形態である。以下の本発明の第五の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0095】

図15は、第五の実施形態のシリアライザを説明する図である。図15では、第一の実施形態のデューティ補正付き位相調整回路100を適用した例を示している。

【0096】

図15に示すシリアライザ500は、4ビットのパラレルデータd[0;3]を差動のシリアルデータD1及びD2に変換する。シリアライザ500は、デューティ補正付き位相調整回路100から出力される正クロック出力信号CK10及び負クロック出力信号CK20に同期してパラレルデータd[0;3]をシリアルデータD1,D2に変換する。以下に図16を参照してデューティ補正付位相調整回路100の効果について説明する。

【0097】

図16は、正クロック出力信号と負クロック出力信号に同期してパラレルデータを

シリアライズする様子を示す図である。図16において、点線はパラレルデータが正クロック出力信号CK10、負クロック出力信号CK20のどちらかのエッジに同期していることを示す。図16のシリアルデータ中に記載されている数字は、パラレルデータd[0;3]のうちどのデータが出力されているかを示している。

【0098】

デューティ補正付位相調整回路100では、正クロック出力信号CK10と負クロック出力信号CK20のエッジが等しく、デューティが50%となるように制御するため、図16ではクロックのばらつきに起因のジッタは存在しないことがわかる。

【0099】

以下に図17、図18を参照して本実施形態による効果について説明する。図17は、デューティにばらつきのあるクロックでシリアライズした場合を説明する図である。

【0100】

図17の例では、パラレルデータd[0;3]を同期させる正クロック信号11と負クロック信号CK21のエッジが揃っているが、デューティが揃っていない。

【0101】

正クロック信号CK11と負クロック信号CK21のデューティが50%でない場合、両クロック信号のデューティの50%からの乖離がそのまま決定論的ジッタ17となる。決定論的ジッタとは、データやクロックに依存して受信信号の波形タイミングが変化するジッタである。

【0102】

図18は、クロックのエッジにばらつきがあるクロックでシリアライズした場合を説明する図である。

【0103】

図18の例では、正クロック信号CK12と負クロック信号CK22のデューティは揃っているが、エッジが揃っていない。

【0104】

この場合、正クロック信号CK12と負クロック信号CK22の位相差がそのまま決定論的ジッタ18となる。

【0105】

本実施形態では、正クロック出力信号CK10と負クロック出力信号CK20は、デューティを50%とし、両クロック出力信号のエッジを揃えるように調整されているため、図17や図18に示すような決定論的ジッタの発生を抑制できる。

【0106】

(第六の実施形態)

以下に図面を参照して本発明の第六の実施形態について説明する。本発明の第六の実施形態は、4ビットのパラレルデータをシリアルデータに変換するシリアライザに第四の実施形態のデューティ補正付き位相調整回路を適用した形態である。以下の本発明の第六の実施形態の説明では、第四の実施形態と同様の機能構成を有するものには第四の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0107】

図19は、第六の実施形態のシリアライザを説明する図である。図19では、第四の実施形態のデューティ補正付き位相調整回路100Dを適用した例を示している。

【0108】

本実施形態のシリアライザ600は、シリアライザ610とデューティ補正付き位相調整回路100Dとを含む構成とした。本実施形態のシリアライザ600において、シリアライザ610は、正クロック信号CK1と負クロック信号CK2に同期してパラレルデータd[0;3]をシリアライズし、正シリアルデータD10と負シリアルデータD20として出力する。また本実施形態のシリアライザ600において、デューティ補正付き位相調整回路100Dは、正シリアルデータD10と負シリアルデータD20に対して、デューティ及び立ち上がり時間と立ち下がり時間の制御を行う。そしてデューティ補正付き位相調整回路100Dは、デューティを50%でありエッジが揃った正シリアル出力データD11と負シリアル出力データD21を、シリアライザ600の出力とする。

【0109】

以下に図20を参照して本実施形態のシリアライザ600及びデューティ補正付き位相調整回路100Dの動作を説明する。図20は、第六の実施形態のシリアライザ及びデューティ補正付き位相調整回路の動作を説明するフローチャートである。

【0110】

パラレルデータのシリアライズがスタートすると、デューティ補正付き位相調整回路100Dに入力されるキャリブレーション信号がオンされてシリアルデータのキャリブレーションが開始される。このときパラレルデータd[3;0]は固定の電圧を入力してシリアルデータが0101と出力されるようにする(ステップS2001)尚キャリブレーション信号は、デューティ補正付き位相調整回路100Dに対して外部の回路から供給されるものとした。

【0111】

ステップS2001に続いてデューティ補正付き位相調整回路100Dは、シリアライザ610から出力された正シリアルデータD10と負シリアルデータD20のデューティの調整と、立ち下がり時間調整、立ち上がり時間調整を行う(ステップS2002)。ステップS2002におけるデューティの調整は、図12で説明した通りである。ステップS2002における立ち下がり時間調整は、図13で説明した通りである。ステップS2002における立ち上がり時間調整は、図14で説明した通りである。

【0112】

続いてデューティ補正付き位相調整回路100Dは、上記の各調整が終了したか否かを判断する(ステップS2003)。ステップS2003において各調整が終了していない場合、ステップS2001へ戻る。

【0113】

ステップS2003において各調整が終了していた場合、キャリブレーション信号がオフされ、シリアライザへのパラレルデータの入力が開始されてリアライザの通常動作を開始する(ステップS2004)。

【0114】

このように本実施形態では、キャリブレーション時のみ正シリアルデータD10と負シリアルデータD20の調整を実施し、通常動作のときは制御を行わないので、データパターンによってデューティを調整することは無くなる。また本実施形態では、シリアルデータが所定のパターンとなるとき、デューティが50%に保たれ、正シリアルデータD10と負シリアルデータD20の立ち上がり時間と立ち下がり時間とが揃うように制御される。所定のパターンとは、例えばシリアルデータのパターンが1010又は1010等である。

【0115】

本実施形態では、このようにデューティ補正付き位相調整回路100Dをシリアルデータの送信に適用することで、低ジッタのデータ送信が可能となる。

【0116】

(第七の実施形態)

以下に図面を参照して本発明の第七の実施形態について説明する。本発明の第七の実施形態は、第六の実施形態のシリアライザ600を適用した通信システムの形態である。以下の本発明の第七の実施形態の説明では、第六の実施形態と同様の機能構成を有するものには第六の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0117】

図21は、第七の実施形態の通信システムを示す図である。

【0118】

本実施形態の通信システム2100は、ドライバ回路620と、受信回路700と、伝送路800から構成される。

【0119】

本実施形態では、ドライバ回路620に、第六の実施形態のシリアライザ600を適用することで、低ジッタのデータ送信が可能となるため、通信システム2100を低ジッタとすることができる。

【0120】

以上、各実施形態に基づき本発明の説明を行ってきたが、上記実施形態に示した要件に本発明が限定されるものではない。これらの点に関しては、本発明の主旨をそこなわない範囲で変更することができ、その応用形態に応じて適切に定めることができる。

【符号の説明】

【0121】

100、100A〜100D デューティ補正付き位相調整回路

110 平均電圧検出部

120 参照電圧制生成部

130 比較器

140 デューティ調整部

150 正の立ち上がり検出部

151 負の立ち下がり検出部

152 正の立ち下がり検出部

153 負の立ち上がり検出部

160 正の位相検出部

161 負の位相検出部

170 立ち下がり時間調整部

171 立ち上がり時間調整部

【先行技術文献】

【特許文献】

【0122】

【特許文献1】特開2011−010066号公報

【特許文献2】特開2004−208004号公報

【技術分野】

【0001】

本発明は、正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路及びシリアライザに関する。

【背景技術】

【0002】

近年の通信システムでは、差動の高速シリアル通信は一般的なものとなっている。シリアル通信では、パラレルデータを高速な差動クロックで同期させてシリアル化する。

【0003】

ところで近年では、クロックの高速化及びデバイスの微細化によって、同一のチップ内部のトランジスタの性能のばらつきも無視できなくなっている。この同一チップ内のトランジスタの性能のばらつきによって、本来差動の関係であるはずのクロックもデューティやエッジ位置が異なることが問題視されている。動作の基準となるクロックのデューティのばらつきは、シリアルデータの決定論的なジッタとなるためである。

【0004】

決定論的なジッタを抑制する方法として、例えば特許文献1には、データパターンによって生じる出力回路の消費電流差を埋めることで消費電流を常に一定に保つ方法で、電源変動起因のジッタを減らすことが記載されている。

【0005】

また特許文献2には、差動信号間に生じた位相差を補正する方法として、位相の検出方法についてCPUで制御することが記載されている。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら特許文献1記載の発明では、クロックのデューティ及び位相ばらつきによるジッタを抑制することはできない。また特許文献2記載の発明では、デューティのばらつきについての補正がないため、デューティのばらつきが引き起こすジッタについては抑制ができない。

【0007】

本発明は、上記事情を鑑みてこれを解決すべくなされたものであり、クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明は、上記目的を達成すべく、以下の如き構成を採用した。

【0009】

本発明は、正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路において、前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、前記立ち下がり時間調整部から出力された前記負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有する。

【0010】

本発明は、正クロック信号と負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路と接続されており、前記正クロック出力信号及び負クロック出力信号に同期してパラレルデータをシリアルデータとするシリアライザであって、前記デューティ補正付位相調整回路は、前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、前記立ち下がり時間調整部から出力された負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有する。

【0011】

本発明は、正クロック信号及び負クロック信号に同期してパラレルデータをシリアルデータとするシリアライザであって、前記正クロック信号及び前記負クロック信号に同期して前記パラレルデータを前記シリアルデータとするシリアライズ手段と、前記シリアライズ手段により正クロック信号に同期した正シリアルデータと、前記負クロック信号に同期した負シリアルデータと、を入力とし、前記正シリアルデータと前記負シリアルデータのデューティ及び位相を調整して正シリアル出力データと負シリアル出力データとを出力するデューティ補正付位相調整回路と、を有し、前記デューティ補正付位相調整回路は、前記正シリアル出力データの平均電圧値を検出する平均電圧検出部と、参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、前記正シリアルデータが入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正シリアルデータのデューティを変化させるデューティ調整部と、前記正シリアル出力データの立ち上がり時間を検出する正の立ち上がり検出部と、前記正シリアル出力データの立ち下がり時間を検出する正の立ち下がり検出部と、前記負シリアル出力データの立ち上がり時間を検出する負の立ち上がり検出部と、前記負シリアル出力データの立ち下がり時間を検出する負の立ち下がり検出部と、前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、前記正の位相差信号に応じて前記負シリアルデータの立ち下がり時間を変化させる立ち下がり時間調整部と、前記立ち下がり時間調整部から出力された負シリアルデータの立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負シリアル出力データとする立ち上がり時間調整部と、を有する。

【発明の効果】

【0012】

本発明によれば、クロックのばらつきが引き起こすジッタを抑制することができる。

【図面の簡単な説明】

【0013】

【図1】第一の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図2】第一の実施形態のデューティ補正付き位相調整回路の機能構成を説明する図である。

【図3】第一の実施形態のデューティ調整機能部の動作を説明するフローチャートである。

【図4】デューティ調整部による調整を説明する図である。

【図5】第一の実施形態の立ち下がり時間機能部を説明するフローチャートである。

【図6】第一の実施形態の立ち上がり時間機能部を説明するフローチャートである。

【図7】第一の実施形態において立ち下がり時間調整部と立ち上がり時間調整部の配置が逆であるデューティ補正付き位相調整回路を示す図である。

【図8】第二の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図9】第二の実施形態における遅延回路の役割を説明する図である。

【図10】第三の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図11】第四の実施形態のデューティ補正付き位相調整回路を説明する図である。

【図12】第四の実施形態のデューティ調整機能部の動作を説明するフローチャートである。

【図13】第四の実施形態の立ち下がり時間調整機能部を説明するフローチャートである。

【図14】第四の実施形態の立ち上がり時間調整機能部を説明するフローチャートである。

【図15】第五の実施形態のシリアライザを説明する図である。

【図16】正クロック出力信号と負クロック出力信号に同期してパラレルデータをシリアライズする様子を示す図である。

【図17】デューティにばらつきのあるクロックでシリアライズした場合を説明する図である。

【図18】クロックのエッジにばらつきがあるクロックでシリアライズした場合を説明する図である。

【図19】第六の実施形態のシリアライザを説明する図である。

【図20】第六の実施形態のシリアライザ及びデューティ補正付き位相調整回路の動作を説明するフローチャートである。

【図21】第七の実施形態の通信システムを示す図である。

【発明を実施するための形態】

【0014】

本発明は、差動クロックまたは差動のシリアルデータのデューティを最適に制御しながら、差動の位相差を調整する。

(第一の実施形態)

以下に図面を参照して本発明の第一の実施形態について説明する。図1は、第一の実施形態のデューティ補正付き位相調整回路を説明する図である。

【0015】

本実施形態のデューティ補正付き位相調整回路100は、正クロック信号CK1が入力される入力端子IN1と、負クロック信号CK2が入力される入力端子IN2とを有する。またデューティ補正付き位相調整回路100は、正クロック出力信号CK10が出力される出力端子OUT1と、負クロック出力信号CK20が出力される出力端子OUT2と、を有する。

【0016】

本実施形態において、正クロック信号CK1と負クロック信号CK2は、ハイレベル(以下、Hレベル)とローレベル(以下、Lレベル)の2値の電圧レベルが一定の周期で遷移する信号である。本実施形態のデューティ補正付き位相調整回路100は、正クロック信号CK1と負クロック信号CK2のデューティと位相を調整する機能を有し、位相とデューティが調整された正クロック出力信号CK10と負クロック出力信号CK20とを出力する。

【0017】

本実施形態のデューティ補正付き位相調整回路100は、平均電圧検出部110、参照電圧生成部120、比較器130、デューティ調整部140、正の立ち上がり検出部150、正の立ち下がり検出部151、負の立ち下がり検出部152、負の立ち上がり検出部153、正の位相検出部160、負の位相検出部161、立ち下がり時間調整部170、立ち上がり時間調整部171を有する。

【0018】

平均電圧検出部110は、正クロック信号CK1の平均値電圧Vavを検出する。比較器130は、参照電圧生成部120により生成された参照電圧Vrefと、平均値電圧Vavとを比較し、比較結果に応じた制御信号Vcntを出力する。デューティ調整部140は、制御信号Vcntによって正クロック出力信号CK10のデューティを調整する。

【0019】

正の立ち上がり検出部150は、正クロック出力信号CK10がLレベルからHレベルに遷移する時間を正の立ち上がり時間として検出し、正の立ち下がり検出部151は、正クロック出力信号CK10がHレベルからLレベルに遷移する時間を正の立ち下がり時間として検出する。

【0020】

負の立ち下がり検出部152は、負クロック出力信号CK20がHレベルからLレベルに遷移する時間を負の立ち下がり時間として検出し、負の立ち上がり検出部153は負クロック出力信号CK20がLレベルからHレベルに遷移する時間を負の立ち上がり時間として検出する。

【0021】

正の位相検出部160は、正の立ち上り検出部150で検出された正の立ち上り時間と、負の立ち下り検出部152で検出された負の立ち下り時間の差に応じた正の位相差信号vdphpを出力する。負の位相検出部161は、正の立ち下り検出部151で検出された正の立ち下り時間と、負の立ち上り検出部153で検出された負の立ち上り時間を比較し、比較結果に応じた負の位相差信号vdphmを出力する。

【0022】

立ち下がり時間調整部170は、負のクロック信号CK2が入力され、正の位相差信号vdphpに応じて負クロック出力信号CK20のHレベルからLレベルに遷移する時間を変化させて出力する。

【0023】

立ち上がり時間調整部171は、負クロック信号CK2が入力され負の位相差信号vdphmに応じて負クロック出力信号CK20がLレベルからHレベルに遷移する時間を変化させて出力する。

【0024】

以下に図2を参照して本実施形態のデューティ補正付き位相調整回路100の機能構成を説明する。図2は、第一の実施形態のデューティ補正付き位相調整回路の機能構成を説明する図である。

【0025】

本実施形態のデューティ補正付き位相調整回路100は、デューティ調整機能部200と、立ち下がり時間調整機能部300と、立ち上がり時間調整機能部400と、を有する。

【0026】

デューティ調整機能部200は、正クロック信号CK1のクロックデューティを適切な値にする。本実施形態のデューティ調整機能部200は、平均電圧検出部110、参照電圧生成部120、比較器130、デューティ調整部140で構成されている。

【0027】

立ち下がり時間調整機能部300は、負クロック出力信号CK20の立ち下り時間を正クロック出力信号CK10の立ち上り時間と等しくする制御を行う。本実施形態の立ち下がり時間調整機能部300は、正の立ち上がり検出部150、負の立ち下がり検出部152、正の位相検出部160、立ち下がり時間調整部170で構成されている。

【0028】

立ち上がり時間調整機能部400は、負クロック出力信号CK20の立ち上り時間を正クロック出力信号CK10の立ち下り時間と等しくする制御を行う。本実施形態の立ち上がり時間調整機能部400は、正の立ち下がり検出部151、負の立ち上がり検出部153、負の位相検出部161、立ち上がり時間調整部171で構成されている。

【0029】

以下に図3を参照して本実施形態のデューティ調整機能部200の動作について説明する。図3は、第一の実施形態のデューティ調整機能部の動作を説明するフローチャートである。尚図3では、正クロック出力信号CK10のデューティが50%ではないと仮定した場合を示している。

【0030】

本実施形態のデューティ調整機能部200において、正クロック出力信号CK10が平均電圧検出部110に取り込まれ、平均電圧Vavが検出される(ステップS301)。尚本実施形態の平均電圧検出部110は、正クロック出力信号CK10に対して十分低いカットオフ周波数を持つローパスフィルタ回路等により実現されても良い。

【0031】

続いてデューティ調整機能部200は、比較器130で参照電圧Vrefと平均電圧Vavとを比較し(ステップS302)、参照電圧Vrefと平均電圧Vavとが等しいか否かを判断する(ステップS303)。

【0032】

ステップS303において、参照電圧Vrefと平均電圧Vavとが等しい場合、デューティ調整機能部200は処理を終了する。

【0033】

ステップS303において参照電圧Vrefと平均電圧Vavとが等しくなく、参照電圧Vref>平均電圧Vavであった場合(ステップS304)、デューティ調整機能部200はデューティ調整部140により正クロック出力信号CK10のディーティを上げ(ステップS305)、ステップS302へ戻る。

【0034】

ステップS304において参照電圧Vref>平均電圧Vavでない場合、デューティ調整部140により正クロック出力信号CK10のディーティを下げ(ステップS306)、ステップS302へ戻る。

【0035】

尚本実施形態のデューティ調整部140は、例えば、電流値を変更できるインバータを連ねる等して、電流値を調整することによって実現されても良く、必ずしもCPU(Central Processing Unit)等を用いたデジタル制御が必要となるわけではない。また本実施形態の参照電圧Vrefは、正クロック出力信号CK10が入力されるドライバの閾値に等しくなるような値に設定されることが好ましい。図1に示す本実施形態では正クロック出力信号CK10が入力されるドライバはインバータとして示される。

【0036】

以下に図4を参照して、正クロック出力信号CK10のデューティが50より大きい場合におけるデューティ調整部140の調整方法について説明する。図4は、デューティ調整部による調整を説明する図である。図4(A)は、デューティが50%より大きい場合に平均電圧検出部110により検出される平均電圧を説明する図である。図4(B)

は、デューティ調整部140によるデューティの調整を示す図である。図4(C)はデューティ調整後の正クロック出力信号CK10を説明する図である。

【0037】

図4(A)に示すように、正クロック出力信号CK10のデューティが50%より大きい場合、平均電圧Vavは、(Hレベル電圧−Lレベル電圧)/2よりも高い値となる。本実施形態では、参照電圧Vrefを(Hレベル電圧−Lレベル電圧)/2としているため、この場合は平均電圧Vavと参照電圧Vrefとを比較すると、参照電圧Vref<平均電圧Vavとなる。

【0038】

以下に図4(B)を参照して本実施形態のデューティ調整部140の構成を説明する。本実施形態のデューティ調整部140は、入力端子IN1、出力端子OUT1、PチャネルトランジスタM1、M2、nチャネルトランジスタM3、M4、電流源141、142を有する。

【0039】

トランジスタM1のソースは電流源141を介して電源ラインと接続されており、トランジスタM1のドレインがトランジスタM3のドレインと接続されている。トランジスタM3のソースは接地されている。トランジスタM1のゲートとトランジスタM3のゲートは入力端子IN1と接続されており、正クロック信号CK1が入力される。トランジスタM1のドレインとトランジスタM3のドレインとの接続点は、トランジスタM2のゲートとトランジスタM4のゲートと接続されている。

【0040】

トランジスタM2のソースは電源ラインと接続されており、トランジスタM2のドレインがトランジスタM4のドレインと接続されている。トランジスタM4のソースは電流源142を介して接地されている。トランジスタM1のドレインとトランジスタM3のドレインとの接続点は、出力端子OUT1と接続されており、正クロック出力信号CK10を出力する。

【0041】

本実施形態のデューティ調整部140では、平均電圧Vavが参照電圧より高い場合、正クロック出力信号CK10のデューティを下げる。具体的にはデューティ調整部140は、電流源141、142を制御してトランジスタM1とトランジスタM3に流れる電流値を制御前より大きくし、トランジスタM2とトランジスタM4に流れる電流値を制御前より小さくする。尚トランジスタM1〜M4に流れる電流値は比較器130から出力される制御信号Vcntによって制御される。本実施形態のデューティ調整部140では、例えば電流値の制御を指示する制御信号Vcntを受ける度に、所定の値ずつ電流値を変化させ、平均電圧Vavと参照電圧Vrefとが等しくなるようにしても良い。

【0042】

本実施形態ではこの制御により、図4(C)に示すように、正クロック出力信号CK10の立ち上がりが遅くなり、立ち下がりが早くなり、デューティが50%になるように改善される。

【0043】

また図4では、デューティが50%より大きいの場合を説明したが、デューティが50%より小さい場合も同様の制御を行うことができる。デューティが50%より小さい場合、平均電圧Vavは参照電圧Vrefより小さい値となる。よってデューティ調整部140は、正クロック出力信号CK10の立ち上がりを早くし、立ち下がりを遅くするようにすれば良い。

【0044】

次に、図5、図6を参照して本実施形態の立ち下がり時間調整機能部300と、立ち上がり時間調整機能部400の動作について説明する。

【0045】

図5は、第一の実施形態の立ち下がり時間機能部を説明するフローチャートである。本実施形態の立ち下がり時間調整機能部300において、正の立ち上がり検出部150は正クロック出力信号CK10の立ち上がり時間を検出し、負の立ち下がり検出部152は負クロック出力信号CK20の立ち下がり時間を検出する(ステップS501)。続いて正の位相検出部160は、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間との差分値を正の位相差信号vdphpとして立ち下がり時間調整部170へ出力する(ステップS502)。

【0046】

立ち下がり時間調整部170は、位相差信号vdphpに基づき、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しいか否かを判断する(ステップS503)。ステップS503で両者が等しい場合、立ち下がり時間調整部170は処理を終了する。

【0047】

ステップS503において両者が等しくない場合、立ち下がり時間調整部170は、負クロック出力信号CK20がHレベルからLレベルへ遷移する時間、すなわち負クロック出力信号CK20の立ち下がり時間を変化させる(ステップS504)。本実施形態では、立ち下がり時間調整部170は、位相差信号vdphpに基づき正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しくなるまで、負クロック出力信号CK20の立ち下がり時間を調整する。そして立ち下がり時間調整部170は、ステップS501へ戻る。

【0048】

図6は、第一の実施形態の立ち上がり時間機能部を説明するフローチャートである。本実施形態の立ち上がり時間調整機能部400において、正の立ち下がり検出部151は正クロック出力信号CK10の立ち下がり時間を検出し、負の立ち上がり検出部153は負クロック出力信号CK20の立ち上がり時間を検出する(ステップS601)。続いて負の位相検出部161は、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間との差分値を負の位相差信号vdphmとして立ち上がり時間調整部171へ出力する(ステップS602)。

【0049】

立ち上がり時間調整部171は、位相差信号vdphmに基づき、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間とが等しいか否かを判断する(ステップS603)。ステップS603で両者が等しい場合、立ち上がり時間調整部171は処理を終了する。

【0050】

ステップS603において両者が等しくない場合、立ち上がり時間調整部171は、負クロック出力信号CK20がLレベルからHレベルへ遷移する時間、すなわち負クロック出力信号CK20の立ち上がり時間を変化させる(ステップS604)。本実施形態では、立ち上がり時間調整部171は、位相差信号vdphmに基づき正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間とが等しくなるまで、負クロック出力信号CK20の立ち上がり時間を調整する。そして立ち上がり時間調整部171は、ステップS601へ戻る。

【0051】

以上に説明したように、本実施形態では、デューティ調整機能部200により、正クロック出力信号CK10のデューティが50%となるように制御される。また本実施形態では、立ち下がり時間調整機能部300により、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しくなるように調整する。さらに本実施形態では、立ち上がり時間調整機能部400により、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間とが等しくなるように調整する。すなわち本実施形態では、正クロック出力信号CK10と負クロック出力信号CK20の位相が等しくなるように調整する。

【0052】

したがって本実施形態では、差動クロックである正クロック出力信号CK10と負クロック出力信号CK20のデューティを最適に制御しながら、差動クロックの位相差を調整することができ、クロックのばらつきが引き起こすジッタを抑制することができる。

【0053】

尚本実施形態では、立ち下がり時間調整部170を入力端子IN2側に配置し、立ち上がり時間調整部171を出力端子OUT2側に配置したが、両者の配置はこれに限定されない。例えば立ち下がり時間調整部170と立ち上がり時間調整部171とは配置が逆であっても良い。

【0054】

図7は、第一の実施形態において立ち下がり時間調整部と立ち上がり時間調整部の配置が逆であるデューティ補正付き位相調整回路を示す図である。

【0055】

図7に示すデューティ補正付き位相調整回路100Aでは、立ち上がり時間調整部171が入力端子IN2側に配置されており、正の位相検出部160から出力される位相差信号が入力される。また立ち下がり時間調整部170が出力端子OUT2側に配置されており、負の位相検出部161から出力される位相差信号が入力される。

【0056】

デューティ補正付き位相調整回路100Aは、上記構成でもデューティ補正付き位相調整回路100と同様の効果を奏することができる。

【0057】

(第二の実施形態)

以下に図面を参照して本発明の第二の実施形態について説明する。本発明の第二の実施形態は、遅延回路が設けられた点が第一の実施形態と相違する。以下の本発明の第二の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0058】

図8は、第二の実施形態のデューティ補正付き位相調整回路を説明する図である。本実施形態のデューティ補正付き位相調整回路100Bは、デューティ調整部140の出力側に遅延回路180を有する。デューティ調整部140から出力された正クロック出力信号CK10は、遅延回路180を介して出力端子OUT1から出力される。

【0059】

以下に図9を参照して遅延回路180を設けた場合と遅延回路180を設けていない場合との違いを説明する。図9は、第二の実施形態における遅延回路の役割を説明する図である。

【0060】

遅延回路180を有していない場合、入力端子IN1から正クロック信号CK1がデューティ調整部140に入力され、正クロック出力信号CK10として出力されるまでに、デューティ調整部140において時間差t1[s]が生じる。

【0061】

これに対し、入力端子IN2から負クロック信号CK2が立ち下がり時間調整部170に入力され、負クロック出力信号CK21として出力されるまでに時間差t2[s]が生じる。さらに負クロック出力信号CK21が立ち上がり時間調整部171に入力され、負クロック出力信号CK20として出力されるまでに時間差t3[s]が生じる。

【0062】

すなわち負クロック出力信号CK2は、出力端子OUT2から出力されるまでにt2+t3[s]の時間差が生じる。

【0063】

本実施形態の遅延回路180は、正クロック出力信号CK10を出力する際に生じる時間t1[s]と、負クロック出力信号CK20を出力する際に生じる時間差t2+t3[s]とが、デューティ調整機能部200、立ち下がり時間調整機能部300、立ち上がり時間調整機能部400の制御により調整できない場合を考慮したものである。

【0064】

本実施形態では、遅延回路180により、デューティ調整部140から出力された正クロック出力信号CK10をt4[s]遅延させる。本実施形態の遅延回路180では、正クロック信号CK1がデューティ調整部140に入力されてから、正クロック出力信号CK10が出力端子OUT1から出力されるまでの時間差t1+t4[s]が、時間差t2+t3[s]と同じになるように設定することが好ましい。

【0065】

このように遅延回路180を設けることで、クロックのばらつきが引き起こすジッタを抑制することができる。

【0066】

(第三の実施形態)

以下に図面を参照して本発明の第三の実施形態について説明する。本発明の第三の実施形態は、分周器が設けられた点が第一の実施形態と相違する。以下の本発明の第三の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0067】

図10は、第三の実施形態のデューティ補正付き位相調整回路を説明する図である。

【0068】

本実施形態のデューティ補正付き位相調整回路100Cはデューティ調整部140から出力された正クロック出力信号CK10を分周する分周器190、191と、立ち上がり時間調整部171から出力された負クロック出力信号CK20を分周する分周器192、193を有する。

【0069】

本実施形態の分周器190〜193は、何れも同様の構成を有するものである。本実施形態では、分周器190で分周された正クロック出力信号CK10は、正の立ち上がり検出部150へ供給される。また分周器191で分周された正クロック出力信号CK10は、正の立ち下がり検出部151へ供給される。

【0070】

また本実施形態では、分周器192で分周された負クロック出力信号CK20が負の立ち下がり検出部152に供給され、分周器193で分周された負クロック出力信号CK20が負の立ち上がり検出部153に供給される。

【0071】

したがって本実施形態では、正の位相検出部160は、分周された正クロック出力信号CK10の立ち上がり時間と立ち下がり時間とを比較することになる。また負の位相検出部161は、分周された負クロック出力信号CK10の立ち下がり時間と立ち上がり時間とを比較することになる。よって本実施形態では、正の位相検出部160と負の位相検出部161とにおいて、比較時間が長くなる。このため本実施形態では、正の位相検出部160と負の位相検出部161の動作速度は分周しない場合と比べて遅くても良くなる。

【0072】

(第四の実施形態)

以下に図面を参照して本発明の第四の実施形態について説明する。本発明の第四の実施形態は、位相検出部の出力側にDAC(Digital to Analog Converter)が設けられた点が第一の実施形態と相違する。以下の本発明の第四の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0073】

図11は、第四の実施形態のデューティ補正付き位相調整回路を説明する図である。本実施形態のデューティ補正付き位相調整回路100Dは、キャリブレーション信号が入力される端子INCと、DAC195、196、197を有する。

【0074】

DAC195には比較器130の出力が供給される。DAC195の出力は、デューティ調整部140に供給される。DAC196には正の位相検出部160の出力が供給される。DAC196の出力は、立ち下がり時間調整部170に供給される。DAC197には負の位相検出部161の出力が供給される。DAC197の出力は、立ち上がり時間調整部171に供給される。

【0075】

DAC195〜197は、キャリブレーション信号に応じて、出力する値を保持している。キャリブレーション信号とは、正クロック出力信号CK10及び負クロック出力信号CK20に同期したシリアルデータのレベルを合わせるために入力される信号である。キャリブレーション信号の周波数は、予め設定された複数種類の周波数の中から選択された周波数である。

【0076】

以下に図12ないし図14を参照して本実施形態のデューティ調整機能部の動作について説明する。図12は、第四の実施形態のデューティ調整機能部の動作を説明するフローチャートである。

【0077】

図12において、キャリブレーション信号がオンになると、デューティ調整機能部は動作を開始する。

【0078】

図12のステップS1201の処理とステップS1202の処理は、図3のステップS301の処理とステップS302の処理とそれぞれ同様であるから説明を省略する。

【0079】

続いて本実施形態では、参照電圧Vrefと平均電圧Vavとが等しいか否か又は参照電圧Vrefと平均電圧Vavの大小関係が逆転したか否かを判断する(ステップS1203)。

【0080】

ステップS1203において、参照電圧Vrefと平均電圧Vavとが等しいか、又は参照電圧Vrefと平均電圧Vavの大小関係が逆転した場合、本実施形態におけるデューティ調整の処理は終了し、キャリブレーション信号がオフされる。

【0081】

ステップS1203において、参照電圧Vrefと平均電圧Vavとが等しくないか、又は参照電圧Vrefと平均電圧Vavの大小関係が逆転していない場合、参照電圧Vref>平均電圧Vavであるか否かを判断する(ステップS1204)。

【0082】

ステップS1204において参照電圧Vref>平均電圧Vavである場合、DAC195は、正クロック出力信号CK10のデューティを上げる方に1LSB(Least Significant Bit)動かし(ステップS1205)、ステップS1202へ戻る。

【0083】

ステップS1204において参照電圧Vref>平均電圧Vavでない場合、DAC195は、正クロック出力信号CK10のデューティを下げる方に1LSB(動かし(ステップS1206)、ステップS1202へ戻る。尚DAC195は比較器130の出力信号に応じて動作する。

【0084】

次に図13、図14を参照して本実施形態における立ち下がり時間調整機能部及び立ち上がり時間調整機能部の動作を説明する。

【0085】

図13は、第四の実施形態の立ち下がり時間調整機能部を説明するフローチャートである。

【0086】

本実施形態において、キャリブレーション信号がオンになると、正の立ち上がり検出部150は正クロック出力信号CK10の立ち上がり時間を検出し、負の立ち下がり検出部152は負クロック出力信号CK20の立ち下がり時間を検出する(ステップS1301)。

【0087】

続いて正の位相検出部160は、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間との差分値を正の位相差信号vdphpとして出力し、DAC196の出力を正の位相差を少なくする方に1LSB動かす(ステップS1302)。

【0088】

立ち下がり時間調整部170は、DAC196から出力される位相差信号vdphpに基づき、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しいか又は両者の大小関係が逆転したか否かを判断する(ステップS1303)。ステップS1303で両者が等しい又は大小関係が逆転した場合、キャリブレーション信号がオフされ、立ち下がり時間調整部170は処理を終了する。ステップS1303で両者が等しくない又は大小関係が逆転しない場合、ステップS1301へ戻る。

【0089】

図14は、第四の実施形態の立ち上がり時間調整機能部を説明するフローチャートである。

【0090】

本実施形態において、キャリブレーション信号がオンになると、正の立ち下がり検出部151は正クロック出力信号CK10の立ち下がり時間を検出し、負の立ち上がり検出部153は負クロック出力信号CK20の立ち上がり時間を検出する(ステップS1401)。

【0091】

続いて負の位相検出部161は、正クロック出力信号CK10の立ち下がり時間と負クロック出力信号CK20の立ち上がり時間との差分値を負の位相差信号vdphmとして出力し、DAC197の出力を正の位相差を少なくする方に1LSB動かす(ステップS1402)。

【0092】

立ち上がり時間調整部171は、DAC197から出力される位相差信号vdphmに基づき、正クロック出力信号CK10の立ち上がり時間と負クロック出力信号CK20の立ち下がり時間とが等しいか又は両者の大小関係が逆転したか否かを判断する(ステップS1403)。ステップS1403で両者が等しい又は大小関係が逆転した場合、キャリブレーション信号はオフされ、立ち上がり時間調整部171は処理を終了する。ステップS1403で両者が等しくない又は大小関係が逆転しない場合、ステップS1401へ戻る。

【0093】

本実施形態では、以上の制御により、第一の実施形態と同等の効果を得ることができる。

【0094】

(第五の実施形態)

以下に図面を参照して本発明の第五の実施形態について説明する。本発明の第五の実施形態は、4ビットのパラレルデータをシリアルデータに変換するシリアライザに第一ないし第四の実施形態のデューティ補正付き位相調整回路の何れかを適用した形態である。以下の本発明の第五の実施形態の説明では、第一の実施形態と同様の機能構成を有するものには第一の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0095】

図15は、第五の実施形態のシリアライザを説明する図である。図15では、第一の実施形態のデューティ補正付き位相調整回路100を適用した例を示している。

【0096】

図15に示すシリアライザ500は、4ビットのパラレルデータd[0;3]を差動のシリアルデータD1及びD2に変換する。シリアライザ500は、デューティ補正付き位相調整回路100から出力される正クロック出力信号CK10及び負クロック出力信号CK20に同期してパラレルデータd[0;3]をシリアルデータD1,D2に変換する。以下に図16を参照してデューティ補正付位相調整回路100の効果について説明する。

【0097】

図16は、正クロック出力信号と負クロック出力信号に同期してパラレルデータを

シリアライズする様子を示す図である。図16において、点線はパラレルデータが正クロック出力信号CK10、負クロック出力信号CK20のどちらかのエッジに同期していることを示す。図16のシリアルデータ中に記載されている数字は、パラレルデータd[0;3]のうちどのデータが出力されているかを示している。

【0098】

デューティ補正付位相調整回路100では、正クロック出力信号CK10と負クロック出力信号CK20のエッジが等しく、デューティが50%となるように制御するため、図16ではクロックのばらつきに起因のジッタは存在しないことがわかる。

【0099】

以下に図17、図18を参照して本実施形態による効果について説明する。図17は、デューティにばらつきのあるクロックでシリアライズした場合を説明する図である。

【0100】

図17の例では、パラレルデータd[0;3]を同期させる正クロック信号11と負クロック信号CK21のエッジが揃っているが、デューティが揃っていない。

【0101】

正クロック信号CK11と負クロック信号CK21のデューティが50%でない場合、両クロック信号のデューティの50%からの乖離がそのまま決定論的ジッタ17となる。決定論的ジッタとは、データやクロックに依存して受信信号の波形タイミングが変化するジッタである。

【0102】

図18は、クロックのエッジにばらつきがあるクロックでシリアライズした場合を説明する図である。

【0103】

図18の例では、正クロック信号CK12と負クロック信号CK22のデューティは揃っているが、エッジが揃っていない。

【0104】

この場合、正クロック信号CK12と負クロック信号CK22の位相差がそのまま決定論的ジッタ18となる。

【0105】

本実施形態では、正クロック出力信号CK10と負クロック出力信号CK20は、デューティを50%とし、両クロック出力信号のエッジを揃えるように調整されているため、図17や図18に示すような決定論的ジッタの発生を抑制できる。

【0106】

(第六の実施形態)

以下に図面を参照して本発明の第六の実施形態について説明する。本発明の第六の実施形態は、4ビットのパラレルデータをシリアルデータに変換するシリアライザに第四の実施形態のデューティ補正付き位相調整回路を適用した形態である。以下の本発明の第六の実施形態の説明では、第四の実施形態と同様の機能構成を有するものには第四の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0107】

図19は、第六の実施形態のシリアライザを説明する図である。図19では、第四の実施形態のデューティ補正付き位相調整回路100Dを適用した例を示している。

【0108】

本実施形態のシリアライザ600は、シリアライザ610とデューティ補正付き位相調整回路100Dとを含む構成とした。本実施形態のシリアライザ600において、シリアライザ610は、正クロック信号CK1と負クロック信号CK2に同期してパラレルデータd[0;3]をシリアライズし、正シリアルデータD10と負シリアルデータD20として出力する。また本実施形態のシリアライザ600において、デューティ補正付き位相調整回路100Dは、正シリアルデータD10と負シリアルデータD20に対して、デューティ及び立ち上がり時間と立ち下がり時間の制御を行う。そしてデューティ補正付き位相調整回路100Dは、デューティを50%でありエッジが揃った正シリアル出力データD11と負シリアル出力データD21を、シリアライザ600の出力とする。

【0109】

以下に図20を参照して本実施形態のシリアライザ600及びデューティ補正付き位相調整回路100Dの動作を説明する。図20は、第六の実施形態のシリアライザ及びデューティ補正付き位相調整回路の動作を説明するフローチャートである。

【0110】

パラレルデータのシリアライズがスタートすると、デューティ補正付き位相調整回路100Dに入力されるキャリブレーション信号がオンされてシリアルデータのキャリブレーションが開始される。このときパラレルデータd[3;0]は固定の電圧を入力してシリアルデータが0101と出力されるようにする(ステップS2001)尚キャリブレーション信号は、デューティ補正付き位相調整回路100Dに対して外部の回路から供給されるものとした。

【0111】

ステップS2001に続いてデューティ補正付き位相調整回路100Dは、シリアライザ610から出力された正シリアルデータD10と負シリアルデータD20のデューティの調整と、立ち下がり時間調整、立ち上がり時間調整を行う(ステップS2002)。ステップS2002におけるデューティの調整は、図12で説明した通りである。ステップS2002における立ち下がり時間調整は、図13で説明した通りである。ステップS2002における立ち上がり時間調整は、図14で説明した通りである。

【0112】

続いてデューティ補正付き位相調整回路100Dは、上記の各調整が終了したか否かを判断する(ステップS2003)。ステップS2003において各調整が終了していない場合、ステップS2001へ戻る。

【0113】

ステップS2003において各調整が終了していた場合、キャリブレーション信号がオフされ、シリアライザへのパラレルデータの入力が開始されてリアライザの通常動作を開始する(ステップS2004)。

【0114】

このように本実施形態では、キャリブレーション時のみ正シリアルデータD10と負シリアルデータD20の調整を実施し、通常動作のときは制御を行わないので、データパターンによってデューティを調整することは無くなる。また本実施形態では、シリアルデータが所定のパターンとなるとき、デューティが50%に保たれ、正シリアルデータD10と負シリアルデータD20の立ち上がり時間と立ち下がり時間とが揃うように制御される。所定のパターンとは、例えばシリアルデータのパターンが1010又は1010等である。

【0115】

本実施形態では、このようにデューティ補正付き位相調整回路100Dをシリアルデータの送信に適用することで、低ジッタのデータ送信が可能となる。

【0116】

(第七の実施形態)

以下に図面を参照して本発明の第七の実施形態について説明する。本発明の第七の実施形態は、第六の実施形態のシリアライザ600を適用した通信システムの形態である。以下の本発明の第七の実施形態の説明では、第六の実施形態と同様の機能構成を有するものには第六の実施形態の説明で用いた符号と同様の符号を付与し、その説明を省略する。

【0117】

図21は、第七の実施形態の通信システムを示す図である。

【0118】

本実施形態の通信システム2100は、ドライバ回路620と、受信回路700と、伝送路800から構成される。

【0119】

本実施形態では、ドライバ回路620に、第六の実施形態のシリアライザ600を適用することで、低ジッタのデータ送信が可能となるため、通信システム2100を低ジッタとすることができる。

【0120】

以上、各実施形態に基づき本発明の説明を行ってきたが、上記実施形態に示した要件に本発明が限定されるものではない。これらの点に関しては、本発明の主旨をそこなわない範囲で変更することができ、その応用形態に応じて適切に定めることができる。

【符号の説明】

【0121】

100、100A〜100D デューティ補正付き位相調整回路

110 平均電圧検出部

120 参照電圧制生成部

130 比較器

140 デューティ調整部

150 正の立ち上がり検出部

151 負の立ち下がり検出部

152 正の立ち下がり検出部

153 負の立ち上がり検出部

160 正の位相検出部

161 負の位相検出部

170 立ち下がり時間調整部

171 立ち上がり時間調整部

【先行技術文献】

【特許文献】

【0122】

【特許文献1】特開2011−010066号公報

【特許文献2】特開2004−208004号公報

【特許請求の範囲】

【請求項1】

正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路において、

前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、

参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、

前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、

前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、

前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、

前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、

前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、

前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、

前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、

前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、

前記立ち下がり時間調整部から出力された負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有するデューティ補正付位相調整回路。

【請求項2】

前記立ち上がり時間調整部は、

前記正の位相差信号に応じて前記負クロック信号の立ち上がり時間を変化させ、

前記立ち下がり時間調整部は、

前記立ち上がり時間調整部から出力された前記負クロック信号の立ち下がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号として出力する請求項1記載のデューティ補正付位相調整回路。

【請求項3】

前記デューティ調整部の出力側に、遅延回路が接続された請求項1又は2記載のデューティ補正付位相調整回路。

【請求項4】

前記正の立ち上がり検出部の入力側と、前記正の立ち下がり検出部の入力側と、前記負の立ち上がり検出部の入力側と、前記負の立ち下がり検出部の入力側とに、それぞれ分周比の等しい分周器が接続された請求項1又は2記載のデューティ補正付位相調整回路。

【請求項5】

前記比較器の出力側と、前記正の位相検出部の出力側と、前記負の位相検出部の出力側とに、それぞれデジタルアナログコンバータが接続されており、

前記デジタルアナログコンバータは、キャリブレーション信号に応じた出力の値を保持する請求項1又は2記載のデューティ補正付位相調整回路

【請求項6】

正クロック信号と負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路と接続されており、前記正クロック出力信号及び負クロック出力信号に同期してパラレルデータをシリアルデータとするシリアライザであって、

前記デューティ補正付位相調整回路は、

前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、

参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、

前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、

前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、

前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、

前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、

前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、

前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、

前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、

前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、

前記立ち下がり時間調整部から出力された負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有するシリアライザ。

【請求項7】

正クロック信号及び負クロック信号に同期してパラレルデータをシリアルデータとするシリアライザであって、

前記正クロック信号及び前記負クロック信号に同期して前記パラレルデータを前記シリアルデータとするシリアライズ手段と、

前記シリアライズ手段により正クロック信号に同期した正シリアルデータと、前記負クロック信号に同期した負シリアルデータと、を入力とし、前記正シリアルデータと前記負シリアルデータのデューティ及び位相を調整して正シリアル出力データと負シリアル出力データとを出力するデューティ補正付位相調整回路と、を有し、

前記デューティ補正付位相調整回路は、

前記正シリアル出力データの平均電圧値を検出する平均電圧検出部と、

参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、

前記正シリアルデータが入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正シリアルデータのデューティを変化させるデューティ調整部と、

前記正シリアル出力データの立ち上がり時間を検出する正の立ち上がり検出部と、

前記正シリアル出力データの立ち下がり時間を検出する正の立ち下がり検出部と、

前記負シリアル出力データの立ち上がり時間を検出する負の立ち上がり検出部と、

前記負シリアル出力データの立ち下がり時間を検出する負の立ち下がり検出部と、

前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、

前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、

前記正の位相差信号に応じて前記負シリアルデータの立ち下がり時間を変化させる立ち下がり時間調整部と、

前記立ち下がり時間調整部から出力された負シリアルデータの立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負シリアル出力データとする立ち上がり時間調整部と、を有するシリアライザ。

【請求項1】

正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路において、

前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、

参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、

前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、

前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、

前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、

前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、

前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、

前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、

前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、

前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、

前記立ち下がり時間調整部から出力された負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有するデューティ補正付位相調整回路。

【請求項2】

前記立ち上がり時間調整部は、

前記正の位相差信号に応じて前記負クロック信号の立ち上がり時間を変化させ、

前記立ち下がり時間調整部は、

前記立ち上がり時間調整部から出力された前記負クロック信号の立ち下がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号として出力する請求項1記載のデューティ補正付位相調整回路。

【請求項3】

前記デューティ調整部の出力側に、遅延回路が接続された請求項1又は2記載のデューティ補正付位相調整回路。

【請求項4】

前記正の立ち上がり検出部の入力側と、前記正の立ち下がり検出部の入力側と、前記負の立ち上がり検出部の入力側と、前記負の立ち下がり検出部の入力側とに、それぞれ分周比の等しい分周器が接続された請求項1又は2記載のデューティ補正付位相調整回路。

【請求項5】

前記比較器の出力側と、前記正の位相検出部の出力側と、前記負の位相検出部の出力側とに、それぞれデジタルアナログコンバータが接続されており、

前記デジタルアナログコンバータは、キャリブレーション信号に応じた出力の値を保持する請求項1又は2記載のデューティ補正付位相調整回路

【請求項6】

正クロック信号と負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力するデューティ補正付位相調整回路と接続されており、前記正クロック出力信号及び負クロック出力信号に同期してパラレルデータをシリアルデータとするシリアライザであって、

前記デューティ補正付位相調整回路は、

前記正クロック出力信号の平均電圧値を検出する平均電圧検出部と、

参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、

前記正クロック信号が入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正クロック信号のデューティを変化させるデューティ調整部と、

前記正クロック出力信号の立ち上がり時間を検出する正の立ち上がり検出部と、

前記正クロック出力信号の立ち下がり時間を検出する正の立ち下がり検出部と、

前記負クロック出力信号の立ち上がり時間を検出する負の立ち上がり検出部と、

前記負クロック出力信号の立ち下がり時間を検出する負の立ち下がり検出部と、

前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、

前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、

前記正の位相差信号に応じて前記負クロック信号の立ち下がり時間を変化させる立ち下がり時間調整部と、

前記立ち下がり時間調整部から出力された負クロック信号の立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負クロック出力信号とする立ち上がり時間調整部と、を有するシリアライザ。

【請求項7】

正クロック信号及び負クロック信号に同期してパラレルデータをシリアルデータとするシリアライザであって、

前記正クロック信号及び前記負クロック信号に同期して前記パラレルデータを前記シリアルデータとするシリアライズ手段と、

前記シリアライズ手段により正クロック信号に同期した正シリアルデータと、前記負クロック信号に同期した負シリアルデータと、を入力とし、前記正シリアルデータと前記負シリアルデータのデューティ及び位相を調整して正シリアル出力データと負シリアル出力データとを出力するデューティ補正付位相調整回路と、を有し、

前記デューティ補正付位相調整回路は、

前記正シリアル出力データの平均電圧値を検出する平均電圧検出部と、

参照電圧と前記平均電圧値を比較し、比較結果に応じた制御信号を出力する比較器と、

前記正シリアルデータが入力され、前記制御信号に応じて前記平均電圧値と前記参照電圧が等しくなるように入力された前記正シリアルデータのデューティを変化させるデューティ調整部と、

前記正シリアル出力データの立ち上がり時間を検出する正の立ち上がり検出部と、

前記正シリアル出力データの立ち下がり時間を検出する正の立ち下がり検出部と、

前記負シリアル出力データの立ち上がり時間を検出する負の立ち上がり検出部と、

前記負シリアル出力データの立ち下がり時間を検出する負の立ち下がり検出部と、

前記正の立ち上がり時間と前記負の立ち下がり時間との正の位相差信号を出力する正の位相検出部と、

前記正の立ち下がり時間と前記負の立ち上がり時間との負の位相差信号を出力する負の位相検出部と、

前記正の位相差信号に応じて前記負シリアルデータの立ち下がり時間を変化させる立ち下がり時間調整部と、

前記立ち下がり時間調整部から出力された負シリアルデータの立ち上がり時間を前記負の位相差信号に応じて変化させ、前記負シリアル出力データとする立ち上がり時間調整部と、を有するシリアライザ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−62668(P2013−62668A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−199585(P2011−199585)

【出願日】平成23年9月13日(2011.9.13)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月13日(2011.9.13)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]