データを符号化および復号するための方法および装置

【課題】ターボ符号に対するインターリーバ・サイズを選択するための方法および装置を提供する。

【解決手段】動作中、サイズKの情報ブロックが受信される。インターリーバ・サイズK’は、K’がK”に関連していて、K”が、一組のサイズからのものである場合に決定される。一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、aは、整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。必要な場合には、サイズKの情報ブロックは、サイズK’の入力ブロック内に詰め込まれる。もとの入力ブロックおよびインターリーブされた入力ブロックは、符号語ブロックを入手するためにターボ符号器により符号化される。符号語ブロックは、チャネルを通して送信される。

【解決手段】動作中、サイズKの情報ブロックが受信される。インターリーバ・サイズK’は、K’がK”に関連していて、K”が、一組のサイズからのものである場合に決定される。一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、aは、整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。必要な場合には、サイズKの情報ブロックは、サイズK’の入力ブロック内に詰め込まれる。もとの入力ブロックおよびインターリーブされた入力ブロックは、符号語ブロックを入手するためにターボ符号器により符号化される。符号語ブロックは、チャネルを通して送信される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、概して、データの符号化および復号に関し、特に、ターボ符号化および復号のための方法および装置に関する。

【背景技術】

【0002】

有線および無線リンクを通してのデジタル・データの送信は、例えば、リンクまたはチャネル内のノイズ、他の送信からの干渉、または他の環境的要因により劣化する場合がある。チャネルにより導入されたエラーを解決するために、多くの通信システムは、通信中の補助のための誤り訂正技術を使用している。

【0003】

誤り訂正のために使用される1つの技術は、チャネルを通して送信する前に情報ブロックをターボ符号化する方法である。このような技術を使用して、通信システムの送信機内の符号器は、長さK’ビットの入力ブロックuをNビットの符号語ブロックxに符号化する。次に、符号語ブロックは、IEEE802.16e仕様に定義されているように、チャネル・インターリーブのような他の処理の後でチャネルを通して送信される。受信機のところでは、ターボ復号器が、長さNの受信した信号ベクトルyを入力として取り入れ、ベクトルuの推定値^uを生成する。

【0004】

通常、ターボ符号器は、2つの構成畳み込み符号器から構成される。第1の構成符号器は、入力ブロックuをそのもとの順序で入力として受け入れ、第2の構成符号器は、uをターボ・インターリーバπに通した後でそのインターリーブした順序で入力ブロックuを受け入れる。ターボ符号器出力xは、(入力ブロックuに等しい)システマティック・ビット、第1の構成符号器からのパリティ・ビット、および第2の構成符号器からのパリティ・ビットから構成される。

【0005】

それに対応して、通信システムの受信機内のターボ復号器は、一方は、各構成符号に対して1つずつ、2つの構成畳み込み復号器から構成される。構成復号器は、インターリーバπおよび対応するデインターリーバπ−1により分離されている。対数尤度比(LLR)のフォーマットのメッセージは、構成復号器間を反復して通過する。決定^uは数回の反復の後で行われる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Designing good permutations for turbo codes: towards a single model、IEEE Communications Society0−7803−8533−0/04/$20.00(c)2004IEEE

【発明の概要】

【発明が解決しようとする課題】

【0007】

ターボ・インターリーバπは、ターボ符号設計の際の重要な構成要素である。このターボ・インターリーバは、擬似ランダム方法で入力ブロックuをスクランブルし、それ故、優れた重み分布を含む符号語xを提供する。それ故、優れた誤り訂正機能を提供する。復号性能の他に、ターボ・インターリーバπの定義は、受信機内のターボ復号器の実施に大きな影響を与える。メモリ・アクセス競合なしで高レベル並列処理ができるように、ターボ・インターリーバπは、競合を起こさない特性を有する必要がある。

【課題を解決するための手段】

【0008】

競合のないインターリーバに上記ニーズを満たすために、以下にターボ符号のインターリーバ・サイズを選択するための方法および装置について説明する。動作中、サイズKの情報ブロックが受信される。インターリーバ・サイズK’は、K’がK”に関連していて、K”が一組のサイズからのものである場合に決定される。一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、aは整数であり、fはfminとfmaxの間の連続している整数であり、pはpminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。サイズKの情報ブロックは、サイズK’の入力ブロック内に詰め込まれる。入力ブロックは、サイズK’のインターリーバによりインターリーブされる。もとの入力ブロックおよびインターリーブされた入力ブロックは、符号語ブロックを入手するために符号化される。符号語ブロックは、チャネルを通して送信される。

【0009】

本発明の他の実施形態の場合には、K”に関連するインターリーバ・サイズK’を決定するステップは、K’=K”を使用するステップを含む。

さらに他の実施形態の場合には、K”に関連するインターリーバ・サイズK’を決定するステップは、K”が(2m−1)の倍数でない場合に、K’=K”を使用するステップを含み、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用するステップを含む。ここで、mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない小さな正の整数または負の整数である。一実施形態の場合には、m=3である。

【0010】

本発明のさらに他の実施形態の場合、入力ブロックをインターリーブするステップは、並べ替えπ(i)=(iP0+A+d(i))modK’を使用するステップを含む。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号のインターリーバのサイズであり、P0は、K’に相対的に素数である数であり、Aは定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。

【0011】

本発明のさらに他の実施形態の場合には、入力ブロックをインターリーブするステップは、並べ替えπ(i)=(f1×i+f2×i2)modK’を使用するステップを含む。0≦i≦K’−1は、インターリービングした後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数である。

【0012】

データの符号化および復号を説明する前に、必要な背景を設定するために、定義について説明する。

・Kは、情報ブロックのサイズである。

【0013】

・K’は、インターリーバのサイズ(すなわち、それに対してターボ符号インターリーバが定義される入力ブロック・サイズ)である。

・K”は、インターリーバのサイズを決定する際に使用することができる補助変数である。

【0014】

・Kfillerは、情報ブロックに追加されるフィラー・ビットの数である。

・πは、ターボ符号の内部インターリーバである。

・フローリング動作

【0015】

【数1】

【0016】

は、xより小さいか、等しい最大の整数であり、シーリング動作

【0017】

【数2】

【0018】

は、xより大きいか、等しい最小の整数である。

・uは、K’の長さを有し、送信機のところのターボ符号器に送信される入力ブロックである。^uは、K’の長さを有し、受信機のところのターボ復号器により生成される推定入力ブロックである。復号エラーがない場合には^u=uであることに留意されたい。そうでない場合には、^u≠uである。

【図面の簡単な説明】

【0019】

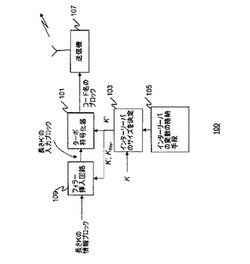

【図1】送信機のブロック図。

【図2】図1のターボ符号器のブロック図。

【図3】受信機のブロック図。

【図4】図4のターボ復号器のブロック図。

【図5】図1の送信機の動作を示すフローチャート。

【図6】図3の受信機の動作を示すフローチャート。

【発明を実施するための形態】

【0020】

類似の参照番号が類似の構成要素を示す図面を参照すると、図1は、送信機100のブロック図であるである。図に示すように、送信機100は、フィラー挿入回路109と、ターボ符号器101と、インターリーバ・サイズ決定回路103と、インターリーバ・パラメータ・テーブル105と、送信機107とを備える。好適には、符号器101は、レート−1/3 3GPPターボ符号器であることが好ましいが、符号器101を動作するための本明細書に記載する技術を、テール・ビットによりまたはテール・ビットを使用しないターボ符号化を実行するターボ符号器、テール・ビッティング、バイナリまたはデュオバイナリ・ターボ符号器、異なるレート・マッチングおよびパンクチャリング技術を使用するターボ符号器等を含むがこれらに限定されない他の符号器に適用することができる。回路103は、K”に関連するインターリーバ・サイズK’を決定する。K”は一組のサイズからのものである。一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含む。aは、整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値をとり、a>1、pmax>pmin、pmin>1である。

【0021】

送信機100の動作中、サイズKの情報ブロックをターボ符号器101で符号化する必要がある。多数の異なるKを使用しているある通信システムの場合には、各情報ブロック・サイズKに対する競合を起こさない(CF)インターリーバを定義するのは効率的ではない(多くの場合不可能である)。好適には、少数の組(K’)のうまく設計されたCFインターリーバがすべての情報ブロック・サイズをカバーすることができることが好ましい。情報ブロック・サイズがKである場合には、適当なインターリーバ・サイズK’は、回路103により一組の使用できるサイズ(例えば、テーブル105内に記載されているインターリーバ・サイズ)から選択することができる。次に、情報ブロックは、回路109によりサイズK’の入力ブロック内に詰め込まれ、入力としてターボ符号器101に送られる。典型的な配置は、(フィラー挿入回路109を介して)Kfillerフィラー・ビットと一緒に情報ブロックを詰め込む。「サイズ」および「長さ」という用語は、ブロックまたはベクトルの素子の数を示すために同義語として使用されることに留意されたい。

【0022】

回路103によりK’を選択すると、K’はターボ符号器101に送られる。符号化中、競合のないインターリーバを(図1に図示せず)使用することができる。例えば、インターリーバは、並べ替えπ(i)=(iP0+A+d(i))modK’を使用することができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前の記号インデックスであり、K’は、記号のインターリーバ・サイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)の「ディザ」ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。他の例としては、インターリーバは、並べ替えπ(i)=(f1×i+f2×i2)modK’を使用することができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前の記号インデックスであり、K’は、記号のインターリーバ・サイズであり、f1およびf2は、インターリーバを定義する係数である。一般に、記号は、複数のビットから構成することができ、インターリービングのステップは、記号内でビットを並べ替える追加のステップを使用することができる。一般性を失わないで、下記の説明は、記号が1つのビットだけから構成され、(それ故、記号内でビットを並べ替える必要がない)通常のケースを考慮し、「ビット」および「記号」という用語は、同義語として使用することができる。

【0023】

ターボ符号器101の出力は、符号語ブロックxを含み、xは送信機107に送られ、チャネルを通して送信される。送信機は、チャネルを通して符号語ブロックxを送信する前に、レート・マッチング、チャネル・インターリービング、変調等のような追加の処理を行う。

【0024】

図2は、図1の符号器101のブロック図である。図に示すように、符号器101は、インターリーバ201と、符号化回路202と、符号化回路203とを備える。符号器の一例としては、3GPP仕様に定義されているターボ符号器がある。3GPPに定義されているターボ符号器のマザー・コード・レートは、R=1/3の本来のコード・レートを有する。ターボ符号器の出力のところで、入力ブロック内で各ビットに対して3つのビット、すなわち(入力ブロック内のビットに等しい)1つのシステマティック・ビット、構成符号器1からの1つのパリティ・ビット、構成符号器2からの1つのパリティ・ビットが生成される。さらに、ターボ符号器の出力は、また、構成符号のトレリスを終了させるために使用されるNTBテール・ビットを含むことができる。例えば、3GPPターボ符号の場合には、ターボ符号器6の出力のところでのNTB=12ビット、構成符号当たりの6テール・ビットである。一方、テール・ビッティング構成畳み込み符号を使用することができる。それ故、NTB=0になる。

【0025】

インターリーバ201は、競合しないインターリーバであってもよい。インターリーバπ(i)(0≦i<K’)は、それがΨ=π(インターリーバ)およびΨ=π−1(デインターリーバ)に対する下記の制約を満たした場合だけ、ウィンドウ・サイズWに対して競合しないインターリーバであるといわれる。

【0026】

【数3】

【0027】

ここで、0≦j<W、0≦t、v<M(=K’/W)であり、t≠vである。いつでもそれが必要なわけではないが、効率的なターボ復号器設計の場合には、通常、M個のウィンドウがすべて満杯である。K’=MWである。(1)の項は、反復復号中に出力メモリ・バンクに外因値を書き込む場合に、M個のプロセッサにより同時にアクセスされるメモリ・バンク・アドレスである。これらすべてのメモリ・バンク・アドレスが、各読出および書込動作中一意のものである場合には、メモリ・アクセス中に競合が起こらないので、(デ)インターリービング待ち時間を避けることができ、復号器の実施が高速になる。

【0028】

ターボ符号器101の動作中、長さK’ビットの入力ブロックはインターリーバ201および符号化回路202の両方に入る。インターリーバ201は、サイズがK’の競合しないインターリーバであってもよい。

【0029】

インターリーバ201は、入力ブロックをインターリーブし、入力ブロックをインターリーブした順序で符号化回路203に送る。次に、符号化回路203は、インターリーブした入力ブロックを符号化する。同じような方法で、符号化回路202は、もとの入力ブロックを符号化する。符号語ブロックxは、(入力ブロックに等しい)システマティック・ブロック、符号化回路202の出力、および符号化回路203の出力から構成される。次に、符号語ブロックxは、入力ブロックのコピーを直接受信することもできる送信機107に送られる。

【0030】

競合しないインターリーバの一例として、下式により表されるほぼ正規の並べ替え(ARP)インターリーバがある。

【0031】

【数4】

【0032】

ここで、0≦i≦K’−1は、インターリービング後のビット位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前のビット・インデックスであり、K’は、インターリーバ・サイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。α(・)およびβ(・)の両方は、複数のCから構成される。このように構成された全インターリーバπ(・)は、周期Cを有する準サイクリック(すなわち、周期的な)特性を有し、テール・ビッティング・ターボ符号で使用した場合には、ターボ符号自身が、準サイクリックになり、符号設計の手順が簡単になる。

【0033】

競合しないインターリーバの他の例としては、二次元多項式の並べ替え(QPP)インターリーバが、下式π(i)=(f1×i+f2×i2)modK’により表される。ここで、0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前の記号インデックスであり、K’は記号内のインターリーバ・サイズであり、f1およびf2は、インターリーバを定義する要因である。ARPインターリーバと同様に、テール・ビッティングである場合には、ターボ符号は同様に準サイクリックである。

【0034】

インターリーバ201がMの種々の値に対して(1)を満たす場合には、(各Mに対して1つずつ)種々の程度の類似を使用して復号器を実施することができる。それ故、種々の係数を有するK’を選択することが望ましい。長さK’のARPインターリーバの場合には、任意のウィンドウ・サイズWを、メモリ・アクセス競合なしで高速復号に使用することができる。Wは、Cの倍数およびK’の係数である。並列ウィンドウの異なる定義を使用して、Kの任意の係数を並列ウィンドウの数として使用することができる。QPPインターリーバの場合には、インターリーバ・サイズK’の各係数が、類似Mの可能なレベルである。これにより類似係数Mの範囲が広くなり、復号器設計を柔軟に行うことができ、スケーラビリティが向上する。それ故、システム(またはユーザ素子のクラス)要件に基づいて復号速度と複雑さの間をうまく妥協することができる。

インターリーバ・サイズK’の選択

すでに説明したように、インターリーバ・サイズ決定回路103は、所与のKに対するインターリーバ・サイズK’を決定しなければならない。この節においては、それに対してターボ符号インターリーバを定義することができる限定された数のサイズ(すなわち、K’)を選択する方法について説明する。すでに説明したように、フィラー挿入回路は(パンクチャリングまたはレート・マッチング方法と一緒に)任意の情報ブロック・サイズKを処理するために使用することができる。一般に、インターリーバ・サイズの選択は、フィラー・ビットによる復号負担および性能の劣化を考慮に入れなければならない。

【0035】

入力ブロックを形成するために情報ブロックに詰め込まれたフィラー・ビットKfillerの数は、情報ブロック・サイズKの低い百分率(例えば、約10〜13%)に制限することが望ましい。このことは、(すべての使用できるK’値が昇順にソートされていると仮定して)隣接するインターリーバ・サイズ、すなわち隣接するK’値間の差を制限することにより達成される。フィラー・ビットの数は、K’≧Kになるような使用可能な最小のK’を選択することにより最小にすることができる。フィラー・ビットの数は、Kfiller=K’−Kである。しかし、必要に応じて、K’≧Kの他の使用できる値も選択することができる。

【0036】

KminとKmaxの間の情報サイズをカバーするように定義した下記の一組のサイズについて考えてみよう。

【0037】

【数5】

【0038】

ここで、aは整数であり、fはfminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値をとり、a>1、pmax>pmin、pmin>1である。必要ではないけれども、必要でない任意のサイズを捨てながら、Kmin=aPmin×fminおよびKmax=aPmax×fmaxとなるようにこれらのパラメータを選択することができる。情報ブロック・サイズのある範囲をカバーするためにサイズの限定した組を選択するこの方法は、片対数スライシングと呼ばれる。サイズKの所与の情報ブロックの場合には、サイズK’は、片対数スライシング・テーブルに基づくK”および入力ブロック・サイズKに関連する。

【0039】

片対数スライシングは、音声コーデックで使用されるA−lawおよびμ−law圧縮伸長器のような広い動的範囲の信号を圧縮する際に使用する圧伸動作に似ている。片対数スライシング規則を使用すれば、広い範囲の情報ブロック・サイズをカバーするために効率的な設計を行うことができる。

【0040】

パラメータを選択するためのいくつかの方法のうちのfminとfmaxを選択するための1つの方法は、隣接するpからのK”値を相互にラインナップさせる方法、すなわちaP×(fmax+1)=aP+1×fminにする方法である。それ故、下式のようになる。

【0041】

【数6】

【0042】

pの所与の値の場合には、2つの隣接するブロック・サイズK”間の距離は、αpで示される。このことは、情報ブロック・サイズKがグループP内に存在し、インターリーバ・サイズがK”に等しい場合には、αp−1フィラー・ビットの最大値が加算されることを意味する。それ故、情報ブロック・サイズK上のフィラー・ビットの一部が以下に示すように囲まれている。このようなことは、ブロック・サイズKが(p,fmin)で表されるサイズより若干大きく、下式に対して(p,fmin+1)で表されるK’=K”を使用する場合に起こる。

【0043】

【数7】

【0044】

別の方法としては、隣接するpからのK”値を、aP×fmax=aP+1×(fmin−1)を介して相互にラインナップすることができる。その結果fmax=a×(fmin−1)となる。これにより類似のKfiller/K境界が得られる。それ故、片対数スライシングに対するパラメータを、支持するブロック・サイズの範囲により、またフィラー・ビットの許容できる部分上で同調させることができる。fminを選択するには、下記の2つの要件の間でバランスをとる必要がある。

【0045】

・fminは、フィラー・ビットの一部を低減するために大きなものでなければならない。

・fminは、インターリーバ・テーブルのサイズを制限するために小さなものでなければならない。何故なら、各pに対して定義したブロック・サイズの数は、fmax=a×fmin−1と仮定した場合、fmax−fmin+1=(a−1)×fminであるからである。

【0046】

片対数スライシング方法は、任意のブロック・サイズに対して、使用するインターリーバ・サイズK’を(2)により計算したK”に基づいて容易に決定することができるという点で非常に簡単なものである。片対数スライス・サイズが定義されると(K”)、インターリーバ・サイズK’を例えば下記により、(ほとんど逸脱することなしに)片対数スライス・サイズから入手することができる。

【0047】

1.K’=K”を使用する。すなわち片対数スライス・サイズを直接有効なインターリーバ・サイズとして使用することができる。

2.K’が(2m−1)の倍数でない場合には、K’=K”を使用して、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用して、ここで、mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない小さな正の整数または負の整数である。このことは構成畳み込み符号がテール・ビッティングである場合に役に立つ。この場合、(2m−1)の倍数は無効である。(2)の片対数スライシング方法により定義したサイズは、場合により、ターボ符号化に対して適していないインターリーバ・サイズであるサイズを含んでいる場合がある。例えば、8状態GPPターボ符号器のテール・ビッティング・バージョンは、7の倍数(すなわち、(2m−1)である入力ブロック・サイズ(すなわち、インターリーバ・サイズ)をサポートしない。このような場合、式(2)が(2m−1)の倍数になる場合はいつでも、結果として得られるサイズが、もはや(2m−1)の倍数にならないように小さな値がそれに加算または減算される。

【0048】

例えば、a=2、fmin=8、およびfmax=15の場合には、形式K’=K”=2P×14のインターリーバ・サイズは7の倍数であり、それ故、テール・ビッティング3GPP TCを使用する場合には、無効なインターリーバ・サイズである。それ故、この場合は、K”が7の倍数でない場合には、例えば、K’=K”を使用して、少し変更して処理しなければならない。そうでない場合で、K”が7の倍数である場合には、K’=K”+δ(K”)を使用して処理しなければならない。δ(K”)は7の倍数に等しくない小さな正の整数または負の整数である。

【0049】

テール・ビッティング・インターリーバに対する無効な選択であるK”サイズの場合には、関連するインターリーバ・サイズK’を決定する簡単な1つの方法は、K”からd×Cを減算(有効として加算)する方法である。ここで、dは小さな正の整数であり、dは7の倍数ではない。ARPインターリーバの場合には、Cは、一組の使用可能なサイズのK’の隣のブロック・サイズに対して使用したARPインターリーバ・サイクル長であってもよい。(ARPインターリーバのブロック・サイズは、サイクル長さCの倍数であることを思い出されたい。) すなわち、K”が7の倍数である場合には下式のようになる。

【0050】

【数8】

【0051】

Cは4、8、12または16のような偶数の整数であるので、このような調整を行うと2つの利点がある。すなわち、(a)K’は7の倍数でないこと、および(b)K’はCの倍数であり、それ故サイズK’に対するARPインターリーバを設計することができることである。

【0052】

簡単にするために、調整する必要があるすべてのK”に対して同じdを選択することができる。dを選択する際の1つの重要な考慮事項は、式(3)または(4)により入手したすべてのサイズが、このように定義したCFインターリーバに対して広い範囲の類似をサポートすることができる係数の実質的な数を有していることである。

インターリーバ・サイズ選択の例

3GPP LTEの場合には、40〜5114ビットの間の各ブロック・サイズに対してCFインターリーバを定義するのは重要なことではない。うまく設計されたCFインターリーバの限定されたまたは小さな一組は、すべてのブロック・サイズをカバーするのに十分である。定義されていない(すなわち、それに対してCFインターリーバが定義されていない)ブロック・サイズの場合には、ゼロパディング(すなわち、追加フィラー・ビット)を、すでに説明したように効率的に使用することができる。

【0053】

第1の例としては、テーブル105内の3GPP長期展開(LTE:Long Term Evolution)に対する情報ブロック・サイズをカバーするのに適している一組のインターリーバを上記片対数スライシング方法に基づいて定義される場合がある。より詳細に説明すると、下式のようになる。

【0054】

【数9】

【0055】

およびK’は、K”から決定される。インターリーバ・サイズは、下記のように決定される。すなわち、K’=K”を使用して、およびp=4、5、6、7、8、9の場合には、およびf=8、9、10、11、12、13、15の場合には、およびK’=K”−dCを使用して、およびf=14の場合には、128〜7680のKをカバーして、p=9に対応する最後の3つのサイズ(f=13、14、15)は、Kmin=128によりKmax=6144になるように除去することができる。式(3)は、テール・ビッティングTCを処理するために、f=14(すなわち7の倍数であるインターリーバ・サイズを避けるために)d=2と一緒に使用される。105内のインターリーバ・サイズが決定されると、各インターリーバ・サイズに対してCFインターリーバを設計することができる。

【0056】

任意の情報ブロック・サイズKの場合には、回路103が、105からKより大きいかまたは等しいK’の最小値を選択することにより、Kに対して使用するインターリーバ・サイズを決定することができる。既知のKにより、fmin=2b、fmax=2b+1−1により(ここで、bは整数)、パラメータpおよびfを下式により計算することができる。

【0057】

【数10】

【0058】

より詳細に説明すると、式(5)のパラメータに対して,b=3であり、pは下式により表される。

【0059】

【数11】

【0060】

パラメータpおよびfにより、式(2)または(5)を使用してブロック・サイズK’を計算することができるし、さらにfが7の倍数であり、テール・ビッティング符号化を使用する場合には、式(3)または(4)を使用して計算したインターリーバ・サイズを加算の際に使用することができる。次に、サイズK’のインターリーバに関連するパラメータが、通常、通信装置用のメモリ内に格納しているインターリーバ・パラメータ105用の格納手段からルックアップされる。

【0061】

第2の例としては、40〜8192ビットのKをカバーするための示唆した一組の完全なインターリーバ・サイズK’は下記の通りである。

K’∈[264,8192]の場合には、K’=2P×f、p=3,...,7、f=33,34,...,64である。

【0062】

264以下のK’の場合には、8のステップ・サイズは、K’=40、48,...256となるように使用される。

下記テーブルはこれらのサイズを示す。

【0063】

【表1】

【0064】

上記テーブルに示すサイズは、8192ビットの最大K’のために定義した一例にしか過ぎず、42の情報ブロック・サイズに比較チェックの際に使用されることに留意されたい。6144ビットのような他の最大値を使用する場合には、最大値より大きい任意のK’がリストから除去される。また、簡単にするために、サイズは、末尾を切った構成符号を使用する場合と、テール・ビッティング構成符号を使用する場合との違いを考慮に入れなかった。ターボ符号器がテール・ビッティングからできている場合には、7の倍数であるK’を使用することができない。これらのものは、すでに説明したように、除去されるか修正される。最後に、追加のインターリーバ・サイズを、インターリーバ間のスペースを小さくするために上記のものに追加することができる。例えば、64の最大スペースを使用する場合には、テーブル内のスペース128を含むインターリーバ間に定義される。次に、テール・ビッティングが使用され、7のK’倍数が除去される場合には、最大スペースは再度128になる。

【0065】

インターリーバ・サイズ選択の他の例として、システムは、トランスポート・ブロック(TB)(分割する前の情報ビットに数)がある値より大きい場合に限って、CFインターリーバを使用することができる。例えば、最大の定義したサイズが5114である場合で、トランスポート・ブロックが5114より大きい場合には、ARPまたはQPPのようなCFインターリーバを使用することができる。これらの場合、分割を行うと、2114より小さいK’を生成することができるが、CFインターリーバはそのK’に対して使用される。それ故、Kは、第1のインターリーバ(3gpp、非CFインターリーバまたは他のインターリーバ)および、分割前のトランスポート・ブロック・サイズにより第2のインターリーバ(競合しないインターリーバ)を使用してターボ・インターリーブすることができる。第1および第2のインターリーバは、異なる組のK’を有することができる。例えば、第1のインターリーバをすべてのK=K’に対して実質的に定義することができ、一方、第2のインターリーバをすでに説明したように、K’で定義することができる。ある場合には、第1のインターリーバに対して1個または数個のプロセッサを使用することができる。

ARPインターリーバの例

テーブル1は、3GPP長期展開(LTE)のための情報ブロック・サイズをカバーするのに適している42CF ARPインターリーバのサブセットを示す。サイクル長さC=4は、K<1024、K≧1024に対するC=8のために使用される。もっと大きなサイクル長さを使用すれば、もっと大きなブロック・サイズのところでもっとよい最少距離が得られる。また、A=3の代わりに、A=0がすべてのサイズに対して使用される。さらに、各Kは異なるα(・)およβ(・)ベクトルを有することができ、小さな一組のαおよびβ値を、インターリーバの定義の格納装置を小さくするために使用することができる。許可されたαおよびβの一組について以下に定義する。

【0066】

サイクル長さC=4の場合、

【0067】

【数12】

【0068】

サイクル長さC=8の場合、

【0069】

【数13】

【0070】

それ故、αの各列をαベクトルとして使用することができ、βの各列はβベクトルとして使用することができる。それ故、インデックスaおよびbが、αおよびβの列を索引するために各Kに対して定義される。ここで、1≦a<2、1≦b≦2Cである。この索引方法によりARPインターリーバの格納装置がかなり小さくなる。何故なら、P0(8ビット)、インデックスa(1ビット)およびb(3〜4ビット)だけをインターリーバ毎に格納しさえすればよいからである。サイクル長さCは、Kが1024ビットよりも小さいか否かに基づいて決定することができる。さらに、C=8対C=4を使用するためのパラメータ格納装置の量は、αおよびβマトリックスのサイズの違いにすぎない。これは些細なことであり、それ故、必要な場合には、もっと大きなCを自由に使用することができる。

【0071】

インターリーバ・パラメータの格納手段105は、テーブル1の少なくとも1つの列から入手したK’C、P0、α(・)およびβ(・)の値を使用してARPインターリーバ・パラメータを格納することができる。インターリーバ201は、下記のテーブルの少なくとも1つの列から入手するK’C、P0、α(・)およびβ(・)の値と一緒にARPインターリーバを使用することができる。

【0072】

テーブル1.LTEのために定義した一組のARインターリーバのパラメータ。一定のオフセットA=0はすべてのサイズに使用される。32より少ないかまたは等しい並列ウィンドウを当然使用する可能な類似Mを示す。

【0073】

【表2】

【0074】

ARPインターリーバの特性

インターリーバ・テーブルを修正するための方法がいくつかある。例えば、2つ以上のインターリーバ・サイズに適用する一組のARPパラメータを使用することにより格納装置を小さくすることができる、例えば、1024ビット、2048ビット、4096ビットのインターリーバは、すべて同じARPパラメータを使用することができる。他の修正実施形態の場合には、そうしたい場合には、テーブルの列のいくつかを異なるC値に基づいて設計することができる。他の改良実施形態の場合には、パラメータ(例えば、α(0)およびβ(0))のエントリのいくつかを固定する(例えば、いつもゼロ)ことができる。

【0075】

下記の記述は、テーブル1を入手するために使用したインターリーバ選択手順についての他のいくつかのコメントである。

1.格納装置を小さくするための一定のオフセット値、A=3またはA=0が選される。

【0076】

2.性能チェックおよび格納装置に基づいて、K’<1024、K’≧1024に対するC=8に対してサイクル長さC=4が使用される。

3.各ブロック・サイズに対して、(テール・ビッティング符号化による)ARPインターリーバ性能が3GPPターボ符号に対する仕様に定義されているインターリーバを含む性能に近いかまたはそれより優れていることを確認するためにシミュレーションを行った。

【0077】

4.テーブル1を特定の一組のインターリーバ・サイズ(例えば、40〜8192)をカバーするように定義した。そうしたい場合には、他のインターリーバ・サイズを削除または追加することもできる。

【0078】

5.7の倍数でない105で定義したすべてのインターリーバを、許容できる性能劣化により、末尾を切ったまたはテール・ビッティング・ターボ符号に対して使用することができる。7の倍数であるこれらのものも末尾を切って使用することができる。

QPPインターリーバの例

テーブル2は、3GPP長期展開(LTE)に対する情報ブロック・サイズをカバーするのに適している42のCF QPPインターリーバのサブセットを示す。これらのインターリーバは、デインターリーバも同様にQPPであるような二次の逆多項式を有する。

【0079】

インターリーバ・パラメータの格納手段105は、テーブル2の少なくとも1つの列から入手するK’f1、f2の値を使用してQPPインターリーバ・パラメータを格納することができる。インターリーバ201は、下記のテーブルの少なくとも1つの列から入手するK’f1、F2の値と一緒にQPPインターリーバを使用することができる。

テーブル2.LTEのために定義した一組のQPPインターリーバのパラメータ。32より少ないかまたは等しい可能な類似を示す。

【0080】

【表3】

【0081】

図3は、受信機300のブロック図である。入力のところで、フィラー処理回路302は、チャネル(例えば、無線)を通して送信された信号ベクトルを受信する。次に、回路306は、例えば、 格納装置308テーブルをルックアップすることにより、または式(7)、(8)および(2)のような計算を行うことにより、上記と類似の方法で行うことができるインターリーバ・サイズK’を決定する。それ故、情報ブロック・サイズKの場合には、復号器304は、符号器101で使用したのと同じインターリーバ・サイズK’を使用する。フィラー処理回路302は、受信した信号ベクトルおよびフィラー・ビット位置を正しく処理するために使用される(例えば、フィラー・ビット位置が分かっている場合には、対応するLLR振幅を復号中に非常に大きな振幅に設定することができる)。次に、ターボ復号器304は、復号を行い、長さK’の入力ブロックの推定値^uを入手する。最後に、情報ブロック抽出物回路310は、^uから推定した情報ブロックを抽出する。フィラー処理回路302は、説明を分かり易くするためにターボ復号器の外側に図示してあるが、これら2つのものは、結合して実施することもできる。

【0082】

図4は、図3のターボ復号器のブロック図である。図を見れば分かるように、インターリーバ402およびデインターリーバ401は、復号回路403と復号回路404の間に位置する。反復復号は、当業者であれば周知のように行われるが、従来技術の復号器とは異なり、インターリーバ・サイズK’はK”と関連する。この場合、K”は一組のサイズからのものである。この一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含む。aは整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。パラメータKfilerは、ターボ復号器が必要とする場合もあるし、必要としない場合もあるので、図4においては鎖線により示してある。

【0083】

すでに説明したように、一実施形態の場合には、K’=K”である。さらに他の実施形態の場合には、K”が(2m−1)の倍数でない場合に、K’=K”であり、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用する。ここで、mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない負の整数である。一実施形態の場合には、m=3である。

【0084】

インターリーバ402は、並べ替えπ(i)=(iP0+A+d(i))modK’を使用することができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。好適には、K’、C、P0、α(・)およびβ(・)の値は、テーブル1の1つの列から取ることが好ましい。デインターリーバ401はインターリーバ402とは逆の機能を実行する。

【0085】

インターリーバ402は、並べ替えπ(i)=(f1×i+f2×i2)modK’を使用することができる。0≦i≦K’−1は、インターリービングした後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数である。好適には、K’、f1、f2は、テーブル2の1つの列から取ることが好ましい。デインターリーバ401は、インターリーバ402とは逆の機能を実行する。

【0086】

図5は、送信機100の動作を示すフローチャートである。ロジックの流れは、ステップ501からスタートする。回路103は、K”に関連するインターリーバ・サイズK’を決定する。K”は、一組のサイズからのものである。この一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、ここで、aは整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。すでに説明したように、一実施形態の場合には、K’=K”である。さらに他の実施形態の場合には、K”が(2m−1)の倍数でない場合に、K’=K”であり、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用する。mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない小さな正の整数または負の整数である。一実施形態の場合には、m=3である。

【0087】

ステップ503において、フィラー挿入回路109は、サイズKの情報ブロックを受信し、サイズKの情報ブロックをサイズK’の入力ブロックu内に詰め込み、入力ブロックuを出力する。次に、インターリーバ201は、サイズKの入力ブロックを(好適には、競合しないインターリーバにより)インターリーブし(ステップ507)、符号化回路203にサイズK’のインターリーブしたブロックを送る(ステップ509)。最後に、ステップ511において、元の入力ブロックおよびインターリーブした入力ブロックが符号化される。

【0088】

すでに説明したように、入力ブロックをインターリーブするステップは、並べ替えπ(i)=(iP0+A+d(i))modK’を使用するステップを含むことができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、ビット内のインターリーバのサイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。好適には、K’、C、P0、α(・)およびβ(・)の値は、テーブル1の1つの列から取ることが好ましい。入力ブロックをインターリーブするステップは、また、並べ替えπ(i)=(f1×i+f2×i2)modK’)を使用するステップを含むことができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数である。好適には、K’、f1、f2はテーブル2の1つの列から取ることが好ましい。

【0089】

図6は、図3の受信機の動作のフローチャートである。ロジックの流れは、ステップ601からスタートする。回路306は、インターリーバ・サイズK’を決定する。ステップ603において、回路302は、受信した信号ベクトルにフィラー・ビット情報を追加する。例えば、フィラー・ビットおよびフィラー・ビット位置が分かっている場合には、回路302は、ターボ復号器入力のこれらの位置の対数尤度比(LLR)を大きな振幅に設定することができる。ステップ607において、ターボ復号器は、インターリーバおよびサイズK’のデインターリーバを使用して、復号器入力ブロックを復号し、長さK’の入力ブロックの推定した^uを出力する。ステップ609において、情報ブロック抽出回路310は、長さKの情報ブロックを入手するためにフィラー・ビットを除去する。最後に、ステップ611において、推定した情報ブロックが出力される。

【0090】

特定の実施形態を参照しながら本発明を詳細に図示し説明してきたが、当業者であれば、本発明の精神および範囲から逸脱することなしに、その形式および詳細を種々に変更することができることを理解することができるだろう。ある例のおいては、(a)例えば、フィラー・ビットを使用しないで、またはもっと少ないフィラー・ビットを使用して、処理しなければならない任意の特殊なサイズをカバーするために定義されたインターリーバの追加の組の使用、(b)片対数スライス・サイズに小さな値を追加することにより、または片対数スライス・サイズから小さな値を抽出することにより、インターリーバ・サイズの若干の調整を含む特殊な場合を処理するために、インターリーバ・テーブルをさらに改善することができる。他の例の場合には、今までバイナリ入力ターボ符号器を仮定して本発明を説明してきたが、ターボ符号器が入力として記号をとった場合には、同じ原理を適用することができる。例えば、デュオバイナリ・ターボ符号は、2つのバイナリビットを同時に取り入れることができ、ターボ・インターリーバは、記号を並べ替える(さらに、記号内でのビットの変更のようなスクランブリングを行うことができる)。そのような場合、入力ブロック・サイズは、記号で測定され、インターリーバ・サイズは入力ブロック内の記号の数に等しい。他の例の場合には、上記説明は、インターリーバ・サイズおよびインターリーバ・パラメータがルックアップ・テーブル内に格納されていると仮定しているが、これらのものを代数計算のような他の手段で決定することもできる。他の例においては、上記説明はターボ符号を仮定しているが、本発明の方法は、例えば、低密度パリティ・チェック(LDPC)符号、リード・ソロモン(RS)符号等を含む他のFECスキームにも適用することができる。このような変更も添付の特許請求の範囲内に含まれる。

【符号の説明】

【0091】

K サイズ

u 入力ブロック

101 ターボ符号器

103 インターリーバ・サイズ決定回路

109 フィラー挿入回路

201,402 インターリーバ

【技術分野】

【0001】

本発明は、概して、データの符号化および復号に関し、特に、ターボ符号化および復号のための方法および装置に関する。

【背景技術】

【0002】

有線および無線リンクを通してのデジタル・データの送信は、例えば、リンクまたはチャネル内のノイズ、他の送信からの干渉、または他の環境的要因により劣化する場合がある。チャネルにより導入されたエラーを解決するために、多くの通信システムは、通信中の補助のための誤り訂正技術を使用している。

【0003】

誤り訂正のために使用される1つの技術は、チャネルを通して送信する前に情報ブロックをターボ符号化する方法である。このような技術を使用して、通信システムの送信機内の符号器は、長さK’ビットの入力ブロックuをNビットの符号語ブロックxに符号化する。次に、符号語ブロックは、IEEE802.16e仕様に定義されているように、チャネル・インターリーブのような他の処理の後でチャネルを通して送信される。受信機のところでは、ターボ復号器が、長さNの受信した信号ベクトルyを入力として取り入れ、ベクトルuの推定値^uを生成する。

【0004】

通常、ターボ符号器は、2つの構成畳み込み符号器から構成される。第1の構成符号器は、入力ブロックuをそのもとの順序で入力として受け入れ、第2の構成符号器は、uをターボ・インターリーバπに通した後でそのインターリーブした順序で入力ブロックuを受け入れる。ターボ符号器出力xは、(入力ブロックuに等しい)システマティック・ビット、第1の構成符号器からのパリティ・ビット、および第2の構成符号器からのパリティ・ビットから構成される。

【0005】

それに対応して、通信システムの受信機内のターボ復号器は、一方は、各構成符号に対して1つずつ、2つの構成畳み込み復号器から構成される。構成復号器は、インターリーバπおよび対応するデインターリーバπ−1により分離されている。対数尤度比(LLR)のフォーマットのメッセージは、構成復号器間を反復して通過する。決定^uは数回の反復の後で行われる。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Designing good permutations for turbo codes: towards a single model、IEEE Communications Society0−7803−8533−0/04/$20.00(c)2004IEEE

【発明の概要】

【発明が解決しようとする課題】

【0007】

ターボ・インターリーバπは、ターボ符号設計の際の重要な構成要素である。このターボ・インターリーバは、擬似ランダム方法で入力ブロックuをスクランブルし、それ故、優れた重み分布を含む符号語xを提供する。それ故、優れた誤り訂正機能を提供する。復号性能の他に、ターボ・インターリーバπの定義は、受信機内のターボ復号器の実施に大きな影響を与える。メモリ・アクセス競合なしで高レベル並列処理ができるように、ターボ・インターリーバπは、競合を起こさない特性を有する必要がある。

【課題を解決するための手段】

【0008】

競合のないインターリーバに上記ニーズを満たすために、以下にターボ符号のインターリーバ・サイズを選択するための方法および装置について説明する。動作中、サイズKの情報ブロックが受信される。インターリーバ・サイズK’は、K’がK”に関連していて、K”が一組のサイズからのものである場合に決定される。一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、aは整数であり、fはfminとfmaxの間の連続している整数であり、pはpminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。サイズKの情報ブロックは、サイズK’の入力ブロック内に詰め込まれる。入力ブロックは、サイズK’のインターリーバによりインターリーブされる。もとの入力ブロックおよびインターリーブされた入力ブロックは、符号語ブロックを入手するために符号化される。符号語ブロックは、チャネルを通して送信される。

【0009】

本発明の他の実施形態の場合には、K”に関連するインターリーバ・サイズK’を決定するステップは、K’=K”を使用するステップを含む。

さらに他の実施形態の場合には、K”に関連するインターリーバ・サイズK’を決定するステップは、K”が(2m−1)の倍数でない場合に、K’=K”を使用するステップを含み、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用するステップを含む。ここで、mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない小さな正の整数または負の整数である。一実施形態の場合には、m=3である。

【0010】

本発明のさらに他の実施形態の場合、入力ブロックをインターリーブするステップは、並べ替えπ(i)=(iP0+A+d(i))modK’を使用するステップを含む。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号のインターリーバのサイズであり、P0は、K’に相対的に素数である数であり、Aは定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。

【0011】

本発明のさらに他の実施形態の場合には、入力ブロックをインターリーブするステップは、並べ替えπ(i)=(f1×i+f2×i2)modK’を使用するステップを含む。0≦i≦K’−1は、インターリービングした後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数である。

【0012】

データの符号化および復号を説明する前に、必要な背景を設定するために、定義について説明する。

・Kは、情報ブロックのサイズである。

【0013】

・K’は、インターリーバのサイズ(すなわち、それに対してターボ符号インターリーバが定義される入力ブロック・サイズ)である。

・K”は、インターリーバのサイズを決定する際に使用することができる補助変数である。

【0014】

・Kfillerは、情報ブロックに追加されるフィラー・ビットの数である。

・πは、ターボ符号の内部インターリーバである。

・フローリング動作

【0015】

【数1】

【0016】

は、xより小さいか、等しい最大の整数であり、シーリング動作

【0017】

【数2】

【0018】

は、xより大きいか、等しい最小の整数である。

・uは、K’の長さを有し、送信機のところのターボ符号器に送信される入力ブロックである。^uは、K’の長さを有し、受信機のところのターボ復号器により生成される推定入力ブロックである。復号エラーがない場合には^u=uであることに留意されたい。そうでない場合には、^u≠uである。

【図面の簡単な説明】

【0019】

【図1】送信機のブロック図。

【図2】図1のターボ符号器のブロック図。

【図3】受信機のブロック図。

【図4】図4のターボ復号器のブロック図。

【図5】図1の送信機の動作を示すフローチャート。

【図6】図3の受信機の動作を示すフローチャート。

【発明を実施するための形態】

【0020】

類似の参照番号が類似の構成要素を示す図面を参照すると、図1は、送信機100のブロック図であるである。図に示すように、送信機100は、フィラー挿入回路109と、ターボ符号器101と、インターリーバ・サイズ決定回路103と、インターリーバ・パラメータ・テーブル105と、送信機107とを備える。好適には、符号器101は、レート−1/3 3GPPターボ符号器であることが好ましいが、符号器101を動作するための本明細書に記載する技術を、テール・ビットによりまたはテール・ビットを使用しないターボ符号化を実行するターボ符号器、テール・ビッティング、バイナリまたはデュオバイナリ・ターボ符号器、異なるレート・マッチングおよびパンクチャリング技術を使用するターボ符号器等を含むがこれらに限定されない他の符号器に適用することができる。回路103は、K”に関連するインターリーバ・サイズK’を決定する。K”は一組のサイズからのものである。一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含む。aは、整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値をとり、a>1、pmax>pmin、pmin>1である。

【0021】

送信機100の動作中、サイズKの情報ブロックをターボ符号器101で符号化する必要がある。多数の異なるKを使用しているある通信システムの場合には、各情報ブロック・サイズKに対する競合を起こさない(CF)インターリーバを定義するのは効率的ではない(多くの場合不可能である)。好適には、少数の組(K’)のうまく設計されたCFインターリーバがすべての情報ブロック・サイズをカバーすることができることが好ましい。情報ブロック・サイズがKである場合には、適当なインターリーバ・サイズK’は、回路103により一組の使用できるサイズ(例えば、テーブル105内に記載されているインターリーバ・サイズ)から選択することができる。次に、情報ブロックは、回路109によりサイズK’の入力ブロック内に詰め込まれ、入力としてターボ符号器101に送られる。典型的な配置は、(フィラー挿入回路109を介して)Kfillerフィラー・ビットと一緒に情報ブロックを詰め込む。「サイズ」および「長さ」という用語は、ブロックまたはベクトルの素子の数を示すために同義語として使用されることに留意されたい。

【0022】

回路103によりK’を選択すると、K’はターボ符号器101に送られる。符号化中、競合のないインターリーバを(図1に図示せず)使用することができる。例えば、インターリーバは、並べ替えπ(i)=(iP0+A+d(i))modK’を使用することができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前の記号インデックスであり、K’は、記号のインターリーバ・サイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)の「ディザ」ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。他の例としては、インターリーバは、並べ替えπ(i)=(f1×i+f2×i2)modK’を使用することができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前の記号インデックスであり、K’は、記号のインターリーバ・サイズであり、f1およびf2は、インターリーバを定義する係数である。一般に、記号は、複数のビットから構成することができ、インターリービングのステップは、記号内でビットを並べ替える追加のステップを使用することができる。一般性を失わないで、下記の説明は、記号が1つのビットだけから構成され、(それ故、記号内でビットを並べ替える必要がない)通常のケースを考慮し、「ビット」および「記号」という用語は、同義語として使用することができる。

【0023】

ターボ符号器101の出力は、符号語ブロックxを含み、xは送信機107に送られ、チャネルを通して送信される。送信機は、チャネルを通して符号語ブロックxを送信する前に、レート・マッチング、チャネル・インターリービング、変調等のような追加の処理を行う。

【0024】

図2は、図1の符号器101のブロック図である。図に示すように、符号器101は、インターリーバ201と、符号化回路202と、符号化回路203とを備える。符号器の一例としては、3GPP仕様に定義されているターボ符号器がある。3GPPに定義されているターボ符号器のマザー・コード・レートは、R=1/3の本来のコード・レートを有する。ターボ符号器の出力のところで、入力ブロック内で各ビットに対して3つのビット、すなわち(入力ブロック内のビットに等しい)1つのシステマティック・ビット、構成符号器1からの1つのパリティ・ビット、構成符号器2からの1つのパリティ・ビットが生成される。さらに、ターボ符号器の出力は、また、構成符号のトレリスを終了させるために使用されるNTBテール・ビットを含むことができる。例えば、3GPPターボ符号の場合には、ターボ符号器6の出力のところでのNTB=12ビット、構成符号当たりの6テール・ビットである。一方、テール・ビッティング構成畳み込み符号を使用することができる。それ故、NTB=0になる。

【0025】

インターリーバ201は、競合しないインターリーバであってもよい。インターリーバπ(i)(0≦i<K’)は、それがΨ=π(インターリーバ)およびΨ=π−1(デインターリーバ)に対する下記の制約を満たした場合だけ、ウィンドウ・サイズWに対して競合しないインターリーバであるといわれる。

【0026】

【数3】

【0027】

ここで、0≦j<W、0≦t、v<M(=K’/W)であり、t≠vである。いつでもそれが必要なわけではないが、効率的なターボ復号器設計の場合には、通常、M個のウィンドウがすべて満杯である。K’=MWである。(1)の項は、反復復号中に出力メモリ・バンクに外因値を書き込む場合に、M個のプロセッサにより同時にアクセスされるメモリ・バンク・アドレスである。これらすべてのメモリ・バンク・アドレスが、各読出および書込動作中一意のものである場合には、メモリ・アクセス中に競合が起こらないので、(デ)インターリービング待ち時間を避けることができ、復号器の実施が高速になる。

【0028】

ターボ符号器101の動作中、長さK’ビットの入力ブロックはインターリーバ201および符号化回路202の両方に入る。インターリーバ201は、サイズがK’の競合しないインターリーバであってもよい。

【0029】

インターリーバ201は、入力ブロックをインターリーブし、入力ブロックをインターリーブした順序で符号化回路203に送る。次に、符号化回路203は、インターリーブした入力ブロックを符号化する。同じような方法で、符号化回路202は、もとの入力ブロックを符号化する。符号語ブロックxは、(入力ブロックに等しい)システマティック・ブロック、符号化回路202の出力、および符号化回路203の出力から構成される。次に、符号語ブロックxは、入力ブロックのコピーを直接受信することもできる送信機107に送られる。

【0030】

競合しないインターリーバの一例として、下式により表されるほぼ正規の並べ替え(ARP)インターリーバがある。

【0031】

【数4】

【0032】

ここで、0≦i≦K’−1は、インターリービング後のビット位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前のビット・インデックスであり、K’は、インターリーバ・サイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。α(・)およびβ(・)の両方は、複数のCから構成される。このように構成された全インターリーバπ(・)は、周期Cを有する準サイクリック(すなわち、周期的な)特性を有し、テール・ビッティング・ターボ符号で使用した場合には、ターボ符号自身が、準サイクリックになり、符号設計の手順が簡単になる。

【0033】

競合しないインターリーバの他の例としては、二次元多項式の並べ替え(QPP)インターリーバが、下式π(i)=(f1×i+f2×i2)modK’により表される。ここで、0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービング前の記号インデックスであり、K’は記号内のインターリーバ・サイズであり、f1およびf2は、インターリーバを定義する要因である。ARPインターリーバと同様に、テール・ビッティングである場合には、ターボ符号は同様に準サイクリックである。

【0034】

インターリーバ201がMの種々の値に対して(1)を満たす場合には、(各Mに対して1つずつ)種々の程度の類似を使用して復号器を実施することができる。それ故、種々の係数を有するK’を選択することが望ましい。長さK’のARPインターリーバの場合には、任意のウィンドウ・サイズWを、メモリ・アクセス競合なしで高速復号に使用することができる。Wは、Cの倍数およびK’の係数である。並列ウィンドウの異なる定義を使用して、Kの任意の係数を並列ウィンドウの数として使用することができる。QPPインターリーバの場合には、インターリーバ・サイズK’の各係数が、類似Mの可能なレベルである。これにより類似係数Mの範囲が広くなり、復号器設計を柔軟に行うことができ、スケーラビリティが向上する。それ故、システム(またはユーザ素子のクラス)要件に基づいて復号速度と複雑さの間をうまく妥協することができる。

インターリーバ・サイズK’の選択

すでに説明したように、インターリーバ・サイズ決定回路103は、所与のKに対するインターリーバ・サイズK’を決定しなければならない。この節においては、それに対してターボ符号インターリーバを定義することができる限定された数のサイズ(すなわち、K’)を選択する方法について説明する。すでに説明したように、フィラー挿入回路は(パンクチャリングまたはレート・マッチング方法と一緒に)任意の情報ブロック・サイズKを処理するために使用することができる。一般に、インターリーバ・サイズの選択は、フィラー・ビットによる復号負担および性能の劣化を考慮に入れなければならない。

【0035】

入力ブロックを形成するために情報ブロックに詰め込まれたフィラー・ビットKfillerの数は、情報ブロック・サイズKの低い百分率(例えば、約10〜13%)に制限することが望ましい。このことは、(すべての使用できるK’値が昇順にソートされていると仮定して)隣接するインターリーバ・サイズ、すなわち隣接するK’値間の差を制限することにより達成される。フィラー・ビットの数は、K’≧Kになるような使用可能な最小のK’を選択することにより最小にすることができる。フィラー・ビットの数は、Kfiller=K’−Kである。しかし、必要に応じて、K’≧Kの他の使用できる値も選択することができる。

【0036】

KminとKmaxの間の情報サイズをカバーするように定義した下記の一組のサイズについて考えてみよう。

【0037】

【数5】

【0038】

ここで、aは整数であり、fはfminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値をとり、a>1、pmax>pmin、pmin>1である。必要ではないけれども、必要でない任意のサイズを捨てながら、Kmin=aPmin×fminおよびKmax=aPmax×fmaxとなるようにこれらのパラメータを選択することができる。情報ブロック・サイズのある範囲をカバーするためにサイズの限定した組を選択するこの方法は、片対数スライシングと呼ばれる。サイズKの所与の情報ブロックの場合には、サイズK’は、片対数スライシング・テーブルに基づくK”および入力ブロック・サイズKに関連する。

【0039】

片対数スライシングは、音声コーデックで使用されるA−lawおよびμ−law圧縮伸長器のような広い動的範囲の信号を圧縮する際に使用する圧伸動作に似ている。片対数スライシング規則を使用すれば、広い範囲の情報ブロック・サイズをカバーするために効率的な設計を行うことができる。

【0040】

パラメータを選択するためのいくつかの方法のうちのfminとfmaxを選択するための1つの方法は、隣接するpからのK”値を相互にラインナップさせる方法、すなわちaP×(fmax+1)=aP+1×fminにする方法である。それ故、下式のようになる。

【0041】

【数6】

【0042】

pの所与の値の場合には、2つの隣接するブロック・サイズK”間の距離は、αpで示される。このことは、情報ブロック・サイズKがグループP内に存在し、インターリーバ・サイズがK”に等しい場合には、αp−1フィラー・ビットの最大値が加算されることを意味する。それ故、情報ブロック・サイズK上のフィラー・ビットの一部が以下に示すように囲まれている。このようなことは、ブロック・サイズKが(p,fmin)で表されるサイズより若干大きく、下式に対して(p,fmin+1)で表されるK’=K”を使用する場合に起こる。

【0043】

【数7】

【0044】

別の方法としては、隣接するpからのK”値を、aP×fmax=aP+1×(fmin−1)を介して相互にラインナップすることができる。その結果fmax=a×(fmin−1)となる。これにより類似のKfiller/K境界が得られる。それ故、片対数スライシングに対するパラメータを、支持するブロック・サイズの範囲により、またフィラー・ビットの許容できる部分上で同調させることができる。fminを選択するには、下記の2つの要件の間でバランスをとる必要がある。

【0045】

・fminは、フィラー・ビットの一部を低減するために大きなものでなければならない。

・fminは、インターリーバ・テーブルのサイズを制限するために小さなものでなければならない。何故なら、各pに対して定義したブロック・サイズの数は、fmax=a×fmin−1と仮定した場合、fmax−fmin+1=(a−1)×fminであるからである。

【0046】

片対数スライシング方法は、任意のブロック・サイズに対して、使用するインターリーバ・サイズK’を(2)により計算したK”に基づいて容易に決定することができるという点で非常に簡単なものである。片対数スライス・サイズが定義されると(K”)、インターリーバ・サイズK’を例えば下記により、(ほとんど逸脱することなしに)片対数スライス・サイズから入手することができる。

【0047】

1.K’=K”を使用する。すなわち片対数スライス・サイズを直接有効なインターリーバ・サイズとして使用することができる。

2.K’が(2m−1)の倍数でない場合には、K’=K”を使用して、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用して、ここで、mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない小さな正の整数または負の整数である。このことは構成畳み込み符号がテール・ビッティングである場合に役に立つ。この場合、(2m−1)の倍数は無効である。(2)の片対数スライシング方法により定義したサイズは、場合により、ターボ符号化に対して適していないインターリーバ・サイズであるサイズを含んでいる場合がある。例えば、8状態GPPターボ符号器のテール・ビッティング・バージョンは、7の倍数(すなわち、(2m−1)である入力ブロック・サイズ(すなわち、インターリーバ・サイズ)をサポートしない。このような場合、式(2)が(2m−1)の倍数になる場合はいつでも、結果として得られるサイズが、もはや(2m−1)の倍数にならないように小さな値がそれに加算または減算される。

【0048】

例えば、a=2、fmin=8、およびfmax=15の場合には、形式K’=K”=2P×14のインターリーバ・サイズは7の倍数であり、それ故、テール・ビッティング3GPP TCを使用する場合には、無効なインターリーバ・サイズである。それ故、この場合は、K”が7の倍数でない場合には、例えば、K’=K”を使用して、少し変更して処理しなければならない。そうでない場合で、K”が7の倍数である場合には、K’=K”+δ(K”)を使用して処理しなければならない。δ(K”)は7の倍数に等しくない小さな正の整数または負の整数である。

【0049】

テール・ビッティング・インターリーバに対する無効な選択であるK”サイズの場合には、関連するインターリーバ・サイズK’を決定する簡単な1つの方法は、K”からd×Cを減算(有効として加算)する方法である。ここで、dは小さな正の整数であり、dは7の倍数ではない。ARPインターリーバの場合には、Cは、一組の使用可能なサイズのK’の隣のブロック・サイズに対して使用したARPインターリーバ・サイクル長であってもよい。(ARPインターリーバのブロック・サイズは、サイクル長さCの倍数であることを思い出されたい。) すなわち、K”が7の倍数である場合には下式のようになる。

【0050】

【数8】

【0051】

Cは4、8、12または16のような偶数の整数であるので、このような調整を行うと2つの利点がある。すなわち、(a)K’は7の倍数でないこと、および(b)K’はCの倍数であり、それ故サイズK’に対するARPインターリーバを設計することができることである。

【0052】

簡単にするために、調整する必要があるすべてのK”に対して同じdを選択することができる。dを選択する際の1つの重要な考慮事項は、式(3)または(4)により入手したすべてのサイズが、このように定義したCFインターリーバに対して広い範囲の類似をサポートすることができる係数の実質的な数を有していることである。

インターリーバ・サイズ選択の例

3GPP LTEの場合には、40〜5114ビットの間の各ブロック・サイズに対してCFインターリーバを定義するのは重要なことではない。うまく設計されたCFインターリーバの限定されたまたは小さな一組は、すべてのブロック・サイズをカバーするのに十分である。定義されていない(すなわち、それに対してCFインターリーバが定義されていない)ブロック・サイズの場合には、ゼロパディング(すなわち、追加フィラー・ビット)を、すでに説明したように効率的に使用することができる。

【0053】

第1の例としては、テーブル105内の3GPP長期展開(LTE:Long Term Evolution)に対する情報ブロック・サイズをカバーするのに適している一組のインターリーバを上記片対数スライシング方法に基づいて定義される場合がある。より詳細に説明すると、下式のようになる。

【0054】

【数9】

【0055】

およびK’は、K”から決定される。インターリーバ・サイズは、下記のように決定される。すなわち、K’=K”を使用して、およびp=4、5、6、7、8、9の場合には、およびf=8、9、10、11、12、13、15の場合には、およびK’=K”−dCを使用して、およびf=14の場合には、128〜7680のKをカバーして、p=9に対応する最後の3つのサイズ(f=13、14、15)は、Kmin=128によりKmax=6144になるように除去することができる。式(3)は、テール・ビッティングTCを処理するために、f=14(すなわち7の倍数であるインターリーバ・サイズを避けるために)d=2と一緒に使用される。105内のインターリーバ・サイズが決定されると、各インターリーバ・サイズに対してCFインターリーバを設計することができる。

【0056】

任意の情報ブロック・サイズKの場合には、回路103が、105からKより大きいかまたは等しいK’の最小値を選択することにより、Kに対して使用するインターリーバ・サイズを決定することができる。既知のKにより、fmin=2b、fmax=2b+1−1により(ここで、bは整数)、パラメータpおよびfを下式により計算することができる。

【0057】

【数10】

【0058】

より詳細に説明すると、式(5)のパラメータに対して,b=3であり、pは下式により表される。

【0059】

【数11】

【0060】

パラメータpおよびfにより、式(2)または(5)を使用してブロック・サイズK’を計算することができるし、さらにfが7の倍数であり、テール・ビッティング符号化を使用する場合には、式(3)または(4)を使用して計算したインターリーバ・サイズを加算の際に使用することができる。次に、サイズK’のインターリーバに関連するパラメータが、通常、通信装置用のメモリ内に格納しているインターリーバ・パラメータ105用の格納手段からルックアップされる。

【0061】

第2の例としては、40〜8192ビットのKをカバーするための示唆した一組の完全なインターリーバ・サイズK’は下記の通りである。

K’∈[264,8192]の場合には、K’=2P×f、p=3,...,7、f=33,34,...,64である。

【0062】

264以下のK’の場合には、8のステップ・サイズは、K’=40、48,...256となるように使用される。

下記テーブルはこれらのサイズを示す。

【0063】

【表1】

【0064】

上記テーブルに示すサイズは、8192ビットの最大K’のために定義した一例にしか過ぎず、42の情報ブロック・サイズに比較チェックの際に使用されることに留意されたい。6144ビットのような他の最大値を使用する場合には、最大値より大きい任意のK’がリストから除去される。また、簡単にするために、サイズは、末尾を切った構成符号を使用する場合と、テール・ビッティング構成符号を使用する場合との違いを考慮に入れなかった。ターボ符号器がテール・ビッティングからできている場合には、7の倍数であるK’を使用することができない。これらのものは、すでに説明したように、除去されるか修正される。最後に、追加のインターリーバ・サイズを、インターリーバ間のスペースを小さくするために上記のものに追加することができる。例えば、64の最大スペースを使用する場合には、テーブル内のスペース128を含むインターリーバ間に定義される。次に、テール・ビッティングが使用され、7のK’倍数が除去される場合には、最大スペースは再度128になる。

【0065】

インターリーバ・サイズ選択の他の例として、システムは、トランスポート・ブロック(TB)(分割する前の情報ビットに数)がある値より大きい場合に限って、CFインターリーバを使用することができる。例えば、最大の定義したサイズが5114である場合で、トランスポート・ブロックが5114より大きい場合には、ARPまたはQPPのようなCFインターリーバを使用することができる。これらの場合、分割を行うと、2114より小さいK’を生成することができるが、CFインターリーバはそのK’に対して使用される。それ故、Kは、第1のインターリーバ(3gpp、非CFインターリーバまたは他のインターリーバ)および、分割前のトランスポート・ブロック・サイズにより第2のインターリーバ(競合しないインターリーバ)を使用してターボ・インターリーブすることができる。第1および第2のインターリーバは、異なる組のK’を有することができる。例えば、第1のインターリーバをすべてのK=K’に対して実質的に定義することができ、一方、第2のインターリーバをすでに説明したように、K’で定義することができる。ある場合には、第1のインターリーバに対して1個または数個のプロセッサを使用することができる。

ARPインターリーバの例

テーブル1は、3GPP長期展開(LTE)のための情報ブロック・サイズをカバーするのに適している42CF ARPインターリーバのサブセットを示す。サイクル長さC=4は、K<1024、K≧1024に対するC=8のために使用される。もっと大きなサイクル長さを使用すれば、もっと大きなブロック・サイズのところでもっとよい最少距離が得られる。また、A=3の代わりに、A=0がすべてのサイズに対して使用される。さらに、各Kは異なるα(・)およβ(・)ベクトルを有することができ、小さな一組のαおよびβ値を、インターリーバの定義の格納装置を小さくするために使用することができる。許可されたαおよびβの一組について以下に定義する。

【0066】

サイクル長さC=4の場合、

【0067】

【数12】

【0068】

サイクル長さC=8の場合、

【0069】

【数13】

【0070】

それ故、αの各列をαベクトルとして使用することができ、βの各列はβベクトルとして使用することができる。それ故、インデックスaおよびbが、αおよびβの列を索引するために各Kに対して定義される。ここで、1≦a<2、1≦b≦2Cである。この索引方法によりARPインターリーバの格納装置がかなり小さくなる。何故なら、P0(8ビット)、インデックスa(1ビット)およびb(3〜4ビット)だけをインターリーバ毎に格納しさえすればよいからである。サイクル長さCは、Kが1024ビットよりも小さいか否かに基づいて決定することができる。さらに、C=8対C=4を使用するためのパラメータ格納装置の量は、αおよびβマトリックスのサイズの違いにすぎない。これは些細なことであり、それ故、必要な場合には、もっと大きなCを自由に使用することができる。

【0071】

インターリーバ・パラメータの格納手段105は、テーブル1の少なくとも1つの列から入手したK’C、P0、α(・)およびβ(・)の値を使用してARPインターリーバ・パラメータを格納することができる。インターリーバ201は、下記のテーブルの少なくとも1つの列から入手するK’C、P0、α(・)およびβ(・)の値と一緒にARPインターリーバを使用することができる。

【0072】

テーブル1.LTEのために定義した一組のARインターリーバのパラメータ。一定のオフセットA=0はすべてのサイズに使用される。32より少ないかまたは等しい並列ウィンドウを当然使用する可能な類似Mを示す。

【0073】

【表2】

【0074】

ARPインターリーバの特性

インターリーバ・テーブルを修正するための方法がいくつかある。例えば、2つ以上のインターリーバ・サイズに適用する一組のARPパラメータを使用することにより格納装置を小さくすることができる、例えば、1024ビット、2048ビット、4096ビットのインターリーバは、すべて同じARPパラメータを使用することができる。他の修正実施形態の場合には、そうしたい場合には、テーブルの列のいくつかを異なるC値に基づいて設計することができる。他の改良実施形態の場合には、パラメータ(例えば、α(0)およびβ(0))のエントリのいくつかを固定する(例えば、いつもゼロ)ことができる。

【0075】

下記の記述は、テーブル1を入手するために使用したインターリーバ選択手順についての他のいくつかのコメントである。

1.格納装置を小さくするための一定のオフセット値、A=3またはA=0が選される。

【0076】

2.性能チェックおよび格納装置に基づいて、K’<1024、K’≧1024に対するC=8に対してサイクル長さC=4が使用される。

3.各ブロック・サイズに対して、(テール・ビッティング符号化による)ARPインターリーバ性能が3GPPターボ符号に対する仕様に定義されているインターリーバを含む性能に近いかまたはそれより優れていることを確認するためにシミュレーションを行った。

【0077】

4.テーブル1を特定の一組のインターリーバ・サイズ(例えば、40〜8192)をカバーするように定義した。そうしたい場合には、他のインターリーバ・サイズを削除または追加することもできる。

【0078】

5.7の倍数でない105で定義したすべてのインターリーバを、許容できる性能劣化により、末尾を切ったまたはテール・ビッティング・ターボ符号に対して使用することができる。7の倍数であるこれらのものも末尾を切って使用することができる。

QPPインターリーバの例

テーブル2は、3GPP長期展開(LTE)に対する情報ブロック・サイズをカバーするのに適している42のCF QPPインターリーバのサブセットを示す。これらのインターリーバは、デインターリーバも同様にQPPであるような二次の逆多項式を有する。

【0079】

インターリーバ・パラメータの格納手段105は、テーブル2の少なくとも1つの列から入手するK’f1、f2の値を使用してQPPインターリーバ・パラメータを格納することができる。インターリーバ201は、下記のテーブルの少なくとも1つの列から入手するK’f1、F2の値と一緒にQPPインターリーバを使用することができる。

テーブル2.LTEのために定義した一組のQPPインターリーバのパラメータ。32より少ないかまたは等しい可能な類似を示す。

【0080】

【表3】

【0081】

図3は、受信機300のブロック図である。入力のところで、フィラー処理回路302は、チャネル(例えば、無線)を通して送信された信号ベクトルを受信する。次に、回路306は、例えば、 格納装置308テーブルをルックアップすることにより、または式(7)、(8)および(2)のような計算を行うことにより、上記と類似の方法で行うことができるインターリーバ・サイズK’を決定する。それ故、情報ブロック・サイズKの場合には、復号器304は、符号器101で使用したのと同じインターリーバ・サイズK’を使用する。フィラー処理回路302は、受信した信号ベクトルおよびフィラー・ビット位置を正しく処理するために使用される(例えば、フィラー・ビット位置が分かっている場合には、対応するLLR振幅を復号中に非常に大きな振幅に設定することができる)。次に、ターボ復号器304は、復号を行い、長さK’の入力ブロックの推定値^uを入手する。最後に、情報ブロック抽出物回路310は、^uから推定した情報ブロックを抽出する。フィラー処理回路302は、説明を分かり易くするためにターボ復号器の外側に図示してあるが、これら2つのものは、結合して実施することもできる。

【0082】

図4は、図3のターボ復号器のブロック図である。図を見れば分かるように、インターリーバ402およびデインターリーバ401は、復号回路403と復号回路404の間に位置する。反復復号は、当業者であれば周知のように行われるが、従来技術の復号器とは異なり、インターリーバ・サイズK’はK”と関連する。この場合、K”は一組のサイズからのものである。この一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含む。aは整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。パラメータKfilerは、ターボ復号器が必要とする場合もあるし、必要としない場合もあるので、図4においては鎖線により示してある。

【0083】

すでに説明したように、一実施形態の場合には、K’=K”である。さらに他の実施形態の場合には、K”が(2m−1)の倍数でない場合に、K’=K”であり、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用する。ここで、mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない負の整数である。一実施形態の場合には、m=3である。

【0084】

インターリーバ402は、並べ替えπ(i)=(iP0+A+d(i))modK’を使用することができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。好適には、K’、C、P0、α(・)およびβ(・)の値は、テーブル1の1つの列から取ることが好ましい。デインターリーバ401はインターリーバ402とは逆の機能を実行する。

【0085】

インターリーバ402は、並べ替えπ(i)=(f1×i+f2×i2)modK’を使用することができる。0≦i≦K’−1は、インターリービングした後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数である。好適には、K’、f1、f2は、テーブル2の1つの列から取ることが好ましい。デインターリーバ401は、インターリーバ402とは逆の機能を実行する。

【0086】

図5は、送信機100の動作を示すフローチャートである。ロジックの流れは、ステップ501からスタートする。回路103は、K”に関連するインターリーバ・サイズK’を決定する。K”は、一組のサイズからのものである。この一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、ここで、aは整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1である。すでに説明したように、一実施形態の場合には、K’=K”である。さらに他の実施形態の場合には、K”が(2m−1)の倍数でない場合に、K’=K”であり、そうでない場合でK”が(2m−1)の倍数である場合には、K’=K”+δ(K”)を使用する。mは、構成畳み込み符号器のメモリ長であり、δ(K”)は、(2m−1)の倍数に等しくない小さな正の整数または負の整数である。一実施形態の場合には、m=3である。

【0087】

ステップ503において、フィラー挿入回路109は、サイズKの情報ブロックを受信し、サイズKの情報ブロックをサイズK’の入力ブロックu内に詰め込み、入力ブロックuを出力する。次に、インターリーバ201は、サイズKの入力ブロックを(好適には、競合しないインターリーバにより)インターリーブし(ステップ507)、符号化回路203にサイズK’のインターリーブしたブロックを送る(ステップ509)。最後に、ステップ511において、元の入力ブロックおよびインターリーブした入力ブロックが符号化される。

【0088】

すでに説明したように、入力ブロックをインターリーブするステップは、並べ替えπ(i)=(iP0+A+d(i))modK’を使用するステップを含むことができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、ビット内のインターリーバのサイズであり、P0は、K’に相対的に素数である数であり、Aは、定数であり、Cは、K’を割る小さな数であり、d(i)は、形式d(i)=β(imodC)+P0×α(imodC)のディザ・ベクトルである。α(・)およびβ(・)は、0≦i≦K’−1に対して周期的に適用されるそれぞれが長さCのベクトルである。好適には、K’、C、P0、α(・)およびβ(・)の値は、テーブル1の1つの列から取ることが好ましい。入力ブロックをインターリーブするステップは、また、並べ替えπ(i)=(f1×i+f2×i2)modK’)を使用するステップを含むことができる。0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数である。好適には、K’、f1、f2はテーブル2の1つの列から取ることが好ましい。

【0089】

図6は、図3の受信機の動作のフローチャートである。ロジックの流れは、ステップ601からスタートする。回路306は、インターリーバ・サイズK’を決定する。ステップ603において、回路302は、受信した信号ベクトルにフィラー・ビット情報を追加する。例えば、フィラー・ビットおよびフィラー・ビット位置が分かっている場合には、回路302は、ターボ復号器入力のこれらの位置の対数尤度比(LLR)を大きな振幅に設定することができる。ステップ607において、ターボ復号器は、インターリーバおよびサイズK’のデインターリーバを使用して、復号器入力ブロックを復号し、長さK’の入力ブロックの推定した^uを出力する。ステップ609において、情報ブロック抽出回路310は、長さKの情報ブロックを入手するためにフィラー・ビットを除去する。最後に、ステップ611において、推定した情報ブロックが出力される。

【0090】

特定の実施形態を参照しながら本発明を詳細に図示し説明してきたが、当業者であれば、本発明の精神および範囲から逸脱することなしに、その形式および詳細を種々に変更することができることを理解することができるだろう。ある例のおいては、(a)例えば、フィラー・ビットを使用しないで、またはもっと少ないフィラー・ビットを使用して、処理しなければならない任意の特殊なサイズをカバーするために定義されたインターリーバの追加の組の使用、(b)片対数スライス・サイズに小さな値を追加することにより、または片対数スライス・サイズから小さな値を抽出することにより、インターリーバ・サイズの若干の調整を含む特殊な場合を処理するために、インターリーバ・テーブルをさらに改善することができる。他の例の場合には、今までバイナリ入力ターボ符号器を仮定して本発明を説明してきたが、ターボ符号器が入力として記号をとった場合には、同じ原理を適用することができる。例えば、デュオバイナリ・ターボ符号は、2つのバイナリビットを同時に取り入れることができ、ターボ・インターリーバは、記号を並べ替える(さらに、記号内でのビットの変更のようなスクランブリングを行うことができる)。そのような場合、入力ブロック・サイズは、記号で測定され、インターリーバ・サイズは入力ブロック内の記号の数に等しい。他の例の場合には、上記説明は、インターリーバ・サイズおよびインターリーバ・パラメータがルックアップ・テーブル内に格納されていると仮定しているが、これらのものを代数計算のような他の手段で決定することもできる。他の例においては、上記説明はターボ符号を仮定しているが、本発明の方法は、例えば、低密度パリティ・チェック(LDPC)符号、リード・ソロモン(RS)符号等を含む他のFECスキームにも適用することができる。このような変更も添付の特許請求の範囲内に含まれる。

【符号の説明】

【0091】

K サイズ

u 入力ブロック

101 ターボ符号器

103 インターリーバ・サイズ決定回路

109 フィラー挿入回路

201,402 インターリーバ

【特許請求の範囲】

【請求項1】

ターボ符号器を操作するための方法であって、

サイズKの情報ブロックを受信するステップと、

一組のサイズからのK”に関連するインターリーバ・サイズK’を決定するステップであって、前記一組のサイズが、K”=aP×f、pmin≦p≦pmax、fmin≦f≦fmaxを含み、aは整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1であり、fmax=a×(fmin−1)である、前記決定するステップと、

サイズKの情報ブロックをサイズK’の入力ブロック内に詰め込むステップと、

サイズK’のインターリーバにより前記入力ブロックをインターリーブするステップであって、前記入力ブロックをインターリーブする前記ステップが、並べ替えπ(i)=(f1×i+f2×i2)modK’)を使用するステップを含み、0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内の前記インターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数であるステップと、

符号語ブロックを入手するためにもとの入力ブロックおよび前記インターリーブした入力ブロックを符号化するステップと、

チャネルを通して前記符号語ブロックを送信するステップと、を含む方法。

【請求項2】

ターボ符号器を操作するための装置であって、

K”に関連するインターリーバ・サイズK’を決定するインターリーバ・サイズ決定回路であって、K”が一組のサイズからのものであり、前記一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、aは、整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1であり、fmax=a×(fmin−1)である、前記インターリーバ・サイズ決定回路と、

サイズKの情報ブロックを受信し、サイズKの前記情報ブロックをサイズK’の入力ブロック内に詰め込むフィラー挿入回路と、

サイズK’の前記入力ブロックをインターリーブするインターリーバであって、インターリーバが並べ替えπ(i)=(f1×i+f2×i2)modK’を使用し、0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数であるインターリーバと、

符号語ブロックを入手するために、前記もとの入力ブロックおよび前記インターリーブした入力ブロックを符号化する符号器と、

を備える装置。

【請求項1】

ターボ符号器を操作するための方法であって、

サイズKの情報ブロックを受信するステップと、

一組のサイズからのK”に関連するインターリーバ・サイズK’を決定するステップであって、前記一組のサイズが、K”=aP×f、pmin≦p≦pmax、fmin≦f≦fmaxを含み、aは整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1であり、fmax=a×(fmin−1)である、前記決定するステップと、

サイズKの情報ブロックをサイズK’の入力ブロック内に詰め込むステップと、

サイズK’のインターリーバにより前記入力ブロックをインターリーブするステップであって、前記入力ブロックをインターリーブする前記ステップが、並べ替えπ(i)=(f1×i+f2×i2)modK’)を使用するステップを含み、0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内の前記インターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数であるステップと、

符号語ブロックを入手するためにもとの入力ブロックおよび前記インターリーブした入力ブロックを符号化するステップと、

チャネルを通して前記符号語ブロックを送信するステップと、を含む方法。

【請求項2】

ターボ符号器を操作するための装置であって、

K”に関連するインターリーバ・サイズK’を決定するインターリーバ・サイズ決定回路であって、K”が一組のサイズからのものであり、前記一組のサイズは、K”=aP×f、pmin≦p≦pmax;fmin≦f≦fmaxを含み、aは、整数であり、fは、fminとfmaxの間の連続している整数であり、pは、pminとpmaxの間の整数値であり、a>1、pmax>pmin、pmin>1であり、fmax=a×(fmin−1)である、前記インターリーバ・サイズ決定回路と、

サイズKの情報ブロックを受信し、サイズKの前記情報ブロックをサイズK’の入力ブロック内に詰め込むフィラー挿入回路と、

サイズK’の前記入力ブロックをインターリーブするインターリーバであって、インターリーバが並べ替えπ(i)=(f1×i+f2×i2)modK’を使用し、0≦i≦K’−1は、インターリービング後の記号位置のシーケンシャルなインデックスであり、π(i)は、位置iに対応するインターリービングする前の記号インデックスであり、K’は、記号内のインターリーバのサイズであり、f1およびf2は、インターリーバを定義する係数であるインターリーバと、

符号語ブロックを入手するために、前記もとの入力ブロックおよび前記インターリーブした入力ブロックを符号化する符号器と、

を備える装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−147188(P2011−147188A)

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願番号】特願2011−97251(P2011−97251)

【出願日】平成23年4月25日(2011.4.25)

【分割の表示】特願2007−308343(P2007−308343)の分割

【原出願日】平成19年11月29日(2007.11.29)

【出願人】(390009597)モトローラ ソリューションズ インコーポレイテッド (649)

【Fターム(参考)】

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願日】平成23年4月25日(2011.4.25)

【分割の表示】特願2007−308343(P2007−308343)の分割

【原出願日】平成19年11月29日(2007.11.29)

【出願人】(390009597)モトローラ ソリューションズ インコーポレイテッド (649)

【Fターム(参考)】

[ Back to top ]