データ伝送回路、及びこれを用いた画像形成装置

【課題】本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減することができるデータ伝送回路、及びこれを用いた画像形成装置を提供する。

【解決手段】データ送信部81によって、テスト用データを転送クロック信号CKと同期させて送信させ、各ビット受信部83により受信されてデュアルポートRAM84に記憶されたデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、位相の異なるクロック信号のうち一つを各マルチプレクサ831で選択させ、受信同期用の同期クロック信号CKnとするタイミング調整処理を実行するデータタイミング調整部46とを備えた。

【解決手段】データ送信部81によって、テスト用データを転送クロック信号CKと同期させて送信させ、各ビット受信部83により受信されてデュアルポートRAM84に記憶されたデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、位相の異なるクロック信号のうち一つを各マルチプレクサ831で選択させ、受信同期用の同期クロック信号CKnとするタイミング調整処理を実行するデータタイミング調整部46とを備えた。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多ビットのデータを転送するデータ伝送回路、及びこれを用いた画像形成装置に関する。

【背景技術】

【0002】

近年、大容量のデータを取り扱う情報処理装置、例えばデジタル複写機、プリンタ、ファクシミリ装置、及びこれらの複合機等において、例えば原稿画像を取得するスキャナと画像処理回路との間や、画像処理回路と画像形成回路との間等、装置内部でのデータの転送速度が高速化しているため、データビットや制御信号間のスキューが僅かに生じただけでデータ転送が困難になるという、不都合が生じている。

【0003】

このようなスキューは、電線長、バターン配線長、コネクタの接触抵抗のバラツキ、あるいは温度、湿度、素子劣化等による遅延量の変動など、種々の要素が影響して生じるので、スキューを発生させないことは困難である。

【0004】

そこで、データの転送に用いる同期クロックと、この同期クロックを反転させた反転クロックとにそれぞれ同期して受信データを取り込み、取り込まれた各受信データをパリティチェックしてパリティ異常が生じていない方の受信データを取得するようにする技術が知られている(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−46182号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に記載の技術では、データにパリティビットを埋め込む必要があるため、データ量が増大してしまうという不都合があった。

【0007】

本発明の目的は、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減することができるデータ伝送回路、及びこれを用いた画像形成装置を提供することである。

【課題を解決するための手段】

【0008】

本発明に係るデータ伝送回路は、複数ビットから構成されるデータの各ビットを、所定の転送クロック信号と同期させて送信するデータ送信部と、前記データ送信部から出力された各ビットを、前記転送クロック信号と同期して受信するデータ受信部と、前記データ送信部及び前記データ受信部の動作を制御する制御部とを備え、前記データ受信部は、前記データの各ビットを、それぞれ1ビットずつ受信する複数のビット受信部と、前記各ビット受信部によって受信された複数のビットを記憶すると共に、当該記憶された複数のビットを、前記データとして外部から読出し可能に構成された記憶部とを含み、前記各ビット受信部は、前記転送クロック信号の位相を所定のクロックシフト量だけシフトさせて同期クロック信号を生成する同期クロック生成部と、当該各ビット受信部の同期クロック生成部によって生成された同期クロック信号と同期して、前記1ビットを受信し、前記記憶部へ出力する同期受信部とを含み、前記制御部は、前記データ送信部によって、予め設定されたテスト用データを前記転送クロック信号と同期させて送信させ、前記各ビット受信部により受信されて前記記憶部に記憶された複数ビットから構成されるデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各同期クロック生成部の前記クロックシフト量をそれぞれ設定するタイミング調整処理を実行するデータタイミング調整部と、前記データタイミング調整部によって前記各同期クロック生成部の前記クロックシフト量がそれぞれ設定された後、前記データ送信部によって、転送しようとする目的データを前記データ受信部へ送信させる転送制御部とを含む。

【0009】

この構成によれば、データ送信部から送信された転送クロック信号が、複数のビット受信部がそれぞれ備える同期クロック生成部によって、所定のクロックシフト量だけシフトされて各同期クロック信号が生成される。そして、データ送信部から送信されたテスト用データの各ビットが、各同期受信部によって、各ビット受信部の同期クロック信号と同期して受信され、記憶部で記憶される。

【0010】

そして、データタイミング調整部によって、記憶部で記憶されたデータとテスト用データとが比較され、当該読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各同期クロック生成部のクロックシフト量がそれぞれ設定される。さらに、データタイミング調整部によって各同期クロック生成部のクロックシフト量がそれぞれ設定された後、データ送信部によって、転送しようとする目的データがデータ受信部へ送信される。

【0011】

この場合、各ビットの受信に用いられる各同期クロック信号の位相が、当該各同期クロック信号と同期して各ビットをそれぞれ受信した場合にテスト用データの各ビットと一致するように、各同期クロック信号の位相が設定されるので、各ビットと各同期クロック信号との間のスキューを低減することができる。そして、このようにしてそれぞれ位相が設定された各同期クロック信号と同期して各ビットが受信されると、受信された各ビット間のタイミングが異なることになるが、記憶部に一旦記憶されることにより、タイミングの異なる各ビットをデータとして外部から読み出すことが可能となる。

【0012】

このようにして、各ビットと各ビットの同期クロック信号との間のスキューが調整された後、転送しようとする目的データがデータ送信部からデータ受信部へ送信され、外部から読出し可能に記憶部に記憶されるので、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減してデータを転送することができる。

【0013】

また、前記データ送信部は、前記データが有効であることを示す有効区間信号と共に前記データを送信し、前記各ビット受信部は、前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成し、前記記憶部へ出力する有効区間信号同期化部と、前記各同期受信部から前記1ビットを前記記憶部へ出力するタイミングを、当該各ビット受信部の同期クロック信号における所定クロック数分遅延させるビットタイミング遅延部とをさらに含み、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各ビットタイミング遅延部における前記所定クロック数を、さらに設定することが好ましい。

【0014】

この構成によれば、有効区間信号が各ビット信号より遅れてスキューが生じている場合であっても、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように各ビットが記憶部へ出力されるタイミングが遅延されて同期化有効区間信号と各ビットとのタイミングが調整されるので、記憶部において、同期化有効区間信号に基づいて、有効区間信号により有効であるとされているデータを正しく記憶することが可能となる。

【0015】

また、前記各ビット受信部は、前記有効区間信号同期化部から出力される同期化有効区間信号を遅延させる有効区間信号遅延部をさらに含み、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各有効区間信号遅延部における前記同期化有効区間信号の遅延量を、さらに設定することが好ましい。

【0016】

この構成によれば、各ビット信号が有効区間信号より遅れてスキューが生じている場合であっても、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように同期化有効区間信号が遅延されて同期化有効区間信号と各ビットとのタイミングが調整されるので、記憶部において、同期化有効区間信号に基づいて、有効区間信号により有効であるとされているデータを正しく記憶することが可能となる。

【0017】

また、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における同期クロック生成部の前記クロックシフト量を変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量をそれぞれ設定することが好ましい。

【0018】

この構成によれば、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各同期クロック生成部のクロックシフト量をそれぞれ設定することができる。

【0019】

また、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数とをそれぞれ設定することが好ましい。

【0020】

この構成によれば、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各クロックシフト量と各所定クロック数とをそれぞれ設定することができる。

【0021】

また、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数と前記有効区間信号遅延部における前記遅延量とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数と前記各遅延量とをそれぞれ設定することが好ましい。

【0022】

この構成によれば、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各クロックシフト量と各所定クロック数と各遅延量とをそれぞれ設定することができる。

【0023】

また、前記テスト用データは、複数のデータが連結されたデータ列であり、前記データ送信部は、前記データ列を、パラレルにされた複数のビット列とし、当該各ビット列を前記転送クロック信号と同期させてシリアルに送信すると共に、前記データ列が送信されている期間中、当該各ビット列が有効であることを示す有効区間信号を送信し、前記各同期受信部は、前記各ビット列をそれぞれ1ビットずつ順次受信して前記記憶部へ出力し、前記各ビット受信部は、前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成する有効区間信号同期化部をさらに備え、前記記憶部は、前記各ビット受信部の有効区間信号同期化部によって生成された同期化有効区間信号が前記有効であることを示す期間中、前記各ビット受信部の同期受信部から順次出力される前記1ビットを、前記各ビット受信部の同期クロック信号と同期して順次記憶することが好ましい。

【0024】

この構成によれば、データ送信部からデータ受信部へ、シリアルのビット列を複数パラレルに送信する態様において、スキューの影響を低減してデータを転送することができる。

【0025】

また、前記データ送信部は、前記複数ビットから構成されるデータを、前記転送クロック信号の整数倍の周期を有する送信クロック信号と同期してシリアルに送信し、前記データ受信部は、前記送信クロック信号を逓倍して前記転送クロック信号を生成し、前記同期クロック生成部へ供給する逓倍回路をさらに備えることが好ましい。

【0026】

この構成によれば、データ送信部からデータ受信部へ送信される同期用のクロック信号として、転送クロック信号より周波数の低い送信クロック信号を用いることができるので、クロック信号による不要輻射を低減することが容易となる。

【0027】

また、前記制御部は、前記データタイミング調整部による前記タイミング調整処理において、前記各同期クロック生成部の前記クロックシフト量をそれぞれ変化させても、前記記憶部から読み出されるデータの各ビットを前記テスト用データの各ビットとそれぞれ一致させることができない場合、異常の発生を報知する報知部をさらに備えることが好ましい。

【0028】

この構成によれば、スキューの調整が困難であって、データを正しく転送できないおそれがある場合に、ユーザに異常の発生を通知することが可能となる。

【0029】

また、本発明に係る画像形成装置は、画像データを取得する画像取得部と、前記画像取得部により取得された画像データに基づき用紙に画像を形成する画像形成部とを備え、前記画像取得部から前記画像形成部へ前記画像データを送信するデータ伝送経路の少なくとも一部に、上述のデータ伝送回路が用いられている。

【0030】

この構成によれば、画像形成装置内部のデータ伝送経路において、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減してデータを転送することができる。

【発明の効果】

【0031】

このような構成のデータ伝送回路、及び画像形成装置は、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減してデータを転送することができる。

【図面の簡単な説明】

【0032】

【図1】本発明の一実施形態に係るデータ伝送回路を備えた画像形成装置の一例であるデジタル複合機の構成の一例を示すブロック図である。

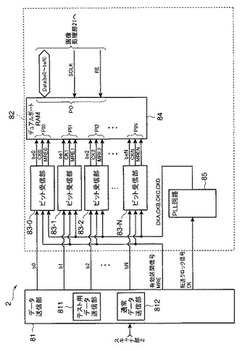

【図2】図1に示すデータ伝送回路の構成の一例を示すブロック図である。

【図3】図2に示すビット受信部の構成の一例を示すブロック図である。

【図4】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図5】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図6】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図7】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図8】変形例を説明するための説明図である。

【発明を実施するための形態】

【0033】

以下、本発明に係る実施形態を図面に基づいて説明する。なお、各図において同一の符号を付した構成は、同一の構成であることを示し、その説明を省略する。図1は、本発明の一実施形態に係るデータ伝送回路を備えた画像形成装置の一例であるデジタル複合機の構成の一例を示すブロック図である。

【0034】

複合機1は、スキャナ部11(画像取得部)、画像処理部21、プリンタ部31、制御部41、操作パネル部51、ファクシミリ通信部61(画像取得部)、ネットワークI/F部71(画像取得部)、パラレルI/F部72(画像取得部)、シリアルI/F部73(画像取得部)及びHDD(ハードディスクドライブ)74、及びデータ伝送回路2,3を備えて構成されている。

【0035】

そして、スキャナ部11、画像処理部21、プリンタ部31、制御部41、操作パネル部51及びファクシミリ通信部61によって、ファクシミリ機能が実現される。また、画像処理部21、プリンタ部31、制御部41、操作パネル部51、ネットワークI/F部71及びパラレルI/F部72によって、プリンタ機能が実現される。また、スキャナ部11、画像処理部21、プリンタ部31、制御部41及び操作パネル部51によって、複写機能が実現される。

【0036】

操作パネル部51は、使用者が複写機能、プリンタ機能、及びファクシミリ機能等に関する操作を行うために使用され、使用者による操作指示、例えば原稿画像の複写を指示する複写指示等を制御部41に与えるものである。操作パネル部51は、タッチパネル等を有する表示部52と、スタートキーやテンキー等を有する操作キー部53とを含む。

【0037】

表示部52は、例えばタッチパネルとLCD(Liquid Crystal Display)とを組み合わせたカラー表示可能なタッチパネルユニット等を有し、種々の操作画面を表示し、ユーザの入力操作を可能とする。表示部52は、例えばファクシミリ機能実行の際に、ユーザ選択、送信先選択、送信設定等に関する情報を表示するとともに、使用者が当該部分をタッチすることで種々の操作指示を入力するための操作ボタン等を表示する。操作キー部53は、使用者によるコピー実行開始指令、あるいはファクシミリ送信開始指令といった種々の指示入力を行うために用いられる。

【0038】

スキャナ部11は、原稿の画像を光学的に取得して画像データを生成するものである。スキャナ部11は、露光ランプ12及びCCD(電荷結合素子)13を含んでいる。スキャナ部11は、露光ランプ12によって原稿を照射し、その反射光をCCD13で受光することで、原稿画像を読み取る。そして、スキャナ部11は、読み取った画像に対応する画像データを、データ伝送回路2によって画像処理部21へ伝送させる。

【0039】

画像処理部21は、画像データに対する各種画像処理を行うものである。例えば、画像処理部21は、スキャナ部11で読み取られるなどして得られた画像データに対して、レベル補正、γ補正等の所定の補正処理、画像データの圧縮または伸張処理、拡大または縮小処理等の種々の画像処理(加工処理)を行う。

【0040】

画像処理部21は、データ伝送回路2に含まれる、後述のデュアルポートRAM84から画像データを読み出すことにより、スキャナ部11で得られた画像データを取得し、例えば画像メモリ22に記憶させる。また、画像処理部21は、例えば画像メモリ22に記憶された画像データを、データ伝送回路3によってプリンタ部31へ伝送させ、プリンタ部31により画像形成を行わせる。

【0041】

プリンタ部31は、画像処理部21からデータ伝送回路3によって伝送された画像データ、ネットワークI/F部71を介して外部のパーソナルコンピュータ等から受信した画像データ、及びファクシミリ通信部61によって外部のファクシミリ装置から受信したファックスデータ等の画像データに基づく画像を所定の記録紙に印刷するものである。

【0042】

プリンタ部31は、給紙カセット及び給紙ローラ等を有する用紙搬送部32、中間転写体ローラ、感光体ドラム、露光装置及び現像装置等を有する画像形成部33、転写ローラ等を有する転写部34並びに定着ローラ等を有する定着部35を含む。具体的には、用紙搬送部32は記録紙を画像形成部33へ搬送し、画像形成部33は上記画像データに対応するトナー像を形成し、転写部34はトナー像を記録紙に転写し、定着部35はトナー像を記録紙に定着させて画像を形成する。

【0043】

ファクシミリ通信部61は、スキャナ部11によって読み取られた原稿の画像データを電話回線等の通信回線611を介して他のファクシミリ装置へ送信したり、他のファクシミリ装置から送信されてきた画像データを受信したりするものである。

【0044】

ネットワークI/F部71は、ネットワークインターフェース(例えば10/100base-TX)等を用い、LAN(Local Area Network)やインターネット等の通信回線711を介して接続されたユーザ側サーバとの間での種々のデータの送受信を制御するものである。また、通信回線711にパーソナルコンピュータ等の図示しない1または複数の通信端末装置が接続されている場合に、ネットワークI/F部71はこれらの通信端末装置との間での種々のデータの送受信を制御する。例えば、ネットワークI/F部71は、スキャナ部11によって読み取られた原稿画像データを通信端末装置へ電子メールとして送信したり、プリンタ部31で印刷するために通信端末装置から送られた画像データを受信したりする。

【0045】

パラレルI/F部72は、例えばIEEE1284準拠等の高速双方向パラレルインターフェイスである。シリアルI/F部73は、例えばUSB(Universal Serial Bus)等のシリアルインターフェイスである。

【0046】

HDD74は、スキャナ部11によって読み取られた画像データや、ファクシミリ通信部61、ネットワークI/F部71、パラレルI/F部72、及びシリアルI/F部73によって外部から受信された画像データ、あるいは当該画像データに設定されている出力形式等を記憶するものである。

【0047】

制御部41は、例えば所定の演算処理を実行するCPU(Central Processing Unit)と、所定の制御プログラムが記憶されたROM(Read Only Memory)と、データを一時的に記憶するRAM(Random Access Memory)と、これらの周辺回路等とを備えて構成されている。そして、例えばROMやHDD74に記憶された制御プログラムを実行することにより、スキャナコントローラ42、ファクシミリコントローラ43、プリンタコントローラ44、コピーコントローラ45、データタイミング調整部46、転送制御部47、及び報知部48として機能する。

【0048】

ファクシミリコントローラ43は、ファクシミリ機能を実現するために用いられる各部の動作を制御するものである。プリンタコントローラ44は、プリンタ機能を実現するために用いられる各部の動作を制御するものである。コピーコントローラ45は、複写機能を実現するために用いられる各部の動作を制御するものである。

【0049】

データタイミング調整部46、及び転送制御部47は、データ伝送回路2,3の動作を後述のように制御する。この場合、データ伝送回路2(又はデータ伝送回路3)、データタイミング調整部46、転送制御部47、及び報知部48で請求項に係るデータ伝送回路が構成されている。なお、データタイミング調整部46、転送制御部47、及び報知部48は、各データ伝送回路にそれぞれ含んで構成されていてもよい。

【0050】

データ伝送回路2は、スキャナ部11から出力された画像データを画像処理部21へ高速伝送する。データ伝送回路3は、画像処理部21から出力された画像データを画像形成部33へ高速伝送する。図2は、図1に示すデータ伝送回路2の構成の一例を示すブロック図である。

【0051】

なお、データ伝送回路3については、データ伝送回路2と、データの転送元及び転送先が異なる以外は同様に構成されているため、図示を省略する。

【0052】

また、スキャナ部11から画像処理部21を介してプリンタ部31へ画像データを送信するデータ伝送経路に、データ伝送回路2,3を備える例を示したが、例えば、ファクシミリ通信部61、ネットワークI/F部71、パラレルI/F部72、及びシリアルI/F部73によって外部から受信された画像データを、HDD74を介してプリンタ部31へ送信するデータ伝送経路等、他の箇所にデータ伝送回路を備えていてもよい。

【0053】

以下、データ伝送回路2の構成について説明する。図2に示すデータ伝送回路2は、データ送信部81と、データ受信部82とを備えている。

【0054】

データ送信部81は、スキャナ部11の近傍に配設されている。また、データ送信部81は、テスト用データ送信部811と、通常データ送信部812とを備えている。

【0055】

テスト用データ送信部811は、データタイミング調整部46からの制御信号に応じて、予め設定されたテスト用データのビットb0〜bNからなるデータDoutと、ビットb0〜bNが有効な期間を示す有効区間信号MREとを、転送クロック信号CKと同期させてデータ受信部82へ送信する。

【0056】

通常データ送信部812は、転送制御部47からの制御信号に応じて、スキャナ部11から出力された画像データのビットb0〜bNと、ビットb0〜bNが有効な期間を示す有効区間信号MREとを、転送クロック信号CKと同期させてデータ受信部82へ送信する。

【0057】

データ受信部82は、画像処理部21の近傍に配設されている。そして、データ受信部82は、N+1個のビット受信部83−0〜83−Nと、デュアルポートRAM(Random Access Memory)84(記憶部)と、PLL(Phase Locked Loop)回路85とを備えている。

【0058】

PLL(Phase Locked Loop)回路85は、例えば、転送クロック信号CKの位相を0°、90°、180°、270°シフトさせた4つのクロック信号CKA,CKB、CKC、CKDを生成し、ビット受信部83−0〜83−Nへ出力する。(クロック信号CKAは転送クロック信号CKと等しい。)

デュアルポートRAM84は、ビット受信部83−0〜83−Nの出力データを受け付けるN+1個の入力ポートPI0〜PINを備えている。そして、デュアルポートRAM84は、記憶しているデータをデータ受信部82の外部に接続された画像処理部21へ出力する出力ポートPOを備えている。

【0059】

また、n番目の入力ポートPInは、n番目のビット受信部83−nから出力されるビットben、同期クロック信号CKn、及び同期化有効区間信号MREnを受け付ける。以下、任意のn番目のビットに対応する構成及び信号を、符号にnを付して示す。

【0060】

そして、デュアルポートRAM84は、各入力ポートPInによって受け付けられたビットben、同期クロック信号CKn、及び同期化有効区間信号MREnに基づいて、同期化有効区間信号MREnが有効であることを示す期間中、ビットbenとして順次出力される1ビットデータを、同期クロック信号CKnと同期して順次記憶する。

【0061】

また、デュアルポートRAM84は、このようにして記憶されたビットbe0〜beNによって構成されるデータDinを、画像処理部21から出力された同期クロック信号SCLKと読出要求信号REとに応じて、出力ポートPOから出力するようになっている。

【0062】

デュアルポートRAM84は、例えば、同期化有効区間信号MREnが有効であることを示す期間中、ビットbenとして順次出力される1ビットデータを、同期クロック信号CKnと同期して順次記憶するN+1個のFIFO(First-In First-Out)を並列接続し、同期クロック信号SCLKと読出要求信号REとを用いて各FIFOからデータを出力させる構成としてもよい。

【0063】

図3は、図2に示すビット受信部83−0〜83−Nの構成の一例を示すブロック図である。ビット受信部83−0〜83−Nは同様に構成されているので、図3においては任意の(n番目の)ビット受信部83−nで代表させて記載している。

【0064】

図3に示すビット受信部83−nは、例えば、マルチプレクサ831(同期クロック生成部)と、フリップフロップFF1(同期受信部)と、ビットタイミング遅延部832と、遅延ブロックDLY1(有効区間信号同期化部)と、有効区間信号遅延部833とを備えている。

【0065】

また、ビットタイミング遅延部832は、フリップフロップFF2,FF3と、マルチプレクサMUX1とを備えている。有効区間信号遅延部833は、遅延ブロックDLY2,DLY3,DLY4と、マルチプレクサMUX2とを備えている。

【0066】

マルチプレクサ831は、制御部41から出力されるクロック切替信号CKSnに応じて、PLL回路85から出力されたクロック信号CKA,CKB,CKC,CKDのうち一つを同期クロック信号CKnとして選択し、フリップフロップFF1(同期受信部)、ビットタイミング遅延部832、遅延ブロックDLY1、有効区間信号遅延部833、及びデュアルポートRAM84の入力ポートPInへ出力する。

【0067】

これによって、転送クロック信号CKからの同期クロック信号CKnのシフト量(クロックシフト量)が、0°、90°、180°、270°のいずれかに設定されるようになっている。

【0068】

フリップフロップFF1は、データ送信部81から出力されたビットbnを、同期クロック信号CKnと同期してラッチし、フリップフロップFF2及びマルチプレクサMUX1へ出力する。

【0069】

フリップフロップFF2は、フリップフロップFF1の出力信号を、同期クロック信号CKnと同期してラッチすることで同期クロック信号CKnの1周期分遅延させ、フリップフロップFF3及びマルチプレクサMUX1へ出力する。

【0070】

フリップフロップFF3は、フリップフロップFF2の出力信号を、同期クロック信号CKnと同期してラッチすることで同期クロック信号CKnの1周期分遅延させ、マルチプレクサMUX1へ出力する。

【0071】

マルチプレクサMUX1は、制御部41から出力されるビット遅延切替信号BDLYnに応じて、フリップフロップFF1,FF2,FF3の出力信号のうち一つを選択し、第nビットのビットbenとしてデュアルポートRAM84へ出力する。

【0072】

これにより、ビット遅延切替信号BDLYnに応じて、ビットbenの遅延時間が設定されるようになっている。

【0073】

遅延ブロックDLY1は、例えば、例えばデータ送信部81から出力された有効区間信号MREを、同期クロック信号CKnと同期してラッチするフリップフロップ回路と、フリップフロップ回路でラッチされた信号を、ビットbenとの関係でセットアップ、ホールドタイムを確保する等のタイミング調整をするための遅延回路とを備えて構成されている。

【0074】

そして、遅延ブロックDLY1は、有効区間信号MREを、同期クロック信号CKnと同期してラッチし、タイミング調整した後に遅延ブロックDLY2及びマルチプレクサMUX2へ出力する。

【0075】

遅延ブロックDLY2,DLY3,DLY4は、遅延ブロックDLY1と同様に構成されている。そして、遅延ブロックDLY2は、遅延ブロックDLY1の出力信号を同期クロック信号CKnと同期してラッチし、タイミング調整した後に遅延ブロックDLY3及びマルチプレクサMUX2へ出力する。

【0076】

遅延ブロックDLY3は、遅延ブロックDLY2の出力信号を同期クロック信号CKnと同期してラッチし、タイミング調整した後に遅延ブロックDLY4及びマルチプレクサMUX2へ出力する。

【0077】

遅延ブロックDLY4は、遅延ブロックDLY3の出力信号を同期クロック信号CKnと同期してラッチし、タイミング調整した後にマルチプレクサMUX2へ出力する。

【0078】

なお、以下の説明においては、説明を簡単にするため、遅延ブロックDLY1,DLY2,DLY3,DLY4は、タイミング調整することなく同期クロック信号CKnと同期してラッチした信号を出力するものとしている。

【0079】

マルチプレクサMUX2は、制御部41から出力される有効区間遅延切替信号MDLYnに応じて、遅延ブロックDLY1,DLY2,DLY3,DLY4の出力信号のうち一つを選択し、第nビット用の同期化有効区間信号MREnとしてデュアルポートRAM84へ出力する。

【0080】

これにより、有効区間遅延切替信号MDLYnに応じて、同期化有効区間信号MREnの遅延時間が設定されるようになっている。

【0081】

そして、このようにしてビット受信部83−0〜83−Nから出力されたビットbe0〜beNが、データDinとしてデュアルポートRAM84によって記憶されるようになっている。

【0082】

データタイミング調整部46は、テスト用データ送信部811によって、予め設定されたテスト用データのビットb0〜bNを転送クロック信号CKと同期させて送信させる。また、このテスト用データと同じデータが、例えば制御部41におけるROMやHDD74に予め記憶されている。

【0083】

そして、データタイミング調整部46は、ビット受信部83−0〜83−Nにより受信されてデュアルポートRAM84にデータDinとして記憶されたデータの各ビットを読み出して、ROM等に記憶されているテスト用データの各ビットとそれぞれ比較し、データDinの各ビットがこのテスト用データの各ビットと一致するように、クロック切替信号CKS0〜CKSN、ビット遅延切替信号BDLY0〜BDLYN、及び有効区間遅延切替信号MDLY0〜MDLYNをビット受信部83−0〜83−Nへ出力し、同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間をそれぞれ設定するタイミング調整処理を実行する。

【0084】

転送制御部47は、データタイミング調整部46によって同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間がそれぞれ設定された後、通常データ送信部812によって、転送しようとする目的データである画像データを、データ受信部82へ送信させる。

【0085】

報知部48は、データタイミング調整部46のタイミング調整処理において、同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間を調整してもなお、データDinの各ビットをテスト用データの各ビットと一致させることができなかった場合、異常が発生した旨のメッセージを表示部52に表示させる。

【0086】

次に、上述のように構成された複合機1及びデータ伝送回路2の動作について説明する。図4〜図7は、図1に示す複合機1及びデータ伝送回路2の動作を説明するための説明図である。

【0087】

まず、例えば複合機1が起動されたときや、あるいは定期的なタイミングで、データタイミング調整部46が、テスト用データ送信部811によって、テストデータをデータDoutとして送信させる。以下、ビット番号0〜Nを、任意の番号nで代表して説明する。

【0088】

テスト用データ送信部811は、初期設定として、クロック切替信号CKSn、ビット遅延切替信号BDLYn、及び有効区間遅延切替信号MDLYnを用いて、マルチプレクサ831により例えばクロック信号CKAを同期クロック信号CKnとして選択させ、マルチプレクサMUX1により例えばフリップフロップFF1の出力信号をビットbenとして選択させ、マルチプレクサMUX1により例えば遅延ブロックDLY1の出力信号を同期化有効区間信号MREnとして選択させる。

【0089】

図4は、テスト用データ送信部811から出力されたデータDoutと、データDoutの各ビットb0〜b3と、転送クロック信号CKとの一例を示している。図4では、テストデータは、16進数の$0、$0、$F、$0、$0、$0という、5つのデータが連結されたデータ列にされている。以下、16進数に「$」を付して表すこととする。

【0090】

そして、このデータ列が送信されている期間中、当該データ(ビットb0〜b3)が有効であることを示すべく、有効区間信号MREが例えばハイレベルにされている。

【0091】

また、ビットb0〜b3は、転送クロック信号CKと同期して出力されている。

【0092】

ところで、スキャナ部11と画像処理部21とは、複合機1の筐体内で離れた位置に配設されているため、ビットb0〜b3、転送クロック信号CK、及び有効区間信号MREは、データ送信部81から、ケーブル等を介してデータ受信部82へ送信されることとなる。そうすると、ケーブルの長さや浮遊容量、あるいはデータ送信部81における出力バッファの特性バラツキ等の影響によって、これらの信号がデータ受信部82で受信される際には各信号間に、例えば図5に示すようなスキューが生じることとなる。

【0093】

この状態で、データ受信部82によって、転送クロック信号CKと同期してビットb0〜b3が受信される。そうすると、転送クロック信号CKと同位相のクロック信号CKA(位相差0°)と、ビットbn(ビットb0〜b3のうち任意のビット)との間にずれが生じ、クロック信号CKAの立上りタイミング(タイミングT1)とビットbnとが同期しないから、ビット受信部83−nにおけるフリップフロップFF1では、正しくビットbnをラッチすることができない。

【0094】

そして、フリップフロップFF1から出力されたビット値がマルチプレクサMUX1によってビットbenとしてデュアルポートRAM84に記憶される。そうすると、ビットbenとして正しいビット値が得られないから、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、テスト用データにおけるnビット目のビット列である「001000」と一致しない。

【0095】

テスト用データ送信部811は、さらに、クロック切替信号CKSnを用いて、マルチプレクサ831により例えばクロック信号CKB,CKC,CKDの順に、マルチプレクサ831で同期クロック信号CKnとして選択させるクロック信号を順次変化させながら、テスト用データ送信部811によるテスト用データのデータ列の送信と、データ受信部82による当該データ列の受信、及びデュアルポートRAM84への書込を繰り返させる。

【0096】

そうすると、図6のタイミングT2,T3,T4に示すように、クロック信号CKB,CKC,CKDの立上りタイミングでは、ビットbnは安定状態になっており、フリップフロップFF1で正しくビット値をラッチすることが可能となっている。そうすると、ビットbnを正しく受信できるタイミングが、クロック信号CKB,CKC,CKDと同期するタイミング、すなわち転送クロック信号CKとの位相差が90°、180°、270°のタイミングで存在することとなる。

【0097】

この場合、データタイミング調整部46は、正しいビット値を読み出せた90°、180°、270°のタイミングのうち、中央の180°に対応するクロック信号CKCを選択し、マルチプレクサ831により同期クロック信号CKnとして選択させるように、クロック切替信号CKSnを設定する。

【0098】

そうすると、図6に示す例では、スキューにより有効区間信号MREがビットbnより遅れており、ビット受信部83−nでクロック信号CKCと同期してラッチされた同期化有効区間信号MREnは、図6(a)に示すように、立上りタイミングが図6(b)に示すクロック信号CKCで同期化されたビットbnの先頭より遅れたタイミングT5になってしまう。

【0099】

そうすると、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、例えば図6(a)(b)におけるビットbnの同期化有効区間信号MREnがハイレベルの期間のデータである「01000X」(Xは不定値)となって、テスト用データにおけるnビット目のビット列である「001000」と一致しない。

【0100】

そこで、テスト用データ送信部811は、さらに、ビットタイミング遅延部832を用いて、マルチプレクサMUX1によって、ビットbnの遅延時間を変化させる。図6(c)に示す例では、マルチプレクサMUX1によって、フリップフロップFF2の出力信号を選択させることで、ビットbnを、同期クロック信号CKn(クロック信号CKC)の1クロック分遅延させている。

【0101】

これにより、同期化有効区間信号MREnと、ビットbnとのタイミングが正しく設定されて、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、「001000」となって、テスト用データにおけるnビット目のビット列である「001000」と一致する。

【0102】

このようにして、ビット受信部83−0〜83−Nによって、各ビットのスキューがそれぞれ調整されて、データ送信部81からデータ受信部82へ、正しくデータを転送することが可能となる。

【0103】

ここで、図6においては、スキューによって、同期化有効区間信号MREnがビットbnより遅れる例を示したが、ビットbnが同期化有効区間信号MREnより遅れる場合、ビットタイミング遅延部832を用いてもスキューを調整することができない。

【0104】

図7は、ビットbnが同期化有効区間信号MREnより遅れる場合の動作を示す説明図である。まず、図7においては、タイミングT12,T13,T14におけるクロック信号CKA,CKB,CKCの立上りタイミングでビットbnが安定状態になっている。

【0105】

従って、図6の場合と同様の動作によって、データタイミング調整部46は、正しいビット値を読み出せる0°、90°、180°のタイミングのうち、中央の90°に対応するクロック信号CKBを選択し、マルチプレクサ831により同期クロック信号CKnとして選択させるように、クロック切替信号CKSnを設定する。

【0106】

そうすると、図7に示す例では、ビット受信部83−nでクロック信号CKBと同期してラッチされた同期化有効区間信号MREnは、図7(a)に示すように、立上りタイミングが図7(b)に示すクロック信号CKBで同期化されたビットbnの先頭より1クロック進んだタイミングT11になってしまう。

【0107】

そうすると、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、例えば図7(a)(b)におけるビットbnの同期化有効区間信号MREnがハイレベルの期間のデータである「X00100」(Xは不定値)となって、テスト用データにおけるnビット目のビット列である「001000」と一致しない。

【0108】

そこで、テスト用データ送信部811は、さらに、有効区間信号遅延部833を用いて、マルチプレクサMUX2によって、同期化有効区間信号MREnの遅延時間を変化させる。図7(c)に示す例では、マルチプレクサMUX2によって、遅延ブロックDLY2の出力信号を選択させることで、同期化有効区間信号MREnを、同期クロック信号CKn(クロック信号CKC)の1クロック分遅延させている。

【0109】

これにより、同期化有効区間信号MREnと、ビットbnとのタイミングが正しく設定されて、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、「001000」となって、テスト用データにおけるnビット目のビット列である「001000」と一致する。

【0110】

このようにして、ビットbnが同期化有効区間信号MREnより遅れる場合であっても、ビット受信部83−0〜83−Nによって、各ビットのスキューがそれぞれ調整されて、データ送信部81からデータ受信部82へ、正しくデータを転送することが可能となる。

【0111】

そして、転送制御部47は、データタイミング調整部46によって同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間がそれぞれ設定された後、通常データ送信部812によって、転送しようとする目的データである画像データを、データ受信部82へ送信させるので、画像データをスキャナ部11から画像処理部21へ、正しく転送することが可能となる。

【0112】

なお、データビット列に有効区間信号が埋め込まれている場合には、同期クロック信号CK0〜CKNの位相シフト量を調整することで、同時にデータビットと有効区間信号との関係も調整されることとなる。

【0113】

また、背景技術のように、データにパリティビットを埋め込む必要がないため、データ量を増大させることなく、スキューの影響を低減することができる。

【0114】

なお、必ずしもビットタイミング遅延部832、及び有効区間信号遅延部833を備える必要はなく、フリップフロップFF1の出力をビットbenとして用い、遅延ブロックDLY1の出力を同期化有効区間信号MREnとして用いるようにしてもよい。また、ビットタイミング遅延部832、及び有効区間信号遅延部833のいずれか一方のみを備えてもよい。

【0115】

また、テスト用データが、複数のデータが連結されたデータ列として構成されている例を示したが、必ずしもデータ列である必要はなく、テスト用データは、一つのデータ、例えば図5における「$F」であってもよく、「$0}であってもよく、その他のデータであってもよい。また、データ列も、$0、$0、$F、$0、$0、$0に限らず、$F、$F、$0、$F、$F、$Fであってもよく、その他のデータ列であってもよい。

【0116】

さらに、データ送信部81からデータ受信部82へ、転送クロック信号CKがそのまま送信される例を示したが、例えば図8に示すように、データ送信部81は、転送クロック信号CKの代わりに転送クロック信号CKのM+1倍の周期を有する送信クロック信号TxCKを送信するようにしてもよい。

【0117】

そして、データ受信部82は、データ送信部81から送信された送信クロック信号TxCKをM+1逓倍して転送クロック信号CKを生成し、PLL回路85へ供給する逓倍回路をさらに備えるようにしてもよい。

【0118】

近年、図8に示すように、複数ビット分で1周期となる送信クロック信号と同期してデータをシリアルに送信/受信する装置として、例えばナショナルセミコンダクタ社のDS90CR283/DS90CR284が知られている。DS90CR283/DS90CR284では、送信クロック信号TxCKの周波数が66MHzであり、1周期で7ビットをシリアル転送するため、送信クロック信号TxCKを7逓倍した転送クロック信号CKは、462MHz、1クロックが2.2nsecという、極めて高速となり、スキューの許容範囲が極めて狭い。

【0119】

本発明に係るデータ伝送回路によれば、スキューを調整することができるので、このようにスキューの許容範囲が極めて狭い高速のデータ転送技術を用いることが容易となる。

【0120】

また、本発明に係るデータ伝送回路を、画像形成装置内のデータ転送に用いる例を示したが、他の用途に用いてもよい。

【符号の説明】

【0121】

1 複合機

2,3 データ伝送回路

11 スキャナ部

12 露光ランプ

21 画像処理部

22 画像メモリ

31 プリンタ部

32 用紙搬送部

33 画像形成部

34 転写部

35 定着部

41 制御部

42 スキャナコントローラ

43 ファクシミリコントローラ

44 プリンタコントローラ

45 コピーコントローラ

46 データタイミング調整部

47 転送制御部

48 報知部

51 操作パネル部

52 表示部

53 操作キー部

61 ファクシミリ通信部

71 ネットワークI/F部

72 パラレルI/F部

73 シリアルI/F部

81 データ送信部

82 データ受信部

83−0〜83−N,83−n ビット受信部

84 デュアルポートRAM

85 PLL回路

811 テスト用データ送信部

812 通常データ送信部

831,MUX1,MUX2 マルチプレクサ

832 ビットタイミング遅延部

833 有効区間信号遅延部

BDLY0〜BDLYN,BDLYn ビット遅延切替信号

CK 転送クロック信号

CKA,CKB,CKC,CKD クロック信号

CKS0〜CKSN,CKSn クロック切替信号

DLY1,DLY2,DLY3,DLY4 遅延ブロック

Din,Dout データ

FF1,FF2,FF3 フリップフロップ

LY MD

MDLY0〜MDLYN,MDLYn 有効区間遅延切替信号

PI0〜PIN,PIn 入力ポート

PO 出力ポート

TxCK 送信クロック信号

b0〜bN,bn、be0〜beN,bn ビット

【技術分野】

【0001】

本発明は、多ビットのデータを転送するデータ伝送回路、及びこれを用いた画像形成装置に関する。

【背景技術】

【0002】

近年、大容量のデータを取り扱う情報処理装置、例えばデジタル複写機、プリンタ、ファクシミリ装置、及びこれらの複合機等において、例えば原稿画像を取得するスキャナと画像処理回路との間や、画像処理回路と画像形成回路との間等、装置内部でのデータの転送速度が高速化しているため、データビットや制御信号間のスキューが僅かに生じただけでデータ転送が困難になるという、不都合が生じている。

【0003】

このようなスキューは、電線長、バターン配線長、コネクタの接触抵抗のバラツキ、あるいは温度、湿度、素子劣化等による遅延量の変動など、種々の要素が影響して生じるので、スキューを発生させないことは困難である。

【0004】

そこで、データの転送に用いる同期クロックと、この同期クロックを反転させた反転クロックとにそれぞれ同期して受信データを取り込み、取り込まれた各受信データをパリティチェックしてパリティ異常が生じていない方の受信データを取得するようにする技術が知られている(例えば、特許文献1参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−46182号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1に記載の技術では、データにパリティビットを埋め込む必要があるため、データ量が増大してしまうという不都合があった。

【0007】

本発明の目的は、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減することができるデータ伝送回路、及びこれを用いた画像形成装置を提供することである。

【課題を解決するための手段】

【0008】

本発明に係るデータ伝送回路は、複数ビットから構成されるデータの各ビットを、所定の転送クロック信号と同期させて送信するデータ送信部と、前記データ送信部から出力された各ビットを、前記転送クロック信号と同期して受信するデータ受信部と、前記データ送信部及び前記データ受信部の動作を制御する制御部とを備え、前記データ受信部は、前記データの各ビットを、それぞれ1ビットずつ受信する複数のビット受信部と、前記各ビット受信部によって受信された複数のビットを記憶すると共に、当該記憶された複数のビットを、前記データとして外部から読出し可能に構成された記憶部とを含み、前記各ビット受信部は、前記転送クロック信号の位相を所定のクロックシフト量だけシフトさせて同期クロック信号を生成する同期クロック生成部と、当該各ビット受信部の同期クロック生成部によって生成された同期クロック信号と同期して、前記1ビットを受信し、前記記憶部へ出力する同期受信部とを含み、前記制御部は、前記データ送信部によって、予め設定されたテスト用データを前記転送クロック信号と同期させて送信させ、前記各ビット受信部により受信されて前記記憶部に記憶された複数ビットから構成されるデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各同期クロック生成部の前記クロックシフト量をそれぞれ設定するタイミング調整処理を実行するデータタイミング調整部と、前記データタイミング調整部によって前記各同期クロック生成部の前記クロックシフト量がそれぞれ設定された後、前記データ送信部によって、転送しようとする目的データを前記データ受信部へ送信させる転送制御部とを含む。

【0009】

この構成によれば、データ送信部から送信された転送クロック信号が、複数のビット受信部がそれぞれ備える同期クロック生成部によって、所定のクロックシフト量だけシフトされて各同期クロック信号が生成される。そして、データ送信部から送信されたテスト用データの各ビットが、各同期受信部によって、各ビット受信部の同期クロック信号と同期して受信され、記憶部で記憶される。

【0010】

そして、データタイミング調整部によって、記憶部で記憶されたデータとテスト用データとが比較され、当該読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各同期クロック生成部のクロックシフト量がそれぞれ設定される。さらに、データタイミング調整部によって各同期クロック生成部のクロックシフト量がそれぞれ設定された後、データ送信部によって、転送しようとする目的データがデータ受信部へ送信される。

【0011】

この場合、各ビットの受信に用いられる各同期クロック信号の位相が、当該各同期クロック信号と同期して各ビットをそれぞれ受信した場合にテスト用データの各ビットと一致するように、各同期クロック信号の位相が設定されるので、各ビットと各同期クロック信号との間のスキューを低減することができる。そして、このようにしてそれぞれ位相が設定された各同期クロック信号と同期して各ビットが受信されると、受信された各ビット間のタイミングが異なることになるが、記憶部に一旦記憶されることにより、タイミングの異なる各ビットをデータとして外部から読み出すことが可能となる。

【0012】

このようにして、各ビットと各ビットの同期クロック信号との間のスキューが調整された後、転送しようとする目的データがデータ送信部からデータ受信部へ送信され、外部から読出し可能に記憶部に記憶されるので、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減してデータを転送することができる。

【0013】

また、前記データ送信部は、前記データが有効であることを示す有効区間信号と共に前記データを送信し、前記各ビット受信部は、前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成し、前記記憶部へ出力する有効区間信号同期化部と、前記各同期受信部から前記1ビットを前記記憶部へ出力するタイミングを、当該各ビット受信部の同期クロック信号における所定クロック数分遅延させるビットタイミング遅延部とをさらに含み、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各ビットタイミング遅延部における前記所定クロック数を、さらに設定することが好ましい。

【0014】

この構成によれば、有効区間信号が各ビット信号より遅れてスキューが生じている場合であっても、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように各ビットが記憶部へ出力されるタイミングが遅延されて同期化有効区間信号と各ビットとのタイミングが調整されるので、記憶部において、同期化有効区間信号に基づいて、有効区間信号により有効であるとされているデータを正しく記憶することが可能となる。

【0015】

また、前記各ビット受信部は、前記有効区間信号同期化部から出力される同期化有効区間信号を遅延させる有効区間信号遅延部をさらに含み、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各有効区間信号遅延部における前記同期化有効区間信号の遅延量を、さらに設定することが好ましい。

【0016】

この構成によれば、各ビット信号が有効区間信号より遅れてスキューが生じている場合であっても、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように同期化有効区間信号が遅延されて同期化有効区間信号と各ビットとのタイミングが調整されるので、記憶部において、同期化有効区間信号に基づいて、有効区間信号により有効であるとされているデータを正しく記憶することが可能となる。

【0017】

また、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における同期クロック生成部の前記クロックシフト量を変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量をそれぞれ設定することが好ましい。

【0018】

この構成によれば、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各同期クロック生成部のクロックシフト量をそれぞれ設定することができる。

【0019】

また、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数とをそれぞれ設定することが好ましい。

【0020】

この構成によれば、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各クロックシフト量と各所定クロック数とをそれぞれ設定することができる。

【0021】

また、前記データタイミング調整部は、前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数と前記有効区間信号遅延部における前記遅延量とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数と前記各遅延量とをそれぞれ設定することが好ましい。

【0022】

この構成によれば、記憶部から読み出されるデータの各ビットがテスト用データの各ビットとそれぞれ一致するように、各クロックシフト量と各所定クロック数と各遅延量とをそれぞれ設定することができる。

【0023】

また、前記テスト用データは、複数のデータが連結されたデータ列であり、前記データ送信部は、前記データ列を、パラレルにされた複数のビット列とし、当該各ビット列を前記転送クロック信号と同期させてシリアルに送信すると共に、前記データ列が送信されている期間中、当該各ビット列が有効であることを示す有効区間信号を送信し、前記各同期受信部は、前記各ビット列をそれぞれ1ビットずつ順次受信して前記記憶部へ出力し、前記各ビット受信部は、前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成する有効区間信号同期化部をさらに備え、前記記憶部は、前記各ビット受信部の有効区間信号同期化部によって生成された同期化有効区間信号が前記有効であることを示す期間中、前記各ビット受信部の同期受信部から順次出力される前記1ビットを、前記各ビット受信部の同期クロック信号と同期して順次記憶することが好ましい。

【0024】

この構成によれば、データ送信部からデータ受信部へ、シリアルのビット列を複数パラレルに送信する態様において、スキューの影響を低減してデータを転送することができる。

【0025】

また、前記データ送信部は、前記複数ビットから構成されるデータを、前記転送クロック信号の整数倍の周期を有する送信クロック信号と同期してシリアルに送信し、前記データ受信部は、前記送信クロック信号を逓倍して前記転送クロック信号を生成し、前記同期クロック生成部へ供給する逓倍回路をさらに備えることが好ましい。

【0026】

この構成によれば、データ送信部からデータ受信部へ送信される同期用のクロック信号として、転送クロック信号より周波数の低い送信クロック信号を用いることができるので、クロック信号による不要輻射を低減することが容易となる。

【0027】

また、前記制御部は、前記データタイミング調整部による前記タイミング調整処理において、前記各同期クロック生成部の前記クロックシフト量をそれぞれ変化させても、前記記憶部から読み出されるデータの各ビットを前記テスト用データの各ビットとそれぞれ一致させることができない場合、異常の発生を報知する報知部をさらに備えることが好ましい。

【0028】

この構成によれば、スキューの調整が困難であって、データを正しく転送できないおそれがある場合に、ユーザに異常の発生を通知することが可能となる。

【0029】

また、本発明に係る画像形成装置は、画像データを取得する画像取得部と、前記画像取得部により取得された画像データに基づき用紙に画像を形成する画像形成部とを備え、前記画像取得部から前記画像形成部へ前記画像データを送信するデータ伝送経路の少なくとも一部に、上述のデータ伝送回路が用いられている。

【0030】

この構成によれば、画像形成装置内部のデータ伝送経路において、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減してデータを転送することができる。

【発明の効果】

【0031】

このような構成のデータ伝送回路、及び画像形成装置は、本来転送しようとしているデータのデータ量を増大させることなく、スキューの影響を低減してデータを転送することができる。

【図面の簡単な説明】

【0032】

【図1】本発明の一実施形態に係るデータ伝送回路を備えた画像形成装置の一例であるデジタル複合機の構成の一例を示すブロック図である。

【図2】図1に示すデータ伝送回路の構成の一例を示すブロック図である。

【図3】図2に示すビット受信部の構成の一例を示すブロック図である。

【図4】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図5】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図6】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図7】図1に示すデータ伝送回路の動作を説明するための説明図である。

【図8】変形例を説明するための説明図である。

【発明を実施するための形態】

【0033】

以下、本発明に係る実施形態を図面に基づいて説明する。なお、各図において同一の符号を付した構成は、同一の構成であることを示し、その説明を省略する。図1は、本発明の一実施形態に係るデータ伝送回路を備えた画像形成装置の一例であるデジタル複合機の構成の一例を示すブロック図である。

【0034】

複合機1は、スキャナ部11(画像取得部)、画像処理部21、プリンタ部31、制御部41、操作パネル部51、ファクシミリ通信部61(画像取得部)、ネットワークI/F部71(画像取得部)、パラレルI/F部72(画像取得部)、シリアルI/F部73(画像取得部)及びHDD(ハードディスクドライブ)74、及びデータ伝送回路2,3を備えて構成されている。

【0035】

そして、スキャナ部11、画像処理部21、プリンタ部31、制御部41、操作パネル部51及びファクシミリ通信部61によって、ファクシミリ機能が実現される。また、画像処理部21、プリンタ部31、制御部41、操作パネル部51、ネットワークI/F部71及びパラレルI/F部72によって、プリンタ機能が実現される。また、スキャナ部11、画像処理部21、プリンタ部31、制御部41及び操作パネル部51によって、複写機能が実現される。

【0036】

操作パネル部51は、使用者が複写機能、プリンタ機能、及びファクシミリ機能等に関する操作を行うために使用され、使用者による操作指示、例えば原稿画像の複写を指示する複写指示等を制御部41に与えるものである。操作パネル部51は、タッチパネル等を有する表示部52と、スタートキーやテンキー等を有する操作キー部53とを含む。

【0037】

表示部52は、例えばタッチパネルとLCD(Liquid Crystal Display)とを組み合わせたカラー表示可能なタッチパネルユニット等を有し、種々の操作画面を表示し、ユーザの入力操作を可能とする。表示部52は、例えばファクシミリ機能実行の際に、ユーザ選択、送信先選択、送信設定等に関する情報を表示するとともに、使用者が当該部分をタッチすることで種々の操作指示を入力するための操作ボタン等を表示する。操作キー部53は、使用者によるコピー実行開始指令、あるいはファクシミリ送信開始指令といった種々の指示入力を行うために用いられる。

【0038】

スキャナ部11は、原稿の画像を光学的に取得して画像データを生成するものである。スキャナ部11は、露光ランプ12及びCCD(電荷結合素子)13を含んでいる。スキャナ部11は、露光ランプ12によって原稿を照射し、その反射光をCCD13で受光することで、原稿画像を読み取る。そして、スキャナ部11は、読み取った画像に対応する画像データを、データ伝送回路2によって画像処理部21へ伝送させる。

【0039】

画像処理部21は、画像データに対する各種画像処理を行うものである。例えば、画像処理部21は、スキャナ部11で読み取られるなどして得られた画像データに対して、レベル補正、γ補正等の所定の補正処理、画像データの圧縮または伸張処理、拡大または縮小処理等の種々の画像処理(加工処理)を行う。

【0040】

画像処理部21は、データ伝送回路2に含まれる、後述のデュアルポートRAM84から画像データを読み出すことにより、スキャナ部11で得られた画像データを取得し、例えば画像メモリ22に記憶させる。また、画像処理部21は、例えば画像メモリ22に記憶された画像データを、データ伝送回路3によってプリンタ部31へ伝送させ、プリンタ部31により画像形成を行わせる。

【0041】

プリンタ部31は、画像処理部21からデータ伝送回路3によって伝送された画像データ、ネットワークI/F部71を介して外部のパーソナルコンピュータ等から受信した画像データ、及びファクシミリ通信部61によって外部のファクシミリ装置から受信したファックスデータ等の画像データに基づく画像を所定の記録紙に印刷するものである。

【0042】

プリンタ部31は、給紙カセット及び給紙ローラ等を有する用紙搬送部32、中間転写体ローラ、感光体ドラム、露光装置及び現像装置等を有する画像形成部33、転写ローラ等を有する転写部34並びに定着ローラ等を有する定着部35を含む。具体的には、用紙搬送部32は記録紙を画像形成部33へ搬送し、画像形成部33は上記画像データに対応するトナー像を形成し、転写部34はトナー像を記録紙に転写し、定着部35はトナー像を記録紙に定着させて画像を形成する。

【0043】

ファクシミリ通信部61は、スキャナ部11によって読み取られた原稿の画像データを電話回線等の通信回線611を介して他のファクシミリ装置へ送信したり、他のファクシミリ装置から送信されてきた画像データを受信したりするものである。

【0044】

ネットワークI/F部71は、ネットワークインターフェース(例えば10/100base-TX)等を用い、LAN(Local Area Network)やインターネット等の通信回線711を介して接続されたユーザ側サーバとの間での種々のデータの送受信を制御するものである。また、通信回線711にパーソナルコンピュータ等の図示しない1または複数の通信端末装置が接続されている場合に、ネットワークI/F部71はこれらの通信端末装置との間での種々のデータの送受信を制御する。例えば、ネットワークI/F部71は、スキャナ部11によって読み取られた原稿画像データを通信端末装置へ電子メールとして送信したり、プリンタ部31で印刷するために通信端末装置から送られた画像データを受信したりする。

【0045】

パラレルI/F部72は、例えばIEEE1284準拠等の高速双方向パラレルインターフェイスである。シリアルI/F部73は、例えばUSB(Universal Serial Bus)等のシリアルインターフェイスである。

【0046】

HDD74は、スキャナ部11によって読み取られた画像データや、ファクシミリ通信部61、ネットワークI/F部71、パラレルI/F部72、及びシリアルI/F部73によって外部から受信された画像データ、あるいは当該画像データに設定されている出力形式等を記憶するものである。

【0047】

制御部41は、例えば所定の演算処理を実行するCPU(Central Processing Unit)と、所定の制御プログラムが記憶されたROM(Read Only Memory)と、データを一時的に記憶するRAM(Random Access Memory)と、これらの周辺回路等とを備えて構成されている。そして、例えばROMやHDD74に記憶された制御プログラムを実行することにより、スキャナコントローラ42、ファクシミリコントローラ43、プリンタコントローラ44、コピーコントローラ45、データタイミング調整部46、転送制御部47、及び報知部48として機能する。

【0048】

ファクシミリコントローラ43は、ファクシミリ機能を実現するために用いられる各部の動作を制御するものである。プリンタコントローラ44は、プリンタ機能を実現するために用いられる各部の動作を制御するものである。コピーコントローラ45は、複写機能を実現するために用いられる各部の動作を制御するものである。

【0049】

データタイミング調整部46、及び転送制御部47は、データ伝送回路2,3の動作を後述のように制御する。この場合、データ伝送回路2(又はデータ伝送回路3)、データタイミング調整部46、転送制御部47、及び報知部48で請求項に係るデータ伝送回路が構成されている。なお、データタイミング調整部46、転送制御部47、及び報知部48は、各データ伝送回路にそれぞれ含んで構成されていてもよい。

【0050】

データ伝送回路2は、スキャナ部11から出力された画像データを画像処理部21へ高速伝送する。データ伝送回路3は、画像処理部21から出力された画像データを画像形成部33へ高速伝送する。図2は、図1に示すデータ伝送回路2の構成の一例を示すブロック図である。

【0051】

なお、データ伝送回路3については、データ伝送回路2と、データの転送元及び転送先が異なる以外は同様に構成されているため、図示を省略する。

【0052】

また、スキャナ部11から画像処理部21を介してプリンタ部31へ画像データを送信するデータ伝送経路に、データ伝送回路2,3を備える例を示したが、例えば、ファクシミリ通信部61、ネットワークI/F部71、パラレルI/F部72、及びシリアルI/F部73によって外部から受信された画像データを、HDD74を介してプリンタ部31へ送信するデータ伝送経路等、他の箇所にデータ伝送回路を備えていてもよい。

【0053】

以下、データ伝送回路2の構成について説明する。図2に示すデータ伝送回路2は、データ送信部81と、データ受信部82とを備えている。

【0054】

データ送信部81は、スキャナ部11の近傍に配設されている。また、データ送信部81は、テスト用データ送信部811と、通常データ送信部812とを備えている。

【0055】

テスト用データ送信部811は、データタイミング調整部46からの制御信号に応じて、予め設定されたテスト用データのビットb0〜bNからなるデータDoutと、ビットb0〜bNが有効な期間を示す有効区間信号MREとを、転送クロック信号CKと同期させてデータ受信部82へ送信する。

【0056】

通常データ送信部812は、転送制御部47からの制御信号に応じて、スキャナ部11から出力された画像データのビットb0〜bNと、ビットb0〜bNが有効な期間を示す有効区間信号MREとを、転送クロック信号CKと同期させてデータ受信部82へ送信する。

【0057】

データ受信部82は、画像処理部21の近傍に配設されている。そして、データ受信部82は、N+1個のビット受信部83−0〜83−Nと、デュアルポートRAM(Random Access Memory)84(記憶部)と、PLL(Phase Locked Loop)回路85とを備えている。

【0058】

PLL(Phase Locked Loop)回路85は、例えば、転送クロック信号CKの位相を0°、90°、180°、270°シフトさせた4つのクロック信号CKA,CKB、CKC、CKDを生成し、ビット受信部83−0〜83−Nへ出力する。(クロック信号CKAは転送クロック信号CKと等しい。)

デュアルポートRAM84は、ビット受信部83−0〜83−Nの出力データを受け付けるN+1個の入力ポートPI0〜PINを備えている。そして、デュアルポートRAM84は、記憶しているデータをデータ受信部82の外部に接続された画像処理部21へ出力する出力ポートPOを備えている。

【0059】

また、n番目の入力ポートPInは、n番目のビット受信部83−nから出力されるビットben、同期クロック信号CKn、及び同期化有効区間信号MREnを受け付ける。以下、任意のn番目のビットに対応する構成及び信号を、符号にnを付して示す。

【0060】

そして、デュアルポートRAM84は、各入力ポートPInによって受け付けられたビットben、同期クロック信号CKn、及び同期化有効区間信号MREnに基づいて、同期化有効区間信号MREnが有効であることを示す期間中、ビットbenとして順次出力される1ビットデータを、同期クロック信号CKnと同期して順次記憶する。

【0061】

また、デュアルポートRAM84は、このようにして記憶されたビットbe0〜beNによって構成されるデータDinを、画像処理部21から出力された同期クロック信号SCLKと読出要求信号REとに応じて、出力ポートPOから出力するようになっている。

【0062】

デュアルポートRAM84は、例えば、同期化有効区間信号MREnが有効であることを示す期間中、ビットbenとして順次出力される1ビットデータを、同期クロック信号CKnと同期して順次記憶するN+1個のFIFO(First-In First-Out)を並列接続し、同期クロック信号SCLKと読出要求信号REとを用いて各FIFOからデータを出力させる構成としてもよい。

【0063】

図3は、図2に示すビット受信部83−0〜83−Nの構成の一例を示すブロック図である。ビット受信部83−0〜83−Nは同様に構成されているので、図3においては任意の(n番目の)ビット受信部83−nで代表させて記載している。

【0064】

図3に示すビット受信部83−nは、例えば、マルチプレクサ831(同期クロック生成部)と、フリップフロップFF1(同期受信部)と、ビットタイミング遅延部832と、遅延ブロックDLY1(有効区間信号同期化部)と、有効区間信号遅延部833とを備えている。

【0065】

また、ビットタイミング遅延部832は、フリップフロップFF2,FF3と、マルチプレクサMUX1とを備えている。有効区間信号遅延部833は、遅延ブロックDLY2,DLY3,DLY4と、マルチプレクサMUX2とを備えている。

【0066】

マルチプレクサ831は、制御部41から出力されるクロック切替信号CKSnに応じて、PLL回路85から出力されたクロック信号CKA,CKB,CKC,CKDのうち一つを同期クロック信号CKnとして選択し、フリップフロップFF1(同期受信部)、ビットタイミング遅延部832、遅延ブロックDLY1、有効区間信号遅延部833、及びデュアルポートRAM84の入力ポートPInへ出力する。

【0067】

これによって、転送クロック信号CKからの同期クロック信号CKnのシフト量(クロックシフト量)が、0°、90°、180°、270°のいずれかに設定されるようになっている。

【0068】

フリップフロップFF1は、データ送信部81から出力されたビットbnを、同期クロック信号CKnと同期してラッチし、フリップフロップFF2及びマルチプレクサMUX1へ出力する。

【0069】

フリップフロップFF2は、フリップフロップFF1の出力信号を、同期クロック信号CKnと同期してラッチすることで同期クロック信号CKnの1周期分遅延させ、フリップフロップFF3及びマルチプレクサMUX1へ出力する。

【0070】

フリップフロップFF3は、フリップフロップFF2の出力信号を、同期クロック信号CKnと同期してラッチすることで同期クロック信号CKnの1周期分遅延させ、マルチプレクサMUX1へ出力する。

【0071】

マルチプレクサMUX1は、制御部41から出力されるビット遅延切替信号BDLYnに応じて、フリップフロップFF1,FF2,FF3の出力信号のうち一つを選択し、第nビットのビットbenとしてデュアルポートRAM84へ出力する。

【0072】

これにより、ビット遅延切替信号BDLYnに応じて、ビットbenの遅延時間が設定されるようになっている。

【0073】

遅延ブロックDLY1は、例えば、例えばデータ送信部81から出力された有効区間信号MREを、同期クロック信号CKnと同期してラッチするフリップフロップ回路と、フリップフロップ回路でラッチされた信号を、ビットbenとの関係でセットアップ、ホールドタイムを確保する等のタイミング調整をするための遅延回路とを備えて構成されている。

【0074】

そして、遅延ブロックDLY1は、有効区間信号MREを、同期クロック信号CKnと同期してラッチし、タイミング調整した後に遅延ブロックDLY2及びマルチプレクサMUX2へ出力する。

【0075】

遅延ブロックDLY2,DLY3,DLY4は、遅延ブロックDLY1と同様に構成されている。そして、遅延ブロックDLY2は、遅延ブロックDLY1の出力信号を同期クロック信号CKnと同期してラッチし、タイミング調整した後に遅延ブロックDLY3及びマルチプレクサMUX2へ出力する。

【0076】

遅延ブロックDLY3は、遅延ブロックDLY2の出力信号を同期クロック信号CKnと同期してラッチし、タイミング調整した後に遅延ブロックDLY4及びマルチプレクサMUX2へ出力する。

【0077】

遅延ブロックDLY4は、遅延ブロックDLY3の出力信号を同期クロック信号CKnと同期してラッチし、タイミング調整した後にマルチプレクサMUX2へ出力する。

【0078】

なお、以下の説明においては、説明を簡単にするため、遅延ブロックDLY1,DLY2,DLY3,DLY4は、タイミング調整することなく同期クロック信号CKnと同期してラッチした信号を出力するものとしている。

【0079】

マルチプレクサMUX2は、制御部41から出力される有効区間遅延切替信号MDLYnに応じて、遅延ブロックDLY1,DLY2,DLY3,DLY4の出力信号のうち一つを選択し、第nビット用の同期化有効区間信号MREnとしてデュアルポートRAM84へ出力する。

【0080】

これにより、有効区間遅延切替信号MDLYnに応じて、同期化有効区間信号MREnの遅延時間が設定されるようになっている。

【0081】

そして、このようにしてビット受信部83−0〜83−Nから出力されたビットbe0〜beNが、データDinとしてデュアルポートRAM84によって記憶されるようになっている。

【0082】

データタイミング調整部46は、テスト用データ送信部811によって、予め設定されたテスト用データのビットb0〜bNを転送クロック信号CKと同期させて送信させる。また、このテスト用データと同じデータが、例えば制御部41におけるROMやHDD74に予め記憶されている。

【0083】

そして、データタイミング調整部46は、ビット受信部83−0〜83−Nにより受信されてデュアルポートRAM84にデータDinとして記憶されたデータの各ビットを読み出して、ROM等に記憶されているテスト用データの各ビットとそれぞれ比較し、データDinの各ビットがこのテスト用データの各ビットと一致するように、クロック切替信号CKS0〜CKSN、ビット遅延切替信号BDLY0〜BDLYN、及び有効区間遅延切替信号MDLY0〜MDLYNをビット受信部83−0〜83−Nへ出力し、同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間をそれぞれ設定するタイミング調整処理を実行する。

【0084】

転送制御部47は、データタイミング調整部46によって同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間がそれぞれ設定された後、通常データ送信部812によって、転送しようとする目的データである画像データを、データ受信部82へ送信させる。

【0085】

報知部48は、データタイミング調整部46のタイミング調整処理において、同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間を調整してもなお、データDinの各ビットをテスト用データの各ビットと一致させることができなかった場合、異常が発生した旨のメッセージを表示部52に表示させる。

【0086】

次に、上述のように構成された複合機1及びデータ伝送回路2の動作について説明する。図4〜図7は、図1に示す複合機1及びデータ伝送回路2の動作を説明するための説明図である。

【0087】

まず、例えば複合機1が起動されたときや、あるいは定期的なタイミングで、データタイミング調整部46が、テスト用データ送信部811によって、テストデータをデータDoutとして送信させる。以下、ビット番号0〜Nを、任意の番号nで代表して説明する。

【0088】

テスト用データ送信部811は、初期設定として、クロック切替信号CKSn、ビット遅延切替信号BDLYn、及び有効区間遅延切替信号MDLYnを用いて、マルチプレクサ831により例えばクロック信号CKAを同期クロック信号CKnとして選択させ、マルチプレクサMUX1により例えばフリップフロップFF1の出力信号をビットbenとして選択させ、マルチプレクサMUX1により例えば遅延ブロックDLY1の出力信号を同期化有効区間信号MREnとして選択させる。

【0089】

図4は、テスト用データ送信部811から出力されたデータDoutと、データDoutの各ビットb0〜b3と、転送クロック信号CKとの一例を示している。図4では、テストデータは、16進数の$0、$0、$F、$0、$0、$0という、5つのデータが連結されたデータ列にされている。以下、16進数に「$」を付して表すこととする。

【0090】

そして、このデータ列が送信されている期間中、当該データ(ビットb0〜b3)が有効であることを示すべく、有効区間信号MREが例えばハイレベルにされている。

【0091】

また、ビットb0〜b3は、転送クロック信号CKと同期して出力されている。

【0092】

ところで、スキャナ部11と画像処理部21とは、複合機1の筐体内で離れた位置に配設されているため、ビットb0〜b3、転送クロック信号CK、及び有効区間信号MREは、データ送信部81から、ケーブル等を介してデータ受信部82へ送信されることとなる。そうすると、ケーブルの長さや浮遊容量、あるいはデータ送信部81における出力バッファの特性バラツキ等の影響によって、これらの信号がデータ受信部82で受信される際には各信号間に、例えば図5に示すようなスキューが生じることとなる。

【0093】

この状態で、データ受信部82によって、転送クロック信号CKと同期してビットb0〜b3が受信される。そうすると、転送クロック信号CKと同位相のクロック信号CKA(位相差0°)と、ビットbn(ビットb0〜b3のうち任意のビット)との間にずれが生じ、クロック信号CKAの立上りタイミング(タイミングT1)とビットbnとが同期しないから、ビット受信部83−nにおけるフリップフロップFF1では、正しくビットbnをラッチすることができない。

【0094】

そして、フリップフロップFF1から出力されたビット値がマルチプレクサMUX1によってビットbenとしてデュアルポートRAM84に記憶される。そうすると、ビットbenとして正しいビット値が得られないから、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、テスト用データにおけるnビット目のビット列である「001000」と一致しない。

【0095】

テスト用データ送信部811は、さらに、クロック切替信号CKSnを用いて、マルチプレクサ831により例えばクロック信号CKB,CKC,CKDの順に、マルチプレクサ831で同期クロック信号CKnとして選択させるクロック信号を順次変化させながら、テスト用データ送信部811によるテスト用データのデータ列の送信と、データ受信部82による当該データ列の受信、及びデュアルポートRAM84への書込を繰り返させる。

【0096】

そうすると、図6のタイミングT2,T3,T4に示すように、クロック信号CKB,CKC,CKDの立上りタイミングでは、ビットbnは安定状態になっており、フリップフロップFF1で正しくビット値をラッチすることが可能となっている。そうすると、ビットbnを正しく受信できるタイミングが、クロック信号CKB,CKC,CKDと同期するタイミング、すなわち転送クロック信号CKとの位相差が90°、180°、270°のタイミングで存在することとなる。

【0097】

この場合、データタイミング調整部46は、正しいビット値を読み出せた90°、180°、270°のタイミングのうち、中央の180°に対応するクロック信号CKCを選択し、マルチプレクサ831により同期クロック信号CKnとして選択させるように、クロック切替信号CKSnを設定する。

【0098】

そうすると、図6に示す例では、スキューにより有効区間信号MREがビットbnより遅れており、ビット受信部83−nでクロック信号CKCと同期してラッチされた同期化有効区間信号MREnは、図6(a)に示すように、立上りタイミングが図6(b)に示すクロック信号CKCで同期化されたビットbnの先頭より遅れたタイミングT5になってしまう。

【0099】

そうすると、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、例えば図6(a)(b)におけるビットbnの同期化有効区間信号MREnがハイレベルの期間のデータである「01000X」(Xは不定値)となって、テスト用データにおけるnビット目のビット列である「001000」と一致しない。

【0100】

そこで、テスト用データ送信部811は、さらに、ビットタイミング遅延部832を用いて、マルチプレクサMUX1によって、ビットbnの遅延時間を変化させる。図6(c)に示す例では、マルチプレクサMUX1によって、フリップフロップFF2の出力信号を選択させることで、ビットbnを、同期クロック信号CKn(クロック信号CKC)の1クロック分遅延させている。

【0101】

これにより、同期化有効区間信号MREnと、ビットbnとのタイミングが正しく設定されて、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、「001000」となって、テスト用データにおけるnビット目のビット列である「001000」と一致する。

【0102】

このようにして、ビット受信部83−0〜83−Nによって、各ビットのスキューがそれぞれ調整されて、データ送信部81からデータ受信部82へ、正しくデータを転送することが可能となる。

【0103】

ここで、図6においては、スキューによって、同期化有効区間信号MREnがビットbnより遅れる例を示したが、ビットbnが同期化有効区間信号MREnより遅れる場合、ビットタイミング遅延部832を用いてもスキューを調整することができない。

【0104】

図7は、ビットbnが同期化有効区間信号MREnより遅れる場合の動作を示す説明図である。まず、図7においては、タイミングT12,T13,T14におけるクロック信号CKA,CKB,CKCの立上りタイミングでビットbnが安定状態になっている。

【0105】

従って、図6の場合と同様の動作によって、データタイミング調整部46は、正しいビット値を読み出せる0°、90°、180°のタイミングのうち、中央の90°に対応するクロック信号CKBを選択し、マルチプレクサ831により同期クロック信号CKnとして選択させるように、クロック切替信号CKSnを設定する。

【0106】

そうすると、図7に示す例では、ビット受信部83−nでクロック信号CKBと同期してラッチされた同期化有効区間信号MREnは、図7(a)に示すように、立上りタイミングが図7(b)に示すクロック信号CKBで同期化されたビットbnの先頭より1クロック進んだタイミングT11になってしまう。

【0107】

そうすると、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、例えば図7(a)(b)におけるビットbnの同期化有効区間信号MREnがハイレベルの期間のデータである「X00100」(Xは不定値)となって、テスト用データにおけるnビット目のビット列である「001000」と一致しない。

【0108】

そこで、テスト用データ送信部811は、さらに、有効区間信号遅延部833を用いて、マルチプレクサMUX2によって、同期化有効区間信号MREnの遅延時間を変化させる。図7(c)に示す例では、マルチプレクサMUX2によって、遅延ブロックDLY2の出力信号を選択させることで、同期化有効区間信号MREnを、同期クロック信号CKn(クロック信号CKC)の1クロック分遅延させている。

【0109】

これにより、同期化有効区間信号MREnと、ビットbnとのタイミングが正しく設定されて、デュアルポートRAM84に記憶されるデータ列におけるn番目のビット列は、「001000」となって、テスト用データにおけるnビット目のビット列である「001000」と一致する。

【0110】

このようにして、ビットbnが同期化有効区間信号MREnより遅れる場合であっても、ビット受信部83−0〜83−Nによって、各ビットのスキューがそれぞれ調整されて、データ送信部81からデータ受信部82へ、正しくデータを転送することが可能となる。

【0111】

そして、転送制御部47は、データタイミング調整部46によって同期クロック信号CK0〜CKNの位相シフト量、ビットbe0〜beNの遅延時間、及び同期化有効区間信号MRE0〜MRENの遅延時間がそれぞれ設定された後、通常データ送信部812によって、転送しようとする目的データである画像データを、データ受信部82へ送信させるので、画像データをスキャナ部11から画像処理部21へ、正しく転送することが可能となる。

【0112】

なお、データビット列に有効区間信号が埋め込まれている場合には、同期クロック信号CK0〜CKNの位相シフト量を調整することで、同時にデータビットと有効区間信号との関係も調整されることとなる。

【0113】

また、背景技術のように、データにパリティビットを埋め込む必要がないため、データ量を増大させることなく、スキューの影響を低減することができる。

【0114】

なお、必ずしもビットタイミング遅延部832、及び有効区間信号遅延部833を備える必要はなく、フリップフロップFF1の出力をビットbenとして用い、遅延ブロックDLY1の出力を同期化有効区間信号MREnとして用いるようにしてもよい。また、ビットタイミング遅延部832、及び有効区間信号遅延部833のいずれか一方のみを備えてもよい。

【0115】

また、テスト用データが、複数のデータが連結されたデータ列として構成されている例を示したが、必ずしもデータ列である必要はなく、テスト用データは、一つのデータ、例えば図5における「$F」であってもよく、「$0}であってもよく、その他のデータであってもよい。また、データ列も、$0、$0、$F、$0、$0、$0に限らず、$F、$F、$0、$F、$F、$Fであってもよく、その他のデータ列であってもよい。

【0116】

さらに、データ送信部81からデータ受信部82へ、転送クロック信号CKがそのまま送信される例を示したが、例えば図8に示すように、データ送信部81は、転送クロック信号CKの代わりに転送クロック信号CKのM+1倍の周期を有する送信クロック信号TxCKを送信するようにしてもよい。

【0117】

そして、データ受信部82は、データ送信部81から送信された送信クロック信号TxCKをM+1逓倍して転送クロック信号CKを生成し、PLL回路85へ供給する逓倍回路をさらに備えるようにしてもよい。

【0118】

近年、図8に示すように、複数ビット分で1周期となる送信クロック信号と同期してデータをシリアルに送信/受信する装置として、例えばナショナルセミコンダクタ社のDS90CR283/DS90CR284が知られている。DS90CR283/DS90CR284では、送信クロック信号TxCKの周波数が66MHzであり、1周期で7ビットをシリアル転送するため、送信クロック信号TxCKを7逓倍した転送クロック信号CKは、462MHz、1クロックが2.2nsecという、極めて高速となり、スキューの許容範囲が極めて狭い。

【0119】

本発明に係るデータ伝送回路によれば、スキューを調整することができるので、このようにスキューの許容範囲が極めて狭い高速のデータ転送技術を用いることが容易となる。

【0120】

また、本発明に係るデータ伝送回路を、画像形成装置内のデータ転送に用いる例を示したが、他の用途に用いてもよい。

【符号の説明】

【0121】

1 複合機

2,3 データ伝送回路

11 スキャナ部

12 露光ランプ

21 画像処理部

22 画像メモリ

31 プリンタ部

32 用紙搬送部

33 画像形成部

34 転写部

35 定着部

41 制御部

42 スキャナコントローラ

43 ファクシミリコントローラ

44 プリンタコントローラ

45 コピーコントローラ

46 データタイミング調整部

47 転送制御部

48 報知部

51 操作パネル部

52 表示部

53 操作キー部

61 ファクシミリ通信部

71 ネットワークI/F部

72 パラレルI/F部

73 シリアルI/F部

81 データ送信部

82 データ受信部

83−0〜83−N,83−n ビット受信部

84 デュアルポートRAM

85 PLL回路

811 テスト用データ送信部

812 通常データ送信部

831,MUX1,MUX2 マルチプレクサ

832 ビットタイミング遅延部

833 有効区間信号遅延部

BDLY0〜BDLYN,BDLYn ビット遅延切替信号

CK 転送クロック信号

CKA,CKB,CKC,CKD クロック信号

CKS0〜CKSN,CKSn クロック切替信号

DLY1,DLY2,DLY3,DLY4 遅延ブロック

Din,Dout データ

FF1,FF2,FF3 フリップフロップ

LY MD

MDLY0〜MDLYN,MDLYn 有効区間遅延切替信号

PI0〜PIN,PIn 入力ポート

PO 出力ポート

TxCK 送信クロック信号

b0〜bN,bn、be0〜beN,bn ビット

【特許請求の範囲】

【請求項1】

複数ビットから構成されるデータの各ビットを、所定の転送クロック信号と同期させて送信するデータ送信部と、

前記データ送信部から出力された各ビットを、前記転送クロック信号と同期して受信するデータ受信部と、

前記データ送信部及び前記データ受信部の動作を制御する制御部とを備え、

前記データ受信部は、

前記データの各ビットを、それぞれ1ビットずつ受信する複数のビット受信部と、

前記各ビット受信部によって受信された複数のビットを記憶するとと共に、当該記憶された複数のビットを、前記データとして外部から読出し可能に構成された記憶部とを含み、

前記各ビット受信部は、

前記転送クロック信号の位相を所定のクロックシフト量だけシフトさせて同期クロック信号を生成する同期クロック生成部と、

当該各ビット受信部の同期クロック生成部によって生成された同期クロック信号と同期して、前記1ビットを受信し、前記記憶部へ出力する同期受信部とを含み、

前記制御部は、

前記データ送信部によって、予め設定されたテスト用データを前記転送クロック信号と同期させて送信させ、前記各ビット受信部により受信されて前記記憶部に記憶された複数ビットから構成されるデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各同期クロック生成部の前記クロックシフト量をそれぞれ設定するタイミング調整処理を実行するデータタイミング調整部と、

前記データタイミング調整部によって前記各同期クロック生成部の前記クロックシフト量がそれぞれ設定された後、前記データ送信部によって、転送しようとする目的データを前記データ受信部へ送信させる転送制御部とを含むこと

を特徴とするデータ伝送回路。

【請求項2】

前記データ送信部は、

前記データが有効であることを示す有効区間信号と共に前記データを送信し、

前記各ビット受信部は、

前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成し、前記記憶部へ出力する有効区間信号同期化部と、

前記各同期受信部から前記1ビットを前記記憶部へ出力するタイミングを、当該各ビット受信部の同期クロック信号における所定クロック数分遅延させるビットタイミング遅延部とをさらに含み、

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各ビットタイミング遅延部における前記所定クロック数を、さらに設定すること

を特徴とする請求項1記載のデータ伝送回路。

【請求項3】

前記各ビット受信部は、

前記有効区間信号同期化部から出力される同期化有効区間信号を遅延させる有効区間信号遅延部をさらに含み、

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各有効区間信号遅延部における前記同期化有効区間信号の遅延量を、さらに設定すること

を特徴とする請求項2記載のデータ伝送回路。

【請求項4】

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における同期クロック生成部の前記クロックシフト量を変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量をそれぞれ設定すること

を特徴とする請求項1に記載のデータ伝送回路。

【請求項5】

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数とをそれぞれ設定すること

を特徴とする請求項2記載のデータ伝送回路。

【請求項6】

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数と前記有効区間信号遅延部における前記遅延量とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数と前記各遅延量とをそれぞれ設定すること

を特徴とする請求項3記載のデータ伝送回路。

【請求項7】

前記テスト用データは、

複数のデータが連結されたデータ列であり、

前記データ送信部は、

前記データ列を、パラレルにされた複数のビット列とし、当該各ビット列を前記転送クロック信号と同期させてシリアルに送信すると共に、前記データ列が送信されている期間中、当該各ビット列が有効であることを示す有効区間信号を送信し、

前記各同期受信部は、

前記各ビット列をそれぞれ1ビットずつ順次受信して前記記憶部へ出力し、

前記各ビット受信部は、

前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成する有効区間信号同期化部をさらに備え、

前記記憶部は、

前記各ビット受信部の有効区間信号同期化部によって生成された同期化有効区間信号が前記有効であることを示す期間中、前記各ビット受信部の同期受信部から順次出力される前記1ビットを、前記各ビット受信部の同期クロック信号と同期して順次記憶すること

を特徴とする請求項1〜6のいずれか1項に記載のデータ伝送回路。

【請求項8】

前記データ送信部は、

前記複数ビットから構成されるデータを、前記転送クロック信号の整数倍の周期を有する送信クロック信号と同期してシリアルに送信し、

前記データ受信部は、

前記送信クロック信号を逓倍して前記転送クロック信号を生成し、前記同期クロック生成部へ供給する逓倍回路をさらに備えること

を特徴とする請求項1〜7のいずれか1項に記載のデータ伝送回路。

【請求項9】

前記制御部は、

前記データタイミング調整部による前記タイミング調整処理において、

前記各同期クロック生成部の前記クロックシフト量をそれぞれ変化させても、前記記憶部から読み出されるデータの各ビットを前記テスト用データの各ビットとそれぞれ一致させることができない場合、異常の発生を報知する報知部をさらに備えること

を特徴とする請求項1記載のデータ伝送回路。

【請求項10】

画像データを取得する画像取得部と、

前記画像取得部により取得された画像データに基づき用紙に画像を形成する画像形成部とを備え、

前記画像取得部から前記画像形成部へ前記画像データを送信するデータ伝送経路の少なくとも一部に、請求項1〜9のいずれか1項に記載のデータ伝送回路が用いられていること

を特徴とする画像形成装置。

【請求項1】

複数ビットから構成されるデータの各ビットを、所定の転送クロック信号と同期させて送信するデータ送信部と、

前記データ送信部から出力された各ビットを、前記転送クロック信号と同期して受信するデータ受信部と、

前記データ送信部及び前記データ受信部の動作を制御する制御部とを備え、

前記データ受信部は、

前記データの各ビットを、それぞれ1ビットずつ受信する複数のビット受信部と、

前記各ビット受信部によって受信された複数のビットを記憶するとと共に、当該記憶された複数のビットを、前記データとして外部から読出し可能に構成された記憶部とを含み、

前記各ビット受信部は、

前記転送クロック信号の位相を所定のクロックシフト量だけシフトさせて同期クロック信号を生成する同期クロック生成部と、

当該各ビット受信部の同期クロック生成部によって生成された同期クロック信号と同期して、前記1ビットを受信し、前記記憶部へ出力する同期受信部とを含み、

前記制御部は、

前記データ送信部によって、予め設定されたテスト用データを前記転送クロック信号と同期させて送信させ、前記各ビット受信部により受信されて前記記憶部に記憶された複数ビットから構成されるデータを読み出して前記テスト用データと比較し、当該読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各同期クロック生成部の前記クロックシフト量をそれぞれ設定するタイミング調整処理を実行するデータタイミング調整部と、

前記データタイミング調整部によって前記各同期クロック生成部の前記クロックシフト量がそれぞれ設定された後、前記データ送信部によって、転送しようとする目的データを前記データ受信部へ送信させる転送制御部とを含むこと

を特徴とするデータ伝送回路。

【請求項2】

前記データ送信部は、

前記データが有効であることを示す有効区間信号と共に前記データを送信し、

前記各ビット受信部は、

前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成し、前記記憶部へ出力する有効区間信号同期化部と、

前記各同期受信部から前記1ビットを前記記憶部へ出力するタイミングを、当該各ビット受信部の同期クロック信号における所定クロック数分遅延させるビットタイミング遅延部とをさらに含み、

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各ビットタイミング遅延部における前記所定クロック数を、さらに設定すること

を特徴とする請求項1記載のデータ伝送回路。

【請求項3】

前記各ビット受信部は、

前記有効区間信号同期化部から出力される同期化有効区間信号を遅延させる有効区間信号遅延部をさらに含み、

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットとそれぞれ一致するように、前記各有効区間信号遅延部における前記同期化有効区間信号の遅延量を、さらに設定すること

を特徴とする請求項2記載のデータ伝送回路。

【請求項4】

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における同期クロック生成部の前記クロックシフト量を変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量をそれぞれ設定すること

を特徴とする請求項1に記載のデータ伝送回路。

【請求項5】

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数とをそれぞれ設定すること

を特徴とする請求項2記載のデータ伝送回路。

【請求項6】

前記データタイミング調整部は、

前記タイミング調整処理において、前記記憶部に記憶されたデータの各ビットと前記テスト用データの各ビットとが一致しなかった場合、一致しなかったビットに該当する前記ビット受信部における、前記同期クロック生成部の前記クロックシフト量と前記ビットタイミング遅延部の前記所定クロック数と前記有効区間信号遅延部における前記遅延量とのうち少なくとも一つを変化させた後、再び前記タイミング調整処理を実行することにより、前記記憶部から読み出されるデータの各ビットが前記テスト用データの各ビットと一致するように、前記各クロックシフト量と前記各所定クロック数と前記各遅延量とをそれぞれ設定すること

を特徴とする請求項3記載のデータ伝送回路。

【請求項7】

前記テスト用データは、

複数のデータが連結されたデータ列であり、

前記データ送信部は、

前記データ列を、パラレルにされた複数のビット列とし、当該各ビット列を前記転送クロック信号と同期させてシリアルに送信すると共に、前記データ列が送信されている期間中、当該各ビット列が有効であることを示す有効区間信号を送信し、

前記各同期受信部は、

前記各ビット列をそれぞれ1ビットずつ順次受信して前記記憶部へ出力し、

前記各ビット受信部は、

前記データ送信部から送信された有効区間信号を、当該各ビット受信部の同期クロック信号と同期させた同期化有効区間信号を生成する有効区間信号同期化部をさらに備え、

前記記憶部は、

前記各ビット受信部の有効区間信号同期化部によって生成された同期化有効区間信号が前記有効であることを示す期間中、前記各ビット受信部の同期受信部から順次出力される前記1ビットを、前記各ビット受信部の同期クロック信号と同期して順次記憶すること

を特徴とする請求項1〜6のいずれか1項に記載のデータ伝送回路。

【請求項8】

前記データ送信部は、

前記複数ビットから構成されるデータを、前記転送クロック信号の整数倍の周期を有する送信クロック信号と同期してシリアルに送信し、

前記データ受信部は、

前記送信クロック信号を逓倍して前記転送クロック信号を生成し、前記同期クロック生成部へ供給する逓倍回路をさらに備えること

を特徴とする請求項1〜7のいずれか1項に記載のデータ伝送回路。

【請求項9】

前記制御部は、

前記データタイミング調整部による前記タイミング調整処理において、

前記各同期クロック生成部の前記クロックシフト量をそれぞれ変化させても、前記記憶部から読み出されるデータの各ビットを前記テスト用データの各ビットとそれぞれ一致させることができない場合、異常の発生を報知する報知部をさらに備えること

を特徴とする請求項1記載のデータ伝送回路。

【請求項10】

画像データを取得する画像取得部と、

前記画像取得部により取得された画像データに基づき用紙に画像を形成する画像形成部とを備え、

前記画像取得部から前記画像形成部へ前記画像データを送信するデータ伝送経路の少なくとも一部に、請求項1〜9のいずれか1項に記載のデータ伝送回路が用いられていること

を特徴とする画像形成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2010−191872(P2010−191872A)

【公開日】平成22年9月2日(2010.9.2)

【国際特許分類】

【出願番号】特願2009−37994(P2009−37994)

【出願日】平成21年2月20日(2009.2.20)

【出願人】(000006150)京セラミタ株式会社 (13,173)

【Fターム(参考)】

【公開日】平成22年9月2日(2010.9.2)

【国際特許分類】

【出願日】平成21年2月20日(2009.2.20)

【出願人】(000006150)京セラミタ株式会社 (13,173)

【Fターム(参考)】

[ Back to top ]