データ伝送方法

【目的】 メインCPUとサブCPU間のデータ伝送に関して、サブCPUのI/O制御効率の向上を目的とするものである。

【構成】 メインCPU20からサブCPU24,26,・・へは、1キャラクタハンドシェイクでデータ伝送し、サブCPU24,26,・・からメインCPU20へは、ブロック単位でデータ伝送する。従って、サブCPU24,26,・・は、メインCPU20との伝送専有時間を短くし、I/O32,34,・・の制御効率を向上することができる。

【構成】 メインCPU20からサブCPU24,26,・・へは、1キャラクタハンドシェイクでデータ伝送し、サブCPU24,26,・・からメインCPU20へは、ブロック単位でデータ伝送する。従って、サブCPU24,26,・・は、メインCPU20との伝送専有時間を短くし、I/O32,34,・・の制御効率を向上することができる。

【発明の詳細な説明】

【0001】

【産業上の利用分野】この発明は、メインCPUとサブCPU間のデータ伝送方法に関し、特に、サブCPUのI/O制御効率の向上に関するものである。

【0002】

【従来の技術】複数の店舗を有して大量販売するような販売業などにおいては、メインCPUと複数のサブCPU間を通信ライン上で接続してデータ伝送する情報管理システムを採用する場合がある。この場合、サブCPUは、販売情報などのデータをカードリーダやプリンタに出力させるなど、複数のI/Oを制御しており、並行して、メインCPUからの指令を受けて、カードリーダやプリンタから出力されるデータをメインCPUに伝送する。このような従来のデータ伝送方法の状態を図3に示す。メインCPU2と複数のサブCPU4〜10およびI/O12〜18が放射状に接続されている。

【0003】図3において、メインCPU2と各サブCPU4〜10間は、POL/SEL方式で通信を行っている。この時、サブCPU4〜10は、メインCPU2へのデータ伝送とI/O制御12〜18との並行処理を行っている。また、メインCPU2とサブCPU4〜10との間の通信方式は、両方向伝送可能であるが伝送時は一方向のみである半二重ハンドシェイク方式であって、1キャラクタ単位のシリアル応答方式である。この伝送データ構成を図4に示す。1キャラクタは、スタートビット40(1ビット),データビット42(8ビット),パリティビット44(1ビット),ストップビット46(1ビット)の11ビットにより構成される。

【0004】図5aに、従来のメインCPU2からサブCPU4〜10への伝送制御手順を示す。図6には、ここで使用される伝送制御コード表を示す。

【0005】まず、メインCPU2からサブCPU4〜10へSEL(セレクティング)を行う。例えば、サブCPU4がデータを受信を受諾できる時は、ACK(肯定応答)を返送する。受信を受諾できない時には、NAK(否定応答)を返送する。サブCPU4のACKの返送により、データリンクが確立する。

【0006】次に、メインCPU2は、LENをサブCPU4に送信する。これを受信したサブCPU4のDACK(データに対する応答)の返送により、メインCPU2は、MSG#(メッセージ)を送信する。サブCPU4のDACKの返送により、メインCPU2は、CMD(コマンド)を送信する。サブCPU4のDACKの返送により、メインCPUは、指令データを1キャラクタ送信する。データが送信されると、サブCPU4は、DACKを返送する。これにより、メインCPU2は、さらに、指令データを1キャラクタ送信する。以下、データが全て送信されるまで、メインCPU2のDATA、サブCPU4のDACKが繰り返される。

【0007】次に、指令データが全て送信されると、メインCPU2は、BCC(エラー検出)を送信する。これを受信したサブCPU4のACKの返送により、データリンクが終結する。これにより、メインCPU2からサブCPU4への伝送制御を終了する。

【0008】次に、図5bに、従来のサブCPU4〜10からメインCPU2への伝送制御手順を示す。まず、メインCPU2からサブCPU4〜10へPOL(ポーリング)を行う。例えば、サブCPU6がデータ(カードリーダなどI/Oのデータ)を送信できる時は、サブCPU6のLENを返送する。メインCPU2のDACKの送信により、データリンクが確立する。

【0009】次に、サブCPU6は、MSG#を返送する。メインCPU2のDACKの送信により、サブCPU6は、RES(レスポンス)を返送する。メインCPU2のDACKの送信により、サブCPU6は、I/Oデータを1キャラクタ送信する。データが送信されると、メインCPU2は、DACKを返送する。これにより、サブCPU6は、さらに、I/Oデータを1キャラクタ送信する。以下、データが全て送信されるまで、サブCPU6のDATA、メインCPU2のDACKが繰り返される。

【0010】次に、I/Oデータが全て送信されると、サブCPU6は、BCC(エラー検出)を返送する。これを受信したメインCPU2のACKの送信により、データリンクが終結する。この後、サブCPU6は、EOT(伝送終了)をメインCPU2に返送して、サブCPU6からメインCPU2への伝送制御を終了する。

【0011】このように、メインCPU2と各サブCPU4〜10との間でデータ伝送がされていた。

【0012】

【発明が解決しようとする課題】しかし、上記のような従来のデータ伝送方法においては、次のような問題点があった。

【0013】メインCPUから各サブCPUへは指令を内容とする伝送であるので、比較的伝送専有時間が短く問題にならないのに対して、各サブCPUからメインCPUへは販売情報などのデータ伝送であるので、伝送専有時間が長い場合がある。このため、サブCPUは、メインCPUとの伝送専有時間が長いと、この間I/O制御が行えず、サブCPUのI/O制御効率が悪いという問題点があった。

【0014】この発明は、上記問題を解決し、メインCPUとの伝送専有時間を短くして、サブCPUのI/O制御効率を向上させることを目的とする。

【0015】

【課題を解決するための手段】請求項1のデータ伝送方法は、メインCPUとサブCPU間に通信ラインを配して、データ伝送するものであって、サブCPUが、メインCPUへのデータ伝送とI/O制御の並行処理を行うデータ伝送システムにおいて、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送すること、を備えている。

【0016】

【作用】請求項1のデータ伝送方法は、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送する。従って、サブCPUは、メインCPUとの伝送専有時間を短くすることができる。

【0017】

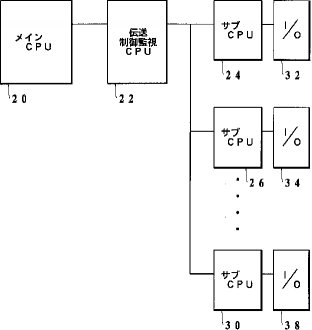

【実施例】図1に、この発明の一実施例であるデータ伝送方法のブロック図を示す。メインCPU20の同一通信ライン上に、伝送制御監視CPU22を介して、複数のサブCPU24〜30が接続されている。これにより、メインCPUは、各サブCPUごとの異なった通信を行う必要がなくなった。伝送制御監視CPU22は各サブCPU24〜30の監視を行うために設けられている。また、サブCPU24〜30には、それぞれ、カードリーダなどのI/O32〜38が接続されている。

【0018】この場合、メインCPU20とサブCPU24〜30間は、POL/SEL方式で通信を行っている。なお、メインCPU20と伝送制御監視CPU22との間の通信方式は、8ビットパラレルハンドシェイク方式になっている。以下、メインCPU20と伝送制御監視CPU22とサブCPU24〜30との間の伝送制御手順を説明する。

【0019】図2aに、メインCPU20と伝送制御監視CPU22とサブCPU24〜30との間の伝送制御手順を示す。伝送制御監視CPU22からサブCPU24〜30への通信方式は、半二重ハンドシェイク方式であって、1キャラクタ単位のシリアル応答方式になっている。

【0020】まず、メインCPU20から伝送制御監視CPU22へADR(サブCPUのアドレス),LEN(データの長さ),DATA(指令データ),・・が送信される。以下、伝送制御監視CPU22とサブCPU24〜30の間で伝送制御される。伝送制御監視CPU22からサブCPU24〜30へSEL(セレクティング)を行う。例えば、サブCPU24がデータ受信を受諾できる時は、ACK(肯定応答)を返送する。受信を受諾できない時には、NAK(否定応答)を返送する。サブCPU24のACKの返送により、データリンクが確立する。次に、伝送制御監視CPU22は、LENをサブCPU24に送信する。これを受信したサブCPU24のDACK(データに対する応答)の返送により、伝送制御監視CPU22は、指令データを1キャラクタ送信する。データが送信されると、サブCPU24は、DACKを返送する。これにより、伝送制御監視CPU22は、さらに、指令データを1キャラクタ送信する。以下、データが全て送信されるまで、伝送制御監視CPU22のDATA、サブCPU24のDACKが繰り返される。

【0021】次に、指令データが全て送信されると、伝送制御監視CPU22は、BCC(エラー検出)を送信する。これを受信したサブCPU24のACKの返送により、データリンクが終結する。この後、伝送制御監視CPU22は、メインCPU20へACKを送信して、メインCPU20と伝送制御監視CPU22とサブCPU24との間の伝送制御を終了する。

【0022】次に、図2bに、サブCPU24〜30と伝送制御監視CPU22とメインCPU20との間の伝送制御手順を示す。なお、サブCPU24〜30から伝送制御監視CPU22への通信方式は、半二重ハンドシェイク方式であって、1キャラクタ単位のデータが直列状に複数配置されてブロックとなっているブロック単位のシリアル応答方式にしている。

【0023】まず、伝送制御監視CPU22からサブCPU24〜30へPOL(ポーリング)を行う。例えば、サブCPU26がデータ(カードリーダなどI/Oのデータ)を送信できる時は、サブCPU26のADRを返送する。伝送制御監視CPU22のACKの送信により、データリンクが確立する。次に、この受信により、サブCPU26のI/OデータをLEN,DATA,BCCのブロックにして伝送制御監視CPU22に送信する。伝送制御監視CPU22は、このデータにADRを付加してメインCPU20に送信する。受信したメインCPU20のACKの返送により伝送制御監視CPU22はサブCPU26にACKを送信する。これにより、データリンクが終結する。サブCPU26は、EOT(伝送終了)を伝送制御監視CPU22に返送して、サブCPU26と伝送制御監視CPU22とメインCPU20との間の伝送制御を終了する。

【0024】このように、サブCPU26から伝送制御監視CPU22へは、I/Oデータをブロックにして送信している。これにより、サブCPUがI/Oデータを1キャラクタ送信するごとに、メインCPUが、DACKを返送することがなくなる。従って、サブCPU26がメインCPU20へ、I/Oデータを送信するために専有される伝送時間が縮小されることになる。

【0025】以上のようにして、この発明に係るデータ伝送方法により、サブCPUは、メインCPUとの伝送専有時間を短くすることができる。従って、サブCPUのI/O制御効率の向上が図られる。

【0026】

【発明の効果】請求項1に係るデータ伝送方法は、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送する。従って、サブCPUの伝送専有時間を短くし、I/O制御効率を向上することができる。

【図面の簡単な説明】

【図1】この発明の一実施例であるI/O伝送制御のブロック図を示す図である。

【図2】この発明の一実施例による伝送制御手順を示す図である。

【図3】従来のI/O伝送制御のブロック図を示す図である。

【図4】伝送データ構成を示す図である。

【図5】従来のI/O伝送制御の伝送制御手順を示す図である。

【図6】制御コード表を示す図である。

【符号の説明】

20・・・メインCPU

22・・・伝送制御監視CPU

24〜30・・・サブCPU

32〜38・・・I/O

【0001】

【産業上の利用分野】この発明は、メインCPUとサブCPU間のデータ伝送方法に関し、特に、サブCPUのI/O制御効率の向上に関するものである。

【0002】

【従来の技術】複数の店舗を有して大量販売するような販売業などにおいては、メインCPUと複数のサブCPU間を通信ライン上で接続してデータ伝送する情報管理システムを採用する場合がある。この場合、サブCPUは、販売情報などのデータをカードリーダやプリンタに出力させるなど、複数のI/Oを制御しており、並行して、メインCPUからの指令を受けて、カードリーダやプリンタから出力されるデータをメインCPUに伝送する。このような従来のデータ伝送方法の状態を図3に示す。メインCPU2と複数のサブCPU4〜10およびI/O12〜18が放射状に接続されている。

【0003】図3において、メインCPU2と各サブCPU4〜10間は、POL/SEL方式で通信を行っている。この時、サブCPU4〜10は、メインCPU2へのデータ伝送とI/O制御12〜18との並行処理を行っている。また、メインCPU2とサブCPU4〜10との間の通信方式は、両方向伝送可能であるが伝送時は一方向のみである半二重ハンドシェイク方式であって、1キャラクタ単位のシリアル応答方式である。この伝送データ構成を図4に示す。1キャラクタは、スタートビット40(1ビット),データビット42(8ビット),パリティビット44(1ビット),ストップビット46(1ビット)の11ビットにより構成される。

【0004】図5aに、従来のメインCPU2からサブCPU4〜10への伝送制御手順を示す。図6には、ここで使用される伝送制御コード表を示す。

【0005】まず、メインCPU2からサブCPU4〜10へSEL(セレクティング)を行う。例えば、サブCPU4がデータを受信を受諾できる時は、ACK(肯定応答)を返送する。受信を受諾できない時には、NAK(否定応答)を返送する。サブCPU4のACKの返送により、データリンクが確立する。

【0006】次に、メインCPU2は、LENをサブCPU4に送信する。これを受信したサブCPU4のDACK(データに対する応答)の返送により、メインCPU2は、MSG#(メッセージ)を送信する。サブCPU4のDACKの返送により、メインCPU2は、CMD(コマンド)を送信する。サブCPU4のDACKの返送により、メインCPUは、指令データを1キャラクタ送信する。データが送信されると、サブCPU4は、DACKを返送する。これにより、メインCPU2は、さらに、指令データを1キャラクタ送信する。以下、データが全て送信されるまで、メインCPU2のDATA、サブCPU4のDACKが繰り返される。

【0007】次に、指令データが全て送信されると、メインCPU2は、BCC(エラー検出)を送信する。これを受信したサブCPU4のACKの返送により、データリンクが終結する。これにより、メインCPU2からサブCPU4への伝送制御を終了する。

【0008】次に、図5bに、従来のサブCPU4〜10からメインCPU2への伝送制御手順を示す。まず、メインCPU2からサブCPU4〜10へPOL(ポーリング)を行う。例えば、サブCPU6がデータ(カードリーダなどI/Oのデータ)を送信できる時は、サブCPU6のLENを返送する。メインCPU2のDACKの送信により、データリンクが確立する。

【0009】次に、サブCPU6は、MSG#を返送する。メインCPU2のDACKの送信により、サブCPU6は、RES(レスポンス)を返送する。メインCPU2のDACKの送信により、サブCPU6は、I/Oデータを1キャラクタ送信する。データが送信されると、メインCPU2は、DACKを返送する。これにより、サブCPU6は、さらに、I/Oデータを1キャラクタ送信する。以下、データが全て送信されるまで、サブCPU6のDATA、メインCPU2のDACKが繰り返される。

【0010】次に、I/Oデータが全て送信されると、サブCPU6は、BCC(エラー検出)を返送する。これを受信したメインCPU2のACKの送信により、データリンクが終結する。この後、サブCPU6は、EOT(伝送終了)をメインCPU2に返送して、サブCPU6からメインCPU2への伝送制御を終了する。

【0011】このように、メインCPU2と各サブCPU4〜10との間でデータ伝送がされていた。

【0012】

【発明が解決しようとする課題】しかし、上記のような従来のデータ伝送方法においては、次のような問題点があった。

【0013】メインCPUから各サブCPUへは指令を内容とする伝送であるので、比較的伝送専有時間が短く問題にならないのに対して、各サブCPUからメインCPUへは販売情報などのデータ伝送であるので、伝送専有時間が長い場合がある。このため、サブCPUは、メインCPUとの伝送専有時間が長いと、この間I/O制御が行えず、サブCPUのI/O制御効率が悪いという問題点があった。

【0014】この発明は、上記問題を解決し、メインCPUとの伝送専有時間を短くして、サブCPUのI/O制御効率を向上させることを目的とする。

【0015】

【課題を解決するための手段】請求項1のデータ伝送方法は、メインCPUとサブCPU間に通信ラインを配して、データ伝送するものであって、サブCPUが、メインCPUへのデータ伝送とI/O制御の並行処理を行うデータ伝送システムにおいて、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送すること、を備えている。

【0016】

【作用】請求項1のデータ伝送方法は、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送する。従って、サブCPUは、メインCPUとの伝送専有時間を短くすることができる。

【0017】

【実施例】図1に、この発明の一実施例であるデータ伝送方法のブロック図を示す。メインCPU20の同一通信ライン上に、伝送制御監視CPU22を介して、複数のサブCPU24〜30が接続されている。これにより、メインCPUは、各サブCPUごとの異なった通信を行う必要がなくなった。伝送制御監視CPU22は各サブCPU24〜30の監視を行うために設けられている。また、サブCPU24〜30には、それぞれ、カードリーダなどのI/O32〜38が接続されている。

【0018】この場合、メインCPU20とサブCPU24〜30間は、POL/SEL方式で通信を行っている。なお、メインCPU20と伝送制御監視CPU22との間の通信方式は、8ビットパラレルハンドシェイク方式になっている。以下、メインCPU20と伝送制御監視CPU22とサブCPU24〜30との間の伝送制御手順を説明する。

【0019】図2aに、メインCPU20と伝送制御監視CPU22とサブCPU24〜30との間の伝送制御手順を示す。伝送制御監視CPU22からサブCPU24〜30への通信方式は、半二重ハンドシェイク方式であって、1キャラクタ単位のシリアル応答方式になっている。

【0020】まず、メインCPU20から伝送制御監視CPU22へADR(サブCPUのアドレス),LEN(データの長さ),DATA(指令データ),・・が送信される。以下、伝送制御監視CPU22とサブCPU24〜30の間で伝送制御される。伝送制御監視CPU22からサブCPU24〜30へSEL(セレクティング)を行う。例えば、サブCPU24がデータ受信を受諾できる時は、ACK(肯定応答)を返送する。受信を受諾できない時には、NAK(否定応答)を返送する。サブCPU24のACKの返送により、データリンクが確立する。次に、伝送制御監視CPU22は、LENをサブCPU24に送信する。これを受信したサブCPU24のDACK(データに対する応答)の返送により、伝送制御監視CPU22は、指令データを1キャラクタ送信する。データが送信されると、サブCPU24は、DACKを返送する。これにより、伝送制御監視CPU22は、さらに、指令データを1キャラクタ送信する。以下、データが全て送信されるまで、伝送制御監視CPU22のDATA、サブCPU24のDACKが繰り返される。

【0021】次に、指令データが全て送信されると、伝送制御監視CPU22は、BCC(エラー検出)を送信する。これを受信したサブCPU24のACKの返送により、データリンクが終結する。この後、伝送制御監視CPU22は、メインCPU20へACKを送信して、メインCPU20と伝送制御監視CPU22とサブCPU24との間の伝送制御を終了する。

【0022】次に、図2bに、サブCPU24〜30と伝送制御監視CPU22とメインCPU20との間の伝送制御手順を示す。なお、サブCPU24〜30から伝送制御監視CPU22への通信方式は、半二重ハンドシェイク方式であって、1キャラクタ単位のデータが直列状に複数配置されてブロックとなっているブロック単位のシリアル応答方式にしている。

【0023】まず、伝送制御監視CPU22からサブCPU24〜30へPOL(ポーリング)を行う。例えば、サブCPU26がデータ(カードリーダなどI/Oのデータ)を送信できる時は、サブCPU26のADRを返送する。伝送制御監視CPU22のACKの送信により、データリンクが確立する。次に、この受信により、サブCPU26のI/OデータをLEN,DATA,BCCのブロックにして伝送制御監視CPU22に送信する。伝送制御監視CPU22は、このデータにADRを付加してメインCPU20に送信する。受信したメインCPU20のACKの返送により伝送制御監視CPU22はサブCPU26にACKを送信する。これにより、データリンクが終結する。サブCPU26は、EOT(伝送終了)を伝送制御監視CPU22に返送して、サブCPU26と伝送制御監視CPU22とメインCPU20との間の伝送制御を終了する。

【0024】このように、サブCPU26から伝送制御監視CPU22へは、I/Oデータをブロックにして送信している。これにより、サブCPUがI/Oデータを1キャラクタ送信するごとに、メインCPUが、DACKを返送することがなくなる。従って、サブCPU26がメインCPU20へ、I/Oデータを送信するために専有される伝送時間が縮小されることになる。

【0025】以上のようにして、この発明に係るデータ伝送方法により、サブCPUは、メインCPUとの伝送専有時間を短くすることができる。従って、サブCPUのI/O制御効率の向上が図られる。

【0026】

【発明の効果】請求項1に係るデータ伝送方法は、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送する。従って、サブCPUの伝送専有時間を短くし、I/O制御効率を向上することができる。

【図面の簡単な説明】

【図1】この発明の一実施例であるI/O伝送制御のブロック図を示す図である。

【図2】この発明の一実施例による伝送制御手順を示す図である。

【図3】従来のI/O伝送制御のブロック図を示す図である。

【図4】伝送データ構成を示す図である。

【図5】従来のI/O伝送制御の伝送制御手順を示す図である。

【図6】制御コード表を示す図である。

【符号の説明】

20・・・メインCPU

22・・・伝送制御監視CPU

24〜30・・・サブCPU

32〜38・・・I/O

【特許請求の範囲】

【請求項1】メインCPUとサブCPU間に通信ラインを配して、データ伝送するものであって、サブCPUが、メインCPUへのデータ伝送とI/O制御の並行処理を行うデータ伝送システムにおいて、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送すること、を特徴とするデータ伝送方法。

【請求項1】メインCPUとサブCPU間に通信ラインを配して、データ伝送するものであって、サブCPUが、メインCPUへのデータ伝送とI/O制御の並行処理を行うデータ伝送システムにおいて、メインCPUからサブCPUへは、1キャラクタハンドシェイクでデータ伝送し、サブCPUからメインCPUへは、ブロック単位でデータ伝送すること、を特徴とするデータ伝送方法。

【図1】

【図2】

【図4】

【図3】

【図5】

【図6】

【図2】

【図4】

【図3】

【図5】

【図6】

【公開番号】特開平5−81190

【公開日】平成5年(1993)4月2日

【国際特許分類】

【出願番号】特願平3−245391

【出願日】平成3年(1991)9月25日

【出願人】(000002945)オムロン株式会社 (3,542)

【公開日】平成5年(1993)4月2日

【国際特許分類】

【出願日】平成3年(1991)9月25日

【出願人】(000002945)オムロン株式会社 (3,542)

[ Back to top ]