データ処理システム、処理装置、記憶装置、及びメモリアクセス制御方法

【課題】 PUがネットワーク手段(接続装置)を介し、複数のMUにアクセスするシステムでは、ネットワーク手段の過負荷が生じ易く、PU内の演算処理がロードデータ待ちし、システムの性能を低下させる要因になっていた。

【解決手段】 複数のPU(処理装置)、複数のMU(記憶装置)がネットワーク手段3で接続されたデータ処理システムであり、PUにはCPUポート(要求元)140より要求情報を受け、これと先行要求情報を比較し、コマンド及びアドレスの所定部が一致すれば、RQ情報に代わり、差分フラグを立てアドレスの差分を出力する削減手段120、RQパケットや差分パケットを作成送信するPパケット手段130とを要求元ごとに備え、MUにはパケットを受信するMパケット手段201、差分フラグがオンで、差分パケットと保持している先行要求情報から今回の要求情報を作成する復元手段202を備える。

【解決手段】 複数のPU(処理装置)、複数のMU(記憶装置)がネットワーク手段3で接続されたデータ処理システムであり、PUにはCPUポート(要求元)140より要求情報を受け、これと先行要求情報を比較し、コマンド及びアドレスの所定部が一致すれば、RQ情報に代わり、差分フラグを立てアドレスの差分を出力する削減手段120、RQパケットや差分パケットを作成送信するPパケット手段130とを要求元ごとに備え、MUにはパケットを受信するMパケット手段201、差分フラグがオンで、差分パケットと保持している先行要求情報から今回の要求情報を作成する復元手段202を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はデータ処理システム、処理装置、記憶装置、及びメモリアクセス制御方法に関し、特に、複数の処理装置がネットワーク手段等を通じ複数の記憶装置にアクセスする際のネットワーク手段の負荷を軽減したデータ処理システム、処理装置、記憶装置、及びメモリアクセス制御方法に関する。

【背景技術】

【0002】

複数の演算装置がネットワーク装置を通じて、複数の主記憶装置にアクセスする技術の第1の従来例として、次のネットワーク装置がある。

【0003】

このネットワーク装置は、複数の演算装置と複数の主記憶装置を接続するネットワーク装置において、複数の演算装置から主記憶の同一アドレスに対する複数の読出リクエスト、または複数の書込リクエストがあると、リクエストそれぞれを1つのリクエストに圧縮する機能と、該リクエストに対する主記憶からのリプライリクエストを前記圧縮対象の複数の演算装置に向けて展開する機能を有する(特許文献1参照。)。

【0004】

また、主記憶装置にアクセスする技術の第2の従来例として、主記憶の同一アドレスに対する複数の書き込みリクエストを一つの書き込みリクエストに縮退する縮退ストア制御装置がある(特許文献2参照。)。

【0005】

【特許文献1】特開平9−44459(第1ページ)

【特許文献2】特開平6−103147(第1ページ)

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記第1の従来例では、システム性能の低下要因である、各リクエストやストアデータによるネットワークの過負荷は、幾らか軽減されるが、リクエストの圧縮が同一アドレスに限られるという問題点がある。

【0007】

その理由は、複数の主記憶装置のうち、同一の主記憶装置へのアドレスのことなる複数のリクエストを圧縮する機能を有しないからである。

【0008】

この従来例は、複数の演算装置からの同一アドレスへのリクエストを圧縮する技術であるが、本発明では同一CPUからの同一主記憶装置へのリクエストの場合に圧縮が可能となる点で相違がある。

【0009】

次に、上記第2の従来例には、次の様な問題点がある。第1の問題点は、読み出しリクエストを縮退することが出来ないことである。

【0010】

その理由は、読み出しリクエストについてのみ縮退可能か判断する手段を備えていないからである。

【0011】

第2の問題点は、物理的に分割された複数の主記憶装置のうち、同一の主記憶装置への複数のリクエストを縮退することが出来ないことである。

【0012】

その理由は、メモリ構成を参照して、主記憶装置毎に縮退を判断する手段を有していないからである。

【0013】

この様に、従来例ではCPUのメモリアクセス負荷が高くなると、CPU内の演算処理がロードデータを待つケースが発生し、システムの性能を低下させる要因になっていた。

【課題を解決するための手段】

【0014】

本発明の第1のデータ処理システムは、コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えた処理装置と、前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えた記憶装置とを含むことを特徴とする。

【0015】

本発明の第2のデータ処理システムは、一つ以上の処理装置と複数の記憶装置とこれらを接続するネットワーク手段を含むデータ処理システムであって、前記処理装置には、メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報とを比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行の要求情報として保持しておく要求情報削減手段と、前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する処理装置パケット手段とを備え、前記記憶装置には、メモリ部と、これの読出、書込アクセスを行うメモリアクセス手段と、ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置パケット手段と、差分フラグがオンであれば、差分情報パケットと自装置に保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とする。

【0016】

本発明の第3のデータ処理システムは、前記第2のデータ処理システムであって、前記処理装置の処理装置パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手段と、ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有し、前記記憶装置がメモリアクセス手段からロードデータを受取り、記憶装置パケット手段に転送する手段も備え、記憶装置パケット手段が、複数パケットで受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする。

【0017】

本発明の第4のデータ処理システムは、前記第3のデータ処理システムであって、前記処理装置が、メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする。

【0018】

本発明の第5のデータ処理システムは、前記第2、又は第4のデータ処理システムであって、前記記憶装置の復元手段が先行の要求情報を処理装置毎に保持し、差分情報パケットに含む或いは付随する処理装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、これをメモリアクセス手段に渡し、またその処理装置の先行要求情報としておくことを特徴とする。

【0019】

本発明の第1の処理装置は、コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えたことを特徴とする。

【0020】

本発明の第2の処理装置は、メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行する要求情報として保持しておく要求情報削減手段と、前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、ネットワーク手段を通じ記憶装置に送信するパケット手段とを備えたことを特徴とする。

【0021】

本発明の第3の処理装置は、前記第2の処理装置であって、前記パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のパケットに変換し、要求情報や差分情報のパケットに続いて送出する手段と、ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有することを特徴とする。

【0022】

本発明の第4の処理装置は、前記第3の処理装置であって、前記メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする。

【0023】

本発明の第1の記憶装置は、アクセス要求情報に関する差分情報パケットを受信すると、これの差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えたことを特徴とする。

【0024】

本発明の第2の記憶装置は、メモリ部と、これの読出やこれへの書込を行うメモリアクセス手段と、ネットワーク手段を通じ、メモリアクセスの要求装置よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻すパケット手段と、差分フラグがオンであれば、差分情報パケットと保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とする。

【0025】

本発明の第3の記憶装置は、前記第2の記憶装置であって、メモリアクセス手段からロードデータを受取り、パケット手段に転送する手段も備え、前記パケット手段が、複数パケットとして受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする。

【0026】

本発明の第4の記憶装置は、前記第2、又は第3の記憶装置であって、前記復元手段が先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、またその要求装置の先行の要求情報としておくことを特徴とする。

【0027】

本発明の第1のメモリアクセス制御方法は、メモリアクセスを要求する装置に、要求元からコマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手順を備え、記憶装置に、前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手順を備えたことを特徴とする。

【0028】

本発明の第2のメモリアクセス制御方法は、一つ以上のメモリアクセス要求装置と複数の記憶装置とこれらを接続するネットワーク手段を含むシステムのメモリアクセス制御方法であって、前記要求装置が、メモリアクセス要求元よりコマンドとアクセスアドレスを含む要求情報を受け、これと先行する要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力する要求情報削減手順と、前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグより前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する要求側パケット手順とを備え、前記記憶装置が、ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置側パケット手順と、差分フラグがオンであれば、差分情報パケットと、保持している先行の要求情報から今回の要求情報を作成する復元手順と、要求情報でメモリ部の読出、書込アクセスを行うメモリアクセス手順とを備えたことを特徴とする。

【0029】

本発明の第3のメモリアクセス制御方法は、前記第2のメモリアクセス制御方法であって、前記要求側パケット手順が、要求元のストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手順と、ネットワーク手段より複数のパケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手順を有し、前記記憶装置が、読み出したロードデータを、記憶装置側パケット手順に渡す手順も備え、記憶装置側パケット手順が、複数のパケットとして受信したストアデータを、もとの一つのデータに戻す手順と、ロードデータを複数のパケットにし、ネットワーク手段を通じ要求装置に返送する手順を有することを特徴とする。

【0030】

本発明の第4のメモリアクセス制御方法は、前記第2、又は第3のメモリアクセス制御方法であって、前記記憶装置の復元手順が、先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に対応する先行の要求情報を選択し、これと差分情報パケットとから今回の要求情報を作成し、これをメモリアクセス手順に渡し、またその要求装置の先行の要求情報として保持しておくことを特徴とする。

【発明の効果】

【0031】

第一の効果は、メモリロード命令、メモリストア命令のレイテンシを短縮し、システム性能を向上させることができる。

【0032】

その理由は、削減手段と復元手段によりPUからMUへ転送するパケット数を削減することで、後続RQの処理を早く開始する為である。

【0033】

第二の効果は、メモリロード命令、メモリストア命令のスループットを高め、システム性能を向上させることができる。

【0034】

その理由は、差分情報を用いることで、PUからMUへ短時間でより多くの情報を送ることが可能となる為である。

【0035】

第三の効果は、PUポートとMUポートの信号本数を大幅に削減する事が可能であり、システムのHW量を削減できる。

【0036】

その理由は、PU、MUそれぞれにRQ及びロードデータまたはストアデータをパケットに分割または合成を可能とする手段を持ち、パケットによりPU−MU間転送を行うことで、同時に転送する情報量を減らすことができる為である。

【発明を実施するための最良の形態】

【0037】

次に、本発明を実施するための最良の形態について図面を参照して詳細に説明する。

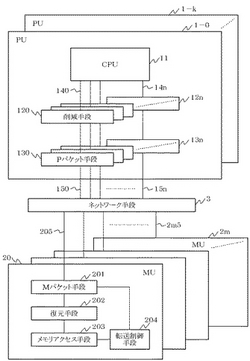

図1は、本発明の実施形態の一般形を示すブロック図である。

【0038】

本発明の実施形態は、メモリアクセスを行う複数のCPUポート140〜14nを持つCPUを含む複数のPU(処理装置)1−0〜1−kと、一つ以上のすべて同型のMU(主記憶装置)20〜2mと、該PUと該MUを接続するネットワーク手段3で構成される。

【0039】

PU1−0とネットワーク手段3とは、PUポート150〜15nでそれぞれ接続され、各MUとネットワーク手段3とはMUポート205〜2m5で接続されている。

【0040】

本実施形態では、一つのPUポート(例えばPUポート150)とネットワーク手段3間の転送性能と、一つのMUポート(例えばMUポート205)とネットワーク手段3間の転送性能は等しいと仮定する。

【0041】

次に本実施形態でPUを1つとした第1実施例について説明する。図2は本発明のデータ処理システムの第1実施例の構成を示したブロック図である。

【0042】

図2のシステムは、図1のシステムでk=0、n=3、m=3として、即ち、PUの数を1、MUの数を4、CPUポート数を4、PUポートの数を4として構成した例である。

【0043】

PU1−0は、CPU11と、削減手段120〜123と、Pパケット手段(処理装置側パケット手段)130〜133と、CPUポート140〜143と、PUポート150〜153で構成される。

【0044】

CPU(中央演算処理装置)11は、

(1)ロードRQ若しくはストアRQ(以下ロードRQ、ストアRQの総称をRQとする)によりメモリへのアクセスを行う。

(2)4個のCPUポート140〜143を持ち、該CPUポート140〜143は、接続先である後述の削減手段120〜123からのRQ受け取り可能な通知により、ロードRQ、または、ストアRQと該ストアRQに対応するストアデータを送る。

【0045】

削減手段120〜123は、

(1)CPU11のCPUポート140〜143にそれぞれ対応している。

(2)CPU11からのRQと、該RQより先行するRQを比較して、該RQの情報量が削減可能な場合に該RQの情報量を削減して後述のPパケット手段130〜133に送る。

(3)CPU11からのRQを一時的に保持する。

【0046】

(4)該RQが削減可能な場合、RQを再構成する。

(5)CPU11からのストアRQに対応し、ストアデータをPパケット手段130〜133へ送る。

(6)CPU11に対し、RQを受け取ることができることを通知する。

【0047】

Pパケット手段130〜133は、

(1)CPU11のCPUポート140〜143にそれぞれ対応している。

(2)削減手段120〜123からのRQもしくはストアデータからパケットを生成し、PUポート150〜153を経由してネットワーク手段3へ送る。

(3)ネットワーク手段3からPUポート150〜153を経由して受け取った複数のパケットを元のデータに合成する。

【0048】

PUポート150〜153は、

(1)CPU11のCPUポート140〜143にそれぞれ対応している。

(2)PU1−0とネットワーク手段3間でパケットの送受信を行う。

【0049】

全て同型の削減手段(ここでは代表して削減手段120)について、図3を用いて説明する。

【0050】

削減手段120は、PRQ保持手段1201と、差分情報生成手段1202と、RQ構成手段1203とで構成される。

【0051】

PRQ保持手段1201は、

(1)CPU11からのRQを一時的に保持する。

(2)保存しているRQの情報を、後述の差分情報生成手段1202へ送る。

【0052】

差分情報生成手段1202は、

(1)CPU11からのRQのRQコマンドと、該RQより1つ前に処理され既にPRQ保持手段1201に保持されている先行RQ(先行するRQ)のRQコマンドを比較して、同じ場合は差分識別フラグを1とし、異なる場合は該フラグを0とする。

(2)CPU11からのRQのMU内アドレスと、PRQ保持手段1201に保持されている先行RQのMU内アドレスから差分情報を生成する。

(3)差分識別フラグと差分情報をRQ構成手段1203へ送る。

【0053】

RQ構成手段1203は、

(1)CPU11からRQを受け取る。

(2)差分情報生成手段1202からの差分識別フラグが0の場合、CPU11からのRQをそのままPパケット手段130へ送る。該フラグが1の場合、差分情報生成手段1202からの識別フラグと差分情報で構成されたRQを作り、Pパケット手段130に送り、CPU11からのRQを破棄する。

(3)CPU11からのストアデータをそのままPパケット手段130へ送る。

【0054】

全ての同型のMU(ここでは代表してMU20)について図2を用いて説明する。MU20は、Mパケット手段201と、復元手段202と、メモリアクセス手段203と、転送制御手段204と、MUポート205と、RAM(図示せず)で構成される。

【0055】

Mパケット手段(記憶装置側パケット手段)201は、

(1)MUポート205を経由でネットワーク手段3から受け取った複数のパケットから元のRQ若しくはストアデータを生成する。

(2)転送制御手段204からのロードデータを複数(実施例では2個)のパケットに分解しMUポート205を経由しネットワーク手段3へ送る。

(3)転送制御手段204に対し、ロードデータを受け取ることが可能なことを通知する。

【0056】

復元手段202は、

(1)Mパケット手段201から受け取ったRQの差分識別フラグの値を参照し、Mパケット手段201から受け取ったRQの差分情報と、先行RQのMU内アドレスから該RQの元のMU内アドレスを再生する。

(2)Mパケット手段201から受け取ったRQの差分識別フラグの値を参照し、該RQをそのままメモリアクセス手段203へ送るか、もしくは1)の処理で再生したRQをメモリアクセス手段203へ送る。

(3)メモリアクセス手段203へ送ったRQを一時的に保持する。

(4)ストアデータをそのままメモリアクセス手段203へ送る。

【0057】

メモリアクセス手段203は、

(1)復元手段202からのRQと、ストアデータが有る場合はストアデータを受け取る。

(2)該RQのRQコマンドに従い、MU内アドレスで指定されたRAMのアドレスをアクセスする。

(3)該RQがロードRQの場合、RAMから読み出したデータ(以下ロードデータとする)を転送制御手段204へ送る。

【0058】

転送制御手段204は、

(1)メモリアクセス手段203からロードデータを受け取る。

(2)Mパケット手段201がロードデータを受け取ることが可能である通知により、該ロードデータをMパケット手段201へ送る。

(3)Mパケット手段201が該ロードデータ受け取る事ができない場合、該ロードデータを一時的に格納する。

【0059】

復元手段202について図4を用いて説明する。復元手段202は、情報再生手段2021と、RQ再生手段2022と、MRQ保持手段2023で構成される。

【0060】

情報再生手段2021は、

(1)Mパケット手段201から受け取ったRQの差分識別フラグが1の場合、該RQの差分情報と、MRQ保持手段2023内に保持している先行RQのMU内アドレスから、該RQの元のMU内アドレスを再生し、該元のMU内アドレスとRQの再生指示をRQ再生手段2022へ送る。

(2)該フラグが0の場合、何もしない。

【0061】

RQ再生手段2022は、

(1)情報再生手段2021からの再生指示に従い、MRQ保持手段2023に保持されている先行RQのRQコマンドと、情報再生手段2021からのMU内アドレスから、元のRQを再生し、メモリアクセス手段203へ送る。

(2)情報再生手段2021からの再生指示が無い場合、Mパケット手段201から送られたRQを加工せずメモリアクセス手段203へ送る。

(3)メモリアクセス手段203へ送ったRQをMRQ保持手段2023へ送る。

(4)Mパケット手段201からのストアデータをそのままメモリアクセス手段203へ送る。

【0062】

MRQ保持手段2023は、

(1)RQ再生手段2022からのRQを一時的に保持する。

(2)先行RQが保持されている場合、先行RQの情報は、RQ再生手段2022からのRQによって上書きされる。

【0063】

転送制御手段204について図5を用いて説明する。転送制御手段204は、データ格納手段2041と、データ制御手段2042で構成される。

【0064】

データ格納手段2041は、複数のワードで構成される先入れ先出しバッファを持ち、(1)メモリアクセス手段203からロードデータを受け取る。

(2)データ制御手段2042の指示に従い、該バッファにメモリアクセス手段203からのロードデータの格納もしくは読み出しを行う。

(3)データ制御手段2042の指示に従い、Mパケット手段201へロードデータを送る。

【0065】

データ制御手段2042は、

(1)Mパケット手段201が前記ロードデータを受け取り可能な通知がある場合、データ格納手段2041に対し、格納されている最も古いロードデータをMパケット手段201へ送る指示を出す。

(2)Mパケット手段201が前記ロードデータを受け取り可能な通知が無い場合、データ格納手段2041に対し、該ロードデータを格納する指示を出す。

【0066】

尚、ネットワーク手段3のPUポート(PU接続口)では、1stRQパケットのMU番号(主記憶アドレスの上位2ビットで、宛先MUを指定する)をレジスタ等に受け、これで出力先MUポートを決めるが、このレジスタを他のパケットではストローブしないようにし、宛先を保持する。

【0067】

MU番号が、実際のMUの物理番号にアドレス変換されるシステムでも同様である。

【0068】

又、ネットワーク手段3からMUに返送先情報として、1stRQパケットに付随して、2ビットのPUポート識別を受信し、Mパケット手段201,復元手段202を通じ、RQ情報と共に持ち回られメモリアクセス手段203に渡される。MRQ保持手段にもRQ情報と同様に保持され、差分情報パケットのRQでは、RQ情報と同様に再生され、渡される。

【0069】

以降ロードデータと共に持ち回られ、ネットワーク手段のMUポートの上り側に送出される。

【0070】

次に、本実施形態の第1実施例の動作について図面を参照して説明する。

【0071】

また、ネットワーク手段3において、PUポート150〜153の各ポートのそれぞれは、RQのMU番号で指定することで、MUポート205〜235にアクセスできる。

【0072】

しかし、この例では、PUポート150〜153の各ポートは並列動作するが、それぞれが異なるMUにアクセスする(CPUポート140〜143の各ポートが排他的にMU番号を指定する)とする。

【0073】

また、説明は、ある期間、PUポート150とMUポート205、PUポート151とMUポート215、PUポート152とMUポート225、PUポート153とMUポート235、がそれぞれ1対1に接続される例で行う。

【0074】

図2を参照し、先ずMU20のメモリをロードする処理について説明する。CPU11ではメモリロード命令が発行される。CPU11では該ロード命令によりロードRQが生成される。

【0075】

該命令のアドレスによりCPUポート140を経由して、該RQは削減手段120へ送られる。

【0076】

該RQのフォーマットを図6(a)を用いて説明する。該RQはロードを指示するRQコマンド、MU20を指定するMUフィールド、MU20内のアドレスを指定するMU内アドレスフィールドで構成されている。

【0077】

CPU11のロード命令のアドレスはMUフィールドと、MU内アドレスフィールドに変換されている。MUフィールドと、MU内アドレスフィールドを合わせてアドレスフィールドと呼ぶ。

【0078】

削減手段120では、該RQのRQコマンド、アドレスフィールドと、該RQに先行しPRQ保持手段1201に保持されているRQ(以下先行RQ)のRQコマンド、アドレスフィールドとをそれぞれ比較し、RQの転送する情報量を削減可能か判断する。

【0079】

削減可能な場合は、差分情報を生成した後にRQを構成してPパケット手段に送る。

【0080】

削減手段120の処理について図3と、図9のフローチャートを用いて説明する。

【0081】

先ず、RQが削減手段120に入力される(ステップA1)。尚、入力されるRQは図6(a)に示すフォーマットである。

【0082】

差分情報生成手段1202において、該RQと、PRQ保持手段1201に既に保持されている先行RQのRQコマンドが一致し、かつ、MUフィールドが一致している場合、該RQの情報量を削減可能と判断して差分識別フラグを1とし(ステップA2)、ステップA3に進む。

【0083】

一致していない場合、該RQの情報量を削減する事は不可能と判断して差分識別フラグを0とし(ステップA2)、ステップA4に進む。

【0084】

差分情報生成手段1202において、該RQと、PRQ保持手段1201に保持されている先行RQのMU内アドレスフィールドを比較し、次の式に従い差分情報を生成する。

【0085】

差分情報 = 該RQのMU内アドレス − 先行RQのMU内アドレス・・(式1)

差分情報は、正の値、0、負の値となり得る。差分情報生成手段1202は、差分識別フラグと、差分情報をRQ構成手段1203に送る(ステップA3)。尚、図6(b)にRQ構成手段1203に送られる情報を示す。

【0086】

PRQ保持手段1201において、CPU11からの送られたRQを保持する。先行RQは該RQによって上書きされ先行RQに関する情報は破棄される(ステップA4)。

【0087】

RQ構成手段1203において、差分識別フラグを参照し、該フラグが1の場合(ステップA5)、CPU11から送られた図6(a)に示すRQを、差分情報生成手段1202から送られた図6(b)に示す差分情報と差分識別フラグに置き換える(ステップA6)。

【0088】

以降、置き換えられた情報をCPU11から送られたRQとして処理する。RQ構成手段1203は、該RQをPパケット手段130に送る(ステップA7)。

【0089】

図2を参照すると、Pパケット手段130において、削減手段120から送られたRQを1つまたは2つのパケットに分解して、ネットワーク手段3におくる。パケット数は差分識別フラグの値によって異なる。

【0090】

差分識別フラグが0の場合、2個のパケットに分解される。パケットは図7(a)に示す様に、RQコマンド、MU番号、差分識別フラグ、パケットフラグを第一パケット(1stパケット)とし、MU内アドレス、差分識別フラグ(1stパケットのコピー)、パケットフラグを第二パケット(2ndパケット)とする。

【0091】

1stパケットではパケットフラグを1とし、2ndパケットではパケットフラグを0とする。

【0092】

差分識別フラグが1の場合、1個のパケットが生成される。パケットは図7(b)に示す様に、差分情報、差分識別フラグ、パケットフラグとを1stパケットとし、パケットフラグを0とする。

【0093】

これらのパケットはPUポート150を経由し、ネットワーク手段3へ1stパケット、2ndパケットの順に連続して送られる。

【0094】

ネットワーク手段3において、PUポート150経由でPU1−0から送られたパケットを、MUポート205経由でMU20に送る。

【0095】

Mパケット手段201において、MUポート205経由でネットワーク手段3から送られた1つまたは2つのパケットから、パケットに分解前のRQを合成する。合成する処理は差分識別フラグの値によって異なる。

【0096】

差分識別フラグが0の場合、図7(a)に示されている2個のパケットから、図8に示されているRQを合成する。合成されたRQの差別識別フラグは0とする。また、元のRQのMU番号のビットは削除される。

【0097】

差分識別フラグが1の場合、図7(b)に示されている1個のパケットから、図6(b)に示されているRQを合成する。合成されたRQの差別識別フラグは1とする。合成された該RQは、復元手段202へ送られる。

【0098】

復元手段202では、Mパケット手段201から送られたRQの差分識別フラグの値を参照する。

【0099】

該RQの差分識別フラグが0の場合、該RQをそのままメモリアクセス手段203へ送る。

【0100】

該RQの差分識別フラグが1の場合、該RQの差分情報と、MRQ保持手段2023に保持されている先行RQのRQコマンドとMU内アドレスから元のRQを再生する。

【0101】

復元手段202の処理について図4のブロック図と、図10のフローチャートを用いて説明する。

【0102】

RQが復元手段202に入力される。入力されるRQのフォーマットは、差分識別フラグが0の場合は図6(a)、1の場合、図6(b)となる(ステップB1)。

【0103】

情報再生手段2021において、差分識別フラグが参照される。差分識別フラグが0の場合、該RQをRQ再生手段2022に送り、ステップB5へ進み、差分識別フラグが1の場合、ステップB3へ進む(ステップB2)。

【0104】

情報再生手段2021において、Mパケット手段201から送られた該RQの差分情報と、MRQ保持手段2023に保持されている先行RQのMU内アドレスから、次の式により該RQの元のMU内アドレスを算出する。

【0105】

元のMU内アドレス = 先行RQのMU内アドレス + 差分情報・・・(式2)

式2で算出した該RQの元のMU内アドレスと、差分識別フラグはRQ再生手段2022へ送られる(ステップB3)。

【0106】

RQ再生手段2022において、差分識別フラグが1の場合、情報再生手段2021から送られたMU内アドレスと、MRQ保持手段2023に保持されている先行RQのRQコマンドを結合し、元のRQを再生する。

【0107】

ここで再生された該RQのフォーマットは、図8に示す様になる。差分識別フラグは0とする。このフォーマットは、ステップB1で復元手段202に入力された差分識別フラグが0のRQを同じである(ステップB4)。

【0108】

RQ再生手段2022において、ステップB2のみの処理が行われたRQと、ステップB2、B3、B4の処理が行われたRQは同じフォーマットとなる。このRQをMRQ保持手段2023へ送る。

【0109】

MRQ保持手段2023で、該RQは保持される。先行RQは該RQによって上書きされ、先行RQに関する情報は破棄される(ステップB5)。

【0110】

RQ再生手段2022の該RQはメモリアクセス手段203へ送られる(ステップB6)。

【0111】

図2を参照すると、メモリアクセス手段203では、復元手段202から送られたRQのRQコマンドに従い、RAM内の、MU内アドレスの示すアドレスからデータ(以下ロードデータとする)を読み出す。

【0112】

ロードデータは、転送制御手段204へ送られ、データ格納手段2041に格納される。

【0113】

データ制御手段2042は、MUポート205の使用状況からデータ格納手段2041に格納されたデータをネットワーク手段3に送出できるタイミングを判断し、データ格納手段2041に送出指示を送る。

【0114】

データ格納手段2041では、データ制御手段2042からの該指示に従い、格納している最も古いロードデータをネットワーク手段3へ送出する。

【0115】

該ロードデータは、MUポート205、ネットワーク手段3、PUポート150を経由し、該ロードデータのRQを送ったCPU11へ送られ、一連の処理を終える。

【0116】

CPU11がロードRQを発行した際の処理を、図11のタイムチャートを用いて説明する。

【0117】

図11のタイムチャートでは先行RQとしてMU20へのロード命令を1と表示、後続RQとしてMU20へのロード命令を2と表示している。

【0118】

時刻T1で、CPU11において、先行RQが発行される。T2で、先行RQは削減手段120で受け取られる。ここでは差分情報は生成されない。

【0119】

T3〜T4で、先行RQは、Pパケット手段130において2個のパケットに分解される。1stパケットはT3で、2ndパケットはT4でネットワーク手段3へ送られる。

【0120】

T4〜T5で、先行RQは、ネットワーク手段3において2個のパケットをMU20へ送られる。1stパケットはT4で、2ndパケットはT5でMU20へ送られる。

【0121】

T5〜T6で、先行RQは、Mパケット手段201において受け取られる。T5で1stパケットが、T6で2ndパケットが受け取られる。

【0122】

一方T3で、CPU11において、後続RQが発行され、T4で削減手段120に受け取られ、RQ情報を削減可能と判断され、差分情報が生成される。

【0123】

T5で、後続RQは、Pパケット手段130に送られ、1stパケットのみ生成される。

【0124】

T6で、先行RQはパケットに分解される前のRQに合成される。後続RQのパケットはネットワーク手段3において、MU20へ送られる。

【0125】

T7で、先行RQは、復元手段202に送られる。先行RQは復元手段202にて変更は加えられない。後続RQは、Mパケット手段201に送られ、パケットに分解される前のRQを合成する。後続RQは1個のパケットのみである。

【0126】

T8で、先行RQはメモリアクセス手段203にてメモリからデータを読み出す(以降 該読み出しデータを先行データとする)。後続RQは、復元手段202において該後続RQの差分情報と先行RQからRQを再生する。

【0127】

T9で、先行RQデータは転送制御手段204に送られ、Mパケット手段201へ転送可能と判断され、これへ送られる。

【0128】

先行データはMパケット手段201において2個のパケットに分解される。

【0129】

後続RQはメモリアクセス手段203にてメモリからデータを読み出す(以降該読み出しデータを後続データとする)。

【0130】

T10で、先行データのパケットがネットワーク手段3に送られる。1stパケットはT10で、2ndパケットはT11でネットワーク手段に送られる。

【0131】

T10で後続データは転送制御手段204に送られる。T10では先行データがMパケット手段201に存在している。このため後続データはMパケット手段201へ送ることが不可能と判断され、データ格納手段2041に格納される。

【0132】

T11で、先行データの2ndパケットがネットワーク手段3に送られる。後続データはデータ格納手段2041から読み出され、Mパケット手段201へ送られ先行データと同様に2個のパケットに分割される。

【0133】

T12で、先行データはPパケット手段130でパケット分割前のデータに合成される。後続データは1stパケットがネットワーク手段3に送られる。

【0134】

T13で、先行データはCPU11へ送られ、先行RQの処理を終える。後続データは、2ndパケットがネットワーク手段3へ送られる。

【0135】

T14で、後続データはPパケット手段130でパケット分割前のデータに合成される。

【0136】

T15で、後続データはCPU11へ送られ、後続RQの処理を終える。

【0137】

次に、本実施例のデータ処理システムにおいて、MU20のメモリへストアする処理について説明する。

【0138】

図2を参照し、CPU11ではメモリストア命令が発行される。CPU11では該ストア命令によりメモリアクセス要求(以下ストアRQとする)が生成される。

【0139】

該命令のアドレスによりCPUポート140を経由して、該ストアRQは削減手段120に送られる。該ストアRQのフォーマットは、ロードRQと同様である。(図6(a)参照)。

【0140】

該ストアRQに対応するストアデータ(以下ストアデータ)は、該ストアRQと同じデータ幅を持ち、該ストアRQと同時に削減手段120に送られる。

【0141】

該ストアデータは、削減手段120では何も加工されず、該RQと同時に、Pパケット手段130に送られる。ストアデータのフォーマットは図6(c)に示す。

【0142】

削減手段120では、該ストアRQに対して前記のロードRQと同様の処理を行う。削減手段120の処理について図9のフローチャートを用いて説明する。

【0143】

ステップA1〜A7までの処理はメモリロード命令と同様である。Pパケット手段130では、該ストアRQに対して、前記のロードRQと同様の処理を行う。

【0144】

該ストアRQのパケットはPUポート150を経由し、ネットワーク手段3へ1stパケット、2ndパケットの順に連続して送られる。

【0145】

該ストアRQに対応するストアデータは差分識別フラグの値に関わらず、つねに2個のパケットに分割される。

【0146】

ストアパケットのフォーマットは図7(c)に示す。差分識別フラグが0の場合、ストアデータの前半部分は3rdパケット、後半部分は4thパケットとなる。

【0147】

差分識別フラグが1の場合、ストアデータの前半部分は2ndパケット、後半部分は3rdパケットとなる。

【0148】

各パケットはPUポート150を経由して、ネットワーク手段3へ送られる。1st〜4thまたは1st〜3rdパケットは常に連続している。

【0149】

ネットワーク手段3において、PUポート150経由でPU1−0から送られたパケットを、MUポート205経由でMU0に送る。

【0150】

Mパケット手段201において、ネットワーク手段3から送られた3つまたは4つに分解されたパケットから、パケットに分解前のRQとストアデータを合成する。合成する処理は差分識別フラグの値によって異なる。

【0151】

差分識別フラグが0の場合、図7(a)に示されている1st、2ndのパケットから図8に示されているRQを、図7(c)に示されている3rd、4thパケットから、図6(c)に示されているストアデータをそれぞれ合成する。

【0152】

合成されたRQの差別識別フラグは0とする。また、RQのMU番号のビットは削除される。

【0153】

差分識別フラグが1の場合、図7(b)に示されている1stパケットを図6(b)に示されているRQに、図7(c)に示されている2nd、3rdパケットから図6(c)に示されているストアデータを合成する。

【0154】

合成されたRQの差別識別フラグは1とする。合成されたRQは、復元手段202へ送られる。

【0155】

復元手段202では、該ストアRQに対して、前記のロードRQと同様の処理を行う。Mパケット手段201から送られたストアデータはそのままメモリアクセス手段203へ送られる。

【0156】

復元手段202の処理について図10のフローチャートを用いて説明する。

ステップB1からB6までの処理はロード命令と同様である。

【0157】

メモリアクセス手段203では、復元手段202から送られたRQのRQコマンドに従い、RAM内の、MU内アドレスの示すアドレスにストアデータを書き込み一連の処理を終える。

【0158】

CPU11がストア命令を発行した際の処理を、図11のタイムチャートを用いて説明する。

【0159】

図11のタイムチャートでは、MU20への先行RQと該RQに対応するストアデータ(以下 先行ストアデータ)を3番、MU20への後続RQと該RQに対応するストアデータ(以下 後続ストアデータ)を4番としている。

【0160】

T10で、CPU11において、先行RQと先行ストアデータが発行される。

【0161】

T11で、先行RQと先行ストアデータは削減手段120で受け取られる。ここでは差分情報は生成されない。

【0162】

T12〜T15で、先行RQと先行ストアデータは、Pパケット手段130において、それぞれ2個のパケット、計4個としてネットワーク手段3へ送られる。

【0163】

T13〜T16で、先行RQと先行ストアデータの4個のパケットは、ネットワーク手段3からMU20へ送られる。

【0164】

T14〜T17で、先行RQと先行ストアデータの4個のパケットは、Mパケット手段201において受け取られる。T17で、4個のパケットから元の先行RQと先行ストアデータが合成される。

【0165】

T14で、後続RQと後続ストアデータはCPU11から発行され、T15で、後続RQは、削減手段120に受け取られ、アドレス情報を削減可能と判断され、差分情報が生成される。

【0166】

T16〜T18で、Pパケット手段130において、後続RQから1個のパケット(1stパケット)が生成され、後続ストアデータは2個のパケット(2ndパケット、3rdパケット)に分割される。

【0167】

T17〜T19で、後続RQと後続ストアデータの3個のパケットは、ネットワーク手段3からMU20へ送られる。

【0168】

T18で、先行RQと先行ストアデータは、復元手段202に送られる。先行RQは復元手段202にて変更は加えられない。T18〜T20で、後続RQと後続ストアデータの3個のパケットは、Mパケット手段201において受け取られ、T20で、3個のパケットから元の後続RQと後続ストアデータが合成される。

【0169】

T19で、先行RQと先行ストアデータは、メモリアクセス手段203に送られ、メモリにデータを書き込む。

【0170】

T21で、後続RQは、復元手段202において該後続RQの差分情報と先行RQからRQを再生する。

【0171】

T22で、後続RQと先行ストアデータは、メモリアクセス手段203に送られ、メモリにデータを書き込む。

【0172】

次に、本実施例のデータ処理システムにおいて、CPU11からMU20へのロードRQが4個、その後ストアRQが4個、その後ロードRQが1個処理されるケースについて図12のタイムチャートを用いて説明する。

【0173】

T1で、最初のロードRQ(以下ロードRQ1とし、タイムチャートでは1と表示)がCPU11から発行される。該RQの処理は前記のメモリロード命令の先行RQと同様である。

【0174】

T3で、2番目のロードRQ(同様にロードRQ2とし2と表示)がCPU11から発行される。該RQの処理は前記のメモリロード命令の後続RQと同様である。

【0175】

T4で、3番目のロードRQ(同様にロードRQ3とし3と表示)がCPU11から発行される。該RQの処理は、前記ロードRQ2と同様である。ただし、T11でデータ格納手段2041に格納され、T13でMパケット手段201へ送られる。

【0176】

T5で、4番目のロードRQ(同様にロードRQ4とし4と表示)がCPU11から発行される。該RQの処理は、前記ロードRQ3と同様である。但し、T12でデータ格納手段2041に格納され、T15でMパケット手段201へ送られる。

【0177】

ロードRQ1〜4のデータがCPU11に到着するのは、それぞれT13、T15、T17、T19である。

【0178】

T6で、最初のストアRQ(同様にストアRQ1とし5と表示)がCPU11から発行される。該RQの処理は前記のメモリストア命令の先行RQと同様である。

【0179】

T10で、2番目のストアRQ(同様にストアRQ2とし6と表示)がCPU11から発行される。該RQの処理は前記のメモリストア命令の後続RQと同様である。

【0180】

T13で、3番目のストアRQ(同様にストアRQ3とし7と表示)が、T16で4番目のストアRQ(同様にストアRQ4とし8と表示)がそれぞれCPU11から発行される。これらのRQの処理は前記のメモリストア命令の後続RQと同様である。

【0181】

T19で、5番目のロードRQ(同様にロードRQ5とし9と表示)がCPU11から発行される。該RQの処理は前記メモリロード命令の先行RQと同様である。ロードRQ5のデータがCPU11の到着するのはT31である。

【0182】

図12のタイムチャートによると、CPU11がロードRQ1(図12のタイムチャートでは1のRQ)を発行してから、ロードRQ5に対応するロードデータを(図12のタイムチャートでは9のロードデータ)CPU11が受け取るまでの処理に要する時間は31Tである。

【0183】

また、ロードRQ1からロードRQ5までの9個のRQにおいて、1タイミングに処理できるRQ数(以下スループットとする)は、CPU11にロードRQ1のロードデータがCPU11に到着してから、CPU11にロード5のロードデータが到着するまでの時間間隔が19Tなので、9RQ/19T=0.47RQ/Tである。

【0184】

後述の参考例のスループットは、0.36RQ/Tであり、本実施例はスループットが充分に向上できるといえる。

【0185】

尚、ロードデータ等の返送先情報は、1stRQパケットに付随して受信するのでなく、ネットワーク手段3が1stRQパケットのMUフィールドに差し替えて乗せるようにする例もある。

【0186】

又、常時、各PUポートが自由に任意のMUにアクセスする例では、MRQ保持手段2023のRQ情報をPUポート毎の4組にし、1stRQパケットのMUフィールドや、差分パケットの上位等の2ビットでPUポート番号を受信するようにすればよい。

【0187】

次に本実施形態でPUを複数とした第2実施例について説明する。図13は本発明のデータ処理システムの第2実施例の構成を示したブロック図である。

【0188】

図13のシステムは、PUの数を例えば2とし、他の数は第1実施例と同様である。

【0189】

本実施例では、PU1−0、1−1は並列に動作し、異なるPUが相前後して同じMUにアクセス出来る様に、各MUの復元手段202のMRQ保持手段2023はPU毎にRQ情報を保持している。

【0190】

又、ロードデータ等の返送先情報には、PU内ポート番号の他PU番号(本例では1ビット)を含む。

【0191】

PU番号については、1stRQパケットや差分パケットに付随して受取り、PUポートは1stRQパケットのMUフィールドを流用しMUが受信する。

【0192】

復元手段202では、差分情報を受けると、付随するPU番号で、RQ情報を選択し、これに差分情報を反映しRQ情報や、返送先PUポート番号を再生する。

【0193】

MRQ保持手段2023のRQ情報更新(上書き)も、PU番号対応のRQ情報を更新する。これら以外は第1実施例に同様である。

【0194】

尚、PUが複数で並列にMUアクセスする場合でも、各PUに排他的にアクセス先MUを割付られる場合には、各MUは第1実施例と同様の構成となる。

【0195】

以上の本発明の実施例の説明では、パケットフラグを1ビットとしたが、RQ情報を3個以上のパケットに分解して送信する場合は、複数ビットのパケットフラグで順番を示す様にしてもよい。

【0196】

本発明のデータ処理システムは、PU、MUがそれぞれ1〜2枚の大型ボードレベルで全体が、1筐体の装置であってもよいし、PU、MUそれぞれが1筐体の装置であってもよい。

【0197】

尚、ネットワーク手段は、スイッチ機能を持つ装置の他、バスであってもよい。またLAN等であってもよい。

【0198】

本発明は、要求装置のメモリアクセスに伴う、通信量を低減したい場合には、1対1の構成でも有効である。

【0199】

次に本発明の実施例のスループットが高くなることを説明(証明)するために、第1実施例の特に特徴とする部分を含まない、参考例の説明をする。

【0200】

図14に、各処理装置が複数の主記憶装置にアクセス出来る、参考のデータ処理システムを示す。

【0201】

このデータ処理システムは、メモリアクセスを行う複数のCPUポートを持つCPUを含むPU(処理装置)4−0〜4−kと、一つ以上のすべて同型のMU(主記憶装置)50〜5mと、該PUと該MUを接続するネットワーク手段3で構成される。

【0202】

PU4−0とネットワーク手段3とは、PUポート150〜15nでそれぞれ接続され、各MUとネットワーク手段3とはMUポート205〜2m5で接続されている。

【0203】

ここでは一つのPUポート(例えばPUポート150)とネットワーク手段3間の転送性能と、一つのMUポート(例えばMUポート205)ネットワーク手段3間の転送性能は等しいとする。ここではk=0、n=3、m=3とする。

【0204】

PU4−0は、メモリアクセスを行う複数(ここでは4とする)のCPUポート140〜143を持ち、ロードRQ(ロード要求)、ストアRQ(ストア要求)、該ストアRQに対応するストアデータを該CPUポート140〜143に発行するCPU11と、該CPUポート140〜143に対応し、該RQを2つのパケットに分解し1stパケット、2ndパケットとして、また、該ストアデータを2つのパケットに分解し3rdパケット、4thパケットとしてPUポート150へ送るパケット手段130とで構成される。

【0205】

CPU11はパケット手段130〜133がRQ受け取り可能な時にRQを発行するものとする。

【0206】

PU11が発行するRQのフォーマットを図6(a)に示す。RQはRQコマンドとアクセス先の主記憶装置を示すMU番号とMU内アドレスから構成されているとする。

【0207】

パケット手段130〜133からPUポート150〜153へ送られるパケットのフォーマットを図7(d)、(c)に示す。

【0208】

図7(d)は1stパケット、2ndパケットを示し、本発明の実施形態のパケット図7(a)の差分識別フラグが無いものと同様とする。

【0209】

図7(c)はストアデータの3rd、4thパケットを示し、本発明の実施形態のパケットと同様である。

【0210】

全て同型のMU(ここでは代表してMU50)は、MUポート205を経由してネットワーク手段3から送られてきた複数のパケットのうち、1stパケット、2ndパケットから元のRQと、3rdパケットと4thパケットから元のストアデータを合成しメモリアクセス手段203へ送り、メモリアクセス手段203からのロードデータを2つのパケットに分解しMUポート203を経由してネットワーク手段3へ送るMパケット手段201と、Mパケット手段201からのRQによりメモリアクセスを行い、ロードデータをMパケット手段201へ送るメモリアクセス手段203と、RAM(図示せず)で構成される。

【0211】

参考例のロードRQの動作は、本発明の実施形態において、ロードRQの動作説明の先行RQと同様である。

【0212】

参考例のロードRQが2個連続した場合、該2個のロードRQの動作は、本発明の実施の形態において、ロードRQの動作説明の先行RQと同様である。

【0213】

参考例において、同一MU(ここではMU50とする)へのロードRQが2個連続した場合の動作を、図15のタームチャートを用いて説明する。

【0214】

T1で、先行RQが発行される。以降、本発明の実施の形態におけるロードRQの動作説明の先行RQと同様である。

【0215】

T3で、後続RQが発行される。以降、本発明の実施の形態におけるロードRQの動作説明の先行RQと同様である。

【0216】

T11で先行RQのロードデータ、T13で後続RQのロードデータがCPU11に到着する。

【0217】

次に、本例において、同一MU(ここではMU50とする)へのストアRQが2個連続した場合動作を、図15のタームチャートを用いて説明する。

【0218】

T10で、先行RQが発行される。以降、本発明の実施の形態におけるストアRQの動作説明の先行RQと同様である。

【0219】

T14で、後続RQが発行される。以降、本発明の実施の形態におけるストアRQの動作説明の先行RQと同様である。

【0220】

T19で先行RQのストアデータが、T23で後続RQのストアデータがメモリに書き込まれる。

【0221】

本例では、ロードRQ、ストアRQ共に、先行RQと後続RQは同様の動作となる。

【0222】

次に、本例において、CPU11からMU20へのロードRQが4個、その後ストアRQが4個、その後ロードRQが1個処理されるケースについて、図16のタイムチャートを用いて説明する。

【0223】

T1で、最初のロードRQ(ロードRQ1とし1と表示)がCPU11から発行される。

【0224】

以降の該RQの処理は、本発明の実施の形態のロードRQの先行RQと同様である。

【0225】

T3、T5、T7で、2番目、3番目、4番目のロードRQがCPU11から発行される。(それぞれロードRQ2、ロードRQ3,ロードRQ4とし、タイムチャートではそれぞれ2、3、4と表示される。)

以降の処理は、それぞれ本発明の実施の形態のロードRQの先行RQと同様である。

【0226】

T11、T13、T15、T17で、ロードRQ1、ロードRQ2、ロードRQ3、ロードRQ4のロードデータがそれぞれCPU11に到着する。

【0227】

T9で、最初のストアRQ(ストアRQ1とし5と表示)がCPU11から発行される。

【0228】

以降の該RQの処理は、本発明の実施の形態のストアRQの先行RQと同様である。

【0229】

T13、T17、T21で、2番目、3番目、4番目のストアRQがCPU11から発行される。(それぞれストアRQ2、ストアRQ3,ストアRQ4とし、タイムチャートではそれぞれ6、7、8と表示される。)

以降の処理は、それぞれ本発明の実施の形態のストアRQの先行RQと同様である。

【0230】

T16、T20、T24、T28で、ストアRQ2、ストアRQ3,ストアRQ4のストアデータをそれぞれメモリに書き込む。

【0231】

T25で、5番目のロードRQ(以下ロードRQ5とする。タイムチャートでは9と表示する。)がCPU11から発行される。

【0232】

以降の該RQの処理は、本発明の実施の形態のロードRQの先行RQと同様である。T35で、ロードRQ5のロードデータがCPU11に到着する。

【0233】

図16のタイムチャートによると、本例において、CPU11がロードRQ1を発行してからロードRQ5のロードデータがCPU11に到着するまでに要する時間は、35Tである。

【0234】

また、ロードRQ1からロードRQ5までの9個のRQにおいて、1タイミングに処理できるRQ数(以下スループットとする)は、CPU11にロードRQ1のロードデータがCPU11に到着してから、CPU11にロード5のロードデータが到着するまでの時間間隔が25Tなので、9RQ/25T=0.36RQ/Tである。

【図面の簡単な説明】

【0235】

【図1】本発明の実施形態の一般形を示すブロック図。

【図2】本発明の第1実施例の構成を示したブロック図。

【図3】図2の削減手段120の詳細ブロック図。

【図4】図2の復元手段202の詳細ブロック図。

【図5】図2の転送制御手段204の詳細ブロック図。

【図6】(a)は本発明の第1実施例のRQ情報のフォーマットを示し、(b)は本発明の第1実施例の差分情報フォーマットを示し、(c)本発明の第1実施例のストアデータフォーマットを示す図。

【図7】(a)、(b)、(c)はそれぞれ本発明の第1実施例の、RQ情報パケットのフォーマット、差分情報パケットのフォーマット、ストアデータパケットのフォーマットを示す図。(d)は参考例のRQパケットのフォーマットを示す図。

【図8】本発明の第1実施例の合成されたRQ情報を示した図。

【図9】本発明の第1実施例の削減手段120の動作を示したフローチャート。

【図10】本発明の第1実施例の復元手段202の動作を示したフローチャート。

【図11】本発明の第1実施例のロードRQ、ストアRQのタイムチャート。

【図12】本発明の第1実施例のロードRQ、ストアRQ混在時のタイムチャート。

【図13】本発明の第2実施例の構成を示したブロック図。

【図14】参考例のデータ処理システムを示したブロック図。

【図15】参考例のロードRQ、ストアRQのタイムチャート。

【図16】参考例のロードRQ、ストアRQ混在時のタイムチャート。

【符号の説明】

【0236】

1−0〜1−k PU

11 CPU

120〜12n 削減手段

1201 PRQ保持手段

1202 差分情報生成手段

1203 RQ構成手段

130〜13n Pパケット手段

140〜14n CPUポート

150〜15n PUポート

20〜2m MU

201 Mパケット手段

202 復元手段

2021 情報再生手段

2022 RQ再生手段

2023 MRQ保持手段

203 メモリアクセス手段

204 転送制御手段

2041 データ格納手段

2042 データ制御手段

205〜2m5 MUポート

3 ネットワーク手段

【技術分野】

【0001】

本発明はデータ処理システム、処理装置、記憶装置、及びメモリアクセス制御方法に関し、特に、複数の処理装置がネットワーク手段等を通じ複数の記憶装置にアクセスする際のネットワーク手段の負荷を軽減したデータ処理システム、処理装置、記憶装置、及びメモリアクセス制御方法に関する。

【背景技術】

【0002】

複数の演算装置がネットワーク装置を通じて、複数の主記憶装置にアクセスする技術の第1の従来例として、次のネットワーク装置がある。

【0003】

このネットワーク装置は、複数の演算装置と複数の主記憶装置を接続するネットワーク装置において、複数の演算装置から主記憶の同一アドレスに対する複数の読出リクエスト、または複数の書込リクエストがあると、リクエストそれぞれを1つのリクエストに圧縮する機能と、該リクエストに対する主記憶からのリプライリクエストを前記圧縮対象の複数の演算装置に向けて展開する機能を有する(特許文献1参照。)。

【0004】

また、主記憶装置にアクセスする技術の第2の従来例として、主記憶の同一アドレスに対する複数の書き込みリクエストを一つの書き込みリクエストに縮退する縮退ストア制御装置がある(特許文献2参照。)。

【0005】

【特許文献1】特開平9−44459(第1ページ)

【特許文献2】特開平6−103147(第1ページ)

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記第1の従来例では、システム性能の低下要因である、各リクエストやストアデータによるネットワークの過負荷は、幾らか軽減されるが、リクエストの圧縮が同一アドレスに限られるという問題点がある。

【0007】

その理由は、複数の主記憶装置のうち、同一の主記憶装置へのアドレスのことなる複数のリクエストを圧縮する機能を有しないからである。

【0008】

この従来例は、複数の演算装置からの同一アドレスへのリクエストを圧縮する技術であるが、本発明では同一CPUからの同一主記憶装置へのリクエストの場合に圧縮が可能となる点で相違がある。

【0009】

次に、上記第2の従来例には、次の様な問題点がある。第1の問題点は、読み出しリクエストを縮退することが出来ないことである。

【0010】

その理由は、読み出しリクエストについてのみ縮退可能か判断する手段を備えていないからである。

【0011】

第2の問題点は、物理的に分割された複数の主記憶装置のうち、同一の主記憶装置への複数のリクエストを縮退することが出来ないことである。

【0012】

その理由は、メモリ構成を参照して、主記憶装置毎に縮退を判断する手段を有していないからである。

【0013】

この様に、従来例ではCPUのメモリアクセス負荷が高くなると、CPU内の演算処理がロードデータを待つケースが発生し、システムの性能を低下させる要因になっていた。

【課題を解決するための手段】

【0014】

本発明の第1のデータ処理システムは、コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えた処理装置と、前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えた記憶装置とを含むことを特徴とする。

【0015】

本発明の第2のデータ処理システムは、一つ以上の処理装置と複数の記憶装置とこれらを接続するネットワーク手段を含むデータ処理システムであって、前記処理装置には、メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報とを比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行の要求情報として保持しておく要求情報削減手段と、前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する処理装置パケット手段とを備え、前記記憶装置には、メモリ部と、これの読出、書込アクセスを行うメモリアクセス手段と、ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置パケット手段と、差分フラグがオンであれば、差分情報パケットと自装置に保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とする。

【0016】

本発明の第3のデータ処理システムは、前記第2のデータ処理システムであって、前記処理装置の処理装置パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手段と、ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有し、前記記憶装置がメモリアクセス手段からロードデータを受取り、記憶装置パケット手段に転送する手段も備え、記憶装置パケット手段が、複数パケットで受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする。

【0017】

本発明の第4のデータ処理システムは、前記第3のデータ処理システムであって、前記処理装置が、メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする。

【0018】

本発明の第5のデータ処理システムは、前記第2、又は第4のデータ処理システムであって、前記記憶装置の復元手段が先行の要求情報を処理装置毎に保持し、差分情報パケットに含む或いは付随する処理装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、これをメモリアクセス手段に渡し、またその処理装置の先行要求情報としておくことを特徴とする。

【0019】

本発明の第1の処理装置は、コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えたことを特徴とする。

【0020】

本発明の第2の処理装置は、メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行する要求情報として保持しておく要求情報削減手段と、前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、ネットワーク手段を通じ記憶装置に送信するパケット手段とを備えたことを特徴とする。

【0021】

本発明の第3の処理装置は、前記第2の処理装置であって、前記パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のパケットに変換し、要求情報や差分情報のパケットに続いて送出する手段と、ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有することを特徴とする。

【0022】

本発明の第4の処理装置は、前記第3の処理装置であって、前記メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする。

【0023】

本発明の第1の記憶装置は、アクセス要求情報に関する差分情報パケットを受信すると、これの差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えたことを特徴とする。

【0024】

本発明の第2の記憶装置は、メモリ部と、これの読出やこれへの書込を行うメモリアクセス手段と、ネットワーク手段を通じ、メモリアクセスの要求装置よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻すパケット手段と、差分フラグがオンであれば、差分情報パケットと保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とする。

【0025】

本発明の第3の記憶装置は、前記第2の記憶装置であって、メモリアクセス手段からロードデータを受取り、パケット手段に転送する手段も備え、前記パケット手段が、複数パケットとして受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする。

【0026】

本発明の第4の記憶装置は、前記第2、又は第3の記憶装置であって、前記復元手段が先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、またその要求装置の先行の要求情報としておくことを特徴とする。

【0027】

本発明の第1のメモリアクセス制御方法は、メモリアクセスを要求する装置に、要求元からコマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手順を備え、記憶装置に、前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手順を備えたことを特徴とする。

【0028】

本発明の第2のメモリアクセス制御方法は、一つ以上のメモリアクセス要求装置と複数の記憶装置とこれらを接続するネットワーク手段を含むシステムのメモリアクセス制御方法であって、前記要求装置が、メモリアクセス要求元よりコマンドとアクセスアドレスを含む要求情報を受け、これと先行する要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力する要求情報削減手順と、前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグより前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する要求側パケット手順とを備え、前記記憶装置が、ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置側パケット手順と、差分フラグがオンであれば、差分情報パケットと、保持している先行の要求情報から今回の要求情報を作成する復元手順と、要求情報でメモリ部の読出、書込アクセスを行うメモリアクセス手順とを備えたことを特徴とする。

【0029】

本発明の第3のメモリアクセス制御方法は、前記第2のメモリアクセス制御方法であって、前記要求側パケット手順が、要求元のストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手順と、ネットワーク手段より複数のパケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手順を有し、前記記憶装置が、読み出したロードデータを、記憶装置側パケット手順に渡す手順も備え、記憶装置側パケット手順が、複数のパケットとして受信したストアデータを、もとの一つのデータに戻す手順と、ロードデータを複数のパケットにし、ネットワーク手段を通じ要求装置に返送する手順を有することを特徴とする。

【0030】

本発明の第4のメモリアクセス制御方法は、前記第2、又は第3のメモリアクセス制御方法であって、前記記憶装置の復元手順が、先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に対応する先行の要求情報を選択し、これと差分情報パケットとから今回の要求情報を作成し、これをメモリアクセス手順に渡し、またその要求装置の先行の要求情報として保持しておくことを特徴とする。

【発明の効果】

【0031】

第一の効果は、メモリロード命令、メモリストア命令のレイテンシを短縮し、システム性能を向上させることができる。

【0032】

その理由は、削減手段と復元手段によりPUからMUへ転送するパケット数を削減することで、後続RQの処理を早く開始する為である。

【0033】

第二の効果は、メモリロード命令、メモリストア命令のスループットを高め、システム性能を向上させることができる。

【0034】

その理由は、差分情報を用いることで、PUからMUへ短時間でより多くの情報を送ることが可能となる為である。

【0035】

第三の効果は、PUポートとMUポートの信号本数を大幅に削減する事が可能であり、システムのHW量を削減できる。

【0036】

その理由は、PU、MUそれぞれにRQ及びロードデータまたはストアデータをパケットに分割または合成を可能とする手段を持ち、パケットによりPU−MU間転送を行うことで、同時に転送する情報量を減らすことができる為である。

【発明を実施するための最良の形態】

【0037】

次に、本発明を実施するための最良の形態について図面を参照して詳細に説明する。

図1は、本発明の実施形態の一般形を示すブロック図である。

【0038】

本発明の実施形態は、メモリアクセスを行う複数のCPUポート140〜14nを持つCPUを含む複数のPU(処理装置)1−0〜1−kと、一つ以上のすべて同型のMU(主記憶装置)20〜2mと、該PUと該MUを接続するネットワーク手段3で構成される。

【0039】

PU1−0とネットワーク手段3とは、PUポート150〜15nでそれぞれ接続され、各MUとネットワーク手段3とはMUポート205〜2m5で接続されている。

【0040】

本実施形態では、一つのPUポート(例えばPUポート150)とネットワーク手段3間の転送性能と、一つのMUポート(例えばMUポート205)とネットワーク手段3間の転送性能は等しいと仮定する。

【0041】

次に本実施形態でPUを1つとした第1実施例について説明する。図2は本発明のデータ処理システムの第1実施例の構成を示したブロック図である。

【0042】

図2のシステムは、図1のシステムでk=0、n=3、m=3として、即ち、PUの数を1、MUの数を4、CPUポート数を4、PUポートの数を4として構成した例である。

【0043】

PU1−0は、CPU11と、削減手段120〜123と、Pパケット手段(処理装置側パケット手段)130〜133と、CPUポート140〜143と、PUポート150〜153で構成される。

【0044】

CPU(中央演算処理装置)11は、

(1)ロードRQ若しくはストアRQ(以下ロードRQ、ストアRQの総称をRQとする)によりメモリへのアクセスを行う。

(2)4個のCPUポート140〜143を持ち、該CPUポート140〜143は、接続先である後述の削減手段120〜123からのRQ受け取り可能な通知により、ロードRQ、または、ストアRQと該ストアRQに対応するストアデータを送る。

【0045】

削減手段120〜123は、

(1)CPU11のCPUポート140〜143にそれぞれ対応している。

(2)CPU11からのRQと、該RQより先行するRQを比較して、該RQの情報量が削減可能な場合に該RQの情報量を削減して後述のPパケット手段130〜133に送る。

(3)CPU11からのRQを一時的に保持する。

【0046】

(4)該RQが削減可能な場合、RQを再構成する。

(5)CPU11からのストアRQに対応し、ストアデータをPパケット手段130〜133へ送る。

(6)CPU11に対し、RQを受け取ることができることを通知する。

【0047】

Pパケット手段130〜133は、

(1)CPU11のCPUポート140〜143にそれぞれ対応している。

(2)削減手段120〜123からのRQもしくはストアデータからパケットを生成し、PUポート150〜153を経由してネットワーク手段3へ送る。

(3)ネットワーク手段3からPUポート150〜153を経由して受け取った複数のパケットを元のデータに合成する。

【0048】

PUポート150〜153は、

(1)CPU11のCPUポート140〜143にそれぞれ対応している。

(2)PU1−0とネットワーク手段3間でパケットの送受信を行う。

【0049】

全て同型の削減手段(ここでは代表して削減手段120)について、図3を用いて説明する。

【0050】

削減手段120は、PRQ保持手段1201と、差分情報生成手段1202と、RQ構成手段1203とで構成される。

【0051】

PRQ保持手段1201は、

(1)CPU11からのRQを一時的に保持する。

(2)保存しているRQの情報を、後述の差分情報生成手段1202へ送る。

【0052】

差分情報生成手段1202は、

(1)CPU11からのRQのRQコマンドと、該RQより1つ前に処理され既にPRQ保持手段1201に保持されている先行RQ(先行するRQ)のRQコマンドを比較して、同じ場合は差分識別フラグを1とし、異なる場合は該フラグを0とする。

(2)CPU11からのRQのMU内アドレスと、PRQ保持手段1201に保持されている先行RQのMU内アドレスから差分情報を生成する。

(3)差分識別フラグと差分情報をRQ構成手段1203へ送る。

【0053】

RQ構成手段1203は、

(1)CPU11からRQを受け取る。

(2)差分情報生成手段1202からの差分識別フラグが0の場合、CPU11からのRQをそのままPパケット手段130へ送る。該フラグが1の場合、差分情報生成手段1202からの識別フラグと差分情報で構成されたRQを作り、Pパケット手段130に送り、CPU11からのRQを破棄する。

(3)CPU11からのストアデータをそのままPパケット手段130へ送る。

【0054】

全ての同型のMU(ここでは代表してMU20)について図2を用いて説明する。MU20は、Mパケット手段201と、復元手段202と、メモリアクセス手段203と、転送制御手段204と、MUポート205と、RAM(図示せず)で構成される。

【0055】

Mパケット手段(記憶装置側パケット手段)201は、

(1)MUポート205を経由でネットワーク手段3から受け取った複数のパケットから元のRQ若しくはストアデータを生成する。

(2)転送制御手段204からのロードデータを複数(実施例では2個)のパケットに分解しMUポート205を経由しネットワーク手段3へ送る。

(3)転送制御手段204に対し、ロードデータを受け取ることが可能なことを通知する。

【0056】

復元手段202は、

(1)Mパケット手段201から受け取ったRQの差分識別フラグの値を参照し、Mパケット手段201から受け取ったRQの差分情報と、先行RQのMU内アドレスから該RQの元のMU内アドレスを再生する。

(2)Mパケット手段201から受け取ったRQの差分識別フラグの値を参照し、該RQをそのままメモリアクセス手段203へ送るか、もしくは1)の処理で再生したRQをメモリアクセス手段203へ送る。

(3)メモリアクセス手段203へ送ったRQを一時的に保持する。

(4)ストアデータをそのままメモリアクセス手段203へ送る。

【0057】

メモリアクセス手段203は、

(1)復元手段202からのRQと、ストアデータが有る場合はストアデータを受け取る。

(2)該RQのRQコマンドに従い、MU内アドレスで指定されたRAMのアドレスをアクセスする。

(3)該RQがロードRQの場合、RAMから読み出したデータ(以下ロードデータとする)を転送制御手段204へ送る。

【0058】

転送制御手段204は、

(1)メモリアクセス手段203からロードデータを受け取る。

(2)Mパケット手段201がロードデータを受け取ることが可能である通知により、該ロードデータをMパケット手段201へ送る。

(3)Mパケット手段201が該ロードデータ受け取る事ができない場合、該ロードデータを一時的に格納する。

【0059】

復元手段202について図4を用いて説明する。復元手段202は、情報再生手段2021と、RQ再生手段2022と、MRQ保持手段2023で構成される。

【0060】

情報再生手段2021は、

(1)Mパケット手段201から受け取ったRQの差分識別フラグが1の場合、該RQの差分情報と、MRQ保持手段2023内に保持している先行RQのMU内アドレスから、該RQの元のMU内アドレスを再生し、該元のMU内アドレスとRQの再生指示をRQ再生手段2022へ送る。

(2)該フラグが0の場合、何もしない。

【0061】

RQ再生手段2022は、

(1)情報再生手段2021からの再生指示に従い、MRQ保持手段2023に保持されている先行RQのRQコマンドと、情報再生手段2021からのMU内アドレスから、元のRQを再生し、メモリアクセス手段203へ送る。

(2)情報再生手段2021からの再生指示が無い場合、Mパケット手段201から送られたRQを加工せずメモリアクセス手段203へ送る。

(3)メモリアクセス手段203へ送ったRQをMRQ保持手段2023へ送る。

(4)Mパケット手段201からのストアデータをそのままメモリアクセス手段203へ送る。

【0062】

MRQ保持手段2023は、

(1)RQ再生手段2022からのRQを一時的に保持する。

(2)先行RQが保持されている場合、先行RQの情報は、RQ再生手段2022からのRQによって上書きされる。

【0063】

転送制御手段204について図5を用いて説明する。転送制御手段204は、データ格納手段2041と、データ制御手段2042で構成される。

【0064】

データ格納手段2041は、複数のワードで構成される先入れ先出しバッファを持ち、(1)メモリアクセス手段203からロードデータを受け取る。

(2)データ制御手段2042の指示に従い、該バッファにメモリアクセス手段203からのロードデータの格納もしくは読み出しを行う。

(3)データ制御手段2042の指示に従い、Mパケット手段201へロードデータを送る。

【0065】

データ制御手段2042は、

(1)Mパケット手段201が前記ロードデータを受け取り可能な通知がある場合、データ格納手段2041に対し、格納されている最も古いロードデータをMパケット手段201へ送る指示を出す。

(2)Mパケット手段201が前記ロードデータを受け取り可能な通知が無い場合、データ格納手段2041に対し、該ロードデータを格納する指示を出す。

【0066】

尚、ネットワーク手段3のPUポート(PU接続口)では、1stRQパケットのMU番号(主記憶アドレスの上位2ビットで、宛先MUを指定する)をレジスタ等に受け、これで出力先MUポートを決めるが、このレジスタを他のパケットではストローブしないようにし、宛先を保持する。

【0067】

MU番号が、実際のMUの物理番号にアドレス変換されるシステムでも同様である。

【0068】

又、ネットワーク手段3からMUに返送先情報として、1stRQパケットに付随して、2ビットのPUポート識別を受信し、Mパケット手段201,復元手段202を通じ、RQ情報と共に持ち回られメモリアクセス手段203に渡される。MRQ保持手段にもRQ情報と同様に保持され、差分情報パケットのRQでは、RQ情報と同様に再生され、渡される。

【0069】

以降ロードデータと共に持ち回られ、ネットワーク手段のMUポートの上り側に送出される。

【0070】

次に、本実施形態の第1実施例の動作について図面を参照して説明する。

【0071】

また、ネットワーク手段3において、PUポート150〜153の各ポートのそれぞれは、RQのMU番号で指定することで、MUポート205〜235にアクセスできる。

【0072】

しかし、この例では、PUポート150〜153の各ポートは並列動作するが、それぞれが異なるMUにアクセスする(CPUポート140〜143の各ポートが排他的にMU番号を指定する)とする。

【0073】

また、説明は、ある期間、PUポート150とMUポート205、PUポート151とMUポート215、PUポート152とMUポート225、PUポート153とMUポート235、がそれぞれ1対1に接続される例で行う。

【0074】

図2を参照し、先ずMU20のメモリをロードする処理について説明する。CPU11ではメモリロード命令が発行される。CPU11では該ロード命令によりロードRQが生成される。

【0075】

該命令のアドレスによりCPUポート140を経由して、該RQは削減手段120へ送られる。

【0076】

該RQのフォーマットを図6(a)を用いて説明する。該RQはロードを指示するRQコマンド、MU20を指定するMUフィールド、MU20内のアドレスを指定するMU内アドレスフィールドで構成されている。

【0077】

CPU11のロード命令のアドレスはMUフィールドと、MU内アドレスフィールドに変換されている。MUフィールドと、MU内アドレスフィールドを合わせてアドレスフィールドと呼ぶ。

【0078】

削減手段120では、該RQのRQコマンド、アドレスフィールドと、該RQに先行しPRQ保持手段1201に保持されているRQ(以下先行RQ)のRQコマンド、アドレスフィールドとをそれぞれ比較し、RQの転送する情報量を削減可能か判断する。

【0079】

削減可能な場合は、差分情報を生成した後にRQを構成してPパケット手段に送る。

【0080】

削減手段120の処理について図3と、図9のフローチャートを用いて説明する。

【0081】

先ず、RQが削減手段120に入力される(ステップA1)。尚、入力されるRQは図6(a)に示すフォーマットである。

【0082】

差分情報生成手段1202において、該RQと、PRQ保持手段1201に既に保持されている先行RQのRQコマンドが一致し、かつ、MUフィールドが一致している場合、該RQの情報量を削減可能と判断して差分識別フラグを1とし(ステップA2)、ステップA3に進む。

【0083】

一致していない場合、該RQの情報量を削減する事は不可能と判断して差分識別フラグを0とし(ステップA2)、ステップA4に進む。

【0084】

差分情報生成手段1202において、該RQと、PRQ保持手段1201に保持されている先行RQのMU内アドレスフィールドを比較し、次の式に従い差分情報を生成する。

【0085】

差分情報 = 該RQのMU内アドレス − 先行RQのMU内アドレス・・(式1)

差分情報は、正の値、0、負の値となり得る。差分情報生成手段1202は、差分識別フラグと、差分情報をRQ構成手段1203に送る(ステップA3)。尚、図6(b)にRQ構成手段1203に送られる情報を示す。

【0086】

PRQ保持手段1201において、CPU11からの送られたRQを保持する。先行RQは該RQによって上書きされ先行RQに関する情報は破棄される(ステップA4)。

【0087】

RQ構成手段1203において、差分識別フラグを参照し、該フラグが1の場合(ステップA5)、CPU11から送られた図6(a)に示すRQを、差分情報生成手段1202から送られた図6(b)に示す差分情報と差分識別フラグに置き換える(ステップA6)。

【0088】

以降、置き換えられた情報をCPU11から送られたRQとして処理する。RQ構成手段1203は、該RQをPパケット手段130に送る(ステップA7)。

【0089】

図2を参照すると、Pパケット手段130において、削減手段120から送られたRQを1つまたは2つのパケットに分解して、ネットワーク手段3におくる。パケット数は差分識別フラグの値によって異なる。

【0090】

差分識別フラグが0の場合、2個のパケットに分解される。パケットは図7(a)に示す様に、RQコマンド、MU番号、差分識別フラグ、パケットフラグを第一パケット(1stパケット)とし、MU内アドレス、差分識別フラグ(1stパケットのコピー)、パケットフラグを第二パケット(2ndパケット)とする。

【0091】

1stパケットではパケットフラグを1とし、2ndパケットではパケットフラグを0とする。

【0092】

差分識別フラグが1の場合、1個のパケットが生成される。パケットは図7(b)に示す様に、差分情報、差分識別フラグ、パケットフラグとを1stパケットとし、パケットフラグを0とする。

【0093】

これらのパケットはPUポート150を経由し、ネットワーク手段3へ1stパケット、2ndパケットの順に連続して送られる。

【0094】

ネットワーク手段3において、PUポート150経由でPU1−0から送られたパケットを、MUポート205経由でMU20に送る。

【0095】

Mパケット手段201において、MUポート205経由でネットワーク手段3から送られた1つまたは2つのパケットから、パケットに分解前のRQを合成する。合成する処理は差分識別フラグの値によって異なる。

【0096】

差分識別フラグが0の場合、図7(a)に示されている2個のパケットから、図8に示されているRQを合成する。合成されたRQの差別識別フラグは0とする。また、元のRQのMU番号のビットは削除される。

【0097】

差分識別フラグが1の場合、図7(b)に示されている1個のパケットから、図6(b)に示されているRQを合成する。合成されたRQの差別識別フラグは1とする。合成された該RQは、復元手段202へ送られる。

【0098】

復元手段202では、Mパケット手段201から送られたRQの差分識別フラグの値を参照する。

【0099】

該RQの差分識別フラグが0の場合、該RQをそのままメモリアクセス手段203へ送る。

【0100】

該RQの差分識別フラグが1の場合、該RQの差分情報と、MRQ保持手段2023に保持されている先行RQのRQコマンドとMU内アドレスから元のRQを再生する。

【0101】

復元手段202の処理について図4のブロック図と、図10のフローチャートを用いて説明する。

【0102】

RQが復元手段202に入力される。入力されるRQのフォーマットは、差分識別フラグが0の場合は図6(a)、1の場合、図6(b)となる(ステップB1)。

【0103】

情報再生手段2021において、差分識別フラグが参照される。差分識別フラグが0の場合、該RQをRQ再生手段2022に送り、ステップB5へ進み、差分識別フラグが1の場合、ステップB3へ進む(ステップB2)。

【0104】

情報再生手段2021において、Mパケット手段201から送られた該RQの差分情報と、MRQ保持手段2023に保持されている先行RQのMU内アドレスから、次の式により該RQの元のMU内アドレスを算出する。

【0105】

元のMU内アドレス = 先行RQのMU内アドレス + 差分情報・・・(式2)

式2で算出した該RQの元のMU内アドレスと、差分識別フラグはRQ再生手段2022へ送られる(ステップB3)。

【0106】

RQ再生手段2022において、差分識別フラグが1の場合、情報再生手段2021から送られたMU内アドレスと、MRQ保持手段2023に保持されている先行RQのRQコマンドを結合し、元のRQを再生する。

【0107】

ここで再生された該RQのフォーマットは、図8に示す様になる。差分識別フラグは0とする。このフォーマットは、ステップB1で復元手段202に入力された差分識別フラグが0のRQを同じである(ステップB4)。

【0108】

RQ再生手段2022において、ステップB2のみの処理が行われたRQと、ステップB2、B3、B4の処理が行われたRQは同じフォーマットとなる。このRQをMRQ保持手段2023へ送る。

【0109】

MRQ保持手段2023で、該RQは保持される。先行RQは該RQによって上書きされ、先行RQに関する情報は破棄される(ステップB5)。

【0110】

RQ再生手段2022の該RQはメモリアクセス手段203へ送られる(ステップB6)。

【0111】

図2を参照すると、メモリアクセス手段203では、復元手段202から送られたRQのRQコマンドに従い、RAM内の、MU内アドレスの示すアドレスからデータ(以下ロードデータとする)を読み出す。

【0112】

ロードデータは、転送制御手段204へ送られ、データ格納手段2041に格納される。

【0113】

データ制御手段2042は、MUポート205の使用状況からデータ格納手段2041に格納されたデータをネットワーク手段3に送出できるタイミングを判断し、データ格納手段2041に送出指示を送る。

【0114】

データ格納手段2041では、データ制御手段2042からの該指示に従い、格納している最も古いロードデータをネットワーク手段3へ送出する。

【0115】

該ロードデータは、MUポート205、ネットワーク手段3、PUポート150を経由し、該ロードデータのRQを送ったCPU11へ送られ、一連の処理を終える。

【0116】

CPU11がロードRQを発行した際の処理を、図11のタイムチャートを用いて説明する。

【0117】

図11のタイムチャートでは先行RQとしてMU20へのロード命令を1と表示、後続RQとしてMU20へのロード命令を2と表示している。

【0118】

時刻T1で、CPU11において、先行RQが発行される。T2で、先行RQは削減手段120で受け取られる。ここでは差分情報は生成されない。

【0119】

T3〜T4で、先行RQは、Pパケット手段130において2個のパケットに分解される。1stパケットはT3で、2ndパケットはT4でネットワーク手段3へ送られる。

【0120】

T4〜T5で、先行RQは、ネットワーク手段3において2個のパケットをMU20へ送られる。1stパケットはT4で、2ndパケットはT5でMU20へ送られる。

【0121】

T5〜T6で、先行RQは、Mパケット手段201において受け取られる。T5で1stパケットが、T6で2ndパケットが受け取られる。

【0122】

一方T3で、CPU11において、後続RQが発行され、T4で削減手段120に受け取られ、RQ情報を削減可能と判断され、差分情報が生成される。

【0123】

T5で、後続RQは、Pパケット手段130に送られ、1stパケットのみ生成される。

【0124】

T6で、先行RQはパケットに分解される前のRQに合成される。後続RQのパケットはネットワーク手段3において、MU20へ送られる。

【0125】

T7で、先行RQは、復元手段202に送られる。先行RQは復元手段202にて変更は加えられない。後続RQは、Mパケット手段201に送られ、パケットに分解される前のRQを合成する。後続RQは1個のパケットのみである。

【0126】

T8で、先行RQはメモリアクセス手段203にてメモリからデータを読み出す(以降 該読み出しデータを先行データとする)。後続RQは、復元手段202において該後続RQの差分情報と先行RQからRQを再生する。

【0127】

T9で、先行RQデータは転送制御手段204に送られ、Mパケット手段201へ転送可能と判断され、これへ送られる。

【0128】

先行データはMパケット手段201において2個のパケットに分解される。

【0129】

後続RQはメモリアクセス手段203にてメモリからデータを読み出す(以降該読み出しデータを後続データとする)。

【0130】

T10で、先行データのパケットがネットワーク手段3に送られる。1stパケットはT10で、2ndパケットはT11でネットワーク手段に送られる。

【0131】

T10で後続データは転送制御手段204に送られる。T10では先行データがMパケット手段201に存在している。このため後続データはMパケット手段201へ送ることが不可能と判断され、データ格納手段2041に格納される。

【0132】

T11で、先行データの2ndパケットがネットワーク手段3に送られる。後続データはデータ格納手段2041から読み出され、Mパケット手段201へ送られ先行データと同様に2個のパケットに分割される。

【0133】

T12で、先行データはPパケット手段130でパケット分割前のデータに合成される。後続データは1stパケットがネットワーク手段3に送られる。

【0134】

T13で、先行データはCPU11へ送られ、先行RQの処理を終える。後続データは、2ndパケットがネットワーク手段3へ送られる。

【0135】

T14で、後続データはPパケット手段130でパケット分割前のデータに合成される。

【0136】

T15で、後続データはCPU11へ送られ、後続RQの処理を終える。

【0137】

次に、本実施例のデータ処理システムにおいて、MU20のメモリへストアする処理について説明する。

【0138】

図2を参照し、CPU11ではメモリストア命令が発行される。CPU11では該ストア命令によりメモリアクセス要求(以下ストアRQとする)が生成される。

【0139】

該命令のアドレスによりCPUポート140を経由して、該ストアRQは削減手段120に送られる。該ストアRQのフォーマットは、ロードRQと同様である。(図6(a)参照)。

【0140】

該ストアRQに対応するストアデータ(以下ストアデータ)は、該ストアRQと同じデータ幅を持ち、該ストアRQと同時に削減手段120に送られる。

【0141】

該ストアデータは、削減手段120では何も加工されず、該RQと同時に、Pパケット手段130に送られる。ストアデータのフォーマットは図6(c)に示す。

【0142】

削減手段120では、該ストアRQに対して前記のロードRQと同様の処理を行う。削減手段120の処理について図9のフローチャートを用いて説明する。

【0143】

ステップA1〜A7までの処理はメモリロード命令と同様である。Pパケット手段130では、該ストアRQに対して、前記のロードRQと同様の処理を行う。

【0144】

該ストアRQのパケットはPUポート150を経由し、ネットワーク手段3へ1stパケット、2ndパケットの順に連続して送られる。

【0145】

該ストアRQに対応するストアデータは差分識別フラグの値に関わらず、つねに2個のパケットに分割される。

【0146】

ストアパケットのフォーマットは図7(c)に示す。差分識別フラグが0の場合、ストアデータの前半部分は3rdパケット、後半部分は4thパケットとなる。

【0147】

差分識別フラグが1の場合、ストアデータの前半部分は2ndパケット、後半部分は3rdパケットとなる。

【0148】

各パケットはPUポート150を経由して、ネットワーク手段3へ送られる。1st〜4thまたは1st〜3rdパケットは常に連続している。

【0149】

ネットワーク手段3において、PUポート150経由でPU1−0から送られたパケットを、MUポート205経由でMU0に送る。

【0150】

Mパケット手段201において、ネットワーク手段3から送られた3つまたは4つに分解されたパケットから、パケットに分解前のRQとストアデータを合成する。合成する処理は差分識別フラグの値によって異なる。

【0151】

差分識別フラグが0の場合、図7(a)に示されている1st、2ndのパケットから図8に示されているRQを、図7(c)に示されている3rd、4thパケットから、図6(c)に示されているストアデータをそれぞれ合成する。

【0152】

合成されたRQの差別識別フラグは0とする。また、RQのMU番号のビットは削除される。

【0153】

差分識別フラグが1の場合、図7(b)に示されている1stパケットを図6(b)に示されているRQに、図7(c)に示されている2nd、3rdパケットから図6(c)に示されているストアデータを合成する。

【0154】

合成されたRQの差別識別フラグは1とする。合成されたRQは、復元手段202へ送られる。

【0155】

復元手段202では、該ストアRQに対して、前記のロードRQと同様の処理を行う。Mパケット手段201から送られたストアデータはそのままメモリアクセス手段203へ送られる。

【0156】

復元手段202の処理について図10のフローチャートを用いて説明する。

ステップB1からB6までの処理はロード命令と同様である。

【0157】

メモリアクセス手段203では、復元手段202から送られたRQのRQコマンドに従い、RAM内の、MU内アドレスの示すアドレスにストアデータを書き込み一連の処理を終える。

【0158】

CPU11がストア命令を発行した際の処理を、図11のタイムチャートを用いて説明する。

【0159】

図11のタイムチャートでは、MU20への先行RQと該RQに対応するストアデータ(以下 先行ストアデータ)を3番、MU20への後続RQと該RQに対応するストアデータ(以下 後続ストアデータ)を4番としている。

【0160】

T10で、CPU11において、先行RQと先行ストアデータが発行される。

【0161】

T11で、先行RQと先行ストアデータは削減手段120で受け取られる。ここでは差分情報は生成されない。

【0162】

T12〜T15で、先行RQと先行ストアデータは、Pパケット手段130において、それぞれ2個のパケット、計4個としてネットワーク手段3へ送られる。

【0163】

T13〜T16で、先行RQと先行ストアデータの4個のパケットは、ネットワーク手段3からMU20へ送られる。

【0164】

T14〜T17で、先行RQと先行ストアデータの4個のパケットは、Mパケット手段201において受け取られる。T17で、4個のパケットから元の先行RQと先行ストアデータが合成される。

【0165】

T14で、後続RQと後続ストアデータはCPU11から発行され、T15で、後続RQは、削減手段120に受け取られ、アドレス情報を削減可能と判断され、差分情報が生成される。

【0166】

T16〜T18で、Pパケット手段130において、後続RQから1個のパケット(1stパケット)が生成され、後続ストアデータは2個のパケット(2ndパケット、3rdパケット)に分割される。

【0167】

T17〜T19で、後続RQと後続ストアデータの3個のパケットは、ネットワーク手段3からMU20へ送られる。

【0168】

T18で、先行RQと先行ストアデータは、復元手段202に送られる。先行RQは復元手段202にて変更は加えられない。T18〜T20で、後続RQと後続ストアデータの3個のパケットは、Mパケット手段201において受け取られ、T20で、3個のパケットから元の後続RQと後続ストアデータが合成される。

【0169】

T19で、先行RQと先行ストアデータは、メモリアクセス手段203に送られ、メモリにデータを書き込む。

【0170】

T21で、後続RQは、復元手段202において該後続RQの差分情報と先行RQからRQを再生する。

【0171】

T22で、後続RQと先行ストアデータは、メモリアクセス手段203に送られ、メモリにデータを書き込む。

【0172】

次に、本実施例のデータ処理システムにおいて、CPU11からMU20へのロードRQが4個、その後ストアRQが4個、その後ロードRQが1個処理されるケースについて図12のタイムチャートを用いて説明する。

【0173】

T1で、最初のロードRQ(以下ロードRQ1とし、タイムチャートでは1と表示)がCPU11から発行される。該RQの処理は前記のメモリロード命令の先行RQと同様である。

【0174】

T3で、2番目のロードRQ(同様にロードRQ2とし2と表示)がCPU11から発行される。該RQの処理は前記のメモリロード命令の後続RQと同様である。

【0175】

T4で、3番目のロードRQ(同様にロードRQ3とし3と表示)がCPU11から発行される。該RQの処理は、前記ロードRQ2と同様である。ただし、T11でデータ格納手段2041に格納され、T13でMパケット手段201へ送られる。

【0176】

T5で、4番目のロードRQ(同様にロードRQ4とし4と表示)がCPU11から発行される。該RQの処理は、前記ロードRQ3と同様である。但し、T12でデータ格納手段2041に格納され、T15でMパケット手段201へ送られる。

【0177】

ロードRQ1〜4のデータがCPU11に到着するのは、それぞれT13、T15、T17、T19である。

【0178】

T6で、最初のストアRQ(同様にストアRQ1とし5と表示)がCPU11から発行される。該RQの処理は前記のメモリストア命令の先行RQと同様である。

【0179】

T10で、2番目のストアRQ(同様にストアRQ2とし6と表示)がCPU11から発行される。該RQの処理は前記のメモリストア命令の後続RQと同様である。

【0180】

T13で、3番目のストアRQ(同様にストアRQ3とし7と表示)が、T16で4番目のストアRQ(同様にストアRQ4とし8と表示)がそれぞれCPU11から発行される。これらのRQの処理は前記のメモリストア命令の後続RQと同様である。

【0181】

T19で、5番目のロードRQ(同様にロードRQ5とし9と表示)がCPU11から発行される。該RQの処理は前記メモリロード命令の先行RQと同様である。ロードRQ5のデータがCPU11の到着するのはT31である。

【0182】

図12のタイムチャートによると、CPU11がロードRQ1(図12のタイムチャートでは1のRQ)を発行してから、ロードRQ5に対応するロードデータを(図12のタイムチャートでは9のロードデータ)CPU11が受け取るまでの処理に要する時間は31Tである。

【0183】

また、ロードRQ1からロードRQ5までの9個のRQにおいて、1タイミングに処理できるRQ数(以下スループットとする)は、CPU11にロードRQ1のロードデータがCPU11に到着してから、CPU11にロード5のロードデータが到着するまでの時間間隔が19Tなので、9RQ/19T=0.47RQ/Tである。

【0184】

後述の参考例のスループットは、0.36RQ/Tであり、本実施例はスループットが充分に向上できるといえる。

【0185】

尚、ロードデータ等の返送先情報は、1stRQパケットに付随して受信するのでなく、ネットワーク手段3が1stRQパケットのMUフィールドに差し替えて乗せるようにする例もある。

【0186】

又、常時、各PUポートが自由に任意のMUにアクセスする例では、MRQ保持手段2023のRQ情報をPUポート毎の4組にし、1stRQパケットのMUフィールドや、差分パケットの上位等の2ビットでPUポート番号を受信するようにすればよい。

【0187】

次に本実施形態でPUを複数とした第2実施例について説明する。図13は本発明のデータ処理システムの第2実施例の構成を示したブロック図である。

【0188】

図13のシステムは、PUの数を例えば2とし、他の数は第1実施例と同様である。

【0189】

本実施例では、PU1−0、1−1は並列に動作し、異なるPUが相前後して同じMUにアクセス出来る様に、各MUの復元手段202のMRQ保持手段2023はPU毎にRQ情報を保持している。

【0190】

又、ロードデータ等の返送先情報には、PU内ポート番号の他PU番号(本例では1ビット)を含む。

【0191】

PU番号については、1stRQパケットや差分パケットに付随して受取り、PUポートは1stRQパケットのMUフィールドを流用しMUが受信する。

【0192】

復元手段202では、差分情報を受けると、付随するPU番号で、RQ情報を選択し、これに差分情報を反映しRQ情報や、返送先PUポート番号を再生する。

【0193】

MRQ保持手段2023のRQ情報更新(上書き)も、PU番号対応のRQ情報を更新する。これら以外は第1実施例に同様である。

【0194】

尚、PUが複数で並列にMUアクセスする場合でも、各PUに排他的にアクセス先MUを割付られる場合には、各MUは第1実施例と同様の構成となる。

【0195】

以上の本発明の実施例の説明では、パケットフラグを1ビットとしたが、RQ情報を3個以上のパケットに分解して送信する場合は、複数ビットのパケットフラグで順番を示す様にしてもよい。

【0196】

本発明のデータ処理システムは、PU、MUがそれぞれ1〜2枚の大型ボードレベルで全体が、1筐体の装置であってもよいし、PU、MUそれぞれが1筐体の装置であってもよい。

【0197】

尚、ネットワーク手段は、スイッチ機能を持つ装置の他、バスであってもよい。またLAN等であってもよい。

【0198】

本発明は、要求装置のメモリアクセスに伴う、通信量を低減したい場合には、1対1の構成でも有効である。

【0199】

次に本発明の実施例のスループットが高くなることを説明(証明)するために、第1実施例の特に特徴とする部分を含まない、参考例の説明をする。

【0200】

図14に、各処理装置が複数の主記憶装置にアクセス出来る、参考のデータ処理システムを示す。

【0201】

このデータ処理システムは、メモリアクセスを行う複数のCPUポートを持つCPUを含むPU(処理装置)4−0〜4−kと、一つ以上のすべて同型のMU(主記憶装置)50〜5mと、該PUと該MUを接続するネットワーク手段3で構成される。

【0202】

PU4−0とネットワーク手段3とは、PUポート150〜15nでそれぞれ接続され、各MUとネットワーク手段3とはMUポート205〜2m5で接続されている。

【0203】

ここでは一つのPUポート(例えばPUポート150)とネットワーク手段3間の転送性能と、一つのMUポート(例えばMUポート205)ネットワーク手段3間の転送性能は等しいとする。ここではk=0、n=3、m=3とする。

【0204】

PU4−0は、メモリアクセスを行う複数(ここでは4とする)のCPUポート140〜143を持ち、ロードRQ(ロード要求)、ストアRQ(ストア要求)、該ストアRQに対応するストアデータを該CPUポート140〜143に発行するCPU11と、該CPUポート140〜143に対応し、該RQを2つのパケットに分解し1stパケット、2ndパケットとして、また、該ストアデータを2つのパケットに分解し3rdパケット、4thパケットとしてPUポート150へ送るパケット手段130とで構成される。

【0205】

CPU11はパケット手段130〜133がRQ受け取り可能な時にRQを発行するものとする。

【0206】

PU11が発行するRQのフォーマットを図6(a)に示す。RQはRQコマンドとアクセス先の主記憶装置を示すMU番号とMU内アドレスから構成されているとする。

【0207】

パケット手段130〜133からPUポート150〜153へ送られるパケットのフォーマットを図7(d)、(c)に示す。

【0208】

図7(d)は1stパケット、2ndパケットを示し、本発明の実施形態のパケット図7(a)の差分識別フラグが無いものと同様とする。

【0209】

図7(c)はストアデータの3rd、4thパケットを示し、本発明の実施形態のパケットと同様である。

【0210】

全て同型のMU(ここでは代表してMU50)は、MUポート205を経由してネットワーク手段3から送られてきた複数のパケットのうち、1stパケット、2ndパケットから元のRQと、3rdパケットと4thパケットから元のストアデータを合成しメモリアクセス手段203へ送り、メモリアクセス手段203からのロードデータを2つのパケットに分解しMUポート203を経由してネットワーク手段3へ送るMパケット手段201と、Mパケット手段201からのRQによりメモリアクセスを行い、ロードデータをMパケット手段201へ送るメモリアクセス手段203と、RAM(図示せず)で構成される。

【0211】

参考例のロードRQの動作は、本発明の実施形態において、ロードRQの動作説明の先行RQと同様である。

【0212】

参考例のロードRQが2個連続した場合、該2個のロードRQの動作は、本発明の実施の形態において、ロードRQの動作説明の先行RQと同様である。

【0213】

参考例において、同一MU(ここではMU50とする)へのロードRQが2個連続した場合の動作を、図15のタームチャートを用いて説明する。

【0214】

T1で、先行RQが発行される。以降、本発明の実施の形態におけるロードRQの動作説明の先行RQと同様である。

【0215】

T3で、後続RQが発行される。以降、本発明の実施の形態におけるロードRQの動作説明の先行RQと同様である。

【0216】

T11で先行RQのロードデータ、T13で後続RQのロードデータがCPU11に到着する。

【0217】

次に、本例において、同一MU(ここではMU50とする)へのストアRQが2個連続した場合動作を、図15のタームチャートを用いて説明する。

【0218】

T10で、先行RQが発行される。以降、本発明の実施の形態におけるストアRQの動作説明の先行RQと同様である。

【0219】

T14で、後続RQが発行される。以降、本発明の実施の形態におけるストアRQの動作説明の先行RQと同様である。

【0220】

T19で先行RQのストアデータが、T23で後続RQのストアデータがメモリに書き込まれる。

【0221】

本例では、ロードRQ、ストアRQ共に、先行RQと後続RQは同様の動作となる。

【0222】

次に、本例において、CPU11からMU20へのロードRQが4個、その後ストアRQが4個、その後ロードRQが1個処理されるケースについて、図16のタイムチャートを用いて説明する。

【0223】

T1で、最初のロードRQ(ロードRQ1とし1と表示)がCPU11から発行される。

【0224】

以降の該RQの処理は、本発明の実施の形態のロードRQの先行RQと同様である。

【0225】

T3、T5、T7で、2番目、3番目、4番目のロードRQがCPU11から発行される。(それぞれロードRQ2、ロードRQ3,ロードRQ4とし、タイムチャートではそれぞれ2、3、4と表示される。)

以降の処理は、それぞれ本発明の実施の形態のロードRQの先行RQと同様である。

【0226】

T11、T13、T15、T17で、ロードRQ1、ロードRQ2、ロードRQ3、ロードRQ4のロードデータがそれぞれCPU11に到着する。

【0227】

T9で、最初のストアRQ(ストアRQ1とし5と表示)がCPU11から発行される。

【0228】

以降の該RQの処理は、本発明の実施の形態のストアRQの先行RQと同様である。

【0229】

T13、T17、T21で、2番目、3番目、4番目のストアRQがCPU11から発行される。(それぞれストアRQ2、ストアRQ3,ストアRQ4とし、タイムチャートではそれぞれ6、7、8と表示される。)

以降の処理は、それぞれ本発明の実施の形態のストアRQの先行RQと同様である。

【0230】

T16、T20、T24、T28で、ストアRQ2、ストアRQ3,ストアRQ4のストアデータをそれぞれメモリに書き込む。

【0231】

T25で、5番目のロードRQ(以下ロードRQ5とする。タイムチャートでは9と表示する。)がCPU11から発行される。

【0232】

以降の該RQの処理は、本発明の実施の形態のロードRQの先行RQと同様である。T35で、ロードRQ5のロードデータがCPU11に到着する。

【0233】

図16のタイムチャートによると、本例において、CPU11がロードRQ1を発行してからロードRQ5のロードデータがCPU11に到着するまでに要する時間は、35Tである。

【0234】

また、ロードRQ1からロードRQ5までの9個のRQにおいて、1タイミングに処理できるRQ数(以下スループットとする)は、CPU11にロードRQ1のロードデータがCPU11に到着してから、CPU11にロード5のロードデータが到着するまでの時間間隔が25Tなので、9RQ/25T=0.36RQ/Tである。

【図面の簡単な説明】

【0235】

【図1】本発明の実施形態の一般形を示すブロック図。

【図2】本発明の第1実施例の構成を示したブロック図。

【図3】図2の削減手段120の詳細ブロック図。

【図4】図2の復元手段202の詳細ブロック図。

【図5】図2の転送制御手段204の詳細ブロック図。

【図6】(a)は本発明の第1実施例のRQ情報のフォーマットを示し、(b)は本発明の第1実施例の差分情報フォーマットを示し、(c)本発明の第1実施例のストアデータフォーマットを示す図。

【図7】(a)、(b)、(c)はそれぞれ本発明の第1実施例の、RQ情報パケットのフォーマット、差分情報パケットのフォーマット、ストアデータパケットのフォーマットを示す図。(d)は参考例のRQパケットのフォーマットを示す図。

【図8】本発明の第1実施例の合成されたRQ情報を示した図。

【図9】本発明の第1実施例の削減手段120の動作を示したフローチャート。

【図10】本発明の第1実施例の復元手段202の動作を示したフローチャート。

【図11】本発明の第1実施例のロードRQ、ストアRQのタイムチャート。

【図12】本発明の第1実施例のロードRQ、ストアRQ混在時のタイムチャート。

【図13】本発明の第2実施例の構成を示したブロック図。

【図14】参考例のデータ処理システムを示したブロック図。

【図15】参考例のロードRQ、ストアRQのタイムチャート。

【図16】参考例のロードRQ、ストアRQ混在時のタイムチャート。

【符号の説明】

【0236】

1−0〜1−k PU

11 CPU

120〜12n 削減手段

1201 PRQ保持手段

1202 差分情報生成手段

1203 RQ構成手段

130〜13n Pパケット手段

140〜14n CPUポート

150〜15n PUポート

20〜2m MU

201 Mパケット手段

202 復元手段

2021 情報再生手段

2022 RQ再生手段

2023 MRQ保持手段

203 メモリアクセス手段

204 転送制御手段

2041 データ格納手段

2042 データ制御手段

205〜2m5 MUポート

3 ネットワーク手段

【特許請求の範囲】

【請求項1】

コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えた処理装置と、

前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えた記憶装置とを含むことを特徴とするデータ処理システム。

【請求項2】

一つ以上の処理装置と複数の記憶装置とこれらを接続するネットワーク手段を含むデータ処理システムであって、

前記処理装置には、メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報とを比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行の要求情報として保持しておく要求情報削減手段と、

前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する処理装置パケット手段とを備え、

前記記憶装置には、メモリ部と、これの読出、書込アクセスを行うメモリアクセス手段と、

ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置パケット手段と、

差分フラグがオンであれば、差分情報パケットと自装置に保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とするデータ処理システム。

【請求項3】

前記処理装置の処理装置パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手段と、ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有し、

前記記憶装置がメモリアクセス手段からロードデータを受取り、記憶装置パケット手段に転送する手段も備え、

記憶装置パケット手段が、複数パケットで受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする請求項2記載のデータ処理システム。

【請求項4】

前記処理装置が、メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする請求項3記載のデータ処理システム。

【請求項5】

前記記憶装置の復元手段が先行の要求情報を処理装置毎に保持し、差分情報パケットに含む或いは付随する処理装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、これをメモリアクセス手段に渡し、またその処理装置の先行要求情報としておくことを特徴とする請求項2、又は4に記載のデータ処理システム。

【請求項6】

コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えたことを特徴とする処理装置。

【請求項7】

メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行する要求情報として保持しておく要求情報削減手段と、

前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、ネットワーク手段を通じ記憶装置に送信するパケット手段とを備えたことを特徴とする処理装置。

【請求項8】

前記パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のパケットに変換し、要求情報や差分情報のパケットに続いて送出する手段と、

ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有することを特徴とする請求項7記載の処理装置。

【請求項9】

前記メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする請求項8記載の処理装置。

【請求項10】

アクセス要求情報に関する差分情報パケットを受信すると、これの差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えたことを特徴とする記憶装置。

【請求項11】

メモリ部と、これの読出やこれへの書込を行うメモリアクセス手段と、

ネットワーク手段を通じ、メモリアクセスの要求装置よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻すパケット手段と、

差分フラグがオンであれば、差分情報パケットと保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とする記憶装置。

【請求項12】

メモリアクセス手段からロードデータを受取り、パケット手段に転送する手段も備え、

前記パケット手段が、複数パケットとして受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする請求項11記載の記憶装置。

【請求項13】

前記復元手段が先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、またその要求装置の先行の要求情報としておくことを特徴とする請求項11、又は12に記載の記憶装置。

【請求項14】

メモリアクセスを要求する装置に、

要求元からコマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手順を備え、

記憶装置に、前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手順を備えたことを特徴とするメモリアクセス制御方法。

【請求項15】

一つ以上のメモリアクセス要求装置と複数の記憶装置とこれらを接続するネットワーク手段を含むシステムのメモリアクセス制御方法であって、

前記要求装置が、メモリアクセス要求元よりコマンドとアクセスアドレスを含む要求情報を受け、これと先行する要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力する要求情報削減手順と、

前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグより前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する要求側パケット手順とを備え、

前記記憶装置が、ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置側パケット手順と、差分フラグがオンであれば、差分情報パケットと、保持している先行の要求情報から今回の要求情報を作成する復元手順と、要求情報でメモリ部の読出、書込アクセスを行うメモリアクセス手順とを備えたことを特徴とするメモリアクセス制御方法。

【請求項16】

前記要求側パケット手順が、要求元のストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手順と、ネットワーク手段より複数のパケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手順を有し、

前記記憶装置が、読み出したロードデータを、記憶装置側パケット手順に渡す手順も備え、

記憶装置側パケット手順が、複数のパケットとして受信したストアデータを、もとの一つのデータに戻す手順と、ロードデータを複数のパケットにし、ネットワーク手段を通じ要求装置に返送する手順を有することを特徴とする請求項15記載のメモリアクセス制御方法。

【請求項17】

前記記憶装置の復元手順が、先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に対応する先行の要求情報を選択し、これと差分情報パケットとから今回の要求情報を作成し、これをメモリアクセス手順に渡し、またその要求装置の先行の要求情報として保持しておくことを特徴とする請求項15、又は16に記載のメモリアクセス制御方法。

【請求項1】

コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えた処理装置と、

前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えた記憶装置とを含むことを特徴とするデータ処理システム。

【請求項2】

一つ以上の処理装置と複数の記憶装置とこれらを接続するネットワーク手段を含むデータ処理システムであって、

前記処理装置には、メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報とを比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行の要求情報として保持しておく要求情報削減手段と、

前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する処理装置パケット手段とを備え、

前記記憶装置には、メモリ部と、これの読出、書込アクセスを行うメモリアクセス手段と、

ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置パケット手段と、

差分フラグがオンであれば、差分情報パケットと自装置に保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とするデータ処理システム。

【請求項3】

前記処理装置の処理装置パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手段と、ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有し、

前記記憶装置がメモリアクセス手段からロードデータを受取り、記憶装置パケット手段に転送する手段も備え、

記憶装置パケット手段が、複数パケットで受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする請求項2記載のデータ処理システム。

【請求項4】

前記処理装置が、メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする請求項3記載のデータ処理システム。

【請求項5】

前記記憶装置の復元手段が先行の要求情報を処理装置毎に保持し、差分情報パケットに含む或いは付随する処理装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、これをメモリアクセス手段に渡し、またその処理装置の先行要求情報としておくことを特徴とする請求項2、又は4に記載のデータ処理システム。

【請求項6】

コマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手段を備えたことを特徴とする処理装置。

【請求項7】

メモリアクセス要求元と、これよりコマンドとアクセスアドレスを含む要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力し、これを先行する要求情報として保持しておく要求情報削減手段と、

前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグを前記複数より少ない数のパケットに変換し、ネットワーク手段を通じ記憶装置に送信するパケット手段とを備えたことを特徴とする処理装置。

【請求項8】

前記パケット手段が、要求元からのストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のパケットに変換し、要求情報や差分情報のパケットに続いて送出する手段と、

ネットワーク手段より複数パケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手段を有することを特徴とする請求項7記載の処理装置。

【請求項9】

前記メモリアクセス要求元と前記要求情報削減手段と前記処理装置パケット手段とを複数組備えたことを特徴とする請求項8記載の処理装置。

【請求項10】

アクセス要求情報に関する差分情報パケットを受信すると、これの差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手段を備えたことを特徴とする記憶装置。

【請求項11】

メモリ部と、これの読出やこれへの書込を行うメモリアクセス手段と、

ネットワーク手段を通じ、メモリアクセスの要求装置よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻すパケット手段と、

差分フラグがオンであれば、差分情報パケットと保持している先行の要求情報から今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、これを先行の要求情報として保持しておく復元手段とを備えたことを特徴とする記憶装置。

【請求項12】

メモリアクセス手段からロードデータを受取り、パケット手段に転送する手段も備え、

前記パケット手段が、複数パケットとして受信するストアデータを、一つのデータに戻し、復元手段に渡す手段と、ロードデータを複数のパケットにしネットワーク手段を通じ要求元に返送する手段を有することを特徴とする請求項11記載の記憶装置。

【請求項13】

前記復元手段が先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に従い、対応する先行の要求情報を選択し、これと差分情報とから今回の要求情報を作成し、要求情報をメモリアクセス手段に渡し、またその要求装置の先行の要求情報としておくことを特徴とする請求項11、又は12に記載の記憶装置。

【請求項14】

メモリアクセスを要求する装置に、

要求元からコマンドとアドレスを含むメモリアクセス要求情報を受け、これと保持している先行の要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分情報であることを示すフラグを立てアドレスの差分情報をパケットにし、これを要求情報パケットの代わりに、記憶装置に向けて送信する手順を備え、

記憶装置に、前記差分情報パケットを受信すると、差分情報を、保持している前回の要求情報に反映し今回の要求情報を作成する手順を備えたことを特徴とするメモリアクセス制御方法。

【請求項15】

一つ以上のメモリアクセス要求装置と複数の記憶装置とこれらを接続するネットワーク手段を含むシステムのメモリアクセス制御方法であって、

前記要求装置が、メモリアクセス要求元よりコマンドとアクセスアドレスを含む要求情報を受け、これと先行する要求情報を比較し、コマンド及び前記アドレスの所定部分が一致すれば、差分フラグをオンにし、アドレスの差分情報を出力し、不一致であれば、受けた要求情報を出力する要求情報削減手順と、

前記アクセス要求情報と差分フラグを複数のパケットに変換し、或いは前記差分情報と差分フラグより前記複数より少ない数のパケットに変換し、前記ネットワーク手段に送信する要求側パケット手順とを備え、

前記記憶装置が、ネットワーク手段よりパケットを受信しその差分フラグがオフであれば、複数の要求情報パケットを一つの要求情報に戻す記憶装置側パケット手順と、差分フラグがオンであれば、差分情報パケットと、保持している先行の要求情報から今回の要求情報を作成する復元手順と、要求情報でメモリ部の読出、書込アクセスを行うメモリアクセス手順とを備えたことを特徴とするメモリアクセス制御方法。

【請求項16】

前記要求側パケット手順が、要求元のストアデータを受け、これを要求情報や差分情報のパケットと同サイズで複数のストアデータパケットに変換し、これを要求情報や差分情報のパケットに続いて送出する手順と、ネットワーク手段より複数のパケットとして受信したロードデータを元の一つのロードデータに戻し、要求元に向けて転送する手順を有し、

前記記憶装置が、読み出したロードデータを、記憶装置側パケット手順に渡す手順も備え、

記憶装置側パケット手順が、複数のパケットとして受信したストアデータを、もとの一つのデータに戻す手順と、ロードデータを複数のパケットにし、ネットワーク手段を通じ要求装置に返送する手順を有することを特徴とする請求項15記載のメモリアクセス制御方法。

【請求項17】

前記記憶装置の復元手順が、先行の要求情報を要求装置毎に保持し、差分情報パケットに含む或いは付随する要求装置番号に対応する先行の要求情報を選択し、これと差分情報パケットとから今回の要求情報を作成し、これをメモリアクセス手順に渡し、またその要求装置の先行の要求情報として保持しておくことを特徴とする請求項15、又は16に記載のメモリアクセス制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2006−11911(P2006−11911A)

【公開日】平成18年1月12日(2006.1.12)

【国際特許分類】

【出願番号】特願2004−189382(P2004−189382)

【出願日】平成16年6月28日(2004.6.28)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成18年1月12日(2006.1.12)

【国際特許分類】

【出願日】平成16年6月28日(2004.6.28)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]