データ処理システム内でシステム・イメージとローカルに接続された外部記憶装置との間の動作を実行するための方法、コンピュータ・プログラム、および装置(キャッシュされたアドレス変換を使用して入出力アダプタと通信するための装置および方法)

【課題】 キャッシュされたアドレス変換を使用して、ローカルに接続された入出力装置と通信するように構成された入出力(I/O)アダプタと通信するための装置および方法を提供することにある。

【解決手段】 この装置および方法により、記憶トランザクション要求を受信したことに応答して、未変換バッファ・アドレスを指定するキュー・エレメントがコマンド・キュー内に作成される。キュー・エレメントは入出力アダプタによって検索することができ、キュー・エレメントが読み取り動作コマンドを含むかどうかに関する判断を行うことができる。キュー・エレメントが読み取り動作コマンドを含む場合、読み取り動作コマンドがローカルに接続された外部記憶装置に送信されるのとほぼ同時に、入出力アダプタからルート複合体に変換要求を送信することができる。キュー・エレメントの未変換アドレスに対応する変換済みアドレスは、外部記憶装置から読み取られたデータを受信する前に、返され、入出力アダプタに保管することができる。

【解決手段】 この装置および方法により、記憶トランザクション要求を受信したことに応答して、未変換バッファ・アドレスを指定するキュー・エレメントがコマンド・キュー内に作成される。キュー・エレメントは入出力アダプタによって検索することができ、キュー・エレメントが読み取り動作コマンドを含むかどうかに関する判断を行うことができる。キュー・エレメントが読み取り動作コマンドを含む場合、読み取り動作コマンドがローカルに接続された外部記憶装置に送信されるのとほぼ同時に、入出力アダプタからルート複合体に変換要求を送信することができる。キュー・エレメントの未変換アドレスに対応する変換済みアドレスは、外部記憶装置から読み取られたデータを受信する前に、返され、入出力アダプタに保管することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、一般に、改良されたデータ処理システムおよび方法に関する。より具体的には、本出願は、キャッシュされたアドレス変換を使用して、1つまたは複数のローカルに接続された入出力装置と通信するように構成された入出力(I/O)アダプタまたはエンドポイントと通信するための装置および方法を対象とする。

【背景技術】

【0002】

システムによっては、現在の周辺装置相互接続(PCI:Peripheral Component Interconnect)プロトコルにより、直接メモリ・アクセス(DMA:direct memory access)を実行するときに、アドレス変換および保護テーブル(ATPT:address translation and protection table)を使用してアドレス変換およびアクセス検査が実行される。ATPTは、数十年間、使用されてきたが、より下位のシステムにとっては新しいものであり、直接メモリ・アクセス(DMA)リマッピング・リソースまたは入出力メモリ管理ユニット(IOMMU:Input/Output Memory Management Unit)などのいくつかの他の名前で知られている。ATPTは、DMAトランザクションで使用されるPCIバス・アドレスを、実メモリ・リソースにアクセスするために使用される実メモリ・アドレスに変換するための項目を保管する。ATPT内の項目は、どのデバイスが対応するメモリの一部分にアクセス可能であるかと、このようなデバイスがこれらのメモリの一部分で実行可能な特定の動作とを識別する保護情報を保管する。

【0003】

最近、PCI−SIG(www.pcisig.com/home)は、ATPTに常駐するアドレス変換をPCIファミリ・アダプタにキャッシュできるようにするメカニズムを標準化している最中であった。これらのメカニズムはアドレス変換サービス(ATS:Address Translation Services)として知られている。ATSにより、PCIファミリ・アダプタは、未変換PCIバス・アドレスに関する変換を要求することができ、ATSをサポートするシステム上でこのような要求が正常に完了すると、変換済み、すなわち、実メモリ・アドレスがPCIファミリ・アダプタに返される。次に、ATSにより、PCIファミリ・アダプタは、DMA動作で使用されるPCIバス・アドレスに変換済みとしてマークを付けることができる。ATSをサポートするシステムは、その後、変換済みアドレスを使用してATPTをバイパスすることになる。また、ATSは、ホスト側(たとえば、ハードウェアまたは仮想化仲介(virtualization intermediary))が前に公示されたアドレス変換を無効化するためのメカニズムも提供する。

【0004】

図1は、ATPTおよびPCIエクスプレス(PCIe:PCI express)通信プロトコルを使用してDMA動作を実行するための従来のメカニズムを例示する模範的な図である。描写された例は、PCIeエンドポイント、たとえば、アドレス変換動作を実行するためにATSを使用するPCIe入出力(I/O)アダプタによって呼び出される、上述のPCIeアドレス変換サービス(ATS)も示している。後述する通り、ATS機能は、PCIeエンドポイントおよびホスト・システムのルート複合体(root complex)内に構築される。PCIe ATSに関する追加情報については、www.pcisig.comの周辺装置相互接続分科会(PCI−SiG:peripheral component interconnect special interest group)Webサイトから入手可能なPCIe ATS規格を参照する。

【0005】

図1に図示されている通り、ホストCPUおよびメモリ110は、システム・バス115を介して、アドレス変換および保護テーブル(ATPT)130を含むPCIeルート複合体120に結合されている。次に、PCIeルート複合体120は、PCIeリンク135を介して、1つまたは複数のPCIeエンドポイント140(「エンドポイント」という用語は、PCIe対応入出力アダプタについて言及するためにPCIe規格で使用されるものである)に結合される。ルート複合体120は、CPU/メモリをPCIeエンドポイント140に接続する入出力階層のルートを意味する。ルート複合体120は、ホスト・ブリッジと、ゼロまたは1つ以上のルート複合体統合エンドポイントと、ゼロまたは1つ以上のルート複合体イベント・コレクタと、1つまたは複数のルート・ポートとを含む。各ルート・ポートは個別の入出力階層をサポートする。入出力階層は、ルート複合体120と、ゼロまたは1つ以上の相互接続スイッチまたはブリッジあるいはその両方(スイッチまたはPCIファブリックを含むもの)と、エンドポイント140などの1つまたは複数のエンドポイントから構成することができる。たとえば、PCIeスイッチは、ルート複合体120に接続されたエンドポイント140などのPCIeエンドポイントの数を増加するために使用することができる。PCIおよびPCIeに関する追加情報については、www.pcisig.comのPCI−SiG Webサイトから入手可能なPCIおよびPCIe規格を参照する。

【0006】

PCIeエンドポイントは、内部ルーティング回路142と、構成管理ロジック144と、1つまたは複数の物理機能(PF:physical function)146と、ゼロまたは1つ以上の仮想機能(VF:virtual function)148〜152とを含み、それぞれのVFは1つのPFに関連づけられている。ATSにより、各仮想機能は、すでに変換されており、DMA動作を実行するときにホストATPT130をバイパスするために仮想機能によって使用できるPCIメモリ・アドレスをキャッシュするためにアドレス変換キャッシュ(ATC:address translation cache)160〜164を使用することができる。

【0007】

実施時に、PCIeエンドポイント140は、PCIe ATSトランザクションを呼び出しを呼び出して、所与のPCIバス・アドレスからシステム・バス・アドレスへの変換を要求し、その後のトランザクション、たとえば、DMA動作がすでに変換されており、ATPTをバイパスできることを示すことができる。ルート複合体120は、PCIeエンドポイント140に提供された変換がもはやPCIeエンドポイント140の物理または仮想あるいはその両方の機能(複数も可)によって使用されないように、その変換を無効化するためにPCIe ATSトランザクションを呼び出すことができる。

【0008】

たとえば、DMA動作を実行する予定である場合、DMA動作のアドレスは、DMA動作を処理する特定の仮想機能148〜152のATC160〜164でルックアップすることができる。アドレス変換がATC160〜164内に存在しない場合、PCIeエンドポイント140によってルート複合体120に対する変換要求を行うことができる。次に、ルート複合体120は、ATPT130を使用してアドレス変換を実行し、PCIeエンドポイント140に変換済みアドレスを返すことができる。次に、PCIeエンドポイント140は、DMA動作を処理する物理または仮想あるいはその両方の機能に対応する適切なATC160〜164内にその変換を保管することができる。DMA動作は、変換済みアドレスを使用してシステム・バス115上に渡すことができる。

【0009】

このアドレスに関する変換がすでにATC160〜164内に存在する場合、変換済みアドレスがDMA動作で使用される。そのアドレスがすでに変換されていることと、このDMAについてルート複合体120内のATPT130をバイパスできることを示すために、DMAヘッダ内にビットを設定することができる。その結果、PCIeリンク135およびシステム・バス115を介してPCIeエンドポイント140とホストCPUおよびメモリ110との間でDMA動作が直接実行される。PCIeエンドポイントの仮想機能の特定のBDF番号が、DMA動作によって要求されたようにアドレスにアクセスすることが許可されているBDFに対応することを保証するために、アクセス検査は依然としてルート複合体120によって実行することができる。

【0010】

その後の何らかの時点で、変換がATPT130内で変化した場合など、PCIeエンドポイント140に提供された変換がもはやPCIeエンドポイント140によって使用されない場合、ルート複合体120はPCIeエンドポイント140にATS無効化要求を発行しなければならない。PCIeエンドポイント140は、無効アドレスに向けられたすべての保留要求を直ちにフラッシュするわけではない。むしろ、PCIeエンドポイント140は、リタイヤすべき無効変換済みアドレスを参照するすべての未解決の読み取り要求を待ち、無効になるようにATC160〜164内の項目にマークを付けるためのビットを設定することなどにより、ATC160〜164内の変換を解放する。PCIeエンドポイント140は、ATC160〜164内の変換の無効化の完了を示すATS無効化完了メッセージをルート複合体120に返す。PCIeエンドポイント140は、無効化されたアドレスを使用する任意の前にポストされた書き込みのあとで、無効化完了表示がルート複合体120に到着することを保証する。

【0011】

典型的には、ATPT130は、システム・メモリ内のツリー構造変換テーブルとして設けることができる。コンピューティング・システムの各PCIバス/デバイス/機能(BDF:Bus/Device/Function)ごとに異なるツリー構造を設けることができる。これらのATPTデータ構造を使用して、複数のデバイスは1つのデバイス・アドレス空間を共用することができ、複数のデバイスは専用アドレス空間を有することができる。したがって、すべてのデバイスがシステム・メモリのすべてのアドレス空間上ですべてのDMA動作を実行できるわけではない。

【0012】

ATPT130のアクセスは、DMAトランザクションの一部として同期的に実行される。これは、DMAトランザクションの未変換PCIバス・メモリ・アドレスをホストのメモリにアクセスするために使用される変換済み実メモリ・アドレスに変換するため、ならびに、DMAトランザクションをサブミットするデバイスが変換済み実メモリ・ドレスにアクセスするための十分な許可を有し、変換済み実メモリ・アドレス上で所望のDMA動作を実行するための十分な許可を有することを保証するためにATPTをチェックするための時間のかかる変換メカニズムを使用することを必要とする。

【0013】

ATPT130のアクセスの一部として、特定のBDFに対応する正しいATPTツリー・データ構造を識別しなければならず、変換およびアクセス検査を実行するためにツリー・データ構造をウォーク(走査)しなければならない。ATPTツリー・データ構造の位置特定は、BDFに関連するツリー・データ構造のアドレスを見つけるために、1回または2回のアクセスを必要とする可能性がある。見つかった場合、ツリーをウォークするためにツリー・データ構造への3回または4回のアクセスを要する可能性がある。したがって、この変換およびアクセス検査には、DMA動作に関連する大規模待ち時間に対する責任がある。このような待ち時間は、低い通信待ち時間を必要とするエンドポイントに関する重大な問題を引き起こす可能性がある。

【0014】

このような待ち時間を緩和する方法として、PCIeエンドポイント140で実現されるATSは、これらの変換をもう一度実行する必要がないように、すでに実行されたアドレス変換を保管するためにATC160〜164を使用する。したがって、ATPTとATCとの組み合わせにより、PCI ATSは、DMA動作に関連する待ち時間を短縮するようにアドレス変換およびアクセス検査を実行する。PCI SiGはPCIe ATSに関する規格を規定しているが、PCI SiGでは、ATSを使用してアドレス変換を実行し、ATPTおよびATCなどのATS構造を管理する役割をPCIe ATSを実現するシステム内でどのように配分すべきかを指定していない。

【特許文献1】米国特許第6629162号

【発明の開示】

【発明が解決しようとする課題】

【0015】

例示的な諸実施形態は、キャッシュされたアドレス変換を使用して、1つまたは複数のローカルに接続された入出力装置と通信するように構成された入出力(I/O)アダプタまたはエンドポイントと通信するための装置および方法を提供する。この装置および方法により、アドレス変換情報のキャッシュ管理に関する役割は、デバイス・ドライバとデバイス・ドライバ・サービスとの間で分散される。デバイス・ドライバは信頼できないミッション・ロジカル・パーティション(LPAR:logical partition)内に設けることができ、デバイス・ドライバ・サービスは仮想化仲介オペレーティング・システム、ハイパーバイザ、サービス・パーティションなどの信頼できる仮想化仲介内に設けることができる。

【0016】

デバイス・ドライバは、LPAR内のアプリケーションとPCIeエンドポイントとの間ならびにその逆において要求を通信するためのキューを管理する役割を担う。デバイス・ドライバはさらに、デバイス・ドライバ・サービスを介してメモリ管理を呼び出す役割を担う。デバイス・ドライバ・サービスは、アドレス変換および保護テーブル(ATPT)ならびにPCIeエンドポイントのアドレス変換キャッシュ(ATC)を含む、PCIeエンドポイントによってアクセス可能なメモリを管理する役割を担う。

【0017】

PCIeエンドポイントと通信する役割をデバイス・ドライバとデバイス・ドライバ・サービスとの間で分割することにより、OS内で実行されるデバイス・ドライバは、他のOSのメモリに関連する変換をPCIeエンドポイントに提供することができない。その結果、システム仮想化に関連する信頼モデルが維持される。すなわち、アドレス変換キャッシュ管理の役割をデバイス・ドライバ・サービス内に置くことにより、あるOSは、そのエンドポイントが他のOSのメモリに対してDMA動作を実行することを要求できなくなる。

【課題を解決するための手段】

【0018】

例示的な一実施形態では、ホスト・システムの信頼できないミッション・ロジカル・パーティション(LPAR)システム・イメージ内のデバイス・ドライバの初期設定中に、PCIeエンドポイント用のデバイス・ドライバは、アドレス変換および保護テーブル(ATPT)項目を初期設定し、コマンド、応答、およびイベント・キューなど、システム・メモリ内に常駐し、直接メモリ・アクセス(DMA)動作によりPCIeエンドポイントによってアクセス可能なアダプタ・リソース用のデバイス・ドライバにPCIメモリ・アドレスを返すためにデバイス・ドライバ・サービス(以下、単純に「ドライバ・サービス」という)を呼び出す。デバイス・ドライバとPCIeエンドポイントは、コマンド、応答、およびイベント・キューにより通信する。本書では、これらのキューを「デバイス・ドライバのキュー」ということにする。

【0019】

本質的に、デバイス・ドライバ・サービスは、デバイス・ドライバのキュー(複数も可)用のホスト・メモリを滞留(pin)させ、デバイス・ドライバのキュー(複数も可)に関するDMAアドレスを割り当て、これらのDMAアドレスに関するATPT項目をプログラミングし、ATPT項目がキャッシュ可能であること、すなわち、PCIeエンドポイント上で、キュー・コンテキスト、たとえば、アドレス変換キャッシュ内にキャッシュ可能であることを示すビットを使用可能にする。次に、デバイス・ドライバ・サービスは、未変換PCIeメモリ・アドレス(複数も可)、すなわち、DMAアドレス(複数も可)、たとえば、キュー内の特定の項目を識別するためにオフセットともに使用可能なデバイス・ドライバのキュー(複数も可)に関する開始アドレスをATPT項目用のデバイス・ドライバに返す。未変換PCIeメモリ・アドレスは、システムのメモリ空間内にないアドレスであり、システム・メモリにアクセスするために使用するには、その前に変換しなければならないものである。

【0020】

例示的な諸実施形態のメカニズムを使用すると、この未変換PCIeメモリ・アドレスをPCIeエンドポイントに提供し、ルート複合体に変換要求を送信するためにPCIeエンドポイントが使用することができる。すなわち、PCIeエンドポイントは、未変換PCIeメモリ・アドレスに関連する1つまたは複数の変換済みPCIeメモリ・アドレスを返すようルート複合体に要求することができる。次に、PCIeエンドポイントは、1つまたは複数の変換済みPCIeメモリ・アドレスをデバイス・ドライバのキュー(複数も可)に関連するコンテキスト、たとえば、PCIeエンドポイント内の1つまたは複数の仮想機能に関連する1つまたは複数のアドレス変換キャッシュに保管することができる。

【0021】

未変換PCIeメモリ・アドレスの変換をアダプタのデバイス・ドライバ・キュー・コンテキストに保管することにより、PCIeエンドポイントは、デバイス・ドライバ・キュー項目をターゲットにするDMAの際にルート複合体のATPTをバイパスすることができる。したがって、ルート複合体が変換済みとしてマークが付けられたPCIe DMAトランザクションを受信すると、ルート複合体は、そのエンドポイントについて変換キャッシュが使用可能になっていることを検証し、ホストの実メモリに直接アクセスするために変換済みPCIeメモリ・アドレスを使用する。

【0022】

PCIeエンドポイントがシステムから切り離された後、デバイス・ドライバに関連する機能(物理または仮想)がシステムから切り離された後など、その後の何らかの時点で、未変換PCIeメモリ・アドレスに対応するATPT項目およびATC項目を無効化する必要がある可能性がある。このような無効化を実行するために、デバイス・ドライバあるいはハイパーバイザ管理コンポーネントなどの何らかの上位エンティティは、ホスト・メモリを滞留解除し、DMAアドレス、すなわち、未変換PCIeメモリ・アドレスを解放するためにデバイス・ドライバ・サービスを呼び出す。次に、デバイス・ドライバ・サービスは、未変換PCIeメモリ・アドレスに対応するATPT項目を消去し、ルート複合体はATC項目無効化要求をPCIeエンドポイントに発行する。次に、PCIeエンドポイントは、未変換PCIeメモリ・アドレスに対応する任意のATC項目を無効化するための動作を実行し、未変換PCIeメモリ・アドレスがもはや使用されなくなった後に、ATC無効化完了応答をデバイス・サービス(device service)に返す。次に、デバイス・サービスはデバイス・ドライバに制御を返す。代替実現例では、デバイス・ドライバ・サービスは、ATC項目無効化要求をPCIeエンドポイントに発行することができ、PCIeエンドポイントがATC項目無効化を完了した後に、デバイス・ドライバ・サービスはATPT項目を消去し、デバイス・ドライバに制御を返すことができる。

【0023】

前述の通り、例示的な諸実施形態のメカニズムは、システム・イメージと、システム・イメージなどで実行されるアプリケーションと、1つまたは複数のキュー・データ構造を使用するPCIeエンドポイントとの間で通信する際に使用するためのATPT項目を確立するために使用することができる。例示的な諸実施形態のこのような実現例では、1つまたは複数のキュー・データ構造に関するATPT項目は、前に上述したように初期設定される。PCIeエンドポイントの初期設定フェーズ中に、PCIeエンドポイントは、デバイス・ドライバが初期設定されていることを検証する。これは、たとえば、PCIeエンドポイントのPCI構成空間、重要プロダクト・データ(VPD:Vital Product Data)フィールド、またはメモリ・マップ入出力(MMIO:memory mapped input/output)フィールドから情報を読み取ることにより、実行することができる。

【0024】

デバイス・ドライバは、1つまたは複数のキューの開始および終了アドレス、開始アドレスおよび長さなどをPCIeエンドポイントに提供することができる。たとえば、デバイス・ドライバは、キュー構成空間に対応するPCIeエンドポイントのPCI構成空間フィールド、VPDまたはMMIOフィールドにこれらのアドレスを書き込むことができる。これらのアドレスは未変換PCIeアドレスである。PCIeエンドポイントは、キュー・アドレスの変換に関するPCIe ATS要求を呼び出すことができる。その結果、ルート複合体は、ATPTを使用してアドレス変換を実行し、1つまたは複数のキューから項目を検索する際に使用するためにキュー・コンテキストに変換済みアドレスをキャッシュすることができるPCIeエンドポイントに結果を返し、項目を1つまたは複数のキュー内に入れることができる。

【0025】

例示的な一実施形態では、デバイス・ドライバは、PCIeエンドポイントと通信するためのキュー・データ構造を生成する。キュー・データ構造は、たとえば、コマンド・キューと応答キューを含むことができる。キュー・データ構造は、たとえば、PCIeエンドポイントに結合された小型コンポーネント・システム・インターフェース(SCSI:small component system interface)入出力装置と通信するためのSCSIキューにすることができる。これらのキュー・データ構造は、リンク・リスト・キュー、サーキュラ・バッファ・キューなどを含む任意の方式で構成することができる。

【0026】

これらのキュー・データ構造を生成する際にデバイス・ドライバによって実行される動作の一部として、デバイス・ドライバは、キュー・データ構造に関するATPT項目をプログラミングし、キューに関する未変換PCIeアドレス、すなわち、DMAアドレスをデバイス・ドライバに返すためにデバイス・ドライバ・サービスを呼び出す。ATPT項目のプログラミングは、キュー・データ構造に使用されるホスト・メモリ空間を滞留させること、未変換PCIeアドレスからシステム・メモリ・アドレスに変換するための変換情報によりルート複合体のATPT内のATPT項目をプログラミングすること、ならびにATPT項目に対応するアドレス変換がPCIeエンドポイントのATC内にキャッシュ可能であることを示すキャッシュ使用可能ビットをATPT項目内に設定することを必要とする可能性がある。このような動作を実行した後、1つまたは複数のATPT項目に関する未変換PCIeアドレス(複数も可)がデバイス・ドライバに返される。これらの未変換PCIeアドレス(複数も可)は、たとえば、キュー・データ構造の開始および終了アドレスを識別することができる。

【0027】

未変換PCIeアドレス(複数も可)は、PCIeエンドポイント内のキュー構成空間にアドレスを書き込むことなどにより、デバイス・ドライバによってPCIeエンドポイントに提供される。キュー構成空間は、たとえば、PCI構成空間、1つまたは複数のVPDフィールド、1つまたは複数のMMIOフィールドなどにすることができる。キュー・データ構造に関するこれらの未変換PCIeアドレス(複数も可)を受信したことに応答して、PCIeエンドポイントは、キュー・アドレスに関するPCIe ATS要求をルート複合体に発行することができる。その結果、ルート複合体は、キュー・データ構造の未変換PCIeアドレスに関するアドレス変換およびアクセス検査を実行し、変換済みアドレスをPCIeエンドポイントに返すことができる。次に、PCIeエンドポイントは、PCIeエンドポイントのATCによって提供されたキュー・コンテキスト内にこれらのアドレス変換を保管することができる。

【0028】

上記の結果として、PCIeエンドポイントはその時点でキュー・データ構造に関連するアドレスに関する変換にアクセスできるので、PCIeエンドポイントは、ルート複合体のATPTアドレス変換を行う必要なしに、キュー・データ構造にキュー項目をサブミットするかまたはキュー・データ構造からキュー項目を検索するためにDMA動作を実行することができる。

【0029】

キュー・データ構造がもはやPCIeエンドポイントによって使用されない場合、これらのキュー・データ構造に関するアドレスに対応するATPTおよびATC項目は、前に上述した方式で無効化することができる。このような無効化は、たとえば、PCIeエンドポイントがシステムから切り離される場合、デバイス・ドライバに関連する機能(物理または仮想)がホスト・システムから切り離された後などに実行することができる。この無効化プロセスは、デバイス・ドライバが、キュー・データ構造に対応するホスト・システム・メモリを滞留解除するためにデバイス・ドライバ・サービスを呼び出すこと、これらのキュー・データ構造に関するDMAアドレスを解放すること、これらのDMAアドレスに関するATPT項目を消去すること、およびATC項目無効化要求をPCIeエンドポイントに発行することを必要とする可能性がある。ATC項目無効化動作がPCIeエンドポイントによって完了されると、デバイス・ドライバ・サービスはデバイス・ドライバに制御を返し、この時点でPCIeエンドポイントをシステムから切り離すことができる。

【0030】

上述の通り、例示的な諸実施形態のメカニズムは、デバイス・ドライバ内のキュー・データ構造と、それに対応するデータ処理システムのルート複合体内のATPT項目を確立するために使用することができる。このようなキュー・データ構造が上述のメカニズムにより初期設定されると、これらのキュー・データ構造およびATPT項目を使用して、ホスト・システムのロジカル・パーティションのアプリケーション・インスタンス、システム・イメージなどとPCIeエンドポイントとの間の通信を実行することができる。

【0031】

これらのキュー・データ構造および対応するATPT項目は、種々のタイプのPCIeエンドポイントとともに使用することができる。たとえば、PCIeエンドポイントは、1つまたは複数のデータ・ネットワークにより他のデバイスと通信するためのイーサネット(登録商標)・アダプタ、ファイバ・チャネル・アダプタ、InfiniBand(R)アダプタなどのネットワーキング・アダプタにすることができる。このようなネットワーキング・アダプタにより、送受信中のデータは、ホスト・システムのデバイス・ドライバに関連するバッファ内に置かれ、データが受信中であるか送信中であるかに応じて、ホスト・システムのシステム・イメージまたはPCIeアダプタのいずれかによって取り出される。例示的な諸実施形態のメカニズムは、データの送信/受信時にルート複合体によるアドレス変換を受ける必要なしに、これらの変換済みアドレスおよびDMA動作を使用して送信バッファまたは受信バッファあるいはその両方にデータを直接送信できるように、キュー・データ構造の確立およびキューに対応する変換済みアドレスのキャッシュを可能にする。このため、このメカニズムは、ネットワーク・アダプタによるデータ送信および受信に関連する待ち時間を短縮する。

【0032】

ネットワーキング・アダプタとの使用に加えて、例示的な諸実施形態のメカニズムはさらに、ローカルに使用可能なデバイスと通信するために他のタイプのPCIeエンドポイントとともに使用することができる。たとえば、PCIeエンドポイントは、PCIeエンドポイントに直接接続された記憶装置と通信するための小型コンポーネント・システム・インターフェース(SCSI)アダプタにすることができる。例示的な諸実施形態のメカニズムは、SCSI読み取り/書き込みに関するアドレス情報をSCSIアダプタ内にキャッシュするためのメカニズムを提供することにより、SCSIアダプタのDMA読み取り待ち時間を短縮するために使用することができる。

【0033】

例示的な一実施形態では、システム・イメージとローカルに接続された外部記憶装置との間の動作を実行するための方法が提供される。この方法は、システム・イメージから記憶トランザクション要求を受信するステップと、コマンド・キュー・データ構造内のコマンド・キュー・エレメント(CQE)を作成するステップであって、そのCQEが、バッファ・データ構造の未変換アドレスを指定し、データ転送動作コマンドを含むステップを含むことができる。この方法はさらに、ローカルに接続された外部記憶装置と通信するための入出力(I/O)アダプタにより、コマンド・キュー・データ構造からCQEを検索するステップと、入出力アダプタに結合されたローカルに接続された外部記憶装置にデータ転送動作コマンドを送信するステップとを含むことができる。その上、この方法は、ローカルに接続された外部記憶装置にデータ転送動作コマンドを送信するのとほぼ同時に、入出力アダプタにより、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスについて、データ処理システムのルート複合体に要求を発行するステップを含むことができる。さらに、この方法は、入出力アダプタにより、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスを入出力アダプタのローカル・アドレス変換キャッシュに保管するステップを含むことができる。データ転送動作は、ローカルに接続された外部記憶装置への書き込みまたはローカルに接続された外部記憶装置からの読み取りのうちの一方にすることができる。

【0034】

この方法はさらに、入出力アダプタにより、ローカル・アドレス変換キャッシュに保管された1つまたは複数の変換済みアドレスを使用して、入出力アダプタとバッファ・データ構造との間の直接メモリ・アクセス(DMA)トランザクションを実行し、ローカルに接続された外部記憶装置から読み取られたデータをバッファ・データ構造に入れるステップを含むことができる。DMAトランザクションには、DMAトランザクションによって使用されるアドレスが変換済みアドレスであることを示す変換ビットが設定される可能性がある。ルート複合体は、変換ビットが設定されていることを検出したことに応答して、アドレス変換動作を実行せずに、DMA動作をバッファ・データ構造に直接渡すことができる。

【0035】

この方法はさらに、データ転送動作コマンドに関連するアドレス変換を入出力アダプタ内のCQEのローカル・コピーに保管するステップを含むことができる。この方法は、CQEを作成したことに応答して、そのCQEが入出力アダプタによる処理のために使用可能であることを示す値を入出力アダプタに関連するドアベル記憶装置に書き込むステップを含むことができる。入出力アダプタは、ドアベル記憶装置に値を書き込んだことに応答して、コマンド・キュー・データ構造からCQEを検索することができる。

【0036】

この方法は、データ処理システムのデバイス・ドライバにより、コマンド・キュー・データ構造に関するルート複合体に関連するアドレス変換データ構造内の1つまたは複数のアドレス変換項目を初期設定するためにデバイス・ドライバ・サービスを呼び出すステップを含むことができる。その上、この方法は、コマンド・キュー・データ構造に関連する1つまたは複数の未変換アドレスを入出力アダプタに提供するステップを含むことができる。1つまたは複数のアドレス変換項目は、コマンド・キュー・データ構造に関連する1つまたは複数の未変換アドレスから1つまたは複数の変換済みアドレスへの変換を指定することができる。入出力アダプタは、小型コンポーネント・システム・インターフェース(SCSI)アダプタ、シリアル接続SCSI(SAS)アダプタ、シリアル先端技術接続(SATA)、または先端技術接続(ATA)アダプタのうちの1つにすることができる。

【0037】

この方法はさらに、CQEのヘッダに提供された値を読み取るステップと、CQEのヘッダに提供された値に基づいて、CQEが読み取りデータ転送動作コマンドを含むかどうかを判断するステップとを含むことができる。1つまたは複数の変換済みアドレスについてルート複合体に要求を発行するステップと、1つまたは複数の変換済みアドレスを保管するステップは、CQEが読み取りデータ転送動作コマンドを含むという判断に応答して、実行することができる。

【0038】

また、この方法は、CQEのデータ転送動作コマンドの完了に応答して、入出力アダプタからシステム・イメージに関連する応答キュー・データ構造に応答キュー項目(RQE)を送信するステップも含むことができる。その上、この方法は、デバイス・ドライバにより、応答キュー・データ構造からRQEを検索するステップと、バッファ・データ構造に関連するホスト・メモリを滞留解除し、バッファ・データ構造に関連する1つまたは複数の未変換アドレスを解放し、バッファ・データ構造に対応するアドレス変換データ構造内のアドレス変換項目を消去するために、デバイス・ドライバにより、デバイス・ドライバ・サービスを呼び出すステップとを含むことができる。

【0039】

他の例示的な諸実施形態では、コンピュータ可読プログラムを有するコンピュータで使用可能な媒体(computer useable medium)を含むコンピュータ・プログラム(computer program product)が提供される。このコンピュータ可読プログラムは、コンピューティング・デバイス上で実行されると、方法の例示的な実施形態に関して上記で概要を示した動作のうちの様々なものおよびそれらの組み合わせをコンピューティング・デバイスに実行させるものである。

【0040】

さらに他の例示的な実施形態では、装置が提供される。この装置は、プロセッサと、プロセッサに結合された入出力アダプタであって、ローカルに接続された外部記憶装置と通信するために構成された入出力アダプタとを含むことができる。このプロセッサは、システム・イメージから記憶トランザクション要求を受信し、コマンド・キュー・データ構造内のコマンド・キュー・エレメント(CQE)を作成することができ、そのCQEは、バッファ・データ構造の未変換アドレスを指定し、データ転送動作コマンドを含む。入出力アダプタは、コマンド・キュー・データ構造からCQEを検索し、入出力アダプタに結合されたローカルに接続された外部記憶装置にデータ転送動作コマンドを送信し、ローカルに接続された外部記憶装置にデータ転送動作コマンドを送信するのとほぼ同時に、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスについて、データ処理システムのルート複合体に要求を発行することができる。その上、入出力アダプタは、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスを入出力アダプタのローカル・アドレス変換キャッシュに保管することができる。

【0041】

本発明の上記その他の特徴および利点は、本発明の模範的な諸実施形態に関する以下の詳細な説明に記載されるか、またはその詳細な説明を考慮すると当業者にとって自明なものになるであろう。

【0042】

本発明ならびにその好ましい使用態様、その他の目的および利点は、添付図面に併せて読んだときに、例示的な諸実施形態に関する以下の詳細な説明を参照することにより最もよく理解されるであろう。

【発明を実施するための最良の形態】

【0043】

例示的な諸実施形態は、エンドポイントとホスト・システムとの間のより効率的な直接メモリ・アクセス(DMA)動作を容易にするためにデバイス・ドライバおよびデバイス・ドライバ・サービスに対してエンドポイント・アドレス変換管理の役割を分散するためのメカニズムを提供する。このため、例示的な諸実施形態は、以下に記載する通り、デバイス・ドライバおよびデバイス・ドライバ・サービスを使用してDMA動作を実行できる任意のコンピューティング・デバイスで実現することができる。このようなコンピューティング・デバイスは、多くの形を取ることができ、様々な構成を有することができる。以下の図2〜図3では、例示的な諸実施形態の模範的な諸態様を実現可能なデータ処理環境およびデータ処理装置の例を示す。図2〜図3は模範的なものに過ぎず、例示的な諸実施形態のメカニズムを使用可能なデータ処理環境および装置のタイプに関して制限するものではないことを認識されたい。

【0044】

次に、添付図面、特に図2〜図3に関して説明すると、本発明の諸実施形態を実現可能なデータ処理環境の模範的な図が示されている。図2〜図3は例示的なものに過ぎず、本発明の諸態様または諸実施形態を実現可能な環境に関していかなる制限も主張または暗示するものではないことを認識されたい。本発明の精神および範囲を逸脱せずに、記述されている環境に対して多くの変更を行うことができる。

【0045】

次に、添付図面に関して説明すると、図2は、例示的な諸実施形態の諸態様を実現可能な模範的な分散データ処理システムの図表現を描写している。分散データ処理システム200は、例示的な諸実施形態の諸実施形態を実現可能なコンピュータのネットワークを含むことができる。分散データ処理システム200は少なくとも1つのネットワーク202を含み、このネットワークは分散データ処理システム200内にまとめて接続された様々な装置およびコンピュータ間の通信リンクを提供するために使用される媒体である。ネットワーク202は、ワイヤ、ワイヤレス通信リンク、または光ファイバ・ケーブルなどの接続を含むことができる。

【0046】

描写された例では、サーバ204およびサーバ206は、記憶装置208とともにネットワーク202に接続されている。加えて、クライアント210、212、および214もネットワーク202に接続されている。これらのクライアント210、212、および214は、たとえば、パーソナル・コンピュータ、ネットワーク・コンピュータなどにすることができる。描写された例では、サーバ204は、ブート・ファイル、オペレーティング・システム・イメージ、およびアプリケーションなどのデータをクライアント210、212、および214に提供する。クライアント210、212、および214は、描写された例ではサーバ204に対するクライアントである。分散データ処理システム200は、図示されていない追加のサーバ、クライアント、およびその他の装置を含むことができる。

【0047】

描写された例では、分散データ処理システム200は、相互に通信するために伝送制御プロトコル/インターネット・プロトコル(TCP/IP:Transmission Control Protocol/Internet Protocol)スイートのプロトコルを使用するネットワークおよびゲートウェイの世界的集合を表すネットワーク202を有するインターネットである。インターネットの中心には、データおよびメッセージをルーティングする、数千の商用、行政用、教育用、およびその他のコンピュータ・システムから構成される、メジャー・ノードまたはホスト・コンピュータ間の高速データ通信回線のバックボーンがある。当然のことながら、分散データ処理システム200は、たとえば、イントラネット、ローカル・エリア・ネットワーク(LAN)、広域ネットワーク(WAN)などのいくつかの異なるタイプのネットワークを含むように実現することもできる。上記の通り、図2は、本発明の種々の実施形態に関するアーキテクチャ上の制限としてではなく、一例として意図されており、したがって、図2に図示されている特定の諸要素は、本発明の例示的な諸実施形態を実現可能な環境に関して制限するものと見なすべきではない。

【0048】

次に、図3に関して説明すると、例示的な諸実施形態の諸態様を実現可能な模範的なデータ処理システムのブロック図が図示されている。データ処理システム300は、図2のホスト210などのコンピュータの一例であり、本発明の例示的な諸実施形態に関するプロセスを実現するコンピュータで使用可能なコードまたは命令をそこに配置することができる。

【0049】

描写された例では、データ処理システム300は、ノース・ブリッジおよびメモリ・コントローラ・ハブ(NB/MCH:north bridge and memory controller hub)302とサウス・ブリッジおよび入出力(I/O)コントローラ・ハブ(SB/ICH:south bridge and input/output controller hub)304とを含むハブ・アーキテクチャを使用している。NB/MCH302には、処理装置306、メイン・メモリ308、およびグラフィックス・プロセッサ310が接続されている。グラフィックス・プロセッサ310は、アクセラレィティッド・グラフィックス・ポート(AGP:accelerated graphics port)を介してNB/MCH302に接続することもできる。

【0050】

描写された例では、SB/ICH304にはローカル・エリア・ネットワーク(LAN)アダプタ312が接続している。オーディオ・アダプタ316、キーボードおよびマウス・アダプタ320、モデム322、読み取り専用メモリ(ROM)324、ハード・ディスク(HDD)326、CD−ROMドライブ330、ユニバーサル・シリアル・バス(USB)ポートおよびその他の通信ポート332、PCI/PCIeデバイス334は、バス338およびバス340を介してSB/ICH304に接続している。PCI/PCIeデバイスとしては、たとえば、イーサネット(登録商標)・アダプタ、アドイン・カード、およびノートブック・コンピュータ用のPCカードを含むことができる。PCIではカード・バス・コントローラを使用し、PCIeでは使用しない。ROM324は、たとえば、フラッシュ・バイナリ入出力システム(BIOS)にすることができる。

【0051】

HDD326およびCD−ROMドライブ330は、バス340を介してSB/ICH304に接続している。HDD326およびCD−ROMドライブ330は、たとえば、統合ドライブ・エレクトロニクス(IDE:integrated drive electronics)またはシリアル先端技術接続(SATA:serial advanced technology attachment)インターフェースを使用することができる。スーパー入出力(SIO:super I/O)デバイス336はSB/ICH304に接続することができる。

【0052】

オペレーティング・システムは処理装置306上で実行される。オペレーティング・システムは、図3のデータ処理システム300内の様々なコンポーネントの制御を調整し提供する。クライアントとしてのオペレーティング・システムは、Microsoft(R)のWindows(登録商標)XPなどの市販のオペレーティング・システムにすることができる(MicrosoftおよびWindowsは、米国、その他の国、あるいはその両方におけるマイクロソフト社の商標である)。Java(登録商標)プログラミング・システムなどのオブジェクト指向プログラミング・システムは、オペレーティング・システムに併せて実行することができ、データ処理システム300上で実行中のJava(登録商標)プログラムまたはアプリケーションからオペレーティング・システムへの呼び出しを提供する(Javaは、米国、その他の国、あるいはその両方におけるサン・マイクロシステムズ社の商標である)。

【0053】

サーバとしてのデータ処理システム300は、たとえば、拡張対話式エグゼクティブ(AIX(R):Advanced Interactive Executive)オペレーティング・システムまたはLINUX(R)オペレーティング・システムを実行するIBM(R)のeServer(R)pSeries(R)コンピュータ・システムにすることができる(eServer、pSeries、およびAIXは、米国、その他の国、あるいはその両方におけるインターナショナル・ビジネス・マシーンズ社の商標であり、LINUXは、米国、その他の国、あるいはその両方におけるLinus Torvaldsの商標である)。データ処理システム300は、処理装置306内に複数のプロセッサを含む対称型マルチプロセッサ(SMP:symmetric multiprocessor)システムにすることができる。代わって、シングル・プロセッサ・システムを使用することもできる。

【0054】

オペレーティング・システム、オブジェクト指向プログラミング・システム、およびアプリケーションまたはプログラムに関する命令は、HDD326などの記憶装置上に配置され、処理装置306によって実行するためにメイン・メモリ308にロードすることができる。本発明の例示的な諸実施形態に関するプロセスは、たとえば、メイン・メモリ308、ROM324などのメモリ内に、または、たとえば、1つまたは複数の周辺装置326および330内に配置することができる、コンピュータで使用可能なプログラム・コードを使用して処理装置306によって実行することができる。

【0055】

図3に図示されているバス338またはバス340などのバス・システムは、1つまたは複数のバスで構成することができる。当然のことながら、バス・システムは、そのファブリックまたはアーキテクチャに接続された種々のコンポーネントまたはデバイス間のデータ転送を可能にする任意のタイプの通信ファブリックまたはアーキテクチャを使用して実現することができる。図3のモデム322またはネットワーク・アダプタ312などの通信装置は、データを送受信するために使用される1つまたは複数の装置を含むことができる。メモリは、たとえば、メイン・メモリ308、ROM324、または図3のNB/MCH302内に見られるようなキャッシュにすることができる。

【0056】

当業者であれば、図2〜図3のハードウェアは実現例に応じて様々になる可能性があることが分かるであろう。図2〜図3に描写されているハードウェアに加えてまたはその代わりに、フラッシュ・メモリ、同等の不揮発性メモリ、または光ディスク・ドライブなどのその他の内部ハードウェアまたは周辺装置を使用することができる。また、例示的な諸実施形態のプロセスは、本発明の精神および範囲を逸脱せずに、前に述べたSMPシステム以外のマルチプロセッサ・データ処理システムに適用することもできる。

【0057】

その上、データ処理システム300は、クライアント・コンピューティング・デバイス、サーバ・コンピューティング・デバイス、タブレット・コンピュータ、ラップトップ・コンピュータ、電話またはその他の通信装置、携帯情報端末(PDA)などを含む、いくつかの異なるデータ処理システムのうちのいずれかの形を取ることができる。いくつかの例示的な例では、データ処理システム300は、たとえば、オペレーティング・システム・ファイルまたはユーザ生成データあるいはその両方を保管するための不揮発性メモリを提供するためにフラッシュ・メモリとともに構成されたポータブル・コンピューティング・デバイスにすることができる。本質的に、データ処理システム300は、アーキテクチャ上の制限なしに、任意の既知のデータ処理システムまたはその後開発されたデータ処理システムにすることができる。

【0058】

前述の通り、例示的な諸実施形態は、デバイス・ドライバとデバイス・ドライバ・サービスとの間でエンドポイント・アドレス変換キャッシュ管理に関する役割を分散するためのシステムおよびメカニズムを提供する。デバイス・ドライバは、たとえば、信頼できないミッション・ロジカル・パーティション(LPAR)内に設けることができ、デバイス・ドライバ・サービスは、たとえば、信頼できる入出力(I/O)仮想化仲介(VI:virtualization intermediary)内に設けることができる。例示的な諸実施形態の説明ではPCIeエンドポイントおよびPCIe通信プロトコルを使用するが、例示的な諸実施形態はこのようなものに限定されず、本発明の精神および範囲を逸脱せずに、任意の通信プロトコルを使用できることを認識されたい。

【0059】

例示的な諸実施形態に関しては、デバイス・ドライバは、ユーザ・アプリケーション/ライブラリとPCIeエンドポイントとの間で通信するためのキュー構造を管理し使用する役割を担う。デバイス・ドライバはさらに、デバイス・ドライバ・サービスによって提供されたメモリ管理サービスを呼び出す役割を担う。デバイス・ドライバ・サービスは、コンピューティング・システムのPCIeルート複合体のアドレス変換および保護テーブル(ATPT)ならびにPCIeエンドポイントのアドレス変換キャッシュ(ATC)を初期設定し管理する。このような初期設定および管理が実行される方法については以下に説明する。

【0060】

例示的な一実施形態では、ホスト・システムのロジカル・パーティションのシステム・イメージ内のPCIeエンドポイント用のデバイス・ドライバの初期設定中に、PCIeエンドポイント用のデバイス・ドライバは、アドレス変換および保護テーブル(ATPT)項目を初期設定し、デバイス・ドライバにPCIメモリ・アドレスを返すためにデバイス・ドライバ・サービスを呼び出す。例示的な一実施形態では、これらのATPT項目およびPCIメモリ・アドレスは、PCIeアダプタと通信するために、「デバイス・ドライバのキュー」というデバイス・ドライバの1つまたは複数のキューに関連づけられる。

【0061】

本質的に、デバイス・ドライバ・サービスは、1つまたは複数のキュー用のホスト・システム・メモリを滞留させ、1つまたは複数のキューにDMAアドレスを割り当て、ATPT項目をプログラミングし、ATPT項目がキャッシュ可能であること、すなわち、PCIeエンドポイント上でアドレス変換キャッシュ内にキャッシュ可能であることを示すビットを使用可能にする。次に、デバイス・ドライバ・サービスは、1つまたは複数の未変換PCIeメモリ・アドレスを、たとえば、1つまたは複数のキューに関連するアドレス(たとえば、キューの開始アドレス、ならびに、任意選択で終了キュー・アドレス)として使用可能なATPT項目用のデバイス・ドライバに返す。未変換PCIeメモリ・アドレスは、システムの実メモリ・アドレス空間内にないアドレスであり、システムの実メモリにアクセスするために使用するには、その前に変換しなければならないものである。

【0062】

例示的な諸実施形態のメカニズムを使用すると、この未変換PCIeメモリ・アドレス(複数も可)をPCIeエンドポイントに提供し、ルート複合体による変換要求動作を実行するためにPCIeエンドポイントがそれを使用することができる。すなわち、PCIeエンドポイントは、ルート複合体が未変換PCIeメモリ・アドレスに対応する1つまたは複数の変換済みPCIeメモリ・アドレスを返すことを要求することができる。次に、PCIeエンドポイントは、1つまたは複数の変換済みPCIeメモリ・アドレスをデバイス・ドライバのキューに関連するコンテキスト、たとえば、PCIeエンドポイント内の仮想機能のアドレス変換キャッシュ(ATC)に保管することができる。

【0063】

未変換PCIeメモリ・アドレスの変換をアダプタのデバイス・ドライバ・キュー・コンテキストに保管することにより、PCIeエンドポイントは、デバイス・ドライバ・キュー項目をターゲットにするDMAの際にルート複合体のATPTをバイパスすることができる。したがって、ルート複合体が変換済みとしてマークが付けられたPCIe DMAトランザクションを受信すると、ルート複合体は、そのエンドポイントについて変換キャッシュが使用可能になっていることを検証し、ホストの実メモリに直接アクセスするために変換済みPCIeメモリ・アドレスを使用する。

【0064】

PCIeエンドポイントがシステムから切り離された後、デバイス・ドライバに関連する機能(物理または仮想)がシステムから切り離された後など、その後の何らかの時点で、未変換PCIeメモリ・アドレスに対応するATPT項目およびATC項目を無効化する必要がある可能性がある。このような無効化を実行するために、デバイス・ドライバあるいはハイパーバイザ管理コンポーネントなどの何らかの上位エンティティは、ホスト・メモリを滞留解除し、DMAアドレス、すなわち、未変換PCIeメモリ・アドレスを解放するためにデバイス・ドライバ・サービスを呼び出す。次に、デバイス・サービスは、未変換PCIeメモリ・アドレスに対応するATPT項目を消去し、ルート複合体はATC項目無効化要求をPCIeエンドポイントに発行する。

【0065】

次に、PCIeエンドポイントは、未変換PCIeメモリ・アドレスに対応する任意のATC項目を無効化するための動作を実行し、未変換PCIeメモリ・アドレスがもはや使用されなくなった後に、ATC無効化完了応答をデバイス・サービスに返す。次に、デバイス・ドライバ・サービスはデバイス・ドライバに制御を返す。代替実現例は、デバイス・ドライバ・サービスによってATC項目無効化要求をPCIeエンドポイントに発行することから構成され、PCIeエンドポイントがATC項目無効化を完了した後に、デバイス・ドライバ・サービスはATPT項目を消去し、デバイス・ドライバに制御を返すことができる。

【0066】

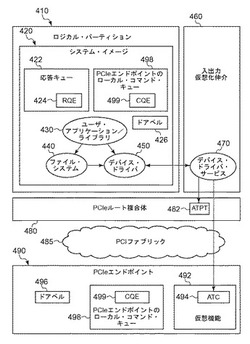

図4は、デバイス・ドライバおよびデバイス・ドライバ・サービスに関する例示的な一実施形態の動作を例示する模範的な図である。図4に図示されている通り、ホスト・システムは、システム・イメージ420、たとえば、オペレーティング・システムなどを実行可能な1つまたは複数のロジカル・パーティション410を有することができる。システム・イメージ420は、アプリケーション・ライブラリなどへのアクセスによりユーザ・アプリケーション430を実行するために使用することができる。システム・イメージ420は、それによりファイル、デバイス・ドライバ、ライブラリ、およびその他のソフトウェア・リソースにアクセス可能な関連ファイル・システム440を有する。デバイス・ドライバ450は、システム・イメージ420とPCIeアダプタ490との間で通信するためにシステム・イメージ420内に設けることができる。

【0067】

デバイス・ドライバ450はさらに、それによりユーザ・アプリケーション430、システム・イメージ420などがPCIeエンドポイント490と通信することができる関連応答キュー422を有する。応答キュー422は、デバイス・ドライバ450、ユーザ・アプリケーション430、システム・イメージ420、ホスト・システム・メモリ、およびその他のホスト・システム・リソースによって実行されることをPCIeエンドポイント490が希望する動作に関する応答キュー項目(RQE:response queue entry)424を有する。ドアベル(doorbell)記憶装置426は、応答キュー422が処理する必要のある応答キュー項目424を有するときにシステム・イメージ420に通知するために、応答キュー422およびシステム・イメージ420に関連して設けられる。このようなキューによって実行可能な作業の例としては、PCIeエンドポイント490から要求された作業システム・イメージ420に関連する完了処理、システム・イメージ420に対してPCIeエンドポイント490によって表面化されたエラーまたはイベントに関連する非同期イベント処理などを含む。

【0068】

同様に、PCIeエンドポイント490は、PCIeエンドポイント490によって実行されることをシステム・イメージ420、ユーザ・アプリケーション430などが希望する動作をPCIeエンドポイント490に通知するためにコマンド・キュー項目(CQE:command queue entry)499を設けることができる、関連PCIeエンドポイント・コマンド・キュー498を有することができる。PCIeエンドポイント490のコマンド・キュー498は、PCIeエンドポイント490そのものに、または、より一般的には、描写されている通り、PCIeエンドポイント490によってアクセス可能なシステム・イメージ420のメモリ・ロケーションに実現することができる。ドアベル記憶装置496は、CQE499が処理のためにPCIeエンドポイント・コマンド・キュー498内に存在する時期をPCIeエンドポイント490に通知するためにPCIeエンドポイント490に設けることができる。

【0069】

PCIeエンドポイント490はさらに、1つまたは複数の物理機能(図示せず)および仮想機能492を有する。仮想機能492はさらに、たとえば、ホスト・システム・メモリにより直接メモリ・アクセス(DMA)動作を実行する際に使用するための変換済みアドレスをキャッシュするためにアドレス変換キャッシュ(ATC)494を維持することができる。ATC494は、PCIeエンドポイント490のデバイス・ドライバのキュー・コンテキストに保管することができる。

【0070】

PCIeエンドポイント490は、通信リンク、1つまたは複数のPCIスイッチなどから構成することができるPCIファブリック485を介して、ホスト・システムに結合されている。ホスト・システムは、PCIファブリック485を介してPCIeエンドポイント490と通信するためのPCIeルート複合体480を有する。ルート複合体480は、未変換PCIeメモリ・アドレスを、システムの実メモリ・アドレス空間で使用される変換済みアドレスに変換するために使用される、アドレス変換および保護テーブル(ATPT)482を維持する。

【0071】

ATPT482およびATC494の管理は、入出力(I/O)仮想化仲介(VI)460内に設けられたデバイス・ドライバ・サービス470によって実行される。IOVI460は、たとえば、信頼できるサービス・パーティションなど、ハイパーバイザまたはその他の仮想化管理コンポーネントにすることができる。デバイス・ドライバ・サービス470は、ATPT482およびATC494内の項目を初期設定し無効化するために必要であるときに、デバイス・ドライバ450によって呼び出すことができる。

【0072】

ホスト・システムとPCIeエンドポイントとの間の通信を管理する役割は、デバイス・ドライバ450とデバイス・ドライバ・サービス470との間で分割される。具体的には、デバイス・ドライバ450は、その応答キュー422およびPCIeエンドポイントのコマンド・キュー498を管理する役割を担う。デバイス・ドライバ450はさらに、ATPT482内のアドレス変換項目を初期設定するために、ならびに、変換がもはやPCIeエンドポイント490によって使用されないときにATPT482およびATC494内の項目を無効化するために必要な機能を実行するために必要であるときに、デバイス・ドライバ・サービス470を呼び出す役割を担う。

【0073】

デバイス・ドライバ450の初期設定中に、デバイス・ドライバ450は、デバイス・ドライバ応答キュー422、PCIeエンドポイント490と通信するためにシステム・イメージ420内に存在するPCIeエンドポイントのコマンド・キュー498などの1つまたは複数のキューに関するDMAアドレス空間を初期設定することができる。次に、PCIeエンドポイント490用のデバイス・ドライバ450は、システム・メモリの一部分にアクセスするためにPCIeアドレスをDMAアドレス空間アドレスに変換するためのATPT482の項目を初期設定するためにデバイス・ドライバ・サービス470を呼び出す。それぞれのATPT項目は、1組の連続PCIバス・アドレスに関するものである。アドレス変換および保護テーブルの項目を初期設定するためのメカニズムは一般に当技術分野で既知のものである。たとえば、このような項目を初期設定するためのメカニズムは、本出願人に譲渡された米国特許第6629162号に記載されている。次に、デバイス・ドライバ・サービス470は、1つまたは複数のPCIメモリ・アドレスをデバイス・ドライバ450に返す。

【0074】

本質的に、描写された例では、デバイス・ドライバ・サービス470は、応答キュー422と、それがシステム・イメージ420内に存在する場合にPCIeエンドポイントのコマンド・キュー498とに関するホスト・メモリを滞留させる。デバイス・ドライバ・サービス470は、デバイス・ドライバの応答キュー422と、それがシステム・イメージ420内に存在する場合にPCIeエンドポイントのコマンド・キュー498とに対して、未変換PCIeメモリ・アドレスであるDMAアドレスを割り当てる。デバイス・ドライバ・サービス470は、ATPT項目をプログラミングし、デバイス・ドライバの応答キュー422と、それがシステム・イメージ420内に存在する場合にPCIeエンドポイントのコマンド・キュー498とに関するATPT項目がキャッシュ可能であること、すなわち、PCIeエンドポイント490上のATC494内にキャッシュ可能であることを示すビットを使用可能にする。次に、デバイス・ドライバ・サービス470は、ATPT項目用のデバイス・ドライバ450に未変換PCIeメモリ・アドレスを返す。

【0075】

例示的な諸実施形態のメカニズムを使用すると、この未変換PCIeメモリ・アドレス(複数も可)をPCIeエンドポイント490に提供して、キュー422および498の位置をPCIeエンドポイント490に通知することができる。この未変換PCIeメモリ・アドレス(複数も可)は、ルート複合体480に変換要求動作を送信するためにPCIeエンドポイント490が使用することができる。すなわち、PCIeエンドポイント490は、ルート複合体480が未変換PCIeメモリ・アドレスに関連する変換済みPCIeメモリ・アドレス(複数も可)を返すことを要求することができる。次に、PCIeエンドポイント490は、変換済みPCIeメモリ・アドレス(複数も可)をデバイス・ドライバのキューに関連するコンテキスト、たとえば、ATC494に保管することができる。その結果、未変換PCIeメモリ・アドレスの変換をPCIeエンドポイントのデバイス・ドライバ・キュー・コンテキストまたはATC494に保管することにより、PCIeエンドポイント490は、デバイス・ドライバ・キュー項目、たとえば、応答キュー422内のRQE424をターゲットにするDMAの際にルート複合体のATPT482をバイパスすることができる。すなわち、ルート複合体480が変換済みとしてマークが付けられたPCIe DMAトランザクションを受信すると、ルート複合体は、PCIeエンドポイント490について変換キャッシュが使用可能になっていることを検証し、ホスト・システムの実メモリに直接アクセスするために変換済みPCIeメモリ・アドレスを使用することになる。

【0076】

PCIeエンドポイント490がシステムから切り離された後、デバイス・ドライバ450に関連する機能(物理または仮想)がホスト・システムから切り離された後など、その後の何らかの時点で、未変換PCIeメモリ・アドレス(複数も可)に対応するATPT項目およびATC項目を無効化する必要がある可能性がある。このような無効化を実行するために、デバイス・ドライバ450、ハイパーバイザ管理コンポーネントなどは、ホスト・メモリを滞留解除し、DMAアドレス(複数も可)、すなわち、未変換PCIeメモリ・アドレス(複数も可)を解放するためにデバイス・ドライバ・サービス470を呼び出す。次に、デバイス・ドライバ・サービス470は、たとえば、その項目がもはや有効ではないことを示すビットをATPT482内に設定するか、またはそれがもはや有効ではないことを示すためにATPT項目を「ゼロにする」ことにより、未変換PCIeメモリ・アドレス(複数も可)に対応するATPT482内のATPT項目を消去する。

【0077】

次に、ルート複合体480は、ATC項目無効化要求をPCIeエンドポイント490に発行する。次に、PCIeエンドポイント490は、未変換PCIeメモリ・アドレス(複数も可)に対応するATC494内の任意のATC項目を無効化するための動作を実行する。このような無効化は、たとえば、変換をキャッシュしていた任意の仮想機能のキュー・コンテキスト、たとえば、ATC494から、キャッシュされた変換を除去することを必要とする可能性がある。未変換PCIeメモリ・アドレスがもはや使用されなくなった後に、すなわち、未変換PCIeメモリ・アドレスを参照するすべての未解決のDMA動作が完了したときに、PCIeエンドポイント490はATC無効化完了応答をデバイス・サービス470に返す。次に、デバイス・ドライバ・サービス470はデバイス・ドライバ450に制御を返す。代替実現例では、デバイス・ドライバ・サービス470は、ATC項目無効化要求をPCIeエンドポイント490に発行することができ、PCIeエンドポイント490がATC項目無効化を完了した後に、デバイス・ドライバ・サービス470はATPT482内のATPT項目を消去し、デバイス・ドライバ450に制御を返すことができる。

【0078】

図5は、例示的な一実施形態によりDMA動作による変換済みおよび未変換PCIeアドレスの処理を例示する模範的な図である。図5に図示されている動作では、前に述べた通り、デバイス・ドライバおよびデバイス・ドライバ・サービスを使用して、DMA動作に関する適切なATPT項目が初期設定されているものと想定している。図5は、PCIeエンドポイント505からホスト・システムのCPUおよびメモリ560に送信されている未変換PCIeアドレスを使用するDMAに関する1つの動作と、PCIeエンドポイント505からCPUおよびメモリ560に送信されている変換済みPCIeアドレスを使用するDMAに関するもう1つの動作を示している。

【0079】

図5に図示されている通り、PCIeエンドポイント505の仮想機能でDMA動作要求が生成または受信されると、未変換PCIeアドレスに関するアドレス変換がATC内に存在するかどうかを判断するために、対応するATCのチェックを実行することができる。未変換PCIeアドレスに関する項目がATC内に存在しない場合、未変換PCIeアドレスを使用する未変換PCIe DMA510として、ルート複合体530にDMA動作要求が転送される。ATC内で項目が使用可能であり、その項目が無効化されていない場合、DMAに関する未変換PCIeアドレスの代わりに変換済みアドレスを使用することができる。その結果、変換済みアドレス520を使用する変換済みPCIe DMAがルート複合体530に転送される。

【0080】

未変換PCIe DMA510の場合、未変換PCIeアドレスはホスト・システム・メモリ・アドレス空間内にないので、まず未変換PCIeアドレスをホスト・システム・メモリ・アドレスに変換することが必要である。この変換は、ATPTを使用して、ルート複合体530によって実行される。加えて、ルート複合体530はさらに、PCIeエンドポイント505のBDF番号およびATPT内の項目に基づいて、アクセス検査を実行する。すなわち、ルート複合体530は、ATPT540内の未変換PCIeアドレスに対応する項目をルックアップし、未変換PCIeアドレスに対応する変換済みホスト・システム・メモリ・アドレスと、変換済みホスト・システム・メモリ・アドレスに関する対応する保護情報とを取得する。保護情報は、どのBDF番号が対応するホスト・システム・アドレスにアクセス可能であるかと、これらのホスト・システム・メモリ・アドレスに対応するシステム・メモリの一部分でこれらが実行可能な特定の動作とを識別することができる。

【0081】

PCIeエンドポイント505が変換済みシステム・メモリ・アドレスに対応するシステム・メモリの一部分にアクセスすることが許可されており、要求されたDMA動作(たとえば、読み取り/書き込み)を実行することが許可されている場合、DMA動作要求は、変換済みシステム・メモリ・アドレス570を使用して、CPUおよびメモリ560に転送される。PCIeエンドポイント505がシステム・メモリの一部分にアクセスすることが許可されていない場合、エラー・メッセージが返される可能性があり、DMA動作要求はCPUおよびメモリ560に転送されない可能性がある。

【0082】

未変換PCIeアドレスに関する変換済みシステム・メモリ・アドレスはPCIeエンドポイント505に返すことができる。次に、PCIeエンドポイント505は、図4に関して上述した通り、DMA動作要求をサブミットした仮想機能のATCに変換を保管することができる。このようにして、この変換を後で実行しなければならないのではなく、ATCを介してPCIeエンドポイント内で変換済みシステム・メモリ・アドレスにアクセスすることができ、これにより、未変換PCIeアドレスのATPT変換に必要なサイクルが節約される。

【0083】

変換済みPCIe DMA520の場合、PCIeアドレスはPCIeエンドポイント505内の仮想機能のATCによってすでにシステム・メモリ・アドレスに変換されているので、DMA動作は、ルート複合体530を通過してCPUおよびメモリ560に移行することができる。たとえば、変換済みPCIe DMA520は、DMA動作要求のヘッダに指定されたアドレスが変換済みアドレスであることを示すビットがDMAヘッダ内に設定されている(たとえば、PCIeエンドポイント505によって設定されている)。ルート複合体530は、このビットを読み取り、DMA動作要求内のアドレスが変換済みアドレスまたは未変換アドレスであることをそのビットが示すかどうかを判断することができる。

【0084】

そのアドレスが未変換アドレスであるとルート複合体530が判断した場合、未変換PCIe DMA動作要求510に関して上記で概要を示した動作が実行される。そのアドレスが変換済みアドレスであるとルート複合体530が判断した場合、ルート複合体530は、DMA動作要求520をCPUおよびメモリ560に渡すことができる。任意選択で、PCIeエンドポイントが変換済みシステム・メモリ・アドレスに対応するシステム・メモリの一部分にアクセスすることが許可されていることを保証するために、依然としてPCIeエンドポイント505のBDF番号に基づいてアクセス検査を実行することができる。このアクセス検査は、そのBDF番号によってアドレス変換をキャッシュできるかどうかを判断するための一般的検査など、非常に単純なものである可能性があり、そのBDF番号によってキャッシュできる場合、検査は成功である。そのBDF番号ではアドレス変換をキャッシュできない場合、アクセス検査は失敗である。

【0085】

図6〜図8は、例示的な諸実施形態の様々な要素の模範的な動作の概要を示している。これらの流れ図の各ブロック、その後の流れ図、ならびに流れ図内のブロックの組み合わせがコンピュータ・プログラム命令によって実現できることは理解されるであろう。これらのコンピュータ・プログラム命令は、プロセッサまたはその他のプログラマブル・データ処理装置上で実行される命令によって流れ図の1つまたは複数のブロックに指定された機能を実現するための手段が作成されるようにマシンを生産するために、プロセッサまたはその他のプログラマブル・データ処理装置に提供することができる。また、これらのコンピュータ・プログラム命令は、コンピュータ可読メモリまたは記憶媒体に保管された命令によって流れ図の1つまたは複数のブロックに指定された機能を実現する命令手段を含む製品(article of manufacture)が生産されるように特定の方法で機能するようプロセッサまたはその他のプログラマブル・データ処理装置に指示できるコンピュータ可読メモリまたは記憶媒体に保管することもできる。

【0086】

したがって、流れ図のブロックは、指定の機能を実行するための手段の組み合わせ、指定の機能を実行するためのステップの組み合わせ、ならびに指定の機能を実行するためのプログラム命令手段をサポートする。また、これらの流れ図の各ブロックならびに流れ図内のブロックの組み合わせが、指定の機能またはステップを実行する特殊目的ハードウェアベースのコンピュータ・システムによって、または特殊目的ハードウェアとコンピュータ命令の組み合わせによって実現できることは理解されるであろう。

【0087】

図6は、例示的な一実施形態によりDMAアドレスに関するATPT項目を初期設定するための模範的な動作の概要を示す流れ図である。図6に図示されている通り、動作は、ホスト・システム上のシステム・イメージの初期設定の一部として、ホスト・システムによって行われるPCIeエンドポイント用のデバイス・ドライバの初期設定から始まる(ステップ610)。ホスト・システムはロジカル・パーティション内のデバイス・ドライバを呼び出し、次にそのデバイス・ドライバが入出力仮想化仲介内のデバイス・ドライバ・サービスを呼び出す(ステップ620)。デバイス・ドライバ・サービスはホスト・システム・メモリを滞留させる(ステップ630)。

【0088】

デバイス・ドライバ・サービスはDMAアドレスをPCIeエンドポイントに割り当てる(ステップ640)。デバイス・ドライバ・サービスは、DMAアドレスに関するATPT項目をプログラミングし、適切であれば、キャッシュ使用可能ビットをATPT項目内に設定する(ステップ650)。次に、デバイス・ドライバ・サービスは未変換PCIeメモリ・アドレス(複数も可)をデバイス・ドライバに返し(ステップ660)、動作は終了する。

【0089】

図7は、例示的な一実施形態によりDMAアドレスに関するATPT項目およびATC項目を無効化するための模範的な動作の概要を示す流れ図である。図7に図示されている通り、動作は、デバイス・ドライバがデバイス・ドライバ・サービスを呼び出すことから始まる(ステップ710)。デバイス・ドライバ・サービスはDMAアドレスを解放し(ステップ720)、次にDMAアドレスに関するATPT項目を消去する(ステップ730)。

【0090】

ルート複合体はATC項目無効化要求をPCIeエンドポイントに発行する(ステップ740)。PCIeエンドポイントは、無効化すべきDMAアドレスに対応するATC項目を無効化する(ステップ750)。デバイス・ドライバ・サービスは、ATC無効化完了応答が受信されるのを待つ(ステップ760)。ATC無効化完了応答が受信されると、デバイス・ドライバ・サービスはホスト・システム・メモリを滞留解除することができ(ステップ770)、ATC無効化が完了すると、デバイス・ドライバに制御を返すことができる(ステップ780)。次に動作は終了する。

【0091】

図8は、例示的な一実施形態によりDMA動作において変換済みおよび未変換PCIeアドレスを処理するための模範的な動作の概要を示す流れ図である。図8に図示されている通り、動作は、ルート複合体においてDMAトランザクションを受信することから始まる(ステップ810)。ルート複合体は、変換済みビットが設定されているかどうかを判断する(ステップ820)。変換済みビットが設定されていない場合、ルート複合体は、ATPTを使用して完全変換およびBDF番号アクセス検査を実行する(ステップ830)。

【0092】

その後、2通りの動作経路をたどる。第1の経路では、DMA動作のソースが変換済みDMA動作を実行することが許可されているかどうかに関する判断、すなわち、アクセス検査が正常に完了したかどうかに関する判断が行われる(ステップ840)。許可されていない場合、エラーが返される(ステップ860)。ソースが変換済みDMA動作を実行することが許可されている場合、ルート複合体はDMAを実行する(ステップ850)。次に動作は終了する。

【0093】

変換済みビットが設定されている場合(ステップ820)、任意選択のBDF番号アクセス検査を実行することができる(ステップ870)。動作は、ステップ830のアドレス変換をバイパスして、ステップ840に進む。

【0094】

したがって、例示的な諸実施形態は、ホスト・システムのルート複合体のアドレス変換データ構造においてアドレス変換を初期設定し無効化するためにデバイス・ドライバ・サービスを呼び出すためのメカニズムを提供する。これらのデバイス・ドライバ・サービスは、入出力仮想化仲介内に設けることができ、システム・イメージに関連してロジカル・パーティション内に設けられたデバイス・ドライバによって呼び出すことができる。デバイス・ドライバ・サービスは、ルート複合体により、仮想アドレス、たとえば、未変換PCIeアドレスをシステム・メモリ・アドレスに変換するためのアドレス変換データ構造項目を作成することができる。その上、デバイス・ドライバ・サービスは、ルート複合体により、アドレス変換データ構造からアドレス変換項目を消去し、PCIeエンドポイントにより、PCIeエンドポイントの任意のアドレス変換キャッシュ内の項目を無効化することができる。

【0095】

前述の通り、例示的な諸実施形態のメカニズムは、システム・イメージと、システム・イメージなどで実行されるアプリケーションと、1つまたは複数のキュー・データ構造を使用するPCIeエンドポイントとの間で通信する際に使用するためのATPT項目を確立するために使用することができる。例示的な諸実施形態のこのような実現例では、1つまたは複数のキュー・データ構造に関するATPT項目は、前に上述したように初期設定される。PCIeエンドポイントの初期設定フェーズ中に、PCIeエンドポイントは、デバイス・ドライバが初期設定されていることを検証する。これは、たとえば、PCIeエンドポイントのPCI構成空間、重要プロダクト・データ(VPD)フィールド、またはメモリ・マップ入出力(MMIO)フィールドから情報を読み取ることにより、実行することができる。

【0096】

デバイス・ドライバは、1つまたは複数のキューの開始および終了アドレス、開始アドレスおよび長さなどをPCIeエンドポイントに提供することができる。たとえば、デバイス・ドライバは、キュー構成空間に対応するPCIeエンドポイントのPCI構成空間フィールド、VPDまたはMMIOフィールドにこれらのアドレスを書き込むことができる。これらのアドレスは未変換PCIeアドレスである。PCIeエンドポイントは、キュー・アドレスの変換に関するPCIe ATS要求を呼び出すことができる。その結果、ルート複合体は、ATPTを使用してアドレス変換を実行し、1つまたは複数のキューから項目を検索する際に使用するためにキュー・コンテキストに変換済みアドレスをキャッシュすることができるPCIeエンドポイントに結果を返し、項目を1つまたは複数のキュー内に入れることができる。このようにしてキュー・アドレスを事前変換することにより、入出力動作を開始する際に必要となる待ち時間は、変換動作の待ち時間を各動作の開始から任意の動作開始前に移動することによって短縮され、したがって、エンドポイントのDMA動作の全体的なパフォーマンスが改善される。

【0097】

図9は、PCIeエンドポイント・キューに関するアドレス変換をキャッシュするための例示的な諸実施形態の実現例を例示している。図9に図示されている通り、デバイス・ドライバ910は、PCIeエンドポイント990と通信するためのキュー・データ構造920〜930を生成する。描写された例では、キュー・データ構造920〜930は、たとえば、図4のPCIeエンドポイントのコマンド・キュー498と同等である可能性のあるコマンド・キュー920と、たとえば、図4の応答キュー422と同等である可能性のある応答キュー930とを含む。デバイス・ドライバ910によって確立可能なキューの数が2に限定されず、本発明の精神および範囲を逸脱せずに、それより少ないかまたは多い数のキューを使用できることを認識されたい。

【0098】

キュー・データ構造920〜930は、たとえば、PCIeエンドポイント990に結合された小型コンポーネント・システム・インターフェース(SCSI)入出力装置と通信するためのSCSIキューにすることができる。これらのキュー・データ構造は、リンク・リスト・キュー、サーキュラ・バッファ・キューなどを含む任意の方式で構成することができる。

【0099】

これらのキュー・データ構造920〜930を生成する際にデバイス・ドライバ910によって実行される動作の一部として、デバイス・ドライバ910は、キュー・データ構造920〜930に関するATPT項目をプログラミングし、キューに関する未変換PCIeアドレスをデバイス・ドライバ910に返すためにデバイス・ドライバ・サービス940を呼び出す。前に上述した通り、例示的な諸実施形態では、ATPT項目のプログラミングは、キュー・データ構造に使用されるホスト・メモリ空間950を滞留させること、未変換PCIeアドレスからシステム・メモリ・アドレスに変換するための変換情報によりルート複合体970のATPT962内のATPT項目をプログラミングすること、ならびにATPT項目に対応するアドレス変換がPCIeエンドポイント990のATC992内にキャッシュ可能であることを示すキャッシュ使用可能ビットをATPT項目内に設定することを必要とする可能性がある。このような動作を実行した後、ATPT項目に関する未変換PCIeアドレスがデバイス・ドライバ910に返される。これらの未変換PCIeアドレスは、たとえば、キュー・データ構造920〜930の開始および終了アドレスを識別することができる。

【0100】

未変換PCIeアドレスは、PCIeエンドポイント990内のキュー構成空間994にアドレスを書き込むことなどにより、デバイス・ドライバ910によってPCIeエンドポイント990に提供される。キュー構成空間994は、たとえば、PCI構成空間、1つまたは複数のVPDフィールド、1つまたは複数のMMIOフィールドなどにすることができる。キュー・データ構造920〜930に関するこれらの未変換PCIeアドレスを受信したことに応答して、PCIeエンドポイント990は、キュー・アドレスに関するPCIe ATS要求をルート複合体970に発行することができる。その結果、ルート複合体970は、キュー・データ構造920〜930の未変換PCIeアドレスに関するアドレス変換およびアクセス検査を実行し、変換済みアドレスをPCIeエンドポイント990に返すことができる。次に、PCIeエンドポイント990は、PCIeエンドポイント990のアドレス変換キャッシュ(ATC)992によって提供されたキュー・コンテキスト内にこれらのアドレス変換を保管することができる。

【0101】

上記の結果として、PCIeエンドポイントはその時点でキュー・データ構造920〜930に関連するアドレスに関する変換にアクセスできるので、PCIeエンドポイントは、ルート複合体970のATPTアドレス変換を行う必要なしに、キュー・データ構造920〜930にキュー項目をサブミットするかまたはキュー・データ構造920〜930からキュー項目を検索するためにDMA動作を実行することができる。

【0102】

キュー・データ構造920〜930がもはやPCIeエンドポイント990によって使用されない場合、これらのキュー・データ構造920〜930に関するアドレスに対応するATPTおよびATC項目は、前に上述した方式で無効化することができる。このような無効化は、たとえば、PCIeエンドポイントがシステムから切り離される場合、デバイス・ドライバに関連する機能(物理または仮想)がホスト・システムから切り離された後などに実行することができる。前に述べた通り、この無効化プロセスは、デバイス・ドライバ910が、キュー・データ構造920〜930に対応するホスト・システム・メモリ950を滞留解除するためにデバイス・ドライバ・サービス940を呼び出すこと、これらのキュー・データ構造920〜930に関するDMAアドレスを解放すること、これらのDMAアドレスに関するATPT項目を消去すること、およびATC項目無効化要求をPCIeエンドポイント990に発行することを必要とする可能性がある。ATC項目無効化動作がPCIeエンドポイント990によって完了されると、デバイス・ドライバ・サービス940はデバイス・ドライバ910に制御を返し、この時点でPCIeエンドポイント990をシステムから切り離すことができる。

【0103】

図10は、例示的な一実施形態によりホスト・システムとPCIeエンドポイントとの間の通信に関するキュー・データ構造を初期設定するための模範的な動作の概要を示す流れ図である。キュー・データ構造のアドレスを無効化するための動作は本質的に上記の図7に概要を示した動作と同じであるので、この説明ではキュー・データ構造に関する初期設定動作についてのみ、流れ図で具体的に例示することにする。

【0104】

図10に図示されている通り、動作は、ホスト・システム上のシステム・イメージの初期設定の一部として、ホスト・システムによって行われるPCIeエンドポイント用のデバイス・ドライバの初期設定から始まる(ステップ1010)。ホスト・システムはロジカル・パーティション内のデバイス・ドライバを呼び出し、次にそのデバイス・ドライバが入出力仮想化仲介内のデバイス・ドライバ・サービスを呼び出す(ステップ1020)。デバイス・ドライバ・サービスはキュー・データ構造(複数も可)用のホスト・システム・メモリを滞留させる(ステップ1030)。

【0105】

デバイス・ドライバ・サービスは未変換DMAアドレス、すなわち、未変換PCIeメモリ・アドレスをキュー・データ構造(複数も可)に割り当てる(ステップ1040)。デバイス・ドライバ・サービスは、未変換DMAアドレスに関するATPT項目をプログラミングし、適切であれば、キャッシュ使用可能ビットをATPT項目内に設定する(ステップ1050)。次に、デバイス・ドライバ・サービスは未変換DMAアドレス、すなわち、キュー・データ構造に関する未変換PCIeメモリ・アドレスをデバイス・ドライバに返す(ステップ1060)。

【0106】

次に、デバイス・ドライバはキュー・データ構造に関する未変換DMAアドレスをPCIeエンドポイントに提供する(ステップ1070)。PCIeエンドポイントはATSアドレス変換要求をルート複合体に発行する(ステップ1080)。ルート複合体は、ATPTを使用して未変換DMAアドレスのアドレス変換を実行し、変換済みアドレスをPCIeエンドポイントに返す(ステップ1090)。PCIeエンドポイントはキュー・データ構造に関するキュー・コンテキストに変換済みアドレスを保管し(ステップ1095)、動作は終了する。その後、PCIeエンドポイントは、キュー・データ構造との間のDMA要求に対してキュー・コンテキスト内の変換済みアドレスを使用することができる。

【0107】

したがって、例示的な諸実施形態は、システム・イメージと、システム・イメージなどで実行されるアプリケーションと、PCIeエンドポイント、たとえば、入出力アダプタとの間で通信するための1つまたは複数のキューを作成するためのメカニズムを提供する。例示的な諸実施形態のメカニズムは、未変換アドレス空間、たとえば、PCIeバス・アドレス空間から、変換済みアドレス空間、たとえば、システム・バス・アドレス空間に、1つまたは複数のキューに関連するアドレスを変換するためにルート複合体におけるATPT項目の初期設定および使用を可能にする。その上、例示的な諸実施形態は、ルート複合体において形式的変換(formal translation)を行う必要なしに、これらの変換に一致する未変換アドレスを使用する要求を1つまたは複数のキューに直接転送できるように、アドレス変換キャッシュの一部としてPCIeエンドポイントに変換を保管するためのメカニズムを提供する。

【0108】

上述の通り、例示的な諸実施形態のメカニズムは、デバイス・ドライバ内のキュー・データ構造と、それに対応するデータ処理システムのルート複合体内のATPT項目とを確立するために使用することができる。このようなキュー・データ構造が上述のメカニズムにより初期設定されると、これらのキュー・データ構造およびATPT項目を使用して、ホスト・システムのロジカル・パーティションのアプリケーション・インスタンス、システム・イメージなどとPCIeエンドポイントとの間の通信を実行することができる。

【0109】

これらのキュー・データ構造および対応するATPT項目は、種々のタイプのPCIeエンドポイントとともに使用することができる。たとえば、PCIeエンドポイントは、1つまたは複数のデータ・ネットワークにより他のデバイスと通信するためのイーサネット(登録商標)・アダプタ、ファイバ・チャネル・アダプタ、InfiniBand(R)アダプタなどのネットワーキング・アダプタにすることができる。このようなネットワーキング・アダプタにより、送受信中のデータは、ホスト・システムのデバイス・ドライバ内のバッファ内に置かれ、データが受信中であるか送信中であるかに応じて、ホスト・システムのシステム・イメージまたはネットワーク・アダプタのいずれかによって取り出される。データ・バッファ・アドレスを事前変換することにより、入出力動作を開始する際に必要となる待ち時間は、変換動作の待ち時間を各動作の開始から任意の動作開始前に移動することによって短縮され、したがって、エンドポイントのDMA動作の全体的なパフォーマンスが改善される。

【0110】

次に、ネットワーキング・アダプタに関連する例示的な諸実施形態の構造を使用するデータの受信および送信のためのプロセスについて、図11および図12に関連して以下に説明する。図11は、「コマンド・キュー項目」またはCQEというキュー項目を使用してPCIeエンドポイントからホスト・システムのバッファにデータを受信するための動作を例示する模範的な図である。最初に、デバイス・ドライバ1110は、イーサネット(登録商標)・アダプタ、ファイバ・チャネル・アダプタ、InfiniBand(R)アダプタなどのネットワーキング・アダプタにすることができるPCIeエンドポイント1190に要求を送信するために、1つまたは複数のキュー・データ構造、たとえば、コマンド・キュー・データ構造1120を初期設定するためにデバイス・ドライバ・サービス1140を呼び出す。前に述べた通り、この初期設定は、キュー・データ構造用のホスト・システム・メモリを滞留させること、DMAアドレスを割り当てること、ATPT項目をプログラミングすること、ATPT項目がキャッシュ可能であることを示すビットを設定すること、ならびに未変換PCIeメモリ・アドレスをデバイス・ドライバ1110に返すことを含むことができる。

【0111】

キュー・データ構造を初期設定した後、デバイス・ドライバは、着信データ・パケットからのデータを保管するためにPCIeエンドポイントが使用するバッファ1124を指すポインタ、すなわち、アドレスを含むCQE1122を作成する。バッファに関するアドレスは未変換PCIeアドレスである。

【0112】

次に、デバイス・ドライバ1110は、PCIeエンドポイント1190内のドアベル記憶装置1192、たとえば、レジスタにドアベル値を書き込む。ドアベル値は、CQE1122が使用可能であることをPCIeエンドポイント1190に対して示すものである。PCIeエンドポイント1190は、ドアベル記憶装置1192内にドアベル値を設定したことに応答して、コマンド・キュー・データ構造1120からCQE1122、したがって、バッファ・アドレスを取り出す。

【0113】

バッファ1124に関する未変換PCIeアドレスを取り出すと、PCIeエンドポイント1190は、バッファ1124に関する未変換PCIeアドレスのアドレス変換のための要求をルート複合体1150に発行する。ルート複合体1150は、ATPT1160を使用して未変換PCIeアドレスを変換済みシステム・メモリ・アドレスに変換し、変換済みシステム・メモリ・アドレスをPCIeエンドポイント1190に返す。PCIeエンドポイント1190は、PCIeエンドポイント1190内のCQE1194のローカル・コピーに変換済みシステム・メモリ・アドレスを保管する。

【0114】

変換ならびにCQE1194のローカル・コピーへの変化済みアドレス、すなわち、システム・メモリまたは実メモリ・アドレスの保管は、CQE1194に関する外部ネットワーク接続装置(図示せず)からデータ・パケットを受信する前に実行できることを認識されたい。したがって、データ・パケット(複数も可)が外部ネットワーク接続装置によって送信され、PCIeエンドポイント1190で受信されるまで、変換済みPCIeアドレスはCQE1194のローカル・コピーに保管することができる。

【0115】

結果のデータ・パケットがPCIeエンドポイント1190で受信されると、PCIeエンドポイント1190は、ローカルに保管されキャッシュされた変換済みアドレス、すなわち、CQE1194のローカル・コピーに保管されたバッファ1124の未変換PCIeアドレスに対応するシステム・メモリ・アドレスを使用して、データをバッファ1124に入れるためのDMA動作要求を発行する。DMA動作要求で使用されるアドレスが変換済みシステム・メモリ・アドレスであることを示すためのビットがDMA動作要求のヘッダに設定されたDMA動作要求が実行される。その結果、ルート複合体1150は、データがバッファ1124に直接書き込まれるように、ATPT1160を使用するアドレス変換なしに、DMA動作要求を通過させる。

【0116】

バッファ1124に書き込むべきデータのすべてがこのようにバッファ1124にDMAされると、PCIeエンドポイント1190は、同様に応答キュー・データ構造1130に応答キュー項目(RQE)1132をDMAすることができる。デバイス・ドライバ1110がRQE1132を受信し処理すると、デバイス・ドライバ1110は、データ・バッファ1124用のホスト・メモリを滞留解除するためにデバイス・ドライバ・サービス1140を呼び出す。デバイス・ドライバ・サービス1140は、データ・バッファ1124に関するDMAアドレスを解放し、データ・バッファ1124に関するATPT項目を消去する。ルート複合体1150は、CQE1194のローカル・コピー内のアドレス情報を消去するために、ATC項目無効化要求をPCIeエンドポイント1190に発行する。PCIeエンドポイント1190は、デバイス・ドライバ・サービス1140に完了を通知するATC項目無効化完了応答をルート複合体1150に返す。次に、デバイス・ドライバ・サービス1140はデバイス・ドライバ1110に制御を返し、次のCQEを作成する必要が発生するまで動作は完了する。また、複数の動作(たとえば、複数のCQE)に1つのデータ・バッファを再利用するすることも可能であり、その場合、データ・バッファがもはや他の動作に必要ではなくなるまで、デバイス・ドライバ・サービス1140は(たとえば、データ・バッファ・アドレスを無効化し、メモリを滞留解除するために)呼び出されることはないであろう。

【0117】

図12は、CQEを使用してPCIeエンドポイントを介してデータを送信するための動作を例示する模範的な図である。PCIeエンドポイント1290を介してホスト・システム内のシステム・イメージからデータが送信される場合、デバイス・ドライバ1210は、バッファ1224用のホスト・メモリを滞留させるためにデバイス・ドライバ・サービス1240を呼び出し、バッファ1224に関するDMAアドレスを割り当て、バッファ1224に関するATPT1260内のATPT項目をプログラミングし、これらの項目内のアドレス変換がキャッシュ可能であることを示すビットをATPT項目内に設定する。デバイス・ドライバ・サービス1240は、バッファ1224に関する未変換PCIeアドレスをデバイス・ドライバ1210に返す。

【0118】

デバイス・ドライバは、PCIeエンドポイント1290がそのポートのうちの1つまたは複数を介してそこからデータを送信する予定のバッファ1224を指すポインタ、すなわち、アドレスを含むCQE1222を作成する。バッファ1224に関するアドレスは未変換PCIeアドレスである。

【0119】

次に、デバイス・ドライバ1210は、PCIeエンドポイント1290内のドアベル記憶装置1292、たとえば、レジスタにドアベル値を書き込む。ドアベル値は、CQE1222が使用可能であることをPCIeエンドポイント1290に対して示すものである。PCIeエンドポイント1290は、ドアベル記憶装置1292内にドアベル値を設定したことに応答して、コマンド・キュー・データ構造1220からCQE1222、したがって、バッファ・アドレスを取り出す。

【0120】

PCIeエンドポイント1290内のデータ・バッファが一杯である場合、たとえば、ダウンストリーム・ポートが飽和している場合、PCIeエンドポイント1290はATS変換要求をルート複合体1250に発行する。PCIeエンドポイント1290がこのATS変換要求の結果として変換済みアドレスを受信すると、それはCQE1294のローカル・コピーに変換済みアドレスを保管する。PCIeエンドポイント1290がデータ・バッファ1224からの送信データをDMAし(たとえば、ポートがデータを送信するために使用可能になった場合)、データを送信した後、PCIeエンドポイント1290は、送信動作が完了したことを示すために応答キュー1230にRQE1232をDMAし、要求された場合、割り込みを生成することもできる。

【0121】

デバイス・ドライバ1210がRQE1232を検索すると、デバイス・ドライバ1210は、バッファ1224用のホスト・メモリを滞留解除するためにデバイス・ドライバ・サービス1240を呼び出し、DMAアドレスを解放し、バッファ1224の未変換アドレスに関するATPT項目を消去する。次に、ルート複合体1250はATC項目無効化要求をPCIeエンドポイント1290に発行し、PCIeエンドポイント1290からの完了メッセージを待つ。PCIeエンドポイント1290によってATC項目無効化動作が実行されると、デバイス・ドライバ・サービス1240はデバイス・ドライバ1210に制御を返す。また、複数の動作(たとえば、複数のCQE)に1つのデータ・バッファを再利用することも可能であり、その場合、データ・バッファがもはや他の動作に必要ではなくなるまで、デバイス・ドライバ・サービス1240は(たとえば、データ・バッファ・アドレスを無効化し、メモリを滞留解除するために)呼び出されることはないであろう。

【0122】

図13〜図14は、例示的な一実施形態によりネットワーク・アダプタの受信動作に関する模範的な動作の概要を示す流れ図を描写している。図13〜図14に図示されている通り、動作は、デバイス・ドライバが1つまたは複数のデータ・バッファ構造を初期設定するためにデバイス・ドライバ・サービスを呼び出すことから始まる(ステップ1310)。より具体的には、デバイス・ドライバは、バッファ(複数も可)に関連するホスト・メモリを滞留させ、バッファ・アドレスに関するATPTをセットアップするためにデバイス・ドライバ・サービスを呼び出す。データ・バッファ構造(複数も可)を初期設定した後、デバイス・ドライバは、着信データ・パケットからのデータを保管するためにPCIeエンドポイントが使用するバッファを指すポインタ、すなわち、未変換PCIeメモリ・アドレスを含むキュー項目を作成する(ステップ1315)。次に、デバイス・ドライバは、PCIeエンドポイント内のドアベル記憶装置にドアベル値を書き込む(ステップ1320)。

【0123】

PCIeエンドポイントは、ドアベル記憶装置内にドアベル値を設定したことに応答して、キュー・データ構造からキュー項目、したがって、未変換PCIeバッファ・メモリ・アドレスを取り出す(ステップ1325)。バッファに関する未変換PCIeメモリ・アドレスを取り出すと、PCIeエンドポイントは、バッファに関する未変換PCIeアドレスのアドレス変換のための要求をルート複合体に発行する(ステップ1330)。ルート複合体は、ATPTを使用して未変換PCIeアドレスを変換済みシステム・メモリ・アドレスに変換し、変換済みシステム・メモリ・アドレスをPCIeエンドポイントに返す(ステップ1335)。PCIeエンドポイントは、PCIeエンドポイント内のキュー項目のローカル・コピーに変換済みシステム・メモリ・アドレスを保管する(ステップ1340)。

【0124】

PCIeエンドポイントは、データ・パケットが受信されたかどうかを判断する(ステップ1345)。受信されていない場合、動作は、ステップ1345に戻ることにより、データ・パケットが受信されるのを待つ。データ・パケットがPCIeエンドポイントで受信された場合、PCIeエンドポイントは、DMA動作要求のヘッダに変換ビットが設定されたDMA動作要求を発行し、ローカルに保管されキャッシュされたシステム・メモリ・アドレスを使用して、データをホスト・システムのバッファに入れる(ステップ1350)。ルート複合体は、データがバッファに直接書き込まれるように、ATPTを使用するアドレス変換なしに、DMA動作要求を通過させる(ステップ1355)。バッファに書き込むべきデータのすべてがバッファにDMAされたかどうかに関する判断が行われる(ステップ1360)。DMAされていない場合、動作はステップ1345に戻る。

【0125】

バッファに書き込むべきデータのすべてがバッファにDMAされると、PCIeエンドポイントは応答キュー項目を応答キュー・データ構造にDMAする(ステップ1365)。RQEを受信したことに応答して、デバイス・ドライバは、データ・バッファ構造用のホスト・メモリを滞留解除するためにデバイス・ドライバ・サービスを呼び出す(ステップ1370)。デバイス・ドライバ・サービスは、キュー・データ構造に関するDMAアドレス、すなわち、未変換PCIeメモリ・アドレスを解放し(ステップ1375)、キュー・データ構造に関するATPT項目を消去する(ステップ1380)。ルート複合体は、キュー項目のローカル・コピー内のアドレス情報を消去するために、PCIeエンドポイントにATC項目無効化要求を発行する(ステップ1385)。次に、PCIeエンドポイントは、キュー項目のローカル・コピー内のアドレス情報を無効化し、デバイス・ドライバ・サービスに完了を通知するATC項目無効化完了応答をルート複合体に発行する(ステップ1390)。次に、デバイス・ドライバ・サービスは、データ・バッファに関連するホスト・メモリを滞留解除する(ステップ1392)。次に、デバイス・ドライバ・サービスはデバイス・ドライバに制御を返し(ステップ1395)、動作は終了する。

【0126】

図15〜図16は、例示的な一実施形態によりネットワーク・アダプタの送信動作に関する模範的な動作の概要を示す流れ図を描写している。図15〜図16に図示されている通り、動作は、デバイス・ドライバがデバイス・ドライバ・サービスを呼び出すことから始まり(ステップ1410)、次にそのデバイス・ドライバ・サービスがバッファ用のホスト・メモリを滞留させ、バッファに関するDMAアドレスを割り当て、バッファに関するATPT内のATPT項目をプログラミングし、これらの項目内のアドレス変換がキャッシュ可能であることを示すビットをATPT項目内に設定する(ステップ1415)。次に、デバイス・ドライバ・サービスは、バッファに関する1つまたは複数の未変換PCIeメモリ・アドレス(複数も可)、すなわち、DMAアドレスをデバイス・ドライバに返す(ステップ1420)。

【0127】

デバイス・ドライバは、PCIeエンドポイントがそのポートのうちの1つまたは複数を介してそこからデータを送信する予定のバッファを指すポインタ、すなわち、未変換PCIeメモリ・アドレスを含むキュー項目を作成する(ステップ1425)。次に、デバイス・ドライバは、PCIeエンドポイント内のドアベル記憶装置にドアベル値を書き込む(ステップ1430)。PCIeエンドポイントは、ドアベル記憶装置内にドアベル値を設定したことに応答して、キュー・データ構造からキュー項目、したがって、バッファの未変換PCIeメモリ・アドレスを取り出す(ステップ1435)。

【0128】

PCIeエンドポイント内のデータ・バッファが一杯であるかどうかに関する判断が行われる(ステップ1440)。データ・バッファが一杯ではない場合、データはDMAを介して転送され、送信のためにPCIeエンドポイントのデータ・バッファ内に置かれ(ステップ1460)、PCIeエンドポイントはそれに応じてデータを送信する(ステップ1465)。

【0129】

データ・バッファが一杯である場合、PCIeエンドポイントはルート複合体にATS変換要求を発行する(ステップ1445)。PCIeエンドポイントがこのATS変換要求の結果として変換済みアドレスを受信すると(ステップ1450)、PCIeエンドポイントはキュー項目のローカル・コピーに変換済みアドレスを保管する(ステップ1455)。エンドポイントは使用可能なバッファを待ち(ステップ1457)、データはDMAを介して転送され、送信のためにPCIeエンドポイントのデータ・バッファ内に置かれ(ステップ1460)、PCIeエンドポイントはそれに応じてデータを送信する(ステップ1465)。

【0130】

次に、PCIeエンドポイントは、送信動作が完了したことを示すために応答キュー項目(RQE)を応答キューにDMAし、要求された場合、割り込みを生成することもできる(ステップ1470)。

【0131】

デバイス・ドライバがRQEを検索すると、デバイス・ドライバは、バッファ用のホスト・メモリを滞留解除し、DMAアドレスを解放し、バッファの未変換アドレスに関するATPT項目を消去するためにデバイス・ドライバ・サービスを呼び出す(ステップ1475)。次に、ルート複合体は、PCIeエンドポイントにATC項目無効化要求を発行し(ステップ1480)、PCIeエンドポイントからの完了メッセージを待つ(ステップ1485)。ATC項目無効化動作がPCIeエンドポイントによって実行されると、デバイス・ドライバ・サービスは、データ・バッファに関連するホスト・メモリを滞留解除し(ステップ1490)、次に、デバイス・ドライバに制御を返し(ステップ1495)、動作は終了する。

【0132】

したがって、例示的な諸実施形態は、ホスト・システム内のデバイス・ドライバのバッファ内にネットワーク・アダプタPCIeエンドポイントを介してデータの受信または送信あるいはその両方を行うためにコマンド・キューおよびコマンド・キュー項目を生成するためのメカニズムを提供する。バッファに関するATPT項目は、ルート複合体内でアドレス変換を実行する必要なしにバッファに直接アクセスする際に使用するためにPCIeエンドポイント内でキャッシュ可能なバッファに対応するアドレスに関する変換により確立することができる。

【0133】

ネットワーキング・アダプタとの使用に加えて、例示的な諸実施形態のメカニズムはさらに、ローカルに使用可能なデバイスと通信するために他のタイプのPCIeエンドポイントとともに使用することができる。たとえば、PCIeエンドポイントは、PCIeエンドポイントに直接接続された記憶装置と通信するための小型コンポーネント・システム・インターフェース(SCSI)アダプタにすることができる。例示的な諸実施形態のメカニズムは、SCSI読み取り/書き込みに関するアドレス情報をSCSIアダプタ内にキャッシュするためのメカニズムを提供することにより、SCSIアダプタのDMA読み取り待ち時間を短縮するために使用することができる。

【0134】

図17は、例示的な一実施形態によりSCSI読み取り動作を例示する模範的な図である。図17に図示されている通り、デバイス・ドライバ1510が、システム・イメージまたはシステム・イメージで実行されるアプリケーションなどから記憶トランザクション要求を受信すると、デバイス・ドライバ1510は、デバイス・ドライバ・バッファ1524用のホスト・メモリを滞留させるためにデバイス・ドライバ・サービス1540を呼び出し、デバイス・ドライバ・バッファ1524にDMAアドレスを割り当て、ATPT項目をプログラミングし、これらのATPT項目がキャッシュ可能であることを示すビットを使用可能にし、バッファ1524用のデバイス・ドライバ1510に未変換PCIeアドレスを返す。

【0135】

デバイス・ドライバ1510は、コマンド・キュー・データ構造1520内にコマンド・キュー項目(CQE)1522を作成する。CQE1522は、SCSIコマンドと、そのコマンドに関連するバッファ、たとえば、バッファ1524を指すポインタ、すなわち、未変換アドレスを含む。次に、デバイス・ドライバ1510は、着信要求が存在することをPCIeエンドポイント1590に示すドアベル値をドアベル記憶装置1592に書き込む。

【0136】

ドアベル記憶装置1592内にドアベル値が設定されたことに応答して、この場合もSCSIアダプタにすることができるPCIeエンドポイントは、コマンド・キュー・データ構造1520からCQE1522を取り出し、どのタイプのコマンドが要求されているかを判断する。この判断は、たとえば、CQE1522のヘッダに提供されている値に基づいて行うことができる。CQE1522が、ディスクから読み取るための読み取りコマンドであるSCSIコマンドを含む場合、PCIeエンドポイント1590は、ディスク読み取り動作を発行し、続いて、ホスト・システム上のルート複合体1550がCQE1522内のポインタ、すなわち、未変換アドレスについてアドレス変換を実行することを要求するATSアドレス変換要求を発行する。PCIeエンドポイント1590がアドレス変換の結果を受信すると、その結果はPCIeエンドポイント1590内のCQE1594のローカル・コピーに保管される。したがって、CQE1522内のポインタのアドレス変換は、読み取り動作が実行されるのとほぼ同時に実行することができる。PCIeエンドポイント1590に結合されたSCSI装置にアクセスするために未変換アドレスが使用されるので、読み取り動作の一部としていかなる変換も行う必要はない。

【0137】

SCSI装置がPCIeエンドポイント1590にデータを返すと、PCIeエンドポイント1590は、CQE1594内のローカルに保管されキャッシュされた変換済みアドレス、すなわち、バッファ1524に関するシステム・バス・アドレスを使用して、データをホスト・システムに返すためのDMA動作を発行する。DMAで使用されるアドレスが変換済みアドレスであることを示すヘッダ・ビットが設定されたDMAが実行される。その結果、ATPT1560を使用してルート複合体1550によっていかなる変換も実行されず、DMAをバッファ1524に通過させる。

【0138】

PCIeエンドポイント1590は、ディスクからの読み取り動作が完了したことを示すために、応答キュー・データ構造1530に応答キュー項目(RQE)1532をDMAする。要求された場合、PCIeエンドポイント1590は、割り込みを生成することもできる。

【0139】

デバイス・ドライバ1510がディスクからの読み取り動作のRQE1532を検索すると、デバイス・ドライバ1510は、データ・バッファ1524用のホスト・メモリを滞留解除するためにデバイス・ドライバ・サービス1540を呼び出す。デバイス・ドライバ・サービス1540はさらに、データ・バッファ1524に関するDMAアドレスを解放し、データ・バッファ1524に関するATPT項目を消去する。ルート複合体1550はPCIeエンドポイント1590にATC項目無効化要求を発行し、それにより、PCIeエンドポイント1590は、消去されたATPT項目に対応するATC項目、すなわち、CQE1594のローカル・コピーを無効化する。ATC無効化動作が完了すると、デバイス・ドライバ・サービス1540はデバイス・ドライバ1510に制御を返す。

【0140】

図18〜図19は、例示的な一実施形態によりSCSI装置からデータを読み取るための模範的な動作の概要を示す流れ図を例示している。図18に図示されている通り、動作は、デバイス・ドライバが記憶トランザクション要求を受信することから始まる(ステップ1602)。デバイス・ドライバは、ドライバ・サービス・バッファ用のホスト・メモリを滞留させるためにデバイス・ドライバ・サービスを呼び出し(ステップ1604)、デバイス・ドライバ・バッファにDMAアドレスを割り当て(ステップ1606)、ATPT項目をプログラミングし、これらのATPT項目がキャッシュ可能であることを示すビットを使用可能にし(ステップ1608)、バッファに関する未変換PCIeメモリ・アドレス、すなわち、DMAアドレスをデバイス・ドライバに返す(ステップ1610)。

【0141】

デバイス・ドライバはコマンド・キュー・データ構造内にコマンド・キュー項目(CQE)を作成し(ステップ1612)、CQEは、SCSIコマンドと、そのコマンドに関連するバッファを指すポインタを含む。次に、デバイス・ドライバはドアベル値をドアベル記憶装置に書き込む(ステップ1614)。ドアベル記憶装置内にドアベル値が設定されたことに応答して、PCIeエンドポイントは、コマンド・キュー・データ構造からCQEを取り出し(ステップ1616)、CQE内のコマンドが読み取りコマンドであるかどうかを判断する(ステップ1620)。

【0142】

CQEが、ディスクから読み取るための読み取りコマンドであるSCSIコマンドを含む場合、PCIeエンドポイントは、ディスク読み取り動作を発行し、続いて、ホスト・システム上のルート複合体1550がCQE内のポインタについてアドレス変換を実行することを要求するATSアドレス変換要求を発行する(ステップ1622)。PCIeエンドポイントがアドレス変換の結果を受信すると、その結果はPCIeエンドポイント内のCQEのローカル・コピーに保管される(ステップ1624)。

【0143】

SCSI装置がPCIeエンドポイントにデータを返すと、PCIeエンドポイントは、CQE内のローカルに保管されキャッシュされた変換済みアドレスを使用して、データをホスト・システムに返すためのDMA動作を発行する(ステップ1626)。DMAで使用されるアドレスが変換済みアドレスであることを示すヘッダ・ビットが設定されたDMAが実行される(ステップ1628)。その結果、ATPTを使用してルート複合体によっていかなる変換も実行されず、DMAをバッファに通過させる。

【0144】

PCIeエンドポイントは、ディスクからの読み取り動作が完了したことを示すために、応答キュー・データ構造に応答キュー項目(RQE)をDMAする(ステップ1630)。要求された場合、PCIeエンドポイントは、割り込みを生成することもできる。

【0145】

デバイス・ドライバがディスクからの読み取り動作のRQEを検索すると、デバイス・ドライバは、メモリを滞留解除し、DMAアドレスを解放し、データ・バッファに関するATPT項目を消去するためにデバイス・ドライバ・サービスを呼び出す(ステップ1632)。デバイス・ドライバ・サービスはさらに、コマンド・キューに関するDMAアドレスを解放し、コマンド・キューに関するATPT項目を消去する(ステップ1634)。ルート複合体はPCIeエンドポイントにATC項目無効化要求を発行し、それにより、PCIeエンドポイントは、消去されたATPT項目に対応するATC項目を無効化する(ステップ1636)。ATC無効化動作が完了すると、デバイス・ドライバ・サービスはバッファ用のホスト・メモリを滞留解除し(ステップ1638)、デバイス・ドライバ・サービスはデバイス・ドライバに制御を返す(ステップ1640)。

【0146】

ステップ1620に戻ると、図19に図示されている通り、そのコマンドが読み取りコマンドではない場合、すなわち、そのコマンドがSCSI書き込みコマンドである場合、エンドポイントは、CQE内の情報に基づいてSCSI装置にディスク・シーク動作を発行し、続いて、CQE内のポインタについてルート複合体に送信されるアドレス変換要求を発行する(ステップ1650)。変換要求を受信するために要する時間は一般に、シーク動作を実行するために物理的SCSI装置が要する時間より短くなり、したがって、動作全体の待ち時間からアドレス変換時間を隠すことになる。

【0147】

エンドポイントがルート複合体から変換済みアドレス(複数も可)を受信すると、エンドポイントは、CQEのローカル・コピーにこれらの変換済みアドレス(複数も可)を保管する(ステップ1652)。次に、エンドポイントは、変換済みアドレスがDMA要求で使用されることを示すようにDMAヘッダを設定し、CQEのローカル・コピー内のローカルにキャッシュされた変換済みアドレス(複数も可)を使用してシステム・メモリ内のデータ・バッファから書き込むべきデータを取得するためにDMA動作を実行する(ステップ1654)。次に、エンドポイントは、前のディスク・シーク動作が完了したことをSCSI装置が示すのを待つ(ステップ1656)。ディスク・シーク動作が完了したことを示すSCSI装置からのメッセージに応答して、エンドポイントは、前にDMAしたデータをSCSI装置に転送する(ステップ1658)。次に、動作は上述のステップ1630に戻る。

【0148】

したがって、例示的な諸実施形態は、デバイス・ドライバおよびデバイス・ドライバ・サービスに対してこの通信の役割を分散するように、ネットワーク・アダプタ、SCSIアダプタ、InfiniBand(R)アダプタなどを含む種々のタイプのPCIeエンドポイントとの通信のためのメカニズムを提供する。例示的な諸実施形態は、使用されるPCIeエンドポイントのタイプに応じて異なる方法でこれらの様々なタイプのPCIeエンドポイントにおける変換済みアドレスのキャッシュの使用を容易にする。これらの変換済みアドレスのキャッシュにより、ホスト・システムのルート複合体においてアドレス変換動作を行う必要なしに、PCIeエンドポイントはホスト・システムのキュー、バッファ、およびシステム・メモリに直接アクセスすることができる。

【0149】

例示的な諸実施形態は、完全にハードウェアの実施形態、完全にソフトウェアの実施形態、またはハードウェアとソフトウェアの両方の要素を含む実施形態の形を取ることができることを認識されたい。模範的な一実施形態では、例示的な諸実施形態のメカニズムは、ファームウェア、常駐ソフトウェア、マイクロコードなどを含むがこれらに限定されないソフトウェアで実現される。

【0150】

さらに、例示的な諸実施形態は、コンピュータまたは任意の命令実行システムにより使用するためのまたはそれに関連するプログラム・コードを提供するコンピュータで使用可能な媒体またはコンピュータ可読媒体からアクセス可能なコンピュータ・プログラムの形を取ることができる。この説明のため、コンピュータで使用可能な媒体またはコンピュータ可読媒体は、命令実行システム、装置、またはデバイスにより使用するためのまたはそれらに関連するプログラムを収容、保管、伝達、伝搬、または転送することができる任意の装置にすることができる。

【0151】

この媒体は、電子、磁気、光、電磁、赤外線、または半導体システム(あるいは装置またはデバイス)もしくは伝搬媒体にすることができる。コンピュータ可読媒体の例としては、半導体またはソリッド・ステート・メモリ、磁気テープ、取り外し可能コンピュータ・ディスケット、ランダム・アクセス・メモリ(RAM)、読み取り専用メモリ(ROM)、剛性磁気ディスク、および光ディスクを含む。光ディスクの現在の例としては、コンパクト・ディスク読み取り専用メモリ(CD−ROM)、コンパクト・ディスク読み取り/書き込み(CD−R/W)、およびDVDを含む。

【0152】

プログラム・コードの保管または実行あるいはその両方に適したデータ処理システムは、システム・バスによりメモリ・エレメントに直接または間接的に結合された少なくとも1つのプロセッサを含むことになる。メモリ・エレメントとしては、プログラム・コードの実際の実行中に使用されるローカル・メモリ、大容量記憶装置、ならびに、実行中に大容量記憶装置からコードを検索しなければならない回数を削減するために少なくとも何らかのプログラム・コードの一時記憶を可能にするキャッシュ・メモリを含むことができる。

【0153】

入出力またはI/O装置(キーボード、ディスプレイ、ポインティング・デバイスなどを含むがこれらに限定されない)は、直接または介在する入出力コントローラを介して、システムに結合することができる。また、データ処理システムが介在する私設網または公衆網を介して他のデータ処理システムまたはリモート・プリンタあるいは記憶装置に結合された状態になるように、ネットワーク・アダプタもシステムに結合することができる。モデム、ケーブル・モデム、およびイーサネット(登録商標)・カードは、現在使用可能なタイプのネットワーク・アダプタのうちのいくつかに過ぎない。

【0154】

本発明の説明は、例示および記述のために提示されたものであり、網羅するためあるいは開示された形の本発明に限定するためのものではない。多くの変更例および変形例は当業者にとって自明なものになるであろう。実施形態は、実際の適用例である本発明の原理を最もよく説明し、他の当業者が企図された特定の用途に適した様々な変更例を含む様々な実施形態について本発明を理解できるようにするために、選択され記載されたものである。

【図面の簡単な説明】

【0155】

【図1】ATPTおよびPCIエクスプレス(PCIe)通信プロトコルを使用してDMA動作を実行するための従来のメカニズムを例示する模範的な図である。

【図2】例示的な諸実施形態の模範的な諸態様を実現可能な分散データ処理環境を例示する模範的な図である。

【図3】例示的な諸実施形態の模範的な諸態様を実現可能なデータ処理装置を例示する模範的な図である。

【図4】デバイス・ドライバおよびデバイス・ドライバ・サービスに関する例示的な一実施形態の動作を例示する模範的な図である。

【図5】例示的な一実施形態によりDMA動作による変換済みおよび未変換PCIeアドレスの処理を例示する模範的な図である。

【図6】例示的な一実施形態によりDMAアドレスに関するATPT項目を初期設定するための模範的な動作の概要を示す流れ図である。

【図7】例示的な一実施形態によりDMAアドレスに関するATPT項目およびATC項目を無効化するための模範的な動作の概要を示す流れ図である。

【図8】例示的な一実施形態によりDMA動作において変換済みおよび未変換PCIeアドレスを処理するための模範的な動作の概要を示す流れ図である。

【図9】PCIeエンドポイント・キューに関するアドレス変換をキャッシュするための例示的な諸実施形態の実現例を例示する図である。

【図10】例示的な一実施形態によりホスト・システムとPCIeエンドポイントとの間の通信に関するキュー・データ構造を初期設定するための模範的な動作の概要を示す流れ図である。

【図11】「コマンド・キュー項目」またはCQEというキュー項目を使用してPCIeエンドポイントからホスト・システムのバッファにデータを受信するための動作を例示する模範的な図である。

【図12】CQEを使用してPCIeエンドポイントを介してデータを送信するための動作を例示する模範的な図である。

【図13】例示的な一実施形態によりネットワーク・アダプタの受信動作に関する模範的な動作の概要を示す流れ図である。

【図14】例示的な一実施形態によりネットワーク・アダプタの受信動作に関する模範的な動作の概要を示す流れ図である。

【図15】例示的な一実施形態によりネットワーク・アダプタの送信動作に関する模範的な動作の概要を示す流れ図である。

【図16】例示的な一実施形態によりネットワーク・アダプタの送信動作に関する模範的な動作の概要を示す流れ図である。

【図17】例示的な一実施形態によりSCSI読み取り動作を例示する模範的な図である。

【図18】例示的な一実施形態によりSCSI装置からデータを読み取るための模範的な動作の概要を示す流れ図である。

【図19】例示的な一実施形態によりSCSI装置からデータを読み取るための模範的な動作の概要を示す流れ図である。

【符号の説明】

【0156】

410:ロジカル・パーティション

420:システム・イメージ

422:応答キュー

424:応答キュー項目(RQE)

426:ドアベル記憶装置

430:ユーザ・アプリケーション/ライブラリ

440:ファイル・システム

450:デバイス・ドライバ

460:入出力(I/O)仮想化仲介(VI)

470:デバイス・ドライバ・サービス

480:PCIeルート複合体

482:アドレス変換および保護テーブル(ATPT)

485:PCIファブリック

490:PCIeエンドポイント

492:仮想機能

494:アドレス変換キャッシュ(ATC)

496:ドアベル記憶装置

498:PCIeエンドポイントのローカル・コマンド・キュー

499:コマンド・キュー項目(CQE)

【技術分野】

【0001】

本出願は、一般に、改良されたデータ処理システムおよび方法に関する。より具体的には、本出願は、キャッシュされたアドレス変換を使用して、1つまたは複数のローカルに接続された入出力装置と通信するように構成された入出力(I/O)アダプタまたはエンドポイントと通信するための装置および方法を対象とする。

【背景技術】

【0002】

システムによっては、現在の周辺装置相互接続(PCI:Peripheral Component Interconnect)プロトコルにより、直接メモリ・アクセス(DMA:direct memory access)を実行するときに、アドレス変換および保護テーブル(ATPT:address translation and protection table)を使用してアドレス変換およびアクセス検査が実行される。ATPTは、数十年間、使用されてきたが、より下位のシステムにとっては新しいものであり、直接メモリ・アクセス(DMA)リマッピング・リソースまたは入出力メモリ管理ユニット(IOMMU:Input/Output Memory Management Unit)などのいくつかの他の名前で知られている。ATPTは、DMAトランザクションで使用されるPCIバス・アドレスを、実メモリ・リソースにアクセスするために使用される実メモリ・アドレスに変換するための項目を保管する。ATPT内の項目は、どのデバイスが対応するメモリの一部分にアクセス可能であるかと、このようなデバイスがこれらのメモリの一部分で実行可能な特定の動作とを識別する保護情報を保管する。

【0003】

最近、PCI−SIG(www.pcisig.com/home)は、ATPTに常駐するアドレス変換をPCIファミリ・アダプタにキャッシュできるようにするメカニズムを標準化している最中であった。これらのメカニズムはアドレス変換サービス(ATS:Address Translation Services)として知られている。ATSにより、PCIファミリ・アダプタは、未変換PCIバス・アドレスに関する変換を要求することができ、ATSをサポートするシステム上でこのような要求が正常に完了すると、変換済み、すなわち、実メモリ・アドレスがPCIファミリ・アダプタに返される。次に、ATSにより、PCIファミリ・アダプタは、DMA動作で使用されるPCIバス・アドレスに変換済みとしてマークを付けることができる。ATSをサポートするシステムは、その後、変換済みアドレスを使用してATPTをバイパスすることになる。また、ATSは、ホスト側(たとえば、ハードウェアまたは仮想化仲介(virtualization intermediary))が前に公示されたアドレス変換を無効化するためのメカニズムも提供する。

【0004】

図1は、ATPTおよびPCIエクスプレス(PCIe:PCI express)通信プロトコルを使用してDMA動作を実行するための従来のメカニズムを例示する模範的な図である。描写された例は、PCIeエンドポイント、たとえば、アドレス変換動作を実行するためにATSを使用するPCIe入出力(I/O)アダプタによって呼び出される、上述のPCIeアドレス変換サービス(ATS)も示している。後述する通り、ATS機能は、PCIeエンドポイントおよびホスト・システムのルート複合体(root complex)内に構築される。PCIe ATSに関する追加情報については、www.pcisig.comの周辺装置相互接続分科会(PCI−SiG:peripheral component interconnect special interest group)Webサイトから入手可能なPCIe ATS規格を参照する。

【0005】

図1に図示されている通り、ホストCPUおよびメモリ110は、システム・バス115を介して、アドレス変換および保護テーブル(ATPT)130を含むPCIeルート複合体120に結合されている。次に、PCIeルート複合体120は、PCIeリンク135を介して、1つまたは複数のPCIeエンドポイント140(「エンドポイント」という用語は、PCIe対応入出力アダプタについて言及するためにPCIe規格で使用されるものである)に結合される。ルート複合体120は、CPU/メモリをPCIeエンドポイント140に接続する入出力階層のルートを意味する。ルート複合体120は、ホスト・ブリッジと、ゼロまたは1つ以上のルート複合体統合エンドポイントと、ゼロまたは1つ以上のルート複合体イベント・コレクタと、1つまたは複数のルート・ポートとを含む。各ルート・ポートは個別の入出力階層をサポートする。入出力階層は、ルート複合体120と、ゼロまたは1つ以上の相互接続スイッチまたはブリッジあるいはその両方(スイッチまたはPCIファブリックを含むもの)と、エンドポイント140などの1つまたは複数のエンドポイントから構成することができる。たとえば、PCIeスイッチは、ルート複合体120に接続されたエンドポイント140などのPCIeエンドポイントの数を増加するために使用することができる。PCIおよびPCIeに関する追加情報については、www.pcisig.comのPCI−SiG Webサイトから入手可能なPCIおよびPCIe規格を参照する。

【0006】

PCIeエンドポイントは、内部ルーティング回路142と、構成管理ロジック144と、1つまたは複数の物理機能(PF:physical function)146と、ゼロまたは1つ以上の仮想機能(VF:virtual function)148〜152とを含み、それぞれのVFは1つのPFに関連づけられている。ATSにより、各仮想機能は、すでに変換されており、DMA動作を実行するときにホストATPT130をバイパスするために仮想機能によって使用できるPCIメモリ・アドレスをキャッシュするためにアドレス変換キャッシュ(ATC:address translation cache)160〜164を使用することができる。

【0007】

実施時に、PCIeエンドポイント140は、PCIe ATSトランザクションを呼び出しを呼び出して、所与のPCIバス・アドレスからシステム・バス・アドレスへの変換を要求し、その後のトランザクション、たとえば、DMA動作がすでに変換されており、ATPTをバイパスできることを示すことができる。ルート複合体120は、PCIeエンドポイント140に提供された変換がもはやPCIeエンドポイント140の物理または仮想あるいはその両方の機能(複数も可)によって使用されないように、その変換を無効化するためにPCIe ATSトランザクションを呼び出すことができる。

【0008】

たとえば、DMA動作を実行する予定である場合、DMA動作のアドレスは、DMA動作を処理する特定の仮想機能148〜152のATC160〜164でルックアップすることができる。アドレス変換がATC160〜164内に存在しない場合、PCIeエンドポイント140によってルート複合体120に対する変換要求を行うことができる。次に、ルート複合体120は、ATPT130を使用してアドレス変換を実行し、PCIeエンドポイント140に変換済みアドレスを返すことができる。次に、PCIeエンドポイント140は、DMA動作を処理する物理または仮想あるいはその両方の機能に対応する適切なATC160〜164内にその変換を保管することができる。DMA動作は、変換済みアドレスを使用してシステム・バス115上に渡すことができる。

【0009】

このアドレスに関する変換がすでにATC160〜164内に存在する場合、変換済みアドレスがDMA動作で使用される。そのアドレスがすでに変換されていることと、このDMAについてルート複合体120内のATPT130をバイパスできることを示すために、DMAヘッダ内にビットを設定することができる。その結果、PCIeリンク135およびシステム・バス115を介してPCIeエンドポイント140とホストCPUおよびメモリ110との間でDMA動作が直接実行される。PCIeエンドポイントの仮想機能の特定のBDF番号が、DMA動作によって要求されたようにアドレスにアクセスすることが許可されているBDFに対応することを保証するために、アクセス検査は依然としてルート複合体120によって実行することができる。

【0010】

その後の何らかの時点で、変換がATPT130内で変化した場合など、PCIeエンドポイント140に提供された変換がもはやPCIeエンドポイント140によって使用されない場合、ルート複合体120はPCIeエンドポイント140にATS無効化要求を発行しなければならない。PCIeエンドポイント140は、無効アドレスに向けられたすべての保留要求を直ちにフラッシュするわけではない。むしろ、PCIeエンドポイント140は、リタイヤすべき無効変換済みアドレスを参照するすべての未解決の読み取り要求を待ち、無効になるようにATC160〜164内の項目にマークを付けるためのビットを設定することなどにより、ATC160〜164内の変換を解放する。PCIeエンドポイント140は、ATC160〜164内の変換の無効化の完了を示すATS無効化完了メッセージをルート複合体120に返す。PCIeエンドポイント140は、無効化されたアドレスを使用する任意の前にポストされた書き込みのあとで、無効化完了表示がルート複合体120に到着することを保証する。

【0011】

典型的には、ATPT130は、システム・メモリ内のツリー構造変換テーブルとして設けることができる。コンピューティング・システムの各PCIバス/デバイス/機能(BDF:Bus/Device/Function)ごとに異なるツリー構造を設けることができる。これらのATPTデータ構造を使用して、複数のデバイスは1つのデバイス・アドレス空間を共用することができ、複数のデバイスは専用アドレス空間を有することができる。したがって、すべてのデバイスがシステム・メモリのすべてのアドレス空間上ですべてのDMA動作を実行できるわけではない。

【0012】

ATPT130のアクセスは、DMAトランザクションの一部として同期的に実行される。これは、DMAトランザクションの未変換PCIバス・メモリ・アドレスをホストのメモリにアクセスするために使用される変換済み実メモリ・アドレスに変換するため、ならびに、DMAトランザクションをサブミットするデバイスが変換済み実メモリ・ドレスにアクセスするための十分な許可を有し、変換済み実メモリ・アドレス上で所望のDMA動作を実行するための十分な許可を有することを保証するためにATPTをチェックするための時間のかかる変換メカニズムを使用することを必要とする。

【0013】

ATPT130のアクセスの一部として、特定のBDFに対応する正しいATPTツリー・データ構造を識別しなければならず、変換およびアクセス検査を実行するためにツリー・データ構造をウォーク(走査)しなければならない。ATPTツリー・データ構造の位置特定は、BDFに関連するツリー・データ構造のアドレスを見つけるために、1回または2回のアクセスを必要とする可能性がある。見つかった場合、ツリーをウォークするためにツリー・データ構造への3回または4回のアクセスを要する可能性がある。したがって、この変換およびアクセス検査には、DMA動作に関連する大規模待ち時間に対する責任がある。このような待ち時間は、低い通信待ち時間を必要とするエンドポイントに関する重大な問題を引き起こす可能性がある。

【0014】

このような待ち時間を緩和する方法として、PCIeエンドポイント140で実現されるATSは、これらの変換をもう一度実行する必要がないように、すでに実行されたアドレス変換を保管するためにATC160〜164を使用する。したがって、ATPTとATCとの組み合わせにより、PCI ATSは、DMA動作に関連する待ち時間を短縮するようにアドレス変換およびアクセス検査を実行する。PCI SiGはPCIe ATSに関する規格を規定しているが、PCI SiGでは、ATSを使用してアドレス変換を実行し、ATPTおよびATCなどのATS構造を管理する役割をPCIe ATSを実現するシステム内でどのように配分すべきかを指定していない。

【特許文献1】米国特許第6629162号

【発明の開示】

【発明が解決しようとする課題】

【0015】

例示的な諸実施形態は、キャッシュされたアドレス変換を使用して、1つまたは複数のローカルに接続された入出力装置と通信するように構成された入出力(I/O)アダプタまたはエンドポイントと通信するための装置および方法を提供する。この装置および方法により、アドレス変換情報のキャッシュ管理に関する役割は、デバイス・ドライバとデバイス・ドライバ・サービスとの間で分散される。デバイス・ドライバは信頼できないミッション・ロジカル・パーティション(LPAR:logical partition)内に設けることができ、デバイス・ドライバ・サービスは仮想化仲介オペレーティング・システム、ハイパーバイザ、サービス・パーティションなどの信頼できる仮想化仲介内に設けることができる。

【0016】

デバイス・ドライバは、LPAR内のアプリケーションとPCIeエンドポイントとの間ならびにその逆において要求を通信するためのキューを管理する役割を担う。デバイス・ドライバはさらに、デバイス・ドライバ・サービスを介してメモリ管理を呼び出す役割を担う。デバイス・ドライバ・サービスは、アドレス変換および保護テーブル(ATPT)ならびにPCIeエンドポイントのアドレス変換キャッシュ(ATC)を含む、PCIeエンドポイントによってアクセス可能なメモリを管理する役割を担う。

【0017】

PCIeエンドポイントと通信する役割をデバイス・ドライバとデバイス・ドライバ・サービスとの間で分割することにより、OS内で実行されるデバイス・ドライバは、他のOSのメモリに関連する変換をPCIeエンドポイントに提供することができない。その結果、システム仮想化に関連する信頼モデルが維持される。すなわち、アドレス変換キャッシュ管理の役割をデバイス・ドライバ・サービス内に置くことにより、あるOSは、そのエンドポイントが他のOSのメモリに対してDMA動作を実行することを要求できなくなる。

【課題を解決するための手段】

【0018】

例示的な一実施形態では、ホスト・システムの信頼できないミッション・ロジカル・パーティション(LPAR)システム・イメージ内のデバイス・ドライバの初期設定中に、PCIeエンドポイント用のデバイス・ドライバは、アドレス変換および保護テーブル(ATPT)項目を初期設定し、コマンド、応答、およびイベント・キューなど、システム・メモリ内に常駐し、直接メモリ・アクセス(DMA)動作によりPCIeエンドポイントによってアクセス可能なアダプタ・リソース用のデバイス・ドライバにPCIメモリ・アドレスを返すためにデバイス・ドライバ・サービス(以下、単純に「ドライバ・サービス」という)を呼び出す。デバイス・ドライバとPCIeエンドポイントは、コマンド、応答、およびイベント・キューにより通信する。本書では、これらのキューを「デバイス・ドライバのキュー」ということにする。

【0019】

本質的に、デバイス・ドライバ・サービスは、デバイス・ドライバのキュー(複数も可)用のホスト・メモリを滞留(pin)させ、デバイス・ドライバのキュー(複数も可)に関するDMAアドレスを割り当て、これらのDMAアドレスに関するATPT項目をプログラミングし、ATPT項目がキャッシュ可能であること、すなわち、PCIeエンドポイント上で、キュー・コンテキスト、たとえば、アドレス変換キャッシュ内にキャッシュ可能であることを示すビットを使用可能にする。次に、デバイス・ドライバ・サービスは、未変換PCIeメモリ・アドレス(複数も可)、すなわち、DMAアドレス(複数も可)、たとえば、キュー内の特定の項目を識別するためにオフセットともに使用可能なデバイス・ドライバのキュー(複数も可)に関する開始アドレスをATPT項目用のデバイス・ドライバに返す。未変換PCIeメモリ・アドレスは、システムのメモリ空間内にないアドレスであり、システム・メモリにアクセスするために使用するには、その前に変換しなければならないものである。

【0020】

例示的な諸実施形態のメカニズムを使用すると、この未変換PCIeメモリ・アドレスをPCIeエンドポイントに提供し、ルート複合体に変換要求を送信するためにPCIeエンドポイントが使用することができる。すなわち、PCIeエンドポイントは、未変換PCIeメモリ・アドレスに関連する1つまたは複数の変換済みPCIeメモリ・アドレスを返すようルート複合体に要求することができる。次に、PCIeエンドポイントは、1つまたは複数の変換済みPCIeメモリ・アドレスをデバイス・ドライバのキュー(複数も可)に関連するコンテキスト、たとえば、PCIeエンドポイント内の1つまたは複数の仮想機能に関連する1つまたは複数のアドレス変換キャッシュに保管することができる。

【0021】

未変換PCIeメモリ・アドレスの変換をアダプタのデバイス・ドライバ・キュー・コンテキストに保管することにより、PCIeエンドポイントは、デバイス・ドライバ・キュー項目をターゲットにするDMAの際にルート複合体のATPTをバイパスすることができる。したがって、ルート複合体が変換済みとしてマークが付けられたPCIe DMAトランザクションを受信すると、ルート複合体は、そのエンドポイントについて変換キャッシュが使用可能になっていることを検証し、ホストの実メモリに直接アクセスするために変換済みPCIeメモリ・アドレスを使用する。

【0022】

PCIeエンドポイントがシステムから切り離された後、デバイス・ドライバに関連する機能(物理または仮想)がシステムから切り離された後など、その後の何らかの時点で、未変換PCIeメモリ・アドレスに対応するATPT項目およびATC項目を無効化する必要がある可能性がある。このような無効化を実行するために、デバイス・ドライバあるいはハイパーバイザ管理コンポーネントなどの何らかの上位エンティティは、ホスト・メモリを滞留解除し、DMAアドレス、すなわち、未変換PCIeメモリ・アドレスを解放するためにデバイス・ドライバ・サービスを呼び出す。次に、デバイス・ドライバ・サービスは、未変換PCIeメモリ・アドレスに対応するATPT項目を消去し、ルート複合体はATC項目無効化要求をPCIeエンドポイントに発行する。次に、PCIeエンドポイントは、未変換PCIeメモリ・アドレスに対応する任意のATC項目を無効化するための動作を実行し、未変換PCIeメモリ・アドレスがもはや使用されなくなった後に、ATC無効化完了応答をデバイス・サービス(device service)に返す。次に、デバイス・サービスはデバイス・ドライバに制御を返す。代替実現例では、デバイス・ドライバ・サービスは、ATC項目無効化要求をPCIeエンドポイントに発行することができ、PCIeエンドポイントがATC項目無効化を完了した後に、デバイス・ドライバ・サービスはATPT項目を消去し、デバイス・ドライバに制御を返すことができる。

【0023】

前述の通り、例示的な諸実施形態のメカニズムは、システム・イメージと、システム・イメージなどで実行されるアプリケーションと、1つまたは複数のキュー・データ構造を使用するPCIeエンドポイントとの間で通信する際に使用するためのATPT項目を確立するために使用することができる。例示的な諸実施形態のこのような実現例では、1つまたは複数のキュー・データ構造に関するATPT項目は、前に上述したように初期設定される。PCIeエンドポイントの初期設定フェーズ中に、PCIeエンドポイントは、デバイス・ドライバが初期設定されていることを検証する。これは、たとえば、PCIeエンドポイントのPCI構成空間、重要プロダクト・データ(VPD:Vital Product Data)フィールド、またはメモリ・マップ入出力(MMIO:memory mapped input/output)フィールドから情報を読み取ることにより、実行することができる。

【0024】

デバイス・ドライバは、1つまたは複数のキューの開始および終了アドレス、開始アドレスおよび長さなどをPCIeエンドポイントに提供することができる。たとえば、デバイス・ドライバは、キュー構成空間に対応するPCIeエンドポイントのPCI構成空間フィールド、VPDまたはMMIOフィールドにこれらのアドレスを書き込むことができる。これらのアドレスは未変換PCIeアドレスである。PCIeエンドポイントは、キュー・アドレスの変換に関するPCIe ATS要求を呼び出すことができる。その結果、ルート複合体は、ATPTを使用してアドレス変換を実行し、1つまたは複数のキューから項目を検索する際に使用するためにキュー・コンテキストに変換済みアドレスをキャッシュすることができるPCIeエンドポイントに結果を返し、項目を1つまたは複数のキュー内に入れることができる。

【0025】

例示的な一実施形態では、デバイス・ドライバは、PCIeエンドポイントと通信するためのキュー・データ構造を生成する。キュー・データ構造は、たとえば、コマンド・キューと応答キューを含むことができる。キュー・データ構造は、たとえば、PCIeエンドポイントに結合された小型コンポーネント・システム・インターフェース(SCSI:small component system interface)入出力装置と通信するためのSCSIキューにすることができる。これらのキュー・データ構造は、リンク・リスト・キュー、サーキュラ・バッファ・キューなどを含む任意の方式で構成することができる。

【0026】

これらのキュー・データ構造を生成する際にデバイス・ドライバによって実行される動作の一部として、デバイス・ドライバは、キュー・データ構造に関するATPT項目をプログラミングし、キューに関する未変換PCIeアドレス、すなわち、DMAアドレスをデバイス・ドライバに返すためにデバイス・ドライバ・サービスを呼び出す。ATPT項目のプログラミングは、キュー・データ構造に使用されるホスト・メモリ空間を滞留させること、未変換PCIeアドレスからシステム・メモリ・アドレスに変換するための変換情報によりルート複合体のATPT内のATPT項目をプログラミングすること、ならびにATPT項目に対応するアドレス変換がPCIeエンドポイントのATC内にキャッシュ可能であることを示すキャッシュ使用可能ビットをATPT項目内に設定することを必要とする可能性がある。このような動作を実行した後、1つまたは複数のATPT項目に関する未変換PCIeアドレス(複数も可)がデバイス・ドライバに返される。これらの未変換PCIeアドレス(複数も可)は、たとえば、キュー・データ構造の開始および終了アドレスを識別することができる。

【0027】

未変換PCIeアドレス(複数も可)は、PCIeエンドポイント内のキュー構成空間にアドレスを書き込むことなどにより、デバイス・ドライバによってPCIeエンドポイントに提供される。キュー構成空間は、たとえば、PCI構成空間、1つまたは複数のVPDフィールド、1つまたは複数のMMIOフィールドなどにすることができる。キュー・データ構造に関するこれらの未変換PCIeアドレス(複数も可)を受信したことに応答して、PCIeエンドポイントは、キュー・アドレスに関するPCIe ATS要求をルート複合体に発行することができる。その結果、ルート複合体は、キュー・データ構造の未変換PCIeアドレスに関するアドレス変換およびアクセス検査を実行し、変換済みアドレスをPCIeエンドポイントに返すことができる。次に、PCIeエンドポイントは、PCIeエンドポイントのATCによって提供されたキュー・コンテキスト内にこれらのアドレス変換を保管することができる。

【0028】

上記の結果として、PCIeエンドポイントはその時点でキュー・データ構造に関連するアドレスに関する変換にアクセスできるので、PCIeエンドポイントは、ルート複合体のATPTアドレス変換を行う必要なしに、キュー・データ構造にキュー項目をサブミットするかまたはキュー・データ構造からキュー項目を検索するためにDMA動作を実行することができる。

【0029】

キュー・データ構造がもはやPCIeエンドポイントによって使用されない場合、これらのキュー・データ構造に関するアドレスに対応するATPTおよびATC項目は、前に上述した方式で無効化することができる。このような無効化は、たとえば、PCIeエンドポイントがシステムから切り離される場合、デバイス・ドライバに関連する機能(物理または仮想)がホスト・システムから切り離された後などに実行することができる。この無効化プロセスは、デバイス・ドライバが、キュー・データ構造に対応するホスト・システム・メモリを滞留解除するためにデバイス・ドライバ・サービスを呼び出すこと、これらのキュー・データ構造に関するDMAアドレスを解放すること、これらのDMAアドレスに関するATPT項目を消去すること、およびATC項目無効化要求をPCIeエンドポイントに発行することを必要とする可能性がある。ATC項目無効化動作がPCIeエンドポイントによって完了されると、デバイス・ドライバ・サービスはデバイス・ドライバに制御を返し、この時点でPCIeエンドポイントをシステムから切り離すことができる。

【0030】

上述の通り、例示的な諸実施形態のメカニズムは、デバイス・ドライバ内のキュー・データ構造と、それに対応するデータ処理システムのルート複合体内のATPT項目を確立するために使用することができる。このようなキュー・データ構造が上述のメカニズムにより初期設定されると、これらのキュー・データ構造およびATPT項目を使用して、ホスト・システムのロジカル・パーティションのアプリケーション・インスタンス、システム・イメージなどとPCIeエンドポイントとの間の通信を実行することができる。

【0031】

これらのキュー・データ構造および対応するATPT項目は、種々のタイプのPCIeエンドポイントとともに使用することができる。たとえば、PCIeエンドポイントは、1つまたは複数のデータ・ネットワークにより他のデバイスと通信するためのイーサネット(登録商標)・アダプタ、ファイバ・チャネル・アダプタ、InfiniBand(R)アダプタなどのネットワーキング・アダプタにすることができる。このようなネットワーキング・アダプタにより、送受信中のデータは、ホスト・システムのデバイス・ドライバに関連するバッファ内に置かれ、データが受信中であるか送信中であるかに応じて、ホスト・システムのシステム・イメージまたはPCIeアダプタのいずれかによって取り出される。例示的な諸実施形態のメカニズムは、データの送信/受信時にルート複合体によるアドレス変換を受ける必要なしに、これらの変換済みアドレスおよびDMA動作を使用して送信バッファまたは受信バッファあるいはその両方にデータを直接送信できるように、キュー・データ構造の確立およびキューに対応する変換済みアドレスのキャッシュを可能にする。このため、このメカニズムは、ネットワーク・アダプタによるデータ送信および受信に関連する待ち時間を短縮する。

【0032】

ネットワーキング・アダプタとの使用に加えて、例示的な諸実施形態のメカニズムはさらに、ローカルに使用可能なデバイスと通信するために他のタイプのPCIeエンドポイントとともに使用することができる。たとえば、PCIeエンドポイントは、PCIeエンドポイントに直接接続された記憶装置と通信するための小型コンポーネント・システム・インターフェース(SCSI)アダプタにすることができる。例示的な諸実施形態のメカニズムは、SCSI読み取り/書き込みに関するアドレス情報をSCSIアダプタ内にキャッシュするためのメカニズムを提供することにより、SCSIアダプタのDMA読み取り待ち時間を短縮するために使用することができる。

【0033】

例示的な一実施形態では、システム・イメージとローカルに接続された外部記憶装置との間の動作を実行するための方法が提供される。この方法は、システム・イメージから記憶トランザクション要求を受信するステップと、コマンド・キュー・データ構造内のコマンド・キュー・エレメント(CQE)を作成するステップであって、そのCQEが、バッファ・データ構造の未変換アドレスを指定し、データ転送動作コマンドを含むステップを含むことができる。この方法はさらに、ローカルに接続された外部記憶装置と通信するための入出力(I/O)アダプタにより、コマンド・キュー・データ構造からCQEを検索するステップと、入出力アダプタに結合されたローカルに接続された外部記憶装置にデータ転送動作コマンドを送信するステップとを含むことができる。その上、この方法は、ローカルに接続された外部記憶装置にデータ転送動作コマンドを送信するのとほぼ同時に、入出力アダプタにより、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスについて、データ処理システムのルート複合体に要求を発行するステップを含むことができる。さらに、この方法は、入出力アダプタにより、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスを入出力アダプタのローカル・アドレス変換キャッシュに保管するステップを含むことができる。データ転送動作は、ローカルに接続された外部記憶装置への書き込みまたはローカルに接続された外部記憶装置からの読み取りのうちの一方にすることができる。

【0034】

この方法はさらに、入出力アダプタにより、ローカル・アドレス変換キャッシュに保管された1つまたは複数の変換済みアドレスを使用して、入出力アダプタとバッファ・データ構造との間の直接メモリ・アクセス(DMA)トランザクションを実行し、ローカルに接続された外部記憶装置から読み取られたデータをバッファ・データ構造に入れるステップを含むことができる。DMAトランザクションには、DMAトランザクションによって使用されるアドレスが変換済みアドレスであることを示す変換ビットが設定される可能性がある。ルート複合体は、変換ビットが設定されていることを検出したことに応答して、アドレス変換動作を実行せずに、DMA動作をバッファ・データ構造に直接渡すことができる。

【0035】

この方法はさらに、データ転送動作コマンドに関連するアドレス変換を入出力アダプタ内のCQEのローカル・コピーに保管するステップを含むことができる。この方法は、CQEを作成したことに応答して、そのCQEが入出力アダプタによる処理のために使用可能であることを示す値を入出力アダプタに関連するドアベル記憶装置に書き込むステップを含むことができる。入出力アダプタは、ドアベル記憶装置に値を書き込んだことに応答して、コマンド・キュー・データ構造からCQEを検索することができる。

【0036】

この方法は、データ処理システムのデバイス・ドライバにより、コマンド・キュー・データ構造に関するルート複合体に関連するアドレス変換データ構造内の1つまたは複数のアドレス変換項目を初期設定するためにデバイス・ドライバ・サービスを呼び出すステップを含むことができる。その上、この方法は、コマンド・キュー・データ構造に関連する1つまたは複数の未変換アドレスを入出力アダプタに提供するステップを含むことができる。1つまたは複数のアドレス変換項目は、コマンド・キュー・データ構造に関連する1つまたは複数の未変換アドレスから1つまたは複数の変換済みアドレスへの変換を指定することができる。入出力アダプタは、小型コンポーネント・システム・インターフェース(SCSI)アダプタ、シリアル接続SCSI(SAS)アダプタ、シリアル先端技術接続(SATA)、または先端技術接続(ATA)アダプタのうちの1つにすることができる。

【0037】

この方法はさらに、CQEのヘッダに提供された値を読み取るステップと、CQEのヘッダに提供された値に基づいて、CQEが読み取りデータ転送動作コマンドを含むかどうかを判断するステップとを含むことができる。1つまたは複数の変換済みアドレスについてルート複合体に要求を発行するステップと、1つまたは複数の変換済みアドレスを保管するステップは、CQEが読み取りデータ転送動作コマンドを含むという判断に応答して、実行することができる。

【0038】

また、この方法は、CQEのデータ転送動作コマンドの完了に応答して、入出力アダプタからシステム・イメージに関連する応答キュー・データ構造に応答キュー項目(RQE)を送信するステップも含むことができる。その上、この方法は、デバイス・ドライバにより、応答キュー・データ構造からRQEを検索するステップと、バッファ・データ構造に関連するホスト・メモリを滞留解除し、バッファ・データ構造に関連する1つまたは複数の未変換アドレスを解放し、バッファ・データ構造に対応するアドレス変換データ構造内のアドレス変換項目を消去するために、デバイス・ドライバにより、デバイス・ドライバ・サービスを呼び出すステップとを含むことができる。

【0039】

他の例示的な諸実施形態では、コンピュータ可読プログラムを有するコンピュータで使用可能な媒体(computer useable medium)を含むコンピュータ・プログラム(computer program product)が提供される。このコンピュータ可読プログラムは、コンピューティング・デバイス上で実行されると、方法の例示的な実施形態に関して上記で概要を示した動作のうちの様々なものおよびそれらの組み合わせをコンピューティング・デバイスに実行させるものである。

【0040】

さらに他の例示的な実施形態では、装置が提供される。この装置は、プロセッサと、プロセッサに結合された入出力アダプタであって、ローカルに接続された外部記憶装置と通信するために構成された入出力アダプタとを含むことができる。このプロセッサは、システム・イメージから記憶トランザクション要求を受信し、コマンド・キュー・データ構造内のコマンド・キュー・エレメント(CQE)を作成することができ、そのCQEは、バッファ・データ構造の未変換アドレスを指定し、データ転送動作コマンドを含む。入出力アダプタは、コマンド・キュー・データ構造からCQEを検索し、入出力アダプタに結合されたローカルに接続された外部記憶装置にデータ転送動作コマンドを送信し、ローカルに接続された外部記憶装置にデータ転送動作コマンドを送信するのとほぼ同時に、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスについて、データ処理システムのルート複合体に要求を発行することができる。その上、入出力アダプタは、バッファ・データ構造の1つまたは複数の未変換アドレスに対応する1つまたは複数の変換済みアドレスを入出力アダプタのローカル・アドレス変換キャッシュに保管することができる。

【0041】

本発明の上記その他の特徴および利点は、本発明の模範的な諸実施形態に関する以下の詳細な説明に記載されるか、またはその詳細な説明を考慮すると当業者にとって自明なものになるであろう。

【0042】

本発明ならびにその好ましい使用態様、その他の目的および利点は、添付図面に併せて読んだときに、例示的な諸実施形態に関する以下の詳細な説明を参照することにより最もよく理解されるであろう。

【発明を実施するための最良の形態】

【0043】

例示的な諸実施形態は、エンドポイントとホスト・システムとの間のより効率的な直接メモリ・アクセス(DMA)動作を容易にするためにデバイス・ドライバおよびデバイス・ドライバ・サービスに対してエンドポイント・アドレス変換管理の役割を分散するためのメカニズムを提供する。このため、例示的な諸実施形態は、以下に記載する通り、デバイス・ドライバおよびデバイス・ドライバ・サービスを使用してDMA動作を実行できる任意のコンピューティング・デバイスで実現することができる。このようなコンピューティング・デバイスは、多くの形を取ることができ、様々な構成を有することができる。以下の図2〜図3では、例示的な諸実施形態の模範的な諸態様を実現可能なデータ処理環境およびデータ処理装置の例を示す。図2〜図3は模範的なものに過ぎず、例示的な諸実施形態のメカニズムを使用可能なデータ処理環境および装置のタイプに関して制限するものではないことを認識されたい。

【0044】

次に、添付図面、特に図2〜図3に関して説明すると、本発明の諸実施形態を実現可能なデータ処理環境の模範的な図が示されている。図2〜図3は例示的なものに過ぎず、本発明の諸態様または諸実施形態を実現可能な環境に関していかなる制限も主張または暗示するものではないことを認識されたい。本発明の精神および範囲を逸脱せずに、記述されている環境に対して多くの変更を行うことができる。

【0045】

次に、添付図面に関して説明すると、図2は、例示的な諸実施形態の諸態様を実現可能な模範的な分散データ処理システムの図表現を描写している。分散データ処理システム200は、例示的な諸実施形態の諸実施形態を実現可能なコンピュータのネットワークを含むことができる。分散データ処理システム200は少なくとも1つのネットワーク202を含み、このネットワークは分散データ処理システム200内にまとめて接続された様々な装置およびコンピュータ間の通信リンクを提供するために使用される媒体である。ネットワーク202は、ワイヤ、ワイヤレス通信リンク、または光ファイバ・ケーブルなどの接続を含むことができる。

【0046】

描写された例では、サーバ204およびサーバ206は、記憶装置208とともにネットワーク202に接続されている。加えて、クライアント210、212、および214もネットワーク202に接続されている。これらのクライアント210、212、および214は、たとえば、パーソナル・コンピュータ、ネットワーク・コンピュータなどにすることができる。描写された例では、サーバ204は、ブート・ファイル、オペレーティング・システム・イメージ、およびアプリケーションなどのデータをクライアント210、212、および214に提供する。クライアント210、212、および214は、描写された例ではサーバ204に対するクライアントである。分散データ処理システム200は、図示されていない追加のサーバ、クライアント、およびその他の装置を含むことができる。

【0047】

描写された例では、分散データ処理システム200は、相互に通信するために伝送制御プロトコル/インターネット・プロトコル(TCP/IP:Transmission Control Protocol/Internet Protocol)スイートのプロトコルを使用するネットワークおよびゲートウェイの世界的集合を表すネットワーク202を有するインターネットである。インターネットの中心には、データおよびメッセージをルーティングする、数千の商用、行政用、教育用、およびその他のコンピュータ・システムから構成される、メジャー・ノードまたはホスト・コンピュータ間の高速データ通信回線のバックボーンがある。当然のことながら、分散データ処理システム200は、たとえば、イントラネット、ローカル・エリア・ネットワーク(LAN)、広域ネットワーク(WAN)などのいくつかの異なるタイプのネットワークを含むように実現することもできる。上記の通り、図2は、本発明の種々の実施形態に関するアーキテクチャ上の制限としてではなく、一例として意図されており、したがって、図2に図示されている特定の諸要素は、本発明の例示的な諸実施形態を実現可能な環境に関して制限するものと見なすべきではない。

【0048】

次に、図3に関して説明すると、例示的な諸実施形態の諸態様を実現可能な模範的なデータ処理システムのブロック図が図示されている。データ処理システム300は、図2のホスト210などのコンピュータの一例であり、本発明の例示的な諸実施形態に関するプロセスを実現するコンピュータで使用可能なコードまたは命令をそこに配置することができる。

【0049】

描写された例では、データ処理システム300は、ノース・ブリッジおよびメモリ・コントローラ・ハブ(NB/MCH:north bridge and memory controller hub)302とサウス・ブリッジおよび入出力(I/O)コントローラ・ハブ(SB/ICH:south bridge and input/output controller hub)304とを含むハブ・アーキテクチャを使用している。NB/MCH302には、処理装置306、メイン・メモリ308、およびグラフィックス・プロセッサ310が接続されている。グラフィックス・プロセッサ310は、アクセラレィティッド・グラフィックス・ポート(AGP:accelerated graphics port)を介してNB/MCH302に接続することもできる。

【0050】

描写された例では、SB/ICH304にはローカル・エリア・ネットワーク(LAN)アダプタ312が接続している。オーディオ・アダプタ316、キーボードおよびマウス・アダプタ320、モデム322、読み取り専用メモリ(ROM)324、ハード・ディスク(HDD)326、CD−ROMドライブ330、ユニバーサル・シリアル・バス(USB)ポートおよびその他の通信ポート332、PCI/PCIeデバイス334は、バス338およびバス340を介してSB/ICH304に接続している。PCI/PCIeデバイスとしては、たとえば、イーサネット(登録商標)・アダプタ、アドイン・カード、およびノートブック・コンピュータ用のPCカードを含むことができる。PCIではカード・バス・コントローラを使用し、PCIeでは使用しない。ROM324は、たとえば、フラッシュ・バイナリ入出力システム(BIOS)にすることができる。

【0051】

HDD326およびCD−ROMドライブ330は、バス340を介してSB/ICH304に接続している。HDD326およびCD−ROMドライブ330は、たとえば、統合ドライブ・エレクトロニクス(IDE:integrated drive electronics)またはシリアル先端技術接続(SATA:serial advanced technology attachment)インターフェースを使用することができる。スーパー入出力(SIO:super I/O)デバイス336はSB/ICH304に接続することができる。

【0052】

オペレーティング・システムは処理装置306上で実行される。オペレーティング・システムは、図3のデータ処理システム300内の様々なコンポーネントの制御を調整し提供する。クライアントとしてのオペレーティング・システムは、Microsoft(R)のWindows(登録商標)XPなどの市販のオペレーティング・システムにすることができる(MicrosoftおよびWindowsは、米国、その他の国、あるいはその両方におけるマイクロソフト社の商標である)。Java(登録商標)プログラミング・システムなどのオブジェクト指向プログラミング・システムは、オペレーティング・システムに併せて実行することができ、データ処理システム300上で実行中のJava(登録商標)プログラムまたはアプリケーションからオペレーティング・システムへの呼び出しを提供する(Javaは、米国、その他の国、あるいはその両方におけるサン・マイクロシステムズ社の商標である)。

【0053】

サーバとしてのデータ処理システム300は、たとえば、拡張対話式エグゼクティブ(AIX(R):Advanced Interactive Executive)オペレーティング・システムまたはLINUX(R)オペレーティング・システムを実行するIBM(R)のeServer(R)pSeries(R)コンピュータ・システムにすることができる(eServer、pSeries、およびAIXは、米国、その他の国、あるいはその両方におけるインターナショナル・ビジネス・マシーンズ社の商標であり、LINUXは、米国、その他の国、あるいはその両方におけるLinus Torvaldsの商標である)。データ処理システム300は、処理装置306内に複数のプロセッサを含む対称型マルチプロセッサ(SMP:symmetric multiprocessor)システムにすることができる。代わって、シングル・プロセッサ・システムを使用することもできる。

【0054】

オペレーティング・システム、オブジェクト指向プログラミング・システム、およびアプリケーションまたはプログラムに関する命令は、HDD326などの記憶装置上に配置され、処理装置306によって実行するためにメイン・メモリ308にロードすることができる。本発明の例示的な諸実施形態に関するプロセスは、たとえば、メイン・メモリ308、ROM324などのメモリ内に、または、たとえば、1つまたは複数の周辺装置326および330内に配置することができる、コンピュータで使用可能なプログラム・コードを使用して処理装置306によって実行することができる。

【0055】

図3に図示されているバス338またはバス340などのバス・システムは、1つまたは複数のバスで構成することができる。当然のことながら、バス・システムは、そのファブリックまたはアーキテクチャに接続された種々のコンポーネントまたはデバイス間のデータ転送を可能にする任意のタイプの通信ファブリックまたはアーキテクチャを使用して実現することができる。図3のモデム322またはネットワーク・アダプタ312などの通信装置は、データを送受信するために使用される1つまたは複数の装置を含むことができる。メモリは、たとえば、メイン・メモリ308、ROM324、または図3のNB/MCH302内に見られるようなキャッシュにすることができる。

【0056】

当業者であれば、図2〜図3のハードウェアは実現例に応じて様々になる可能性があることが分かるであろう。図2〜図3に描写されているハードウェアに加えてまたはその代わりに、フラッシュ・メモリ、同等の不揮発性メモリ、または光ディスク・ドライブなどのその他の内部ハードウェアまたは周辺装置を使用することができる。また、例示的な諸実施形態のプロセスは、本発明の精神および範囲を逸脱せずに、前に述べたSMPシステム以外のマルチプロセッサ・データ処理システムに適用することもできる。

【0057】

その上、データ処理システム300は、クライアント・コンピューティング・デバイス、サーバ・コンピューティング・デバイス、タブレット・コンピュータ、ラップトップ・コンピュータ、電話またはその他の通信装置、携帯情報端末(PDA)などを含む、いくつかの異なるデータ処理システムのうちのいずれかの形を取ることができる。いくつかの例示的な例では、データ処理システム300は、たとえば、オペレーティング・システム・ファイルまたはユーザ生成データあるいはその両方を保管するための不揮発性メモリを提供するためにフラッシュ・メモリとともに構成されたポータブル・コンピューティング・デバイスにすることができる。本質的に、データ処理システム300は、アーキテクチャ上の制限なしに、任意の既知のデータ処理システムまたはその後開発されたデータ処理システムにすることができる。

【0058】

前述の通り、例示的な諸実施形態は、デバイス・ドライバとデバイス・ドライバ・サービスとの間でエンドポイント・アドレス変換キャッシュ管理に関する役割を分散するためのシステムおよびメカニズムを提供する。デバイス・ドライバは、たとえば、信頼できないミッション・ロジカル・パーティション(LPAR)内に設けることができ、デバイス・ドライバ・サービスは、たとえば、信頼できる入出力(I/O)仮想化仲介(VI:virtualization intermediary)内に設けることができる。例示的な諸実施形態の説明ではPCIeエンドポイントおよびPCIe通信プロトコルを使用するが、例示的な諸実施形態はこのようなものに限定されず、本発明の精神および範囲を逸脱せずに、任意の通信プロトコルを使用できることを認識されたい。

【0059】

例示的な諸実施形態に関しては、デバイス・ドライバは、ユーザ・アプリケーション/ライブラリとPCIeエンドポイントとの間で通信するためのキュー構造を管理し使用する役割を担う。デバイス・ドライバはさらに、デバイス・ドライバ・サービスによって提供されたメモリ管理サービスを呼び出す役割を担う。デバイス・ドライバ・サービスは、コンピューティング・システムのPCIeルート複合体のアドレス変換および保護テーブル(ATPT)ならびにPCIeエンドポイントのアドレス変換キャッシュ(ATC)を初期設定し管理する。このような初期設定および管理が実行される方法については以下に説明する。

【0060】

例示的な一実施形態では、ホスト・システムのロジカル・パーティションのシステム・イメージ内のPCIeエンドポイント用のデバイス・ドライバの初期設定中に、PCIeエンドポイント用のデバイス・ドライバは、アドレス変換および保護テーブル(ATPT)項目を初期設定し、デバイス・ドライバにPCIメモリ・アドレスを返すためにデバイス・ドライバ・サービスを呼び出す。例示的な一実施形態では、これらのATPT項目およびPCIメモリ・アドレスは、PCIeアダプタと通信するために、「デバイス・ドライバのキュー」というデバイス・ドライバの1つまたは複数のキューに関連づけられる。

【0061】

本質的に、デバイス・ドライバ・サービスは、1つまたは複数のキュー用のホスト・システム・メモリを滞留させ、1つまたは複数のキューにDMAアドレスを割り当て、ATPT項目をプログラミングし、ATPT項目がキャッシュ可能であること、すなわち、PCIeエンドポイント上でアドレス変換キャッシュ内にキャッシュ可能であることを示すビットを使用可能にする。次に、デバイス・ドライバ・サービスは、1つまたは複数の未変換PCIeメモリ・アドレスを、たとえば、1つまたは複数のキューに関連するアドレス(たとえば、キューの開始アドレス、ならびに、任意選択で終了キュー・アドレス)として使用可能なATPT項目用のデバイス・ドライバに返す。未変換PCIeメモリ・アドレスは、システムの実メモリ・アドレス空間内にないアドレスであり、システムの実メモリにアクセスするために使用するには、その前に変換しなければならないものである。

【0062】

例示的な諸実施形態のメカニズムを使用すると、この未変換PCIeメモリ・アドレス(複数も可)をPCIeエンドポイントに提供し、ルート複合体による変換要求動作を実行するためにPCIeエンドポイントがそれを使用することができる。すなわち、PCIeエンドポイントは、ルート複合体が未変換PCIeメモリ・アドレスに対応する1つまたは複数の変換済みPCIeメモリ・アドレスを返すことを要求することができる。次に、PCIeエンドポイントは、1つまたは複数の変換済みPCIeメモリ・アドレスをデバイス・ドライバのキューに関連するコンテキスト、たとえば、PCIeエンドポイント内の仮想機能のアドレス変換キャッシュ(ATC)に保管することができる。

【0063】

未変換PCIeメモリ・アドレスの変換をアダプタのデバイス・ドライバ・キュー・コンテキストに保管することにより、PCIeエンドポイントは、デバイス・ドライバ・キュー項目をターゲットにするDMAの際にルート複合体のATPTをバイパスすることができる。したがって、ルート複合体が変換済みとしてマークが付けられたPCIe DMAトランザクションを受信すると、ルート複合体は、そのエンドポイントについて変換キャッシュが使用可能になっていることを検証し、ホストの実メモリに直接アクセスするために変換済みPCIeメモリ・アドレスを使用する。

【0064】