データ処理システム内で第1のホスト・システムと第2のホスト・システムとの間で通信するための方法、プログラム、およびシステム(トランザクション・プロトコルおよび共用メモリを使用するホスト・システム間の通信のためのシステムおよび方法)

【課題】 トランザクション・プロトコルおよび共用メモリを使用するホスト・システム間の通信のためのシステムおよび方法を提供することにある。

【解決手段】 少なくとも1つのエンドポイントが少なくとも2つのホスト・システムの共用メモリ内にアドレス範囲を有するように、通信ファブリック内の発見プロセスに基づいて共用メモリが初期設定される。ホスト・システムの共用メモリを使用して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信するために、トランザクション指向プロトコルを確立することができる。このトランザクション指向プロトコルは、データをプッシュまたはプルするために、様々なエレメント、たとえば、ルート複合体またはエンドポイントによって実行すべき一連のトランザクションを指定する。プッシュ・トランザクションとプル・トランザクションの様々な組み合わせを使用することができる。

【解決手段】 少なくとも1つのエンドポイントが少なくとも2つのホスト・システムの共用メモリ内にアドレス範囲を有するように、通信ファブリック内の発見プロセスに基づいて共用メモリが初期設定される。ホスト・システムの共用メモリを使用して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信するために、トランザクション指向プロトコルを確立することができる。このトランザクション指向プロトコルは、データをプッシュまたはプルするために、様々なエレメント、たとえば、ルート複合体またはエンドポイントによって実行すべき一連のトランザクションを指定する。プッシュ・トランザクションとプル・トランザクションの様々な組み合わせを使用することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、一般に、改良されたデータ処理システムおよび方法に関する。より具体的には、本出願は、トランザクション・プロトコルおよび共用メモリを使用するホスト・システム間の通信のためのメカニズムを対象とする。

【背景技術】

【0002】

多くの近代的なコンピューティング・デバイスは、そもそも1990年代にインテル社によって作成された周辺装置相互接続規格のあるバージョンまたは実装例を使用する入出力(I/O:input/output)アダプタおよびバスを利用する。周辺装置相互接続(PCI:Peripheral ComponentInterconnect)規格は、コンピュータ・マザーボードに周辺装置を接続するためのコンピュータ・バスを規定するものである。PCI ExpressまたはPCIeは、既存のPCIプログラミング概念を使用するPCIコンピュータ・バスの実装例の1つであるが、大きく異なり、より高速のシリアル物理層通信プロトコルをそのコンピュータ・バスの基礎とする。この物理層は、複数のデバイス間で共用できる双方向バスから構成されるのではなく、正確に2つのデバイスに接続される1つの単一方向リンクから構成される。

【0003】

図1は、PCIe規格によるPCI Express(PCIe)のファブリック・トポロジ(ネットワークの接続形態の構造)を例示する図である。図1に図示されている通り、PCIeファブリック・トポロジ100は、ルート複合体130に結合されたホスト・プロセッサ(CPU)110およびメモリ120から構成され、次に、そのルート複合体130は、PCIeエンドポイント140(「エンドポイント」という用語は、PCIe対応入出力アダプタについて言及するためにPCIe規格で使用されるものである)、PCI Express/PCIブリッジ150、および1つまたは複数の相互接続スイッチ160のうちの1つまたは複数に結合されている。ルート複合体130は、CPU/メモリを入出力アダプタに接続する入出力階層のルートを意味する。ルート複合体130は、ホスト・ブリッジと、ゼロまたは1つ以上のルート複合体統合エンドポイントと、ゼロまたは1つ以上のルート複合体イベント・コレクタと、1つまたは複数のルート・ポートとを含む。各ルート・ポートは個別の入出力階層をサポートする。入出力階層は、ルート複合体130と、ゼロまたは1つ以上の相互接続スイッチ160またはブリッジ150あるいはその両方(スイッチまたはPCIeファブリックを含むもの)と、エンドポイント170および182〜188などの1つまたは複数のエンドポイントから構成することができる。PCIおよびPCIeに関する追加情報については、www.pcisig.comの周辺装置相互接続分科会(PCI−SiG:peripheral component interconnect special interest group)Webサイトから入手可能なPCIおよびPCIe規格を参照する。

【0004】

現在、PCIおよびPCIe入出力アダプタ、バスなどは、ブレード・サーバのブレードを含む、ほとんどすべてのコンピューティング・デバイスのマザーボードに統合されている。ブレード・サーバは、本質的に、いくつかの個別最小パッケージ・コンピュータ・マザーボード「ブレード」用のハウジングであり、そのそれぞれは、1つまたは複数のプロセッサと、コンピュータ・メモリと、コンピュータ記憶域と、コンピュータ・ネットワーク接続とを含むが、シャーシの共通電源および空冷リソースを共用する。ブレード・サーバは、Webホスティングおよびクラスタ・コンピューティングなどの特殊用途には理想的なものである。

【0005】

前述の通り、PCIおよびPCIe入出力アダプタは、典型的には、ブレード自体に統合される。その結果として、入出力アダプタは、同じブレード・サーバ内のブレード全域で共用することができない。その上、入出力アダプタの統合により、リンク・レートのスケーラビリティが制限される。すなわち、リンク・レートは、時間の経過につれてプロセッサ・パフォーマンスでスケーリングすることができない。現時点では、複数のブレード全域の複数のシステム・イメージによってPCIおよびPCIe入出力アダプタを共用できるようにするメカニズムは、まったく考案されていない。その上、1つのブレード・サーバ内の複数のブレードによって使用するためにPCIおよびPCIe入出力アダプタを非統合方式で提供できるようにするメカニズムは、まったく考案されていない。

【発明の開示】

【発明が解決しようとする課題】

【0006】

現行のPCIおよびPCIe入出力アダプタの統合による制限に対処するために、例示的な諸実施形態は、1つのPCIeアダプタを2つまたはそれ以上のシステム・イメージ(SI:system image)によって固有に共用できるようにするメカニズムを提供する。たとえば、エンドポイント、たとえば、PCIe入出力アダプタを同じルート複合体内の複数のSIによって、または共通PCIスイッチ・ファブリックを共用する、すなわち、共通PCIスイッチ・ファブリックに結合される複数のルート複合体(RC:rootcomplex)全域で同時に共用できるようにするためのメカニズムが提供される。このメカニズムにより、各ルート複合体ならびにそれに関連する物理エンドポイントまたは仮想エンドポイント(VEP:virtualendpoint)あるいはその両方は、それぞれ専用の固有のPCIメモリ・アドレス空間を有することができる。

【0007】

加えて、基本PCI規格から欠落しているが、エンドポイントの共用の結果として得られる複合体構成を管理するために必要なことは、エンドポイント内のPCI機能の組み合わせとして可能なものを決定し、それを管理する必要性である。したがって、本明細書の例示的な諸実施形態は、ブレード・サーバ内の第1のブレードの1つのルート複合体が同じかまたは異なるブレード・サーバ内の第2のブレードの第2のルート複合体と通信するためのメカニズムを提供する。例示的な諸実施形態では、このような通信を容易にするために使用されるマルチルート・ブレード・クラスタ内のルート複合体とエンドポイントとの間の共用メモリを初期設定するためのメカニズムを提供することにより、このような通信をサポートする。

【課題を解決するための手段】

【0008】

例示的な一実施形態では、マルチルートPCIe構成マネージャ(MR−PCIM:multi-root PCIe configuration manager)は、PCIeスイッチ・ファブリックの相互接続スイッチによりアクセス可能なすべてのリンクをトラバースすることによってPCIeスイッチ・ファブリック、すなわち、PCIe階層を発見することにより、ルート複合体とエンドポイントとの間の共用メモリを初期設定する。リンクをトラバースするにつれて、MR−PCIMは、ルート複合体およびエンドポイントのそれぞれについて入手した情報を比較して、どのエンドポイントおよびルート複合体が同じブレード上に存在するかを判断する。次に、PCIeスイッチ・ファブリック上で使用可能なエンドポイントを各ルート複合体に結合する仮想PCIeツリー・データ構造が生成される。同じPCIeツリーの一部であるエンドポイント、すなわち、同じルート複合体に関連するエンドポイントは、この仮想PCIeツリー・データ構造で関連付けられる。

【0009】

次に、MR−PCIMは、各エンドポイントが属すPCIeメモリ・アドレス空間内の基底および限界をそのエンドポイントに与えることができる。同様に、次に、MR−PCIMは、各ルート複合体が属すPCIeメモリ・アドレス空間内の基底および限界をそのルート複合体に与えることができる。様々なエンドポイントおよびルート複合体のPCIeメモリ・アドレス空間同士をマッピングするために、メモリ変換および保護テーブル・データ構造を生成することができる。

【0010】

たとえば、特定のエンドポイントまたはルート複合体の場合、そのエンドポイントまたはルート複合体は、第1のホストの実メモリ・アドレス空間に関連付けることができる。同じエンドポイントまたはルート複合体は、第1のホストのPCIバス・メモリ・アドレスにより直接メモリ・アクセス入出力としてアクセス可能な第2のホスト・メモリ上のPCIeアパーチャを介して第2のホストによりアクセス可能なものになりうる。第1のホストは、第2のホストによって認識されるPCIeメモリ・アドレスを第1のホストの実メモリ・アドレスにマッピングするために、メモリ変換および保護テーブル・データ構造を使用することができる。

【0011】

さらに他の例示的な実施形態では、エンドポイントがホスト・システム全域のルート複合体によりアクセス可能なものになりうるようにホスト・システムのメモリ・アドレス空間を初期設定すると、その後、これらのメモリ・アドレス空間を使用して、これらのルート複合体に関連するシステム・イメージとそれに対応するアプリケーションがエンドポイントと通信できるようにすることができる。

【0012】

このような通信を容易にする方法の1つは、様々なホスト・システム内のこれらの初期設定済みメモリ・アドレス空間を使用するキューイング・システムを介するものである。このようなキューイング・システムは、作業キュー構造と完了キュー構造とを含むことができる。作業キュー構造と完了キュー構造はいずれも、いくつかのキュー・エレメント(そのキュー構造が作業キュー構造であるか完了キュー構造であるかに応じて、作業キュー・エレメント(WQE:work queue element)または完了キュー・エレメント(CQE:completion queue element)のいずれか一方)を識別するためのドアベル構造と、キューの始まりに関する基底アドレスと、キューの終わりに関する限界アドレスと、キュー内で次に処理すべきWQEまたはCQEを示すオフセットとを含むことができる。作業キュー構造と完了キュー構造はいずれも、データの送信とデータの受信の両方に使用することができる。

【0013】

キュー構造およびドアベル構造は、実行すべき通信の対象であるルート複合体およびエンドポイントに対応するホスト・システム・メモリの一部分に設けることができる。キュー・エレメントを生成してキュー構造に追加することができ、それによりキュー・エレメントが処理のために使用可能であることをエンドポイントまたはルート複合体に通知するために、ドアベル構造を書き込むことができる。キュー・エレメントおよびキュー・エレメントに対応するデータを検索するために、PCIe DMA動作を実行することができる。その上、キュー・エレメントの処理の完了を示すための完了キュー・エレメント(CQE)を返すために、PCIe DMA動作を実行することができる。

【0014】

例示的な一実施形態によれば、例示的な諸実施形態の共用メモリを使用して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信するために、トランザクション指向プロトコルを確立することができる。このトランザクション指向プロトコルは、データをプッシュまたはプルするために、様々なエレメント、たとえば、ルート複合体またはエンドポイントによって実行すべき一連のトランザクションを指定する。本発明の精神および範囲を逸脱せずに、プッシュ・トランザクションとプル・トランザクションの様々な組み合わせを使用することができる。この様々な組み合わせについては、以下の詳細な説明でより詳細に説明する。

【0015】

加えて、例示的な諸実施形態のメカニズムをさらに使用して、上述の共用メモリを介して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間のソケット・プロトコル・ベースの通信をサポートすることができる。このようなソケット・ベースの通信では、ホスト・システム内の作業キューを使用して、着信ソケット初期設定要求を聴取(listen)することができる。すなわち、第2のホスト・システムとのソケット通信接続を確立することを希望する第1のホスト・システムは、その作業キュー内にソケット初期設定要求WQEを生成することができ、そのソケット初期設定要求WQEが処理のために使用可能であることを第2のホスト・システムに通知することができる。

【0016】

その後、第2のホスト・システムは、その要求を受諾または拒否することができる。第2のホスト・システムがその要求を受諾する場合、そのホスト・システムは、第1および第2のホスト・システム間でソケット・ベースの通信を実行する際に第1のホスト・システムによって使用するためのソケットのパラメータのうちの後半部分を返す。これらのパラメータは、ソケットに関連付けるべきキュー構造の一部分と、キュー・エレメントがソケットを介して処理のための使用可能であるときにホスト・システムに通知するために使用されるドアベル構造とを指定することができる。実際のソケット通信は、たとえば、ホスト・システム間のプル・トランザクションまたはプッシュ・トランザクションあるいはその両方を伴う可能性がある。

【0017】

ルート複合体間のリソースの固有の共用により、システム・イメージ間またはエンドポイント間あるいはその両方で機能およびそれに関連するアプリケーションの移行のためのメカニズムを提供するために活用可能なPCIeファブリック内のホスト・システムとエンティティとの関係が作り出される。この移行機能は、システム管理の領域においてワークロード・バランシング機能の需要の増大を満足するために必要である。このようなメカニズムは、現在、PCIe規格から欠落している。

【0018】

例示的な一実施形態では、単一ルートPCI構成マネージャ(SR−PCIM:Single-Root PCI Configuration Manager)は、エンドポイント(EP)によってサポートされる仮想機能(VF:virtualfunction)移行シナリオとして可能なものを備えたシステム・イメージ(SI)を提供する。システム管理者または管理用タスクを実行するソフトウェア・アプリケーション、たとえば、ワークロード・バランシング・アプリケーションは、あるSIから他のSIへのVFおよびそれに関連するアプリケーション(複数も可)のステートレス移行が必要であることを単一ルートPCIマネージャ(SR−PCIM)に示すコマンドを実行することができる。VFおよびそれに関連するアプリケーション(複数も可)(動作すべきVFに依存するアプリケーションである)を移行することにより、より効率的な環境で動作を続行するために種々のリソースをリクルートすることができる。たとえば、ワークロード・バランシングでは、例示的な諸実施形態のメカニズムを使用してイーサネット(登録商標)VFおよびそれに関連する従属アプリケーションを移動し、異なるSIまたは同等EPと完全に関連付けることができる異なる物理機能(PF:physicalfunction)上で使用可能なより高速の(あまり輻輳していない)接続を利用することができる。

【0019】

ホスト・システム上で実行されるソフトウェア仲介(SWI:Software Intermediary)または仮想化仲介(virtualization intermediary)は、VFに対する未解決の要求を完了し、次にそれを停止するために必要な任意のプロセスを開始するようSIに指示する。VFに対するすべての要求が完了したことがSIによってSWIに通知されると、SWIは、VFに関連する任意のアプリケーションをSIから除去することができ、VFを関連の物理機能(PF)から切り離すことができる。

【0020】

その後、SWIは、同じかまたは異なるEP内に存在する可能性のあるターゲットPFにVFを接続することができる。その上、ターゲットPFは、異なるSIに関連付けることができる。SWIは、VFをそのVFが現在関連付けられているSIにとって使用可能なものにし、VFを構成するようSIに指示する。SIはVFを構成し、それにより、それを関連アプリケーションによる使用のために使用可能なものにする。次に、SWIは、新たに移行されたVF上のリソースを使用できるように、関連アプリケーションを開始するようSIに指示することができる。

【0021】

上記のメカニズムに加えて、例示的な諸実施形態は、実行中のマルチルートPCIeファブリックへの新しいコンポーネントのホット・プラグ/除去を実行するための機能をさらに提供する。これらのメカニズムにより、たとえば、ルート複合体を実行中のPCIeファブリックにホット・プラグするかまたはそこから除去することができる。たとえば、ブレードはブレード・シャーシにホット・プラグすることができ、それに関連するルート複合体は既存のシステム内のPCIeファブリックにリアルタイムで組み込むことができる。

【0022】

このようなホット・プラグ/除去機能により、PCIeファブリックが増大することができ、新たに組み込まれたルート複合体全域で仮想機能を固有に共用することができる。したがって、PCIeファブリックは、それを実行するためにシステムを停止せずに拡張することができる。PCI−SiG入出力仮想化規格は、PCIeファブリックのこのような動的拡張に関するこのような機能または標準をまったく提供していない。

【0023】

例示的な一実施形態では、第1のホスト・システムと第2のホスト・システムとの間で通信するための方法が提供される。この方法は、第2のホスト・システムに関連するエンドポイントに割り当てられた第1のアドレス範囲を含むように第1の共用メモリ内に第1のメモリ・アドレス空間を初期設定するステップを含むことができる。この方法は、第2のホスト・システムに関連するエンドポイントに割り当てられた第2のアドレス範囲を含むように第2の共用メモリ内に第2のメモリ・アドレス空間を初期設定するステップをさらに含むことができる。その上、この方法は、第1のアドレス範囲内に作業キュー構造を生成するステップと、第2のアドレス範囲内に完了キュー構造を生成するステップであって、その完了キュー構造が第2のドアベル構造を含むステップとを含むことができる。作業キュー構造と第2のホスト・システムとの間ならびに完了キュー構造と第1のホスト・システムとの間で作業キュー・エレメントおよび完了キュー・エレメントを転送するために、確立されたトランザクション・プロトコルにより第1のホスト・システムおよび第2のホスト・システムによってプッシュ動作またはプル動作のうちの少なくとも一方を実行することができる。

【0024】

確立されたトランザクション・プロトコルは、プルプルプッシュ・トランザクション・プロトコルにすることができる。このプルプルプッシュ・トランザクション・プロトコルにより、エンドポイントは、作業キュー構造からエンドポイントに作業キュー・エレメントをプルするために直接メモリ・アクセス動作を実行する。その上、エンドポイントは、作業キュー・エレメントに対応するデータを第1の共用メモリからプルするために直接メモリ・アクセス動作を実行する。さらに、エンドポイントは、第1のホスト・システムに完了キュー・エレメントをプッシュするための動作を実行する。

【0025】

確立されたトランザクション・プロトコルは、エンドポイントによって施行することができる。第1のアドレス範囲および第2のアドレス範囲は、メモリ・マップ入出力(I/O)動作ならびに少なくとも1つのアドレス変換および保護テーブルを介してホスト・システムによりアクセス可能なものにすることができる。プッシュ動作およびプル動作は、直接メモリ・アクセス(DMA)動作にすることができる。

【0026】

第1のホスト・システムに関連する第1のメモリ・アドレス空間を初期設定するステップならびに第2のホスト・システムに関連する第2のメモリ・アドレス空間を初期設定するステップは、データ処理システムの通信ファブリック内のリンクをトラバースして、通信ファブリック内に存在するエンドポイントおよびルート複合体に関する情報を収集するステップを含むことができる。この方法は、物理的にまたは論理的に相互に関連付けられている少なくとも1つのエンドポイントおよび少なくとも1つのルート複合体を識別する少なくとも1つの仮想階層を生成するステップをさらに含むことができる。その上、この方法は、第1のホスト・システムのルート複合体に関連する各エンドポイントが第1のメモリ・アドレス空間内に対応するアドレス範囲を有し、第2のホスト・システムのルート複合体に関連する各エンドポイントが第2のメモリ・アドレス空間内に対応するアドレス範囲を有するように、少なくとも1つの仮想階層に基づいて第1のメモリ・アドレス空間および第2のメモリ・アドレス空間を初期設定するステップを含むことができる。少なくとも1つのエンドポイントは、第1のメモリ・アドレス空間内と第2のメモリ・アドレス空間内の両方に、対応するアドレス範囲を有することができる。

【0027】

データ処理システムはブレード・サーバにすることができ、第1のホスト・システムおよび第2のホスト・システムはブレード・サーバ内のブレードにすることができる。データ処理システムは、第1のホスト・システムおよび第2のホスト・システムが結合される周辺装置相互接続高速(PCIe)ファブリックを含むことができる。エンドポイントはPCIeアダプタにすることができる。PCIeファブリックは、1つまたは複数の複数ルート認識(MRA:multiple root aware)スイッチを含む複数ルート認識PCIeファブリックにすることができる。

【0028】

他の例示的な諸実施形態では、コンピュータ可読プログラムを有するコンピュータで使用可能な媒体を含むコンピュータ・プログラム(computer program product)が提供される。このコンピュータ可読プログラムは、コンピューティング・デバイス上で実行されると、方法の例示的な実施形態に関して上記で概要を示した動作のうちの様々な動作ならびにそれらの組み合わせをコンピューティング・デバイスに実行させる。

【0029】

さらに他の例示的な実施形態では、データ処理システムが提供される。このデータ処理システムは、第1のホスト・システムと、第2のホスト・システムと、第1のホスト・システムおよび第2のホスト・システムを結合する通信ファブリックとを含むことができる。このデータ処理システムは、方法の例示的な実施形態に関して上記で概要を示した動作のうちの様々な動作ならびにそれらの組み合わせを実行することができる。

【0030】

本発明の上記その他の特徴および利点は、本発明の典型的な諸実施形態に関する以下の詳細な説明に記載され、その詳細な説明を考慮すると、当業者には自明なものになるであろう。

【0031】

本発明に特有と思われる新規の特徴は特許請求の範囲に規定されている。しかし、本発明そのもの、ならびにその好ましい使用態様、他の目的および利点は、添付図面に併せて読んだときに、例示的な一実施形態に関する以下の詳細な説明を参照することによって最もよく理解されるであろう。

【発明を実施するための最良の形態】

【0032】

例示的な諸実施形態は、同じかまたは異なるルート・ノード、たとえば、ブレード・サーバのブレード上にある可能性のある、同じかまたは異なるルート複合体の2つまたはそれ以上のシステム・イメージ(SI)によって1つのPCIeアダプタまたは「エンドポイント」を固有に共用できるようにするメカニズムを提供する。さらに、例示的な諸実施形態は、それによりシステム・イメージと固有に共用されるエンドポイントとの間の通信を容易にするメカニズムを提供する。加えて、例示的な諸実施形態は、PCIeファブリックの管理を容易にするために、仮想プレーン、ルート複合体、およびシステム・イメージ間で仮想機能を移行するためのメカニズムを提供する。その上、例示的な諸実施形態は、それによりエンドポイントを設計するときにエンドポイント・インプリメンタが許可した機能の有効な組み合わせをルート複合体の単一ルートPCIマネージャ(SR−PCIM)がエンドポイントから読み取ることができるメカニズムを提供する。その場合、SR−PCIMは、エンドポイントが使用されている現行構成で使用されることになる機能の組み合わせを設定することができる。

【0033】

図2は、一般に当技術分野で知られているシステム仮想化を例示する典型的な図である。システム仮想化とは、各セットのリソースがそれ専用のシステム・イメージ・インスタンスおよびアプリケーションにより独立して動作するように物理システムのプロセッサ、メモリ、入出力アダプタ、記憶域、およびその他のリソースを分割することである。このようなシステム仮想化では、仮想リソースは、物理リソースから構成され、たとえば、同じ外部インターフェースおよび機能を有し、設計されたインターフェース/機能を備えたメモリ、ディスク・ドライブ、およびその他のハードウェア・コンポーネントなどの物理リソース用のプロキシとして動作する。システム仮想化は、典型的には、仮想リソースを作成し、それを物理リソースにマッピングし、それにより仮想リソース間の分離を可能にする仮想化仲介を使用する。仮想化仲介は、典型的には、ソフトウェア、ファームウェア、およびハードウェア・メカニズムのうちの1つまたはこれらの組み合わせとして提供される。

【0034】

図2に図示されている通り、仮想化システムにおいて典型的には、アプリケーション210は、それにより特定の仮想リソースおよび物理リソースが割り当てられる汎用または特殊目的オペレーティング・システムなどのソフトウェア・コンポーネントであるシステム・イメージ(SI)220と通信する。システム・イメージ220は、単一SIインスタンスを実行するために必要な物理リソースまたは仮想化リソース、たとえば、仮想化プロセッサ、メモリ、入出力アダプタ、記憶域などから構成される仮想システム230に関連付けられている。

【0035】

システム・イメージ220は、仮想システム230の使用により、仮想化仲介240を介して物理システム・リソース250にアクセスする。仮想化仲介240は、SIへのリソースの割り振りを管理し、SIに割り当てられたリソースを他のSIによるアクセスから分離する。この割り振りおよび分離は、仮想化仲介240によって実行されるリソース・マッピングならびに仮想化仲介240によって維持される1つまたは複数のリソース・マッピング・データ構造に基づいて実行される場合が多い。

【0036】

このような仮想化を使用して、入出力動作および入出力リソースの仮想化を可能にすることができる。すなわち、入出力仮想化(IOV:I/O virtualization)に関しては、仮想化仲介240などの入出力仮想化仲介(IOVI:I/O virtualizationintermediary)を使用して、2つ以上のSIによって単一の物理入出力装置を共用することができる。IOVIは、たとえば、SIからの構成、入出力、およびメモリ動作、ならびにSIへの直接メモリ・アクセス(DMA)、完了、および割り込み動作のうちの1つまたは複数に介入することによりIOVをサポートするために使用されるソフトウェア、ファームウェアなどにすることができる。

【0037】

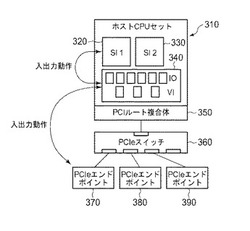

図3は、入出力仮想化仲介を使用してPCIルート複合体の入出力を仮想化するための第1の手法を例示する典型的な図である。図3に図示されている通り、ホスト・プロセッサ・セット310は、チップ、マザーボード、ブレードなどの1つまたは複数のプロセッサにすることができ、それによりアプリケーション(図示せず)がPCIeエンドポイント370〜390などのシステム・リソースにアクセスできる複数のシステム・イメージ320〜330をサポートすることができる。システム・イメージは、入出力仮想化仲介340、PCIeルート複合体350、1つまたは複数のPCIeスイッチ360、およびその他のPCIeファブリック・エレメント、あるいはこれらの組み合わせを介して仮想化リソースと通信する。

【0038】

図3に例示されている手法では、入出力仮想化仲介340は、すべての入出力トランザクションに関わり、すべての入出力仮想化機能を実行する。たとえば、入出力仮想化仲介340は、様々なSIの入出力キューからの入出力要求をPCIeエンドポイント370〜390内の単一キューに多重化する。したがって、入出力仮想化仲介は、SI320〜330と物理PCIeエンドポイント370〜390との間のプロキシとして働く。

【0039】

入出力仮想化仲介340によるこのような関わりは、入出力動作に追加の遅延をもたらす可能性があり、それにより単位時間あたりの入出力動作の数が制限され、その結果、入出力パフォーマンスが制限される。加えて、入出力仲介の関わりによって余分なCPUサイクルが必要になり、その結果、他のシステム動作に使用可能なCPUパフォーマンスが低減される。また、この手法が必要とする余分なコンテキスト・スイッチおよび割り込みリダイレクション・メカニズムも、全体的なシステム・パフォーマンスに影響を及ぼす可能性がある。さらに、エンドポイント370〜390が複数のルート複合体間で共用される場合、IOVI340は実現可能なものではない。

【0040】

図4は、固有に共用されるPCI入出力アダプタを使用してPCIルート複合体の入出力を仮想化するための第2の手法を例示する典型的な図である。図4に図示されている通り、ホスト・プロセッサ・セット410は、チップ、マザーボード、ブレードなどの1つまたは複数のプロセッサにすることができ、それによりアプリケーション(図示せず)がPCIe入出力仮想化(IOV)エンドポイント470〜490などのシステム・リソースにアクセスできる複数のシステム・イメージ420〜430をサポートすることができる。システム・イメージ420〜430は、PCIeルート複合体440、1つまたは複数のPCIeスイッチ460、およびその他のPCIeファブリック・エレメント、あるいはこれらの組み合わせを介して仮想化リソースと通信する。

【0041】

PCIeルート複合体440は、1つまたは複数のアドレス変換および保護テーブル・データ構造、割り込みテーブル・データ構造などを含むことができ、IOV対応エンドポイント470〜490との入出力動作の仮想化を容易にするルート複合体仮想化イネーブラ(RCVE:root complex virtualization enabler)442を含む。アドレス変換および保護テーブル・データ構造は、たとえば、仮想化リソースに関する仮想アドレスと実アドレスとのアドレス変換を実行し、SIへの仮想リソースのマッピングに基づいて仮想リソースへのアクセスを制御し、その他の仮想化動作を実行するために、PCIeルート複合体440によって使用することができる。これらのルート複合体割り込みテーブル・データ構造は、PCIeメモリ・アドレス空間によりアクセス可能であり、たとえば、SIに関連する適切な割り込みハンドラに割り込みをマッピングするために使用される。

【0042】

図3に図示されている配置構成のように、入出力仮想化インターフェース450も図4の仮想化構造内に設けられている。入出力仮想化インターフェース450は、PCIeスイッチ460に結合可能な非IOV対応PCIeエンドポイントとともに使用される。すなわち、入出力仮想化インターフェース(IOVI)450は、入出力仮想化(IOV)のための固有のサポート、すなわち、エンドポイント内部のサポートを備えていないPCIeエンドポイントについて図3に関して前述したものと同様にPCIeエンドポイントともに使用される。

【0043】

IOV対応PCIeエンドポイント470〜490の場合、IOVI450は、主に構成トランザクション目的に使用され、SIから開始されるメモリ・マップ入出力(MMIO:memory mapped input/output)動作またはPCIeエンドポイント470〜490から開始される直接メモリ・アクセス(DMA)動作などのメモリ・アドレス空間動作には関わらない。それとは反対に、SI420〜430とエンドポイント470〜490との間のデータ転送は、IOVI450による介入なしに直接実行される。SI420〜430とエンドポイント470〜490との間の直接入出力動作は、以下により詳細に記載するように、RCVE442ならびにIOV対応PCIeエンドポイント470〜490の組み込み入出力仮想化ロジック、たとえば、物理機能および仮想機能を介して可能になる。直接入出力動作を実行する能力は、入出力動作を実行可能な速度を大幅に増加するが、PCIeエンドポイント470〜490が入出力仮想化をサポートすることを必要とする。

【0044】

図5は、PCIe入出力仮想化(IOV)対応エンドポイントの典型的な図である。図5に図示されている通り、PCIe IOVエンドポイント500は、それによりPCIeファブリックのPCIeスイッチなどとの通信を実行可能なPCIeポート510を含む。内部ルーティング520は、構成管理機能520および複数の仮想機能(VF)540〜560への通信パスを提供する。構成管理機能530は、仮想機能540〜560とは対照的に物理機能にすることができる。物理「機能」とは、PCI規格で使用される用語であり、単一の構成空間(configuration space)によって表される1組のロジックである。換言すれば、物理「機能」とは、たとえば、非分離型リソース570内に設けることができるものなど、メモリ内のその機能に関連する構成空間内に保管されたデータに基づいて構成可能な回路ロジックである。

【0045】

構成管理機能530を使用して、仮想機能540〜560を構成することができる。仮想機能とは、入出力仮想化対応エンドポイント内で、1つまたは複数の物理エンドポイント・リソース、たとえば、リンクを共用する機能であり、たとえば、他の機能とともに、PCIe IOVエンドポイント500の共用可能リソース・プール580内に設けることができる機能である。仮想機能は、入出力仮想化仲介によるランタイム介入なしに、直接、システム・イメージからの入出力およびメモリ動作用のシンクにすることができ、システム・イメージ(SI)への直接メモリ・アクセス(DMA)、完了、および割り込み動作のソースにすることができる。

【0046】

PCIeエンドポイントは、PCIeエンドポイントによってサポートされる「機能」に関して多種多様なタイプの構成を有することができる。たとえば、エンドポイントは、単一の物理機能(PF)、複数の独立PF、または複数の従属PFさえサポートすることができる。固有の入出力仮想化をサポートするエンドポイントでは、エンドポイントによってサポートされる各PFは、1つまたは複数の仮想機能(VF)に関連付けることができ、その仮想機能自体は、他のPFに関連するVFに従属している可能性がある。物理機能と仮想機能との典型的な関係については以下の図6および図7に例示されている。

【0047】

図6は、固有の仮想化なしの単一ルート・エンドポイントの物理機能および仮想機能を例示する典型的な図である。「単一ルート・エンドポイント」という用語は、単一ルート・ノードの単一ルート複合体、すなわち、単一ホスト・システムに関連するエンドポイントを指す。単一ルート・エンドポイントでは、エンドポイントは、単一ルート複合体に関連する複数のシステム・イメージ(SI)によって共用することができるが、同じかまたは異なるルート・ノード上の複数のルート複合体間で共用することはできない。

【0048】

図6に図示されている通り、ルート・ノード600は、PCIeエンドポイント670〜690と通信する複数のシステム・イメージ610、612、入出力仮想化仲介630(前述したように使用されるもの)、PCIeルート複合体640、1つまたは複数のPCIeスイッチ650、およびその他のPCIeファブリック・エレメント、あるいはこれらの組み合わせを含む。ルート・ノード600は、単一ルートPCIe構成管理(SR−PCIM)ユニット620をさらに含む。SR−PCIMユニット620は、ルート複合体640、1つまたは複数のPCIeスイッチ650などを含むPCIeファブリック、ならびにエンドポイント670〜690を管理する役割を担う。SR−PCIM620の管理責任としては、どの機能をどのSI610、612に割り当てるべきかを判断することと、エンドポイント670〜690の構成空間をセットアップすることを含む。SR−PCIM620は、SIの機能およびシステム管理者などのユーザからの入力に基づいて、あるいはどのリソースをどのSI610、612に割り当てるべきかについてはロード・バランシング・ソフトウェアに基づいて、様々なエンドポイント670〜690の機能を構成することができる。SIの機能としては、エンドポイント670〜690に割り振るためにどの程度の大きさのアドレス空間が使用可能であるか、エンドポイント670〜690に割り当てるためにどの程度の数の割り込みが使用可能であるかなどを含む様々な要因を含むことができる。

【0049】

PCIeエンドポイント670〜690のそれぞれは、1つまたは複数の物理機能(PF)をサポートすることができる。1つまたは複数のPFは、相互に独立している場合もあれば、何らかの方式で相互に従属している場合もある。たとえば、適切に動作するために、あるPFが他のPFの動作または他のPFによって生成された結果を必要とするというようなベンダ定義の機能依存関係に基づいて、PFは他のPFに従属している可能性がある。描かれている例では、PCIeエンドポイント670は単一PFをサポートし、PCIeエンドポイント680は異なるタイプ1〜Mの複数の独立PF、すなわち、PF0〜PFNをサポートする。タイプはPFまたはVFの機能に関し、たとえば、イーサネット(登録商標)機能およびファイバ・チャネル機能は2つの異なるタイプの機能である。エンドポイント690は異なるタイプの複数のPFをサポートし、全PFのうちの2つまたはそれ以上のPFは従属している。描かれている例では、PF0はPF1に従属しているか、またはその逆になる。

【0050】

図6に図示されている例では、エンドポイント670〜690は、入出力仮想化仲介(IOVI)630によって使用可能なものになっている仮想化メカニズムによりシステム・イメージ(SI)610および612によって共用される。前述の通り、このような配置構成では、IOVI630は、SI610、612とPCIeエンドポイント670〜690との間のすべてのPCIeトランザクションに関わる。仮想化を処理する義務は完全にIOVI630にあるので、個々のPCIeエンドポイント670〜690は本質的に仮想化をサポートする必要はない。その結果として、このような配置構成で仮想化のための既知のメカニズムを使用することができるが、入出力動作を実行可能なレートは、IOVI630があらゆる入出力動作に関わらない場合に入出力レート用の潜在能力に比べて比較的遅くなる。

【0051】

図7は、固有の入出力仮想化に使用可能になっている単一ルート・エンドポイントの物理機能および仮想機能を例示する典型的な図である。図7に図示されている配置構成は図6の配置構成と同様であるが、PCIeエンドポイント770〜790が入出力仮想化(IOV)を固有に、すなわち、エンドポイントそのものの内部でサポートすることによるいくつかの重要な相違点がある。その結果として、IOV対応PCIeエンドポイント770〜790に関しては、当然のことながら構成動作を除いて、図6の入出力仮想化仲介630を事実上省略することができる。しかし、この配置構成で非IOV対応PCIeエンドポイント(図示せず)、たとえば、レガシー・エンドポイントも使用する場合、システム・イメージ710および712間でこのような非IOV対応PCIeエンドポイントの共用を処理するために、図7に図示されているエレメントに併せて入出力仮想化仲介を使用することができる。

【0052】

図7に図示されている通り、IOV対応PCIeエンドポイント770〜790は、1つまたは複数の独立または従属物理機能(PF)をサポートすることができ、次にその物理機能は1つまたは複数の独立または従属仮想機能(VF)に関連付けることができる。これに関連して、PFは、1組のVFを管理するためにSR−PCIM720によって使用され、物理エラーおよびイベントなどのエンドポイント機能を管理するためにも使用される。PFに関連する構成空間は、PFに関連する最大数のVF、PFおよびVFと他のPFおよびVFとの組み合わせなどを含む、VFの機能を定義する。

【0053】

VFは、IOV対応PCIeエンドポイント770〜790上のリソース、たとえば、メモリ空間、キュー、割り込みなどにアクセスするためにSIによって使用される。したがって、固有のPFを共用する各SI710、712ごとに異なるVFが生成される。VFは、対応するPFの構成空間内のSR−PCIM720によるVFの数の設定に基づいて、エンドポイント770〜790によって生成される。このようにして、PFは、複数のSI710、712によって共用できるように仮想化される。

【0054】

図7に図示されている通り、VFおよびPFは他のVFおよびPFに従属している可能性がある。典型的には、あるPFが従属PFである場合、そのPFに関連するすべてのVFも従属することになる。したがって、たとえば、PF0のVFはPF1の対応するVFに従属している可能性がある。

【0055】

図7に図示されている配置構成では、SI710、712は、入出力仮想化仲介による関わりの必要なしに、PCIルート複合体730およびPCIeスイッチ740を介して、IOV対応PCIeエンドポイント770〜790と直接通信することができ、その逆も同様である。このような直接通信は、エンドポイント770〜790内ならびにエンドポイント770〜790のPFおよびVFを構成するSR−PCIM720内に設けられたIOVサポートによって可能なものになる。

【0056】

SIとエンドポイントとの間の直接通信は、複数のSI710、712と共用されたIOV対応PCIeエンドポイント770〜790との間で入出力動作を実行できる速度を大幅に増加する。しかし、このようなパフォーマンス強化を可能なものにするために、PCIeエンドポイント770〜790は、仮想機能(VF)を生成し管理するためにSR−PCIM720内のメカニズムならびにエンドポイント770〜790の物理機能(PF)を提供することにより、入出力仮想化をサポートしなければならない。

【0057】

PCIe階層の上記の例示は単一ルート階層に制限されている。換言すれば、PCIeエンドポイントは、単一PCIルート複合体730に関連する単一ルート・ノード700上のSI710、712のみによって共用される。上述のメカニズムは、PCIeエンドポイントを共用する複数ルート複合体のためのサポートを提供しない。したがって、複数ルート・ノードにPCIeエンドポイントのリソースへの共用アクセスを提供することはできない。これにより、各ルート・ノードごとに個別のエンドポイント・セットが必要になるので、このような配置構成を使用するシステムのスケーラビリティが制限される。

【0058】

本明細書の例示的な諸実施形態は、複数のPCIルート複合体が同じセットのIOV対応PCIeエンドポイントへのアクセスを共用できる、マルチルート入出力仮想化を利用する。その結果として、これらのPCIルート複合体のそれぞれに関連するシステム・イメージはそれぞれ、同じセットのIOV対応PCIeエンドポイントへのアクセスを共用することができるが、仮想化の保護は各ルート・ノード上の各SIごとに所定の位置にある。したがって、同じ既存のセットのIOV対応PCIeエンドポイントを共用できるルート・ノードおよび対応するPCIルート複合体の追加を可能にするためのメカニズムを提供することにより、スケーラビリティが最大になる。

【0059】

図8は、例示的な一実施形態によるマルチルート仮想化入出力トポロジを例示する典型的な図である。図8に図示されている通り、複数のルート・ノード810および820が設けられ、それぞれのルート・ノードは、単一ルートPCI構成マネージャ(SR−PCIM)812、822と、1つまたは複数のシステム・イメージ(SI)814、816、824、826と、PCIルート複合体818、828とを有する。これらのルート・ノード810および820は、たとえば、ブレード・サーバ内のブレードにすることができ、PCIeスイッチ・ファブリックの1つまたは複数のマルチルート認識(MRA)PCIeスイッチ840に結合されており、そのPCIeスイッチ・ファブリックは、1つまたは複数のこのようなMRA PCIeスイッチ840およびその他のPCIeファブリック・エレメントあるいはその両方を含むことができる。MRAスイッチ840は追加のルート・ノード用の接続を有し、これらの異なるルート・ノードのアドレス空間を個別かつ独特なものとして保持するために必要なメカニズムを収容しているという点で、MRAスイッチ840は図7の非MRAスイッチ740とは異なるタイプのものである。

【0060】

これらのルート・ノード810および820に加えて、マルチルートPCI構成マネージャ(MR−PCIM)832および対応するPCIルート複合体834を含む第3のルート・ノード830が設けられている。MR−PCIM832は、以下により詳細に論じるように、図8に図示されているマルチルート(MR)トポロジ内の仮想階層を発見し構成する役割を担う。したがって、MR−PCIM832は、複数ルート・ノードの複数ルート複合体に関してエンドポイントの物理機能および仮想機能を構成する。SR−PCIM812および822は、それぞれに関連する単一ルート複合体の物理機能および仮想機能を構成する。換言すれば、以下により詳細に記載するように、MR−PCIMはMRトポロジを全体として認識するが、SR−PCIMはMRトポロジ内のそれ専用の仮想階層のみを認識する。

【0061】

図8に図示されている通り、IOV対応PCIeエンドポイント850および860は、1つまたは複数の仮想エンドポイント(VE)852、854、862、および864をサポートする。VEは、ルート複合体に割り当てられた1組の物理機能および仮想機能である。したがって、たとえば、ルート・ノード810のPCIルート複合体818のためにIOV対応PCIeエンドポイント850および860上に個別のVE852および862が設けられている。同様に、ルート・ノード820のPCIルート複合体828のためにIOV対応PCIeエンドポイント850および860上に個別のVE854および864が設けられている。

【0062】

各VEは、仮想階層(VH)のルートとして単一ルート複合体を有し、階層内の終端ノードとしてVEを有する仮想階層(VH)に割り当てられている。VHは、ルート複合体またはSR−PCIMに割り当てられた完全に機能しうるPCIe階層である。VE内のすべての物理機能(PF)および仮想機能(VF)が同じVHに割り当てられることに留意されたい。

【0063】

各IOV対応PCIeエンドポイント850および860は、基本機能(BF:base function)859および869をサポートする。BF859、869は、対応するエンドポイント850、860のVEを管理するためにMR−PCIM832によって使用される物理機能である。たとえば、BF859、869は、対応するエンドポイント850、860のVEに機能を割り当てる役割を担う。MR−PCIM832は、エンドポイント850、860内のPFのそれぞれに対するVH番号の割り当てを可能にするBFの構成空間内のフィールドを使用することによって、VEに機能を割り当てる。例示的な諸実施形態では、エンドポイントあたり1つのBFのみ存在することができるが、本発明はこのような構成に制限されない。

【0064】

図8に図示されている通り、各VE852、854、862、および864は、それ専用の1組の物理機能および仮想機能をサポートすることができる。前述の通り、このような機能セットは、独立物理機能、従属物理機能、およびそれに関連する独立/従属仮想機能を含むことができる。図8に図示されている通り、VE852は、それに関連する仮想機能(VF)とともに単一物理機能(PF0)をサポートする。同様にVE854は、それに関連する仮想機能(VF)とともに単一物理機能(PF0)をサポートする。VE862は、複数の独立物理機能(PF0〜PFN)およびそれに関連する仮想機能(VF)をサポートする。しかし、VE864は、複数の従属物理機能(PF0〜PFN)をサポートする。

【0065】

VE852、854、862、または864は、SIがアクセスできるVHにVEが割り当てられている場合およびその逆の場合にのみ、ルート・ノード810および820のSI814、816、824、および826と直接通信することができる。エンドポイント850および860そのものは、上記で前述したものなどの単一ルート入出力仮想化ならびにこの例示的な諸実施形態に関して記載したマルチルート入出力仮想化をサポートしなければならない。この要件は、そのトポロジが複数ルート複合体をサポートすることに基づくものであるが、それぞれの個別ルート・ノードはそれに関連する単一ルート・ベースの仮想階層のみを認識する。

【0066】

図9は、例示的な一実施形態によるルート・ノードのルート複合体の観点から見たマルチルート仮想化入出力トポロジの仮想階層表示を例示する典型的な図である。図9に図示されている通り、マルチルート(MR)トポロジは図8に図示されている通りにすることができるが、それぞれの個別ルート・ノードの各ルート複合体は、MRトポロジのうち、それが占める部分のみを表示する。したがって、たとえば、ルート・ノード810に関連するPCIルート複合体818は、そのホスト・プロセッサ・セット、それ専用のシステム・イメージ(SI)814、816、MRAスイッチ840、およびそれ専用の仮想エンドポイント(VE)852、862を認識する。この仮想階層内には完全なPCIe機能が存在するが、PCIルート複合体818は、それ専用の仮想階層の一部ではないVE、ルート複合体、システム・イメージなどを認識しない。

【0067】

この配置構成のために、MRトポロジ内のルート・ノードのルート複合体間の通信に制限が課せられる。すなわち、PCIe機能はルート複合体に関連する仮想階層に制限されるので、ルート複合体は相互に通信することができない。その上、様々なルート複合体に関連するシステム・イメージは他のルート複合体のシステム・イメージと通信することができない。このような制限に対処するために、本明細書の例示的な諸実施形態は、仮想階層間、具体的には、種々のルート・ノードのルート複合体間の通信に関するサポートを提供するための様々なメカニズムを提供する。

【0068】

例示的な諸実施形態のホスト・システムがそのルート複合体を介して複数のエンドポイントと通信するために、ホスト・システムは、ホスト・システムが関連付けられる様々なエンドポイントおよびルート複合体によって共用される共用メモリを使用する。ホスト・システムとともにエンドポイントの適切な動作を保証するために、ホスト・システムに関連する各エンドポイントに対し、共用メモリのうち、それにより様々な通信を実行することができる専用の部分が提供されるように、この共用メモリを初期設定しなければならない。例示的な諸実施形態は、PCIeファブリックが発見され、PCIeファブリックのエンドポイントがホスト・システムのルート複合体に実質的に結合されるようなホスト・システムの共用メモリを初期設定するためのメカニズムを使用する。その場合、各エンドポイントおよびルート複合体には、それが実質的に結合される各ホスト・システムの共用メモリ・アドレス空間のうち、専用の部分が与えられる。ホスト・システムの共用メモリのこれらの部分により、1つのホスト・システムのルート複合体に関連するエンドポイントは、他のホスト・システムの1つまたは複数の他のルート複合体と通信することができる。

【0069】

図10は、例示的な一実施形態による共用メモリPCIeベース・システムを例示する典型的な図である。図10に図示されている通り、システム1000は、第1のルート複合体(RC1)1012と第1のエンドポイント(EP1)1014とを含むホスト・システム1010を有し、同じくホスト・システム1010の一部として設けることもできる第1の複数ルート認識(MRA)スイッチ1016に関連付けられている。システム1000は、第2のルート複合体(RC2)1022と第2のエンドポイント(EP2)1024とを含む第2のホスト・システム1020を有し、同じくホスト・システム1020の一部として設けることもできる第2の複数ルート認識(MRA)スイッチ1026に関連付けられている。これらのホスト・システム1010および1020のそれぞれは、たとえば、同じマルチルート・ブレード・クラスタ・システム1000内の個別ブレードを表すことができる。代わって、ホスト・システム1010および1020は、完全に別々のコンピューティング・デバイス上に設けることもできる。各ホスト・システム1010および1020はそれ専用の仮想階層(VH)内にある。ホスト・システム1010および1020は、相互に接続され、PCIeファブリック1030の1つまたは複数のMRAスイッチ1016、1026、および1032との通信リンクを介して、他の共用エンドポイントEP3〜EP6 1042〜1044および1052〜1054に接続される。ホスト・システム1010および1020ならびにエンドポイント1042〜1044および1052〜1054に関連する通信リンクは、1つまたは複数の仮想プレーン(VP)に関連付けることができる。

【0070】

どのホスト・システム1010および1020が所与のPCIeトランザクションに関連付けられるかを区別するために、PCIeファブリックではいかなる仮想階層(VH)IDも使用されていない。その代わりに、リンク・ローカル仮想プレーン(VP)IDが使用される。VP IDはリンク・ローカルであるので、RC1のVHは、たとえば、1032と1016との間のリンク上でVP=4を有し、1032と1042との間のリンク上でVP=4を有することができる。換言すれば、VHは、1組のPCIeコンポーネントと、これらのコンポーネントを接続するリンクから構成され、これらのリンクのそれぞれは、所与のトランザクションがどのVHを参照しているかを指定するために使用されるリンク・ローカルVP IDを有する。

【0071】

描かれている例では、目標は、ルート複合体1012、したがって、ルート複合体1012に関連する1つまたは複数のシステム・イメージに関連して実行されるアプリケーションが他のルート複合体に関連するエンドポイント、たとえば、ルート複合体RC2 1022に関連するエンドポイントEP2 1024と通信することを許可することである。したがって、たとえば、EP2 1024は、ルート複合体RC2 1012上で実行されるシステム・イメージによりエンドポイントとして使用することができる。このようにして、ルート複合体と共存しているエンドポイントは、様々な仮想プレーンまたはホスト・システムあるいはその両方のシステム・イメージ全域で共用することができる。その結果として、ノード間で通信するときにInfiniBandまたはイーサネット(登録商標)・スイッチなどの外部ネットワーキング・アダプタおよびスイッチを通過する必要性を省略することにより、高性能のノード間通信、すなわち、ホスト・システム間の通信およびロード・バランシングをシステム・コストの削減と同様に容易にすることができる。

【0072】

ホスト・システム全域でシステム・イメージによってエンドポイントを共用できるようにするために、ホスト・システム1010または1020の一方あるいは個別のホスト・システム1060に設けられたマルチルートPCI構成マネージャ(MR−PCIM)1062は、ルート複合体およびエンドポイントに関する基底および限界アパーチャを確立するようにホスト・システムのメモリ空間1070および1080を初期設定する。MR−PCIM1062は、MRAスイッチ1064ならびにPCIeファブリック1030内の1つまたは複数のMRAスイッチ1032を介してPCIeファブリック1030にアクセスする。

【0073】

MR−PCIM1062は、PCIeファブリック1030に関連するルート複合体およびエンドポイントを識別するために、当技術分野で一般に知られている方法で様々な相互接続スイッチによりPCIeファブリック1030のリンクをトラバースする。しかし、例示的な諸実施形態によって実行されるトラバースでは、ルート複合体(RC)が発見ファブリック・トラバース動作(discovery fabric traversal operation)を実行することを除いて、発見ファブリック・トラバース中にすべてのルート複合体(RC)がエンドポイントとして扱われる。

【0074】

MR−PCIM1062がPCIeファブリックをトラバースするにつれて、MR−PCIM1062はルート複合体とエンドポイントとの間でいくつかのチェックを実行し、所与のルート複合体が所与のエンドポイントに関連付けられているかどうかを判断する。MR−PCIM1062は、結果として得られる情報から、PCIeファブリック1030で使用可能なエンドポイントをそれぞれのルート複合体に結合する1つまたは複数の仮想PCIツリー・データ構造を生成する。同じルート複合体に関連するエンドポイントは、仮想PCIツリー・データ構造内で相互に関連付けられる。

【0075】

MR−PCIM1062がファブリックを発見し構成した後、それぞれのRCにより、それに関連するSR−PCIM1018および1028がVHを発見し構成できるようになる。各SR−PCIM1018、1028は、所与のエンドポイントごとに、それが属すPCIeメモリ・アドレス空間(複数も可)、たとえば、ホスト・システム1のメモリ1070およびホスト・システム2のメモリ1080に関連するPCIeメモリ・アドレス空間(複数も可)内の基底アドレスおよび限界を割り当てる。SR−PCIM1018、1028は、この基底アドレスおよび限界をEPの基底アドレス・レジスタ(BAR)に書き込む。以下により詳細に記載するように、その後、ホスト・システム1010および1020の全域で様々なルート複合体とエンドポイントとの通信を容易にするために、PCIメモリ・アドレス空間(複数も可)のこれらの部分に作業要求および完了メッセージを書き込むことができる。

【0076】

前述の通り、例示的な諸実施形態では、MR−PCIM1062は、PCIeファブリック1030をトラバースするときに、ルート複合体とエンドポイントとの間でいくつかのチェックを実行する。たとえば、MR−PCIM1062は、EPの各機能、物理機能、および仮想機能のPCIe構成空間にアクセスし、PCI規格によって定義されている通り、そのPCIe構成空間はEP内に位置する。また、MR−PCIMは、各エンドポイントに関する重要プロダクト・データ(VPD:Vital Product Data)にアクセスし、たとえば、MR−PCIM1062に結合された不揮発性記憶域(図示せず)内などに、その後の比較のためにVPD情報を保管する。

【0077】

VPDは、システムのハードウェア、ソフトウェア、およびマイクロコード・エレメントなどの項目を明確に定義する情報である。VPDは、管理、資産管理、ならびにPCIデバイスの明確な識別を必要とするいなかるものにも有用な、ベンダ名、部品番号、シリアル番号、その他の詳細な情報を含む、様々な現場交換可能ユニット(FRU:field replaceable unit)に関する情報をシステムに提供する。VPD情報は、典型的には、エンドポイント1014、1024などのPCIデバイス内の記憶装置、たとえば、シリアルEEPROMに常駐する。VPDに関する追加情報は、www.pcisig.comで入手可能なPCIローカル・バス規格、改訂版3.0から入手することができる。

【0078】

MR−PCIM1062は、エンドポイント1014、1024、1042、1044、1052、および1054のそれぞれについてVPD情報を検索し保管した後、どのEPおよびRCが同じハードウェア装置、たとえば、ブレード上に存在するかを識別する。たとえば、MR−PCIM1062は、それがRCおよびEPを保持するハードウェア装置に関連付けられていることを示す共存フィールドを収容している、MRAスイッチ1016、1026、1032のVPD情報にアクセスする。MRAスイッチ1016、1026、1032は、どのEPおよびRCが同じハードウェア装置上に存在するかを判断するために使用できる、RCに割り当てられたVHを保管する。

【0079】

EPが同じホスト上のRCと共存していると判断した後、MR−PCIM1062は、図11および図12に例示されているような1つまたは複数の仮想PCIツリー・データ構造を作成する。図11および図12に図示されている通り、仮想PCIツリー・データ構造は、PCIeファブリック上で使用可能なエンドポイントを各ルート複合体に結合する。

【0080】

図11に図示されている仮想PCIツリー・データ構造では、ユーザによってMR−PCIM1062に対して示された割り当てを介して、エンドポイントEP2 1024、EP4 1044、およびEP5 1052がルート複合体RC1 1012に関連付けられているものと想定されている。上述のVPDマッチングは、EPがRCのホスト上に物理的に存在していることをRCが判断できるようにするためにのみ実行される。これは、RCのアドレス空間における標準的なPCIメモリ・マップ・アドレス指定によりEPがRCにとってアクセス可能であることをRCに知らせるものである。これは、物理的関連付けである。仮想PCIツリー・データ構造では、ユーザが論理的関連付けを作成するためにMR−PCIM1062を必要としていることを示すことにより、このような論理的関連付けが指定される。

【0081】

同様に、図12では、論理的関連付けを指定するユーザ入力ならびにそれぞれのVPD情報およびMR−PCIM1062によって行われた比較を介して、エンドポイントEP1 1014、EP3 1042、およびEP6 1054がルート複合体RC1 1012に関連付けられているものと想定されている。したがって、図11に図示され描かれている例では、エンドポイントEP2 1024は、スイッチ2 1026およびスイッチ1 1016を介して、ルート複合体RC1 1012に関連付けられているかまたは結合されている。エンドポイントEP4 1044およびEP5 1052は、スイッチ3 1032およびスイッチ1 1016を介して、ルート複合体RC1 1012に関連付けられている。図12では、エンドポイントEP1 1014は、スイッチ1 1016およびスイッチ2 1026を介して、ルート複合体RC2 1022に関連付けられているかまたは結合されている。エンドポイントEP3 1042およびEP6 1054は、スイッチ3 1032を介して、ルート複合体RC2 1022に関連付けられている。

【0082】

これらの仮想PCIツリー・データ構造に基づいて、MR−PCIM1062は、それが属すPCIeメモリ・アドレス空間(複数も可)内の基底アドレスおよび限界を各エンドポイントに割り当てる。基底アドレスは、エンドポイントの基底アドレス・レジスタ(BAR)に保管することができる。たとえば、EP1 1014は、2つのPCIeメモリ・アドレス空間1070および1080によりアクセス可能である。ホスト・システム1 1010では、EP1 1014は、ホスト・システムのメモリ1070のアドレス空間によりホスト・システムのプロセッサ(図示せず)からアクセス可能である。ホスト・システム2 1020では、EP1 1014は、PCIバス・メモリ・アドレスによりメモリ・マップ入出力を介してアクセス可能なホスト・システム2のメモリ1080のアドレス空間において、EP1の基底アドレスおよび限界によって定義されたPCIeアパーチャを有する。ホスト・システム1 1010のプロセッサは、たとえば、ホスト・システム2 1020のプロセッサによって認識されたPCIeメモリ・アドレスをホスト・システム1のメモリ・アドレスにマッピングするために、ハイパーバイザ、ルート複合体1012などの仮想化仲介内に設けることができるものなどのメモリ・アドレス変換および保護テーブル(図示せず)を使用することができる。

【0083】

同様に、エンドポイントEP2 1024は、ホスト・システム・メモリ1070および1080のための2つのPCIeメモリ・アドレス空間によりアクセス可能である。ホスト・システム2 1020では、EP2 1024は、そのメモリ1080のためのホスト・システム2の実メモリ・アドレスによりホスト・システム2のプロセッサからアクセス可能である。ホスト・システム1 1010では、EP2 1024は、PCIバス・メモリ・アドレスによりメモリ・マップ入出力としてアクセス可能なホスト・システム1のメモリ1070において、EP2 1024の基底アドレスおよび限界によって定義されたPCIeアパーチャを有する。ホスト・システム2 1020は、ホスト・システム1 1010によって認識されたPCIeメモリ・アドレスをホスト・システム2の実メモリ・アドレスにマッピングするために、メモリ・アドレス変換および保護テーブル(図示せず)を使用することができる。

【0084】

ルート複合体RC1 1012およびRC2 1022のために、ホスト・システム・メモリ1070および1080の同様の部分を初期設定することができる。たとえば、ホスト・システム1 1010では、RC1 1012は、ホスト・システム1のメモリ1070のためのホスト・システム1の実メモリ・アドレスによりホスト・システム1のプロセッサからアクセス可能である。RC1 1012は、ホスト・システム1のPCIバス・メモリ・アドレスにより直接メモリ・アクセス(DMA)入出力を介してアクセス可能なホスト・システム2のメモリ空間においてPCIeアパーチャを有する。ホスト・システム1 1010は、ホスト・システム2 1020によって認識されたPCIeメモリ・アドレスをホスト・システム1の実メモリ・アドレスにマッピングするために、メモリ・アドレス変換および保護テーブル(図示せず)を使用することができる。

【0085】

同様に、ホスト・システム2 1020では、RC2 1022は、メモリ1080のためのホスト・システム2の実メモリ・アドレスによりホスト・システム2のプロセッサからアクセス可能である。RC2 1022は、ホスト・システム2のPCIバス・メモリ・アドレスによりDMA入出力としてアクセス可能なホスト・システム1のメモリ1070においてPCIeアパーチャを有する。ホスト・システム2 1020は、ホスト・システム1 1010によって認識されたPCIeメモリ・アドレスをホスト・システム2の実メモリ・アドレスにマッピングするために、メモリ・アドレス変換および保護テーブル(図示せず)を使用することができる。

【0086】

したがって、例示的な諸実施形態のメカニズムは、1つのエンドポイントが複数のホスト・システム内の2つ以上のルート複合体によってアクセス可能なものになるように、ホスト・システム内のメモリ空間の初期設定を可能にするものである。その場合、様々なエンドポイントに割り当てられたメモリ空間の部分は、そのエンドポイントとの間で要求および完了メッセージを送信するためにルート複合体によって使用することができる。

【0087】

図13は、例示的な一実施形態によりエンドポイントの共用のためのホスト・システムのメモリ・アドレス空間を初期設定するための典型的な動作の概要を示す流れ図である。図13の流れ図の各ブロック、その後に記載されている流れ図、ならびに流れ図内のブロックの組み合わせがコンピュータ・プログラム命令によって実現できることは理解されるであろう。これらのコンピュータ・プログラム命令は、プロセッサまたはその他のプログラマブル・データ処理装置上で実行される命令によって流れ図の1つまたは複数のブロックに指定された機能を実現するための手段が作成されるようにマシンを生産するために、プロセッサまたはその他のプログラマブル・データ処理装置に提供することができる。また、これらのコンピュータ・プログラム命令は、コンピュータ可読メモリまたは記憶媒体に保管された命令によって流れ図の1つまたは複数のブロックに指定された機能を実現する命令手段を含む製品(article of manufacture)が生産されるように特定の方法で機能するようプロセッサまたはその他のプログラマブル・データ処理装置に指示できるコンピュータ可読メモリまたは記憶媒体に保管することもできる。

【0088】

したがって、流れ図のブロックは、指定の機能を実行するための手段の組み合わせ、指定の機能を実行するためのステップの組み合わせ、ならびに指定の機能を実行するためのプログラム命令手段をサポートする。また、これらの流れ図の各ブロックならびに流れ図内のブロックの組み合わせが、指定の機能またはステップを実行する特殊目的ハードウェアベースのコンピュータ・システムによって、または特殊目的ハードウェアとコンピュータ命令の組み合わせによって実現できることは理解されるであろう。

【0089】

図13に図示されている通り、動作は、PCIeファブリックの相互接続スイッチを介してアクセス可能なすべてのリンクをトラバースすることにより、MR−PCIMがPCIeファブリックを発見することから始まる(ステップ1210)。PCIeファブリックの発見中に発見されたエンドポイントおよびルート複合体のそれぞれに関するVPD情報が保管される(ステップ1220)。

【0090】

MR−PCIMは、各エンドポイントに関するVPD情報を各ルート複合体に関するVPD情報と比較して、所与のエンドポイントが所与のルート複合体に関連付けられているかどうかを判断する(ステップ1230)。各比較ごとに、VPD情報がエンドポイントおよびルート複合体に関して一致する場合に、MR−PCIMは対応する共存フィールドを設定する(ステップ1240)。発見されたエンドポイントおよびルート複合体の情報ならびにそれぞれの比較に関する共存フィールドの設定に基づいて、MR−PCIMは1つまたは複数の仮想PCIツリー・データ構造を生成する(ステップ1250)。

【0091】

生成された仮想PCIツリー・データ構造(複数も可)に基づいて、MR−PCIMは、エンドポイントが属す各PCIeメモリ・アドレス空間内の基底アドレスおよび限界を各エンドポイントに割り当てる(ステップ1260)。生成された仮想PCIツリー・データ構造(複数も可)に基づいて、MR−PCIMは、ルート複合体が属す各PCIeメモリ・アドレス空間内の基底アドレスおよび限界を各ルート複合体に割り当てる(ステップ1270)。その後、動作は終了する。

【0092】

エンドポイントがホスト・システム全域のルート複合体によりアクセス可能なものになりうるようにホスト・システムのメモリ・アドレス空間を初期設定すると、その後、これらのメモリ・アドレス空間を使用して、これらのルート複合体に関連するシステム・イメージとそれに対応するアプリケーションがエンドポイントと通信できるようにすることができる。このような通信を容易にする方法の1つは、様々なホスト・システム内のこれらの初期設定済みメモリ・アドレス空間を使用するキューイング・システムを介するものである。このようなキューイング・システムは、作業キュー構造と完了キュー構造とを含むことができる。作業キュー構造と完了キュー構造はいずれも、いくつかのキュー・エレメント(そのキュー構造が作業キュー構造であるか完了キュー構造であるかに応じて、作業キュー・エレメント(WQE)または完了キュー・エレメント(CQE)のいずれか一方)を識別するためのドアベル構造と、キューの始まりに関する基底アドレスと、キューの終わりに関する限界アドレスと、キュー内で次に処理すべきWQEまたはCQEを示すオフセットとを含むことができる。作業キュー構造と完了キュー構造はいずれも、データの送信とデータの受信の両方に使用することができる。

【0093】

図14は、例示的な一実施形態により第1のホスト・システムから第2のホスト・システムに作業キュー・エレメント(WQE)を送信するためのプロセスを例示する典型的なブロック図である。この説明のために、システムは、MRAスイッチ1316および1326も含むことができるPCIeファブリック1330によって接続された複数の共用PCIルート複合体、たとえば、RC1 1312およびRC2 1322とともに、ホスト・システム、たとえば、第1のホスト・システム1310と第2のホスト・システム1320とを備えて確立されるものと想定されている。さらに、ルート複合体RC2 1322とともに第2のホスト・システム1320内に存在するエンドポイント、たとえば、EP2 1324は、PCIeファブリック1330全域で第1のホスト・システム1310のルート複合体RC1 1312とともに共用される予定であり、第2のホスト・システム1320の内部メモリ1380のアドレス空間および第1のホスト・システムのPCIバス・メモリ・アドレス空間にほぼマッピングされるものと想定されている。このシステム構成は、たとえば、図10〜図13に関して前述した初期設定メカニズムを使用することにより、達成することができる。

【0094】

図14に図示されている通り、エンドポイントEP1 1314は、2つのホスト・システム・メモリ1370および1380に関連するメモリ空間を介してアクセス可能である。第1のホスト・システム1310上では、エンドポイントEP1 1314は、第1のホスト・システムのメモリ1370に関する第1のホスト・システムの実メモリ・アドレスを介して第1のホスト・システムのプロセッサによってアクセス可能である。第2のホスト・システム1320上では、エンドポイントEP1 1314は、PCIバス・メモリ・アドレスを介してメモリ・マップ入出力としてアクセス可能な第2のホスト・システムのメモリ1380上のPCIeアパーチャ1382を有する。第1のホスト・システム1310は、メモリ・アドレス変換および保護テーブル(ATPT)1318を使用して、第2のホスト・システム1320によって認識されたPCIeメモリ・アドレスを第1のホスト・システムのメモリ空間1370に関する実メモリ・アドレスにマッピングすることができる。

【0095】

同様に、エンドポイントEP2 1324は、2つのホスト・システム・メモリ空間1370および1380を介してアクセス可能である。第2のホスト・システム1320上では、エンドポイントEP2 1324は、第2のホスト・システムの実メモリ・アドレスおよびメモリ・アドレス空間1380を介して第2のホスト・システムのプロセッサによってアクセス可能である。第1のホスト・システム1310上では、エンドポイントEP2 1324は、PCIバス・メモリ・アドレスを介してメモリ・マップ入出力としてアクセス可能な第1のホスト・システムのメモリ1370上のPCIeアパーチャ1372を有する。第2のホスト・システム1320は、メモリ・アドレス変換および保護テーブル(ATPT)1328を使用して、第1のホスト・システム1310によって認識されたPCIeメモリ・アドレスを第2のホスト・システムのメモリ空間1380のメモリ・アドレスにマッピングすることができる。

【0096】

作業キュー構造1374は、いくつかのWQEを渡すために使用されるドアベル構造1375と、キューの始まりに関する基底アドレスと、キューの終わりに関する限界アドレスと、作業キュー内で次に処理すべきWQEを示すオフセットとを含むことができる。同様に、完了キュー構造1376は、いくつかのCQEを渡すために使用されるドアベル構造1377と、キューの始まりに関する基底アドレスと、キューの終わりに関する限界アドレスと、完了キュー内で次に処理すべきCQEを示すオフセットとを含むことができる。

【0097】

第1のホスト・システム1310から第2のホスト・システム1320にWQEを送信するために、第1のホスト・システム1310は、1つまたは複数のWQEをその送信作業キュー1374に挿入することによってプロセスを開始する。各WQEはデータ・セグメントのリストを収容しており、各データ・セグメントは、いずれも第2のホスト・システムのPCIeメモリ・バス・アドレス空間内にあって、同じくアドレス変換および保護テーブル(ATPT)を介して第1のホスト・システムのメモリ空間1370内の実メモリ・アドレスにマッピングされる、基底アドレスと限界アドレスとを含む。

【0098】

次に、第1のホスト・システム1310は、送信中のいくつかのWQEをドアベル構造1375に関するエンドポイントEP2のPCIeアドレスに書き込む。このドアベル構造に関するアドレスは、ATPTを介して第1のホスト・システムのPCIeメモリ・バス・アドレス空間にマッピングされ、第2のホスト・システムのメモリ空間1380内の実メモリ・アドレスにもマッピングされる。ドアベル書き込み動作が完了すると、第2のホスト・システム1320のRCは、ポーリングするか、または割り込みを取得してからポーリングして、第1のホスト・システムの実メモリ・アドレス空間1380を介してドアベル構造1375を検索する。すなわち、第2のホスト・システム1320のRCは、ドアベル構造1375に関するアドレスを定期的にポーリングして、新しいWQEを処理すべきかどうかを判断するように構成することができる。代わって、第1のホスト・システム1310によるドアベル構造1375の設定により、第2のホスト・システム1320への割り込みを生成して、処理のために使用可能な新しいWQEを第2のホスト・システム1320のRCに通知することができる。次に、第2のホスト・システム1320のRCは、新しいWQEの情報についてドアベル構造1375をポーリングし、それに応じて新しいWQEを処理することができる。

【0099】

次に、エンドポイントEP2 1324は、ルート複合体RC1 1312に対するPCIe DMA動作を実行して、WQEを検索する。各DMA動作は、第1のホスト・システムのPCIeメモリ・バス・アドレス空間を使用し、その実メモり・アドレス空間を介して第2のホスト・システム1320上でアクセス可能な第2のホスト・システムのメモリ1380内にDMA動作の結果を入れる。したがって、ホスト・システム1310および1320の初期設定済み共用メモリを使用すると、異なるホスト・システム1310および1320内のルート複合体とエンドポイントとの間の作業キュー・エレメントの通信が容易になる。

【0100】

図15は、例示的な一実施形態により第2のホスト・システム1320から第1のホスト・システム1310に完了キュー・エレメント(CQE)を送信するためのプロセスを例示する典型的なブロック図である。図15に図示されている通り、1つのWQEまたはWQEグループに関連する作業が完了すると、エンドポイントEP2 1324は、ルート複合体RC1 1312に対する1つまたは複数のPCIe DMA動作を実行して、1つまたは複数のCQEをルート複合体RC1 1312に送信する。RC1 1312がポーリングするかまたはCQEが使用可能であることを示す割り込みを待つことができると言う意味で、ドアベルを使用することができる。

【0101】

各DMA動作は、第1のホスト・システムのPCIeメモリ・バス・アドレス空間を使用し、その実メモり・アドレス空間を介して第1のホスト・システム1310上でアクセス可能な第1のホスト・システムのメモリ1370内に結果を入れる。その結果は、好ましくは、メモリ1370のDMAアドレス可能部分に保管され、そのDMAアドレス可能部分は、使用される特定のOS次第でメモり1370内の異なる位置にある。

【0102】

図16は、例示的な一実施形態により第1のホスト・システムのルート複合体と第2のホスト・システムに関連するエンドポイントとの間でWQEを伝送するための典型的な動作の概要を示す典型的な流れ図である。図16に図示されている通り、動作は、第1のホスト・システムが1つまたは複数のWQEをその送信作業キューに挿入することから始まる(ステップ1510)。次に、第1のホスト・システムは、送信中のいくつかのWQEをドアベル構造に関するターゲット・エンドポイントのPCIeアドレスに書き込む(ステップ1520)。ドアベル書き込み動作が完了すると、第2のホスト・システムは、ポーリングするか、または割り込みを取得してからポーリングして、第1のホスト・システムの実メモリ・アドレス空間を介してドアベル構造を検索する(1530)。

【0103】

次に、ターゲット・エンドポイントは、第1のホスト・システムのルート複合体に対するPCIe DMA動作を実行して、WQEを検索する(ステップ1540)。次に、ターゲット・エンドポイントは、第2のホスト・システムのメモリ内にDMA動作の結果を入れる(ステップ1550)。その後、動作は終了する。

【0104】

図17は、例示的な一実施形態により第2のホスト・システムのエンドポイントから第1のホスト・システムのルート複合体にCQEを伝送するための典型的な動作の概要を示す典型的な流れ図である。動作は、エンドポイントがそのエンドポイントにサブミットされた1つまたは複数のWQEに関連する処理作業を完了することから始まる(ステップ1610)。次に、エンドポイントは、1つまたは複数のWQEが受信されたホスト・システムに関連するルート複合体に対する1つまたは複数のPCIe DMA動作を実行して、1つまたは複数のCQEをルート複合体に送信する(ステップ1620)。DMA動作の結果は、第1のホスト・システムのメモリ内に置かれる(ステップ1630)。その後、動作は終了する。

【0105】

したがって、例示的な諸実施形態の共用メモリを使用して、それにより異なるホスト・システム上のルート複合体とエンドポイントとの間で作業要求および完了メッセージを交換できるキューイング構造を提供することができる。したがって、ルート複合体は、そのルート複合体が設けられているホスト・システムとは異なるホスト・システム上のエンドポイントと通信することができ、その逆も同様である。

【0106】

本明細書の例示的な諸実施形態によれば、例示的な諸実施形態の共用メモリを使用して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信するために、トランザクション指向プロトコルを確立することができる。このトランザクション指向プロトコルは、以下に記載するように、データをプッシュまたはプルするために、様々なエレメント、たとえば、ルート複合体またはエンドポイントによって実行すべき一連のトランザクションを指定する。

【0107】

図14に戻ると、WQEがエンドポイントに提供され、CQEがルート複合体に返される方法に関する上記の説明は、プルプルプッシュ(pull-pull-push)プロトコルの一例である。すなわち、第2のホスト・システム1320のエンドポイントEP2 1324は、第1のホスト・システム1310によるドアベル構造1375の書き込みに応答して、PCIe DMA動作を使用して、第1のホスト・システムの共用メモリ1370からWQEをプルする。これらのWQEは、実行すべき動作に関する「コマンド」を提供する。WQEに保管されたセグメント情報に基づいて、第2のホスト・システム1320のエンドポイントEP2 1324は、第1のホスト・システムの共用メモリ1370内の作業キュー構造1374から対応するデータをプルする。WQEに対応する作業が完了すると、第2のホスト・システム1320のエンドポイントEP2 1324は、1つまたは複数のPCIe DMA動作を使用して、第1のホスト・システム1310のルート複合体RC1 1312にCQEをプッシュする。したがって、上述の図14の例では、プルプルプッシュ・トランザクション・プロトコルが使用される。

【0108】

異なるトランザクション・プロトコルを確立するために、その他のプル・トランザクションとプッシュ・トランザクションの組み合わせが可能である。図18は、同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信を実行するために使用可能なトランザクションの組み合わせとして可能な様々なものを例示する典型的な表である。図18に図示されている通り、例示的な諸実施形態のメカニズムとともにプル・トランザクションとプッシュ・トランザクションの任意の組み合わせを使用して、例示的な諸実施形態の共用メモリを使用するためのトランザクション・プロトコルを確立することができる。

【0109】

ルート複合体とエンドポイントは、選択されたプロトコルを施行する役割を担う。たとえば、OSシステム・スタックおよびエンドポイントは、前述のような選択されたトランザクション・プロトコルの一部として、データをプルしプッシュするための動作を実行する。使用すべきプロトコルの選択は、エンドポイントによって使用される特定のPCIeファブリック、たとえば、InfiniBandまたはイーサネット(登録商標)・ファブリックに依存する。プロトコルの特殊性は、プログラミング上の選択、たとえば、ポーリングを使用するか、割り込み処理を使用するか、ポーリングと割り込み処理の組み合わせを使用するかに応じて決定することができる。

【0110】

例示的な諸実施形態のメカニズムをさらに使用して、上述の共用メモリを介して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間のソケット・プロトコル・ベースの通信をサポートすることができる。このようなソケット・プロトコルは、常時接続(constant connection)が存在する予定であるときに使用することができる。ソケット・プロトコルを使用すべきか、または上述のプッシュプル・トランザクションなどのトランザクションベースのプロトコルを使用すべきかに関する判断は、所望の効率および信頼性に基づいて行うことができる。

【0111】

ソケット・プロトコルでは、ホスト・システム内の作業キューを使用して、着信ソケット初期設定要求を聴取することができる。すなわち、第2のホスト・システムとのソケット通信接続を確立することを希望する第1のホスト・システムは、その作業キュー内にソケット初期設定要求WQEを生成することができ、そのソケット初期設定要求WQEが処理のために使用可能であることを第2のホスト・システムに通知する。その後、第2のホスト・システムは、その要求を受諾または拒否することができる。第2のホスト・システムがその要求を受諾する場合、そのホスト・システムは、第1および第2のホスト・システム間でソケット・ベースの通信を実行する際に第1のホスト・システムによって使用するためのソケットのパラメータのうちの後半部分を返す。このような通信は、たとえば、ホスト・システム間のプル・トランザクションまたはプッシュ・トランザクションあるいはその両方を伴う可能性がある。

【0112】

図19は、例示的な一実施形態によりソケットを確立し、第1のホスト・システムと第2のホスト・システムとの間でソケット・ベースの通信を実行するためのプロセスを例示する典型的なブロック図である。例示的な諸実施形態のソケット・ベースの実現例では、ホスト・システム、たとえば、ホスト・システム1810上のEP2 1824などのエンドポイントは、受信バッファ1876と、バッファ・フル・フラグ(buffer full flag)1877と、ドアベル構造1878とを収容している。バッファ・フル・フラグ1877およびドアベル構造1878は、イベントが発生したことを示すように働くメモリ内のアドレスを含むことができる。送信側ホスト・システム、たとえば、ホスト・システム1810は、接続エンドポイント、たとえば、エンドポイントEP2 1824に対応する、送信側ホスト・システムのルート複合体RC1 1812によってアクセス可能な受信側ホスト・システム1820のメモリ1870内のPCIeアパーチャ1872を介してドアベル構造1878に書き込む。

【0113】

前述の通り、同じかまたは異なるホスト・システム上の複数のルート複合体全域のエンドポイントの共用を容易にするためのホスト・システムの共用メモリの初期設定中に、仮想PCIツリー・データ構造を生成するために、発見されたルート複合体およびエンドポイントのそれぞれについて重要プロダクト・データ(VPD)情報が読み取られる。このVPD情報は、特定のルート複合体またはエンドポイントがPCIeによりソケットをサポートするかどうかを示すフィールドを含むことができる。この情報を使用して、例示的な一実施形態によるソケット・ベースの通信のためにどのエンドポイントとのソケットを確立できるかを識別することができる。

【0114】

したがって、初期設定中に、第1のホスト・システム1810は、たとえば、エンドポイントEP2 1824に関するVPD内のベンダ固有フィールドにより、エンドポイントEP2 1824がPCIeによりソケットをサポートすると判断することができ、EP内のVPD情報は上記で前述したMR−PCIMならびにホスト・システムそのものによりアクセス可能である。同様に、第2のホスト・システム1820は、エンドポイントEP1 1814に関するVPD情報内のそのベンダ固有フィールドにより、エンドポイントEP1 1814がPCIeによりソケットをサポートすると判断することができる。

【0115】

各ホスト・システム1810および1820は、着信ソケット初期設定要求を聴取するために使用する作業キュー(WQ)1850および1860を有する。たとえば、第2のホスト・システム1820、すなわち、受信側ホスト・システムは、ブロックしてソケット初期設定要求がその作業キュー1860上に表面化するのを待つか、エンドポイントEP2 1824のドアベル構造1878をポーリングして、ソケット初期設定要求が到着したかどうかを判断する。ソケット初期設定要求は、そのソケットのうち第1のホスト・システム分の半分に使用するための作業キュー1850への基底、限界、および開始オフセットを収容している。

【0116】

第1のホスト・システム1810、すなわち、送信側ホスト・システムは、その作業キュー1850内にソケット初期設定要求を生成することができ、ソケット初期設定要求WQEが使用可能であることを示すドアベル構造1878をエンドポイントEP2 1824に書き込むことができる。ドアベル構造1878内のデータを検索すると、第2のホスト・システムのエンドポイントEP2 1824は、PCIe DMA動作を実行し、エンドポイントEP2 1824によってアクセス可能なルート複合体RC1のPCIeバス・メモリ・アドレスを使用して第1のホスト・システムの作業キュー1850からソケット初期設定要求を検索することができる。

【0117】

次に、第2のホスト・システム1820は、ソケット初期設定要求を解析し、アプリケーションまたはオペレーティング・システム固有の方法でソケット初期設定要求を受諾するか拒否するかを決定することができる。第2のホスト・システム1820がソケット初期設定要求を拒否する場合、第2のホスト・システム1820は、第1のホスト・システムのルート複合体RC1 1812に非接続応答PCIe DMAを送信し、所望であれば、第1のホスト・システムのルート複合体RC1 1812に割り込む。

【0118】

第2のホスト・システム1820がソケット初期設定要求を受諾する場合、エンドポイントEP2 1824は、第1のホスト・システムのルート複合体RC1 1812に対するPCIe DMA動作を実行し、ソケットのパラメータの後半部分、すなわち、そのソケットのうち第2のホスト・システム分の半分に使用するための作業キュー1860への基底、限界、および開始オフセットを示す。

【0119】

ソケットが上述のように初期設定されると、プル・トランザクションまたはプッシュ・トランザクションという2通りの方法の一方で、確立されたソケットを使用して送信/受信動作を実行することができる。プル・トランザクションでは、第1のホスト・システム1810のルート複合体RC1 1812は、その作業キュー1850にWQEを書き込み、次にルート複合体RC1 1812のPCIeバス・メモリ・アドレス空間によりアクセス可能なエンドポイントEP2 1823に関連するドアベル構造1878に書き込むことにより、送信動作を実行する。ドアベル書き込み動作が完了すると、第2のホスト・システム1820は、ポーリングするか、または割り込みを取得してからポーリングして、第2のホスト・システムの実メモリ・アドレス空間を介してドアベル構造1878を検索する。次に、エンドポイントEP2 1824は、ルート複合体RC1 1812に対するPCIe DMA動作を実行して、送信動作に関連するWQEを検索する。このPCIe DMA動作は、第1のホスト・システムのPCIeメモリ・バス・アドレス空間を使用し、第2のホスト・システムの実メモり・アドレス空間を介してアクセス可能な第2のホスト・システム上のメモリ1880内に結果を入れる。次に、第2のホスト・システム1820は、WQEに指定され、送信動作に関連するデータ・セグメントを検索する。

【0120】

第2のホスト・システムがWQEで要求された作業を完了すると、エンドポイントEP2 1824は、ルート複合体RC1 1812に対するPCIe DMA動作を実行して、送信動作が完了したことを通知するCQEをプッシュする。このDMA動作は、第1のホスト・システムのPCIeメモリ・バス・アドレス空間を使用し、第1のホスト・システムの実メモり・アドレス空間を介してアクセス可能な第1のホスト・システム1810上のメモリ1870内に結果を入れる。

【0121】

プッシュ・トランザクションの場合、ルート複合体RC2 1822は、エンドポイントEP1 1814に関するドアベル構造1888に書き込み、それが使用可能な状態で有する受信WQEの数を示す。エンドポイントEP1 1814が送信すべきデータを有する場合、エンドポイントEP1 1814はチェックを行って、エンドポイントEP1 1814がルート複合体RC2 1822の作業キュー1860上で使用可能な任意の受信WQEを有するかどうかを判断する。使用可能な受信WQEがまったくない場合、ルート複合体RC1 1812はエンドポイントEP2のバッファ・フル・フラグ1887に書き込んで、第1のホスト・システム1810がソケット上で送信すべきデータを有し、第2のホスト・システム1820がそのソケットのために受信WQEを介していくつかのバッファを通知する必要があることを示す。

【0122】

使用可能な受信WQEがある場合、第2のエンドポイントEP2 1824は、ルート複合体RC1 1812に対するPCIe DMA動作を実行して、ルート複合体RC1の作業キュー1850上で次に使用可能なWQEを検索する。このDMA動作は、第1のホスト・システムのPCIeメモリ・バス・アドレス空間を使用し、第2のホスト・システムの実メモり・アドレス空間を介してアクセス可能な第2のホスト・システム1820上のメモリ1880内に結果を入れる。次に、第2のホスト・システム1820は、受信WQEで渡されたデータ・セグメントにそのデータを送信する。

【0123】

第2のホスト・システム1820が要求された作業を完了すると、エンドポイントEP2 1824は、ルート複合体RC1 1812に対するPCIe DMA動作を実行して、送信動作が完了したことを通知するCQEをプッシュする。このDMA動作は、第1のホスト・システムのPCIeメモリ・バス・アドレス空間を使用し、第1のホスト・システムの実メモり・アドレス空間を介してアクセス可能な第1のホスト・システム1810上のメモリ内に結果を入れる。

【0124】

図20は、例示的な一実施形態によりソケット・ベースの通信接続を使用してプル・トランザクションを実行するための典型的な動作の概要を示す流れ図である。動作は、第1のホスト・システムのルート複合体がその作業キューにWQEを書き込み(ステップ1910)、次にターゲット・エンドポイントに関連するドアベル構造に書き込むことから始まる(ステップ1920)。ドアベル書き込み動作が完了すると、第2のホスト・システムは、ポーリングするか、または割り込みを取得してからポーリングして、第2のホスト・システムの実メモリ・アドレス空間を介してドアベルを検索する(ステップ1930)。

【0125】

次に、ターゲット・エンドポイントは、第1のホスト・システムのルート複合体に対するPCIe DMA動作を実行して、送信動作に関連するWQEを検索する(ステップ1940)。ターゲット・エンドポイントは、第2のホスト・システム上のメモリ内にPCIe DMA動作の結果を入れる(ステップ1950)。次に、第2のホスト・システムは、WQEに指定され、送信動作に関連するデータ・セグメントを検索する(ステップ1960)。

【0126】

第2のホスト・システムがWQEで要求された作業を完了したことに応答して、ターゲット・エンドポイントは、第1のホスト・システムのルート複合体に対するPCIe DMA動作を実行して、送信動作が完了したことを通知するCQEをプッシュする(ステップ1980)。第1のホスト・システムのルート複合体は、第1のホスト・システムのメモリ内にPCIe DMA動作の結果を入れる(ステップ1990)。その後、動作は終了する。

【0127】

図21は、例示的な一実施形態によりソケット・ベースの通信接続を使用してプッシュ・トランザクションを実行するための典型的な動作の概要を示す流れ図である。第2のホスト・システムのルート複合体は、第1のホスト・システムのエンドポイントに関するドアベル構造に書き込み、そのルート複合体が使用可能な状態で有する受信WQEの数を示す(ステップ2010)。第1のホスト・システムのエンドポイントが送信すべきデータを有することに応答して(ステップ2020)、第1のホスト・システムのエンドポイントはチェックを行って、エンドポイントが第2のホスト・システムのルート複合体の作業キュー上で使用可能な任意の受信WQEを有するかどうかを判断する(ステップ2030)。使用可能な受信WQEがまったくない場合、第1のホスト・システムのルート複合体は第2のホスト・システムの第2のエンドポイントのバッファ・フル・フラグに書き込んで、第1のホスト・システムがソケット上で送信すべきデータを有し、第2のホスト・システムがそのソケットのために受信WQEを介していくつかのバッファを通知する必要があることを示す(ステップ2040)。次に、動作はステップ2030に戻る。

【0128】

使用可能な受信WQEがある場合、第2のエンドポイントは、第1のホスト・システムのルート複合体に対するPCIe DMA動作を実行して、第1のホスト・システムのルート複合体の作業キュー上で次に使用可能なWQEを検索する(ステップ2050)。第2のエンドポイントは、第2のホスト・システムのメモリ内にPCIe DMA動作の結果を入れる(ステップ2060)。次に、第2のホスト・システムは、受信WQEで渡されたデータ・セグメントにそのデータを送信する(ステップ2070)。

【0129】

第2のホスト・システムが要求された作業を完了すると、第2のエンドポイントは、第1のホスト・システムのルート複合体に対するPCIe DMA動作を実行して、送信動作が完了したことを通知するCQEをプッシュする(ステップ2080)。第2のエンドポイントは、第1のホスト・システム上のメモリ内にPCIe DMA動作の結果を入れる(ステップ2090)。その後、動作は終了する。

【0130】

上記で論じた通り、マルチルート・システムのエンドポイントは、1つまたは複数の関連仮想機能を有する1つまたは複数の物理機能をサポートすることができる。例示的な諸実施形態のメカニズムは、同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間の通信を可能にすることに加えて、エンドポイントの物理機能および仮想機能を管理するためのメカニズムも提供する。例示的な諸実施形態のメカニズムによって提供される機能の1つは、同じエンドポイント上の1つの物理機能から他の物理機能に単一ルート・ステートレス仮想機能およびそれに関連するアプリケーションを移行する能力を提供する。この移行機能は、システム管理の領域でワークロード・バランシング機能に関する需要の拡大を満足するために重要なものである。

【0131】

VFおよびそれに関連するアプリケーション(複数も可)(動作すべきVFに依存するアプリケーションである)を移行することにより、より効率的な環境で動作を続行するために種々のリソースをリクルートすることができる。たとえば、ワークロード・バランシングでは、例示的な諸実施形態のメカニズムを使用してイーサネット(登録商標)VFおよびそれに関連する従属アプリケーションを移動し、異なるSIまたは同等EPと完全に関連付けることができる異なるPF上で使用可能なより高速の(たとえば、あまり輻輳していない)接続を利用することができる。

【0132】

図22および図23は、例示的な一実施形態により同じエンドポイント、たとえば、PCIeアダプタ上の1つの物理機能から他の物理機能への仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。図22に図示されている通り、システム・イメージ(SI)2105に関連するアプリケーション2110は、エレメント2110を2120と接続する点線によって表されている通り、仮想機能(VF)2120に関連付けられている。ソフトウェア仲介2115は、SR−PCIM2100からの情報に基づいて、システム管理者または同等の管理権限に対して移行シナリオを描くことができる。これは、システム管理インターフェース(描写せず)を介して移行のためのターゲットになりうるPCIeファブリック内で使用可能な同等のVFを示すことを含むことができるが、これに限定されない。

【0133】

SR−PCIM2100によって描くことができる特定の移行シナリオは、たとえば、特定のVFを移行可能であるかどうかを判断するためにSR−PCIMがアクセスするVF移行機能ビットに基づいて、決定することができる。SR−PCIM2100からのこの情報に基づいて、SWI2115は、このデータを解釈し、管理コンソールまたはエンティティを介してユーザにとって使用可能なVF移行シナリオに変換することができる。これらの移行シナリオは、問題のコンポーネントの設計に非常に依存したものになる。たとえば、イーサネット(登録商標)・アダプタを移行するために、OSは、それを構成解除する(de-configure)ことができなければならない可能性がある。この機能がOSによって提供されない場合、管理ユーティリティはこのようなシナリオを描くことができないであろう。換言すれば、管理ユーティリティは、移行シナリオを描くためにそれが後で使用するコンポーネント(システム・イメージ・タイプ、ハードウェアなど)の知識を維持する。この情報は、VF移行機能ビットに保管された移行可能性(migratability)情報に加えて、移行に関するどのシナリオが選択のために使用可能であるかを識別する。

【0134】

システム管理者は、所望のVF2120および関連アプリケーション2110を移行するためのプロセスを開始する。たとえば、管理ソフトウェア(描写せず)は、ホスト・システムおよびPCIeファブリック上の使用可能なリソース間で移行可能なVFおよびそれに関連するアプリケーションをグラフィカル・ユーザ・インターフェース・ディスプレイなどにエンティティとして描くことができる。管理ソフトウェアは、インターナショナル・ビジネス・マシーンズ社から入手可能なHMCなどのハードウェア管理コンソール上に、あるいはファームウェア(たとえば、ソフトウェア仲介またはハイパーバイザ)と対話するように設計されたシステム実行ソフトウェアの一部または任意のその他のコンソール内に、ならびにハードウェア・リソースの制御機能に存在することができる。

【0135】

ホスト・システム上で実行されるソフトウェア仲介(SWI)2115は、追加の機能を可能にする抽象化層(layer of abstraction)を作成するために管理アプリケーションとハードウェアとの間で使用される任意のタイプのファームウェアまたはソフトウェア・コードにすることができ、移行すべきVF2120または柔軟性のためにすべての未解決の要求を完了しなければならないという要求をSI−A2105に送信することができる。たとえば、SI−A2105およびSWI2115は、それにより両者が通信するアプリケーション・プログラム・インターフェース(API:applicationprogram interface)を有することができる。SI−A2105は、VF2120を使用して任意のアプリケーション2110を休止または停止することにより、要求に応答することができる。SI−A2105は、VF2120に対するすべての未解決の要求が完了されることを保証することができる。本質的に、SI−A2105はチェックを行って、いかなる要求も保留中ではないことと、すべてのトランザクションが完了していることを表す状態にすべてのキューが入っていることを確認する。たとえば、これを実行するための方法の1つは、すべてのWQEが対応するCQEを有することをチェックすることである。

【0136】

次に、SI−A2105は、SI−AによるVF2120の使用を事実上停止して、VF2120のその論理表現を構成解除することができる。これは、たとえば、SI−A2105上のVF2120用のデバイス・ドライバ(図示せず)によって実行可能な動作である。次に、SI−A2105は、すべての要求が完了していることと、VF2120を除去できることをSWI2115に通知することができる。次に、SWI2115は、SI−A2105からVF2120を除去することができる。これにより、VF2120がSI−A2105によって検出不能かつ構成不能なものになる。次に、SWI2115は、エンドポイントの構成空間内のVFの表現をクリアすることにより、ターゲット物理機能(PF)2135からVF2120を切り離すことができる。

【0137】

次に、図23を参照すると、SWI2115は、ターゲットVF2145をそのPF2140に接続することができる。次に、SWI2115は、構成のためにVF2145をSI−A2105にとって使用可能なものにすることができ、VF2145を構成するようSI−A2105に指示する。たとえば、SWI2115は、新しいデバイス、たとえば、新しいエンドポイントであるように見える可能性のあるVF2145を含むよう、ファームウェア内のSI−Aのデバイス・ツリーを更新する。この新しいエンドポイントまたはVF2145は、OS内のその論理表現がファームウェア・コードによってOSに提示されたSI−Aのデバイス・ツリー内でそれを検出するデバイス・ドライバに依存する任意のタイプのエンドポイント・デバイスにすることができる。新しいデバイス、たとえば、VF2145に関するSI−Aのデバイス・ツリー内に1つの項目が存在すると、そのデバイス用のデバイス・ドライバは、新しいデバイスを検出し構成することになる。

【0138】

たとえば、デバイス・ドライバを使用して、SI−A2105がVF2145を構成すると、関連アプリケーション2110は、VF2145を使用することができる可能性がある。次に、SWI2115は、移行を完了する関連アプリケーション2110を開始するよう、SI−A2105に指示することができる。その結果として、アプリケーション2110とVF2120は、点線によって表される通り、依然として関連付けられているが、VF2120は、その時点でPF2140に関連付けられるように、PF2135との関連付けからすでに移行されている。

【0139】

図24および図25は、例示的な一実施形態により1つのエンドポイント、たとえば、PCIeアダプタから他のエンドポイントへの仮想機能(VF)およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。1つのエンドポイントから他のエンドポイントへのVFのステートレス移行に関する動作は、図22および図23に関して上述したものと同様である。図22および図23の動作と図24〜図25の動作との主な違いは、VFが同じエンドポイント内の異なる物理機能にのみ関連付けられるのではなく、VFがまったく異なるエンドポイント内に置かれることである。

【0140】

図24に図示されている通り、システム・イメージ(SI)2205に関連するアプリケーション2210は、エレメント2210を2220と接続する点線によって表されている通り、仮想機能(VF)2220に関連付けられている。SR−PCIM2200は、システム管理者または同等の管理権限に対して移行シナリオを描く。これは、システム管理インターフェース(描写せず)による移行のためのターゲットになりうるPCIeファブリック内で使用可能な同等のVFを示すことを含むことができるが、これに限定されない。

【0141】

システム管理者は、所望のVF2220および関連アプリケーション2210を移行するためのプロセスを開始する。たとえば、管理ソフトウェア(描写せず)は、管理コンソールまたはエンティティのグラフィカル・ユーザ・インターフェース・ディスプレイ内などに、ホスト・システムおよびPCIeファブリック上の使用可能なリソース間で移行可能なエンティティとしてVFおよびそれに関連するアプリケーションを例示することができる。ホスト・システム上で実行されるソフトウェア仲介(SWI)2215は、移行すべきVF2220のためにすべての未解決の要求を完了しなければならないという要求をSI−A2205に送信することができる。たとえば、SI−A2205およびSWI2215は、それにより両者が通信するアプリケーション・プログラム・インターフェース(API)を有することができる。SI−A2205は、VF2220を使用して任意のアプリケーション2210を休止または停止することにより、要求に応答することができる。SI−A2205は、VF2220に対するすべての未解決の要求が完了されることを保証することができる。

【0142】

次に、SI−A2205は、SI−AによるVF2220の使用を事実上停止して、VF2220のその論理表現を構成解除することができる。これは、たとえば、SI−A2205上のVF2220用のデバイス・ドライバ(図示せず)によって実行可能な動作である。次に、SI−A2205は、すべての要求が完了していることと、VF2220を除去できることをSWI2215に通知することができる。次に、SWI2215は、SI−A2205からVF2220を除去することができる。これにより、VF2220がSI−A2205によって検出不能かつ構成不能なものになる。次に、SWI2215は、エンドポイントの構成空間内のVFの表現をクリアすることにより、ターゲット物理機能(PF)2235からVF2220を切り離すことができる。

【0143】

次に、図25を参照すると、SWI2215は、VF2220(その時点でVF2245)が元々関連付けられていたPF2235とはまったく異なるエンドポイント内にあるそのPF2240にターゲットVF2245を接続することができる。次に、SWI2215は、構成のためにVF2245をSI−A2205にとって使用可能なものにすることができ、VF2245を構成するようSI−A2205に指示する。たとえば、SWI2215は、新しいデバイスを含むよう、ファームウェア内のSI−Aのデバイス・ツリーを更新する。SI−A2205は、たとえば、そのタイプが問題のデバイスまたは機能の特定の特性に依存することになるデバイス・ドライバを使用して、VF2245を構成することができる。次に、関連アプリケーション2210は、VF2245を使用することができる可能性がある。次に、SWI2215は、移行を完了する関連アプリケーション2210を開始するよう、SI−A2205に指示することができる。その結果として、アプリケーション2210とVF2220は、点線によって表される通り、依然として関連付けられているが、VF2220は、PF2235との関連付けから異なるエンドポイント内のPF2240に関連付けられるように移行されている。

【0144】

1つのシステム・イメージから他のシステム・イメージに仮想機能を移行するために同様の動作を実行することができる。図26および図27は、例示的な一実施形態により1つのシステム・イメージから他のシステム・イメージへの仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。図26に図示されている通り、移行すべきVF2320をターゲットとする動作を停止するための動作は、本質的に、図22および図24に関して前述したものと同じである。VF2320に関連するアプリケーション2310が停止され、VF2320をターゲットとする動作が完了すると、SI−A2305は、VF2320のその論理表現を構成解除し、すべての要求が完了しており、VF2320を除去できることをSWI2315に通知する。

【0145】

VF2320に関してSIの変更を実行する予定である場合、SWI2315は、関連のPF2335からVF2320を切り離し、ターゲットPF2340にVF2345を接続する。ターゲットPF2340は、同じかまたは異なるエンドポイント上に位置することができる。SWI2315は、構成のためにVF2345をターゲットSI、たとえば、SI−B2350にとって使用可能なものにし、VF2345を構成するようターゲットSI2350に指示する。ターゲットSI2350は、その時点でSI−B2350に関連する関連アプリケーション2310による使用のために事実上使用可能なものにして、VF2345を構成する。SWI2315は、新しいVF2345上のリソースを使用するために関連アプリケーションを開始するよう、ターゲットSI2350に通知する。

【0146】

図28は、例示的な一実施形態により仮想機能を移行するための典型的な動作の概要を示す流れ図である。図28に図示されている通り、動作は、ユーザが移行すべきVFとVFに関するターゲット宛先を指定することから始まる(ステップ2410)。ホスト・システム上で実行されるSWIは、VFを移行するためにVFに対するすべての未解決の要求を完了しなければならないという要求をSIに送信する(ステップ2420)。SIは、VFを使用する任意のアプリケーションを休止または停止し(ステップ2430)、VFに対するすべての未解決の要求が完了していることを保証する(ステップ2440)。次に、SIは、VFのその論理表現を構成解除する(ステップ2450)。SIは、すべての要求が完了していることと、VFを除去できることをSWIに通知する(ステップ2460)。

【0147】

次に、SWIは、SIからVFを除去し、関連のPFからVFを切り離す(ステップ2470)。次に、SWIは、同じかまたは異なるエンドポイント内にある可能性のあるターゲットPFにVFを接続し、同じかまたは異なるシステム・イメージに関連付けることができる(ステップ2480)。次に、SWIは、VFを構成するよう、VFがその時点で関連付けられているSIに指示し、それにより、それを関連アプリケーションによる使用のために使用可能なものにする(ステップ2490)。SWIは、新しいVF上のリソースを使用するために関連アプリケーションを開始するようSIに指示する(ステップ2495)。その後、動作は終了する。

【0148】

したがって、例示的な諸実施形態のメカニズムでは、同じエンドポイント内で、異なるエンドポイント間で、ならびに同じかまたは異なるエンドポイント上の異なるシステム・イメージ間で、仮想機能を移行することができる。このような移行により、様々なロード・バランシング動作を実行することが可能になる。その上、このような移行により、仮想機能の効率的な動作に対してより役立つ動作環境に仮想機能を移動することができる。

【0149】

したがって、概略が示されている例示的な諸実施形態は、同じルート複合体内または複数のルート複合体(RC)全域の複数のシステム・イメージ(SI)間でエンドポイント、たとえば、PCIe入出力アダプタを同時に共用するためのメカニズムを提供する。その上、例示的な諸実施形態のメカニズムは、キュー・ベースの通信、プッシュプル・ベースのプロトコル通信、およびソケット・ベースの通信を使用する能力をサポートする。さらに、例示的な諸実施形態は、仮想機能およびそれに関連するアプリケーション・インスタンスを同じかまたは異なるエンドポイント内の1つの物理機能から他の物理機能にならびに1つのシステム・イメージから他のシステム・イメージに移行するためのメカニズムを提供する。

【0150】

これらのメカニズムに加えて、例示的な諸実施形態は、実行中のマルチルートPCIeファブリック内への新しいコンポーネントのホット・プラグ/除去を実行するための機能をさらに提供する。これらのメカニズムにより、たとえば、ルート複合体を実行中のPCIeファブリックにホット・プラグするかまたはそこから除去することができる。たとえば、ブレードはブレード・シャーシにホット・プラグすることができ、それに関連するルート複合体は既存のシステム内のPCIeファブリックにリアルタイムで組み込むことができる。

【0151】

このようなホット・プラグ/除去機能により、PCIeファブリックが増大することができ、新たに組み込まれたルート複合体全域で仮想機能を固有に共用することができる。したがって、PCIeファブリックは、それを実行するためにシステムを停止せずに拡張することができる。PCI−SiG入出力仮想化規格は、PCIeファブリックのこのような動的拡張に関するこのような機能または標準をまったく提供していない。

【0152】

例示的な諸実施形態のメカニズムでは、1つまたは複数のPCIルート複合体および複数ルート認識(MRA)対応スイッチを備えた既存のホスト・システムが存在するものと想定されている。たとえば、ホスト・システムは、1つまたは複数のMRAスイッチを有するPCIファブリックによって接続された2つのルート複合体RC2およびRC2を有することができる。その上、既存のルート複合体ならびに新たに組み込まれたルート複合体と通信するように構成可能な1つまたは複数のエンドポイントがPCIeファブリックに結合されているものと想定されている。その上、複数ルート(MR)PCI構成マネージャ(MR−PCIM)は、1つのホスト・システム上の帯域内にまたは帯域外に存在することができ、PCIeファブリックの相互接続スイッチを介してアクセス可能なすべてのリンクをトラバースすることができ、それをトラバースすることによってPCIファブリックを発見したものと想定されている。これらの想定はいずれも、本明細書に示されている例示的な諸実施形態に関して上記で前述した様々なメカニズムによって満足される。

【0153】

上記で想定されている構成では、システム管理者などが既存のPCIeファブリックに新しいルート複合体を追加する(たとえば、ブレード・シャーシに新しいブレードを挿入する)と、ホット・プラグ・コントローラなどの自動化メカニズムまたはシステム管理者のうちの少なくとも一方が、管理者インターフェースなどを介するなどにより、ルート複合体の追加をMR−PCIMに通知する。このような通知は、たとえば、新しいエンティティをファブリックに追加する動作が行われたことを示すイベントをMR−PCIMに通知することにより行うことができる。このようなイベントは、新しいルート複合体がその時点でPCIeファブリックに接続されている場合、すなわち、ルート複合体がプラグインされている場合に、スイッチおよびスイッチ・ポートを識別することができる。

【0154】

次に、MR−PCIMは、既存のPCIeファブリック内の新しいルート複合体を初期設定するためにいくつかの動作を実行することにより、通知されたイベントを処理することができる。たごえば、MR−PCIMは、新たに追加されたコンポーネントに関する情報でそのPCIeファブリック構成データ構造を更新することができる。PCIeファブリック構成データ構造は、PCIeファブリックの構成を表現するためにMR−PCIMによって使用される。PCIeファブリック構成データ構造内に保管された情報は、たとえば、MR−PCIMとの管理ユーザ・インターフェースを介して、PCIeファブリック構成レジスタから、ならびに、システム管理者による入力から、MR−PCIMによって収集される。PCIeファブリック構成データ構造の内容およびこの内容の使用法については、以下により詳細に説明する。

【0155】

PCIeファブリック構成データ構造を更新した後、MR−PCIMは、PCI規格によって定義される通り、PCI構成空間動作を実行して、PCI規格通り、新たに追加されたコンポーネントの特性、たとえば、それがエンドポイント、ルート複合体、スイッチなどであるか、それがどのタイプのエンドポイント、ルート複合体、スイッチなどであるかなどを判断する。新たに追加されたコンポーネントがスイッチであると判断された場合、スイッチの各ポートに関してPCI構成空間動作を実行して、そのスイッチに結合された追加コンポーネントの存在を判断する。次に、新たに追加されたコンポーネントに関する特性情報、たとえば、コンポーネント・タイプ、ベンダ名、部品番号、シリアル番号などは、MR−PCIMによる使用のために仮想PCIeファブリック構成データ構造に保管される。

【0156】

コンポーネントが新しいルート複合体または新しいエンドポイントである場合、MR−PCIMは、新しいルート複合体またはエンドポイントを仮想プレーンに関連付ける。このようにして、新しいルート複合体またはエンドポイントは、システムによる使用のために使用可能なものになる。コンポーネントがMRAスイッチである場合、MR−PCIMは、PCI入出力仮想化規格通り、スイッチの仮想プレーン・テーブルを構成する。コンポーネントがスイッチである場合、スイッチ・ポートをチェックして、コンポーネントがあれば、どのコンポーネントがそれに接続されているかを確認し、MR−PCIMは、同様にこれらのコンポーネントに関する情報に基づいて、そのPCIeファブリック構成データ構造も構成する。このようにして、新しいコンポーネント(複数も可)は、PCIeファブリックに動的に追加することができる。

【0157】

新しいルート複合体に関して、新しいルート複合体に関する特性情報を含むようMR−PCIMを構成し、その新しいルート複合体を仮想プレーンに関連付けると、PCIeファブリック内で新しいルート複合体を使用することができる。したがって、例示的な諸実施形態のメカニズムにより、ルート複合体およびそれに関連するコンポーネントを既存の実行中のPCIeファブリックに追加することができる。その結果として、追加のコンポーネントを含めるためにシステムを拡張するときにシステムに関するダウン時間はまったく発生しない。

【0158】

図29は、例示的な一実施形態によりルート複合体に関するホット・プラグイン動作を例示する典型的なブロック図である。図29はルート複合体に関するホット・プラグイン動作を図示しているが、例示的な諸実施形態はこれに限定されないことを理解されたい。むしろ、上記で論じた通り、ホット・プラグ動作は、本発明の精神および範囲を逸脱せずに、エンドポイント、スイッチ、およびその他のタイプのコンポーネントに関して実行することができる。

【0159】

図29に図示されている通り、ホスト・システム2510は、それぞれ仮想プレーン2511および2513に関連する既存のルート複合体RC1 2512およびRC2 2514を有する。既存のルート複合体RC1 2512およびRC2 2514は、仮想プレーン2540および2550内のエンドポイント2542、2544、2552,および2554と通信するようにMR−PCIM2562によって構成される。MR−PCIM2562は、ホスト・システム2510のコンポーネントを含む、PCIeファブリック2530のコンポーネントおよびPCIeファブリック2530に接続されたコンポーネントのすべてに関する特性情報を保管するファブリック構成データ構造2566を維持する。

【0160】

描かれている例では、新しいルート複合体RC N 2516がホスト・システム2510に追加されているものと想定されている。たとえば、ルート複合体RC N 2516はブレードに関連付けることができ、ホスト・システム2510は、RC N 2516に関連するブレードを挿入可能なシャーシを有するブレード・サーバにすることができる。RC N 2516をサポートできるその他のタイプのデバイスは、例示的な諸実施形態の精神および範囲を逸脱せずに使用することができる。

【0161】

例示的な諸実施形態では、コンポーネントのホット・プラグ/除去を可能にする予定の各スイッチ・ポートに関連する2通りのタイプの標準的なPCIホット・プラグ・コントローラが存在する。これらのホット・プラグ・コントローラの一方は、ホット・プラグ/除去動作の物理的側面のためにMR−PCIM2562によって使用され、「物理ホット・プラグ」コントローラと呼ばれる。ホット・プラグ可能なポートごとに、このような物理ホット・プラグ・コントローラが1つずつ存在する。

【0162】

加えて、スイッチ・ポートの下にある共用コンポーネントへの論理接続を制御するために仮想ホット・プラグ・コントローラを使用するルート複合体のために、「仮想ホット・プラグ」コントローラが提供される。スイッチ・ポートによってサポートされる仮想プレーンごとに1つの仮想ホット・プラグ・コントローラが存在する。

【0163】

例示的な諸実施形態では、新しいRC N 2516の追加に応答して、RC N 2516に関連するスイッチ2532のポートにある物理ホット・プラグ・コントローラが「プレゼンス検出変更(Presence Detect Change)」割り込みメッセージをMR−PCIM2562に送信して、新しいコンポーネントがPCIeファブリックに追加されていることをMR−PCIM2562に通知する。この割り込みメッセージはPCI規格によって定義されているが、ここでの使用法は、MR−PCIM2562を実行しないルート複合体ではなく、MR−PCIM2562に対して割り込みを指示することである。代わって、システム管理者は、新しいコンポーネントの追加に関する他の形式の通知として、挿入の前に、MR−PCIM2562への管理インターフェース(図示せず)を介してMR−PCIM2562にも通知している可能性がある。

【0164】

次に、MR−PCIM2562は、既存のPCIeファブリック2530内の新しいコンポーネント、たとえば、ルート複合体RC N 2516を初期設定するためにいくつかの動作を実行することにより、「プレゼンス検出変更」割り込みを処理することができる。たとえば、MR−PCIM2562は、新たに追加されたコンポーネントに関する情報でそのファブリック構成データ構造2566を更新する。ファブリック構成データ構造2566を更新する際に、MR−PCIM2562はPCI構成空間動作を実行して、新たに追加されたコンポーネントの特性、たとえば、それがエンドポイント、ルート複合体、スイッチなどであるか、それがどのタイプのエンドポイント、ルート複合体、スイッチなどであるか、ベンダ名、部品番号、シリアル番号などを照会し判断する。

【0165】

この自動化照会に加えて、追加コンポーネントがルート複合体である場合、システム管理者は、MR−PCIM2562への管理インターフェース(図示せず)などにより、新たに追加されたルート複合体に対してどのコンポーネントを構成すべきかをMR−PCIM2562に指示することができる。たとえば、MR−PCIM2562は、新しいRC N 2516がアクセスできるようにするためにそのエンドポイントを正しい仮想プレーンに追加できるように、システム管理者がどのエンドポイントを新しいRC N 2516に割り当てたいと希望しているかを把握する必要がある。仮想プレーンに対するエンドポイントのこのような割り当ては、MR−PCIM2562がMRAスイッチ2532のPCI構成空間内のPCIマルチルート構成構造にアクセスし、エンドポイントがMRAエンドポイントである場合は、MRAスイッチ2532に加えて、エンドポイント内のPCIマルチルート構成構造にアクセスすることによって実行される。

【0166】

描かれている例では、追加された新しいコンポーネントは、ルート複合体RC N 2516、たとえば、RC N 2516を提供するブレードである。しかし、このコンポーネントは、いくつかの異なるタイプのコンポーネントのいずれでもよく、したがって、MR−PCIM2562は、追加コンポーネントから収集された特性情報に基づいて、追加されるコンポーネントのタイプを判断することができる。追加されるコンポーネントについて判断されたタイプに基づいて、MR−PCIM2562により様々な動作を実行してPCIeファブリック2530にそのコンポーネントを動的に追加し、PCIeファブリック2530の通信および動作においてそれを使用できるようにすることができる。

【0167】

描かれている例では、追加コンポーネントは新しいルート複合体RC N 2516であるので、MR−PCIM2562は、新しいルート複合体RC N 2516を仮想プレーン2515に関連付け、次に、前に詳述した通り、システム管理者が新しいルート複合体RC N2516に対して指定したエンドポイントを関連付ける。このようにして、新しいコンポーネントをPCIeファブリックに動的に追加することができる。

【0168】

MR−PCIM2562によりPCIeファブリック2530に新しいルート複合体RC N 2516が追加された場合、新しいルート複合体RC N 2516に関する特性情報をファブリック構成データ構造2566に含め、新しいルート複合体に関連付けるコンポーネントのPCI構成空間をセットアップし、新しいルート複合体を仮想プレーン2515に関連付けることにより、新しいルート複合体RC N 2516をPCIeファブリック2530で使用することができる。上記の動作は、PCIeファブリック2530が機能し続けている間に動的に実行される。したがって、例示的な諸実施形態は、実行中のPCIeファブリック2530にコンポーネントをホット・プラグするためのメカニズムを提供する。

【0169】

ファブリック構成データ構造は、MR−PCIM2562によりシステム構成とともに現行状態に保持され、いくつかの目的に使用できることに留意されたい。たとえば、それは、MR−PCIMの管理インターフェースを介して、PCIeファブリック2530の入出力構成をシステム管理者に対して表示するために使用することができる。すなわち、どのエンドポイントがどのルート複合体に割り当てられるか、どのエンドポイントがどのルート複合体にも割り当てられておらず、したがって、割り当てるために使用可能であるかなどの表現は、MR−PCIM2562によって提供される管理インターフェースを介してシステム管理者に提供することができる。また、ファブリック構成データ構造2566は、フラッシュ・メモリまたはハード・ディスクなどの不揮発性記憶装置内のシステム電源サイクル全体で持続することもでき、その結果、システムの電源を投入したときに、システム管理者によって前に割り当てられたルート複合体に対するエンドポイントの事前割り当てをMR−PCIM2562によって自動的に復元することができる。

【0170】

ファブリック構成データ構造2566は、入出力通信ファブリック2530、エンドポイントPCI構成レジスタ、およびMR−PCIM2562の管理インターフェースを介してシステム管理者によって入力された情報から入手したすべての既知の情報で維持される。ファブリック構成データ構造2566は、入出力構造のツリー構造を識別し、このため、後述する通り、除去動作が実行されたときにどのコンポーネントが除去されるかを把握するために使用することができる。

【0171】

上記の例では、ルート複合体が追加されている。これが行われると、ルート複合体のファームウェアおよびソフトウェアは、通常の電源投入動作の一部として、通常のPCI構成アクセスを使用して、ファブリック構成データ構造2566内の入出力構成情報を調べることになる。実行中の入出力通信ファブリック2530に追加されるコンポーネントがエンドポイントである場合、システム管理者がMR−PCIMの管理インターフェースを介して所望のルート複合体にコンポーネントを追加すると、MR−PCIM2562は、上述の通り、所望の仮想プレーンに対してエンドポイントを構成した後、前述の仮想ホット・プラグ・コントローラを介してエンドポイントが追加されたことをルート複合体に通知する。その結果として、ルート複合体は、仮想ホット・プラグ・コントローラから割り込みを受信し、新しいエンドポイントを構成し、その使用を開始するソフトウェアを開始する。このため、現行のシステム動作を停止せずに、エンドポイントを追加することができる。

【0172】

加えて、例示的な諸実施形態のメカニズムは、PCIeファブリック2530からコンポーネントを動的に除去するための機能も提供する。「追加(Add)」イベントと同様に、MR−PCIM2562には、インターフェース、自動検出メカニズムなどを介して、システム管理者から「除去(Remove)」イベントを通知することができる。「除去」イベントの場合、このイベントは、MR−PCIM2562によって管理される仮想階層のうちのどの仮想ツリー・ブランチで除去動作(すなわち、コンポーネントのホット・プラグ除去)が行われたかまたは行われるかをMR−PCIM2562に対して識別する。

【0173】

除去動作では、除去すべきコンポーネントがファブリック構成データ構造2566によって識別される。前述の通り、このファブリック構成データ構造2566は、入出力コンポーネントのツリー構造を識別する。除去動作はツリー構造内の除去すべきコンポーネントを指し、そのコンポーネントの下にあるものもすべて除去されることになる。たとえば、除去すべきコンポーネントは、MR−PCIM2562管理インターフェースを介してシステム管理者に対して表示されるグラフィック管理インターフェースによって指し示される可能性がある。その場合、MR−PCIM2562は、ファブリック構成データ構造2566を介してその選択されたコンポーネントがどのように他のコンポーネントに関連するかを把握する。

【0174】

代わって、コンポーネントの関係は、そのコンポーネントに関連する仮想ホット・プラグ・コントローラ内の状況ビットによって識別することができる。この後者の場合、仮想ホット・プラグ・コントローラは、どのコンポーネントを除去すべきであったかを確認するために、仮想ホット・プラグ・コントローラのレジスタから状況を読み取ることができるMR−PCIM2562に対して割り込みメッセージを発行することができる。このような場合、MR−PCIM2562は、どのコンポーネントを除去する必要があるかを発見するために、ファブリック構成データ構造2566を走査してそのコンポーネントを見つけることができる。

【0175】

除去動作の例としては、エンドポイントEP5 2552を除去するための動作を含み、その場合、ファブリック構成データ構造2566内のツリー構造に基づいて、そのエンドポイントのみが除去のために識別されるであろう。他の例として、MRAスイッチ3 2532の除去は、ファブリック構成データ構造2566のツリー構造に基づいて、MRAスイッチ3 2532およびエンドポイントEP3 2542〜EP6 2554の除去を伴うことになるであろう。

【0176】

MR−PCIM2562は、「除去」イベントに関連するコンポーネントを除去するようにその仮想PCIeファブリック構成データ構造2566を更新し、それらが前に占めていた仮想プレーンからそれらを除去するように関連する1つまたは複数のツリー・ブランチ内のコンポーネントのPCI構成空間を更新することにより、「除去」イベントを処理する。除去後、エンドポイントを未使用コンポーネント・プールに返すことができ、システム管理者によって後で他のルート複合体に割り当てることができる。具体的には、ファブリック構成データ構造2566に内のPCI構成情報によって識別された通り、コンポーネントがエンドポイントである場合、MR−PCIM2562は、それが入っていた仮想ツリー階層内の仮想プレーンからそのエンドポイントを除去する。コンポーネントがルート複合体であるかまたはルート複合体を提供する場合、そのコンポーネントに関連する仮想プレーンは、その仮想プレーンの一部であったすべてのコンポーネントから除去される。したがって、PCIeファブリックにコンポーネントを動的に追加できることに加えて、例示的な諸実施形態のメカニズムは、PCIeファブリックが動作中または実行中である間にPCIeファブリックからコンポーネントを動的に除去する能力をさらに提供する。

【0177】

図30は、例示的な一実施形態によりPCIeファブリックにコンポーネントを追加するための典型的な動作の概要を示す流れ図である。図30に図示されている通り、動作は、PCIeファブリックへのコンポーネントの追加を示す「追加」イベントをMR−PCIMで受信することから始まる(ステップ2610)。前に論じた通り、このイベントは、コンポーネントが追加されるスイッチおよびスイッチ・ポートを識別することができ、たとえば、コンポーネントの追加の自動検出に応答してまたはシステム管理者のコマンド入力に応答して生成することができる。「追加」イベントは、たとえば、新しいコンポーネントの追加の検出に応答して、PCIeスイッチの物理ホット・プラグ・コントローラによって送信された「プレゼンス検出変更」割り込みの一部として受信することができる。

【0178】

MR−PCIMは、追加コンポーネントに関する特性情報を収集する(ステップ2620)。この収集は、コンポーネントなどに関連するVPD記憶装置などから特性情報を検索するためにコンポーネントと通信することを含むことができる。その上、この収集は、MR−PCIMがPCI構成空間動作を実行して、新たに追加されたコンポーネントのこのような特性を決定することを含むことができる。MR−PCIMは、収集された特性情報に基づいて、コンポーネントがスイッチであるかどうかを判断する(ステップ2630)。コンポーネントがスイッチである場合、MR−PCIMは、スイッチのポートに接続された任意のコンポーネントに関する特性情報を収集する(ステップ2640)。MR−PCIMは、そのコンポーネントに関する特性情報に基づいて、スイッチがMRAスイッチであるかベース・スイッチ(base switch)であるかを判断する(ステップ2650)。スイッチがMRAスイッチである場合、MR−PCIMはMRAスイッチ仮想プレーン・テーブルを構成する(ステップ2660)。スイッチがベース・スイッチである場合、MR−PCIMはスイッチ上のすべてのポートを1つの仮想プレーンに割り当てる(ステップ2670)。

【0179】

コンポーネントがスイッチではない場合、MR−PCIMは、コンポーネントが新しいルート複合体またはエンドポイントを提供するものと判断する。MR−PCIMはルート複合体またはエンドポイントを仮想プレーンに関連付ける(ステップ2680)。次に、コンポーネントに関する特性情報を使用して、関連の仮想プレーン(複数も可)に基づいてMR−PCIMに関連するPCIeファブリック構成データ構造を更新する(ステップ2690)。この更新は、たとえば、ファブリック構成データ構造内に維持される1つまたは複数の仮想階層を更新することを含むことができる。最後に、MR−PCIMはPCI構成空間VP IDを更新する(ステップ2695)。その後、動作は終了する。

【0180】

図31は、例示的な一実施形態によりPCIeファブリックからコンポーネントを動的に除去するための典型的な動作の概要を示す流れ図である。図31に図示されている通り、動作は、MR−PCIMが「除去」イベントを受信することから始まる(ステップ2710)。上記で論じた通り、このイベントは、たとえば、コンポーネントの除去の自動検出に応答してまたはシステム管理者のコマンド入力に応答して生成することができる。

【0181】

MR−PCIMは、除去されるコンポーネントがエンドポイントであるかどうかを判断する(ステップ2720)。コンポーネントがエンドポイントである場合、コンポーネントは、それがMR−PCIMに関連するPCIeファブリック構成データ構造で割り当てられていた仮想プレーンから除去される(ステップ2730)。コンポーネントがエンドポイントではない場合、コンポーネントはルート複合体である。コンポーネントがルート複合体である場合、MR−PCIMは、PCIeファブリック構成データ構造内でその仮想プレーンの一部であったすべてのコンポーネントからルート複合体に関連する仮想プレーンを除去する(ステップ2740)。コンポーネントがMR−PCIMのファブリック構成データ構造から除去されることに加えて、MR−PCIMは、コンポーネント内のVP番号を更新するために、影響を受けるコンポーネントに対してPCI構成動作も発行する(ステップ2750)。その後、動作は終了する。

【0182】

したがって、例示的な諸実施形態のメカニズムは、複数のシステム・イメージおよびルート複合体全域でエンドポイントを共用するための様々な機能を提供する。これらの機能としては、ルート複合体とエンドポイントとの間で通信する際に使用するための共用メモリ空間を構成すること、ルート複合体およびその他のコンポーネントを動的に追加または除去することなどを含む。これらの様々なメカニズムはいずれも、時間の経過とともに要件が変化するにつれてシステムの拡張能力を増すものである。その上、これらの様々なメカニズムは、ワークロード・バランシング、並行保守、および大量なその他の所望のシステム機能を強化するものである。

【0183】

本発明は完全に機能するデータ処理システムに関して記載されているが、本発明のプロセスを複数命令からなるコンピュータ可読媒体の形式および様々な形式で分散することができ、その分散を実行するために実際に使用される信号伝送媒体の特定のタイプにかかわらず、本発明が等しく適用されることを当業者が理解することは留意すべき重要なことである。コンピュータ可読媒体の例としては、フレキシブル・ディスク、ハード・ディスク、RAM、CD−ROM、DVD−ROMなどの書き込み可能タイプの媒体と、デジタルおよびアナログ通信リンク、たとえば、無線周波数および光波伝送などの伝送形式を使用する有線または無線通信リンクなどの伝送タイプの媒体とを含む。コンピュータ可読媒体は、特定のデータ処理システムで実際に使用するためにデコードされたコード化フォーマットの形を取ることができる。

【0184】

本発明の説明は、例示および説明のために提示されたものであり、網羅するためあるいは開示された形の本発明に限定するためのものではない。多くの変更例および変形例は当業者にとって自明なものになるであろう。実施形態は、実際の適用例である本発明の原理を最もよく説明し、他の当業者が企図された特定の用途に適した様々な変更例を含む様々な実施形態について本発明を理解できるようにするために、選択され記載されたものである。

【図面の簡単な説明】

【0185】

【図1】一般に当技術分野で知られているPCIeファブリック・トポロジを例示する典型的な図である。

【図2】一般に当技術分野で知られているシステム仮想化を例示する典型的な図である。

【図3】入出力仮想化仲介を使用してPCIルート複合体の入出力を仮想化するための第1の手法を例示する典型的な図である。

【図4】固有に共用されるPCI入出力アダプタを使用してPCIルート複合体の入出力を仮想化するための第2の手法を例示する典型的な図である。

【図5】PCIe入出力仮想化対応エンドポイントの典型的な図である。

【図6】固有の仮想化なしの単一ルート・エンドポイントの物理機能および仮想機能を例示する典型的な図である。

【図7】固有の入出力仮想化に使用可能になっている単一ルート・エンドポイントの物理機能および仮想機能を例示する典型的な図である。

【図8】例示的な一実施形態によるマルチルート仮想化入出力トポロジを例示する典型的な図である。

【図9】例示的な一実施形態によるルート・ノードのSR−PCIMの観点から見たマルチルート仮想化入出力トポロジの仮想階層表示を例示する典型的な図である。

【図10】例示的な一実施形態による共用メモリPCIeベース・システムを例示する典型的な図である。

【図11】例示的な一実施形態による典型的な仮想PCIツリー・データ構造を表す図である。

【図12】例示的な一実施形態による典型的な仮想PCIツリー・データ構造を表す図である。

【図13】例示的な一実施形態によりエンドポイントの共用のためのホスト・システムのメモリ・アドレス空間を初期設定するための典型的な動作の概要を示す流れ図である。

【図14】例示的な一実施形態により第1のホスト・システムから第2のホスト・システムに作業キュー・エレメント(WQE)を送信するためのプロセスを例示する典型的なブロック図である。

【図15】例示的な一実施形態により第2のホスト・システムから第1のホスト・システムに完了キュー・エレメント(CQE)を送信するためのプロセスを例示する典型的なブロック図である。

【図16】例示的な一実施形態により第1のホスト・システムのルート複合体と第2のホスト・システムに関連するエンドポイントとの間でWQEを伝送するための典型的な動作の概要を示す典型的な流れ図である。

【図17】例示的な一実施形態により第2のホスト・システムのエンドポイントから第1のホスト・システムのルート複合体にCQEを伝送するための典型的な動作の概要を示す典型的な流れ図である。

【図18】同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信を実行するために使用可能なトランザクションの組み合わせとして可能な様々なものを例示する典型的な表である。

【図19】例示的な一実施形態によりソケットを確立し、第1のホスト・システムと第2のホスト・システムとの間でソケット・ベースの通信を実行するためのプロセスを例示する典型的なブロック図である。

【図20】例示的な一実施形態によりソケット・ベースの通信接続を使用してプル・トランザクションを実行するための典型的な動作の概要を示す流れ図である。

【図21】例示的な一実施形態によりソケット・ベースの通信接続を使用してプッシュ・トランザクションを実行するための典型的な動作の概要を示す流れ図である。

【図22】例示的な一実施形態により同じPCIeアダプタ上の1つの物理機能から他の物理機能への仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。

【図23】例示的な一実施形態により同じPCIeアダプタ上の1つの物理機能から他の物理機能への仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。

【図24】例示的な一実施形態により1つのPCIeアダプタから他のPCIeアダプタへの仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。

【図25】例示的な一実施形態により1つのPCIeアダプタから他のPCIeアダプタへの仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。

【図26】例示的な一実施形態により1つのシステム・イメージから他のシステム・イメージへの仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。

【図27】例示的な一実施形態により1つのシステム・イメージから他のシステム・イメージへの仮想機能およびそれに関連するアプリケーションの単一ルート・ステートレス移行を例示する典型的な図である。

【図28】例示的な一実施形態により仮想機能を移行するための典型的な動作の概要を示す流れ図である。

【図29】例示的な一実施形態によりルート複合体に関するホット・プラグイン動作を例示する典型的なブロック図である。

【図30】例示的な一実施形態によりPCIeファブリックにコンポーネントを追加するための典型的な動作の概要を示す流れ図である。

【図31】例示的な一実施形態によりPCIeファブリックからコンポーネントを動的に除去するための典型的な動作の概要を示す流れ図である。

【符号の説明】

【0186】

310:ホストCPUセット

320:システム・イメージ(SI)1

330:システム・イメージ(SI)2

340:入出力仮想化仲介

350:PCIルート複合体

360:PCIeスイッチ

370:PCIeエンドポイント

380:PCIeエンドポイント

390:PCIeエンドポイント

【技術分野】

【0001】

本出願は、一般に、改良されたデータ処理システムおよび方法に関する。より具体的には、本出願は、トランザクション・プロトコルおよび共用メモリを使用するホスト・システム間の通信のためのメカニズムを対象とする。

【背景技術】

【0002】

多くの近代的なコンピューティング・デバイスは、そもそも1990年代にインテル社によって作成された周辺装置相互接続規格のあるバージョンまたは実装例を使用する入出力(I/O:input/output)アダプタおよびバスを利用する。周辺装置相互接続(PCI:Peripheral ComponentInterconnect)規格は、コンピュータ・マザーボードに周辺装置を接続するためのコンピュータ・バスを規定するものである。PCI ExpressまたはPCIeは、既存のPCIプログラミング概念を使用するPCIコンピュータ・バスの実装例の1つであるが、大きく異なり、より高速のシリアル物理層通信プロトコルをそのコンピュータ・バスの基礎とする。この物理層は、複数のデバイス間で共用できる双方向バスから構成されるのではなく、正確に2つのデバイスに接続される1つの単一方向リンクから構成される。

【0003】

図1は、PCIe規格によるPCI Express(PCIe)のファブリック・トポロジ(ネットワークの接続形態の構造)を例示する図である。図1に図示されている通り、PCIeファブリック・トポロジ100は、ルート複合体130に結合されたホスト・プロセッサ(CPU)110およびメモリ120から構成され、次に、そのルート複合体130は、PCIeエンドポイント140(「エンドポイント」という用語は、PCIe対応入出力アダプタについて言及するためにPCIe規格で使用されるものである)、PCI Express/PCIブリッジ150、および1つまたは複数の相互接続スイッチ160のうちの1つまたは複数に結合されている。ルート複合体130は、CPU/メモリを入出力アダプタに接続する入出力階層のルートを意味する。ルート複合体130は、ホスト・ブリッジと、ゼロまたは1つ以上のルート複合体統合エンドポイントと、ゼロまたは1つ以上のルート複合体イベント・コレクタと、1つまたは複数のルート・ポートとを含む。各ルート・ポートは個別の入出力階層をサポートする。入出力階層は、ルート複合体130と、ゼロまたは1つ以上の相互接続スイッチ160またはブリッジ150あるいはその両方(スイッチまたはPCIeファブリックを含むもの)と、エンドポイント170および182〜188などの1つまたは複数のエンドポイントから構成することができる。PCIおよびPCIeに関する追加情報については、www.pcisig.comの周辺装置相互接続分科会(PCI−SiG:peripheral component interconnect special interest group)Webサイトから入手可能なPCIおよびPCIe規格を参照する。

【0004】

現在、PCIおよびPCIe入出力アダプタ、バスなどは、ブレード・サーバのブレードを含む、ほとんどすべてのコンピューティング・デバイスのマザーボードに統合されている。ブレード・サーバは、本質的に、いくつかの個別最小パッケージ・コンピュータ・マザーボード「ブレード」用のハウジングであり、そのそれぞれは、1つまたは複数のプロセッサと、コンピュータ・メモリと、コンピュータ記憶域と、コンピュータ・ネットワーク接続とを含むが、シャーシの共通電源および空冷リソースを共用する。ブレード・サーバは、Webホスティングおよびクラスタ・コンピューティングなどの特殊用途には理想的なものである。

【0005】

前述の通り、PCIおよびPCIe入出力アダプタは、典型的には、ブレード自体に統合される。その結果として、入出力アダプタは、同じブレード・サーバ内のブレード全域で共用することができない。その上、入出力アダプタの統合により、リンク・レートのスケーラビリティが制限される。すなわち、リンク・レートは、時間の経過につれてプロセッサ・パフォーマンスでスケーリングすることができない。現時点では、複数のブレード全域の複数のシステム・イメージによってPCIおよびPCIe入出力アダプタを共用できるようにするメカニズムは、まったく考案されていない。その上、1つのブレード・サーバ内の複数のブレードによって使用するためにPCIおよびPCIe入出力アダプタを非統合方式で提供できるようにするメカニズムは、まったく考案されていない。

【発明の開示】

【発明が解決しようとする課題】

【0006】

現行のPCIおよびPCIe入出力アダプタの統合による制限に対処するために、例示的な諸実施形態は、1つのPCIeアダプタを2つまたはそれ以上のシステム・イメージ(SI:system image)によって固有に共用できるようにするメカニズムを提供する。たとえば、エンドポイント、たとえば、PCIe入出力アダプタを同じルート複合体内の複数のSIによって、または共通PCIスイッチ・ファブリックを共用する、すなわち、共通PCIスイッチ・ファブリックに結合される複数のルート複合体(RC:rootcomplex)全域で同時に共用できるようにするためのメカニズムが提供される。このメカニズムにより、各ルート複合体ならびにそれに関連する物理エンドポイントまたは仮想エンドポイント(VEP:virtualendpoint)あるいはその両方は、それぞれ専用の固有のPCIメモリ・アドレス空間を有することができる。

【0007】

加えて、基本PCI規格から欠落しているが、エンドポイントの共用の結果として得られる複合体構成を管理するために必要なことは、エンドポイント内のPCI機能の組み合わせとして可能なものを決定し、それを管理する必要性である。したがって、本明細書の例示的な諸実施形態は、ブレード・サーバ内の第1のブレードの1つのルート複合体が同じかまたは異なるブレード・サーバ内の第2のブレードの第2のルート複合体と通信するためのメカニズムを提供する。例示的な諸実施形態では、このような通信を容易にするために使用されるマルチルート・ブレード・クラスタ内のルート複合体とエンドポイントとの間の共用メモリを初期設定するためのメカニズムを提供することにより、このような通信をサポートする。

【課題を解決するための手段】

【0008】

例示的な一実施形態では、マルチルートPCIe構成マネージャ(MR−PCIM:multi-root PCIe configuration manager)は、PCIeスイッチ・ファブリックの相互接続スイッチによりアクセス可能なすべてのリンクをトラバースすることによってPCIeスイッチ・ファブリック、すなわち、PCIe階層を発見することにより、ルート複合体とエンドポイントとの間の共用メモリを初期設定する。リンクをトラバースするにつれて、MR−PCIMは、ルート複合体およびエンドポイントのそれぞれについて入手した情報を比較して、どのエンドポイントおよびルート複合体が同じブレード上に存在するかを判断する。次に、PCIeスイッチ・ファブリック上で使用可能なエンドポイントを各ルート複合体に結合する仮想PCIeツリー・データ構造が生成される。同じPCIeツリーの一部であるエンドポイント、すなわち、同じルート複合体に関連するエンドポイントは、この仮想PCIeツリー・データ構造で関連付けられる。

【0009】

次に、MR−PCIMは、各エンドポイントが属すPCIeメモリ・アドレス空間内の基底および限界をそのエンドポイントに与えることができる。同様に、次に、MR−PCIMは、各ルート複合体が属すPCIeメモリ・アドレス空間内の基底および限界をそのルート複合体に与えることができる。様々なエンドポイントおよびルート複合体のPCIeメモリ・アドレス空間同士をマッピングするために、メモリ変換および保護テーブル・データ構造を生成することができる。

【0010】

たとえば、特定のエンドポイントまたはルート複合体の場合、そのエンドポイントまたはルート複合体は、第1のホストの実メモリ・アドレス空間に関連付けることができる。同じエンドポイントまたはルート複合体は、第1のホストのPCIバス・メモリ・アドレスにより直接メモリ・アクセス入出力としてアクセス可能な第2のホスト・メモリ上のPCIeアパーチャを介して第2のホストによりアクセス可能なものになりうる。第1のホストは、第2のホストによって認識されるPCIeメモリ・アドレスを第1のホストの実メモリ・アドレスにマッピングするために、メモリ変換および保護テーブル・データ構造を使用することができる。

【0011】

さらに他の例示的な実施形態では、エンドポイントがホスト・システム全域のルート複合体によりアクセス可能なものになりうるようにホスト・システムのメモリ・アドレス空間を初期設定すると、その後、これらのメモリ・アドレス空間を使用して、これらのルート複合体に関連するシステム・イメージとそれに対応するアプリケーションがエンドポイントと通信できるようにすることができる。

【0012】

このような通信を容易にする方法の1つは、様々なホスト・システム内のこれらの初期設定済みメモリ・アドレス空間を使用するキューイング・システムを介するものである。このようなキューイング・システムは、作業キュー構造と完了キュー構造とを含むことができる。作業キュー構造と完了キュー構造はいずれも、いくつかのキュー・エレメント(そのキュー構造が作業キュー構造であるか完了キュー構造であるかに応じて、作業キュー・エレメント(WQE:work queue element)または完了キュー・エレメント(CQE:completion queue element)のいずれか一方)を識別するためのドアベル構造と、キューの始まりに関する基底アドレスと、キューの終わりに関する限界アドレスと、キュー内で次に処理すべきWQEまたはCQEを示すオフセットとを含むことができる。作業キュー構造と完了キュー構造はいずれも、データの送信とデータの受信の両方に使用することができる。

【0013】

キュー構造およびドアベル構造は、実行すべき通信の対象であるルート複合体およびエンドポイントに対応するホスト・システム・メモリの一部分に設けることができる。キュー・エレメントを生成してキュー構造に追加することができ、それによりキュー・エレメントが処理のために使用可能であることをエンドポイントまたはルート複合体に通知するために、ドアベル構造を書き込むことができる。キュー・エレメントおよびキュー・エレメントに対応するデータを検索するために、PCIe DMA動作を実行することができる。その上、キュー・エレメントの処理の完了を示すための完了キュー・エレメント(CQE)を返すために、PCIe DMA動作を実行することができる。

【0014】

例示的な一実施形態によれば、例示的な諸実施形態の共用メモリを使用して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間で通信するために、トランザクション指向プロトコルを確立することができる。このトランザクション指向プロトコルは、データをプッシュまたはプルするために、様々なエレメント、たとえば、ルート複合体またはエンドポイントによって実行すべき一連のトランザクションを指定する。本発明の精神および範囲を逸脱せずに、プッシュ・トランザクションとプル・トランザクションの様々な組み合わせを使用することができる。この様々な組み合わせについては、以下の詳細な説明でより詳細に説明する。

【0015】

加えて、例示的な諸実施形態のメカニズムをさらに使用して、上述の共用メモリを介して同じかまたは異なるホスト・システムのルート複合体とエンドポイントとの間のソケット・プロトコル・ベースの通信をサポートすることができる。このようなソケット・ベースの通信では、ホスト・システム内の作業キューを使用して、着信ソケット初期設定要求を聴取(listen)することができる。すなわち、第2のホスト・システムとのソケット通信接続を確立することを希望する第1のホスト・システムは、その作業キュー内にソケット初期設定要求WQEを生成することができ、そのソケット初期設定要求WQEが処理のために使用可能であることを第2のホスト・システムに通知することができる。

【0016】

その後、第2のホスト・システムは、その要求を受諾または拒否することができる。第2のホスト・システムがその要求を受諾する場合、そのホスト・システムは、第1および第2のホスト・システム間でソケット・ベースの通信を実行する際に第1のホスト・システムによって使用するためのソケットのパラメータのうちの後半部分を返す。これらのパラメータは、ソケットに関連付けるべきキュー構造の一部分と、キュー・エレメントがソケットを介して処理のための使用可能であるときにホスト・システムに通知するために使用されるドアベル構造とを指定することができる。実際のソケット通信は、たとえば、ホスト・システム間のプル・トランザクションまたはプッシュ・トランザクションあるいはその両方を伴う可能性がある。

【0017】

ルート複合体間のリソースの固有の共用により、システム・イメージ間またはエンドポイント間あるいはその両方で機能およびそれに関連するアプリケーションの移行のためのメカニズムを提供するために活用可能なPCIeファブリック内のホスト・システムとエンティティとの関係が作り出される。この移行機能は、システム管理の領域においてワークロード・バランシング機能の需要の増大を満足するために必要である。このようなメカニズムは、現在、PCIe規格から欠落している。

【0018】

例示的な一実施形態では、単一ルートPCI構成マネージャ(SR−PCIM:Single-Root PCI Configuration Manager)は、エンドポイント(EP)によってサポートされる仮想機能(VF:virtualfunction)移行シナリオとして可能なものを備えたシステム・イメージ(SI)を提供する。システム管理者または管理用タスクを実行するソフトウェア・アプリケーション、たとえば、ワークロード・バランシング・アプリケーションは、あるSIから他のSIへのVFおよびそれに関連するアプリケーション(複数も可)のステートレス移行が必要であることを単一ルートPCIマネージャ(SR−PCIM)に示すコマンドを実行することができる。VFおよびそれに関連するアプリケーション(複数も可)(動作すべきVFに依存するアプリケーションである)を移行することにより、より効率的な環境で動作を続行するために種々のリソースをリクルートすることができる。たとえば、ワークロード・バランシングでは、例示的な諸実施形態のメカニズムを使用してイーサネット(登録商標)VFおよびそれに関連する従属アプリケーションを移動し、異なるSIまたは同等EPと完全に関連付けることができる異なる物理機能(PF:physicalfunction)上で使用可能なより高速の(あまり輻輳していない)接続を利用することができる。

【0019】

ホスト・システム上で実行されるソフトウェア仲介(SWI:Software Intermediary)または仮想化仲介(virtualization intermediary)は、VFに対する未解決の要求を完了し、次にそれを停止するために必要な任意のプロセスを開始するようSIに指示する。VFに対するすべての要求が完了したことがSIによってSWIに通知されると、SWIは、VFに関連する任意のアプリケーションをSIから除去することができ、VFを関連の物理機能(PF)から切り離すことができる。

【0020】

その後、SWIは、同じかまたは異なるEP内に存在する可能性のあるターゲットPFにVFを接続することができる。その上、ターゲットPFは、異なるSIに関連付けることができる。SWIは、VFをそのVFが現在関連付けられているSIにとって使用可能なものにし、VFを構成するようSIに指示する。SIはVFを構成し、それにより、それを関連アプリケーションによる使用のために使用可能なものにする。次に、SWIは、新たに移行されたVF上のリソースを使用できるように、関連アプリケーションを開始するようSIに指示することができる。

【0021】

上記のメカニズムに加えて、例示的な諸実施形態は、実行中のマルチルートPCIeファブリックへの新しいコンポーネントのホット・プラグ/除去を実行するための機能をさらに提供する。これらのメカニズムにより、たとえば、ルート複合体を実行中のPCIeファブリックにホット・プラグするかまたはそこから除去することができる。たとえば、ブレードはブレード・シャーシにホット・プラグすることができ、それに関連するルート複合体は既存のシステム内のPCIeファブリックにリアルタイムで組み込むことができる。

【0022】

このようなホット・プラグ/除去機能により、PCIeファブリックが増大することができ、新たに組み込まれたルート複合体全域で仮想機能を固有に共用することができる。したがって、PCIeファブリックは、それを実行するためにシステムを停止せずに拡張することができる。PCI−SiG入出力仮想化規格は、PCIeファブリックのこのような動的拡張に関するこのような機能または標準をまったく提供していない。

【0023】

例示的な一実施形態では、第1のホスト・システムと第2のホスト・システムとの間で通信するための方法が提供される。この方法は、第2のホスト・システムに関連するエンドポイントに割り当てられた第1のアドレス範囲を含むように第1の共用メモリ内に第1のメモリ・アドレス空間を初期設定するステップを含むことができる。この方法は、第2のホスト・システムに関連するエンドポイントに割り当てられた第2のアドレス範囲を含むように第2の共用メモリ内に第2のメモリ・アドレス空間を初期設定するステップをさらに含むことができる。その上、この方法は、第1のアドレス範囲内に作業キュー構造を生成するステップと、第2のアドレス範囲内に完了キュー構造を生成するステップであって、その完了キュー構造が第2のドアベル構造を含むステップとを含むことができる。作業キュー構造と第2のホスト・システムとの間ならびに完了キュー構造と第1のホスト・システムとの間で作業キュー・エレメントおよび完了キュー・エレメントを転送するために、確立されたトランザクション・プロトコルにより第1のホスト・システムおよび第2のホスト・システムによってプッシュ動作またはプル動作のうちの少なくとも一方を実行することができる。

【0024】

確立されたトランザクション・プロトコルは、プルプルプッシュ・トランザクション・プロトコルにすることができる。このプルプルプッシュ・トランザクション・プロトコルにより、エンドポイントは、作業キュー構造からエンドポイントに作業キュー・エレメントをプルするために直接メモリ・アクセス動作を実行する。その上、エンドポイントは、作業キュー・エレメントに対応するデータを第1の共用メモリからプルするために直接メモリ・アクセス動作を実行する。さらに、エンドポイントは、第1のホスト・システムに完了キュー・エレメントをプッシュするための動作を実行する。

【0025】

確立されたトランザクション・プロトコルは、エンドポイントによって施行することができる。第1のアドレス範囲および第2のアドレス範囲は、メモリ・マップ入出力(I/O)動作ならびに少なくとも1つのアドレス変換および保護テーブルを介してホスト・システムによりアクセス可能なものにすることができる。プッシュ動作およびプル動作は、直接メモリ・アクセス(DMA)動作にすることができる。

【0026】

第1のホスト・システムに関連する第1のメモリ・アドレス空間を初期設定するステップならびに第2のホスト・システムに関連する第2のメモリ・アドレス空間を初期設定するステップは、データ処理システムの通信ファブリック内のリンクをトラバースして、通信ファブリック内に存在するエンドポイントおよびルート複合体に関する情報を収集するステップを含むことができる。この方法は、物理的にまたは論理的に相互に関連付けられている少なくとも1つのエンドポイントおよび少なくとも1つのルート複合体を識別する少なくとも1つの仮想階層を生成するステップをさらに含むことができる。その上、この方法は、第1のホスト・システムのルート複合体に関連する各エンドポイントが第1のメモリ・アドレス空間内に対応するアドレス範囲を有し、第2のホスト・システムのルート複合体に関連する各エンドポイントが第2のメモリ・アドレス空間内に対応するアドレス範囲を有するように、少なくとも1つの仮想階層に基づいて第1のメモリ・アドレス空間および第2のメモリ・アドレス空間を初期設定するステップを含むことができる。少なくとも1つのエンドポイントは、第1のメモリ・アドレス空間内と第2のメモリ・アドレス空間内の両方に、対応するアドレス範囲を有することができる。

【0027】

データ処理システムはブレード・サーバにすることができ、第1のホスト・システムおよび第2のホスト・システムはブレード・サーバ内のブレードにすることができる。データ処理システムは、第1のホスト・システムおよび第2のホスト・システムが結合される周辺装置相互接続高速(PCIe)ファブリックを含むことができる。エンドポイントはPCIeアダプタにすることができる。PCIeファブリックは、1つまたは複数の複数ルート認識(MRA:multiple root aware)スイッチを含む複数ルート認識PCIeファブリックにすることができる。

【0028】

他の例示的な諸実施形態では、コンピュータ可読プログラムを有するコンピュータで使用可能な媒体を含むコンピュータ・プログラム(computer program product)が提供される。このコンピュータ可読プログラムは、コンピューティング・デバイス上で実行されると、方法の例示的な実施形態に関して上記で概要を示した動作のうちの様々な動作ならびにそれらの組み合わせをコンピューティング・デバイスに実行させる。

【0029】

さらに他の例示的な実施形態では、データ処理システムが提供される。このデータ処理システムは、第1のホスト・システムと、第2のホスト・システムと、第1のホスト・システムおよび第2のホスト・システムを結合する通信ファブリックとを含むことができる。このデータ処理システムは、方法の例示的な実施形態に関して上記で概要を示した動作のうちの様々な動作ならびにそれらの組み合わせを実行することができる。

【0030】

本発明の上記その他の特徴および利点は、本発明の典型的な諸実施形態に関する以下の詳細な説明に記載され、その詳細な説明を考慮すると、当業者には自明なものになるであろう。

【0031】

本発明に特有と思われる新規の特徴は特許請求の範囲に規定されている。しかし、本発明そのもの、ならびにその好ましい使用態様、他の目的および利点は、添付図面に併せて読んだときに、例示的な一実施形態に関する以下の詳細な説明を参照することによって最もよく理解されるであろう。

【発明を実施するための最良の形態】

【0032】

例示的な諸実施形態は、同じかまたは異なるルート・ノード、たとえば、ブレード・サーバのブレード上にある可能性のある、同じかまたは異なるルート複合体の2つまたはそれ以上のシステム・イメージ(SI)によって1つのPCIeアダプタまたは「エンドポイント」を固有に共用できるようにするメカニズムを提供する。さらに、例示的な諸実施形態は、それによりシステム・イメージと固有に共用されるエンドポイントとの間の通信を容易にするメカニズムを提供する。加えて、例示的な諸実施形態は、PCIeファブリックの管理を容易にするために、仮想プレーン、ルート複合体、およびシステム・イメージ間で仮想機能を移行するためのメカニズムを提供する。その上、例示的な諸実施形態は、それによりエンドポイントを設計するときにエンドポイント・インプリメンタが許可した機能の有効な組み合わせをルート複合体の単一ルートPCIマネージャ(SR−PCIM)がエンドポイントから読み取ることができるメカニズムを提供する。その場合、SR−PCIMは、エンドポイントが使用されている現行構成で使用されることになる機能の組み合わせを設定することができる。

【0033】

図2は、一般に当技術分野で知られているシステム仮想化を例示する典型的な図である。システム仮想化とは、各セットのリソースがそれ専用のシステム・イメージ・インスタンスおよびアプリケーションにより独立して動作するように物理システムのプロセッサ、メモリ、入出力アダプタ、記憶域、およびその他のリソースを分割することである。このようなシステム仮想化では、仮想リソースは、物理リソースから構成され、たとえば、同じ外部インターフェースおよび機能を有し、設計されたインターフェース/機能を備えたメモリ、ディスク・ドライブ、およびその他のハードウェア・コンポーネントなどの物理リソース用のプロキシとして動作する。システム仮想化は、典型的には、仮想リソースを作成し、それを物理リソースにマッピングし、それにより仮想リソース間の分離を可能にする仮想化仲介を使用する。仮想化仲介は、典型的には、ソフトウェア、ファームウェア、およびハードウェア・メカニズムのうちの1つまたはこれらの組み合わせとして提供される。

【0034】

図2に図示されている通り、仮想化システムにおいて典型的には、アプリケーション210は、それにより特定の仮想リソースおよび物理リソースが割り当てられる汎用または特殊目的オペレーティング・システムなどのソフトウェア・コンポーネントであるシステム・イメージ(SI)220と通信する。システム・イメージ220は、単一SIインスタンスを実行するために必要な物理リソースまたは仮想化リソース、たとえば、仮想化プロセッサ、メモリ、入出力アダプタ、記憶域などから構成される仮想システム230に関連付けられている。

【0035】

システム・イメージ220は、仮想システム230の使用により、仮想化仲介240を介して物理システム・リソース250にアクセスする。仮想化仲介240は、SIへのリソースの割り振りを管理し、SIに割り当てられたリソースを他のSIによるアクセスから分離する。この割り振りおよび分離は、仮想化仲介240によって実行されるリソース・マッピングならびに仮想化仲介240によって維持される1つまたは複数のリソース・マッピング・データ構造に基づいて実行される場合が多い。

【0036】

このような仮想化を使用して、入出力動作および入出力リソースの仮想化を可能にすることができる。すなわち、入出力仮想化(IOV:I/O virtualization)に関しては、仮想化仲介240などの入出力仮想化仲介(IOVI:I/O virtualizationintermediary)を使用して、2つ以上のSIによって単一の物理入出力装置を共用することができる。IOVIは、たとえば、SIからの構成、入出力、およびメモリ動作、ならびにSIへの直接メモリ・アクセス(DMA)、完了、および割り込み動作のうちの1つまたは複数に介入することによりIOVをサポートするために使用されるソフトウェア、ファームウェアなどにすることができる。

【0037】