データ処理装置、データ処理方法、及びプログラム

【課題】誤差を適切に考慮した処理を行う。

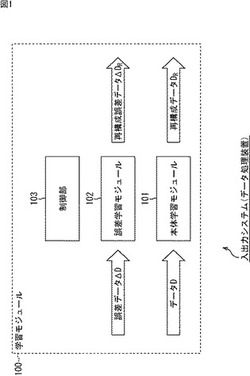

【解決手段】本体学習モジュール101は、データを学習する。誤差学習モジュール102は、データと、本体学習モジュール101がデータを再構成した再構成データとの誤差を学習する。また、本体学習モジュール101は、データの入力があると、そのデータを再構成して、再構成データを出力し、誤差学習モジュール102は、データと、再構成データとの誤差データを再構成して、再構成誤差データを出力する。そして、学習モジュール100は、再構成データと、再構成誤差データとを加算して出力する。本発明は、例えば、ロボット等に適用できる。

【解決手段】本体学習モジュール101は、データを学習する。誤差学習モジュール102は、データと、本体学習モジュール101がデータを再構成した再構成データとの誤差を学習する。また、本体学習モジュール101は、データの入力があると、そのデータを再構成して、再構成データを出力し、誤差学習モジュール102は、データと、再構成データとの誤差データを再構成して、再構成誤差データを出力する。そして、学習モジュール100は、再構成データと、再構成誤差データとを加算して出力する。本発明は、例えば、ロボット等に適用できる。

Notice: Undefined index: DEJ in /mnt/www/gzt_disp.php on line 298

【特許請求の範囲】

【請求項1】

データを学習する学習処理を行うデータ処理装置において、

データを学習する本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習する誤差学習モジュールと

を有する学習モジュールを備える

データ処理装置。

【請求項2】

前記本体学習モジュールは、入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行い、

前記誤差学習モジュールは、前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行う

請求項1に記載のデータ処理装置。

【請求項3】

前記本体学習モジュールは、

前記入力データの学習用のSOM(Self-Organization Map)である入力本体SOMと、前記出力データの学習用のSOMである出力本体SOMとのノードどうしが結合された本体入出力関係モデルを有し、

前記入力本体SOMの自己組織的な学習を、前記入力データを用いて行い、

前記出力本体SOMの自己組織的な学習を、前記出力データを用いて行い、

前記入力本体SOMを構成する複数のノードのうちの、前記入力データに対する勝者ノードと、前記出力本体SOMを構成する複数のノードのうちの、前記出力データに対する勝者ノードとの結合の度合いを強めるように、ノードどうしの結合の度合いを表す結合重みを更新し、

前記誤差学習モジュールは、

前記入力誤差の学習用のSOMである入力誤差SOMと、前記出力誤差の学習用のSOMである出力誤差SOMとのノードどうしが結合された誤差入出力関係モデルを有し、

前記入力誤差SOMの自己組織的な学習を、前記入力誤差を用いて行い、

前記出力誤差SOMの自己組織的な学習を、前記出力誤差を用いて行い、

前記入力誤差SOMを構成する複数のノードのうちの、前記入力誤差に対する勝者ノードと、前記出力誤差SOMを構成する複数のノードのうちの、前記出力誤差に対する勝者ノードとの結合の度合いを強めるように、ノードどうしの結合の度合いを表す結合重みを更新する

請求項2に記載のデータ処理装置。

【請求項4】

前記本体学習モジュールは、さらに、

前記入力本体SOMを構成する複数のノードの中から、前記入力データに対する勝者ノードを決定し、

前記入力本体SOMの勝者ノードを用いて、前記入力データを再構成して、前記再構成入力データを出力し、

前記入力本体SOMの勝者ノードとの結合が最も強い前記出力本体SOMのノードを用いて、前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、さらに、

前記入力誤差SOMを構成する複数のノードの中から、前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対する勝者ノードを決定し、

前記入力誤差SOMの勝者ノードとの結合が最も強い前記出力誤差SOMのノードを用いて、前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

請求項3に記載のデータ処理装置。

【請求項5】

前記本体学習モジュールは、

前記入力データの学習用のSOM(Self-Organization Map)である入力本体SOMと、前記出力データの学習用のSOMである出力本体SOMとのノードどうしが結合された本体入出力関係モデルを有し、

前記入力本体SOMを構成する複数のノードの中から、前記入力データに対する勝者ノードを決定し、

前記入力本体SOMの勝者ノードを用いて、前記入力データを再構成して、前記再構成入力データを出力し、

前記入力本体SOMの勝者ノードとの結合が最も強い前記出力本体SOMのノードを用いて、前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力誤差の学習用のSOMである入力誤差SOMと、前記出力誤差の学習用のSOMである出力誤差SOMとのノードどうしが結合された誤差入出力関係モデルを有し、

前記入力誤差SOMを構成する複数のノードの中から、前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対する勝者ノードを決定し、

前記入力誤差SOMの勝者ノードとの結合が最も強い前記出力誤差SOMのノードを用いて、前記出力誤差を再構成して、再構成出力誤差を出力し、

前記本体学習モジュールは、

前記入力本体SOMの自己組織的な学習を、前記再構成出力データと前記再構成出力誤差とを加算した加算データに対応する入力データである対応データを用いて行い、

前記出力本体SOMの自己組織的な学習を、前記加算データを用いて行い、

前記入力本体SOMを構成する複数のノードのうちの、前記対応データに対する勝者ノードと、前記出力本体SOMを構成する複数のノードのうちの、前記加算データに対する勝者ノードとの結合の度合いを強めるように、前記本体入出力関係モデルの前記結合重みを更新し、

前記誤差学習モジュールは、

前記入力誤差SOMの自己組織的な学習を、前記対応データと、前記本体学習モジュールが前記対応データを再構成した再構成対応データとの誤差を、前記入力誤差として用いて行い、

前記出力誤差SOMの自己組織的な学習を、前記加算データと、前記本体学習モジュールが前記加算データを再構成した再構成加算データとの誤差を、前記出力誤差として用いて行い、

前記入力誤差SOMを構成する複数のノードのうちの、前記入力誤差に対する勝者ノードと、前記出力誤差SOMを構成する複数のノードのうちの、前記出力誤差に対する勝者ノードとの結合の度合いを強めるように、前記誤差入出力関係モデルの前記結合重みを更新する

請求項2に記載のデータ処理装置。

【請求項6】

前記対応データが、前記再構成出力データに対応する入力データよりも、目標とする入力データに類似している場合に、

前記本体学習モジュールは、前記入力本体SOMの自己組織的な学習、前記出力本体SOMの自己組織的な学習、及び、前記本体入出力関係モデルの前記結合重みの更新を行い、

前記誤差学習モジュールは、前記入力誤差SOMの自己組織的な学習、前記出力誤差SOMの自己組織的な学習、及び、前記誤差入出力関係モデルの前記結合重みの更新を行う

請求項5に記載のデータ処理装置。

【請求項7】

前記本体学習モジュールは、さらに、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、さらに、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

請求項2に記載のデータ処理装置。

【請求項8】

前記本体学習モジュールは、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記本体学習モジュールは、

前記入力データの学習として、前記再構成出力データと前記再構成出力誤差とを加算した加算データに対応する入力データである対応データの学習を行い、

前記入力データの学習として、前記加算データの学習を行い、

前記誤差学習モジュールは、

前記入力誤差の学習として、前記対応データと、前記本体学習モジュールが前記対応データを再構成した再構成対応データとの誤差の学習を行い、

前記出力誤差の学習として、前記加算データと、前記本体学習モジュールが前記加算データを再構成した再構成加算データとの誤差の学習を行う

請求項2に記載のデータ処理装置。

【請求項9】

前記本体学習モジュールは、

前記データの学習用のSOM(Self-Organization Map)である本体SOMを有し、

前記本体SOMの自己組織的な学習を、前記データを用いて行い、

前記誤差学習モジュールは、

前記誤差の学習用のSOMである誤差SOMを有し、

前記誤差SOMの自己組織的な学習を、前記誤差を用いて行う

請求項1に記載のデータ処理装置。

【請求項10】

前記本体学習モジュールは、さらに、

前記本体SOMを構成する複数のノードの中から、前記データに対する勝者ノードを決定し、

前記本体SOMの勝者ノードを用いて、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、さらに、

前記誤差SOMを構成する複数のノードの中から、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差に対する勝者ノードを決定し、

前記誤差SOMの勝者ノードを用いて、前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

請求項9に記載のデータ処理装置。

【請求項11】

前記本体学習モジュールは、さらに、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、さらに、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

請求項1に記載のデータ処理装置。

【請求項12】

データを学習する学習処理を行うデータ処理装置のデータ処理方法において、

データを学習する本体学習モジュールにおいて、前記データを学習し、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習する誤差学習モジュールにおいて、前記誤差を学習する

ステップを含むデータ処理方法。

【請求項13】

データを学習する学習処理を行うデータ処理装置として、コンピュータを機能させるプログラムにおいて、

データを学習する本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習する誤差学習モジュールと

を有する学習モジュールを備える

データ処理装置として、コンピュータを機能させるプログラム。

【請求項14】

データを出力するデータ処理装置において、

入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行った前記本体学習モジュールと、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行った誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

データ処理装置。

【請求項15】

前記本体学習モジュールは、

前記入力データの学習用のSOM(Self-Organization Map)である入力本体SOMと、前記出力データの学習用のSOMである出力本体SOMとのノードどうしが結合された本体入出力関係モデルを有し、

前記入力本体SOMを構成する複数のノードの中から、前記入力データに対する勝者ノードを決定し、

前記入力本体SOMの勝者ノードを用いて、前記入力データを再構成して、前記再構成入力データを出力し、

前記入力本体SOMの勝者ノードとの結合が最も強い前記出力本体SOMのノードを用いて、前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力誤差の学習用のSOMである入力誤差SOMと、前記出力誤差の学習用のSOMである出力誤差SOMとのノードどうしが結合された誤差入出力関係モデルを有し、

前記入力誤差SOMを構成する複数のノードの中から、前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対する勝者ノードを決定し、

前記入力誤差SOMの勝者ノードとの結合が最も強い前記出力誤差SOMのノードを用いて、前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

請求項14に記載のデータ処理装置。

【請求項16】

データを出力するデータ処理装置のデータ処理方法において、

前記データ処理装置は、

入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行った前記本体学習モジュールと、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行った誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールにおいて、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールにおいて、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールにおいて、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

ステップを含むデータ処理方法。

【請求項17】

データを出力するデータ処理装置として、コンピュータを機能させるプログラムにおいて、

入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行った前記本体学習モジュールと、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行った誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

データ処理装置として、コンピュータを機能させるプログラム。

【請求項18】

データを出力するデータ処理装置において、

データを学習した本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習した誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

データ処理装置。

【請求項19】

前記本体学習モジュールは、

前記データの学習用のSOM(Self-Organization Map)である本体SOMを有し、

前記本体SOMを構成する複数のノードの中から、前記データに対する勝者ノードを決定し、

前記本体SOMの勝者ノードを用いて、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、

前記誤差の学習用のSOMである誤差SOMを有し、

前記誤差SOMを構成する複数のノードの中から、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差に対する勝者ノードを決定し、

前記誤差SOMの勝者ノードを用いて、前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

請求項18に記載のデータ処理装置。

【請求項20】

データを出力するデータ処理装置のデータ処理方法において、

前記データ処理装置は、

データを学習した本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習した誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールにおいて、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールにおいて、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールにおいて、前記再構成データと、前記再構成誤差とを加算して出力する

ステップを含むデータ処理方法。

【請求項21】

データを出力するデータ処理装置として、コンピュータを機能させるプログラムにおいて、

データを学習した本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習した誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

データ処理装置として、コンピュータを機能させるプログラム。

【請求項1】

データを学習する学習処理を行うデータ処理装置において、

データを学習する本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習する誤差学習モジュールと

を有する学習モジュールを備える

データ処理装置。

【請求項2】

前記本体学習モジュールは、入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行い、

前記誤差学習モジュールは、前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行う

請求項1に記載のデータ処理装置。

【請求項3】

前記本体学習モジュールは、

前記入力データの学習用のSOM(Self-Organization Map)である入力本体SOMと、前記出力データの学習用のSOMである出力本体SOMとのノードどうしが結合された本体入出力関係モデルを有し、

前記入力本体SOMの自己組織的な学習を、前記入力データを用いて行い、

前記出力本体SOMの自己組織的な学習を、前記出力データを用いて行い、

前記入力本体SOMを構成する複数のノードのうちの、前記入力データに対する勝者ノードと、前記出力本体SOMを構成する複数のノードのうちの、前記出力データに対する勝者ノードとの結合の度合いを強めるように、ノードどうしの結合の度合いを表す結合重みを更新し、

前記誤差学習モジュールは、

前記入力誤差の学習用のSOMである入力誤差SOMと、前記出力誤差の学習用のSOMである出力誤差SOMとのノードどうしが結合された誤差入出力関係モデルを有し、

前記入力誤差SOMの自己組織的な学習を、前記入力誤差を用いて行い、

前記出力誤差SOMの自己組織的な学習を、前記出力誤差を用いて行い、

前記入力誤差SOMを構成する複数のノードのうちの、前記入力誤差に対する勝者ノードと、前記出力誤差SOMを構成する複数のノードのうちの、前記出力誤差に対する勝者ノードとの結合の度合いを強めるように、ノードどうしの結合の度合いを表す結合重みを更新する

請求項2に記載のデータ処理装置。

【請求項4】

前記本体学習モジュールは、さらに、

前記入力本体SOMを構成する複数のノードの中から、前記入力データに対する勝者ノードを決定し、

前記入力本体SOMの勝者ノードを用いて、前記入力データを再構成して、前記再構成入力データを出力し、

前記入力本体SOMの勝者ノードとの結合が最も強い前記出力本体SOMのノードを用いて、前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、さらに、

前記入力誤差SOMを構成する複数のノードの中から、前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対する勝者ノードを決定し、

前記入力誤差SOMの勝者ノードとの結合が最も強い前記出力誤差SOMのノードを用いて、前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

請求項3に記載のデータ処理装置。

【請求項5】

前記本体学習モジュールは、

前記入力データの学習用のSOM(Self-Organization Map)である入力本体SOMと、前記出力データの学習用のSOMである出力本体SOMとのノードどうしが結合された本体入出力関係モデルを有し、

前記入力本体SOMを構成する複数のノードの中から、前記入力データに対する勝者ノードを決定し、

前記入力本体SOMの勝者ノードを用いて、前記入力データを再構成して、前記再構成入力データを出力し、

前記入力本体SOMの勝者ノードとの結合が最も強い前記出力本体SOMのノードを用いて、前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力誤差の学習用のSOMである入力誤差SOMと、前記出力誤差の学習用のSOMである出力誤差SOMとのノードどうしが結合された誤差入出力関係モデルを有し、

前記入力誤差SOMを構成する複数のノードの中から、前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対する勝者ノードを決定し、

前記入力誤差SOMの勝者ノードとの結合が最も強い前記出力誤差SOMのノードを用いて、前記出力誤差を再構成して、再構成出力誤差を出力し、

前記本体学習モジュールは、

前記入力本体SOMの自己組織的な学習を、前記再構成出力データと前記再構成出力誤差とを加算した加算データに対応する入力データである対応データを用いて行い、

前記出力本体SOMの自己組織的な学習を、前記加算データを用いて行い、

前記入力本体SOMを構成する複数のノードのうちの、前記対応データに対する勝者ノードと、前記出力本体SOMを構成する複数のノードのうちの、前記加算データに対する勝者ノードとの結合の度合いを強めるように、前記本体入出力関係モデルの前記結合重みを更新し、

前記誤差学習モジュールは、

前記入力誤差SOMの自己組織的な学習を、前記対応データと、前記本体学習モジュールが前記対応データを再構成した再構成対応データとの誤差を、前記入力誤差として用いて行い、

前記出力誤差SOMの自己組織的な学習を、前記加算データと、前記本体学習モジュールが前記加算データを再構成した再構成加算データとの誤差を、前記出力誤差として用いて行い、

前記入力誤差SOMを構成する複数のノードのうちの、前記入力誤差に対する勝者ノードと、前記出力誤差SOMを構成する複数のノードのうちの、前記出力誤差に対する勝者ノードとの結合の度合いを強めるように、前記誤差入出力関係モデルの前記結合重みを更新する

請求項2に記載のデータ処理装置。

【請求項6】

前記対応データが、前記再構成出力データに対応する入力データよりも、目標とする入力データに類似している場合に、

前記本体学習モジュールは、前記入力本体SOMの自己組織的な学習、前記出力本体SOMの自己組織的な学習、及び、前記本体入出力関係モデルの前記結合重みの更新を行い、

前記誤差学習モジュールは、前記入力誤差SOMの自己組織的な学習、前記出力誤差SOMの自己組織的な学習、及び、前記誤差入出力関係モデルの前記結合重みの更新を行う

請求項5に記載のデータ処理装置。

【請求項7】

前記本体学習モジュールは、さらに、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、さらに、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

請求項2に記載のデータ処理装置。

【請求項8】

前記本体学習モジュールは、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記本体学習モジュールは、

前記入力データの学習として、前記再構成出力データと前記再構成出力誤差とを加算した加算データに対応する入力データである対応データの学習を行い、

前記入力データの学習として、前記加算データの学習を行い、

前記誤差学習モジュールは、

前記入力誤差の学習として、前記対応データと、前記本体学習モジュールが前記対応データを再構成した再構成対応データとの誤差の学習を行い、

前記出力誤差の学習として、前記加算データと、前記本体学習モジュールが前記加算データを再構成した再構成加算データとの誤差の学習を行う

請求項2に記載のデータ処理装置。

【請求項9】

前記本体学習モジュールは、

前記データの学習用のSOM(Self-Organization Map)である本体SOMを有し、

前記本体SOMの自己組織的な学習を、前記データを用いて行い、

前記誤差学習モジュールは、

前記誤差の学習用のSOMである誤差SOMを有し、

前記誤差SOMの自己組織的な学習を、前記誤差を用いて行う

請求項1に記載のデータ処理装置。

【請求項10】

前記本体学習モジュールは、さらに、

前記本体SOMを構成する複数のノードの中から、前記データに対する勝者ノードを決定し、

前記本体SOMの勝者ノードを用いて、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、さらに、

前記誤差SOMを構成する複数のノードの中から、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差に対する勝者ノードを決定し、

前記誤差SOMの勝者ノードを用いて、前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

請求項9に記載のデータ処理装置。

【請求項11】

前記本体学習モジュールは、さらに、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、さらに、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

請求項1に記載のデータ処理装置。

【請求項12】

データを学習する学習処理を行うデータ処理装置のデータ処理方法において、

データを学習する本体学習モジュールにおいて、前記データを学習し、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習する誤差学習モジュールにおいて、前記誤差を学習する

ステップを含むデータ処理方法。

【請求項13】

データを学習する学習処理を行うデータ処理装置として、コンピュータを機能させるプログラムにおいて、

データを学習する本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習する誤差学習モジュールと

を有する学習モジュールを備える

データ処理装置として、コンピュータを機能させるプログラム。

【請求項14】

データを出力するデータ処理装置において、

入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行った前記本体学習モジュールと、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行った誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

データ処理装置。

【請求項15】

前記本体学習モジュールは、

前記入力データの学習用のSOM(Self-Organization Map)である入力本体SOMと、前記出力データの学習用のSOMである出力本体SOMとのノードどうしが結合された本体入出力関係モデルを有し、

前記入力本体SOMを構成する複数のノードの中から、前記入力データに対する勝者ノードを決定し、

前記入力本体SOMの勝者ノードを用いて、前記入力データを再構成して、前記再構成入力データを出力し、

前記入力本体SOMの勝者ノードとの結合が最も強い前記出力本体SOMのノードを用いて、前記入力データに対して出力すべき前記出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力誤差の学習用のSOMである入力誤差SOMと、前記出力誤差の学習用のSOMである出力誤差SOMとのノードどうしが結合された誤差入出力関係モデルを有し、

前記入力誤差SOMを構成する複数のノードの中から、前記入力データと、前記本体学習モジュールが出力する前記再構成入力データとの前記入力誤差に対する勝者ノードを決定し、

前記入力誤差SOMの勝者ノードとの結合が最も強い前記出力誤差SOMのノードを用いて、前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

請求項14に記載のデータ処理装置。

【請求項16】

データを出力するデータ処理装置のデータ処理方法において、

前記データ処理装置は、

入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行った前記本体学習モジュールと、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行った誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールにおいて、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールにおいて、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールにおいて、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

ステップを含むデータ処理方法。

【請求項17】

データを出力するデータ処理装置として、コンピュータを機能させるプログラムにおいて、

入力データの学習、及び、前記入力データに対して出力すべき出力データの学習を行った前記本体学習モジュールと、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差の学習、及び、前記出力データと、前記本体学習モジュールが前記出力データを再構成した再構成出力データとの誤差である出力誤差の学習を行った誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、

前記入力データを再構成して、前記再構成入力データを出力し、

前記入力データに対して出力すべき出力データを再構成して、前記再構成出力データを出力し、

前記誤差学習モジュールは、

前記入力データと、前記本体学習モジュールが前記入力データを再構成した再構成入力データとの誤差である入力誤差に対応する前記出力誤差を再構成して、再構成出力誤差を出力し、

前記学習モジュールは、前記再構成出力データと、前記再構成出力誤差とを加算して出力する

データ処理装置として、コンピュータを機能させるプログラム。

【請求項18】

データを出力するデータ処理装置において、

データを学習した本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習した誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

データ処理装置。

【請求項19】

前記本体学習モジュールは、

前記データの学習用のSOM(Self-Organization Map)である本体SOMを有し、

前記本体SOMを構成する複数のノードの中から、前記データに対する勝者ノードを決定し、

前記本体SOMの勝者ノードを用いて、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、

前記誤差の学習用のSOMである誤差SOMを有し、

前記誤差SOMを構成する複数のノードの中から、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差に対する勝者ノードを決定し、

前記誤差SOMの勝者ノードを用いて、前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

請求項18に記載のデータ処理装置。

【請求項20】

データを出力するデータ処理装置のデータ処理方法において、

前記データ処理装置は、

データを学習した本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習した誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールにおいて、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールにおいて、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールにおいて、前記再構成データと、前記再構成誤差とを加算して出力する

ステップを含むデータ処理方法。

【請求項21】

データを出力するデータ処理装置として、コンピュータを機能させるプログラムにおいて、

データを学習した本体学習モジュールと、

前記データと、前記本体学習モジュールが前記データを再構成した再構成データとの誤差を学習した誤差学習モジュールと

を有する学習モジュールを備え、

前記本体学習モジュールは、前記データを再構成して、前記再構成データを出力し、

前記誤差学習モジュールは、前記データと、前記本体学習モジュールが出力する前記再構成データとの前記誤差を再構成して、再構成誤差を出力し、

前記学習モジュールは、前記再構成データと、前記再構成誤差とを加算して出力する

データ処理装置として、コンピュータを機能させるプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

【図54】

【図55】

【図56】

【図57】

【図58】

【図59】

【図60】

【図61】

【図62】

【図63】

【図64】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

【図54】

【図55】

【図56】

【図57】

【図58】

【図59】

【図60】

【図61】

【図62】

【図63】

【図64】

【公開番号】特開2008−293259(P2008−293259A)

【公開日】平成20年12月4日(2008.12.4)

【国際特許分類】

【出願番号】特願2007−137873(P2007−137873)

【出願日】平成19年5月24日(2007.5.24)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成20年12月4日(2008.12.4)

【国際特許分類】

【出願日】平成19年5月24日(2007.5.24)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]