データ処理装置、データ処理方法、及びプログラム

【課題】 入力画像の画素数と出力画像の画素数の変動に対して、入力ローカルバッファや出力ローカルバッファの容量を適切に規定することが困難であった。

【解決手段】 データ処理装置は、画像データに含まれる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理後の画素値を画像処理手段から取得して出力画素領域を出力するデータ処理装置であって、入力画素領域のデータと、出力画素領域のデータとを一時的に記憶し、入力画素領域の画素数と、出力画素領域の画素数とに基づいて、入力画素領域のデータを記憶する入力領域と、出力画素領域のデータを記憶する出力領域との大きさを設定する。

【解決手段】 データ処理装置は、画像データに含まれる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理後の画素値を画像処理手段から取得して出力画素領域を出力するデータ処理装置であって、入力画素領域のデータと、出力画素領域のデータとを一時的に記憶し、入力画素領域の画素数と、出力画素領域の画素数とに基づいて、入力画素領域のデータを記憶する入力領域と、出力画素領域のデータを記憶する出力領域との大きさを設定する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像処理の前後における画像データを一時的に記憶するためのデータ処理装置、データ処理方法、及びプログラムに関する。

【背景技術】

【0002】

従来から、画像形成を行って出力する際に、空間フィルタ処理などによる局所(近傍)画像処理が行なわれている。局所画像処理では、処理対象となる画素(以下、処理画素と略称する)を含む空間フィルタ領域に対して、その領域のすべてまたは大半の画素を用いて所定の演算を行なう。

【0003】

この局所(近傍)画像処理の一つとして解像度変換がある。解像度変換とは、入力した画像を拡大、もしくは縮小して所望の大きさの画像に変換する処理である。解像度変換では、当然ながら入力画素数と処理後の出力画素数が大きく異なることとなるため、一般的な局所(近傍)画像処理に比べて装置化が難しくなる。例えば特許文献1では、遅延メモリと空間フィルタ処理との組み合わせを複数用いる場合で、それぞれの組み合わせの間で解像度変換を実行する場合、この処理の前後にある2つの遅延メモリが有効活用できないことを指摘している。

【0004】

この問題に対して、特許文献1は、拡大もしくは縮小によって入力された画像の主走査方向の画素数が変化する主走査変倍と呼ばれる解像度変換の処理を開示している。特許文献1の技術では、解像度変換の前後にある2つの空間フィルタが二次元領域の処理画素について演算を行っており、この2つの空間フィルタに各々遅延メモリが必要となる。そして、特許文献1は、この2つの遅延メモリと画素数の変化とに着目してメモリを有効活用する技術が記載されている。また特許文献1では、画像を主走査、副走査方向共に二次元に領域分割して、分割後の画素領域について逐次的に画像処理を行う、ブロック(タイル)処理を採用している。

【0005】

一方、特許文献2には、上記のブロック(タイル)処理と類似の技術のバンド処理技術が記載されている。バンド処理では、画像を主走査方向にのみ一次元的に領域分割して、分割後の画素領域について逐次的に画像処理を行うものである。このような技術では、各バンド領域間で隙間なく局所(近傍)画像処理を行なうために、各バンド領域が、それぞれ隣接する領域との境界で一部分が互いに重なり合うように工夫している。また特許文献2では、各バンド領域の高さと同一の方向に1画素ずつ画素を走査することで、局所(近傍)画像処理に必要な処理画素を保持する遅延メモリの容量を各バンド領域の高さの大きさで規定する。これにより、特許文献2では、この遅延メモリの省メモリ化を実現している。

【0006】

特許文献1のブロック(タイル)処理と同様、特許文献2のバンド処理も領域分割して逐次的、もしくは分散並列的に画像処理を行う手法である。以後、このような手法を領域分割手法と総称する。これらの領域分割手法にとって相性の良くない画像処理は、特許文献1で言及する解像度変換だけではない。

【0007】

例えば、プリンタ画像処理などで使用される、トリミング処理や端部拡張処理などもあげられる。トリミング処理とは画像を部分的に削除する処理で、入力画像より出力画像の方が画素数は少なくなる。また端部拡張とは画像の端部の画素のみ、所定画素数だけコピー拡張したり、特定色の画素で拡張したりする処理で、入力画像より出力画像の方が画素数は多くなる。

【0008】

また、映像処理などで使用される、IP変換などもあげられる。IP変換とは、副走査方向に画素が間引かれたインターレース画像を、時間軸方向に複数フレーム用いて1フレームの画素が間引かれていないプログレッシブ画像を合成する処理である。例えば、2フレームのインターレース画像から1フレームのプログレッシブ画像を合成する場合、入力画像の総画素数と出力画像の画素数は同じとなる。しかしながら高品位なIP変換では、3〜5フレームのインターレース画像から1フレームのプログレッシブ画像を合成することになるので、入力画像より出力画像の方が画素数は少なくなる。IP変換の例では、ユーザが選択した動作モード(画質モード)により、入力画像と出力画像の画素数の関係が変わることになる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2010−087804号公報

【特許文献2】特開2006−139606号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

近年の画像処理装置は、上述のような空間フィルタ処理、解像度変換、トリミング処理、端部拡張処理、IP変換を含め、様々な画像処理を多く内包する。そして画像処理装置は、装置全体で所望の高画質化を実現するために、それらの処理をアプリケーションに応じて取捨選択して組み合せて用いることが多い。

【0011】

しかしながら、このような複数の処理の組合せを領域分割手法で実現する場合、さらなる注意が必要となる。空間フィルタ処理のように二次元領域の処理画素を用いて演算する場合、フィルタが取り扱う画素のサイズに対応して周辺画素を累積し、画像を処理する必要がある。そして空間フィルタ処理が複数回あれば、その都度、周辺画素を累積し、すべての周辺画素を累積した、より広い範囲の画像について処理を行う必要がある。

【0012】

さらに、映像処理のクロマ・アップサンプリングのような空間フィルタ処理では、前述のように周辺画素を累積するだけでは不十分となる。このような空間フィルタ処理では、入力する処理画素の画像上での位相も考慮する必要がある。そのため、その空間フィルタ処理に入力する画像の縦や横の画素数が4の倍数でなければならないという特殊な制約を合わせ持つ。

【0013】

アプリケーションに応じて取捨選択して組み合された複数の処理に対し、各々の制約を満たしつつ、所望の画像処理を行うには、入力画像の画素数と出力画像の画素数との関係性を簡単に規定することができない。アプリケーションは、複数の空間フィルタ処理の周辺画素を累積した画像より、わざと余分な画素数の画像を処理する。アプリケーションは、場合によっては、処理後の画像の一部を最後にトリミング処理で削除し、所望の大きさの画像に調整することも必要となる。

【0014】

ここで、領域分割手法を用いる場合に、これらの多くの画像処理を取捨選択して組み合せた画像処理方法を、ハードウェアでいかに実現するかを考えることは重要である。

【0015】

ハードウェアを用いる画像処理装置では、一般的に、入力ローカルバッファと出力ローカルバッファを介して外部記憶装置と画像を互いに転送することで、各種部品の同時動作と部品間の連係動作を実現する。しかしながら、上述の通り、複数の処理を取捨選択して組み合せて画像処理をする場合、入力画像の画素数と出力画像の画素数は簡単には規定できない。そのため、入力ローカルバッファや出力ローカルバッファの容量を適切に規定することが難しく、過大なバッファを用意することによる利用効率の低下や、過小な記憶容量を用意することによる処理の停滞などの課題が生じる。

【0016】

特許文献1では、主走査変倍の前後にある2つのフィルタ処理(プレフィルタとポストフィルタ)の遅延メモリに着目している。しかしながら、特許文献1では様々な複数の画像処理を取捨選択して組み合せるための画像処理方法を実現するためのハードウェア構成としての画像処理装置については検討されていない。このため、特許文献1では、前述のような入力する画像と出力する画像の画素数の様々なバリエーションに対応する方法については、有用な解決策を開示していない。また特許文献1では、画像を外部記憶装置から読み込むときに必要となる入力ローカルバッファと、処理後の画像を外部記憶装置へ書き出すときに必要となる出力ローカルバッファに着目した有用な解決策を開示していない。

【0017】

本発明は、上記課題に鑑みてなされたもので、様々な処理を組み合わせた画像処理により入力と出力の画素数が変動する条件において、入力画像と出力画像とを一時的に記憶する記憶装置の効率的な利用を可能とする技術を実現することを目的としている。

【課題を解決するための手段】

【0018】

上記目的を達成するため、本発明によるデータ処理装置は、画像データに含まれる1つ以上の画素からなる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して出力画素領域を出力するデータ処理装置であって、前記入力画素領域のデータと、前記出力画素領域のデータとを一時的に記憶する記憶手段と、前記入力画素領域の画素数と、前記出力画素領域の画素数とに基づいて、前記入力画素領域のデータを記憶する前記記憶手段の入力領域の大きさと、前記出力画素領域のデータを記憶する前記記憶手段の出力領域の大きさとを設定する設定手段と、を有することを特徴とする。

【発明の効果】

【0019】

本発明によれば、入力と出力の画素数が変動する条件において、入力画像と出力画像とを一時的に記憶する記憶装置の効率的な利用を可能とするデータ処理装置、データ処理方法およびプログラムを提供することができる。

【図面の簡単な説明】

【0020】

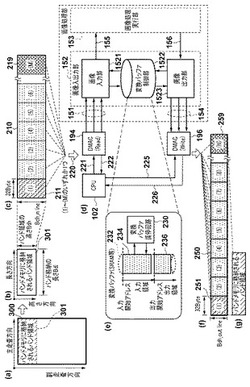

【図1A】画像処理装置の全体構成と画像処理部の構成例を示すブロック図。

【図1B】画像処理装置の全体構成と画像処理部の構成例を示すブロック図。

【図2】画像データの入出力に係る動作例を示す図。

【図3】バンド処理の動作の例を説明する図。

【図4A】画像データの格納方法とデータ構造の例を説明する図。

【図4B】画像データの格納方法とデータ構造の例を説明する図。

【図5】従来の画像処理装置の動作例を説明する図。

【図6】本発明の画像処理装置の動作例を説明する図。

【図7】別の例に係る画像処理部の一例を説明するブロック図。

【発明を実施するための形態】

【0021】

以下、添付図面を参照して本発明の実施の形態を詳細に説明する。

【0022】

<<実施形態1>>

(画像処理装置)

図1Aは、本実施形態に係る画像処理装置の全体構成の一例を示すブロック図である。画像処理装置は、例えば、CPU回路部100、画像読み取り部120、画像処理部150を備える。

【0023】

画像読み取り部120は、レンズ124、CCDセンサ126、及びアナログ信号処理部127等を有する。画像読み取り部120では、レンズ124を介してCCDセンサ126に原稿110の画像情報が結像され、CCDセンサ126によりその画像情報がR(Red)、G(Green)、B(Blue)のアナログ電気信号に変換される。アナログ電気信号に変換された画像情報は、アナログ信号処理部127に入力され、R、G、Bの色毎に補正等が行われた後にアナログ/デジタル変換(A/D変換)される。こうして、デジタル化されたフルカラーのデジタル画像信号(画素値)が生成される。生成されたデジタル画像信号は、映像入力部130へ入力され、その後、DMAC(Direct Memory Access Controller)192へ入力される。

【0024】

DMAC192は、CPU102により予め動作が設定されており、共有バス190を介して、入力されたデジタル画像信号をCPU回路部100のRAM106に記憶させる。なお、複数の画素についてのデジタル画像信号を、1枚の画像を形成するように集合させたデータを、以下では画像データと呼ぶ。本実施形態では、デジタル画像信号は画像データの形式でRAM106に記憶されるものとする。画像処理を行う場合、CPU102はDMAC194を起動してRAM106に記憶された画像データを読み出させ、処理の対象となる画素に対応するデジタル画像信号を画像処理部150に入力させる。

【0025】

画像処理部150は、例えば、入力されたデジタル画像信号に対して、例えば、スキャナなどのセンサ・デバイスの読み取り素子の個体差の補正と入力ガンマ補正などの色補正とを行い、画像データを作成するデータ処理装置である。そして、DMAC196は、これらの処理が施された画像データをRAM106に格納する。なお、DMAC196の制御については、例えばCPU102が予めDMAC196の動作を設定し、また、CPU102がDMAC196を起動するようにする。なお、DMAC196の動作は、例えば処理後の画像データをRAM106へ書き込むように設定しておく。

【0026】

これにより、例えば、画像処理部150は入力されたデジタル画像信号に対し、入力色補正処理、空間フィルタ処理、色空間変換、濃度補正処理、及び中間調処理などの、画像の印刷のための画像処理を施す。そして、画像処理部150は、印刷可能な画像データを作成し、その画像データはDMAC196によりRAM106に格納させる。

【0027】

DMAC198は、RAM106に格納された画像処理済みの画像データを読み出して画像印刷部170へ出力する。画像印刷部170は例えばプリンタである。DMAC198の設定は例えばCPU102が行う。画像印刷部170は、たとえば、インクジェットヘッドやサーマルヘッド等を使用したラスタプロッタ等の印刷出力部(不図示)を備える。そして、入力された画像データのデジタル画像信号に基づいて紙上に画像を記録する。上述の説明では、画像印刷部170を用いる例を説明したがこれに限られない。例えば、映像入力部130や映像表示部160等を用いることにより、入力された映像に対し所望の画像(映像)処理を施し、処理後の映像をディスプレイなどの表示装置(不図示)に表示してもよい。

【0028】

CPU回路部100は、演算制御用のCPU102、固定データやプログラムを格納するROM104、データの一時保存やプログラムのロードに使用されるRAM106、及び外部記憶装置108等を備える。CPU回路部100は、画像読み取り部120、画像処理部150、及び画像印刷部170等を制御し、本実施形態の画像処理装置のシーケンスを統括的に制御する。外部記憶装置108は、本実施形態の画像処理装置が使用するパラメータやプログラムや補正データを記憶するディスク等の記憶媒体であり、RAM106のデータやプログラム等は、外部記憶装置108からロードされる構成としてもよい。

【0029】

(画像処理部)

続いて、画像データに画像処理を施す画像処理部150について図1Bを用いて詳細に説明する。CPU102がDMAC194を起動し、DMAC194はRAM106から画像データを読み出す。画像データのデータ構造については後述する。読み出された画像データは、入力ポート151を介して、画像処理部150の画像入出力部152へ入力される。画像入出力部152において、画像入力部1521は、画像データを取得すると、中間バッファ制御部1522に含まれる後述の記憶部(中間バッファ)に取得した画像データを記憶させる。そして、画像入力部1521は、中間バッファに一時的に記憶された画像データを読み出しながら画素値を生成し、入力画素値155として画像処理実行部153へ入力する。

【0030】

画像処理実行部153は、入力画素値155に対して所定の画像処理を実行し、出力画素値156を画像入出力部152へ出力する。画像処理実行部153の詳細については後述する。なお、ここでは、入力画素値155および出力画素値156は、1つ以上の画素値であり、例えば複数の画素値が入力画素値155として入力され、それに対して1つの画素値が出力画素値156として出力される。

【0031】

画像入出力部152では、画像出力部1523は、処理後の出力画素値156から出力画像データを生成して中間バッファ制御部1522内の記憶部(中間バッファ)に記憶する。画像出力部1523は、記憶部(中間バッファ)に一時的に記憶された処理後の画像データを読み出し、出力画像データとして出力ポート154を介してDMAC196へ送出する。DMAC196は前述の通り、CPU102により既に起動されており、受け取った出力画像データをRAM106へ書き出す。

【0032】

すなわち、画像処理部150では、画像入出力部152を介してDMAC194から画像データを取得し、画像処理実行部153で画像に対するデータ処理を実行し、データ処理後の画像データを画像入出力部152を介してDMAC196へ出力する。このようにして、画像処理部150は、画像処理装置内に含まれる画像データにデータ処理を施し、データ処理後の画像データを画像処理装置へ戻す役割を担う。また、画像入出力部152は、データの入出力の調節を行うデータ入出力制御装置としての役割を有する。

【0033】

(画像処理実行部)

次に、画像処理部150内の画像処理実行部153について詳細に説明する。画像処理実行部153は、画像処理回路(1)1531から画像処理回路(P)1537の、P個の画像処理回路と、インターコネクト1531とで構成される。P個の画像処理回路と、インターコネクト1531とは、入力ポート1532、1535、並びに1538、および出力ポート1533、1536、並びに1539等のポートを介して互いに接続される。

【0034】

画像処理回路は、例えば、入力色補正処理、色空間変換、濃度補正処理、中間調処理、空間フィルタ処理、解像度変換、トリミング処理、端部拡張処理、IP変換、クロマ・アップサンプリングのうち、1つの処理を行う。これらの画像処理回路は、パイプライン回路等のハードウェアで実現されてもよいし、プロセッサとプログラム(ソフトウェア)等で実現されてもよい。そして、例えば、入力ポート1532、1535、1538等から入力画素値155を受け取り、処理を施した後に、出力ポート1533、1536、1539から処理後の出力画素値156を出力する。

【0035】

また、インターコネクト1531はクロスバーやリングバス等の接続手段で実現されており、入力ポートと出力ポートの接続先を任意に切り替えることができる。したがって、CPU102がこれらポートの接続先の指定を設定することで、インターコネクト1531は、例えばP個の画像処理回路の実行順序を変更し、または一部の処理をバイパスすることができる。このように、画像処理実行部153は、アプリケーションに応じて、各種の処理を取捨選択して組み合せ、所望の画像処理を実現する。

【0036】

(領域分割)

次に、本実施形態における画像データの領域分割について説明する。本実施形態では、領域分割手法の1つであるバンド処理を用いるものとする。以下、バンド処理について、図3を用いて説明する。バンド処理では、図3(a)〜(d)に示されるように、1枚の画像データ300を帯状のバンド領域301〜304に分割し、この領域毎に逐次的に各種の画像処理を行う。なお、バンド領域は、画像データを主走査方向または副走査方向のいずれかにおいて分割したものであり、バンド領域と画像データとは、主走査方向または副走査方向のいずれかにおいて長さが一致する。例えば、図3(a)〜(d)では、画像データは副走査方向において分割され、画像データとバンド領域とでは、主走査方向について同一の長さを有し、副走査方向において異なる長さを有する。以下では、この分割された細長い領域をバンド領域と呼び、バンド領域が展開される記憶領域をバンドメモリと呼び、画像データを分割する行為をバンド分割と呼ぶ。バンドメモリは、RAM106内に記憶領域として確保されてもよく、また、システム上の適切な記憶領域に確保されてもよい。なお、ここでは説明を簡潔にするためにバンドメモリをRAM106に確保する場合を例に挙げて説明する。

【0037】

また、以下では、図3(e)に示すように、画像データの座標系(主走査方向−副走査方向)を、長さ方向、高さ方向という新たな座標系(バンド領域座標系)によって定義し、バンド領域を長さ×高さで表現する。バンド領域の長さ、すなわちバンド領域の長さ方向の一辺の大きさは、画像データの主走査方向の長さ、または副走査方向の長さの何れかの値とする。また、バンド領域の高さ、すなわちバンド領域の高さ方向の一辺の大きさは任意の値となる。例えば、図3(a)〜(d)では、長さ方向は主走査方向であり、高さ方向は副走査方向である。これに対し、図3(p)〜(r)のように、例えば画像データを主走査方向において分割した場合、図3(s)に示すように、長さ方向が副走査方向となり高さ方向が主走査方向となる。図3(p)〜(r)のようなバンド分割は、例えば画像データの主走査方向の大きさが副走査方向の大きさより大きい場合に行うようにしてもよい。

【0038】

バンド処理では、まず、図3(a)に示す第1のバンド領域301を、RAM106上のバンドメモリに展開して画像処理を行う。次に、図3(b)に示す第2のバンド領域302を、第1のバンド領域301が展開されたRAM106上のバンドメモリに上書き展開して、画像処理を行なう。さらにその後、図3(c)に示す第3のバンド領域303を、第2のバンド領域302が展開されたRAM106上のバンドメモリに上書き展開し、画像処理を行なう。最後に、図3(d)に示す第4のバンド領域304を、第3のバンド領域303が展開されたRAM106上のバンドメモリに上書き展開して画像処理を行なう。図3(a)〜(d)で明らかなように、バンド領域301〜304の長さは同じであるが、高さは同じでなくてもよい。したがって、メインメモリに確保される記憶領域であるバンドメモリの高さは、高さ方向の一辺の大きさが最も大きいバンド領域(図3の場合、第1〜第3のバンド領域301〜303)によって決定される。

【0039】

なお、バンド処理では、各バンド領域間で隙間なく空間フィルタ処理などの局所(近傍)画像処理を行なうため、図3(f)〜(h)のように、各バンド領域が、それぞれ隣接する領域との境界で一部分が互いに重なり合うようにする。

【0040】

(画像データのデータ構造)

次に、画像データのデータ構造の一例について詳細に説明する。本実施形態では、前述のように、画像データはRAM106に一時的に格納される。一般的にRAM106は安価なDRAMで構成されることが多い。したがって、前述のようにDMACを介して画像データを読み書きする場合、DRAMが性能を落とさずに読み書きできる単位で画像データを取り扱うことが望ましい。そこで、RAM106の画像データの格納方法の一例と、画像データのデータ構造の一例について、図4Aを用いて詳しく説明する。図4Aは、RAM106(DRAM)上にデータが格納された状態を示している。図4Aの例では、あるデータ領域(IMG_AREA_STR_ADDRからIMG_AREA_END_ADDRまでの領域)が確保され、ここに画像処理に必要な種々の画像データが格納される。

【0041】

図4Aは、点順次形式の画像データの構造のRAM106への格納例であり、RAM106(DRAM)のデータ領域に、S5_IMG425とS6_IMG426の2種の画像データが格納された例を示している。例では、DRAMの性能を落とさずに画像データを読み書きできるように、格納される画像データの容量の最小単位は、408に示すように、32bit×8wordの32Byteとしている。すなわち、S5_IMG425とS6_IMG426の画像データの格納容量は、32Byteの整数倍となる。

【0042】

次に、画像データのデータ構造を詳しく説明する。画像データ440は点順次形式で、R(Red)、G(Green)、B(Blue)の画素値を有する。画像データ440に含まれる1つの領域442は32Byte単位のデータであり、1つの領域442の中には、444で示すように、複数個(8つ)の画素値がパッキングされている。そして、444に含まれる8つの画素値のそれぞれには、446で示すようにそれぞれ10bitのR、G、Bの値がパッキングされている。なお、図の例では、残りの2bitは、DRAMへのアクセスを簡単にするための無効データであり、データを格納しないものとする。図中太線で表される画像データ440は、8M×N画素のサイズを有する。なお、上述の例では、縦1画素、横8画素を単位として32Byte単位のデータの領域442を定めた例を示したが、画像データ494の例のように、縦2画素、横4画素を単位とするデータの領域492を定めてもよい。

【0043】

(画像データの入出力方法)

図2は、本実施形態の画像処理方法を用いた場合の、RAM106から画像入出力部152への、または画像入出力部152からRAM106への、画像データの入出力方法についての説明図である。画像処理装置は、図2(a)及び図2(b)のように、1つの画像データ300からバンド領域301を抜き出し、入力画像データとしてRAM106に格納する。そして、このバンド領域の入力画像データは、図4Aで説明したように、RAM106で取り扱いやすくなるように、32Byteを単位としたデータ構造とする。データ構造を図2(c)の210に示す。

【0044】

図2(d)において、CPU102は、DMAC194に指示信号(図2(d)の221)を送信する。DMAC194は、図1の共有バス190を介して、このバンド領域の入力画像データ210をRAM106から読み出し、画像処理部150へ入力する。入力画像データ210は、先のデータ構造にしたがって、32Byte×Bdh_inの処理単位で、領域(1)211から領域(M)219までのM個の小さい画素領域(小領域)に分けられる。そして、DMAC194は、このM個の小領域(処理単位)の入力画像データを、小領域(1)211から小領域(M)219まで順番に1つずつ読み出し、画像処理部150に入力する。画像処理部150は、この小領域(処理単位)の入力画像データを受け取り、この単位で画像処理を実行する。なお、処理単位の大きさに応じて、図2(d)のようにバンドの一部の領域である小領域ごとに読出し処理を行ってもよいし、バンドの全部の画素領域に対して一度に読出し処理を行ってもよい。

【0045】

上記のCPU102のDMAC194への指示信号には、例えば、「読み出し先の先頭アドレス」、「連続読み出し量(32Byte単位のデータを連続何回読み出すか)」、「インクリメント・アドレス」および「繰り返し回数」が含まれる。例えば、図4Aの点順次形式の画像データでは以下の通りとする。

【0046】

・「先頭アドレス」:S5_IMG_STR_ADDR

・「連続読み出し量」:1回(32Byte)

・「インクリメント・アドレス」:1ラインのデータ量=32Byte×M

・「繰り返し数」:バンド領域の高さ=Bdh_in回

このようにすることにより、先頭アドレスS5_IMG_STR_ADDRから、まず32Byteのデータが読みだされる。そして、次のデータを取得するため、アドレスを32Byte×Mだけ増加させることで、小領域(2)〜(M)の1行目のデータの読み出しが飛ばされて、小領域(1)211の第2行目の32Byteのデータを読み出すこととなる。そして、繰返し数Bdh_in回、すなわち、小領域(1)211のBdh_in行分のデータを読み出すことにより、小領域(1)211の全てのデータを読み出すことができる。小領域(2)〜小領域(M)の入力画像データの読み出しでは、順次「先頭アドレス」を順次32ByteずつずらしてDMAC194を動作させる。このように画像処理装置は、所望する小領域の入力画像データをRAM106からDMA転送で読み出す。

【0047】

画像入出力部152の画像入力部1521は、DMAC194から、入力画像データを受け取りながら、そのデータを中間バッファ制御部1522へ転送する。中間バッファ制御部1522は、図2(e)のように中間バッファ調停回路230と中間バッファ232とで構成される。中間バッファ232は入力画像データを格納する領域である入力領域234と後述する出力画像データを格納する領域である出力領域236とで構成される。CPU102は、中間バッファ232の入力領域の先頭アドレスを入力領域先頭アドレスとして、出力領域の先頭アドレスを出力領域先頭アドレスとして予め設定しておく。なお、画像入力部1521から入力された入力画像データは、まず中間バッファ調停回路230へ入力される。

【0048】

中間バッファ調停回路230は受け取った入力画像データを、中間バッファ232の入力領域234へ一時的に格納する。通常、中間バッファ232はSRAM等の記憶装置で実現される。例えば、この記憶装置の1ワードあたりのビット長が256ビット(32Byte)長の場合、入力領域234で記憶するべきワード数はバンド領域の高さに相当し、DMA転送の繰り返し数であるBdh_inワードとなる。また、この記憶装置の1ワードあたりのビット長が64ビット(8Byte)長の場合、32Byte長のデータを受けるのに4ワード必要となる。そのため、入力領域234で記憶すべきワード数は、バンド領域の高さ(DMA転送の繰り返し数)Bdh_inを4倍したワード数となる。つまり、入力領域の容量は、1回のDMA転送の単位である小領域(処理単位)の入力画像データが格納できる容量となる。なお、DMAC194は、DMA転送や1つのバンド領域の入力画像データの転送が完了すると、そのことを割り込み信号222を用いてCPU102へ通知してもよい。

【0049】

その後、画像入力部1521は、中間バッファ調停回路230を介して、一時的に記憶された小領域の入力画像データを読み出し、1画素ずつの画素値を順次生成して、画像処理実行部153へ入力する。なお、画像入力部1521と画像出力部1523とは非同期で動作してもよく、例えば入力画素領域(1)211と入力画素領域(2)の一部とを用いて、出力画素領域(1)251が生成され、出力されてもよい。

【0050】

画像処理実行部153は、入力された1つ以上の画素からなる画素領域に画像処理を施す。具体的には、例えば、複数の画素からなる画素領域に対して、所定の重み係数を乗算し、それらの値を全て加算することにより、1つの出力画素を得る。そして、例えば、画素領域をバンド領域の高さ方向にスライドさせながらこのような処理を進め、高さ方向に1列分の画素値を出力すると、次の列の画素を出力するための処理を実行する。処理後の画素値は1画素ずつ画像入出力部152の画像出力部1523へ出力される。

【0051】

画像出力部1523では、処理後の出力画素値から出力画像データを生成し、32Byte単位で中間バッファ調停回路230を介して中間バッファ232の出力領域236へ生成した出力画像データを格納する。生成済みの出力画像データのデータ構造は前述の図4Aの点順次形式のままであるが、出力画像データの形状は、図2(f)の250のように、入力時から形状が変わっていてもよい。画像処理実行部153では、入力画素領域のサイズと出力画素領域のサイズが異なる様々な画像処理が実行される。そのため、入力画像データ210と出力画像データ250の画素数は異なり、出力画像データ250の出力バンド領域の高さは、Bdh_outとなる。また出力画像データ250のバンド領域の長さは、8×Nとなる。すなわち、入力画像データ210と出力画像データ250では、バンド領域の高さが異なるため小領域(処理単位)の容量が異なる。そして、バンド領域の長さも異なるため小領域(処理単位)の数もM個からN個に変化する。

【0052】

しかしながら、入力と出力ではデータ構造が同一であるため、中間バッファ232の出力領域236の容量は入力領域234の容量と同じ考え方で設定できる。例えば、記憶装置が1ワードあたりのビット長が256ビット(32Byte)長の場合、出力領域236で記憶すべきワード数は、出力バンドの高さと同じ、Bdh_outワードとなる。また、中間バッファ232の1ワードあたりのビット長が64ビット(8Byte)長の場合、出力領域236で記憶すべきワード数は、先の出力バンドの高さであるBdh_outを4倍したワード数となる。

【0053】

画像出力部1523は、例えば、Bdh_out個の画素が4列分入力され、小領域(1)251の出力画像データが中間バッファ232の出力領域236に揃った時点で、画像処理実行部153からの処理後の出力画素値156の受け取りを停止する。そして、出力領域236の出力画像データを順次読み出し、DMAC196へ送出する。そしてDMAC196は、CPU102からの指示信号(図2(d)の225)に従って、処理後の画像データをRAM106へ書き込む。

【0054】

同様の動作を小領域(2)から小領域(N)まで順次繰り返し実行し、図2(g)記載の出力バンド領域の出力画像データをすべてRAM106へ書き戻す。

【0055】

以上のように中間バッファの容量は、入力バンドの高さBdh_inと出力バンドの高さBdh_outで規定できる。例えば、一定の中間バッファの容量を、入力領域先頭アドレスと出力領域先頭アドレスを変更することにより、入力バンドの高さBdh_inと出力バンドの高さBdh_outに応じて割り振ることが可能となる。なお、本実施形態では、入力バンドの高さと出力バンドの高さとから入力領域と出力領域とを定めているが、画像処理における入出力の画素数の比に基づいて入力領域と出力領域との容量を定めてもよい。例えば、本実施形態では、画像処理実行部153の画像処理により、Bdh_in=30行のデータがBdh_out=70行のデータとして出力される場合、中間バッファのうち、30%を入力領域に割り当て、残りの70%を出力領域に割り当ててもよい。このようにすることにより、中間バッファを最大限に活用することができる。また、入力領域の大きさに合わせて、入力バンドの高さを設定することで、処理すべきバンドの数を最小とすることが可能となる。例えば、上述の例で、中間バッファのうち、60行分のデータを記憶することができる場合には、Bdh_inを30行でなく、60行とすることにより、処理すべきバンドの数を減少させることができるようになる。

【0056】

領域分割処理の場合、前述の小領域(処理単位)毎に順次画像処理を行うため、小領域(処理単位)の個数が、入力M個から出力N個に変わったとしても、中間バッファの容量に影響を及ぼす訳ではない。このため、入力画像データと出力画像データのデータ構造が同じ場合、入力バンドの高さBdh_inと出力のバンドの高さBdh_outという、画素領域の一辺の変化に応じて入力領域と出力領域の容量を割り当てればよい。これにより、入力画素領域のサイズと出力画素領域のサイズが異なる様々な画像処理に対して入出力のバンドの高さの変化のみを管理するだけでよい。また、2次元の画像の変化に対して「一辺」が指し示す1次元の情報を管理するだけでよいため、中間バッファを管理し、画像入出力部152を制御するソフトウェアは、DMACや画像処理部150の設定値を容易に算出することができる。

【0057】

(本実施形態の効果)

図5と図6を用いて本実施形態の効果について説明する。

【0058】

図5には、従来技術の一般的な画像処理装置を示している。従来の画像処理装置では、画像データを入力するデータ入力装置と処理後の画像データを出力するデータ出力装置とは別々に構成されており、当然ながら各々にローカルバッファを備える。例えば、バンド処理を行うときに、空間フィルタや縮小処理によりバンドの高さが減るケース(図5(a)記載)が最も頻繁に使用するアプリケーションであるとする。そのケースでは、入力ローカルバッファと出力ローカルバッファとを最適化すると、入力ローカルバッファを出力ローカルバッファより大きい容量として画像処理装置を構成にすることになる。

【0059】

一方、一部のアプリケーションで拡大処理や高品位のIP変換を行う必要が生じた場合、処理後にバンドの高さが増えることとなる(図5(b)記載)。この場合、出力画像データを出力ローカルバッファへ格納できるように、出力ローカルバッファを基準に出力バンドの高さを定める。そのとき、バンドの高さの増分を出力バンドの高さから減じた値を入力バンドの高さに設定することとなる。それ以上の高さの入力バンドを処理すると、出力バンドの高さが出力ローカルバッファの記憶容量を超えてしまうからである。この場合、先の最適化により、入力ローカルバッファの方が出力ローカルバッファより大きい容量としていたため、入力ローカルバッファの多くが未使用のままとなる。このように図5(a)と図5(b)のケースでは、いずれかのケースを中心にローカルバッファの容量を最適化することで、他のケースにおいてはローカルバッファを効率的に利用できない。

【0060】

また、上記の例では図5(b)のケースでは、入力画像データの1回のバンド領域が非常に小さくなってしまうことから、1つの画像データを処理するためのバンド処理の回数が増える。バンド処理毎に逐次的に画像処理を行う場合、バンド処理間でCPU102は同期を取る必要がある。そして同期のために、CPU102は割り込み通知待ちを行うため、同期の度に少なからず待ち時間がオーバヘッドとなって発生してしまう。そのため、ローカルバッファの利用効率が劣化するにしたがって、1つの画像処理の処理速度も遅くなることが懸念される。

【0061】

これに対して、図6に、本実施形態の画像処理装置を用いた場合の動作例を図5と同様のケースについて示す。なお、図5(a)と同様のケースを図6(a)に、図5(b)のケースを図6(b)に示している。本実施形態の画像処理装置は、図6に示すように、従来技術に係るデータ入力装置とデータ出力装置に相当する機能部が一体化した入出力装置を備える。また、本実施形態の画像処理装置は、先の入力ローカルバッファと出力ローカルバッファを1つの中間バッファで構成している。本実施形態では、実行する画像処理の種類が変更された場合、その画像処理へ入力される画素領域の画素数とその画像処理から出力される画素領域の画素数との関係の変化を察知し、中間バッファの入力領域と出力領域の割り当てを変更することができる。その結果、図6(a)のケースでも図6(b)のケースでも未使用の領域の発生を抑え、中間バッファを効率的に使用することができる。また、図6(b)では、図5(b)と比べて入力画像データのバンド領域の高さを増やすことができるため、バンド処理の回数を削減できる。したがって、本実施形態に係る画像処理装置により、1つの画像処理の処理速度を従来技術と比べて高速化することができる。

【0062】

<<実施形態2>>

本実施形態では、実施形態1と異なるデータ構造を持つ画像データを取り扱う場合について説明する。例えば、図4Bは、面順次形式の画像データの構造の一例である。図示の例では、RAM106(DRAM)のデータ領域に、S0_IMG420からS3_IMG423までの4種の画像データが格納されている。この4種のデータは、例えば、画像読み取り部120で読み取られた画像を色空間変換や濃度補正処理を施し、第1色K(Black)、第2色M(Magenta)、第3色C(Cyan)、第4色Y(Yellow)に変換したものである。そしてDRAMの性能を落とさずに画像データを読み書きできるように、各々格納される画像データの容量の最小単位は、第1実施形態と同様に、408に示すような32bit×8wordの32Byteとなっている。当然ながら、S0_IMG420からS3_IMG423までのデータの格納容量は、32Byteの整数倍となる。

【0063】

次に画像データのデータ構造を詳しく説明する。画像データ430は前述のS0_IMG420の領域の第1色K(Black)の画像データを示している。画像データ430の領域432は上述の32Byte単位のデータであり、その中に434で示す8個の32bit長のデータがパッキングされている。そして、1つの32bit長のデータは、436が示すように8bit長のK(Black)の色要素が複数個(4つ)パッキングされている。すなわち、図の太枠430の範囲は、8×4×M×N個の画素数の画像データを表す。残りの第2色から第4色までの画像データについても同様である。

【0064】

上記の面順次形式の画像データを入力画像データとして画像処理する場合、上記の第1色K(Black)から第4色Y(Yellow)の4種の画像データについて、第1実施形態で説明した小領域(処理単位)ごとにRAM106から読み出す。例えば、小領域(1)に対応する画像データとしては、DMAC194の先頭アドレスの設定としては、以下の4種を順に切り替えて設定し、DMA転送を4回実行する。

【0065】

・先頭アドレス[1回目]:図4BのS0_IMG_STR_ADDR

・先頭アドレス[2回目]:図4BのS1_IMG_STR_ADDR

・先頭アドレス[3回目]:図4BのS2_IMG_STR_ADDR

・先頭アドレス[4回目]:図4BのS3_IMG_STR_ADDR

そして、読み出した4種の画像データをすべて、一旦、中間バッファ232へ格納する。画像入力部1521は、4種の画像データの所定の位置(座標)の4つの色要素を読み出し、1つにまとめて点順次形式の画素値(C、M、Y、K)として画像処理実行部153へ入力する。また処理後の点順次形式の画素値(C、M、Y、K)から4つの色要素を取り出し、出力領域内の4種の出力画像データの領域に各々格納する。なお、この場合、当然ながら、出力画像データのRAM106への書き出しについても、DMA転送を4回実行する必要がある。

【0066】

<<実施形態3>>

図7を用いて実施形態3について詳細説明する。本実施形態では、DMAC194とDMAC196は3チャネルのチャネルDMACであり、異なる3種の画像データを同時に取り扱う。そして、画像処理部150の入力ポート151と出力ポート154は3チャネルに対応して3つのポートで構成されている。そして、画像処理部150も異なる3種の画像データを取り扱うことができる。本実施形態では、3つの入力ポート711、712、713と3つの出力ポート791、792、793を備える。

【0067】

3つのポートのうち、入力ポート[C]713は、外部入力回路715と、出力ポート[C]793は、外部出力回路795と接続されており、前述までの画像入力部と画像出力部をバイパスする機能がある。外部入力回路715は、入力ポート[C]713を介して受け取った入力画像データから入力画素値を生成し、画像処理実行部153へ送出する。また外部出力回路795は画像処理実行部153から受け取った出力画素値をもとに出力画像データを生成し、出力ポート[C]793を介してDMAC196へ送出する。

【0068】

残りの2つの入力ポート(入力ポート[A]711、入力ポート[B]712)から入力される画像データは、上述の画像入力部1521の機能に基づいて処理される。また、残りの2つの出力ポート(出力ポート[A]791、出力ポート[B]792)へ出力される画像データが、上述の画像出力部1523の機能に基づいて生成される。

【0069】

本実施形態では、中間バッファとして2バンクの記憶部を有する。2バンクの構成のため、前述までの説明の小領域(処理単位)を2つまで同時に格納できる。上述の中間バッファは1バンク構成であったため、画像入力部1521は、入力画像データの受け取りと入力画像データからの画素値の生成とを時分割で行っていた。また、画像出力部1523も、出力画素値からの出力画像データの生成と出力画像データの出力とを時分割で行っていた。本実施形態では、2バンクの記憶部を有するため、入力画像データから画素値を生成している間も、次の小領域(処理単位)の入力画像データを受け取ることができる。また、出力画素値から出力画像データを生成している間も、生成済みの出力画像データを出力することができる。すなわち、DMAC194と画像入力部1521の処理、およびDMAC196と画像出力部1523の処理を並列化することができる。

【0070】

本実施形態では、2種の画像データを同時に入出力するため、中間バッファの入力領域と出力領域は、さらに2つの領域([A]と[B])に分けられる。そして各々の領域を分けるため、CPU102は、領域ごとに先頭アドレスを予め設定する。すなわち、CPU102は、領域[A]の入力領域と出力領域、そして領域[B]の入力領域と出力領域との4つについて、それぞれ先頭アドレスを設定する。処理を簡単に行うためには、2バンク構成の記憶部で1セットの共通する先頭アドレスがあればよい。入力される画素領域の単位と出力される画素領域の単位とは不変であり、バンクごとに変更する必要がないからである。そして各々の領域の容量は、2種の画像データの2つの入力バンドの高さと2つの出力バンドの高さをもとに算出すればよい。

【0071】

本実施形態によれば、画像処理部150で同時に扱う複数種の画像データに対し、中間バッファを各々割り当て、さらに柔軟性に富んだ画像処理を行うことができる。上記の一例では、2つの入力画像データと2つの出力画像データに対応する方法を述べた。しかしながら、例えばIP変換や画像合成のように2つの入力画像を1枚の出力画像にする場合についても、本実施形態の画像処理装置では、入力領域を2つ割り当て、出力領域を1つ割り当てることにより容易に対応することができる。このようなケースにおいても、本実施形態の画像処理装置では、中間バッファの使用率を向上させることができる。

【0072】

なお、本実施形態では、2バンクの記憶部を有する例を説明したが、上述のように入出力を時分割で行うことを許容すれば、1バンクの記憶部において複数データを用いることも可能である。例えば、大容量の記憶部を用いて、複数データのそれぞれに対応する入力先頭アドレスと出力先頭アドレスを設定することによって本実施形態と同様に処理することができる。

【0073】

<<その他の実施形態>>

また、上述の説明では、画像データの読み書きの単位を32Byteとして説明した。しかしながら、画像処理装置上でのRAM106の構成や、RAM106を実現する記憶装置(DRAM等)の種類、そして実行する画像処理の種類等により、画像データの読み書き単位は必ずしも32Byteでなくてもよい。読み書きの単位が変わったとしても、画像データを記憶する中間バッファの容量の算出式を変えるだけで、画像処理装置と画像処理方法を適用することができる。

【0074】

また、画像データの32Byte単位のデータ構造が図4Aの494のように4×2画素を示すような場合においても、同様に画像データを記憶する中間バッファの容量の算出のしかたが変わるだけである。上述の説明では、入力バンドの高さBdh_inや出力バンドの高さBdh_outで中間バッファの容量を割り当てた。4×2画素のデータ構造においては、入力バンドの高さBdh_inや出力バンドの高さBdh_outを2で除算した値を基準に、中間バッファの容量を割り当てることにより、対処可能である。

【0075】

また、前述までの説明では、主にバンド処理について説明した。しかしながら、別の領域分割手法であるブロック(タイル)処理についても上述の画像処理方法を適用できる。ブロック(タイル)処理では、主走査方向と副走査方向に沿って画像データを2次元で領域分割する。例えば、前述までに説明した小領域(処理単位)が、この2次元で領域分割された画素領域と考えればよい。小領域(1)から小領域(M)まで順次読み出す手法はブロック(タイル)処理そのものである。特許文献1のブロック(タイル)処理と特許文献2のバンド処理の主な違いは、画像データから画素値を生成するときの画素の走査方向の違いにすぎない。特許文献1のブロック(タイル)処理では、画像処理実行部に入力する画素の走査を主走査方向に沿って行う。一方、特許文献2のバンド処理では、画像処理実行部に入力する画素の走査をバンドの高さ(副走査方向)に沿って行う。しかしながら、いずれの場合も、画像データを記憶する中間バッファの容量の算出のし方は変わらない。

【0076】

また、もしRAM106の記憶容量に余裕があり、局所(近傍)画像処理における遅延メモリを省容量化する必要がなければ、バンド処理を行わず、1つ分の画像データ300をRAM106に格納し、1画像の単位で画像処理を行ってもよい。そのときバンドの高さではなく副走査方向の画像データの大きさで中間バッファの入力領域と出力領域の容量を割り当てればよい。

【0077】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【技術分野】

【0001】

本発明は、画像処理の前後における画像データを一時的に記憶するためのデータ処理装置、データ処理方法、及びプログラムに関する。

【背景技術】

【0002】

従来から、画像形成を行って出力する際に、空間フィルタ処理などによる局所(近傍)画像処理が行なわれている。局所画像処理では、処理対象となる画素(以下、処理画素と略称する)を含む空間フィルタ領域に対して、その領域のすべてまたは大半の画素を用いて所定の演算を行なう。

【0003】

この局所(近傍)画像処理の一つとして解像度変換がある。解像度変換とは、入力した画像を拡大、もしくは縮小して所望の大きさの画像に変換する処理である。解像度変換では、当然ながら入力画素数と処理後の出力画素数が大きく異なることとなるため、一般的な局所(近傍)画像処理に比べて装置化が難しくなる。例えば特許文献1では、遅延メモリと空間フィルタ処理との組み合わせを複数用いる場合で、それぞれの組み合わせの間で解像度変換を実行する場合、この処理の前後にある2つの遅延メモリが有効活用できないことを指摘している。

【0004】

この問題に対して、特許文献1は、拡大もしくは縮小によって入力された画像の主走査方向の画素数が変化する主走査変倍と呼ばれる解像度変換の処理を開示している。特許文献1の技術では、解像度変換の前後にある2つの空間フィルタが二次元領域の処理画素について演算を行っており、この2つの空間フィルタに各々遅延メモリが必要となる。そして、特許文献1は、この2つの遅延メモリと画素数の変化とに着目してメモリを有効活用する技術が記載されている。また特許文献1では、画像を主走査、副走査方向共に二次元に領域分割して、分割後の画素領域について逐次的に画像処理を行う、ブロック(タイル)処理を採用している。

【0005】

一方、特許文献2には、上記のブロック(タイル)処理と類似の技術のバンド処理技術が記載されている。バンド処理では、画像を主走査方向にのみ一次元的に領域分割して、分割後の画素領域について逐次的に画像処理を行うものである。このような技術では、各バンド領域間で隙間なく局所(近傍)画像処理を行なうために、各バンド領域が、それぞれ隣接する領域との境界で一部分が互いに重なり合うように工夫している。また特許文献2では、各バンド領域の高さと同一の方向に1画素ずつ画素を走査することで、局所(近傍)画像処理に必要な処理画素を保持する遅延メモリの容量を各バンド領域の高さの大きさで規定する。これにより、特許文献2では、この遅延メモリの省メモリ化を実現している。

【0006】

特許文献1のブロック(タイル)処理と同様、特許文献2のバンド処理も領域分割して逐次的、もしくは分散並列的に画像処理を行う手法である。以後、このような手法を領域分割手法と総称する。これらの領域分割手法にとって相性の良くない画像処理は、特許文献1で言及する解像度変換だけではない。

【0007】

例えば、プリンタ画像処理などで使用される、トリミング処理や端部拡張処理などもあげられる。トリミング処理とは画像を部分的に削除する処理で、入力画像より出力画像の方が画素数は少なくなる。また端部拡張とは画像の端部の画素のみ、所定画素数だけコピー拡張したり、特定色の画素で拡張したりする処理で、入力画像より出力画像の方が画素数は多くなる。

【0008】

また、映像処理などで使用される、IP変換などもあげられる。IP変換とは、副走査方向に画素が間引かれたインターレース画像を、時間軸方向に複数フレーム用いて1フレームの画素が間引かれていないプログレッシブ画像を合成する処理である。例えば、2フレームのインターレース画像から1フレームのプログレッシブ画像を合成する場合、入力画像の総画素数と出力画像の画素数は同じとなる。しかしながら高品位なIP変換では、3〜5フレームのインターレース画像から1フレームのプログレッシブ画像を合成することになるので、入力画像より出力画像の方が画素数は少なくなる。IP変換の例では、ユーザが選択した動作モード(画質モード)により、入力画像と出力画像の画素数の関係が変わることになる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2010−087804号公報

【特許文献2】特開2006−139606号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

近年の画像処理装置は、上述のような空間フィルタ処理、解像度変換、トリミング処理、端部拡張処理、IP変換を含め、様々な画像処理を多く内包する。そして画像処理装置は、装置全体で所望の高画質化を実現するために、それらの処理をアプリケーションに応じて取捨選択して組み合せて用いることが多い。

【0011】

しかしながら、このような複数の処理の組合せを領域分割手法で実現する場合、さらなる注意が必要となる。空間フィルタ処理のように二次元領域の処理画素を用いて演算する場合、フィルタが取り扱う画素のサイズに対応して周辺画素を累積し、画像を処理する必要がある。そして空間フィルタ処理が複数回あれば、その都度、周辺画素を累積し、すべての周辺画素を累積した、より広い範囲の画像について処理を行う必要がある。

【0012】

さらに、映像処理のクロマ・アップサンプリングのような空間フィルタ処理では、前述のように周辺画素を累積するだけでは不十分となる。このような空間フィルタ処理では、入力する処理画素の画像上での位相も考慮する必要がある。そのため、その空間フィルタ処理に入力する画像の縦や横の画素数が4の倍数でなければならないという特殊な制約を合わせ持つ。

【0013】

アプリケーションに応じて取捨選択して組み合された複数の処理に対し、各々の制約を満たしつつ、所望の画像処理を行うには、入力画像の画素数と出力画像の画素数との関係性を簡単に規定することができない。アプリケーションは、複数の空間フィルタ処理の周辺画素を累積した画像より、わざと余分な画素数の画像を処理する。アプリケーションは、場合によっては、処理後の画像の一部を最後にトリミング処理で削除し、所望の大きさの画像に調整することも必要となる。

【0014】

ここで、領域分割手法を用いる場合に、これらの多くの画像処理を取捨選択して組み合せた画像処理方法を、ハードウェアでいかに実現するかを考えることは重要である。

【0015】

ハードウェアを用いる画像処理装置では、一般的に、入力ローカルバッファと出力ローカルバッファを介して外部記憶装置と画像を互いに転送することで、各種部品の同時動作と部品間の連係動作を実現する。しかしながら、上述の通り、複数の処理を取捨選択して組み合せて画像処理をする場合、入力画像の画素数と出力画像の画素数は簡単には規定できない。そのため、入力ローカルバッファや出力ローカルバッファの容量を適切に規定することが難しく、過大なバッファを用意することによる利用効率の低下や、過小な記憶容量を用意することによる処理の停滞などの課題が生じる。

【0016】

特許文献1では、主走査変倍の前後にある2つのフィルタ処理(プレフィルタとポストフィルタ)の遅延メモリに着目している。しかしながら、特許文献1では様々な複数の画像処理を取捨選択して組み合せるための画像処理方法を実現するためのハードウェア構成としての画像処理装置については検討されていない。このため、特許文献1では、前述のような入力する画像と出力する画像の画素数の様々なバリエーションに対応する方法については、有用な解決策を開示していない。また特許文献1では、画像を外部記憶装置から読み込むときに必要となる入力ローカルバッファと、処理後の画像を外部記憶装置へ書き出すときに必要となる出力ローカルバッファに着目した有用な解決策を開示していない。

【0017】

本発明は、上記課題に鑑みてなされたもので、様々な処理を組み合わせた画像処理により入力と出力の画素数が変動する条件において、入力画像と出力画像とを一時的に記憶する記憶装置の効率的な利用を可能とする技術を実現することを目的としている。

【課題を解決するための手段】

【0018】

上記目的を達成するため、本発明によるデータ処理装置は、画像データに含まれる1つ以上の画素からなる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して出力画素領域を出力するデータ処理装置であって、前記入力画素領域のデータと、前記出力画素領域のデータとを一時的に記憶する記憶手段と、前記入力画素領域の画素数と、前記出力画素領域の画素数とに基づいて、前記入力画素領域のデータを記憶する前記記憶手段の入力領域の大きさと、前記出力画素領域のデータを記憶する前記記憶手段の出力領域の大きさとを設定する設定手段と、を有することを特徴とする。

【発明の効果】

【0019】

本発明によれば、入力と出力の画素数が変動する条件において、入力画像と出力画像とを一時的に記憶する記憶装置の効率的な利用を可能とするデータ処理装置、データ処理方法およびプログラムを提供することができる。

【図面の簡単な説明】

【0020】

【図1A】画像処理装置の全体構成と画像処理部の構成例を示すブロック図。

【図1B】画像処理装置の全体構成と画像処理部の構成例を示すブロック図。

【図2】画像データの入出力に係る動作例を示す図。

【図3】バンド処理の動作の例を説明する図。

【図4A】画像データの格納方法とデータ構造の例を説明する図。

【図4B】画像データの格納方法とデータ構造の例を説明する図。

【図5】従来の画像処理装置の動作例を説明する図。

【図6】本発明の画像処理装置の動作例を説明する図。

【図7】別の例に係る画像処理部の一例を説明するブロック図。

【発明を実施するための形態】

【0021】

以下、添付図面を参照して本発明の実施の形態を詳細に説明する。

【0022】

<<実施形態1>>

(画像処理装置)

図1Aは、本実施形態に係る画像処理装置の全体構成の一例を示すブロック図である。画像処理装置は、例えば、CPU回路部100、画像読み取り部120、画像処理部150を備える。

【0023】

画像読み取り部120は、レンズ124、CCDセンサ126、及びアナログ信号処理部127等を有する。画像読み取り部120では、レンズ124を介してCCDセンサ126に原稿110の画像情報が結像され、CCDセンサ126によりその画像情報がR(Red)、G(Green)、B(Blue)のアナログ電気信号に変換される。アナログ電気信号に変換された画像情報は、アナログ信号処理部127に入力され、R、G、Bの色毎に補正等が行われた後にアナログ/デジタル変換(A/D変換)される。こうして、デジタル化されたフルカラーのデジタル画像信号(画素値)が生成される。生成されたデジタル画像信号は、映像入力部130へ入力され、その後、DMAC(Direct Memory Access Controller)192へ入力される。

【0024】

DMAC192は、CPU102により予め動作が設定されており、共有バス190を介して、入力されたデジタル画像信号をCPU回路部100のRAM106に記憶させる。なお、複数の画素についてのデジタル画像信号を、1枚の画像を形成するように集合させたデータを、以下では画像データと呼ぶ。本実施形態では、デジタル画像信号は画像データの形式でRAM106に記憶されるものとする。画像処理を行う場合、CPU102はDMAC194を起動してRAM106に記憶された画像データを読み出させ、処理の対象となる画素に対応するデジタル画像信号を画像処理部150に入力させる。

【0025】

画像処理部150は、例えば、入力されたデジタル画像信号に対して、例えば、スキャナなどのセンサ・デバイスの読み取り素子の個体差の補正と入力ガンマ補正などの色補正とを行い、画像データを作成するデータ処理装置である。そして、DMAC196は、これらの処理が施された画像データをRAM106に格納する。なお、DMAC196の制御については、例えばCPU102が予めDMAC196の動作を設定し、また、CPU102がDMAC196を起動するようにする。なお、DMAC196の動作は、例えば処理後の画像データをRAM106へ書き込むように設定しておく。

【0026】

これにより、例えば、画像処理部150は入力されたデジタル画像信号に対し、入力色補正処理、空間フィルタ処理、色空間変換、濃度補正処理、及び中間調処理などの、画像の印刷のための画像処理を施す。そして、画像処理部150は、印刷可能な画像データを作成し、その画像データはDMAC196によりRAM106に格納させる。

【0027】

DMAC198は、RAM106に格納された画像処理済みの画像データを読み出して画像印刷部170へ出力する。画像印刷部170は例えばプリンタである。DMAC198の設定は例えばCPU102が行う。画像印刷部170は、たとえば、インクジェットヘッドやサーマルヘッド等を使用したラスタプロッタ等の印刷出力部(不図示)を備える。そして、入力された画像データのデジタル画像信号に基づいて紙上に画像を記録する。上述の説明では、画像印刷部170を用いる例を説明したがこれに限られない。例えば、映像入力部130や映像表示部160等を用いることにより、入力された映像に対し所望の画像(映像)処理を施し、処理後の映像をディスプレイなどの表示装置(不図示)に表示してもよい。

【0028】

CPU回路部100は、演算制御用のCPU102、固定データやプログラムを格納するROM104、データの一時保存やプログラムのロードに使用されるRAM106、及び外部記憶装置108等を備える。CPU回路部100は、画像読み取り部120、画像処理部150、及び画像印刷部170等を制御し、本実施形態の画像処理装置のシーケンスを統括的に制御する。外部記憶装置108は、本実施形態の画像処理装置が使用するパラメータやプログラムや補正データを記憶するディスク等の記憶媒体であり、RAM106のデータやプログラム等は、外部記憶装置108からロードされる構成としてもよい。

【0029】

(画像処理部)

続いて、画像データに画像処理を施す画像処理部150について図1Bを用いて詳細に説明する。CPU102がDMAC194を起動し、DMAC194はRAM106から画像データを読み出す。画像データのデータ構造については後述する。読み出された画像データは、入力ポート151を介して、画像処理部150の画像入出力部152へ入力される。画像入出力部152において、画像入力部1521は、画像データを取得すると、中間バッファ制御部1522に含まれる後述の記憶部(中間バッファ)に取得した画像データを記憶させる。そして、画像入力部1521は、中間バッファに一時的に記憶された画像データを読み出しながら画素値を生成し、入力画素値155として画像処理実行部153へ入力する。

【0030】

画像処理実行部153は、入力画素値155に対して所定の画像処理を実行し、出力画素値156を画像入出力部152へ出力する。画像処理実行部153の詳細については後述する。なお、ここでは、入力画素値155および出力画素値156は、1つ以上の画素値であり、例えば複数の画素値が入力画素値155として入力され、それに対して1つの画素値が出力画素値156として出力される。

【0031】

画像入出力部152では、画像出力部1523は、処理後の出力画素値156から出力画像データを生成して中間バッファ制御部1522内の記憶部(中間バッファ)に記憶する。画像出力部1523は、記憶部(中間バッファ)に一時的に記憶された処理後の画像データを読み出し、出力画像データとして出力ポート154を介してDMAC196へ送出する。DMAC196は前述の通り、CPU102により既に起動されており、受け取った出力画像データをRAM106へ書き出す。

【0032】

すなわち、画像処理部150では、画像入出力部152を介してDMAC194から画像データを取得し、画像処理実行部153で画像に対するデータ処理を実行し、データ処理後の画像データを画像入出力部152を介してDMAC196へ出力する。このようにして、画像処理部150は、画像処理装置内に含まれる画像データにデータ処理を施し、データ処理後の画像データを画像処理装置へ戻す役割を担う。また、画像入出力部152は、データの入出力の調節を行うデータ入出力制御装置としての役割を有する。

【0033】

(画像処理実行部)

次に、画像処理部150内の画像処理実行部153について詳細に説明する。画像処理実行部153は、画像処理回路(1)1531から画像処理回路(P)1537の、P個の画像処理回路と、インターコネクト1531とで構成される。P個の画像処理回路と、インターコネクト1531とは、入力ポート1532、1535、並びに1538、および出力ポート1533、1536、並びに1539等のポートを介して互いに接続される。

【0034】

画像処理回路は、例えば、入力色補正処理、色空間変換、濃度補正処理、中間調処理、空間フィルタ処理、解像度変換、トリミング処理、端部拡張処理、IP変換、クロマ・アップサンプリングのうち、1つの処理を行う。これらの画像処理回路は、パイプライン回路等のハードウェアで実現されてもよいし、プロセッサとプログラム(ソフトウェア)等で実現されてもよい。そして、例えば、入力ポート1532、1535、1538等から入力画素値155を受け取り、処理を施した後に、出力ポート1533、1536、1539から処理後の出力画素値156を出力する。

【0035】

また、インターコネクト1531はクロスバーやリングバス等の接続手段で実現されており、入力ポートと出力ポートの接続先を任意に切り替えることができる。したがって、CPU102がこれらポートの接続先の指定を設定することで、インターコネクト1531は、例えばP個の画像処理回路の実行順序を変更し、または一部の処理をバイパスすることができる。このように、画像処理実行部153は、アプリケーションに応じて、各種の処理を取捨選択して組み合せ、所望の画像処理を実現する。

【0036】

(領域分割)

次に、本実施形態における画像データの領域分割について説明する。本実施形態では、領域分割手法の1つであるバンド処理を用いるものとする。以下、バンド処理について、図3を用いて説明する。バンド処理では、図3(a)〜(d)に示されるように、1枚の画像データ300を帯状のバンド領域301〜304に分割し、この領域毎に逐次的に各種の画像処理を行う。なお、バンド領域は、画像データを主走査方向または副走査方向のいずれかにおいて分割したものであり、バンド領域と画像データとは、主走査方向または副走査方向のいずれかにおいて長さが一致する。例えば、図3(a)〜(d)では、画像データは副走査方向において分割され、画像データとバンド領域とでは、主走査方向について同一の長さを有し、副走査方向において異なる長さを有する。以下では、この分割された細長い領域をバンド領域と呼び、バンド領域が展開される記憶領域をバンドメモリと呼び、画像データを分割する行為をバンド分割と呼ぶ。バンドメモリは、RAM106内に記憶領域として確保されてもよく、また、システム上の適切な記憶領域に確保されてもよい。なお、ここでは説明を簡潔にするためにバンドメモリをRAM106に確保する場合を例に挙げて説明する。

【0037】

また、以下では、図3(e)に示すように、画像データの座標系(主走査方向−副走査方向)を、長さ方向、高さ方向という新たな座標系(バンド領域座標系)によって定義し、バンド領域を長さ×高さで表現する。バンド領域の長さ、すなわちバンド領域の長さ方向の一辺の大きさは、画像データの主走査方向の長さ、または副走査方向の長さの何れかの値とする。また、バンド領域の高さ、すなわちバンド領域の高さ方向の一辺の大きさは任意の値となる。例えば、図3(a)〜(d)では、長さ方向は主走査方向であり、高さ方向は副走査方向である。これに対し、図3(p)〜(r)のように、例えば画像データを主走査方向において分割した場合、図3(s)に示すように、長さ方向が副走査方向となり高さ方向が主走査方向となる。図3(p)〜(r)のようなバンド分割は、例えば画像データの主走査方向の大きさが副走査方向の大きさより大きい場合に行うようにしてもよい。

【0038】

バンド処理では、まず、図3(a)に示す第1のバンド領域301を、RAM106上のバンドメモリに展開して画像処理を行う。次に、図3(b)に示す第2のバンド領域302を、第1のバンド領域301が展開されたRAM106上のバンドメモリに上書き展開して、画像処理を行なう。さらにその後、図3(c)に示す第3のバンド領域303を、第2のバンド領域302が展開されたRAM106上のバンドメモリに上書き展開し、画像処理を行なう。最後に、図3(d)に示す第4のバンド領域304を、第3のバンド領域303が展開されたRAM106上のバンドメモリに上書き展開して画像処理を行なう。図3(a)〜(d)で明らかなように、バンド領域301〜304の長さは同じであるが、高さは同じでなくてもよい。したがって、メインメモリに確保される記憶領域であるバンドメモリの高さは、高さ方向の一辺の大きさが最も大きいバンド領域(図3の場合、第1〜第3のバンド領域301〜303)によって決定される。

【0039】

なお、バンド処理では、各バンド領域間で隙間なく空間フィルタ処理などの局所(近傍)画像処理を行なうため、図3(f)〜(h)のように、各バンド領域が、それぞれ隣接する領域との境界で一部分が互いに重なり合うようにする。

【0040】

(画像データのデータ構造)

次に、画像データのデータ構造の一例について詳細に説明する。本実施形態では、前述のように、画像データはRAM106に一時的に格納される。一般的にRAM106は安価なDRAMで構成されることが多い。したがって、前述のようにDMACを介して画像データを読み書きする場合、DRAMが性能を落とさずに読み書きできる単位で画像データを取り扱うことが望ましい。そこで、RAM106の画像データの格納方法の一例と、画像データのデータ構造の一例について、図4Aを用いて詳しく説明する。図4Aは、RAM106(DRAM)上にデータが格納された状態を示している。図4Aの例では、あるデータ領域(IMG_AREA_STR_ADDRからIMG_AREA_END_ADDRまでの領域)が確保され、ここに画像処理に必要な種々の画像データが格納される。

【0041】

図4Aは、点順次形式の画像データの構造のRAM106への格納例であり、RAM106(DRAM)のデータ領域に、S5_IMG425とS6_IMG426の2種の画像データが格納された例を示している。例では、DRAMの性能を落とさずに画像データを読み書きできるように、格納される画像データの容量の最小単位は、408に示すように、32bit×8wordの32Byteとしている。すなわち、S5_IMG425とS6_IMG426の画像データの格納容量は、32Byteの整数倍となる。

【0042】

次に、画像データのデータ構造を詳しく説明する。画像データ440は点順次形式で、R(Red)、G(Green)、B(Blue)の画素値を有する。画像データ440に含まれる1つの領域442は32Byte単位のデータであり、1つの領域442の中には、444で示すように、複数個(8つ)の画素値がパッキングされている。そして、444に含まれる8つの画素値のそれぞれには、446で示すようにそれぞれ10bitのR、G、Bの値がパッキングされている。なお、図の例では、残りの2bitは、DRAMへのアクセスを簡単にするための無効データであり、データを格納しないものとする。図中太線で表される画像データ440は、8M×N画素のサイズを有する。なお、上述の例では、縦1画素、横8画素を単位として32Byte単位のデータの領域442を定めた例を示したが、画像データ494の例のように、縦2画素、横4画素を単位とするデータの領域492を定めてもよい。

【0043】

(画像データの入出力方法)

図2は、本実施形態の画像処理方法を用いた場合の、RAM106から画像入出力部152への、または画像入出力部152からRAM106への、画像データの入出力方法についての説明図である。画像処理装置は、図2(a)及び図2(b)のように、1つの画像データ300からバンド領域301を抜き出し、入力画像データとしてRAM106に格納する。そして、このバンド領域の入力画像データは、図4Aで説明したように、RAM106で取り扱いやすくなるように、32Byteを単位としたデータ構造とする。データ構造を図2(c)の210に示す。

【0044】

図2(d)において、CPU102は、DMAC194に指示信号(図2(d)の221)を送信する。DMAC194は、図1の共有バス190を介して、このバンド領域の入力画像データ210をRAM106から読み出し、画像処理部150へ入力する。入力画像データ210は、先のデータ構造にしたがって、32Byte×Bdh_inの処理単位で、領域(1)211から領域(M)219までのM個の小さい画素領域(小領域)に分けられる。そして、DMAC194は、このM個の小領域(処理単位)の入力画像データを、小領域(1)211から小領域(M)219まで順番に1つずつ読み出し、画像処理部150に入力する。画像処理部150は、この小領域(処理単位)の入力画像データを受け取り、この単位で画像処理を実行する。なお、処理単位の大きさに応じて、図2(d)のようにバンドの一部の領域である小領域ごとに読出し処理を行ってもよいし、バンドの全部の画素領域に対して一度に読出し処理を行ってもよい。

【0045】

上記のCPU102のDMAC194への指示信号には、例えば、「読み出し先の先頭アドレス」、「連続読み出し量(32Byte単位のデータを連続何回読み出すか)」、「インクリメント・アドレス」および「繰り返し回数」が含まれる。例えば、図4Aの点順次形式の画像データでは以下の通りとする。

【0046】

・「先頭アドレス」:S5_IMG_STR_ADDR

・「連続読み出し量」:1回(32Byte)

・「インクリメント・アドレス」:1ラインのデータ量=32Byte×M

・「繰り返し数」:バンド領域の高さ=Bdh_in回

このようにすることにより、先頭アドレスS5_IMG_STR_ADDRから、まず32Byteのデータが読みだされる。そして、次のデータを取得するため、アドレスを32Byte×Mだけ増加させることで、小領域(2)〜(M)の1行目のデータの読み出しが飛ばされて、小領域(1)211の第2行目の32Byteのデータを読み出すこととなる。そして、繰返し数Bdh_in回、すなわち、小領域(1)211のBdh_in行分のデータを読み出すことにより、小領域(1)211の全てのデータを読み出すことができる。小領域(2)〜小領域(M)の入力画像データの読み出しでは、順次「先頭アドレス」を順次32ByteずつずらしてDMAC194を動作させる。このように画像処理装置は、所望する小領域の入力画像データをRAM106からDMA転送で読み出す。

【0047】

画像入出力部152の画像入力部1521は、DMAC194から、入力画像データを受け取りながら、そのデータを中間バッファ制御部1522へ転送する。中間バッファ制御部1522は、図2(e)のように中間バッファ調停回路230と中間バッファ232とで構成される。中間バッファ232は入力画像データを格納する領域である入力領域234と後述する出力画像データを格納する領域である出力領域236とで構成される。CPU102は、中間バッファ232の入力領域の先頭アドレスを入力領域先頭アドレスとして、出力領域の先頭アドレスを出力領域先頭アドレスとして予め設定しておく。なお、画像入力部1521から入力された入力画像データは、まず中間バッファ調停回路230へ入力される。

【0048】

中間バッファ調停回路230は受け取った入力画像データを、中間バッファ232の入力領域234へ一時的に格納する。通常、中間バッファ232はSRAM等の記憶装置で実現される。例えば、この記憶装置の1ワードあたりのビット長が256ビット(32Byte)長の場合、入力領域234で記憶するべきワード数はバンド領域の高さに相当し、DMA転送の繰り返し数であるBdh_inワードとなる。また、この記憶装置の1ワードあたりのビット長が64ビット(8Byte)長の場合、32Byte長のデータを受けるのに4ワード必要となる。そのため、入力領域234で記憶すべきワード数は、バンド領域の高さ(DMA転送の繰り返し数)Bdh_inを4倍したワード数となる。つまり、入力領域の容量は、1回のDMA転送の単位である小領域(処理単位)の入力画像データが格納できる容量となる。なお、DMAC194は、DMA転送や1つのバンド領域の入力画像データの転送が完了すると、そのことを割り込み信号222を用いてCPU102へ通知してもよい。

【0049】

その後、画像入力部1521は、中間バッファ調停回路230を介して、一時的に記憶された小領域の入力画像データを読み出し、1画素ずつの画素値を順次生成して、画像処理実行部153へ入力する。なお、画像入力部1521と画像出力部1523とは非同期で動作してもよく、例えば入力画素領域(1)211と入力画素領域(2)の一部とを用いて、出力画素領域(1)251が生成され、出力されてもよい。

【0050】

画像処理実行部153は、入力された1つ以上の画素からなる画素領域に画像処理を施す。具体的には、例えば、複数の画素からなる画素領域に対して、所定の重み係数を乗算し、それらの値を全て加算することにより、1つの出力画素を得る。そして、例えば、画素領域をバンド領域の高さ方向にスライドさせながらこのような処理を進め、高さ方向に1列分の画素値を出力すると、次の列の画素を出力するための処理を実行する。処理後の画素値は1画素ずつ画像入出力部152の画像出力部1523へ出力される。

【0051】

画像出力部1523では、処理後の出力画素値から出力画像データを生成し、32Byte単位で中間バッファ調停回路230を介して中間バッファ232の出力領域236へ生成した出力画像データを格納する。生成済みの出力画像データのデータ構造は前述の図4Aの点順次形式のままであるが、出力画像データの形状は、図2(f)の250のように、入力時から形状が変わっていてもよい。画像処理実行部153では、入力画素領域のサイズと出力画素領域のサイズが異なる様々な画像処理が実行される。そのため、入力画像データ210と出力画像データ250の画素数は異なり、出力画像データ250の出力バンド領域の高さは、Bdh_outとなる。また出力画像データ250のバンド領域の長さは、8×Nとなる。すなわち、入力画像データ210と出力画像データ250では、バンド領域の高さが異なるため小領域(処理単位)の容量が異なる。そして、バンド領域の長さも異なるため小領域(処理単位)の数もM個からN個に変化する。

【0052】

しかしながら、入力と出力ではデータ構造が同一であるため、中間バッファ232の出力領域236の容量は入力領域234の容量と同じ考え方で設定できる。例えば、記憶装置が1ワードあたりのビット長が256ビット(32Byte)長の場合、出力領域236で記憶すべきワード数は、出力バンドの高さと同じ、Bdh_outワードとなる。また、中間バッファ232の1ワードあたりのビット長が64ビット(8Byte)長の場合、出力領域236で記憶すべきワード数は、先の出力バンドの高さであるBdh_outを4倍したワード数となる。

【0053】

画像出力部1523は、例えば、Bdh_out個の画素が4列分入力され、小領域(1)251の出力画像データが中間バッファ232の出力領域236に揃った時点で、画像処理実行部153からの処理後の出力画素値156の受け取りを停止する。そして、出力領域236の出力画像データを順次読み出し、DMAC196へ送出する。そしてDMAC196は、CPU102からの指示信号(図2(d)の225)に従って、処理後の画像データをRAM106へ書き込む。

【0054】

同様の動作を小領域(2)から小領域(N)まで順次繰り返し実行し、図2(g)記載の出力バンド領域の出力画像データをすべてRAM106へ書き戻す。

【0055】

以上のように中間バッファの容量は、入力バンドの高さBdh_inと出力バンドの高さBdh_outで規定できる。例えば、一定の中間バッファの容量を、入力領域先頭アドレスと出力領域先頭アドレスを変更することにより、入力バンドの高さBdh_inと出力バンドの高さBdh_outに応じて割り振ることが可能となる。なお、本実施形態では、入力バンドの高さと出力バンドの高さとから入力領域と出力領域とを定めているが、画像処理における入出力の画素数の比に基づいて入力領域と出力領域との容量を定めてもよい。例えば、本実施形態では、画像処理実行部153の画像処理により、Bdh_in=30行のデータがBdh_out=70行のデータとして出力される場合、中間バッファのうち、30%を入力領域に割り当て、残りの70%を出力領域に割り当ててもよい。このようにすることにより、中間バッファを最大限に活用することができる。また、入力領域の大きさに合わせて、入力バンドの高さを設定することで、処理すべきバンドの数を最小とすることが可能となる。例えば、上述の例で、中間バッファのうち、60行分のデータを記憶することができる場合には、Bdh_inを30行でなく、60行とすることにより、処理すべきバンドの数を減少させることができるようになる。

【0056】

領域分割処理の場合、前述の小領域(処理単位)毎に順次画像処理を行うため、小領域(処理単位)の個数が、入力M個から出力N個に変わったとしても、中間バッファの容量に影響を及ぼす訳ではない。このため、入力画像データと出力画像データのデータ構造が同じ場合、入力バンドの高さBdh_inと出力のバンドの高さBdh_outという、画素領域の一辺の変化に応じて入力領域と出力領域の容量を割り当てればよい。これにより、入力画素領域のサイズと出力画素領域のサイズが異なる様々な画像処理に対して入出力のバンドの高さの変化のみを管理するだけでよい。また、2次元の画像の変化に対して「一辺」が指し示す1次元の情報を管理するだけでよいため、中間バッファを管理し、画像入出力部152を制御するソフトウェアは、DMACや画像処理部150の設定値を容易に算出することができる。

【0057】

(本実施形態の効果)

図5と図6を用いて本実施形態の効果について説明する。

【0058】

図5には、従来技術の一般的な画像処理装置を示している。従来の画像処理装置では、画像データを入力するデータ入力装置と処理後の画像データを出力するデータ出力装置とは別々に構成されており、当然ながら各々にローカルバッファを備える。例えば、バンド処理を行うときに、空間フィルタや縮小処理によりバンドの高さが減るケース(図5(a)記載)が最も頻繁に使用するアプリケーションであるとする。そのケースでは、入力ローカルバッファと出力ローカルバッファとを最適化すると、入力ローカルバッファを出力ローカルバッファより大きい容量として画像処理装置を構成にすることになる。

【0059】

一方、一部のアプリケーションで拡大処理や高品位のIP変換を行う必要が生じた場合、処理後にバンドの高さが増えることとなる(図5(b)記載)。この場合、出力画像データを出力ローカルバッファへ格納できるように、出力ローカルバッファを基準に出力バンドの高さを定める。そのとき、バンドの高さの増分を出力バンドの高さから減じた値を入力バンドの高さに設定することとなる。それ以上の高さの入力バンドを処理すると、出力バンドの高さが出力ローカルバッファの記憶容量を超えてしまうからである。この場合、先の最適化により、入力ローカルバッファの方が出力ローカルバッファより大きい容量としていたため、入力ローカルバッファの多くが未使用のままとなる。このように図5(a)と図5(b)のケースでは、いずれかのケースを中心にローカルバッファの容量を最適化することで、他のケースにおいてはローカルバッファを効率的に利用できない。

【0060】

また、上記の例では図5(b)のケースでは、入力画像データの1回のバンド領域が非常に小さくなってしまうことから、1つの画像データを処理するためのバンド処理の回数が増える。バンド処理毎に逐次的に画像処理を行う場合、バンド処理間でCPU102は同期を取る必要がある。そして同期のために、CPU102は割り込み通知待ちを行うため、同期の度に少なからず待ち時間がオーバヘッドとなって発生してしまう。そのため、ローカルバッファの利用効率が劣化するにしたがって、1つの画像処理の処理速度も遅くなることが懸念される。

【0061】

これに対して、図6に、本実施形態の画像処理装置を用いた場合の動作例を図5と同様のケースについて示す。なお、図5(a)と同様のケースを図6(a)に、図5(b)のケースを図6(b)に示している。本実施形態の画像処理装置は、図6に示すように、従来技術に係るデータ入力装置とデータ出力装置に相当する機能部が一体化した入出力装置を備える。また、本実施形態の画像処理装置は、先の入力ローカルバッファと出力ローカルバッファを1つの中間バッファで構成している。本実施形態では、実行する画像処理の種類が変更された場合、その画像処理へ入力される画素領域の画素数とその画像処理から出力される画素領域の画素数との関係の変化を察知し、中間バッファの入力領域と出力領域の割り当てを変更することができる。その結果、図6(a)のケースでも図6(b)のケースでも未使用の領域の発生を抑え、中間バッファを効率的に使用することができる。また、図6(b)では、図5(b)と比べて入力画像データのバンド領域の高さを増やすことができるため、バンド処理の回数を削減できる。したがって、本実施形態に係る画像処理装置により、1つの画像処理の処理速度を従来技術と比べて高速化することができる。

【0062】

<<実施形態2>>

本実施形態では、実施形態1と異なるデータ構造を持つ画像データを取り扱う場合について説明する。例えば、図4Bは、面順次形式の画像データの構造の一例である。図示の例では、RAM106(DRAM)のデータ領域に、S0_IMG420からS3_IMG423までの4種の画像データが格納されている。この4種のデータは、例えば、画像読み取り部120で読み取られた画像を色空間変換や濃度補正処理を施し、第1色K(Black)、第2色M(Magenta)、第3色C(Cyan)、第4色Y(Yellow)に変換したものである。そしてDRAMの性能を落とさずに画像データを読み書きできるように、各々格納される画像データの容量の最小単位は、第1実施形態と同様に、408に示すような32bit×8wordの32Byteとなっている。当然ながら、S0_IMG420からS3_IMG423までのデータの格納容量は、32Byteの整数倍となる。

【0063】

次に画像データのデータ構造を詳しく説明する。画像データ430は前述のS0_IMG420の領域の第1色K(Black)の画像データを示している。画像データ430の領域432は上述の32Byte単位のデータであり、その中に434で示す8個の32bit長のデータがパッキングされている。そして、1つの32bit長のデータは、436が示すように8bit長のK(Black)の色要素が複数個(4つ)パッキングされている。すなわち、図の太枠430の範囲は、8×4×M×N個の画素数の画像データを表す。残りの第2色から第4色までの画像データについても同様である。

【0064】

上記の面順次形式の画像データを入力画像データとして画像処理する場合、上記の第1色K(Black)から第4色Y(Yellow)の4種の画像データについて、第1実施形態で説明した小領域(処理単位)ごとにRAM106から読み出す。例えば、小領域(1)に対応する画像データとしては、DMAC194の先頭アドレスの設定としては、以下の4種を順に切り替えて設定し、DMA転送を4回実行する。

【0065】

・先頭アドレス[1回目]:図4BのS0_IMG_STR_ADDR

・先頭アドレス[2回目]:図4BのS1_IMG_STR_ADDR

・先頭アドレス[3回目]:図4BのS2_IMG_STR_ADDR

・先頭アドレス[4回目]:図4BのS3_IMG_STR_ADDR

そして、読み出した4種の画像データをすべて、一旦、中間バッファ232へ格納する。画像入力部1521は、4種の画像データの所定の位置(座標)の4つの色要素を読み出し、1つにまとめて点順次形式の画素値(C、M、Y、K)として画像処理実行部153へ入力する。また処理後の点順次形式の画素値(C、M、Y、K)から4つの色要素を取り出し、出力領域内の4種の出力画像データの領域に各々格納する。なお、この場合、当然ながら、出力画像データのRAM106への書き出しについても、DMA転送を4回実行する必要がある。

【0066】

<<実施形態3>>

図7を用いて実施形態3について詳細説明する。本実施形態では、DMAC194とDMAC196は3チャネルのチャネルDMACであり、異なる3種の画像データを同時に取り扱う。そして、画像処理部150の入力ポート151と出力ポート154は3チャネルに対応して3つのポートで構成されている。そして、画像処理部150も異なる3種の画像データを取り扱うことができる。本実施形態では、3つの入力ポート711、712、713と3つの出力ポート791、792、793を備える。

【0067】

3つのポートのうち、入力ポート[C]713は、外部入力回路715と、出力ポート[C]793は、外部出力回路795と接続されており、前述までの画像入力部と画像出力部をバイパスする機能がある。外部入力回路715は、入力ポート[C]713を介して受け取った入力画像データから入力画素値を生成し、画像処理実行部153へ送出する。また外部出力回路795は画像処理実行部153から受け取った出力画素値をもとに出力画像データを生成し、出力ポート[C]793を介してDMAC196へ送出する。

【0068】

残りの2つの入力ポート(入力ポート[A]711、入力ポート[B]712)から入力される画像データは、上述の画像入力部1521の機能に基づいて処理される。また、残りの2つの出力ポート(出力ポート[A]791、出力ポート[B]792)へ出力される画像データが、上述の画像出力部1523の機能に基づいて生成される。

【0069】

本実施形態では、中間バッファとして2バンクの記憶部を有する。2バンクの構成のため、前述までの説明の小領域(処理単位)を2つまで同時に格納できる。上述の中間バッファは1バンク構成であったため、画像入力部1521は、入力画像データの受け取りと入力画像データからの画素値の生成とを時分割で行っていた。また、画像出力部1523も、出力画素値からの出力画像データの生成と出力画像データの出力とを時分割で行っていた。本実施形態では、2バンクの記憶部を有するため、入力画像データから画素値を生成している間も、次の小領域(処理単位)の入力画像データを受け取ることができる。また、出力画素値から出力画像データを生成している間も、生成済みの出力画像データを出力することができる。すなわち、DMAC194と画像入力部1521の処理、およびDMAC196と画像出力部1523の処理を並列化することができる。

【0070】

本実施形態では、2種の画像データを同時に入出力するため、中間バッファの入力領域と出力領域は、さらに2つの領域([A]と[B])に分けられる。そして各々の領域を分けるため、CPU102は、領域ごとに先頭アドレスを予め設定する。すなわち、CPU102は、領域[A]の入力領域と出力領域、そして領域[B]の入力領域と出力領域との4つについて、それぞれ先頭アドレスを設定する。処理を簡単に行うためには、2バンク構成の記憶部で1セットの共通する先頭アドレスがあればよい。入力される画素領域の単位と出力される画素領域の単位とは不変であり、バンクごとに変更する必要がないからである。そして各々の領域の容量は、2種の画像データの2つの入力バンドの高さと2つの出力バンドの高さをもとに算出すればよい。

【0071】

本実施形態によれば、画像処理部150で同時に扱う複数種の画像データに対し、中間バッファを各々割り当て、さらに柔軟性に富んだ画像処理を行うことができる。上記の一例では、2つの入力画像データと2つの出力画像データに対応する方法を述べた。しかしながら、例えばIP変換や画像合成のように2つの入力画像を1枚の出力画像にする場合についても、本実施形態の画像処理装置では、入力領域を2つ割り当て、出力領域を1つ割り当てることにより容易に対応することができる。このようなケースにおいても、本実施形態の画像処理装置では、中間バッファの使用率を向上させることができる。

【0072】

なお、本実施形態では、2バンクの記憶部を有する例を説明したが、上述のように入出力を時分割で行うことを許容すれば、1バンクの記憶部において複数データを用いることも可能である。例えば、大容量の記憶部を用いて、複数データのそれぞれに対応する入力先頭アドレスと出力先頭アドレスを設定することによって本実施形態と同様に処理することができる。

【0073】

<<その他の実施形態>>

また、上述の説明では、画像データの読み書きの単位を32Byteとして説明した。しかしながら、画像処理装置上でのRAM106の構成や、RAM106を実現する記憶装置(DRAM等)の種類、そして実行する画像処理の種類等により、画像データの読み書き単位は必ずしも32Byteでなくてもよい。読み書きの単位が変わったとしても、画像データを記憶する中間バッファの容量の算出式を変えるだけで、画像処理装置と画像処理方法を適用することができる。

【0074】

また、画像データの32Byte単位のデータ構造が図4Aの494のように4×2画素を示すような場合においても、同様に画像データを記憶する中間バッファの容量の算出のしかたが変わるだけである。上述の説明では、入力バンドの高さBdh_inや出力バンドの高さBdh_outで中間バッファの容量を割り当てた。4×2画素のデータ構造においては、入力バンドの高さBdh_inや出力バンドの高さBdh_outを2で除算した値を基準に、中間バッファの容量を割り当てることにより、対処可能である。

【0075】

また、前述までの説明では、主にバンド処理について説明した。しかしながら、別の領域分割手法であるブロック(タイル)処理についても上述の画像処理方法を適用できる。ブロック(タイル)処理では、主走査方向と副走査方向に沿って画像データを2次元で領域分割する。例えば、前述までに説明した小領域(処理単位)が、この2次元で領域分割された画素領域と考えればよい。小領域(1)から小領域(M)まで順次読み出す手法はブロック(タイル)処理そのものである。特許文献1のブロック(タイル)処理と特許文献2のバンド処理の主な違いは、画像データから画素値を生成するときの画素の走査方向の違いにすぎない。特許文献1のブロック(タイル)処理では、画像処理実行部に入力する画素の走査を主走査方向に沿って行う。一方、特許文献2のバンド処理では、画像処理実行部に入力する画素の走査をバンドの高さ(副走査方向)に沿って行う。しかしながら、いずれの場合も、画像データを記憶する中間バッファの容量の算出のし方は変わらない。

【0076】

また、もしRAM106の記憶容量に余裕があり、局所(近傍)画像処理における遅延メモリを省容量化する必要がなければ、バンド処理を行わず、1つ分の画像データ300をRAM106に格納し、1画像の単位で画像処理を行ってもよい。そのときバンドの高さではなく副走査方向の画像データの大きさで中間バッファの入力領域と出力領域の容量を割り当てればよい。

【0077】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【特許請求の範囲】

【請求項1】

画像データに含まれる1つ以上の画素からなる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して出力画素領域を出力するデータ処理装置であって、

前記入力画素領域のデータと、前記出力画素領域のデータとを一時的に記憶する記憶手段と、

前記入力画素領域の画素数と、前記出力画素領域の画素数とに基づいて、前記入力画素領域のデータを記憶する前記記憶手段の入力領域の大きさと、前記出力画素領域のデータを記憶する前記記憶手段の出力領域の大きさとを設定する設定手段と、

を有することを特徴とするデータ処理装置。

【請求項2】

前記設定手段は、前記画像処理手段で実行する処理が変更された場合に、前記入力画素領域の画素数と前記出力画素領域の画素数との変化に基づいて、前記入力領域の大きさと前記出力領域の大きさとを変更する、

ことを特徴とする請求項1に記載のデータ処理装置。

【請求項3】

前記設定手段は、前記入力画素領域の一辺の画素数と、前記出力画素領域の一辺の画素数とに基づいて、前記入力領域と前記出力領域の大きさとを設定する、

ことを特徴とする請求項1又は2に記載のデータ処理装置。

【請求項4】

前記入力画素領域は、前記画像データを主走査方向または副走査方向のいずれかにおいて分割して得られる領域の一部または全部の領域の画素値を有するデータであり、

前記入力画素領域の一辺は前記画素領域における前記画像データが分割された側の一辺であり、前記出力画素領域の一辺は画像処理を施した後の画素領域における前記分割された側の一辺に対応する辺である、

ことを特徴とする請求項3に記載のデータ処理装置。

【請求項5】

前記データ処理装置は、1つ以上の入力画素領域に含まれる画素値をそれぞれ前記画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して1つ以上の出力画素領域としてそれぞれ出力し、

前記設定手段は、前記1つ以上の入力画素領域の数と、前記1つ以上の出力画素領域の数とに基づいて、前記入力領域と前記出力領域の大きさとを設定することを特徴とする請求項1から4のいずれか1項に記載のデータ処理装置。

【請求項6】

前記設定手段は、前記入力画素領域の数に応じた数の前記入力領域を設定し、前記出力画素領域の数に応じた数の前記出力領域を設定する、

ことを特徴とする請求項5に記載のデータ処理装置。

【請求項7】

前記設定手段は、前記入力画素領域の画素数と、前記出力画素領域の画素数との比に基づいて前記入力領域の大きさと前記出力領域の大きさとを設定する、

ことを特徴とする請求項1から6のいずれか1項に記載のデータ処理装置。

【請求項8】

前記設定手段は、前記記憶手段の前記入力領域と前記出力領域の大きさに基づいて、その入力領域と出力領域との前記記憶手段における先頭アドレスを設定することにより、前記入力領域と前記出力領域とを設定する、

ことを特徴とする請求項1から7のいずれか1項に記載のデータ処理装置。

【請求項9】

前記記憶手段は複数のバンクを有し、

前記設定手段は、その複数のバンクに対して共通の前記先頭アドレスを、前記記憶手段の前記入力領域と前記出力領域とについてそれぞれ設定する、

ことを特徴とする請求項8に記載のデータ処理装置。

【請求項10】

前記入力画素領域は、前記画像データを前記記憶手段の前記入力領域の大きさに基づいて分割して得られる1つ以上の画素値を含む領域である、

ことを特徴とする請求項1から9のいずれか1項に記載のデータ処理装置。

【請求項11】

画像データに含まれる1つ以上の画素からなる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して出力画素領域を出力し、前記入力画素領域のデータと、前記出力画素領域のデータとを一時的に記憶する記憶手段を有するデータ処理装置におけるデータ処理方法であって、

設定手段が、前記入力画素領域の画素数と、前記出力画素領域の画素数とに基づいて、前記入力画素領域のデータを記憶する前記記憶手段の入力領域の大きさと、前記出力画素領域のデータを記憶する前記記憶手段の出力領域の大きさとを設定する設定工程、

を有することを特徴とする処理方法。

【請求項12】

コンピュータを請求項1から10のいずれか1項に記載のデータ処理装置が備える各手段として機能させるためのプログラム。

【請求項1】

画像データに含まれる1つ以上の画素からなる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して出力画素領域を出力するデータ処理装置であって、

前記入力画素領域のデータと、前記出力画素領域のデータとを一時的に記憶する記憶手段と、

前記入力画素領域の画素数と、前記出力画素領域の画素数とに基づいて、前記入力画素領域のデータを記憶する前記記憶手段の入力領域の大きさと、前記出力画素領域のデータを記憶する前記記憶手段の出力領域の大きさとを設定する設定手段と、

を有することを特徴とするデータ処理装置。

【請求項2】

前記設定手段は、前記画像処理手段で実行する処理が変更された場合に、前記入力画素領域の画素数と前記出力画素領域の画素数との変化に基づいて、前記入力領域の大きさと前記出力領域の大きさとを変更する、

ことを特徴とする請求項1に記載のデータ処理装置。

【請求項3】

前記設定手段は、前記入力画素領域の一辺の画素数と、前記出力画素領域の一辺の画素数とに基づいて、前記入力領域と前記出力領域の大きさとを設定する、

ことを特徴とする請求項1又は2に記載のデータ処理装置。

【請求項4】

前記入力画素領域は、前記画像データを主走査方向または副走査方向のいずれかにおいて分割して得られる領域の一部または全部の領域の画素値を有するデータであり、

前記入力画素領域の一辺は前記画素領域における前記画像データが分割された側の一辺であり、前記出力画素領域の一辺は画像処理を施した後の画素領域における前記分割された側の一辺に対応する辺である、

ことを特徴とする請求項3に記載のデータ処理装置。

【請求項5】

前記データ処理装置は、1つ以上の入力画素領域に含まれる画素値をそれぞれ前記画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して1つ以上の出力画素領域としてそれぞれ出力し、

前記設定手段は、前記1つ以上の入力画素領域の数と、前記1つ以上の出力画素領域の数とに基づいて、前記入力領域と前記出力領域の大きさとを設定することを特徴とする請求項1から4のいずれか1項に記載のデータ処理装置。

【請求項6】

前記設定手段は、前記入力画素領域の数に応じた数の前記入力領域を設定し、前記出力画素領域の数に応じた数の前記出力領域を設定する、

ことを特徴とする請求項5に記載のデータ処理装置。

【請求項7】

前記設定手段は、前記入力画素領域の画素数と、前記出力画素領域の画素数との比に基づいて前記入力領域の大きさと前記出力領域の大きさとを設定する、

ことを特徴とする請求項1から6のいずれか1項に記載のデータ処理装置。

【請求項8】

前記設定手段は、前記記憶手段の前記入力領域と前記出力領域の大きさに基づいて、その入力領域と出力領域との前記記憶手段における先頭アドレスを設定することにより、前記入力領域と前記出力領域とを設定する、

ことを特徴とする請求項1から7のいずれか1項に記載のデータ処理装置。

【請求項9】

前記記憶手段は複数のバンクを有し、

前記設定手段は、その複数のバンクに対して共通の前記先頭アドレスを、前記記憶手段の前記入力領域と前記出力領域とについてそれぞれ設定する、

ことを特徴とする請求項8に記載のデータ処理装置。

【請求項10】

前記入力画素領域は、前記画像データを前記記憶手段の前記入力領域の大きさに基づいて分割して得られる1つ以上の画素値を含む領域である、

ことを特徴とする請求項1から9のいずれか1項に記載のデータ処理装置。

【請求項11】

画像データに含まれる1つ以上の画素からなる入力画素領域を取得して、その入力画素領域に含まれる画素値を画像処理手段へ入力し、画像処理を施された後の画素値を前記画像処理手段から取得して出力画素領域を出力し、前記入力画素領域のデータと、前記出力画素領域のデータとを一時的に記憶する記憶手段を有するデータ処理装置におけるデータ処理方法であって、

設定手段が、前記入力画素領域の画素数と、前記出力画素領域の画素数とに基づいて、前記入力画素領域のデータを記憶する前記記憶手段の入力領域の大きさと、前記出力画素領域のデータを記憶する前記記憶手段の出力領域の大きさとを設定する設定工程、

を有することを特徴とする処理方法。

【請求項12】

コンピュータを請求項1から10のいずれか1項に記載のデータ処理装置が備える各手段として機能させるためのプログラム。

【図1A】

【図1B】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図1B】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【公開番号】特開2013−73508(P2013−73508A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−213380(P2011−213380)

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月28日(2011.9.28)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]