データ処理装置およびデータ処理方法およびプログラム

【課題】演算部の演算開始タイミングを変化させてデータ処理を行うデータ処理装置を実現する。

【解決手段】メモリ400aは、先行して演算を実行する処理部200aが生成したデータを蓄積する。メモリ監視部450は、メモリ400aが蓄積するデータのデータ数を監視し、後続して演算を実行する処理部200bが演算に必要なデータ数が蓄積されたら、メモリ400aが蓄積するデータを処理部200bに出力させる。処理部200bはデータが出力されるタイミングで演算を開始し、データが出力されるタイミングの変化に対応して、処理部200bの演算開始タイミングが変化する。

【解決手段】メモリ400aは、先行して演算を実行する処理部200aが生成したデータを蓄積する。メモリ監視部450は、メモリ400aが蓄積するデータのデータ数を監視し、後続して演算を実行する処理部200bが演算に必要なデータ数が蓄積されたら、メモリ400aが蓄積するデータを処理部200bに出力させる。処理部200bはデータが出力されるタイミングで演算を開始し、データが出力されるタイミングの変化に対応して、処理部200bの演算開始タイミングが変化する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、複数の異なる処理を行うデータ処理装置およびデータ処理方法およびプログラムに関する。

【背景技術】

【0002】

従来、複数の異なる演算を行う複数の演算部(演算ブロック)を備え、演算部の実行順序を入れ替えることで複数の異なるシステムに対応した複数の異なる処理を行うデータ処理装置が知られている(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−110528号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来のデータ処理装置は、先行して演算が行われる演算部の演算終了後に、後続して演算が行われる演算部の演算が開始される為、各演算部の演算時間が考慮された各演算部の制御情報を予め記憶しておく必要があるという課題があった。

また、先行して演算が行われる演算部から入力される演算結果に応じて、演算内容が変化する演算部がある。そして、この演算内容が変化する演算部は、演算時間が変化するため、演算内容が変化する演算部に後続して演算が行われる演算部の演算の開始タイミングが変化することとなる。しかし、従来のデータ処理装置は、演算部の演算開始タイミングを変化させて処理を行うことが出来ないという課題があった。

【0005】

この発明は前記のような課題を解決することを主な目的とするもので、例えば、演算部の演算開始タイミングを変化させて処理を行うデータ処理装置を実現することを主な目的とする。

【課題を解決するための手段】

【0006】

この発明に係るデータ処理装置は、

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部と、

演算部毎に、演算単位データ数を記憶するデータ数記憶部と、

前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択部と、

前記選択部により選択された先行演算部が生成したデータを蓄積するデータ蓄積部と、

前記データ蓄積部に蓄積されるデータのデータ数を監視し、前記データ蓄積部のデータ数が前記後続演算部の演算単位データ数に達した際に、前記データ蓄積部に蓄積されているデータを前記データ蓄積部から前記後続演算部に出力させるデータ監視部と

を備えることを特徴とする。

【発明の効果】

【0007】

この発明に係るデータ処理装置は、先行演算部のデータをデータ蓄積部が蓄積する。そして、データ蓄積部に蓄積されたデータのデータ数が後続演算部の必要データ数になった場合に、データ蓄積部からデータが出力される。そして、後続演算部は、データが出力されたタイミングで、演算を開始し、データが出力されるタイミングの変化に対応して、後続演算部の演算開始タイミングが変化する。

したがって、演算部の演算開始タイミングを変化させて処理を行うデータ処理装置を実現する。

【図面の簡単な説明】

【0008】

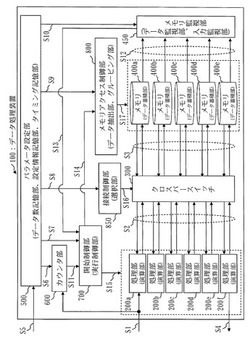

【図1】実施の形態1を示す図で、データ処理装置の構成の例を示す図。

【図2】実施の形態1を示す図で、データ処理の具体例を示す図。

【図3】実施の形態1を示す図で、データ処理の例を示すフローチャート。

【図4】実施の形態1を示す図で、イネーブル信号の例を示す図。

【図5】実施の形態1を示す図で、メモリアドレスの例を示す図。

【図6】実施の形態1を示す図で、データ蓄積処理の例を示すフローチャート。

【図7】実施の形態2を示す図で、データ処理装置の構成の例を示す図。

【図8】実施の形態2を示す図で、データ処理の例を示すフローチャート。

【図9】実施の形態1〜2を示す図で、本実施の形態に示したデータ処理装置のハードウェア資源の例を示す図。

【発明を実施するための形態】

【0009】

実施の形態1.

まず、図1と図2とを用いてデータ処理装置の概要と構成とについて説明する。

図1は、データ処理装置の構成の例を示す図である。

図2は、データ処理の具体例を示す図である。

【0010】

(データ処理装置の概要)

データ処理装置100は、複数の処理部200と複数のメモリ400とを備える。

複数の処理部200は、それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する。

また、メモリ400は、処理部200が生成したデータを蓄積する。

ここで、処理部200は、演算部に対応する。また、処理部200は信号処理ブロックや前述の演算ブロックにも対応する。

また、メモリ400は、データ蓄積部に対応する。

なお、図1には、6個の処理部200と5個のメモリ400との例を示したが、処理部200は3個以上であり、メモリ400は2個以上であればよい。

ここで、特に具体例を用いず、データ処理装置100に備えられる複数の処理部200の数を示す場合は、M個の処理部200と以降称する。

【0011】

データ処理装置100は、外部のシステムから入力信号S1(図1)を入力し、データ処理を行った後、出力信号S4(図1)を外部のシステムに出力する。データ処理装置100は、外部のシステムからの信号にデータ処理を行い、外部のシステムに転送するデータ転送装置である。

【0012】

データ処理装置100は、例えばシステムX用のデータ処理においては、図2に示すように、「処理部200a→メモリ400a→処理部200b→メモリ400b→処理部200f」と接続されることにより、システムX用のデータ処理を行う。

また、図示は省略するが、例えばシステムY用のデータ処理においては、「処理部200a→メモリ400b→処理部200c→メモリ400c→処理部200e」と接続されることにより、システムY用のデータ処理を行う。

このように、データ処理装置100は、使用する処理部200とその実行順序を入れ替えることで複数の異なるシステムに対応した複数の異なるデータ処理を行う。

【0013】

(データ処理装置の構成)

データ処理装置100は、前述で説明の処理部200とメモリ400との他に、クロスバースイッチ300、メモリ監視部450、パラメータ設定部500、カウンタ部600、開始制御部700、メモリアクセス制御部800、接続制御部850を備える。

【0014】

クロスバースイッチ300は、処理部200とメモリ400とを接続する接続部である。なお、処理部200とメモリ400とのデータ通信が可能であれば、接続部はクロスバースイッチ300に限定するものではない。

【0015】

メモリ監視部450は、メモリ400に蓄積されるデータのデータ数を監視する。ここで、メモリ監視部450は、データ監視部と入力監視部とに対応する。

パラメータ設定部500は、外部からパラメータ信号S5(図1)を入力する。このパラメータ信号S5には、各種のパラメータ(後述)が含まれる。データ処理装置100は、この各種のパラメータが示す情報を用いることにより各種の制御を行う。そして、パラメータ設定部500は、パラメータ信号S5に含まれる各種のパラメータを記憶する。なお、パラメータの種類によっては、パラメータがパラメータ信号S5の入力以前に、予めパラメータ設定部500に記憶されていてもよい。ここで、パラメータ設定部500は、データ数記憶部、設定情報記憶部、タイミング記憶部に対応する。

カウンタ部600は、所定のカウント(後述)を行う。

開始制御部700は、特定の処理部200に演算処理を開始させる。開始制御部700は、実行制御部に対応する。

接続制御部850は、クロスバースイッチ300(接続部)による処理部200とメモリ400との接続を制御する。接続制御部850は、選択部に対応する。

メモリアクセス制御部800は、データが蓄積されるメモリ400内のメモリアドレスや、イネーブル信号(後述)を生成する。メモリアクセス制御部800は、データ抽出部、グルーピング部に対応する。

【0016】

(設定情報の説明)

次に設定情報の説明を行う。

データ処理装置100は、前述の通り複数の処理部200(M個の処理部200)を備える。

パラメータ設定部500は、システム毎(システムX、システムY等)にM個の処理部200のうちのいずれかN個(N≧3)の処理部200が指定される設定情報を記憶する。ここでM≧Nである。パラメータ設定部500は、設定情報記憶部に対応する。なお、設定情報は前述のパラメータの一種である。

【0017】

そして、図1と図2との例の設定情報は、M個の処理部200である処理部200a〜200fの6個のうち、N個の処理部200として、処理部200a、処理部200b、処理部200fの3個が指定される。そして、図2の例の設定情報は、処理部200a→処理部200b→処理部200fの実行順序が示される。

更に、パラメータ設定部500は、例えば、前例のシステムX用とシステムY用との複数種の設定情報を記憶し、それぞれの設定情報に指定される処理部200の組合せは異なる。

【0018】

パラメータ設定部500が記憶する複数種の設定情報は、前述のようにそれぞれ複数種の異なるシステム(例えば前述のシステムXやシステムY)に対応付けられている。

そして、データ処理装置100がデータ処理を行う対象のシステム(例えばシステムX)が例えばデータ処理装置100のユーザに選択されることにより、設定情報が選択されることとなる。

【0019】

また、図示は省略するが、設定情報に指定されるN個の処理部200が同じであったとしても、その実行順序が異なれば、データ処理装置100は、異なるデータ処理を行う。

すなわち、この場合、パラメータ設定部500は、N個の処理部200の実行順序が相互に異なる複数種の設定情報を記憶する。

【0020】

データ処理装置100は、データ処理を開始する前に、外部からパラメータ信号S5を入力する。このパラメータ信号S5には、データ処理装置100がデータ処理を行う対象のシステム(例えばシステムX)が示されている。

そして、パラメータ設定部500は、設定情報を予め複数種の異なるシステムに対応付けて記憶していてもよい。また、パラメータ設定部500は、パラメータ信号S5として入力された設定情報を複数種の異なるシステムに対応付けて、パラメータ信号S5が入力される度に蓄積して記憶してもよい。また、パラメータ設定部500は、特定のシステムに対応するパラメータ信号S5として入力された設定情報のみを記憶してもよい。

【0021】

(接続制御部の動作説明)

次に、接続制御部850の動作説明を行う。

接続制御部850は、複数種の設定情報の中から、パラメータ設定部500に記憶されている設定情報を選択する。ここで、パラメータ設定部500が予め複数種の異なるシステムに対応付けて複数種の設定情報を記憶している場合、接続制御部850はパラメータ信号S5に示されるデータ処理装置100がデータ処理を行う対象のシステムに対応付けられた設定情報を選択する。また、接続制御部850がパラメータ信号S5として入力された設定情報のみを記憶している場合は、接続制御部850は、その入力された設定情報を選択する。

【0022】

そして、接続制御部850は、例えば、図2の例の設定情報に従って、先行演算部と後続演算部とを選択する。

ここで、例えば、処理部200aは処理部200bに対して、先行して演算を実行する処理部200であり、この先行して演算を実行する処理部200を「先行演算部」と称する。また、処理部200bは、処理部200a(先行演算部)により生成されるデータを用いて演算を実行する処理部200であり、この先行演算部により生成されるデータを用いて演算を実行する処理部200を「後続演算部」と称する。

【0023】

例えば、図2の例の設定情報において、前述のように実行順序が「処理部200a→処理部200b→処理部200f」と示される。接続制御部850は、設定情報に示される実行順序に従って最初に処理部200aを先行演算部として選択する。そして、接続制御部850は、処理部200bを後続演算部として選択する。引き続き、接続制御部850は、処理部200bを先行演算部として選択し、処理部200fを後続演算部として選択する。

ここで、メモリ400aは、接続制御部850により先行演算部として選択された処理部200aが生成したデータを蓄積する。同様にメモリ400bは、接続制御部850により先行演算部として選択された処理部200bが生成したデータを蓄積する。

【0024】

ここで、図2の例において、接続制御部850は、6個(M個)の演算部から設定情報で指定されているN個の処理部200として、3個の演算部を選択している。

また、接続制御部850は、3個(N個)の処理部200に対して、2個(N−1)個のメモリ400を選択している。

ここで、接続制御部850により選択されるメモリ400の情報が設定情報に含まれている場合は、接続制御部850は設定情報に従ってメモリ400を選択してもよい。また、データ処理装置100は任意のメモリ400を選択してもよい(特に、メモリ400が全て同性能(データ蓄積に要する時間や、蓄積可能な容量などが同じ)である場合など)。

【0025】

そして、接続制御部850は、3個(N個)の処理部200において先行演算部と後続演算部とのペアを2個(N−1)個生成している。

各メモリ400は、いずれかのペアの先行演算部と後続演算部とに対応付けられ、対応付けられた先行演算部が生成したデータを蓄積する。

【0026】

なお、接続制御部850は、前述のように、いずれかのペアの後続演算部として選択した演算部を、他のいずれかのペアの先行演算部として選択する。

【0027】

そして、接続制御部850は、選択した処理部200とメモリ400とで設定情報に示された実行順序に沿ってデータ通信が行われるように、クロスバースイッチ300(接続部)の接続を制御する。

【0028】

(データ処理の動作説明)

次に、図3を用いて、データ処理の動作について説明する。

図3は、データ処理の例を示すフローチャートである。

なお、ここでは、図2に示すデータ処理の具体例を想定して説明を進める。

【0029】

まず、パラメータ設定部500は、外部のシステムからパラメータ信号S5(図1)を入力する(図3のST301)。このパラメータ信号S5には、演算単位データ数(各処理部200が演算に必要なデータのデータ数)の情報が含まれている。そして、パラメータ設定部500は、パラメータ信号S5に示される演算単位データ数を処理部200毎に記憶する。

開始制御部700は、パラメータ設定部500から先頭演算部(処理部200a)の演算単位データ数を読み出す(図1のS7)。

また、同様に、メモリ監視部450は、各処理部200の演算単位データ数を読み出す(図1のS10)。

【0030】

そして、接続制御部850は、前述で説明の通り、設定情報を読み出し(図1のS8)、図2に示すデータ処理が行われるようにクロスバースイッチ300を制御する(図1のS16、図3のST302)。つまり、クロスバースイッチ300は、「処理部200a→メモリ400a→処理部200b→メモリ400b→処理部200f」とデータ通信が行われるように接続を行う。

【0031】

次に、処理部200のうち実行順序において先頭に位置する演算部(先頭に位置する演算部を先頭演算部と称する)は、演算実行時に外部から入力信号S1(図1)を入力する(図3のST303)。

図2の例においては、先頭演算部は処理部200aとなっているが、データ処理装置100が行うデータ処理の内容によっては、先頭演算部は処理部200a以外(例えば処理部200b)であってもよい。

ここで、入力信号S1は、クロック信号に同期している。そして、このクロック信号は、データ処理装置100と外部のシステムとの間でも同期されている。

そして、入力信号S1は、例えば、16ビットのデータがクロック信号毎に対応付けられている。

【0032】

カウンタ部600は、入力信号S1が入力されるとカウントアップを開始する(図3のST304)。具体的には、カウンタ部600は、クロック信号をカウントする。すなわち、カウンタ部600は、入力信号S1が入力されてからのクロック信号をカウントすることで、先頭演算部(処理部200a)に入力されるデータのデータ数をカウントする。

なお、入力信号S1が入力されるタイミングのクロック信号は予め特定されており、その特定されているクロック信号の情報がパラメータ信号S5に含まれていてもよい。そして、パラメータ設定部500は、カウントアップ開始信号S6(図1)を生成し、カウントアップの開始をカウンタ部600に通知することができる。

【0033】

そして、開始制御部700は、カウンタ部600のカウント値を入力し(図1のS11)、カウンタ部600のカウント値が演算単位データ数と等しくなるまで待機する(図3のST305の「NO」)。そして、開始制御部700は、カウンタ部600のカウント値が演算単位データ数と等しくなったら、演算を実行させるコマンドを先頭演算部に出力する(図1のS15、図3のST305の「YES」)。すなわち、開始制御部700は、先頭演算部(処理部200a)により入力されたデータのデータ数が先頭演算部(処理部200a)の演算単位データ数に達したら、演算を実行させるコマンドを先頭演算部に出力する。

【0034】

なお、先頭演算部(処理部200a)の演算が実行された後も、先頭演算部(処理部200a)に継続して入力信号S1が入力される場合、カウンタ部600は、カウンタ値をリセットして再度カウントアップを開始し、開始制御部700は前述と同様の処理を行う。

【0035】

先頭演算部(処理部200a)は、演算を実行すると、順次演算結果を例えば16ビット毎にクロック信号と同期させて出力する(図1のS2、図3のST306)。

ここで、処理部200aは、先頭演算部でもあり、処理部200bを後続演算部とした場合の先行演算部でもある。以降、処理部200aを先行演算部として説明を進める。

【0036】

メモリ400aは、データを蓄積する(図1のS3、図3のST308)。

ここでは、メモリ400は、先頭演算部が出力したデータを全て蓄積し、後続演算部は先頭演算部が出力したデータを全て用いて演算するものとする。

そして、例えば、メモリ400は、データがクロック信号毎に同期されて入力される度に、メモリアドレスを1つずつインクリメントし、各メモリアドレスに順次データを蓄積するものとする。

この場合は、図3のST307の処理は省略可能である。

【0037】

一方、メモリ400は、先頭演算部が出力したデータのうち、後続演算部が演算に必要なデータのみを蓄積することも可能である。また、メモリ400は、生成されたメモリアドレスの情報に基づき、データを蓄積することも可能である。この場合、図3のST307の処理において、メモリアクセス制御部800は、イネーブル信号や、メモリアドレスを生成し(図1のS17)、メモリ400に蓄積されるデータとメモリアドレスの制御をすることが出来る(図3のST307)。この処理については後述で説明する。

【0038】

メモリ監視部450は、メモリ400bに蓄積されるデータのデータ数を監視する(図1のS12)。そして、メモリ監視部450は、メモリ400bのデータ数が後続演算部(処理部200b)の演算単位データ数に達した際に(図3のST309の「YES」)、メモリ400bに蓄積されているデータをメモリ400bから後続演算部(処理部200b)に出力させる(図1のS3、図3のST310)。

【0039】

ここで、メモリ監視部450がメモリ400に蓄積されているデータをメモリ400から処理部200に出力させる処理について説明する。

前述の例の場合、メモリ監視部450は、メモリ400bのデータ数が後続演算部(処理部200b)の演算単位データ数に達した際に、メモリ400bからデータを出力させるコマンドを開始制御部700に出力する(図1のS13)。

そして、開始制御部700は、メモリアクセス制御部800にデータ出力のコマンドを転送し(図1のS14)、メモリアクセス制御部800はメモリ400bに蓄積されているデータを出力させる。あるいは、開始制御部700は、データ出力のコマンドを後続演算部(処理部200b)に転送し、後続演算部(処理部200b)がメモリ400bからデータを入力してもよい。

以降、メモリ監視部450がメモリ400に蓄積されているデータをメモリ400から処理部200に出力させる処理は同様であり、説明を省略する。

【0040】

ここで、メモリ監視部450はメモリ400bのデータ数が後続演算部(処理部200b)の演算単位データ数に達しない場合は、待機する(図3のST309の「NO」)。

【0041】

処理部200bは、クロスバースイッチ300経由でメモリ400bからデータを入力し(図1のS2)、演算を開始する。すなわち、処理部200bは、処理部200bの演算に必要なデータ数のデータが揃った時点で演算を開始する。

【0042】

ここで、処理部200bは、先行演算部として前述と同様に演算を開始する(図3のST306)。つまり、今度は、処理部200bが先行演算部となり、処理部200fが後続演算部となる。そして、図3のST306〜ST310の処理が同様に行われ、処理部200bは、演算結果をメモリ400bに蓄積し、処理部200fは、メモリ400bに処理部200fの演算に必要なデータ数のデータが揃った時点で演算を開始する。

ここで、処理部200fよりも後続の処理部200は設定されていないので、処理部200fは、演算結果を出力信号S4(図1)として外部に出力する。

【0043】

すなわち、接続制御部850により選択された先行演算部と後続演算部とのペア毎に、図3のST306〜ST310の処理が行われる。

【0044】

なお、例えば、メモリ400aに蓄積されたデータが処理部200bに出力された後も継続して、処理部200aからデータが生成されメモリ400aに蓄積される場合、メモリ監視部450は、データ数をリセットして再度監視を開始し、前述で説明と同様な処理を行う。

【0045】

そして、各処理部200は並列処理が可能であり、接続制御部850により選択された先行演算部と後続演算部とのペアは、継続して先行演算部にデータが入力されれば、図3のST306〜ST310の処理を各ペア間で並列して行う。

【0046】

つまり、メモリ監視部450は、いずれかのメモリ400のデータ数が、当該メモリ400に対応付けられている後続演算部の演算単位データ数に達した際に、当該メモリ400に蓄積されているデータを当該メモリ400から、当該メモリ400に対応付けられている後続演算部に出力させる。

【0047】

そして、最後に処理が行われる処理部200(図2の例では処理部200f)にデータが入力されなくなった場合にデータ処理装置100はデータ処理を終了する。ここで、最後に処理が行われる処理部200fにデータが入力されなくなった場合とは、例えば、入力信号S1が外部から入力されなくなり、メモリ400bに蓄積されるデータのデータ数が処理部200fのいずれかの処理部200の演算単位データ数に達しなくなる場合などが想定される。

【0048】

(イネーブル信号の説明)

ここで、前述では説明を省略したメモリ400が、先頭演算部が出力したデータのうち、後続演算部が演算に必要なデータのみを蓄積する場合や、メモリ400が、生成されたメモリアドレスの情報に基づき、データを蓄積する場合について説明する。

まず、メモリ400が、先頭演算部が出力したデータのうち、後続演算部が演算に必要なデータのみを蓄積する場合について説明する。

図4は、イネーブル信号の例を示す図である。

メモリアクセス制御部800は、パラメータ設定部500に記憶されているパラメータを入力し(図1のS9)、イネーブル信号を生成する(図3のST307)。

【0049】

イネーブル信号は、信号レベルが所定の値よりも高い「ハイレベル信号(H信号と称する)」と信号レベルが所定の値よりも低い「ローレベル信号(L信号と称する)」とから成る。デジタル信号で表現した場合に、H信号は「1」の信号で、L信号は「0」の信号となる。

そして、図4に示すイネーブル信号は、周期性を持った例であり、H信号である区間(H区間と称する)とL信号である区間(L区間と称する)とが1セットとなり、この1セットの周期が予めパラメータで設定された回数繰り返される。

そして、H区間には、予めパラメータで設定されたクロック信号の回数分のH信号が含まれ、同様にL区間には、予めパラメータで設定されたクロック信号の回数分のL信号が含まれる。

【0050】

前述で説明の通り、各処理部200は、データをクロック信号と同期させて出力する。すなわち、各処理部200は、各々に設けられている生成タイミングごとに繰り返しデータを生成する。

そして、イネーブル信号もクロック信号を同期している。

【0051】

そして、例えば、処理部200aがデータを生成する生成タイミングのうち、処理部200bが演算に必要なデータが生成されるタイミングが予めパラメータとして設定されている。そして、そのパラメータをパラメータ設定部500は外部からパラメータ信号S5として入力し、記憶している。

同様に、パラメータ設定部500は例えば、処理部200bがデータを生成する生成タイミングのうち、処理部200fが演算に必要なデータが生成されるタイミングが予めパラメータとして設定されている。

【0052】

前述の通り、接続制御部850は、先行演算部及び後続演算部として2つの処理部200を選択し、選択される2つの処理部200の組合せは1つ以上である。そして、パラメータ設定部500は、その組合せ毎に、先行演算部の生成タイミングのうち、後続演算部の演算に必要なデータが生成される必要データタイミングを記憶している。

【0053】

そして、メモリアクセス制御部800は、必要データタイミングにおいてH信号となるイネーブル信号を生成する。これによりメモリアクセス制御部800は、H区間のイネーブル信号に同期するクロック信号に対応したデータを抽出する。

すなわち、メモリアクセス制御部800は、接続制御部850により選択された先行演算部により生成されるデータのうち、必要データタイミングで生成されるデータを抽出する(図3のST307)。

【0054】

そして、メモリ400は、メモリアクセス制御部800により抽出されるデータを蓄積する(図3のST308)。

よって、後続演算部は、必要なデータのみを入力して処理を行うことができる。

【0055】

なお、イネーブル信号がH信号である状態とは、メモリへのデータ蓄積が有効な状態である。そして、イネーブル信号がH信号になることを「イネーブルがアサートされる」と称する。

例えば、H区間において、H信号が50回生成されているとすると、イネーブルが50回アサートされていることになる。

【0056】

(メモリアドレスの説明)

次に、メモリ400が、生成されたメモリアドレスの情報に基づき、データを蓄積する場合について説明する。

図5は、メモリアドレスの例を示す図である。

図6は、データ蓄積処理の例を示すフローチャートである。

前述で説明のように、メモリアドレスを1つずつインクリメントしながらデータを蓄積する場合は、メモリアクセス制御部800は、イネーブルが1回アサートされる時に、メモリアドレスを1つインクリメントしてメモリ400にデータを蓄積すればよい。

【0057】

ここでは、イネーブル信号を使ったデータ蓄積処理の例を説明する。

メモリアクセス制御部800は、パラメータ設定部500に記憶されているパラメータを入力する(図1のS9)。ここでは、メモリアクセス制御部800は、パラメータとして、オフセットアドレス、インクリメント値、不連続間隔値、不連続時の加算値が示される。これらのパラメータはパラメータ信号S5(図1)としてパラメータ設定部500により入力され、記憶されている。

【0058】

まず、処理部200が演算結果の出力を開始すると、メモリアクセス制御部800は、開始制御部700から処理の開始指示を入力する(図1のS14、図6のST1)。

【0059】

そして、メモリアクセス制御部800は、メモリアドレスとしてパラメータに示されるオフセットアドレスを設定する(図6のST2)。ここでオフセットアドレスとは、データの格納を開始するメモリアドレスの値である。図5においてはオフセットアドレスを「A」で示している。

【0060】

メモリアクセス制御部800は、イネーブルがアサートされたか否かを判定し、イネーブルがアサートされていない場合は(図6のST3の「NO」)、メモリアドレスの更新は行わず保持する(図6のST5)。

そして、イネーブルがアサートされた場合(図6のST3の「YES」)、メモリアクセス制御部800はイネーブル数をカウントする(図6のST4)。

すなわち、メモリアクセス制御部800はイネーブル信号に基づき、抽出されるデータのデータ数と抽出される順番とを監視する。

【0061】

そして、メモリアクセス制御部800は、イネーブル数がパラメータに示される不連続間隔値を超えるか否かを判定する(図6のST6)。ここで不連続間隔値は、後続演算部の演算単位データ数と等しく設定される。

すなわち、メモリアクセス制御部800は、抽出されるデータのデータ数が演算単位データ数を超えるか否かを判定する。

【0062】

イネーブル数が不連続間隔値を超えない場合(図6のST6の「NO」)、メモリアクセス制御部800は、パラメータに示されるインクリメント値を用いてデータが格納されるメモリアドレスを生成する(図6のST9)。

図5の例では、インクリメント値が「2」、不連続間隔値が「28」として設定されており、メモリアクセス制御部800は、抽出されたデータ数が「28」以内であれば、「A+0」、「A+2」と2つずつインクリメントしたメモリアドレスに各データを格納する。

【0063】

一方、イネーブル数が不連続間隔値を超える場合(図6のST6の「YES」)、メモリアクセス制御部800は、パラメータに示される不連続時の加算値を用いてメモリアドレスを生成する(図6のST7)。

図5の例では不連続時の加算値は「170」として設定されており、メモリアクセス制御部800は、抽出されたデータ数が「28」を超えた場合、「29」個目のデータが蓄積されるメモリアドレスを生成する。ここで、「28」個目のデータは「A+54」のメモリアドレスに蓄積されるので、「29」個目のデータは不連続時の加算値「170」を加えた「A+224」のメモリアドレスに蓄積される。

【0064】

そして、メモリアクセス制御部800は、イネーブル数のカウントを初期化(カウント値を「1」に設定)し(図6のST8)、再度イネーブル数をカウントする(図6のST3〜ST4)。

【0065】

すなわち、メモリアクセス制御部800は、抽出されるデータを、選択部により後続演算部として選択された演算部の演算単位データ数毎に、最初に抽出されるデータから順次グルーピングしている。そして、メモリ400は、メモリアクセス制御部800によりグルーピングされたグループ毎に区別してデータを蓄積する。

【0066】

(実施の形態1の効果)

以上のように、実施の形態1のデータ処理装置100は、各処理部200の動作開始をメモリ400の蓄積量に基づいて行う。そのため、データ処理装置100は、各演算部の制御情報を予め記憶しておく必要はなく、実際の信号処理の状態に合わせて各処理部200の動作タイミングを制御することができる。

【0067】

また、実施の形態1のデータ処理装置100は、メモリ400の蓄積量に基づいて処理部200の動作開始タイミングが与えられる。したがって、演算結果によって演算時間が変化する処理部200が有っても、演算時間が変化する処理部200に後続して演算が行われる処理部200も正しく動作開始タイミングが与えられる。よって、実施の形態1のデータ処理装置100は、演算結果によって演算時間が変化する処理部200が有っても、システム全体が正しく動作するように制御することができる。

【0068】

以上、実施の形態1においては、以下の特徴を備えたデータ処理装置100について説明した。

(1)複数のシステムの信号処理を行うことができるデータ処理装置100は、信号処理を行う複数の処理部200と、データを格納する複数のメモリ400と、処理部200とメモリ400を接続するクロスバースイッチ300と、信号処理に必要なパラメータを保持するパラメータ設定部500と、カウンタを保有するカウンタ部600と、メモリ400の蓄積量を監視するメモリ監視部450と、パラメータ設定部500からのパラメータとカウンタ部600からのカウント値の比較やメモリ監視部450からの情報に基づいて動作開始タイミングを指示する開始制御部700と、メモリ400のメモリアドレスやイネーブル信号を生成するメモリアクセス制御部800と、クロスバースイッチ300の接続先を設定する接続制御部850とを備える。

(2)開始制御部700は、カウンタ部600からのカウンタ値とパラメータ設定部500からの動作開始タイミングパラメータを比較し、一致した場合に処理部200に動作開始指示を与える。

(3)メモリ監視部450は、メモリ400に蓄積されたデータ量を監視し、パラメータ設定部500から与えられる次にメモリ400から読み出しを行う処理部200が必要なデータ量が蓄積された場合に、開始制御部700に開始指示を通知する。

(4)メモリアクセス制御部800は、パラメータに基づいてイネーブル信号を生成する。例えば、メモリアクセス制御部800は、H区間サイクル数パラメータ、L区間サイクル数パラメータ、セット回数パラメータを用いてイネーブル信号を生成する。

(5)メモリアクセス制御部800は、パラメータに基づいてメモリアドレスを生成する。例えば、メモリアクセス制御部800は、オフセットアドレスパラメータ、インクリメント値パラメータ、不連続間隔パラメータ、不連続時の加算値パラメータを用いてアドレスを生成する。

【0069】

実施の形態2.

(実施の形態2におけるデータ処理装置の概要)

実施の形態1におけるデータ処理装置100では、処理部200が外部からの入力信号S1を入力したが、実施の形態2におけるデータ処理装置100では、メモリ400が外部からの入力信号S1を入力する実施形態を説明する。

【0070】

図7は、データ処理装置の構成の例を示す図である。

実施の形態2のデータ処理装置100は、図1に示す実施の形態1のデータ処理装置100と比べ、前述の通り、メモリ400が入力信号S1を入力する点とカウンタ部600が無い点とが異なる。

そして、以上の相違点以外、実施の形態2におけるデータ処理装置100は、実施の形態1におけるデータ処理装置100と同じ構成である。従って、実施の形態1と同じ構成要素と同じ処理内容とについては説明を省略する。

【0071】

(データ処理の動作説明)

図8は、データ処理の例を示すフローチャートである。

ここでは、「メモリ400a→処理部200b→メモリ400b→処理部200f」の順番でデータ処理が行われるものとする。この例においては、処理部200bが先頭演算部である。

【0072】

まず、実行順序において先頭に位置するメモリ400(メモリ400a)は、外部から入力信号S1(図7)を入力し、蓄積する(図8のST801)。ここで、外部からデータを入力し、入力したデータを蓄積するメモリ400を入力蓄積部と称する(図7において「入力蓄積部」の図示は省略する)。

本例においては、入力蓄積部はメモリ400aとなっているが、データ処理装置100が行うデータ処理の内容によっては、入力蓄積部はメモリ400a以外(例えばメモリ400b)であってもよい。

【0073】

メモリ監視部450は、入力蓄積部(メモリ400a)に蓄積されるデータのデータ数を監視する(図7のS12)。

そして、メモリ監視部450は、入力蓄積部(メモリ400a)のデータ数が先頭演算部(処理部200b)の演算単位データ数に達した際に(図8のST802の「YES」)、入力蓄積部に蓄積されているデータを入力蓄積部から先頭演算部(処理部200b)に出力させる(図8のST803)。

なお、メモリ監視部450は、入力蓄積部のデータ数が先頭演算部の演算単位データ数に達しない場合は、待機する(図8のST802の「NO」)。

【0074】

そして、先頭演算部(処理部200b)は、後続演算部(処理部200f)に対する先行演算部として図3のST306に示す処理を行う。以降は、実施の形態1と同様である為、説明を省略する。

【0075】

(実施の形態2の効果)

以上のように、実施の形態2のデータ処理装置100は、実施の形態1の効果に加えて、外部からのデータをメモリ400が入力することにより、すべての処理部200の動作開始タイミングをメモリ蓄積量に基づいて指示することができる。

【0076】

以上、実施の形態2においては、以下の特徴を備えたデータ処理装置100について説明した。

(1)複数のシステムの信号処理を行うことができるデータ処理装置100は、信号処理を行う複数の処理部200と、データを格納する複数のメモリ400と、処理部200とメモリ400を接続するクロスバースイッチ300と、信号処理に必要なパラメータを保持するパラメータ設定部500と、メモリ400の蓄積量を監視するメモリ監視部450と、メモリ監視部450からの情報に基づいて動作開始タイミングを指示する開始制御部700と、メモリ400のメモリアドレスやイネーブル信号を生成するメモリアクセス制御部800と、クロスバースイッチ300の接続先を設定する接続制御部850とを備える。

(2)メモリ監視部450は、メモリ400に蓄積されたデータ量を監視し、パラメータ設定部500から与えられる次にメモリ400から読み出しを行う処理部200が必要なデータ量が蓄積された場合に、開始制御部700に開始指示を通知する。

【0077】

(実施の形態1〜2のデータ処理装置100のハードウェア構成)

最後に、実施の形態1〜2に示したデータ処理装置100のハードウェア構成例について説明する。

図9は、本実施の形態に示したデータ処理装置100のハードウェア資源の一例を示す図である。

なお、図9の構成は、あくまでもデータ処理装置100のハードウェア構成の一例を示すものであり、データ処理装置100のハードウェア構成は図9に記載の構成に限らず、他の構成であってもよい。

【0078】

図9において、データ処理装置100は、プログラムを実行するCPU911(Central Processing Unit、中央処理装置、処理装置、演算装置、マイクロプロセッサ、マイクロコンピュータ、プロセッサともいう)を備えている。

CPU911は、バス912を介して、例えば、ROM(Read Only Memory)913、RAM(Random Access Memory)914、通信ボード915、表示装置901、キーボード902、マウス903、磁気ディスク装置920と接続され、これらのハードウェアデバイスを制御する。

更に、CPU911は、FDD904(Flexible Disk Drive)、コンパクトディスク装置905(CDD)と接続していてもよい。また、磁気ディスク装置920の代わりに、SSD(Solid State Drive)、光ディスク装置、メモリカード(登録商標)読み書き装置などの記憶装置でもよい。

RAM914は、揮発性メモリの一例である。ROM913、FDD904、CDD905、磁気ディスク装置920の記憶媒体は、不揮発性メモリの一例である。これらは、記憶装置の一例である。

本実施の形態で説明したパラメータ設定部500、メモリ400は、磁気ディスク装置920等により実現される。

通信ボード915、キーボード902、マウス903、FDD904などは、入力装置の一例である。

また、通信ボード915、表示装置901などは、出力装置の一例である。

【0079】

磁気ディスク装置920には、オペレーティングシステム921(OS)、ウィンドウシステム922、プログラム群923、ファイル群924が記憶されている。

プログラム群923のプログラムは、CPU911がオペレーティングシステム921、ウィンドウシステム922を利用しながら実行する。

【0080】

また、RAM914には、CPU911に実行させるオペレーティングシステム921のプログラムやアプリケーションプログラムの少なくとも一部が一時的に格納される。

また、RAM914には、CPU911による処理に必要な各種データが格納される。

【0081】

また、ROM913には、BIOS(Basic Input Output System)プログラムが格納され、磁気ディスク装置920にはブートプログラムが格納されている。

データ処理装置100の起動時には、ROM913のBIOSプログラム及び磁気ディスク装置920のブートプログラムが実行され、BIOSプログラム及びブートプログラムによりオペレーティングシステム921が起動される。

【0082】

上記プログラム群923には、本実施の形態の説明において「〜部」(「〜記憶部」以外、以下同様)として説明している機能を実行するプログラムが記憶されている。プログラムは、CPU911により読み出され実行される。

【0083】

ファイル群924には、本実施の形態の説明において、「〜の判断」、「〜の計算」、「〜の比較」、「〜の照合」、「〜の参照」、「〜の検索」、「〜の抽出」、「〜の検査」、「〜の生成」、「〜の設定」、「〜の登録」、「〜の選択」、「〜の入力」、「〜の受信」、「〜の判定」、「〜の定義」、「〜の算出」、「〜の更新」、「〜の登録」等として説明している処理の結果を示す情報やデータや信号値や変数値やパラメータが、「ファイル」や「データベース」の各項目として記憶されている。

「ファイル」や「データベース」は、ディスクやメモリなどの記録媒体に記憶される。

ディスクやメモリなどの記憶媒体に記憶された情報やデータや信号値や変数値やパラメータは、読み書き回路を介してCPU911によりメインメモリやキャッシュメモリに読み出される。

そして、読み出された情報やデータや信号値や変数値やパラメータは、抽出・検索・参照・比較・演算・計算・処理・編集・出力・印刷・表示・制御・判定・識別・検知・判別・選択・算出・導出・更新・生成・取得・通知・指示・判断・区別・削除・登録・付与・監視・待機などのCPUの動作に用いられる。

抽出・検索・参照・比較・演算・計算・処理・編集・出力・印刷・表示・制御・判定・識別・検知・判別・選択・算出・導出・更新・生成・取得・通知・指示・判断・区別・削除・登録・付与・監視・待機などのCPUの動作の間、情報やデータや信号値や変数値やパラメータは、メインメモリ、レジスタ、キャッシュメモリ、バッファメモリ等に一時的に記憶される。

また、本実施の形態で説明しているフローチャートの矢印の部分は主としてデータや信号の入出力を示す。

データや信号値は、RAM914のメモリ、FDD904のフレキシブルディスク、CDD905のコンパクトディスク、磁気ディスク装置920の磁気ディスク、その他光ディスク、ミニディスク、DVD等の記録媒体に記録される。

また、データや信号は、バス912や信号線やケーブルその他の伝送媒体によりオンライン伝送される。

【0084】

また、本実施の形態の説明において「〜部」として説明しているものは、「〜回路」、「〜装置」、「〜機器」であってもよく、また、「〜ステップ」、「〜手順」、「〜処理」であってもよい。

すなわち、本実施の形態で説明したフローチャートに示すステップ、手順、処理により、本発明に係る情報処理方法を実現することができる。

また、「〜部」として説明しているものは、ROM913に記憶されたファームウェアで実現されていても構わない。

或いは、ソフトウェアのみ、或いは、素子・デバイス・基板・配線などのハードウェアのみ、或いは、ソフトウェアとハードウェアとの組み合わせ、さらには、ファームウェアとの組み合わせで実施されても構わない。

ファームウェアとソフトウェアは、プログラムとして、磁気ディスク、フレキシブルディスク、光ディスク、コンパクトディスク、ミニディスク、DVD等の記録媒体に記憶される。

プログラムはCPU911により読み出され、CPU911により実行される。

すなわち、プログラムは、本実施の形態の「〜部」としてコンピュータを機能させるものである。あるいは、本実施の形態の「〜部」の手順や方法をコンピュータに実行させるものである。

【0085】

このように、本実施の形態に示すデータ処理装置100は、処理装置たるCPU、記憶装置たるメモリ、磁気ディスク等、入力装置たるキーボード、マウス、通信ボード等、出力装置たる表示装置、通信ボード等を備えるコンピュータである。

そして、上記したように「〜部」として示された機能をこれら処理装置、記憶装置、入力装置、出力装置を用いて実現するものである。

【符号の説明】

【0086】

100 データ処理装置、200 処理部、300 クロスバースイッチ、400 メモリ、450 メモリ監視部、500 パラメータ設定部、600 カウンタ部、700 開始制御部、800 メモリアクセス制御部、850 接続制御部、901 表示装置、902 キーボード、903 マウス、904 FDD、905 コンパクトディスク装置、911 CPU、912 バス、913 ROM、914 RAM、915 通信ボード、920 磁気ディスク装置、921 オペレーティングシステム、922 ウィンドウシステム、923 プログラム群、924 ファイル群。

【技術分野】

【0001】

この発明は、複数の異なる処理を行うデータ処理装置およびデータ処理方法およびプログラムに関する。

【背景技術】

【0002】

従来、複数の異なる演算を行う複数の演算部(演算ブロック)を備え、演算部の実行順序を入れ替えることで複数の異なるシステムに対応した複数の異なる処理を行うデータ処理装置が知られている(例えば、特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2004−110528号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来のデータ処理装置は、先行して演算が行われる演算部の演算終了後に、後続して演算が行われる演算部の演算が開始される為、各演算部の演算時間が考慮された各演算部の制御情報を予め記憶しておく必要があるという課題があった。

また、先行して演算が行われる演算部から入力される演算結果に応じて、演算内容が変化する演算部がある。そして、この演算内容が変化する演算部は、演算時間が変化するため、演算内容が変化する演算部に後続して演算が行われる演算部の演算の開始タイミングが変化することとなる。しかし、従来のデータ処理装置は、演算部の演算開始タイミングを変化させて処理を行うことが出来ないという課題があった。

【0005】

この発明は前記のような課題を解決することを主な目的とするもので、例えば、演算部の演算開始タイミングを変化させて処理を行うデータ処理装置を実現することを主な目的とする。

【課題を解決するための手段】

【0006】

この発明に係るデータ処理装置は、

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部と、

演算部毎に、演算単位データ数を記憶するデータ数記憶部と、

前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択部と、

前記選択部により選択された先行演算部が生成したデータを蓄積するデータ蓄積部と、

前記データ蓄積部に蓄積されるデータのデータ数を監視し、前記データ蓄積部のデータ数が前記後続演算部の演算単位データ数に達した際に、前記データ蓄積部に蓄積されているデータを前記データ蓄積部から前記後続演算部に出力させるデータ監視部と

を備えることを特徴とする。

【発明の効果】

【0007】

この発明に係るデータ処理装置は、先行演算部のデータをデータ蓄積部が蓄積する。そして、データ蓄積部に蓄積されたデータのデータ数が後続演算部の必要データ数になった場合に、データ蓄積部からデータが出力される。そして、後続演算部は、データが出力されたタイミングで、演算を開始し、データが出力されるタイミングの変化に対応して、後続演算部の演算開始タイミングが変化する。

したがって、演算部の演算開始タイミングを変化させて処理を行うデータ処理装置を実現する。

【図面の簡単な説明】

【0008】

【図1】実施の形態1を示す図で、データ処理装置の構成の例を示す図。

【図2】実施の形態1を示す図で、データ処理の具体例を示す図。

【図3】実施の形態1を示す図で、データ処理の例を示すフローチャート。

【図4】実施の形態1を示す図で、イネーブル信号の例を示す図。

【図5】実施の形態1を示す図で、メモリアドレスの例を示す図。

【図6】実施の形態1を示す図で、データ蓄積処理の例を示すフローチャート。

【図7】実施の形態2を示す図で、データ処理装置の構成の例を示す図。

【図8】実施の形態2を示す図で、データ処理の例を示すフローチャート。

【図9】実施の形態1〜2を示す図で、本実施の形態に示したデータ処理装置のハードウェア資源の例を示す図。

【発明を実施するための形態】

【0009】

実施の形態1.

まず、図1と図2とを用いてデータ処理装置の概要と構成とについて説明する。

図1は、データ処理装置の構成の例を示す図である。

図2は、データ処理の具体例を示す図である。

【0010】

(データ処理装置の概要)

データ処理装置100は、複数の処理部200と複数のメモリ400とを備える。

複数の処理部200は、それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する。

また、メモリ400は、処理部200が生成したデータを蓄積する。

ここで、処理部200は、演算部に対応する。また、処理部200は信号処理ブロックや前述の演算ブロックにも対応する。

また、メモリ400は、データ蓄積部に対応する。

なお、図1には、6個の処理部200と5個のメモリ400との例を示したが、処理部200は3個以上であり、メモリ400は2個以上であればよい。

ここで、特に具体例を用いず、データ処理装置100に備えられる複数の処理部200の数を示す場合は、M個の処理部200と以降称する。

【0011】

データ処理装置100は、外部のシステムから入力信号S1(図1)を入力し、データ処理を行った後、出力信号S4(図1)を外部のシステムに出力する。データ処理装置100は、外部のシステムからの信号にデータ処理を行い、外部のシステムに転送するデータ転送装置である。

【0012】

データ処理装置100は、例えばシステムX用のデータ処理においては、図2に示すように、「処理部200a→メモリ400a→処理部200b→メモリ400b→処理部200f」と接続されることにより、システムX用のデータ処理を行う。

また、図示は省略するが、例えばシステムY用のデータ処理においては、「処理部200a→メモリ400b→処理部200c→メモリ400c→処理部200e」と接続されることにより、システムY用のデータ処理を行う。

このように、データ処理装置100は、使用する処理部200とその実行順序を入れ替えることで複数の異なるシステムに対応した複数の異なるデータ処理を行う。

【0013】

(データ処理装置の構成)

データ処理装置100は、前述で説明の処理部200とメモリ400との他に、クロスバースイッチ300、メモリ監視部450、パラメータ設定部500、カウンタ部600、開始制御部700、メモリアクセス制御部800、接続制御部850を備える。

【0014】

クロスバースイッチ300は、処理部200とメモリ400とを接続する接続部である。なお、処理部200とメモリ400とのデータ通信が可能であれば、接続部はクロスバースイッチ300に限定するものではない。

【0015】

メモリ監視部450は、メモリ400に蓄積されるデータのデータ数を監視する。ここで、メモリ監視部450は、データ監視部と入力監視部とに対応する。

パラメータ設定部500は、外部からパラメータ信号S5(図1)を入力する。このパラメータ信号S5には、各種のパラメータ(後述)が含まれる。データ処理装置100は、この各種のパラメータが示す情報を用いることにより各種の制御を行う。そして、パラメータ設定部500は、パラメータ信号S5に含まれる各種のパラメータを記憶する。なお、パラメータの種類によっては、パラメータがパラメータ信号S5の入力以前に、予めパラメータ設定部500に記憶されていてもよい。ここで、パラメータ設定部500は、データ数記憶部、設定情報記憶部、タイミング記憶部に対応する。

カウンタ部600は、所定のカウント(後述)を行う。

開始制御部700は、特定の処理部200に演算処理を開始させる。開始制御部700は、実行制御部に対応する。

接続制御部850は、クロスバースイッチ300(接続部)による処理部200とメモリ400との接続を制御する。接続制御部850は、選択部に対応する。

メモリアクセス制御部800は、データが蓄積されるメモリ400内のメモリアドレスや、イネーブル信号(後述)を生成する。メモリアクセス制御部800は、データ抽出部、グルーピング部に対応する。

【0016】

(設定情報の説明)

次に設定情報の説明を行う。

データ処理装置100は、前述の通り複数の処理部200(M個の処理部200)を備える。

パラメータ設定部500は、システム毎(システムX、システムY等)にM個の処理部200のうちのいずれかN個(N≧3)の処理部200が指定される設定情報を記憶する。ここでM≧Nである。パラメータ設定部500は、設定情報記憶部に対応する。なお、設定情報は前述のパラメータの一種である。

【0017】

そして、図1と図2との例の設定情報は、M個の処理部200である処理部200a〜200fの6個のうち、N個の処理部200として、処理部200a、処理部200b、処理部200fの3個が指定される。そして、図2の例の設定情報は、処理部200a→処理部200b→処理部200fの実行順序が示される。

更に、パラメータ設定部500は、例えば、前例のシステムX用とシステムY用との複数種の設定情報を記憶し、それぞれの設定情報に指定される処理部200の組合せは異なる。

【0018】

パラメータ設定部500が記憶する複数種の設定情報は、前述のようにそれぞれ複数種の異なるシステム(例えば前述のシステムXやシステムY)に対応付けられている。

そして、データ処理装置100がデータ処理を行う対象のシステム(例えばシステムX)が例えばデータ処理装置100のユーザに選択されることにより、設定情報が選択されることとなる。

【0019】

また、図示は省略するが、設定情報に指定されるN個の処理部200が同じであったとしても、その実行順序が異なれば、データ処理装置100は、異なるデータ処理を行う。

すなわち、この場合、パラメータ設定部500は、N個の処理部200の実行順序が相互に異なる複数種の設定情報を記憶する。

【0020】

データ処理装置100は、データ処理を開始する前に、外部からパラメータ信号S5を入力する。このパラメータ信号S5には、データ処理装置100がデータ処理を行う対象のシステム(例えばシステムX)が示されている。

そして、パラメータ設定部500は、設定情報を予め複数種の異なるシステムに対応付けて記憶していてもよい。また、パラメータ設定部500は、パラメータ信号S5として入力された設定情報を複数種の異なるシステムに対応付けて、パラメータ信号S5が入力される度に蓄積して記憶してもよい。また、パラメータ設定部500は、特定のシステムに対応するパラメータ信号S5として入力された設定情報のみを記憶してもよい。

【0021】

(接続制御部の動作説明)

次に、接続制御部850の動作説明を行う。

接続制御部850は、複数種の設定情報の中から、パラメータ設定部500に記憶されている設定情報を選択する。ここで、パラメータ設定部500が予め複数種の異なるシステムに対応付けて複数種の設定情報を記憶している場合、接続制御部850はパラメータ信号S5に示されるデータ処理装置100がデータ処理を行う対象のシステムに対応付けられた設定情報を選択する。また、接続制御部850がパラメータ信号S5として入力された設定情報のみを記憶している場合は、接続制御部850は、その入力された設定情報を選択する。

【0022】

そして、接続制御部850は、例えば、図2の例の設定情報に従って、先行演算部と後続演算部とを選択する。

ここで、例えば、処理部200aは処理部200bに対して、先行して演算を実行する処理部200であり、この先行して演算を実行する処理部200を「先行演算部」と称する。また、処理部200bは、処理部200a(先行演算部)により生成されるデータを用いて演算を実行する処理部200であり、この先行演算部により生成されるデータを用いて演算を実行する処理部200を「後続演算部」と称する。

【0023】

例えば、図2の例の設定情報において、前述のように実行順序が「処理部200a→処理部200b→処理部200f」と示される。接続制御部850は、設定情報に示される実行順序に従って最初に処理部200aを先行演算部として選択する。そして、接続制御部850は、処理部200bを後続演算部として選択する。引き続き、接続制御部850は、処理部200bを先行演算部として選択し、処理部200fを後続演算部として選択する。

ここで、メモリ400aは、接続制御部850により先行演算部として選択された処理部200aが生成したデータを蓄積する。同様にメモリ400bは、接続制御部850により先行演算部として選択された処理部200bが生成したデータを蓄積する。

【0024】

ここで、図2の例において、接続制御部850は、6個(M個)の演算部から設定情報で指定されているN個の処理部200として、3個の演算部を選択している。

また、接続制御部850は、3個(N個)の処理部200に対して、2個(N−1)個のメモリ400を選択している。

ここで、接続制御部850により選択されるメモリ400の情報が設定情報に含まれている場合は、接続制御部850は設定情報に従ってメモリ400を選択してもよい。また、データ処理装置100は任意のメモリ400を選択してもよい(特に、メモリ400が全て同性能(データ蓄積に要する時間や、蓄積可能な容量などが同じ)である場合など)。

【0025】

そして、接続制御部850は、3個(N個)の処理部200において先行演算部と後続演算部とのペアを2個(N−1)個生成している。

各メモリ400は、いずれかのペアの先行演算部と後続演算部とに対応付けられ、対応付けられた先行演算部が生成したデータを蓄積する。

【0026】

なお、接続制御部850は、前述のように、いずれかのペアの後続演算部として選択した演算部を、他のいずれかのペアの先行演算部として選択する。

【0027】

そして、接続制御部850は、選択した処理部200とメモリ400とで設定情報に示された実行順序に沿ってデータ通信が行われるように、クロスバースイッチ300(接続部)の接続を制御する。

【0028】

(データ処理の動作説明)

次に、図3を用いて、データ処理の動作について説明する。

図3は、データ処理の例を示すフローチャートである。

なお、ここでは、図2に示すデータ処理の具体例を想定して説明を進める。

【0029】

まず、パラメータ設定部500は、外部のシステムからパラメータ信号S5(図1)を入力する(図3のST301)。このパラメータ信号S5には、演算単位データ数(各処理部200が演算に必要なデータのデータ数)の情報が含まれている。そして、パラメータ設定部500は、パラメータ信号S5に示される演算単位データ数を処理部200毎に記憶する。

開始制御部700は、パラメータ設定部500から先頭演算部(処理部200a)の演算単位データ数を読み出す(図1のS7)。

また、同様に、メモリ監視部450は、各処理部200の演算単位データ数を読み出す(図1のS10)。

【0030】

そして、接続制御部850は、前述で説明の通り、設定情報を読み出し(図1のS8)、図2に示すデータ処理が行われるようにクロスバースイッチ300を制御する(図1のS16、図3のST302)。つまり、クロスバースイッチ300は、「処理部200a→メモリ400a→処理部200b→メモリ400b→処理部200f」とデータ通信が行われるように接続を行う。

【0031】

次に、処理部200のうち実行順序において先頭に位置する演算部(先頭に位置する演算部を先頭演算部と称する)は、演算実行時に外部から入力信号S1(図1)を入力する(図3のST303)。

図2の例においては、先頭演算部は処理部200aとなっているが、データ処理装置100が行うデータ処理の内容によっては、先頭演算部は処理部200a以外(例えば処理部200b)であってもよい。

ここで、入力信号S1は、クロック信号に同期している。そして、このクロック信号は、データ処理装置100と外部のシステムとの間でも同期されている。

そして、入力信号S1は、例えば、16ビットのデータがクロック信号毎に対応付けられている。

【0032】

カウンタ部600は、入力信号S1が入力されるとカウントアップを開始する(図3のST304)。具体的には、カウンタ部600は、クロック信号をカウントする。すなわち、カウンタ部600は、入力信号S1が入力されてからのクロック信号をカウントすることで、先頭演算部(処理部200a)に入力されるデータのデータ数をカウントする。

なお、入力信号S1が入力されるタイミングのクロック信号は予め特定されており、その特定されているクロック信号の情報がパラメータ信号S5に含まれていてもよい。そして、パラメータ設定部500は、カウントアップ開始信号S6(図1)を生成し、カウントアップの開始をカウンタ部600に通知することができる。

【0033】

そして、開始制御部700は、カウンタ部600のカウント値を入力し(図1のS11)、カウンタ部600のカウント値が演算単位データ数と等しくなるまで待機する(図3のST305の「NO」)。そして、開始制御部700は、カウンタ部600のカウント値が演算単位データ数と等しくなったら、演算を実行させるコマンドを先頭演算部に出力する(図1のS15、図3のST305の「YES」)。すなわち、開始制御部700は、先頭演算部(処理部200a)により入力されたデータのデータ数が先頭演算部(処理部200a)の演算単位データ数に達したら、演算を実行させるコマンドを先頭演算部に出力する。

【0034】

なお、先頭演算部(処理部200a)の演算が実行された後も、先頭演算部(処理部200a)に継続して入力信号S1が入力される場合、カウンタ部600は、カウンタ値をリセットして再度カウントアップを開始し、開始制御部700は前述と同様の処理を行う。

【0035】

先頭演算部(処理部200a)は、演算を実行すると、順次演算結果を例えば16ビット毎にクロック信号と同期させて出力する(図1のS2、図3のST306)。

ここで、処理部200aは、先頭演算部でもあり、処理部200bを後続演算部とした場合の先行演算部でもある。以降、処理部200aを先行演算部として説明を進める。

【0036】

メモリ400aは、データを蓄積する(図1のS3、図3のST308)。

ここでは、メモリ400は、先頭演算部が出力したデータを全て蓄積し、後続演算部は先頭演算部が出力したデータを全て用いて演算するものとする。

そして、例えば、メモリ400は、データがクロック信号毎に同期されて入力される度に、メモリアドレスを1つずつインクリメントし、各メモリアドレスに順次データを蓄積するものとする。

この場合は、図3のST307の処理は省略可能である。

【0037】

一方、メモリ400は、先頭演算部が出力したデータのうち、後続演算部が演算に必要なデータのみを蓄積することも可能である。また、メモリ400は、生成されたメモリアドレスの情報に基づき、データを蓄積することも可能である。この場合、図3のST307の処理において、メモリアクセス制御部800は、イネーブル信号や、メモリアドレスを生成し(図1のS17)、メモリ400に蓄積されるデータとメモリアドレスの制御をすることが出来る(図3のST307)。この処理については後述で説明する。

【0038】

メモリ監視部450は、メモリ400bに蓄積されるデータのデータ数を監視する(図1のS12)。そして、メモリ監視部450は、メモリ400bのデータ数が後続演算部(処理部200b)の演算単位データ数に達した際に(図3のST309の「YES」)、メモリ400bに蓄積されているデータをメモリ400bから後続演算部(処理部200b)に出力させる(図1のS3、図3のST310)。

【0039】

ここで、メモリ監視部450がメモリ400に蓄積されているデータをメモリ400から処理部200に出力させる処理について説明する。

前述の例の場合、メモリ監視部450は、メモリ400bのデータ数が後続演算部(処理部200b)の演算単位データ数に達した際に、メモリ400bからデータを出力させるコマンドを開始制御部700に出力する(図1のS13)。

そして、開始制御部700は、メモリアクセス制御部800にデータ出力のコマンドを転送し(図1のS14)、メモリアクセス制御部800はメモリ400bに蓄積されているデータを出力させる。あるいは、開始制御部700は、データ出力のコマンドを後続演算部(処理部200b)に転送し、後続演算部(処理部200b)がメモリ400bからデータを入力してもよい。

以降、メモリ監視部450がメモリ400に蓄積されているデータをメモリ400から処理部200に出力させる処理は同様であり、説明を省略する。

【0040】

ここで、メモリ監視部450はメモリ400bのデータ数が後続演算部(処理部200b)の演算単位データ数に達しない場合は、待機する(図3のST309の「NO」)。

【0041】

処理部200bは、クロスバースイッチ300経由でメモリ400bからデータを入力し(図1のS2)、演算を開始する。すなわち、処理部200bは、処理部200bの演算に必要なデータ数のデータが揃った時点で演算を開始する。

【0042】

ここで、処理部200bは、先行演算部として前述と同様に演算を開始する(図3のST306)。つまり、今度は、処理部200bが先行演算部となり、処理部200fが後続演算部となる。そして、図3のST306〜ST310の処理が同様に行われ、処理部200bは、演算結果をメモリ400bに蓄積し、処理部200fは、メモリ400bに処理部200fの演算に必要なデータ数のデータが揃った時点で演算を開始する。

ここで、処理部200fよりも後続の処理部200は設定されていないので、処理部200fは、演算結果を出力信号S4(図1)として外部に出力する。

【0043】

すなわち、接続制御部850により選択された先行演算部と後続演算部とのペア毎に、図3のST306〜ST310の処理が行われる。

【0044】

なお、例えば、メモリ400aに蓄積されたデータが処理部200bに出力された後も継続して、処理部200aからデータが生成されメモリ400aに蓄積される場合、メモリ監視部450は、データ数をリセットして再度監視を開始し、前述で説明と同様な処理を行う。

【0045】

そして、各処理部200は並列処理が可能であり、接続制御部850により選択された先行演算部と後続演算部とのペアは、継続して先行演算部にデータが入力されれば、図3のST306〜ST310の処理を各ペア間で並列して行う。

【0046】

つまり、メモリ監視部450は、いずれかのメモリ400のデータ数が、当該メモリ400に対応付けられている後続演算部の演算単位データ数に達した際に、当該メモリ400に蓄積されているデータを当該メモリ400から、当該メモリ400に対応付けられている後続演算部に出力させる。

【0047】

そして、最後に処理が行われる処理部200(図2の例では処理部200f)にデータが入力されなくなった場合にデータ処理装置100はデータ処理を終了する。ここで、最後に処理が行われる処理部200fにデータが入力されなくなった場合とは、例えば、入力信号S1が外部から入力されなくなり、メモリ400bに蓄積されるデータのデータ数が処理部200fのいずれかの処理部200の演算単位データ数に達しなくなる場合などが想定される。

【0048】

(イネーブル信号の説明)

ここで、前述では説明を省略したメモリ400が、先頭演算部が出力したデータのうち、後続演算部が演算に必要なデータのみを蓄積する場合や、メモリ400が、生成されたメモリアドレスの情報に基づき、データを蓄積する場合について説明する。

まず、メモリ400が、先頭演算部が出力したデータのうち、後続演算部が演算に必要なデータのみを蓄積する場合について説明する。

図4は、イネーブル信号の例を示す図である。

メモリアクセス制御部800は、パラメータ設定部500に記憶されているパラメータを入力し(図1のS9)、イネーブル信号を生成する(図3のST307)。

【0049】

イネーブル信号は、信号レベルが所定の値よりも高い「ハイレベル信号(H信号と称する)」と信号レベルが所定の値よりも低い「ローレベル信号(L信号と称する)」とから成る。デジタル信号で表現した場合に、H信号は「1」の信号で、L信号は「0」の信号となる。

そして、図4に示すイネーブル信号は、周期性を持った例であり、H信号である区間(H区間と称する)とL信号である区間(L区間と称する)とが1セットとなり、この1セットの周期が予めパラメータで設定された回数繰り返される。

そして、H区間には、予めパラメータで設定されたクロック信号の回数分のH信号が含まれ、同様にL区間には、予めパラメータで設定されたクロック信号の回数分のL信号が含まれる。

【0050】

前述で説明の通り、各処理部200は、データをクロック信号と同期させて出力する。すなわち、各処理部200は、各々に設けられている生成タイミングごとに繰り返しデータを生成する。

そして、イネーブル信号もクロック信号を同期している。

【0051】

そして、例えば、処理部200aがデータを生成する生成タイミングのうち、処理部200bが演算に必要なデータが生成されるタイミングが予めパラメータとして設定されている。そして、そのパラメータをパラメータ設定部500は外部からパラメータ信号S5として入力し、記憶している。

同様に、パラメータ設定部500は例えば、処理部200bがデータを生成する生成タイミングのうち、処理部200fが演算に必要なデータが生成されるタイミングが予めパラメータとして設定されている。

【0052】

前述の通り、接続制御部850は、先行演算部及び後続演算部として2つの処理部200を選択し、選択される2つの処理部200の組合せは1つ以上である。そして、パラメータ設定部500は、その組合せ毎に、先行演算部の生成タイミングのうち、後続演算部の演算に必要なデータが生成される必要データタイミングを記憶している。

【0053】

そして、メモリアクセス制御部800は、必要データタイミングにおいてH信号となるイネーブル信号を生成する。これによりメモリアクセス制御部800は、H区間のイネーブル信号に同期するクロック信号に対応したデータを抽出する。

すなわち、メモリアクセス制御部800は、接続制御部850により選択された先行演算部により生成されるデータのうち、必要データタイミングで生成されるデータを抽出する(図3のST307)。

【0054】

そして、メモリ400は、メモリアクセス制御部800により抽出されるデータを蓄積する(図3のST308)。

よって、後続演算部は、必要なデータのみを入力して処理を行うことができる。

【0055】

なお、イネーブル信号がH信号である状態とは、メモリへのデータ蓄積が有効な状態である。そして、イネーブル信号がH信号になることを「イネーブルがアサートされる」と称する。

例えば、H区間において、H信号が50回生成されているとすると、イネーブルが50回アサートされていることになる。

【0056】

(メモリアドレスの説明)

次に、メモリ400が、生成されたメモリアドレスの情報に基づき、データを蓄積する場合について説明する。

図5は、メモリアドレスの例を示す図である。

図6は、データ蓄積処理の例を示すフローチャートである。

前述で説明のように、メモリアドレスを1つずつインクリメントしながらデータを蓄積する場合は、メモリアクセス制御部800は、イネーブルが1回アサートされる時に、メモリアドレスを1つインクリメントしてメモリ400にデータを蓄積すればよい。

【0057】

ここでは、イネーブル信号を使ったデータ蓄積処理の例を説明する。

メモリアクセス制御部800は、パラメータ設定部500に記憶されているパラメータを入力する(図1のS9)。ここでは、メモリアクセス制御部800は、パラメータとして、オフセットアドレス、インクリメント値、不連続間隔値、不連続時の加算値が示される。これらのパラメータはパラメータ信号S5(図1)としてパラメータ設定部500により入力され、記憶されている。

【0058】

まず、処理部200が演算結果の出力を開始すると、メモリアクセス制御部800は、開始制御部700から処理の開始指示を入力する(図1のS14、図6のST1)。

【0059】

そして、メモリアクセス制御部800は、メモリアドレスとしてパラメータに示されるオフセットアドレスを設定する(図6のST2)。ここでオフセットアドレスとは、データの格納を開始するメモリアドレスの値である。図5においてはオフセットアドレスを「A」で示している。

【0060】

メモリアクセス制御部800は、イネーブルがアサートされたか否かを判定し、イネーブルがアサートされていない場合は(図6のST3の「NO」)、メモリアドレスの更新は行わず保持する(図6のST5)。

そして、イネーブルがアサートされた場合(図6のST3の「YES」)、メモリアクセス制御部800はイネーブル数をカウントする(図6のST4)。

すなわち、メモリアクセス制御部800はイネーブル信号に基づき、抽出されるデータのデータ数と抽出される順番とを監視する。

【0061】

そして、メモリアクセス制御部800は、イネーブル数がパラメータに示される不連続間隔値を超えるか否かを判定する(図6のST6)。ここで不連続間隔値は、後続演算部の演算単位データ数と等しく設定される。

すなわち、メモリアクセス制御部800は、抽出されるデータのデータ数が演算単位データ数を超えるか否かを判定する。

【0062】

イネーブル数が不連続間隔値を超えない場合(図6のST6の「NO」)、メモリアクセス制御部800は、パラメータに示されるインクリメント値を用いてデータが格納されるメモリアドレスを生成する(図6のST9)。

図5の例では、インクリメント値が「2」、不連続間隔値が「28」として設定されており、メモリアクセス制御部800は、抽出されたデータ数が「28」以内であれば、「A+0」、「A+2」と2つずつインクリメントしたメモリアドレスに各データを格納する。

【0063】

一方、イネーブル数が不連続間隔値を超える場合(図6のST6の「YES」)、メモリアクセス制御部800は、パラメータに示される不連続時の加算値を用いてメモリアドレスを生成する(図6のST7)。

図5の例では不連続時の加算値は「170」として設定されており、メモリアクセス制御部800は、抽出されたデータ数が「28」を超えた場合、「29」個目のデータが蓄積されるメモリアドレスを生成する。ここで、「28」個目のデータは「A+54」のメモリアドレスに蓄積されるので、「29」個目のデータは不連続時の加算値「170」を加えた「A+224」のメモリアドレスに蓄積される。

【0064】

そして、メモリアクセス制御部800は、イネーブル数のカウントを初期化(カウント値を「1」に設定)し(図6のST8)、再度イネーブル数をカウントする(図6のST3〜ST4)。

【0065】

すなわち、メモリアクセス制御部800は、抽出されるデータを、選択部により後続演算部として選択された演算部の演算単位データ数毎に、最初に抽出されるデータから順次グルーピングしている。そして、メモリ400は、メモリアクセス制御部800によりグルーピングされたグループ毎に区別してデータを蓄積する。

【0066】

(実施の形態1の効果)

以上のように、実施の形態1のデータ処理装置100は、各処理部200の動作開始をメモリ400の蓄積量に基づいて行う。そのため、データ処理装置100は、各演算部の制御情報を予め記憶しておく必要はなく、実際の信号処理の状態に合わせて各処理部200の動作タイミングを制御することができる。

【0067】

また、実施の形態1のデータ処理装置100は、メモリ400の蓄積量に基づいて処理部200の動作開始タイミングが与えられる。したがって、演算結果によって演算時間が変化する処理部200が有っても、演算時間が変化する処理部200に後続して演算が行われる処理部200も正しく動作開始タイミングが与えられる。よって、実施の形態1のデータ処理装置100は、演算結果によって演算時間が変化する処理部200が有っても、システム全体が正しく動作するように制御することができる。

【0068】

以上、実施の形態1においては、以下の特徴を備えたデータ処理装置100について説明した。

(1)複数のシステムの信号処理を行うことができるデータ処理装置100は、信号処理を行う複数の処理部200と、データを格納する複数のメモリ400と、処理部200とメモリ400を接続するクロスバースイッチ300と、信号処理に必要なパラメータを保持するパラメータ設定部500と、カウンタを保有するカウンタ部600と、メモリ400の蓄積量を監視するメモリ監視部450と、パラメータ設定部500からのパラメータとカウンタ部600からのカウント値の比較やメモリ監視部450からの情報に基づいて動作開始タイミングを指示する開始制御部700と、メモリ400のメモリアドレスやイネーブル信号を生成するメモリアクセス制御部800と、クロスバースイッチ300の接続先を設定する接続制御部850とを備える。

(2)開始制御部700は、カウンタ部600からのカウンタ値とパラメータ設定部500からの動作開始タイミングパラメータを比較し、一致した場合に処理部200に動作開始指示を与える。

(3)メモリ監視部450は、メモリ400に蓄積されたデータ量を監視し、パラメータ設定部500から与えられる次にメモリ400から読み出しを行う処理部200が必要なデータ量が蓄積された場合に、開始制御部700に開始指示を通知する。

(4)メモリアクセス制御部800は、パラメータに基づいてイネーブル信号を生成する。例えば、メモリアクセス制御部800は、H区間サイクル数パラメータ、L区間サイクル数パラメータ、セット回数パラメータを用いてイネーブル信号を生成する。

(5)メモリアクセス制御部800は、パラメータに基づいてメモリアドレスを生成する。例えば、メモリアクセス制御部800は、オフセットアドレスパラメータ、インクリメント値パラメータ、不連続間隔パラメータ、不連続時の加算値パラメータを用いてアドレスを生成する。

【0069】

実施の形態2.

(実施の形態2におけるデータ処理装置の概要)

実施の形態1におけるデータ処理装置100では、処理部200が外部からの入力信号S1を入力したが、実施の形態2におけるデータ処理装置100では、メモリ400が外部からの入力信号S1を入力する実施形態を説明する。

【0070】

図7は、データ処理装置の構成の例を示す図である。

実施の形態2のデータ処理装置100は、図1に示す実施の形態1のデータ処理装置100と比べ、前述の通り、メモリ400が入力信号S1を入力する点とカウンタ部600が無い点とが異なる。

そして、以上の相違点以外、実施の形態2におけるデータ処理装置100は、実施の形態1におけるデータ処理装置100と同じ構成である。従って、実施の形態1と同じ構成要素と同じ処理内容とについては説明を省略する。

【0071】

(データ処理の動作説明)

図8は、データ処理の例を示すフローチャートである。

ここでは、「メモリ400a→処理部200b→メモリ400b→処理部200f」の順番でデータ処理が行われるものとする。この例においては、処理部200bが先頭演算部である。

【0072】

まず、実行順序において先頭に位置するメモリ400(メモリ400a)は、外部から入力信号S1(図7)を入力し、蓄積する(図8のST801)。ここで、外部からデータを入力し、入力したデータを蓄積するメモリ400を入力蓄積部と称する(図7において「入力蓄積部」の図示は省略する)。

本例においては、入力蓄積部はメモリ400aとなっているが、データ処理装置100が行うデータ処理の内容によっては、入力蓄積部はメモリ400a以外(例えばメモリ400b)であってもよい。

【0073】

メモリ監視部450は、入力蓄積部(メモリ400a)に蓄積されるデータのデータ数を監視する(図7のS12)。

そして、メモリ監視部450は、入力蓄積部(メモリ400a)のデータ数が先頭演算部(処理部200b)の演算単位データ数に達した際に(図8のST802の「YES」)、入力蓄積部に蓄積されているデータを入力蓄積部から先頭演算部(処理部200b)に出力させる(図8のST803)。

なお、メモリ監視部450は、入力蓄積部のデータ数が先頭演算部の演算単位データ数に達しない場合は、待機する(図8のST802の「NO」)。

【0074】

そして、先頭演算部(処理部200b)は、後続演算部(処理部200f)に対する先行演算部として図3のST306に示す処理を行う。以降は、実施の形態1と同様である為、説明を省略する。

【0075】

(実施の形態2の効果)

以上のように、実施の形態2のデータ処理装置100は、実施の形態1の効果に加えて、外部からのデータをメモリ400が入力することにより、すべての処理部200の動作開始タイミングをメモリ蓄積量に基づいて指示することができる。

【0076】

以上、実施の形態2においては、以下の特徴を備えたデータ処理装置100について説明した。

(1)複数のシステムの信号処理を行うことができるデータ処理装置100は、信号処理を行う複数の処理部200と、データを格納する複数のメモリ400と、処理部200とメモリ400を接続するクロスバースイッチ300と、信号処理に必要なパラメータを保持するパラメータ設定部500と、メモリ400の蓄積量を監視するメモリ監視部450と、メモリ監視部450からの情報に基づいて動作開始タイミングを指示する開始制御部700と、メモリ400のメモリアドレスやイネーブル信号を生成するメモリアクセス制御部800と、クロスバースイッチ300の接続先を設定する接続制御部850とを備える。

(2)メモリ監視部450は、メモリ400に蓄積されたデータ量を監視し、パラメータ設定部500から与えられる次にメモリ400から読み出しを行う処理部200が必要なデータ量が蓄積された場合に、開始制御部700に開始指示を通知する。

【0077】

(実施の形態1〜2のデータ処理装置100のハードウェア構成)

最後に、実施の形態1〜2に示したデータ処理装置100のハードウェア構成例について説明する。

図9は、本実施の形態に示したデータ処理装置100のハードウェア資源の一例を示す図である。

なお、図9の構成は、あくまでもデータ処理装置100のハードウェア構成の一例を示すものであり、データ処理装置100のハードウェア構成は図9に記載の構成に限らず、他の構成であってもよい。

【0078】

図9において、データ処理装置100は、プログラムを実行するCPU911(Central Processing Unit、中央処理装置、処理装置、演算装置、マイクロプロセッサ、マイクロコンピュータ、プロセッサともいう)を備えている。

CPU911は、バス912を介して、例えば、ROM(Read Only Memory)913、RAM(Random Access Memory)914、通信ボード915、表示装置901、キーボード902、マウス903、磁気ディスク装置920と接続され、これらのハードウェアデバイスを制御する。

更に、CPU911は、FDD904(Flexible Disk Drive)、コンパクトディスク装置905(CDD)と接続していてもよい。また、磁気ディスク装置920の代わりに、SSD(Solid State Drive)、光ディスク装置、メモリカード(登録商標)読み書き装置などの記憶装置でもよい。

RAM914は、揮発性メモリの一例である。ROM913、FDD904、CDD905、磁気ディスク装置920の記憶媒体は、不揮発性メモリの一例である。これらは、記憶装置の一例である。

本実施の形態で説明したパラメータ設定部500、メモリ400は、磁気ディスク装置920等により実現される。

通信ボード915、キーボード902、マウス903、FDD904などは、入力装置の一例である。

また、通信ボード915、表示装置901などは、出力装置の一例である。

【0079】

磁気ディスク装置920には、オペレーティングシステム921(OS)、ウィンドウシステム922、プログラム群923、ファイル群924が記憶されている。

プログラム群923のプログラムは、CPU911がオペレーティングシステム921、ウィンドウシステム922を利用しながら実行する。

【0080】

また、RAM914には、CPU911に実行させるオペレーティングシステム921のプログラムやアプリケーションプログラムの少なくとも一部が一時的に格納される。

また、RAM914には、CPU911による処理に必要な各種データが格納される。

【0081】

また、ROM913には、BIOS(Basic Input Output System)プログラムが格納され、磁気ディスク装置920にはブートプログラムが格納されている。

データ処理装置100の起動時には、ROM913のBIOSプログラム及び磁気ディスク装置920のブートプログラムが実行され、BIOSプログラム及びブートプログラムによりオペレーティングシステム921が起動される。

【0082】

上記プログラム群923には、本実施の形態の説明において「〜部」(「〜記憶部」以外、以下同様)として説明している機能を実行するプログラムが記憶されている。プログラムは、CPU911により読み出され実行される。

【0083】

ファイル群924には、本実施の形態の説明において、「〜の判断」、「〜の計算」、「〜の比較」、「〜の照合」、「〜の参照」、「〜の検索」、「〜の抽出」、「〜の検査」、「〜の生成」、「〜の設定」、「〜の登録」、「〜の選択」、「〜の入力」、「〜の受信」、「〜の判定」、「〜の定義」、「〜の算出」、「〜の更新」、「〜の登録」等として説明している処理の結果を示す情報やデータや信号値や変数値やパラメータが、「ファイル」や「データベース」の各項目として記憶されている。

「ファイル」や「データベース」は、ディスクやメモリなどの記録媒体に記憶される。

ディスクやメモリなどの記憶媒体に記憶された情報やデータや信号値や変数値やパラメータは、読み書き回路を介してCPU911によりメインメモリやキャッシュメモリに読み出される。

そして、読み出された情報やデータや信号値や変数値やパラメータは、抽出・検索・参照・比較・演算・計算・処理・編集・出力・印刷・表示・制御・判定・識別・検知・判別・選択・算出・導出・更新・生成・取得・通知・指示・判断・区別・削除・登録・付与・監視・待機などのCPUの動作に用いられる。

抽出・検索・参照・比較・演算・計算・処理・編集・出力・印刷・表示・制御・判定・識別・検知・判別・選択・算出・導出・更新・生成・取得・通知・指示・判断・区別・削除・登録・付与・監視・待機などのCPUの動作の間、情報やデータや信号値や変数値やパラメータは、メインメモリ、レジスタ、キャッシュメモリ、バッファメモリ等に一時的に記憶される。

また、本実施の形態で説明しているフローチャートの矢印の部分は主としてデータや信号の入出力を示す。

データや信号値は、RAM914のメモリ、FDD904のフレキシブルディスク、CDD905のコンパクトディスク、磁気ディスク装置920の磁気ディスク、その他光ディスク、ミニディスク、DVD等の記録媒体に記録される。

また、データや信号は、バス912や信号線やケーブルその他の伝送媒体によりオンライン伝送される。

【0084】

また、本実施の形態の説明において「〜部」として説明しているものは、「〜回路」、「〜装置」、「〜機器」であってもよく、また、「〜ステップ」、「〜手順」、「〜処理」であってもよい。

すなわち、本実施の形態で説明したフローチャートに示すステップ、手順、処理により、本発明に係る情報処理方法を実現することができる。

また、「〜部」として説明しているものは、ROM913に記憶されたファームウェアで実現されていても構わない。

或いは、ソフトウェアのみ、或いは、素子・デバイス・基板・配線などのハードウェアのみ、或いは、ソフトウェアとハードウェアとの組み合わせ、さらには、ファームウェアとの組み合わせで実施されても構わない。

ファームウェアとソフトウェアは、プログラムとして、磁気ディスク、フレキシブルディスク、光ディスク、コンパクトディスク、ミニディスク、DVD等の記録媒体に記憶される。

プログラムはCPU911により読み出され、CPU911により実行される。

すなわち、プログラムは、本実施の形態の「〜部」としてコンピュータを機能させるものである。あるいは、本実施の形態の「〜部」の手順や方法をコンピュータに実行させるものである。

【0085】

このように、本実施の形態に示すデータ処理装置100は、処理装置たるCPU、記憶装置たるメモリ、磁気ディスク等、入力装置たるキーボード、マウス、通信ボード等、出力装置たる表示装置、通信ボード等を備えるコンピュータである。

そして、上記したように「〜部」として示された機能をこれら処理装置、記憶装置、入力装置、出力装置を用いて実現するものである。

【符号の説明】

【0086】

100 データ処理装置、200 処理部、300 クロスバースイッチ、400 メモリ、450 メモリ監視部、500 パラメータ設定部、600 カウンタ部、700 開始制御部、800 メモリアクセス制御部、850 接続制御部、901 表示装置、902 キーボード、903 マウス、904 FDD、905 コンパクトディスク装置、911 CPU、912 バス、913 ROM、914 RAM、915 通信ボード、920 磁気ディスク装置、921 オペレーティングシステム、922 ウィンドウシステム、923 プログラム群、924 ファイル群。

【特許請求の範囲】

【請求項1】

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部と、

演算部毎に、演算単位データ数を記憶するデータ数記憶部と、

前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択部と、

前記選択部により選択された先行演算部が生成したデータを蓄積するデータ蓄積部と、

前記データ蓄積部に蓄積されるデータのデータ数を監視し、前記データ蓄積部のデータ数が前記後続演算部の演算単位データ数に達した際に、前記データ蓄積部に蓄積されているデータを前記データ蓄積部から前記後続演算部に出力させるデータ監視部と

を備えることを特徴とするデータ処理装置。

【請求項2】

前記データ処理装置は、

前記複数の演算部として、N(N≧3)個の演算部を備え、

前記データ蓄積部として、(N−1)個のデータ蓄積部を備え、

前記データ処理装置は、更に、

前記N個の演算部で演算が実行される順序が実行順序として示される設定情報を記憶する設定情報記憶部を備え、

前記選択部は、

前記設定情報に示される実行順序に従って、前記N個の演算部から順次、前記先行演算部と前記後続演算部とを選択して、前記N個の演算部において前記先行演算部と前記後続演算部とのペアを(N−1)個生成し、

各データ蓄積部は、

いずれかのペアの先行演算部と後続演算部とに対応付けられ、対応付けられた先行演算部が生成したデータを蓄積し、

前記データ監視部は、

各データ蓄積部に蓄積されるデータのデータ数を監視し、いずれかのデータ蓄積部のデータ数が、当該データ蓄積部に対応付けられている後続演算部の演算単位データ数に達した際に、当該データ蓄積部に蓄積されているデータを当該データ蓄積部から、当該データ蓄積部に対応付けられている後続演算部に出力させることを特徴とする請求項1記載のデータ処理装置。

【請求項3】

前記設定情報記憶部は、

前記N個の演算部の実行順序が相互に異なる複数種の設定情報を記憶し、

前記選択部は、

前記複数種の設定情報の中から選択された設定情報に示される実行順序に従って、前記N個の演算部から順次、前記先行演算部と前記後続演算部とを選択して、前記N個の演算部において前記先行演算部と前記後続演算部とのペアを(N−1)個生成することを特徴とする請求項2記載のデータ処理装置。

【請求項4】

前記データ処理装置は、

M(M≧N)個の演算部を備え、

前記設定情報記憶部は、

前記M個の演算部のうちのいずれかN個の演算部が指定され、指定されているN個の演算部での実行順序が示され、各々において指定されているN個の演算部の組合せが一様でない複数種の設定情報を記憶し、

前記選択部は、

前記複数種の設定情報の中から選択された設定情報で指定されているN個の演算部を前記M個の演算部から選択し、選択された設定情報に示される実行順序に従って、当該N個の演算部から順次、前記先行演算部と前記後続演算部とを選択することを特徴とする請求項3記載のデータ処理装置。

【請求項5】

各演算部は、

各々に設けられている生成タイミングごとに繰り返しデータを生成し、

前記データ処理装置は、更に、

前記選択部により先行演算部及び後続演算部として選択される2つの演算部の組合せが1つ以上示され、

前記組合せ毎に、先行演算部として選択される演算部の生成タイミングのうち、後続演算部として選択される演算部の演算に必要なデータが生成される必要データタイミングを記憶するタイミング記憶部と、

前記選択部により先行演算部が選択された後に、

前記選択部により選択された先行演算部により生成されるデータのうち、前記必要データタイミングで生成されるデータを抽出するデータ抽出部と

を備え、

前記データ蓄積部は、

前記データ抽出部により抽出されるデータを蓄積することを特徴とする請求項1〜4いずれか記載のデータ処理装置。

【請求項6】

前記N個の演算部のうち前記実行順序において先頭に位置する演算部は、

演算実行時に、先頭演算部として外部からデータを入力し、

前記データ処理装置は、更に、

前記先頭演算部により入力されたデータのデータ数が前記先頭演算部の演算単位データ数に達した際に、前記先頭演算部に演算を実行させる実行制御部と

を備えることを特徴とする請求項2〜5いずれか記載のデータ処理装置。

【請求項7】

前記データ処理装置は、更に、

外部からデータを入力し、入力したデータを蓄積する入力蓄積部と、

前記入力蓄積部に蓄積されるデータのデータ数を監視し、前記入力蓄積部のデータ数が前記N個の演算部のうち前記実行順序において先頭に位置する演算部の演算単位データ数に達した際に、前記入力蓄積部に蓄積されているデータを前記入力蓄積部から前記実行順序において先頭に位置する演算部に出力させる入力監視部と

を備えることを特徴とする請求項2〜5いずれか記載のデータ処理装置。

【請求項8】

前記選択部は、

いずれかのペアの後続演算部として選択した演算部を、他のいずれかのペアの先行演算部として選択することを特徴とする請求項2〜7いずれか記載のデータ処理装置。

【請求項9】

前記データ処理装置は、更に、

前記データ抽出部により抽出されるデータのデータ数と抽出される順番とを監視し、

前記データ抽出部により抽出されるデータを、前記選択部により後続演算部として選択された演算部の演算単位データ数毎に、最初に抽出されるデータから順次グルーピングするグルーピング部を備え、

前記データ蓄積部は、

前記グルーピング部によりグルーピングされたグループ毎に区別してデータを蓄積することを特徴とする請求項5記載のデータ処理装置。

【請求項10】

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部を有するコンピュータが、

演算部毎に、演算単位データ数を前記コンピュータが所定のデータ数記憶領域から読み出すデータ数読み出しステップと、

前記コンピュータが、前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択ステップと、

前記コンピュータが、前記選択ステップにより選択された先行演算部が生成したデータを所定の蓄積データ記憶領域に蓄積するデータ蓄積ステップと、

前記コンピュータが、前記蓄積データ記憶領域に蓄積されるデータのデータ数を監視し、前記蓄積データ記憶領域のデータ数が前記後続演算部の演算単位データ数に達した際に、前記蓄積データ記憶領域に蓄積されているデータを前記蓄積データ記憶領域から前記後続演算部に出力させるデータ監視ステップと

を備えることを特徴とするデータ処理方法。

【請求項11】

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部を有するコンピュータに、

演算部毎に、演算単位データ数を所定のデータ数記憶領域から読み出すデータ数読み出しステップと、

前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択ステップと、

前記選択ステップにより選択された先行演算部が生成したデータを所定の蓄積データ記憶領域に蓄積するデータ蓄積ステップと、

前記蓄積データ記憶領域に蓄積されるデータのデータ数を監視し、前記蓄積データ記憶領域のデータ数が前記後続演算部の演算単位データ数に達した際に、前記蓄積データ記憶領域に蓄積されているデータを前記蓄積データ記憶領域から前記後続演算部に出力させるデータ監視ステップと

を実行させることを特徴とするプログラム。

【請求項1】

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部と、

演算部毎に、演算単位データ数を記憶するデータ数記憶部と、

前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択部と、

前記選択部により選択された先行演算部が生成したデータを蓄積するデータ蓄積部と、

前記データ蓄積部に蓄積されるデータのデータ数を監視し、前記データ蓄積部のデータ数が前記後続演算部の演算単位データ数に達した際に、前記データ蓄積部に蓄積されているデータを前記データ蓄積部から前記後続演算部に出力させるデータ監視部と

を備えることを特徴とするデータ処理装置。

【請求項2】

前記データ処理装置は、

前記複数の演算部として、N(N≧3)個の演算部を備え、

前記データ蓄積部として、(N−1)個のデータ蓄積部を備え、

前記データ処理装置は、更に、

前記N個の演算部で演算が実行される順序が実行順序として示される設定情報を記憶する設定情報記憶部を備え、

前記選択部は、

前記設定情報に示される実行順序に従って、前記N個の演算部から順次、前記先行演算部と前記後続演算部とを選択して、前記N個の演算部において前記先行演算部と前記後続演算部とのペアを(N−1)個生成し、

各データ蓄積部は、

いずれかのペアの先行演算部と後続演算部とに対応付けられ、対応付けられた先行演算部が生成したデータを蓄積し、

前記データ監視部は、

各データ蓄積部に蓄積されるデータのデータ数を監視し、いずれかのデータ蓄積部のデータ数が、当該データ蓄積部に対応付けられている後続演算部の演算単位データ数に達した際に、当該データ蓄積部に蓄積されているデータを当該データ蓄積部から、当該データ蓄積部に対応付けられている後続演算部に出力させることを特徴とする請求項1記載のデータ処理装置。

【請求項3】

前記設定情報記憶部は、

前記N個の演算部の実行順序が相互に異なる複数種の設定情報を記憶し、

前記選択部は、

前記複数種の設定情報の中から選択された設定情報に示される実行順序に従って、前記N個の演算部から順次、前記先行演算部と前記後続演算部とを選択して、前記N個の演算部において前記先行演算部と前記後続演算部とのペアを(N−1)個生成することを特徴とする請求項2記載のデータ処理装置。

【請求項4】

前記データ処理装置は、

M(M≧N)個の演算部を備え、

前記設定情報記憶部は、

前記M個の演算部のうちのいずれかN個の演算部が指定され、指定されているN個の演算部での実行順序が示され、各々において指定されているN個の演算部の組合せが一様でない複数種の設定情報を記憶し、

前記選択部は、

前記複数種の設定情報の中から選択された設定情報で指定されているN個の演算部を前記M個の演算部から選択し、選択された設定情報に示される実行順序に従って、当該N個の演算部から順次、前記先行演算部と前記後続演算部とを選択することを特徴とする請求項3記載のデータ処理装置。

【請求項5】

各演算部は、

各々に設けられている生成タイミングごとに繰り返しデータを生成し、

前記データ処理装置は、更に、

前記選択部により先行演算部及び後続演算部として選択される2つの演算部の組合せが1つ以上示され、

前記組合せ毎に、先行演算部として選択される演算部の生成タイミングのうち、後続演算部として選択される演算部の演算に必要なデータが生成される必要データタイミングを記憶するタイミング記憶部と、

前記選択部により先行演算部が選択された後に、

前記選択部により選択された先行演算部により生成されるデータのうち、前記必要データタイミングで生成されるデータを抽出するデータ抽出部と

を備え、

前記データ蓄積部は、

前記データ抽出部により抽出されるデータを蓄積することを特徴とする請求項1〜4いずれか記載のデータ処理装置。

【請求項6】

前記N個の演算部のうち前記実行順序において先頭に位置する演算部は、

演算実行時に、先頭演算部として外部からデータを入力し、

前記データ処理装置は、更に、

前記先頭演算部により入力されたデータのデータ数が前記先頭演算部の演算単位データ数に達した際に、前記先頭演算部に演算を実行させる実行制御部と

を備えることを特徴とする請求項2〜5いずれか記載のデータ処理装置。

【請求項7】

前記データ処理装置は、更に、

外部からデータを入力し、入力したデータを蓄積する入力蓄積部と、

前記入力蓄積部に蓄積されるデータのデータ数を監視し、前記入力蓄積部のデータ数が前記N個の演算部のうち前記実行順序において先頭に位置する演算部の演算単位データ数に達した際に、前記入力蓄積部に蓄積されているデータを前記入力蓄積部から前記実行順序において先頭に位置する演算部に出力させる入力監視部と

を備えることを特徴とする請求項2〜5いずれか記載のデータ処理装置。

【請求項8】

前記選択部は、

いずれかのペアの後続演算部として選択した演算部を、他のいずれかのペアの先行演算部として選択することを特徴とする請求項2〜7いずれか記載のデータ処理装置。

【請求項9】

前記データ処理装置は、更に、

前記データ抽出部により抽出されるデータのデータ数と抽出される順番とを監視し、

前記データ抽出部により抽出されるデータを、前記選択部により後続演算部として選択された演算部の演算単位データ数毎に、最初に抽出されるデータから順次グルーピングするグルーピング部を備え、

前記データ蓄積部は、

前記グルーピング部によりグルーピングされたグループ毎に区別してデータを蓄積することを特徴とする請求項5記載のデータ処理装置。

【請求項10】

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部を有するコンピュータが、

演算部毎に、演算単位データ数を前記コンピュータが所定のデータ数記憶領域から読み出すデータ数読み出しステップと、

前記コンピュータが、前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択ステップと、

前記コンピュータが、前記選択ステップにより選択された先行演算部が生成したデータを所定の蓄積データ記憶領域に蓄積するデータ蓄積ステップと、

前記コンピュータが、前記蓄積データ記憶領域に蓄積されるデータのデータ数を監視し、前記蓄積データ記憶領域のデータ数が前記後続演算部の演算単位データ数に達した際に、前記蓄積データ記憶領域に蓄積されているデータを前記蓄積データ記憶領域から前記後続演算部に出力させるデータ監視ステップと

を備えることを特徴とするデータ処理方法。

【請求項11】

それぞれの演算に必要なデータ数が演算単位データ数として定められており、それぞれが異なる演算を実行してデータを生成する複数の演算部を有するコンピュータに、

演算部毎に、演算単位データ数を所定のデータ数記憶領域から読み出すデータ数読み出しステップと、

前記複数の演算部の中から、いずれかの演算部を、先行して演算を実行する先行演算部として選択し、他のいずれかの演算部を、前記先行演算部により生成されるデータを用いて演算を実行する後続演算部として選択する選択ステップと、

前記選択ステップにより選択された先行演算部が生成したデータを所定の蓄積データ記憶領域に蓄積するデータ蓄積ステップと、

前記蓄積データ記憶領域に蓄積されるデータのデータ数を監視し、前記蓄積データ記憶領域のデータ数が前記後続演算部の演算単位データ数に達した際に、前記蓄積データ記憶領域に蓄積されているデータを前記蓄積データ記憶領域から前記後続演算部に出力させるデータ監視ステップと

を実行させることを特徴とするプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−114391(P2013−114391A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−259065(P2011−259065)

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]