データ処理装置およびデータ処理方法

【課題】特にマシン語のプログラムデータの圧縮符号化および復号処理を行うために用いて好適なデータ処理方法を提供する。

【解決手段】RISCによるマシン語のプログラムデータは、データ長が32ビットの固定フォーマットで決められた所定領域に対して、同じ意味のコードが格納されるため、LZ77符号による符号化を行う際のスライドが4バイト毎に一致する可能性が高くなる。そこで、バイト単位でプログラムデータの4バイト毎に小さい値の変換アドレス値TAddressを割り当てる変換テーブルを用いて、アドレス値Addressを変換する。そして、値が「0」〜「15」までの変換アドレス値TAddressを、符号長が4ビットの符号に符号化し、値が「15」〜「255」の変換アドレス値TAddressを符号長が8ビットの符号に符号化する。

【解決手段】RISCによるマシン語のプログラムデータは、データ長が32ビットの固定フォーマットで決められた所定領域に対して、同じ意味のコードが格納されるため、LZ77符号による符号化を行う際のスライドが4バイト毎に一致する可能性が高くなる。そこで、バイト単位でプログラムデータの4バイト毎に小さい値の変換アドレス値TAddressを割り当てる変換テーブルを用いて、アドレス値Addressを変換する。そして、値が「0」〜「15」までの変換アドレス値TAddressを、符号長が4ビットの符号に符号化し、値が「15」〜「255」の変換アドレス値TAddressを符号長が8ビットの符号に符号化する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データの符号化および復号を行うデータ処理装置およびデータ処理方法に関する。

【背景技術】

【0002】

従来から、ハードディスクドライブ(HDD)といった2次記憶媒体に対して格納するプログラムやデータ(以下、特に記載のない限り、これらを纏めてデータと呼ぶ)を圧縮符号化することが行われていた。データを圧縮符号化してHDDなどに格納することで、記憶領域を節約してより多くのデータが格納可能となる。また、圧縮符号化により格納されるデータのデータサイズが小さくなるため、HDDに対するアクセス速度が向上するという効果もある。

【0003】

特許文献1には、HDDに格納されるデータに対して参照頻度や属性値を付加し、より頻繁にアクセスされるデータは圧縮符号化を行わず、アクセス頻度のより低いデータを圧縮符号化してHDDに格納する技術が開示されている。特許文献1によれば、データの圧縮符号化および復号処理を含めたHDDに対するアクセス速度を向上させることが可能となる。

【0004】

また、近年では、機器を休止状態から高速に起動するために、機器が休止状態に移行する際にメモリの状態をイメージ化したスナップショットを保持しておき、機器が休止状態から復帰する際に、このスナップショットをメモリの元の位置に展開し直すことで、当該メモリの状態をスナップショット取得時の状態に復元する技術が知られている。特許文献2には、パーティション、ファイル、ディレクトリ単位でのスナップショットの取得方法について開示されている。

【0005】

さらに、近年では、主記憶装置の状態を丸ごとイメージ化したスナップショットをハードディスクドライブなどに保持することで、省電力モードなどの休止状態から復帰する際の起動を高速化する、ハイバネーションと呼ばれる技術が実用化されている。

【0006】

ところで、データを効率よく圧縮符号化する方法として、ユニバーサル符号により圧縮符号化する方法が実用化されている。このユニバーサル符号は、情報保存型のデータ圧縮方法であり、データ圧縮時に情報源の統計的な性質を予め仮定しないため、種々のタイプ(文字コード、オブジェクトコードなど)のデータに適用することができる。

【0007】

ユニバーサル符号の代表的な方法として、ジブ−レンペル(Ziv-Lempel)符号がある。Ziv-Lempel符号では、ユニバーサル型と、増分分解型(Incremental parsing) の2つのアルゴリズムが提案されている。これらのうち、ユニバーサル型アルゴリズムを用いた実用的な方法として、LZSS(Lempel-Ziv-Storer-Syzmanski)符号がある。

【0008】

LZSS符号のベースとなるLZ77符号の符号化アルゴリズムは、符号化データを、過去のデータ系列の任意の位置から一致する最大長の系列に区切り、過去の系列の複製として符号化する。

【0009】

より具体的には、符号化済みの入力データを格納する移動窓と、これから符号化するデータを格納する先読みバッファとを備え、先読みバッファのデータ系列と移動窓のデータ系列の全ての部分系列とを照合して、移動窓中で一致する最大長の部分系列を求める。そして、移動窓中でこの最大長の部分系列を指定するために、「その最大長の部分系列の開始位置」と「一致する長さ」と「不一致をもたらした次のシンボル」との組を符号化する。

【0010】

次に、先読みバッファ内の符号化したデータ系列を移動窓に移して、先読みバッファ内に符号化したデータ系列分の新たなデータ系列を入力する。以下、同様の処理を繰り返していくことで、データを部分系列に分解して符号化を実行していく。

【発明の概要】

【発明が解決しようとする課題】

【0011】

ところで、上述したハイバネーションでは、主記憶装置の状態を丸ごとイメージ化したスナップショットを作成する。すなわち、ハイバネーションにより作成されるスナップショットは、スナップショット作成直前に起動していたプログラムのコードデータを含むことになる。

【0012】

近年の多くのCPU(Central Processing Unit)は、RISC(Reduced Instruction Set Computer)方式を採用しているため、マシン語によるプログラムのコードデータは、4バイトや8バイト単位で命令が並び、この4バイトや8バイト毎にデータが一致する可能性が高い。また、この4バイトや8バイト毎の一致可能性のピークを無視して全体を考えた場合、最近出現したバイトで一致可能性が高くなる。一方、ある程度離れたバイトでは、一致可能性の低い同じような確率が続くことになる。

【0013】

そのため、上述したユニバーサル符号を用いて一致位置に対して静的なハフマン符号化を行っても、余り符号化効率が良くないという問題点があった。また、符号化効率の割にはハードウェア構成が複雑となり、設計コストが嵩むと共にバグの可能性が増加するおそれがあるという問題点があった。

【0014】

本発明は、上記に鑑みてなされたものであって、特にマシン語のプログラムデータの圧縮符号化および復号処理を行うために用いて好適なデータ処理装置およびデータ処理方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

上述した課題を解決し、目的を達成するために、本発明は、入力データを順次記憶するスライド記憶手段と、連続的に入力された入力データからなる入力データ列と一致する、スライド記憶手段に記憶されるデータ列を探索する探索手段と、探索手段で探索されたデータ列から1を選択して、選択されたデータ列の長さを求めてレングス値を生成するレングス生成手段と、レングス生成手段でレングス値を生成するために用いたデータ列における開始データの、スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成手段と、アドレス値の出現頻度に従い、アドレス値生成手段で生成されたアドレス値のうち、出現頻度が高いアドレス値から所定数のアドレス値を、予め定められた値以下の変換アドレス値に変換する変換手段と、レングス値と変換アドレス値とを符号化する符号化手段とを有することを特徴とする。

【0016】

また、本発明は、スライド記憶手段が、入力データを順次記憶するスライド記憶ステップと、比較手段が、探索手段が、連続的に入力された入力データからなる入力データ列と一致する、スライド記憶手段に記憶されるデータ列を探索する探索ステップと、レングス生成手段が、探索ステップで探索されたデータ列から1を選択して、選択されたデータ列の長さを求めてレングス値を生成するレングス生成ステップと、アドレス値生成手段が、レングス生成ステップでレングス値を生成するために用いたデータ列における開始データの、スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成ステップと、変換手段が、アドレス値の出現頻度に従い、アドレス値生成ステップで生成されたアドレス値のうち、出現頻度が高いアドレス値から所定数のアドレス値を、予め定められた値以下の変換アドレス値に変換する変換ステップと符号化手段が、レングス値と変換アドレス値とを符号化する符号化ステップとを有することを特徴とする。

【発明の効果】

【0017】

本発明によれば、特にマシン語のプログラムデータの圧縮符号化および復号処理を行うために用いて好適なデータ処理装置およびデータ処理方法が提供可能となる効果がある。

【図面の簡単な説明】

【0018】

【図1】図1は、本発明に係るデータ処理装置を適用可能なプリンタ装置の一例の構成を示すブロック図である。

【図2】図2は、本発明の実施形態に適用可能なプリンタ装置の全体的な処理を示すフローチャートである。

【図3】図3は、エンコーダの一例の構成を示すブロック図である。

【図4】図4は、符号フォーマットの例を示す略線図である。

【図5】図5は、本実施形態に適用可能な符号化処理について説明するための略線図である。

【図6】図6は、スライド探索処理およびリスト探索処理におけるフラグ処理を説明するための略線図である。

【図7】図7は、スライド探索処理およびリスト探索処理におけるフラグ処理を説明するための略線図である。

【図8】図8は、マシン語のプログラムデータの特徴について説明するための略線図である。

【図9】図9は、マシン語のプログラムデータの特徴について説明するための略線図である。

【図10】図10は、変換テーブルETRANSTABLEの例を示す略線図である。

【図11】図11は、本発明の実施形態による符号化処理の全体的な流れを示す一例のフローチャートである。

【図12】図12は、スライド探索処理の例をより詳細に示すフローチャートである。

【図13】図13は、リスト探索処理の例をより詳細に示すフローチャートである。

【図14】図14は、スライド追加処理の例をより詳細に示すフローチャートである。

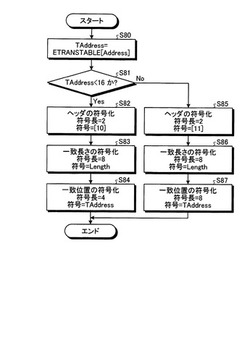

【図15】図15は、スライド符号化処理の例をより詳細に示すフローチャートである。

【図16】図16は、エンコーダの一例の構成をより詳細に示すブロック図である。

【図17】図17は、スライド/リスト生成処理部の一例のハードウェア構成を示すブロック図である。

【図18】図18は、デコーダの一例の構成を示すブロック図である。

【図19】図19は、逆変換テーブルDTRANSTABLEの一例を示す略線図である。

【図20】図20は、符号データを復号する一例の処理を示すフローチャートである。

【図21】図21は、デコーダの一例の構成をより詳細に示すブロック図である。

【図22】図22は、スライド展開部の一例のハードウェア構成を示すブロック図である。

【発明を実施するための形態】

【0019】

以下に添付図面を参照して、この発明に係るデータ処理装置の一実施形態を詳細に説明する。図1は、本発明に係るデータ処理装置を適用可能なプリンタ装置の一例の構成を示す。図1の例では、プリンタ装置は、制御部200、メインメモリ210、プリンタエンジン211および不揮発性のメモリであるフラッシュメモリ240を備える。フラッシュメモリ240は、図1に例示されるようにプリンタ装置に内蔵されていてもよいし、プリンタ装置に対して脱着可能とされていてもよい。

【0020】

制御部200は、CPU(Central Processing Unit)212、CPU I/F201、メモリコントローラ202、符号化部204、復号部205、画像処理部206、ディレイメモリ207、エンジンコントローラ208、パネルコントローラ220、パネル221、スキャナ230、平滑フィルタ231、フラッシュメモリコントローラ241、エンコーダ242およびデコーダ243を含む。

【0021】

CPU212は、メインメモリ210に格納されるプログラムに従い、このプリンタ装置の全体の動作を制御する。CPU212は、CPU I/F201を介してメモリコントローラ202に接続される。メモリコントローラ202は、CPU212、符号化部204、復号部205、画像処理部206、通信I/F209、平滑フィルタ231、フラッシュメモリコントローラ241、エンコーダ242およびデコーダ243の、メインメモリ210に対するアクセスを調停する。

【0022】

メインメモリ210は、メモリコントローラ202に接続される。メモリコントローラ202は、メインメモリ210に対するアクセスの制御を行う。

【0023】

メインメモリ210は、プログラム領域210Aおよびデータ領域210Bを有する。プログラム領域210Aは、CPU212が動作するためのプログラムが格納される。データ領域210Bは、例えばネットワークを介して供給PDLデータが格納されると共に、CMYKバンドデータ、バンドデータが圧縮符号化された符号データ、ならびに、その他のデータが格納される。

【0024】

符号化部204は、メインメモリ210に格納されるバンドデータを符号化する。符号化されたバンドデータは、メモリコントローラ202を介してメインメモリ210に供給される。復号部205は、後述するプリンタエンジン211に同期して、符号化部204で符号化されメインメモリ210に書き込まれた符号化バンドデータをメインメモリ210から読み出して復号する。復号されたバンドデータは、メモリコントローラ202を介して画像処理部206に供給される。画像処理部206は、復号部205から供給されたバンドデータに対して階調処理など所定の画像処理を施す。

【0025】

画像処理が施されたバンドデータは、ディレイメモリ207を介してエンジンコントローラ208に転送される。ディレイメモリ207は、画像処理部206から出力されるバンドデータの転送速度と、エンジンコントローラ208からプリンタエンジン211に転送されるバンドデータの転送速度との違いを吸収する。

【0026】

エンジンコントローラ208は、プリンタエンジン211を制御する。図1では、プリンタエンジン211としてCMYK各色の版のうち1の版のものだけが記載され、その他の版については煩雑さを避けるために省略されている。

【0027】

通信I/F209は、ネットワークを介しての通信を制御する。例えば、ネットワークに接続されるコンピュータから出力されたPDL(Page Description Language)データは、通信I/F209により受信される。通信I/F209は、受信したPDLデータを、メモリコントローラ202を介してメインメモリ210に転送する。

【0028】

なお、ネットワークは、LAN(Local Area Network)などの所定の範囲内で通信を行うものでもよいし、インターネットなどより広範囲に通信可能なものでもよい。また、ネットワークは、有線通信に限らず無線通信を用いたものでもよいし、USB(Universal Serial Bus)やIEEE(Institute Electrical and Electronics Engineers)1394といったシリアル通信を行うものでもよい。

【0029】

フラッシュメモリ240は、CPU212上で動作するためのプログラムや、当該プログラムに用いられる各種データが、本実施形態による圧縮符号化方法により圧縮符号化されて格納される。例えば、メインメモリ210のプログラム領域210Aに対して、マシン語によるコードとして展開されるプログラムデータが、展開イメージのまま圧縮符号化され、スナップショットとしてフラッシュメモリ240に記憶される。フラッシュメモリコントローラ241は、フラッシュメモリ240に対するアクセスの制御を行う。

【0030】

エンコーダ242は、本実施形態による、LZ77符号を用いた圧縮符号化方法により、プログラムデータの圧縮符号化を行う。また、デコーダ243は、当該圧縮符号化方法により圧縮符号化された圧縮データの復号を行う。

【0031】

プリンタ装置の全体的な動作について、概略的に説明する。例えばコンピュータで生成されたPDLデータがネットワークを介して通信I/F209に受信され、メインメモリ210のデータ領域210Bに記憶される。CPU212は、メインメモリ210のデータ領域210BからPDLデータを読み出し、PDLを解析して、解析結果に基づきCMYKのバンド画像を描画する。描画されたCMYKのバンド画像によるCMYKバンドデータは、メインメモリ210のデータ領域210Bに格納される。

【0032】

符号化部204は、データ領域210BからCMYKバンドデータを読み出して、例えば予測符号化などを用いて符号化する。CMYKバンドデータが符号化された符号データは、メインメモリ210のデータ領域210Bに格納される。

【0033】

復号部205は、メインメモリ210のデータ領域210BからCMYKバンドデータが符号化された符号データを読み出して復号し、復号されたCMYKバンドデータをメモリコントローラ202を介して画像処理部206に供給する。画像処理部206は、復号部205から供給されたCMYKバンドデータに対して所定の画像処理を施す。画像処理されたCMYKバンドデータは、ディレイメモリ207およびプリンタエンジンコントローラ208を介してプリンタエンジン211に供給される。プリンタエンジン211は、供給されたCMYKバンドデータに基づきプリントアウトを行う。

【0034】

図2は、本実施形態に適用可能なプリンタ装置の全体的な処理を示すフローチャートである。概略的には、例えばユーザがプリンタ装置の電源をONとすると、電源立ち上げ処理が行われ(ステップS1)、プリンタ装置がRUN状態(稼働状態)になる(ステップS2)。ユーザの電源OFF操作などにより、電源立ち下げ処理が行われ(ステップS3)、プリンタ装置がスリープ状態となる(ステップS4)。

【0035】

ステップS1の電源立ち上げ処理では、フラッシュメモリ240に圧縮符号化されてスナップショットとして格納されたプログラムデータがフラッシュメモリ240から読み出され(ステップS1−1)、デコーダ243で本実施形態による復号方法に従い復号され、マシン語によるプログラムデータとされる(ステップS1−2)。このマシン語のプログラムデータは、メモリコントローラ202を介してメインメモリ210に供給され、プログラム領域210Aに格納される(ステップS1−3)。

【0036】

一方、ステップS3の電源立ち下げ処理では、メインメモリ210のプログラム領域210Aに格納されるマシン語によるプログラムデータがメインメモリ210から読み出され(ステップS3−1)、エンコーダ242で本実施形態による符号化方法に従い圧縮符号化される(ステップS3−2)。圧縮符号化されたマシン語プログラムデータは、フラッシュメモリ240に対してスナップショットとして格納される(ステップS3−3)。

【0037】

このように、電源立ち下げ処理時に、メインメモリ210のプログラム領域210Aに格納されるマシン語のプログラムデータを、メモリ上のイメージのまま圧縮符号化し、スナップショットとしてフラッシュメモリ240に格納することで、電源立ち上げ処理を高速化することができる。

【0038】

<エンコーダ>

図3は、エンコーダ242の一例の構成を示す。エンコーダ242において、データ読み込み部300により、メインメモリ210のプログラム領域210Aから、マシン語によるプログラムデータがメモリコントローラ202を介して読み出される。データ読み込み部300に読み込まれたデータは、スライド/リスト生成処理部301に供給される。

【0039】

スライド/リスト生成処理部301は、入力されたデータを順次記憶するFIFO方式のスライド記憶部を有する。スライド/リスト生成処理部301は、供給されたデータとスライド記憶部に記憶された過去の入力データとを順次比較する。そして、供給されたデータと過去の入力データとが一致した場合には、当該過去の入力データのスライド記憶部内の位置を示すアドレス値Addressを保持すると共に、一致した長さを示す値であるレングスLengthをカウントアップする。両者が一致しない場合には、データ値そのものをPASS符号として符号化する。

【0040】

ここで、本実施形態においては、詳細を後述する規則に従いアドレス値Addressを変換し、変換アドレス値TAddressとする。そして、これらPASS符号と、変換アドレス値TAddressおよびレングスLengthと、符号の種類を示すヘッダとを出力する。

【0041】

スライド/リスト生成処理部301のから出力された各値は、符号フォーマット生成処理部302に供給される。符号フォーマット生成処理部302は、供給されたPASS符号、変換アドレス値TAddress、レングスLengthおよびヘッダとを、図4に例示されるようなフォーマットで符号化する。

【0042】

図4において、PASS符号は、データ長が1ビットで値が「0」のヘッダに対して、後に8ビットのデータ長を持つデータ値が接続されてなる。スライド符号は、データ長が2ビットのヘッダに対して、レングスLengthおよびアドレス値Addressが順次接続される。レングスLengthは、符号長が8ビットとされる。

【0043】

ここで、本実施形態においては、変換アドレス値TAddressは、自身の値に応じて2種類の符号長のうち何れか一方を選択されて符号化される。図4の例では、変換アドレス値TAddressは、符号長が8ビットの符号と、符号長が4ビットの符号とのうち何れかに符号化される。符号長が8ビットの符号に符号化された変換アドレス値TAddressを含むスライド符号を、第1スライド符号と呼び、ヘッダが「10」とされる。また、符号長が4ビットの符号に符号化された変換アドレス値TAddressを含むスライド符号を、第2スライド符号と呼び、ヘッダが「11」とされる。

【0044】

なお、この図4に例示される符号フォーマットは、一例であって、これに限られるものではない。例えば、変換アドレス値TAddressの符号長は、第1および第2のスライド符号それぞれで8ビットまたは4ビットに限られない。

【0045】

符号フォーマット生成処理部302で生成されたPASS符号、ならびに、第1および第2スライド符号は、符号書き込み部303に供給される。符号書き込み部303は、供給されたPASS符号、ならびに、第1および第2およびスライド符号を、メモリコントローラ202およびフラッシュメモリコントローラ241を介してフラッシュメモリ240に書き込む。

【0046】

<符号化処理の概略>

次に、本実施形態に適用可能な、スライド/リスト生成処理部301における符号化処理について説明する。本実施形態では、LZ77符号を用い、スライド探索処理とリスト探索処理とを繰り返すことによって、データの符号化を行う。スライド探索処理は、1単位(例えば1バイト)の入力データと一致する、所定単位分の長さを持つスライド記憶部に記憶される過去の入力データを探索する。スライド記憶部内の過去の入力データに、入力データと一致するデータが探索されなかった場合には、入力データそのものをPASS符号として用いる。

【0047】

スライド探索処理において、入力データに一致するスライド記憶部内の過去の入力データが探索された場合、その一致した過去の入力データをルートとして、リスト探索処理が行われる。リスト探索処理は、ルートとされた入力データに対して連続的に入力された入力データ列と一致する、スライド記憶部内の過去の入力データ列(リストと呼ぶ)を探索する。

【0048】

リスト探索処理時に、入力データと一致するリストが無くなると、直前のリストから1を選び、選択されたリストのルートとなる過去の入力データのスライド記憶部内での位置をアドレス値Addressとし、当該リストの長さをレングスLengthとして出力する。

【0049】

すなわち、スライド/リスト生成処理部301では、スライド探索処理でリスト探索処理のルートとなる過去の入力データを形成する。そして、リスト探索処理で、ルートに基づくリストの成長および淘汰を行い、最終的に残ったリストに基づき符号化を行う。

【0050】

図5を用いてより具体的に説明する。図5の例では、スライド記憶部は、番号#0〜#15で示されるように、直列に接続された16個のレジスタを持ち、FIFO(First In First Out)として構成される。各レジスタは、それぞれ1単位(例えば1バイト)のデータを格納可能であるものとする。なお、以下では、このスライド記憶部が有するレジスタをスライドと呼ぶ。

【0051】

処理#1において、スライド記憶部の各スライドには、入力の新しい順、すなわち図5の右側から左側に向けて、「a,b,c,a,a,b,c,a,b,c,d,b,c,a,c,a」と、16個の過去に入力されたデータが既に格納されているものとする。最初に、スライド/リスト生成処理部301に対して入力データ「a」が入力される。スライド探索処理により、この入力データ「a」と、各スライドに記憶された過去の入力データのそれぞれとを比較し、一致しているデータを探索する。図5の例では、番号#0、#3、#4、#7、#13および#15のスライドに格納されているデータが入力データと一致していることが分かる。したがって、これらの番号のスライドに格納されているデータが、リスト探索処理におけるルートとなる。

【0052】

スライド探索処理によって、各スライドに記憶された過去の入力データから、入力データ「a」と一致しているデータが探索されたので、処理#2のリスト探索処理が行われる。

【0053】

処理#2では、各スライドに記憶される過去の入力データを左に1だけシフトさせて、処理#1で入力された入力データ「a」をスライド記憶部の番号#0のスライドに追加する。それと共に、次の入力データ「c」がスライド/リスト生成処理部301に対して入力される。リスト探索処理では、各スライドに記憶される過去の入力データのうち、直前の処理#1において入力データが一致した各スライド内の過去の入力データが格納されていたスライドから、新たな入力データ「c」と一致するデータを探索する。

【0054】

図5の例では、処理#1において入力データと一致した番号#0および#4のスライドに格納される過去の入力データは、処理#2において入力データと一致していない。一方、処理#1において入力データと一致した番号#3、#7、#13および#15のスライドに格納された過去の入力データは、データ「c」であって、新たな入力データ「c」と一致する。

【0055】

処理#2のリスト探索処理によって、直前の処理#1において入力データが一致した各スライド内の過去の入力データが格納されたスライドから、処理#2における入力データ「c」と一致するデータが探索されたので、次の処理はリスト探索処理となる。なお、処理#2は、リスト探索処理の開始点であるので、リストの長さを示すレングスLengthは、値「0」とされる。

【0056】

処理#3では、上述の処理#2と同様にして、各スライドに記憶される過去の入力データを左に1だけシフトさせて、処理#2で入力された入力データ「c」をスライド記憶部の番号#0のスライドに追加する。それと共に、次の入力データ「b」がスライド/リスト生成処理部301に対して入力される。そして、各スライドに記憶される過去の入力データのうち、直前の処理#2において入力データが一致した各スライド内の過去の入力データが格納されたスライドから、新たな入力データ「b」と一致するデータを探索する。

【0057】

図5の例では、処理#2において探索された番号#15のスライドに格納される過去の入力データは、処理#3において入力データと一致していない。一方、処理#2において探索された番号#3、#7および#13のスライドに格納される、処理#3における過去の入力データはデータ「b」であって、新たな入力データ「b」と一致する。次の処理#4では、この番号#3、#7および#13のスライドに格納される過去の入力データが、リスト探索の対象となる。すなわち、この処理#3の段階では、番号#3、#7および#13に係るリストが残っている。処理#3では、リストの長さが「1」となり、レングスLengthが値「1」とされる。

【0058】

このような処理を繰り返していき、リストが最も長くなるデータ列を求める。図5の例では、処理#5において、直前の処理#4においてリスト探索された番号#13のスライドに格納される過去の入力データ「c」と、新たな入力データ「g」とが一致しなくなり、リストが途切れる。そこで、処理#5では、1つ前の処理#4において残っているリストから1を選択し、そのスライドのスライド記憶部における位置(番号)をアドレス値Addressとし、リストの長さをレングスLengthとしてスライド符号に符号化する。図5の例では、アドレス値Addressが「13」、レングスLengthが「3」とされる。

【0059】

さらに、処理#5では、入力データ「g」についてスライド探索処理を行う。この例では、各スライドに過去の入力データとしてデータ「g」が記憶されていないため、一致するデータがないとされる。この場合、処理は処理#6に移行され、入力データ「g」がそのまま用いられてPASS符号に符号化される。

【0060】

PASS符号への符号化が行われると、処理#7で、各スライドに記憶される過去の入力データが左に1だけシフトされると共に、直前のリスト探索処理(処理#5)で入力された入力データ「g」がスライド記憶部の番号#0のスライドに追加される。そして、次の入力データ「b」に対してスライド探索処理が行われる。

【0061】

ここで、スライド記憶部は、FIFO方式により各スライドに格納されたデータのシフトを行うことができるため、入力データとの一致を記憶したリストをそのままの状態で保持しながら、次の入力データの処理に移行することができる。

【0062】

例えば、図5の例では、入力データが、処理#1において番号#0、#3、#4、#7、#13および#15のスライドに格納される過去の入力データと一致している。各スライドに格納されたデータを、新たなデータの入力に伴い順次シフトさせることで、例えば処理#2の当該番号#0、#3、#4、#7、#13および#15のスライドに対して次のデータが格納されることになる。したがって、スライド記憶部において、スライド探索処理で一致が探索された番号のスライドに格納されるデータを、リスト探索処理毎に入力データと比較していくことで、入力データのデータ列と一致する、過去の入力データのデータ列を探索することができる。

【0063】

このように、スライド記憶部をFIFO方式とすることで、リスト探索処理を簡易に行うことができる。

【0064】

なお、上述の処理によれば、リスト探索処理において入力データと一致するリストが無く、処理がリスト探索処理からスライド探索処理に移行する際に、1処理分、符号化が進行しない時間が生じることになる。すなわち、1処理を1クロックで行うとした場合、リスト探索処理からスライド探索処理に移行する際に、1クロック分の無駄が生じてしまうことになる。

【0065】

<フラグ処理>

上述したスライド探索処理およびリスト探索処理は、フラグによって制御される。このスライド探索処理およびリスト探索処理におけるフラグ処理について、図6および図7を用いて説明する。

【0066】

図6は、スライド探索処理の結果を示すRフラグRFLGmを示す。図6に例示されるように、スライド記憶部の各スライドに対して、図の右側から左側へ向けて「a,b,c,a,a,b,c,a,b,c,d,b,c,a,c,a」のように過去の入力データが格納された状態で、入力データ「a」が入力された場合、番号#0、#3、#4、#7、#13および#15のスライドで、入力データと各スライドに記憶される過去の入力データとが一致する。そこで、これらの番号のスライドに対応するRフラグRFLG0、RFLG3、RFLG4、RFLG7、RFLG13およびRFLG15を、それぞれ一致したことを示す値「1」とする。

【0067】

このように、入力データと、各スライドに記憶される過去の入力データとが一致する場合は、符号化処理を行わずにリスト探索処理が行われる。このとき、RフラグRFLGmの各スライドに対する位置は、固定的である。入力データと一致する、各スライドに記憶される過去の入力データが無い場合は、入力データをそのまま用いてPASS符号に符号化し、次の入力データに対してスライド探索処理を行う。

【0068】

図7は、リスト探索処理の結果を示すWフラグWFLGmの例を示す。リスト探索処理では、新たに入力された入力データと一致するデータが、各スライドのうちRフラグRFLGmが「1」とされたスライドに格納されるデータから探索される。若し、一致するデータが探索されたら、当該スライドに対するWフラグWFLGmの値を、一致したことを示す値「1」とする。

【0069】

図7の例では、各スライドに記憶される過去の入力データのうち、RフラグRFLGmが値「1」である番号#0、#3、#4、#7、#13および#15のスライドに格納されるデータに対してリスト探索処理が行われる。これらのうち、入力データ「c」に対して、番号#3、#7、#13および#15のスライドに格納されるデータが一致するので、対応するWフラグWFLG3、WFLG7、WFLG13およびWFLG15の値を、一致したことを示す値「1」とする。各スライドに記憶される過去の入力データのうち、このWフラグWFLGmの値が「1」とされたスライドに格納されるデータは、直前に入力データと一致したスライドに格納される過去の入力データと、現在入力データと一致した過去の入力データとが連なっていることを示す。

【0070】

次に、値が「1」のWフラグWFLGmを探索する。この値「1」のWフラグWFLGmが存在する場合は、各WフラグWFLGmを新たなRフラグRFLGmとし、上述と同様にして次の入力データに対してリスト探索処理を行う。

【0071】

一方、探索の結果、値が「1」のWフラグWFLGmが存在しないとされた場合は、リストが途絶えたことを意味する。この場合は、値が「1」のRフラグRFLGmを1つ選択し、選択したRフラグRFLGmに対応するスライドのアドレス値Addressと、そのときのレングスLengthとをスライド符号に符号化する。

【0072】

ここで、図8および図9を用いて、マシン語のプログラムデータの特徴について、概略的に説明する。図8は、RISC(Reduced Instruction Set Computer)技術によるCPUに対するマシン語プログラムにおける命令フォーマットの例を示す。図8(a)は、R(レジスタ)タイプ命令の例、図8(b)は、I(イミディエイト)タイプ命令の例、図8(c)は、J(ジャンプ)タイプ命令の例をそれぞれ示す。各命令は、32ビットを所定に分割した領域に所定のニーモニックが格納される。各ニーモニックの意味を、図8(d)に示す。

【0073】

各ニーモニックのうち、オペレーションコードを示すニーモニック「Op」は、Rタイプ、IタイプおよびJタイプそれぞれの命令において、固定的に先頭の6ビットの領域に格納される。このように、RISCにおいては、データ長が32ビットの固定フォーマットで決められた所定領域に対して、同じ意味のコードが格納されるため、スライドが4バイト(32ビット)毎または8バイト毎に一致する可能性が高くなる。

【0074】

図9は、マシン語のプログラムデータにおけるスライドの一致位置に関する統計結果の例を示す。図9において、横軸がスライドの一致位置(アドレス値Address)を示し、縦軸が一致回数(出現頻度)を示す。図9に示される統計結果によれば、4バイト毎に一致回数の大きなピークが現れることが示されている。また、4バイト毎のピークを除外して全体的な変化を見ると、一致位置がより近いほどスライドの一致する確率が高くなることが分かる。一方、スライドの一致位置がある程度離れると、低い一致確率に収束することが分かる。

【0075】

本実施形態では、上述したような、マシン語のプログラムデータにおいて、4バイト毎にスライドの一致確率のピークが現れることを利用して、スライド符号の符号化を行う。

【0076】

具体的には、スライド符号のアドレス値Addressを、対応するスライドの一致回数が多い順に並べ替えて、並べ替え後の順序を示す値からなる変換アドレス値TAddressを生成する。そして、4ビットで表現可能な所定数の変換アドレス値TAddress、すなわち値が「0」〜「15」までの変換アドレス値TAddressを、符号長が4ビットの符号に符号化する。この符号長が4ビットの符号に符号化された変換アドレス値TAddressにより、第2スライド符号が形成される。一方、値が「15」〜「255」の変換アドレス値TAddressは、符号長が8ビットの符号に符号化する。この符号長が8ビットの符号に符号化された変換アドレス値TAddressにより、第1スライド符号が形成される。

【0077】

アドレス値Addressを変換アドレス値TAddressに変換するためには、例えば図10に例示されるような変換テーブルETRANSTABLEを用いることができる。この変換テーブルETRANSTABLEに列挙される数値は、変換後の変換アドレス値TAddressを示す。また、変換テーブルETRANSTABLEに列挙される数値の順番を示す値(「0」から始まるものとする)が変換前のアドレス値Addressを示す。すなわち、変換テーブルETRANSTABLEに対してアドレス値Addressを入力すると、入力されたアドレス値Addressに対応する位置の値が変換アドレス値TAddressとして出力される。

【0078】

変換テーブルETRANSTABLEは、図10から分かるように、4個のアドレス値Address毎に小さい値の変換アドレス値TAddressを割り当てている。換言すれば、図9の統計結果に従い、バイト単位でプログラムデータの4バイト毎に小さい値の変換アドレス値TAddressを割り当てる。また、図9の統計結果によれば、スライドの一致位置がある程度離れると一致回数が少ない値に収束するので、変換テーブルETRANSTABLEの後方に行くに従い、最後尾の値(すなわちアドレス値Address「255」)を除き、この変換アドレス値TAddressの規則性を弱めている。

【0079】

さらに、変換テーブルETRANSTABLEの先頭部分において、アドレス値Address「0」に対して変換アドレス値TAddress「15」を割り当てている。これは、図9を用いて説明したように、統計結果の全体的な特性として、スライドの一致位置が近いほど一致回数も大きい傾向にあることから来ている。

【0080】

具体的には、変換テーブルETRANSTABLEにおいて、変換前のアドレス値Address「3」は、変換アドレス値TAddress「0」に変換される。また、変換前のアドレス値Address「0」は、変換アドレス値TAddress「15」に変換される。同様に、変換前のアドレス値Address「11」は、変換アドレス値TAddress「2」に変換される。

【0081】

なお、上述したように、値が「0」〜「15」までの変換アドレス値TAddressは、全て符号長が4ビットの符号に変換される。そのため、実際には、変換テーブルETRANSTABLEにおいて変換アドレス値TAddress「0」〜「15」に対応付けるアドレス値Addressの順番は、変更することができる。同様に、変換アドレス値TAddress「16」〜「255」に対応付けるアドレス値Addressの順番も変更できる。

【0082】

ここでは、変換テーブルETRANSTABLEが、変換アドレス値TAddressが列挙され、変換アドレス値TAddressの順番が元のアドレス値Addressを示すように説明したが、これはこの例に限定されない。例えば、変換前のアドレス値Addressと、変換後の変換アドレス値TAddressとを1対1に対応付けたテーブルとしてもよい。

【0083】

また、ここでは、小さい値の変換アドレス値TAddressを4バイト毎に割り当てているが、これはこの例に限定されない。すなわち、小さい値の変換アドレス値TAddressの割り当て単位は、プログラムデータの命令フォーマットに応じて設定することができる。例えば、命令フォーマットが64ビットのデータ長で構成されていれば、小さい値の変換アドレス値TAddressを8バイト毎に割り当てることが考えられる。

【0084】

<符号化処理の詳細>

次に、スライド/リスト生成処理部301における符号化処理について、より詳細に説明する。図11は、本実施形態による符号化処理の全体的な流れを示す一例のフローチャートである。なお、図11のフローチャートの処理に先立って、符号読み込み部300は、ある長さのデータを処理対象のデータとして予め保持しているものとする。

【0085】

最初のステップS10で、スライド/リスト生成処理部301は、スライド探索処理およびリスト探索処理のうち何れが有効かを示すフラグListFLGを、スライド探索処理を行っていることを示す値「0」に初期化する。次に、ステップS11で、スライド/リスト生成処理部301は、符号読み込み部300から1単位分のデータを入力データとして読み込む。読み込んだ入力データは、スライド記憶部に格納される。

【0086】

入力データがスライド記憶部に格納されると、ステップS12で、1単位分のデータに対するスライド探索処理が行われると共に、ステップS13で、1単位分のデータに対するリスト探索処理が行われる。詳細は後述するが、本実施形態においては、スライド探索処理を行うスライド探索部と、リスト探索処理を行うリスト探索部とが別個の構成とされているので、ステップS12およびステップS13の処理を並列的に行うことが可能である。

【0087】

処理はステップS14に移行され、スライド/リスト生成処理部301は、フラグListFLGの値が「0」か否かを判定する。若し、「0」であると判定されたら、現在スライド探索処理が有効であるとされ、処理はステップS15に移行される。ステップS15では、フラグSFINDFLGの値が「1」であるか否かが判定される。若し、値が「1」であれば、スライド記憶部101において入力データと一致する過去の入力データが探索されたとされ、ステップS16でフラグListFLGの値がリスト探索処理が有効であることを示す「1」とされる。

【0088】

そして、処理がステップS25に移行され、スライド記憶部に対して入力データが追加される。次のステップS26で、処理対象のデータ全てに対する処理が終了したか否かが判定される。若し、終了していないと判定されたら、処理はステップS11に戻され、次の1単位分のデータが入力データとして読み込まれる。一方、終了していると判定されたら、一連の符号化処理が終了される。

【0089】

一方、ステップS15で、フラグSFINDFLGの値が「0」であると判定されたら、スライド記憶部101において入力データと一致する過去の入力データが探索されなかったとされ、処理はステップS17に移行される。ステップS17では、フラグListFLGの値が「0」とされてスライド探索処理が有効であるとされ、次のステップS18で入力データがPASS符号に符号化される。また、一致フラグFLAGが値「0」とされる。そして、処理はステップS25に移行される。

【0090】

また、上述のステップS14において、フラグListFLGの値が「0」ではない、すなわち「1」であると判定されたら、現在リスト探索処理が有効であるとされ、処理がステップS19に移行される。ステップS19では、フラグLFINDFLGの値が「1」か否かを判定する。若し、「1」であると判定されたら、処理はステップS25に移行される。

【0091】

一方、ステップS19で、フラグLFINDFLGの値が「1」ではない、すなわち、フラグLFINDFLGの値が「0」であると判定されたら、処理はステップS20に移行される。ステップS20では、アドレス値Addressが変換テーブルETRANSTABLEに従い変換アドレス値TAddressに変換され、この変換アドレス値TAddressと、レングスLengthおよびヘッダとが、図4に例示される第1または第2スライド符号に符号化される。そして、処理はステップS21に移行され、フラグSFINDFLGの値が「1」であるか否かが判定される。若し、「1」であると判定されたら、リスト探索処理においてリストが継続されたとされて処理がステップS22に移行され、フラグListFLGの値が「1」とされる。そして、処理がステップS25に移行される。

【0092】

一方、ステップS20でフラグSFINDFLGの値が「0」であると判定されたら、リスト探索処理においてリストが途切れたとされ、処理がステップS23に移行され、フラグListFLGの値が「0」とされる。次のステップS24で入力データがそのままPASS符号に符号化され、レジスタ141に格納される。そして、処理はステップS25に移行される。

【0093】

図12は、図11のステップS12における一例のスライド探索処理をより詳細に示すフローチャートである。なお、この図12、ならびに、以下の図13および図14では、スライド記憶部におけるスライドを、スライドの番号を含めるように、スライド[x]のように表す。また、FIFO構成とされるスライド記憶部において先頭のスライドを、スライド[0]とする。

【0094】

先ず、ステップS30〜ステップS32で、レングスLength、フラグSFINDFLGおよび変数IWがそれぞれ値「0」に初期化される。処理はステップS33に移行され、入力データとスライド[IW]に格納された過去の入力データとが一致するか否かが判定される。若し、一致すると判定されたら、処理はステップS34に移行され、フラグSFINDFLGの値が「1」とされ、次のステップS35で、RフラグRFLG[IW]の値が「1」とされる。

【0095】

そして、処理はステップS37に移行され、変数IWがスライドサイズ未満、すなわち、スライド記憶部が有するスライド数未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS38で変数IWに「1」が加えられ、処理がステップS33に戻される。一方、ステップS37で、変数IWがスライドサイズ以上であると判定されたら、一連の処理が終了される。

【0096】

一方、ステップS33で入力データとスライド[IW]に格納された過去の入力データとが一致しないと判定されたら、処理はステップS36に移行され、RフラグRFLG[IW]の値が「0」とされる。そして、処理がステップS37に移行される。

【0097】

図13は、図11のステップS13による一例のリスト探索処理をより詳細に示すフローチャートである。先ず、ステップS40およびステップS41で、フラグLFINDFLGおよび変数IWがそれぞれ値「0」に初期化される。

【0098】

ステップS42で、入力データとスライド[IW]に格納された過去の入力データとが一致し、且つ、RフラグRFLG[IW]の値が「1」であるか否かが判定される。若し、それぞれの条件を満たすと判定されたら、処理はステップS43に移行され、WフラグWFLG[IW]の値が「1」とされ、次のステップS44で、フラグLFINDFLGの値が「1」とされる。そして、処理がステップS46に移行される。

【0099】

一方、ステップS42で、上述の条件を満たさない、すなわち、入力データとスライド[IW]に格納された過去の入力データとが一致しない、または、RフラグRFLG[IW]の値が「1」でないと判定されたら、処理はステップS45に移行され、WフラグWFLG[IW]の値が「0」とされる。そして、処理がステップS46に移行される。

【0100】

ステップS46では、変数IWがスライドサイズ未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS47で変数IWに「1」が加えられ、処理がステップS42に戻される。一方、変数IWがスライドサイズ以上であると判定されたら、処理がステップS48に移行される。

【0101】

ステップS48では、フラグLFINDFLGの値が「0」であるか否かが判定される。若し、値が「0」であると判定されたら、処理がステップS49に移行されて変数IWが値「0」に初期化され、次のステップS50でRフラグRFLG[IW]の値が「1」であるか否かが判定される。若し、「1」であると判定されたら、処理はステップS51に移行される。

【0102】

ステップS51では、変数IWがアドレス値Addressとされ、次のステップS52で、スライドサイズを変数IWに代入する。そして、処理がステップS53に移行される。ステップS53では、変数IWがスライドサイズ未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS54で変数IWに「1」が加算されて処理がステップS50に戻される。

【0103】

一方、ステップS53で、変数IWがスライドサイズ以上であると判定されたら、一連の処理が終了される。例えば、上述したステップS52を経由してこのステップS53に到達した場合、ステップS52で変数IWにスライドサイズが代入されているため、必ず処理が終了される。

【0104】

上述したステップS48で、フラグLFINDFLGの値が「0」ではないと判定されたら、処理はステップS55に移行され、変数IWが値「0」に初期化される。次のステップS56で、RフラグRFLG[IW]に対してWフラグWFLG[IW]が設定される。そして、ステップS57で、変数IWがスライドサイズ未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS58で変数IWに「1」が加算されて処理がステップS56に戻される。一方、ステップS57で変数IWがスライドサイズ以上であると判定されたら、処理は次のステップS59に移行され、レングスLengthに対して1が加算され、一連の処理が終了される。

【0105】

図14は、図11のステップS25による一例のスライド追加処理をより詳細に示す一例のフローチャートである。先ず、ステップS70で、変数IWがスライド数から1を減じた値に設定される。次のステップS71で、スライド[IW]に、スライド[IW−1]の値が格納され、ステップS72で、変数IWが「0」を超えるか否かが判定される。若し、変数IWが「0」を超えると判定されたら、処理はステップS73に移行され、変数IWから「1」が減じられる。そして、処理がステップS71に戻される。一方、ステップS72で、変数IWが「0」以下であると判定されたら、処理はステップS74に移行され、スライド[0]に対して入力データが格納される。

【0106】

図15は、図11のステップS20による一例のスライド符号化処理をより詳細に示す。符号フォーマットは、図4に示したフォーマットに従うものとする。先ず、ステップS80で、アドレス値Addressが変換テーブルETRANSTABLEにより変換アドレス値TAddressに変換される。次に、ステップS81で、変換アドレス値TAddressの値が「16」未満であるか否かが判定される。なお、変換アドレス値TAddressは、値「0」から開始されるものとする。

【0107】

若し、変換アドレス値TAddressが値「16」未満であると判定されたら、処理はステップS82に移行され、ヘッダの符号化が行われる。この例では、ヘッダは、符号長が2ビット、値「10」の符号に符号化される。ヘッダの符号化が行われると、次のステップS83で、一致長さすなわちレングスLengthの符号化が行われる。この例では、レングスLengthは、符号長が8ビットの符号に符号化される。そして、次のステップS84で、一致位置すなわち変換アドレス値TAddressの符号化がなされる。変換アドレス値TAddressが値「16」未満であるので、符号長が4ビットの符号に符号化される。

【0108】

一方、変換アドレス値TAddressが値「16」以上であると判定されたら、処理はステップS85に移行され、ヘッダの符号化が行われる。この例では、ヘッダは、符号長が2ビット、値「11」の符号に符号化される。ヘッダの符号化が行われると、次のステップS86で、一致長さすなわちレングスLengthの符号化が行われる。この例では、レングスLengthは、符号長が8ビットの符号に符号化される。そして、次のステップS87で、一致位置すなわち変換アドレス値TAddressの符号化がなされる。変換アドレス値TAddressが値「16」以上であるので、符号長が8ビットの符号に符号化される。

【0109】

図16は、エンコーダ242の一例の構成をより詳細に示す。なお、図16において、上述の図3と共通する部分には同一の符号を付し、詳細な説明を省略する。エンコーダ242は、データ読み込み部300、スライド/リスト生成処理部301、符号フォーマット生成処理部302および符号書き込み部303を有すると共に、メモリコントローラI/F310、データアドレス生成部311および符号アドレス生成部312を有する。

【0110】

データアドレス生成部311は、メインメモリ210のプログラム領域210Aからプログラムデータを読み出す際のメモリアドレスを生成する。データ読み込み部300は、データアドレス生成部311で生成されたメモリアドレスからのデータの読み出しを、メモリコントローラI/F310を介してメモリコントローラ202に対して要求する。この要求に応じてメモリコントローラ202によりメインメモリ210のプログラム領域210Aから読み出されたプログラムデータがメモリコントローラ202からエンコーダ242に対して供給され、メモリコントローラI/F310を介してデータ読み込み部300に供給される。データ読み込み部300は、供給されたプログラムデータを、スライド/リスト生成処理部301に供給する。

【0111】

スライド/リスト生成処理部301は、供給されたプログラムデータから、既に説明したようにしてアドレス値Address、レングスLength、PASS符号およびヘッダを生成する。ここで、アドレス値Addressは、変換テーブルETRANSTABLEにより変換アドレス値TAddressに変換される。これら変換アドレス値TAddress、レングスLength、PASS符号(データ値)およびヘッダは、符号フォーマット生成処理部302に供給される。符号フォーマット生成処理部302は、図4で説明した符号フォーマットに従い、供給された各値からPASS符号、第1スライド符号および第2スライド符号を生成する。生成されたPASS符号、第1スライド符号および第2スライド符号は、符号書き込み部303に供給される。

【0112】

符号書き込み部303は、供給されたPASS符号、第1スライド符号および第2スライド符号をメモリコントローラI/F310を介してメモリコントローラ202に供給する。それと共に、符号書き込み部303は、これらの符号を符号アドレス生成部312で生成されたメモリアドレスに従いフラッシュメモリ240に書き込むように、メモリコントローラI/F310を介してメモリコントローラ202に要求する。メモリコントローラ202は、この要求に従い、供給された符号を、フラッシュメモリコントローラ241を介してフラッシュメモリ240に書き込む。

【0113】

<スライド/リスト生成処理部のハードウェア構成例>

図17は、上述したスライド探索処理、リスト探索処理および符号化処理を実行するスライド/リスト生成処理部301の、一例のハードウェア構成を示す。スライド/リスト生成処理部301は、スライド探索部100、スライド記憶部101、リスト探索部102およびコントローラ103を有する。

【0114】

コントローラ103は、例えばマイクロプロセッサからなり、図11のフローチャートを用いて説明した、ステップS12およびステップS13の処理を除いた、ステップS11〜ステップS26による処理を行い、スライド/リスト生成処理部301の動作を制御する。例えば、コントローラ103は、上述した現在スライド探索処理およびリスト探索処理のうち何れが有効かを示すフラグListFLGによる動作制御を行う。

【0115】

スライド/リスト生成処理部301に対して、例えば1クロック毎に1単位の入力データが入力され、スライド探索部100、スライド記憶部101およびリスト探索部102にそれぞれ供給される。入力データは、さらに、出力側のレジスタ141にも格納される。レジスタ141に格納される入力データは、PASS符号の符号化の際のデータ値として用いられる。以下では、データの1単位を1バイトとする。

【0116】

スライド記憶部101は、各々がレジスタからなり、それぞれ1単位のデータが格納されるn個(例えば256個)のスライド1201、1202、…、120nが直列に接続されて構成される。また、各スライド1201、1202、…、120nの出力は、次のレジスタに供給されると共に、後述するスライド探索部100の対応する比較器111mの一方の入力端と、リスト探索部102の対応する比較器130mの一方の入力端にそれぞれ供給される。

【0117】

なお、比較器130mは、比較器1301〜130nのうち任意の比較器を表す。このような表記は、比較器1111〜111n、セレクタ1311〜131n、レジスタ1321〜132nにおいて共通とする。

【0118】

なお、アドレス値AddressおよびレングスLengthのデータ長は、スライド記憶部101が有するスライド数nに応じて決められる。すなわち、スライド数n=256であれば、アドレス値AddressおよびレングスLengthが「256」までの値を表現可能に、それぞれのデータ長が8ビットに決められる。

【0119】

スライド記憶部101は、これらn個のスライド1201、1202、…、120nによりFIFOが構成され、入力されたデータがスライド1201からスライド1202、スライド1203、…と1クロック毎に順次送られていく。

【0120】

スライド探索部100は、n個の比較器1111、1112、…、111nと、n入力の論理和回路110とを有する。比較器1111、1112、…、111nのそれぞれは、一方および他方の入力端に入力されたデータを比較し、両者が一致していれば値「1」を出力し、一致していなければ値「0」を出力する。

【0121】

比較器1111、1112、…、111nの一方の入力端には、上述したように、スライド記憶部101が有するスライド1201、1202、…、120nの出力がそれぞれ入力される。また、比較器1111、1112、…、111nそれぞれの他方の入力端には、入力データが入力される。

【0122】

比較器1111、1112、…、111nそれぞれの出力は、n入力の論理和回路110に入力されると共に、後述するリスト探索部102のセレクタ(SEL)1311、1312、…、131nの一方の入力端にそれぞれ入力される。論理和回路110の出力は、フラグSFINDFLGとしてコントローラ103に供給される。このフラグSFINDFLGは、スライド1201、1202、…、120nのデータのうち少なくとも1が入力データと一致しているか否かを示す。

【0123】

リスト探索部102は、それぞれn個の比較器1301、1302、…、130n、セレクタ1311、1312、…、131n、ならびに、レジスタ1321、1322、…、132nと、アドレス値生成部133と、n入力の論理和回路134とを有する。比較器1301、1302、…、130nのそれぞれは、一方および他方の入力端に入力されたデータを比較し、両者が一致していれば値「1」を出力し、一致していなければ値「0」を出力する。

【0124】

比較器1301、1302、…、130nの一方の入力端には、上述したように、スライド記憶部101が有するスライド1201、1202、…、120nの出力がそれぞれ入力される。また、比較器1301、1302、…、130nそれぞれの他方の入力端には、入力データが入力される。

【0125】

比較器1301、1302、…、130nの出力は、WフラグWFLGmであって、n入力の論理和回路134にそれぞれ入力されると共に、セレクタ1311、1312、…、131nの他方の入力端にそれぞれ入力される。論理和回路134の出力は、フラグLFINDFLGとしてコントローラ103に供給される。フラグLFINDFLGは、WフラグWFLG1、WFLG2、…、WFLGnのうち少なくとも1の値が「1」であることを示す。

【0126】

セレクタ1311、1312、…、131nの出力は、RフラグRFLGmとされて、それぞれレジスタ1321、1322、…、132nに格納される。セレクタ1311、1312、…、131nは、コントローラ103から図示しない経路を経て供給されるフラグListFLGにより、一方および他方の端子のうち何れを選択するかが制御される。

【0127】

若し、フラグListFLGの値が「0」であって、現在スライド探索処理が有効であることが示されていれば、セレクタ1311、1312、…、131nは、それぞれの一方の入力端に入力された、スライド探索部100における比較器1111、1112、…、111nの出力をレジスタ1321、1322、…、132nに供給するように制御される。例えば、セレクタ131m(なお、1≦m≦nとする)は、対応するレジスタ132mに格納される値が「0」のときに入力端が選択されるように制御される。

【0128】

一方、フラグListFLGの値が「1」であって、現在リスト探索処理が有効であることが示されていれば、セレクタ1311、1312、…、131nは、それぞれの他方の入力端に入力された、リスト探索部102における比較器1301、1302、…、130nを選択してレジスタ1321、1322、…、132nに供給するように制御される。例えば、セレクタ131mは、対応するレジスタ132mに格納される値が「1」のときに他方の入力端が選択されるように制御される。

【0129】

レジスタ1321、1322、…、132nは、セレクタ1311、1312、…、131nからの出力が供給されると、格納されているRフラグRFLG1、RFLG2、…、RFLGnを出力する。すなわち、レジスタ1321、1322、…、132nに格納されるRフラグRFLG1、RFLG2、…、RFLGnは、供給されたセレクタ1311、1312、…、131nからの出力により更新される。

【0130】

レジスタ1321、1322、…、132nから出力されたRフラグRFLG1、RFLG2、…、RFLGnは、比較器1301、1302、…、130nの動作を制御する制御信号として、比較器1301、1302、…、130nの制御端にそれぞれ供給される。例えば、例えば比較器130mは、対応するレジスタ132mから供給された制御信号が値「1」を示していれば比較動作を行い、値「0」を示していれば比較動作を行わない。これは、比較器1301、1302、…、130nそれぞれの動作は、比較器1301、1302、…、130n自身の出力により絞り込まれていくことを意味する。

【0131】

レジスタ1321、1322、…、132nから出力されたRフラグRFLG1、RFLG2、…、RFLGnは、さらにアドレス値生成部133にも供給される。アドレス値生成部133は、図4の処理#5で説明したように、リスト探索処理が終了した際に、レジスタ1321、1322、…、132nから供給されるRフラグRFLG1、RFLG2、…、RFLGnのうち、値が「1」であるRフラグRFLGmを選択し、選択されたRフラグRFLGmの番号をアドレス値Addressとして出力する。アドレス値生成部133から出力されたアドレス値Addressは、アドレス変換部144に供給される。

【0132】

アドレス変換部144は、図10を用いて説明した変換テーブルETRANSTABLEを持ち、供給されたアドレス値Addressを、変換テーブルETRANSTABLEに従い変換アドレス値TAddressに変換する。アドレス値Addressが変換された変換アドレス値TAddressは、レジスタ140に格納されると共に、コントローラ103に供給される。

【0133】

コントローラ103は、スライド探索部100から供給されたフラグSFINDFLGと、リスト探索部102から供給されたフラグLFINDFLGと、アドレス変換部144から供給された変換アドレス値TAddress値とに基づき、レングスLengthおよびヘッダを生成する。レングスLengthおよび一致フラグFLAGは、それぞれレジスタ143および142に格納される。

【0134】

なお、レジスタ140〜143にそれぞれ格納された変換アドレス値TAddress、データ値、ヘッダおよびレングスLengthは、それぞれ符号フォーマット生成処理部302に読み出され、図4に例示する符号フォーマットに従い符号化され符号データが生成される。

【0135】

このような構成において、スライド探索処理は、以下のように行われる。すなわち、比較器1111、1112、…、111nによる、入力データと、スライド1201、1202、…、120nに格納された過去の入力データとの比較処理が行われる。比較結果がそれぞれ論理和回路110に供給され、フラグSFINDFLGが出力される。比較結果は、セレクタ1311、1312、…、131nにも供給され、スライド探索処理の間は、レジスタ1321、1322、…、132nに格納される。図17の構成によれば、この一連の処理を1クロックで実行可能である。

【0136】

また、リスト探索処理は、以下のように行われる。すなわち、比較器1301、1302、…、130nによる、入力データと、スライド1201、1202、…、120nに格納された過去の入力データとの比較処理が行われる。このとき、レジスタ1321、1322、…、132nに格納されるRフラグRFLG1、RFLG2、…、RFLGnの値に基づき、比較器1301、1302、…、130nの比較動作が制御される。例えば、RフラグRFLG1、RFLG2、…、RFLGnの値が全て「0」であれば、比較器1301、1302、…、130n全ての比較動作が行われないことになる。この状態を、リスト探索処理が行われていない状態とする。

【0137】

比較器1301、1302、…、130nによる比較結果がそれぞれ論理和回路134に供給され、フラグLFINDFLGが出力される。また、各比較結果は、セレクタ1311、1312、…、131nに供給され、リスト探索処理の間は、レジスタ1321、1322、…、132nに格納される。また、レジスタ1321、1322、…、132nに格納されるRフラグRFLG1、RFLG2、…、RFLGnは、アドレス値生成部133にも保持される。

【0138】

アドレス値生成部133は、レジスタ1321、1322、…、132nに格納される値が全て「0」であれば、保持しているRフラグRFLG1、RFLG2、…、RFLGnのうち値が「1」のRフラグRFLGmの位置を、アドレス値Addressとし、さらにアドレス変換部144で変換アドレス値TAddressとしてコントローラ103に渡す。図17の構成によれば、このリスト探索処理による一連の処理を1クロックで実行可能である。

【0139】

図17の構成によれば、スライド探索部100と、リスト探索部102とがそれぞれ別個の構成とされると共に、スライド探索部100とリスト探索部102とでスライド記憶部100を共有する。そのため、スライド探索部100によるスライド探索処理と、リスト探索部102によるリスト探索処理とを並列的に実行することが可能である。したがって、リスト探索処理からスライド探索処理へと移行する際の1クロック分の無駄が生じず、符号化処理をより高速化できる。また、図17の構成によれば、先読みバッファや大規模なマトリクスアレイなどの構成が不要なので、ハードウェア規模を小さくできる。

【0140】

なお、エンコーダ242の構成は、図17に示した構成に限定されない。すなわち、LZ77符号の符号化を行い、レングスLengthおよびアドレス値Addressを出力するものであれば、他の構成のエンコーダを適用することができる。

【0141】

<デコーダ>

図18は、デコーダ243の一例の構成を示す。デコーダ243において、符号読み込み部400により、上述したエンコーダ242で符号化された符号データがフラッシュメモリ240から読み込まれる。符号読み込み部400に読み込まれた符号データは、符号フォーマット解析部401に供給される。符号フォーマット解析部401は、図4を用いて説明した符号フォーマットに従い、供給された符号データを解釈してデータ値、変換アドレス値TAddress、レングスLengthおよびヘッダを取り出す。取り出されたこれらのデータは、スライド展開部402に供給される。

【0142】

スライド展開部402は、図5を用いて説明したように、直列に接続された複数のレジスタがFIFOとして構成される、スライド記憶部を持つ。各レジスタは、スライドと呼ばれ、それぞれ1単位(例えば1バイト)のデータを格納可能とされる。スライド展開部402は、供給された変換アドレス値TAddressを元のアドレス値Addressに逆変換し、このアドレス値Addressと、供給されたデータ値、レングスLengthおよびヘッダに基づき、スライド記憶部における各スライドに対してデータを展開し、符号データを復号する。復号されたデータは、データ書き込み部403に供給され、メインメモリ210のプログラム領域210Aに書き込まれる。

【0143】

図19は、変換アドレス値TAddressを元のアドレス値Addressに変換するための逆変換テーブルDTRANSTABLEの一例を示す。この逆変換テーブルDTRANSTABLEに列挙される数値は、元のアドレス値Addressを示す。また、逆変換テーブルDTRANSTABLEに列挙される数値の順番を示す値が、変換アドレス値TAddressを示す。

【0144】

すなわち、逆変換テーブルDTRANSTABLEにおいて、変換アドレス値TAddress「0」は、元のアドレス値Address「3」に変換される。また、変換アドレス値TAddress「15」は、元のアドレス値Address「0」に変換される。同様に、変換アドレス値TAddress「2」は、元のアドレス値Address「11」に変換される。

【0145】

<復号処理の詳細>

図20は、上述した本実施形態の符号化方法により符号化された符号データを、デコーダ243で復号する一例の処理を示すフローチャートである。なお、符号読み込み部400により、フラッシュメモリ240から予め符号データが読み込まれているものとする。先ず、ステップS100で、符号フォーマット解析部401は、符号読み込み部400に読み込まれている圧縮データのヘッダを読み込み、ヘッダの値が「0」であるか否かを判定する(ステップS101)。

【0146】

若し、ヘッダの値が「0」であれば、当該ヘッダを含む符号がPASS符号であると判定され、処理がステップS102に移行される。ステップS102で、符号フォーマット解析部401は、次のステップS102でヘッダに続く8ビットをデータ値として読み込む。読み込まれたデータ値は、そのまま出力データとして出力される(ステップS103)と共に、スライド展開部402に供給されスライドに追加される(ステップS104)。データ値のスライドに対する追加処理は、図14のフローチャートで説明したのと同様の手順により行われる。そして、処理がステップS115に移行される。

【0147】

ステップS115では、例えば符号読み込み部400により、読み込まれている符号データに対する処理が全て終了したか否かが判定される。全て終了したと判定されたら、一連の復号処理が終了される。一方、符号読み込み部400に読み込まれている全ての符号データに対する処理が終了していないと判定されたら、処理はステップS100に戻され、次の符号に対する処理が行われる。

【0148】

符号フォーマット解析部401は、ステップS101でヘッダの値が「0」ではないと判定したら、処理をステップS105に移行させ、ヘッダに続く8ビットをレングスLengthとして読み込む。読み込んだレングスLengthは、スライド展開部402に供給される。

【0149】

次のステップS106で、符号フォーマット解析部401は、ヘッダの値が「11」であるか否かを判定する。若し、ヘッダの値が「11」であると判定したら、処理をステップS107に移行させ、ヘッダに続く4ビットを変換アドレス値TAddressとして読み込む。一方、ヘッダの値が「11」ではないと判定したら、処理をステップS108に移行させ、ヘッダに続く8ビットを変換アドレス値TAddressとして読み込む。ステップS107またはステップS108で読み込まれた変換アドレス値TAddressは、スライド展開部402に供給される。

【0150】

次のステップS109で、スライド展開部402は、図19に例示した逆変換テーブルDTRANSTABLEを用いて、変換アドレス値TAddressを元のアドレス値Addressに変換する。

【0151】

次のステップS110で、スライド展開部402は、スライド記憶部のアドレス値Addressで示されるスライドに格納されるデータを読み込む。読み込まれたデータは、出力データとして出力される(ステップS111)と共に、スライド展開部402に供給されスライドに追加される(ステップS112)。

【0152】

処理はステップS113に移行され、レングスLengthが「0」より大きいか否かが判定される。若し、レングスLengthが「0」以下であると判定されたら、処理はステップS115に移行される。一方、レングスLengthが「0」より大きいと判定されたら、ステップS114でレングスLengthから「1」が減じられた値が新たなレングスLengthとされて、処理がステップS110に戻される。

【0153】

図21は、デコーダ243の一例の構成をより詳細に示す。なお、図21において、上述の図18と共通する部分には同一の符号を付し、詳細な説明を省略する。デコーダ243は、符号読み込み部400、符号フォーマット解析部401、スライド展開部402およびデータ書き込み部403を有すると共に、メモリコントローラI/F410、符号アドレス生成部411およびデータアドレス生成部412を有する。

【0154】

符号アドレス生成部411は、フラッシュメモリ240から圧縮符号化されたプログラムデータを読み出す際のメモリアドレスを生成する。符号読み込み部400は、符号アドレス生成部411で生成されたメモリアドレスからのデータの読み出しを、メモリコントローラI/F410を介してメモリコントローラ202に対して要求する。この要求に応じてメモリコントローラ202によりフラッシュメモリ240から読み出された、プログラムデータが圧縮符号化された符号データが、メモリコントローラ202からデコーダ243に対して供給され、メモリコントローラI/F410を介して符号読み込み部400に供給される。符号読み込み部400は、この符号データを、符号フォーマット解析部401に供給する。

【0155】

符号フォーマット解析部401は、図4で説明した符号フォーマットに従い、供給された符号データから、ヘッダ、レングスLength、データ値および変換アドレス値TAddressを取り出して、スライド展開部402に供給する。ここで、変換アドレス値TAddressは、逆変換テーブルDTRANSTABLEを用いて元のアドレス値Addressに変換される。スライド展開部402は、このアドレス値Addressと、供給されたデータ値、レングスLengthおよびヘッダに基づき、スライド記憶部における各スライドに対してデータを展開し、符号データを元のプログラムデータに復号する。復号されたプログラムデータは、データ書き込み部403に供給される。

【0156】

データ書き込み部403は、供給されたプログラムデータをメモリコントローラI/F410を介してメモリコントローラ202に供給する。それと共に、データ書き込み部403は、当該プログラムデータをデータアドレス生成部412で生成されたメモリアドレスに従いメインメモリ210のプログラム領域210Aに書き込むように、メモリコントローラI/F310を介してメモリコントローラ202に要求する。メモリコントローラ202は、この要求に従い、供給されたプログラムデータを、メインメモリ210のプログラム領域210Aに書き込む。

【0157】

<スライド展開部のハードウェア構成>

図22は、スライド展開部402の一例のハードウェア構成を示す。スライド展開部402は、スライド記憶部500、コントローラ501、セレクタ502および503、ならびに、アドレス逆変換部520を有する。アドレス逆変換部520は、上述した逆変換テーブルDTRANSTABLEを有し、符号フォーマット解析部401から供給された変換アドレス値TAddressを逆変換テーブルDTRANSTABLEを用いて元のアドレス値Addressに変換して、コントローラ501に渡す。

【0158】

コントローラ501は、例えばマイクロプロセッサからなり、アドレス値Address、レングスLengthおよび一致フラグFLAGが供給され、供給されたこれらのデータに基づきこのスライド展開部402の全体の動作を制御する。例えばコントローラ501は、スライド記憶部500におけるデータ値のスライドに対する追加処理や、セレクタ502および503の動作などを制御する。

【0159】

スライド記憶部500は、各々がレジスタからなり、それぞれ1単位のデータが格納されるn個のスライド5111、5112、…、511nが直列に接続されて構成されたFIFOと、当該FIFOの先頭に接続されるセレクタ510とを有する。

【0160】

各スライド5101、5102、…、510nの出力は、さらに、それぞれセレクタ502に供給される。セレクタ502の出力は、セレクタ503に供給されると共に、セレクタ510にも供給される。

【0161】

符号フォーマット解析部401から読み込まれたデータ値がセレクタ510に供給されると共に、セレクタ503にも供給される。セレクタ510は、図13のステップS104のスライド追加処理時には、入力されたデータ値をスライド5111に追加する。また、図13のステップS108のスライド追加処理時には、ステップS106においてスライド符号のアドレス値Addressに基づき選択されたスライドから出力されたデータを、スライド5111に追加する。

【0162】

セレクタ502は、図13のステップS106の処理時に、コントローラ501から供給されるアドレス値Addressに従い、スライド記憶部500の各スライド5111、5112、…、511nの出力からスライド511Addressの出力を選択し、選択した出力を、セレクタ503および510にそれぞれ供給する。

【0163】

セレクタ503は、図13のステップS103において、ステップS102で読み込まれたデータ値を出力する。また、図13のステップS107のデータ出力処理時に、セレクタ502から供給されたデータを出力する。

【0164】

なお、デコーダ243の構成は、図22に示した構成に限定されない。すなわち、レングスLengthおよびアドレス値Addressに基づきLZ77符号の復号を行うものであれば、他の構成のデコーダを適用することができる。

【0165】

また、上述では、本発明がプリンタ装置に適用されるように説明したが、これは一例でありこの例に限定されない。すなわち、本発明は、マシン語のプログラムデータの可逆符号化をハードウェアを用いて行う他の装置にも適用することが可能である。

【符号の説明】

【0166】

100 スライド探索部

101 スライド記憶部

102 リスト探索部

103 コントローラ

110,134 論理和回路

1111〜111n,1301〜130n 比較器

1201〜120n スライド

1311〜131n セレクタ

1321〜132n レジスタ

133 アドレス値生成部

144 アドレス変換部

200 プリンタ装置

210 メインメモリ

210A プログラム領域

240 フラッシュメモリ

242 エンコーダ

243 デコーダ

301 スライド/リスト生成処理部

402 スライド展開部

500 スライド記憶部

501 コントローラ

502,503,510 セレクタ

5111〜511n スライド

520 アドレス逆変換部

【先行技術文献】

【特許文献】

【0167】

【特許文献1】特開平7−319743号公報

【特許文献2】特開2004−178289号公報

【技術分野】

【0001】

本発明は、データの符号化および復号を行うデータ処理装置およびデータ処理方法に関する。

【背景技術】

【0002】

従来から、ハードディスクドライブ(HDD)といった2次記憶媒体に対して格納するプログラムやデータ(以下、特に記載のない限り、これらを纏めてデータと呼ぶ)を圧縮符号化することが行われていた。データを圧縮符号化してHDDなどに格納することで、記憶領域を節約してより多くのデータが格納可能となる。また、圧縮符号化により格納されるデータのデータサイズが小さくなるため、HDDに対するアクセス速度が向上するという効果もある。

【0003】

特許文献1には、HDDに格納されるデータに対して参照頻度や属性値を付加し、より頻繁にアクセスされるデータは圧縮符号化を行わず、アクセス頻度のより低いデータを圧縮符号化してHDDに格納する技術が開示されている。特許文献1によれば、データの圧縮符号化および復号処理を含めたHDDに対するアクセス速度を向上させることが可能となる。

【0004】

また、近年では、機器を休止状態から高速に起動するために、機器が休止状態に移行する際にメモリの状態をイメージ化したスナップショットを保持しておき、機器が休止状態から復帰する際に、このスナップショットをメモリの元の位置に展開し直すことで、当該メモリの状態をスナップショット取得時の状態に復元する技術が知られている。特許文献2には、パーティション、ファイル、ディレクトリ単位でのスナップショットの取得方法について開示されている。

【0005】

さらに、近年では、主記憶装置の状態を丸ごとイメージ化したスナップショットをハードディスクドライブなどに保持することで、省電力モードなどの休止状態から復帰する際の起動を高速化する、ハイバネーションと呼ばれる技術が実用化されている。

【0006】

ところで、データを効率よく圧縮符号化する方法として、ユニバーサル符号により圧縮符号化する方法が実用化されている。このユニバーサル符号は、情報保存型のデータ圧縮方法であり、データ圧縮時に情報源の統計的な性質を予め仮定しないため、種々のタイプ(文字コード、オブジェクトコードなど)のデータに適用することができる。

【0007】

ユニバーサル符号の代表的な方法として、ジブ−レンペル(Ziv-Lempel)符号がある。Ziv-Lempel符号では、ユニバーサル型と、増分分解型(Incremental parsing) の2つのアルゴリズムが提案されている。これらのうち、ユニバーサル型アルゴリズムを用いた実用的な方法として、LZSS(Lempel-Ziv-Storer-Syzmanski)符号がある。

【0008】

LZSS符号のベースとなるLZ77符号の符号化アルゴリズムは、符号化データを、過去のデータ系列の任意の位置から一致する最大長の系列に区切り、過去の系列の複製として符号化する。

【0009】

より具体的には、符号化済みの入力データを格納する移動窓と、これから符号化するデータを格納する先読みバッファとを備え、先読みバッファのデータ系列と移動窓のデータ系列の全ての部分系列とを照合して、移動窓中で一致する最大長の部分系列を求める。そして、移動窓中でこの最大長の部分系列を指定するために、「その最大長の部分系列の開始位置」と「一致する長さ」と「不一致をもたらした次のシンボル」との組を符号化する。

【0010】

次に、先読みバッファ内の符号化したデータ系列を移動窓に移して、先読みバッファ内に符号化したデータ系列分の新たなデータ系列を入力する。以下、同様の処理を繰り返していくことで、データを部分系列に分解して符号化を実行していく。

【発明の概要】

【発明が解決しようとする課題】

【0011】

ところで、上述したハイバネーションでは、主記憶装置の状態を丸ごとイメージ化したスナップショットを作成する。すなわち、ハイバネーションにより作成されるスナップショットは、スナップショット作成直前に起動していたプログラムのコードデータを含むことになる。

【0012】

近年の多くのCPU(Central Processing Unit)は、RISC(Reduced Instruction Set Computer)方式を採用しているため、マシン語によるプログラムのコードデータは、4バイトや8バイト単位で命令が並び、この4バイトや8バイト毎にデータが一致する可能性が高い。また、この4バイトや8バイト毎の一致可能性のピークを無視して全体を考えた場合、最近出現したバイトで一致可能性が高くなる。一方、ある程度離れたバイトでは、一致可能性の低い同じような確率が続くことになる。

【0013】

そのため、上述したユニバーサル符号を用いて一致位置に対して静的なハフマン符号化を行っても、余り符号化効率が良くないという問題点があった。また、符号化効率の割にはハードウェア構成が複雑となり、設計コストが嵩むと共にバグの可能性が増加するおそれがあるという問題点があった。

【0014】

本発明は、上記に鑑みてなされたものであって、特にマシン語のプログラムデータの圧縮符号化および復号処理を行うために用いて好適なデータ処理装置およびデータ処理方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

上述した課題を解決し、目的を達成するために、本発明は、入力データを順次記憶するスライド記憶手段と、連続的に入力された入力データからなる入力データ列と一致する、スライド記憶手段に記憶されるデータ列を探索する探索手段と、探索手段で探索されたデータ列から1を選択して、選択されたデータ列の長さを求めてレングス値を生成するレングス生成手段と、レングス生成手段でレングス値を生成するために用いたデータ列における開始データの、スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成手段と、アドレス値の出現頻度に従い、アドレス値生成手段で生成されたアドレス値のうち、出現頻度が高いアドレス値から所定数のアドレス値を、予め定められた値以下の変換アドレス値に変換する変換手段と、レングス値と変換アドレス値とを符号化する符号化手段とを有することを特徴とする。

【0016】

また、本発明は、スライド記憶手段が、入力データを順次記憶するスライド記憶ステップと、比較手段が、探索手段が、連続的に入力された入力データからなる入力データ列と一致する、スライド記憶手段に記憶されるデータ列を探索する探索ステップと、レングス生成手段が、探索ステップで探索されたデータ列から1を選択して、選択されたデータ列の長さを求めてレングス値を生成するレングス生成ステップと、アドレス値生成手段が、レングス生成ステップでレングス値を生成するために用いたデータ列における開始データの、スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成ステップと、変換手段が、アドレス値の出現頻度に従い、アドレス値生成ステップで生成されたアドレス値のうち、出現頻度が高いアドレス値から所定数のアドレス値を、予め定められた値以下の変換アドレス値に変換する変換ステップと符号化手段が、レングス値と変換アドレス値とを符号化する符号化ステップとを有することを特徴とする。

【発明の効果】

【0017】

本発明によれば、特にマシン語のプログラムデータの圧縮符号化および復号処理を行うために用いて好適なデータ処理装置およびデータ処理方法が提供可能となる効果がある。

【図面の簡単な説明】

【0018】

【図1】図1は、本発明に係るデータ処理装置を適用可能なプリンタ装置の一例の構成を示すブロック図である。

【図2】図2は、本発明の実施形態に適用可能なプリンタ装置の全体的な処理を示すフローチャートである。

【図3】図3は、エンコーダの一例の構成を示すブロック図である。

【図4】図4は、符号フォーマットの例を示す略線図である。

【図5】図5は、本実施形態に適用可能な符号化処理について説明するための略線図である。

【図6】図6は、スライド探索処理およびリスト探索処理におけるフラグ処理を説明するための略線図である。

【図7】図7は、スライド探索処理およびリスト探索処理におけるフラグ処理を説明するための略線図である。

【図8】図8は、マシン語のプログラムデータの特徴について説明するための略線図である。

【図9】図9は、マシン語のプログラムデータの特徴について説明するための略線図である。

【図10】図10は、変換テーブルETRANSTABLEの例を示す略線図である。

【図11】図11は、本発明の実施形態による符号化処理の全体的な流れを示す一例のフローチャートである。

【図12】図12は、スライド探索処理の例をより詳細に示すフローチャートである。

【図13】図13は、リスト探索処理の例をより詳細に示すフローチャートである。

【図14】図14は、スライド追加処理の例をより詳細に示すフローチャートである。

【図15】図15は、スライド符号化処理の例をより詳細に示すフローチャートである。

【図16】図16は、エンコーダの一例の構成をより詳細に示すブロック図である。

【図17】図17は、スライド/リスト生成処理部の一例のハードウェア構成を示すブロック図である。

【図18】図18は、デコーダの一例の構成を示すブロック図である。

【図19】図19は、逆変換テーブルDTRANSTABLEの一例を示す略線図である。

【図20】図20は、符号データを復号する一例の処理を示すフローチャートである。

【図21】図21は、デコーダの一例の構成をより詳細に示すブロック図である。

【図22】図22は、スライド展開部の一例のハードウェア構成を示すブロック図である。

【発明を実施するための形態】

【0019】

以下に添付図面を参照して、この発明に係るデータ処理装置の一実施形態を詳細に説明する。図1は、本発明に係るデータ処理装置を適用可能なプリンタ装置の一例の構成を示す。図1の例では、プリンタ装置は、制御部200、メインメモリ210、プリンタエンジン211および不揮発性のメモリであるフラッシュメモリ240を備える。フラッシュメモリ240は、図1に例示されるようにプリンタ装置に内蔵されていてもよいし、プリンタ装置に対して脱着可能とされていてもよい。

【0020】

制御部200は、CPU(Central Processing Unit)212、CPU I/F201、メモリコントローラ202、符号化部204、復号部205、画像処理部206、ディレイメモリ207、エンジンコントローラ208、パネルコントローラ220、パネル221、スキャナ230、平滑フィルタ231、フラッシュメモリコントローラ241、エンコーダ242およびデコーダ243を含む。

【0021】

CPU212は、メインメモリ210に格納されるプログラムに従い、このプリンタ装置の全体の動作を制御する。CPU212は、CPU I/F201を介してメモリコントローラ202に接続される。メモリコントローラ202は、CPU212、符号化部204、復号部205、画像処理部206、通信I/F209、平滑フィルタ231、フラッシュメモリコントローラ241、エンコーダ242およびデコーダ243の、メインメモリ210に対するアクセスを調停する。

【0022】

メインメモリ210は、メモリコントローラ202に接続される。メモリコントローラ202は、メインメモリ210に対するアクセスの制御を行う。

【0023】

メインメモリ210は、プログラム領域210Aおよびデータ領域210Bを有する。プログラム領域210Aは、CPU212が動作するためのプログラムが格納される。データ領域210Bは、例えばネットワークを介して供給PDLデータが格納されると共に、CMYKバンドデータ、バンドデータが圧縮符号化された符号データ、ならびに、その他のデータが格納される。

【0024】

符号化部204は、メインメモリ210に格納されるバンドデータを符号化する。符号化されたバンドデータは、メモリコントローラ202を介してメインメモリ210に供給される。復号部205は、後述するプリンタエンジン211に同期して、符号化部204で符号化されメインメモリ210に書き込まれた符号化バンドデータをメインメモリ210から読み出して復号する。復号されたバンドデータは、メモリコントローラ202を介して画像処理部206に供給される。画像処理部206は、復号部205から供給されたバンドデータに対して階調処理など所定の画像処理を施す。

【0025】

画像処理が施されたバンドデータは、ディレイメモリ207を介してエンジンコントローラ208に転送される。ディレイメモリ207は、画像処理部206から出力されるバンドデータの転送速度と、エンジンコントローラ208からプリンタエンジン211に転送されるバンドデータの転送速度との違いを吸収する。

【0026】

エンジンコントローラ208は、プリンタエンジン211を制御する。図1では、プリンタエンジン211としてCMYK各色の版のうち1の版のものだけが記載され、その他の版については煩雑さを避けるために省略されている。

【0027】

通信I/F209は、ネットワークを介しての通信を制御する。例えば、ネットワークに接続されるコンピュータから出力されたPDL(Page Description Language)データは、通信I/F209により受信される。通信I/F209は、受信したPDLデータを、メモリコントローラ202を介してメインメモリ210に転送する。

【0028】

なお、ネットワークは、LAN(Local Area Network)などの所定の範囲内で通信を行うものでもよいし、インターネットなどより広範囲に通信可能なものでもよい。また、ネットワークは、有線通信に限らず無線通信を用いたものでもよいし、USB(Universal Serial Bus)やIEEE(Institute Electrical and Electronics Engineers)1394といったシリアル通信を行うものでもよい。

【0029】

フラッシュメモリ240は、CPU212上で動作するためのプログラムや、当該プログラムに用いられる各種データが、本実施形態による圧縮符号化方法により圧縮符号化されて格納される。例えば、メインメモリ210のプログラム領域210Aに対して、マシン語によるコードとして展開されるプログラムデータが、展開イメージのまま圧縮符号化され、スナップショットとしてフラッシュメモリ240に記憶される。フラッシュメモリコントローラ241は、フラッシュメモリ240に対するアクセスの制御を行う。

【0030】

エンコーダ242は、本実施形態による、LZ77符号を用いた圧縮符号化方法により、プログラムデータの圧縮符号化を行う。また、デコーダ243は、当該圧縮符号化方法により圧縮符号化された圧縮データの復号を行う。

【0031】

プリンタ装置の全体的な動作について、概略的に説明する。例えばコンピュータで生成されたPDLデータがネットワークを介して通信I/F209に受信され、メインメモリ210のデータ領域210Bに記憶される。CPU212は、メインメモリ210のデータ領域210BからPDLデータを読み出し、PDLを解析して、解析結果に基づきCMYKのバンド画像を描画する。描画されたCMYKのバンド画像によるCMYKバンドデータは、メインメモリ210のデータ領域210Bに格納される。

【0032】

符号化部204は、データ領域210BからCMYKバンドデータを読み出して、例えば予測符号化などを用いて符号化する。CMYKバンドデータが符号化された符号データは、メインメモリ210のデータ領域210Bに格納される。

【0033】

復号部205は、メインメモリ210のデータ領域210BからCMYKバンドデータが符号化された符号データを読み出して復号し、復号されたCMYKバンドデータをメモリコントローラ202を介して画像処理部206に供給する。画像処理部206は、復号部205から供給されたCMYKバンドデータに対して所定の画像処理を施す。画像処理されたCMYKバンドデータは、ディレイメモリ207およびプリンタエンジンコントローラ208を介してプリンタエンジン211に供給される。プリンタエンジン211は、供給されたCMYKバンドデータに基づきプリントアウトを行う。

【0034】

図2は、本実施形態に適用可能なプリンタ装置の全体的な処理を示すフローチャートである。概略的には、例えばユーザがプリンタ装置の電源をONとすると、電源立ち上げ処理が行われ(ステップS1)、プリンタ装置がRUN状態(稼働状態)になる(ステップS2)。ユーザの電源OFF操作などにより、電源立ち下げ処理が行われ(ステップS3)、プリンタ装置がスリープ状態となる(ステップS4)。

【0035】

ステップS1の電源立ち上げ処理では、フラッシュメモリ240に圧縮符号化されてスナップショットとして格納されたプログラムデータがフラッシュメモリ240から読み出され(ステップS1−1)、デコーダ243で本実施形態による復号方法に従い復号され、マシン語によるプログラムデータとされる(ステップS1−2)。このマシン語のプログラムデータは、メモリコントローラ202を介してメインメモリ210に供給され、プログラム領域210Aに格納される(ステップS1−3)。

【0036】

一方、ステップS3の電源立ち下げ処理では、メインメモリ210のプログラム領域210Aに格納されるマシン語によるプログラムデータがメインメモリ210から読み出され(ステップS3−1)、エンコーダ242で本実施形態による符号化方法に従い圧縮符号化される(ステップS3−2)。圧縮符号化されたマシン語プログラムデータは、フラッシュメモリ240に対してスナップショットとして格納される(ステップS3−3)。

【0037】

このように、電源立ち下げ処理時に、メインメモリ210のプログラム領域210Aに格納されるマシン語のプログラムデータを、メモリ上のイメージのまま圧縮符号化し、スナップショットとしてフラッシュメモリ240に格納することで、電源立ち上げ処理を高速化することができる。

【0038】

<エンコーダ>

図3は、エンコーダ242の一例の構成を示す。エンコーダ242において、データ読み込み部300により、メインメモリ210のプログラム領域210Aから、マシン語によるプログラムデータがメモリコントローラ202を介して読み出される。データ読み込み部300に読み込まれたデータは、スライド/リスト生成処理部301に供給される。

【0039】

スライド/リスト生成処理部301は、入力されたデータを順次記憶するFIFO方式のスライド記憶部を有する。スライド/リスト生成処理部301は、供給されたデータとスライド記憶部に記憶された過去の入力データとを順次比較する。そして、供給されたデータと過去の入力データとが一致した場合には、当該過去の入力データのスライド記憶部内の位置を示すアドレス値Addressを保持すると共に、一致した長さを示す値であるレングスLengthをカウントアップする。両者が一致しない場合には、データ値そのものをPASS符号として符号化する。

【0040】

ここで、本実施形態においては、詳細を後述する規則に従いアドレス値Addressを変換し、変換アドレス値TAddressとする。そして、これらPASS符号と、変換アドレス値TAddressおよびレングスLengthと、符号の種類を示すヘッダとを出力する。

【0041】

スライド/リスト生成処理部301のから出力された各値は、符号フォーマット生成処理部302に供給される。符号フォーマット生成処理部302は、供給されたPASS符号、変換アドレス値TAddress、レングスLengthおよびヘッダとを、図4に例示されるようなフォーマットで符号化する。

【0042】

図4において、PASS符号は、データ長が1ビットで値が「0」のヘッダに対して、後に8ビットのデータ長を持つデータ値が接続されてなる。スライド符号は、データ長が2ビットのヘッダに対して、レングスLengthおよびアドレス値Addressが順次接続される。レングスLengthは、符号長が8ビットとされる。

【0043】

ここで、本実施形態においては、変換アドレス値TAddressは、自身の値に応じて2種類の符号長のうち何れか一方を選択されて符号化される。図4の例では、変換アドレス値TAddressは、符号長が8ビットの符号と、符号長が4ビットの符号とのうち何れかに符号化される。符号長が8ビットの符号に符号化された変換アドレス値TAddressを含むスライド符号を、第1スライド符号と呼び、ヘッダが「10」とされる。また、符号長が4ビットの符号に符号化された変換アドレス値TAddressを含むスライド符号を、第2スライド符号と呼び、ヘッダが「11」とされる。

【0044】

なお、この図4に例示される符号フォーマットは、一例であって、これに限られるものではない。例えば、変換アドレス値TAddressの符号長は、第1および第2のスライド符号それぞれで8ビットまたは4ビットに限られない。

【0045】

符号フォーマット生成処理部302で生成されたPASS符号、ならびに、第1および第2スライド符号は、符号書き込み部303に供給される。符号書き込み部303は、供給されたPASS符号、ならびに、第1および第2およびスライド符号を、メモリコントローラ202およびフラッシュメモリコントローラ241を介してフラッシュメモリ240に書き込む。

【0046】

<符号化処理の概略>

次に、本実施形態に適用可能な、スライド/リスト生成処理部301における符号化処理について説明する。本実施形態では、LZ77符号を用い、スライド探索処理とリスト探索処理とを繰り返すことによって、データの符号化を行う。スライド探索処理は、1単位(例えば1バイト)の入力データと一致する、所定単位分の長さを持つスライド記憶部に記憶される過去の入力データを探索する。スライド記憶部内の過去の入力データに、入力データと一致するデータが探索されなかった場合には、入力データそのものをPASS符号として用いる。

【0047】

スライド探索処理において、入力データに一致するスライド記憶部内の過去の入力データが探索された場合、その一致した過去の入力データをルートとして、リスト探索処理が行われる。リスト探索処理は、ルートとされた入力データに対して連続的に入力された入力データ列と一致する、スライド記憶部内の過去の入力データ列(リストと呼ぶ)を探索する。

【0048】

リスト探索処理時に、入力データと一致するリストが無くなると、直前のリストから1を選び、選択されたリストのルートとなる過去の入力データのスライド記憶部内での位置をアドレス値Addressとし、当該リストの長さをレングスLengthとして出力する。

【0049】

すなわち、スライド/リスト生成処理部301では、スライド探索処理でリスト探索処理のルートとなる過去の入力データを形成する。そして、リスト探索処理で、ルートに基づくリストの成長および淘汰を行い、最終的に残ったリストに基づき符号化を行う。

【0050】

図5を用いてより具体的に説明する。図5の例では、スライド記憶部は、番号#0〜#15で示されるように、直列に接続された16個のレジスタを持ち、FIFO(First In First Out)として構成される。各レジスタは、それぞれ1単位(例えば1バイト)のデータを格納可能であるものとする。なお、以下では、このスライド記憶部が有するレジスタをスライドと呼ぶ。

【0051】

処理#1において、スライド記憶部の各スライドには、入力の新しい順、すなわち図5の右側から左側に向けて、「a,b,c,a,a,b,c,a,b,c,d,b,c,a,c,a」と、16個の過去に入力されたデータが既に格納されているものとする。最初に、スライド/リスト生成処理部301に対して入力データ「a」が入力される。スライド探索処理により、この入力データ「a」と、各スライドに記憶された過去の入力データのそれぞれとを比較し、一致しているデータを探索する。図5の例では、番号#0、#3、#4、#7、#13および#15のスライドに格納されているデータが入力データと一致していることが分かる。したがって、これらの番号のスライドに格納されているデータが、リスト探索処理におけるルートとなる。

【0052】

スライド探索処理によって、各スライドに記憶された過去の入力データから、入力データ「a」と一致しているデータが探索されたので、処理#2のリスト探索処理が行われる。

【0053】

処理#2では、各スライドに記憶される過去の入力データを左に1だけシフトさせて、処理#1で入力された入力データ「a」をスライド記憶部の番号#0のスライドに追加する。それと共に、次の入力データ「c」がスライド/リスト生成処理部301に対して入力される。リスト探索処理では、各スライドに記憶される過去の入力データのうち、直前の処理#1において入力データが一致した各スライド内の過去の入力データが格納されていたスライドから、新たな入力データ「c」と一致するデータを探索する。

【0054】

図5の例では、処理#1において入力データと一致した番号#0および#4のスライドに格納される過去の入力データは、処理#2において入力データと一致していない。一方、処理#1において入力データと一致した番号#3、#7、#13および#15のスライドに格納された過去の入力データは、データ「c」であって、新たな入力データ「c」と一致する。

【0055】

処理#2のリスト探索処理によって、直前の処理#1において入力データが一致した各スライド内の過去の入力データが格納されたスライドから、処理#2における入力データ「c」と一致するデータが探索されたので、次の処理はリスト探索処理となる。なお、処理#2は、リスト探索処理の開始点であるので、リストの長さを示すレングスLengthは、値「0」とされる。

【0056】

処理#3では、上述の処理#2と同様にして、各スライドに記憶される過去の入力データを左に1だけシフトさせて、処理#2で入力された入力データ「c」をスライド記憶部の番号#0のスライドに追加する。それと共に、次の入力データ「b」がスライド/リスト生成処理部301に対して入力される。そして、各スライドに記憶される過去の入力データのうち、直前の処理#2において入力データが一致した各スライド内の過去の入力データが格納されたスライドから、新たな入力データ「b」と一致するデータを探索する。

【0057】

図5の例では、処理#2において探索された番号#15のスライドに格納される過去の入力データは、処理#3において入力データと一致していない。一方、処理#2において探索された番号#3、#7および#13のスライドに格納される、処理#3における過去の入力データはデータ「b」であって、新たな入力データ「b」と一致する。次の処理#4では、この番号#3、#7および#13のスライドに格納される過去の入力データが、リスト探索の対象となる。すなわち、この処理#3の段階では、番号#3、#7および#13に係るリストが残っている。処理#3では、リストの長さが「1」となり、レングスLengthが値「1」とされる。

【0058】

このような処理を繰り返していき、リストが最も長くなるデータ列を求める。図5の例では、処理#5において、直前の処理#4においてリスト探索された番号#13のスライドに格納される過去の入力データ「c」と、新たな入力データ「g」とが一致しなくなり、リストが途切れる。そこで、処理#5では、1つ前の処理#4において残っているリストから1を選択し、そのスライドのスライド記憶部における位置(番号)をアドレス値Addressとし、リストの長さをレングスLengthとしてスライド符号に符号化する。図5の例では、アドレス値Addressが「13」、レングスLengthが「3」とされる。

【0059】

さらに、処理#5では、入力データ「g」についてスライド探索処理を行う。この例では、各スライドに過去の入力データとしてデータ「g」が記憶されていないため、一致するデータがないとされる。この場合、処理は処理#6に移行され、入力データ「g」がそのまま用いられてPASS符号に符号化される。

【0060】

PASS符号への符号化が行われると、処理#7で、各スライドに記憶される過去の入力データが左に1だけシフトされると共に、直前のリスト探索処理(処理#5)で入力された入力データ「g」がスライド記憶部の番号#0のスライドに追加される。そして、次の入力データ「b」に対してスライド探索処理が行われる。

【0061】

ここで、スライド記憶部は、FIFO方式により各スライドに格納されたデータのシフトを行うことができるため、入力データとの一致を記憶したリストをそのままの状態で保持しながら、次の入力データの処理に移行することができる。

【0062】

例えば、図5の例では、入力データが、処理#1において番号#0、#3、#4、#7、#13および#15のスライドに格納される過去の入力データと一致している。各スライドに格納されたデータを、新たなデータの入力に伴い順次シフトさせることで、例えば処理#2の当該番号#0、#3、#4、#7、#13および#15のスライドに対して次のデータが格納されることになる。したがって、スライド記憶部において、スライド探索処理で一致が探索された番号のスライドに格納されるデータを、リスト探索処理毎に入力データと比較していくことで、入力データのデータ列と一致する、過去の入力データのデータ列を探索することができる。

【0063】

このように、スライド記憶部をFIFO方式とすることで、リスト探索処理を簡易に行うことができる。

【0064】

なお、上述の処理によれば、リスト探索処理において入力データと一致するリストが無く、処理がリスト探索処理からスライド探索処理に移行する際に、1処理分、符号化が進行しない時間が生じることになる。すなわち、1処理を1クロックで行うとした場合、リスト探索処理からスライド探索処理に移行する際に、1クロック分の無駄が生じてしまうことになる。

【0065】

<フラグ処理>

上述したスライド探索処理およびリスト探索処理は、フラグによって制御される。このスライド探索処理およびリスト探索処理におけるフラグ処理について、図6および図7を用いて説明する。

【0066】

図6は、スライド探索処理の結果を示すRフラグRFLGmを示す。図6に例示されるように、スライド記憶部の各スライドに対して、図の右側から左側へ向けて「a,b,c,a,a,b,c,a,b,c,d,b,c,a,c,a」のように過去の入力データが格納された状態で、入力データ「a」が入力された場合、番号#0、#3、#4、#7、#13および#15のスライドで、入力データと各スライドに記憶される過去の入力データとが一致する。そこで、これらの番号のスライドに対応するRフラグRFLG0、RFLG3、RFLG4、RFLG7、RFLG13およびRFLG15を、それぞれ一致したことを示す値「1」とする。

【0067】

このように、入力データと、各スライドに記憶される過去の入力データとが一致する場合は、符号化処理を行わずにリスト探索処理が行われる。このとき、RフラグRFLGmの各スライドに対する位置は、固定的である。入力データと一致する、各スライドに記憶される過去の入力データが無い場合は、入力データをそのまま用いてPASS符号に符号化し、次の入力データに対してスライド探索処理を行う。

【0068】

図7は、リスト探索処理の結果を示すWフラグWFLGmの例を示す。リスト探索処理では、新たに入力された入力データと一致するデータが、各スライドのうちRフラグRFLGmが「1」とされたスライドに格納されるデータから探索される。若し、一致するデータが探索されたら、当該スライドに対するWフラグWFLGmの値を、一致したことを示す値「1」とする。

【0069】

図7の例では、各スライドに記憶される過去の入力データのうち、RフラグRFLGmが値「1」である番号#0、#3、#4、#7、#13および#15のスライドに格納されるデータに対してリスト探索処理が行われる。これらのうち、入力データ「c」に対して、番号#3、#7、#13および#15のスライドに格納されるデータが一致するので、対応するWフラグWFLG3、WFLG7、WFLG13およびWFLG15の値を、一致したことを示す値「1」とする。各スライドに記憶される過去の入力データのうち、このWフラグWFLGmの値が「1」とされたスライドに格納されるデータは、直前に入力データと一致したスライドに格納される過去の入力データと、現在入力データと一致した過去の入力データとが連なっていることを示す。

【0070】

次に、値が「1」のWフラグWFLGmを探索する。この値「1」のWフラグWFLGmが存在する場合は、各WフラグWFLGmを新たなRフラグRFLGmとし、上述と同様にして次の入力データに対してリスト探索処理を行う。

【0071】

一方、探索の結果、値が「1」のWフラグWFLGmが存在しないとされた場合は、リストが途絶えたことを意味する。この場合は、値が「1」のRフラグRFLGmを1つ選択し、選択したRフラグRFLGmに対応するスライドのアドレス値Addressと、そのときのレングスLengthとをスライド符号に符号化する。

【0072】

ここで、図8および図9を用いて、マシン語のプログラムデータの特徴について、概略的に説明する。図8は、RISC(Reduced Instruction Set Computer)技術によるCPUに対するマシン語プログラムにおける命令フォーマットの例を示す。図8(a)は、R(レジスタ)タイプ命令の例、図8(b)は、I(イミディエイト)タイプ命令の例、図8(c)は、J(ジャンプ)タイプ命令の例をそれぞれ示す。各命令は、32ビットを所定に分割した領域に所定のニーモニックが格納される。各ニーモニックの意味を、図8(d)に示す。

【0073】

各ニーモニックのうち、オペレーションコードを示すニーモニック「Op」は、Rタイプ、IタイプおよびJタイプそれぞれの命令において、固定的に先頭の6ビットの領域に格納される。このように、RISCにおいては、データ長が32ビットの固定フォーマットで決められた所定領域に対して、同じ意味のコードが格納されるため、スライドが4バイト(32ビット)毎または8バイト毎に一致する可能性が高くなる。

【0074】

図9は、マシン語のプログラムデータにおけるスライドの一致位置に関する統計結果の例を示す。図9において、横軸がスライドの一致位置(アドレス値Address)を示し、縦軸が一致回数(出現頻度)を示す。図9に示される統計結果によれば、4バイト毎に一致回数の大きなピークが現れることが示されている。また、4バイト毎のピークを除外して全体的な変化を見ると、一致位置がより近いほどスライドの一致する確率が高くなることが分かる。一方、スライドの一致位置がある程度離れると、低い一致確率に収束することが分かる。

【0075】

本実施形態では、上述したような、マシン語のプログラムデータにおいて、4バイト毎にスライドの一致確率のピークが現れることを利用して、スライド符号の符号化を行う。

【0076】

具体的には、スライド符号のアドレス値Addressを、対応するスライドの一致回数が多い順に並べ替えて、並べ替え後の順序を示す値からなる変換アドレス値TAddressを生成する。そして、4ビットで表現可能な所定数の変換アドレス値TAddress、すなわち値が「0」〜「15」までの変換アドレス値TAddressを、符号長が4ビットの符号に符号化する。この符号長が4ビットの符号に符号化された変換アドレス値TAddressにより、第2スライド符号が形成される。一方、値が「15」〜「255」の変換アドレス値TAddressは、符号長が8ビットの符号に符号化する。この符号長が8ビットの符号に符号化された変換アドレス値TAddressにより、第1スライド符号が形成される。

【0077】

アドレス値Addressを変換アドレス値TAddressに変換するためには、例えば図10に例示されるような変換テーブルETRANSTABLEを用いることができる。この変換テーブルETRANSTABLEに列挙される数値は、変換後の変換アドレス値TAddressを示す。また、変換テーブルETRANSTABLEに列挙される数値の順番を示す値(「0」から始まるものとする)が変換前のアドレス値Addressを示す。すなわち、変換テーブルETRANSTABLEに対してアドレス値Addressを入力すると、入力されたアドレス値Addressに対応する位置の値が変換アドレス値TAddressとして出力される。

【0078】

変換テーブルETRANSTABLEは、図10から分かるように、4個のアドレス値Address毎に小さい値の変換アドレス値TAddressを割り当てている。換言すれば、図9の統計結果に従い、バイト単位でプログラムデータの4バイト毎に小さい値の変換アドレス値TAddressを割り当てる。また、図9の統計結果によれば、スライドの一致位置がある程度離れると一致回数が少ない値に収束するので、変換テーブルETRANSTABLEの後方に行くに従い、最後尾の値(すなわちアドレス値Address「255」)を除き、この変換アドレス値TAddressの規則性を弱めている。

【0079】

さらに、変換テーブルETRANSTABLEの先頭部分において、アドレス値Address「0」に対して変換アドレス値TAddress「15」を割り当てている。これは、図9を用いて説明したように、統計結果の全体的な特性として、スライドの一致位置が近いほど一致回数も大きい傾向にあることから来ている。

【0080】

具体的には、変換テーブルETRANSTABLEにおいて、変換前のアドレス値Address「3」は、変換アドレス値TAddress「0」に変換される。また、変換前のアドレス値Address「0」は、変換アドレス値TAddress「15」に変換される。同様に、変換前のアドレス値Address「11」は、変換アドレス値TAddress「2」に変換される。

【0081】

なお、上述したように、値が「0」〜「15」までの変換アドレス値TAddressは、全て符号長が4ビットの符号に変換される。そのため、実際には、変換テーブルETRANSTABLEにおいて変換アドレス値TAddress「0」〜「15」に対応付けるアドレス値Addressの順番は、変更することができる。同様に、変換アドレス値TAddress「16」〜「255」に対応付けるアドレス値Addressの順番も変更できる。

【0082】

ここでは、変換テーブルETRANSTABLEが、変換アドレス値TAddressが列挙され、変換アドレス値TAddressの順番が元のアドレス値Addressを示すように説明したが、これはこの例に限定されない。例えば、変換前のアドレス値Addressと、変換後の変換アドレス値TAddressとを1対1に対応付けたテーブルとしてもよい。

【0083】

また、ここでは、小さい値の変換アドレス値TAddressを4バイト毎に割り当てているが、これはこの例に限定されない。すなわち、小さい値の変換アドレス値TAddressの割り当て単位は、プログラムデータの命令フォーマットに応じて設定することができる。例えば、命令フォーマットが64ビットのデータ長で構成されていれば、小さい値の変換アドレス値TAddressを8バイト毎に割り当てることが考えられる。

【0084】

<符号化処理の詳細>

次に、スライド/リスト生成処理部301における符号化処理について、より詳細に説明する。図11は、本実施形態による符号化処理の全体的な流れを示す一例のフローチャートである。なお、図11のフローチャートの処理に先立って、符号読み込み部300は、ある長さのデータを処理対象のデータとして予め保持しているものとする。

【0085】

最初のステップS10で、スライド/リスト生成処理部301は、スライド探索処理およびリスト探索処理のうち何れが有効かを示すフラグListFLGを、スライド探索処理を行っていることを示す値「0」に初期化する。次に、ステップS11で、スライド/リスト生成処理部301は、符号読み込み部300から1単位分のデータを入力データとして読み込む。読み込んだ入力データは、スライド記憶部に格納される。

【0086】

入力データがスライド記憶部に格納されると、ステップS12で、1単位分のデータに対するスライド探索処理が行われると共に、ステップS13で、1単位分のデータに対するリスト探索処理が行われる。詳細は後述するが、本実施形態においては、スライド探索処理を行うスライド探索部と、リスト探索処理を行うリスト探索部とが別個の構成とされているので、ステップS12およびステップS13の処理を並列的に行うことが可能である。

【0087】

処理はステップS14に移行され、スライド/リスト生成処理部301は、フラグListFLGの値が「0」か否かを判定する。若し、「0」であると判定されたら、現在スライド探索処理が有効であるとされ、処理はステップS15に移行される。ステップS15では、フラグSFINDFLGの値が「1」であるか否かが判定される。若し、値が「1」であれば、スライド記憶部101において入力データと一致する過去の入力データが探索されたとされ、ステップS16でフラグListFLGの値がリスト探索処理が有効であることを示す「1」とされる。

【0088】

そして、処理がステップS25に移行され、スライド記憶部に対して入力データが追加される。次のステップS26で、処理対象のデータ全てに対する処理が終了したか否かが判定される。若し、終了していないと判定されたら、処理はステップS11に戻され、次の1単位分のデータが入力データとして読み込まれる。一方、終了していると判定されたら、一連の符号化処理が終了される。

【0089】

一方、ステップS15で、フラグSFINDFLGの値が「0」であると判定されたら、スライド記憶部101において入力データと一致する過去の入力データが探索されなかったとされ、処理はステップS17に移行される。ステップS17では、フラグListFLGの値が「0」とされてスライド探索処理が有効であるとされ、次のステップS18で入力データがPASS符号に符号化される。また、一致フラグFLAGが値「0」とされる。そして、処理はステップS25に移行される。

【0090】

また、上述のステップS14において、フラグListFLGの値が「0」ではない、すなわち「1」であると判定されたら、現在リスト探索処理が有効であるとされ、処理がステップS19に移行される。ステップS19では、フラグLFINDFLGの値が「1」か否かを判定する。若し、「1」であると判定されたら、処理はステップS25に移行される。

【0091】

一方、ステップS19で、フラグLFINDFLGの値が「1」ではない、すなわち、フラグLFINDFLGの値が「0」であると判定されたら、処理はステップS20に移行される。ステップS20では、アドレス値Addressが変換テーブルETRANSTABLEに従い変換アドレス値TAddressに変換され、この変換アドレス値TAddressと、レングスLengthおよびヘッダとが、図4に例示される第1または第2スライド符号に符号化される。そして、処理はステップS21に移行され、フラグSFINDFLGの値が「1」であるか否かが判定される。若し、「1」であると判定されたら、リスト探索処理においてリストが継続されたとされて処理がステップS22に移行され、フラグListFLGの値が「1」とされる。そして、処理がステップS25に移行される。

【0092】

一方、ステップS20でフラグSFINDFLGの値が「0」であると判定されたら、リスト探索処理においてリストが途切れたとされ、処理がステップS23に移行され、フラグListFLGの値が「0」とされる。次のステップS24で入力データがそのままPASS符号に符号化され、レジスタ141に格納される。そして、処理はステップS25に移行される。

【0093】

図12は、図11のステップS12における一例のスライド探索処理をより詳細に示すフローチャートである。なお、この図12、ならびに、以下の図13および図14では、スライド記憶部におけるスライドを、スライドの番号を含めるように、スライド[x]のように表す。また、FIFO構成とされるスライド記憶部において先頭のスライドを、スライド[0]とする。

【0094】

先ず、ステップS30〜ステップS32で、レングスLength、フラグSFINDFLGおよび変数IWがそれぞれ値「0」に初期化される。処理はステップS33に移行され、入力データとスライド[IW]に格納された過去の入力データとが一致するか否かが判定される。若し、一致すると判定されたら、処理はステップS34に移行され、フラグSFINDFLGの値が「1」とされ、次のステップS35で、RフラグRFLG[IW]の値が「1」とされる。

【0095】

そして、処理はステップS37に移行され、変数IWがスライドサイズ未満、すなわち、スライド記憶部が有するスライド数未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS38で変数IWに「1」が加えられ、処理がステップS33に戻される。一方、ステップS37で、変数IWがスライドサイズ以上であると判定されたら、一連の処理が終了される。

【0096】

一方、ステップS33で入力データとスライド[IW]に格納された過去の入力データとが一致しないと判定されたら、処理はステップS36に移行され、RフラグRFLG[IW]の値が「0」とされる。そして、処理がステップS37に移行される。

【0097】

図13は、図11のステップS13による一例のリスト探索処理をより詳細に示すフローチャートである。先ず、ステップS40およびステップS41で、フラグLFINDFLGおよび変数IWがそれぞれ値「0」に初期化される。

【0098】

ステップS42で、入力データとスライド[IW]に格納された過去の入力データとが一致し、且つ、RフラグRFLG[IW]の値が「1」であるか否かが判定される。若し、それぞれの条件を満たすと判定されたら、処理はステップS43に移行され、WフラグWFLG[IW]の値が「1」とされ、次のステップS44で、フラグLFINDFLGの値が「1」とされる。そして、処理がステップS46に移行される。

【0099】

一方、ステップS42で、上述の条件を満たさない、すなわち、入力データとスライド[IW]に格納された過去の入力データとが一致しない、または、RフラグRFLG[IW]の値が「1」でないと判定されたら、処理はステップS45に移行され、WフラグWFLG[IW]の値が「0」とされる。そして、処理がステップS46に移行される。

【0100】

ステップS46では、変数IWがスライドサイズ未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS47で変数IWに「1」が加えられ、処理がステップS42に戻される。一方、変数IWがスライドサイズ以上であると判定されたら、処理がステップS48に移行される。

【0101】

ステップS48では、フラグLFINDFLGの値が「0」であるか否かが判定される。若し、値が「0」であると判定されたら、処理がステップS49に移行されて変数IWが値「0」に初期化され、次のステップS50でRフラグRFLG[IW]の値が「1」であるか否かが判定される。若し、「1」であると判定されたら、処理はステップS51に移行される。

【0102】

ステップS51では、変数IWがアドレス値Addressとされ、次のステップS52で、スライドサイズを変数IWに代入する。そして、処理がステップS53に移行される。ステップS53では、変数IWがスライドサイズ未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS54で変数IWに「1」が加算されて処理がステップS50に戻される。

【0103】

一方、ステップS53で、変数IWがスライドサイズ以上であると判定されたら、一連の処理が終了される。例えば、上述したステップS52を経由してこのステップS53に到達した場合、ステップS52で変数IWにスライドサイズが代入されているため、必ず処理が終了される。

【0104】

上述したステップS48で、フラグLFINDFLGの値が「0」ではないと判定されたら、処理はステップS55に移行され、変数IWが値「0」に初期化される。次のステップS56で、RフラグRFLG[IW]に対してWフラグWFLG[IW]が設定される。そして、ステップS57で、変数IWがスライドサイズ未満であるか否かが判定される。若し、変数IWがスライドサイズ未満であると判定されたら、ステップS58で変数IWに「1」が加算されて処理がステップS56に戻される。一方、ステップS57で変数IWがスライドサイズ以上であると判定されたら、処理は次のステップS59に移行され、レングスLengthに対して1が加算され、一連の処理が終了される。

【0105】

図14は、図11のステップS25による一例のスライド追加処理をより詳細に示す一例のフローチャートである。先ず、ステップS70で、変数IWがスライド数から1を減じた値に設定される。次のステップS71で、スライド[IW]に、スライド[IW−1]の値が格納され、ステップS72で、変数IWが「0」を超えるか否かが判定される。若し、変数IWが「0」を超えると判定されたら、処理はステップS73に移行され、変数IWから「1」が減じられる。そして、処理がステップS71に戻される。一方、ステップS72で、変数IWが「0」以下であると判定されたら、処理はステップS74に移行され、スライド[0]に対して入力データが格納される。

【0106】

図15は、図11のステップS20による一例のスライド符号化処理をより詳細に示す。符号フォーマットは、図4に示したフォーマットに従うものとする。先ず、ステップS80で、アドレス値Addressが変換テーブルETRANSTABLEにより変換アドレス値TAddressに変換される。次に、ステップS81で、変換アドレス値TAddressの値が「16」未満であるか否かが判定される。なお、変換アドレス値TAddressは、値「0」から開始されるものとする。

【0107】

若し、変換アドレス値TAddressが値「16」未満であると判定されたら、処理はステップS82に移行され、ヘッダの符号化が行われる。この例では、ヘッダは、符号長が2ビット、値「10」の符号に符号化される。ヘッダの符号化が行われると、次のステップS83で、一致長さすなわちレングスLengthの符号化が行われる。この例では、レングスLengthは、符号長が8ビットの符号に符号化される。そして、次のステップS84で、一致位置すなわち変換アドレス値TAddressの符号化がなされる。変換アドレス値TAddressが値「16」未満であるので、符号長が4ビットの符号に符号化される。

【0108】

一方、変換アドレス値TAddressが値「16」以上であると判定されたら、処理はステップS85に移行され、ヘッダの符号化が行われる。この例では、ヘッダは、符号長が2ビット、値「11」の符号に符号化される。ヘッダの符号化が行われると、次のステップS86で、一致長さすなわちレングスLengthの符号化が行われる。この例では、レングスLengthは、符号長が8ビットの符号に符号化される。そして、次のステップS87で、一致位置すなわち変換アドレス値TAddressの符号化がなされる。変換アドレス値TAddressが値「16」以上であるので、符号長が8ビットの符号に符号化される。

【0109】

図16は、エンコーダ242の一例の構成をより詳細に示す。なお、図16において、上述の図3と共通する部分には同一の符号を付し、詳細な説明を省略する。エンコーダ242は、データ読み込み部300、スライド/リスト生成処理部301、符号フォーマット生成処理部302および符号書き込み部303を有すると共に、メモリコントローラI/F310、データアドレス生成部311および符号アドレス生成部312を有する。

【0110】

データアドレス生成部311は、メインメモリ210のプログラム領域210Aからプログラムデータを読み出す際のメモリアドレスを生成する。データ読み込み部300は、データアドレス生成部311で生成されたメモリアドレスからのデータの読み出しを、メモリコントローラI/F310を介してメモリコントローラ202に対して要求する。この要求に応じてメモリコントローラ202によりメインメモリ210のプログラム領域210Aから読み出されたプログラムデータがメモリコントローラ202からエンコーダ242に対して供給され、メモリコントローラI/F310を介してデータ読み込み部300に供給される。データ読み込み部300は、供給されたプログラムデータを、スライド/リスト生成処理部301に供給する。

【0111】

スライド/リスト生成処理部301は、供給されたプログラムデータから、既に説明したようにしてアドレス値Address、レングスLength、PASS符号およびヘッダを生成する。ここで、アドレス値Addressは、変換テーブルETRANSTABLEにより変換アドレス値TAddressに変換される。これら変換アドレス値TAddress、レングスLength、PASS符号(データ値)およびヘッダは、符号フォーマット生成処理部302に供給される。符号フォーマット生成処理部302は、図4で説明した符号フォーマットに従い、供給された各値からPASS符号、第1スライド符号および第2スライド符号を生成する。生成されたPASS符号、第1スライド符号および第2スライド符号は、符号書き込み部303に供給される。

【0112】

符号書き込み部303は、供給されたPASS符号、第1スライド符号および第2スライド符号をメモリコントローラI/F310を介してメモリコントローラ202に供給する。それと共に、符号書き込み部303は、これらの符号を符号アドレス生成部312で生成されたメモリアドレスに従いフラッシュメモリ240に書き込むように、メモリコントローラI/F310を介してメモリコントローラ202に要求する。メモリコントローラ202は、この要求に従い、供給された符号を、フラッシュメモリコントローラ241を介してフラッシュメモリ240に書き込む。

【0113】

<スライド/リスト生成処理部のハードウェア構成例>

図17は、上述したスライド探索処理、リスト探索処理および符号化処理を実行するスライド/リスト生成処理部301の、一例のハードウェア構成を示す。スライド/リスト生成処理部301は、スライド探索部100、スライド記憶部101、リスト探索部102およびコントローラ103を有する。

【0114】

コントローラ103は、例えばマイクロプロセッサからなり、図11のフローチャートを用いて説明した、ステップS12およびステップS13の処理を除いた、ステップS11〜ステップS26による処理を行い、スライド/リスト生成処理部301の動作を制御する。例えば、コントローラ103は、上述した現在スライド探索処理およびリスト探索処理のうち何れが有効かを示すフラグListFLGによる動作制御を行う。

【0115】

スライド/リスト生成処理部301に対して、例えば1クロック毎に1単位の入力データが入力され、スライド探索部100、スライド記憶部101およびリスト探索部102にそれぞれ供給される。入力データは、さらに、出力側のレジスタ141にも格納される。レジスタ141に格納される入力データは、PASS符号の符号化の際のデータ値として用いられる。以下では、データの1単位を1バイトとする。

【0116】

スライド記憶部101は、各々がレジスタからなり、それぞれ1単位のデータが格納されるn個(例えば256個)のスライド1201、1202、…、120nが直列に接続されて構成される。また、各スライド1201、1202、…、120nの出力は、次のレジスタに供給されると共に、後述するスライド探索部100の対応する比較器111mの一方の入力端と、リスト探索部102の対応する比較器130mの一方の入力端にそれぞれ供給される。

【0117】

なお、比較器130mは、比較器1301〜130nのうち任意の比較器を表す。このような表記は、比較器1111〜111n、セレクタ1311〜131n、レジスタ1321〜132nにおいて共通とする。

【0118】

なお、アドレス値AddressおよびレングスLengthのデータ長は、スライド記憶部101が有するスライド数nに応じて決められる。すなわち、スライド数n=256であれば、アドレス値AddressおよびレングスLengthが「256」までの値を表現可能に、それぞれのデータ長が8ビットに決められる。

【0119】

スライド記憶部101は、これらn個のスライド1201、1202、…、120nによりFIFOが構成され、入力されたデータがスライド1201からスライド1202、スライド1203、…と1クロック毎に順次送られていく。

【0120】

スライド探索部100は、n個の比較器1111、1112、…、111nと、n入力の論理和回路110とを有する。比較器1111、1112、…、111nのそれぞれは、一方および他方の入力端に入力されたデータを比較し、両者が一致していれば値「1」を出力し、一致していなければ値「0」を出力する。

【0121】

比較器1111、1112、…、111nの一方の入力端には、上述したように、スライド記憶部101が有するスライド1201、1202、…、120nの出力がそれぞれ入力される。また、比較器1111、1112、…、111nそれぞれの他方の入力端には、入力データが入力される。

【0122】

比較器1111、1112、…、111nそれぞれの出力は、n入力の論理和回路110に入力されると共に、後述するリスト探索部102のセレクタ(SEL)1311、1312、…、131nの一方の入力端にそれぞれ入力される。論理和回路110の出力は、フラグSFINDFLGとしてコントローラ103に供給される。このフラグSFINDFLGは、スライド1201、1202、…、120nのデータのうち少なくとも1が入力データと一致しているか否かを示す。

【0123】

リスト探索部102は、それぞれn個の比較器1301、1302、…、130n、セレクタ1311、1312、…、131n、ならびに、レジスタ1321、1322、…、132nと、アドレス値生成部133と、n入力の論理和回路134とを有する。比較器1301、1302、…、130nのそれぞれは、一方および他方の入力端に入力されたデータを比較し、両者が一致していれば値「1」を出力し、一致していなければ値「0」を出力する。

【0124】

比較器1301、1302、…、130nの一方の入力端には、上述したように、スライド記憶部101が有するスライド1201、1202、…、120nの出力がそれぞれ入力される。また、比較器1301、1302、…、130nそれぞれの他方の入力端には、入力データが入力される。

【0125】

比較器1301、1302、…、130nの出力は、WフラグWFLGmであって、n入力の論理和回路134にそれぞれ入力されると共に、セレクタ1311、1312、…、131nの他方の入力端にそれぞれ入力される。論理和回路134の出力は、フラグLFINDFLGとしてコントローラ103に供給される。フラグLFINDFLGは、WフラグWFLG1、WFLG2、…、WFLGnのうち少なくとも1の値が「1」であることを示す。

【0126】

セレクタ1311、1312、…、131nの出力は、RフラグRFLGmとされて、それぞれレジスタ1321、1322、…、132nに格納される。セレクタ1311、1312、…、131nは、コントローラ103から図示しない経路を経て供給されるフラグListFLGにより、一方および他方の端子のうち何れを選択するかが制御される。

【0127】

若し、フラグListFLGの値が「0」であって、現在スライド探索処理が有効であることが示されていれば、セレクタ1311、1312、…、131nは、それぞれの一方の入力端に入力された、スライド探索部100における比較器1111、1112、…、111nの出力をレジスタ1321、1322、…、132nに供給するように制御される。例えば、セレクタ131m(なお、1≦m≦nとする)は、対応するレジスタ132mに格納される値が「0」のときに入力端が選択されるように制御される。

【0128】

一方、フラグListFLGの値が「1」であって、現在リスト探索処理が有効であることが示されていれば、セレクタ1311、1312、…、131nは、それぞれの他方の入力端に入力された、リスト探索部102における比較器1301、1302、…、130nを選択してレジスタ1321、1322、…、132nに供給するように制御される。例えば、セレクタ131mは、対応するレジスタ132mに格納される値が「1」のときに他方の入力端が選択されるように制御される。

【0129】

レジスタ1321、1322、…、132nは、セレクタ1311、1312、…、131nからの出力が供給されると、格納されているRフラグRFLG1、RFLG2、…、RFLGnを出力する。すなわち、レジスタ1321、1322、…、132nに格納されるRフラグRFLG1、RFLG2、…、RFLGnは、供給されたセレクタ1311、1312、…、131nからの出力により更新される。

【0130】

レジスタ1321、1322、…、132nから出力されたRフラグRFLG1、RFLG2、…、RFLGnは、比較器1301、1302、…、130nの動作を制御する制御信号として、比較器1301、1302、…、130nの制御端にそれぞれ供給される。例えば、例えば比較器130mは、対応するレジスタ132mから供給された制御信号が値「1」を示していれば比較動作を行い、値「0」を示していれば比較動作を行わない。これは、比較器1301、1302、…、130nそれぞれの動作は、比較器1301、1302、…、130n自身の出力により絞り込まれていくことを意味する。

【0131】

レジスタ1321、1322、…、132nから出力されたRフラグRFLG1、RFLG2、…、RFLGnは、さらにアドレス値生成部133にも供給される。アドレス値生成部133は、図4の処理#5で説明したように、リスト探索処理が終了した際に、レジスタ1321、1322、…、132nから供給されるRフラグRFLG1、RFLG2、…、RFLGnのうち、値が「1」であるRフラグRFLGmを選択し、選択されたRフラグRFLGmの番号をアドレス値Addressとして出力する。アドレス値生成部133から出力されたアドレス値Addressは、アドレス変換部144に供給される。

【0132】

アドレス変換部144は、図10を用いて説明した変換テーブルETRANSTABLEを持ち、供給されたアドレス値Addressを、変換テーブルETRANSTABLEに従い変換アドレス値TAddressに変換する。アドレス値Addressが変換された変換アドレス値TAddressは、レジスタ140に格納されると共に、コントローラ103に供給される。

【0133】

コントローラ103は、スライド探索部100から供給されたフラグSFINDFLGと、リスト探索部102から供給されたフラグLFINDFLGと、アドレス変換部144から供給された変換アドレス値TAddress値とに基づき、レングスLengthおよびヘッダを生成する。レングスLengthおよび一致フラグFLAGは、それぞれレジスタ143および142に格納される。

【0134】

なお、レジスタ140〜143にそれぞれ格納された変換アドレス値TAddress、データ値、ヘッダおよびレングスLengthは、それぞれ符号フォーマット生成処理部302に読み出され、図4に例示する符号フォーマットに従い符号化され符号データが生成される。

【0135】

このような構成において、スライド探索処理は、以下のように行われる。すなわち、比較器1111、1112、…、111nによる、入力データと、スライド1201、1202、…、120nに格納された過去の入力データとの比較処理が行われる。比較結果がそれぞれ論理和回路110に供給され、フラグSFINDFLGが出力される。比較結果は、セレクタ1311、1312、…、131nにも供給され、スライド探索処理の間は、レジスタ1321、1322、…、132nに格納される。図17の構成によれば、この一連の処理を1クロックで実行可能である。

【0136】

また、リスト探索処理は、以下のように行われる。すなわち、比較器1301、1302、…、130nによる、入力データと、スライド1201、1202、…、120nに格納された過去の入力データとの比較処理が行われる。このとき、レジスタ1321、1322、…、132nに格納されるRフラグRFLG1、RFLG2、…、RFLGnの値に基づき、比較器1301、1302、…、130nの比較動作が制御される。例えば、RフラグRFLG1、RFLG2、…、RFLGnの値が全て「0」であれば、比較器1301、1302、…、130n全ての比較動作が行われないことになる。この状態を、リスト探索処理が行われていない状態とする。

【0137】

比較器1301、1302、…、130nによる比較結果がそれぞれ論理和回路134に供給され、フラグLFINDFLGが出力される。また、各比較結果は、セレクタ1311、1312、…、131nに供給され、リスト探索処理の間は、レジスタ1321、1322、…、132nに格納される。また、レジスタ1321、1322、…、132nに格納されるRフラグRFLG1、RFLG2、…、RFLGnは、アドレス値生成部133にも保持される。

【0138】

アドレス値生成部133は、レジスタ1321、1322、…、132nに格納される値が全て「0」であれば、保持しているRフラグRFLG1、RFLG2、…、RFLGnのうち値が「1」のRフラグRFLGmの位置を、アドレス値Addressとし、さらにアドレス変換部144で変換アドレス値TAddressとしてコントローラ103に渡す。図17の構成によれば、このリスト探索処理による一連の処理を1クロックで実行可能である。

【0139】

図17の構成によれば、スライド探索部100と、リスト探索部102とがそれぞれ別個の構成とされると共に、スライド探索部100とリスト探索部102とでスライド記憶部100を共有する。そのため、スライド探索部100によるスライド探索処理と、リスト探索部102によるリスト探索処理とを並列的に実行することが可能である。したがって、リスト探索処理からスライド探索処理へと移行する際の1クロック分の無駄が生じず、符号化処理をより高速化できる。また、図17の構成によれば、先読みバッファや大規模なマトリクスアレイなどの構成が不要なので、ハードウェア規模を小さくできる。

【0140】

なお、エンコーダ242の構成は、図17に示した構成に限定されない。すなわち、LZ77符号の符号化を行い、レングスLengthおよびアドレス値Addressを出力するものであれば、他の構成のエンコーダを適用することができる。

【0141】

<デコーダ>

図18は、デコーダ243の一例の構成を示す。デコーダ243において、符号読み込み部400により、上述したエンコーダ242で符号化された符号データがフラッシュメモリ240から読み込まれる。符号読み込み部400に読み込まれた符号データは、符号フォーマット解析部401に供給される。符号フォーマット解析部401は、図4を用いて説明した符号フォーマットに従い、供給された符号データを解釈してデータ値、変換アドレス値TAddress、レングスLengthおよびヘッダを取り出す。取り出されたこれらのデータは、スライド展開部402に供給される。

【0142】

スライド展開部402は、図5を用いて説明したように、直列に接続された複数のレジスタがFIFOとして構成される、スライド記憶部を持つ。各レジスタは、スライドと呼ばれ、それぞれ1単位(例えば1バイト)のデータを格納可能とされる。スライド展開部402は、供給された変換アドレス値TAddressを元のアドレス値Addressに逆変換し、このアドレス値Addressと、供給されたデータ値、レングスLengthおよびヘッダに基づき、スライド記憶部における各スライドに対してデータを展開し、符号データを復号する。復号されたデータは、データ書き込み部403に供給され、メインメモリ210のプログラム領域210Aに書き込まれる。

【0143】

図19は、変換アドレス値TAddressを元のアドレス値Addressに変換するための逆変換テーブルDTRANSTABLEの一例を示す。この逆変換テーブルDTRANSTABLEに列挙される数値は、元のアドレス値Addressを示す。また、逆変換テーブルDTRANSTABLEに列挙される数値の順番を示す値が、変換アドレス値TAddressを示す。

【0144】

すなわち、逆変換テーブルDTRANSTABLEにおいて、変換アドレス値TAddress「0」は、元のアドレス値Address「3」に変換される。また、変換アドレス値TAddress「15」は、元のアドレス値Address「0」に変換される。同様に、変換アドレス値TAddress「2」は、元のアドレス値Address「11」に変換される。

【0145】

<復号処理の詳細>

図20は、上述した本実施形態の符号化方法により符号化された符号データを、デコーダ243で復号する一例の処理を示すフローチャートである。なお、符号読み込み部400により、フラッシュメモリ240から予め符号データが読み込まれているものとする。先ず、ステップS100で、符号フォーマット解析部401は、符号読み込み部400に読み込まれている圧縮データのヘッダを読み込み、ヘッダの値が「0」であるか否かを判定する(ステップS101)。

【0146】

若し、ヘッダの値が「0」であれば、当該ヘッダを含む符号がPASS符号であると判定され、処理がステップS102に移行される。ステップS102で、符号フォーマット解析部401は、次のステップS102でヘッダに続く8ビットをデータ値として読み込む。読み込まれたデータ値は、そのまま出力データとして出力される(ステップS103)と共に、スライド展開部402に供給されスライドに追加される(ステップS104)。データ値のスライドに対する追加処理は、図14のフローチャートで説明したのと同様の手順により行われる。そして、処理がステップS115に移行される。

【0147】

ステップS115では、例えば符号読み込み部400により、読み込まれている符号データに対する処理が全て終了したか否かが判定される。全て終了したと判定されたら、一連の復号処理が終了される。一方、符号読み込み部400に読み込まれている全ての符号データに対する処理が終了していないと判定されたら、処理はステップS100に戻され、次の符号に対する処理が行われる。

【0148】

符号フォーマット解析部401は、ステップS101でヘッダの値が「0」ではないと判定したら、処理をステップS105に移行させ、ヘッダに続く8ビットをレングスLengthとして読み込む。読み込んだレングスLengthは、スライド展開部402に供給される。

【0149】

次のステップS106で、符号フォーマット解析部401は、ヘッダの値が「11」であるか否かを判定する。若し、ヘッダの値が「11」であると判定したら、処理をステップS107に移行させ、ヘッダに続く4ビットを変換アドレス値TAddressとして読み込む。一方、ヘッダの値が「11」ではないと判定したら、処理をステップS108に移行させ、ヘッダに続く8ビットを変換アドレス値TAddressとして読み込む。ステップS107またはステップS108で読み込まれた変換アドレス値TAddressは、スライド展開部402に供給される。

【0150】

次のステップS109で、スライド展開部402は、図19に例示した逆変換テーブルDTRANSTABLEを用いて、変換アドレス値TAddressを元のアドレス値Addressに変換する。

【0151】

次のステップS110で、スライド展開部402は、スライド記憶部のアドレス値Addressで示されるスライドに格納されるデータを読み込む。読み込まれたデータは、出力データとして出力される(ステップS111)と共に、スライド展開部402に供給されスライドに追加される(ステップS112)。

【0152】

処理はステップS113に移行され、レングスLengthが「0」より大きいか否かが判定される。若し、レングスLengthが「0」以下であると判定されたら、処理はステップS115に移行される。一方、レングスLengthが「0」より大きいと判定されたら、ステップS114でレングスLengthから「1」が減じられた値が新たなレングスLengthとされて、処理がステップS110に戻される。

【0153】

図21は、デコーダ243の一例の構成をより詳細に示す。なお、図21において、上述の図18と共通する部分には同一の符号を付し、詳細な説明を省略する。デコーダ243は、符号読み込み部400、符号フォーマット解析部401、スライド展開部402およびデータ書き込み部403を有すると共に、メモリコントローラI/F410、符号アドレス生成部411およびデータアドレス生成部412を有する。

【0154】

符号アドレス生成部411は、フラッシュメモリ240から圧縮符号化されたプログラムデータを読み出す際のメモリアドレスを生成する。符号読み込み部400は、符号アドレス生成部411で生成されたメモリアドレスからのデータの読み出しを、メモリコントローラI/F410を介してメモリコントローラ202に対して要求する。この要求に応じてメモリコントローラ202によりフラッシュメモリ240から読み出された、プログラムデータが圧縮符号化された符号データが、メモリコントローラ202からデコーダ243に対して供給され、メモリコントローラI/F410を介して符号読み込み部400に供給される。符号読み込み部400は、この符号データを、符号フォーマット解析部401に供給する。

【0155】

符号フォーマット解析部401は、図4で説明した符号フォーマットに従い、供給された符号データから、ヘッダ、レングスLength、データ値および変換アドレス値TAddressを取り出して、スライド展開部402に供給する。ここで、変換アドレス値TAddressは、逆変換テーブルDTRANSTABLEを用いて元のアドレス値Addressに変換される。スライド展開部402は、このアドレス値Addressと、供給されたデータ値、レングスLengthおよびヘッダに基づき、スライド記憶部における各スライドに対してデータを展開し、符号データを元のプログラムデータに復号する。復号されたプログラムデータは、データ書き込み部403に供給される。

【0156】

データ書き込み部403は、供給されたプログラムデータをメモリコントローラI/F410を介してメモリコントローラ202に供給する。それと共に、データ書き込み部403は、当該プログラムデータをデータアドレス生成部412で生成されたメモリアドレスに従いメインメモリ210のプログラム領域210Aに書き込むように、メモリコントローラI/F310を介してメモリコントローラ202に要求する。メモリコントローラ202は、この要求に従い、供給されたプログラムデータを、メインメモリ210のプログラム領域210Aに書き込む。

【0157】

<スライド展開部のハードウェア構成>

図22は、スライド展開部402の一例のハードウェア構成を示す。スライド展開部402は、スライド記憶部500、コントローラ501、セレクタ502および503、ならびに、アドレス逆変換部520を有する。アドレス逆変換部520は、上述した逆変換テーブルDTRANSTABLEを有し、符号フォーマット解析部401から供給された変換アドレス値TAddressを逆変換テーブルDTRANSTABLEを用いて元のアドレス値Addressに変換して、コントローラ501に渡す。

【0158】

コントローラ501は、例えばマイクロプロセッサからなり、アドレス値Address、レングスLengthおよび一致フラグFLAGが供給され、供給されたこれらのデータに基づきこのスライド展開部402の全体の動作を制御する。例えばコントローラ501は、スライド記憶部500におけるデータ値のスライドに対する追加処理や、セレクタ502および503の動作などを制御する。

【0159】

スライド記憶部500は、各々がレジスタからなり、それぞれ1単位のデータが格納されるn個のスライド5111、5112、…、511nが直列に接続されて構成されたFIFOと、当該FIFOの先頭に接続されるセレクタ510とを有する。

【0160】

各スライド5101、5102、…、510nの出力は、さらに、それぞれセレクタ502に供給される。セレクタ502の出力は、セレクタ503に供給されると共に、セレクタ510にも供給される。

【0161】

符号フォーマット解析部401から読み込まれたデータ値がセレクタ510に供給されると共に、セレクタ503にも供給される。セレクタ510は、図13のステップS104のスライド追加処理時には、入力されたデータ値をスライド5111に追加する。また、図13のステップS108のスライド追加処理時には、ステップS106においてスライド符号のアドレス値Addressに基づき選択されたスライドから出力されたデータを、スライド5111に追加する。

【0162】

セレクタ502は、図13のステップS106の処理時に、コントローラ501から供給されるアドレス値Addressに従い、スライド記憶部500の各スライド5111、5112、…、511nの出力からスライド511Addressの出力を選択し、選択した出力を、セレクタ503および510にそれぞれ供給する。

【0163】

セレクタ503は、図13のステップS103において、ステップS102で読み込まれたデータ値を出力する。また、図13のステップS107のデータ出力処理時に、セレクタ502から供給されたデータを出力する。

【0164】

なお、デコーダ243の構成は、図22に示した構成に限定されない。すなわち、レングスLengthおよびアドレス値Addressに基づきLZ77符号の復号を行うものであれば、他の構成のデコーダを適用することができる。

【0165】

また、上述では、本発明がプリンタ装置に適用されるように説明したが、これは一例でありこの例に限定されない。すなわち、本発明は、マシン語のプログラムデータの可逆符号化をハードウェアを用いて行う他の装置にも適用することが可能である。

【符号の説明】

【0166】

100 スライド探索部

101 スライド記憶部

102 リスト探索部

103 コントローラ

110,134 論理和回路

1111〜111n,1301〜130n 比較器

1201〜120n スライド

1311〜131n セレクタ

1321〜132n レジスタ

133 アドレス値生成部

144 アドレス変換部

200 プリンタ装置

210 メインメモリ

210A プログラム領域

240 フラッシュメモリ

242 エンコーダ

243 デコーダ

301 スライド/リスト生成処理部

402 スライド展開部

500 スライド記憶部

501 コントローラ

502,503,510 セレクタ

5111〜511n スライド

520 アドレス逆変換部

【先行技術文献】

【特許文献】

【0167】

【特許文献1】特開平7−319743号公報

【特許文献2】特開2004−178289号公報

【特許請求の範囲】

【請求項1】

入力データを順次記憶するスライド記憶手段と、

連続的に入力された前記入力データからなる入力データ列と一致する、前記スライド記憶手段に記憶されるデータ列を探索する探索手段と、

前記探索手段で探索された前記データ列から1を選択して、選択された該データ列の長さを求めてレングス値を生成するレングス生成手段と、

前記レングス生成手段で前記レングス値を生成するために用いた前記データ列における開始データの、前記スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成手段と、

前記アドレス値の出現頻度に従い、該アドレス値生成手段で生成された前記アドレス値のうち、該出現頻度が高い該アドレス値から所定数の該アドレス値を、予め定められた値以下の変換アドレス値に変換する変換手段と、

前記レングス値と前記変換アドレス値とを符号化する符号化手段と

を有する

ことを特徴とするデータ処理装置。

【請求項2】

前記変換手段は、

前記アドレス値生成手段で生成された前記アドレス値のうち、該アドレス値の所定単位毎の前記出現頻度が高い該アドレス値から所定数の該アドレス値を、予め定められた値以下の変換アドレス値に変換する

ことを特徴とする請求項1に記載のデータ処理装置。

【請求項3】

前記変換手段は、

前記アドレス値生成手段で生成された前記アドレス値のうち、前記所定単位毎の出現頻度を除外した全体の前記出現頻度が高い側のアドレス値を前記所定数のアドレス値に含めて、該所定数のアドレス値を予め定められた値以下の変換アドレス値に変換する

ことを特徴とする請求項2に記載のデータ処理装置。

【請求項4】

前記所定単位は4バイトである

ことを特徴とする請求項2または請求項3に記載のデータ処理装置。

【請求項5】

前記データは、マシン語によるプログラムデータである

ことを特徴とする請求項1乃至請求項4の何れか1項に記載のデータ処理装置。

【請求項6】

スライド記憶手段が、入力データを順次記憶するスライド記憶ステップと、

探索手段が、連続的に入力された前記入力データからなる入力データ列と一致する、前記スライド記憶手段に記憶されるデータ列を探索する探索ステップと、

レングス生成手段が、前記探索ステップで探索された前記データ列から1を選択して、選択された該データ列の長さを求めてレングス値を生成するレングス生成ステップと、

アドレス値生成手段が、前記レングス生成ステップで前記レングス値を生成するために用いた前記データ列における開始データの、前記スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成ステップと、

変換手段が、前記アドレス値の出現頻度に従い、該アドレス値生成ステップで生成された前記アドレス値のうち、該出現頻度が高い該アドレス値から所定数の該アドレス値を、予め定められた値以下の変換アドレス値に変換する変換ステップと、

符号化手段が、前記レングス値と前記変換アドレス値とを符号化する符号化ステップと

を有する

ことを特徴とするデータ処理方法。

【請求項1】

入力データを順次記憶するスライド記憶手段と、

連続的に入力された前記入力データからなる入力データ列と一致する、前記スライド記憶手段に記憶されるデータ列を探索する探索手段と、

前記探索手段で探索された前記データ列から1を選択して、選択された該データ列の長さを求めてレングス値を生成するレングス生成手段と、

前記レングス生成手段で前記レングス値を生成するために用いた前記データ列における開始データの、前記スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成手段と、

前記アドレス値の出現頻度に従い、該アドレス値生成手段で生成された前記アドレス値のうち、該出現頻度が高い該アドレス値から所定数の該アドレス値を、予め定められた値以下の変換アドレス値に変換する変換手段と、

前記レングス値と前記変換アドレス値とを符号化する符号化手段と

を有する

ことを特徴とするデータ処理装置。

【請求項2】

前記変換手段は、

前記アドレス値生成手段で生成された前記アドレス値のうち、該アドレス値の所定単位毎の前記出現頻度が高い該アドレス値から所定数の該アドレス値を、予め定められた値以下の変換アドレス値に変換する

ことを特徴とする請求項1に記載のデータ処理装置。

【請求項3】

前記変換手段は、

前記アドレス値生成手段で生成された前記アドレス値のうち、前記所定単位毎の出現頻度を除外した全体の前記出現頻度が高い側のアドレス値を前記所定数のアドレス値に含めて、該所定数のアドレス値を予め定められた値以下の変換アドレス値に変換する

ことを特徴とする請求項2に記載のデータ処理装置。

【請求項4】

前記所定単位は4バイトである

ことを特徴とする請求項2または請求項3に記載のデータ処理装置。

【請求項5】

前記データは、マシン語によるプログラムデータである

ことを特徴とする請求項1乃至請求項4の何れか1項に記載のデータ処理装置。

【請求項6】

スライド記憶手段が、入力データを順次記憶するスライド記憶ステップと、

探索手段が、連続的に入力された前記入力データからなる入力データ列と一致する、前記スライド記憶手段に記憶されるデータ列を探索する探索ステップと、

レングス生成手段が、前記探索ステップで探索された前記データ列から1を選択して、選択された該データ列の長さを求めてレングス値を生成するレングス生成ステップと、

アドレス値生成手段が、前記レングス生成ステップで前記レングス値を生成するために用いた前記データ列における開始データの、前記スライド記憶手段内での位置を求めアドレス値を生成するアドレス値生成ステップと、

変換手段が、前記アドレス値の出現頻度に従い、該アドレス値生成ステップで生成された前記アドレス値のうち、該出現頻度が高い該アドレス値から所定数の該アドレス値を、予め定められた値以下の変換アドレス値に変換する変換ステップと、

符号化手段が、前記レングス値と前記変換アドレス値とを符号化する符号化ステップと

を有する

ことを特徴とするデータ処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2011−193406(P2011−193406A)

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願番号】特願2010−60008(P2010−60008)

【出願日】平成22年3月16日(2010.3.16)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願日】平成22年3月16日(2010.3.16)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]