データ処理装置

【課題】イベントに対応して待機状態から起動状態に移行するときの消費電力を低減することができるデータ処理装置を提供する。

【解決手段】周辺デバイス20はロジック電源部13の状態移行に関係なく処理データを出力することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰して無駄な電力の消費を低減することができる。

【解決手段】周辺デバイス20はロジック電源部13の状態移行に関係なく処理データを出力することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰して無駄な電力の消費を低減することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、イベントに対応して待機状態から起動状態に移行するデータ処理装置に関する。

【背景技術】

【0002】

データ処理装置であるモバイル機器に要求される性能は、日々高まっている。高速性能を出すには、CPU(Central Processing Unit)を高い周波数で動かす必要があり、それだけ電力を消費することとなる。

【0003】

また、高速性能を出すには、プロセスの進んだ半導体を用いる必要があり、よりプロセスの進んだ半導体を使うことで、リーク電流が増加することとなる。限られた電池で、長時間使用することを要求されているモバイル機器では、高速動作電流、リーク電流を減らすことが必須となる。

【0004】

そのリーク電流を抑えるため、現在の技術では、CPU、およびその周辺ロジック回路の電源を落とし、リーク電流が流れないような対策がとられている。しかし、リーク電流対策のため、電源を落とし、クロックも停止しているため、周辺モジュールからの割り込みを受けて、通常動作に復帰するまでに、長い時間を要するようになってきている。

【0005】

例えば、たかだか数Byteのデータをやり取りするのに、電源やクロックが供給されていれば50usの時間で済むところ、CPUの源振である水晶振動子の発振安定待ちをし、CPU、ロジック回路部分の電源復帰、その安定待ちをし、電源を落としてあった部分の回路の初期化、レジスタの書き戻し等に、数msの時間を要するようになってきている。

【0006】

発振安定待ちの速い回路(PLL(Phase Locked Loop)含む)、電圧が速く立ち上がる電源が開発され、システムCPU内部のレジスタ復帰等もハードウェア化されて、高速復帰が可能になってきているが、それでも、システムCPUのWakeupには、実際のアクセスに必要な時間の100倍はかかっているのが状況である。

【0007】

また、モバイル機器は、使用している時間よりも、何も動かさずただ持ち歩いている状態が多い。このような状態でも、メール着信などがあるため、電源を完全に落とすことはできない。このような持ち歩き状態では、CPUの動作電流ではなく、リーク電流がもっとも電池消費に影響を与える。

【0008】

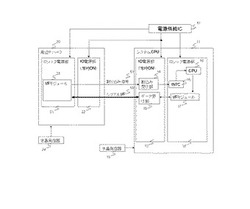

ここで、従来のモバイル機器の、システムCPU11と、周辺デバイス20の主な構成を、図6ないし図8を参照して以下に説明する。システムCPU11は、水晶発振器18を持ち、システムCPU11が動くのに必要なクロックを、この水晶発振器18から得ている。

【0009】

周辺デバイス20も同様に、水晶発振器24を持っており、システムCPU11とは非同期に動作可能である。水晶発振器が、周辺デバイス20や、システムCPU11に内蔵されており、水晶振動子が付属していることも多いが特に違いは無いので、ここでは代表して水晶発振器とする。

【0010】

周辺デバイス20と、システムCPU11は、IO(Input/Output)が接続されているので、周辺デバイス20のIO電源部22、システムCPU11のIO電源部12の共通のIO電源として、電源供給IC10を持っていることが多く、その電源供給IC10が、周辺デバイス20のロジック電源部21と、システムCPU11のロジック電源部13を共有しているのが普通である。電源構成についても、各機器の都合により変更されるものであり、特に本構成である必要性は無い。

【0011】

周辺デバイス20は、システムCPU11と通信するためのI/F(Interface)モジュール23を、ロジック電源部21内に持ち、システムCPU11側も、同様のI/Fモジュール17を、ロジック電源部13内に持つ。二つのI/Fモジュール17,23は、シリアルI/F60で接続される。

【0012】

周辺デバイス20のI/Fモジュール23は、システムCPU11に対して割り込み信号61を発生する機能を持ち、その割り込み信号61は、割り込み信号ラインを伝わって、システムCPU11のIO電源部12内の割り込み受け部14に伝わる。割り込み受け部14に割り込みが通知されたことで、ロジック電源部13は、Wakeup動作を開始する。

【0013】

Wakeupが完了すると、割り込み受け部14から、割り込みコントローラ(INTC)15に割り込みが伝わり、CPU16に割り込みが通知される。CPU16は、割り込みを受けて、I/Fモジュール17に命令し、割り込み要因の確認とデータの送受信を行う。

【0014】

つぎに、上述のような構成の従来のモバイル機器における省電力状態からの復帰動作について、図4と図7と図8を参照して以下に説明する。まず、周辺デバイス20で、何らかのイベントが発生した場合(S11)、周辺デバイス20は、ロジック電源部21の電源をオンする(40)。

【0015】

その後、イベントの内容を解読し、CPUに割り込みを通知する(S12,41)。割り込みは、IO(Input/Output)電源部12の割り込み受け部14で検出される(42)。割り込みを受けた割り込み受け部14は、システムCPU11に対して、Wakeup指示を出す。

【0016】

これを受けたCPU16は、Wakeup動作を開始する(S13,43)。この間、周辺デバイス20は、システムCPU11のWakeupが完了するまで待ち状態となる。

【0017】

システムCPU11のWakeup完了後、データの送受信が行われる(S14,45,50)。データ送受信完了後、システムCPU11は、周辺デバイス20の電源を落とし(S15,49)、その後自らも省電力状態に遷移する(S16,47)。

【0018】

現在、上述のようなモバイル機器として各種の提案がある(特許文献1、2)。

【先行技術文献】

【特許文献】

【0019】

【特許文献1】特開2008−181329号公報

【特許文献2】特開平07−028660号公報

【発明の概要】

【発明が解決しようとする課題】

【0020】

しかし、上述のようなモバイル機器には以下のような課題がある。まず、第1の課題は、周辺デバイス20からシステムCPU11に割り込みを通知し、必要なデータのやり取りをしようとしても、システムCPU11がすぐに応答できる状態にならないことである。

【0021】

第2の課題は、第1の課題で、システムCPU11の応答を待っている間、周辺デバイス20には電源がかかっており、無駄な電力が消費されていることである。第3の課題は、第2の課題で、周辺デバイス20に電源がかかっている時間が長くなり、周辺デバイス20の動作率が高いことで、電池消費率が高いことである。

【0022】

本発明は上述のような課題に鑑みてなされたものであり、イベントに対応して待機状態から起動状態に移行するときに消費する無駄な電力を低減することができるデータ処理装置を提供するものである。

【課題を解決するための手段】

【0023】

本発明のデータ処理装置は、イベントに対応して待機状態から起動状態に移行するとともに処理データと割り込み信号とを出力する周辺デバイスと、割り込み信号に対応して待機状態から起動状態に移行するとともに処理データに対応して動作するロジック電源部と、システムCPUの常時電源オン状態であるIO電源部と、IO電源部に形成されて常時電源オン状態であり処理データを保持して起動状態に移行したロジック電源部に転送するデータ受け部と、を有する。

【0024】

従って、本発明のデータ処理装置では、周辺デバイスはロジック電源部の状態移行に関係なく処理データの出力を完了することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰することができる。

【発明の効果】

【0025】

本発明のデータ処理装置では、周辺デバイスはロジック電源部の状態移行に関係なく処理データを出力することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰して無駄な電力の消費を低減することができる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施の形態のデータ処理装置であるモバイル機器の回路構造を示すブロック図である。

【図2】モバイル機器のデータ受け部の回路構造を示すブロック図である。

【図3】データ受け部の動作を示す模式的なタイムチャートである。

【図4】モバイル機器の動作を示す模式的なタイムチャートである。

【図5】モバイル機器の動作を示す模式的なフローチャートである。

【図6】一従来例のモバイル機器の回路構造を示すブロック図である。

【図7】モバイル機器の動作を示す模式的なタイムチャートである。

【図8】モバイル機器の動作を示す模式的なフローチャートである。

【発明を実施するための形態】

【0027】

本発明の実施の一形態を図面を参照して以下に説明する。ただし、本実施の形態に関して前述した一従来例と同一の部分は、同一の名称および符号を使用して詳細な説明は省略する。

【0028】

本実施の形態のデータ処理装置であるモバイル機器は、図1に示すように、イベントに対応して待機状態から起動状態に移行するとともに処理データと割り込み信号61とを出力する周辺デバイス20と、割り込み信号61に対応して待機状態から起動状態に移行するとともに処理データに対応して動作するロジック電源部13と、システムCPUの常時電源オン状態であるIO電源部12と、IO電源部12に形成されて常時電源オン状態であり処理データを保持して起動状態に移行したロジック電源部13に転送するデータ受け部19と、を有する。

【0029】

データ受け部19は、図2に示すように、周辺デバイス20から供給されるクロック63で動作して取得する処理データを蓄積するシフトレジスタ70と、シフトレジスタ70に蓄積された処理データをロジック電源部13から起動完了通知を受信すると出力するFIFO72と、を有する。

【0030】

なお、周辺デバイス20は、処理データと割り込み信号61とを出力すると起動状態から待機状態に復帰する。同様に、ロジック電源部13は、処理データに対応して動作すると起動状態から待機状態に復帰する。本実施の形態のモバイル機器は、バッテリ(図示せず)から供給される電力で各部が作動する。

【0031】

より具体的には、本実施の形態のモバイル機器は、基本的な構成は従来のモバイル機器(図6)と同じであるが、上述のようにシステムCPU11の常時電源オン状態であるIO電源部12に、データ受け部19を持っている。

【0032】

データ受け部19には、データ64を受け取るシフトレジスタ70があり、周辺デバイス20から供給されるクロック63にて動作する。また、シフトレジスタ70に1データ分のデータが溜まったら、それを、FIFO72に移動する構成とする。

【0033】

システムCPU11から、Wakeup完了通知74が来ると、それに応答する形で、FIFO72から、データ73を吐き出す。シフトレジスタ70、FIFO72は、チップセレクト62がイネーブルのときのみ有効となるようデータ受け部制御回路71にて制御される。

【0034】

周辺デバイス20とシステムCPU11が一対一で接続されている場合は、データ受け部19は、自分が選択されているかどうか確認する必要が無くなるので、チップセレクト62は不要となる。

【0035】

本発明では、図2に示すような、シリアルI/F60を用いている。有効データ65は、クロック63に同期して送られ、有効データ65送信前には、受信側の内部同期用に数クロック、有効データ65の後にも、受信側ロジックの後処理用に数クロック分のクロックが付加された波形とする。また、有効データ65、およびクロック63の出力されている間は、チップセレクト62は、有効な状態としておく必要がある。

【0036】

つぎに、図4および図5を参照して、本実施の形態のモバイル機器の動作について説明する。まず、周辺デバイス20で、何らかのイベントが発生した場合(S21,40)、周辺デバイス20は、ロジック電源部21の電源をオンする(40)。

【0037】

その後イベントの内容を解読し、CPU16に割り込みを通知する(S22,41)。割り込みは、IO電源部12の割り込み受け部で検出される(42)。割り込みを受けた割り込み受け部14は、システムCPU11に対して、Wakeup指示を出す。

【0038】

これを受けたCPU16は、Wakeup動作を開始する(S25,43)。この間、周辺デバイス20が、システムCPU11のWakeupが完了するのを待っているのは動作率の悪化となるので、周辺デバイス20は、割り込みに続いて、当該割り込み発生の際、通常CPUから読み出されるであろう値を、システムCPU11に送信し(S23,45)、送信が完了したら、自らの電源をOFFする(S24,49)。

【0039】

システムCPU11は、Wakeup完了後、割り込み内容から、データ受け部19にデータが入っていることを知り、データ受け部から必要なデータを受信する(S26,46)。

【0040】

図2に示すように、データ受け部19は、なるべく簡単な構成にすることが望ましい。システムCPU11は、待機中の待ち受け電流(半導体のリーク電流)を減らすため、なるべく多くの半導体回路をロジック電源部13に持っている。

【0041】

そのため、データ受け部19は、簡単な回路とし、システムCPU11のWakeupが完了したのと同時に(74)、I/Fモジュール17にデータを移動するだけの簡素な回路とする。データ送受信完了後、システムCPU11は、省電力状態に復帰する(S27,47)。

【0042】

本実施の形態のモバイル機器では、上述のようにシステムCPU11のIO電源部(常時電源オン)12に、周辺デバイス20側がマスターで、システムCPU11側がスレーブとなるような、シリアルI/F60の受信バッファを設けることで、周辺デバイス20は、システムCPU11のWakeupを待たず、必要なデータをシステムCPU11に渡して、先に省電力状態に戻ることでき、無駄なリーク電流を発生させないようにすることで、問題を解決している。

【0043】

なお、本発明は本実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で各種の変形を許容する。例えば、上記形態では周辺デバイス20とシステムCPU11とがシリアルI/F60で接続されていることを例示した。しかし、これはNOR LikeのメモリバスやDDR(Double Data Rate)バスなど、クロック同期で動くバスであれば対応可能である。

【0044】

なお、当然ながら、上述した実施の形態および複数の変形例は、その内容が相反しない範囲で組み合わせることができる。また、上述した実施の形態および変形例では、各部の構造などを具体的に説明したが、その構造などは本願発明を満足する範囲で各種に変更することができる。

【符号の説明】

【0045】

10 電源供給IC

11 システムCPU

12 IO電源部

13 ロジック電源部

14 割り込み受け部

17 I/Fモジュール

18 水晶発振器

19 データ受け部

20 周辺デバイス

21 ロジック電源部

22 IO電源部

23 I/Fモジュール

24 水晶発振器

60 シリアルI/F

61 割り込み信号

62 チップセレクト

63 クロック

64 データ

65 有効データ

70 シフトレジスタ

71 データ受け部制御回路

73 データ

74 Wakeup完了通知

【技術分野】

【0001】

本発明は、イベントに対応して待機状態から起動状態に移行するデータ処理装置に関する。

【背景技術】

【0002】

データ処理装置であるモバイル機器に要求される性能は、日々高まっている。高速性能を出すには、CPU(Central Processing Unit)を高い周波数で動かす必要があり、それだけ電力を消費することとなる。

【0003】

また、高速性能を出すには、プロセスの進んだ半導体を用いる必要があり、よりプロセスの進んだ半導体を使うことで、リーク電流が増加することとなる。限られた電池で、長時間使用することを要求されているモバイル機器では、高速動作電流、リーク電流を減らすことが必須となる。

【0004】

そのリーク電流を抑えるため、現在の技術では、CPU、およびその周辺ロジック回路の電源を落とし、リーク電流が流れないような対策がとられている。しかし、リーク電流対策のため、電源を落とし、クロックも停止しているため、周辺モジュールからの割り込みを受けて、通常動作に復帰するまでに、長い時間を要するようになってきている。

【0005】

例えば、たかだか数Byteのデータをやり取りするのに、電源やクロックが供給されていれば50usの時間で済むところ、CPUの源振である水晶振動子の発振安定待ちをし、CPU、ロジック回路部分の電源復帰、その安定待ちをし、電源を落としてあった部分の回路の初期化、レジスタの書き戻し等に、数msの時間を要するようになってきている。

【0006】

発振安定待ちの速い回路(PLL(Phase Locked Loop)含む)、電圧が速く立ち上がる電源が開発され、システムCPU内部のレジスタ復帰等もハードウェア化されて、高速復帰が可能になってきているが、それでも、システムCPUのWakeupには、実際のアクセスに必要な時間の100倍はかかっているのが状況である。

【0007】

また、モバイル機器は、使用している時間よりも、何も動かさずただ持ち歩いている状態が多い。このような状態でも、メール着信などがあるため、電源を完全に落とすことはできない。このような持ち歩き状態では、CPUの動作電流ではなく、リーク電流がもっとも電池消費に影響を与える。

【0008】

ここで、従来のモバイル機器の、システムCPU11と、周辺デバイス20の主な構成を、図6ないし図8を参照して以下に説明する。システムCPU11は、水晶発振器18を持ち、システムCPU11が動くのに必要なクロックを、この水晶発振器18から得ている。

【0009】

周辺デバイス20も同様に、水晶発振器24を持っており、システムCPU11とは非同期に動作可能である。水晶発振器が、周辺デバイス20や、システムCPU11に内蔵されており、水晶振動子が付属していることも多いが特に違いは無いので、ここでは代表して水晶発振器とする。

【0010】

周辺デバイス20と、システムCPU11は、IO(Input/Output)が接続されているので、周辺デバイス20のIO電源部22、システムCPU11のIO電源部12の共通のIO電源として、電源供給IC10を持っていることが多く、その電源供給IC10が、周辺デバイス20のロジック電源部21と、システムCPU11のロジック電源部13を共有しているのが普通である。電源構成についても、各機器の都合により変更されるものであり、特に本構成である必要性は無い。

【0011】

周辺デバイス20は、システムCPU11と通信するためのI/F(Interface)モジュール23を、ロジック電源部21内に持ち、システムCPU11側も、同様のI/Fモジュール17を、ロジック電源部13内に持つ。二つのI/Fモジュール17,23は、シリアルI/F60で接続される。

【0012】

周辺デバイス20のI/Fモジュール23は、システムCPU11に対して割り込み信号61を発生する機能を持ち、その割り込み信号61は、割り込み信号ラインを伝わって、システムCPU11のIO電源部12内の割り込み受け部14に伝わる。割り込み受け部14に割り込みが通知されたことで、ロジック電源部13は、Wakeup動作を開始する。

【0013】

Wakeupが完了すると、割り込み受け部14から、割り込みコントローラ(INTC)15に割り込みが伝わり、CPU16に割り込みが通知される。CPU16は、割り込みを受けて、I/Fモジュール17に命令し、割り込み要因の確認とデータの送受信を行う。

【0014】

つぎに、上述のような構成の従来のモバイル機器における省電力状態からの復帰動作について、図4と図7と図8を参照して以下に説明する。まず、周辺デバイス20で、何らかのイベントが発生した場合(S11)、周辺デバイス20は、ロジック電源部21の電源をオンする(40)。

【0015】

その後、イベントの内容を解読し、CPUに割り込みを通知する(S12,41)。割り込みは、IO(Input/Output)電源部12の割り込み受け部14で検出される(42)。割り込みを受けた割り込み受け部14は、システムCPU11に対して、Wakeup指示を出す。

【0016】

これを受けたCPU16は、Wakeup動作を開始する(S13,43)。この間、周辺デバイス20は、システムCPU11のWakeupが完了するまで待ち状態となる。

【0017】

システムCPU11のWakeup完了後、データの送受信が行われる(S14,45,50)。データ送受信完了後、システムCPU11は、周辺デバイス20の電源を落とし(S15,49)、その後自らも省電力状態に遷移する(S16,47)。

【0018】

現在、上述のようなモバイル機器として各種の提案がある(特許文献1、2)。

【先行技術文献】

【特許文献】

【0019】

【特許文献1】特開2008−181329号公報

【特許文献2】特開平07−028660号公報

【発明の概要】

【発明が解決しようとする課題】

【0020】

しかし、上述のようなモバイル機器には以下のような課題がある。まず、第1の課題は、周辺デバイス20からシステムCPU11に割り込みを通知し、必要なデータのやり取りをしようとしても、システムCPU11がすぐに応答できる状態にならないことである。

【0021】

第2の課題は、第1の課題で、システムCPU11の応答を待っている間、周辺デバイス20には電源がかかっており、無駄な電力が消費されていることである。第3の課題は、第2の課題で、周辺デバイス20に電源がかかっている時間が長くなり、周辺デバイス20の動作率が高いことで、電池消費率が高いことである。

【0022】

本発明は上述のような課題に鑑みてなされたものであり、イベントに対応して待機状態から起動状態に移行するときに消費する無駄な電力を低減することができるデータ処理装置を提供するものである。

【課題を解決するための手段】

【0023】

本発明のデータ処理装置は、イベントに対応して待機状態から起動状態に移行するとともに処理データと割り込み信号とを出力する周辺デバイスと、割り込み信号に対応して待機状態から起動状態に移行するとともに処理データに対応して動作するロジック電源部と、システムCPUの常時電源オン状態であるIO電源部と、IO電源部に形成されて常時電源オン状態であり処理データを保持して起動状態に移行したロジック電源部に転送するデータ受け部と、を有する。

【0024】

従って、本発明のデータ処理装置では、周辺デバイスはロジック電源部の状態移行に関係なく処理データの出力を完了することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰することができる。

【発明の効果】

【0025】

本発明のデータ処理装置では、周辺デバイスはロジック電源部の状態移行に関係なく処理データを出力することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰して無駄な電力の消費を低減することができる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施の形態のデータ処理装置であるモバイル機器の回路構造を示すブロック図である。

【図2】モバイル機器のデータ受け部の回路構造を示すブロック図である。

【図3】データ受け部の動作を示す模式的なタイムチャートである。

【図4】モバイル機器の動作を示す模式的なタイムチャートである。

【図5】モバイル機器の動作を示す模式的なフローチャートである。

【図6】一従来例のモバイル機器の回路構造を示すブロック図である。

【図7】モバイル機器の動作を示す模式的なタイムチャートである。

【図8】モバイル機器の動作を示す模式的なフローチャートである。

【発明を実施するための形態】

【0027】

本発明の実施の一形態を図面を参照して以下に説明する。ただし、本実施の形態に関して前述した一従来例と同一の部分は、同一の名称および符号を使用して詳細な説明は省略する。

【0028】

本実施の形態のデータ処理装置であるモバイル機器は、図1に示すように、イベントに対応して待機状態から起動状態に移行するとともに処理データと割り込み信号61とを出力する周辺デバイス20と、割り込み信号61に対応して待機状態から起動状態に移行するとともに処理データに対応して動作するロジック電源部13と、システムCPUの常時電源オン状態であるIO電源部12と、IO電源部12に形成されて常時電源オン状態であり処理データを保持して起動状態に移行したロジック電源部13に転送するデータ受け部19と、を有する。

【0029】

データ受け部19は、図2に示すように、周辺デバイス20から供給されるクロック63で動作して取得する処理データを蓄積するシフトレジスタ70と、シフトレジスタ70に蓄積された処理データをロジック電源部13から起動完了通知を受信すると出力するFIFO72と、を有する。

【0030】

なお、周辺デバイス20は、処理データと割り込み信号61とを出力すると起動状態から待機状態に復帰する。同様に、ロジック電源部13は、処理データに対応して動作すると起動状態から待機状態に復帰する。本実施の形態のモバイル機器は、バッテリ(図示せず)から供給される電力で各部が作動する。

【0031】

より具体的には、本実施の形態のモバイル機器は、基本的な構成は従来のモバイル機器(図6)と同じであるが、上述のようにシステムCPU11の常時電源オン状態であるIO電源部12に、データ受け部19を持っている。

【0032】

データ受け部19には、データ64を受け取るシフトレジスタ70があり、周辺デバイス20から供給されるクロック63にて動作する。また、シフトレジスタ70に1データ分のデータが溜まったら、それを、FIFO72に移動する構成とする。

【0033】

システムCPU11から、Wakeup完了通知74が来ると、それに応答する形で、FIFO72から、データ73を吐き出す。シフトレジスタ70、FIFO72は、チップセレクト62がイネーブルのときのみ有効となるようデータ受け部制御回路71にて制御される。

【0034】

周辺デバイス20とシステムCPU11が一対一で接続されている場合は、データ受け部19は、自分が選択されているかどうか確認する必要が無くなるので、チップセレクト62は不要となる。

【0035】

本発明では、図2に示すような、シリアルI/F60を用いている。有効データ65は、クロック63に同期して送られ、有効データ65送信前には、受信側の内部同期用に数クロック、有効データ65の後にも、受信側ロジックの後処理用に数クロック分のクロックが付加された波形とする。また、有効データ65、およびクロック63の出力されている間は、チップセレクト62は、有効な状態としておく必要がある。

【0036】

つぎに、図4および図5を参照して、本実施の形態のモバイル機器の動作について説明する。まず、周辺デバイス20で、何らかのイベントが発生した場合(S21,40)、周辺デバイス20は、ロジック電源部21の電源をオンする(40)。

【0037】

その後イベントの内容を解読し、CPU16に割り込みを通知する(S22,41)。割り込みは、IO電源部12の割り込み受け部で検出される(42)。割り込みを受けた割り込み受け部14は、システムCPU11に対して、Wakeup指示を出す。

【0038】

これを受けたCPU16は、Wakeup動作を開始する(S25,43)。この間、周辺デバイス20が、システムCPU11のWakeupが完了するのを待っているのは動作率の悪化となるので、周辺デバイス20は、割り込みに続いて、当該割り込み発生の際、通常CPUから読み出されるであろう値を、システムCPU11に送信し(S23,45)、送信が完了したら、自らの電源をOFFする(S24,49)。

【0039】

システムCPU11は、Wakeup完了後、割り込み内容から、データ受け部19にデータが入っていることを知り、データ受け部から必要なデータを受信する(S26,46)。

【0040】

図2に示すように、データ受け部19は、なるべく簡単な構成にすることが望ましい。システムCPU11は、待機中の待ち受け電流(半導体のリーク電流)を減らすため、なるべく多くの半導体回路をロジック電源部13に持っている。

【0041】

そのため、データ受け部19は、簡単な回路とし、システムCPU11のWakeupが完了したのと同時に(74)、I/Fモジュール17にデータを移動するだけの簡素な回路とする。データ送受信完了後、システムCPU11は、省電力状態に復帰する(S27,47)。

【0042】

本実施の形態のモバイル機器では、上述のようにシステムCPU11のIO電源部(常時電源オン)12に、周辺デバイス20側がマスターで、システムCPU11側がスレーブとなるような、シリアルI/F60の受信バッファを設けることで、周辺デバイス20は、システムCPU11のWakeupを待たず、必要なデータをシステムCPU11に渡して、先に省電力状態に戻ることでき、無駄なリーク電流を発生させないようにすることで、問題を解決している。

【0043】

なお、本発明は本実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で各種の変形を許容する。例えば、上記形態では周辺デバイス20とシステムCPU11とがシリアルI/F60で接続されていることを例示した。しかし、これはNOR LikeのメモリバスやDDR(Double Data Rate)バスなど、クロック同期で動くバスであれば対応可能である。

【0044】

なお、当然ながら、上述した実施の形態および複数の変形例は、その内容が相反しない範囲で組み合わせることができる。また、上述した実施の形態および変形例では、各部の構造などを具体的に説明したが、その構造などは本願発明を満足する範囲で各種に変更することができる。

【符号の説明】

【0045】

10 電源供給IC

11 システムCPU

12 IO電源部

13 ロジック電源部

14 割り込み受け部

17 I/Fモジュール

18 水晶発振器

19 データ受け部

20 周辺デバイス

21 ロジック電源部

22 IO電源部

23 I/Fモジュール

24 水晶発振器

60 シリアルI/F

61 割り込み信号

62 チップセレクト

63 クロック

64 データ

65 有効データ

70 シフトレジスタ

71 データ受け部制御回路

73 データ

74 Wakeup完了通知

【特許請求の範囲】

【請求項1】

イベントに対応して待機状態から起動状態に移行するとともに処理データと割り込み信号とを出力する周辺デバイスと、

前記割り込み信号に対応して前記待機状態から前記起動状態に移行するとともに前記処理データに対応して動作するロジック電源部と、

システムCPU(Central Processing Unit)の常時電源オン状態であるIO(Input/Output)電源部と、

前記IO電源部に形成されて常時電源オン状態であり前記処理データを保持して起動状態に移行した前記ロジック電源部に転送するデータ受け部と、

を有するデータ処理装置。

【請求項2】

前記データ受け部は、前記周辺デバイスから供給されるクロックで動作して取得する前記処理データを蓄積するシフトレジスタと、

前記シフトレジスタに蓄積された前記処理データを前記ロジック電源部から起動完了通知を受信すると出力するFIFO(First In First Out)と、

を有する請求項1に記載のデータ処理装置。

【請求項3】

前記周辺デバイスは、前記処理データと前記割り込み信号とを出力すると前記起動状態から前記待機状態に復帰する請求項1または2に記載のデータ処理装置。

【請求項4】

前記ロジック電源部は、前記処理データに対応して動作すると前記起動状態から前記待機状態に復帰する請求項1ないし3の何れか一項に記載のデータ処理装置。

【請求項5】

バッテリから供給される電力で各部が作動するモバイル機器として形成されている請求項1ないし4の何れか一項に記載のデータ処理装置。

【請求項1】

イベントに対応して待機状態から起動状態に移行するとともに処理データと割り込み信号とを出力する周辺デバイスと、

前記割り込み信号に対応して前記待機状態から前記起動状態に移行するとともに前記処理データに対応して動作するロジック電源部と、

システムCPU(Central Processing Unit)の常時電源オン状態であるIO(Input/Output)電源部と、

前記IO電源部に形成されて常時電源オン状態であり前記処理データを保持して起動状態に移行した前記ロジック電源部に転送するデータ受け部と、

を有するデータ処理装置。

【請求項2】

前記データ受け部は、前記周辺デバイスから供給されるクロックで動作して取得する前記処理データを蓄積するシフトレジスタと、

前記シフトレジスタに蓄積された前記処理データを前記ロジック電源部から起動完了通知を受信すると出力するFIFO(First In First Out)と、

を有する請求項1に記載のデータ処理装置。

【請求項3】

前記周辺デバイスは、前記処理データと前記割り込み信号とを出力すると前記起動状態から前記待機状態に復帰する請求項1または2に記載のデータ処理装置。

【請求項4】

前記ロジック電源部は、前記処理データに対応して動作すると前記起動状態から前記待機状態に復帰する請求項1ないし3の何れか一項に記載のデータ処理装置。

【請求項5】

バッテリから供給される電力で各部が作動するモバイル機器として形成されている請求項1ないし4の何れか一項に記載のデータ処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−190097(P2012−190097A)

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願番号】特願2011−51073(P2011−51073)

【出願日】平成23年3月9日(2011.3.9)

【出願人】(310006855)NECカシオモバイルコミュニケーションズ株式会社 (1,081)

【Fターム(参考)】

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願日】平成23年3月9日(2011.3.9)

【出願人】(310006855)NECカシオモバイルコミュニケーションズ株式会社 (1,081)

【Fターム(参考)】

[ Back to top ]