データ処理装置

【課題】外乱が発生しても正常な演算結果を出力する構成を実現する。

【解決手段】切替部10は、出力タイミングの度にデータKeyとデータDataとを並行して出力する。演算部20は、データKeyとデータDataとを用いた演算を行って、バスデータBus1とBus2とを並行して出力する。比較部30は、同タイミングで入力したバスデータBus1とBus2のデータ値を比較し、データ値が一致する場合は値が“H”の、一致しない場合は値が“L”の信号S1を出力する。切替部10は、出力されたバスデータBus1を入力し、出力タイミングの度に、入力した信号S1の値が“H”であれば、新たに入力したデータKIを新たなデータKeyとして演算部20に出力し、入力したバスデータBus1を新たなデータDataとして出力し、“L”であれば、演算部20に出力済のデータKeyとデータDataとを、再度、演算部20に出力する。

【解決手段】切替部10は、出力タイミングの度にデータKeyとデータDataとを並行して出力する。演算部20は、データKeyとデータDataとを用いた演算を行って、バスデータBus1とBus2とを並行して出力する。比較部30は、同タイミングで入力したバスデータBus1とBus2のデータ値を比較し、データ値が一致する場合は値が“H”の、一致しない場合は値が“L”の信号S1を出力する。切替部10は、出力されたバスデータBus1を入力し、出力タイミングの度に、入力した信号S1の値が“H”であれば、新たに入力したデータKIを新たなデータKeyとして演算部20に出力し、入力したバスデータBus1を新たなデータDataとして出力し、“L”であれば、演算部20に出力済のデータKeyとデータDataとを、再度、演算部20に出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ処理装置に関する。

【背景技術】

【0002】

特許文献1に記載の技術では、論理的にみて同じ暗号関連処理が行われる複数の回路を並列に配置し、各回路での暗号関連処理の結果を比較し、比較結果が異なった場合に、暗号関連処理を停止させることを行っている。

これにより、特許文献1に記載の技術では、電力差分攻撃やフォールト攻撃に耐性を持たせている。

【0003】

また、特許文献2に記載の技術では、データ撹拌部でデータが確定する時間と、鍵スケジュール部で鍵が確定する時間を一致させるための遅延回路を設けることにより、故障発生時にサンプリングされる故障データが複数となるようにしている。

この結果、特許文献2に記載の技術では、フォールト攻撃ができない故障を有するデータを出力させて、これにより、フォールト攻撃に耐性を持たせている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−229485号公報

【特許文献2】特開2010−273161号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1の技術では、論理的にみて同じ回路を並列に配置しているため、回路規模が大きくなるという課題がある。

また、異常時に暗号関連処理が停止するので、外乱により異常が頻発する環境、例えば、宇宙空間における放射線による異常発生の場合、正常な結果が得られるのはごくまれであるという課題がある。

【0006】

また、特許文献2の技術においても、異常時に複数の故障が発生するように遅延回路が設けられ、故障を有するデータを出力しているので、外乱により異常が頻発する環境、例えば、宇宙空間における放射線による異常発生の場合、正常な結果が得られないという課題がある。

【0007】

この発明は上記のような課題を解決することを主な目的としており、簡易な構成により、外乱が発生しても正常な演算結果を出力する構成を実現することを主な目的とする。

【課題を解決するための手段】

【0008】

本発明に係るデータ処理装置は、

繰り返し到来する出力タイミングの度に第1のデータと第2のデータとを並行して出力する切替部と、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いた演算を行って第3のデータと第4のデータを生成し、生成した第3のデータと第4のデータとを並行して出力する演算部と、

前記演算部から出力された第3のデータと第4のデータとを並行して入力し、同じタイミングで入力した第3のデータのデータ値と第4のデータのデータ値とを比較し、第3のデータと第4のデータとの間でデータ値が一致する場合は、前記切替部に一致信号を出力し、第3のデータと第4のデータとの間でデータ値が一致しない場合は、前記切替部に不一致信号を出力する比較部とを有し、

前記切替部は、

前記演算部から第3のデータが出力される度に、出力された第3のデータを入力し、

出力タイミングが到来する度に、到来した出力タイミングにおいて前記比較部から入力した信号が一致信号であるか不一致信号であるかを判断し、

前記比較部から入力した信号が一致信号である場合は、前記演算部に出力済の第1のデータと異なるデータを新たな第1のデータとして前記演算部に出力するとともに、前記演算部から入力した第3のデータを新たな第2のデータとして出力し、

前記比較部から入力した信号が不一致信号である場合は、前記演算部に出力済の第1のデータと第2データとを、再度、前記演算部に出力することを特徴とする。

【発明の効果】

【0009】

本発明によれば、外乱が生じた場合は、出力タイミングが到来した際の第3のデータと第4のデータとの間でデータ値が一致しなくなり、演算部に出力済の第1のデータと第2データとを、再度、演算部に出力するため、出力済の第1のデータと第2データとを用いた演算を演算部に行わせることができ、外乱が発生しても正常な演算結果を出力することができる。

【図面の簡単な説明】

【0010】

【図1】実施の形態1に係るデータ処理装置の機能構成例を示す図。

【図2】実施の形態1に係るデータ処理装置の回路構成例を示す図。

【図3】実施の形態1に係るデータ処理装置における正常時のタイミングチャート図。

【図4】実施の形態1に係るデータ処理装置におけるクロック異常発生時のタイミングチャート図。

【図5】実施の形態1に係るデータ処理装置における誤動作発生時のタイミングチャート図。

【図6】実施の形態2に係るデータ処理装置の回路構成例を示す図。

【図7】実施の形態2に係るデータ処理装置における正常時のタイミングチャート図。

【図8】実施の形態2に係るデータ処理装置におけるクロック異常発生時のタイミングチャート図。

【図9】実施の形態2に係るデータ処理装置における誤動作発生時のタイミングチャート図。

【図10】一般的なデータ処理装置の機能構成例を示す図。

【図11】一般的なデータ処理装置の回路構成例を示す図。

【図12】一般的なデータ処理装置における正常時のタイミングチャート図。

【図13】一般的なデータ処理装置におけるクロック異常発生時のタイミングチャート図。

【図14】確定状態と不確定状態を説明する図。

【発明を実施するための形態】

【0011】

実施の形態1及び実施の形態2では、フォールト攻撃のように異常な外乱が発生しても、正常な演算結果を出力し、また、宇宙空間のように異常な外乱が頻発する環境においても、正常な演算結果を出力するデータ処理装置を説明する。

【0012】

以下では、まず、一般的なデータ処理装置を説明し、その後、実施の形態1及び実施の形態2に係るデータ処理装置を説明する。

【0013】

実施の形態1.

図10は、一般的なデータ処理装置の構成図である。

一般的なデータ処理装置は、被演算データを切り替える切替器100、演算を行う演算器200、最終演算結果を出力する出力器400とで構成される。

切替器100は、入力データKI、入力データDI、バスデータBus1を、クロックCKのタイミングで切り替えて、データData、データKeyを出力する。

演算器200はデータData、データKeyを受けて、演算を行い、演算結果をバスデータBus1に出力する。

出力器400は、イネーブル信号Eを見て、最終演算結果がバスデータBus1に出力されたことが分かると、クロックCKのタイミングでバスデータBus1を保持して、データDOに出力する。

なお、図10において、太い線の接続線は複数ビットの信号が入出力されることを表し、細い線の接続線は1ビットの信号が入出力されることを表している。

以降で説明する図面においても、太い線の接続線は複数ビットの信号が入出力されることを表し、細い線の接続線は1ビットの信号が入出力されることを表している。

【0014】

このような一般的なデータ処理装置にて、フォールト攻撃を行う場合は、切替器100、演算器200に外乱を与えて、データの一部に故障を誘発させる。

具体的には、一定周期のクロックCKに、異なる周期のクロックを一瞬発生させて、バスデータBus1の切替タイミングを変えることで、データDataの値に故障を誘発させる。

また、レーザーや放射線を演算器200に照射することで、演算ビットの状態を変化させて、故障を誘発させる。

このように、故障を一瞬誘発し、その後は正常なデータで演算を行い、最終結果を故障データとして入手することで、フォールト攻撃は成立する。

図10では図示していないが、切替器100のループ制御や、イネーブル信号Eの生成を行う演算制御部への攻撃は対象外とする。

なぜなら、フォールト攻撃は正常な演算制御の下で、演算データの一部に故障を誘発させることで成り立つ攻撃であるからである。

また、宇宙空間のような外乱が多い環境では、切替器100、演算器200が放射線などにより誤動作して、データが破壊される。

【0015】

図11は一般的な演算装置の回路構成図である。

これを用いて、異常クロックにおけるフォールト攻撃の一例を説明する。

【0016】

図11において、演算回路201は演算を行う組合せ回路である。

フリップフロップ101は、入力データKIをクロックCKのタイミングで保持して、データKeyとして出力するフリップフロップである。

セレクタ103は、入力データDIとバスデータBus1をセレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ102は、セレクタ103の出力をクロックCKのタイミングで保持し、データDataとして出力するフリップフロップである。

イネーブル付フリップフロップ401は、イネーブル信号Eを判断し、クロックCKのタイミングでバスデータBus1を保持するイネーブル付フリップフロップである。

図10との対応は、フリップフロップ101、フリップフロップ102、セレクタ103が切替器100に、演算回路201が演算器200に、イネーブル付フリップフロップ401が出力器400に相当する。

【0017】

次に正常な動作について、図12を用いて説明する。

図12は、図11の回路に正常なクロックCKが入力されたときのタイミングチャートである。

【0018】

入力データKIは、クロックCKに同期して、図に示すように、<K1>、<K2>、・・・、<Kn−1>と入力されるデータである。

入力データKIの生成回路は図11には図示されていない。

入力データDIは、<K1>と同じタイミングで<D1>が入力される。

その他のタイミングでは、特に意味を持たないので、<X>と示している。

セレクタ信号S2の値が、図12のように”H”であれば、<K1>、<D1>がフリップフロップ101、フリップフロップ102で保持されるので、1クロック遅れたタイミングで、データKey、データDataに現れる。

【0019】

演算回路201にデータが入力されると演算が開始されるが、回路遅延によりある期間データが不安定で確定しない区間が存在する。

これを、バスデータBus1では、ハッチングでバス表記している。

この区間ではデータが刻一刻と変化している。

この不確定区間を過ぎるとデータが安定し、確定したデータが出力される。

つまり、図14に例示するように、演算回路201の出力データでは、データ値が一定していない不確定状態710とデータ値が一定している確定状態720とが存在する。

確定状態720は、次のデータData及びデータKeyが演算回路201に入力されるまで持続する。

不確定状態710の時間、換言すると、確定状態720が持続する時間は、演算の種類によって異なる。

演算回路201では、入力されたデータDataとデータKeyの組合せに応じて、複数種の演算が行われる。

演算完了までに要する時間は演算の種類により様々であり、演算完了までに長時間を要する演算の場合は、不確定状態710の時間が長く、従って、確定状態720が持続する時間は短くなる。

【0020】

図12では、<K1>、<D1>を演算した結果を<D2>と表記して、バスデータBus1に示している。

<D2>と確定しているときは、セレクタ信号S2が“L”であるので、セレクタ103はバスデータBus1を選択、すなわち、このタイミングでは<D2>を選択している。

クロックCKの立ち上がり時に、フリップフロップ101、フリップフロップ102が<K2>、<D2>を保持するので、データKey、データDataは<K2>、<D2>に変化する。

このように、演算結果をループして演算が進行する。

イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ401がバスデータBus1を保持し、<Dn>を出力する。

このように、順次データDataが変化して、最終結果である<Dn>が出力される。

【0021】

次に、異常なクロックCKが入力された場合のタイミングチャートを図13に示す。

タイミングT0が異常なクロックCKの立ち上りタイミングである。

このタイミングT0におけるバスデータBus1の状態を見ると、<K2>、<D2>が演算回路201に入力されてから、データが安定するまでの時間を経ていない区間でクロックの立ち上りが来たため、ハッチングのバス表記のデータを保持することになる。

データDataにおける、この保持された不確定なデータを<ハッチングD3>と表記する。

すなわち、故障したデータがデータDataに取り込まれた。

演算回路201は<K3>と<ハッチングD3>が入力されたので、データが不安定な区間ののち、データが確定した<ハッチングD4>を出力することになる。

<ハッチングD3>から<ハッチングD4>が生成されたので、故障したデータを引き継いだことになる。

このように、故障したデータを引き継いだ<ハッチングDn>が生成され、最終結果として出力されると、フォールト攻撃は成立する。

【0022】

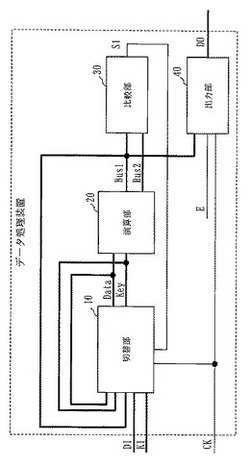

図1に本実施の形態に係るデータ処理装置の機能構成例を示す。

本実施の形態の係るデータ処理装置は、被演算データを切り替える切替部10、演算を行う演算部20、演算部20からのデータを比較する比較部30、最終演算結果を出力する出力部40とで構成される。

【0023】

切替部10は、入力データKI、データKey、入力データDI、データData、バスデータBus1を、クロックCKのタイミングで切り替えて、データData、データKeyを出力する。

つまり、切替部10は、外部より入力データKIと入力データDIを入力する。

切替部10は、入力データKIは周期的に外部から入力するが、入力データDIは初回のみ入力する。

また、切替部10は、繰り返し到来する出力タイミングであるクロックCK立ち上がり時に、データDataとデータKeyとを並行して出力するとともに、出力したデータDataとデータKeyをフィードバック入力する。

更に、切替部10は、演算部20がデータDataとデータKeyを用いた演算結果であるバスデータBus1を入力する。

データKeyは第1のデータの例であり、データDataは第2のデータの例であり、バスデータBus1は第3のデータの例である。

また、演算部20が出力するバスデータBus2が第4のデータの例である。

切替部10は、バスデータBus2は入力しない。

詳細は後述するが、切替部10は、クロックCK立ち上がり時に比較部30からセレクタ信号S1を入力し、入力したセレクタ信号S1の値を判断する。

値が“H”のセレクタ信号S1は、比較部30においてバスデータBus1とバスデータBus2とを比較した結果、両者のデータ値が一致していたことを表す。

一方、値が“L”のセレクタ信号S1は、比較部30においてバスデータBus1とバスデータBus2とを比較した結果、両者のデータ値が一致していなかったことを表す。

セレクタ信号S1の値が“H”であれば、前回の出力タイミングにおいて演算部20に出力したデータKeyと異なるデータ(具体的には、新たに入力した入力データKI)を新たなデータKeyとして演算部20に出力するとともに、演算部20から入力したバスデータBus1を新たなデータDataとして出力する。

一方、セレクタ信号S1の値が“L”であれば、前回の出力タイミングにおいて演算部20に出力したデータKeyとデータDataとを、再度、演算部20に出力する。

例えば、データKeyは、演算部20の暗号処理又は復号処理に用いられる鍵データであり、データDataは、演算部20の暗号処理又は復号処理の対象となるデータである。

【0024】

演算部20は切替部10から出力されたデータDataとデータKeyとを並行して入力し、入力したデータDataとデータKeyとを用いて所定の演算(例えば、暗号処理又は復号処理のための演算)を行い、演算結果をバスデータBus1、バスデータBus2として出力する。

実施の形態1では、後述するように、バスデータBus2は、バスデータBus1を遅延させたデータである。

【0025】

比較部30は、バスデータBus1、バスデータBus2を比較し、その結果をセレクタ信号S1として出力する。

つまり、演算部20から出力されたバスデータBus1とバスデータBus2とを並行して入力し、同じタイミングで入力したバスデータBus1のデータ値とバスデータBus2のデータ値とを比較し、バスデータBus1とバスデータBus2との間でデータ値が一致する場合は、値が“H”のセレクタ信号S1を切替部10に出力する。

一方、バスデータBus1とバスデータBus2との間でデータ値が一致しない場合は、値が“L”のセレクタ信号S1を切替部10に出力する。

値が“H”のセレクタ信号S1は、一致信号の例に相当し、値が“L”のセレクタ信号S1は、不一致信号の例に相当する。

前述したように、バスデータBus2は、バスデータBus1を遅延させたデータである。

このため、正常時では、バスデータBus1の確定状態720(図14)のデータ値とバスデータBus2の確定状態720のデータ値は同じである。

そして、比較部30は、バスデータBus1の確定状態720(図14)のデータ値とバスデータBus2の確定状態720のデータ値を並行して入力している間は、値が“H”のセレクタ信号Sを出力する。

なお、演算部20における遅延量は、比較部30においてバスデータBus1の確定状態720のデータとバスデータBus2の確定状態720のデータを並行して入力できる遅延量である。

一方、比較部30は、確定状態720同士の組合せ以外の組合せでバスデータBus1とバスデータBus2を入力している間は、値が“L”のセレクタ信号Sを出力する。

【0026】

出力部40は、イネーブル信号Eを見て、最終演算結果がバスデータBus1に出力されたことが分かると、クロックCKのタイミングでバスデータBus1を保持して、データDOに出力する。

【0027】

図2は実施の形態1に係るデータ処理装置の回路構成例を示す。

これを用いて、フォールト攻撃や外乱による誤動作に対して耐性があることを示す。

【0028】

図2において、演算回路21は演算を行う組合せ回路である。

セレクタ13は入力データKIとデータKeyをセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ11は、セレクタ13からの信号をクロックCKのタイミングで保持して、データKeyとして出力するフリップフロップである。

セレクタ14は、入力データDI、データDataとバスデータBus1をセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ12は、セレクタ14の出力をクロックCKのタイミングで保持し、データDataとして出力するフリップフロップである。

遅延素子22は、バスデータBus1を遅延させる遅延回路である。

NXOR素子31はバスデータBus1とバスデータBus2のNXOR(Not−eXclusive OR)をとり、セレクタ信号S1を出力する回路である。

イネーブル付フリップフロップ41は、イネーブル信号Eを判断し、クロックCKのタイミングでバスデータBus1を保持するイネーブル付フリップフロップである。

図1との対応は、フリップフロップ11、フリップフロップ12、セレクタ13、セレクタ14が切替部10に、演算回路21、遅延素子22が演算部20に、NXOR素子31が比較部30に、イネーブル付フリップフロップ41が出力部40に相当する。

【0029】

次に正常な動作について、図3を用いて説明する。

図3は、図2の回路に正常なクロックCKが入力されたときのタイミングチャートである。

【0030】

入力データKIは、クロックCKに同期して、図に示すように、<K1>、<K2>、・・・、<Kn−1>と入力されるデータである。

入力データKIの生成回路は図2には図示されていない。

入力データDIは、<K1>と同じタイミングで<D1>が入力される。

その他のタイミングでは、特に意味を持たないので、<X>と示している。

セレクタ信号S1に関係なく、値が“H”のセレクタ信号S2がセレクタ13に入力されると、セレクタ13は入力データKIを、セレクタ14は入力データDIを選択する。

ここで選択されたデータをフリップフロップ11、フリップフロップ12が保持するので、<K1>、<D1>が、1クロック遅れたタイミングで、データKey、データDataに現れる。

【0031】

演算回路21にデータが入力されると演算が開始されるが、回路遅延によりある期間データが不安定で確定しないタイミングが存在する。

これを、バスデータBus1では、ハッチング色のバス表記で示している。

この区間ではデータが刻一刻と変化している。この不確定区間を過ぎるとデータが安定し、確定したデータが出力される。

つまり、図14に示したように、演算回路21からの出力には、不確定状態710と確定状態720とが含まれる。

<K1>、<D1>を演算した結果を<D2>と表記して、バスデータBus1に示している。

バスデータBus2は、遅延素子22による遅延分だけバスデータBus1を遅延させたものであるので、図3ではバスデータBus1が少し遅れた表記になっている。

NXOR素子31には、バスデータBus1とバスデータBus2が入力されるので、両バスデータの値が一致した区間だけ“H”となるセレクタ信号S1となる。

つまり、バスデータBus1の<D2>(確定状態のデータ)とバスデータBus2の<D2>(確定状態のデータ)が重なる区間、セレクタ信号S1は“H”となる。

セレクタ信号S1が“H”、セレクタ信号S2が“L”であれば、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が<K2>、<D2>を保持するので、データKeyは<K2>、データDataは<D2>となる。

このように、演算結果がループして、演算が進行して、データDataは、<D3>、<D4>、<D5>と変化していく。

イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

このように、データDataが順次変化して、最終結果が出力される。

【0032】

次に、異常なクロックCKが入力された場合の、タイミングチャートを図4に示す。

【0033】

図4において、タイミングT0が、規定周期を外れた異常なクロックCKの立ち上りタイミングである。

このタイミングT0におけるバスデータBus1の状態を見ると、<K2>、<D2>が演算回路21に入力されてから、データが安定するまでの時間を経ていない区間(すなわち、図14の不確定状態710)でクロックの立ち上りが来たため、ハッチングのバス表記の状態である。

このタイミングT0では、セレクタ信号S1が“L”、セレクタ信号S2が“L”であるので、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21に出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1は<D3>と確定し、遅延素子22の遅延量だけ遅れて、バスデータBus2も<D3>と確定する。

バスデータBus1の<D3>(確定状態のデータ)とバスデータBus2の<D3>(確定状態のデータ)が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0034】

なお、図2で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“L”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図4では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、異常なクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、フォールト攻撃は成立しない。

なお、異常なクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0035】

次に、外乱が発生して演算回路21が誤動作した場合の、タイミングチャートを図5に示す。

【0036】

バスデータBus1に<Damaged>と書かれた区間に演算回路21が誤動作したとしてタイミングチャートは書かれている。

誤動作している区間は、データは不安定で刻一刻と変化する(つまり、図14の不確定状態710となっている)ため、<Damaged>はハッチングで表記している。

この<Damaged>の区間に発生したクロックCKの立ち上りタイミングT0におけるバスデータBus1の状態は<Damaged>である。

そのため、このタイミングT0では、セレクタ信号S1が“L”、セレクタ信号S2が“L”である。

よって、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21に出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1は<D3>と確定し、遅延素子22の遅延量だけ遅れて、バスデータBus2も<D3>と確定する。

バスデータBus1の<D3>(確定状態のデータ)とバスデータBus2の<D3>(確定状態のデータ)が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0037】

なお、図2で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“L”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図5では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、誤動作が発生した区間のクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、誤動作による影響はない。

なお、誤動作が発生した区間のクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0038】

以上のように、実施の形態1では、遅延素子を設けて、演算回路のデータ出力が安定、すなわち、一致することを確認し、演算ループが回るようにした。

さらに、演算回路のデータ出力が不安定な区間に異常なクロックを入力するフォールト攻撃に対しては、演算回路に入力されているデータを、異常クロック入力後の次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、異常なクロックを使用するフォールト攻撃に対して耐性を有する効果がある。

さらに、実施の形態1では、正常時の演算時間が最も短く、異常時は演算時間が延びるのでフォールト攻撃に手間がかかるという効果もある。

【0039】

また、遅延素子を設けて、演算回路のデータ出力が安定、すなわち、一致することを確認し、演算ループが回るようにしたことにより、演算回路の誤動作に対しても耐性を有する。

つまり、意図的で有る無しに関わらず外乱により演算回路が誤動作し、その区間にクロックが発生した場合は、演算回路に入力されているデータを、誤動作の発生した次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、演算回路の誤動作に対して耐性を有する効果がある。

【0040】

実施の形態2.

以上の実施の形態1では、遅延素子を用いて演算回路のデータ出力が安定することを確認するようにしたものであるが、演算結果を直接比較するような場合においても、フォールト攻撃や誤動作に対して耐性を有する実施の形態を示す。

【0041】

図6は実施の形態2に係るデータ処理装置の回路構成例を示す。

これを用いて、フォールト攻撃や外乱による誤動作に対して耐性があることを示す。

【0042】

図6において、演算回路21は演算を行う組合せ回路であり、2系統ある。

つまり、図6では、演算回路21aと演算回路21bが存在する。

演算回路21aと演算回路21bは、それぞれ同時に、データDataとデータKeyとを並行して入力し、並行して同じ演算を行う。

演算回路21aは演算結果をバスデータBus1として出力し、演算回路21bは演算結果をバスデータBus2として出力する。

演算回路21aからのバスデータBus1の出力と演算回路21bからのバスデータBus2の出力は同時である。

正常時では、バスデータBus1の確定状態720のデータ値とバスデータBus2の確定状態720のデータ値は一致する。

演算回路21aは第1の演算部の例に相当し、演算回路21bは第2の演算部の例に相当する。

また、演算回路21aから出力されたバスデータBus1は第3のデータの例に相当し、演算回路21bから出力されたバスデータBus2は第4のデータの例に相当する。

なお、本実施の形態においても、データKeyが第1のデータの例であり、データDataが第2のデータの例である。

【0043】

セレクタ13は、入力データKIとデータKeyをセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ11は、セレクタ13からの信号をクロックCKのタイミングで保持して、データKeyとして出力するフリップフロップである。

セレクタ14は、入力データDI、データDataとバスデータBus1をセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ12は、セレクタ14の出力をクロックCKのタイミングで保持し、データDataとして出力するフリップフロップである。

NXOR素子31は、バスデータBus1とバスデータBus2のNXORをとりセレクタ信号S1を出力する回路である。

イネーブル付フリップフロップ41は、イネーブル信号Eを判断し、クロックCKのタイミングでバスデータBus1を保持するイネーブル付フリップフロップである。

図2との差異は、遅延素子22が存在しない代わりに2つの演算回路21(演算回路21aと演算回路21b)が存在することであり、他の要素は、図2に示したものと同様である。

図1との対応は、フリップフロップ11、フリップフロップ12、セレクタ13、セレクタ14が切替部10に、2系統の演算回路21が演算部20に、NXOR素子31が比較部30に、イネーブル付フリップフロップ41が出力部40に相当する。

【0044】

次に正常な動作について、図7を用いて説明する。

図7は、図6の回路に正常なクロックCKが入力されたときのタイミングチャートである。

【0045】

入力データKIは、クロックCKに同期して、図に示すように、<K1>、<K2>、・・・、<Kn−1>と入力されるデータである。

入力データKIの生成回路は図6には図示されていない。

入力データDIは、<K1>と同じタイミングで<D1>が入力される。

その他のタイミングでは、特に意味を持たないので、<X>と示している。

セレクタ信号S1に関係なく、値が“H”のセレクタ信号S2が入力されると、セレクタ13は入力データKIを、セレクタ14は入力データDIを選択する。

ここで選択されたデータをフリップフロップ11、フリップフロップ12が保持するので、<K1>、<D1>が、1クロック遅れたタイミングで、データKey、データDataに現れる。

【0046】

演算回路21a及び演算回路21bにデータが入力されると演算が開始されるが、回路遅延によりある期間データが不安定で確定しないタイミングが存在する。

これを、バスデータBus1、バスデータBus2では、ハッチングのバス表記で示している。

この区間ではデータが刻一刻と変化している。

この不確定区間を過ぎるとデータが安定し、確定したデータが出力される。

<K1>、<D1>を演算した結果を<D2>と表記して、バスデータBus1、バスデータBus2に示している。

NXOR素子31には、バスデータBus1とバスデータBus2が入力されるので、両バスデータの値が一致した区間だけ“H”となるセレクタ信号S1となる。

つまり、バスデータBus1の<D2>(確定状態のデータ)とバスデータBus2の<D2>(確定状態のデータ)が重なる区間、セレクタ信号S1は“H”となる。

セレクタ信号S1が“H”、セレクタ信号S2が“L”であれば、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が<K2>、<D2>を保持するので、データKeyは<K2>、データDataは<D2>となる。

このように、演算結果がループして、演算が進行して、データDataは、<D3>、<D4>、<D5>と変化していく。

イネーブル信号Eが”H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

このように、データDataが順次変化して、最終結果が出力される。

【0047】

次に、異常なクロックCKが入力された場合の、タイミングチャートを図8に示す。

【0048】

図8において、タイミングT0が、規定周期を外れた異常なクロックCKの立ち上りタイミングである。

このタイミングT0におけるバスデータBus1、バスデータBus2の状態を見ると、<K2>、<D2>が演算回路1に入力されてから、データが安定するまでの時間を経ていない区間でクロックの立ち上りが来たため、ハッチングのバス表記の状態である。

このタイミングT0では、セレクタ信号S1が“L”、セレクタ信号S2が“L”であるので、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21a及び演算回路21bに出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1は<D3>と確定し、バスデータBus2も<D3>と確定する。

バスデータBus1の<D3>(確定状態のデータ)とバスデータBus2の<D3>(確定状態のデータ)が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0049】

なお、図6で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“L”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図8では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、異常なクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、フォールト攻撃は成立しない。

なお、異常なクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0050】

次に、外乱が発生して演算回路1が誤動作した場合の、タイミングチャートを図9に示す。

【0051】

バスデータBus1に<Damaged>と書かれた区間に一方の演算回路21が誤動作したとしてタイミングチャートは書かれている(図9では演算回路21aに誤動作が発生している)。

誤動作している区間は、データは不安定で刻一刻と変化するため、<Damaged>はハッチングのバス表記で示している。

この<Damaged>の区間に発生したクロックCKの立ち上りタイミングT0におけるバスデータBus1の状態は<Damaged>である。

一方、バスデータBus2の状態は<D3>である。

そのため、このタイミングT0では、セレクタ信号S1が”L”、セレクタ信号S2が”L”である。

よって、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21a及び演算回路21bに出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1、バスデータBus2は<D3>と確定する。

バスデータBus1の<D3>とバスデータBus2の<D3>が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0052】

なお、図6で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“H”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図9では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、誤動作が発生した区間のクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、誤動作による影響はない。

なお、誤動作が発生した区間のクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0053】

以上のように、実施の形態2では、演算回路を2系統設けて、両者の演算回路のデータ出力が安定すなわち、一致することを確認し、演算ループが回るようにした。

さらに、演算回路のデータ出力が不安定な区間に異常なクロックを入力するフォールト攻撃に対しては、演算回路に入力されているデータを、異常クロック入力後の次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、異常なクロックを使用するフォールト攻撃に対して耐性を有する効果がある。

さらに、実施の形態2では、正常時の演算時間が最も短く、異常時は演算時間が延びるのでフォールト攻撃に手間がかかるという効果もある。

【0054】

また、演算回路を2系統設けて、両者の演算回路のデータ出力が安定すなわち、一致することを確認し、演算ループが回るようにしたことにより、演算回路の誤動作に対しても耐性を有する。

つまり、意図的で有る無しに関わらず外乱により演算回路が誤動作し、その区間にクロックが発生した場合は、演算回路に入力されているデータを、誤動作の発生した次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、演算回路の誤動作に対して耐性を有する効果がある。

【0055】

以上、実施の形態1及び実施の形態2では、

被演算データである入力データが入力され、演算結果が出力される演算部を中心とする演算装置であって、

演算部から、正常演算時に安定したデータが一致すると期待される複数の演算結果を出力し、その複数の演算結果が一致したことを確認し、次の演算を開始し、複数の演算結果が一致しない場合は、同一の演算を再度行う演算装置を説明した。

【0056】

また、実施の形態1及び実施の形態2では、

被演算データは、

1)切替部入力データ、

2)切替部出力データ、

3)演算部出力データ

を切り替える切替部の出力データであって、

切替部は、演算部からの複数の演算結果を比較した結果に基づき、上記1)〜3)のデータを切り替え、

その複数の演算結果が一致した場合は、次の演算を開始し、

複数の演算結果が一致しない場合は、同一の演算を再度行う演算装置を説明した。

【0057】

また、実施の形態1では、

演算部の複数の演算結果は、演算回路からの出力を遅延させることにより生成することを説明した。

【0058】

また、実施の形態2では、

演算部の複数の演算結果は、演算回路を複数設けるにより生成することを説明した。

【符号の説明】

【0059】

10 切替部、11 フリップフロップ、12 フリップフロップ、13 セレクタ、14 セレクタ、20 演算部、21 演算回路、22 遅延素子、30 比較部、31 NXOR素子、40 出力部、41 イネーブル付フリップフロップ。

【技術分野】

【0001】

本発明は、データ処理装置に関する。

【背景技術】

【0002】

特許文献1に記載の技術では、論理的にみて同じ暗号関連処理が行われる複数の回路を並列に配置し、各回路での暗号関連処理の結果を比較し、比較結果が異なった場合に、暗号関連処理を停止させることを行っている。

これにより、特許文献1に記載の技術では、電力差分攻撃やフォールト攻撃に耐性を持たせている。

【0003】

また、特許文献2に記載の技術では、データ撹拌部でデータが確定する時間と、鍵スケジュール部で鍵が確定する時間を一致させるための遅延回路を設けることにより、故障発生時にサンプリングされる故障データが複数となるようにしている。

この結果、特許文献2に記載の技術では、フォールト攻撃ができない故障を有するデータを出力させて、これにより、フォールト攻撃に耐性を持たせている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−229485号公報

【特許文献2】特開2010−273161号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1の技術では、論理的にみて同じ回路を並列に配置しているため、回路規模が大きくなるという課題がある。

また、異常時に暗号関連処理が停止するので、外乱により異常が頻発する環境、例えば、宇宙空間における放射線による異常発生の場合、正常な結果が得られるのはごくまれであるという課題がある。

【0006】

また、特許文献2の技術においても、異常時に複数の故障が発生するように遅延回路が設けられ、故障を有するデータを出力しているので、外乱により異常が頻発する環境、例えば、宇宙空間における放射線による異常発生の場合、正常な結果が得られないという課題がある。

【0007】

この発明は上記のような課題を解決することを主な目的としており、簡易な構成により、外乱が発生しても正常な演算結果を出力する構成を実現することを主な目的とする。

【課題を解決するための手段】

【0008】

本発明に係るデータ処理装置は、

繰り返し到来する出力タイミングの度に第1のデータと第2のデータとを並行して出力する切替部と、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いた演算を行って第3のデータと第4のデータを生成し、生成した第3のデータと第4のデータとを並行して出力する演算部と、

前記演算部から出力された第3のデータと第4のデータとを並行して入力し、同じタイミングで入力した第3のデータのデータ値と第4のデータのデータ値とを比較し、第3のデータと第4のデータとの間でデータ値が一致する場合は、前記切替部に一致信号を出力し、第3のデータと第4のデータとの間でデータ値が一致しない場合は、前記切替部に不一致信号を出力する比較部とを有し、

前記切替部は、

前記演算部から第3のデータが出力される度に、出力された第3のデータを入力し、

出力タイミングが到来する度に、到来した出力タイミングにおいて前記比較部から入力した信号が一致信号であるか不一致信号であるかを判断し、

前記比較部から入力した信号が一致信号である場合は、前記演算部に出力済の第1のデータと異なるデータを新たな第1のデータとして前記演算部に出力するとともに、前記演算部から入力した第3のデータを新たな第2のデータとして出力し、

前記比較部から入力した信号が不一致信号である場合は、前記演算部に出力済の第1のデータと第2データとを、再度、前記演算部に出力することを特徴とする。

【発明の効果】

【0009】

本発明によれば、外乱が生じた場合は、出力タイミングが到来した際の第3のデータと第4のデータとの間でデータ値が一致しなくなり、演算部に出力済の第1のデータと第2データとを、再度、演算部に出力するため、出力済の第1のデータと第2データとを用いた演算を演算部に行わせることができ、外乱が発生しても正常な演算結果を出力することができる。

【図面の簡単な説明】

【0010】

【図1】実施の形態1に係るデータ処理装置の機能構成例を示す図。

【図2】実施の形態1に係るデータ処理装置の回路構成例を示す図。

【図3】実施の形態1に係るデータ処理装置における正常時のタイミングチャート図。

【図4】実施の形態1に係るデータ処理装置におけるクロック異常発生時のタイミングチャート図。

【図5】実施の形態1に係るデータ処理装置における誤動作発生時のタイミングチャート図。

【図6】実施の形態2に係るデータ処理装置の回路構成例を示す図。

【図7】実施の形態2に係るデータ処理装置における正常時のタイミングチャート図。

【図8】実施の形態2に係るデータ処理装置におけるクロック異常発生時のタイミングチャート図。

【図9】実施の形態2に係るデータ処理装置における誤動作発生時のタイミングチャート図。

【図10】一般的なデータ処理装置の機能構成例を示す図。

【図11】一般的なデータ処理装置の回路構成例を示す図。

【図12】一般的なデータ処理装置における正常時のタイミングチャート図。

【図13】一般的なデータ処理装置におけるクロック異常発生時のタイミングチャート図。

【図14】確定状態と不確定状態を説明する図。

【発明を実施するための形態】

【0011】

実施の形態1及び実施の形態2では、フォールト攻撃のように異常な外乱が発生しても、正常な演算結果を出力し、また、宇宙空間のように異常な外乱が頻発する環境においても、正常な演算結果を出力するデータ処理装置を説明する。

【0012】

以下では、まず、一般的なデータ処理装置を説明し、その後、実施の形態1及び実施の形態2に係るデータ処理装置を説明する。

【0013】

実施の形態1.

図10は、一般的なデータ処理装置の構成図である。

一般的なデータ処理装置は、被演算データを切り替える切替器100、演算を行う演算器200、最終演算結果を出力する出力器400とで構成される。

切替器100は、入力データKI、入力データDI、バスデータBus1を、クロックCKのタイミングで切り替えて、データData、データKeyを出力する。

演算器200はデータData、データKeyを受けて、演算を行い、演算結果をバスデータBus1に出力する。

出力器400は、イネーブル信号Eを見て、最終演算結果がバスデータBus1に出力されたことが分かると、クロックCKのタイミングでバスデータBus1を保持して、データDOに出力する。

なお、図10において、太い線の接続線は複数ビットの信号が入出力されることを表し、細い線の接続線は1ビットの信号が入出力されることを表している。

以降で説明する図面においても、太い線の接続線は複数ビットの信号が入出力されることを表し、細い線の接続線は1ビットの信号が入出力されることを表している。

【0014】

このような一般的なデータ処理装置にて、フォールト攻撃を行う場合は、切替器100、演算器200に外乱を与えて、データの一部に故障を誘発させる。

具体的には、一定周期のクロックCKに、異なる周期のクロックを一瞬発生させて、バスデータBus1の切替タイミングを変えることで、データDataの値に故障を誘発させる。

また、レーザーや放射線を演算器200に照射することで、演算ビットの状態を変化させて、故障を誘発させる。

このように、故障を一瞬誘発し、その後は正常なデータで演算を行い、最終結果を故障データとして入手することで、フォールト攻撃は成立する。

図10では図示していないが、切替器100のループ制御や、イネーブル信号Eの生成を行う演算制御部への攻撃は対象外とする。

なぜなら、フォールト攻撃は正常な演算制御の下で、演算データの一部に故障を誘発させることで成り立つ攻撃であるからである。

また、宇宙空間のような外乱が多い環境では、切替器100、演算器200が放射線などにより誤動作して、データが破壊される。

【0015】

図11は一般的な演算装置の回路構成図である。

これを用いて、異常クロックにおけるフォールト攻撃の一例を説明する。

【0016】

図11において、演算回路201は演算を行う組合せ回路である。

フリップフロップ101は、入力データKIをクロックCKのタイミングで保持して、データKeyとして出力するフリップフロップである。

セレクタ103は、入力データDIとバスデータBus1をセレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ102は、セレクタ103の出力をクロックCKのタイミングで保持し、データDataとして出力するフリップフロップである。

イネーブル付フリップフロップ401は、イネーブル信号Eを判断し、クロックCKのタイミングでバスデータBus1を保持するイネーブル付フリップフロップである。

図10との対応は、フリップフロップ101、フリップフロップ102、セレクタ103が切替器100に、演算回路201が演算器200に、イネーブル付フリップフロップ401が出力器400に相当する。

【0017】

次に正常な動作について、図12を用いて説明する。

図12は、図11の回路に正常なクロックCKが入力されたときのタイミングチャートである。

【0018】

入力データKIは、クロックCKに同期して、図に示すように、<K1>、<K2>、・・・、<Kn−1>と入力されるデータである。

入力データKIの生成回路は図11には図示されていない。

入力データDIは、<K1>と同じタイミングで<D1>が入力される。

その他のタイミングでは、特に意味を持たないので、<X>と示している。

セレクタ信号S2の値が、図12のように”H”であれば、<K1>、<D1>がフリップフロップ101、フリップフロップ102で保持されるので、1クロック遅れたタイミングで、データKey、データDataに現れる。

【0019】

演算回路201にデータが入力されると演算が開始されるが、回路遅延によりある期間データが不安定で確定しない区間が存在する。

これを、バスデータBus1では、ハッチングでバス表記している。

この区間ではデータが刻一刻と変化している。

この不確定区間を過ぎるとデータが安定し、確定したデータが出力される。

つまり、図14に例示するように、演算回路201の出力データでは、データ値が一定していない不確定状態710とデータ値が一定している確定状態720とが存在する。

確定状態720は、次のデータData及びデータKeyが演算回路201に入力されるまで持続する。

不確定状態710の時間、換言すると、確定状態720が持続する時間は、演算の種類によって異なる。

演算回路201では、入力されたデータDataとデータKeyの組合せに応じて、複数種の演算が行われる。

演算完了までに要する時間は演算の種類により様々であり、演算完了までに長時間を要する演算の場合は、不確定状態710の時間が長く、従って、確定状態720が持続する時間は短くなる。

【0020】

図12では、<K1>、<D1>を演算した結果を<D2>と表記して、バスデータBus1に示している。

<D2>と確定しているときは、セレクタ信号S2が“L”であるので、セレクタ103はバスデータBus1を選択、すなわち、このタイミングでは<D2>を選択している。

クロックCKの立ち上がり時に、フリップフロップ101、フリップフロップ102が<K2>、<D2>を保持するので、データKey、データDataは<K2>、<D2>に変化する。

このように、演算結果をループして演算が進行する。

イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ401がバスデータBus1を保持し、<Dn>を出力する。

このように、順次データDataが変化して、最終結果である<Dn>が出力される。

【0021】

次に、異常なクロックCKが入力された場合のタイミングチャートを図13に示す。

タイミングT0が異常なクロックCKの立ち上りタイミングである。

このタイミングT0におけるバスデータBus1の状態を見ると、<K2>、<D2>が演算回路201に入力されてから、データが安定するまでの時間を経ていない区間でクロックの立ち上りが来たため、ハッチングのバス表記のデータを保持することになる。

データDataにおける、この保持された不確定なデータを<ハッチングD3>と表記する。

すなわち、故障したデータがデータDataに取り込まれた。

演算回路201は<K3>と<ハッチングD3>が入力されたので、データが不安定な区間ののち、データが確定した<ハッチングD4>を出力することになる。

<ハッチングD3>から<ハッチングD4>が生成されたので、故障したデータを引き継いだことになる。

このように、故障したデータを引き継いだ<ハッチングDn>が生成され、最終結果として出力されると、フォールト攻撃は成立する。

【0022】

図1に本実施の形態に係るデータ処理装置の機能構成例を示す。

本実施の形態の係るデータ処理装置は、被演算データを切り替える切替部10、演算を行う演算部20、演算部20からのデータを比較する比較部30、最終演算結果を出力する出力部40とで構成される。

【0023】

切替部10は、入力データKI、データKey、入力データDI、データData、バスデータBus1を、クロックCKのタイミングで切り替えて、データData、データKeyを出力する。

つまり、切替部10は、外部より入力データKIと入力データDIを入力する。

切替部10は、入力データKIは周期的に外部から入力するが、入力データDIは初回のみ入力する。

また、切替部10は、繰り返し到来する出力タイミングであるクロックCK立ち上がり時に、データDataとデータKeyとを並行して出力するとともに、出力したデータDataとデータKeyをフィードバック入力する。

更に、切替部10は、演算部20がデータDataとデータKeyを用いた演算結果であるバスデータBus1を入力する。

データKeyは第1のデータの例であり、データDataは第2のデータの例であり、バスデータBus1は第3のデータの例である。

また、演算部20が出力するバスデータBus2が第4のデータの例である。

切替部10は、バスデータBus2は入力しない。

詳細は後述するが、切替部10は、クロックCK立ち上がり時に比較部30からセレクタ信号S1を入力し、入力したセレクタ信号S1の値を判断する。

値が“H”のセレクタ信号S1は、比較部30においてバスデータBus1とバスデータBus2とを比較した結果、両者のデータ値が一致していたことを表す。

一方、値が“L”のセレクタ信号S1は、比較部30においてバスデータBus1とバスデータBus2とを比較した結果、両者のデータ値が一致していなかったことを表す。

セレクタ信号S1の値が“H”であれば、前回の出力タイミングにおいて演算部20に出力したデータKeyと異なるデータ(具体的には、新たに入力した入力データKI)を新たなデータKeyとして演算部20に出力するとともに、演算部20から入力したバスデータBus1を新たなデータDataとして出力する。

一方、セレクタ信号S1の値が“L”であれば、前回の出力タイミングにおいて演算部20に出力したデータKeyとデータDataとを、再度、演算部20に出力する。

例えば、データKeyは、演算部20の暗号処理又は復号処理に用いられる鍵データであり、データDataは、演算部20の暗号処理又は復号処理の対象となるデータである。

【0024】

演算部20は切替部10から出力されたデータDataとデータKeyとを並行して入力し、入力したデータDataとデータKeyとを用いて所定の演算(例えば、暗号処理又は復号処理のための演算)を行い、演算結果をバスデータBus1、バスデータBus2として出力する。

実施の形態1では、後述するように、バスデータBus2は、バスデータBus1を遅延させたデータである。

【0025】

比較部30は、バスデータBus1、バスデータBus2を比較し、その結果をセレクタ信号S1として出力する。

つまり、演算部20から出力されたバスデータBus1とバスデータBus2とを並行して入力し、同じタイミングで入力したバスデータBus1のデータ値とバスデータBus2のデータ値とを比較し、バスデータBus1とバスデータBus2との間でデータ値が一致する場合は、値が“H”のセレクタ信号S1を切替部10に出力する。

一方、バスデータBus1とバスデータBus2との間でデータ値が一致しない場合は、値が“L”のセレクタ信号S1を切替部10に出力する。

値が“H”のセレクタ信号S1は、一致信号の例に相当し、値が“L”のセレクタ信号S1は、不一致信号の例に相当する。

前述したように、バスデータBus2は、バスデータBus1を遅延させたデータである。

このため、正常時では、バスデータBus1の確定状態720(図14)のデータ値とバスデータBus2の確定状態720のデータ値は同じである。

そして、比較部30は、バスデータBus1の確定状態720(図14)のデータ値とバスデータBus2の確定状態720のデータ値を並行して入力している間は、値が“H”のセレクタ信号Sを出力する。

なお、演算部20における遅延量は、比較部30においてバスデータBus1の確定状態720のデータとバスデータBus2の確定状態720のデータを並行して入力できる遅延量である。

一方、比較部30は、確定状態720同士の組合せ以外の組合せでバスデータBus1とバスデータBus2を入力している間は、値が“L”のセレクタ信号Sを出力する。

【0026】

出力部40は、イネーブル信号Eを見て、最終演算結果がバスデータBus1に出力されたことが分かると、クロックCKのタイミングでバスデータBus1を保持して、データDOに出力する。

【0027】

図2は実施の形態1に係るデータ処理装置の回路構成例を示す。

これを用いて、フォールト攻撃や外乱による誤動作に対して耐性があることを示す。

【0028】

図2において、演算回路21は演算を行う組合せ回路である。

セレクタ13は入力データKIとデータKeyをセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ11は、セレクタ13からの信号をクロックCKのタイミングで保持して、データKeyとして出力するフリップフロップである。

セレクタ14は、入力データDI、データDataとバスデータBus1をセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ12は、セレクタ14の出力をクロックCKのタイミングで保持し、データDataとして出力するフリップフロップである。

遅延素子22は、バスデータBus1を遅延させる遅延回路である。

NXOR素子31はバスデータBus1とバスデータBus2のNXOR(Not−eXclusive OR)をとり、セレクタ信号S1を出力する回路である。

イネーブル付フリップフロップ41は、イネーブル信号Eを判断し、クロックCKのタイミングでバスデータBus1を保持するイネーブル付フリップフロップである。

図1との対応は、フリップフロップ11、フリップフロップ12、セレクタ13、セレクタ14が切替部10に、演算回路21、遅延素子22が演算部20に、NXOR素子31が比較部30に、イネーブル付フリップフロップ41が出力部40に相当する。

【0029】

次に正常な動作について、図3を用いて説明する。

図3は、図2の回路に正常なクロックCKが入力されたときのタイミングチャートである。

【0030】

入力データKIは、クロックCKに同期して、図に示すように、<K1>、<K2>、・・・、<Kn−1>と入力されるデータである。

入力データKIの生成回路は図2には図示されていない。

入力データDIは、<K1>と同じタイミングで<D1>が入力される。

その他のタイミングでは、特に意味を持たないので、<X>と示している。

セレクタ信号S1に関係なく、値が“H”のセレクタ信号S2がセレクタ13に入力されると、セレクタ13は入力データKIを、セレクタ14は入力データDIを選択する。

ここで選択されたデータをフリップフロップ11、フリップフロップ12が保持するので、<K1>、<D1>が、1クロック遅れたタイミングで、データKey、データDataに現れる。

【0031】

演算回路21にデータが入力されると演算が開始されるが、回路遅延によりある期間データが不安定で確定しないタイミングが存在する。

これを、バスデータBus1では、ハッチング色のバス表記で示している。

この区間ではデータが刻一刻と変化している。この不確定区間を過ぎるとデータが安定し、確定したデータが出力される。

つまり、図14に示したように、演算回路21からの出力には、不確定状態710と確定状態720とが含まれる。

<K1>、<D1>を演算した結果を<D2>と表記して、バスデータBus1に示している。

バスデータBus2は、遅延素子22による遅延分だけバスデータBus1を遅延させたものであるので、図3ではバスデータBus1が少し遅れた表記になっている。

NXOR素子31には、バスデータBus1とバスデータBus2が入力されるので、両バスデータの値が一致した区間だけ“H”となるセレクタ信号S1となる。

つまり、バスデータBus1の<D2>(確定状態のデータ)とバスデータBus2の<D2>(確定状態のデータ)が重なる区間、セレクタ信号S1は“H”となる。

セレクタ信号S1が“H”、セレクタ信号S2が“L”であれば、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が<K2>、<D2>を保持するので、データKeyは<K2>、データDataは<D2>となる。

このように、演算結果がループして、演算が進行して、データDataは、<D3>、<D4>、<D5>と変化していく。

イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

このように、データDataが順次変化して、最終結果が出力される。

【0032】

次に、異常なクロックCKが入力された場合の、タイミングチャートを図4に示す。

【0033】

図4において、タイミングT0が、規定周期を外れた異常なクロックCKの立ち上りタイミングである。

このタイミングT0におけるバスデータBus1の状態を見ると、<K2>、<D2>が演算回路21に入力されてから、データが安定するまでの時間を経ていない区間(すなわち、図14の不確定状態710)でクロックの立ち上りが来たため、ハッチングのバス表記の状態である。

このタイミングT0では、セレクタ信号S1が“L”、セレクタ信号S2が“L”であるので、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21に出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1は<D3>と確定し、遅延素子22の遅延量だけ遅れて、バスデータBus2も<D3>と確定する。

バスデータBus1の<D3>(確定状態のデータ)とバスデータBus2の<D3>(確定状態のデータ)が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0034】

なお、図2で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“L”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図4では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、異常なクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、フォールト攻撃は成立しない。

なお、異常なクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0035】

次に、外乱が発生して演算回路21が誤動作した場合の、タイミングチャートを図5に示す。

【0036】

バスデータBus1に<Damaged>と書かれた区間に演算回路21が誤動作したとしてタイミングチャートは書かれている。

誤動作している区間は、データは不安定で刻一刻と変化する(つまり、図14の不確定状態710となっている)ため、<Damaged>はハッチングで表記している。

この<Damaged>の区間に発生したクロックCKの立ち上りタイミングT0におけるバスデータBus1の状態は<Damaged>である。

そのため、このタイミングT0では、セレクタ信号S1が“L”、セレクタ信号S2が“L”である。

よって、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21に出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1は<D3>と確定し、遅延素子22の遅延量だけ遅れて、バスデータBus2も<D3>と確定する。

バスデータBus1の<D3>(確定状態のデータ)とバスデータBus2の<D3>(確定状態のデータ)が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0037】

なお、図2で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“L”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図5では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、誤動作が発生した区間のクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、誤動作による影響はない。

なお、誤動作が発生した区間のクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0038】

以上のように、実施の形態1では、遅延素子を設けて、演算回路のデータ出力が安定、すなわち、一致することを確認し、演算ループが回るようにした。

さらに、演算回路のデータ出力が不安定な区間に異常なクロックを入力するフォールト攻撃に対しては、演算回路に入力されているデータを、異常クロック入力後の次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、異常なクロックを使用するフォールト攻撃に対して耐性を有する効果がある。

さらに、実施の形態1では、正常時の演算時間が最も短く、異常時は演算時間が延びるのでフォールト攻撃に手間がかかるという効果もある。

【0039】

また、遅延素子を設けて、演算回路のデータ出力が安定、すなわち、一致することを確認し、演算ループが回るようにしたことにより、演算回路の誤動作に対しても耐性を有する。

つまり、意図的で有る無しに関わらず外乱により演算回路が誤動作し、その区間にクロックが発生した場合は、演算回路に入力されているデータを、誤動作の発生した次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、演算回路の誤動作に対して耐性を有する効果がある。

【0040】

実施の形態2.

以上の実施の形態1では、遅延素子を用いて演算回路のデータ出力が安定することを確認するようにしたものであるが、演算結果を直接比較するような場合においても、フォールト攻撃や誤動作に対して耐性を有する実施の形態を示す。

【0041】

図6は実施の形態2に係るデータ処理装置の回路構成例を示す。

これを用いて、フォールト攻撃や外乱による誤動作に対して耐性があることを示す。

【0042】

図6において、演算回路21は演算を行う組合せ回路であり、2系統ある。

つまり、図6では、演算回路21aと演算回路21bが存在する。

演算回路21aと演算回路21bは、それぞれ同時に、データDataとデータKeyとを並行して入力し、並行して同じ演算を行う。

演算回路21aは演算結果をバスデータBus1として出力し、演算回路21bは演算結果をバスデータBus2として出力する。

演算回路21aからのバスデータBus1の出力と演算回路21bからのバスデータBus2の出力は同時である。

正常時では、バスデータBus1の確定状態720のデータ値とバスデータBus2の確定状態720のデータ値は一致する。

演算回路21aは第1の演算部の例に相当し、演算回路21bは第2の演算部の例に相当する。

また、演算回路21aから出力されたバスデータBus1は第3のデータの例に相当し、演算回路21bから出力されたバスデータBus2は第4のデータの例に相当する。

なお、本実施の形態においても、データKeyが第1のデータの例であり、データDataが第2のデータの例である。

【0043】

セレクタ13は、入力データKIとデータKeyをセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ11は、セレクタ13からの信号をクロックCKのタイミングで保持して、データKeyとして出力するフリップフロップである。

セレクタ14は、入力データDI、データDataとバスデータBus1をセレクタ信号S1、セレクタ信号S2で切り替えるセレクタ回路である。

フリップフロップ12は、セレクタ14の出力をクロックCKのタイミングで保持し、データDataとして出力するフリップフロップである。

NXOR素子31は、バスデータBus1とバスデータBus2のNXORをとりセレクタ信号S1を出力する回路である。

イネーブル付フリップフロップ41は、イネーブル信号Eを判断し、クロックCKのタイミングでバスデータBus1を保持するイネーブル付フリップフロップである。

図2との差異は、遅延素子22が存在しない代わりに2つの演算回路21(演算回路21aと演算回路21b)が存在することであり、他の要素は、図2に示したものと同様である。

図1との対応は、フリップフロップ11、フリップフロップ12、セレクタ13、セレクタ14が切替部10に、2系統の演算回路21が演算部20に、NXOR素子31が比較部30に、イネーブル付フリップフロップ41が出力部40に相当する。

【0044】

次に正常な動作について、図7を用いて説明する。

図7は、図6の回路に正常なクロックCKが入力されたときのタイミングチャートである。

【0045】

入力データKIは、クロックCKに同期して、図に示すように、<K1>、<K2>、・・・、<Kn−1>と入力されるデータである。

入力データKIの生成回路は図6には図示されていない。

入力データDIは、<K1>と同じタイミングで<D1>が入力される。

その他のタイミングでは、特に意味を持たないので、<X>と示している。

セレクタ信号S1に関係なく、値が“H”のセレクタ信号S2が入力されると、セレクタ13は入力データKIを、セレクタ14は入力データDIを選択する。

ここで選択されたデータをフリップフロップ11、フリップフロップ12が保持するので、<K1>、<D1>が、1クロック遅れたタイミングで、データKey、データDataに現れる。

【0046】

演算回路21a及び演算回路21bにデータが入力されると演算が開始されるが、回路遅延によりある期間データが不安定で確定しないタイミングが存在する。

これを、バスデータBus1、バスデータBus2では、ハッチングのバス表記で示している。

この区間ではデータが刻一刻と変化している。

この不確定区間を過ぎるとデータが安定し、確定したデータが出力される。

<K1>、<D1>を演算した結果を<D2>と表記して、バスデータBus1、バスデータBus2に示している。

NXOR素子31には、バスデータBus1とバスデータBus2が入力されるので、両バスデータの値が一致した区間だけ“H”となるセレクタ信号S1となる。

つまり、バスデータBus1の<D2>(確定状態のデータ)とバスデータBus2の<D2>(確定状態のデータ)が重なる区間、セレクタ信号S1は“H”となる。

セレクタ信号S1が“H”、セレクタ信号S2が“L”であれば、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が<K2>、<D2>を保持するので、データKeyは<K2>、データDataは<D2>となる。

このように、演算結果がループして、演算が進行して、データDataは、<D3>、<D4>、<D5>と変化していく。

イネーブル信号Eが”H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

このように、データDataが順次変化して、最終結果が出力される。

【0047】

次に、異常なクロックCKが入力された場合の、タイミングチャートを図8に示す。

【0048】

図8において、タイミングT0が、規定周期を外れた異常なクロックCKの立ち上りタイミングである。

このタイミングT0におけるバスデータBus1、バスデータBus2の状態を見ると、<K2>、<D2>が演算回路1に入力されてから、データが安定するまでの時間を経ていない区間でクロックの立ち上りが来たため、ハッチングのバス表記の状態である。

このタイミングT0では、セレクタ信号S1が“L”、セレクタ信号S2が“L”であるので、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21a及び演算回路21bに出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1は<D3>と確定し、バスデータBus2も<D3>と確定する。

バスデータBus1の<D3>(確定状態のデータ)とバスデータBus2の<D3>(確定状態のデータ)が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0049】

なお、図6で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“L”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図8では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、異常なクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、フォールト攻撃は成立しない。

なお、異常なクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0050】

次に、外乱が発生して演算回路1が誤動作した場合の、タイミングチャートを図9に示す。

【0051】

バスデータBus1に<Damaged>と書かれた区間に一方の演算回路21が誤動作したとしてタイミングチャートは書かれている(図9では演算回路21aに誤動作が発生している)。

誤動作している区間は、データは不安定で刻一刻と変化するため、<Damaged>はハッチングのバス表記で示している。

この<Damaged>の区間に発生したクロックCKの立ち上りタイミングT0におけるバスデータBus1の状態は<Damaged>である。

一方、バスデータBus2の状態は<D3>である。

そのため、このタイミングT0では、セレクタ信号S1が”L”、セレクタ信号S2が”L”である。

よって、セレクタ13はデータKeyを、セレクタ14はデータDataを選択する。

よって、クロックCKの立ち上がり時に、フリップフロップ11、フリップフロップ12が、データKeyの<K2>、データDataの<D2>を保持することになる。

すなわち、タイミングT0以前のデータKey、データDataを維持し、タイミングT0以前のデータKey、データDataを演算回路21a及び演算回路21bに出力する。

タイミングT0後、データが不安定な区間を経て、バスデータBus1、バスデータBus2は<D3>と確定する。

バスデータBus1の<D3>とバスデータBus2の<D3>が重なっている間に、次のクロックCKのタイミングT1が発生する。

このとき、正常時と同じくセレクタ信号S1が“H”、セレクタ信号S2が“L”であるので、セレクタ13は入力データKIを、セレクタ14はバスデータBus1を選択する。

よって、データKeyは<K3>に、データDataは<D3>に変化する。

以後、正常時と同じく演算が進行し、イネーブル信号Eが“H”の区間で、クロックCKが立ち上がると、イネーブル付フリップフロップ41がバスデータBus1を保持し、<Dn>を出力する。

【0052】

なお、図6で図示していない入力データKIの生成回路は、セレクタ信号S1、セレクタ信号S2を監視しており、セレクタ信号S1が“H”、セレクタ信号S2が“L”のときに、クロックCKの立ち上りが発生した場合は、クロック立ち上りタイミング以前に出力していた入力データKIを、次のサイクルでも出力するものとする。

図9では、入力データKIにおいて、<K3>、<K3>と連続しているのが、これに相当する。

この結果、誤動作が発生した区間のクロックタイミングT0は無視されて、最終結果は正常な出力<Dn>となる。

つまり、誤動作による影響はない。

なお、誤動作が発生した区間のクロックタイミングT0は無視されるので、その分だけ最終結果が出力される時間は延びる。

【0053】

以上のように、実施の形態2では、演算回路を2系統設けて、両者の演算回路のデータ出力が安定すなわち、一致することを確認し、演算ループが回るようにした。

さらに、演算回路のデータ出力が不安定な区間に異常なクロックを入力するフォールト攻撃に対しては、演算回路に入力されているデータを、異常クロック入力後の次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、異常なクロックを使用するフォールト攻撃に対して耐性を有する効果がある。

さらに、実施の形態2では、正常時の演算時間が最も短く、異常時は演算時間が延びるのでフォールト攻撃に手間がかかるという効果もある。

【0054】

また、演算回路を2系統設けて、両者の演算回路のデータ出力が安定すなわち、一致することを確認し、演算ループが回るようにしたことにより、演算回路の誤動作に対しても耐性を有する。

つまり、意図的で有る無しに関わらず外乱により演算回路が誤動作し、その区間にクロックが発生した場合は、演算回路に入力されているデータを、誤動作の発生した次のクロックサイクルでも維持するようにループを制御し、同一の演算を再度行うようにするとともに、演算回路のデータ出力が安定、すなわち、一致したことを確認して、次の演算に移るようにしたので、演算回路の誤動作に対して耐性を有する効果がある。

【0055】

以上、実施の形態1及び実施の形態2では、

被演算データである入力データが入力され、演算結果が出力される演算部を中心とする演算装置であって、

演算部から、正常演算時に安定したデータが一致すると期待される複数の演算結果を出力し、その複数の演算結果が一致したことを確認し、次の演算を開始し、複数の演算結果が一致しない場合は、同一の演算を再度行う演算装置を説明した。

【0056】

また、実施の形態1及び実施の形態2では、

被演算データは、

1)切替部入力データ、

2)切替部出力データ、

3)演算部出力データ

を切り替える切替部の出力データであって、

切替部は、演算部からの複数の演算結果を比較した結果に基づき、上記1)〜3)のデータを切り替え、

その複数の演算結果が一致した場合は、次の演算を開始し、

複数の演算結果が一致しない場合は、同一の演算を再度行う演算装置を説明した。

【0057】

また、実施の形態1では、

演算部の複数の演算結果は、演算回路からの出力を遅延させることにより生成することを説明した。

【0058】

また、実施の形態2では、

演算部の複数の演算結果は、演算回路を複数設けるにより生成することを説明した。

【符号の説明】

【0059】

10 切替部、11 フリップフロップ、12 フリップフロップ、13 セレクタ、14 セレクタ、20 演算部、21 演算回路、22 遅延素子、30 比較部、31 NXOR素子、40 出力部、41 イネーブル付フリップフロップ。

【特許請求の範囲】

【請求項1】

繰り返し到来する出力タイミングの度に第1のデータと第2のデータとを並行して出力する切替部と、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いた演算を行って第3のデータと第4のデータを生成し、生成した第3のデータと第4のデータとを並行して出力する演算部と、

前記演算部から出力された第3のデータと第4のデータとを並行して入力し、同じタイミングで入力した第3のデータのデータ値と第4のデータのデータ値とを比較し、第3のデータと第4のデータとの間でデータ値が一致する場合は、前記切替部に一致信号を出力し、第3のデータと第4のデータとの間でデータ値が一致しない場合は、前記切替部に不一致信号を出力する比較部とを有し、

前記切替部は、

前記演算部から第3のデータが出力される度に、出力された第3のデータを入力し、

出力タイミングが到来する度に、到来した出力タイミングにおいて前記比較部から入力した信号が一致信号であるか不一致信号であるかを判断し、

前記比較部から入力した信号が一致信号である場合は、前記演算部に出力済の第1のデータと異なるデータを新たな第1のデータとして前記演算部に出力するとともに、前記演算部から入力した第3のデータを新たな第2のデータとして出力し、

前記比較部から入力した信号が不一致信号である場合は、前記演算部に出力済の第1のデータと第2データとを、再度、前記演算部に出力することを特徴とするデータ処理装置。

【請求項2】

前記切替部は、

到来した出力タイミングにおいて前記比較部から入力した信号が一致信号である場合は、前回の出力タイミングにおいて前記演算部に出力した第1のデータと異なるデータを新たな第1のデータとして前記演算部に出力するとともに、前記演算部から直近に入力した第3のデータを新たな第2のデータとして出力し、

到来した出力タイミングにおいて前記比較部から入力した信号が不一致信号である場合は、前回の出力タイミングにおいて前記演算部に出力した第1のデータと第2データとを、再度、前記演算部に出力することを特徴とする請求項1に記載のデータ処理装置。

【請求項3】

前記演算部は、

正常時は、

データ値が一定しない不確定状態の第3のデータを生成し、出力し、不確定状態の第3のデータの生成及び出力の後に、データ値が一定している確定状態の第3のデータを生成し、出力し、

データ値が一定しない不確定状態の第4のデータを生成し、出力し、不確定状態の第4のデータの生成及び出力の後に、データ値が一定している確定状態の第4のデータを生成し、出力し、

前記比較部は、

確定状態の第3のデータと確定状態の第4のデータとを同じタイミングで入力し、確定状態の第3のデータのデータ値と確定状態の第4のデータのデータ値とを比較した場合は、第3のデータと第4のデータとの間でデータ値が一致し、前記切替部に一致信号を出力し、

確定状態の第3のデータと確定状態の第4のデータとの組み合わせ以外の組み合わせでデータ値を比較した場合は、第3のデータと第4のデータとの間でデータ値が一致せず、前記切替部に不一致信号を出力することを特徴とする請求項1又は2に記載のデータ処理装置。

【請求項4】

前記比較部は、

前記切替部の出力タイミングが規定周期ごとに到来している場合は、規定周期ごとの各出力タイミングにおいて、確定状態の第3のデータのデータ値と確定状態の第4のデータのデータ値とを比較することになり、前記切替部に一致信号を出力し、

前記切替部の出力タイミングが規定周期から外れた場合は、規定周期から外れた出力タイミングにおいて、確定状態の第3のデータと確定状態の第4のデータとの組み合わせ以外の組み合わせでデータ値を比較することになり、前記切替部に不一致信号を出力することを特徴とする請求項3に記載のデータ処理装置。

【請求項5】

前記演算部は、

異常が発生した場合は、第3のデータ及び第4のデータの少なくともいずれかにおいて、確定状態のデータが生成されず、不確定状態のデータのみを出力し、

前記比較部は、

前記演算部で異常が発生した場合は、前記切替部の出力タイミングが規定周期ごとに到来している場合であっても、規定周期ごとの各出力タイミングにおいて、確定状態の第3のデータと確定状態の第4のデータとの組み合わせ以外の組み合わせでデータ値を比較することになり、前記切替部に不一致信号を出力することを特徴とする請求項3又は4に記載のデータ処理装置。

【請求項6】

前記演算部は、

第1のデータと第2のデータとを用いた演算を行って第3のデータを生成し、生成した第3のデータを前記比較部に出力するとともに、生成した第3のデータを遅延させ、遅延後の第3のデータを第4のデータとして、第3のデータの出力と並行して前記比較部に出力することを特徴とする請求項1〜5のいずれかに記載のデータ処理装置。

【請求項7】

前記演算部は、

第1の演算部と、第2の演算部とを有し、

前記切替部は、

出力タイミングごとに、前記第1の演算部と前記第2の演算部の各々に、同時に、第1のデータと第2のデータとを並行して出力し、

前記第1の演算部は、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いた演算を行って第3のデータを生成し、生成した第3のデータを前記比較部に出力し、

前記第2の演算部は、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いて前記第1の演算部と同じ演算を行って第4のデータを生成し、生成した第4のデータを第3のデータの出力と並行して前記比較部に出力することを特徴とする請求項1〜5のいずれかに記載のデータ処理装置。

【請求項8】

前記切替部は、

前記演算部に出力した第1のデータと第2のデータをフィードバック入力し、

到来した出力タイミングにおいて前記比較部から入力した信号が不一致信号である場合は、フィードバック入力した、前記演算部に出力済の第1のデータと第2データを、再度、前記演算部に出力することを特徴とする請求項1〜7のいずれかに記載のデータ処理装置。

【請求項9】

前記切替部は、

暗号処理又は復号処理に用いられる鍵データを第1のデータとして前記演算部に出力するとともに、暗号処理又は復号処理の対象となるデータを第2のデータとして前記演算部に出力し、

前記演算部は、

第1のデータを用いて第2のデータを暗号化する演算又は復号する演算を行い、暗号化後の第2のデータ又は復号後の第2のデータを第3のデータ及び第4のデータとして前記比較部に出力することを特徴とする請求項1〜8のいずれかに記載のデータ処理装置。

【請求項1】

繰り返し到来する出力タイミングの度に第1のデータと第2のデータとを並行して出力する切替部と、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いた演算を行って第3のデータと第4のデータを生成し、生成した第3のデータと第4のデータとを並行して出力する演算部と、

前記演算部から出力された第3のデータと第4のデータとを並行して入力し、同じタイミングで入力した第3のデータのデータ値と第4のデータのデータ値とを比較し、第3のデータと第4のデータとの間でデータ値が一致する場合は、前記切替部に一致信号を出力し、第3のデータと第4のデータとの間でデータ値が一致しない場合は、前記切替部に不一致信号を出力する比較部とを有し、

前記切替部は、

前記演算部から第3のデータが出力される度に、出力された第3のデータを入力し、

出力タイミングが到来する度に、到来した出力タイミングにおいて前記比較部から入力した信号が一致信号であるか不一致信号であるかを判断し、

前記比較部から入力した信号が一致信号である場合は、前記演算部に出力済の第1のデータと異なるデータを新たな第1のデータとして前記演算部に出力するとともに、前記演算部から入力した第3のデータを新たな第2のデータとして出力し、

前記比較部から入力した信号が不一致信号である場合は、前記演算部に出力済の第1のデータと第2データとを、再度、前記演算部に出力することを特徴とするデータ処理装置。

【請求項2】

前記切替部は、

到来した出力タイミングにおいて前記比較部から入力した信号が一致信号である場合は、前回の出力タイミングにおいて前記演算部に出力した第1のデータと異なるデータを新たな第1のデータとして前記演算部に出力するとともに、前記演算部から直近に入力した第3のデータを新たな第2のデータとして出力し、

到来した出力タイミングにおいて前記比較部から入力した信号が不一致信号である場合は、前回の出力タイミングにおいて前記演算部に出力した第1のデータと第2データとを、再度、前記演算部に出力することを特徴とする請求項1に記載のデータ処理装置。

【請求項3】

前記演算部は、

正常時は、

データ値が一定しない不確定状態の第3のデータを生成し、出力し、不確定状態の第3のデータの生成及び出力の後に、データ値が一定している確定状態の第3のデータを生成し、出力し、

データ値が一定しない不確定状態の第4のデータを生成し、出力し、不確定状態の第4のデータの生成及び出力の後に、データ値が一定している確定状態の第4のデータを生成し、出力し、

前記比較部は、

確定状態の第3のデータと確定状態の第4のデータとを同じタイミングで入力し、確定状態の第3のデータのデータ値と確定状態の第4のデータのデータ値とを比較した場合は、第3のデータと第4のデータとの間でデータ値が一致し、前記切替部に一致信号を出力し、

確定状態の第3のデータと確定状態の第4のデータとの組み合わせ以外の組み合わせでデータ値を比較した場合は、第3のデータと第4のデータとの間でデータ値が一致せず、前記切替部に不一致信号を出力することを特徴とする請求項1又は2に記載のデータ処理装置。

【請求項4】

前記比較部は、

前記切替部の出力タイミングが規定周期ごとに到来している場合は、規定周期ごとの各出力タイミングにおいて、確定状態の第3のデータのデータ値と確定状態の第4のデータのデータ値とを比較することになり、前記切替部に一致信号を出力し、

前記切替部の出力タイミングが規定周期から外れた場合は、規定周期から外れた出力タイミングにおいて、確定状態の第3のデータと確定状態の第4のデータとの組み合わせ以外の組み合わせでデータ値を比較することになり、前記切替部に不一致信号を出力することを特徴とする請求項3に記載のデータ処理装置。

【請求項5】

前記演算部は、

異常が発生した場合は、第3のデータ及び第4のデータの少なくともいずれかにおいて、確定状態のデータが生成されず、不確定状態のデータのみを出力し、

前記比較部は、

前記演算部で異常が発生した場合は、前記切替部の出力タイミングが規定周期ごとに到来している場合であっても、規定周期ごとの各出力タイミングにおいて、確定状態の第3のデータと確定状態の第4のデータとの組み合わせ以外の組み合わせでデータ値を比較することになり、前記切替部に不一致信号を出力することを特徴とする請求項3又は4に記載のデータ処理装置。

【請求項6】

前記演算部は、

第1のデータと第2のデータとを用いた演算を行って第3のデータを生成し、生成した第3のデータを前記比較部に出力するとともに、生成した第3のデータを遅延させ、遅延後の第3のデータを第4のデータとして、第3のデータの出力と並行して前記比較部に出力することを特徴とする請求項1〜5のいずれかに記載のデータ処理装置。

【請求項7】

前記演算部は、

第1の演算部と、第2の演算部とを有し、

前記切替部は、

出力タイミングごとに、前記第1の演算部と前記第2の演算部の各々に、同時に、第1のデータと第2のデータとを並行して出力し、

前記第1の演算部は、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いた演算を行って第3のデータを生成し、生成した第3のデータを前記比較部に出力し、

前記第2の演算部は、

前記切替部から出力された第1のデータと第2のデータとを並行して入力し、入力した第1のデータと第2のデータとを用いて前記第1の演算部と同じ演算を行って第4のデータを生成し、生成した第4のデータを第3のデータの出力と並行して前記比較部に出力することを特徴とする請求項1〜5のいずれかに記載のデータ処理装置。

【請求項8】

前記切替部は、

前記演算部に出力した第1のデータと第2のデータをフィードバック入力し、

到来した出力タイミングにおいて前記比較部から入力した信号が不一致信号である場合は、フィードバック入力した、前記演算部に出力済の第1のデータと第2データを、再度、前記演算部に出力することを特徴とする請求項1〜7のいずれかに記載のデータ処理装置。

【請求項9】

前記切替部は、

暗号処理又は復号処理に用いられる鍵データを第1のデータとして前記演算部に出力するとともに、暗号処理又は復号処理の対象となるデータを第2のデータとして前記演算部に出力し、

前記演算部は、

第1のデータを用いて第2のデータを暗号化する演算又は復号する演算を行い、暗号化後の第2のデータ又は復号後の第2のデータを第3のデータ及び第4のデータとして前記比較部に出力することを特徴とする請求項1〜8のいずれかに記載のデータ処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−38488(P2013−38488A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−170807(P2011−170807)

【出願日】平成23年8月4日(2011.8.4)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月4日(2011.8.4)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]