データ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法

【課題】複数のPEとメモリコントローラ部とラインバッファメモリなどの記憶手段とを利用して簡単構成かつ単純な処理でデータを圧縮伸張することができるデータ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法を提供する。

【解決手段】GP2が、隣接する左隣の汎用レジスタの値と比較して同じ値の場合は制御コードを0に、異なる値の場合は制御コードを1に設定し、その制御コードに基づいて汎用レジスタのデータをラインバッファメモリ7にライトし、ライトしたデータを倍率2倍で汎用レジスタに書き戻し、制御コードの0の連続数をカウントしてラインバッファメモリ7にライトし、そのカウント数を倍率2倍で汎用レジスタに書き戻しデータとカウント数とが交互に並ぶように合成して圧縮データを生成する。

【解決手段】GP2が、隣接する左隣の汎用レジスタの値と比較して同じ値の場合は制御コードを0に、異なる値の場合は制御コードを1に設定し、その制御コードに基づいて汎用レジスタのデータをラインバッファメモリ7にライトし、ライトしたデータを倍率2倍で汎用レジスタに書き戻し、制御コードの0の連続数をカウントしてラインバッファメモリ7にライトし、そのカウント数を倍率2倍で汎用レジスタに書き戻しデータとカウント数とが交互に並ぶように合成して圧縮データを生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、1つの演算命令により複数の画像データ等を並列処理するSIMD(Single Instruction-stream Multiple Data-stream)型マイクロプロセッサを用いてデータ圧縮および伸張を行うデータ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法に関する。

【背景技術】

【0002】

近年、デジタル複写機やファクリミリ装置等において、画素数を増加させて解像度を上げたり、或いはカラー対応にするなど画質の向上が図られている。 そして、この画質の向上に伴い処理すべきデータ数が増加している。

【0003】

ところで、デジタル複写機やファクリミリ装置等におけるデータ処理は全ての画素に対して同じ演算処理を施すことが一般的に多い。 そこで、1つの命令で複数のデータに対して同時に同じ演算処理を行うSIMD方式のマイクロプロセッサが用いられるようになっている。 通常、SIMD方式のマイクロプロセッサを用いて画像処理を行う場合、主走査方向にプロセッサエレメント(PE)を展開する。

【0004】

この種のSIMD型マイクロプロセッサとして、特許文献1に記載の信号処理装置が提案されている。特許文献1においては、シングルポートメモリ(RAM)を用いることで回路規模の増加を抑えながら、同時に変倍機能もメモリコントローラに内蔵可能とした簡単な構成のSIMD型マイクロプロセッサを用いた信号処理装置が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、高画質化、高速化が進むことによって扱う画像データ量も飛躍的に大きくなってきている。例えば、印字解像度という観点では、従来は300dpi(dot per inch)程度であったが、最新の記録装置では3600dpiという機器も登場し、従来に比べて100倍以上のデータ量が必要となっている。 従って、データ帯域は従来の100倍以上必要な状況になってきており、データ圧縮技術の重要性が高まってきている。

【0006】

画像劣化のない可逆圧縮技術としては、ファクシミリ等で用いられるMH(ハフマン符号化方式:一次元圧縮法によるG3ファクシミリの標準符号化方式)、MR(二次元圧縮法によるG3ファクシミリではオプションの符号化方式)、MMR(MR符号化方式の変形で、G4ファクシミリの標準符号化方式)や、コンピュータで扱うテキストファイルやバイナリファイルに用いられるLZ方式等が挙げられる。 また、国際標準である算術符号化を用いたJPEG(Joint Photographic Experts Group)方式やJBIG(Joint Bi-level Image Experts Group)方式もある。

【0007】

しかしながら、いずれも画像データを順に処理する逐次的な処理を必要としており、特許文献1などに記載されたSIMD型マイクロプロセッサで実現するには容易ではなく不向きな圧縮形態であるという問題があった。

【0008】

本発明はかかる問題を解決することを目的としている。

【0009】

すなわち、本発明は、複数のPEとメモリコントローラ部とラインバッファメモリなどの記憶手段とを利用して簡単構成かつ単純な処理でデータを圧縮および伸張することができるデータ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法を提供することを目的としている。

【課題を解決するための手段】

【0010】

上記課題を解決するためになされた請求項1に記載された発明は、複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ圧縮装置において、前記複数の汎用レジスタに、同じアドレスの前記PEの汎用レジスタ上のデータに対応させた制御コードを格納する制御コード格納領域を設け、前記メモリコントローラ部が、前記制御コード格納領域を参照して前記制御コードに従い前記汎用レジスタ上のデータを前記記憶手段にライト可能とし、前記汎用レジスタ上のデータを前記PEのアドレス順に読み出して該データが予め定めた特定の値の場合にカウントアップするとともに他の値の場合に前記特定の値のカウント値を前記記憶手段にライト可能とするように構成され、一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に前記制御コードを前記特定の値に設定させて不一致の場合に前記制御コードを前記他の値に設定させ、次に、前記メモリコントローラ部に、前記制御コードに従って前記PEの前記アドレス順に前記汎用レジスタ上のデータを前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、該ライトしたデータを前記記憶手段からリードさせて前記PEの前記汎用レジスタ上に格納させ(以下、この格納されたデータを書き戻しデータという)、次に、前記メモリコントローラ部に、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納させ、次に、前記メモリコントローラ部に、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納させて前記汎用レジスタ上のデータを圧縮するデータ圧縮制御部を有していることを特徴とするデータ圧縮装置である。

【0011】

請求項2に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されていることを特徴とするものである。

【0012】

請求項3に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成され、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とするものである。

【0013】

請求項4に記載された発明は、請求項1乃至3のうちいずれか一項に記載のデータ圧縮装置で圧縮されたデータを伸張するデータ伸張装置であって、前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成するように構成され、前記メモリコントローラ部に、前記圧縮データが格納されている前記汎用レジスタを読み出させて、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成させて伸張データとして前記記憶手段にライトさせる前記データ伸張制御部を有していることを特徴とするデータ伸張装置である。

【0014】

請求項5に記載された発明は、複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ処理装置のデータ圧縮方法において、一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に当該データに対応して設定される制御コードを予め定めた特定の値に設定して不一致の場合に前記制御コードを他の値に設定する第一の工程と、前記メモリコントローラ部が、前記制御コードが前記他の値が設定されている前記PEの前記汎用レジスタ上のデータを前記アドレス順に前記記憶手段にライトする第二の工程と、前記メモリコントローラ部が、前記第二の工程でライトしたデータを前記記憶手段からリードして前記PEの前記汎用レジスタ上に格納する(以下、この格納されたデータを書き戻しデータという)第三の工程と、前記メモリコントローラ部が、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトする第四の工程と、前記メモリコントローラ部が、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納する第五の工程と、前記メモリコントローラ部が、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納する第六の工程と、を順次実行することを特徴とするデータ圧縮方法である。

【0015】

請求項6に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納することを特徴とするものである。

【0016】

請求項7に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納し、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とするものである。

【0017】

請求項8に記載された発明は、請求項5乃至7のうちいずれか一項に記載のデータ圧縮方法で圧縮されたデータを伸張するデータ伸張方法であって、前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成し、前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成されて伸張データとして前記記憶手段にライトすることを特徴とするデータ伸張方法である。

【発明の効果】

【0018】

請求項1に記載の発明によれば、メモリコントローラ部に簡単な構成の回路を追加し、例えばグローバルプロセッサなどをデータ圧縮伸張制御部として動作させることで、複数のPEとメモリコントローラ部と記憶手段とを用いて効率的にデータの圧縮を行うことができる。

【0019】

請求項2に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順に同じデータを2回ずつ重複してPEの汎用レジスタ上に格納しているので、例えば、奇数アドレスのPEの汎用レジスタを書き戻しデータ、偶数アドレスのPEの汎用レジスタをカウント値として合成すれば、書き戻しアドレスとカウント値とを交互に並べることができる。

【0020】

請求項3に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順で1つおきのPEの汎用レジスタ上に格納し、書き戻しデータとカウント値はアドレスが1ずれているので、例えば、書き戻しデータを奇数アドレスのPEの汎用レジスタに格納して、カウント値を偶数アドレスのPEの汎用レジスタに格納すれば、それらを単純に合成するだけで、書き戻しアドレスとカウント値とを交互に並べることができる。

【0021】

請求項4に記載の発明によれば、メモリコントローラ部に簡単な構成の回路を追加し、例えばグローバルプロセッサなどをデータ圧縮伸張制御部として動作させることで、複数のPEとメモリコントローラ部と記憶手段とを用いて効率的にデータの伸張を行うことができる。

【0022】

請求項5に記載の発明によれば、データに制御コードを付加し、メモリコントローラを用いたリードライト処理を行うことで、複数のPEとメモリコントローラ部と記憶手段とを用いてデータの圧縮を効率的に行うことができる。

【0023】

請求項6に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順に同じデータを2回ずつ重複してPEの汎用レジスタ上に格納しているので、例えば、奇数アドレスのPEの汎用レジスタを書き戻しデータ、偶数アドレスのPEの汎用レジスタをカウント値として合成すれば、書き戻しアドレスとカウント値とを交互に並べることができる。

【0024】

請求項7に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順で1つおきのPEの汎用レジスタ上に格納し、書き戻しデータとカウント値はアドレスが1ずれているので、例えば、書き戻しデータを奇数アドレスのPEの汎用レジスタに格納して、カウント値を偶数アドレスのPEの汎用レジスタに格納すれば、それらを単純に合成するだけで、書き戻しアドレスとカウント値とを交互に並べることができる。

【0025】

請求項8に記載の発明によれば、データに制御コードを付加し、メモリコントローラを用いたリードライト処理を行うことで、複数のPEとメモリコントローラ部と記憶手段とを用いてデータの伸張を効率的に行うことができる。

【図面の簡単な説明】

【0026】

【図1】本発明の一実施形態にかかるデータ伸張装置およびデータ伸張装置の構成図である。

【図2】図1に示されたGPとPEコアの一部分を抜き出した概略図である。

【図3】図1に示されたメモリコントローラの構成図である。

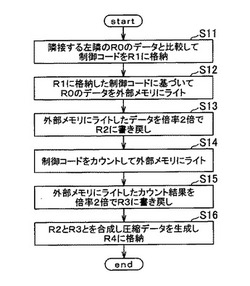

【図4】図1に示されたデータ圧縮装置のデータ圧縮動作を示したフローチャートである。

【図5】汎用レジスタに圧縮前のデータを格納した状態を示した説明図である。

【図6】図5に示された汎用レジスタに制御コードを加えた状態を示した説明図である。

【図7】データをラインバッファメモリから書き戻した状態を示した説明図である。

【図8】制御コードをラインバッファメモリから書き戻した状態を示した説明図である。

【図9】データと制御コードを合成した状態を示した説明図である。

【図10】図1に示されたデータ伸張装置のデータ伸張動作を示したフローチャートである。

【発明を実施するための形態】

【0027】

以下、本発明の一実施形態を、図1ないし図10を参照して説明する。図1は、本発明の一実施形態にかかるデータ圧縮装置およびデータ伸張装置の構成図である。図2は、図1に示されたGPとPEコアの一部分を抜き出した概略図である。図3は、図1に示されたメモリコントローラの構成図である。図4は、図1に示されたデータ圧縮装置のデータ圧縮動作を示したフローチャートである。図5は、汎用レジスタに圧縮前のデータを格納した状態を示した説明図である。図6は、図5に示された汎用レジスタに制御コードを加えた状態を示した説明図である。図7は、データをラインバッファメモリから書き戻した状態を示した説明図である。図8は、制御コードをラインバッファメモリから書き戻した状態を示した説明図である。図9は、データと制御コードを合成した状態を示した説明図である。図10は、図1に示されたデータ伸張装置のデータ伸張動作を示したフローチャートである。

【0028】

図1に本発明の一実施形態にかかるデータ圧縮装置およびデータ伸張装置としてのデータ圧縮伸張装置1を示す。図1に示したデータ圧縮伸張装置1は、グローバルプロセッサ(GP)2と、PEコア3と、PEIF4と、メモリコントローラ6と、ラインバッファメモリ7と、を備えている。

【0029】

データ圧縮制御部としてのGP2は、所謂SISD(Single Instruction-stream, Single Data-stream)タイプのプロセッサである。GP2にはSIMD型マイクロプロセッサ8のプログラム格納用のプログラムRAMと演算データ格納用のデータRAMとが内蔵されている。さらに、プログラムのアドレスを保持するプログラムカウンタ(PC)、演算処理のデータ格納のための汎用レジスタであるG0〜G3レジスタ、レジスタ退避、復帰時に退避先データRAMのアドレスを保持しているスタックポインタ(SP)、サブルーチンコール時にコール元のアドレスを保持するリンクレジスタ(LS)、同様に割り込み(IRQ)時とマスク不可割り込み(NMI)時の分岐元アドレスを保持するLI、LNレジスタ、プロセッサの状態を保持しているプロセッサステータスレジスタ(P)を備えている。これらのレジスタと図示していない命令デコーダ、ALU、メモリ制御回路、割り込み制御回路、外部I/O制御回路、GP演算制御回路を使用してGP2内で実行される命令であるGP命令の実行が行われる。また、PEコア3に対する命令であるPE命令実行時は命令デコーダ、レジスタファイル制御回路、PE演算制御回路を使用して、PEコア3内のレジスタファイル31の制御と演算アレイ32の制御を行う。

【0030】

PEコア3は、図2に示すようにレジスタファイル31と、演算アレイ32と、から構成されている。レジスタファイル31は、PE命令で処理されるデータを保持している。PE命令は、SIMDタイプの命令であり、レジスタファイル31に保持されている複数のデータに対して同時に同じ処理を行う。このレジスタファイル31からのデータの読み出し/書き込みの制御はGP2からの制御によって行われる。読み出されたデータは演算アレイ32に送られ、演算アレイ32での演算処理後に再度レジスタファイル31に書き込まれる。また、レジスタファイル31は、GP2とPEコア3と後述するPEIF4とから構成されるプロセッサコア5の外部からのアクセスが可能であり、GP2の制御とは別に外部から特定のレジスタ33に対して読み出し/書き込みが行われる。

【0031】

レジスタファイル31には、1つのPE単位に8ビットの汎用レジスタとしてのレジスタ33を例えば32本備えており、PEが例えば512PEの場合は512組分がアレイ構成になっている。32本のレジスタ33は、1つのPE内でR0、R1、R2、...R31と呼び区別される。それぞれのレジスタ33は演算アレイ32に対して1つの読み出しポートと1つの書き込みポートとを備えており、8ビットのリード/ライト兼用のバスで演算アレイ32からアクセスされる。32本のレジスタ33の複数本をプロセッサコア5の外部からアクセス可能として、外部からクロックとアドレス、リード/ライト制御を入力することで任意のレジスタ33を読み書きできるようにしている。レジスタ33の外部からのアクセスは、1つの外部ポートで各PEの1つのレジスタ33がアクセス可能であり外部から入力されたアドレスでPEの番号(512PEの場合は0〜511)を指定する。このポートを使用して後述するメモリコントローラ6がラインバッファメモリ7とのアクセスを行う。したがって複数の外部ポートを設けることで一度に複数のPEのレジスタ33がアクセス可能となる。

【0032】

演算アレイ32は、マルチプレクサ34と、シフタ35と、ALU36と、Aレジスタ37と、Fレジスタ38と、フラグレジスタ39と、を備え、PE命令の演算処理が行われる。また、処理の制御はすべてGP2から行われる。

【0033】

演算アレイ32におけるPE命令による演算は、基本的にレジスタファイル31から読み出されたデータをALU36の片側の入力としてもう片側にはAレジスタ37の内容を入力として結果をAレジスタ37に格納する。したがって、Aレジスタ37とレジスタファイル31のレジスタ33との演算が行われることとなる。

【0034】

レジスタファイル31と演算アレイ32との接続には7to1のマルチプレクサ34が設けられており、PE方向で左に1、2、3つ離れたデータと右に1、2、3つ離れたデータ、中央(自PE)のデータを演算対象として選択している。マルチプレクサ34は、自PEのレジスタファイル31に接続されるとともに、両隣3つのPEのレジスタファイル31にも接続されている。このマルチプレクサ34は7つのPEから1つを選択し、その選択したPEにおけるレジスタ33で保持されているデータをALU36へ送る。或いはALU36で演算処理されたデータを、選択したPEにおけるレジスタ33へ送る。これによって、隣のPEにおけるレジスタ33で保持されているデータを利用した演算処理が可能になり、SIMD型マイクロプロセッサ8の演算処理能力を高めることができる。

【0035】

シフタ35は、レジスタファイル31の8ビットのデータを任意ビットの左シフト演算を行ってALU36に入力する。

【0036】

ALU36は、シフタ35から送られてきたデータと、Aレジスタ37に保持されているデータとに基づき算術論理演算を行う。なお、本実施形態では、ALU36は16ビットのデータに対応できるものとして扱うが、データに応じて適宜変更しても問題ない。演算処理されたデータは、Aレジスタ37に保持され、シフタ35へ転送されたり、或いはGP2の汎用レジスタなどへ転送される。

【0037】

さらに、演算アレイ32は、図示していない8ビットの条件レジスタ(T)により、PEごとに演算実行の無効/有効が制御されており、特定のPEだけを演算対象として選択できるように構成している。

【0038】

上述したように、レジスタ33のR0〜R32、マルチプレクサ34、シフタ35、ALU36、Aレジスタ37、Fレジスタ38、フラグレジスタ39で1つのPE3aを構成している(図2の点線で囲まれた範囲)。

【0039】

PEIF4は、レジスタファイル31へのプロセッサコア5外部からのアクセスを制御する。

【0040】

メモリコントローラ6は、図3に示すように、PEIFコントローラ61と、ラインバッファコントローラ62と、コマンド発行部63と、アドレス生成部64と、FIFO65と、メイン制御部66と、を備えている。

【0041】

PEIFコントローラ61は、レジスタファイル31へのアドレス、アクセスクロック、リード/ライトコントロール信号の生成およびデータの入出力バッファなどを行う。ラインバッファコントローラ62は、ラインバッファメモリ7をコントロールする。コマンド発行部63は、ラインバッファコントローラ62へのリードコマンド、ライトコマンドを発行する。リードコマンド、ライトコマンドはリードもしくはライトの識別とアクセスを行うスタートアドレスとしてページメモリ上の論理アドレス、さらにアクセスバースト数などで構成される。

【0042】

アドレス生成部64は、後述するメイン制御部66からのコントロールでコマンド発行部63に対してアクセスを行うためのスタートアドレス情報を生成する。FIFO65は、ラインバッファコントローラ62とPEIFコントローラ61への入出力データを管理するバッファとして機能させるFIFO(First In First Out)方式のバッファである。メイン制御部66は、メモリコントローラ6を全体的に制御する。メイン制御部66はGP2からの命令により動作する。

【0043】

記憶手段としてのラインバッファメモリ7は、SIMD型マイクロプロセッサ8の外部に接続されるページメモリであり、例えばSRAMなどで構成される。

【0044】

そして、本実施形態では、GP2とPEコア3とPEIF4から構成されるプロセッサコア5にメモリコントローラ6を加えてSIMD型マイクロプロセッサ8を構成している。なお、SIMD型マイクロプロセッサ8はこの構成に限らず、プロセッサコア5の部分のみをSIMD型マイクロプロセッサとしてメモリコントローラ6がプロセッサの外付け回路としてもよい。

【0045】

前述したSIMD型マイクロプロセッサ8では、メモリコントローラ6によりラインバッファメモリ7とデータ入出力を行うレジスタファイル31(PE3a)は、1つのPE3aを単位としてメモリコントローラ6からアクセスする順にアドレスを割り振って管理されている。例えば、SIMD型マイクロプロセッサ8が512個のPE3aを備えているとすると、PE0〜PE511とアドレスを割り振って管理する。これらレジスタファイル31内のレジスタ33は1つのPE3a内にいくつも持ってよい。その1つのPE3a内の複数のレジスタ33間でデータのやりとりは自由に行うことができる構成とする。それらをR0,R1,R2・・・と順に呼ぶこととする。すなわち、R0はPE0〜PE511の512個の汎用レジスタ(レジスタ33)で構成され、R1以降も同様にPE0〜PE511の512個ずつの汎用レジスタ(レジスタ33)で構成されている。

【0046】

ここで、上述したメモリコントローラ6の有する機能を説明する。まず、汎用レジスタ上のデータを一定の倍率で間引いてラインバッファメモリ7上にライトする機能を持つ。例えば、1/2の倍率であれば偶数アドレスを持つPE3aの汎用レジスタのデータのみをラインバッファメモリ7にライトする。これはGP2が予めメイン制御部66に行った設定にしたがってPEIFコントローラ61を制御して偶数アドレスを持つPE3aの汎用レジスタのデータのみを読み出させて、ラインバッファコントローラ62にラインバッファメモリ7へライトさせる。同様に倍率が1/4であればPE3aのアドレスの下位2bitが“00”の場合にそのPE3aの汎用レジスタのデータをラインバッファメモリ7にライトする。このようにして元データを間引いてラインバッファメモリ7にライトできる。倍率に関しては予め決められた倍率で外部からGP2を介しての設定によって選択可能であるものとする。

【0047】

次に、上述した機能と同様に汎用レジスタ上のデータを間引いてライトする機能であるが、汎用レジスタ上のデータを制御コードとして、その制御コードに従って別の汎用レジスタのデータを間引いてラインバッファメモリ7にライトする機能を持つ。例えば、図6のR0のデータをR1のデータを制御コードとして、制御コードが“1”のPE3aのR0のデータはラインバッファメモリ7にライトし、“0”の場合にはラインバッファメモリ7にライトしないようにしてデータを間引く。これはPEIFコントローラ61がR0とR1のデータを読み出してR1の内容に基づいてR0をFIFO65に格納するか否かを選択している。すなわち、図6の場合には間引いた後にラインバッファメモリ7にライトされるデータは、A,B,C,D,E,F,G・・・となる。なお、上述した1/2、1/4の倍率に間引く際もこの制御コードを用いてもよい。

【0048】

次に、メモリコントローラ6の別の機能として、ラインバッファメモリ7上のデータを一定の倍率で重複して汎用レジスタ上にライトする機能を持つ。例えば、2倍であればラインバッファメモリ7上のデータをPE3aの汎用レジスタに対して2度ずつライトする機能である。例えば、ラインバッファメモリ7から順にA,B,C,D,E,F,G・・・とデータが読み出され、それをR0にライトする場合、PE0とPE1にAを、PE2とPE3にBを、PE4とPE5にCを、PE6とPE7にDを、PE8とPE9にEを、PE10とPE11にFを、PE12とPE13にGをライトする。これはラインバッファコントローラ62が読み出したデータをGP2が予めメイン制御部66に行った設定にしたがってPEIFコントローラ61を制御して1つのデータにつき2つのPE3aの汎用レジスタへライトさせる。同様に倍率が4倍であれば、ラインバッファメモリ7上のデータをPE3aの汎用レジスタに対して4度ずつライトする。倍率に関しては予め決められた倍率で外部からGP2を介しての設定によって選択可能であるものとする。

【0049】

さらに、メモリコントローラ6の別の機能として、汎用レジスタ上の制御コードのうち予め定めた特定の値の場合はカウントアップし、特定の値とは異なる他の値の場合はそれまでのカウント値をラインバッファメモリ7上に記録してカウント値を“1”に初期化する機能を持つ。例えば、制御コードを2値のデータ“0”、“1”とすると、“0”の場合には特定の値としてカウントアップし、“1”の場合には他の値としてそれまでのカウント値をラインバッファメモリ7上に記録してカウント値を“1”に初期化する。これはPEIFコントローラ61で制御コードをカウントおよび初期化を行い、カウント値はラインバッファコントローラ62からラインバッファメモリ7へライトする。

【0050】

次に、前述した構成のデータ圧縮伸張装置1を用いてデータ圧縮を行う方法を図4のフローチャートを参照して説明する。なお、図4に示したフローチャートはGP2で実行される。まず、圧縮を行う元となるデータが前述の汎用レジスタR0に図5に示すように記憶されているとする。図中のA,B,C,D,E,F,G・・は多値のデータを表す。

【0051】

このデータに対して、最初にステップS11において、PE命令として、隣接する左隣のPEの汎用レジスタと自身の汎用レジスタを比較してその値が一致する場合に “0”、一致しない場合に “1”を別の汎用レジスタR1に比較結果として保持する。すなわち、R1を制御コード格納領域としている。この命令は全てのPE3aに対して同時に実行されるので複数のデータを瞬時に処理できることになる。なお、“1”と“0”の論理はもちろん逆でもよく後述の説明を全て逆にすればよい。ここでは前述のように一致するときに“0”とすることで以下の説明を行う。命令実行後のR1は図6のようになる。

【0052】

次に、ステップS12において、メモリコントローラ6に、汎用レジスタR1を制御コードとして汎用レジスタR0のデータを間引いてラインバッファメモリ7上にライトさせる。図6の場合ラインバッファメモリ7上にライトされるデータは前述した本機能の説明の通り、A,B,C,D,E,F,G・・・となる。

【0053】

次に、ステップS13において、メモリコントローラ6に、ラインバッファメモリ7に間引いてライトしたデータを倍率2倍で汎用レジスタ上にライトさせる(書き戻させる)。このときライトする汎用レジスタは、元のデータや制御コードが記憶されている汎用レジスタとは異なるレジスタとし、例えば、R2にライトする。以下、本ステップでR2に書き戻されたデータを書き戻しデータという。すなわち、R2は図7(a)に示すようになる。なお、倍率2倍で汎用レジスタ上にライトする機能ではなく、メモリコントローラ6の別の機能として、図7(b)に示すようにラインバッファメモリ7上のデータをPEのアドレス順で1つおきにライトする機能を持って実現しても良い。

【0054】

次に、ステップS14において、メモリコントローラ6に、前述した制御コードのカウント機能を使用してR1上の比較結果をカウントし、ラインバッファメモリ7上にライトさせる。すなわち、制御コード“0”を特定の値としてカウントアップし、制御コードが“1”を他の値としてカウント値をラインバッファメモリ7にライトするとともにカウント値を“1”に初期化する。図6に示す汎用レジスタR1上のデータの場合、ラインバッファメモリ7上にライトされるデータは、4,3,5,1,1,1,・・・となる。

【0055】

次に、ステップS15において、メモリコントローラ6に、ラインバッファメモリ7上にライトしたカウント値を、倍率2倍で重複して汎用レジスタ上にライトさせる。このときライトする汎用レジスタは、元のデータや制御コードや書き戻しデータが記憶されている汎用レジスタとは異なるレジスタとし、例えば、R3にライトする。すなわち、図8(a)に示すようになる。なお、書き戻しデータと同様に、倍率2倍で汎用レジスタ上にライトする機能ではなく、メモリコントローラ6の別の機能として、図8(b)に示すようにラインバッファメモリ7上のデータをPEのアドレス順で1つおきにライトする機能を持って実現しても良い。但し、PEのアドレス順で1つおきにライトする場合は、書き戻しデータに対して1アドレスずれてライトする(書き戻しデータが奇数アドレスの場合は偶数アドレスにライトする)。

【0056】

なお、前述したステップS12、S13と、ステップS14,S15は並行して実行してもよく、その場合より短時間で処理できるためさらによい。

【0057】

次に、ステップS16において、ステップS5とステップS3により別々の汎用レジスタに書き戻したデータとカウント値を合成するPE命令を実行する。例えば、図9のようにR4に合成したデータをライトする。つまり、R3の偶数番号のカウント値をR4にコピーし、R2の奇数番号のデータを同じくR4にコピーする命令を発行して、R4にカウント値と書き戻しデータが交互に並ぶようにしている。

【0058】

このようにすることで、R4にはデータとその連続数が格納され、所謂ランレングス圧縮を行うことができる。

【0059】

次に、図9ように圧縮したデータをデータ圧縮伸張装置1用いて伸張する方法について説明する。

【0060】

まず、動作を説明する前に、圧縮データを伸張するためにメモリコントローラ6に追加される機能について説明する。この機能は、奇数アドレスのPE3aの汎用レジスタから読み出したデータを例えば画像データなどのデータ本体、偶数アドレスのPE3aの汎用レジスタから読み出したデータをデータ本体の連続数として、圧縮データからデータ本体を連続数分生成する機能である。例えばPE0とPE1の汎用レジスタから読み出した圧縮データが“4A”であった場合はPE0のデータである“4”を連続数、PE1のデータである“A”をデータ本体として、“AAAA”というデータ列を生成してラインバッファメモリ7にライトする。すなわち、圧縮データが格納されている汎用レジスタを読み出して、該汎用レジスタ上の書き戻しデータをカウント値の数分連続して生成している。これは、PEIFコントローラ61で圧縮データの読み取りおよびデータの生成を行い、ラインバッファコントローラ62からラインバッファメモリ7へライトする。

【0061】

次に、図9ように圧縮したデータをデータ圧縮伸張装置1を用いて伸張する方法について図10のフローチャートを参照して説明する。なお、図10に示したフローチャートはGP2で実行される。すなわち、GP2がデータ伸張制御部として動作する。

【0062】

まず、ステップS21において、メモリコントローラ6に、図9のR4のように格納された圧縮データを読み出させる。

【0063】

次に、メモリコントローラ6に、読み出したデータの偶数番号のPE3aのデータを連続数として奇数番号のPE3aのデータをデータ本体として、連続数分のデータ本体を生成してラインバッファメモリ7にライトさせる。

【0064】

このようにすることで、R4に格納されたランレングス圧縮データを伸張してラインバッファメモリ7に記憶させることができる。

【0065】

本実施形態によれば、メモリコントローラ6に、ラインバッファメモリ7から読み出したデータを所定の倍率で汎用レジスタに書き込む機能と、汎用レジスタに設定された制御コードに基づいて他の汎用レジスタのデータをラインバッファメモリ7にライトする機能と、制御コードのうち“0”の連続数をカウントして“1”が出現した際にそのカウント値をラインバッファメモリ7にライトする機能と、を設ける。そして、GP2が、隣接する左隣の汎用レジスタの値と比較して同じ値の場合は制御コードを“0”に、異なる値の場合は制御コードを“1”に設定し、その制御コードに基づいて汎用レジスタのデータをラインバッファメモリ7にライトし、ライトしたデータを倍率2倍で汎用レジスタに書き戻す。一方、制御コードは、“0”の連続数をカウントしてラインバッファメモリ7にライトし、そのカウント数を倍率2倍で汎用レジスタに書き戻し、データとカウント数とを交互に並ぶように合成して圧縮データを生成するので、SIMD型マイクロプロセッサと簡単なメモリコントローラ6の構成によって、簡単かつ効率的にデータを圧縮することができる。

【0066】

また、汎用レジスタに格納された圧縮されたデータを、メモリコントローラ6が読み出して、奇数アドレスのPE3aの汎用レジスタから読み出したデータをデータ本体、偶数アドレスのPE3aの汎用レジスタから読み出したデータをデータ本体の連続数として、圧縮データからデータ本体を連続数分生成してラインバッファメモリ7にライトして圧縮データを伸張しているので、SIMD型マイクロプロセッサと簡単なメモリコントローラ6の構成によって、簡単かつ効率的にデータを伸張することができる。

【0067】

なお、上述した実施形態では、左隣のPEの汎用レジスタと比較して制御コードを生成していたが右隣でもよい。右隣の場合は、図6を例にすると、PE3、PE6、PE11、PE12、PE13、PE14のR1に“1”が格納される。

【0068】

また、上述した実施形態で、書き戻しデータとカウント値を汎用レジスタに格納する際に図7(b)や図8(b)のようにPE3aのアドレスで1つおきに格納してもよいと記載したが、その場合は、図7(b)でR2に書き戻しデータを格納した後に、偶数アドレス(書き戻しデータが格納されていないアドレス)のR2にカウント値を格納することで圧縮データを生成しても良い。

【0069】

なお、本発明は上記実施形態に限定されるものではない。即ち、本発明の骨子を逸脱しない範囲で種々変形して実施することができる。

【符号の説明】

【0070】

1 データ圧縮伸張装置(データ圧縮装置、データ伸張装置)

2 グローバルプロセッサ(データ圧縮制御部、データ伸張制御部)

3 PEコア

31 レジスタファイル

32 演算アレイ

33 レジスタ(汎用レジスタ)

3a PE

6 メモリコントローラ

7 ラインバッファメモリ

8 SIMD型マイクロプロセッサ

【先行技術文献】

【特許文献】

【0071】

【特許文献1】特許第3821198号公報

【技術分野】

【0001】

本発明は、1つの演算命令により複数の画像データ等を並列処理するSIMD(Single Instruction-stream Multiple Data-stream)型マイクロプロセッサを用いてデータ圧縮および伸張を行うデータ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法に関する。

【背景技術】

【0002】

近年、デジタル複写機やファクリミリ装置等において、画素数を増加させて解像度を上げたり、或いはカラー対応にするなど画質の向上が図られている。 そして、この画質の向上に伴い処理すべきデータ数が増加している。

【0003】

ところで、デジタル複写機やファクリミリ装置等におけるデータ処理は全ての画素に対して同じ演算処理を施すことが一般的に多い。 そこで、1つの命令で複数のデータに対して同時に同じ演算処理を行うSIMD方式のマイクロプロセッサが用いられるようになっている。 通常、SIMD方式のマイクロプロセッサを用いて画像処理を行う場合、主走査方向にプロセッサエレメント(PE)を展開する。

【0004】

この種のSIMD型マイクロプロセッサとして、特許文献1に記載の信号処理装置が提案されている。特許文献1においては、シングルポートメモリ(RAM)を用いることで回路規模の増加を抑えながら、同時に変倍機能もメモリコントローラに内蔵可能とした簡単な構成のSIMD型マイクロプロセッサを用いた信号処理装置が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、高画質化、高速化が進むことによって扱う画像データ量も飛躍的に大きくなってきている。例えば、印字解像度という観点では、従来は300dpi(dot per inch)程度であったが、最新の記録装置では3600dpiという機器も登場し、従来に比べて100倍以上のデータ量が必要となっている。 従って、データ帯域は従来の100倍以上必要な状況になってきており、データ圧縮技術の重要性が高まってきている。

【0006】

画像劣化のない可逆圧縮技術としては、ファクシミリ等で用いられるMH(ハフマン符号化方式:一次元圧縮法によるG3ファクシミリの標準符号化方式)、MR(二次元圧縮法によるG3ファクシミリではオプションの符号化方式)、MMR(MR符号化方式の変形で、G4ファクシミリの標準符号化方式)や、コンピュータで扱うテキストファイルやバイナリファイルに用いられるLZ方式等が挙げられる。 また、国際標準である算術符号化を用いたJPEG(Joint Photographic Experts Group)方式やJBIG(Joint Bi-level Image Experts Group)方式もある。

【0007】

しかしながら、いずれも画像データを順に処理する逐次的な処理を必要としており、特許文献1などに記載されたSIMD型マイクロプロセッサで実現するには容易ではなく不向きな圧縮形態であるという問題があった。

【0008】

本発明はかかる問題を解決することを目的としている。

【0009】

すなわち、本発明は、複数のPEとメモリコントローラ部とラインバッファメモリなどの記憶手段とを利用して簡単構成かつ単純な処理でデータを圧縮および伸張することができるデータ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法を提供することを目的としている。

【課題を解決するための手段】

【0010】

上記課題を解決するためになされた請求項1に記載された発明は、複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ圧縮装置において、前記複数の汎用レジスタに、同じアドレスの前記PEの汎用レジスタ上のデータに対応させた制御コードを格納する制御コード格納領域を設け、前記メモリコントローラ部が、前記制御コード格納領域を参照して前記制御コードに従い前記汎用レジスタ上のデータを前記記憶手段にライト可能とし、前記汎用レジスタ上のデータを前記PEのアドレス順に読み出して該データが予め定めた特定の値の場合にカウントアップするとともに他の値の場合に前記特定の値のカウント値を前記記憶手段にライト可能とするように構成され、一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に前記制御コードを前記特定の値に設定させて不一致の場合に前記制御コードを前記他の値に設定させ、次に、前記メモリコントローラ部に、前記制御コードに従って前記PEの前記アドレス順に前記汎用レジスタ上のデータを前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、該ライトしたデータを前記記憶手段からリードさせて前記PEの前記汎用レジスタ上に格納させ(以下、この格納されたデータを書き戻しデータという)、次に、前記メモリコントローラ部に、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納させ、次に、前記メモリコントローラ部に、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納させて前記汎用レジスタ上のデータを圧縮するデータ圧縮制御部を有していることを特徴とするデータ圧縮装置である。

【0011】

請求項2に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されていることを特徴とするものである。

【0012】

請求項3に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成され、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とするものである。

【0013】

請求項4に記載された発明は、請求項1乃至3のうちいずれか一項に記載のデータ圧縮装置で圧縮されたデータを伸張するデータ伸張装置であって、前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成するように構成され、前記メモリコントローラ部に、前記圧縮データが格納されている前記汎用レジスタを読み出させて、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成させて伸張データとして前記記憶手段にライトさせる前記データ伸張制御部を有していることを特徴とするデータ伸張装置である。

【0014】

請求項5に記載された発明は、複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ処理装置のデータ圧縮方法において、一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に当該データに対応して設定される制御コードを予め定めた特定の値に設定して不一致の場合に前記制御コードを他の値に設定する第一の工程と、前記メモリコントローラ部が、前記制御コードが前記他の値が設定されている前記PEの前記汎用レジスタ上のデータを前記アドレス順に前記記憶手段にライトする第二の工程と、前記メモリコントローラ部が、前記第二の工程でライトしたデータを前記記憶手段からリードして前記PEの前記汎用レジスタ上に格納する(以下、この格納されたデータを書き戻しデータという)第三の工程と、前記メモリコントローラ部が、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトする第四の工程と、前記メモリコントローラ部が、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納する第五の工程と、前記メモリコントローラ部が、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納する第六の工程と、を順次実行することを特徴とするデータ圧縮方法である。

【0015】

請求項6に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納することを特徴とするものである。

【0016】

請求項7に記載された発明は、請求項1に記載された発明において、前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納し、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とするものである。

【0017】

請求項8に記載された発明は、請求項5乃至7のうちいずれか一項に記載のデータ圧縮方法で圧縮されたデータを伸張するデータ伸張方法であって、前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成し、前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成されて伸張データとして前記記憶手段にライトすることを特徴とするデータ伸張方法である。

【発明の効果】

【0018】

請求項1に記載の発明によれば、メモリコントローラ部に簡単な構成の回路を追加し、例えばグローバルプロセッサなどをデータ圧縮伸張制御部として動作させることで、複数のPEとメモリコントローラ部と記憶手段とを用いて効率的にデータの圧縮を行うことができる。

【0019】

請求項2に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順に同じデータを2回ずつ重複してPEの汎用レジスタ上に格納しているので、例えば、奇数アドレスのPEの汎用レジスタを書き戻しデータ、偶数アドレスのPEの汎用レジスタをカウント値として合成すれば、書き戻しアドレスとカウント値とを交互に並べることができる。

【0020】

請求項3に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順で1つおきのPEの汎用レジスタ上に格納し、書き戻しデータとカウント値はアドレスが1ずれているので、例えば、書き戻しデータを奇数アドレスのPEの汎用レジスタに格納して、カウント値を偶数アドレスのPEの汎用レジスタに格納すれば、それらを単純に合成するだけで、書き戻しアドレスとカウント値とを交互に並べることができる。

【0021】

請求項4に記載の発明によれば、メモリコントローラ部に簡単な構成の回路を追加し、例えばグローバルプロセッサなどをデータ圧縮伸張制御部として動作させることで、複数のPEとメモリコントローラ部と記憶手段とを用いて効率的にデータの伸張を行うことができる。

【0022】

請求項5に記載の発明によれば、データに制御コードを付加し、メモリコントローラを用いたリードライト処理を行うことで、複数のPEとメモリコントローラ部と記憶手段とを用いてデータの圧縮を効率的に行うことができる。

【0023】

請求項6に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順に同じデータを2回ずつ重複してPEの汎用レジスタ上に格納しているので、例えば、奇数アドレスのPEの汎用レジスタを書き戻しデータ、偶数アドレスのPEの汎用レジスタをカウント値として合成すれば、書き戻しアドレスとカウント値とを交互に並べることができる。

【0024】

請求項7に記載の発明によれば、メモリコントローラが、書き戻しデータとカウント値ともにPEのアドレス順で1つおきのPEの汎用レジスタ上に格納し、書き戻しデータとカウント値はアドレスが1ずれているので、例えば、書き戻しデータを奇数アドレスのPEの汎用レジスタに格納して、カウント値を偶数アドレスのPEの汎用レジスタに格納すれば、それらを単純に合成するだけで、書き戻しアドレスとカウント値とを交互に並べることができる。

【0025】

請求項8に記載の発明によれば、データに制御コードを付加し、メモリコントローラを用いたリードライト処理を行うことで、複数のPEとメモリコントローラ部と記憶手段とを用いてデータの伸張を効率的に行うことができる。

【図面の簡単な説明】

【0026】

【図1】本発明の一実施形態にかかるデータ伸張装置およびデータ伸張装置の構成図である。

【図2】図1に示されたGPとPEコアの一部分を抜き出した概略図である。

【図3】図1に示されたメモリコントローラの構成図である。

【図4】図1に示されたデータ圧縮装置のデータ圧縮動作を示したフローチャートである。

【図5】汎用レジスタに圧縮前のデータを格納した状態を示した説明図である。

【図6】図5に示された汎用レジスタに制御コードを加えた状態を示した説明図である。

【図7】データをラインバッファメモリから書き戻した状態を示した説明図である。

【図8】制御コードをラインバッファメモリから書き戻した状態を示した説明図である。

【図9】データと制御コードを合成した状態を示した説明図である。

【図10】図1に示されたデータ伸張装置のデータ伸張動作を示したフローチャートである。

【発明を実施するための形態】

【0027】

以下、本発明の一実施形態を、図1ないし図10を参照して説明する。図1は、本発明の一実施形態にかかるデータ圧縮装置およびデータ伸張装置の構成図である。図2は、図1に示されたGPとPEコアの一部分を抜き出した概略図である。図3は、図1に示されたメモリコントローラの構成図である。図4は、図1に示されたデータ圧縮装置のデータ圧縮動作を示したフローチャートである。図5は、汎用レジスタに圧縮前のデータを格納した状態を示した説明図である。図6は、図5に示された汎用レジスタに制御コードを加えた状態を示した説明図である。図7は、データをラインバッファメモリから書き戻した状態を示した説明図である。図8は、制御コードをラインバッファメモリから書き戻した状態を示した説明図である。図9は、データと制御コードを合成した状態を示した説明図である。図10は、図1に示されたデータ伸張装置のデータ伸張動作を示したフローチャートである。

【0028】

図1に本発明の一実施形態にかかるデータ圧縮装置およびデータ伸張装置としてのデータ圧縮伸張装置1を示す。図1に示したデータ圧縮伸張装置1は、グローバルプロセッサ(GP)2と、PEコア3と、PEIF4と、メモリコントローラ6と、ラインバッファメモリ7と、を備えている。

【0029】

データ圧縮制御部としてのGP2は、所謂SISD(Single Instruction-stream, Single Data-stream)タイプのプロセッサである。GP2にはSIMD型マイクロプロセッサ8のプログラム格納用のプログラムRAMと演算データ格納用のデータRAMとが内蔵されている。さらに、プログラムのアドレスを保持するプログラムカウンタ(PC)、演算処理のデータ格納のための汎用レジスタであるG0〜G3レジスタ、レジスタ退避、復帰時に退避先データRAMのアドレスを保持しているスタックポインタ(SP)、サブルーチンコール時にコール元のアドレスを保持するリンクレジスタ(LS)、同様に割り込み(IRQ)時とマスク不可割り込み(NMI)時の分岐元アドレスを保持するLI、LNレジスタ、プロセッサの状態を保持しているプロセッサステータスレジスタ(P)を備えている。これらのレジスタと図示していない命令デコーダ、ALU、メモリ制御回路、割り込み制御回路、外部I/O制御回路、GP演算制御回路を使用してGP2内で実行される命令であるGP命令の実行が行われる。また、PEコア3に対する命令であるPE命令実行時は命令デコーダ、レジスタファイル制御回路、PE演算制御回路を使用して、PEコア3内のレジスタファイル31の制御と演算アレイ32の制御を行う。

【0030】

PEコア3は、図2に示すようにレジスタファイル31と、演算アレイ32と、から構成されている。レジスタファイル31は、PE命令で処理されるデータを保持している。PE命令は、SIMDタイプの命令であり、レジスタファイル31に保持されている複数のデータに対して同時に同じ処理を行う。このレジスタファイル31からのデータの読み出し/書き込みの制御はGP2からの制御によって行われる。読み出されたデータは演算アレイ32に送られ、演算アレイ32での演算処理後に再度レジスタファイル31に書き込まれる。また、レジスタファイル31は、GP2とPEコア3と後述するPEIF4とから構成されるプロセッサコア5の外部からのアクセスが可能であり、GP2の制御とは別に外部から特定のレジスタ33に対して読み出し/書き込みが行われる。

【0031】

レジスタファイル31には、1つのPE単位に8ビットの汎用レジスタとしてのレジスタ33を例えば32本備えており、PEが例えば512PEの場合は512組分がアレイ構成になっている。32本のレジスタ33は、1つのPE内でR0、R1、R2、...R31と呼び区別される。それぞれのレジスタ33は演算アレイ32に対して1つの読み出しポートと1つの書き込みポートとを備えており、8ビットのリード/ライト兼用のバスで演算アレイ32からアクセスされる。32本のレジスタ33の複数本をプロセッサコア5の外部からアクセス可能として、外部からクロックとアドレス、リード/ライト制御を入力することで任意のレジスタ33を読み書きできるようにしている。レジスタ33の外部からのアクセスは、1つの外部ポートで各PEの1つのレジスタ33がアクセス可能であり外部から入力されたアドレスでPEの番号(512PEの場合は0〜511)を指定する。このポートを使用して後述するメモリコントローラ6がラインバッファメモリ7とのアクセスを行う。したがって複数の外部ポートを設けることで一度に複数のPEのレジスタ33がアクセス可能となる。

【0032】

演算アレイ32は、マルチプレクサ34と、シフタ35と、ALU36と、Aレジスタ37と、Fレジスタ38と、フラグレジスタ39と、を備え、PE命令の演算処理が行われる。また、処理の制御はすべてGP2から行われる。

【0033】

演算アレイ32におけるPE命令による演算は、基本的にレジスタファイル31から読み出されたデータをALU36の片側の入力としてもう片側にはAレジスタ37の内容を入力として結果をAレジスタ37に格納する。したがって、Aレジスタ37とレジスタファイル31のレジスタ33との演算が行われることとなる。

【0034】

レジスタファイル31と演算アレイ32との接続には7to1のマルチプレクサ34が設けられており、PE方向で左に1、2、3つ離れたデータと右に1、2、3つ離れたデータ、中央(自PE)のデータを演算対象として選択している。マルチプレクサ34は、自PEのレジスタファイル31に接続されるとともに、両隣3つのPEのレジスタファイル31にも接続されている。このマルチプレクサ34は7つのPEから1つを選択し、その選択したPEにおけるレジスタ33で保持されているデータをALU36へ送る。或いはALU36で演算処理されたデータを、選択したPEにおけるレジスタ33へ送る。これによって、隣のPEにおけるレジスタ33で保持されているデータを利用した演算処理が可能になり、SIMD型マイクロプロセッサ8の演算処理能力を高めることができる。

【0035】

シフタ35は、レジスタファイル31の8ビットのデータを任意ビットの左シフト演算を行ってALU36に入力する。

【0036】

ALU36は、シフタ35から送られてきたデータと、Aレジスタ37に保持されているデータとに基づき算術論理演算を行う。なお、本実施形態では、ALU36は16ビットのデータに対応できるものとして扱うが、データに応じて適宜変更しても問題ない。演算処理されたデータは、Aレジスタ37に保持され、シフタ35へ転送されたり、或いはGP2の汎用レジスタなどへ転送される。

【0037】

さらに、演算アレイ32は、図示していない8ビットの条件レジスタ(T)により、PEごとに演算実行の無効/有効が制御されており、特定のPEだけを演算対象として選択できるように構成している。

【0038】

上述したように、レジスタ33のR0〜R32、マルチプレクサ34、シフタ35、ALU36、Aレジスタ37、Fレジスタ38、フラグレジスタ39で1つのPE3aを構成している(図2の点線で囲まれた範囲)。

【0039】

PEIF4は、レジスタファイル31へのプロセッサコア5外部からのアクセスを制御する。

【0040】

メモリコントローラ6は、図3に示すように、PEIFコントローラ61と、ラインバッファコントローラ62と、コマンド発行部63と、アドレス生成部64と、FIFO65と、メイン制御部66と、を備えている。

【0041】

PEIFコントローラ61は、レジスタファイル31へのアドレス、アクセスクロック、リード/ライトコントロール信号の生成およびデータの入出力バッファなどを行う。ラインバッファコントローラ62は、ラインバッファメモリ7をコントロールする。コマンド発行部63は、ラインバッファコントローラ62へのリードコマンド、ライトコマンドを発行する。リードコマンド、ライトコマンドはリードもしくはライトの識別とアクセスを行うスタートアドレスとしてページメモリ上の論理アドレス、さらにアクセスバースト数などで構成される。

【0042】

アドレス生成部64は、後述するメイン制御部66からのコントロールでコマンド発行部63に対してアクセスを行うためのスタートアドレス情報を生成する。FIFO65は、ラインバッファコントローラ62とPEIFコントローラ61への入出力データを管理するバッファとして機能させるFIFO(First In First Out)方式のバッファである。メイン制御部66は、メモリコントローラ6を全体的に制御する。メイン制御部66はGP2からの命令により動作する。

【0043】

記憶手段としてのラインバッファメモリ7は、SIMD型マイクロプロセッサ8の外部に接続されるページメモリであり、例えばSRAMなどで構成される。

【0044】

そして、本実施形態では、GP2とPEコア3とPEIF4から構成されるプロセッサコア5にメモリコントローラ6を加えてSIMD型マイクロプロセッサ8を構成している。なお、SIMD型マイクロプロセッサ8はこの構成に限らず、プロセッサコア5の部分のみをSIMD型マイクロプロセッサとしてメモリコントローラ6がプロセッサの外付け回路としてもよい。

【0045】

前述したSIMD型マイクロプロセッサ8では、メモリコントローラ6によりラインバッファメモリ7とデータ入出力を行うレジスタファイル31(PE3a)は、1つのPE3aを単位としてメモリコントローラ6からアクセスする順にアドレスを割り振って管理されている。例えば、SIMD型マイクロプロセッサ8が512個のPE3aを備えているとすると、PE0〜PE511とアドレスを割り振って管理する。これらレジスタファイル31内のレジスタ33は1つのPE3a内にいくつも持ってよい。その1つのPE3a内の複数のレジスタ33間でデータのやりとりは自由に行うことができる構成とする。それらをR0,R1,R2・・・と順に呼ぶこととする。すなわち、R0はPE0〜PE511の512個の汎用レジスタ(レジスタ33)で構成され、R1以降も同様にPE0〜PE511の512個ずつの汎用レジスタ(レジスタ33)で構成されている。

【0046】

ここで、上述したメモリコントローラ6の有する機能を説明する。まず、汎用レジスタ上のデータを一定の倍率で間引いてラインバッファメモリ7上にライトする機能を持つ。例えば、1/2の倍率であれば偶数アドレスを持つPE3aの汎用レジスタのデータのみをラインバッファメモリ7にライトする。これはGP2が予めメイン制御部66に行った設定にしたがってPEIFコントローラ61を制御して偶数アドレスを持つPE3aの汎用レジスタのデータのみを読み出させて、ラインバッファコントローラ62にラインバッファメモリ7へライトさせる。同様に倍率が1/4であればPE3aのアドレスの下位2bitが“00”の場合にそのPE3aの汎用レジスタのデータをラインバッファメモリ7にライトする。このようにして元データを間引いてラインバッファメモリ7にライトできる。倍率に関しては予め決められた倍率で外部からGP2を介しての設定によって選択可能であるものとする。

【0047】

次に、上述した機能と同様に汎用レジスタ上のデータを間引いてライトする機能であるが、汎用レジスタ上のデータを制御コードとして、その制御コードに従って別の汎用レジスタのデータを間引いてラインバッファメモリ7にライトする機能を持つ。例えば、図6のR0のデータをR1のデータを制御コードとして、制御コードが“1”のPE3aのR0のデータはラインバッファメモリ7にライトし、“0”の場合にはラインバッファメモリ7にライトしないようにしてデータを間引く。これはPEIFコントローラ61がR0とR1のデータを読み出してR1の内容に基づいてR0をFIFO65に格納するか否かを選択している。すなわち、図6の場合には間引いた後にラインバッファメモリ7にライトされるデータは、A,B,C,D,E,F,G・・・となる。なお、上述した1/2、1/4の倍率に間引く際もこの制御コードを用いてもよい。

【0048】

次に、メモリコントローラ6の別の機能として、ラインバッファメモリ7上のデータを一定の倍率で重複して汎用レジスタ上にライトする機能を持つ。例えば、2倍であればラインバッファメモリ7上のデータをPE3aの汎用レジスタに対して2度ずつライトする機能である。例えば、ラインバッファメモリ7から順にA,B,C,D,E,F,G・・・とデータが読み出され、それをR0にライトする場合、PE0とPE1にAを、PE2とPE3にBを、PE4とPE5にCを、PE6とPE7にDを、PE8とPE9にEを、PE10とPE11にFを、PE12とPE13にGをライトする。これはラインバッファコントローラ62が読み出したデータをGP2が予めメイン制御部66に行った設定にしたがってPEIFコントローラ61を制御して1つのデータにつき2つのPE3aの汎用レジスタへライトさせる。同様に倍率が4倍であれば、ラインバッファメモリ7上のデータをPE3aの汎用レジスタに対して4度ずつライトする。倍率に関しては予め決められた倍率で外部からGP2を介しての設定によって選択可能であるものとする。

【0049】

さらに、メモリコントローラ6の別の機能として、汎用レジスタ上の制御コードのうち予め定めた特定の値の場合はカウントアップし、特定の値とは異なる他の値の場合はそれまでのカウント値をラインバッファメモリ7上に記録してカウント値を“1”に初期化する機能を持つ。例えば、制御コードを2値のデータ“0”、“1”とすると、“0”の場合には特定の値としてカウントアップし、“1”の場合には他の値としてそれまでのカウント値をラインバッファメモリ7上に記録してカウント値を“1”に初期化する。これはPEIFコントローラ61で制御コードをカウントおよび初期化を行い、カウント値はラインバッファコントローラ62からラインバッファメモリ7へライトする。

【0050】

次に、前述した構成のデータ圧縮伸張装置1を用いてデータ圧縮を行う方法を図4のフローチャートを参照して説明する。なお、図4に示したフローチャートはGP2で実行される。まず、圧縮を行う元となるデータが前述の汎用レジスタR0に図5に示すように記憶されているとする。図中のA,B,C,D,E,F,G・・は多値のデータを表す。

【0051】

このデータに対して、最初にステップS11において、PE命令として、隣接する左隣のPEの汎用レジスタと自身の汎用レジスタを比較してその値が一致する場合に “0”、一致しない場合に “1”を別の汎用レジスタR1に比較結果として保持する。すなわち、R1を制御コード格納領域としている。この命令は全てのPE3aに対して同時に実行されるので複数のデータを瞬時に処理できることになる。なお、“1”と“0”の論理はもちろん逆でもよく後述の説明を全て逆にすればよい。ここでは前述のように一致するときに“0”とすることで以下の説明を行う。命令実行後のR1は図6のようになる。

【0052】

次に、ステップS12において、メモリコントローラ6に、汎用レジスタR1を制御コードとして汎用レジスタR0のデータを間引いてラインバッファメモリ7上にライトさせる。図6の場合ラインバッファメモリ7上にライトされるデータは前述した本機能の説明の通り、A,B,C,D,E,F,G・・・となる。

【0053】

次に、ステップS13において、メモリコントローラ6に、ラインバッファメモリ7に間引いてライトしたデータを倍率2倍で汎用レジスタ上にライトさせる(書き戻させる)。このときライトする汎用レジスタは、元のデータや制御コードが記憶されている汎用レジスタとは異なるレジスタとし、例えば、R2にライトする。以下、本ステップでR2に書き戻されたデータを書き戻しデータという。すなわち、R2は図7(a)に示すようになる。なお、倍率2倍で汎用レジスタ上にライトする機能ではなく、メモリコントローラ6の別の機能として、図7(b)に示すようにラインバッファメモリ7上のデータをPEのアドレス順で1つおきにライトする機能を持って実現しても良い。

【0054】

次に、ステップS14において、メモリコントローラ6に、前述した制御コードのカウント機能を使用してR1上の比較結果をカウントし、ラインバッファメモリ7上にライトさせる。すなわち、制御コード“0”を特定の値としてカウントアップし、制御コードが“1”を他の値としてカウント値をラインバッファメモリ7にライトするとともにカウント値を“1”に初期化する。図6に示す汎用レジスタR1上のデータの場合、ラインバッファメモリ7上にライトされるデータは、4,3,5,1,1,1,・・・となる。

【0055】

次に、ステップS15において、メモリコントローラ6に、ラインバッファメモリ7上にライトしたカウント値を、倍率2倍で重複して汎用レジスタ上にライトさせる。このときライトする汎用レジスタは、元のデータや制御コードや書き戻しデータが記憶されている汎用レジスタとは異なるレジスタとし、例えば、R3にライトする。すなわち、図8(a)に示すようになる。なお、書き戻しデータと同様に、倍率2倍で汎用レジスタ上にライトする機能ではなく、メモリコントローラ6の別の機能として、図8(b)に示すようにラインバッファメモリ7上のデータをPEのアドレス順で1つおきにライトする機能を持って実現しても良い。但し、PEのアドレス順で1つおきにライトする場合は、書き戻しデータに対して1アドレスずれてライトする(書き戻しデータが奇数アドレスの場合は偶数アドレスにライトする)。

【0056】

なお、前述したステップS12、S13と、ステップS14,S15は並行して実行してもよく、その場合より短時間で処理できるためさらによい。

【0057】

次に、ステップS16において、ステップS5とステップS3により別々の汎用レジスタに書き戻したデータとカウント値を合成するPE命令を実行する。例えば、図9のようにR4に合成したデータをライトする。つまり、R3の偶数番号のカウント値をR4にコピーし、R2の奇数番号のデータを同じくR4にコピーする命令を発行して、R4にカウント値と書き戻しデータが交互に並ぶようにしている。

【0058】

このようにすることで、R4にはデータとその連続数が格納され、所謂ランレングス圧縮を行うことができる。

【0059】

次に、図9ように圧縮したデータをデータ圧縮伸張装置1用いて伸張する方法について説明する。

【0060】

まず、動作を説明する前に、圧縮データを伸張するためにメモリコントローラ6に追加される機能について説明する。この機能は、奇数アドレスのPE3aの汎用レジスタから読み出したデータを例えば画像データなどのデータ本体、偶数アドレスのPE3aの汎用レジスタから読み出したデータをデータ本体の連続数として、圧縮データからデータ本体を連続数分生成する機能である。例えばPE0とPE1の汎用レジスタから読み出した圧縮データが“4A”であった場合はPE0のデータである“4”を連続数、PE1のデータである“A”をデータ本体として、“AAAA”というデータ列を生成してラインバッファメモリ7にライトする。すなわち、圧縮データが格納されている汎用レジスタを読み出して、該汎用レジスタ上の書き戻しデータをカウント値の数分連続して生成している。これは、PEIFコントローラ61で圧縮データの読み取りおよびデータの生成を行い、ラインバッファコントローラ62からラインバッファメモリ7へライトする。

【0061】

次に、図9ように圧縮したデータをデータ圧縮伸張装置1を用いて伸張する方法について図10のフローチャートを参照して説明する。なお、図10に示したフローチャートはGP2で実行される。すなわち、GP2がデータ伸張制御部として動作する。

【0062】

まず、ステップS21において、メモリコントローラ6に、図9のR4のように格納された圧縮データを読み出させる。

【0063】

次に、メモリコントローラ6に、読み出したデータの偶数番号のPE3aのデータを連続数として奇数番号のPE3aのデータをデータ本体として、連続数分のデータ本体を生成してラインバッファメモリ7にライトさせる。

【0064】

このようにすることで、R4に格納されたランレングス圧縮データを伸張してラインバッファメモリ7に記憶させることができる。

【0065】

本実施形態によれば、メモリコントローラ6に、ラインバッファメモリ7から読み出したデータを所定の倍率で汎用レジスタに書き込む機能と、汎用レジスタに設定された制御コードに基づいて他の汎用レジスタのデータをラインバッファメモリ7にライトする機能と、制御コードのうち“0”の連続数をカウントして“1”が出現した際にそのカウント値をラインバッファメモリ7にライトする機能と、を設ける。そして、GP2が、隣接する左隣の汎用レジスタの値と比較して同じ値の場合は制御コードを“0”に、異なる値の場合は制御コードを“1”に設定し、その制御コードに基づいて汎用レジスタのデータをラインバッファメモリ7にライトし、ライトしたデータを倍率2倍で汎用レジスタに書き戻す。一方、制御コードは、“0”の連続数をカウントしてラインバッファメモリ7にライトし、そのカウント数を倍率2倍で汎用レジスタに書き戻し、データとカウント数とを交互に並ぶように合成して圧縮データを生成するので、SIMD型マイクロプロセッサと簡単なメモリコントローラ6の構成によって、簡単かつ効率的にデータを圧縮することができる。

【0066】

また、汎用レジスタに格納された圧縮されたデータを、メモリコントローラ6が読み出して、奇数アドレスのPE3aの汎用レジスタから読み出したデータをデータ本体、偶数アドレスのPE3aの汎用レジスタから読み出したデータをデータ本体の連続数として、圧縮データからデータ本体を連続数分生成してラインバッファメモリ7にライトして圧縮データを伸張しているので、SIMD型マイクロプロセッサと簡単なメモリコントローラ6の構成によって、簡単かつ効率的にデータを伸張することができる。

【0067】

なお、上述した実施形態では、左隣のPEの汎用レジスタと比較して制御コードを生成していたが右隣でもよい。右隣の場合は、図6を例にすると、PE3、PE6、PE11、PE12、PE13、PE14のR1に“1”が格納される。

【0068】

また、上述した実施形態で、書き戻しデータとカウント値を汎用レジスタに格納する際に図7(b)や図8(b)のようにPE3aのアドレスで1つおきに格納してもよいと記載したが、その場合は、図7(b)でR2に書き戻しデータを格納した後に、偶数アドレス(書き戻しデータが格納されていないアドレス)のR2にカウント値を格納することで圧縮データを生成しても良い。

【0069】

なお、本発明は上記実施形態に限定されるものではない。即ち、本発明の骨子を逸脱しない範囲で種々変形して実施することができる。

【符号の説明】

【0070】

1 データ圧縮伸張装置(データ圧縮装置、データ伸張装置)

2 グローバルプロセッサ(データ圧縮制御部、データ伸張制御部)

3 PEコア

31 レジスタファイル

32 演算アレイ

33 レジスタ(汎用レジスタ)

3a PE

6 メモリコントローラ

7 ラインバッファメモリ

8 SIMD型マイクロプロセッサ

【先行技術文献】

【特許文献】

【0071】

【特許文献1】特許第3821198号公報

【特許請求の範囲】

【請求項1】

複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ圧縮装置において、

前記複数の汎用レジスタに、同じアドレスの前記PEの汎用レジスタ上のデータに対応させた制御コードを格納する制御コード格納領域を設け、

前記メモリコントローラ部が、前記制御コード格納領域を参照して前記制御コードに従い前記汎用レジスタ上のデータを前記記憶手段にライト可能とし、前記汎用レジスタ上のデータを前記PEのアドレス順に読み出して該データが予め定めた特定の値の場合にカウントアップするとともに他の値の場合に前記特定の値のカウント値を前記記憶手段にライト可能とするように構成され、

一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に前記制御コードを前記特定の値に設定させて不一致の場合に前記制御コードを前記他の値に設定させ、次に、前記メモリコントローラ部に、前記制御コードに従って前記PEの前記アドレス順に前記汎用レジスタ上のデータを前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、該ライトしたデータを前記記憶手段からリードさせて前記PEの前記汎用レジスタ上に格納させ(以下、この格納されたデータを書き戻しデータという)、次に、前記メモリコントローラ部に、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納させ、次に、前記メモリコントローラ部に、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納させて前記汎用レジスタ上のデータを圧縮するデータ圧縮制御部を有している

ことを特徴とするデータ圧縮装置。

【請求項2】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されていることを特徴とする請求項1に記載のデータ圧縮装置。

【請求項3】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成され、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とする請求項1に記載のデータ圧縮装置。

【請求項4】

請求項1乃至3のうちいずれか一項に記載のデータ圧縮装置で圧縮されたデータを伸張するデータ伸張装置であって、

前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成するように構成され、

前記メモリコントローラ部に、前記圧縮データが格納されている前記汎用レジスタを読み出させて、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成させて伸張データとして前記記憶手段にライトさせる前記データ伸張制御部を有している

ことを特徴とするデータ伸張装置。

【請求項5】

複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ処理装置のデータ圧縮方法において、

一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に当該データに対応して設定される制御コードを予め定めた特定の値に設定して不一致の場合に前記制御コードを他の値に設定する第一の工程と、

前記メモリコントローラ部が、前記制御コードが前記他の値が設定されている前記PEの前記汎用レジスタ上のデータを前記アドレス順に前記記憶手段にライトする第二の工程と、

前記メモリコントローラ部が、前記第二の工程でライトしたデータを前記記憶手段からリードして前記PEの前記汎用レジスタ上に格納する(以下、この格納されたデータを書き戻しデータという)第三の工程と、

前記メモリコントローラ部が、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトする第四の工程と、

前記メモリコントローラ部が、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納する第五の工程と、

前記メモリコントローラ部が、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納する第六の工程と、

を順次実行することを特徴とするデータ圧縮方法。

【請求項6】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納することを特徴とする請求項5に記載のデータ圧縮方法。

【請求項7】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納し、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とする請求項5に記載のデータ圧縮方法。

【請求項8】

請求項5乃至7のうちいずれか一項に記載のデータ圧縮方法で圧縮されたデータを伸張するデータ伸張方法であって、

前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成し、

前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成されて伸張データとして前記記憶手段にライトする

ことを特徴とするデータ伸張方法。

【請求項1】

複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ圧縮装置において、

前記複数の汎用レジスタに、同じアドレスの前記PEの汎用レジスタ上のデータに対応させた制御コードを格納する制御コード格納領域を設け、

前記メモリコントローラ部が、前記制御コード格納領域を参照して前記制御コードに従い前記汎用レジスタ上のデータを前記記憶手段にライト可能とし、前記汎用レジスタ上のデータを前記PEのアドレス順に読み出して該データが予め定めた特定の値の場合にカウントアップするとともに他の値の場合に前記特定の値のカウント値を前記記憶手段にライト可能とするように構成され、

一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に前記制御コードを前記特定の値に設定させて不一致の場合に前記制御コードを前記他の値に設定させ、次に、前記メモリコントローラ部に、前記制御コードに従って前記PEの前記アドレス順に前記汎用レジスタ上のデータを前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、該ライトしたデータを前記記憶手段からリードさせて前記PEの前記汎用レジスタ上に格納させ(以下、この格納されたデータを書き戻しデータという)、次に、前記メモリコントローラ部に、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトさせ、次に、前記メモリコントローラ部に、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納させ、次に、前記メモリコントローラ部に、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納させて前記汎用レジスタ上のデータを圧縮するデータ圧縮制御部を有している

ことを特徴とするデータ圧縮装置。

【請求項2】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納可能に構成されていることを特徴とする請求項1に記載のデータ圧縮装置。

【請求項3】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成されているとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納可能に構成され、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とする請求項1に記載のデータ圧縮装置。

【請求項4】

請求項1乃至3のうちいずれか一項に記載のデータ圧縮装置で圧縮されたデータを伸張するデータ伸張装置であって、

前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成するように構成され、

前記メモリコントローラ部に、前記圧縮データが格納されている前記汎用レジスタを読み出させて、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成させて伸張データとして前記記憶手段にライトさせる前記データ伸張制御部を有している

ことを特徴とするデータ伸張装置。

【請求項5】

複数の汎用レジスタが設けられているPE(Processor Element)であって、予めアドレスが付与された複数の前記PEと、前記汎用レジスタにアクセスするとともに記憶手段に対して前記汎用レジスタのデータをリードまたはライトするメモリコントローラ部と、を有したデータ処理装置のデータ圧縮方法において、

一つの前記PEの前記汎用レジスタ上のデータと前記アドレスが隣接する前記PEの汎用レジスタ上のデータとを比較して一致する場合に当該データに対応して設定される制御コードを予め定めた特定の値に設定して不一致の場合に前記制御コードを他の値に設定する第一の工程と、

前記メモリコントローラ部が、前記制御コードが前記他の値が設定されている前記PEの前記汎用レジスタ上のデータを前記アドレス順に前記記憶手段にライトする第二の工程と、

前記メモリコントローラ部が、前記第二の工程でライトしたデータを前記記憶手段からリードして前記PEの前記汎用レジスタ上に格納する(以下、この格納されたデータを書き戻しデータという)第三の工程と、

前記メモリコントローラ部が、前記制御コードを前記制御コード格納領域から順次読み出しながら前記特定の値の数をカウントし前記他の値が読み出された場合に前記特定の値のカウント値を前記記憶手段にライトする第四の工程と、

前記メモリコントローラ部が、前記記憶手段にライトした前記特定の値のカウント値をリードして前記書き戻しデータとは異なる前記汎用レジスタ上に格納する第五の工程と、

前記メモリコントローラ部が、前記書き戻しデータが格納されている前記汎用レジスタのデータと前記特定の値のカウント値が格納されている前記汎用レジスタのデータとを交互に並べるように合成させて圧縮データとして前記書き戻しデータと前記カウント値が格納されている前記汎用レジスタと異なる前記汎用レジスタに格納する第六の工程と、

を順次実行することを特徴とするデータ圧縮方法。

【請求項6】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順に同じデータを2回ずつ重複して前記PEの前記汎用レジスタ上に格納することを特徴とする請求項5に記載のデータ圧縮方法。

【請求項7】

前記メモリコントローラ部が、前記書き戻しデータを前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納するとともに、前記記憶手段から読み出した前記特定の値のカウント値を前記PEの前記アドレス順で1つおきの前記PEの前記汎用レジスタ上に格納し、前記書き戻しデータが格納されている前記PEのアドレスと前記特定の値のカウント値が格納されている前記PEのアドレスとが1ずれていることを特徴とする請求項5に記載のデータ圧縮方法。

【請求項8】

請求項5乃至7のうちいずれか一項に記載のデータ圧縮方法で圧縮されたデータを伸張するデータ伸張方法であって、

前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成し、

前記メモリコントローラ部が、前記圧縮データが格納されている前記汎用レジスタを読み出して、該汎用レジスタ上の前記書き戻しデータを前記カウント値の数分連続して生成されて伸張データとして前記記憶手段にライトする

ことを特徴とするデータ伸張方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−14576(P2012−14576A)

【公開日】平成24年1月19日(2012.1.19)

【国際特許分類】

【出願番号】特願2010−152181(P2010−152181)

【出願日】平成22年7月2日(2010.7.2)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年1月19日(2012.1.19)

【国際特許分類】

【出願日】平成22年7月2日(2010.7.2)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]