データ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラム

【課題】過渡遷移に基づく解析を困難とし、例えばDPA攻撃に対する耐性の高い演算構成を実現する。

【解決手段】非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

【解決手段】非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムに関する。さらに詳細には、本発明は、AES(Advanced Encryption Standard)に代表されるような共通鍵暗号方式や、RSA(Rivest−Shamir−Adleman)暗号に代表されるような公開鍵暗号方式、またはSHA−1に代表されるようなハッシュ関数などの演算を効率的に実行する論理回路を利用したデータ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムに関する。

【背景技術】

【0002】

昨今、ネットワーク通信、電子商取引の発展に伴い、通信におけるセキュリティ確保が重要な問題となっている。セキュリティ確保の1つの方法が暗号技術であり、現在、様々な暗号化手法を用いた通信が実現され、運用されている。

【0003】

暗号化方式には大きく分けて共通鍵暗号方式と公開鍵暗号方式が存在する。共通鍵暗号方式には、DES(Data Encryption Standard)やAES(Advanced Encryption Standard)がある。AES暗号方式はDES暗号方式の後継暗号方式として位置づけられている。また、公開鍵暗号方式には、RSA(Rivest−Shamir−Adleman)暗号方式やECC(Elliptic Curve Cryptosystems)暗号方式が存在する。

【0004】

このような様々な暗号方式に従った暗号処理を実行する装置、すなわち暗号処理デバイスとしては、例えば、C言語のようなプログラミング言語を用いてCPUを利用してプログラムの処理によって実行させる構成、あるいは様々なゲート回路を使用してハードウェア上で実行させる構成などがある。

【0005】

暗号処理デバイスにおいては、例えば、平文を入力し暗号文を出力するデータ暗号化処理、あるいは暗号文を入力し平文を出力する復号化処理が実行される。これらの暗号処理は、セキュアに行なわれ、情報の漏洩を防ぐ工夫がなされているが、一方で、暗号処理の適用鍵や、アルゴリズムを解析する攻撃手法も存在する。攻撃方法は大別して破壊攻撃と非破壊攻撃に分類することができる。

【0006】

このうち破壊攻撃は、ICチップなどのパッケージを硝酸などの薬品を用いて化学的処理により溶解しICチップのダイをあらわにした後、物理的な方法で秘密情報を読み取る攻撃である。ダイがあらわになると、配線パターンから構成された回路を導出するリバースエンジニアリングが可能であり、配線から直接秘密情報を抽出することが可能となる。また配線だけでなくメモリセルからもレーザーや電磁波を用いてメモリ状態を検知することによって、メモリ内に書き込まれている秘密情報を観測することができる。

【0007】

また非破壊攻撃はサイドチャネル攻撃(Side−Channel Attack)とも呼ばれる。基本的にICチップのパッケージを溶解するという処理を行なわず、外部から得られる物理的情報、たとえば消費電流、輻射電磁波、演算終了時間等の情報を利用して、秘密情報を盗み出すものである。実際に共通鍵暗号方式であるDESが実装されたデバイスの暗号処理中の消費電流を観測して、秘密情報である鍵情報を漏洩させる方法がKocherらによって1999年に発表された。この手法については、例えば非特許文献1に記載されている。この攻撃技術の存在は、暗号の実装方法が適切でない場合、安全性が確保できないことを意味するものである。

【0008】

非特許文献1に記載されているDPA(Differential Power Analysis)攻撃は、入力平文の異なる数多くの暗号演算処理中の消費電流を観測して、秘密情報のビット値をもとに消費電流波形を統計処理することにより、秘密情報との相関の有無によって統計処理した消費電流波形に表れる特徴的なパターンから秘密情報を導き出すという攻撃手法である。

【0009】

このような攻撃に対して、様々な防御方法も提案されている。例えば、共通鍵暗号方式であるAESについて例を挙げれば、非特許文献2に1つの防御手法が記載されている。この非特許文献2に記載の手法は、AESの演算のうちSubByteと呼ばれている内部のS−Box演算に対して対策を施したものである。この対策は演算途中の秘密情報を含んだ中間値があらわに存在しないように乱数を用いて秘匿する技術である。

【0010】

しかしながら、この方法を単純にハードウェアに実装しても内部信号の遅延差による過渡遷移が生じるために、乱数を用いて秘密情報を含んだ中間値の秘匿が完全にできない状況が生じるためにDPA攻撃によって秘密情報が漏洩してしまうことがあるという問題がある。

【0011】

さらに、非特許文献3には、上述の非特許文献2の構成における欠点である過渡遷移を解消した構成として、WDDL(Wave Differential Dynamic Logic)を用いた対策が開示されている。この対策はロジックの状態として、Pre−Charge Phase、およびEvaluation Phaseという2つの状態を持ち、この2つの状態を行き来することによって演算を行なう処理を漏洩防止策としたものである。

【0012】

Pre−Charge Phaseはゲート回路が初期化されている状態であり、Evaluation Phaseは実際の演算を行なっている状態ということができる。さらにゲート回路の入出力に対して相補的な入力および出力が存在する。この相補的入力に対して正論理ゲートと負論理ゲートが形成され、相補的な出力が得られる。WDDLはこの2つの機構、Pre−Charge PhaseとEvaluation Phaseの2状態および相補的な入出力の存在によって、いかなる入力信号に対しても出力はPre−Charge PhaseからEvaluationo PhaseおよびEvaluation PhaseからPre−Charge Phaseに状態が遷移するときに一度だけ出力が変化するMonotonicityを満たしている。

【0013】

WDDLにはこのような性質があるため、不要な過渡遷移が生じることがない。さらに相補的な出力は任意の入力に対してどちらかの出力のみ変化するので、状態が遷移したときにのみ充放電が行なわれるCMOS(Complemetary Metal Oxide Semiconductor)プロセスを用いたロジックでは消費電流が一定となる。よって秘密情報を含むビット値の違いによって消費電流の相違がなくなるので、DPA攻撃に対して有効な対策となる。

【0014】

しかしながらWDDLは相補的入出力が存在し、その入出力の遅延差をなくすようにレイアウトを行なわなければならない。さらに演算構成上で2つの演算入力に対して大幅な遅延差がある場合には、DPA攻撃によって秘密情報が漏洩してしまう危険が存在するという問題点を有する。

【0015】

上述のAESにおけるSubByteと呼ばれている内部のS−Box演算は、例えば二分決定グラフ(BDD: Binary Decision Diagram)を用いたハードウェアによって実行可能である。二分決定グラフ(BDD)については、例えば、特許文献1に記載されている。なお、二分決定グラフ(BDD)については本明細書中においても後段で説明する。

【0016】

特許文献1には二分決定グラフ(BDD)で構成されたS−Boxなどの組合せ回路の構成およびその論理合成方法に関することが記載されている。共通鍵暗号による暗号処理を実行する場合、S−Boxと呼ばれる非線形変換部を利用した非線形変換処理を実行することが必要であり、このS−Boxの処理速度が暗号処理演算自体の処理速度に大きく影響している。例えば、AESのS−Boxはガロア体の逆元演算回路が必要である。

【0017】

この回路を二分決定グラフ(BDD)で構成せず、例えば、合成体(composite field)で実現しようとすると、BDDのような真理値表から直接回路を導出する構成に比べて数倍程度の回路遅延が生じてしまうことになる。従って、高速な実装が要求される場合はBDD構成とすることが好ましい。しかしながら、BDDを用いたS−Boxは高速動作が実現されるが、DPA攻撃に関する考慮を行わないと、不要な過渡遷移等の信号伝搬に基づく解析が可能となり秘密鍵等の秘密情報の漏洩の危険が発生するという問題がある。すなわち、二分決定グラフ(BDD)を適用した論理回路構成による演算を実行した場合、内部信号の遅延差による過渡遷移が生じ、DPA攻撃によって秘密情報が漏洩してしまうことがあるという問題がある。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】特開2003−223100

【非特許文献】

【0019】

【非特許文献1】Paul C.Kocher,Joshaua Jaffe and Benjamin Jun,"Differential Power Analysis",CRYPTO 1999,Lecture Note in Computer Science,Vol.1666,Springer−Verlag(1999),pp.388−397.

【非特許文献2】Elisabeth Oswald, Stefan Mangard, Norbert Pramstaller,"A Side−Channel Analysis Resistant Description of the AES S−Box",FSE 2005,LNCS 3557,pp.413−423.

【非特許文献3】Kris Tiri, Ingrid Verbauwhede,"Securing Encryption Algorithms against DPA at the Logic Level: Next Generation Smart Card Technology",CHES 2003,LNCS 2779,pp.125−136.

【発明の開示】

【発明が解決しようとする課題】

【0020】

本発明は、上記問題点に鑑みてなされたものであり、不要な過渡遷移を生じさせることなく、また遅延差も少なくした論理回路による演算処理構成を実現するものであり、例えば、DPA攻撃による秘密情報漏洩の可能性を低減させて、攻撃に対する耐性を高めたデータ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムを提供することを目的とする。

【課題を解決するための手段】

【0021】

本発明の第1の側面は、

入力データを第1下層セレクタ及び第2下層セレクタからの出力信号に応じて変換するデータ変換装置であって、

前記データ変換装置は、

前記入力データがセレクタ信号として入力されるセレクタ信号入力部、

前記入力データが反転され、反転セレクタ信号として入力される反転セレクタ信号入力部、

前記第1下層セレクタから出力される第1下層セレクタ出力信号が入力される第1下層セレクタ出力信号入力部、

前記第2下層セレクタから出力される第2下層セレクタ出力信号が入力される第2下層セレクタ出力信号入力部を有する上層セレクタを備え、

前記上層セレクタは、

前記セレクタ信号と、前記第1下層セレクタ出力信号とのアンド演算を行う第1アンド回路、

前記反転セレクタ信号と、前記第2下層セレクタ出力信号とのアンド演算を行う第2アンド回路、

前記第2アンド回路からの出力信号と、前記第1アンド回路からの出力信号とのオア演算を行うオア回路、

前記セレクタ信号の伝播を制限することにより、前記第1アンド回路から、前記セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、

前記反転セレクタ信号の伝播を制限することにより、前記第2アンド回路から、前記セレクタ信号及び前記第2下層セレクタ出力信号の出力が制限される第2出力制限素子、

を有するデータ変換装置にある。

【0022】

さらに、本発明の第2の側面は、

入力ビットのデータ変換処理を実行する演算処理装置であり、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、

定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路と、

前記論理回路を適用したデータ変換処理の制御を行う制御部とを備え、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を有し、

前記論理回路を構成する最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記制御部は、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させる制御を行うことを特徴とする演算処理装置にある。

【0023】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路は、さらに前記定数項を入力する複数の最下層セレクタの前段にプリチャージ信号入力部を備えた定数項入力部対応演算回路を有し、前記制御部は、前記定数項入力部対応演算回路に対するプリチャージ信号の切り替え制御により、前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする。

【0024】

さらに、本発明の演算処理装置の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたアンドゲートによって構成され、前記制御部は、前記アンドゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする。

【0025】

さらに、本発明の演算処理装置の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたオアゲートによって構成され、前記制御部は、前記オアゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする。

【0026】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路を構成するセレクタは、同一値を入力値とする複数のセレクタを1つのセレクタとした共有セレクタを有する構成であることを特徴とする。

【0027】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路を構成するセレクタは、反転出力を行なうセレクタおよび反転入力を行なうセレクタであることを特徴とする。

【0028】

さらに、本発明の演算処理装置の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力を固定値とし、前記エバリュエーション・フェーズにおいて、前記定数項または乱数を前記最下層セレクタの入力として設定する構成であることを特徴とする。

【0029】

さらに、本発明の演算処理装置の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力をランダムに0または1とするように前記ゲート回路の出力制御を行う構成であることを特徴とする。

【0030】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路は、二分決定グラフ(BDD: Binary Decision Diagram)を用いた構成を有することを特徴とする。

【0031】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路は、入力ビットのデータ変換処理として、入力ビットの非線形変換処理を実行する構成であることを特徴とする。

【0032】

さらに、本発明の第3の側面は、

演算処理装置において入力ビットのデータ変換処理を実行する演算処理制御方法であり、

前記演算処理装置は、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路を有し、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を備え、

最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記論理回路を適用したデータ変換処理の制御を行なう制御部が、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させる制御を行うことを特徴とする演算処理制御方法にある。

【0033】

さらに、本発明の演算処理制御方法の一実施態様において、前記論理回路は、さらに前記定数項を入力する複数の最下層セレクタの前段にプリチャージ信号入力部を備えた定数項入力部対応演算回路を有し、前記制御部は、前記定数項入力部対応演算回路に対するプリチャージ信号の切り替えにより、前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行うことを特徴とする。

【0034】

さらに、本発明の演算処理制御方法の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたアンドゲートによって構成され、前記制御部は、前記アンドゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行うことを特徴とする。

【0035】

さらに、本発明の演算処理制御方法の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたオアゲートによって構成され、前記制御部は、前記オアゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行うことを特徴とする。

【0036】

さらに、本発明の演算処理制御方法の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力を固定値とし、前記エバリュエーション・フェーズにおいて、前記定数項または乱数を前記最下層セレクタの入力として設定することを特徴とする。

【0037】

さらに、本発明の演算処理制御方法の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力をランダムに0または1とする制御を行うことを特徴とする。

【0038】

さらに、本発明の第4の側面は、

演算処理装置において入力ビットのデータ変換処理を実行させるコンピュータ・プログラムであり、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路を有し、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を備え、

最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記コンピュータ・プログラムは、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させることを特徴とするコンピュータ・プログラムにある。

【0039】

なお、本発明のコンピュータ・プログラムは、例えば、様々なプログラム・コードを実行可能なコンピュータ・システムに対して、コンピュータ可読な形式で提供する記憶媒体、通信媒体、例えば、CDやFD、MOなどの記録媒体、あるいは、ネットワークなどの通信媒体によって提供可能なコンピュータ・プログラムである。このようなプログラムをコンピュータ可読な形式で提供することにより、コンピュータ・システム上でプログラムに応じた処理が実現される。

【0040】

本発明のさらに他の目的、特徴や利点は、後述する本発明の実施例や添付する図面に基づくより詳細な説明によって明らかになるであろう。なお、本明細書においてシステムとは、複数の装置の論理的集合構成であり、各構成の装置が同一筐体内にあるものには限らない。

【発明の効果】

【0041】

本発明の構成によれば、非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう構成とした。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

【0042】

さらに、本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。従って、セレクタ信号および反転セレクタ信号の信号変化がオア回路から出力されることを防止できると共に、第1下層セレクタ出力信号及び第2下層セレクタ信号出力信号の信号変化も防止することができる。そのため、電力差分攻撃への耐性を高めることができる。

【0043】

さらに、本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。本構成によって、第1アンド回路に入力されるセレクタ信号及び第2アンド回路に入力される反転セレクタ信号の伝播が制限されるので、第1下層セレクタ出力信号又は第2下層セレクタ出力信号の伝播を制限することなく、第1下層セレクタ出力信号及び第2下層セレクタ出力信号の信号変換がオア回路から出力されることを制限できる。

【0044】

すなわち、第1下層セレクタ出力信号及び第2下層セレクタ出力信号に対して直接制限素子を付与する必要がなくなるため、回路規模の削減が可能になる。このように、本願発明の一実施例構成によれば、第1下層セレクタ出力信号及び第2下層セレクタ出力信号から信号変化が検出されることを少ない信号伝播素子で実現することができるため、電力差分攻撃への耐性向上と回路規模の削減を同時に達成することができる。

【図面の簡単な説明】

【0045】

【図1】AESやDESなどの共通鍵暗号方式の暗号処理を実行する基本構成を示す図である。

【図2】AES暗号処理構成例を示す図である。

【図3】AES暗号処理を実行するハードウェア構成例を示す図である。

【図4】非線形変換処理に適用する変換テーブル(S−Boxテーブル)を示す図である。

【図5】非線形変換テーブル(S−Boxテーブル)に基づく変換結果中の出力の下位1ビットを出力する論理回路としての二分決定グラフ(BDD)を示す図である。

【図6】図4に示すテーブルに示される256個の出力値の最下位ビットに対応するビット値のみを示す変換テーブルを示す図である。

【図7】図5に示す非線形変換論理回路に適用されるセレクタの構成例を示す図である。

【図8】過渡遷移について説明する図である。

【図9】プリチャージ・フェーズ(Pre−Charge Phase)とエバリュエーション・フェーズ(Evaluation Phase)を設定可能とした論理回路構成を示す図である。

【図10】図9に示す非線形変換論理回路に適用されるセレクタの構成例を示す図である。

【図11】本発明の第1の実施形態としての非線形変換処理を実行する論理回路構成を示す図である。

【図12】本発明の第1の実施形態としての論理回路における信号遷移を説明する図である。

【図13】本発明の第1の実施形態としての非線形変換処理を実行する論理回路の制御構成例を示す図である。

【図14】セレクタの共有化構成について説明する図である。

【図15】反転出力セレクタおよび反転入力セレクタを利用した本発明の実施例構成について説明する図である。

【図16】乱数入力構成を持つ本発明の実施例構成について説明する図である。

【図17】オアゲートを持つ本発明の実施例構成について説明する図である。

【図18】本発明の構成が適用可能な暗号処理実行デバイスとしてのICモジュールの構成例を示す図である。

【発明を実施するための形態】

【0046】

以下、本発明のデータ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムの詳細について説明する。

【0047】

以下、本発明の実施の形態として、共通鍵暗号方式であるAES(Advanced Encryption Standard)における本発明の適用例を説明する。共通鍵暗号方式であるAESは、例えば、入力128ビットの平文を128ビットの暗号文に変換する処理を行なう。従来の共通鍵暗号方式であるDES(Data Encryption Standard)と同様、データ変換処理単位としてのラウンド演算を繰り返し実行する構成を持つ。なお、本発明は、AESやDESなどの共通鍵暗号処理のみならずRSAなどの公開鍵暗号処理やSHA−1などのハッシュ関数の演算など、非線形変換処理や線形変換処理などのデータ変換処理を実行する各種の演算において適用可能である。

【0048】

以下、下記の項目に従って、本発明について順次説明する。

1.共通鍵暗号方式の暗号処理を実行する基本構成について

2.BDDを用いた非線形変換部(S−Box)の一般的構成について

3.本発明に従った非線形変換部の構成例1

4.本発明に従った非線形変換部の構成例2(セレクタの共有構成例)

5.本発明に従った非線形変換部の構成例3(反転出力セレクタおよび反転入力セレクタ利用構成)

6.本発明に従った非線形変換部の構成例4(乱数の入力構成)

7.本発明に従った非線形変換部の構成例5(ORゲート利用構成)

8.暗号処理装置の構成例

【0049】

[1.共通鍵暗号方式の暗号処理を実行する基本構成について]

図1にAESやDESなどの共通鍵暗号方式の暗号処理を実行する基本構成を示す。図1に示すように、共通鍵暗号の基本的な暗号処理構成は、鍵スケジュール部101と、データ変換部110からなる。鍵スケジュール部101は、秘密鍵100を入力して、秘密鍵100に基づいて各ラウンドにおいて適用するラウンド鍵を生成して各ラウンド演算部151−1〜151-nに出力する。

【0050】

データ変換部110は、変換対象のデータを入力し、複数のラウンド演算部151−1〜151−nにおいて、鍵スケジュール部101から入力するラウンド鍵を適用し、データ変換を行って変換データを出力する。

【0051】

ラウンド演算部151−1〜151−nでは同様のラウンド演算を繰り返し実行する。1つのラウンドでは、入力ビットの変換処理として、変換テーブルを利用した入力ビットの非線形変換や、線形変換、入力鍵(ラウンド鍵)を適用したデータ変換処理などが実行される。その結果に基づいて次のラウンド演算部の入力が生成される。

【0052】

例えば、AES暗号では、ラウンド演算部151−1〜151−nにおいて実行される非線形変換処理はSubByteと呼ばれる。このSubByteと呼ばれる非線形変換処理は、予め用意された非線形変換テーブル(S−Boxテーブル)を利用した変換処理として実行される。

【0053】

図2にAES暗号処理の詳細構成を示す。鍵スケジュール部201は、秘密鍵200を入力して、秘密鍵200に基づいて各ラウンドにおいて適用するラウンド鍵を生成して各ラウンド演算部210に出力する。AES暗号におけるラウンド演算部210は、図に示すように、ラウンド鍵との排他的論理和演算を実行する排他的論理和演算部211、SubByteと呼ばれる非線形変換処理を実行するS−Box212、各S−Box212の出力の入れ替え処理を実行するMix−Colum213、さらにMix−Colum213とラウンド鍵との排他的論理和演算を実行する排他的論理和演算部214、排他的論理和演算部214の出力に対して非線形変換処理を実行するS−Box215によって構成される。なお、これらの各処理は、図に示すように8ビットデータに分割されたデータを単位として実行される。

【0054】

なお、ラウンド演算は繰り返し実行されるが、AES暗号演算実行部をハードウェアとして構成する場合は、繰り返し実行されるラウンド演算部を1つ構成し、繰り返し利用する構成とする。例えば、図3にAES暗号を実行するハードウェア構成例を示す。

【0055】

AES暗号演算実行部250は、最初のラウンド鍵0を入力して、排他的論理和演算部251において、暗号処理対象データ(128ビット)と排他的論理和演算処理を実行し、セレクタ252を介してレジスタ253に入力し、レジスタ253から8ビットデータ単位で、S−Box254において非線形変換処理が実行され、Mix−Colum255においてビット値入れ替えがなされ、セレクタ256を介して排他的論理和演算部257においてラウンド鍵との排他的論理和演算が実行され、この結果データが再びセレクタ252を介してレジスタ253に入力されて、S−Box254に入力される。この処理が繰り返し実行され、予め規定されたラウンド数の処理が終了すると、結果データとしての暗号文がレジスタ253から出力される。

【0056】

ラウンド演算部の非線形変換部であるS−Boxの各々では、8ビットデータをそれぞれ入力して、非線形変換テーブル(S−Boxテーブル)を適用して非線形変換処理を実行して出力8ビットを生成する。すなわち、16個のS−Boxの各々において8ビット毎の非線形変換データを順次生成して、16×8=128ビット分の非線形変換データを生成し出力する。図4に非線形変換処理に適用する変換テーブル(S−Boxテーブル)を示す。

【0057】

図4に示す変換テーブルにおいて、最上段の横ラインに示す(0,1,2,・・・d,e,f)は変換処理対象となる入力8ビットの下位4ビットを16進表現で示している。0〜fは、2進表現では0000〜1111に相当する。左端の縦ラインに示す(0,1,2,・・・d,e,f)は変換処理対象となる入力8ビットの上位4ビットを16進表現で示している。これらの上位、下位ビットの計8ビット(00000000〜11111111)に対する出力としての8ビットがテーブル内部に記録されている。

【0058】

すなわち、入力ビットは8ビット00〜FF(00000000〜11111111)であり、28=256種類のビット状態がある。これを上位4ビットと下位4ビットに分割して、図4に示すテーブルを適用して256種類の出力8ビット00〜FF(00000000〜11111111)を決定する。

【0059】

例えば、入力が16進表現で00(2進表現で00000000)である場合、図4に示すテーブルに基づいて出力が63(16進表現)となる。すなわち、左上端のテーブル値[63]が出力値として選定される。また、入力がC0(16進数)である場合、図4に示すテーブルに基づいて出力がBA(16進表現)となる。このように、ラウンド演算部における非線形変換処理は、図4に示された変換テーブルを適用した8ビット入力、8ビット出力の1対1写像を実行する。

【0060】

[2.BDDを用いた非線形変換部(S−Box)の一般的構成について]

このような非線形変換テーブル(S−Boxテーブル)による変換処理を実行するハードウェアの回路構成例として、二分決定グラフ(BDD: Binary Decision Diagram)を用いた構成がある。図5に非線形変換テーブル(S−Boxテーブル)に基づく変換結果中の出力の下位1ビットを出力する論理回路としての二分決定グラフ(BDD)を示す。

【0061】

図5には、論理関数としての2入力1出力のセレクタを、第1層から第8層の階層構成として論理回路としての二分決定グラフ(BDD)を示している。ピラミッド型の8層構造にセレクタが接続された構成を持つ。最終1ビットを出力するセレクタは、第1層のセレクタである。

【0062】

第1層にはセレクタが1個、第2層にはセレクタが2個、第3層にはセレクタが4個、第4層にはセレクタが8個、第5層にはセレクタが16個、第6層にはセレクタが32個、第7層にはセレクタが64個、第8層にはセレクタが128個あり、全部で255個のセレクタで構成されている。

【0063】

第1層のセレクタ入力は第2層のセレクタ出力が供給され、

第2層のセレクタ入力は第3層のセレクタ出力が供給され、

第3層のセレクタ入力は第4層のセレクタ出力が供給され、

第4層のセレクタ入力は第5層のセレクタ出力が供給され、

第5層のセレクタ入力は第6層のセレクタ出力が供給され、

第6層のセレクタ入力は第7層のセレクタ出力が供給され、

第7層のセレクタ入力は第8層のセレクタ出力が供給され、

第8層のセレクタ入力は0もしくは1の定数項が供給される。

【0064】

第8層のセレクタ入力は、図4に示す非線形変換テーブル(S−Boxテーブル)に基づいて決定される0もしくは1の定数項であり、256ビットデータである。

図5に示す論理回路は、非線形変換結果としての出力8ビットの最下位ビットを出力する選択回路である。この場合、図5の最下段に示される第8層のセレクタ入力値としての256ビット[10110111・・・11110010]は、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値として設定される。

【0065】

例えば、図5の最下段に示される第8層のセレクタ入力値の左端のビット値[1]は図4に示すテーブルの最上段の左端に示す出力値である(63)の最下位ビットに相当し、図5の最下段に示される第8層のセレクタ入力値の右端のビット値[0]は図4に示すテーブルの最下段の右端に示す出力値である(16)の最下位ビットに相当する。

【0066】

図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値のみを示す変換テーブルを図6に示す。この図6に示す16×16=256個の出力値は、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値であり、このビット値が、図5に示す回路構成の第8層のセレクタ入力値として設定される。

【0067】

各層のセレクタに入力するセレクト信号は、非線形変換対象データとして入力される128ビットを8ビット毎に分割した8−bitの各1ビットが利用される。入力8−bit中の最上位ビット(in[7])が、第1層のセレクタに対するセレクト信号として入力され、第2番目のビット(in[6])が、第2層のセレクタに対するセレクト信号として入力され、以下、各層に各ビットが入力され、最下位ビット(in[0])は、第8層のセレクタに対するセレクト信号として入力される。

【0068】

入力8ビットは、非線形変換対象データとしての128ビットの分割データであり、128ビットを構成する8ビット毎に、順次、入力値が変更(遷移)され、次々に8ビット単位で非線形変換処理が行なわれることになる。

【0069】

各セレクタに入力されるセレクト信号が[0]の場合にはセレクタ入力の左側の入力が選択されて上位層に出力され、セレクト信号が[1]の場合にはセレクタ入力の右側が選択されて上位層に出力される。従って、セレクト信号8ビットが決まると、第8層のセレクタ入力256個のうちのひとつが出力される。第8層のセレクタ入力の定数は第1層から第8層のセレクト入力の順列で一意に決定される。

【0070】

例えば、非線形変換対象データとしての入力8ビットが[00000000]である場合、セレクト信号は、すべて[0]であり、すべてのセレクタにおいて、左側の入力が選択されて上位層に出力されることになり、結果として、図5の最下段に示される第8層のセレクタ入力値の左端のビット値[1]が最終的な出力(第1層のセレクタ出力)とされる。この出力は、図4に示すテーブルの最上段の左端に示す出力値である(63)の最下位ビットに相当する。このように、非線形変換対象データとしての入力ビットの値(00000000〜11111111)の値に応じて、第8層のセレクタ入力256個のうちのひとつが出力される。これらの第8層のセレクタ入力256個のそれぞれは、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値である。

【0071】

この図5に示す階層構成のセレクタからなる構成を8つ適用することで、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の8ビット全てに対応するビット値を決定する。

【0072】

図5に示す構成においては、最下段の第8層のセレクタ入力値としての256ビット[10110111・・・11110010]は、図6を参照して説明したビット値、すなわち、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値として設定されている。

【0073】

最下段の第8層のセレクタ入力値を、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類を設定してその出力を組み合わせることで、入力8ビットを図4に示すテーブルによって非線形変換した結果としての出力8ビットを得ることができる。

【0074】

このようにして、図4に示す非線形変換テーブル(S−Boxテーブル)と同等の値を出力する構成が実現される。すなわち、図4に示す非線形変換テーブル(S−Boxテーブル)と同等の値を出力される論理関数は図5のような二分決定グラフ(BDD)によって構成することができる。

【0075】

図5に示す論理回路には、先に説明したように、第1層にはセレクタが1個、第2層にはセレクタが2個、第3層にはセレクタが4個、第4層にはセレクタが8個、第5層にはセレクタが16個、第6層にはセレクタが32個、第7層にはセレクタが64個、第8層にはセレクタが128個あり、全部で255個のセレクタで構成されている。これらのセレクタの構成例を図7に示す。

【0076】

セレクタ270の構成はたとえば図7に示すように、S−boxテーブルから求められる定数項aとセレクト信号の反転値を入力するアンドゲート271、S−boxテーブルから求められる定数項bとセレクト信号の信号値を入力するアンドゲート272、さらに、アンドゲート271,272の出力を入力するORゲート273によって構成される。

【0077】

例えば、セレクタに入力されるセレクト信号が[0]の場合にはセレクタ入力の定数項[a]が選択されて出力され、セレクト信号が[1]の場合にはセレクタ入力の定数項[b]が選択されて出力される。

【0078】

この図7に示す構成を持つセレクタが図5のような二分決定グラフ(BDD)の各層に設定されて下位から上位層に順次、出力を決定していくことになる。しかしながら、このようなセレクタ構成を採用すると、それぞれの層のセレクト信号の入力タイミングが乱れによる過渡遷移が発生する。

【0079】

過渡遷移について、図8を参照して説明する。図8(1)は、図5に示す従来型の二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路構成において、各層に入力される(p)セレクト信号[in]と、(q)最終セレクタ出力[out]の遷移を示すタイミングチャートであり、

【0080】

図8(2)は、図8(1)に示すデータ領域281の拡大図である。(p)セレクト信号[in]は、例えば図5の論理回路における第1層から第8層までの8つのセレクタ層に対する8つの入力ビットの遷移タイミングが図8(2)(p)セレクト信号[in[0]〜[7]]に示す信号線の交差領域で発生する。この入力8ビットの遷移は、完全な同一タイミングで発生させることは困難であり、各入力ビットの遷移タイミングにはずれが発生することになる。

【0081】

従って、入力8ビットの遷移が開始されてから完全に全ビットの遷移が終了するまでには、一定の期間を要することになる。これが、図8(2)に示すΔtの遷移期間に相当する。このような、遷移期間において、図8(2)(q)に示す出力[out]は、8層のセレクタ層に対する入力8ビットの遷移に応じて、出力値を変化させることになる。図8(2)(q)に示す点線部では、セレクト信号の遷移タイミングのずれに応じた出力値変化が発生する。

【0082】

この出力値の変化の解析により、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路構成で利用されている信号値が解析される可能性がある。すなわち、先に背景技術の欄で説明したように、この過渡遷移に起因して、DPA攻撃によって秘密情報が漏洩してしまうことがある。

【0083】

なお、背景技術の欄で説明したように、この過渡遷移を防止する従来構成としてWDDL(Wave Differential Dynamic Logic)を用いた対策が開示されているが、WDDLは相補的入出力が存在し、その入出力の遅延差をなくすようにレイアウトを行なわなければならないというレイアウト構築の困難性という問題がある。さらに演算構成上で2つの演算入力に対して大幅な遅延差がある場合には、DPA攻撃を確実に防止できないという問題がある。

【0084】

[3.本発明に従った非線形変換部の構成例1]

本発明は、不要な過渡遷移を生じさせることなく、また遅延差も少なくした論理回路による演算処理構成を実現するものである。以下、本発明に従った非線形変換部(S−Box)の実施例について説明する。

【0085】

本発明の暗号処理装置は、共通鍵ブロック暗号に従った暗号処理を実行する暗号処理装置であり、入力ビットの非線形変換処理を実行して出力ビットを生成する論理回路と、この論理回路に対する入力ビットの切り替え処理としての入力ビット遷移処理を、論理回路の出力を固定値に維持したプリチャージ・フェーズにおいて実行させ、入力ビット遷移処理が終了した後、エバリュエーション・フェーズへ移行させて遷移後の入力ビットの非線形変換処理に基づく出力ビットの生成処理を行なわせる制御部とを有する。

【0086】

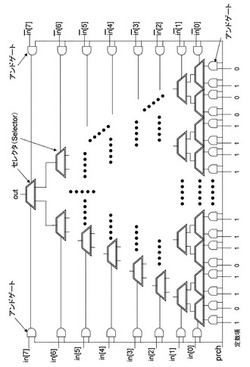

非線形変換処理を実行する本発明に係るピラミッド型のセレクタ階層構成を持つ二分決定グラフ(BDD)の基本構成を図9に示す。図9に示すように本実施例におけるS−Boxを構成する論理回路は、図5を参照して説明したピラミッド型のセレクタ階層構成を持つ二分決定グラフ(BDD)と同様8層のピラミッド型セレクタ構成を有する。最下層の第8層のセレクタ入力は、図5を参照して説明した第8層のセレクタの入力値と同様の定数項であり、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類のいずれかである。

【0087】

図9に示す論理回路に、第1層にはセレクタが1個、第2層にはセレクタが2個、第3層にはセレクタが4個、第4層にはセレクタが8個、第5層にはセレクタが16個、第6層にはセレクタが32個、第7層にはセレクタが64個、第8層にはセレクタが128個あり、全部で255個のセレクタで構成されている。これらのセレクタには、図9に示すようにセレクト信号と反転セレクト信号の2つの信号が入力される。セレクタの構成例を図10に示す。

【0088】

図10に示すようにセレクタ300は、S−boxテーブルから求められる定数項aとセレクト信号の反転値を入力するアンドゲート301、S−boxテーブルから求められる定数項bとセレクト信号の信号値を入力するアンドゲート302、さらに、アンドゲート301,302の出力を入力するORゲート303によって構成される。

【0089】

このセレクタ300の構成は、先に図7を参照して説明したセレクタ270の構成と異なり、セレクト信号の入力と、反転セレクト信号とが独立に入力される構成となっている。すなわち、アンドゲート301,302の入力の4系統の信号は、それぞれ独立した信号となっている。先に図7を参照して説明したセレクタ270では、アンドゲート271に入力される反転セレクト信号と、アンドゲート272に入力されるセレクト信号は、1つの入力セレクト信号に基づいて生成された信号である点が、10に示す構成と異なる点である。

【0090】

なお、出力信号Cは、セレクタに入力されるセレクト信号が[0]の場合にはセレクタ入力の定数項[a]が選択されて出力され、セレクト信号が[1]の場合にはセレクタ入力の定数項[b]が選択されて出力される点は、先に図10を参照して説明したと同様である。

【0091】

本発明の第1実施例に係る非線形変換処理を実行するS−Boxとしての二分決定グラフ(BDD)の具体的な論理回路構成例を図11に示す。図11に示す回路に設定されるセレクタは、図10を参照して説明したセレクト信号と、反転セレクト信号を独立に入力可能とした構成をもつ。

【0092】

図11に示すように、本発明の第1実施例に係る非線形変換処理を実行する論理回路は、

第8層のセレクタ入力部の前段に演算回路(アンドゲート)、

各セレクタに対するセレクト信号入力部の前段に演算回路(アンドゲート)、

各セレクタに対する反転セレクト信号入力部の前段に演算回路(アンドゲート)、

これらの演算回路(アンドゲート)を設けている。

【0093】

第8層のセレクタの入力は256個であり、256個のアンドゲート回路によって第8層のセレクタの入力値を生成する。256個のアンドゲート回路の一方の入力は、図5を参照して説明した第8層のセレクタの入力値と同様の定数項であり、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類のいずれかである。

【0094】

各層のセレクタに入力するセレクト信号は、非線形変換対象データとして入力される128ビットを8ビット毎に分割した8−bitの各1ビットが利用される。入力8−bit中の最上位ビット(in[7])が、第1層のセレクタに対するセレクト信号として演算回路(アンドゲート)を介して入力され、第2番目のビット(in[6])が、第2層のセレクタに対するセレクト信号として演算回路(アンドゲート)を介して入力され、以下、各層に各ビットが演算回路(アンドゲート)を介して入力され、最下位ビット(in[0])は、第8層のセレクタに対するセレクト信号として演算回路(アンドゲート)を介して入力される。

【0095】

なお、入力8ビットは、前述したように非線形変換対象データとしての128ビットの分割データであり、128ビットを構成する8ビット毎に、順次、入力値が変更(遷移)され、次々に8ビット単位で非線形変換処理が行なわれることになる。

【0096】

各セレクタには、セレクト信号の他に反転セレクト信号も、演算回路(アンドゲート)を介して入力される。

【0097】

このように、本実施例に係る論理回路は、

定数項の入力部である第8層のセレクタ入力部の前段に演算回路(アンドゲート)、

各セレクタに対するセレクト信号入力部の前段に演算回路(アンドゲート)、

各セレクタに対する反転セレクト信号入力部の前段に演算回路(アンドゲート)、

これらの演算回路(アンドゲート)を設けており、

第8層のセレクタの入力値をアンドゲート回路の出力値、

各セレクタに対するセレクト信号入力値をアンドゲート回路の出力値、

各セレクタに対する反転セレクト信号入力値をアンドゲート回路の出力値、

としている。これらの演算回路の処理によってプリチャージ・フェーズ(Pre−Charge Phase)とエバリュエーション・フェーズ(Evaluation Phase)状態を設定可能としている。なお、これらのフェーズの移行制御や入力情報の設定、遷移制御は図示しない制御部によって実行される。

【0098】

図11に示す例は、図5と同様、図6に示すビット値、すなわち図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最下位ビットを定数項として設定した例を示している。従って、図11に示す構成は、図5の構成と同様、非線形変換処理による出力8ビットの最下位ビットを出力する回路構成である。

【0099】

図11に示す第8層のセレクタに接続された256個のアンドゲート回路と、各層の8つのセレクト信号および8つの反転セレクト信号の入力部に接続されたそれぞれ8つのアンドゲート回路のもう一方の入力は、プリチャージ信号入力[prch]である。プリチャージ信号入力[prch]が[0]の場合には第8層のセレクタ入力の256個の入力、各層のセレクタに対するセレクト信号入力、各層のセレクタに対する反転セレクト信号入力、これらのすべてが0となる。この状態が、プリチャージ・フェーズ(Pre−Charge Phase)状態である。すなわち、プリチャージ・フェーズ(Pre−Charge Phase)では、すべてのセレクタ入力値が0となる。

【0100】

プリチャージ信号入力[prch]が[1]の場合には、定数項が第8層のセレクタ入力として設定され、さらに、真のセレクト信号と反転セレクト信号、すなわち、非線形変換対象データとして入力される128ビットを8ビット毎に分割した8−bitのデータの値がセレクト信号として各セレクタに入力され、その反転値が反転セレクト信号とし各セレクタにアンドゲートを介して入力される。この入力状態が、エバリュエーション・フェーズ(Evaluation Phase)状態である。

【0101】

本実施例においては、

8階層のセレクタを適用した出力ビットの算出処理を実行するエバリュエーション・フェーズ(Evaluation Phase)と、

セレクタ入力のすべてを0とするプリチャージ・フェーズ(Pre−Charge Phase)と、

これらの2つのフェーズを交互に繰り返す。

【0102】

各セレクタにおける入力値の遷移について、図12を参照して説明する。図12(a)には、先に図10を参照して説明したセレクタ300の構成を示している。図12(b)は、セレクタに対する入力信号の遷移を示している。図12(a)に示すセレクタ300は、S−boxテーブルから求められる定数項aとセレクト信号の反転値を入力するアンドゲート301、S−boxテーブルから求められる定数項bとセレクト信号の信号値を入力するアンドゲート302、さらに、アンドゲート301,302の出力を入力するORゲート303によって構成される。

【0103】

図12(b)は、セレクタに対する入力信号の時間的遷移を示している。左から右に時間が推移し、フェーズが交互に切り替わり、セレクタ入力値が入れ替えられる。上述したように、本発明に従った論理回路では、セレクタに対するすべての入力を[0]とするプリチャージ・フェーズと、正しい定数項とセレクト信号、および反転セレクト信号をセレクタに入力して出力ビットの算出処理を実行するエバリュエーション・フェーズとを交互に繰り返す。

【0104】

図12(b)は、セレクタに対する入力信号、すなわち、

定数項(a)の入力、

定数項(b)の入力、

セレクト信号の入力、

反転セレクト信号の入力、

これらの入力値の時間的遷移を示している。これらの入力は、すべて一方の入力をプリチャージ信号としたアンドゲートを介して入力されており、プリチャージ信号は、プリチャージ・フェーズでは[0]、エバリュエーション・フェーズでは[1]となる。

【0105】

最初のプリチャージ・フェーズでは、プリチャージ信号は[0]に設定されるので、すべてのセレクタ入力値は[0]となる。その後のエバリュエーション・フェーズでは、プリチャージ信号は[1]に設定され、定数項、セレクト信号、反転セレクト信号のそれぞれの正しい値がセレクタに入力される。このエバリュエーション・フェーズにおいて、1組の8ビットのセレクト信号に対応する出力値(非線形変換結果)が、最上段(第1層)のセレクタから出力される。

【0106】

さらに、このエバリュエーション・フェーズの後、プリチャージ・フェーズに移行し、すべてのセレクタ入力値は[0]に設定される。このプリチャージ・フェーズ期間において、セレクト信号と反転セレクト信号は次の入力値(8ビット)に入れ替えられる。プリチャージ・フェーズ期間が終了すると、エバリュエーション・フェーズに移行し、新たなセレクト信号と反転セレクト信号に基づいて新たな8ビットのセレクト信号に対応する出力値(非線形変換結果)が、最上段(第1層)のセレクタから出力される。

【0107】

このようにして、エバリュエーション・フェーズとプリチャージ・フェーズとを交互に繰り返し実行する。この構成によれば、各セレクタにおける新たなセレクト信号の入力タイミングは、常にセレクタ入力がオール0のプリチャージ・フェーズからエバリュエーション・フェーズへの切り替え時となる。このタイミングにおけるセレクタ入力値変化は、すべて[0]から真の入力値への変化として設定される。従って、先に図8を参照して説明した過渡遷移、すなわち8層の各セレクタ層に対する真のデータ値である8ビットの遷移に応じた出力値変化を電力変化として解析することは困難となる。

【0108】

すなわち、セレクタに対するセレクト信号の遷移は、セレクタ入出力が[0]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、セレクタ出力は[0]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがなく秘密情報の漏洩防止が可能となる。

【0109】

本実施例の構成では、1組の8ビットのセレクト信号に対応する出力値が決定された後、すべてのセレクタに対する入力をすべて[0]とする初期状態にリセットし、リセット状態から新たなセレクト信号の入力が実行される構成としている。本構成によりセレクト信号の切り替えに伴って発生するセレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0110】

図13を参照して、エバリュエーション・フェーズとプリチャージ・フェーズとを交互に繰り返し実行する場合の、非線形変換部としてのS−Box(BBD)に対する入力信号の切り替え処理構成例について説明する。

【0111】

図11を参照して説明したように、非線形変換部としての論理回路である二分決定グラフ(BDD)としてのS−Boxにはセレクト信号および反転セレクト信号が入力され、さらに、第8層から定数項が入力される。エバリュエーション・フェーズにおいては、これらはすべて真の入力値が入力されるが、プリチャージ・フェーズにおいては、これらの値はすべて[0]に切り替えられることになる。

【0112】

図13に示すS−Box(BBD)に対する入力信号の切り替え処理実行部の構成において、データレジスタ321には、非線形変換処理対象としてのデータが入力され、データレジスタ制御部324の制御により、8ビット単位のデータが順次出力される。この8ビットデータが、エバリュエーション・フェーズにおいて、セレクト信号および反転セレクト信号としてS−Box(BBD)323に入力される。反転セレクト信号は反転素子322においてセレクト信号に対する反転処理が実行されて生成される。

【0113】

プリチャージ制御部325は、エバリュエーション・フェーズにおいては、プリチャージ信号[1]を出力する。この処理によって、エバリュエーション・フェーズにおいて、セレクト信号および反転セレクト信号がS−Box(BBD)323のセレクタに入力される。なお、図では示していないが、プリチャージ信号[1]は、S−Box(BBD)323内の最下層のセレクタの前段の定数項入力部を持つアンドゲートの一方の入力としても利用されており、エバリュエーション・フェーズにおいては、定数項が最下層のセレクタに入力され、真の非線形変換結果がS−Box(BBD)323から出力される。

【0114】

プリチャージ・フェーズにおいては、プリチャージ制御部325からプリチャージ信号、すなわち全てのセレクト信号、反転セレクト信号、および第8層入力値のすべてを[0]とするためのプリチャージ信号[0]がS−Box(BBD)323に入力される。この場合は、S−Box(BBD)323を構成するすべてのセレクタ入力は0となり、S−Box(BBD)323出力も0とされる。

【0115】

データレジスタ制御部324およびプリチャージ制御部325には、クロック信号が入力され、エバリュエーション・フェーズにおいてはプリチャージ制御部から[1]が出力されて、データレジスタ制御部324からのセレクタ信号の出力が有効値としてS−Box(BBD)323において利用され、真の非線形変換結果が出力される。が実行され、プリチャージ・フェーズにおいてはプリチャージ制御部325からプリチャージ信号[0]が出力され、S−Box(BBD)323を構成するすべてのセレクタ入力は0となり、S−Box(BBD)323出力も0とされる。各信号の出力タイミングは各フェーズの切り替えにクロックに従って実行される。

【0116】

この構成を適用することで、エバリュエーション・フェーズにおいては、1組の8ビットのセレクト信号および反転セレクト信号がS−Box323に入力され、その後、プリチャージ・フェーズに切り替わり、プリチャージ制御部325からのプリチャージ信号[0]がS−Box323に入力され、すべてのセレクタの入力が[0]にリセットされる。さらに、次のエバリュエーション・フェーズにおいて、リセット状態から新たなセレクト信号の入力が開始されるという処理を繰り返し実行することが可能となる。この処理構成とすることで、セレクト信号の切り替えに伴って発生するセレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0117】

[4.本発明に従った非線形変換部の構成例2(セレクタの共有構成例)]

例えば図11に示す二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路構成は、出力8ビット中の1ビットを出力するために適用される論理回路であり、入力8ビットから非線形変換結果としての出力8ビットを、並列に得るためには、図11に示す二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路を8個、組み合わせて動作させることが必要である。

【0118】

このように各出力ビット対応の二分決定グラフ(BDD)を用いた論理回路構成とする場合、回路規模が大きくなるが、回路規模の縮小のためセレクタを共有する構成が可能である。

【0119】

図14を参照して、セレクタの共有化構成について説明する。例えば、図14(A)に示すように、同一の入力値を持つ複数のセレクタ351,352が存在する場合、これらの複数のセレクタを1つのセレクタとして構成する。すなわち、図14(B)に示すように、セレクタ351,352の代用として1つのセレクタ361を設ける。このセレクタ共有化処理により、二分決定グラフ(BDD)を用いた論理回路構成を小さくすることが可能であり、回路規模の縮小およびコストダウンが可能となる。また、回路規模の削減により消費電流も小さくすることができる。

【0120】

[5.本発明に従った非線形変換部の構成例3(反転出力セレクタおよび反転入力セレクタ利用構成)]

次に、本発明の実施例3として、反転出力セレクタおよび反転入力セレクタを利用した構成例について説明する。図15を参照して本発明の実施例3の構成および処理について説明する。

【0121】

本発明の第3の実施形態は、先に図11を参照して説明した実施例1の二分決定グラフ(BDD)を用いた論理回路構成において適用するセレクタを偶数階層の場合には反転出力セレクタと、奇数階層の場合には反転入力セレクタとした構成である。セレクタは8階層であり、偶数回の反転が行なわれることになる。従って、最終出力は8階層のセレクタとした場合も、合わせて8階層の反転出力セレクタおよび反転入力セレクタとした場合も同一となる。

【0122】

反転出力つきセレクタおよび反転入力つきセレクタは、図11を参照して説明した構成において使用するセレクタよりも占有面積が小さくできる。従って、よって回路規模を削減でき、消費電流も小さくできる。

【0123】

なお、本構成においても、

(a)エバリュエーション・フェーズにおいては、セレクタ入力は、真の出力値(非線形変換結果)を得るための入力値として、8ビット単位の非線形変換処理対象としてのデータであるセレクト信号および反転セレクト信号が各セレクタに入力され、第8層のセレクタには、非線形変換テーブル(S−Boxテーブル)に基づいて設定される定数項(例えば図4、図6に示すテーブル参照)が入力される。

(b)プリチャージ・フェーズにおいては、すべてのセレクタ入力は[0]、すなわち、セレクト信号、反転セレクト信号、および定数項入力がなされる最下層のセレクタ入力も[0]に設定される。

【0124】

すなわち、反転出力つきセレクタおよび反転入力つきセレクタに対するセレクト信号[in]の遷移は、すべてのセレクタ入力が[0]とされるプリチャージ・フェーズ(Pre−Charge Phase)と、真の出力値(非線形変換結果)を得るための定数項、セレクト信号、反転セレクト信号が入力されるエバリュエーション・フェーズ(Evaluation Phase)とが交互に繰り返される。

【0125】

この構成においても、プリチャージ・フェーズでは、すべてのセレクタの入力が[0]にリセットされ、次のエバリュエーション・フェーズにおいて、リセット状態から新たなセレクト信号の入力が開始されるという処理を繰り返し実行される。セレクタに対するセレクト信号の遷移は、セレクタ入出力が[0]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、セレクタ出力は[0]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがない。すなわち、セレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0126】

[6.本発明に従った非線形変換部の構成例4(乱数の入力構成)]

次に、本発明の実施例4として、乱数入力を利用した構成例について説明する。図16を参照して本発明の実施例4の構成および処理について説明する。

【0127】

本発明の第4の実施形態は、先に図11を参照して説明した実施例1の二分決定グラフ(BDD)を用いた論理回路構成において、第8層の入力値を生成するアンドゲート回路に対する一方の入力値を実施例1とは異なる設定としている。

【0128】

実施例1では、先に説明したように、256個のアンドゲート回路の一方の入力は、図5を参照して説明した第8層のセレクタの入力値と同様の定数項であり、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類のいずれかの定数項である。例えば、図11に示す例は、図6に示すビット値、すなわち図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最下位ビットを定数項として設定した例である。

【0129】

すなわち、実施例1では、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットのビット値[0]または[1]に従った256個の定数項からなるビット値がアンドゲート回路に対する入力値としてそのまま適用されていた。本実施例4では、この256個のアンドゲート回路の入力を定数項、およびその反転値、乱数、これらを適宜、組み合わせて入力する設定とする。

【0130】

具体的には、例えば、

(a1)実施例1と同様の非線形変換テーブル(S−Boxテーブル)の出力値対応のビット値からなる定数項、

(a2)上記定数項の反転値、

(a3)乱数

これら(a1)〜(a3)のデータを入力値として適用する。(a1)〜(a3)のすべてを利用する構成やいずれか2つを組み合わせて利用する構成などが可能である。

【0131】

なお、この場合には、どのタイミングで(a1)〜(a3)のいずれのデータが入力されたかを示す管理情報を保持し、管理情報に従って、正しい出力値を取得することになる。なお、(a2)の定数項の反転値を入力した場合の最終出力は正式な出力ビットの反転値(正式出力が1の場合0、0の場合1)となるため、出力を反転させて正式な出力ビットとして適用することが可能である。

【0132】

具体的には、例えば、図16に示す回路を非線形変換結果の8ビット中の最下位ビットを得るための回路とする場合、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最下位ビットのビット値、すなわち、先に図6を参照して説明したビット値[1,0,1,1,0・・・,0,0,1,0]を入力するか、あるいはその反転入力としての反転ビット値[0,1,0,0,1・・・,1,1,0,1]を入力する設定とする。この反転値入力に基づいて得た出力を反転処理することで、正式な非線形変換出力ビットを得ることができる。

【0133】

この実施例においては、定数項入力のみならず、乱数の入力を行なうので、セレクタ出力におけるビットの0および1の生起確率が平均化され、DPA解析をさらに困難とすることが可能となる。

【0134】

なお、本構成においては、

(a)エバリュエーション・フェーズにおいて。

(a1)実施例1と同様の非線形変換テーブル(S−Boxテーブル)の出力値対応のビット値からなる定数項、

(a2)上記定数項の反転値、

(a3)乱数、

これら(a1)〜(a3)のデータを入力値として適用する。なお(a1)〜(a3)のすべてを利用する構成やいずれか2つを組み合わせて利用する構成などが可能である。適用する乱数は、論理関数8組のそれぞれにおいて同一のものを適用してもよいし異なるものを適用してもよい。さらに、

(b)プリチャージ・フェーズにおいては、すべてのセレクタ入力は[0]、すなわち、セレクト信号、反転セレクト信号、および定数項入力がなされる最下層のセレクタ入力も[0]に設定される。

【0135】

すなわち、本実施例では、セレクタに対するセレクト信号[in]の遷移は、すべてのセレクタ入力が[0]とされるプリチャージ・フェーズ(Pre−Charge Phase)と、

セレクト信号、反転セレクト信号は、真の設定値が入力され、最下層のセレクタ入力として、

(a1)実施例1と同様の非線形変換テーブル(S−Boxテーブル)の出力値対応のビット値からなる定数項、

(a2)上記定数項の反転値、

(a3)乱数、

これらのいずれかの信号が入力されるエバリュエーション・フェーズ(Evaluation Phase)とが交互に繰り返される。ただし、この構成の場合には、どのタイミングで(a1)〜(a3)のいずれのデータが入力されたかを示す管理情報を保持し、管理情報に従って、正しい出力値を取得する。

【0136】

この構成においても、プリチャージ・フェーズでは、すべてのセレクタの入力が[0]にリセットされ、次のエバリュエーション・フェーズにおいて、リセット状態から新たなセレクト信号の入力が開始されるという処理を繰り返し実行される。セレクタに対するセレクト信号の遷移は、セレクタ入出力が[0]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、セレクタ出力は[0]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがない。すなわち、セレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0137】

[7.本発明に従った非線形変換部の構成例5(ORゲート利用構成)]

上述した各実施例においては、各層のセレクト信号の遷移処理を実行するタイミングにおいて、プリチャージ信号[prch]=[0]として、セレクタ入力をオール[0]に維持するリセット処理(初期化処理)を実行する構成として説明したが、このリセット処理(初期化処理)タイミングにおいて、各層のセレクタ入力をオール[0]とするのではなくオール[1]とする構成としても、過渡遷移によるDPA攻撃を困難化することが可能である。

【0138】

本実施例の二分決定グラフ(BDD)を用いた論理回路構成を図17に示す。本実施例の論理回路は、図17に示すように、

定数項を入力する最下層のセレクタの前段、

セレクタに対するセレクト信号入力部、

セレクタに対する反転セレクト信号入力部、

これらの各構成部にORゲートを設けた構成としている。

各オアゲートの1つの入力をプリチャージ信号の入力部として設定したものである。

【0139】

プリチャージ信号は前述の実施例とは異なり[1]として入力される。この場合、プリチャージ・フェーズでは、全てのセレクタ入力値が[1]に設定され、エバリュエーション・フェーズにおいては、真の定数項、セレクト信号および反転セレクト信号がセレクタに入力される。すなわち本実施例では、上述の各実施例と異なり、リセット状態ではすべてのセレクタ入力が[1]に設定される。

【0140】

この構成においても、セレクタに対するセレクト信号[in]の遷移は、出力が[1]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、出力は[1]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがなく秘密情報の漏洩防止が可能となる。

【0141】

さらに、各層のセレクト信号の遷移処理を実行するタイミングでの出力を[0]と[1]を不規則に変更する構成としてもよい。この構成は、第8層に入力する出力信号を生成するゲート回路の出力を、

オール1、または、

オール0、または、

定数項あるいは乱数、

これらの3種類の出力を選択して出力可能なゲート回路を構成し、プリチャージ・フェーズ(Pre−Charge Phase)において、オール1またはオール0の出力をランダムに選択するスイッチを設けてスイッチをランダムに切り替えて第8層のセレクタにオール0またはオール1を入力する構成とする。

【0142】

この構成においても、セレクタに対するセレクト信号[in]の遷移は、出力を[0]または[1]のいずれかの選択された値とするプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、出力はランダムに選択された[0]または[1]に維持される。従って、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがなく秘密情報の漏洩が防止される。

【0143】

なお、上述した各実施例は、単独で適用することも可能であるが、複数組み合わせた構成としてもよい、

【0144】

なお、上述した実施例では、共通鍵暗号処理における非線形変換処理例を中心として説明したが、本発明は、AESやDESなどの共通鍵暗号処理のみならずRSAなどの公開鍵暗号処理やSHA−1などのハッシュ関数の演算など、非線形変換処理や線形変換処理などのデータ変換処理を実行する各種の演算において適用可能である。

【0145】

[8.暗号処理装置の構成例]

最後に、暗号文の生成、あるいは暗号文の復号処理等の暗号処理を実行する暗号処理装置としてのICモジュール500の構成例について図18を参照して説明する。上述の処理は、例えばPC、ICカード、リーダライタ、その他、様々な情報処理装置において実行可能であり、図18に示すICモジュール500は、これら様々な機器に構成することが可能である。

【0146】

図18に示すCPU(Central processing Unit)501は、暗号処理の開始や、終了、データの送受信の制御、各構成部間のデータ転送制御、その他の各種プログラムを実行する制御部として機能するプロセッサである。メモリ502は、CPU501が実行するプログラム、あるいは演算パラメータとしての固定データを格納するROM(Read-Only-Memory)、CPU501の処理において実行されるプログラム、およびプログラム処理において適宜変化するパラメータの格納エリア、ワーク領域として使用されるRAM(Random Access Memory)等からなる。また、メモリ502は暗号処理に必要な鍵データ等の格納領域として使用可能である。例えば暗号処理に適用する秘密鍵:Kが格納される。データ格納領域は、耐タンパ構造を持つメモリとして構成されることが好ましい。

【0147】

暗号処理部503は、上述した各実施例において説明した階層構成のセレクタ構成からなる二分決定グラフ(BDD)を用いた論理回路構成を有し、上述したプリチャージ・フェーズ(Pre−Charge Phase)と、エバリュエーション・フェーズ(Evaluation Phase)を設定可能とした非線形変換処理回路を有する構成である。

【0148】

各フェーズの切り替え制御や、ゲート回路の出力制御、セレクタに対するセレクト信号の遷移、出力の選択処理など、上述した実施例において説明した論理回路から正当な出力を得るために必要となる制御は、例えば制御部としてのCPU501において予め設定されたプログラムに従って実行される。例えば暗号処理の実行プログラムをROMに格納し、CPU501がROM格納プログラムを読み出して、暗号処理部503に構成された二分決定グラフ(BDD)を用いた論理回路構成を用いた処理を実行する。

【0149】

乱数発生器504は、暗号処理に適用する鍵、乱数情報の生成処理において適用される。あるいはデバイス間の認証処理において必要となる乱数生成、その他、暗号処理に必要となる乱数生成処理に適用される。乱数発生器504は、例えばLFSR(線形フィードバックシフトレジスタ)を適用した乱数生成器、あるいは擬似乱数生成器などによって構成される。

【0150】

送受信部505は、外部とのデータ通信を実行するデータ通信処理部であり、例えばリーダライタ等、ICモジュールとのデータ通信を実行し、ICモジュール内で生成した暗号文の出力、あるいは外部のリーダライタ等の機器からのデータ入力などを実行する。

【0151】

本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。従って、セレクタ信号および反転セレクタ信号の信号変化がオア回路から出力されることを防止できると共に、第1下層セレクタ出力信号及び第2下層セレクタ信号出力信号の信号変化も防止することができる。そのため、電力差分攻撃への耐性を高めることができる。

【0152】

さらに、本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。本構成によって、第1アンド回路に入力されるセレクタ信号及び第2アンド回路に入力される反転セレクタ信号の伝播が制限されるので、第1下層セレクタ出力信号又は第2下層セレクタ出力信号の伝播を制限することなく、第1下層セレクタ出力信号及び第2下層セレクタ出力信号の信号変換がオア回路から出力されることを制限できる。

【0153】

すなわち、第1下層セレクタ出力信号及び第2下層セレクタ出力信号に対して直接制限素子を付与する必要がなくなるため、回路規模の削減が可能になる。このように、本願発明の一実施例構成によれば、第1下層セレクタ出力信号及び第2下層セレクタ出力信号から信号変化が検出されることを少ない信号伝播素子で実現することができるため、電力差分攻撃への耐性向上と回路規模の削減を同時に達成することができる。

【0154】

以上、特定の実施例を参照しながら、本発明について詳解してきた。しかしながら、本発明の要旨を逸脱しない範囲で当業者が該実施例の修正や代用を成し得ることは自明である。すなわち、例示という形態で本発明を開示してきたのであり、限定的に解釈されるべきではない。本発明の要旨を判断するためには、冒頭に記載した特許請求の範囲の欄を参酌すべきである。

【0155】

なお、明細書中において説明した一連の処理はハードウェア、またはソフトウェア、あるいは両者の複合構成によって実行することが可能である。ソフトウェアによる処理を実行する場合は、処理シーケンスを記録したプログラムを、専用のハードウェアに組み込まれたコンピュータ内のメモリにインストールして実行させるか、あるいは、各種処理が実行可能な汎用コンピュータにプログラムをインストールして実行させることが可能である。

【0156】

なお、明細書に記載された各種の処理は、記載に従って時系列に実行されるのみならず、処理を実行する装置の処理能力あるいは必要に応じて並列的にあるいは個別に実行されてもよい。また、本明細書においてシステムとは、複数の装置の論理的集合構成であり、各構成の装置が同一筐体内にあるものには限らない。

【産業上の利用可能性】

【0157】

上述した本発明の構成によれば、非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう構成とした。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

【符号の説明】

【0158】

101 鍵スケジュール部

110 データ変換部

115 ラウンド演算部

200 秘密鍵

201 鍵スケジュール部

210 ラウンド演算部

211 排他的論理和演算部

212 S−Box

213 Mix−Colum

214 排他的論理和演算部

215 S−Box

250 AES暗号演算実行部

251 排他的論理和演算部

252 セレクタ

253 レジスタ

254 S−Box

255 Mix−Colum

256 セレクタ

270 セレクタ

271,272 アンドゲート

273 オアゲート

300 セレクタ

301,302 アンドゲート

303 オアゲート

500 ICモジュール

501 CPU(Central processing Unit)

502 メモリ

503 暗号処理部

504 乱数発生器

505 送受信部

【技術分野】

【0001】

本発明は、データ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムに関する。さらに詳細には、本発明は、AES(Advanced Encryption Standard)に代表されるような共通鍵暗号方式や、RSA(Rivest−Shamir−Adleman)暗号に代表されるような公開鍵暗号方式、またはSHA−1に代表されるようなハッシュ関数などの演算を効率的に実行する論理回路を利用したデータ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムに関する。

【背景技術】

【0002】

昨今、ネットワーク通信、電子商取引の発展に伴い、通信におけるセキュリティ確保が重要な問題となっている。セキュリティ確保の1つの方法が暗号技術であり、現在、様々な暗号化手法を用いた通信が実現され、運用されている。

【0003】

暗号化方式には大きく分けて共通鍵暗号方式と公開鍵暗号方式が存在する。共通鍵暗号方式には、DES(Data Encryption Standard)やAES(Advanced Encryption Standard)がある。AES暗号方式はDES暗号方式の後継暗号方式として位置づけられている。また、公開鍵暗号方式には、RSA(Rivest−Shamir−Adleman)暗号方式やECC(Elliptic Curve Cryptosystems)暗号方式が存在する。

【0004】

このような様々な暗号方式に従った暗号処理を実行する装置、すなわち暗号処理デバイスとしては、例えば、C言語のようなプログラミング言語を用いてCPUを利用してプログラムの処理によって実行させる構成、あるいは様々なゲート回路を使用してハードウェア上で実行させる構成などがある。

【0005】

暗号処理デバイスにおいては、例えば、平文を入力し暗号文を出力するデータ暗号化処理、あるいは暗号文を入力し平文を出力する復号化処理が実行される。これらの暗号処理は、セキュアに行なわれ、情報の漏洩を防ぐ工夫がなされているが、一方で、暗号処理の適用鍵や、アルゴリズムを解析する攻撃手法も存在する。攻撃方法は大別して破壊攻撃と非破壊攻撃に分類することができる。

【0006】

このうち破壊攻撃は、ICチップなどのパッケージを硝酸などの薬品を用いて化学的処理により溶解しICチップのダイをあらわにした後、物理的な方法で秘密情報を読み取る攻撃である。ダイがあらわになると、配線パターンから構成された回路を導出するリバースエンジニアリングが可能であり、配線から直接秘密情報を抽出することが可能となる。また配線だけでなくメモリセルからもレーザーや電磁波を用いてメモリ状態を検知することによって、メモリ内に書き込まれている秘密情報を観測することができる。

【0007】

また非破壊攻撃はサイドチャネル攻撃(Side−Channel Attack)とも呼ばれる。基本的にICチップのパッケージを溶解するという処理を行なわず、外部から得られる物理的情報、たとえば消費電流、輻射電磁波、演算終了時間等の情報を利用して、秘密情報を盗み出すものである。実際に共通鍵暗号方式であるDESが実装されたデバイスの暗号処理中の消費電流を観測して、秘密情報である鍵情報を漏洩させる方法がKocherらによって1999年に発表された。この手法については、例えば非特許文献1に記載されている。この攻撃技術の存在は、暗号の実装方法が適切でない場合、安全性が確保できないことを意味するものである。

【0008】

非特許文献1に記載されているDPA(Differential Power Analysis)攻撃は、入力平文の異なる数多くの暗号演算処理中の消費電流を観測して、秘密情報のビット値をもとに消費電流波形を統計処理することにより、秘密情報との相関の有無によって統計処理した消費電流波形に表れる特徴的なパターンから秘密情報を導き出すという攻撃手法である。

【0009】

このような攻撃に対して、様々な防御方法も提案されている。例えば、共通鍵暗号方式であるAESについて例を挙げれば、非特許文献2に1つの防御手法が記載されている。この非特許文献2に記載の手法は、AESの演算のうちSubByteと呼ばれている内部のS−Box演算に対して対策を施したものである。この対策は演算途中の秘密情報を含んだ中間値があらわに存在しないように乱数を用いて秘匿する技術である。

【0010】

しかしながら、この方法を単純にハードウェアに実装しても内部信号の遅延差による過渡遷移が生じるために、乱数を用いて秘密情報を含んだ中間値の秘匿が完全にできない状況が生じるためにDPA攻撃によって秘密情報が漏洩してしまうことがあるという問題がある。

【0011】

さらに、非特許文献3には、上述の非特許文献2の構成における欠点である過渡遷移を解消した構成として、WDDL(Wave Differential Dynamic Logic)を用いた対策が開示されている。この対策はロジックの状態として、Pre−Charge Phase、およびEvaluation Phaseという2つの状態を持ち、この2つの状態を行き来することによって演算を行なう処理を漏洩防止策としたものである。

【0012】

Pre−Charge Phaseはゲート回路が初期化されている状態であり、Evaluation Phaseは実際の演算を行なっている状態ということができる。さらにゲート回路の入出力に対して相補的な入力および出力が存在する。この相補的入力に対して正論理ゲートと負論理ゲートが形成され、相補的な出力が得られる。WDDLはこの2つの機構、Pre−Charge PhaseとEvaluation Phaseの2状態および相補的な入出力の存在によって、いかなる入力信号に対しても出力はPre−Charge PhaseからEvaluationo PhaseおよびEvaluation PhaseからPre−Charge Phaseに状態が遷移するときに一度だけ出力が変化するMonotonicityを満たしている。

【0013】

WDDLにはこのような性質があるため、不要な過渡遷移が生じることがない。さらに相補的な出力は任意の入力に対してどちらかの出力のみ変化するので、状態が遷移したときにのみ充放電が行なわれるCMOS(Complemetary Metal Oxide Semiconductor)プロセスを用いたロジックでは消費電流が一定となる。よって秘密情報を含むビット値の違いによって消費電流の相違がなくなるので、DPA攻撃に対して有効な対策となる。

【0014】

しかしながらWDDLは相補的入出力が存在し、その入出力の遅延差をなくすようにレイアウトを行なわなければならない。さらに演算構成上で2つの演算入力に対して大幅な遅延差がある場合には、DPA攻撃によって秘密情報が漏洩してしまう危険が存在するという問題点を有する。

【0015】

上述のAESにおけるSubByteと呼ばれている内部のS−Box演算は、例えば二分決定グラフ(BDD: Binary Decision Diagram)を用いたハードウェアによって実行可能である。二分決定グラフ(BDD)については、例えば、特許文献1に記載されている。なお、二分決定グラフ(BDD)については本明細書中においても後段で説明する。

【0016】

特許文献1には二分決定グラフ(BDD)で構成されたS−Boxなどの組合せ回路の構成およびその論理合成方法に関することが記載されている。共通鍵暗号による暗号処理を実行する場合、S−Boxと呼ばれる非線形変換部を利用した非線形変換処理を実行することが必要であり、このS−Boxの処理速度が暗号処理演算自体の処理速度に大きく影響している。例えば、AESのS−Boxはガロア体の逆元演算回路が必要である。

【0017】

この回路を二分決定グラフ(BDD)で構成せず、例えば、合成体(composite field)で実現しようとすると、BDDのような真理値表から直接回路を導出する構成に比べて数倍程度の回路遅延が生じてしまうことになる。従って、高速な実装が要求される場合はBDD構成とすることが好ましい。しかしながら、BDDを用いたS−Boxは高速動作が実現されるが、DPA攻撃に関する考慮を行わないと、不要な過渡遷移等の信号伝搬に基づく解析が可能となり秘密鍵等の秘密情報の漏洩の危険が発生するという問題がある。すなわち、二分決定グラフ(BDD)を適用した論理回路構成による演算を実行した場合、内部信号の遅延差による過渡遷移が生じ、DPA攻撃によって秘密情報が漏洩してしまうことがあるという問題がある。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】特開2003−223100

【非特許文献】

【0019】

【非特許文献1】Paul C.Kocher,Joshaua Jaffe and Benjamin Jun,"Differential Power Analysis",CRYPTO 1999,Lecture Note in Computer Science,Vol.1666,Springer−Verlag(1999),pp.388−397.

【非特許文献2】Elisabeth Oswald, Stefan Mangard, Norbert Pramstaller,"A Side−Channel Analysis Resistant Description of the AES S−Box",FSE 2005,LNCS 3557,pp.413−423.

【非特許文献3】Kris Tiri, Ingrid Verbauwhede,"Securing Encryption Algorithms against DPA at the Logic Level: Next Generation Smart Card Technology",CHES 2003,LNCS 2779,pp.125−136.

【発明の開示】

【発明が解決しようとする課題】

【0020】

本発明は、上記問題点に鑑みてなされたものであり、不要な過渡遷移を生じさせることなく、また遅延差も少なくした論理回路による演算処理構成を実現するものであり、例えば、DPA攻撃による秘密情報漏洩の可能性を低減させて、攻撃に対する耐性を高めたデータ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムを提供することを目的とする。

【課題を解決するための手段】

【0021】

本発明の第1の側面は、

入力データを第1下層セレクタ及び第2下層セレクタからの出力信号に応じて変換するデータ変換装置であって、

前記データ変換装置は、

前記入力データがセレクタ信号として入力されるセレクタ信号入力部、

前記入力データが反転され、反転セレクタ信号として入力される反転セレクタ信号入力部、

前記第1下層セレクタから出力される第1下層セレクタ出力信号が入力される第1下層セレクタ出力信号入力部、

前記第2下層セレクタから出力される第2下層セレクタ出力信号が入力される第2下層セレクタ出力信号入力部を有する上層セレクタを備え、

前記上層セレクタは、

前記セレクタ信号と、前記第1下層セレクタ出力信号とのアンド演算を行う第1アンド回路、

前記反転セレクタ信号と、前記第2下層セレクタ出力信号とのアンド演算を行う第2アンド回路、

前記第2アンド回路からの出力信号と、前記第1アンド回路からの出力信号とのオア演算を行うオア回路、

前記セレクタ信号の伝播を制限することにより、前記第1アンド回路から、前記セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、

前記反転セレクタ信号の伝播を制限することにより、前記第2アンド回路から、前記セレクタ信号及び前記第2下層セレクタ出力信号の出力が制限される第2出力制限素子、

を有するデータ変換装置にある。

【0022】

さらに、本発明の第2の側面は、

入力ビットのデータ変換処理を実行する演算処理装置であり、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、

定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路と、

前記論理回路を適用したデータ変換処理の制御を行う制御部とを備え、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を有し、

前記論理回路を構成する最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記制御部は、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させる制御を行うことを特徴とする演算処理装置にある。

【0023】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路は、さらに前記定数項を入力する複数の最下層セレクタの前段にプリチャージ信号入力部を備えた定数項入力部対応演算回路を有し、前記制御部は、前記定数項入力部対応演算回路に対するプリチャージ信号の切り替え制御により、前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする。

【0024】

さらに、本発明の演算処理装置の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたアンドゲートによって構成され、前記制御部は、前記アンドゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする。

【0025】

さらに、本発明の演算処理装置の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたオアゲートによって構成され、前記制御部は、前記オアゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする。

【0026】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路を構成するセレクタは、同一値を入力値とする複数のセレクタを1つのセレクタとした共有セレクタを有する構成であることを特徴とする。

【0027】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路を構成するセレクタは、反転出力を行なうセレクタおよび反転入力を行なうセレクタであることを特徴とする。

【0028】

さらに、本発明の演算処理装置の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力を固定値とし、前記エバリュエーション・フェーズにおいて、前記定数項または乱数を前記最下層セレクタの入力として設定する構成であることを特徴とする。

【0029】

さらに、本発明の演算処理装置の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力をランダムに0または1とするように前記ゲート回路の出力制御を行う構成であることを特徴とする。

【0030】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路は、二分決定グラフ(BDD: Binary Decision Diagram)を用いた構成を有することを特徴とする。

【0031】

さらに、本発明の演算処理装置の一実施態様において、前記論理回路は、入力ビットのデータ変換処理として、入力ビットの非線形変換処理を実行する構成であることを特徴とする。

【0032】

さらに、本発明の第3の側面は、

演算処理装置において入力ビットのデータ変換処理を実行する演算処理制御方法であり、

前記演算処理装置は、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路を有し、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を備え、

最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記論理回路を適用したデータ変換処理の制御を行なう制御部が、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させる制御を行うことを特徴とする演算処理制御方法にある。

【0033】

さらに、本発明の演算処理制御方法の一実施態様において、前記論理回路は、さらに前記定数項を入力する複数の最下層セレクタの前段にプリチャージ信号入力部を備えた定数項入力部対応演算回路を有し、前記制御部は、前記定数項入力部対応演算回路に対するプリチャージ信号の切り替えにより、前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行うことを特徴とする。

【0034】

さらに、本発明の演算処理制御方法の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたアンドゲートによって構成され、前記制御部は、前記アンドゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行うことを特徴とする。

【0035】

さらに、本発明の演算処理制御方法の一実施態様において、前記演算回路は、一方の入力をプリチャージ信号としたオアゲートによって構成され、前記制御部は、前記オアゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行うことを特徴とする。

【0036】

さらに、本発明の演算処理制御方法の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力を固定値とし、前記エバリュエーション・フェーズにおいて、前記定数項または乱数を前記最下層セレクタの入力として設定することを特徴とする。

【0037】

さらに、本発明の演算処理制御方法の一実施態様において、前記制御部は、前記プリチャージ・フェーズにおいて、前記最下層セレクタの入力をランダムに0または1とする制御を行うことを特徴とする。

【0038】

さらに、本発明の第4の側面は、

演算処理装置において入力ビットのデータ変換処理を実行させるコンピュータ・プログラムであり、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路を有し、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を備え、

最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記コンピュータ・プログラムは、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させることを特徴とするコンピュータ・プログラムにある。

【0039】

なお、本発明のコンピュータ・プログラムは、例えば、様々なプログラム・コードを実行可能なコンピュータ・システムに対して、コンピュータ可読な形式で提供する記憶媒体、通信媒体、例えば、CDやFD、MOなどの記録媒体、あるいは、ネットワークなどの通信媒体によって提供可能なコンピュータ・プログラムである。このようなプログラムをコンピュータ可読な形式で提供することにより、コンピュータ・システム上でプログラムに応じた処理が実現される。

【0040】

本発明のさらに他の目的、特徴や利点は、後述する本発明の実施例や添付する図面に基づくより詳細な説明によって明らかになるであろう。なお、本明細書においてシステムとは、複数の装置の論理的集合構成であり、各構成の装置が同一筐体内にあるものには限らない。

【発明の効果】

【0041】

本発明の構成によれば、非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう構成とした。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

【0042】

さらに、本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。従って、セレクタ信号および反転セレクタ信号の信号変化がオア回路から出力されることを防止できると共に、第1下層セレクタ出力信号及び第2下層セレクタ信号出力信号の信号変化も防止することができる。そのため、電力差分攻撃への耐性を高めることができる。

【0043】

さらに、本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。本構成によって、第1アンド回路に入力されるセレクタ信号及び第2アンド回路に入力される反転セレクタ信号の伝播が制限されるので、第1下層セレクタ出力信号又は第2下層セレクタ出力信号の伝播を制限することなく、第1下層セレクタ出力信号及び第2下層セレクタ出力信号の信号変換がオア回路から出力されることを制限できる。

【0044】

すなわち、第1下層セレクタ出力信号及び第2下層セレクタ出力信号に対して直接制限素子を付与する必要がなくなるため、回路規模の削減が可能になる。このように、本願発明の一実施例構成によれば、第1下層セレクタ出力信号及び第2下層セレクタ出力信号から信号変化が検出されることを少ない信号伝播素子で実現することができるため、電力差分攻撃への耐性向上と回路規模の削減を同時に達成することができる。

【図面の簡単な説明】

【0045】

【図1】AESやDESなどの共通鍵暗号方式の暗号処理を実行する基本構成を示す図である。

【図2】AES暗号処理構成例を示す図である。

【図3】AES暗号処理を実行するハードウェア構成例を示す図である。

【図4】非線形変換処理に適用する変換テーブル(S−Boxテーブル)を示す図である。

【図5】非線形変換テーブル(S−Boxテーブル)に基づく変換結果中の出力の下位1ビットを出力する論理回路としての二分決定グラフ(BDD)を示す図である。

【図6】図4に示すテーブルに示される256個の出力値の最下位ビットに対応するビット値のみを示す変換テーブルを示す図である。

【図7】図5に示す非線形変換論理回路に適用されるセレクタの構成例を示す図である。

【図8】過渡遷移について説明する図である。

【図9】プリチャージ・フェーズ(Pre−Charge Phase)とエバリュエーション・フェーズ(Evaluation Phase)を設定可能とした論理回路構成を示す図である。

【図10】図9に示す非線形変換論理回路に適用されるセレクタの構成例を示す図である。

【図11】本発明の第1の実施形態としての非線形変換処理を実行する論理回路構成を示す図である。

【図12】本発明の第1の実施形態としての論理回路における信号遷移を説明する図である。

【図13】本発明の第1の実施形態としての非線形変換処理を実行する論理回路の制御構成例を示す図である。

【図14】セレクタの共有化構成について説明する図である。

【図15】反転出力セレクタおよび反転入力セレクタを利用した本発明の実施例構成について説明する図である。

【図16】乱数入力構成を持つ本発明の実施例構成について説明する図である。

【図17】オアゲートを持つ本発明の実施例構成について説明する図である。

【図18】本発明の構成が適用可能な暗号処理実行デバイスとしてのICモジュールの構成例を示す図である。

【発明を実施するための形態】

【0046】

以下、本発明のデータ変換装置、演算処理装置、および演算処理制御方法、並びにコンピュータ・プログラムの詳細について説明する。

【0047】

以下、本発明の実施の形態として、共通鍵暗号方式であるAES(Advanced Encryption Standard)における本発明の適用例を説明する。共通鍵暗号方式であるAESは、例えば、入力128ビットの平文を128ビットの暗号文に変換する処理を行なう。従来の共通鍵暗号方式であるDES(Data Encryption Standard)と同様、データ変換処理単位としてのラウンド演算を繰り返し実行する構成を持つ。なお、本発明は、AESやDESなどの共通鍵暗号処理のみならずRSAなどの公開鍵暗号処理やSHA−1などのハッシュ関数の演算など、非線形変換処理や線形変換処理などのデータ変換処理を実行する各種の演算において適用可能である。

【0048】

以下、下記の項目に従って、本発明について順次説明する。

1.共通鍵暗号方式の暗号処理を実行する基本構成について

2.BDDを用いた非線形変換部(S−Box)の一般的構成について

3.本発明に従った非線形変換部の構成例1

4.本発明に従った非線形変換部の構成例2(セレクタの共有構成例)

5.本発明に従った非線形変換部の構成例3(反転出力セレクタおよび反転入力セレクタ利用構成)

6.本発明に従った非線形変換部の構成例4(乱数の入力構成)

7.本発明に従った非線形変換部の構成例5(ORゲート利用構成)

8.暗号処理装置の構成例

【0049】

[1.共通鍵暗号方式の暗号処理を実行する基本構成について]

図1にAESやDESなどの共通鍵暗号方式の暗号処理を実行する基本構成を示す。図1に示すように、共通鍵暗号の基本的な暗号処理構成は、鍵スケジュール部101と、データ変換部110からなる。鍵スケジュール部101は、秘密鍵100を入力して、秘密鍵100に基づいて各ラウンドにおいて適用するラウンド鍵を生成して各ラウンド演算部151−1〜151-nに出力する。

【0050】

データ変換部110は、変換対象のデータを入力し、複数のラウンド演算部151−1〜151−nにおいて、鍵スケジュール部101から入力するラウンド鍵を適用し、データ変換を行って変換データを出力する。

【0051】

ラウンド演算部151−1〜151−nでは同様のラウンド演算を繰り返し実行する。1つのラウンドでは、入力ビットの変換処理として、変換テーブルを利用した入力ビットの非線形変換や、線形変換、入力鍵(ラウンド鍵)を適用したデータ変換処理などが実行される。その結果に基づいて次のラウンド演算部の入力が生成される。

【0052】

例えば、AES暗号では、ラウンド演算部151−1〜151−nにおいて実行される非線形変換処理はSubByteと呼ばれる。このSubByteと呼ばれる非線形変換処理は、予め用意された非線形変換テーブル(S−Boxテーブル)を利用した変換処理として実行される。

【0053】

図2にAES暗号処理の詳細構成を示す。鍵スケジュール部201は、秘密鍵200を入力して、秘密鍵200に基づいて各ラウンドにおいて適用するラウンド鍵を生成して各ラウンド演算部210に出力する。AES暗号におけるラウンド演算部210は、図に示すように、ラウンド鍵との排他的論理和演算を実行する排他的論理和演算部211、SubByteと呼ばれる非線形変換処理を実行するS−Box212、各S−Box212の出力の入れ替え処理を実行するMix−Colum213、さらにMix−Colum213とラウンド鍵との排他的論理和演算を実行する排他的論理和演算部214、排他的論理和演算部214の出力に対して非線形変換処理を実行するS−Box215によって構成される。なお、これらの各処理は、図に示すように8ビットデータに分割されたデータを単位として実行される。

【0054】

なお、ラウンド演算は繰り返し実行されるが、AES暗号演算実行部をハードウェアとして構成する場合は、繰り返し実行されるラウンド演算部を1つ構成し、繰り返し利用する構成とする。例えば、図3にAES暗号を実行するハードウェア構成例を示す。

【0055】

AES暗号演算実行部250は、最初のラウンド鍵0を入力して、排他的論理和演算部251において、暗号処理対象データ(128ビット)と排他的論理和演算処理を実行し、セレクタ252を介してレジスタ253に入力し、レジスタ253から8ビットデータ単位で、S−Box254において非線形変換処理が実行され、Mix−Colum255においてビット値入れ替えがなされ、セレクタ256を介して排他的論理和演算部257においてラウンド鍵との排他的論理和演算が実行され、この結果データが再びセレクタ252を介してレジスタ253に入力されて、S−Box254に入力される。この処理が繰り返し実行され、予め規定されたラウンド数の処理が終了すると、結果データとしての暗号文がレジスタ253から出力される。

【0056】

ラウンド演算部の非線形変換部であるS−Boxの各々では、8ビットデータをそれぞれ入力して、非線形変換テーブル(S−Boxテーブル)を適用して非線形変換処理を実行して出力8ビットを生成する。すなわち、16個のS−Boxの各々において8ビット毎の非線形変換データを順次生成して、16×8=128ビット分の非線形変換データを生成し出力する。図4に非線形変換処理に適用する変換テーブル(S−Boxテーブル)を示す。

【0057】

図4に示す変換テーブルにおいて、最上段の横ラインに示す(0,1,2,・・・d,e,f)は変換処理対象となる入力8ビットの下位4ビットを16進表現で示している。0〜fは、2進表現では0000〜1111に相当する。左端の縦ラインに示す(0,1,2,・・・d,e,f)は変換処理対象となる入力8ビットの上位4ビットを16進表現で示している。これらの上位、下位ビットの計8ビット(00000000〜11111111)に対する出力としての8ビットがテーブル内部に記録されている。

【0058】

すなわち、入力ビットは8ビット00〜FF(00000000〜11111111)であり、28=256種類のビット状態がある。これを上位4ビットと下位4ビットに分割して、図4に示すテーブルを適用して256種類の出力8ビット00〜FF(00000000〜11111111)を決定する。

【0059】

例えば、入力が16進表現で00(2進表現で00000000)である場合、図4に示すテーブルに基づいて出力が63(16進表現)となる。すなわち、左上端のテーブル値[63]が出力値として選定される。また、入力がC0(16進数)である場合、図4に示すテーブルに基づいて出力がBA(16進表現)となる。このように、ラウンド演算部における非線形変換処理は、図4に示された変換テーブルを適用した8ビット入力、8ビット出力の1対1写像を実行する。

【0060】

[2.BDDを用いた非線形変換部(S−Box)の一般的構成について]

このような非線形変換テーブル(S−Boxテーブル)による変換処理を実行するハードウェアの回路構成例として、二分決定グラフ(BDD: Binary Decision Diagram)を用いた構成がある。図5に非線形変換テーブル(S−Boxテーブル)に基づく変換結果中の出力の下位1ビットを出力する論理回路としての二分決定グラフ(BDD)を示す。

【0061】

図5には、論理関数としての2入力1出力のセレクタを、第1層から第8層の階層構成として論理回路としての二分決定グラフ(BDD)を示している。ピラミッド型の8層構造にセレクタが接続された構成を持つ。最終1ビットを出力するセレクタは、第1層のセレクタである。

【0062】

第1層にはセレクタが1個、第2層にはセレクタが2個、第3層にはセレクタが4個、第4層にはセレクタが8個、第5層にはセレクタが16個、第6層にはセレクタが32個、第7層にはセレクタが64個、第8層にはセレクタが128個あり、全部で255個のセレクタで構成されている。

【0063】

第1層のセレクタ入力は第2層のセレクタ出力が供給され、

第2層のセレクタ入力は第3層のセレクタ出力が供給され、

第3層のセレクタ入力は第4層のセレクタ出力が供給され、

第4層のセレクタ入力は第5層のセレクタ出力が供給され、

第5層のセレクタ入力は第6層のセレクタ出力が供給され、

第6層のセレクタ入力は第7層のセレクタ出力が供給され、

第7層のセレクタ入力は第8層のセレクタ出力が供給され、

第8層のセレクタ入力は0もしくは1の定数項が供給される。

【0064】

第8層のセレクタ入力は、図4に示す非線形変換テーブル(S−Boxテーブル)に基づいて決定される0もしくは1の定数項であり、256ビットデータである。

図5に示す論理回路は、非線形変換結果としての出力8ビットの最下位ビットを出力する選択回路である。この場合、図5の最下段に示される第8層のセレクタ入力値としての256ビット[10110111・・・11110010]は、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値として設定される。

【0065】

例えば、図5の最下段に示される第8層のセレクタ入力値の左端のビット値[1]は図4に示すテーブルの最上段の左端に示す出力値である(63)の最下位ビットに相当し、図5の最下段に示される第8層のセレクタ入力値の右端のビット値[0]は図4に示すテーブルの最下段の右端に示す出力値である(16)の最下位ビットに相当する。

【0066】

図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値のみを示す変換テーブルを図6に示す。この図6に示す16×16=256個の出力値は、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値であり、このビット値が、図5に示す回路構成の第8層のセレクタ入力値として設定される。

【0067】

各層のセレクタに入力するセレクト信号は、非線形変換対象データとして入力される128ビットを8ビット毎に分割した8−bitの各1ビットが利用される。入力8−bit中の最上位ビット(in[7])が、第1層のセレクタに対するセレクト信号として入力され、第2番目のビット(in[6])が、第2層のセレクタに対するセレクト信号として入力され、以下、各層に各ビットが入力され、最下位ビット(in[0])は、第8層のセレクタに対するセレクト信号として入力される。

【0068】

入力8ビットは、非線形変換対象データとしての128ビットの分割データであり、128ビットを構成する8ビット毎に、順次、入力値が変更(遷移)され、次々に8ビット単位で非線形変換処理が行なわれることになる。

【0069】

各セレクタに入力されるセレクト信号が[0]の場合にはセレクタ入力の左側の入力が選択されて上位層に出力され、セレクト信号が[1]の場合にはセレクタ入力の右側が選択されて上位層に出力される。従って、セレクト信号8ビットが決まると、第8層のセレクタ入力256個のうちのひとつが出力される。第8層のセレクタ入力の定数は第1層から第8層のセレクト入力の順列で一意に決定される。

【0070】

例えば、非線形変換対象データとしての入力8ビットが[00000000]である場合、セレクト信号は、すべて[0]であり、すべてのセレクタにおいて、左側の入力が選択されて上位層に出力されることになり、結果として、図5の最下段に示される第8層のセレクタ入力値の左端のビット値[1]が最終的な出力(第1層のセレクタ出力)とされる。この出力は、図4に示すテーブルの最上段の左端に示す出力値である(63)の最下位ビットに相当する。このように、非線形変換対象データとしての入力ビットの値(00000000〜11111111)の値に応じて、第8層のセレクタ入力256個のうちのひとつが出力される。これらの第8層のセレクタ入力256個のそれぞれは、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値である。

【0071】

この図5に示す階層構成のセレクタからなる構成を8つ適用することで、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の8ビット全てに対応するビット値を決定する。

【0072】

図5に示す構成においては、最下段の第8層のセレクタ入力値としての256ビット[10110111・・・11110010]は、図6を参照して説明したビット値、すなわち、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)の最下位ビットに対応するビット値として設定されている。

【0073】

最下段の第8層のセレクタ入力値を、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類を設定してその出力を組み合わせることで、入力8ビットを図4に示すテーブルによって非線形変換した結果としての出力8ビットを得ることができる。

【0074】

このようにして、図4に示す非線形変換テーブル(S−Boxテーブル)と同等の値を出力する構成が実現される。すなわち、図4に示す非線形変換テーブル(S−Boxテーブル)と同等の値を出力される論理関数は図5のような二分決定グラフ(BDD)によって構成することができる。

【0075】

図5に示す論理回路には、先に説明したように、第1層にはセレクタが1個、第2層にはセレクタが2個、第3層にはセレクタが4個、第4層にはセレクタが8個、第5層にはセレクタが16個、第6層にはセレクタが32個、第7層にはセレクタが64個、第8層にはセレクタが128個あり、全部で255個のセレクタで構成されている。これらのセレクタの構成例を図7に示す。

【0076】

セレクタ270の構成はたとえば図7に示すように、S−boxテーブルから求められる定数項aとセレクト信号の反転値を入力するアンドゲート271、S−boxテーブルから求められる定数項bとセレクト信号の信号値を入力するアンドゲート272、さらに、アンドゲート271,272の出力を入力するORゲート273によって構成される。

【0077】

例えば、セレクタに入力されるセレクト信号が[0]の場合にはセレクタ入力の定数項[a]が選択されて出力され、セレクト信号が[1]の場合にはセレクタ入力の定数項[b]が選択されて出力される。

【0078】

この図7に示す構成を持つセレクタが図5のような二分決定グラフ(BDD)の各層に設定されて下位から上位層に順次、出力を決定していくことになる。しかしながら、このようなセレクタ構成を採用すると、それぞれの層のセレクト信号の入力タイミングが乱れによる過渡遷移が発生する。

【0079】

過渡遷移について、図8を参照して説明する。図8(1)は、図5に示す従来型の二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路構成において、各層に入力される(p)セレクト信号[in]と、(q)最終セレクタ出力[out]の遷移を示すタイミングチャートであり、

【0080】

図8(2)は、図8(1)に示すデータ領域281の拡大図である。(p)セレクト信号[in]は、例えば図5の論理回路における第1層から第8層までの8つのセレクタ層に対する8つの入力ビットの遷移タイミングが図8(2)(p)セレクト信号[in[0]〜[7]]に示す信号線の交差領域で発生する。この入力8ビットの遷移は、完全な同一タイミングで発生させることは困難であり、各入力ビットの遷移タイミングにはずれが発生することになる。

【0081】

従って、入力8ビットの遷移が開始されてから完全に全ビットの遷移が終了するまでには、一定の期間を要することになる。これが、図8(2)に示すΔtの遷移期間に相当する。このような、遷移期間において、図8(2)(q)に示す出力[out]は、8層のセレクタ層に対する入力8ビットの遷移に応じて、出力値を変化させることになる。図8(2)(q)に示す点線部では、セレクト信号の遷移タイミングのずれに応じた出力値変化が発生する。

【0082】

この出力値の変化の解析により、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路構成で利用されている信号値が解析される可能性がある。すなわち、先に背景技術の欄で説明したように、この過渡遷移に起因して、DPA攻撃によって秘密情報が漏洩してしまうことがある。

【0083】

なお、背景技術の欄で説明したように、この過渡遷移を防止する従来構成としてWDDL(Wave Differential Dynamic Logic)を用いた対策が開示されているが、WDDLは相補的入出力が存在し、その入出力の遅延差をなくすようにレイアウトを行なわなければならないというレイアウト構築の困難性という問題がある。さらに演算構成上で2つの演算入力に対して大幅な遅延差がある場合には、DPA攻撃を確実に防止できないという問題がある。

【0084】

[3.本発明に従った非線形変換部の構成例1]

本発明は、不要な過渡遷移を生じさせることなく、また遅延差も少なくした論理回路による演算処理構成を実現するものである。以下、本発明に従った非線形変換部(S−Box)の実施例について説明する。

【0085】

本発明の暗号処理装置は、共通鍵ブロック暗号に従った暗号処理を実行する暗号処理装置であり、入力ビットの非線形変換処理を実行して出力ビットを生成する論理回路と、この論理回路に対する入力ビットの切り替え処理としての入力ビット遷移処理を、論理回路の出力を固定値に維持したプリチャージ・フェーズにおいて実行させ、入力ビット遷移処理が終了した後、エバリュエーション・フェーズへ移行させて遷移後の入力ビットの非線形変換処理に基づく出力ビットの生成処理を行なわせる制御部とを有する。

【0086】

非線形変換処理を実行する本発明に係るピラミッド型のセレクタ階層構成を持つ二分決定グラフ(BDD)の基本構成を図9に示す。図9に示すように本実施例におけるS−Boxを構成する論理回路は、図5を参照して説明したピラミッド型のセレクタ階層構成を持つ二分決定グラフ(BDD)と同様8層のピラミッド型セレクタ構成を有する。最下層の第8層のセレクタ入力は、図5を参照して説明した第8層のセレクタの入力値と同様の定数項であり、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類のいずれかである。

【0087】

図9に示す論理回路に、第1層にはセレクタが1個、第2層にはセレクタが2個、第3層にはセレクタが4個、第4層にはセレクタが8個、第5層にはセレクタが16個、第6層にはセレクタが32個、第7層にはセレクタが64個、第8層にはセレクタが128個あり、全部で255個のセレクタで構成されている。これらのセレクタには、図9に示すようにセレクト信号と反転セレクト信号の2つの信号が入力される。セレクタの構成例を図10に示す。

【0088】

図10に示すようにセレクタ300は、S−boxテーブルから求められる定数項aとセレクト信号の反転値を入力するアンドゲート301、S−boxテーブルから求められる定数項bとセレクト信号の信号値を入力するアンドゲート302、さらに、アンドゲート301,302の出力を入力するORゲート303によって構成される。

【0089】

このセレクタ300の構成は、先に図7を参照して説明したセレクタ270の構成と異なり、セレクト信号の入力と、反転セレクト信号とが独立に入力される構成となっている。すなわち、アンドゲート301,302の入力の4系統の信号は、それぞれ独立した信号となっている。先に図7を参照して説明したセレクタ270では、アンドゲート271に入力される反転セレクト信号と、アンドゲート272に入力されるセレクト信号は、1つの入力セレクト信号に基づいて生成された信号である点が、10に示す構成と異なる点である。

【0090】

なお、出力信号Cは、セレクタに入力されるセレクト信号が[0]の場合にはセレクタ入力の定数項[a]が選択されて出力され、セレクト信号が[1]の場合にはセレクタ入力の定数項[b]が選択されて出力される点は、先に図10を参照して説明したと同様である。

【0091】

本発明の第1実施例に係る非線形変換処理を実行するS−Boxとしての二分決定グラフ(BDD)の具体的な論理回路構成例を図11に示す。図11に示す回路に設定されるセレクタは、図10を参照して説明したセレクト信号と、反転セレクト信号を独立に入力可能とした構成をもつ。

【0092】

図11に示すように、本発明の第1実施例に係る非線形変換処理を実行する論理回路は、

第8層のセレクタ入力部の前段に演算回路(アンドゲート)、

各セレクタに対するセレクト信号入力部の前段に演算回路(アンドゲート)、

各セレクタに対する反転セレクト信号入力部の前段に演算回路(アンドゲート)、

これらの演算回路(アンドゲート)を設けている。

【0093】

第8層のセレクタの入力は256個であり、256個のアンドゲート回路によって第8層のセレクタの入力値を生成する。256個のアンドゲート回路の一方の入力は、図5を参照して説明した第8層のセレクタの入力値と同様の定数項であり、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類のいずれかである。

【0094】

各層のセレクタに入力するセレクト信号は、非線形変換対象データとして入力される128ビットを8ビット毎に分割した8−bitの各1ビットが利用される。入力8−bit中の最上位ビット(in[7])が、第1層のセレクタに対するセレクト信号として演算回路(アンドゲート)を介して入力され、第2番目のビット(in[6])が、第2層のセレクタに対するセレクト信号として演算回路(アンドゲート)を介して入力され、以下、各層に各ビットが演算回路(アンドゲート)を介して入力され、最下位ビット(in[0])は、第8層のセレクタに対するセレクト信号として演算回路(アンドゲート)を介して入力される。

【0095】

なお、入力8ビットは、前述したように非線形変換対象データとしての128ビットの分割データであり、128ビットを構成する8ビット毎に、順次、入力値が変更(遷移)され、次々に8ビット単位で非線形変換処理が行なわれることになる。

【0096】

各セレクタには、セレクト信号の他に反転セレクト信号も、演算回路(アンドゲート)を介して入力される。

【0097】

このように、本実施例に係る論理回路は、

定数項の入力部である第8層のセレクタ入力部の前段に演算回路(アンドゲート)、

各セレクタに対するセレクト信号入力部の前段に演算回路(アンドゲート)、

各セレクタに対する反転セレクト信号入力部の前段に演算回路(アンドゲート)、

これらの演算回路(アンドゲート)を設けており、

第8層のセレクタの入力値をアンドゲート回路の出力値、

各セレクタに対するセレクト信号入力値をアンドゲート回路の出力値、

各セレクタに対する反転セレクト信号入力値をアンドゲート回路の出力値、

としている。これらの演算回路の処理によってプリチャージ・フェーズ(Pre−Charge Phase)とエバリュエーション・フェーズ(Evaluation Phase)状態を設定可能としている。なお、これらのフェーズの移行制御や入力情報の設定、遷移制御は図示しない制御部によって実行される。

【0098】

図11に示す例は、図5と同様、図6に示すビット値、すなわち図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最下位ビットを定数項として設定した例を示している。従って、図11に示す構成は、図5の構成と同様、非線形変換処理による出力8ビットの最下位ビットを出力する回路構成である。

【0099】

図11に示す第8層のセレクタに接続された256個のアンドゲート回路と、各層の8つのセレクト信号および8つの反転セレクト信号の入力部に接続されたそれぞれ8つのアンドゲート回路のもう一方の入力は、プリチャージ信号入力[prch]である。プリチャージ信号入力[prch]が[0]の場合には第8層のセレクタ入力の256個の入力、各層のセレクタに対するセレクト信号入力、各層のセレクタに対する反転セレクト信号入力、これらのすべてが0となる。この状態が、プリチャージ・フェーズ(Pre−Charge Phase)状態である。すなわち、プリチャージ・フェーズ(Pre−Charge Phase)では、すべてのセレクタ入力値が0となる。

【0100】

プリチャージ信号入力[prch]が[1]の場合には、定数項が第8層のセレクタ入力として設定され、さらに、真のセレクト信号と反転セレクト信号、すなわち、非線形変換対象データとして入力される128ビットを8ビット毎に分割した8−bitのデータの値がセレクト信号として各セレクタに入力され、その反転値が反転セレクト信号とし各セレクタにアンドゲートを介して入力される。この入力状態が、エバリュエーション・フェーズ(Evaluation Phase)状態である。

【0101】

本実施例においては、

8階層のセレクタを適用した出力ビットの算出処理を実行するエバリュエーション・フェーズ(Evaluation Phase)と、

セレクタ入力のすべてを0とするプリチャージ・フェーズ(Pre−Charge Phase)と、

これらの2つのフェーズを交互に繰り返す。

【0102】

各セレクタにおける入力値の遷移について、図12を参照して説明する。図12(a)には、先に図10を参照して説明したセレクタ300の構成を示している。図12(b)は、セレクタに対する入力信号の遷移を示している。図12(a)に示すセレクタ300は、S−boxテーブルから求められる定数項aとセレクト信号の反転値を入力するアンドゲート301、S−boxテーブルから求められる定数項bとセレクト信号の信号値を入力するアンドゲート302、さらに、アンドゲート301,302の出力を入力するORゲート303によって構成される。

【0103】

図12(b)は、セレクタに対する入力信号の時間的遷移を示している。左から右に時間が推移し、フェーズが交互に切り替わり、セレクタ入力値が入れ替えられる。上述したように、本発明に従った論理回路では、セレクタに対するすべての入力を[0]とするプリチャージ・フェーズと、正しい定数項とセレクト信号、および反転セレクト信号をセレクタに入力して出力ビットの算出処理を実行するエバリュエーション・フェーズとを交互に繰り返す。

【0104】

図12(b)は、セレクタに対する入力信号、すなわち、

定数項(a)の入力、

定数項(b)の入力、

セレクト信号の入力、

反転セレクト信号の入力、

これらの入力値の時間的遷移を示している。これらの入力は、すべて一方の入力をプリチャージ信号としたアンドゲートを介して入力されており、プリチャージ信号は、プリチャージ・フェーズでは[0]、エバリュエーション・フェーズでは[1]となる。

【0105】

最初のプリチャージ・フェーズでは、プリチャージ信号は[0]に設定されるので、すべてのセレクタ入力値は[0]となる。その後のエバリュエーション・フェーズでは、プリチャージ信号は[1]に設定され、定数項、セレクト信号、反転セレクト信号のそれぞれの正しい値がセレクタに入力される。このエバリュエーション・フェーズにおいて、1組の8ビットのセレクト信号に対応する出力値(非線形変換結果)が、最上段(第1層)のセレクタから出力される。

【0106】

さらに、このエバリュエーション・フェーズの後、プリチャージ・フェーズに移行し、すべてのセレクタ入力値は[0]に設定される。このプリチャージ・フェーズ期間において、セレクト信号と反転セレクト信号は次の入力値(8ビット)に入れ替えられる。プリチャージ・フェーズ期間が終了すると、エバリュエーション・フェーズに移行し、新たなセレクト信号と反転セレクト信号に基づいて新たな8ビットのセレクト信号に対応する出力値(非線形変換結果)が、最上段(第1層)のセレクタから出力される。

【0107】

このようにして、エバリュエーション・フェーズとプリチャージ・フェーズとを交互に繰り返し実行する。この構成によれば、各セレクタにおける新たなセレクト信号の入力タイミングは、常にセレクタ入力がオール0のプリチャージ・フェーズからエバリュエーション・フェーズへの切り替え時となる。このタイミングにおけるセレクタ入力値変化は、すべて[0]から真の入力値への変化として設定される。従って、先に図8を参照して説明した過渡遷移、すなわち8層の各セレクタ層に対する真のデータ値である8ビットの遷移に応じた出力値変化を電力変化として解析することは困難となる。

【0108】

すなわち、セレクタに対するセレクト信号の遷移は、セレクタ入出力が[0]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、セレクタ出力は[0]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがなく秘密情報の漏洩防止が可能となる。

【0109】

本実施例の構成では、1組の8ビットのセレクト信号に対応する出力値が決定された後、すべてのセレクタに対する入力をすべて[0]とする初期状態にリセットし、リセット状態から新たなセレクト信号の入力が実行される構成としている。本構成によりセレクト信号の切り替えに伴って発生するセレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0110】

図13を参照して、エバリュエーション・フェーズとプリチャージ・フェーズとを交互に繰り返し実行する場合の、非線形変換部としてのS−Box(BBD)に対する入力信号の切り替え処理構成例について説明する。

【0111】

図11を参照して説明したように、非線形変換部としての論理回路である二分決定グラフ(BDD)としてのS−Boxにはセレクト信号および反転セレクト信号が入力され、さらに、第8層から定数項が入力される。エバリュエーション・フェーズにおいては、これらはすべて真の入力値が入力されるが、プリチャージ・フェーズにおいては、これらの値はすべて[0]に切り替えられることになる。

【0112】

図13に示すS−Box(BBD)に対する入力信号の切り替え処理実行部の構成において、データレジスタ321には、非線形変換処理対象としてのデータが入力され、データレジスタ制御部324の制御により、8ビット単位のデータが順次出力される。この8ビットデータが、エバリュエーション・フェーズにおいて、セレクト信号および反転セレクト信号としてS−Box(BBD)323に入力される。反転セレクト信号は反転素子322においてセレクト信号に対する反転処理が実行されて生成される。

【0113】

プリチャージ制御部325は、エバリュエーション・フェーズにおいては、プリチャージ信号[1]を出力する。この処理によって、エバリュエーション・フェーズにおいて、セレクト信号および反転セレクト信号がS−Box(BBD)323のセレクタに入力される。なお、図では示していないが、プリチャージ信号[1]は、S−Box(BBD)323内の最下層のセレクタの前段の定数項入力部を持つアンドゲートの一方の入力としても利用されており、エバリュエーション・フェーズにおいては、定数項が最下層のセレクタに入力され、真の非線形変換結果がS−Box(BBD)323から出力される。

【0114】

プリチャージ・フェーズにおいては、プリチャージ制御部325からプリチャージ信号、すなわち全てのセレクト信号、反転セレクト信号、および第8層入力値のすべてを[0]とするためのプリチャージ信号[0]がS−Box(BBD)323に入力される。この場合は、S−Box(BBD)323を構成するすべてのセレクタ入力は0となり、S−Box(BBD)323出力も0とされる。

【0115】

データレジスタ制御部324およびプリチャージ制御部325には、クロック信号が入力され、エバリュエーション・フェーズにおいてはプリチャージ制御部から[1]が出力されて、データレジスタ制御部324からのセレクタ信号の出力が有効値としてS−Box(BBD)323において利用され、真の非線形変換結果が出力される。が実行され、プリチャージ・フェーズにおいてはプリチャージ制御部325からプリチャージ信号[0]が出力され、S−Box(BBD)323を構成するすべてのセレクタ入力は0となり、S−Box(BBD)323出力も0とされる。各信号の出力タイミングは各フェーズの切り替えにクロックに従って実行される。

【0116】

この構成を適用することで、エバリュエーション・フェーズにおいては、1組の8ビットのセレクト信号および反転セレクト信号がS−Box323に入力され、その後、プリチャージ・フェーズに切り替わり、プリチャージ制御部325からのプリチャージ信号[0]がS−Box323に入力され、すべてのセレクタの入力が[0]にリセットされる。さらに、次のエバリュエーション・フェーズにおいて、リセット状態から新たなセレクト信号の入力が開始されるという処理を繰り返し実行することが可能となる。この処理構成とすることで、セレクト信号の切り替えに伴って発生するセレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0117】

[4.本発明に従った非線形変換部の構成例2(セレクタの共有構成例)]

例えば図11に示す二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路構成は、出力8ビット中の1ビットを出力するために適用される論理回路であり、入力8ビットから非線形変換結果としての出力8ビットを、並列に得るためには、図11に示す二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路を8個、組み合わせて動作させることが必要である。

【0118】

このように各出力ビット対応の二分決定グラフ(BDD)を用いた論理回路構成とする場合、回路規模が大きくなるが、回路規模の縮小のためセレクタを共有する構成が可能である。

【0119】

図14を参照して、セレクタの共有化構成について説明する。例えば、図14(A)に示すように、同一の入力値を持つ複数のセレクタ351,352が存在する場合、これらの複数のセレクタを1つのセレクタとして構成する。すなわち、図14(B)に示すように、セレクタ351,352の代用として1つのセレクタ361を設ける。このセレクタ共有化処理により、二分決定グラフ(BDD)を用いた論理回路構成を小さくすることが可能であり、回路規模の縮小およびコストダウンが可能となる。また、回路規模の削減により消費電流も小さくすることができる。

【0120】

[5.本発明に従った非線形変換部の構成例3(反転出力セレクタおよび反転入力セレクタ利用構成)]

次に、本発明の実施例3として、反転出力セレクタおよび反転入力セレクタを利用した構成例について説明する。図15を参照して本発明の実施例3の構成および処理について説明する。

【0121】

本発明の第3の実施形態は、先に図11を参照して説明した実施例1の二分決定グラフ(BDD)を用いた論理回路構成において適用するセレクタを偶数階層の場合には反転出力セレクタと、奇数階層の場合には反転入力セレクタとした構成である。セレクタは8階層であり、偶数回の反転が行なわれることになる。従って、最終出力は8階層のセレクタとした場合も、合わせて8階層の反転出力セレクタおよび反転入力セレクタとした場合も同一となる。

【0122】

反転出力つきセレクタおよび反転入力つきセレクタは、図11を参照して説明した構成において使用するセレクタよりも占有面積が小さくできる。従って、よって回路規模を削減でき、消費電流も小さくできる。

【0123】

なお、本構成においても、

(a)エバリュエーション・フェーズにおいては、セレクタ入力は、真の出力値(非線形変換結果)を得るための入力値として、8ビット単位の非線形変換処理対象としてのデータであるセレクト信号および反転セレクト信号が各セレクタに入力され、第8層のセレクタには、非線形変換テーブル(S−Boxテーブル)に基づいて設定される定数項(例えば図4、図6に示すテーブル参照)が入力される。

(b)プリチャージ・フェーズにおいては、すべてのセレクタ入力は[0]、すなわち、セレクト信号、反転セレクト信号、および定数項入力がなされる最下層のセレクタ入力も[0]に設定される。

【0124】

すなわち、反転出力つきセレクタおよび反転入力つきセレクタに対するセレクト信号[in]の遷移は、すべてのセレクタ入力が[0]とされるプリチャージ・フェーズ(Pre−Charge Phase)と、真の出力値(非線形変換結果)を得るための定数項、セレクト信号、反転セレクト信号が入力されるエバリュエーション・フェーズ(Evaluation Phase)とが交互に繰り返される。

【0125】

この構成においても、プリチャージ・フェーズでは、すべてのセレクタの入力が[0]にリセットされ、次のエバリュエーション・フェーズにおいて、リセット状態から新たなセレクト信号の入力が開始されるという処理を繰り返し実行される。セレクタに対するセレクト信号の遷移は、セレクタ入出力が[0]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、セレクタ出力は[0]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがない。すなわち、セレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0126】

[6.本発明に従った非線形変換部の構成例4(乱数の入力構成)]

次に、本発明の実施例4として、乱数入力を利用した構成例について説明する。図16を参照して本発明の実施例4の構成および処理について説明する。

【0127】

本発明の第4の実施形態は、先に図11を参照して説明した実施例1の二分決定グラフ(BDD)を用いた論理回路構成において、第8層の入力値を生成するアンドゲート回路に対する一方の入力値を実施例1とは異なる設定としている。

【0128】

実施例1では、先に説明したように、256個のアンドゲート回路の一方の入力は、図5を参照して説明した第8層のセレクタの入力値と同様の定数項であり、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットの8種類のいずれかの定数項である。例えば、図11に示す例は、図6に示すビット値、すなわち図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最下位ビットを定数項として設定した例である。

【0129】

すなわち、実施例1では、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最上位ビット〜最下位ビットのビット値[0]または[1]に従った256個の定数項からなるビット値がアンドゲート回路に対する入力値としてそのまま適用されていた。本実施例4では、この256個のアンドゲート回路の入力を定数項、およびその反転値、乱数、これらを適宜、組み合わせて入力する設定とする。

【0130】

具体的には、例えば、

(a1)実施例1と同様の非線形変換テーブル(S−Boxテーブル)の出力値対応のビット値からなる定数項、

(a2)上記定数項の反転値、

(a3)乱数

これら(a1)〜(a3)のデータを入力値として適用する。(a1)〜(a3)のすべてを利用する構成やいずれか2つを組み合わせて利用する構成などが可能である。

【0131】

なお、この場合には、どのタイミングで(a1)〜(a3)のいずれのデータが入力されたかを示す管理情報を保持し、管理情報に従って、正しい出力値を取得することになる。なお、(a2)の定数項の反転値を入力した場合の最終出力は正式な出力ビットの反転値(正式出力が1の場合0、0の場合1)となるため、出力を反転させて正式な出力ビットとして適用することが可能である。

【0132】

具体的には、例えば、図16に示す回路を非線形変換結果の8ビット中の最下位ビットを得るための回路とする場合、図4に示すテーブルに示される256個の出力値(63,7C,77・・・54,BB,16)各々の最下位ビットのビット値、すなわち、先に図6を参照して説明したビット値[1,0,1,1,0・・・,0,0,1,0]を入力するか、あるいはその反転入力としての反転ビット値[0,1,0,0,1・・・,1,1,0,1]を入力する設定とする。この反転値入力に基づいて得た出力を反転処理することで、正式な非線形変換出力ビットを得ることができる。

【0133】

この実施例においては、定数項入力のみならず、乱数の入力を行なうので、セレクタ出力におけるビットの0および1の生起確率が平均化され、DPA解析をさらに困難とすることが可能となる。

【0134】

なお、本構成においては、

(a)エバリュエーション・フェーズにおいて。

(a1)実施例1と同様の非線形変換テーブル(S−Boxテーブル)の出力値対応のビット値からなる定数項、

(a2)上記定数項の反転値、

(a3)乱数、

これら(a1)〜(a3)のデータを入力値として適用する。なお(a1)〜(a3)のすべてを利用する構成やいずれか2つを組み合わせて利用する構成などが可能である。適用する乱数は、論理関数8組のそれぞれにおいて同一のものを適用してもよいし異なるものを適用してもよい。さらに、

(b)プリチャージ・フェーズにおいては、すべてのセレクタ入力は[0]、すなわち、セレクト信号、反転セレクト信号、および定数項入力がなされる最下層のセレクタ入力も[0]に設定される。

【0135】

すなわち、本実施例では、セレクタに対するセレクト信号[in]の遷移は、すべてのセレクタ入力が[0]とされるプリチャージ・フェーズ(Pre−Charge Phase)と、

セレクト信号、反転セレクト信号は、真の設定値が入力され、最下層のセレクタ入力として、

(a1)実施例1と同様の非線形変換テーブル(S−Boxテーブル)の出力値対応のビット値からなる定数項、

(a2)上記定数項の反転値、

(a3)乱数、

これらのいずれかの信号が入力されるエバリュエーション・フェーズ(Evaluation Phase)とが交互に繰り返される。ただし、この構成の場合には、どのタイミングで(a1)〜(a3)のいずれのデータが入力されたかを示す管理情報を保持し、管理情報に従って、正しい出力値を取得する。

【0136】

この構成においても、プリチャージ・フェーズでは、すべてのセレクタの入力が[0]にリセットされ、次のエバリュエーション・フェーズにおいて、リセット状態から新たなセレクト信号の入力が開始されるという処理を繰り返し実行される。セレクタに対するセレクト信号の遷移は、セレクタ入出力が[0]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、セレクタ出力は[0]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがない。すなわち、セレクト信号の遷移に依存した出力値変化を発生させることがなく、二分決定グラフ(BDD: Binary Decision Diagram)を用いた論理回路で利用されている信号値が解析される可能性を低減させることが可能となり、DPA攻撃に対する耐性を高めることが可能となる。

【0137】

[7.本発明に従った非線形変換部の構成例5(ORゲート利用構成)]

上述した各実施例においては、各層のセレクト信号の遷移処理を実行するタイミングにおいて、プリチャージ信号[prch]=[0]として、セレクタ入力をオール[0]に維持するリセット処理(初期化処理)を実行する構成として説明したが、このリセット処理(初期化処理)タイミングにおいて、各層のセレクタ入力をオール[0]とするのではなくオール[1]とする構成としても、過渡遷移によるDPA攻撃を困難化することが可能である。

【0138】

本実施例の二分決定グラフ(BDD)を用いた論理回路構成を図17に示す。本実施例の論理回路は、図17に示すように、

定数項を入力する最下層のセレクタの前段、

セレクタに対するセレクト信号入力部、

セレクタに対する反転セレクト信号入力部、

これらの各構成部にORゲートを設けた構成としている。

各オアゲートの1つの入力をプリチャージ信号の入力部として設定したものである。

【0139】

プリチャージ信号は前述の実施例とは異なり[1]として入力される。この場合、プリチャージ・フェーズでは、全てのセレクタ入力値が[1]に設定され、エバリュエーション・フェーズにおいては、真の定数項、セレクト信号および反転セレクト信号がセレクタに入力される。すなわち本実施例では、上述の各実施例と異なり、リセット状態ではすべてのセレクタ入力が[1]に設定される。

【0140】

この構成においても、セレクタに対するセレクト信号[in]の遷移は、出力が[1]に維持されるプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、出力は[1]のままに維持され、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがなく秘密情報の漏洩防止が可能となる。

【0141】

さらに、各層のセレクト信号の遷移処理を実行するタイミングでの出力を[0]と[1]を不規則に変更する構成としてもよい。この構成は、第8層に入力する出力信号を生成するゲート回路の出力を、

オール1、または、

オール0、または、

定数項あるいは乱数、

これらの3種類の出力を選択して出力可能なゲート回路を構成し、プリチャージ・フェーズ(Pre−Charge Phase)において、オール1またはオール0の出力をランダムに選択するスイッチを設けてスイッチをランダムに切り替えて第8層のセレクタにオール0またはオール1を入力する構成とする。

【0142】

この構成においても、セレクタに対するセレクト信号[in]の遷移は、出力を[0]または[1]のいずれかの選択された値とするプリチャージ・フェーズ(Pre−Charge Phase)への移行後、プリチャージ・フェーズ(Pre−Charge Phase)が定常状態になった時点に実行される。従って、各層のセレクト信号の遷移タイミングがずれても、出力はランダムに選択された[0]または[1]に維持される。従って、出力値[out]が変化せず、過渡遷移に基づく出力値の遷移状態を検出されることがなく秘密情報の漏洩が防止される。

【0143】

なお、上述した各実施例は、単独で適用することも可能であるが、複数組み合わせた構成としてもよい、

【0144】

なお、上述した実施例では、共通鍵暗号処理における非線形変換処理例を中心として説明したが、本発明は、AESやDESなどの共通鍵暗号処理のみならずRSAなどの公開鍵暗号処理やSHA−1などのハッシュ関数の演算など、非線形変換処理や線形変換処理などのデータ変換処理を実行する各種の演算において適用可能である。

【0145】

[8.暗号処理装置の構成例]

最後に、暗号文の生成、あるいは暗号文の復号処理等の暗号処理を実行する暗号処理装置としてのICモジュール500の構成例について図18を参照して説明する。上述の処理は、例えばPC、ICカード、リーダライタ、その他、様々な情報処理装置において実行可能であり、図18に示すICモジュール500は、これら様々な機器に構成することが可能である。

【0146】

図18に示すCPU(Central processing Unit)501は、暗号処理の開始や、終了、データの送受信の制御、各構成部間のデータ転送制御、その他の各種プログラムを実行する制御部として機能するプロセッサである。メモリ502は、CPU501が実行するプログラム、あるいは演算パラメータとしての固定データを格納するROM(Read-Only-Memory)、CPU501の処理において実行されるプログラム、およびプログラム処理において適宜変化するパラメータの格納エリア、ワーク領域として使用されるRAM(Random Access Memory)等からなる。また、メモリ502は暗号処理に必要な鍵データ等の格納領域として使用可能である。例えば暗号処理に適用する秘密鍵:Kが格納される。データ格納領域は、耐タンパ構造を持つメモリとして構成されることが好ましい。

【0147】

暗号処理部503は、上述した各実施例において説明した階層構成のセレクタ構成からなる二分決定グラフ(BDD)を用いた論理回路構成を有し、上述したプリチャージ・フェーズ(Pre−Charge Phase)と、エバリュエーション・フェーズ(Evaluation Phase)を設定可能とした非線形変換処理回路を有する構成である。

【0148】

各フェーズの切り替え制御や、ゲート回路の出力制御、セレクタに対するセレクト信号の遷移、出力の選択処理など、上述した実施例において説明した論理回路から正当な出力を得るために必要となる制御は、例えば制御部としてのCPU501において予め設定されたプログラムに従って実行される。例えば暗号処理の実行プログラムをROMに格納し、CPU501がROM格納プログラムを読み出して、暗号処理部503に構成された二分決定グラフ(BDD)を用いた論理回路構成を用いた処理を実行する。

【0149】

乱数発生器504は、暗号処理に適用する鍵、乱数情報の生成処理において適用される。あるいはデバイス間の認証処理において必要となる乱数生成、その他、暗号処理に必要となる乱数生成処理に適用される。乱数発生器504は、例えばLFSR(線形フィードバックシフトレジスタ)を適用した乱数生成器、あるいは擬似乱数生成器などによって構成される。

【0150】

送受信部505は、外部とのデータ通信を実行するデータ通信処理部であり、例えばリーダライタ等、ICモジュールとのデータ通信を実行し、ICモジュール内で生成した暗号文の出力、あるいは外部のリーダライタ等の機器からのデータ入力などを実行する。

【0151】

本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。従って、セレクタ信号および反転セレクタ信号の信号変化がオア回路から出力されることを防止できると共に、第1下層セレクタ出力信号及び第2下層セレクタ信号出力信号の信号変化も防止することができる。そのため、電力差分攻撃への耐性を高めることができる。

【0152】

さらに、本願発明の一実施例構成においては、「セレクタ信号の伝播を制限することにより、第1アンド回路から、セレクタ信号及び第1下層セレクタ出力信号の出力が制限される第1出力制限素子、反転セレクタ信号の伝播を制限することにより、第2アンド回路から、セレクタ信号及び第2下層セレクタ出力信号の出力が制限される第2出力制限素子」を備えている。本構成によって、第1アンド回路に入力されるセレクタ信号及び第2アンド回路に入力される反転セレクタ信号の伝播が制限されるので、第1下層セレクタ出力信号又は第2下層セレクタ出力信号の伝播を制限することなく、第1下層セレクタ出力信号及び第2下層セレクタ出力信号の信号変換がオア回路から出力されることを制限できる。

【0153】

すなわち、第1下層セレクタ出力信号及び第2下層セレクタ出力信号に対して直接制限素子を付与する必要がなくなるため、回路規模の削減が可能になる。このように、本願発明の一実施例構成によれば、第1下層セレクタ出力信号及び第2下層セレクタ出力信号から信号変化が検出されることを少ない信号伝播素子で実現することができるため、電力差分攻撃への耐性向上と回路規模の削減を同時に達成することができる。

【0154】

以上、特定の実施例を参照しながら、本発明について詳解してきた。しかしながら、本発明の要旨を逸脱しない範囲で当業者が該実施例の修正や代用を成し得ることは自明である。すなわち、例示という形態で本発明を開示してきたのであり、限定的に解釈されるべきではない。本発明の要旨を判断するためには、冒頭に記載した特許請求の範囲の欄を参酌すべきである。

【0155】

なお、明細書中において説明した一連の処理はハードウェア、またはソフトウェア、あるいは両者の複合構成によって実行することが可能である。ソフトウェアによる処理を実行する場合は、処理シーケンスを記録したプログラムを、専用のハードウェアに組み込まれたコンピュータ内のメモリにインストールして実行させるか、あるいは、各種処理が実行可能な汎用コンピュータにプログラムをインストールして実行させることが可能である。

【0156】

なお、明細書に記載された各種の処理は、記載に従って時系列に実行されるのみならず、処理を実行する装置の処理能力あるいは必要に応じて並列的にあるいは個別に実行されてもよい。また、本明細書においてシステムとは、複数の装置の論理的集合構成であり、各構成の装置が同一筐体内にあるものには限らない。

【産業上の利用可能性】

【0157】

上述した本発明の構成によれば、非線形変換処理などのデータ変換処理を行う演算装置において、論理回路を構成するセレクタ入力値をすべて同一値に維持したプリチャージ・フェーズにおいて入力ビット遷移処理を実行させ、遷移処理終了後にエバリュエーション・フェーズへ移行してデータ変換処理に基づく出力ビット生成を行なう構成とした。プリチャージ・フェーズにおいては全てのセレクタ入力値を同一値とするリセットを実行するので、入力ビット遷移処理時の過渡遷移に基づく解析が困難となり、例えばDPA(Differential Power Analysis)攻撃に対する耐性の高い演算装置が実現される。

【符号の説明】

【0158】

101 鍵スケジュール部

110 データ変換部

115 ラウンド演算部

200 秘密鍵

201 鍵スケジュール部

210 ラウンド演算部

211 排他的論理和演算部

212 S−Box

213 Mix−Colum

214 排他的論理和演算部

215 S−Box

250 AES暗号演算実行部

251 排他的論理和演算部

252 セレクタ

253 レジスタ

254 S−Box

255 Mix−Colum

256 セレクタ

270 セレクタ

271,272 アンドゲート

273 オアゲート

300 セレクタ

301,302 アンドゲート

303 オアゲート

500 ICモジュール

501 CPU(Central processing Unit)

502 メモリ

503 暗号処理部

504 乱数発生器

505 送受信部

【特許請求の範囲】

【請求項1】

入力データを第1下層セレクタ及び第2下層セレクタからの出力信号に応じて変換するデータ変換装置であって、

前記データ変換装置は、

前記入力データがセレクタ信号として入力されるセレクタ信号入力部、

前記入力データが反転され、反転セレクタ信号として入力される反転セレクタ信号入力部、

前記第1下層セレクタから出力される第1下層セレクタ出力信号が入力される第1下層セレクタ出力信号入力部、

前記第2下層セレクタから出力される第2下層セレクタ出力信号が入力される第2下層セレクタ出力信号入力部を有する上層セレクタを備え、

前記上層セレクタは、

前記セレクタ信号と、前記第1下層セレクタ出力信号とのアンド演算を行う第1アンド回路、

前記反転セレクタ信号と、前記第2下層セレクタ出力信号とのアンド演算を行う第2アンド回路、

前記第2アンド回路からの出力信号と、前記第1アンド回路からの出力信号とのオア演算を行うオア回路、

前記セレクタ信号の伝播を制限することにより、前記第1アンド回路から、前記セレクタ信号及び前記第1下層セレクタ出力信号の出力が制限される第1出力制限素子、

前記反転セレクタ信号の伝播を制限することにより、前記第2アンド回路から、前記セレクタ信号及び前記第2下層セレクタ出力信号の出力が制限される第2出力制限素子、

を有するデータ変換装置。

【請求項2】

入力ビットのデータ変換処理を実行する演算処理装置であり、

入力ビットをセレクト信号として設定した複数のセレクタによる階層構成を有し、

定数項を複数の最下層セレクタから入力して、前記セレクト信号に従って下層セレクタから上層セレクタへ前記定数項を転送して最上層セレクタから選択された定数項を出力する論理回路と、

前記論理回路を適用したデータ変換処理の制御を行う制御部とを備え、

前記論理回路は、

前記セレクト信号を入力し、第2演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力したセレクト信号値を出力するエバリュエーション処理を実行する第1演算回路と、

前記セレクト信号の反転値である反転セレクト信号を入力し、前記第1演算回路の出力値と同一値を出力するプリチャージ処理、又は、入力した反転セレクト信号値を出力するエバリュエーション処理を実行する第2演算回路を有し、

前記論理回路を構成する最下層以外のセレクタは、

前記下層セレクタの一つである第1下層セレクタの出力及び前記第1演算回路の出力が入力される第1アンドゲートと、

前記第1下層セレクタとは異なる第2下層セレクタの出力及び前記第2演算回路の出力が入力される第2アンドゲートと、

前記第1アンドゲートの出力及び前記第2アンドゲートの出力が入力されるオアゲートによって構成され、

前記制御部は、

前記第1下層セレクタ及び第2下層セレクタの出力に対するプリチャージ処理を行うことなく、前記プリチャージ処理及び前記エバリュエーション処理を交互に実行させる制御を行うことを特徴とする演算処理装置。

【請求項3】

前記論理回路は、さらに前記定数項を入力する複数の最下層セレクタの前段にプリチャージ信号入力部を備えた定数項入力部対応演算回路を有し、

前記制御部は、

前記定数項入力部対応演算回路に対するプリチャージ信号の切り替え制御により、前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする請求項2に記載の演算処理装置。

【請求項4】

前記演算回路は、一方の入力をプリチャージ信号としたアンドゲートによって構成され、

前記制御部は、

前記アンドゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする請求項2に記載の演算処理装置。

【請求項5】

前記演算回路は、一方の入力をプリチャージ信号としたオアゲートによって構成され、

前記制御部は、

前記オアゲートの一方の入力であるプリチャージ信号の切り替えを実行して前記プリチャージ・フェーズと、前記エバリュエーション・フェーズとの切り替え制御を行う構成であることを特徴とする請求項2に記載の演算処理装置。

【請求項6】

前記論理回路を構成するセレクタは、同一値を入力値とする複数のセレクタを1つのセレクタとした共有セレクタを有する構成であることを特徴とする請求項2に記載の演算処理装置。

【請求項7】

前記論理回路を構成するセレクタは、反転出力を行なうセレクタおよび反転入力を行なうセレクタであることを特徴とする請求項2に記載の演算処理装置。

【請求項8】