データ書込装置および基地局

【課題】 現用系に書き込まれたデータを精度良く高速に予備系にも書き込むことが可能なデータ書込装置およびこれを適用した基地局を提供する。

【解決手段】 基地局は、冗長構成をなし、アドレスに比べ2倍以上の速度でデータを転送しCPUからメモリにデータを書き込む呼処理制御部を含む。呼処理制御部は、現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出し、検出されたアドレスに基づき現用系メモリに書き込まれたデータを現用系CPUを介して読み出し、検出されたアドレスと同じ予備系メモリのアドレスに、読み出されたデータを書き込むように予備系CPUに指示する。

【解決手段】 基地局は、冗長構成をなし、アドレスに比べ2倍以上の速度でデータを転送しCPUからメモリにデータを書き込む呼処理制御部を含む。呼処理制御部は、現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出し、検出されたアドレスに基づき現用系メモリに書き込まれたデータを現用系CPUを介して読み出し、検出されたアドレスと同じ予備系メモリのアドレスに、読み出されたデータを書き込むように予備系CPUに指示する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込むデータ書込装置、およびこのような呼処理制御部を含み、移動体通信端末との間で無線通信を行う基地局に関する。

【背景技術】

【0002】

従来の技術として、現用系CPUから現用系メモリに転送されるデータを分岐させて検出し、これを予備系CPUを介して予備系メモリに書き込ませる技術があった。

【0003】

【特許文献1】特開平11-168559号公報

【特許文献2】特開平07-240754号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、近年は高速な書き込みが可能なメモリが登場してきており、従来の技術のように、現用系CPUから現用系メモリに転送されるデータを分岐させて検出しようとすると、現用系CPUおよび現用系メモリの間で反射が影響し信号波形が崩れてしまい、現用系で書き込んだデータを予備系に精度良く書き込むことが難しくなっていた。

【0005】

本発明の目的は、現用系に書き込まれたデータを精度良く高速に予備系にも書き込むことが可能なデータ書込装置およびこれを適用した基地局を提供することである。

【課題を解決するための手段】

【0006】

本発明は、冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込むデータ書込装置であって、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とするデータ書込装置である。

【0007】

また本発明は、冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込む呼処理制御部を含み、移動体通信端末との間で無線通信を行う基地局であって、前記呼処理制御部は、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とする基地局である。

【発明の効果】

【0008】

本発明によれば、現用系に書き込まれたデータを精度良く高速に予備系にも書き込むことができる。

【発明を実施するための最良の形態】

【0009】

図1は、本発明の実施の形態に係る基地局の構成および動作イメージを示す図である。基地局は、移動体通信に適用される基地局であって、移動体通信端末との間で無線通信を行い上位装置との間で有線通信を行う。

【0010】

スイッチ(HWY-MUX)11は、バッファメモリを具備しないスイッチであり、高速バスライン(HWYバス)で接続された各構成要素間を自由にスイッチングして相互にデータを転送させる。制御部(CNT)12は、移動体通信端末と通信相手との間に呼を張る制御を行う他、基地局内の各構成要素を制御する。ベースバンド信号処理部(BB)13は、移動体通信端末から受信しベースバンドにダウンコンバートされた信号を処理し、かつ上位装置から受信したベースバンドの信号を移動体通信端末に送信するための処理を行う。動作確認試験部(MISC)14は、動作確認試験部(MISC)14を起点として他の各構成要素を通過して動作確認試験部(MISC)14に戻ってくる試験パスに沿って試験信号を流し、戻ってきた試験信号を検出することによって動作確認試験を行う。ハイウエイインタフェース(HWY-INF)15は、上位装置と有線接続されたインタフェースであって、上位装置との間で高速にデータを送受信する。

【0011】

制御部(CNT)12、ベースバンド信号処理部(BB)13、動作確認試験部(MISC)14およびハイウエイインタフェース(HWY-INF)15は、それぞれ物理的に分離されたカードで構成されている。なかでも、制御部(CNT)12は、冗長構成をなしている。ベースバンド信号処理部(BB)13およびハイウエイインタフェース(HWY-INF)15は複数のカードからなり、通信の容量を確保している。スイッチ(HWY-MUX)11は、制御部(CNT)12を構成するカードに搭載されている。

【0012】

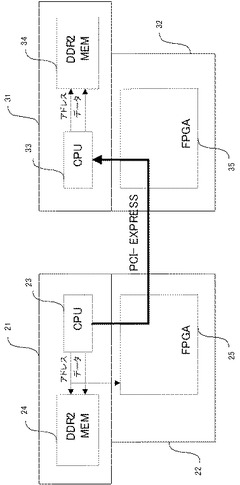

図2は、制御部の構成および動作イメージを示す図である。制御(CNT)カードは、呼処理監視制御部(CP/SV)、スイッチ(HWY-MUX)およびセキュリティ管理(SDM)部を具備している。呼処理監視制御部(CP/SV)およびスイッチ(HWY-MUX)のうち、通信中呼を継続するための構成を図2に図示している。

【0013】

呼処理監視制御部21,31およびスイッチ22,32は、それぞれ冗長構成をなしている。呼処理監視制御部21およびスイッチ22が現用系のとき、呼処理監視制御部31およびスイッチ32は予備系となる。呼処理監視制御部21,31は、CPU(Central Processing Unit)23,33およびDDR2(Double Data Rate 2)メモリ24,34をそれぞれ備えている。スイッチ22,32は、FPGA(Field Programmable Gate Array)25,35をそれぞれ備えている。

【0014】

呼処理監視制御部21,31は、通信中呼の情報を保持しており、冗長切替後も通信中呼を維持するために、相互に呼情報を共有する必要がある。この呼情報は、DDR2メモリ24,34にそれぞれ格納される。

【0015】

次に、現用系から予備系に呼情報を複製する動作を説明する。

【0016】

呼処理監視制御部21およびスイッチ22が現用系であり、呼処理監視制御部31およびスイッチ32が予備系のとき、CPU23は呼情報に関するデータをDDR2メモリ24の所定のアドレスに書き込む。具体的には、データをデータバスを介して、アドレスをアドレスバスを介して、それぞれDDR2メモリ24に送ることによって、呼情報がDDR2メモリ24に書き込まれる。例えば、アドレスは133MHzで送られ、データは約4倍の533Mbpsで送られる。このように、アドレスに比して高速にデータを送ることにより、高速な書き込みを可能としている。

【0017】

CPU23がDDR2メモリ24に呼情報の書き込みを行う際、FPGA25は、アドレスバスから分岐した信号を検出する。検出したアドレスを基に、FPGA25は、CPU23を介してDDR2メモリ24にアクセスして、呼情報に関するデータを読み出す。読み出されたデータとこれに対応するアドレスを、FPGA25は、予備系のFPGA35に送る。FPGA35は、現用系から得られた呼情報に関するデータを、CPU33を介してDDR2メモリ34に書き込ませる。

【0018】

こうした一連の動作によって、現用系で保持する呼情報と、予備系で保持する呼情報とを常に同じ内容に合せている。

【0019】

なお、アドレスバスから分岐した信号をFPGA25に検出させて、データバスから信号を分岐させないのは、比較的高速なデータ信号を分岐させるとCPU23、DDR2メモリ24およびFPGA25の各端子で反射が起こり信号波形への影響が大きいのに比して、アドレス信号は分岐させてもその影響が小さいことによる。アドレス信号の速度がデータ信号の速度に対して2分の1程度以下であれば、信号波形への影響を小さくすることが可能である。

【0020】

このように、比較的高速なデータを分岐させることなく、比較的低速なアドレスを分岐させて検出することにより、現用系に書き込まれたデータを精度良く高速に予備系に転送することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施の形態に係る基地局の構成及び動作イメージを示す図である。

【図2】制御部の構成および動作イメージを示す図である。

【符号の説明】

【0022】

11 スイッチ(HWY-MUX)

12 呼処理制御部(CNT)

13 ベースバンド信号処理部(BB)

14 動作確認試験部(MISC)

15 ハイウエイインタフェース(HWY-INF)

21 呼処理監視制御部(現用系)

22 スイッチ(現用系)

23 CPU(現用系)

24 DDR2メモリ(現用系)

25 FPGA(現用系)

31 呼処理監視制御部(予備系)

32 スイッチ(予備系)

33 CPU(予備系)

34 DDR2メモリ(予備系)

35 FPGA(予備系)

【技術分野】

【0001】

本発明は、冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込むデータ書込装置、およびこのような呼処理制御部を含み、移動体通信端末との間で無線通信を行う基地局に関する。

【背景技術】

【0002】

従来の技術として、現用系CPUから現用系メモリに転送されるデータを分岐させて検出し、これを予備系CPUを介して予備系メモリに書き込ませる技術があった。

【0003】

【特許文献1】特開平11-168559号公報

【特許文献2】特開平07-240754号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、近年は高速な書き込みが可能なメモリが登場してきており、従来の技術のように、現用系CPUから現用系メモリに転送されるデータを分岐させて検出しようとすると、現用系CPUおよび現用系メモリの間で反射が影響し信号波形が崩れてしまい、現用系で書き込んだデータを予備系に精度良く書き込むことが難しくなっていた。

【0005】

本発明の目的は、現用系に書き込まれたデータを精度良く高速に予備系にも書き込むことが可能なデータ書込装置およびこれを適用した基地局を提供することである。

【課題を解決するための手段】

【0006】

本発明は、冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込むデータ書込装置であって、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とするデータ書込装置である。

【0007】

また本発明は、冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込む呼処理制御部を含み、移動体通信端末との間で無線通信を行う基地局であって、前記呼処理制御部は、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とする基地局である。

【発明の効果】

【0008】

本発明によれば、現用系に書き込まれたデータを精度良く高速に予備系にも書き込むことができる。

【発明を実施するための最良の形態】

【0009】

図1は、本発明の実施の形態に係る基地局の構成および動作イメージを示す図である。基地局は、移動体通信に適用される基地局であって、移動体通信端末との間で無線通信を行い上位装置との間で有線通信を行う。

【0010】

スイッチ(HWY-MUX)11は、バッファメモリを具備しないスイッチであり、高速バスライン(HWYバス)で接続された各構成要素間を自由にスイッチングして相互にデータを転送させる。制御部(CNT)12は、移動体通信端末と通信相手との間に呼を張る制御を行う他、基地局内の各構成要素を制御する。ベースバンド信号処理部(BB)13は、移動体通信端末から受信しベースバンドにダウンコンバートされた信号を処理し、かつ上位装置から受信したベースバンドの信号を移動体通信端末に送信するための処理を行う。動作確認試験部(MISC)14は、動作確認試験部(MISC)14を起点として他の各構成要素を通過して動作確認試験部(MISC)14に戻ってくる試験パスに沿って試験信号を流し、戻ってきた試験信号を検出することによって動作確認試験を行う。ハイウエイインタフェース(HWY-INF)15は、上位装置と有線接続されたインタフェースであって、上位装置との間で高速にデータを送受信する。

【0011】

制御部(CNT)12、ベースバンド信号処理部(BB)13、動作確認試験部(MISC)14およびハイウエイインタフェース(HWY-INF)15は、それぞれ物理的に分離されたカードで構成されている。なかでも、制御部(CNT)12は、冗長構成をなしている。ベースバンド信号処理部(BB)13およびハイウエイインタフェース(HWY-INF)15は複数のカードからなり、通信の容量を確保している。スイッチ(HWY-MUX)11は、制御部(CNT)12を構成するカードに搭載されている。

【0012】

図2は、制御部の構成および動作イメージを示す図である。制御(CNT)カードは、呼処理監視制御部(CP/SV)、スイッチ(HWY-MUX)およびセキュリティ管理(SDM)部を具備している。呼処理監視制御部(CP/SV)およびスイッチ(HWY-MUX)のうち、通信中呼を継続するための構成を図2に図示している。

【0013】

呼処理監視制御部21,31およびスイッチ22,32は、それぞれ冗長構成をなしている。呼処理監視制御部21およびスイッチ22が現用系のとき、呼処理監視制御部31およびスイッチ32は予備系となる。呼処理監視制御部21,31は、CPU(Central Processing Unit)23,33およびDDR2(Double Data Rate 2)メモリ24,34をそれぞれ備えている。スイッチ22,32は、FPGA(Field Programmable Gate Array)25,35をそれぞれ備えている。

【0014】

呼処理監視制御部21,31は、通信中呼の情報を保持しており、冗長切替後も通信中呼を維持するために、相互に呼情報を共有する必要がある。この呼情報は、DDR2メモリ24,34にそれぞれ格納される。

【0015】

次に、現用系から予備系に呼情報を複製する動作を説明する。

【0016】

呼処理監視制御部21およびスイッチ22が現用系であり、呼処理監視制御部31およびスイッチ32が予備系のとき、CPU23は呼情報に関するデータをDDR2メモリ24の所定のアドレスに書き込む。具体的には、データをデータバスを介して、アドレスをアドレスバスを介して、それぞれDDR2メモリ24に送ることによって、呼情報がDDR2メモリ24に書き込まれる。例えば、アドレスは133MHzで送られ、データは約4倍の533Mbpsで送られる。このように、アドレスに比して高速にデータを送ることにより、高速な書き込みを可能としている。

【0017】

CPU23がDDR2メモリ24に呼情報の書き込みを行う際、FPGA25は、アドレスバスから分岐した信号を検出する。検出したアドレスを基に、FPGA25は、CPU23を介してDDR2メモリ24にアクセスして、呼情報に関するデータを読み出す。読み出されたデータとこれに対応するアドレスを、FPGA25は、予備系のFPGA35に送る。FPGA35は、現用系から得られた呼情報に関するデータを、CPU33を介してDDR2メモリ34に書き込ませる。

【0018】

こうした一連の動作によって、現用系で保持する呼情報と、予備系で保持する呼情報とを常に同じ内容に合せている。

【0019】

なお、アドレスバスから分岐した信号をFPGA25に検出させて、データバスから信号を分岐させないのは、比較的高速なデータ信号を分岐させるとCPU23、DDR2メモリ24およびFPGA25の各端子で反射が起こり信号波形への影響が大きいのに比して、アドレス信号は分岐させてもその影響が小さいことによる。アドレス信号の速度がデータ信号の速度に対して2分の1程度以下であれば、信号波形への影響を小さくすることが可能である。

【0020】

このように、比較的高速なデータを分岐させることなく、比較的低速なアドレスを分岐させて検出することにより、現用系に書き込まれたデータを精度良く高速に予備系に転送することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施の形態に係る基地局の構成及び動作イメージを示す図である。

【図2】制御部の構成および動作イメージを示す図である。

【符号の説明】

【0022】

11 スイッチ(HWY-MUX)

12 呼処理制御部(CNT)

13 ベースバンド信号処理部(BB)

14 動作確認試験部(MISC)

15 ハイウエイインタフェース(HWY-INF)

21 呼処理監視制御部(現用系)

22 スイッチ(現用系)

23 CPU(現用系)

24 DDR2メモリ(現用系)

25 FPGA(現用系)

31 呼処理監視制御部(予備系)

32 スイッチ(予備系)

33 CPU(予備系)

34 DDR2メモリ(予備系)

35 FPGA(予備系)

【特許請求の範囲】

【請求項1】

冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込むデータ書込装置であって、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とするデータ書込装置。

【請求項2】

冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込む呼処理制御部を含み、移動体通信端末との間で無線通信を行う基地局であって、前記呼処理制御部は、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とする基地局。

【請求項1】

冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込むデータ書込装置であって、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とするデータ書込装置。

【請求項2】

冗長構成をなし、アドレスに比べて2倍以上の速度でデータを転送することによってCPUからメモリにデータを書き込む呼処理制御部を含み、移動体通信端末との間で無線通信を行う基地局であって、前記呼処理制御部は、

現用系CPUから現用系メモリに転送されるアドレス信号を分岐させて検出するアドレス検出部と、

前記アドレス検出部によって検出されたアドレスに基づき、これに対応して現用系メモリに書き込まれたデータを現用系CPUを介して読み出すデータ読出部と、

前記アドレス検出部によって検出されたアドレスと同じ予備系メモリのアドレスに、前記データ読出部によって読み出されたデータを書き込むように予備系CPUに指示する書込指示部と

を備えたことを特徴とする基地局。

【図1】

【図2】

【図2】

【公開番号】特開2009−86876(P2009−86876A)

【公開日】平成21年4月23日(2009.4.23)

【国際特許分類】

【出願番号】特願2007−253975(P2007−253975)

【出願日】平成19年9月28日(2007.9.28)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成21年4月23日(2009.4.23)

【国際特許分類】

【出願日】平成19年9月28日(2007.9.28)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]