データ管理システム、データ管理方法、RFIDタグ及びタグリーダ/ライタ

【課題】放射線に晒されるような特殊環境でデータエラーを確実且つ簡単に検出することができ、データエラーの発生を防止することができるデータ管理システム、データ管理方法、RFIDタグ及びタグリーダ/ライタを提供する。

【解決手段】マスタとスレーブとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システムにおいて、前記スレーブは、データと共に当該データの誤りを訂正するための冗長データが記憶された不揮発性記憶手段を備える。前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対として符号化したデータを含む。スレーブ側制御部又はマスタ側制御部は、誤り検出処理において、前記不揮発性記憶手段から読出したデータについて前記ビット対をなす双方のビットの値が0であれば前記ビット対に誤りが有ると判断する。

【解決手段】マスタとスレーブとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システムにおいて、前記スレーブは、データと共に当該データの誤りを訂正するための冗長データが記憶された不揮発性記憶手段を備える。前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対として符号化したデータを含む。スレーブ側制御部又はマスタ側制御部は、誤り検出処理において、前記不揮発性記憶手段から読出したデータについて前記ビット対をなす双方のビットの値が0であれば前記ビット対に誤りが有ると判断する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スレーブ側電子機器とマスタとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システム、データ管理方法、RFIDタグ及びタグリーダ/ライタに関する。

【背景技術】

【0002】

上記RFID(Radio Frequency Identification)タグは、アンテナと当該アンテナに電気的に接続されたIC(Integrated Circuit)チップ等のRFID回路とを備えており、RFID回路に内蔵されたメモリ部に対して、アンテナを通じてタグリーダ/ライタにより非接触で情報の書込み及び読取りが行われるようになっている。この場合、RFIDタグは、マスタたるタグリーダ/ライタに対するスレーブとして、RFIDシステムを構成するもので、近年では商品の管理や物品の履歴のトレーサビリティー等を目的として様々な分野で導入されつつある。

【0003】

ところで、RFIDタグにおいてはその寿命等に起因して、メモリ部に記憶されたデータの異常、つまりデータエラーが発生することがある。そこで、例えば、特許文献1のRFIDタグでは、CRCチェックコードを用いてデータエラーを検出し、ECCチェックチェックコードをもとに、1ビットのエラーを訂正して正しいデータを復元するようになっている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−250426号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

一方、近年では、原子力発電所等の放射線被曝環境下においても、RFIDタグによる種々の管理を行うことで事故の未然防止を図ることが要請されている。しかしながら、引用文献1のようにデータエラーの訂正が可能RFIDタグでも、放射線によりデータエラーが発生する惧れがあるような特殊環境の下では、RFIDタグを使用することはできない。つまり、RFIDタグが放射線に晒されると、その放射線の照射時間の経過に伴いメモリ部におけるデータエラーが蓄積される。また、放射線量によっては、メモリ部にて複数ビットにわたる連続したバーストエラーが発生する虞もあり、1ビットのエラー訂正はもとより、データエラーの検出すらできない事態も生じうる。特許文献1では、放射線或は宇宙線に晒されるような特殊環境においてRFIDタグを使用することは想定されておらず、特許文献1のような対処では上記の特殊環境でRFIDタグを用いることは困難である。

【0006】

本発明は上記事情に鑑みてなされたものであり、その目的は、放射線に晒されるような特殊環境でデータエラーを確実且つ簡単に検出することができ、データエラーの発生を防止することができるデータ管理システム、データ管理方法、RFIDタグ及びタグリーダ/ライタを提供することである。

【課題を解決するための手段】

【0007】

上記した目的を達成するために、本発明のデータ管理システムは、マスタとスレーブとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システムにおいて、前記スレーブは、データと共に当該データの誤りを訂正するための冗長データが記憶された不揮発性記憶手段と、当該スレーブ全体の制御を行うスレーブ側制御部とを備え、前記マスタは、前記無線通信手段を介したデータの読出し及び書込みを制御するマスタ側制御部を備え、前記スレーブ側制御部又は前記マスタ側制御部によって、前記不揮発性記憶手段から読出したデータについて前記冗長データをもとに誤り検出処理を行い、その検出処理において誤りが検出された場合には誤り訂正処理を行う構成にあって、前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対として符号化したデータを含み、前記スレーブ側制御部又は前記マスタ側制御部は、前記誤り検出処理において、前記不揮発性記憶手段から読出したデータについて前記ビット対をなす双方のビットの値が0であれば前記ビット対に誤りが有ると判断することを特徴とする。

【発明の効果】

【0008】

例えば透過放射線により、不揮発性記憶手段においてデータが"1"から"0"に片方向へ変化するデータエラーが生じる状況にあるとする。この場合、前記スレーブ側制御部又はマスタ側制御部によって、ビット対をなす双方のビットが値0であれば、当該ビット対により表現されたデータが誤りであると判定でき、ビット対をもとにデータエラーを確実且つ簡単に検出することができる。従って、放射線に晒される特殊環境でデータエラーの発生を防止することができ、データ管理システムとして正常に機能させることができる。よって、原子力産業や航空・宇宙産業等において、安全性及び信頼性を確保しつつ、設備の保守、作業効率化やトレーサビリティーの確立等を実現することができるデータ管理システムを提供できる。

【図面の簡単な説明】

【0009】

【図1】第1実施形態のデータ管理システムを概略的に示す全体図

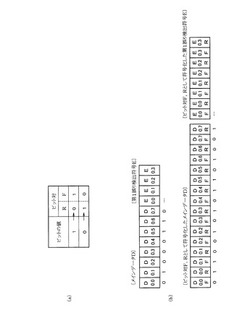

【図2】RFIDタグとタグリーダ/ライタの種類、並びにこれらの組合わせを説明するための図

【図3】(a)はアクティブ型のRFIDタグの電気的構成を示し、(b)は、パッシブ型のRFIDタグ及びタグリーダ/ライタの電気的構成、並びにデータ管理システムの概略を示すブロック図

【図4】(a)及び(b)は、アクティブ型のRFIDタグ及びタグリーダ/ライタにおけるメモリ部の夫々のマップイメージを示す図

【図5】パッシブ型のRFIDタグにおけるメモリ部のマップイメージを示す図

【図6】(a)並びに(b)は、メインデータ及び第1誤り検出符号、並びに第2誤り検出符号を説明するための図

【図7】RFIDタグにおけるメモリ部のメモリマップを示す図

【図8】メインデータ及び第1誤り検出符号の夫々のビット対と、各ビット対における実際の使用アドレスの例を説明するための図

【図9】パリティ符号を用いた誤り検出処理と誤り訂正処理を説明するための図

【図10】(a)はビット対として符号化したデータを示す図、(b)は、ビット対として符号化したメインデータ及び第1誤り検出符号の一例を示す図

【図11】データが1から0に片方向へ変化するエラーと、代入データの代入パターンの一例を示す図

【図12】データを書込む場合における全体の処理の流れを示すフローチャート

【図13】データを読出す場合における全体の処理の流れを示すフローチャート

【図14】同じアドレスについて連続してデータを読出す処理の一例を示すフローチャート

【図15】関連データ読込み処理の流れを示すフローチャート

【図16】各冗長データを用いた誤り訂正処理の流れを示すフローチャート

【図17】第1誤り検出符号に係る誤り訂正処理の流れを示すフローチャート

【図18】多重化に係る誤り訂正処理の流れを示すフローチャート

【図19】パリティ符号に係る誤り訂正処理の流れを示すフローチャート

【図20】第1誤り検出符号及び第2誤り検出符号に係る誤り訂正処理の流れを示すフローチャート

【図21】二重化したデータに基づく誤り訂正処理を説明するための図

【図22】第2実施形態を示すもので、三重化したデータに基づく誤り訂正処理を説明するための図

【図23】第3実施形態を示す図10(b)相当図

【図24】第4実施形態を示す図23相当図

【図25】第5実施形態を示すもので、IDデータに関する誤り訂正処理の流れを示すフローチャート

【図26】第6実施形態を示すもので、各種の誤り訂正プログラムについて、夫々の誤り訂正を行う対象を説明するための図

【図27】主又は副誤り訂正プログラムによる処理内容を示すフローチャート

【図28】簡易誤り訂正プログラムの処理内容を示すフローチャート

【図29】第7実施形態を示す図6(a)相当図

【図30】図29相当図

【発明を実施するための形態】

【0010】

<第1実施形態>

以下、本発明の第1実施形態について、図1〜図21を参照しながら説明する。

図1に示すように、データ管理システム11は、所謂データ担体或はデータキャリアとしてのRFIDタグ10と、このRFIDタグ10と非接触でデータの交信を行うタグリーダ/ライタ12と、このタグリーダ/ライタ12に通信回線13aで接続されたパソコン14と、パソコン14に通信回線(通信ネットワーク)13を介して接続されたサーバ15とから構成されている。

【0011】

図2に示すように、前記RFIDタグ10は、電源を内蔵し内部回路の動作電力と電波を返送する電力に内部の電源を用いるアクティブ型のRFIDタグ10Aと、内部回路の動作電力にのみ内部の電源を用い、電波を返送する電力には外部から受信した電波をエネルギー源として動作するセミパッシブ型のRFIDタグ10Bと、内部に電源を内蔵せず、外部から受信した電波をエネルギー源として動作するパッシブ型のRFIDタグ10Cとに大別される。RFIDタグ10A〜10Cはマスタたるタグリーダ/ライタ12に対するスレーブであって、当該タグ10A〜10Cには夫々、スレーブ側制御部と、データを記憶するための不揮発性記憶手段とが内蔵されている。

【0012】

具体的には、例えば図3(a)に示すRFIDタグ10Aは、例えば基板1aに実装されたアンテナ2a、RFID回路3a、電源(電池4a)等を備えている。アンテナ2aは、RFID回路3aに対して電気的に接続されている。RFID回路3aは、制御部5aを主体として、これに接続されるメモリ部6a、通信部7a及び外部インターフェイス(I/F)部8a等から構成されている。外部I/F部8aには、外部環境を検出するための検出手段としてセンサ部9aが接続されている。センサ部9aとしては、例えば温度センサ、放射線センサ、振動センサ、音センサ等、RFIDタグ10Aの用途に応じて各種の検出手段を用いることができる。

【0013】

前記不揮発性記憶手段としてのメモリ部6aは、通信部7aや、センサ部9a、外部検出手段等から得たデータを書換え可能に記憶する。図4(a)に示すように、メモリ部6aには、制御部5aにより実行される制御プログラムを含む一般プログラム等が記憶されたプログラム領域100、前記データと共に当該データの誤りを訂正するための冗長データが記憶されたデータ領域(ユーザ領域)101等の複数の記憶領域が設けられている。プログラム領域100には、前記一般プログラム用の記憶領域102の他、後述の主誤り訂正プログラム、副誤り訂正プログラム、簡易誤り訂正プログラム用の記憶領域103〜105が設けられている。また、詳しくは後述するように、冗長データは、ビット対に係るデータ、誤り検出符号、パリティ符号等の付加データを含む。

【0014】

制御部5aは、RFIDタグ10A全体の制御を司るスレーブ側制御部として、例えばMPU(Micro Processing Unit)から構成されている。通信部7aは、アンテナ2aで受信した電波に含まれるデータ信号が伝達されると、そのデータ信号を元のデータに復調する処理を行うもので、アンテナ2aと共に無線通信手段を構成する。制御部5aは、タグリーダ/ライタ12からの命令(コマンド)の内容に従って、制御プログラムに基づきメモリ部6aの記憶内容の書換え或は書込み等を行う。また、制御部5aは、タグリーダ/ライタ12からのコマンドの内容に従い、メモリ部6aに保存しているデータを送信するための制御を通信部7aに対して行い、メモリ部6aから取出されたデータにより、通信部7aにおいて所定の周波数帯の搬送波が変調され、アンテナ2aからタグリーダ/ライタ12側に送信される。

【0015】

一方、図3(b)に示すRFIDタグ10Cはパッシブ型であり、上記RFIDタグ10Aと異なり、電池4a、外部I/F部8a、センサ部9a等が省略されている。以下、相違点につき簡単に説明すると、RFIDタグ10Cは、例えばPETフィルムからなるフィルム基材1cに実装されたアンテナ2c及びRFID回路3cを備えている。RFID回路3cは、制御部5c、メモリ部6c及び通信部7cと、アンテナ2cで受信した電波から電源電圧を生成する電源電圧発生部4cとの機能をワンチップ化したICチップであって、電源電圧発生部4cで得た電源電圧に基づいて動作する。

【0016】

図5に示すように、メモリ部6cには、RFIDタグ10C固有のIDデータを含む識別データが記憶されるTID記憶領域200、RFIDタグ10Cの貼付対象物に関する電子製品コード(Electronic Product Code)等が記憶されるEPC記憶領域201、通信部7c等から得た各種のデータと共に当該データの誤りを訂正するための冗長データが記憶されたデータ領域(ユーザ領域)202等の複数の記憶領域が設けられている。前記IDデータは、RFIDタグ10Cが本来有するIDであって、TID記憶領域200に書換え不能に記憶されている。

【0017】

制御部5cは、ハードロジック回路からなり、タグリーダ/ライタ12との交信時において、メモリ部6cへの書込みを行う処理や、メモリ部6aに保存しているデータを送信するため処理等、所定の処理を行うようになっている。

【0018】

尚、上記RFIDタグ10Cの制御部5cはCPUを用いて構成してもよい。また、RFIDタグ10Bについては、電池4b(図2参照)を内蔵する一方、タグリーダ/ライタ12から受信した電波をエネルギー源として電波を発するセミパッシブ型であり、その詳細な説明を省略することとする。

【0019】

前記タグリーダ/ライタ12は、上記RFIDタグ10A〜10Cに対するマスタとして構成された読み書き装置である。即ち、図3(b)に示すように、タグリーダ/ライタ12は、基板17に実装されたマスタ側制御部(制御部18)を主体として、これに接続されるメモリ部19、通信部20及び外部I/F部21を備えている。通信部20は、アンテナ22と共に無線通信手段を構成しており、外部I/F部21は、前記パソコン14等の上位装置に接続されている。詳細には、タグリーダ/ライタ12としては、ハンディ型タグリーダ/ライタ12A、或は据置型タグリーダ/ライタ12Bが用いられ(図1、図2参照)、パソコン14との間で無線通信、或は通信回線13aを介した通信を行う。

【0020】

タグリーダ/ライタ12のメモリ部19には、RFIDタグ10Aのメモリ部6aと同様に(図4参照)、制御部18により実行される制御プログラムを含む一般プログラム等が記憶されたプログラム領域300、データと共に当該データの誤りを訂正するための冗長データが記憶されたデータ領域(ユーザ領域)301等の複数の記憶領域が設けられている。プログラム領域300には、前記一般プログラム用の記憶領域302の他、後述の主誤り訂正プログラム、副誤り訂正プログラム、簡易誤り訂正プログラム用の記憶領域303〜305が記憶されている。

【0021】

そして、制御部18は、一般プログラム記憶領域302の制御プログラムに基づいて、通信指令を通信部20に対して行うことにより、通信部20にて送信データを用いて変調した所定周波数の電波信号をアンテナ22から送信する送信処理と、アンテナ22で受信した電波信号より元のデータを復調する受信処理とを行う。

【0022】

尚、RFIDタグ10A〜10Cのメモリ部6a〜6c、並びにタグリーダ/ライタ12A,12Bのメモリ部19は、何れもフローティングゲートに電荷を保持することでデータを記録するタイプのメモリである。即ち、このようなメモリとしては、フラッシュメモリやEEPROM(Electrically Erasable Programmable ROM)等、各種の不揮発性の半導体メモリを使用してもよく、メモリ部6a〜6c、19は不揮発性記憶手段として構成されている。

【0023】

前記パソコン14は情報処理/操作装置であって、その操作入力による指示データ等が通信回線13a或は無線通信を介してタグリーダ/ライタ12へ出力され、タグリーダ/ライタ12から上記したRFIDタグ10に係るデータがパソコン14へと出力される。

【0024】

ここで、図1では、データ管理システム11を、例えば熱中性子炉等の原子力施設のように放射線に晒される設備24の保全管理に適用した一例を示している。当該設備24には、流路を形成する配管24aの温度を検出するための温度センサを配したRFIDタグ10Aや、設備24における放射線量を検出するための放射線センサを内蔵したRFIDタグ10Aが設けられている。また、設備24に対して搬入・搬出される物品24bや、作業者のヘルメット24cにRFIDタグ10Cが貼付される等、様々な管理ポイントに対応したRFIDタグ10が設けられている。パソコン14は、例えば設備24から隔離された操作室に配置され、通信回線13を介してサーバ15への指示やサーバ15からの応答等、種々のデータのやり取りが行えるようになっている。サーバ15のデータベース15aには、例えば設備24や物品24bの管理番号、点検/交換履歴、前記の各センサで検出されたデータ等、設備24に係る各種データが記憶されており、サーバ15からの呼び出しに応じてデータの取得、参照が行われ、または必要に応じてデータが書込まれる。

【0025】

上記データ管理システム11において、ハンディ型或は据置型タグリーダ/ライタ12A,12Bを用いて、設備24から離れた位置でRFIDタグ10A〜10Cから各種の情報を得ることができる。また、RFIDタグ10A〜10Cに係る各種情報がデータベース15aによって総合的に管理され、パソコン14により取得した情報を分析、把握することができる。そして、例えばRFIDタグ10の温度センサから得られた温度データに基づいて、その温度の上昇傾向が識別される場合には、当該温度データが正常値の範囲内であっても、パソコン14での画面や音声等を通じてシステム管理者に注意を喚起する。また、これと同様に、振動、放射線、音等のセンサ情報について夫々正常なデータの範囲内であっても、通常時のデータと異なる傾向を示す場合には、パソコン14等の報知手段により報知する等して、異常が顕在化する前の注意喚起を行うことができる。従って、設備24や機器の温度、放射線レベル等を集約監視することができ、設備24等において異常が顕在化する前のメンテナンスを行うことができると共に、トレーサビリティーの確立と、保全管理の効率化を図ることができる。

【0026】

さて、上記のような放射線環境下では、RFIDタグ10或はタグリーダ/ライタ12において、透過放射線によりデータエラーが発生する事態が想定される。具体的には、例えばRFIDタグ10Cのメモリ部6cにおいてマトリクス状に配列されたメモリセルのフローティングゲートに注入された電子(電荷)量が、例えばガンマ線の入射に基づく光電効果等に起因して低減する。この場合、メモリセルにおいて例えばデータが"1"から"0"に片方向へ変化するデータエラーが生じる虞があり、その損傷の度合いは、次の第1段階〜第3段階に分類される。

(第1段階)前記メモリセルの電子に対する放射線の衝突により損傷が発生しており、更なる放射線の衝突によりデータエラーに至る可能性がある段階。

(第2段階)メモリセルにおいて例えば8ビットからなるワードデータのうち1ビットのデータエラーが発生している段階。

(第3段階)メモリ部6cの損傷の度合いが大きく前記ワードデータにおいて2ビット以上のデータエラーが発生した段階であって、複数ビットにわたる連続したデータエラー(バーストエラー)、或は複数箇所に散在した1ビットのデータエラー(ランダムエラー)が発生している段階。

【0027】

そこで、発明者は、放射線の照射に起因する全ての段階のエラー訂正が可能なデータ管理システム11を構築した。ここで、前記RFIDタグ10の種類10A〜10Cとタグリーダ/ライタ12の種類12A,12Bとの組合わせは(図2参照)、通信距離との関係上、

(a)アクティブ型の電池4a付きRFIDタグ10Aと、据置型タグリーダ/ライタ12B

(b)セミパッシブ型の電池4b付きのRFIDタグ10Bと、ハンディ型或は据置型タグリーダ/ライタ12A,12B

(c)パッシブ型のRFIDタグ10Cと、ハンディ型或は据置型タグリーダ/ライタ12A,12B

に分類されるが、以下では(c)のRFIDタグ10Cとハンディ型タグリーダ/ライタ12Aとの組合せにおけるエラー訂正について説明する。尚、RFIDタグ10Cの制御部5c及びメモリ部6cを、タグ側制御部5c及びタグ側メモリ部6cとし、タグリーダ/ライタ12Aの制御部18をRW側制御部18とする。

【0028】

図6(a)及び(b)は、タグ側メモリ部6cに記憶されるデータに対して生成される冗長データを説明するための図である。前記データ領域202は、本来のデータたるメインデータを記憶するためのメインデータ領域210と、前記冗長データを記憶するための冗長領域220とを有する。ここでは、メインデータ領域210を8バイト分だけ示している。

【0029】

冗長領域220に記憶されている冗長データは、ここでは、メインデータ領域210に記憶されているメインデータの誤りを訂正するための誤り検出符号であって、メインデータのアドレスごとに生成される横方向の第1誤り検出符号と、同じビット位置ごとに生成される縦方向の第2誤り検出符号とを含む。

【0030】

前記誤り検出符号として例えばハミング符号が用いられ、2ビットの誤り検出ができるように設定されている。ここで、ハミング符号についてエラー訂正用ビットの数をmとした時、その符号長は2m−1で表される。従って、例えばm=4の場合、11ビットのメインデータに対して、15ビットの符号語(符号長)に置き換えるハミング符号が形成される。そこで、本実施形態では、後述する誤り検出処理の際、前記8ビット単位のメインデータに対して、3ビットのダミーデータを付して(つまりメインデータの上位3ビットを"0"にして)見かけ上、11ビットのメインデータに付随する4ビットの誤り検出符号として誤り検出処理を行うようになっている。尚、上記ハミング符号にパリティビットを付加して、2ビット誤り検出と1ビット誤り訂正とを行うようにしてもよい。

【0031】

図6(a)では、前記メインデータを記憶した領域210と第1誤り検出符号(第1冗長データ)を記憶した領域221において、同図中、縦方向の座標値(アドレス)をx、横方向の座標値(ビット位置)をyとした場合における、メインデータD(x、y)及び第1誤り検出符号E(x、y)を示している。ここで、第1誤り検出符号E0,1〜E0,3及びE1,0〜E1,3は、同じアドレスの上位4ビット及び下位4ビットに書込まれている(図7のアドレス200、図8(a)参照)。従って、2列のデータ列D0,0〜E0,3及びD1,0〜E1,3は、3バイトで表現されることとなる。また、図6(b)には、冗長領域220のうち、第2誤り検出符号(第2冗長データ)を記憶した領域222において、上記メインデータD0,0〜D7,7の同じビット位置の列ごと生成された第2誤り検出符号F(x、y)と、第1誤り検出符号Eの同じビット位置の列ごと生成された第2誤り検出符号G(x、y)とを夫々示している。尚、図6に示す符号D(x、y)、F(x、y)、G(x、y)は、データの配列を説明するために便宜的に付したものであり、実際のデータビットの配列は、LSB(Least Significant Bit:最下位ビット)ファースト、MSB(Most Significant Bit:最上位ビット)ファーストの何れについても適用が可能である。

【0032】

本実施形態のパリティ符号は、データを構成する各ビットに対して、互いに隣り合う当該ビットとの組合わせに対応して付加される。具体的には例えば、パリティ符号をもとに奇数パリティ検査を行うようになっており、メインデータD0,0の示す値が0、D0,1の示す値が1のとき、値が0のパリティビットを付加する(図9(a)(b)参照)。従って例えば、メインデータD0,0〜D0,7及び第1誤り検出符号E0,0〜E0,3が示す値が「01000110…」のとき、その隣り合う値の組合せに対応した「0011010…」からなる奇数パリティ符号Pが生成される。このパリティ符号Pを用いて、メインデータD及び第1誤り検出符号Eについて誤り検出処理と誤り訂正処理が行われるようになっている。尚、パリティ符号Pは、偶数パリティ符号であってもよい。

【0033】

本実施形態の冗長データの一種であるビット対は、データの各ビットが示す1,0の値の何れか一方を01、他方を10とするビット対として符号化したデータであり、1ビットデータを2ビットデータで表現する。具体的には例えば、図10(a)に示すように、メインデータD0,0が示す0の値を10、メインデータD0,1における1の値を01とするビット対として符号化する。従って、図10(b)に示すメインデータD0,0〜D0,7及び第1誤り検出符号E0,0〜0,3が示す値が「01000110…」のとき、「0110010101101001…」からなるデータD0,0F〜E0,3Rが生成される。この場合、メインデータD0,0における本来のデータ0の値は、ビット対における一方のビット0(図10(a)中、Fで示す)であり、他方のビット1(Rで示す)は当該0を反転させたデータである。

【0034】

よって、図22(b)に示すように、ビット対として符号化された4列のデータD0,0F〜E1,3Rのうち、上から1列目のデータD0,0F〜E0,3Fは、図22(a)のメインデータD0,0〜D0,7及び第1誤り検出符号E0,0〜E0,3と一致し[(D0,0F〜E0,3F)=(D0,0〜E0,3)]、図22(b)の上から3列目のデータD0,0R〜E0,3Rは、1列目のデータD0,0F〜E0,3Fの反転データである。また、図7、図8(b)に示すように、前記ビット対F,Rのうち一方のビットFと他方のビットRは、タグ側メモリ部6cのデータ領域202において、相互に異なるアドレスの同じビット位置に記憶される。換言すれば、符号化されたデータD0,0F〜E0,3F及び反転データD0,0R〜E0,3Rは、相互に異なるアドレスに記憶され、且つ対応する各ビットが示す値は相互に反転した内容となっている。

【0035】

ここで、図11は、メインデータD0,0〜D0,7における一部のビットの値が"1"から"0"に片方向へ変化する、前述したデータエラーが生じている状況を例示している。即ち、ビット対F,Rはその何れか一方のビットに1を含むことから、前記の片方向への変化を前提とした場合、00のビット対(図11の網掛部分)がエラーパターンとなることで、そのエラーが発生した数とビット対F,Rの位置を特定することができるのである。例えば、各ビット対F,Rにおいて、一方のビットFと他方のビットRとの論理和演算を行うことにより、誤りを検出することができる。

【0036】

上記の符号化と異なり、データの各ビットが示す0の値を01、1の値を10とするビット対として符号化してもよい。また、メモリがデータを記憶している状態に対する定義によっては、透過放射線により"0"から"1"の片方向の変化が生じるケースもあるが、0と1とを反転して扱えば足りるので、本実施形態では"1"から"0"への片方向への変化を前提として説明する。

【0037】

前記冗長領域220は、多重化データを記憶するための多重化データ記憶領域224を含む(図7参照)。本実施形態では、例えば、メインデータD0,0〜D7,7のビット対F,Rが、メインデータ領域210と多重化データ記憶領域224とに書込まれることにより二重化されており、第1誤り検出符号E0,0〜E7,3のビット対F,Rも、第1誤り検出符号領域221と多重化データ記憶領域224とに書込まれることにより二重化されている。以下では、多重化されたメインデータ及び第1誤り検出符号について、D0,0F´〜D7,7R´及びE0,0F´〜E7,3R´の如く該当符号に「ダッシュ」を付すものとする(図7参照)。尚、第1誤り検出符号E、第2誤り検出符号F,G、パリティ符号Pの多重化、並びにこれら冗長データE,F,G、Pのビット対F,Rの多重化についても、必要に応じて行うことができる。また、第1誤り検出符号E、第2誤り検出符号F,G、パリティ符号Pの生成対象、並びにビット対F,Rとして符号化を行う対象は、本実施形態の記載に限定するものではなく、冗長データE,F,G、P相互間とするなど適宜設定することができる。

【0038】

次に、上記構成の作用について、図12〜図20も参照しながら説明する。図12は、ハンディ型タグリーダ/ライタ12Aを用いてRFIDタグ10Cにデータを書込む場合の処理内容を示すフローチャートである。

【0039】

先ず、タグリーダ/ライタ12Aの操作部(図示せず)が作業者により操作されると、RW側制御部18は、その操作部から入力された操作信号に基づいて、書込むべきデータを受付けて処理する(ステップA1)。そして、詳しくは後述するように、RW側制御部18は、その書込み用データをRFIDタグ10Cに送信する前に、タグ側メモリ部6cから当該書込み用データを書込むアドレス以外の全てのアドレスのデータを読出して、前記冗長データをもとに誤りを検出して訂正するようになっている(ステップA2)。

【0040】

ステップA2の読取り処理の後、RW側制御部18は、書込み用データたるメインデータDについてアドレスごとに第1誤り検出符号Eを生成すると共に、同じビット位置ごとに第2誤り検出符号F,Gを生成する処理を行う(ステップA3、A4)。次いで、RW側制御部18は、メインデータD及び第1誤り検出符号Eを構成する各ビットに対して、互いに隣り合う当該ビットの組み合せに対応してパリティ符号Pを生成する(ステップA5)。また、メインデータD、第1誤り検出符号E及びパリティ符号Pの各ビットが示す1と0の値は、01と10のビット対F,Rとして符号化される(ステップA6)。更に、メインデータD及び第1誤り検出符号Eの夫々のビット対F,Rは、ステップA7において二重化されることにより、メインデータD及び第1誤り検出符号Eのビット対F´,R´が生成される。こうして生成された、メインデータD及び第1誤り検出符号Eの夫々のビット対F,R、二重化されたビット対F´,R´、第2誤り検出符号F,G、並びにパリティ符号Pが送信されることにより、タグ側メモリ部6cに書込まれ(ステップA8)、タグリーダ/ライタ12Aを用いた書込み処理を終了する。これにより、RFIDタグ10Cに対して、メインデータDのビット対Fと併せて各種の冗長データが記憶されることから、その冗長データをもとに誤り検出処理と誤り訂正処理を行うことが可能となる。

【0041】

図13は、上記の書込み処理に際して前記ステップA2で行われる読取り処理の内容を示すフローチャートである。

先ず、RW側制御部18は、タグ側メモリ部6cから前記書込み用データを書込むアドレス以外の全てのアドレスのデータを読出す関連データ読込み処理を実行する(ステップB1、図15のステップC1〜C11参照)。即ち、関連データ読込み処理では、メインデータD及び第1誤り検出符号Eのビット対F,Rがタグ側メモリ部6cから読込まれる(ステップC1,C2)。次いで、これらメインデータD及び第1誤り検出符号Eのビット対F,Rが多重化されている場合は(ステップC3:YES)、多重化データとしてのメインデータD及び第1誤り検出符号Eのビット対F´,R´がタグ側メモリ部6cから読込まれる(ステップC4,C5)。また、パリティ符号Pが付加されている場合は(ステップC6:YES)、メインデータDのパリティ符号P及び第1誤り検出符号Eのパリティ符号Pがタグ側メモリ部6cから読込まれる(ステップC7,C8)。更に、第2誤り検出符号F,Gが付加されている場合は(ステップC9:YES)、メインデータDの第2誤り検出符号F、及び第1誤り検出符号Eの第2誤り検出符号Gがタグ側メモリ部6cから読込まれる(ステップC10,C11)。

【0042】

尚、RW側制御部18において、タグ側メモリ部6cの冗長領域220に記憶された冗長データが、メインデータD及び第1誤り検出符号Eに係るビット対Rのみと判断した場合は(ステップC3,C6,C9:NO)、ステップC1,C2でメインデータD及び第1誤り検出符号Eに係るビット対F,Rを読込みこんだ後、ステップB2(図13参照)の誤り検出処理に移行する。また、上記のステップB1の読込み処理では、RW側制御部18は、同じアドレスについて連続して少なくとも2度同じデータを読出すまで、繰り返しデータを読出す。具体的には、例えば8ビットのメインデータD0,0〜D0,7は、2回続けて読出され(図14のステップD1,D2)、1回目と2回目のデータが異なる場合には(ステップD3:NO)、再度2回続けて読出される。即ち、放射線に晒された環境においてRFIDタグ10Cからデータを出す場合、データを送信するRFIDタグ10C側あるいは受信したタグリーダ/ライタ12A側で放射線によりデータが化ける可能性がある。そこで、RW側制御部18は、連続して少なくとも2度同じデータを読出すまで繰り返しデータを取得することで、タグ側メモリ部6cからデータを読出す際のデータ化けを防止することができる。また、後述の誤り検出処理で誤りが検出されず(図13のステップB3:NO)、誤り訂正処理が行われなくても、ステップB1(ステップD1〜D3)のデータ読出しの際、その読出しと同時に各メモリセルの電荷の再チャージ、つまりリフレッシュを行うことができる。従って、各メモリセルにおいて放射線の衝突により電子が失われていたとしても、前記第1段階にある損傷は修復されることになる。

【0043】

ステップB2では、上記のようにして読出したメインデータD及び第1誤り検出符号Eの各ビット対F,Rについて、一方のビットFと他方のビットRとの論理和演算を行う。ここで、RW側制御部18は、その演算結果が1であればビット対F,Rの何れかに誤りが無く(ステップB3:NO)、当該演算結果が0であればビット対F,Rに誤りが有ると判断して(ステップB3:YES)、誤り訂正処理(ステップB4、図16のステップE1〜E10)に移行する。

【0044】

この誤り訂正処理では、先ず、メインデータD及び第1誤り検出符号Eのビット対F,Rに係る訂正処理が1バイトごとに行われる(ステップE1、図17のステップF1〜F5)。具体的には、RW側制御部18は、バイト数をカウントするためのカウンタNをゼロクリアして(ステップF1)、メインデータD0,0F〜D0,7Fについて、メインデータD0,0R〜D0,7Rとのビットごとの論理和演算に基づき、0となるビット対F,Rが3つ以上有るか、或は演算結果が全て1かを判断する(ステップF2)。例えば図11の網掛部分で示すように、メインデータD0,0〜D0,7のビット対F,Rのうち、その組合わせが00となっているメインデータD0,2及びD0,5のビット対F,Rは演算結果が0となる。このため、メインデータD0,2及びD0,5についてのビット対F,Rについて誤りと判断され(ステップF2:NO)、そのメインデータD0,2、D0,5の誤りを訂正する処理が行われる(ステップF3)。この場合、該当するメインデータD0,2、D0,5の夫々のビット対F,Rに、データ01或は10(これらを代入データと称す)を順次代入し、当該代入データを代入したメインデータD0,0F〜D0,7F、D0,0R〜D0,7Rについて、第1誤り検出符号E0,0F〜E0,3F、E0,0R〜E0,3Rをもとに誤り検出処理を行う。このとき、メインデータD0,2、D0,5のビット対F,Rに対する代入データの代入パターンとしては、メインデータD0,2のビット対F,Rにおける01と10、メインデータD0,5のビット対F,Rにおける01と10とで、計4通り存在する(図11参照)。従って、1バイト内の2ビットのデータエラーは、前記の代入データと第1誤り検出符号Eとをもとに、多くても4回、誤り検出処理を行えば誤りが非検出となり、誤りを訂正することができる(第1誤り訂正処理)。

【0045】

0バイト目の誤り訂正を終え、或は前記ステップF2でYESと判断された場合、7バイト目までの処理を終えていないことから(ステップF4:YES)、前記カウンタNをインクリメントして(ステップF5)、1バイト目のメインデータD1,0F〜D1,7Fについても、メインデータD1,0R〜D1,7Rとの論理和演算の結果に基づき、データエラーとなるビット対F,Rが3つ以上あるか(或はエラーが無いか)を判断する(ステップF2)。そして、上記と同様にビット対F,Rの誤りが2つ若しくは1つ存在すれば、代入データを順次代入して第1誤り検出符号E1,0F〜E1,3F、E1,0R〜E1,3Rをもとに誤りを訂正する処理を行う(ステップF3)。こうして、ステップF2〜F5が繰り返し実行されることにより、1バイト目以降のメインデータDについても1バイトずつ誤り検出処理と誤り訂正処理とが行われ、7バイト目の誤り訂正を終えることにより(ステップF4:NO)、図16のステップE2に移行する。ステップE2において、RW側制御部18は、タグ側メモリ部6cから読込んだ全てのデータについて、上記の誤り訂正処理によりデータエラーが解消されたと判断すると(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。尚、上記ステップF1〜F5では、メインデータDの誤りを訂正する処理について説明したが、第1誤り検出符号Eについては、予めそのビット対F,Rをもとに誤り検出を行い、同じビット位置の列ごとに代入データと第2誤り検出符号Gとに基づく誤り訂正処理を行う(後述のステップI1〜I5参照)。つまり、予め第1誤り検出符号Eの誤り訂正処理を実行した後、ステップF1〜F5を実行するのである。

【0046】

一方、上記メインデータD或は第1誤り検出符号Eのデータについて1バイトに3ビット以上のエラーが含まれ(図16のステップE2:YES)或は他のデータについてエラーが含まれる場合には、データが多重化されているか否かを判断する(ステップE3)。データが多重化されている場合には(YES)、その多重化に係る訂正処理が行われる(ステップE4.図18のステップG1〜G8)。即ち、ステップG1では、多重化したメインデータD´及び第1誤り検出符号E´について、前記ステップE1(つまりステップF1〜F5)と同様に、1バイトずつ誤り検出処理と誤り訂正処理とが行われる。RW側制御部18は、この訂正処理によって、タグ側メモリ部6cから読込んだ全てのデータについてエラーが解消されたと判断すると(ステップG2:YES)、図16のステップE5にリターンする。そして、ステップE5でも、同様にエラーが解消されたものとして(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0047】

RW側制御部18は、図18のステップG2でエラーが解消されていないと判断すると(NO)、バイト数をカウントするためのカウンタNをゼロクリアする(ステップG3)。そして、ステップG4では、本来のメインデータDと多重化したメインデータD´との間で対応するビットごとに論理和演算が行われると共に、第1誤り検出符号Eと多重化した第1誤り検出符号E´との論理和演算との間で対応するビットごとに論理和演算を行う(ステップG4)。例えば図21において上側のメインデータD0,0F〜D0,7Fと、その直ぐ下側の多重化したメインデータD0,0F´〜D0,7F´との間で対応するビットごとに論理和演算を行う。尚、同図では、説明の便宜上、メインデータD0,0R〜D0,7R及びD0,0R´〜D0,7R´を併せて図示している。同図の網掛部分で示すように、メインデータD0,2、D0,6の夫々のビット対F,Rと、多重化したメインデータD0,3、D0,5の夫々のビット対F´,R´とが00となるデータエラーが生じていても、同じビット位置に正しいデータが存在すれば、そのビットの論理和演算の結果、データエラーを修復したビット列を得ることができる。

【0048】

ステップG4の誤り訂正処理の後、RW側制御部18は、メインデータD0,0F〜D0,7Fについて、ビットごとにメインデータD0,0R〜D0,7Rとの論理和演算を行い、演算結果が0となるビット対F,Rが3つ以上有るか、或は演算結果が全て1かを判断する(ステップG5)。ここで、前記ビット列に1つ2つの誤りが含まれていても(NO)、前記代入データと第1誤り検出符号とをもとに誤りが非検出となるまで誤り検出処理を行うことで、誤りは訂正される。

【0049】

この0バイト目誤り訂正を終え、或は前記ステップG5でYESと判断された場合、7バイト目までの処理を終えていないことから(ステップG7:YES)、前記カウンタNをインクリメントして(ステップG8)、1バイト目のメインデータD1,0F〜D1,7Fについて、多重化したメインデータD1,0F´〜D1,7F´との間で対応するビットごとに論理和演算を行う(ステップG4)。そして、その論理和演算から得られたビット列について、上記と同様に2ビット(或は1ビット)の誤りがあれば、代入データを順次代入して誤りを訂正する処理を行う(ステップG5,G6)。こうして、ステップG4〜G8が繰り返し実行されることにより、1バイト目以降のメインデータDについても1バイトずつ誤り検出処理と誤り訂正処理とが行われ、7バイト目の誤り訂正を終えることにより(ステップG7:NO)、図16のステップE5に移行する。ステップE5において、RW側制御部18は、タグ側メモリ部6cから読込んだ全てのデータについて、上記の誤り訂正処理によりデータエラーが解消されたと判断すると(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0050】

上記の多重化に係る誤り訂正処理の後、未だデータにエラーが含まれる場合には(ステップE5:NO)、パリティ符号Pが付加されているか否かを判断する(ステップE6)。パリティ符号Pが付加されている場合には(YES)、そのパリティ符号Pに係る訂正処理が行われる(ステップE7、図19のステップH1〜H8)。即ち、RW側制御部18は、ビット数をカウントするためのカウンタMをゼロクリアして(ステップH1)、訂正の対象となるアドレスのデータ、例えばメインデータD0,0F〜D0,7Fについて誤りを訂正する。具体的には、図9(b)の破線で囲うように、メインデータD0,0Fの示す値0は、隣のデータD0,1Fの示す値1との関係上、奇数パリティ検査(パリティビットP0,0)により、誤りが無いと判断される(ステップH2:NO)。この0ビット目に続いて、1ビット目の処理を行うべくカウンタMをインクリメントし(ステップH3、H4)、メインデータD0,1Fについても上記と同様に奇数パリティ検査を行う(ステップH2)。こうして、ステップH1〜H4が繰り返し実行される過程において、奇数パリティ検査に基づきメインデータD0,6Fに誤りが有ると判断されると(ステップH2:YES、図9(b)参照)、左データたるD0,6Fと左パリティたるP0,5とに誤りが有るか否かが判断される(ステップH5)。両者D0,6F、P0,5に誤りがなければそのパリティビットP0,5をもとにD0,6Fの値が訂正される(ステップH6)。この点、左データD0,6や左パリティP0,5の何れかに誤りが存する場合でも(ステップH5:NO)、右データたるD0,7Fと右パリティたるP0,6とに誤りが無ければ(ステップH7:NO)、そのパリティビットP0,6をもとにD0,6Fの値を訂正することができる(ステップH8)。こうして、7バイト目まで訂正の対象となるアドレスの処理を終えることにより(ステップH3:NO)、図16のステップE8に移行する。ステップE8において、RW側制御部18は、タグ側メモリ部6cから読込んだ全てのデータについて、上記の誤り訂正処理によりデータエラーが解消されたと判断すると(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0051】

上記のパリティ符号に係る誤り訂正処理の後、未だデータにエラーが含まれる場合には(ステップE8:NO)、第2誤り検出符号F,Gが付加されているか否かを判断する(ステップE9)。第2誤り検出符号F,Gが付加されている場合には(YES)、その第2誤り検出符号F,Gに係る誤り訂正処理が行われる(ステップE10、図20のステップI1〜I11)。この誤り訂正処理では、先ず、ビット数をカウントするためのカウンタMがゼロクリアされ(ステップI1)、訂正の対象となるデータについて、同じビット位置の列ごとに誤りを検出する処理が行われる。具体的には例えば、メインデータD0,0F〜D7,0Fの列(図6参照)について、ビット対をなすD0,0R〜D7,0Rの列とビットごとの論理和演算を行い、3ビット以上の誤りが有るか或は誤りが無いかを判断する(ステップI2)。何れの条件も満たさない場合つまり2ビット若しくは1ビットの誤りがあれば(NO)、その誤りが検出されたメインデータD0,0〜D7,0のビット対F,Rに、前記代入データを順次代入して第2誤り検出符号F0,0F〜F3,0F、E0,0R〜E3,0Rをもとに誤りを訂正する処理を行う(ステップI3:第2誤り訂正処理)。

【0052】

0ビット目の誤り訂正を終え、或は前記ステップI2でYESと判断された場合、11ビット目までの処理を終えていないことから(ステップI4:YES)、前記カウンタMをインクリメントして(ステップI5)、1ビット目以降のメインデータDについても同じビット位置の列ごとに、ビット対F,Rに基づく誤り検出処理と(ステップI2)、代入データと第2誤り検出符号Fとに基づく誤り訂正処理を行う(ステップI3)。こうして、ステップI2〜I5を繰り返し実行し、8ビット目(実際には上位のビット)以降は、第1誤り検出符号Eについて、同じビット位置の列ごとにビット対F,Rに基づく誤り検出処理と(ステップI2)、代入データと第2誤り検出符号Gとに基づく誤り訂正処理を行う(ステップI3)。

【0053】

そして、11ビット目の誤り訂正を終えると(ステップI4:NO)、バイト数をカウントするためのカウンタNをゼロクリアして(ステップI6)、今度は、アドレスごとに、ビット対F,Rに基づく誤り検出処理と(ステップI7)、前記代入データと第1誤り検出符号Eとに基づく誤り訂正処理を行う(ステップI8)。この0バイト目の処理を終えると、7バイト目までの訂正処理を行うべく(ステップI9:YES)、前記カウンタNをインクリメントして(ステップI10)、ステップI7にリターンする。そして、1バイト目以降のメインデータDについてもアドレスごとに、ビット対F,Rに基づく誤り検出処理と(ステップI7)、代入データと第1誤り検出符号Eとに基づく誤り訂正処理を行う(ステップI8)。こうして、RW側制御部18は、ステップI7〜I10を繰り返し実行し、7ビット目の誤り訂正を終えると(ステップI9:NO)、全てのデータについてエラーが解消されたか否かを判断する(ステップI11)。ここで、エラーが解消されていなければステップI1にリターンし(NO)、エラーが解消されていれば(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0054】

上記した一連の誤り訂正処理(ステップE1〜E10)、特にはステップE10(ステップI1〜I10)では、そのステップI1〜I5における同じビット位置の列ごとの誤り訂正処理と、ステップI7〜I10におけるアドレスことの誤り訂正処理とが夫々繰り返し実行されため、データエラーをより確実に解消することができる。即ち、例えばメインデータD0,0〜D7,7の各アドレス或は同じビット位置の列に、3ビット以上のバーストエラーが複数箇所に発生していたとする。この場合でも、前記ビット対をもとに当該エラーを確実に検出し、前記代入データと第1及び第2誤り検出符号E及びF,Gとに基づく誤り訂正処理を、アドレスごとに或は同じビット位置の列ごとに繰り返し実行することで、一部のデータが修復されれば、そのデータをもとに他のデータについても連鎖的に修復される。こうして、所謂訂正なだれが発生することで、タグ側メモリ部6cに前述したバーストエラーやランダムエラーが発生した第3段階の状態にあっても、その全てのエラーを訂正することが可能となるのである。

【0055】

以上説明したように、データ管理システム11において、前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対F,Rとして符号化したデータを含み、RW側制御部18は、前記誤り検出処理において、タグ側メモリ部6cから読出したデータについてビット対をなす双方のビットの値が0であれば当該ビット対に誤りが有ると判断する。これによれば、例えば透過放射線によりタグ側メモリ部6cのメモリセルにおいてデータが"1"から"0"に片方向へ変化するデータエラーが生じる状況にあっても、RW側制御部18によって、ビット対F,Rをなす双方のビットが値0であれば、当該ビット対により表現されたデータが誤りであると判定できる。従って、ビット対F,Rをもとにデータエラーを確実且つ簡単に検出することができる。従って、放射線に晒される特殊環境でデータエラーの発生を防止し且つ正常に機能させることが可能なデータ管理システム11を提供することができる。

【0056】

また、RW側制御部18は、前記の片方向へ変化するデータエラーが生じる状況にあっても、ビット対F,Rをなす双方のビットの論理和演算を行い、その演算結果が1であれば前記ビット対に誤りが無く、当該演算結果が0であれば前記ビットに誤りがあると判断する。即ち、ビット対F,Rは01又は10として生成され、何れもF,Rの論理和をとれば必ず1となるが、データエラーが発生すると00になり、その論理和をとれば0となる。従って、RW側制御部18によって、タグ側メモリ部6cに記憶されたデータのエラーを簡単に特定し且つ確実に検出することができ、その処理速度を高めることができる。

【0057】

しかも、前記ビット対F,Rのうち一方のビットFと他方のビットRは、タグ側メモリ部6cにおいて相互に異なるアドレスの同じビット位置に記憶されるため、一層、処理速度を高めることができる。

【0058】

前記冗長データは、1バイトのデータごとに生成される第1誤り検出符号Eと、前記データの同じビット位置ごとに生成される第2誤り検出符号F,Gとのうち、少なくとも何れかの誤り検出符号を含む。従って、RW側制御部18は、前記ビット対F,Rに基づく誤り検出のみならず、第1及び第2誤り検出符号E及びF,Gに基づく誤り検出を行うことができ、誤りをより確実に検出することができると共に誤り訂正処理による訂正確率を高めることができる。

【0059】

RW側制御部18は、前記ビット対F,Rをなす双方のビットの論理和演算に基づき誤りが検出されると、その誤りが検出されたビット対F,Rにデータ0,1(これらは前記代入データ)を代入して前記誤り検出符号をもとに誤り検出処理を行い、誤りが非検出となるまで誤り訂正処理を行う。従って例えば、データエラーが発生しているビット対F,Rが2組(この組数をxとする)あるとき、当該2組のビット対F,Rに対する代入データの代入パターンは計4通り(つまり2x)存在する。よって、その代入データをもとにデータエラーを確実に修復することができる。

【0060】

RW側制御部18は、前記ビット対F,Rをなす双方のビットの論理和演算に基づき誤りが検出されると、誤りが検出されたアドレスごとに前記代入データと前記第1誤り検出符号Eとをもとに誤りが非検出となるまで誤り訂正処理を行う第1誤り訂正処理と、同じビット位置の列ごとに前記代入データと前記第2誤り検出符号F,Gとをもとに誤りが非検出となるまで誤り訂正処理を行う第2誤り訂正処理とを実行する。これによれば、例えば第1誤り訂正処理と第2誤り訂正処理とを繰り返し実行することで、一部のデータが修復されれば、そのデータをもとに他のデータについても連鎖的に修復することができる。よって、タグ側メモリ部6cに前述したバーストエラーやランダムエラーが発生した第3段階の状態にあっても、その全てのエラーを訂正できる確率を高めることができる。

【0061】

RW側制御部18は、タグ側メモリ部6cにデータを書込む際、そのデータを書込むアドレス以外の全てのアドレスのデータを読出して、前記冗長データをもとに誤り検出処理と誤り訂正処理とを行う(前記ステップB1〜B4)。これによれば、タグ側メモリ部6cにデータを書込む度に、当該メモリ部6cの全てのアドレスのデータについて誤りの無いデータを作成することができる。また、当該データエラーが無くても、全てのデータの読出すことにより各メモリセルの電荷の再チャージ、つまりリフレッシュを行うことができ、放射線照射によりフローティングゲート中の電子が失われていたとしても、前記第1段階にある損傷を修復することができる。

【0062】

RW側制御部18は、前記読出したデータについて誤り訂正処理を行った場合は、訂正したデータを前記不揮発性記憶手段に書込むことから(前記ステップB5)、タグ側メモリ部6cにデータを書込む度に、当該メモリ部6cの全てのアドレスのデータについて、誤りを訂正する機会を設けることができる。

【0063】

タグ側メモリ部6cには、複数の異なる領域に同じデータが書込まれてデータが多重化されており、RW側制御部18は、多重化された複数のデータの同一ビット間で、想定されるデータの誤りパターンに応じて論理演算を行い、その演算により得られたビット列について、前記冗長データをもとに誤り検出処理を行った結果、誤りが検出されなければ、当該ビット列のデータが正しいデータであると判断する。

【0064】

これによれば、1バイトのデータのあるビットにデータエラーが生じていても、多重化した他方のデータの対応するビットに正しいデータが存在すれば、当該ビットとの論理和演算の結果、そのビット位置のデータについてエラーを確実に修復することができる。また、前記ビット列について冗長データをもとに誤りが無いことを判断することができ、データ管理システム11の信頼性をより高めることができる。尚、透過放射線等により"0"から"1"の片方向の変化が生じる場合には、前記論理和演算に代えて論理積演算を行うことにより、上記と同様にエラーを修復することができる。

【0065】

RW側制御部18は、前記ビット対F,Rと誤り検出符号E、F,Gとをもとに誤り検出処理及び誤り訂正処理を行い、その訂正処理後のデータに誤りが有ると、多重化された複数のデータ間で対応するビットごとに論理和演算を行う。これによれば、上記の効果に加え、複数種の冗長データR,E,F,G,F´,R´を用いた重畳的な誤り訂正処理により、訂正確率を一層高めることができる。

【0066】

前記冗長データは、データを構成する各ビットに対して、隣り合うビットとの組み合わせについて付加されたパリティ符号Pを含み、(ここも「ビット対」は止めた方が良いのでは)RW側制御部18は、誤り訂正処理において、前記隣り合うビットのうち誤りが無いビットのデータとパリティ符号Pとをもとにビットの誤りを訂正する。これによれば、パリティ符号Pは、前記隣り合うビットの組み合わせに対応して付加されたものであるから、前記冗長データR,E,F,G,F´,R´に基づく訂正処理とは異なる訂正処理を行うことができ、より訂正確率を高めることができる。

【0067】

RW側制御部18は、タグ側メモリ部6cからデータを読出す場合、同じアドレスについて連続して少なくとも2度同じデータを読出すまで、繰り返しデータを読出す。例えば、上記のように通信の際、例えばRFIDタグ10Cのアンテナ2cに照射された放射線によりデータが化ける可能性があるが、連続して少なくとも2度同じデータを読出すまで繰り返しデータを取得することで、タグリーダ/ライタ12A側からのデータ読出し時における化けを確実に防止することができる。

【0068】

上記実施形態では、ハンディ型タグリーダ/ライタ12Aを用いてデータを書込む際に、データの読出し処理から訂正データの書込み処理まで(ステップB1〜B5)を行うこととしたが、例えば据置型タグリーダ/ライタ12Bを用いて、予め設定された所定時間毎にタグ側メモリ部6cからデータを読出すようにしてもよい。ここで、前記所定時間は、放射線量としての放射線強度やその照射期間に応じて設定されるものであり、その放射線環境の下、タグ側メモリ部6cにおいて放射線照射等によりデータ破壊に至る時間よりも短い時間に設定する。そして、放射線量は、放射線源からの距離の2乗に反比例することから、例えばRFIDタグ10Cが放射線源の近くで用いられる場合には、前記パソコン14等の上位装置から比較的短い時間毎(例えば数分ごと)に指示が与えられることに基づき、タグリーダ/ライタ12Bの制御部18によって、ステップB1〜B5を実行するようにしてもよい。

【0069】

尚、高温環境の下でも、放射線環境と同様に、前記の片方向へ変化するデータエラーが生じる虞がある。従って、データエラーに至るメモリ部6a,6cの温度特性等により、前記所定時間を適宜設定してステップB1〜B5を実行することで、上記と同様の効果を得ることができる。

【0070】

この点、アクティブ型のRFIDタグ10Aでも同様に、自身が有するメモリ部6aについて制御部5aが主体となり、前記所定時間毎に、若しくは他に優先する処理の無い時に、ステップB1〜B5を実行するようにしてもよい。即ち、前述したように、RFIDタグ10Aのメモリ部6aには、タグリーダ/ライタ12のメモリ部19と同様の制御プログラムや誤り訂正プログラム等が記憶されると共に、タグ側メモリ部6cと同様の冗長データが記憶されている。従って、RFIDタグ10Aにおいて、制御部5aによりメモリ部6aから読出したデータについてその冗長データをもとに誤り検出処理を行い、その検出処理において誤りが検出された場合には誤り訂正処理を行うことができる。

【0071】

また、アクティブ型のRFIDタグ10Aにおいて、制御部5aは、タグリーダ/ライタ12から前記無線通信手段を介して書込み用データを受信した際、その受信したデータから前記冗長データを生成して前記データと共にメモリ部6aに書込むようにする。そして、タグリーダ/ライタ12へ前記無線通信手段を介してデータを送信する際、その送信するデータに付された冗長データをもとに誤り検出処理と誤り訂正処理とを行うことにより、誤りの無いデータを送信するようにしてもよい。つまり、アクティブ型のRFIDタグ10Aであれば、上記したタグリーダ/ライタ12Bと同様の処理を行うことができることから、自身のメモリ部6aに記憶されるデータ関して冗長データを生成し、或はステップB1〜B5を実行する等してデータを管理することができる。

【0072】

RFIDタグ10A〜10Cは、何れもハンディ型或は据置型タグリーダ/ライタ12A,12B(外部の電子機器)に対するスレーブとして構成されている。従って、上記データ管理システム11の下、RFIDタグ10A〜10Cの信頼性を高めることができる。

【0073】

タグリーダ/ライタ12A,12Bは、RFIDタグ10A〜10Cの何れかのマスタ(電子機器)として構成されていることから、タグリーダ/ライタ12A,12Bを用いて上記データ管理システム11の信頼性を高めることができる。

【0074】

図22〜図30は、第2〜第7実施形態を示すものであり、第1実施形態と同一部分には同一符号を付す等して説明を省略し、以下異なる点につき説明する。

<第2実施形態>

図22は、本発明の第2実施形態を示す図21相当図である。

【0075】

多重化データ記憶領域224には、例えば、メインデータD0,0〜D7,7のビット対F´,R´と同じデータF´´,R´´が書込まれることにより、メインデータD0,0〜D7,7が三重化されている(図22参照)。従って、前記多重化に係る訂正処理における論理和演算(図18のステップG4)では、本来のメインデータDと、多重化したメインデータD´とD´´との間で対応するビットごとに論理和演算が行われる。即ち、図22の網掛部分で示すように、例えばメインデータD0,1、D0,2、D0,6については、三重化による3組のビット対F,R、F´,R´、F´´,R´´のうち、値が00となるデータエラーが生じたビット対が2組ずつ含まれている。このような場合でも、同じビット位置に正しいデータが1つでも存在すれば、そのビットの論理和演算の結果、データエラーを修復したビット列を得ることができる。

【0076】

本実施形態と異なり、上記3組のビット対F,R、F´,R´、F´´,R´´のビット対について多数決に基づきビットごとに誤り訂正をすると、前記第3段階のデータエラーについては、誤りが過半数となって間違った訂正を行う虞がある。これに対し、本実施形態のように論理和演算をもとに誤り訂正を行うことで、同じビット位置に正しいデータが1つでも存在すれば、そのビットに対応する他の2組のビット対のデータエラーを完全に修復することができる。従って、データ管理システム11の信頼性をより高めることができる。尚、多重化は、二重化や三重化に限定されるものではなく、四重化以上のデータを冗長データとして含むようにしてもよい。

【0077】

<第3実施形態>

図23は、本発明の第3実施形態を示す図10(b)相当図である。

前述したように、RW側制御部18は、タグ側メモリ部6cから読出したメインデータD及び第1誤り検出符号Eの各ビット対F,Rについて、一方のビットFと他方のビットRとの論理和演算を行う(前記ステップB2)。そして、本実施形態では、前記ステップS3でビット対F,Rに誤りが有ると判断された場合(YES)、前記ステップS4に代えて、以下のステップを実行する。

【0078】

即ち、図示は省略するが、メインデータDのビット対F,Rに誤りが無く、且つ誤り検出符号(例えば第1誤り検出符号E)のビット対F,Rの誤りか否かを判断する。そして、メインデータDのビット対F,Rに誤りがあれば前記ステップB4へ移行する一方、第1誤り検出符号Eのビット対F,Rにのみ誤りが発生していれば(図23参照)、誤りのないメインデータDのビット対F,Rをもとに、アドレスごとに新たに第1誤り検出符号を生成する。これにより、第1誤り検出符号Eのビット対F,Rの誤りを訂正することができ、その訂正データをタグ側メモリ部6cに書込むのである(前記ステップB5へ移行)。

【0079】

ここで、図23の網掛部分で示すように、メインデータDのビット対F,Rに誤りが無く、且つ第1誤り検出符号E0,0、E0,2のビット対F,Rにのみ誤りが発生するケースも生じ得る。この点、上記したように、第1誤り検出符号Eもビット対F,Rとして符号化されていることから(誤り検出符号用のビット対)、そのビットF,Rの論理和演算を行うことにより、第1誤り検出符号Eにおける誤り検出を確実に行うことができ、誤りの無いメインデータDのビット対F,Rをもとに、誤り訂正処理を確実に行うことができるのである。尚、第2誤り検出符号F,Gもビット対F,Rとして符号化してもよい。

【0080】

<第4実施形態>

図24は、本発明の第4実施形態を示す図23相当図である。

第1実施形態の誤り訂正処理、例えば図17に示すフローチャート(ステップF1〜F5)では、メインデータDをその訂正の対象として、1バイトごとに代入データをもとに誤りを訂正する例を説明した。この点、図24に示すように、メインデータD0,3のビット対F,Rと、第1誤り検出符号E0,2のビット対F,Rとに、夫々誤りが発生するケースも生じ得る。このような場合でも、ビット対F,Rの誤りが2つ以内であれば、該当するメインデータD0,3及び第1誤り検出符号E0,2の夫々のビット対F,Rに代入データを順次代入して、第1誤り検出符号E0,0F〜E0,3Rをもとに誤り検出処理を行い、誤りが非検出となるまで誤り訂正を行うことができる。つまり、誤り訂正処理は、その訂正の対象となる範囲(アドレスやビット位置)について、データの誤りパターン等に応じて適宜設定すればよい。

【0081】

<第5実施形態>

図25は、本発明の第5実施形態を示すものであり、ハンディ型タグリーダ/ライタ12Aを用いてRFIDタグ10Cから前記IDデータを取得する際の処理内容を示すフローチャートである。

【0082】

タグリーダ/ライタ12Aは、その交信領域に存在する複数のRFIDタグ10Cを識別する同時読取り処理が可能に構成されている。第5実施形態では、前述した設備24において搬入・搬出される複数の物品24bに夫々貼付されたRFIDタグ10Cの同時読取りを例とする。また、IDデータは、前述したように前記TID記憶領域200(図5参照)に書換え不能に記憶される一方、IDデータの冗長データが、前記冗長領域220における専用の領域(IDデータ用の冗長領域)に記憶されている。このIDデータ用の冗長データは、IDデータの各ビットが示す1,0の値の何れか一方を01、他方を10として符号化したビット対のうち、他方のビットR(つまり図7中、[ID]DRで示す反転データDR)を含む。また、冗長データは、例えばIDデータの反転データDRの誤りを訂正するための第1誤り検出符号(図7中、[ID]ERで示す)を含む。そして、複数のRFIDタグ10Cの同時読取りに際し、RW側制御部18は、各RFIDタグ10Cにおけるタグ側メモリ部6cのTID記憶領域200からIDデータを夫々読出す(ステップJ1)。尚、以下では1つのRFIDタグ10Cに着目して説明するが、実際には、各RFIDタグ10CについてステップJ1〜J6が夫々実行される。

【0083】

RW側制御部18は、前記ステップJ1の後、タグ側メモリ部6cの前記の冗長領域からIDデータの反転データDRと第1誤り検出符号ERとを読出して(ステップJ2)、IDデータと反転データDRとで対応するビットごとの論理和演算を行う。そして、この演算の結果、各ビットが全て1で無い場合には(ステップJ3:YES)、反転データDRに係る訂正処理を行う(ステップJ4)。この場合、誤りと判断されたビット対Rに、0或は1(代入データ)を順次代入し、当該代入データを代入した反転データDRについて第1誤り検出符号ERをもとに誤り検出処理を行う。こうして、代入データと第1誤り検出符号ERとをもとに誤りが非検出となるまで誤り訂正処理を行うことで、2ビットまでの誤りについては正しい反転データDRを得ることができる。この誤り訂正処理後の反転データDRは、タグ側メモリ部6cに書込まれ(ステップJ5)、反転データDRを反転させたデータは、タグリーダ/ライタ12Aにおいて本来のIDデータとして利用され、当該IDデータに基づき各種の処理が開始される(ステップJ6)。

【0084】

ステップJ3で検出されるエラーは、TID記憶領域200から読み出したIDデータに誤りがある場合と、冗長データ領域から読み出したその反転データDR側に誤りがある場合とがある。前者の場合、ユーザはTID記憶領域200を書き換えることができないので、ステップJ4では反転データDRに係る訂正処理を行う。そして以降は、どちらのデータに誤りがあったかに関係なく、TID記憶領域200から読み出したIDデータではなく、反転データDRを反転させたデータをIDデータとして利用する。

【0085】

以上のようにRW側制御部18は、タグ側メモリ部6cから読出したIDデータについてその冗長データDR、ERをもとに誤り検出処理を行うことから、IDデータについて、第1実施形態と同様の効果を得ることができる。また、IDデータは、RFIDタグ10Cにおける他のデータ(例えば製品コード等の識別情報)と関連付けられていることから、冗長データDR、ERをもとに誤り訂正処理を行うことで、誤り訂正処理後のIDデータと他のデータとを対応させることができ、各種の処理を支障なく実行することができる。尚、IDデータの冗長データは、ビット対Rや第1誤り検出符号ERに限定するものではなく、上記した各種の冗長データをもとに誤り検出処理及び誤り訂正処理を行うことができる。

【0086】

また、第5実施形態と同様に、以下の第6実施形態以降についても、各種の冗長データをもとに誤り検出処理及び誤り訂正を行うことができることから、前記冗長データに基づく誤り検出処理及び誤り訂正処理について冗長データの符号を省略する等、その詳細な説明を省略する。

【0087】

<第6実施形態>

図26〜図28は本発明の第6実施形態を示す。図26は、図4(a)に示すRFIDタグ10Aにおけるメモリ部6aのマップイメージに示した3種類の誤り訂正プログラムである、主誤り訂正プログラム,副誤り訂正プログラム及び簡易誤り訂正プログラムが、それぞれ誤り訂正を行う対象を示している。主誤り訂正プログラムが誤り訂正を行う対象は、データ領域101と、自身を除く一般プログラム領域102,副誤り訂正プログラム領域104及び簡易誤り訂正プログラム領域105であり、副誤り訂正プログラムが誤り訂正を行う対象は、主誤り訂正プログラム領域103のみである。

【0088】

主,副誤り訂正プログラムは、全く同じ内容のプログラムであり、スタートアップ時の初期設定において、一方が主,他方が副として動作するように指定されることで、誤り訂正を行う領域(アドレスの範囲)が決定される。主,副誤り訂正プログラムは、上記各実施形態においてデータ領域101のデータについて行った誤り検出・誤り訂正と同様の処理を、プログラム領域102〜105の各プログラムについて行うようになっている。

【0089】

また、簡易誤り訂正プログラムが誤り訂正を行う対象は、主誤り訂正プログラム領域103及び副誤り訂正プログラム領域104となっている。簡易誤り訂正プログラムは、主又は副誤り訂正プログラムが実行された結果、実行中である自身のプログラムに誤りが検出された場合に起動され、誤りがある方の訂正プログラムにおいて誤りが検出されたアドレスに、誤りが無い方の訂正プログラムにおいて対応するアドレスの内容をコピーすることで修復する。各プログラムは、例えばマルチタスクOS(オペレーティング)上で動作するようになっており、そのマルチタスクOSがタスクスイッチングを行うことで各プログラムの実行状態が切り替えられる。

【0090】

次に、第6実施形態の作用について図27及び図28を参照して説明する。図27は、主又は副誤り訂正プログラムによる処理内容を示すフローチャートである。タスクスイッチングにより主又は副何れかの誤り訂正プログラムが指定されて起動されると(ステップK1)、主,副のそれぞれに応じて、訂正対象とするアドレス領域を取得する(ステップK2)。ここでは、訂正対象とする各プログラム領域102〜105又はデータ領域101と、対応する冗長データの領域とを一括して読出す。そして、訂正の対象がデータ領域101である場合は(ステップK3:NO)、誤り検出処理を行う(ステップK7)。ここで誤りが検出されなければ(ステップK8,NO)、ステップK2に戻る。

【0091】

一方、ステップK3において訂正の対象がプログラム領域101〜105の何れかであり(YES)、それが自分自身のプログラム領域でなければ(ステップK4:NO)、訂正を行うため、動作を停止させる必要があるプログラムか否かを判断する(ステップK5)。すなわち、主誤り訂正プログラムが動作している場合は一般プログラム又は副誤り訂正プログラムか否か、副誤り訂正プログラムが動作している場合は主誤り訂正プログラムか否かを判断する。これらのプログラムである場合は(YES)、そのプログラムの起動を停止させる(ステップK6)。尚、ステップK5,K6の処理は、例えばマルチCPU等の構成において、複数のプログラムが並行して実行される可能性がある場合に必要な処理であり、シングルCPUにおいてタスクスイッチングを実行する場合には不要である。

【0092】

そして、ステップK7を実行した結果、誤りが検出されると(ステップK8:YES)、訂正対象が主又は副誤り訂正プログラムか否かを判断し(ステップK9)、訂正対象がデータ領域101であれば(NO)冗長データに基づいて誤り訂正処理を行う(ステップK15)。一方、訂正対象が主又は副誤り訂正プログラムである場合は(YES)、冗長データに基づく通常の訂正処理が可能か否かを判断し(ステップK10)、可能であれば(YES)ステップK15に移行する。尚、各プログラムについて用意する冗長データは、データ領域101のデータと同様に、ビット対,パリティ符号,多重化データ,誤り検出符号等であり、誤り検出及び誤り訂正は、データ領域101のデータと同様に実行すれば良い。

【0093】

ステップK10において、主又は副誤り訂正プログラムの通常訂正処理が不能であれば(NO)、自身のプログラムについて冗長データに基づき誤り検出処理を行う(ステップK11)。そして、誤りが無ければ(ステップK12:NO)、ステップK8で検出された対象プログラムの誤り検出アドレスに、自身のプログラムの対応するアドレスの内容を書き込んでコピーする(ステップK13)。一方、誤りがあれば(YES)、簡易誤り訂正プログラムを起動する(ステップK14)。

【0094】

図28は、簡易誤り訂正プログラムの処理内容を示すフローチャートである。先ず、主誤り訂正プログラムについて誤りが生じたアドレスを検出すると(ステップL1)、そのアドレスに対応する副誤り訂正プログラムのアドレスの内容を検出する(ステップL2)。尚、ステップL1におけるアドレスの検出は、例えばステップK12で誤りが検出された場合に、主又は副誤り訂正プログラムが、そのアドレス値を所定の領域に書き込んで記憶させておき、簡易誤り訂正プログラムがその領域を読出すことで行っても良い。また、簡易誤り訂正プログラムが、主誤り訂正プログラムについて冗長データに基づき改めて誤り検出を行っても良い。

【0095】

続くステップL3において、副誤り訂正プログラムの対応するアドレスの内容に誤りが無ければ(NO)、当該アドレスの内容を主誤り訂正プログラムの誤りが生じたアドレスにコピーして、主誤り訂正プログラムを修復する(ステップL4)。以降のステップL5〜L8については、ステップK12において副誤り訂正プログラム側に誤りが検出された場合に、対応する主誤り訂正プログラムのアドレスの内容によって副誤り訂正プログラムを修復する処理である。ステップL3,L7において、副誤り訂正プログラム,主誤り訂正プログラムに誤りがあった場合は(YES)、相手側のプログラムを修復することができないので処理を終了する。

【0096】

ここで、RFIDタグ10Aが、放射能や宇宙線等の被曝環境下や高温環境下に配置されている場合には、メモリ部6aのプログラム領域102〜105に配置されている各プログラムについても、データ領域101に配置されているデータに等しい確率で誤りが発生する。そこで、第6実施形態では、上述のように主,副,簡易誤り訂正プログラムが動作することで、一般プログラムに誤りが生じた場合の訂正・修復を図っている。すなわち、一般プログラム,副及び簡易誤り訂正プログラムに誤りが発生すると、その誤りは主誤り訂正プログラムによって訂正され、主誤り訂正プログラムに誤りが発生すると、その誤りは副誤り訂正プログラムによって訂正される。

【0097】

更に、主,副誤り訂正プログラムの一方に、冗長データでは訂正できない誤りが発生し、且つ他方のプログラムにも誤りが発生している場合には、簡易誤り訂正プログラムが起動されて、他方のプログラムの誤りが発生していない部分により修復が可能であれば、当該部分を一方の側にコピーして修復を図る。主,副誤り訂正プログラムは同一内容のプログラムであり、双方で同じプログラムステップに相当するアドレスに、同時に誤りが発生する確率は極めて低い。したがって、これらの作用により3重に誤り訂正を行うことが可能となっている。

【0098】

ここでプログラムとして実行されるオブジェクトコードは、ビット対F,Rの片側、即ち、0を01、1を10とした元のプログラムと同じ値の側である。

以上のように第6実施形態によれば、RFIDタグ10Aにおけるメモリ部6aに、一般プログラムと共に、主誤り訂正プログラム,副誤り訂正プログラム及び簡易誤り訂正プログラムを配置し、データ領域101には、これらの各プログラムについて誤り訂正を行うための冗長データを配置する。そして、主誤り訂正プログラムは、一般プログラム,副及び簡易誤り訂正プログラムに発生した誤りを訂正し、副誤り訂正プログラムは、主誤り訂正プログラムに発生した誤りを訂正し、主,副誤り訂正プログラムの一方に、冗長データでは訂正できない誤りが発生し、且つ他方のプログラムにも誤りが発生している場合には、簡易誤り訂正プログラムによって、主,副誤り訂正プログラム中の誤りが発生していない部分を他方にコピーして修復するようにした。したがって、RFIDタグ10Aが、放射能や宇宙線等の被曝環境下や高温環境下に配置されている場合でも、一般プログラムに発生した誤りを極めて高い確率で訂正することができる。

【0099】

尚、上記の誤り検出・誤り訂正処理については、タグリーダ/ライタ12Aにおいても、図4(b)に示すメモリ部19のプログラム領域303〜305に、同様の主,副,簡易誤り訂正プログラムが配置されているので、プログラム領域302〜305及びデータ領域301について同様の処理が行われる。

【0100】

<第7実施形態>

図29及び図30は、本発明の第7実施形態を示す。図29は図6(a)相当図であり、ここではメインデータ領域210と、第1誤り検出符号(第1冗長データ)領域221に代わる第3冗長データ領域223とを示しており、第1誤り検出符号E,第2誤り検出符号F,Gとは異なる第3誤り検出符号データを用いる場合を説明する。図29及び図30に示す各ビットの図示パターン(網掛け等)は、同じパターンのビットが同じビット列に属することを示している。

【0101】

例えば図29では、1アドレス増加する毎に、ビット位置を1ビットずつずらしたビットをとることで、8ビットを組み合わせたビット列を構成し、その8ビットデータについて4ビットの誤り検出符号を付加する(第3誤り検出符号)。例えば、データD0,0、D1,1、D2,2、〜D7,7が同一のビット列に属しており、このビット列に対して、同様に、アドレスが増加する毎にビット位置を1ビットずつずらした配列で、冗長データE0,0、E1,1、E2,2、E3,3が生成されている。また、第2ビットのデータD0,1から始まるビット列については、末尾のビットは第1ビットのデータD,0となり、第3ビットのデータD0,2から始まるビット列については、7ビット目は第1ビットのデータD6,0,末尾のビットは第2ビットのデータD7,1となる。

【0102】

図30では、2アドレスが増加する毎に、ビット位置を1ビットずつずらしたビットをとることで、8ビットを組み合わせたビット列を構成している。例えば、データD0,0、D2,1、D6,3、D0,4、D2,5、D4,6、D6,7が同一のビット列に属しており、このビット列に対して、同様に、2アドレスが増加する毎にビット位置を1ビットずつずらした配列で、冗長データE0,0、E2,1、E4,2、E6,3が生成されている。すなわち、「アドレスが増加する毎に」と言ってもその範囲は1ワードのデータビット数で制限され、最初のビットを取得するアドレスから「+7」を超えることはなく、「+7」を超える分は「8」を減じたアドレスに折り返される。

【0103】

第3誤り検出符号を付すためのビット列を構成するパターンは、図29,図30に示すものに限らない。例えば1アドレスが増加する毎に、ビット位置を2ビットずつ,或いは3ビットずつずらしたビットをとっても良い。

【0104】

また、図29,図30では説明の都合上、第3冗長データ領域223を図6(a)に示す第1冗長データ領域221に置き換えて示しているが、実際にはこれらは異なるデータ領域であり独立に存在するので、第3誤り検出符号は、第1,第2誤り検出符号と併用して誤り検出に使用することが可能である。そして、第3冗長データ領域223については、必ずしも対応するビット列と同様の配列にする必要はなく、例えば第1誤り検出符号と同様の配列にしても良い。

【0105】

以上のように、第7実施形態によれば、アドレスが増加する毎にビット位置を1ビット以上ずつずらしてなるビット列について、第3誤り検出符号を付すようにした。これにより、データ領域210において、通常のデータ配列について誤りが連続するバースト誤りが発生しているとしても、上記のビット列に関しては、誤りが生じているビットの数を少なくすることができる。したがって、第3誤り検出符号に基づき誤り検出を行い、誤りを訂正すれば、より多くの誤りを訂正できる可能性を向上させることができる。

【0106】

本発明は上記し且つ図面に記載した実施形態にのみ限定されるものではなく、上記したデータ管理方法について、制御部によりデータの読取り及び書込みが行われる不揮発性記憶手段を備えた各種のメモリ装置に適用することができる。

【0107】

上記実施形態のタグリーダ/ライタ12は、タグ側メモリ部6cから読出したデータについて誤り検出処理や誤り訂正処理を行う構成としたが、自身のメモリ部19に係るデータについて誤り検出処理や誤り訂正処理を行うようにしてもよい。即ち、タグリーダ/ライタ12も、内蔵するマスタ側記憶手段たるメモリ部19に、前記データエラーが頻発する環境下で用いるケースも想定されることから、データと共に当該データの誤りを訂正するための冗長データを記憶させておく。そして、冗長データとして上記実施形態と同様のビット対等を用いて誤り検出処理や誤り訂正処理を行うことにより、タグリーダ/ライタ12についても、データエラーの発生を防止し且つ正常に機能させることができる。

【0108】

また、マスタ側記憶手段たるメモリ部19において、前述した主誤り訂正プログラム及び副誤り訂正プログラム、並びにこれらの誤り訂正プログラムの誤りを訂正するための冗長データ等について、タグリーダ/ライタ12自身が正常に機能するためのデータとして構成することで、タグリーダ/ライタ12もRFIDタグ10Cと同様に信頼性を高めることができる。

【0109】

ここで、例えばハンディ型タグリーダ/ライタ12Aの電源が投入された時、制御部18は、メモリ部19から読出したデータのうち少なくとも当該制御部18により実行される制御プログラムについてその冗長データをもとに誤り検出処理を行うように構成する。これによれば、メモリ部19にデータエラーが発生していても、制御プログラムを実行する前に、そのプログラムの誤りを優先的に検出して訂正することができ、正常に起動させることができる。

【0110】

また、アクティブ型のRFIDタグ10Aの電源が投入された時、制御部5aは、自身のメモリ部6aから読出したデータのうち少なくとも当該制御部5aにより実行される制御プログラムについてその冗長データをもとに誤り検出処理を行うように構成する。これによれば、RFIDタグ10Aにおいて、上記と同様に制御プログラムを実行する前に、そのプログラムの誤りを優先的に検出して訂正することができ、正常に起動させることができる。

【0111】

例えば前記RFIDタグ10Cは別個に、他のRFIDタグ10Cを備え、ビット対F,Rのうちの一方のビットFを、一方のRFIDタグ10Cのタグ側メモリ部6cに書込み、他方のビットRを、他方のRFIDタグ10Cのタグ側メモリ部6cに書込む。そして、RW側制御部18は、双方のタグ側メモリ部6c,6cからデータを読出することにより、ビット対F,Rに基づく誤り検出処理を行う。これによれば、一方のタグ側メモリ部6cには本来のデータが記憶され、そのデータを反転した反転データが他方のタグ側メモリ部6cに記憶されることから、一対のRFIDタグ10Cを用いて第1実施形態と同様の効果を得ることができる。

【0112】

RFIDタグ10の種類10A〜10Cとタグリーダ/ライタ12の種類12A,12Bとの各組合わせ(図2参照)に応じて、RFIDタグ10A側が主体となり、或はタグリーダ/ライタ12A,12B側が主体となって、上記した各種の処理を実行することで、RFIDタグ10とタグリーダ/ライタ12との双方について信頼性を高めることのできるデータ管理方法を提供することができる。

【0113】

また、前記ハミング符号の他、拡張ゴレイ符号を用いて誤り検出処理を行い、或は誤り訂正処理を行うようにしてもよい。具体的には、例えば12ビットのメインデータに対して、エラー訂正用ビットの数を12として24ビットの符号語に置き換える拡張ゴレイ符号を形成する。この場合、7ビット誤り検出機能を備えるか、或は4ビット誤り検出機能及び3ビット誤り訂正機能を備える等、適宜設定することができる。よって、ハミング符号に比し、多くの記憶領域が必要となるが、誤り検出機能或は誤り訂正機能を高めることができる。

【0114】

上記したデータ管理システム11或はデータ管理方法は、制御部によってデータの読取り及び書込みが行われる不揮発性記憶手段を有する電子機器や記憶装置一般に適用できるものである。即ち、電子機器や記憶装置としては、データ及びプログラムと共に当該データ等の誤りを訂正するための前記冗長データが記憶された不揮発性記憶手段と、前記不揮発性記憶手段に対するデータの読取り及び書込みを制御する制御部とを備えたものであればよい。従って、電子機器や記憶装置としては、マスタとスレーブとの関係にあるRFIDタグやタグリーダ/ライタに限定するものではなく、パソコンや他の通信機器等において、上記した各種の冗長データをもとに誤り検出処理や誤り訂正処理を行うことで、各実施形態と同様の効果を得ることができる。

【0115】

この他、本発明は、上記ステップD1〜D3の処理を省略したりする等、適宜変更して実施することができ、これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0116】

図面中、2a〜2cはアンテナ(無線通信手段)、5a〜5cはスレーブ側制御部、6a〜6cは不揮発性記憶手段、7a〜7cは通信部(無線通信手段)、10,10A〜10CはRFIDタグ(スレーブ、記憶装置)、11はデータ管理システム、12,12A,12Bはタグリーダ/ライタ(マスタ、電子機器、記憶装置)、18はマスタ側制御部、20は通信部(無線通信手段)、22はアンテナ(無線通信手段)を示す。

【技術分野】

【0001】

本発明は、スレーブ側電子機器とマスタとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システム、データ管理方法、RFIDタグ及びタグリーダ/ライタに関する。

【背景技術】

【0002】

上記RFID(Radio Frequency Identification)タグは、アンテナと当該アンテナに電気的に接続されたIC(Integrated Circuit)チップ等のRFID回路とを備えており、RFID回路に内蔵されたメモリ部に対して、アンテナを通じてタグリーダ/ライタにより非接触で情報の書込み及び読取りが行われるようになっている。この場合、RFIDタグは、マスタたるタグリーダ/ライタに対するスレーブとして、RFIDシステムを構成するもので、近年では商品の管理や物品の履歴のトレーサビリティー等を目的として様々な分野で導入されつつある。

【0003】

ところで、RFIDタグにおいてはその寿命等に起因して、メモリ部に記憶されたデータの異常、つまりデータエラーが発生することがある。そこで、例えば、特許文献1のRFIDタグでは、CRCチェックコードを用いてデータエラーを検出し、ECCチェックチェックコードをもとに、1ビットのエラーを訂正して正しいデータを復元するようになっている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−250426号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

一方、近年では、原子力発電所等の放射線被曝環境下においても、RFIDタグによる種々の管理を行うことで事故の未然防止を図ることが要請されている。しかしながら、引用文献1のようにデータエラーの訂正が可能RFIDタグでも、放射線によりデータエラーが発生する惧れがあるような特殊環境の下では、RFIDタグを使用することはできない。つまり、RFIDタグが放射線に晒されると、その放射線の照射時間の経過に伴いメモリ部におけるデータエラーが蓄積される。また、放射線量によっては、メモリ部にて複数ビットにわたる連続したバーストエラーが発生する虞もあり、1ビットのエラー訂正はもとより、データエラーの検出すらできない事態も生じうる。特許文献1では、放射線或は宇宙線に晒されるような特殊環境においてRFIDタグを使用することは想定されておらず、特許文献1のような対処では上記の特殊環境でRFIDタグを用いることは困難である。

【0006】

本発明は上記事情に鑑みてなされたものであり、その目的は、放射線に晒されるような特殊環境でデータエラーを確実且つ簡単に検出することができ、データエラーの発生を防止することができるデータ管理システム、データ管理方法、RFIDタグ及びタグリーダ/ライタを提供することである。

【課題を解決するための手段】

【0007】

上記した目的を達成するために、本発明のデータ管理システムは、マスタとスレーブとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システムにおいて、前記スレーブは、データと共に当該データの誤りを訂正するための冗長データが記憶された不揮発性記憶手段と、当該スレーブ全体の制御を行うスレーブ側制御部とを備え、前記マスタは、前記無線通信手段を介したデータの読出し及び書込みを制御するマスタ側制御部を備え、前記スレーブ側制御部又は前記マスタ側制御部によって、前記不揮発性記憶手段から読出したデータについて前記冗長データをもとに誤り検出処理を行い、その検出処理において誤りが検出された場合には誤り訂正処理を行う構成にあって、前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対として符号化したデータを含み、前記スレーブ側制御部又は前記マスタ側制御部は、前記誤り検出処理において、前記不揮発性記憶手段から読出したデータについて前記ビット対をなす双方のビットの値が0であれば前記ビット対に誤りが有ると判断することを特徴とする。

【発明の効果】

【0008】

例えば透過放射線により、不揮発性記憶手段においてデータが"1"から"0"に片方向へ変化するデータエラーが生じる状況にあるとする。この場合、前記スレーブ側制御部又はマスタ側制御部によって、ビット対をなす双方のビットが値0であれば、当該ビット対により表現されたデータが誤りであると判定でき、ビット対をもとにデータエラーを確実且つ簡単に検出することができる。従って、放射線に晒される特殊環境でデータエラーの発生を防止することができ、データ管理システムとして正常に機能させることができる。よって、原子力産業や航空・宇宙産業等において、安全性及び信頼性を確保しつつ、設備の保守、作業効率化やトレーサビリティーの確立等を実現することができるデータ管理システムを提供できる。

【図面の簡単な説明】

【0009】

【図1】第1実施形態のデータ管理システムを概略的に示す全体図

【図2】RFIDタグとタグリーダ/ライタの種類、並びにこれらの組合わせを説明するための図

【図3】(a)はアクティブ型のRFIDタグの電気的構成を示し、(b)は、パッシブ型のRFIDタグ及びタグリーダ/ライタの電気的構成、並びにデータ管理システムの概略を示すブロック図

【図4】(a)及び(b)は、アクティブ型のRFIDタグ及びタグリーダ/ライタにおけるメモリ部の夫々のマップイメージを示す図

【図5】パッシブ型のRFIDタグにおけるメモリ部のマップイメージを示す図

【図6】(a)並びに(b)は、メインデータ及び第1誤り検出符号、並びに第2誤り検出符号を説明するための図

【図7】RFIDタグにおけるメモリ部のメモリマップを示す図

【図8】メインデータ及び第1誤り検出符号の夫々のビット対と、各ビット対における実際の使用アドレスの例を説明するための図

【図9】パリティ符号を用いた誤り検出処理と誤り訂正処理を説明するための図

【図10】(a)はビット対として符号化したデータを示す図、(b)は、ビット対として符号化したメインデータ及び第1誤り検出符号の一例を示す図

【図11】データが1から0に片方向へ変化するエラーと、代入データの代入パターンの一例を示す図

【図12】データを書込む場合における全体の処理の流れを示すフローチャート

【図13】データを読出す場合における全体の処理の流れを示すフローチャート

【図14】同じアドレスについて連続してデータを読出す処理の一例を示すフローチャート

【図15】関連データ読込み処理の流れを示すフローチャート

【図16】各冗長データを用いた誤り訂正処理の流れを示すフローチャート

【図17】第1誤り検出符号に係る誤り訂正処理の流れを示すフローチャート

【図18】多重化に係る誤り訂正処理の流れを示すフローチャート

【図19】パリティ符号に係る誤り訂正処理の流れを示すフローチャート

【図20】第1誤り検出符号及び第2誤り検出符号に係る誤り訂正処理の流れを示すフローチャート

【図21】二重化したデータに基づく誤り訂正処理を説明するための図

【図22】第2実施形態を示すもので、三重化したデータに基づく誤り訂正処理を説明するための図

【図23】第3実施形態を示す図10(b)相当図

【図24】第4実施形態を示す図23相当図

【図25】第5実施形態を示すもので、IDデータに関する誤り訂正処理の流れを示すフローチャート

【図26】第6実施形態を示すもので、各種の誤り訂正プログラムについて、夫々の誤り訂正を行う対象を説明するための図

【図27】主又は副誤り訂正プログラムによる処理内容を示すフローチャート

【図28】簡易誤り訂正プログラムの処理内容を示すフローチャート

【図29】第7実施形態を示す図6(a)相当図

【図30】図29相当図

【発明を実施するための形態】

【0010】

<第1実施形態>

以下、本発明の第1実施形態について、図1〜図21を参照しながら説明する。

図1に示すように、データ管理システム11は、所謂データ担体或はデータキャリアとしてのRFIDタグ10と、このRFIDタグ10と非接触でデータの交信を行うタグリーダ/ライタ12と、このタグリーダ/ライタ12に通信回線13aで接続されたパソコン14と、パソコン14に通信回線(通信ネットワーク)13を介して接続されたサーバ15とから構成されている。

【0011】

図2に示すように、前記RFIDタグ10は、電源を内蔵し内部回路の動作電力と電波を返送する電力に内部の電源を用いるアクティブ型のRFIDタグ10Aと、内部回路の動作電力にのみ内部の電源を用い、電波を返送する電力には外部から受信した電波をエネルギー源として動作するセミパッシブ型のRFIDタグ10Bと、内部に電源を内蔵せず、外部から受信した電波をエネルギー源として動作するパッシブ型のRFIDタグ10Cとに大別される。RFIDタグ10A〜10Cはマスタたるタグリーダ/ライタ12に対するスレーブであって、当該タグ10A〜10Cには夫々、スレーブ側制御部と、データを記憶するための不揮発性記憶手段とが内蔵されている。

【0012】

具体的には、例えば図3(a)に示すRFIDタグ10Aは、例えば基板1aに実装されたアンテナ2a、RFID回路3a、電源(電池4a)等を備えている。アンテナ2aは、RFID回路3aに対して電気的に接続されている。RFID回路3aは、制御部5aを主体として、これに接続されるメモリ部6a、通信部7a及び外部インターフェイス(I/F)部8a等から構成されている。外部I/F部8aには、外部環境を検出するための検出手段としてセンサ部9aが接続されている。センサ部9aとしては、例えば温度センサ、放射線センサ、振動センサ、音センサ等、RFIDタグ10Aの用途に応じて各種の検出手段を用いることができる。

【0013】

前記不揮発性記憶手段としてのメモリ部6aは、通信部7aや、センサ部9a、外部検出手段等から得たデータを書換え可能に記憶する。図4(a)に示すように、メモリ部6aには、制御部5aにより実行される制御プログラムを含む一般プログラム等が記憶されたプログラム領域100、前記データと共に当該データの誤りを訂正するための冗長データが記憶されたデータ領域(ユーザ領域)101等の複数の記憶領域が設けられている。プログラム領域100には、前記一般プログラム用の記憶領域102の他、後述の主誤り訂正プログラム、副誤り訂正プログラム、簡易誤り訂正プログラム用の記憶領域103〜105が設けられている。また、詳しくは後述するように、冗長データは、ビット対に係るデータ、誤り検出符号、パリティ符号等の付加データを含む。

【0014】

制御部5aは、RFIDタグ10A全体の制御を司るスレーブ側制御部として、例えばMPU(Micro Processing Unit)から構成されている。通信部7aは、アンテナ2aで受信した電波に含まれるデータ信号が伝達されると、そのデータ信号を元のデータに復調する処理を行うもので、アンテナ2aと共に無線通信手段を構成する。制御部5aは、タグリーダ/ライタ12からの命令(コマンド)の内容に従って、制御プログラムに基づきメモリ部6aの記憶内容の書換え或は書込み等を行う。また、制御部5aは、タグリーダ/ライタ12からのコマンドの内容に従い、メモリ部6aに保存しているデータを送信するための制御を通信部7aに対して行い、メモリ部6aから取出されたデータにより、通信部7aにおいて所定の周波数帯の搬送波が変調され、アンテナ2aからタグリーダ/ライタ12側に送信される。

【0015】

一方、図3(b)に示すRFIDタグ10Cはパッシブ型であり、上記RFIDタグ10Aと異なり、電池4a、外部I/F部8a、センサ部9a等が省略されている。以下、相違点につき簡単に説明すると、RFIDタグ10Cは、例えばPETフィルムからなるフィルム基材1cに実装されたアンテナ2c及びRFID回路3cを備えている。RFID回路3cは、制御部5c、メモリ部6c及び通信部7cと、アンテナ2cで受信した電波から電源電圧を生成する電源電圧発生部4cとの機能をワンチップ化したICチップであって、電源電圧発生部4cで得た電源電圧に基づいて動作する。

【0016】

図5に示すように、メモリ部6cには、RFIDタグ10C固有のIDデータを含む識別データが記憶されるTID記憶領域200、RFIDタグ10Cの貼付対象物に関する電子製品コード(Electronic Product Code)等が記憶されるEPC記憶領域201、通信部7c等から得た各種のデータと共に当該データの誤りを訂正するための冗長データが記憶されたデータ領域(ユーザ領域)202等の複数の記憶領域が設けられている。前記IDデータは、RFIDタグ10Cが本来有するIDであって、TID記憶領域200に書換え不能に記憶されている。

【0017】

制御部5cは、ハードロジック回路からなり、タグリーダ/ライタ12との交信時において、メモリ部6cへの書込みを行う処理や、メモリ部6aに保存しているデータを送信するため処理等、所定の処理を行うようになっている。

【0018】

尚、上記RFIDタグ10Cの制御部5cはCPUを用いて構成してもよい。また、RFIDタグ10Bについては、電池4b(図2参照)を内蔵する一方、タグリーダ/ライタ12から受信した電波をエネルギー源として電波を発するセミパッシブ型であり、その詳細な説明を省略することとする。

【0019】

前記タグリーダ/ライタ12は、上記RFIDタグ10A〜10Cに対するマスタとして構成された読み書き装置である。即ち、図3(b)に示すように、タグリーダ/ライタ12は、基板17に実装されたマスタ側制御部(制御部18)を主体として、これに接続されるメモリ部19、通信部20及び外部I/F部21を備えている。通信部20は、アンテナ22と共に無線通信手段を構成しており、外部I/F部21は、前記パソコン14等の上位装置に接続されている。詳細には、タグリーダ/ライタ12としては、ハンディ型タグリーダ/ライタ12A、或は据置型タグリーダ/ライタ12Bが用いられ(図1、図2参照)、パソコン14との間で無線通信、或は通信回線13aを介した通信を行う。

【0020】

タグリーダ/ライタ12のメモリ部19には、RFIDタグ10Aのメモリ部6aと同様に(図4参照)、制御部18により実行される制御プログラムを含む一般プログラム等が記憶されたプログラム領域300、データと共に当該データの誤りを訂正するための冗長データが記憶されたデータ領域(ユーザ領域)301等の複数の記憶領域が設けられている。プログラム領域300には、前記一般プログラム用の記憶領域302の他、後述の主誤り訂正プログラム、副誤り訂正プログラム、簡易誤り訂正プログラム用の記憶領域303〜305が記憶されている。

【0021】

そして、制御部18は、一般プログラム記憶領域302の制御プログラムに基づいて、通信指令を通信部20に対して行うことにより、通信部20にて送信データを用いて変調した所定周波数の電波信号をアンテナ22から送信する送信処理と、アンテナ22で受信した電波信号より元のデータを復調する受信処理とを行う。

【0022】

尚、RFIDタグ10A〜10Cのメモリ部6a〜6c、並びにタグリーダ/ライタ12A,12Bのメモリ部19は、何れもフローティングゲートに電荷を保持することでデータを記録するタイプのメモリである。即ち、このようなメモリとしては、フラッシュメモリやEEPROM(Electrically Erasable Programmable ROM)等、各種の不揮発性の半導体メモリを使用してもよく、メモリ部6a〜6c、19は不揮発性記憶手段として構成されている。

【0023】

前記パソコン14は情報処理/操作装置であって、その操作入力による指示データ等が通信回線13a或は無線通信を介してタグリーダ/ライタ12へ出力され、タグリーダ/ライタ12から上記したRFIDタグ10に係るデータがパソコン14へと出力される。

【0024】

ここで、図1では、データ管理システム11を、例えば熱中性子炉等の原子力施設のように放射線に晒される設備24の保全管理に適用した一例を示している。当該設備24には、流路を形成する配管24aの温度を検出するための温度センサを配したRFIDタグ10Aや、設備24における放射線量を検出するための放射線センサを内蔵したRFIDタグ10Aが設けられている。また、設備24に対して搬入・搬出される物品24bや、作業者のヘルメット24cにRFIDタグ10Cが貼付される等、様々な管理ポイントに対応したRFIDタグ10が設けられている。パソコン14は、例えば設備24から隔離された操作室に配置され、通信回線13を介してサーバ15への指示やサーバ15からの応答等、種々のデータのやり取りが行えるようになっている。サーバ15のデータベース15aには、例えば設備24や物品24bの管理番号、点検/交換履歴、前記の各センサで検出されたデータ等、設備24に係る各種データが記憶されており、サーバ15からの呼び出しに応じてデータの取得、参照が行われ、または必要に応じてデータが書込まれる。

【0025】

上記データ管理システム11において、ハンディ型或は据置型タグリーダ/ライタ12A,12Bを用いて、設備24から離れた位置でRFIDタグ10A〜10Cから各種の情報を得ることができる。また、RFIDタグ10A〜10Cに係る各種情報がデータベース15aによって総合的に管理され、パソコン14により取得した情報を分析、把握することができる。そして、例えばRFIDタグ10の温度センサから得られた温度データに基づいて、その温度の上昇傾向が識別される場合には、当該温度データが正常値の範囲内であっても、パソコン14での画面や音声等を通じてシステム管理者に注意を喚起する。また、これと同様に、振動、放射線、音等のセンサ情報について夫々正常なデータの範囲内であっても、通常時のデータと異なる傾向を示す場合には、パソコン14等の報知手段により報知する等して、異常が顕在化する前の注意喚起を行うことができる。従って、設備24や機器の温度、放射線レベル等を集約監視することができ、設備24等において異常が顕在化する前のメンテナンスを行うことができると共に、トレーサビリティーの確立と、保全管理の効率化を図ることができる。

【0026】

さて、上記のような放射線環境下では、RFIDタグ10或はタグリーダ/ライタ12において、透過放射線によりデータエラーが発生する事態が想定される。具体的には、例えばRFIDタグ10Cのメモリ部6cにおいてマトリクス状に配列されたメモリセルのフローティングゲートに注入された電子(電荷)量が、例えばガンマ線の入射に基づく光電効果等に起因して低減する。この場合、メモリセルにおいて例えばデータが"1"から"0"に片方向へ変化するデータエラーが生じる虞があり、その損傷の度合いは、次の第1段階〜第3段階に分類される。

(第1段階)前記メモリセルの電子に対する放射線の衝突により損傷が発生しており、更なる放射線の衝突によりデータエラーに至る可能性がある段階。

(第2段階)メモリセルにおいて例えば8ビットからなるワードデータのうち1ビットのデータエラーが発生している段階。

(第3段階)メモリ部6cの損傷の度合いが大きく前記ワードデータにおいて2ビット以上のデータエラーが発生した段階であって、複数ビットにわたる連続したデータエラー(バーストエラー)、或は複数箇所に散在した1ビットのデータエラー(ランダムエラー)が発生している段階。

【0027】

そこで、発明者は、放射線の照射に起因する全ての段階のエラー訂正が可能なデータ管理システム11を構築した。ここで、前記RFIDタグ10の種類10A〜10Cとタグリーダ/ライタ12の種類12A,12Bとの組合わせは(図2参照)、通信距離との関係上、

(a)アクティブ型の電池4a付きRFIDタグ10Aと、据置型タグリーダ/ライタ12B

(b)セミパッシブ型の電池4b付きのRFIDタグ10Bと、ハンディ型或は据置型タグリーダ/ライタ12A,12B

(c)パッシブ型のRFIDタグ10Cと、ハンディ型或は据置型タグリーダ/ライタ12A,12B

に分類されるが、以下では(c)のRFIDタグ10Cとハンディ型タグリーダ/ライタ12Aとの組合せにおけるエラー訂正について説明する。尚、RFIDタグ10Cの制御部5c及びメモリ部6cを、タグ側制御部5c及びタグ側メモリ部6cとし、タグリーダ/ライタ12Aの制御部18をRW側制御部18とする。

【0028】

図6(a)及び(b)は、タグ側メモリ部6cに記憶されるデータに対して生成される冗長データを説明するための図である。前記データ領域202は、本来のデータたるメインデータを記憶するためのメインデータ領域210と、前記冗長データを記憶するための冗長領域220とを有する。ここでは、メインデータ領域210を8バイト分だけ示している。

【0029】

冗長領域220に記憶されている冗長データは、ここでは、メインデータ領域210に記憶されているメインデータの誤りを訂正するための誤り検出符号であって、メインデータのアドレスごとに生成される横方向の第1誤り検出符号と、同じビット位置ごとに生成される縦方向の第2誤り検出符号とを含む。

【0030】

前記誤り検出符号として例えばハミング符号が用いられ、2ビットの誤り検出ができるように設定されている。ここで、ハミング符号についてエラー訂正用ビットの数をmとした時、その符号長は2m−1で表される。従って、例えばm=4の場合、11ビットのメインデータに対して、15ビットの符号語(符号長)に置き換えるハミング符号が形成される。そこで、本実施形態では、後述する誤り検出処理の際、前記8ビット単位のメインデータに対して、3ビットのダミーデータを付して(つまりメインデータの上位3ビットを"0"にして)見かけ上、11ビットのメインデータに付随する4ビットの誤り検出符号として誤り検出処理を行うようになっている。尚、上記ハミング符号にパリティビットを付加して、2ビット誤り検出と1ビット誤り訂正とを行うようにしてもよい。

【0031】

図6(a)では、前記メインデータを記憶した領域210と第1誤り検出符号(第1冗長データ)を記憶した領域221において、同図中、縦方向の座標値(アドレス)をx、横方向の座標値(ビット位置)をyとした場合における、メインデータD(x、y)及び第1誤り検出符号E(x、y)を示している。ここで、第1誤り検出符号E0,1〜E0,3及びE1,0〜E1,3は、同じアドレスの上位4ビット及び下位4ビットに書込まれている(図7のアドレス200、図8(a)参照)。従って、2列のデータ列D0,0〜E0,3及びD1,0〜E1,3は、3バイトで表現されることとなる。また、図6(b)には、冗長領域220のうち、第2誤り検出符号(第2冗長データ)を記憶した領域222において、上記メインデータD0,0〜D7,7の同じビット位置の列ごと生成された第2誤り検出符号F(x、y)と、第1誤り検出符号Eの同じビット位置の列ごと生成された第2誤り検出符号G(x、y)とを夫々示している。尚、図6に示す符号D(x、y)、F(x、y)、G(x、y)は、データの配列を説明するために便宜的に付したものであり、実際のデータビットの配列は、LSB(Least Significant Bit:最下位ビット)ファースト、MSB(Most Significant Bit:最上位ビット)ファーストの何れについても適用が可能である。

【0032】

本実施形態のパリティ符号は、データを構成する各ビットに対して、互いに隣り合う当該ビットとの組合わせに対応して付加される。具体的には例えば、パリティ符号をもとに奇数パリティ検査を行うようになっており、メインデータD0,0の示す値が0、D0,1の示す値が1のとき、値が0のパリティビットを付加する(図9(a)(b)参照)。従って例えば、メインデータD0,0〜D0,7及び第1誤り検出符号E0,0〜E0,3が示す値が「01000110…」のとき、その隣り合う値の組合せに対応した「0011010…」からなる奇数パリティ符号Pが生成される。このパリティ符号Pを用いて、メインデータD及び第1誤り検出符号Eについて誤り検出処理と誤り訂正処理が行われるようになっている。尚、パリティ符号Pは、偶数パリティ符号であってもよい。

【0033】

本実施形態の冗長データの一種であるビット対は、データの各ビットが示す1,0の値の何れか一方を01、他方を10とするビット対として符号化したデータであり、1ビットデータを2ビットデータで表現する。具体的には例えば、図10(a)に示すように、メインデータD0,0が示す0の値を10、メインデータD0,1における1の値を01とするビット対として符号化する。従って、図10(b)に示すメインデータD0,0〜D0,7及び第1誤り検出符号E0,0〜0,3が示す値が「01000110…」のとき、「0110010101101001…」からなるデータD0,0F〜E0,3Rが生成される。この場合、メインデータD0,0における本来のデータ0の値は、ビット対における一方のビット0(図10(a)中、Fで示す)であり、他方のビット1(Rで示す)は当該0を反転させたデータである。

【0034】

よって、図22(b)に示すように、ビット対として符号化された4列のデータD0,0F〜E1,3Rのうち、上から1列目のデータD0,0F〜E0,3Fは、図22(a)のメインデータD0,0〜D0,7及び第1誤り検出符号E0,0〜E0,3と一致し[(D0,0F〜E0,3F)=(D0,0〜E0,3)]、図22(b)の上から3列目のデータD0,0R〜E0,3Rは、1列目のデータD0,0F〜E0,3Fの反転データである。また、図7、図8(b)に示すように、前記ビット対F,Rのうち一方のビットFと他方のビットRは、タグ側メモリ部6cのデータ領域202において、相互に異なるアドレスの同じビット位置に記憶される。換言すれば、符号化されたデータD0,0F〜E0,3F及び反転データD0,0R〜E0,3Rは、相互に異なるアドレスに記憶され、且つ対応する各ビットが示す値は相互に反転した内容となっている。

【0035】

ここで、図11は、メインデータD0,0〜D0,7における一部のビットの値が"1"から"0"に片方向へ変化する、前述したデータエラーが生じている状況を例示している。即ち、ビット対F,Rはその何れか一方のビットに1を含むことから、前記の片方向への変化を前提とした場合、00のビット対(図11の網掛部分)がエラーパターンとなることで、そのエラーが発生した数とビット対F,Rの位置を特定することができるのである。例えば、各ビット対F,Rにおいて、一方のビットFと他方のビットRとの論理和演算を行うことにより、誤りを検出することができる。

【0036】

上記の符号化と異なり、データの各ビットが示す0の値を01、1の値を10とするビット対として符号化してもよい。また、メモリがデータを記憶している状態に対する定義によっては、透過放射線により"0"から"1"の片方向の変化が生じるケースもあるが、0と1とを反転して扱えば足りるので、本実施形態では"1"から"0"への片方向への変化を前提として説明する。

【0037】

前記冗長領域220は、多重化データを記憶するための多重化データ記憶領域224を含む(図7参照)。本実施形態では、例えば、メインデータD0,0〜D7,7のビット対F,Rが、メインデータ領域210と多重化データ記憶領域224とに書込まれることにより二重化されており、第1誤り検出符号E0,0〜E7,3のビット対F,Rも、第1誤り検出符号領域221と多重化データ記憶領域224とに書込まれることにより二重化されている。以下では、多重化されたメインデータ及び第1誤り検出符号について、D0,0F´〜D7,7R´及びE0,0F´〜E7,3R´の如く該当符号に「ダッシュ」を付すものとする(図7参照)。尚、第1誤り検出符号E、第2誤り検出符号F,G、パリティ符号Pの多重化、並びにこれら冗長データE,F,G、Pのビット対F,Rの多重化についても、必要に応じて行うことができる。また、第1誤り検出符号E、第2誤り検出符号F,G、パリティ符号Pの生成対象、並びにビット対F,Rとして符号化を行う対象は、本実施形態の記載に限定するものではなく、冗長データE,F,G、P相互間とするなど適宜設定することができる。

【0038】

次に、上記構成の作用について、図12〜図20も参照しながら説明する。図12は、ハンディ型タグリーダ/ライタ12Aを用いてRFIDタグ10Cにデータを書込む場合の処理内容を示すフローチャートである。

【0039】

先ず、タグリーダ/ライタ12Aの操作部(図示せず)が作業者により操作されると、RW側制御部18は、その操作部から入力された操作信号に基づいて、書込むべきデータを受付けて処理する(ステップA1)。そして、詳しくは後述するように、RW側制御部18は、その書込み用データをRFIDタグ10Cに送信する前に、タグ側メモリ部6cから当該書込み用データを書込むアドレス以外の全てのアドレスのデータを読出して、前記冗長データをもとに誤りを検出して訂正するようになっている(ステップA2)。

【0040】

ステップA2の読取り処理の後、RW側制御部18は、書込み用データたるメインデータDについてアドレスごとに第1誤り検出符号Eを生成すると共に、同じビット位置ごとに第2誤り検出符号F,Gを生成する処理を行う(ステップA3、A4)。次いで、RW側制御部18は、メインデータD及び第1誤り検出符号Eを構成する各ビットに対して、互いに隣り合う当該ビットの組み合せに対応してパリティ符号Pを生成する(ステップA5)。また、メインデータD、第1誤り検出符号E及びパリティ符号Pの各ビットが示す1と0の値は、01と10のビット対F,Rとして符号化される(ステップA6)。更に、メインデータD及び第1誤り検出符号Eの夫々のビット対F,Rは、ステップA7において二重化されることにより、メインデータD及び第1誤り検出符号Eのビット対F´,R´が生成される。こうして生成された、メインデータD及び第1誤り検出符号Eの夫々のビット対F,R、二重化されたビット対F´,R´、第2誤り検出符号F,G、並びにパリティ符号Pが送信されることにより、タグ側メモリ部6cに書込まれ(ステップA8)、タグリーダ/ライタ12Aを用いた書込み処理を終了する。これにより、RFIDタグ10Cに対して、メインデータDのビット対Fと併せて各種の冗長データが記憶されることから、その冗長データをもとに誤り検出処理と誤り訂正処理を行うことが可能となる。

【0041】

図13は、上記の書込み処理に際して前記ステップA2で行われる読取り処理の内容を示すフローチャートである。

先ず、RW側制御部18は、タグ側メモリ部6cから前記書込み用データを書込むアドレス以外の全てのアドレスのデータを読出す関連データ読込み処理を実行する(ステップB1、図15のステップC1〜C11参照)。即ち、関連データ読込み処理では、メインデータD及び第1誤り検出符号Eのビット対F,Rがタグ側メモリ部6cから読込まれる(ステップC1,C2)。次いで、これらメインデータD及び第1誤り検出符号Eのビット対F,Rが多重化されている場合は(ステップC3:YES)、多重化データとしてのメインデータD及び第1誤り検出符号Eのビット対F´,R´がタグ側メモリ部6cから読込まれる(ステップC4,C5)。また、パリティ符号Pが付加されている場合は(ステップC6:YES)、メインデータDのパリティ符号P及び第1誤り検出符号Eのパリティ符号Pがタグ側メモリ部6cから読込まれる(ステップC7,C8)。更に、第2誤り検出符号F,Gが付加されている場合は(ステップC9:YES)、メインデータDの第2誤り検出符号F、及び第1誤り検出符号Eの第2誤り検出符号Gがタグ側メモリ部6cから読込まれる(ステップC10,C11)。

【0042】

尚、RW側制御部18において、タグ側メモリ部6cの冗長領域220に記憶された冗長データが、メインデータD及び第1誤り検出符号Eに係るビット対Rのみと判断した場合は(ステップC3,C6,C9:NO)、ステップC1,C2でメインデータD及び第1誤り検出符号Eに係るビット対F,Rを読込みこんだ後、ステップB2(図13参照)の誤り検出処理に移行する。また、上記のステップB1の読込み処理では、RW側制御部18は、同じアドレスについて連続して少なくとも2度同じデータを読出すまで、繰り返しデータを読出す。具体的には、例えば8ビットのメインデータD0,0〜D0,7は、2回続けて読出され(図14のステップD1,D2)、1回目と2回目のデータが異なる場合には(ステップD3:NO)、再度2回続けて読出される。即ち、放射線に晒された環境においてRFIDタグ10Cからデータを出す場合、データを送信するRFIDタグ10C側あるいは受信したタグリーダ/ライタ12A側で放射線によりデータが化ける可能性がある。そこで、RW側制御部18は、連続して少なくとも2度同じデータを読出すまで繰り返しデータを取得することで、タグ側メモリ部6cからデータを読出す際のデータ化けを防止することができる。また、後述の誤り検出処理で誤りが検出されず(図13のステップB3:NO)、誤り訂正処理が行われなくても、ステップB1(ステップD1〜D3)のデータ読出しの際、その読出しと同時に各メモリセルの電荷の再チャージ、つまりリフレッシュを行うことができる。従って、各メモリセルにおいて放射線の衝突により電子が失われていたとしても、前記第1段階にある損傷は修復されることになる。

【0043】

ステップB2では、上記のようにして読出したメインデータD及び第1誤り検出符号Eの各ビット対F,Rについて、一方のビットFと他方のビットRとの論理和演算を行う。ここで、RW側制御部18は、その演算結果が1であればビット対F,Rの何れかに誤りが無く(ステップB3:NO)、当該演算結果が0であればビット対F,Rに誤りが有ると判断して(ステップB3:YES)、誤り訂正処理(ステップB4、図16のステップE1〜E10)に移行する。

【0044】

この誤り訂正処理では、先ず、メインデータD及び第1誤り検出符号Eのビット対F,Rに係る訂正処理が1バイトごとに行われる(ステップE1、図17のステップF1〜F5)。具体的には、RW側制御部18は、バイト数をカウントするためのカウンタNをゼロクリアして(ステップF1)、メインデータD0,0F〜D0,7Fについて、メインデータD0,0R〜D0,7Rとのビットごとの論理和演算に基づき、0となるビット対F,Rが3つ以上有るか、或は演算結果が全て1かを判断する(ステップF2)。例えば図11の網掛部分で示すように、メインデータD0,0〜D0,7のビット対F,Rのうち、その組合わせが00となっているメインデータD0,2及びD0,5のビット対F,Rは演算結果が0となる。このため、メインデータD0,2及びD0,5についてのビット対F,Rについて誤りと判断され(ステップF2:NO)、そのメインデータD0,2、D0,5の誤りを訂正する処理が行われる(ステップF3)。この場合、該当するメインデータD0,2、D0,5の夫々のビット対F,Rに、データ01或は10(これらを代入データと称す)を順次代入し、当該代入データを代入したメインデータD0,0F〜D0,7F、D0,0R〜D0,7Rについて、第1誤り検出符号E0,0F〜E0,3F、E0,0R〜E0,3Rをもとに誤り検出処理を行う。このとき、メインデータD0,2、D0,5のビット対F,Rに対する代入データの代入パターンとしては、メインデータD0,2のビット対F,Rにおける01と10、メインデータD0,5のビット対F,Rにおける01と10とで、計4通り存在する(図11参照)。従って、1バイト内の2ビットのデータエラーは、前記の代入データと第1誤り検出符号Eとをもとに、多くても4回、誤り検出処理を行えば誤りが非検出となり、誤りを訂正することができる(第1誤り訂正処理)。

【0045】

0バイト目の誤り訂正を終え、或は前記ステップF2でYESと判断された場合、7バイト目までの処理を終えていないことから(ステップF4:YES)、前記カウンタNをインクリメントして(ステップF5)、1バイト目のメインデータD1,0F〜D1,7Fについても、メインデータD1,0R〜D1,7Rとの論理和演算の結果に基づき、データエラーとなるビット対F,Rが3つ以上あるか(或はエラーが無いか)を判断する(ステップF2)。そして、上記と同様にビット対F,Rの誤りが2つ若しくは1つ存在すれば、代入データを順次代入して第1誤り検出符号E1,0F〜E1,3F、E1,0R〜E1,3Rをもとに誤りを訂正する処理を行う(ステップF3)。こうして、ステップF2〜F5が繰り返し実行されることにより、1バイト目以降のメインデータDについても1バイトずつ誤り検出処理と誤り訂正処理とが行われ、7バイト目の誤り訂正を終えることにより(ステップF4:NO)、図16のステップE2に移行する。ステップE2において、RW側制御部18は、タグ側メモリ部6cから読込んだ全てのデータについて、上記の誤り訂正処理によりデータエラーが解消されたと判断すると(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。尚、上記ステップF1〜F5では、メインデータDの誤りを訂正する処理について説明したが、第1誤り検出符号Eについては、予めそのビット対F,Rをもとに誤り検出を行い、同じビット位置の列ごとに代入データと第2誤り検出符号Gとに基づく誤り訂正処理を行う(後述のステップI1〜I5参照)。つまり、予め第1誤り検出符号Eの誤り訂正処理を実行した後、ステップF1〜F5を実行するのである。

【0046】

一方、上記メインデータD或は第1誤り検出符号Eのデータについて1バイトに3ビット以上のエラーが含まれ(図16のステップE2:YES)或は他のデータについてエラーが含まれる場合には、データが多重化されているか否かを判断する(ステップE3)。データが多重化されている場合には(YES)、その多重化に係る訂正処理が行われる(ステップE4.図18のステップG1〜G8)。即ち、ステップG1では、多重化したメインデータD´及び第1誤り検出符号E´について、前記ステップE1(つまりステップF1〜F5)と同様に、1バイトずつ誤り検出処理と誤り訂正処理とが行われる。RW側制御部18は、この訂正処理によって、タグ側メモリ部6cから読込んだ全てのデータについてエラーが解消されたと判断すると(ステップG2:YES)、図16のステップE5にリターンする。そして、ステップE5でも、同様にエラーが解消されたものとして(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0047】

RW側制御部18は、図18のステップG2でエラーが解消されていないと判断すると(NO)、バイト数をカウントするためのカウンタNをゼロクリアする(ステップG3)。そして、ステップG4では、本来のメインデータDと多重化したメインデータD´との間で対応するビットごとに論理和演算が行われると共に、第1誤り検出符号Eと多重化した第1誤り検出符号E´との論理和演算との間で対応するビットごとに論理和演算を行う(ステップG4)。例えば図21において上側のメインデータD0,0F〜D0,7Fと、その直ぐ下側の多重化したメインデータD0,0F´〜D0,7F´との間で対応するビットごとに論理和演算を行う。尚、同図では、説明の便宜上、メインデータD0,0R〜D0,7R及びD0,0R´〜D0,7R´を併せて図示している。同図の網掛部分で示すように、メインデータD0,2、D0,6の夫々のビット対F,Rと、多重化したメインデータD0,3、D0,5の夫々のビット対F´,R´とが00となるデータエラーが生じていても、同じビット位置に正しいデータが存在すれば、そのビットの論理和演算の結果、データエラーを修復したビット列を得ることができる。

【0048】

ステップG4の誤り訂正処理の後、RW側制御部18は、メインデータD0,0F〜D0,7Fについて、ビットごとにメインデータD0,0R〜D0,7Rとの論理和演算を行い、演算結果が0となるビット対F,Rが3つ以上有るか、或は演算結果が全て1かを判断する(ステップG5)。ここで、前記ビット列に1つ2つの誤りが含まれていても(NO)、前記代入データと第1誤り検出符号とをもとに誤りが非検出となるまで誤り検出処理を行うことで、誤りは訂正される。

【0049】

この0バイト目誤り訂正を終え、或は前記ステップG5でYESと判断された場合、7バイト目までの処理を終えていないことから(ステップG7:YES)、前記カウンタNをインクリメントして(ステップG8)、1バイト目のメインデータD1,0F〜D1,7Fについて、多重化したメインデータD1,0F´〜D1,7F´との間で対応するビットごとに論理和演算を行う(ステップG4)。そして、その論理和演算から得られたビット列について、上記と同様に2ビット(或は1ビット)の誤りがあれば、代入データを順次代入して誤りを訂正する処理を行う(ステップG5,G6)。こうして、ステップG4〜G8が繰り返し実行されることにより、1バイト目以降のメインデータDについても1バイトずつ誤り検出処理と誤り訂正処理とが行われ、7バイト目の誤り訂正を終えることにより(ステップG7:NO)、図16のステップE5に移行する。ステップE5において、RW側制御部18は、タグ側メモリ部6cから読込んだ全てのデータについて、上記の誤り訂正処理によりデータエラーが解消されたと判断すると(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0050】

上記の多重化に係る誤り訂正処理の後、未だデータにエラーが含まれる場合には(ステップE5:NO)、パリティ符号Pが付加されているか否かを判断する(ステップE6)。パリティ符号Pが付加されている場合には(YES)、そのパリティ符号Pに係る訂正処理が行われる(ステップE7、図19のステップH1〜H8)。即ち、RW側制御部18は、ビット数をカウントするためのカウンタMをゼロクリアして(ステップH1)、訂正の対象となるアドレスのデータ、例えばメインデータD0,0F〜D0,7Fについて誤りを訂正する。具体的には、図9(b)の破線で囲うように、メインデータD0,0Fの示す値0は、隣のデータD0,1Fの示す値1との関係上、奇数パリティ検査(パリティビットP0,0)により、誤りが無いと判断される(ステップH2:NO)。この0ビット目に続いて、1ビット目の処理を行うべくカウンタMをインクリメントし(ステップH3、H4)、メインデータD0,1Fについても上記と同様に奇数パリティ検査を行う(ステップH2)。こうして、ステップH1〜H4が繰り返し実行される過程において、奇数パリティ検査に基づきメインデータD0,6Fに誤りが有ると判断されると(ステップH2:YES、図9(b)参照)、左データたるD0,6Fと左パリティたるP0,5とに誤りが有るか否かが判断される(ステップH5)。両者D0,6F、P0,5に誤りがなければそのパリティビットP0,5をもとにD0,6Fの値が訂正される(ステップH6)。この点、左データD0,6や左パリティP0,5の何れかに誤りが存する場合でも(ステップH5:NO)、右データたるD0,7Fと右パリティたるP0,6とに誤りが無ければ(ステップH7:NO)、そのパリティビットP0,6をもとにD0,6Fの値を訂正することができる(ステップH8)。こうして、7バイト目まで訂正の対象となるアドレスの処理を終えることにより(ステップH3:NO)、図16のステップE8に移行する。ステップE8において、RW側制御部18は、タグ側メモリ部6cから読込んだ全てのデータについて、上記の誤り訂正処理によりデータエラーが解消されたと判断すると(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0051】

上記のパリティ符号に係る誤り訂正処理の後、未だデータにエラーが含まれる場合には(ステップE8:NO)、第2誤り検出符号F,Gが付加されているか否かを判断する(ステップE9)。第2誤り検出符号F,Gが付加されている場合には(YES)、その第2誤り検出符号F,Gに係る誤り訂正処理が行われる(ステップE10、図20のステップI1〜I11)。この誤り訂正処理では、先ず、ビット数をカウントするためのカウンタMがゼロクリアされ(ステップI1)、訂正の対象となるデータについて、同じビット位置の列ごとに誤りを検出する処理が行われる。具体的には例えば、メインデータD0,0F〜D7,0Fの列(図6参照)について、ビット対をなすD0,0R〜D7,0Rの列とビットごとの論理和演算を行い、3ビット以上の誤りが有るか或は誤りが無いかを判断する(ステップI2)。何れの条件も満たさない場合つまり2ビット若しくは1ビットの誤りがあれば(NO)、その誤りが検出されたメインデータD0,0〜D7,0のビット対F,Rに、前記代入データを順次代入して第2誤り検出符号F0,0F〜F3,0F、E0,0R〜E3,0Rをもとに誤りを訂正する処理を行う(ステップI3:第2誤り訂正処理)。

【0052】

0ビット目の誤り訂正を終え、或は前記ステップI2でYESと判断された場合、11ビット目までの処理を終えていないことから(ステップI4:YES)、前記カウンタMをインクリメントして(ステップI5)、1ビット目以降のメインデータDについても同じビット位置の列ごとに、ビット対F,Rに基づく誤り検出処理と(ステップI2)、代入データと第2誤り検出符号Fとに基づく誤り訂正処理を行う(ステップI3)。こうして、ステップI2〜I5を繰り返し実行し、8ビット目(実際には上位のビット)以降は、第1誤り検出符号Eについて、同じビット位置の列ごとにビット対F,Rに基づく誤り検出処理と(ステップI2)、代入データと第2誤り検出符号Gとに基づく誤り訂正処理を行う(ステップI3)。

【0053】

そして、11ビット目の誤り訂正を終えると(ステップI4:NO)、バイト数をカウントするためのカウンタNをゼロクリアして(ステップI6)、今度は、アドレスごとに、ビット対F,Rに基づく誤り検出処理と(ステップI7)、前記代入データと第1誤り検出符号Eとに基づく誤り訂正処理を行う(ステップI8)。この0バイト目の処理を終えると、7バイト目までの訂正処理を行うべく(ステップI9:YES)、前記カウンタNをインクリメントして(ステップI10)、ステップI7にリターンする。そして、1バイト目以降のメインデータDについてもアドレスごとに、ビット対F,Rに基づく誤り検出処理と(ステップI7)、代入データと第1誤り検出符号Eとに基づく誤り訂正処理を行う(ステップI8)。こうして、RW側制御部18は、ステップI7〜I10を繰り返し実行し、7ビット目の誤り訂正を終えると(ステップI9:NO)、全てのデータについてエラーが解消されたか否かを判断する(ステップI11)。ここで、エラーが解消されていなければステップI1にリターンし(NO)、エラーが解消されていれば(YES)、その誤りの無いデータをタグ側メモリ部6cに書込んで(図13のステップB5にリターン)、処理を終了する。

【0054】

上記した一連の誤り訂正処理(ステップE1〜E10)、特にはステップE10(ステップI1〜I10)では、そのステップI1〜I5における同じビット位置の列ごとの誤り訂正処理と、ステップI7〜I10におけるアドレスことの誤り訂正処理とが夫々繰り返し実行されため、データエラーをより確実に解消することができる。即ち、例えばメインデータD0,0〜D7,7の各アドレス或は同じビット位置の列に、3ビット以上のバーストエラーが複数箇所に発生していたとする。この場合でも、前記ビット対をもとに当該エラーを確実に検出し、前記代入データと第1及び第2誤り検出符号E及びF,Gとに基づく誤り訂正処理を、アドレスごとに或は同じビット位置の列ごとに繰り返し実行することで、一部のデータが修復されれば、そのデータをもとに他のデータについても連鎖的に修復される。こうして、所謂訂正なだれが発生することで、タグ側メモリ部6cに前述したバーストエラーやランダムエラーが発生した第3段階の状態にあっても、その全てのエラーを訂正することが可能となるのである。

【0055】

以上説明したように、データ管理システム11において、前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対F,Rとして符号化したデータを含み、RW側制御部18は、前記誤り検出処理において、タグ側メモリ部6cから読出したデータについてビット対をなす双方のビットの値が0であれば当該ビット対に誤りが有ると判断する。これによれば、例えば透過放射線によりタグ側メモリ部6cのメモリセルにおいてデータが"1"から"0"に片方向へ変化するデータエラーが生じる状況にあっても、RW側制御部18によって、ビット対F,Rをなす双方のビットが値0であれば、当該ビット対により表現されたデータが誤りであると判定できる。従って、ビット対F,Rをもとにデータエラーを確実且つ簡単に検出することができる。従って、放射線に晒される特殊環境でデータエラーの発生を防止し且つ正常に機能させることが可能なデータ管理システム11を提供することができる。

【0056】

また、RW側制御部18は、前記の片方向へ変化するデータエラーが生じる状況にあっても、ビット対F,Rをなす双方のビットの論理和演算を行い、その演算結果が1であれば前記ビット対に誤りが無く、当該演算結果が0であれば前記ビットに誤りがあると判断する。即ち、ビット対F,Rは01又は10として生成され、何れもF,Rの論理和をとれば必ず1となるが、データエラーが発生すると00になり、その論理和をとれば0となる。従って、RW側制御部18によって、タグ側メモリ部6cに記憶されたデータのエラーを簡単に特定し且つ確実に検出することができ、その処理速度を高めることができる。

【0057】

しかも、前記ビット対F,Rのうち一方のビットFと他方のビットRは、タグ側メモリ部6cにおいて相互に異なるアドレスの同じビット位置に記憶されるため、一層、処理速度を高めることができる。

【0058】

前記冗長データは、1バイトのデータごとに生成される第1誤り検出符号Eと、前記データの同じビット位置ごとに生成される第2誤り検出符号F,Gとのうち、少なくとも何れかの誤り検出符号を含む。従って、RW側制御部18は、前記ビット対F,Rに基づく誤り検出のみならず、第1及び第2誤り検出符号E及びF,Gに基づく誤り検出を行うことができ、誤りをより確実に検出することができると共に誤り訂正処理による訂正確率を高めることができる。

【0059】

RW側制御部18は、前記ビット対F,Rをなす双方のビットの論理和演算に基づき誤りが検出されると、その誤りが検出されたビット対F,Rにデータ0,1(これらは前記代入データ)を代入して前記誤り検出符号をもとに誤り検出処理を行い、誤りが非検出となるまで誤り訂正処理を行う。従って例えば、データエラーが発生しているビット対F,Rが2組(この組数をxとする)あるとき、当該2組のビット対F,Rに対する代入データの代入パターンは計4通り(つまり2x)存在する。よって、その代入データをもとにデータエラーを確実に修復することができる。

【0060】

RW側制御部18は、前記ビット対F,Rをなす双方のビットの論理和演算に基づき誤りが検出されると、誤りが検出されたアドレスごとに前記代入データと前記第1誤り検出符号Eとをもとに誤りが非検出となるまで誤り訂正処理を行う第1誤り訂正処理と、同じビット位置の列ごとに前記代入データと前記第2誤り検出符号F,Gとをもとに誤りが非検出となるまで誤り訂正処理を行う第2誤り訂正処理とを実行する。これによれば、例えば第1誤り訂正処理と第2誤り訂正処理とを繰り返し実行することで、一部のデータが修復されれば、そのデータをもとに他のデータについても連鎖的に修復することができる。よって、タグ側メモリ部6cに前述したバーストエラーやランダムエラーが発生した第3段階の状態にあっても、その全てのエラーを訂正できる確率を高めることができる。

【0061】

RW側制御部18は、タグ側メモリ部6cにデータを書込む際、そのデータを書込むアドレス以外の全てのアドレスのデータを読出して、前記冗長データをもとに誤り検出処理と誤り訂正処理とを行う(前記ステップB1〜B4)。これによれば、タグ側メモリ部6cにデータを書込む度に、当該メモリ部6cの全てのアドレスのデータについて誤りの無いデータを作成することができる。また、当該データエラーが無くても、全てのデータの読出すことにより各メモリセルの電荷の再チャージ、つまりリフレッシュを行うことができ、放射線照射によりフローティングゲート中の電子が失われていたとしても、前記第1段階にある損傷を修復することができる。

【0062】

RW側制御部18は、前記読出したデータについて誤り訂正処理を行った場合は、訂正したデータを前記不揮発性記憶手段に書込むことから(前記ステップB5)、タグ側メモリ部6cにデータを書込む度に、当該メモリ部6cの全てのアドレスのデータについて、誤りを訂正する機会を設けることができる。

【0063】

タグ側メモリ部6cには、複数の異なる領域に同じデータが書込まれてデータが多重化されており、RW側制御部18は、多重化された複数のデータの同一ビット間で、想定されるデータの誤りパターンに応じて論理演算を行い、その演算により得られたビット列について、前記冗長データをもとに誤り検出処理を行った結果、誤りが検出されなければ、当該ビット列のデータが正しいデータであると判断する。

【0064】

これによれば、1バイトのデータのあるビットにデータエラーが生じていても、多重化した他方のデータの対応するビットに正しいデータが存在すれば、当該ビットとの論理和演算の結果、そのビット位置のデータについてエラーを確実に修復することができる。また、前記ビット列について冗長データをもとに誤りが無いことを判断することができ、データ管理システム11の信頼性をより高めることができる。尚、透過放射線等により"0"から"1"の片方向の変化が生じる場合には、前記論理和演算に代えて論理積演算を行うことにより、上記と同様にエラーを修復することができる。

【0065】

RW側制御部18は、前記ビット対F,Rと誤り検出符号E、F,Gとをもとに誤り検出処理及び誤り訂正処理を行い、その訂正処理後のデータに誤りが有ると、多重化された複数のデータ間で対応するビットごとに論理和演算を行う。これによれば、上記の効果に加え、複数種の冗長データR,E,F,G,F´,R´を用いた重畳的な誤り訂正処理により、訂正確率を一層高めることができる。

【0066】

前記冗長データは、データを構成する各ビットに対して、隣り合うビットとの組み合わせについて付加されたパリティ符号Pを含み、(ここも「ビット対」は止めた方が良いのでは)RW側制御部18は、誤り訂正処理において、前記隣り合うビットのうち誤りが無いビットのデータとパリティ符号Pとをもとにビットの誤りを訂正する。これによれば、パリティ符号Pは、前記隣り合うビットの組み合わせに対応して付加されたものであるから、前記冗長データR,E,F,G,F´,R´に基づく訂正処理とは異なる訂正処理を行うことができ、より訂正確率を高めることができる。

【0067】

RW側制御部18は、タグ側メモリ部6cからデータを読出す場合、同じアドレスについて連続して少なくとも2度同じデータを読出すまで、繰り返しデータを読出す。例えば、上記のように通信の際、例えばRFIDタグ10Cのアンテナ2cに照射された放射線によりデータが化ける可能性があるが、連続して少なくとも2度同じデータを読出すまで繰り返しデータを取得することで、タグリーダ/ライタ12A側からのデータ読出し時における化けを確実に防止することができる。

【0068】

上記実施形態では、ハンディ型タグリーダ/ライタ12Aを用いてデータを書込む際に、データの読出し処理から訂正データの書込み処理まで(ステップB1〜B5)を行うこととしたが、例えば据置型タグリーダ/ライタ12Bを用いて、予め設定された所定時間毎にタグ側メモリ部6cからデータを読出すようにしてもよい。ここで、前記所定時間は、放射線量としての放射線強度やその照射期間に応じて設定されるものであり、その放射線環境の下、タグ側メモリ部6cにおいて放射線照射等によりデータ破壊に至る時間よりも短い時間に設定する。そして、放射線量は、放射線源からの距離の2乗に反比例することから、例えばRFIDタグ10Cが放射線源の近くで用いられる場合には、前記パソコン14等の上位装置から比較的短い時間毎(例えば数分ごと)に指示が与えられることに基づき、タグリーダ/ライタ12Bの制御部18によって、ステップB1〜B5を実行するようにしてもよい。

【0069】

尚、高温環境の下でも、放射線環境と同様に、前記の片方向へ変化するデータエラーが生じる虞がある。従って、データエラーに至るメモリ部6a,6cの温度特性等により、前記所定時間を適宜設定してステップB1〜B5を実行することで、上記と同様の効果を得ることができる。

【0070】

この点、アクティブ型のRFIDタグ10Aでも同様に、自身が有するメモリ部6aについて制御部5aが主体となり、前記所定時間毎に、若しくは他に優先する処理の無い時に、ステップB1〜B5を実行するようにしてもよい。即ち、前述したように、RFIDタグ10Aのメモリ部6aには、タグリーダ/ライタ12のメモリ部19と同様の制御プログラムや誤り訂正プログラム等が記憶されると共に、タグ側メモリ部6cと同様の冗長データが記憶されている。従って、RFIDタグ10Aにおいて、制御部5aによりメモリ部6aから読出したデータについてその冗長データをもとに誤り検出処理を行い、その検出処理において誤りが検出された場合には誤り訂正処理を行うことができる。

【0071】

また、アクティブ型のRFIDタグ10Aにおいて、制御部5aは、タグリーダ/ライタ12から前記無線通信手段を介して書込み用データを受信した際、その受信したデータから前記冗長データを生成して前記データと共にメモリ部6aに書込むようにする。そして、タグリーダ/ライタ12へ前記無線通信手段を介してデータを送信する際、その送信するデータに付された冗長データをもとに誤り検出処理と誤り訂正処理とを行うことにより、誤りの無いデータを送信するようにしてもよい。つまり、アクティブ型のRFIDタグ10Aであれば、上記したタグリーダ/ライタ12Bと同様の処理を行うことができることから、自身のメモリ部6aに記憶されるデータ関して冗長データを生成し、或はステップB1〜B5を実行する等してデータを管理することができる。

【0072】

RFIDタグ10A〜10Cは、何れもハンディ型或は据置型タグリーダ/ライタ12A,12B(外部の電子機器)に対するスレーブとして構成されている。従って、上記データ管理システム11の下、RFIDタグ10A〜10Cの信頼性を高めることができる。

【0073】

タグリーダ/ライタ12A,12Bは、RFIDタグ10A〜10Cの何れかのマスタ(電子機器)として構成されていることから、タグリーダ/ライタ12A,12Bを用いて上記データ管理システム11の信頼性を高めることができる。

【0074】

図22〜図30は、第2〜第7実施形態を示すものであり、第1実施形態と同一部分には同一符号を付す等して説明を省略し、以下異なる点につき説明する。

<第2実施形態>

図22は、本発明の第2実施形態を示す図21相当図である。

【0075】

多重化データ記憶領域224には、例えば、メインデータD0,0〜D7,7のビット対F´,R´と同じデータF´´,R´´が書込まれることにより、メインデータD0,0〜D7,7が三重化されている(図22参照)。従って、前記多重化に係る訂正処理における論理和演算(図18のステップG4)では、本来のメインデータDと、多重化したメインデータD´とD´´との間で対応するビットごとに論理和演算が行われる。即ち、図22の網掛部分で示すように、例えばメインデータD0,1、D0,2、D0,6については、三重化による3組のビット対F,R、F´,R´、F´´,R´´のうち、値が00となるデータエラーが生じたビット対が2組ずつ含まれている。このような場合でも、同じビット位置に正しいデータが1つでも存在すれば、そのビットの論理和演算の結果、データエラーを修復したビット列を得ることができる。

【0076】

本実施形態と異なり、上記3組のビット対F,R、F´,R´、F´´,R´´のビット対について多数決に基づきビットごとに誤り訂正をすると、前記第3段階のデータエラーについては、誤りが過半数となって間違った訂正を行う虞がある。これに対し、本実施形態のように論理和演算をもとに誤り訂正を行うことで、同じビット位置に正しいデータが1つでも存在すれば、そのビットに対応する他の2組のビット対のデータエラーを完全に修復することができる。従って、データ管理システム11の信頼性をより高めることができる。尚、多重化は、二重化や三重化に限定されるものではなく、四重化以上のデータを冗長データとして含むようにしてもよい。

【0077】

<第3実施形態>

図23は、本発明の第3実施形態を示す図10(b)相当図である。

前述したように、RW側制御部18は、タグ側メモリ部6cから読出したメインデータD及び第1誤り検出符号Eの各ビット対F,Rについて、一方のビットFと他方のビットRとの論理和演算を行う(前記ステップB2)。そして、本実施形態では、前記ステップS3でビット対F,Rに誤りが有ると判断された場合(YES)、前記ステップS4に代えて、以下のステップを実行する。

【0078】

即ち、図示は省略するが、メインデータDのビット対F,Rに誤りが無く、且つ誤り検出符号(例えば第1誤り検出符号E)のビット対F,Rの誤りか否かを判断する。そして、メインデータDのビット対F,Rに誤りがあれば前記ステップB4へ移行する一方、第1誤り検出符号Eのビット対F,Rにのみ誤りが発生していれば(図23参照)、誤りのないメインデータDのビット対F,Rをもとに、アドレスごとに新たに第1誤り検出符号を生成する。これにより、第1誤り検出符号Eのビット対F,Rの誤りを訂正することができ、その訂正データをタグ側メモリ部6cに書込むのである(前記ステップB5へ移行)。

【0079】

ここで、図23の網掛部分で示すように、メインデータDのビット対F,Rに誤りが無く、且つ第1誤り検出符号E0,0、E0,2のビット対F,Rにのみ誤りが発生するケースも生じ得る。この点、上記したように、第1誤り検出符号Eもビット対F,Rとして符号化されていることから(誤り検出符号用のビット対)、そのビットF,Rの論理和演算を行うことにより、第1誤り検出符号Eにおける誤り検出を確実に行うことができ、誤りの無いメインデータDのビット対F,Rをもとに、誤り訂正処理を確実に行うことができるのである。尚、第2誤り検出符号F,Gもビット対F,Rとして符号化してもよい。

【0080】

<第4実施形態>

図24は、本発明の第4実施形態を示す図23相当図である。

第1実施形態の誤り訂正処理、例えば図17に示すフローチャート(ステップF1〜F5)では、メインデータDをその訂正の対象として、1バイトごとに代入データをもとに誤りを訂正する例を説明した。この点、図24に示すように、メインデータD0,3のビット対F,Rと、第1誤り検出符号E0,2のビット対F,Rとに、夫々誤りが発生するケースも生じ得る。このような場合でも、ビット対F,Rの誤りが2つ以内であれば、該当するメインデータD0,3及び第1誤り検出符号E0,2の夫々のビット対F,Rに代入データを順次代入して、第1誤り検出符号E0,0F〜E0,3Rをもとに誤り検出処理を行い、誤りが非検出となるまで誤り訂正を行うことができる。つまり、誤り訂正処理は、その訂正の対象となる範囲(アドレスやビット位置)について、データの誤りパターン等に応じて適宜設定すればよい。

【0081】

<第5実施形態>

図25は、本発明の第5実施形態を示すものであり、ハンディ型タグリーダ/ライタ12Aを用いてRFIDタグ10Cから前記IDデータを取得する際の処理内容を示すフローチャートである。

【0082】

タグリーダ/ライタ12Aは、その交信領域に存在する複数のRFIDタグ10Cを識別する同時読取り処理が可能に構成されている。第5実施形態では、前述した設備24において搬入・搬出される複数の物品24bに夫々貼付されたRFIDタグ10Cの同時読取りを例とする。また、IDデータは、前述したように前記TID記憶領域200(図5参照)に書換え不能に記憶される一方、IDデータの冗長データが、前記冗長領域220における専用の領域(IDデータ用の冗長領域)に記憶されている。このIDデータ用の冗長データは、IDデータの各ビットが示す1,0の値の何れか一方を01、他方を10として符号化したビット対のうち、他方のビットR(つまり図7中、[ID]DRで示す反転データDR)を含む。また、冗長データは、例えばIDデータの反転データDRの誤りを訂正するための第1誤り検出符号(図7中、[ID]ERで示す)を含む。そして、複数のRFIDタグ10Cの同時読取りに際し、RW側制御部18は、各RFIDタグ10Cにおけるタグ側メモリ部6cのTID記憶領域200からIDデータを夫々読出す(ステップJ1)。尚、以下では1つのRFIDタグ10Cに着目して説明するが、実際には、各RFIDタグ10CについてステップJ1〜J6が夫々実行される。

【0083】

RW側制御部18は、前記ステップJ1の後、タグ側メモリ部6cの前記の冗長領域からIDデータの反転データDRと第1誤り検出符号ERとを読出して(ステップJ2)、IDデータと反転データDRとで対応するビットごとの論理和演算を行う。そして、この演算の結果、各ビットが全て1で無い場合には(ステップJ3:YES)、反転データDRに係る訂正処理を行う(ステップJ4)。この場合、誤りと判断されたビット対Rに、0或は1(代入データ)を順次代入し、当該代入データを代入した反転データDRについて第1誤り検出符号ERをもとに誤り検出処理を行う。こうして、代入データと第1誤り検出符号ERとをもとに誤りが非検出となるまで誤り訂正処理を行うことで、2ビットまでの誤りについては正しい反転データDRを得ることができる。この誤り訂正処理後の反転データDRは、タグ側メモリ部6cに書込まれ(ステップJ5)、反転データDRを反転させたデータは、タグリーダ/ライタ12Aにおいて本来のIDデータとして利用され、当該IDデータに基づき各種の処理が開始される(ステップJ6)。

【0084】

ステップJ3で検出されるエラーは、TID記憶領域200から読み出したIDデータに誤りがある場合と、冗長データ領域から読み出したその反転データDR側に誤りがある場合とがある。前者の場合、ユーザはTID記憶領域200を書き換えることができないので、ステップJ4では反転データDRに係る訂正処理を行う。そして以降は、どちらのデータに誤りがあったかに関係なく、TID記憶領域200から読み出したIDデータではなく、反転データDRを反転させたデータをIDデータとして利用する。

【0085】

以上のようにRW側制御部18は、タグ側メモリ部6cから読出したIDデータについてその冗長データDR、ERをもとに誤り検出処理を行うことから、IDデータについて、第1実施形態と同様の効果を得ることができる。また、IDデータは、RFIDタグ10Cにおける他のデータ(例えば製品コード等の識別情報)と関連付けられていることから、冗長データDR、ERをもとに誤り訂正処理を行うことで、誤り訂正処理後のIDデータと他のデータとを対応させることができ、各種の処理を支障なく実行することができる。尚、IDデータの冗長データは、ビット対Rや第1誤り検出符号ERに限定するものではなく、上記した各種の冗長データをもとに誤り検出処理及び誤り訂正処理を行うことができる。

【0086】

また、第5実施形態と同様に、以下の第6実施形態以降についても、各種の冗長データをもとに誤り検出処理及び誤り訂正を行うことができることから、前記冗長データに基づく誤り検出処理及び誤り訂正処理について冗長データの符号を省略する等、その詳細な説明を省略する。

【0087】

<第6実施形態>

図26〜図28は本発明の第6実施形態を示す。図26は、図4(a)に示すRFIDタグ10Aにおけるメモリ部6aのマップイメージに示した3種類の誤り訂正プログラムである、主誤り訂正プログラム,副誤り訂正プログラム及び簡易誤り訂正プログラムが、それぞれ誤り訂正を行う対象を示している。主誤り訂正プログラムが誤り訂正を行う対象は、データ領域101と、自身を除く一般プログラム領域102,副誤り訂正プログラム領域104及び簡易誤り訂正プログラム領域105であり、副誤り訂正プログラムが誤り訂正を行う対象は、主誤り訂正プログラム領域103のみである。

【0088】

主,副誤り訂正プログラムは、全く同じ内容のプログラムであり、スタートアップ時の初期設定において、一方が主,他方が副として動作するように指定されることで、誤り訂正を行う領域(アドレスの範囲)が決定される。主,副誤り訂正プログラムは、上記各実施形態においてデータ領域101のデータについて行った誤り検出・誤り訂正と同様の処理を、プログラム領域102〜105の各プログラムについて行うようになっている。

【0089】

また、簡易誤り訂正プログラムが誤り訂正を行う対象は、主誤り訂正プログラム領域103及び副誤り訂正プログラム領域104となっている。簡易誤り訂正プログラムは、主又は副誤り訂正プログラムが実行された結果、実行中である自身のプログラムに誤りが検出された場合に起動され、誤りがある方の訂正プログラムにおいて誤りが検出されたアドレスに、誤りが無い方の訂正プログラムにおいて対応するアドレスの内容をコピーすることで修復する。各プログラムは、例えばマルチタスクOS(オペレーティング)上で動作するようになっており、そのマルチタスクOSがタスクスイッチングを行うことで各プログラムの実行状態が切り替えられる。

【0090】

次に、第6実施形態の作用について図27及び図28を参照して説明する。図27は、主又は副誤り訂正プログラムによる処理内容を示すフローチャートである。タスクスイッチングにより主又は副何れかの誤り訂正プログラムが指定されて起動されると(ステップK1)、主,副のそれぞれに応じて、訂正対象とするアドレス領域を取得する(ステップK2)。ここでは、訂正対象とする各プログラム領域102〜105又はデータ領域101と、対応する冗長データの領域とを一括して読出す。そして、訂正の対象がデータ領域101である場合は(ステップK3:NO)、誤り検出処理を行う(ステップK7)。ここで誤りが検出されなければ(ステップK8,NO)、ステップK2に戻る。

【0091】

一方、ステップK3において訂正の対象がプログラム領域101〜105の何れかであり(YES)、それが自分自身のプログラム領域でなければ(ステップK4:NO)、訂正を行うため、動作を停止させる必要があるプログラムか否かを判断する(ステップK5)。すなわち、主誤り訂正プログラムが動作している場合は一般プログラム又は副誤り訂正プログラムか否か、副誤り訂正プログラムが動作している場合は主誤り訂正プログラムか否かを判断する。これらのプログラムである場合は(YES)、そのプログラムの起動を停止させる(ステップK6)。尚、ステップK5,K6の処理は、例えばマルチCPU等の構成において、複数のプログラムが並行して実行される可能性がある場合に必要な処理であり、シングルCPUにおいてタスクスイッチングを実行する場合には不要である。

【0092】

そして、ステップK7を実行した結果、誤りが検出されると(ステップK8:YES)、訂正対象が主又は副誤り訂正プログラムか否かを判断し(ステップK9)、訂正対象がデータ領域101であれば(NO)冗長データに基づいて誤り訂正処理を行う(ステップK15)。一方、訂正対象が主又は副誤り訂正プログラムである場合は(YES)、冗長データに基づく通常の訂正処理が可能か否かを判断し(ステップK10)、可能であれば(YES)ステップK15に移行する。尚、各プログラムについて用意する冗長データは、データ領域101のデータと同様に、ビット対,パリティ符号,多重化データ,誤り検出符号等であり、誤り検出及び誤り訂正は、データ領域101のデータと同様に実行すれば良い。

【0093】

ステップK10において、主又は副誤り訂正プログラムの通常訂正処理が不能であれば(NO)、自身のプログラムについて冗長データに基づき誤り検出処理を行う(ステップK11)。そして、誤りが無ければ(ステップK12:NO)、ステップK8で検出された対象プログラムの誤り検出アドレスに、自身のプログラムの対応するアドレスの内容を書き込んでコピーする(ステップK13)。一方、誤りがあれば(YES)、簡易誤り訂正プログラムを起動する(ステップK14)。

【0094】

図28は、簡易誤り訂正プログラムの処理内容を示すフローチャートである。先ず、主誤り訂正プログラムについて誤りが生じたアドレスを検出すると(ステップL1)、そのアドレスに対応する副誤り訂正プログラムのアドレスの内容を検出する(ステップL2)。尚、ステップL1におけるアドレスの検出は、例えばステップK12で誤りが検出された場合に、主又は副誤り訂正プログラムが、そのアドレス値を所定の領域に書き込んで記憶させておき、簡易誤り訂正プログラムがその領域を読出すことで行っても良い。また、簡易誤り訂正プログラムが、主誤り訂正プログラムについて冗長データに基づき改めて誤り検出を行っても良い。

【0095】

続くステップL3において、副誤り訂正プログラムの対応するアドレスの内容に誤りが無ければ(NO)、当該アドレスの内容を主誤り訂正プログラムの誤りが生じたアドレスにコピーして、主誤り訂正プログラムを修復する(ステップL4)。以降のステップL5〜L8については、ステップK12において副誤り訂正プログラム側に誤りが検出された場合に、対応する主誤り訂正プログラムのアドレスの内容によって副誤り訂正プログラムを修復する処理である。ステップL3,L7において、副誤り訂正プログラム,主誤り訂正プログラムに誤りがあった場合は(YES)、相手側のプログラムを修復することができないので処理を終了する。

【0096】

ここで、RFIDタグ10Aが、放射能や宇宙線等の被曝環境下や高温環境下に配置されている場合には、メモリ部6aのプログラム領域102〜105に配置されている各プログラムについても、データ領域101に配置されているデータに等しい確率で誤りが発生する。そこで、第6実施形態では、上述のように主,副,簡易誤り訂正プログラムが動作することで、一般プログラムに誤りが生じた場合の訂正・修復を図っている。すなわち、一般プログラム,副及び簡易誤り訂正プログラムに誤りが発生すると、その誤りは主誤り訂正プログラムによって訂正され、主誤り訂正プログラムに誤りが発生すると、その誤りは副誤り訂正プログラムによって訂正される。

【0097】

更に、主,副誤り訂正プログラムの一方に、冗長データでは訂正できない誤りが発生し、且つ他方のプログラムにも誤りが発生している場合には、簡易誤り訂正プログラムが起動されて、他方のプログラムの誤りが発生していない部分により修復が可能であれば、当該部分を一方の側にコピーして修復を図る。主,副誤り訂正プログラムは同一内容のプログラムであり、双方で同じプログラムステップに相当するアドレスに、同時に誤りが発生する確率は極めて低い。したがって、これらの作用により3重に誤り訂正を行うことが可能となっている。

【0098】

ここでプログラムとして実行されるオブジェクトコードは、ビット対F,Rの片側、即ち、0を01、1を10とした元のプログラムと同じ値の側である。

以上のように第6実施形態によれば、RFIDタグ10Aにおけるメモリ部6aに、一般プログラムと共に、主誤り訂正プログラム,副誤り訂正プログラム及び簡易誤り訂正プログラムを配置し、データ領域101には、これらの各プログラムについて誤り訂正を行うための冗長データを配置する。そして、主誤り訂正プログラムは、一般プログラム,副及び簡易誤り訂正プログラムに発生した誤りを訂正し、副誤り訂正プログラムは、主誤り訂正プログラムに発生した誤りを訂正し、主,副誤り訂正プログラムの一方に、冗長データでは訂正できない誤りが発生し、且つ他方のプログラムにも誤りが発生している場合には、簡易誤り訂正プログラムによって、主,副誤り訂正プログラム中の誤りが発生していない部分を他方にコピーして修復するようにした。したがって、RFIDタグ10Aが、放射能や宇宙線等の被曝環境下や高温環境下に配置されている場合でも、一般プログラムに発生した誤りを極めて高い確率で訂正することができる。

【0099】

尚、上記の誤り検出・誤り訂正処理については、タグリーダ/ライタ12Aにおいても、図4(b)に示すメモリ部19のプログラム領域303〜305に、同様の主,副,簡易誤り訂正プログラムが配置されているので、プログラム領域302〜305及びデータ領域301について同様の処理が行われる。

【0100】

<第7実施形態>

図29及び図30は、本発明の第7実施形態を示す。図29は図6(a)相当図であり、ここではメインデータ領域210と、第1誤り検出符号(第1冗長データ)領域221に代わる第3冗長データ領域223とを示しており、第1誤り検出符号E,第2誤り検出符号F,Gとは異なる第3誤り検出符号データを用いる場合を説明する。図29及び図30に示す各ビットの図示パターン(網掛け等)は、同じパターンのビットが同じビット列に属することを示している。

【0101】

例えば図29では、1アドレス増加する毎に、ビット位置を1ビットずつずらしたビットをとることで、8ビットを組み合わせたビット列を構成し、その8ビットデータについて4ビットの誤り検出符号を付加する(第3誤り検出符号)。例えば、データD0,0、D1,1、D2,2、〜D7,7が同一のビット列に属しており、このビット列に対して、同様に、アドレスが増加する毎にビット位置を1ビットずつずらした配列で、冗長データE0,0、E1,1、E2,2、E3,3が生成されている。また、第2ビットのデータD0,1から始まるビット列については、末尾のビットは第1ビットのデータD,0となり、第3ビットのデータD0,2から始まるビット列については、7ビット目は第1ビットのデータD6,0,末尾のビットは第2ビットのデータD7,1となる。

【0102】

図30では、2アドレスが増加する毎に、ビット位置を1ビットずつずらしたビットをとることで、8ビットを組み合わせたビット列を構成している。例えば、データD0,0、D2,1、D6,3、D0,4、D2,5、D4,6、D6,7が同一のビット列に属しており、このビット列に対して、同様に、2アドレスが増加する毎にビット位置を1ビットずつずらした配列で、冗長データE0,0、E2,1、E4,2、E6,3が生成されている。すなわち、「アドレスが増加する毎に」と言ってもその範囲は1ワードのデータビット数で制限され、最初のビットを取得するアドレスから「+7」を超えることはなく、「+7」を超える分は「8」を減じたアドレスに折り返される。

【0103】

第3誤り検出符号を付すためのビット列を構成するパターンは、図29,図30に示すものに限らない。例えば1アドレスが増加する毎に、ビット位置を2ビットずつ,或いは3ビットずつずらしたビットをとっても良い。

【0104】

また、図29,図30では説明の都合上、第3冗長データ領域223を図6(a)に示す第1冗長データ領域221に置き換えて示しているが、実際にはこれらは異なるデータ領域であり独立に存在するので、第3誤り検出符号は、第1,第2誤り検出符号と併用して誤り検出に使用することが可能である。そして、第3冗長データ領域223については、必ずしも対応するビット列と同様の配列にする必要はなく、例えば第1誤り検出符号と同様の配列にしても良い。

【0105】

以上のように、第7実施形態によれば、アドレスが増加する毎にビット位置を1ビット以上ずつずらしてなるビット列について、第3誤り検出符号を付すようにした。これにより、データ領域210において、通常のデータ配列について誤りが連続するバースト誤りが発生しているとしても、上記のビット列に関しては、誤りが生じているビットの数を少なくすることができる。したがって、第3誤り検出符号に基づき誤り検出を行い、誤りを訂正すれば、より多くの誤りを訂正できる可能性を向上させることができる。

【0106】

本発明は上記し且つ図面に記載した実施形態にのみ限定されるものではなく、上記したデータ管理方法について、制御部によりデータの読取り及び書込みが行われる不揮発性記憶手段を備えた各種のメモリ装置に適用することができる。

【0107】

上記実施形態のタグリーダ/ライタ12は、タグ側メモリ部6cから読出したデータについて誤り検出処理や誤り訂正処理を行う構成としたが、自身のメモリ部19に係るデータについて誤り検出処理や誤り訂正処理を行うようにしてもよい。即ち、タグリーダ/ライタ12も、内蔵するマスタ側記憶手段たるメモリ部19に、前記データエラーが頻発する環境下で用いるケースも想定されることから、データと共に当該データの誤りを訂正するための冗長データを記憶させておく。そして、冗長データとして上記実施形態と同様のビット対等を用いて誤り検出処理や誤り訂正処理を行うことにより、タグリーダ/ライタ12についても、データエラーの発生を防止し且つ正常に機能させることができる。

【0108】

また、マスタ側記憶手段たるメモリ部19において、前述した主誤り訂正プログラム及び副誤り訂正プログラム、並びにこれらの誤り訂正プログラムの誤りを訂正するための冗長データ等について、タグリーダ/ライタ12自身が正常に機能するためのデータとして構成することで、タグリーダ/ライタ12もRFIDタグ10Cと同様に信頼性を高めることができる。

【0109】

ここで、例えばハンディ型タグリーダ/ライタ12Aの電源が投入された時、制御部18は、メモリ部19から読出したデータのうち少なくとも当該制御部18により実行される制御プログラムについてその冗長データをもとに誤り検出処理を行うように構成する。これによれば、メモリ部19にデータエラーが発生していても、制御プログラムを実行する前に、そのプログラムの誤りを優先的に検出して訂正することができ、正常に起動させることができる。

【0110】

また、アクティブ型のRFIDタグ10Aの電源が投入された時、制御部5aは、自身のメモリ部6aから読出したデータのうち少なくとも当該制御部5aにより実行される制御プログラムについてその冗長データをもとに誤り検出処理を行うように構成する。これによれば、RFIDタグ10Aにおいて、上記と同様に制御プログラムを実行する前に、そのプログラムの誤りを優先的に検出して訂正することができ、正常に起動させることができる。

【0111】

例えば前記RFIDタグ10Cは別個に、他のRFIDタグ10Cを備え、ビット対F,Rのうちの一方のビットFを、一方のRFIDタグ10Cのタグ側メモリ部6cに書込み、他方のビットRを、他方のRFIDタグ10Cのタグ側メモリ部6cに書込む。そして、RW側制御部18は、双方のタグ側メモリ部6c,6cからデータを読出することにより、ビット対F,Rに基づく誤り検出処理を行う。これによれば、一方のタグ側メモリ部6cには本来のデータが記憶され、そのデータを反転した反転データが他方のタグ側メモリ部6cに記憶されることから、一対のRFIDタグ10Cを用いて第1実施形態と同様の効果を得ることができる。

【0112】

RFIDタグ10の種類10A〜10Cとタグリーダ/ライタ12の種類12A,12Bとの各組合わせ(図2参照)に応じて、RFIDタグ10A側が主体となり、或はタグリーダ/ライタ12A,12B側が主体となって、上記した各種の処理を実行することで、RFIDタグ10とタグリーダ/ライタ12との双方について信頼性を高めることのできるデータ管理方法を提供することができる。

【0113】

また、前記ハミング符号の他、拡張ゴレイ符号を用いて誤り検出処理を行い、或は誤り訂正処理を行うようにしてもよい。具体的には、例えば12ビットのメインデータに対して、エラー訂正用ビットの数を12として24ビットの符号語に置き換える拡張ゴレイ符号を形成する。この場合、7ビット誤り検出機能を備えるか、或は4ビット誤り検出機能及び3ビット誤り訂正機能を備える等、適宜設定することができる。よって、ハミング符号に比し、多くの記憶領域が必要となるが、誤り検出機能或は誤り訂正機能を高めることができる。

【0114】

上記したデータ管理システム11或はデータ管理方法は、制御部によってデータの読取り及び書込みが行われる不揮発性記憶手段を有する電子機器や記憶装置一般に適用できるものである。即ち、電子機器や記憶装置としては、データ及びプログラムと共に当該データ等の誤りを訂正するための前記冗長データが記憶された不揮発性記憶手段と、前記不揮発性記憶手段に対するデータの読取り及び書込みを制御する制御部とを備えたものであればよい。従って、電子機器や記憶装置としては、マスタとスレーブとの関係にあるRFIDタグやタグリーダ/ライタに限定するものではなく、パソコンや他の通信機器等において、上記した各種の冗長データをもとに誤り検出処理や誤り訂正処理を行うことで、各実施形態と同様の効果を得ることができる。

【0115】

この他、本発明は、上記ステップD1〜D3の処理を省略したりする等、適宜変更して実施することができ、これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0116】

図面中、2a〜2cはアンテナ(無線通信手段)、5a〜5cはスレーブ側制御部、6a〜6cは不揮発性記憶手段、7a〜7cは通信部(無線通信手段)、10,10A〜10CはRFIDタグ(スレーブ、記憶装置)、11はデータ管理システム、12,12A,12Bはタグリーダ/ライタ(マスタ、電子機器、記憶装置)、18はマスタ側制御部、20は通信部(無線通信手段)、22はアンテナ(無線通信手段)を示す。

【特許請求の範囲】

【請求項1】

マスタとスレーブとの間で無線通信手段を介して非接触で交信されるデータを管理するためのデータ管理システムにおいて、

前記スレーブは、データと共に当該データの誤りを訂正するための冗長データが記憶された不揮発性記憶手段と、当該スレーブ全体の制御を行うスレーブ側制御部とを備え、

前記マスタは、前記無線通信手段を介したデータの読出し及び書込みを制御するマスタ側制御部を備え、

前記スレーブ側制御部又は前記マスタ側制御部によって、前記不揮発性記憶手段から読出したデータについて前記冗長データをもとに誤り検出処理を行い、その検出処理において誤りが検出された場合には誤り訂正処理を行う構成にあって、

前記冗長データは、データの各ビットが示す0,1の値の何れか一方を01、他方を10とするビット対として符号化したデータを含み、

前記スレーブ側制御部又は前記マスタ側制御部は、前記誤り検出処理において、前記不揮発性記憶手段から読出したデータについて前記ビット対をなす双方のビットの値が0であれば前記ビット対に誤りが有ると判断することを特徴とするデータ管理システム。

【請求項2】

前記ビット対のうち一方のビットと他方のビットは、前記不揮発性記憶手段において相互に異なるアドレスの同じビット位置に記憶されることを特徴とする請求項1記載のデータ管理システム。

【請求項3】

前記冗長データは、データごとに生成される第1誤り検出符号と、前記データの同じビット位置ごとに生成される第2誤り検出符号とのうち少なくとも何れかの誤り検出符号を含み、

前記スレーブ側制御部又は前記マスタ側制御部は、前記ビット対に基づく誤り検出処理と、前記誤り検出符号に基づく誤り検出処理との実行が可能に構成されていることを特徴とする請求項1又は2記載のデータ管理システム。

【請求項4】

前記スレーブ側制御部又は前記マスタ側制御部は、前記ビット対をなす双方のビットの論理和演算に基づき誤りが検出されると、その誤りが検出された前記ビット対にデータ0,1(これらを代入データと称す)を代入して前記誤り検出符号をもとに誤り検出処理を行い、誤りが非検出となるまで誤り訂正処理を行うことを特徴とする請求項3記載のデータ管理システム。

【請求項5】

前記スレーブ側制御部又は前記マスタ側制御部は、前記ビット対をなす双方のビットの論理和演算に基づき誤りが検出されると、

誤りが検出されたアドレスごとに前記代入データと前記第1誤り検出符号とをもとに誤りが非検出となるまで誤り訂正処理を行う第1誤り訂正処理と、

同じビット位置の列ごとに前記代入データと前記第2誤り検出符号とをもとに誤りが非検出となるまで誤り訂正処理を行う第2誤り訂正処理とを実行することを特徴とする請求項4記載のデータ管理システム。

【請求項6】

前記誤り検出符号は、アドレスを1アドレス以上一定のパターンでずらし、且つビット位置を1ビット以上一定のパターンでずらしてなるビット列について生成される第3誤り検出符号を含むことを特徴とする請求項3乃至5の何れかに記載のデータ管理システム。

【請求項7】