データ転送制御装置及び電子機器

【課題】パラレルATAとシリアルATAのバスブリッジ機能を実現しながら初期化シーケンス処理についても適正に実現する。

【解決手段】データ転送制御装置は、PATAバスに接続されるPATAI/F10と、SATAバスに接続されるSATAI/F50と、転送シーケンス制御を行うシーケンスコントローラ30を含む。シーケンスコントローラ30は、SATAのデバイス4に代わって初期化シーケンス管理を代行する初期化シーケンス管理部34を含む。初期化シーケンス管理部34は、マスタ・スレーブ設定端子(CSEL)によりデータ転送制御装置がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行い、マスタ・スレーブ設定端子によりデータ転送制御装置がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行う。

【解決手段】データ転送制御装置は、PATAバスに接続されるPATAI/F10と、SATAバスに接続されるSATAI/F50と、転送シーケンス制御を行うシーケンスコントローラ30を含む。シーケンスコントローラ30は、SATAのデバイス4に代わって初期化シーケンス管理を代行する初期化シーケンス管理部34を含む。初期化シーケンス管理部34は、マスタ・スレーブ設定端子(CSEL)によりデータ転送制御装置がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行い、マスタ・スレーブ設定端子によりデータ転送制御装置がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データ転送制御装置及び電子機器に関する。

【背景技術】

【0002】

近年、ストレージデバイス等のシリアルインターフェースとして、シリアルATA(Serial AT Attachment)と呼ばれる規格が脚光を浴びている。このシリアルATAは、パラレルATA(IDE)との間のソフトウェアレベルでの互換性を備えた規格である。そして最初の規格であるシリアルATA Iのデータ転送速度は1.5Gbpsであったが、次の規格であるシリアルATA II Gen2ではデータ転送速度が3.0Gbpsに高速化している。このシリアルATAを用いれば、電子機器が内蔵する回路基板間の配線本数を減らすことができ、電子機器のコンパクト化を図れる。

【0003】

ところが、電子機器のホスト(ホストデバイス、ホスト基板)は、パラレルATA(以下、適宜、PATAと呼ぶ)のインターフェース(以下、適宜、I/Fと呼ぶ)は備えているが、シリアルATA(以下、適宜、SATAと呼ぶ)のI/Fについては備えていないものが多い。このため、PATAI/Fのみを備えた既存のホストに対しては、SATAのデバイスを接続できないという問題がある。従って、PATAとSATAのブリッジ機能を有するデータ転送制御装置の提供が望まれる。

【0004】

しかしながら、このようなブリッジ機能を有するデータ転送制御装置において、SATAバスに接続されるSATAデバイスには、マスタ、スレーブの区別の概念が無く、PATAシステムに必要な初期化シーケンス管理機能を有しない。従って、単にSATAデバイスをデータ転送制御装置を介してPATAデバイスにブリッジ接続しただけでは、PATAにおける初期化シーケンスの処理主体が無く、PATAにおけるマスタ、スレーブの使い分けを実現できないという課題がある。

【特許文献1】特開2005−346123号公報

【特許文献2】特開2006−121621号公報

【特許文献3】特開2006−18428号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、以上のような課題に鑑みてなされたものであり、本発明に係る幾つかの態様によれば、パラレルATAとシリアルATAのバスブリッジ機能を実現しながら初期化シーケンス処理についても適正に実現できる。

【課題を解決するための手段】

【0006】

本発明は、パラレルATAとシリアルATAのバスブリッジ機能を有するデータ転送制御装置であって、パラレルATAバスに接続され、ホストとの間のインターフェースを行うパラレルATAインターフェースと、シリアルATAバスに接続され、初期化シーケンス管理機能を有しないシリアルATAのデバイスとの間のインターフェースを行うシリアルATAインターフェースと、転送シーケンス制御を行うシーケンスコントローラを含み、前記シーケンスコントローラは、前記シリアルATAの前記デバイスに代わって初期化シーケンス管理を代行する初期化シーケンス管理部を含み、前記初期化シーケンス管理部は、マスタ・スレーブ設定端子によりデータ転送制御装置がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行い、前記マスタ・スレーブ設定端子によりデータ転送制御装置がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行うデータ転送制御装置に関係する。

【0007】

本発明によれば、シリアルATAデバイスが初期化シーケンス管理機能を有しない場合にも、この初期化シーケンス管理を代行して、スレーブ検知等の初期化シーケンス処理を実行できるようになる。そしてこのようにシリアルATAのデバイスに代わって初期化シーケンス処理を代行すれば、マスタ、スレーブの区別の概念の無いシリアルATAのデバイスを、マスタ、スレーブの区別が可能なパラレルATAのデバイスのように扱うことが可能になると共に、パラレルATAに準拠した適正な初期化シーケンス処理を実現できる。

【0008】

また本発明では、前記パラレルATAインターフェースは、タスクファイル・レジスタを有し、前記シリアルATAインターフェースは、前記タスクファイル・レジスタとの間でレジスタ値が転送されるシャドウ・タスクファイル・レジスタを含み、前記シーケンスコントローラは、データ転送制御装置がマスタ側に設定されているときに、前記ホストがマスタへのATAコマンドを発行した場合には、前記タスクファイル・レジスタのレジスタ値をそのまま前記シャドウ・タスクファイル・レジスタに転送し、データ転送制御装置がスレーブ側に設定されているときに、前記ホストがスレーブへのATAコマンドを発行した場合には、前記タスクファイル・レジスタのデバイス/ヘッドレジスタのDEVビットをマスタ設定に書き換えて前記タスクファイル・レジスタのレジスタ値を前記シャドウ・タスクファイル・レジスタに転送してもよい。

【0009】

このようにすれば、マスタ・スレーブ設定端子の状態に応じた適正な値に、デバイス/ヘッドレジスタのDEVビットが書き換えられるため、データ転送制御装置が例えばスレーブ側に設定された場合にも、ホストから、自身をマスタと認識しているシリアルATAデバイスに対して、コマンド、パラメータ等の適正な転送処理を実現できる。

【0010】

また本発明では、前記シーケンスコントローラは、データ転送制御装置がマスタ側に設定されているときに、前記ホストからのATAコマンドに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合には、前記シャドウ・タスクファイル・レジスタのレジスタ値を前記タスクファイル・レジスタにそのままに転送し、データ転送制御装置がスレーブ側に設定されているときに、前記ホストからのATAコマンドに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合には、前記シャドウ・タスクファイル・レジスタのデバイス/ヘッドレジスタのDEVビットをスレーブ設定に書き換えて前記シャドウ・タスクファイル・レジスタのレジスタ値を前記タスクファイル・レジスタに転送してもよい。

【0011】

このようにすれば、マスタ・スレーブ設定端子の状態に応じた適正な値に、デバイス/ヘッドレジスタのDEVビットが書き換えられるため、データ転送制御装置が例えばスレーブ側に設定された場合にも、自身をマスタと認識しているシリアルATAデバイスから、ホストに対して、ステータス等の適正な転送処理を実現できる。

【0012】

また本発明では、前記パラレルATAインターフェースは、ATAコマンドが前記タスクファイル・レジスタに書き込まれた場合に、コマンドライト検出信号をアクティブにし、前記シーケンスコントローラは、前記コマンドライト検出信号がアクティブになった場合に、前記タスクファイル・レジスタから前記シャドウ・タスクファイル・レジスタへのレジスタ値の転送処理及びDEVビットの書き換え処理を行ってもよい。

【0013】

このようなコマンドライト検出信号を利用すれば、少ない信号線でレジスタ値の転送処理やDEVビットの書き換え処理を実現できる。

【0014】

また本発明では、前記シリアルATAインターフェースは、前記パラレルATAバスを介して前記ホストがATAコマンドを発行した場合に、発行された前記ATAコマンドを含むレジスタFISを前記シリアルATAバスを介して前記デバイスに送信し、前記シーケンスコントローラは、前記レジスタFISに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合に、前記ホストから発行された前記ATAコマンドの転送シーケンス制御として、受信したFISの種類に応じた転送シーケンス制御を行ってもよい。

【0015】

このようにすれば、データ転送制御装置は、ホストが発行したATAコマンドの詳細な内容をデコードすることなく、ATAコマンドを含むレジスタFISをそのままデバイスに送信できる。そしてレジスタFISに対してデバイスが返却して来たFISの種類によって、転送シーケンスが制御される。従って、ATAコマンドのデコーダ回路を節約でき、データ転送制御装置の小規模化を図れる。また、新規コマンドの追加が発生しても、これに容易に対応できるようになる。

【0016】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISがPIOセットアップFISであり、PIOセットアップFISにより指定される転送方向がリード方向である場合には、PIOリードの転送シーケンス制御を行い、PIOセットアップFISにより指定される転送方向がライト方向である場合には、PIOライトの転送シーケンス制御を行ってもよい。

【0017】

このようにすれば、受信したFISがPIOセットアップか否かや、PIOセットアップFISで指定される転送方向を判断するだけで、PIOリードやPIOライトの転送シーケンスを制御できるようになる。

【0018】

また本発明では、前記シーケンスコントローラは、受信したPIOセットアップFISのパラメータに基づいて、転送方向、転送種別を設定してもよい。

【0019】

このようにすれば、転送方向、転送種別を設定した適正な転送シーケンス制御を実現できる。

【0020】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISがデータFISである場合には、DMAリードの転送シーケンス制御を行ってもよい。

【0021】

このようにすれば、受信したFISがデータFISか否かを判断するだけで、DMAリードの転送シーケンスを制御できるようになる。

【0022】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISがDMAアクティベートFISである場合には、DMAライトの転送シーケンス制御を行ってもよい。

【0023】

このようにすれば、受信したFISがDMAアクティベートFISか否かを判断するだけで、DMAライトの転送シーケンスを制御できるようになる。

【0024】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISが、デバイスからホストへのレジスタFISである場合には、ノーデータコマンドであると判断してもよい。

【0025】

また本発明は、上記のいずれかに記載のデータ転送制御装置と、前記データ転送制御装置に接続される前記ホストと、前記データ転送制御装置に接続される前記デバイスとを含む電子機器に関係する。

【発明を実施するための最良の形態】

【0026】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0027】

1.データ転送制御装置の構成

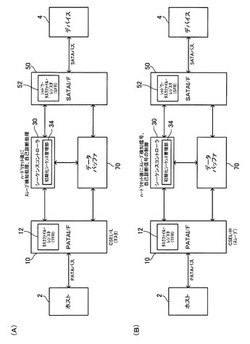

図1(A)、図1(B)に本実施形態のデータ転送制御装置の構成例を示す。このデータ転送制御装置はPATA(Parallel AT Attachment)とSATA(Serial AT Attachment)のバスブリッジ機能を有する。

【0028】

なお本実施形態のデータ転送制御装置は図1(A)、図1(B)の構成に限定されず、その構成要素の一部(例えばデータバッファ)を省略したり、他の構成要素(例えば外部I/F回路、CPU、タイマ)を追加するなどの種々の変形実施が可能である。例えば本実施形態のデータ転送制御装置は、PATAとSATAのバスブリッジ機能以外にも、PATAとUSB、PATAとSD(Secure Digital)カードインターフェス、PATAとCE−ATAのバスブリッジ機能を実現できるようにしてもよい。

【0029】

PATAI/F10(パラレルATAインターフェース)は、PATAバス(ATAバス、IDEバス)に接続され、ホスト2(ホストデバイス)との間のインターフェースを行う。具体的にはPATAI/F10は、ホスト2が有するホスト側のPATAI/FにPATAバスを介して接続される。そしてATAで規格化された後述する各種信号によりやり取りを行い、PATA(IDE)のデータ転送を実現する。またPATAI/F10は、データバッファ70を介したSATAI/F50との間のデータ転送制御も行う。このPATAI/F10は、PATAとSATAのブリッジ用に擬似的(仮想的)に設けられたタスクファイル・レジスタ12(以下、適宜、TFRと呼ぶ)を含むことができる。

【0030】

なおホスト2としては、例えばCPU、MPU、DSPなどのプロセッサや、専用制御ICや、これらのプロセッサ又は専用制御ICが実装されたホスト回路基板などが考えられる。またデバイス4としては、ハードディスクドライブ(HDD)、光ディスクドライブ(CD、DVD)、磁気ディスクドライブなどのSATAI/Fを備える各種デバイスが考えられる。

【0031】

SATAI/F50(シリアルATAインターフェース)は、SATAバス(高速シリアルバス)に接続され、SATAのデバイス4との間のインターフェースを行う。具体的にはSATAI/F50は、デバイス4が有するデバイス側のSATAI/Fに接続され、小振幅の差動信号によりやり取りを行い、SATAのデータ転送を実現する。またSATAI/F50は、データバッファ70を介したPATAI/F10との間のデータ転送制御も行う。このSATAI/F50は、SATA規格のシャドウ・タスクファイル・レジスタ52(以下、適宜SFRと呼ぶ)を含むことができる。

【0032】

シーケンスコントローラ30は転送のシーケンス制御を行う。具体的には、PATAとSATAのブリッジ機能を実現するために、PATAI/F10、SATAI/F50、データバッファ70の間のデータ転送のシーケンス制御を行ったり、レジスタ値の転送シーケンス制御を行う。

【0033】

データバッファ70は、ホスト2(PATAI/F)、デバイス4(SATAI/F)の間で転送されるデータのバッファリングを行う。そしてPATA側とSATA側のクロック周波数の差を吸収するための緩衝用のバッファ(FIFO)として機能する。即ちPATA側のクロック周波数が例えば50MHz(或いは60MHz)で、SATA側のクロック周波数が例えば37.5MHzである場合に、データバッファ70を設けることでこのクロック周波数の差を吸収できる。このデータバッファ70は、例えば50MHz(第1の周波数)でデータが入出力されるPATAI/F10側の第1のポートと、例えば37.5MHz(第2の周波数)でデータが入出力されるSATAI/F50側の第2のポートとを有するデュアルポートのメモリ(RAM)などにより実現できる。

【0034】

図1(A)、図1(B)の構成によれば、ホスト2がPATAI/Fしか備えていない場合にも、SATAI/Fを有するデバイス4をデータ転送制御装置を介してホスト2に接続できる。従って、ホスト2のファームウェア、ソフトウェアとして、既存のPATA(IDE)用のファームウェア、ソフトウェアを使用できる。これにより電子機器の開発期間の短縮化や低コスト化を図れる。またデバイス4として、市場供給量が多い大容量のHDDをホスト2に接続できるようになり、電子機器の内蔵HDDの大容量化を図れる。

【0035】

またホスト2が搭載される回路基板とデバイス4が搭載される回路基板の間を、シリアルバスであるSATAバスで接続できるため、回路基板間の配線本数を減らすことができ、電子機器のコンパクト化を図れる。

【0036】

そして実施形態では図1(A)、図1(B)に示すように、シーケンスコントローラ30が、初期化シーケンス管理機能を有しないSATAのデバイス4に代わって初期化シーケンス管理を代行する初期化シーケンス管理部34を含む。そして初期化シーケンス管理部34は、ハードリセット(ハードウェアリセット)等の後に初期化シーケンス処理を実行する。

【0037】

例えばSATAのデバイス4にはマスタ、スレーブの区別の概念が無いため、SATAのデバイス4はスレーブ検知等の初期化シーケンス管理機能を有しない。従って、PATAとSATAのブリッジ機能を有するデータ転送制御装置のSATAバスにSATAのデバイス4を接続する場合に、初期化シーケンス管理を行う処理主体が無くなってしまう。

【0038】

この点、図1(A)、図1(B)では初期化シーケンス管理部34が、初期化シーケンス管理機能を有しないSATAのデバイス4に代わって初期化シーケンス管理を代行して、初期化シーケンス処理を実行する。

【0039】

具体的には、図1(A)に示すように、データ転送制御装置に設けられたCSEL端子(マスタ・スレーブ設定端子)が例えばLレベルに設定され、データ転送制御装置がマスタ側に設定された場合には、初期化シーケンス管理部34は、ハードリセット後にスレーブ検知処理と自己診断処理を行う。

【0040】

一方、図1(B)に示すように、CSEL端子が例えばHレベルに設定され、データ転送制御装置がスレーブ側に設定された場合には、初期化シーケンス管理部34は、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行う。

【0041】

このようにすれば、ホスト2上で動作するドライバソフトウェアは、マスタ、スレーブの区別の概念の無いSATAのデバイス4を、マスタ、スレーブの区別が可能なPATAのデバイスのように扱うことが可能になり、利便性を大幅に向上できる。

【0042】

2.詳細な構成例

図2にデータ転送制御装置の詳細な構成例を示す。PATAI/F10はタスクファイル・レジスタTFR12、転送コントローラ14を含む。ここでTFR12は、PATAとSATAのバスブリッジ用に擬似的に設けられたレジスタである。このTFR12を設けることで、ホスト2は、SATAのデバイス4を、あたかもPATAのデバイスのように扱ってデータのリードやライトを行うことが可能になる。即ちホスト2は、既存のPATA用のファームウェアやソフトウェアを使用して、SATAのデバイス4を制御できるようになる。

【0043】

転送コントローラ14は、PATA用の信号XCS〜XPDIAGを用いてPATA(IDE)のインターフェースを実現したり、データ転送用の制御信号を用いて、データバッファ70との間のデータ転送を制御する。

【0044】

データバッファ70は、メモリコントローラ72、FIFOメモリ(FIFORAM)74を含む。メモリコントローラ72は、FIFOメモリ74のデータの書き込み制御や読み出し制御を行う。またPATAI/F10やSATAI/F50との間で、例えばREQ信号やACK信号などの制御信号を用いたデータ転送制御を行う。

【0045】

SATAI/F50は、シャドウ・タスクファイル・レジスタSFR52、トランスポートコントローラ110、リンクコントローラ150、物理層回路200を含む。

【0046】

トランスポートコントローラ110、リンクコントローラ150、物理層回路200は、各々、SATA規格のトランスポート層、リンク層、物理層の処理を行う回路である。

【0047】

シャドウ・タスクファイル・レジスタSFR52はSATAで規格化されているレジスタである。即ちSATAでは、従来のPATA(IDE)との間でソフトウェアレベルでの互換性が維持されており、タスクファイル・レジスタが2つ存在することが特徴になっている。即ちホスト(HBA)側のシャドウ・タスクファイル・レジスタとデバイス側の本来のタスクファイル・レジスタである。

【0048】

一方、PATAI/F10に設けられたTFR12はSATAで規格化されるレジスタではなく、PATAとSATAのブリッジ用に設けられた擬似的なレジスタである。ホスト2は、TFR12をPATAのタスクファイル・レジスタとして認識してアクセスし、レジスタ値を書き込んだり、レジスタ値を読み出す。すると本実施形態のデータ転送制御装置が、TFR12のレジスタ値をSFR52に転送したり、SFR52のレジスタ値をTFR12に転送するなどの処理を行う。

【0049】

このようにすれば、ホスト2が、PATAのTFR12にレジスタ値を書き込むと、そのレジスタ値がSATAのSFR52に転送されて書き込まれ、SATAバスを介してFIS(Frame Information Structure)によりデバイス4に転送されるようになる。またデバイス4からのFISによりSFR52に書き込まれたレジスタ値が、TFR12に転送されてホスト2に読み出されるようになる。従ってホスト2は、SATAのデバイス4を、あたかもPATAのデバイスのように扱ってデータのリードやライトを行うことが可能になり、PATAとSATAのブリッジ機能を効率良く実現できる。

【0050】

なおTFR12とSFR52の間のレジスタ値の転送は次のような手法により実現できる。即ちTFR12のレジスタ群のビット(全ビット)とSFR52のレジスタ群のビット(全ビット)を、シーケンスコントローラ30を介して信号線により接続しておく。そしてレジスタ値の転送を行う場合には、シーケンスコントローラ30が転送トリガ信号を生成し、この転送トリガ信号に基づいて、TFR12のレジスタ値をSFR52に転送したり、SFR52のレジスタ値をTFR12に転送すればよい。

【0051】

3.PATAI/F

次に、PATAI/F10のデータ転送処理について、図2の構成及び図3(A)〜図4(B)の信号波形を用いて説明する。

【0052】

XCS[1:0]は、PATAの各レジスタにアクセスするために使用するチップセレクト信号である。DA[2:0]は、データ又はデータポートにアクセスするためのアドレス信号である。DMARQ、XDMACKは、DMA転送に使用される信号である。データ転送の準備が整った時にデバイス側がDMARQをアクティブ(アサート)にし、これに応答して、ホスト側がXDMACKをアクティブにする。

【0053】

XDIOWは、レジスタ又はデータポートの書き込み時に使用するライト信号である。XDIORは、レジスタ又はデータポートの読み出し時に使用するリード信号である。IORDYは、デバイス側のデータ転送の準備が整っていない時のウェイト信号等に使用される。

【0054】

INTRQは、デバイス側が、ホスト側に対して割り込みを要求するために使用される信号である。このINTRQがアクティブになった後、ホスト側がデバイス側のTFR12のステータスレジスタの内容を読むと、所定時間後にデバイス側はINTRQを非アクティブ(ネゲート)にする。このINTRQを用いることで、デバイス側は、コマンド処理の終了をホスト側に通知できる。

【0055】

図3(A)、図3(B)は、PIO(Programmed I/O)リード、PIOライトの信号波形例である。PATAのTFR12のステータスレジスタのリードは図3(A)のPIOリードにより行い、コマンドレジスタへのライトは図3(B)のPIOライトにより行う。例えばホスト2によるATAコマンドの発行は、PIOライトにより実現できる。

【0056】

図4(A)、図4(B)は、DMAリード、DMAライトの信号波形例である。データ転送の準備ができると、デバイス側(データ転送制御装置)が、DMARQをアクティブにする。そして、それを受けて、ホスト側が、XDMACKをアクティブにして、DMA転送を開始する。その後、XDIOR(リード時)又はXDIOW(ライト時)を使用して、データDD[15:0]のDMA転送を行う。

【0057】

4.SATAI/F

次にSATAI/F50のデータ転送処理について説明する。図5はSATAの送信側のデータ転送処理の流れを示し、図6は受信側のデータ転送処理の流れを示している。

【0058】

図5に示すように送信側のトランスポートコントローラ(トランスポート層)では、シャドウ・タスクファイル・レジスタに書き込まれたコマンドやデータポートに入力されたデータによりFIS(Frame Information Structure)が生成される。ここでFISは、フレームのペイロード部であり、Dword(32ビット)単位で構成される。またフレームは、ホストとデバイスの間で交換される情報ユニットであり、SOF(Start Of Frame)プリミティブと、FISと、FISに対して計算されたCRC(Cyclic Redundancy Check)と、EOF(End Of Frame)プリミティブにより構成される。

【0059】

送信側のリンクコントローラでは、FISに対するCRCが演算されてFISの最後尾に付加される。そしてFIS及びCRCとスクランブルデータとの排他的論理和(XOR)をとるスクランブル処理が行われる。このようにスクランブルされたFIS及びCRCに対して、8b/10bのエンコードが行われる。ここで8b/10bエンコードは、8ビットのデータを10ビットの伝送キャラクタに変換するデータ伝送符号化のアルゴリズムであり、符号列内の1と0の数を揃え、連続的な伝送を保証する。そして8b/10bエンコード後のFIS及びCRCに対してSOF、EOFなどのプリミティブが付加される。

【0060】

送信側の物理層回路では、リンクコントローラからのパラレルデータがシリアルデータに変換され、小振幅の差動信号としてSATAバスに送信される。

【0061】

図6に示すように受信側の物理層回路では、SATAバスを介して受信したシリアルデータがパラレルデータに変換される。

【0062】

受信側のリンクコントローラでは、FIS及びCRCに付加されたプリミティブに対するデコードが行われる。またFIS及びCRCに対する8b/10bのデコードが行われる。即ち10ビットの伝送キャラクタが8ビットのデータに変換される。次に、スクランブルされたFIS及びCRCとスクランブルデータとの排他的論理和をとるデスクランブル処理が行われる。そしてFISの最後尾に付加されたCRCがチェックされる。

【0063】

受信側のトランスポートコントローラでは、FISのコマンドがシャドウ・タスクファイル・レジスタに書き込まれ、ステータスや割り込みが出力されると共に、データがデータポートを介して出力される。

【0064】

なお図7にATAのタスクファイル・レジスタのフォーマット例を示す。タスクファイル・レジスタはコントロールブロックレジスタとコマンドブロックレジスタを有し、チップセレクト信号XCS0、XCS1が、Hレベル(ネゲート)、Lレベル(アサート)である場合にはコントロールブロックレジスタが選択され、Lレベル、Hレベルである場合にはコマンドブロックレジスタが選択される。またコマンドブロックレジスタには、ステータスレジスタ(Status)やATAコマンドレジスタ(ATA Command)が設けられる。

【0065】

また図8(A)〜図8(D)に、SATAI/F50により送受信されるFISのフォーマット例を示す。図8(A)はホストからデバイスへのレジスタFIS、図8(B)はデバイスからホストへのレジスタFIS、図8(C)はPIOセットアップFIS、図8(D)はDMAアクティベートFISのフォーマットである。

【0066】

5.初期化シーケンス

次に、本実施形態の初期化シーケンス処理手法について具体的に説明する。

【0067】

5.1 CSEL端子

PATAデバイスのシステムでは、PATAバスに対して最大で2台のデバイスを接続でき、これらの2台のデバイスのうちの一方がマスタになり、他方がスレーブになる。そして各デバイスは、自身がマスタなのかスレーブなのかを、ジャンパピンの設定又はケーブルセレクトの設定により判断する。またPATAバスに対して2台のデバイスを接続した場合にも、同じアドレスが2台のデバイスで共有して使用される。従って、ATAレジスタ(タスクファイル・レジスタ)に対してホストから書き込み動作があった場合には、マスタ及びスレーブの両方のデバイスが、PATAのデータDD[15:0](図2参照)のバスからそのデータを受け取り、各デバイスは、DEVビット等に基づいて、そのデータが自身に宛てたデータなのか否かを判断する。またATAレジスタに対するホストからの読み出し動作があった場合には、マスタ、スレーブの各デバイスは、その時点でのDEVビットの状態と自身のデバイス番号を比較し、一致した場合にのみ、アクセスされたATAレジスタの内容をデータDD[15:0]のバスに出力する。

【0068】

このようにPATAデバイスにおいては、マスタ、スレーブの区別の概念があり、例えばATAのマスタ側にHDD等のデバイスを接続し、スレーブ側にCD、DVD等の光ディスクドライブのデバイスを接続するなどのシステム構成が可能になる。

【0069】

ところが、SATAデバイスにはマスタ、スレーブの区別の概念が無く、SATAデバイスはマスタとして取り扱われる。従って、データ転送制御装置にPATAとSATAのブリッジ機能を持たせた場合に、何ら工夫をしないと、例えばSATAデバイスをマスタとしてのみ取り扱うことができるマスタ専用のデータ転送制御装置になってしまう。従って、例えば光ディスクドライブなどのSATAデバイスを、スレーブとして、本実施形態のデータ転送制御装置を介してPATAバスにブリッジ接続するようなシステム構成等を実現できないという問題がある。

【0070】

そこで本実施形態では、マスタ・スレーブの設定端子(決定端子)であるCSEL端子をデータ転送制御装置に設けている。そしてデータ転送制御装置は、このCSEL端子の状態(電圧設定状態)により、自身がマスタ側なのかスレーブ側なのかを判断するようにしている。

【0071】

例えば図9(A)では、CSEL端子がLレベル(GNDレベル)に設定されており、この場合には本実施形態のデータ転送制御装置3は、自身がマスタ側に設定されたと判断する。そしてデータ転送制御装置3とそれに接続されるSATAデバイス4により、PATAのマスタ側が構成される。これにより、本実施形態のデータ転送制御装置3を含むPATAのマスタ側と、PATAのスレーブ側とが、PATAバスに接続されるシステム構成を実現できる。

【0072】

一方、図9(B)では、CSEL端子がHレベル(VDDレベル)に設定されており、この場合には本実施形態のデータ転送制御装置3は、自身がスレーブ側に設定されたと判断する。そしてデータ転送制御装置3とそれに接続されるSATAデバイス4により、PATAのスレーブ側が構成される。これにより、PATAのマスタ側と、本実施形態のデータ転送制御装置3を含むPATAのスレーブ側とが、PATAバスに接続されるシステム構成を実現できる。

【0073】

以上のように本実施形態では、PATAとSATAのブリッジ機能を有するデータ転送制御装置3に対して、マスタ・スレーブの設定端子であるCSEL端子を設けているため、例えば本来はマスタ、スレーブの区別の概念が無く、マスタとしてのみ取り扱われるSATAデバイス4を、データ転送制御装置3を介してPATAバスにブリッジ接続して、PATAのスレーブ側を構成することが可能になる。この結果、例えばSATAインターフェースを有する光ディスクドライブなどを、スレーブとして、PATAバスにブリッジ接続するシステム構成等を実現でき、利便性を大幅に向上できる。

【0074】

5.2 初期化シーケンス管理の代行

前述のように、SATAデバイスにはマスタ、スレーブの区別の概念が無く、SATAデバイスはマスタとしてのみ取り扱われる。従って、SATAデバイスは、マスタ、スレーブを区別するための初期化シーケンス管理機能を有しない。従って、このようなSATAデバイスを、PATAとSATAのブリッジ機能を有するデータ転送制御装置を介してPATAバスにブリッジ接続した場合に、初期化シーケンスの処理を行う処理主体が存在しなくなってしまうという問題がある。

【0075】

そこで本実施形態では、図1(A)、図1(B)の初期化シーケンス管理部34が、PATAにおける初期化シーケンス管理機能を有しないSATAデバイス4に代わって初期化シーケンス管理を代行する。例えば初期化シーケンス管理部34は、ハードリセット後、デバイス存在検知期間(10ms)内にSATAデバイス4の存在が検知された場合に、初期化シーケンス処理を実行する。具体的にはハードリセット後に、ホスト側であるSATAI/F50はOOBシーケンスにおけるCOMRESETを発行し、SATAデバイス4からのCOMINITを検出する。そして初期化シーケンス管理部34は、デバイス存在検知期間(10ms)内にSATAデバイス4からのCOMINITが検知された場合には、SATAデバイス4が存在すると判断して、本実施形態の初期化シーケンス処理を実行する。

【0076】

更に具体的には初期化シーケンス管理部34は、図9(A)のようにCSEL端子(マスタ・スレーブ設定端子)によりデータ転送制御装置3がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行う。一方、図9(B)のようにCSEL端子によりデータ転送制御装置3がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号の制御と自己診断信号の制御を行う。

【0077】

このようにすれば、SATAデバイス4が初期化シーケンス管理機能を有しない場合にも、データ転送制御装置3が、この初期化シーケンス管理を代行して、スレーブ検知等のPATAにおける初期化シーケンス処理を実行できる。従って、マスタとしてのみ取り扱われるSATAデバイス4を、例えばデータ転送制御装置3を介してPATAバスにブリッジ接続して、PATAのスレーブ側を構成した場合に、PATA規格に準拠した適正な初期化シーケンス処理を実行できるようになる。

【0078】

次に初期化シーケンス処理の詳細について図10、図11を用いて説明する。図10はホスト側の動作を説明するためのフローチャートであり、図11はデバイス側の動作を説明するためのフローチャートである。

【0079】

図10に示すようにホスト側は、ハードリセット信号をアクティブ(アサート状態)にした後、非アクティブ(ネゲート状態)にする(ステップS21、S22)。そしてステータスレジスタのBUSYビットが1から0にクリアされるのをウェイトし、0にクリアされるとホストアイドル状態に移行する(ステップS23、S24)。

【0080】

一方、図11に示すようにデバイス側は、ハードリセットが行われると、リリースバスステートに移行し、CSEL(CSEL端子、CSEL信号)がLレベルか否かを判断する(ステップS31、S32、S33)。即ち自身がマスタ側に設定されているか、スレーブ側に設定されているかを判断する。

【0081】

そしてCSELがLレベルに設定され、自身がマスタ側に設定されていると判断した場合には、XDASPウェイトステートに移行した後、サンプルXDASPステートに移行する(ステップS34、S35)。このサンプルXDASPステートでは、自身の初期化及び自己診断処理を行うと共に、スレーブ側からのスレーブ検知信号XDASPをサンプルしてモニタする。

【0082】

そして信号XDASPがLレベル(アクティブ)であると判断した場合には、スレーブの存在が検知されたと判断して、サンプルXPDIAGステートに移行する(ステップS36、S37)。このサンプルXPDIAGステートでは、スレーブ側からの自己診断信号XPDIAG(スレーブの自己診断結果の通知信号)をサンプルしてモニタする。

【0083】

そして信号XPDIAGがLレベル(アクティブ)であると判断した場合には、スレーブ側の自己診断がパスしたと判断し、タスクファイル・レジスタのエラーレジスタのビット7を0に設定する(ステップS38、S39)。一方、信号XPDIAGがHレベル(非アクティブ)であると判断した場合には、スレーブ側の自己診断がフェイルしたと判断し、エラーレジスタのビット7を1に設定する(ステップS40)。なおステップS36で、信号XDASPがHレベルであると判断された場合には、スレーブが非存在であると判断すると共に、エラーレジスタのビット7を0に設定する(ステップS41)。そしてセットステータスステートに移行し(ステップS42)、自己診断処理を完了すると共に、タスクファイル・レジスタのステータスレジスタのBUSYビットを0にクリアする。そしてデバイスアイドル状態に移行する(ステップS43)。

【0084】

一方、ステップS33でCSELがHレベルに設定され、自身がスレーブ側に設定されていると判断した場合には、セットXDASPステートに移行する(ステップS44)。このセットXDASPステートでは、スレーブ検知信号XDASPをLレベル(アクティブ)にすると共に、自身の初期化及び自己診断処理を行う。このようにスレーブ側がスレーブ検知信号XDASPをLレベルにすることで、ステップS36に示すようにマスタ側はスレーブの存在を検知できる。

【0085】

次に、セットステータスステートに移行する(ステップS45)。そして自己診断信号XPDIAGをLレベル(アクティブ)又はHレベル(非アクティブ)にすると共に、タスクファイル・レジスタのステータスレジスタのBUSYビットを0にクリアし、デバイスアイドル状態に移行する(ステップS46)。このようにスレーブ側が信号XPDIAGをLレベルにすることで、ステップS39に示すようにマスタ側はスレーブ側の自己診断がパスしたと判断できる。またスレーブ側が信号XPDIAGをHレベルにすることで、ステップS40に示すようにマスタ側はスレーブ側の自己診断がフェイルしたと判断できる。

【0086】

そして本実施形態では、初期化シーケンス管理部34は、CSEL端子がLレベルに設定され、自身がマスタ側に設定されたと判断した場合には、図11のステップS34〜S43に示すように、スレーブ検知処理と自己診断処理を行う。即ち、信号XDASPに基づいてスレーブが検知されたか否かを判断すると共に、マスタ側の自己診断処理や信号XPDIAGに基づくスレーブ側の自己診断結果の確認処理を行う。

【0087】

また初期化シーケンス管理部34は、CSEL端子がHレベルに設定され、自身がスレーブ側に設定されたと判断した場合には、図11のステップS44〜S46に示すように、スレーブ検知信号XDASP、自己診断信号XPDIAGの制御を行う。即ち、スレーブ検知信号XDASPをLレベルにして、スレーブの存在をマスタ側に通知する。また自己診断信号XPDIAGをLレベルにしたり、Hレベルにして、スレーブ側の自己診断結果をホスト側に通知する。

【0088】

以上のような初期化シーケンス処理を初期化シーケンス管理部34に代行させることで、マスタとしてのみ取り扱われるSATAデバイスに、マスタ、スレーブの区別の概念を導入できると共に、PATAの規格にしたがった適正な初期化シーケンス処理を実現できる。

【0089】

5.3 DEVビットの設定

前述したようにPATAでは、データDD[15:0]やアドレスDA[2:0]のバスは、マスタとスレーブで共用される。従って、マスタ及びスレーブの両方が、データDD[15:0]のバスからのコマンド、パラメータをタスクファイル・レジスタを介して受け取ることになる。そして、マスタへ宛てたものであるか、スレーブへ宛てたものであるかは、デバイス/ヘッドレジスタのDEVビットにより判断する。具体的にはDEVビットが0である場合にはマスタに宛てたものであると判断し、DEVビットが1である場合にはスレーブに宛てたものであると判断する。

【0090】

一方、SATAデバイスは、常にマスタとして取り扱われる。従ってSATAデバイスは、DEVビットが0に設定されたコマンド、パラメータだけを、自身に宛てたものとして受け取ることになる。

【0091】

ところが、図9(B)に示すように、CSEL端子をHレベルにしてスレーブ設定にした場合には、ホスト2はSATAデバイス4をスレーブと見なしている。従って、SATAデバイス4に対してコマンドやパラメータを送る場合には、DEVビットをスレーブ設定である1に設定する。従って、自身がマスタであると認識しているSATAデバイス4は、これらのコマンドやパラメータを受け取れなくなってしまう。そこで本実施形態では、以下のようなDEVビット設定手法を採用している。

【0092】

例えば図12(A)では、CSEL端子(CSEL信号)がLレベルに設定され、データ転送制御装置がマスタ側に設定されている。そしてホスト2がマスタへのATAコマンドを発行している。この場合には、シーケンスコントローラ30は、TFR12のレジスタ値(コマンド、パラメータ)をそのままSFR52に転送する。するとSATAI/F50は、SFR52のレジスタ値に基づいて、レジスタFIS(Host to Device)等を生成して、SATAデバイス4に送信する。

【0093】

このとき、TFR12のデバイス/ヘッドレジスタのDEVビット=0(マスタ設定)も、TFR12からSFR52にそのまま転送されて、SATAデバイス4に送信される。そしてSATAデバイス4は、自身をマスタとして認識しているため、ホスト2からのコマンドやパラメータを、問題なく受け取ることができる。

【0094】

また図12(B)では、データ転送制御装置がマスタ側に設定されているときに、ホスト2からのATAコマンドに対応するFIS(例えばレジスタFIS、PIOセットアップFIS、DMAアクティベートFIS等)を、SATAI/F50がSATAデバイス4から受信している。この場合には、シーケンスコントローラ30は、SFR52のレジスタ値をTFR12にそのまま転送する。そしてホスト2は、SATAデバイス4からのステータス等を受け取る。

【0095】

このとき、SFR52のデバイス/ヘッドレジスタのDEVビット=0(マスタ設定)も、SFR52からTFR12にそのまま転送される。従って、PATAI/F10は、マスタ側であるSATAデバイス4からのステータス等を、PATAのDD[15:0]のバスに適正に出力できるようになる。

【0096】

一方、図13(A)では、CSEL端子がHレベルに設定され、データ転送制御装置がスレーブ側に設定されている。そしてホスト2がスレーブへのATAコマンドを発行している。この場合には、シーケンスコントローラ30は、デバイス/ヘッドレジスタのDEVビットを1(スレーブ設定)から0(マスタ設定)に書き換えて、TFR12のレジスタ値をSFR52に転送する。するとSATAI/F50は、SFR52のレジスタ値に基づいて、レジスタFIS(H to D)等を生成して、SATAデバイス4に送信する。

【0097】

このとき、SATAデバイス4は、自身をマスタとして認識しているが、本実施形態ではDEVビットを1(スレーブ設定)から0(マスタ設定)に書き換えているため、ホスト2からのコマンドやパラメータを問題なく受け取ることができる。

【0098】

また図13(B)では、データ転送制御装置がスレーブ側に設定されているときに、ホスト2からのATAコマンドに対応するFISを、SATAI/F50がSATAデバイス4から受信している。この場合には、シーケンスコントローラ30は、SFR52のデバイス/ヘッドレジスタのDEVビットを0(マスタ設定)から1(スレーブ設定)に書き換えて、SFR52のレジスタ値をTFR12に転送する。そしてホスト2は、SATAデバイス4からのステータス等を受け取る。

【0099】

このとき、ホスト2は、SATAデバイス4をスレーブとして認識しているが、本実施形態ではDEVビットを0(マスタ設定)から1(スレーブ設定)に書き換えているため、SATAデバイス4からのステータス等を問題なく受け取ることができる。

【0100】

以上のように本実施形態では、CSEL端子の状態に応じた適正な値に、デバイス/ヘッドレジスタのDEVビットを書き換えている。従って、CSEL端子によりデータ転送制御装置をスレーブ側に設定した場合にも、ホスト2と、自身をマスタと認識しているSATAデバイス4との間で、コマンド、パラメータやステータスの適正な転送処理を実現できる。

【0101】

次に本実施形態のDEVビットの設定手法について図14、図15のフローチャートを用いて更に詳細に説明する。

【0102】

図14では、ホスト2がマスタへのATAコマンドを発行している(ステップS51)。そしてCSEL端子がLレベルか否かを判断し(ステップS52)、Lレベルである場合には、図12(A)で説明したようにTFR12のレジスタ値をそのままSFR52に転送する(ステップS53)。そしてSATAデバイス4へのコマンドの転送及び実行が行われる(ステップS54)。

【0103】

次に、SATAデバイス4からステータス返送のためのFIS(レジスタFIS等)を受信すると(ステップS55)、図12(B)で説明したようにSFR52のレジスタ値をそのままTFR12に転送する(ステップS56)。

【0104】

一方、ステップS52でCSEL端子がHレベルであると判断された場合には、ホスト2により発行されたATAコマンドは非実行になる(ステップS57)。即ち、ホスト2が発行したATAコマンドはマスタへ宛てたものであり、CSEL端子はスレーブ側に設定されているため、スレーブ側であるデータ転送制御装置は、このATAコマンドの実行処理を行わない。

【0105】

図15では、ホスト2がスレーブへのATAコマンドを発行している(ステップS61)。そしてCSEL端子がLレベルか否かを判断し(ステップS62)、LレベルではなくHレベルである場合には、図13(A)で説明したようにTFR12のデバイス/ヘッドレジスタのDEVビットを0(マスタ設定)に書き換えて、TFR12のレジスタ値をSFR52に転送する(ステップS63)。そしてSATAデバイス4へのコマンドの転送及び実行が行われる(ステップS64)。

【0106】

次に、SATAデバイス4からステータス返送のためのFIS(レジスタFIS等)を受信すると(ステップS65)、図13(B)で説明したようにSFR52のデバイス/ヘッドレジスタのDEVビットを1(スレーブ設定)に書き換えて、SFR52のレジスタ値をTFR12に転送する(ステップS66)。

【0107】

一方、ステップS62でCSEL端子がLレベルであると判断された場合には、ホスト2により発行されたATAコマンドは非実行になる(ステップS67)。即ち、ホスト2が発行したATAコマンドはスレーブへ宛てたものであり、CSEL端子はマスタ側に設定されているため、マスタ側であるデータ転送制御装置は、このATAコマンドの実行処理を行わない。

【0108】

6.コマンドライト検出によるレジスタ値の転送処理

次に、TFR12とSFR52の間でのレジスタ値の転送処理の具体的に説明する。

【0109】

本実施形態ではシーケンスコントローラ30は、図16(A)に示すようにTFR12にパラメータ(コマンドのパラメータ)が書き込まれた後、図16(B)に示すようにTFR12にATAコマンドが書き込まれたことを条件に、TFR12からSFR52へのレジスタ値の転送(更新)を行っている。具体的には、ATAコマンドがTFR12に書き込まれた場合に、コマンドライト検出信号がアクティブになる。シーケンスコントローラ30は、このようにコマンドライト検出信号がアクティブになった場合に、図12(A)、図12(B)で説明したTFR12からSFR52へのレジスタ値の転送処理を行う。更に、このようにコマンドライト検出信号がアクティブになった場合に、図13(A)、図13(B)で説明したDEVビットの書き換え処理も行う。

【0110】

即ちホスト2は、ATAコマンドを書き込む前に、そのATAコマンドに関連するパラメータをPATAバスを介してTFR12に書き込む。このようにパラメータの書き込みが行われたタイミングでは、シーケンスコントローラ30は、TFR12からSFR52へのレジスタ値の転送処理やDEVビットの書き換え処理を行わない。

【0111】

そして、ホスト2がパラメータの書き込み後にATAコマンド(例えばPIOリード、PIOライト、DMAリード、DMAライト、ノーデータコマンド等)をTFR12に書き込むと、コマンドライト検出信号がアクティブになってシーケンスコントローラ30に出力される。するとシーケンスコントローラ30は、TFR12に書き込まれたパラメータやATAコマンドのレジスタ値を、SFR52に転送して書き込む。またこの際にDEVビットの書き換え処理も行う。

【0112】

このようにすれば、レジスタ値の転送処理等を、ATAコマンドの書き込み時に一斉に行うことが可能になる。従って、転送処理を簡素化できると共に、転送処理に必要な信号線の数も減らすことができ、回路の小規模化や処理の簡素化を図れる。

【0113】

即ちパラメータの書き込み時にもレジスタ値を転送する手法を採用すると、複数回のレジスタ値の転送処理が必要になってしまい、処理が繁雑化する。またパラメータの書き込みの検出信号も必要になり、信号線の数も増える。

【0114】

一方、従来のPATA(IDE)用に作成されたホスト2のソフトウェアでは、パラメータを書き込んだ後に、ATAコマンドを書き込む手順となっているのが一般的である。図16(A)、図16(B)では、この点に着目し、ホスト2のソフトウェアがパラメータを書き込んだ後、ATAコマンドを書き込んだタイミングで、TFR12からSFR52へのレジスタ値の転送を行っている。これにより、従来のPATA用のソフトウェアをそのまま用いることができると共に、転送処理を簡素化でき、データ転送制御装置を小規模化できる。

【0115】

更に具体的にはレジスタ値の転送処理は以下のような手法により実現できる。

【0116】

例えば図16(C)のG1、G2に示すように、TFR12のレジスタ群の各ビット(全ビット)とSFR52のレジスタ群の各ビット(全ビット)は、シーケンスコントローラ30(信号線)を介して接続される。即ちTFR12のコントロールブロックレジスタやコマンドブロックレジスタ(ステータスレジスタ、コマンドレジスタ)などのレジスタ群から出力された信号(信号線)は、シーケンスコントローラ30に入力される。そしてこれらの信号は、シーケンスコントローラ30を介してSFR52に出力される。またSFR52のコントロールブロックレジスタやコマンドブロックレジスタなどのレジスタ群から出力された信号(信号線)も、シーケンスコントローラ30に入力され、シーケンスコントローラ30からTFR12に出力される。

【0117】

そしてシーケンスコントローラ30は、レジスタ値の転送トリガ信号(書き換えトリガ信号)TRG1、TRG2を生成し、生成され転送トリガ信号TRG1、TRG2に基づいて、TFR12、SFR52の間でのレジスタ値の転送を行う。例えばTFR12のレジスタ値を書き換える場合には、トリガ信号TRG1をアクティブにして、SFR52(或いは一時保存レジスタ)からのレジスタ値をTFR12に書き込む。またSFR52のレジスタ値を書き換える場合には、トリガ信号TRG2をアクティブにして、TFR12からのレジスタ値をSFR52に書き込む。なおこれらのトリガ信号TRG1、TRG2は、図16(B)で説明したコマンドライト検出信号等に基づいて生成できる。

【0118】

図16(C)のようにすれば、トリガ信号TRG1、TRG2をアクティブにするだけという簡素な制御で、レジスタ値の転送を実現できるため、回路の小規模化や処理の簡素化を図れる。またシーケンスコントローラ30は、転送されるレジスタ値をモニタできるため、よりインテリジェントなレジスタ値の転送制御を実現できる。

【0119】

7.受信FISの種類による転送シーケンス制御

本実施形態のようにブリッジ機能を有するデータ転送制御装置では、ホスト2が発行したATAコマンドに応じた転送シーケンス制御を行う必要がある。そして転送シーケンス制御の内容をデータ転送制御装置が知るためには、ATAコマンドをデコードする必要があり、そのために、コマンドデコーダやパラメータテーブルが必要になる。即ちホスト2が発行したコマンドをデコードし、転送方向(リード、ライト)や転送種別(PIO(Programmed I/O)、DMA)を判別し、内部転送シーケンスを決定する。

【0120】

しかしながら、このようなコマンドデコーダを設けると、データ転送制御装置のロジック回路の大規模化やメモリ容量の増加に繋がる。またATAコマンドのデコードを行うためには、デコードのためのコマンドテーブルを持たなければならないが、データ転送制御装置の開発終了後に、規格において新規コマンドの追加が発生した場合には、データ転送制御装置の回路修正を行わない限り、新規コマンドをサポートできなくなる。例えばATAPIでは、ブルーレイディスクなどの新しい規格の光ディスクドライブが追加されると、パラメータテーブルの変更が必要になる。従って、開発が終了している既存のデータ転送制御装置を使用できず、パラメータテーブル(テーブルメモリ)を変更するための回路修正が必要になり、余分な開発期間や開発コストがかかってしまう。更にベンダーにユニークな特殊コマンドに対しても、対応することが難しい。

【0121】

この場合にデータ転送制御装置にCPU(処理部)を内蔵させ、パラメータテーブルの変更をファームウェア等の書き換えにより実現すれば、新規コマンドが増えたり、コマンドの内容が変更された場合にも、これに対応できる。

【0122】

しかしながら、データ転送制御装置にCPUを内蔵させると、CPU上で動作するファームウェアの開発や、CPUの動作確認のためのデバッグツールの開発などが必要になってしまい、開発期間の長期化や高コスト化を招く。

【0123】

このような問題を解決するための図17(A)〜図18(C)に示す手法では、ホストが発行したコマンドをデコードすることなくデバイスに転送し、デバイスから返送されてきたFISの情報に基づいて、発行されたコマンドについての転送シーケンスを制御する。即ちATAコマンドのデコードを、データ転送制御装置が行うのではなく、SATAデバイスに行わせる。そしてデータ転送制御装置は、ATAコマンドをデコードせずに(一部をデコードしてもよい)、SATAデバイスにそのまま転送し、SATAデバイスの反応を観察することで、自身の転送シーケンスを決定して実行する。

【0124】

具体的には図17(A)に示すようにホスト2がPATAバスを介してATAコマンド(転送コマンド)を発行すると、PATAI/F10がこのコマンドを受ける。そしてSATAI/F50は、発行されたATAコマンドを含むレジスタFIS(Host to Device)を作成して、SATAバスを介してデバイス4に送信する。

【0125】

デバイス4側のSATAI/F(図示せず)は、レジスタFISを受信すると、デコード処理を行い、レジスタFIS(ATAコマンド)に対応するFISを送信し、このFISをSATAI/F50が受信する。

【0126】

シーケンスコントローラ30(転送シーケンサ、ブリッジシーケンサ)は、レジスタFISに対応するFISをSATAI/F50がデバイス4から受信すると、ホスト2から発行されたATAコマンドの転送シーケンス制御として、受信したFISの種類に応じた転送シーケンス制御を行う。

【0127】

より具体的には図17(B)ではホスト2はPIOリードのATAコマンドを発行している。この場合にはデバイス4は、転送方向がリード方向であるPIOセットアップFISを送信する。即ちPIOのデータ転送の直前にデバイス4がホスト2に転送するFISであるPIOセットアップFISを、デバイス4が送信し、SATAI/F50が受信する。このPIOセットアップFISは、データ転送の初期ステータス(Status)及びステータス終了値(E_Status)を有する。

【0128】

このように受信FISがPIOセットアップFISであり、PIOセットアップFISにより指定される転送方向がリード方向である場合には、シーケンスコントローラ30は、PIOリードの転送シーケンス制御を行う。即ちシーケンスコントローラ30は、PIOリードの転送シーケンスのための制御信号(転送方向設定信号、転送開始信号、転送停止信号等)をSATAI/F50、データバッファ70、PATAI/F10に出力する。これにより、デバイス4から読み出されたデータが、SATAI/F50、データバッファ70、PATAI/F10を介してホスト2に転送される。

【0129】

図17(C)では、ホスト2はPIOライトのATAコマンドを発行している。この場合にはデバイス4は、転送方向がライト方向であるPIOセットアップFISを送信し、SATAI/F50が受信する。

【0130】

このように受信FISがPIOセットアップFISであり、PIOセットアップFISにより指定される転送方向がライト方向である場合には、シーケンスコントローラ30は、PIOライトの転送シーケンス制御を行う。即ちシーケンスコントローラ30は、PIOライトの転送シーケンスのための制御信号をPATAI/F10、データバッファ70、SATAI/F50に出力する。これにより、ホスト2からのデータが、PATAI/F10、データバッファ70、SATAI/F50を介してデバイス4に転送される。

【0131】

図18(A)では、ホスト2はDMAリードのATAコマンドを発行している。この場合にはデバイス4はデータFISを送信する。即ちデバイス4はデータ転送のためのFISであるデータFISを送信し、SATAI/F50が受信する。

【0132】

このように受信FISがデータFISである場合には、シーケンスコントローラ30は、DMAリードの転送シーケンス制御を行う。これにより、デバイス4から読み出されたデータが、SATAI/F50、データバッファ70、PATAI/F10を介してホスト2にDMA転送される。

【0133】

図18(B)では、ホスト2はDMAライトのATAコマンドを発行している。この場合にはデバイス4はDMAアクティベートFISを送信する。即ちDMAの実行準備が出来ていることをホスト2に知らせるためのDMAアクティベートFISを、デバイス4が送信し、SATAI/F50が受信する。

【0134】

このように受信FISがDMAアクティベートFISである場合には、シーケンスコントローラ30は、DMAライトの転送シーケンス制御を行う。これにより、ホスト2からのデータが、PATAI/F10、データバッファ70、SATAI/F50を介してデバイス4にDMA転送される。

【0135】

図18(C)では、ホスト2はノーデータコマンドのATAコマンドを発行している。この場合にはデバイス4はレジスタFIS(Device to Host)を送信し、SATAI/F50が受信する。このように、ATAコマンドに対応する受信FISが、デバイス4からホスト2へのレジスタFISである場合には、シーケンスコントローラ30は、ホスト2から発行されたATAコマンドはノーデータコマンドであると判断する。そしてレジスタFISのレジスタ値を、SATAI/F50のシャドウ・タスクファイル・レジスタからPATAI/F10のタスクファイル・レジスタに反映させる。

【0136】

以上のように、図17(A)〜図18(C)の手法によれば、ホスト2が発行したATAコマンドをデコードしなくても、デバイス4からの受信FIS情報に基づいて、発行されたATAコマンドの種別を判断して、そのATAコマンドに対応する転送シーケンス制御を実現できる。従って、コマンドデコーダの回路を節約でき、データ転送制御装置の小規模化を図れる。また、規格において新規コマンドの追加が発生しても、データ転送制御装置の回路修正を行うことなく、これに対応できる。またデータ転送制御装置にCPUを内蔵させなくても済むため、CPU上で動作するファームウェアの開発やデバッグツールの開発が不要になり、開発期間を短縮化でき、開発コストを低減できる。なおデータ転送制御装置にATAコマンドの一部をデコードする回路を設けたり、CPU(処理部)を内蔵させる変形実施も可能である。

【0137】

そして図17(A)〜図18(C)の手法を実現するために、本実施形態では、シーケンスコントローラ30が、TFR12とSFR52の間でのレジスタ値の転送処理を行っている。具体的には図12(A)に示すように、ホスト2によりマスタへのATAコマンドが発行され、CSEL端子がマスタ側であるLレベルに設定されている場合に、TFR12のレジスタ値をSFR52にそのまま転送する。即ちシーケンスコントローラ30は、TFR12のレジスタ値をデコードすることなく、SFR52にそのままコピーする。また図12(B)に示すように、発行されたATAコマンドに対応するFISを受信した場合には、シーケンスコントローラ30は、SFR52のレジスタ値をそのままTFR12に転送(コピー)する。このようにすれば、コマンドデコード処理などの負荷が重い処理を行うことなく、ホスト2からのコマンド、パラメータ等をデバイス4に転送したり、デバイス4からのステータス等をホスト2に転送することが可能になる。

【0138】

一方、ホスト2によりスレーブへのATAコマンドが発行され、CSEL端子がスレーブ側であるHレベルに設定されている場合に、図17(A)〜図18(C)の手法を実現するためにTFR12とSFR52の間でレジスタ値をそのまま転送すると、誤った転送処理が行われてしまう。

【0139】

そこで図13(A)では、TFR12からSFR52にレジスタ値をそのまま転送するのではなく、DEVビットをマスタ設定である0に書き換えて転送している。また図13(B)では、SFR52からTFR12にレジスタ値をそのまま転送するのではなく、DEVビットをスレーブ設定である1に書き換えて転送している。

【0140】

このようにすれば、図17(A)〜図18(C)の手法を採用した場合にも、ホスト2と、自身をマスタと認識しているSATAデバイス4との間で、コマンド、パラメータ、ステータス等の適正な転送処理を実現できる。

【0141】

8.PIO転送、DMA転送

次に本実施形態のデータ転送制御装置により実現されるPIO転送、DMA転送の詳細について図19〜図22を用いて更に具体的に説明する。

【0142】

図19はPIOリードの転送シーケンス図である。ホスト2によりPIOリードのコマンドが発行されると、図19のA1に示すようにTFR12のステータスレジスタがD0hに設定される。即ちPATAI/F10によりBUSYビットが1にセットされ、デバイス4がビジー状態であることがホスト2に知らされる。そしてシーケンスコントローラ30によりTFR12のレジスタ値がSFR52に転送(コピー)される。するとA2に示すように、SATAI/F50は、SFR52のレジスタ値に基づいてPIOリードコマンドを含むレジスタFIS(Host to Device)を作成し、SATAバスを介してデバイス4に送信する。

【0143】

このレジスタFISを受信したデバイス4は、A3に示すようにPIOセットアップFISを送信する。この場合に図8(C)のPIOセットアップFISのステータス(Status)には58hが設定され、エンドステータス(E_Status)にはD0hが設定される。ここでD0hではBUSYビットが1にセットされ、58hではDRQビットが1にセットされる。また50hではBUSYビット及びDRQビットが共に0にクリア(解除)される。またエンドステータスは例えばSATAI/F50の一時保存レジスタに保存される。

【0144】

シーケンスコントローラ30は、デバイス4からPIOセットアップFISを受信し、その方向パラメータD(図8(C)参照)がデバイスからホストへの方向である場合には、ホスト2が発行したコマンドはPIOリードであると判断する。そしてSFR52からTFR12にレジスタ値を転送し、A4に示すようにTFR12のステータスレジスタを58hに設定して、DRQビットを1にセットする。これによりホスト2に対する割り込みINTRQが発生する。なおINTRQの代わりにホスト2によるポーリングを採用してもよい。

【0145】

そしてデバイス4からデータFISを受信し、ホスト2がデータをリードすると、A5に示すように、PIOセットアップFISのエンドステータスであるD0hがTFR12のステータスレジスタに設定され、BUSYビットが1にセットされる。即ちSATAI/F50の一時保存レジスタに保存されたエンドステータス(D0h)が、TFR12のステータスレジスタに転送されて書き込まれる。これにより、デバイス4がビジー状態であることがホスト2に知らされる。

【0146】

以上のようにして各セクタのPIOリードが繰り返される。そしてA6に示すように最後のセクタのPIOセットアップFISではエンドステータスが50h又は51hになっている。従ってA7に示すようにこのエンドステータス50h又は51hがTFR12のステータスレジスタに設定され、DRQビットがクリアされる。これにより、全てのデータ転送が完了したことがホスト2に知らされる。

【0147】

図20はPIOライトの転送シーケンス図である。ホスト2によりPIOライトのコマンドが発行されると、B1に示すようにBUSYビットが1にセットされる(D0h)。そしてTFR12のレジスタ値がSFR52に転送され、B2に示すようにPIOライトコマンドを含むレジスタFISがデバイス4に送信される。

【0148】

このレジスタFISを受信したデバイス4は、B3に示すようにPIOセットアップFISを送信する。そしてシーケンスコントローラ30は、デバイス4からPIOセットアップFISを受信し、その方向パラメータD(図8(C)参照)がホストからデバイスへの方向である場合には、ホスト2が発行したコマンドはPIOライトであると判断する。そしてSFR52からTFR12にレジスタ値を転送し、B4に示すようにTFR12のステータスレジスタを58hに設定して、DRQビットを1にセットする。これによりホスト2に対する割り込みINTRQが発生する。

【0149】

そしてホスト2がデータをライトすると、B5に示すように、PIOセットアップFISのエンドステータスであるD0hがTFR12のステータスレジスタに設定される。

【0150】

以上のようにして各セクタのPIOライトが繰り返される。そしてB6に示すように最後のセクタの転送が終わると、デバイス4がレジスタFISを送信する。するとこのレジスタFISのステータス(50h又は51h)が、SFR52からTFR12に転送されて、B7に示すようにDRQビットがクリアされる。

【0151】

図21はDMAリードの転送シーケンス図である。ホスト2によりDMAリードのコマンドが発行されると、C1に示すようにBUSYビットが1にセットされる(D0h)。PIO転送とは異なりDMA転送では、データ転送中にBUSYビットが1にセットされたままになる。そしてTFR12のレジスタ値がSFR52に転送され、C2に示すようにDMAリードコマンドを含むレジスタFISがデバイス4に送信される。

【0152】

このレジスタFISを受信したデバイス4は、C3に示すようにデータFISを送信する。シーケンスコントローラ30は、デバイス4から受信したFISがデータFISである場合には、ホスト2が発行したコマンドはDMAリードであると判断する。そしてC4に示すようにDMARQがアサートされて、DMA転送が開始し、デバイス4のデータがホスト2にリードされる。

【0153】

そしてDMA転送が終了し、デバイス4がレジスタFISを送信すると、C5に示すように、SFR52のレジスタ値がTFR12に転送されて、BUSYビットがクリアされる(50h又は51h)。

【0154】

図22はDMAライトの転送シーケンス図である。ホスト2によりDMAライトのコマンドが発行されると、D1に示すようにBUSYビットが1にセットされる(D0h)。そしてTFR12のレジスタ値がSFR52に転送され、D2に示すようにDMAライトコマンドを含むレジスタFISがデバイス4に送信される。

【0155】

このレジスタFISを受信したデバイス4は、D3に示すようにDMAアクティベートFISを送信する。シーケンスコントローラ30は、デバイス4から受信したFISがDMAアクティベートFISである場合には、ホスト2が発行したコマンドはDMAライトであると判断する。そしてD4に示すようにDMARQがアサートされて、DMA転送が開始し、ホスト2のデータがデバイス4にライトされる。

【0156】

そしてDMA転送が終了し、デバイス4がレジスタFISを送信すると、D5に示すように、SFR52のレジスタ値がTFR12に転送され、BUSYビットがクリアされる(50h又は51h)。

【0157】

9.SATAI/Fの構成

図23にSATAI/F50の構成例を示す。なおSATAI/F50の構成は図23に限定されず、その構成要素の一部を削除したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えば物理層回路200を設けない構成としてもよい。

【0158】

SATAでは、データは32ビット(4バイト)単位で処理される。この32ビットのデータが、リンクコントローラ150により8b/10bでエンコードされて40ビットのデータになり、物理層回路200に送られる。物理層回路200は、この40ビットのデータをシリアル化してSATAのケーブルに送信する。受信も逆の手順で、シリアルデータが物理層回路200で40ビットのデータに変換され、リンクコントローラ150で32ビットのデータに変換され、トランスポートコントローラ110に送られる。

【0159】

トランスポートコントローラ110はトランスポート層の制御を行うものである。具体的にはトランスポートコントローラ110は、上位層(アプリケーション層)からFISの送信要求が来た時に、以下の処理を行う。

【0160】

まずトランスポートコントローラ110は、FISタイプの要件に基づいてFISの内容を収集する。また送信する情報をFISのタイプ毎に定義フォーマットに配置する。次にリンクコントローラ150に対して送信要求を通知する。これによりリンクコントローラ150はX_RDYの送信処理を行う。そして相手ノードからのR_RDYを受信し、リンクコントローラ150から受信のアクノリッジが来ると、トランスポートコントローラ110はFISをリンクコントローラ150に転送する。そして送信FIFO120のフロー管理を行い、必要なフロー制御をリンクコントローラ150に通知する。その後、リンクコントローラ150から送信結果を受信すると、必要に応じて上位層に送信結果を通知する。

【0161】

トランスポートコントローラ110は、リンクコントローラ150からFISを受信した時には、以下の処理を行う。

【0162】

トランスポートコントローラ110は、リンクコントローラ150からFISを受信すると、受信したFISのタイプを判別する。そしてFISのタイプに応じた適切なレジスタやFIFOにデータを転送する。そして受信FIFO122のフロー管理を行い、必要なフロー制御をリンクコントローラ150に通知する。その後、リンクコントローラ150及び上位層(アプリケーション層)に受信結果を通知する。

【0163】

リンクコントローラ150はリンク層の制御を行うものである。具体的にはリンクコントローラ150は、送信時には以下の処理を行う。

【0164】

まずリンクコントローラ150はトランスポートコントローラ110からのデータ(FIS)を受け取る。そしてFISのCRCを生成し、FISの最後尾に付加する。次にデータのスクランブルを行い、その後、8b/10bのエンコードを行う。そしてSATA通信のプロトコルにしたがったプリミティブ、FISの送信を行う。そして送信結果をトランスポートコントローラ110に通知する。

【0165】

リンクコントローラ150は受信時には以下の処理を行う。即ちリンクコントローラ150は物理層回路200から、8b/10bエンコードキャラクタを受信する。そして8b/10bエンコードキャラクタをデコードし、デコードしたプリミティブを処理部等に通知する。次にデコードしたFISのデスクランブル処理を行い、CRCをチェックする。そしてトランスポートコントローラ110にデータを渡す。またデコード結果やCRCのチェック結果をトランスポートコントローラ110に通知する。

【0166】

物理層回路200は物理層を実現するアナログフロントエンド回路である。この物理層回路200は、シリアルデータ(シリアルストリーム)の送受信や、シリアルデータからパラレルデータへの変換や、パラレルデータからシリアルデータへの変換を行う。また8b/10bのK28.5キャラクタの検出や、OOB(Out Of Band)信号の検出と送信を行う。またデバイスステータス(デバイスの有無、転送状態、パワー状態)の提供や、通信制御用のインターフェース(転送レート制御、ループバック)の提供を行う。またオプションでパワーマネージメントも行う。

【0167】

物理層回路(PHY)200はトランスミッタ(ドライバ)210、レシーバ220、OOB検出回路230などを含む。

【0168】

トランスミッタ210は、差動信号線(差動信号線ペア)TX+/−を介してシリアルデータ(パケット)の送信を行い、レシーバ220は、差動信号線(差動信号線ペア)RX+/−を介してシリアルデータ(パケット)の受信を行う。TX+/−、RX+/−のSATAバス(広義にはシリアルバス)では、振幅電圧+/−250mVのNRZ差動信号によるシリアルストリーム転送が行われる。

【0169】

OOB検出回路230はOOB信号の検出処理を行う。このOOB信号は、SATAインターフェースのリセット/初期化、通信の確立や、スピード・ネゴシエーションをつかさどる信号である。

【0170】

リンクコントローラ150は、リンクステート制御回路160、フレーム生成回路190、フレームデコード回路192を含む。

【0171】

リンクステート制御回路160は、リンクコントローラ150のステート制御を行う。例えばリセットステート、アイドルステート、送信ステート、受信ステート等のステート間の遷移処理等を行う。

【0172】

フレーム生成回路190は、トランスポートコントローラ110からの送信データ(FIS)や、リンクステート制御回路160からの送信制御信号などに基づいてフレームの生成処理を行う。具体的には、トランスポートコントローラ110からのFISのCRCを演算したり、スクランブル処理を行ったり、8b/10bエンコード処理を行ったり、プリミティブを生成して付加する処理などを行う。

【0173】

フレームデコード回路192は、受信したフレームの解析(分解)処理を行い、受信解析信号(パワーダウンリクエスト信号等)をリンクステート制御回路160に出力する。具体的には、FISに付加されたプリミティブを解析したり、8b/10bのデコード処理を行ったり、デスクランブル処理を行ったり、CRCを演算してチェックする処理などを行う。

【0174】

トランスポートコントローラ110は、割りこみコントローラ118、DMA制御回路119、送信FIFO120、受信FIFO122、FIS生成回路130、FISデコード回路132、トランスポートステート制御回路140を含む。

【0175】

割り込みコントローラ118は、デバイス4からの受信FIS情報などを知らせるための割り込み信号を生成する。DMA制御回路119は、FISに含まれる送信データや受信データ(コンテンツ・データ)のDMA転送を制御する。送信FIFO120は、DMA制御回路119からの送信データのバッファとなるFIFOである。受信FIFO122は、リンクコントローラ150からの受信データのバッファとなるFIFOである。FIS生成回路130はFISの生成を行う回路であり、FISデコード回路132はFISの解析を行う回路である。トランスポートステート制御回路140は、トランスポートコントローラ110のステート制御を行う。

【0176】

10.シーケンスコントローラ

図24にシーケンスコントローラ30の構成例を示す。シーケンスコントローラ30はレジスタ更新部32、初期化シーケンス管理部34、パラメータ書き換え部36、DMAモード設定記憶部38、転送制御部40を含む。なおシーケンスコントローラ30の構成は図24に限定されず、その構成要素の一部を削除したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0177】

レジスタ更新部32はTFR12(タスクファイル・レジスタ)、SFR52(シャドウ・タスクファイル・レジスタ)のレジスタ値の更新処理を行う。具体的にはTFR12のレジスタ値をSFR52に転送してSFR52のレジスタ値を更新したり、SFR52のレジスタ値をTFR12に転送してTFR12のレジスタ値を更新する。

【0178】

例えばTFR12にホスト2によりATAコマンドが書き込まれると、PATAI/F10はコマンドライト検出信号をアクティブにする。そしてコマンドライト検出信号がアクティブになると、レジスタ更新部32はTFR12のレジスタ値をSFR52に転送する処理を行う。

【0179】

またSATAI/F50は、デバイス4から受信したFISをデコードし、デコード結果に基づいて、FISの種類を知らせるための割り込み信号(広義には受信FIS情報)を生成して出力する。レジスタ更新部32は、この割り込み信号に基づいて受信FISの種類を判別して、SFR52からTFR12へのレジスタ値の転送処理などを行って、レジスタ値の更新処理を行う。

【0180】

初期化シーケンス管理部34は、HRST(ハードリセット)、SRST(ソフトリセット)に伴う初期化シーケンスを管理する。具体的には、マスター、スレーブなどの設定をモニタして、PATAの初期化シーケンスを管理する。

【0181】

パラメータ書き換え部36は、ホスト2がデバイス4に対してアイデンティファイ・デバイス・コマンドを発行し、デバイス4からデバイス情報のパラメータを受信した場合に、パラメータの書き換え処理を行う。即ち転送速度などのパラメータを自身が対応可能なパラメータに書き換える。

【0182】

DMAモード設定記憶部38は、ホスト2がセットフューチャー・コマンドを発行した場合に、セットフューチャー・コマンドを解析して、DMA転送のモード設定を記憶する。

【0183】

転送制御部40はデータ転送制御装置の転送シーケンスを制御するものであり、モニタ部42、制御信号生成部44を含む。モニタ部42は、PATAI/F10からのコマンドライト検出信号や、SATAI/F50からの割り込み信号(受信FIS情報)などの信号をモニタする。そして制御信号生成部44は、モニタ結果に基づいて、転送方向設定信号、転送開始信号、転送停止信号などの制御信号を生成し、PATI/F10、データバッファ70、SATAI/F50に出力して、転送シーケンス制御を実行する。なおデータバッファ70に対しては転送開始信号、転送停止信号は出力せず、転送方向設定信号を出力する。

【0184】

11.電子機器

図25に本実施形態の電子機器の構成例を示す。この電子機器は、本実施形態で説明したデータ転送制御装置310とホスト302とデバイス304を含む。ホスト302とデータ転送制御装置310はPATAバスを介して接続され、データ転送制御装置310とデバイス304はSATAバスを介して接続される。なお本実施形態の電子機器の構成は図25に限定されず、その構成要素の一部を省略したり、他の構成要素を付加する変形実施が可能である。

【0185】

同図においてデバイス304は、HDD(ハードディスクドライブ)等のストレージデバイスや、光ディスクドライブ(CD、DVD)等である。

【0186】

ホスト302は、処理部330(CPU)、ROM340、RAM350、表示部360、操作部370を含むことができる。処理部330(CPU)はデータ転送制御装置310や電子機器の全体制御を行う。なおデータ転送制御装置310を制御する処理部と、電子機器を制御する処理部とを別々に設けてもよい。ROM340は制御プログラムや各種データを記憶する。RAM350は処理部330やデータ転送制御装置310のワーク領域やデータ格納領域として機能する。表示部360は種々の情報をユーザに表示する。操作部370はユーザが電子機器を操作するためのものである。

【0187】

本実施形態の電子機器によれば、ホスト302がSATAI/Fを有していない場合にも、データ転送制御装置310を介してSATAのデバイス304をホスト302に接続して、あたかもPATAのデバイスのように扱うことが可能になる。

【0188】

なお、本実施形態を適用できる電子機器としては、カーナビゲーションシステム、車載用オーディオ機器、HDDレコーダ、ビデオカメラ、携帯型音楽プレーヤ、携帯型映像プレーヤ、ゲーム装置、又は携帯型ゲーム装置等の種々のものが考えられる。

【0189】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。またデータ転送制御装置、電子機器の構成、動作も本実施形態で説明したものに限定に限定されず、種々の変形実施が可能である。また本実施形態では、SATAへの本発明の適用例について説明したが、本発明は、SATAと同様の思想に基づく規格や、SATA(SATA I、SATA II、SAS)を発展させた規格等にも適用できる。

【図面の簡単な説明】

【0190】

【図1】図1(A)、図1(B)は本実施形態のデータ転送制御装置の構成例。

【図2】本実施形態のデータ転送制御装置の詳細な構成例。

【図3】図3(A)、図3(B)はPIOリード、PIOライトの信号波形例。

【図4】図4(A)、図4(B)はDMAリード、DMAライトの信号波形例。

【図5】SATAの送信側のデータ処理の説明図。

【図6】SATAの受信側のデータ処理の説明図。

【図7】タスクファイル・レジスタのフォーマット例。

【図8】図8(A)〜図8(D)はFISのフォーマット例。

【図9】図9(A)、図9(B)はCSEL端子の設定手法の説明図。

【図10】初期化シーケンス処理を説明するためのフローチャート。

【図11】初期化シーケンス処理を説明するためのフローチャート。

【図12】図12(A)、図12(B)は本実施形態のDEVビットの設定手法の説明図。

【図13】図13(A)、図13(B)は本実施形態のDEVビットの設定手法の説明図。

【図14】本実施形態のDEVビットの設定手法を説明するためのフローチャート。

【図15】本実施形態のDEVビットの設定手法を説明するためのフローチャート。

【図16】図16(A)〜図16(C)は本実施形態のレジスタ値転送手法の説明図。

【図17】図17(A)〜図17(C)は本実施形態のシーケンス制御手法の説明図。

【図18】図18(A)〜図18(C)は本実施形態のシーケンス制御手法の説明図。

【図19】PIOリードの転送シーケンス図。

【図20】PIOライトの転送シーケンス図。

【図21】DMAリードの転送シーケンス図。

【図22】DMAライトの転送シーケンス図。

【図23】SATAI/Fの構成例。

【図24】シーケンスコントローラの構成例。

【図25】電子機器の構成例。

【符号の説明】

【0191】

2 ホスト、4 デバイス、10 PATAI/F、

12 タスクファイル・レジスタ(TFR)、14 転送コントローラ、

30 シーケンスコントローラ、32 レジスタ更新部、

34 初期化シーケンス管理部、36 パラメータ書き換え部、

38 DMA転送設定記憶部、40 転送制御部、

42 モニタ部、44 制御信号生成部、50 SATAI/F、

52 シャドウ・タスクファイル・レジスタ(SFR)、70 データバッファ、

72 メモリコントローラ、74 FIFOメモリ、

110 トランスポートコントローラ、118 割りこみコントローラ、

120 送信FIFO、122 受信FIFO、130 FIS生成回路、

132 FISデコード回路、150 リンクコントローラ、

160 リンクステート制御回路、190 フレーム生成回路、

192 フレームデコード回路、200 物理層回路、210 トランスミッタ、

220 レシーバ、230 OOB検出回路

【技術分野】

【0001】

本発明は、データ転送制御装置及び電子機器に関する。

【背景技術】

【0002】

近年、ストレージデバイス等のシリアルインターフェースとして、シリアルATA(Serial AT Attachment)と呼ばれる規格が脚光を浴びている。このシリアルATAは、パラレルATA(IDE)との間のソフトウェアレベルでの互換性を備えた規格である。そして最初の規格であるシリアルATA Iのデータ転送速度は1.5Gbpsであったが、次の規格であるシリアルATA II Gen2ではデータ転送速度が3.0Gbpsに高速化している。このシリアルATAを用いれば、電子機器が内蔵する回路基板間の配線本数を減らすことができ、電子機器のコンパクト化を図れる。

【0003】

ところが、電子機器のホスト(ホストデバイス、ホスト基板)は、パラレルATA(以下、適宜、PATAと呼ぶ)のインターフェース(以下、適宜、I/Fと呼ぶ)は備えているが、シリアルATA(以下、適宜、SATAと呼ぶ)のI/Fについては備えていないものが多い。このため、PATAI/Fのみを備えた既存のホストに対しては、SATAのデバイスを接続できないという問題がある。従って、PATAとSATAのブリッジ機能を有するデータ転送制御装置の提供が望まれる。

【0004】

しかしながら、このようなブリッジ機能を有するデータ転送制御装置において、SATAバスに接続されるSATAデバイスには、マスタ、スレーブの区別の概念が無く、PATAシステムに必要な初期化シーケンス管理機能を有しない。従って、単にSATAデバイスをデータ転送制御装置を介してPATAデバイスにブリッジ接続しただけでは、PATAにおける初期化シーケンスの処理主体が無く、PATAにおけるマスタ、スレーブの使い分けを実現できないという課題がある。

【特許文献1】特開2005−346123号公報

【特許文献2】特開2006−121621号公報

【特許文献3】特開2006−18428号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は、以上のような課題に鑑みてなされたものであり、本発明に係る幾つかの態様によれば、パラレルATAとシリアルATAのバスブリッジ機能を実現しながら初期化シーケンス処理についても適正に実現できる。

【課題を解決するための手段】

【0006】

本発明は、パラレルATAとシリアルATAのバスブリッジ機能を有するデータ転送制御装置であって、パラレルATAバスに接続され、ホストとの間のインターフェースを行うパラレルATAインターフェースと、シリアルATAバスに接続され、初期化シーケンス管理機能を有しないシリアルATAのデバイスとの間のインターフェースを行うシリアルATAインターフェースと、転送シーケンス制御を行うシーケンスコントローラを含み、前記シーケンスコントローラは、前記シリアルATAの前記デバイスに代わって初期化シーケンス管理を代行する初期化シーケンス管理部を含み、前記初期化シーケンス管理部は、マスタ・スレーブ設定端子によりデータ転送制御装置がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行い、前記マスタ・スレーブ設定端子によりデータ転送制御装置がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行うデータ転送制御装置に関係する。

【0007】

本発明によれば、シリアルATAデバイスが初期化シーケンス管理機能を有しない場合にも、この初期化シーケンス管理を代行して、スレーブ検知等の初期化シーケンス処理を実行できるようになる。そしてこのようにシリアルATAのデバイスに代わって初期化シーケンス処理を代行すれば、マスタ、スレーブの区別の概念の無いシリアルATAのデバイスを、マスタ、スレーブの区別が可能なパラレルATAのデバイスのように扱うことが可能になると共に、パラレルATAに準拠した適正な初期化シーケンス処理を実現できる。

【0008】

また本発明では、前記パラレルATAインターフェースは、タスクファイル・レジスタを有し、前記シリアルATAインターフェースは、前記タスクファイル・レジスタとの間でレジスタ値が転送されるシャドウ・タスクファイル・レジスタを含み、前記シーケンスコントローラは、データ転送制御装置がマスタ側に設定されているときに、前記ホストがマスタへのATAコマンドを発行した場合には、前記タスクファイル・レジスタのレジスタ値をそのまま前記シャドウ・タスクファイル・レジスタに転送し、データ転送制御装置がスレーブ側に設定されているときに、前記ホストがスレーブへのATAコマンドを発行した場合には、前記タスクファイル・レジスタのデバイス/ヘッドレジスタのDEVビットをマスタ設定に書き換えて前記タスクファイル・レジスタのレジスタ値を前記シャドウ・タスクファイル・レジスタに転送してもよい。

【0009】

このようにすれば、マスタ・スレーブ設定端子の状態に応じた適正な値に、デバイス/ヘッドレジスタのDEVビットが書き換えられるため、データ転送制御装置が例えばスレーブ側に設定された場合にも、ホストから、自身をマスタと認識しているシリアルATAデバイスに対して、コマンド、パラメータ等の適正な転送処理を実現できる。

【0010】

また本発明では、前記シーケンスコントローラは、データ転送制御装置がマスタ側に設定されているときに、前記ホストからのATAコマンドに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合には、前記シャドウ・タスクファイル・レジスタのレジスタ値を前記タスクファイル・レジスタにそのままに転送し、データ転送制御装置がスレーブ側に設定されているときに、前記ホストからのATAコマンドに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合には、前記シャドウ・タスクファイル・レジスタのデバイス/ヘッドレジスタのDEVビットをスレーブ設定に書き換えて前記シャドウ・タスクファイル・レジスタのレジスタ値を前記タスクファイル・レジスタに転送してもよい。

【0011】

このようにすれば、マスタ・スレーブ設定端子の状態に応じた適正な値に、デバイス/ヘッドレジスタのDEVビットが書き換えられるため、データ転送制御装置が例えばスレーブ側に設定された場合にも、自身をマスタと認識しているシリアルATAデバイスから、ホストに対して、ステータス等の適正な転送処理を実現できる。

【0012】

また本発明では、前記パラレルATAインターフェースは、ATAコマンドが前記タスクファイル・レジスタに書き込まれた場合に、コマンドライト検出信号をアクティブにし、前記シーケンスコントローラは、前記コマンドライト検出信号がアクティブになった場合に、前記タスクファイル・レジスタから前記シャドウ・タスクファイル・レジスタへのレジスタ値の転送処理及びDEVビットの書き換え処理を行ってもよい。

【0013】

このようなコマンドライト検出信号を利用すれば、少ない信号線でレジスタ値の転送処理やDEVビットの書き換え処理を実現できる。

【0014】

また本発明では、前記シリアルATAインターフェースは、前記パラレルATAバスを介して前記ホストがATAコマンドを発行した場合に、発行された前記ATAコマンドを含むレジスタFISを前記シリアルATAバスを介して前記デバイスに送信し、前記シーケンスコントローラは、前記レジスタFISに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合に、前記ホストから発行された前記ATAコマンドの転送シーケンス制御として、受信したFISの種類に応じた転送シーケンス制御を行ってもよい。

【0015】

このようにすれば、データ転送制御装置は、ホストが発行したATAコマンドの詳細な内容をデコードすることなく、ATAコマンドを含むレジスタFISをそのままデバイスに送信できる。そしてレジスタFISに対してデバイスが返却して来たFISの種類によって、転送シーケンスが制御される。従って、ATAコマンドのデコーダ回路を節約でき、データ転送制御装置の小規模化を図れる。また、新規コマンドの追加が発生しても、これに容易に対応できるようになる。

【0016】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISがPIOセットアップFISであり、PIOセットアップFISにより指定される転送方向がリード方向である場合には、PIOリードの転送シーケンス制御を行い、PIOセットアップFISにより指定される転送方向がライト方向である場合には、PIOライトの転送シーケンス制御を行ってもよい。

【0017】

このようにすれば、受信したFISがPIOセットアップか否かや、PIOセットアップFISで指定される転送方向を判断するだけで、PIOリードやPIOライトの転送シーケンスを制御できるようになる。

【0018】

また本発明では、前記シーケンスコントローラは、受信したPIOセットアップFISのパラメータに基づいて、転送方向、転送種別を設定してもよい。

【0019】

このようにすれば、転送方向、転送種別を設定した適正な転送シーケンス制御を実現できる。

【0020】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISがデータFISである場合には、DMAリードの転送シーケンス制御を行ってもよい。

【0021】

このようにすれば、受信したFISがデータFISか否かを判断するだけで、DMAリードの転送シーケンスを制御できるようになる。

【0022】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISがDMAアクティベートFISである場合には、DMAライトの転送シーケンス制御を行ってもよい。

【0023】

このようにすれば、受信したFISがDMAアクティベートFISか否かを判断するだけで、DMAライトの転送シーケンスを制御できるようになる。

【0024】

また本発明では、前記シーケンスコントローラは、前記デバイスから受信したFISが、デバイスからホストへのレジスタFISである場合には、ノーデータコマンドであると判断してもよい。

【0025】

また本発明は、上記のいずれかに記載のデータ転送制御装置と、前記データ転送制御装置に接続される前記ホストと、前記データ転送制御装置に接続される前記デバイスとを含む電子機器に関係する。

【発明を実施するための最良の形態】

【0026】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0027】

1.データ転送制御装置の構成

図1(A)、図1(B)に本実施形態のデータ転送制御装置の構成例を示す。このデータ転送制御装置はPATA(Parallel AT Attachment)とSATA(Serial AT Attachment)のバスブリッジ機能を有する。

【0028】

なお本実施形態のデータ転送制御装置は図1(A)、図1(B)の構成に限定されず、その構成要素の一部(例えばデータバッファ)を省略したり、他の構成要素(例えば外部I/F回路、CPU、タイマ)を追加するなどの種々の変形実施が可能である。例えば本実施形態のデータ転送制御装置は、PATAとSATAのバスブリッジ機能以外にも、PATAとUSB、PATAとSD(Secure Digital)カードインターフェス、PATAとCE−ATAのバスブリッジ機能を実現できるようにしてもよい。

【0029】

PATAI/F10(パラレルATAインターフェース)は、PATAバス(ATAバス、IDEバス)に接続され、ホスト2(ホストデバイス)との間のインターフェースを行う。具体的にはPATAI/F10は、ホスト2が有するホスト側のPATAI/FにPATAバスを介して接続される。そしてATAで規格化された後述する各種信号によりやり取りを行い、PATA(IDE)のデータ転送を実現する。またPATAI/F10は、データバッファ70を介したSATAI/F50との間のデータ転送制御も行う。このPATAI/F10は、PATAとSATAのブリッジ用に擬似的(仮想的)に設けられたタスクファイル・レジスタ12(以下、適宜、TFRと呼ぶ)を含むことができる。

【0030】

なおホスト2としては、例えばCPU、MPU、DSPなどのプロセッサや、専用制御ICや、これらのプロセッサ又は専用制御ICが実装されたホスト回路基板などが考えられる。またデバイス4としては、ハードディスクドライブ(HDD)、光ディスクドライブ(CD、DVD)、磁気ディスクドライブなどのSATAI/Fを備える各種デバイスが考えられる。

【0031】

SATAI/F50(シリアルATAインターフェース)は、SATAバス(高速シリアルバス)に接続され、SATAのデバイス4との間のインターフェースを行う。具体的にはSATAI/F50は、デバイス4が有するデバイス側のSATAI/Fに接続され、小振幅の差動信号によりやり取りを行い、SATAのデータ転送を実現する。またSATAI/F50は、データバッファ70を介したPATAI/F10との間のデータ転送制御も行う。このSATAI/F50は、SATA規格のシャドウ・タスクファイル・レジスタ52(以下、適宜SFRと呼ぶ)を含むことができる。

【0032】

シーケンスコントローラ30は転送のシーケンス制御を行う。具体的には、PATAとSATAのブリッジ機能を実現するために、PATAI/F10、SATAI/F50、データバッファ70の間のデータ転送のシーケンス制御を行ったり、レジスタ値の転送シーケンス制御を行う。

【0033】

データバッファ70は、ホスト2(PATAI/F)、デバイス4(SATAI/F)の間で転送されるデータのバッファリングを行う。そしてPATA側とSATA側のクロック周波数の差を吸収するための緩衝用のバッファ(FIFO)として機能する。即ちPATA側のクロック周波数が例えば50MHz(或いは60MHz)で、SATA側のクロック周波数が例えば37.5MHzである場合に、データバッファ70を設けることでこのクロック周波数の差を吸収できる。このデータバッファ70は、例えば50MHz(第1の周波数)でデータが入出力されるPATAI/F10側の第1のポートと、例えば37.5MHz(第2の周波数)でデータが入出力されるSATAI/F50側の第2のポートとを有するデュアルポートのメモリ(RAM)などにより実現できる。

【0034】

図1(A)、図1(B)の構成によれば、ホスト2がPATAI/Fしか備えていない場合にも、SATAI/Fを有するデバイス4をデータ転送制御装置を介してホスト2に接続できる。従って、ホスト2のファームウェア、ソフトウェアとして、既存のPATA(IDE)用のファームウェア、ソフトウェアを使用できる。これにより電子機器の開発期間の短縮化や低コスト化を図れる。またデバイス4として、市場供給量が多い大容量のHDDをホスト2に接続できるようになり、電子機器の内蔵HDDの大容量化を図れる。

【0035】

またホスト2が搭載される回路基板とデバイス4が搭載される回路基板の間を、シリアルバスであるSATAバスで接続できるため、回路基板間の配線本数を減らすことができ、電子機器のコンパクト化を図れる。

【0036】

そして実施形態では図1(A)、図1(B)に示すように、シーケンスコントローラ30が、初期化シーケンス管理機能を有しないSATAのデバイス4に代わって初期化シーケンス管理を代行する初期化シーケンス管理部34を含む。そして初期化シーケンス管理部34は、ハードリセット(ハードウェアリセット)等の後に初期化シーケンス処理を実行する。

【0037】

例えばSATAのデバイス4にはマスタ、スレーブの区別の概念が無いため、SATAのデバイス4はスレーブ検知等の初期化シーケンス管理機能を有しない。従って、PATAとSATAのブリッジ機能を有するデータ転送制御装置のSATAバスにSATAのデバイス4を接続する場合に、初期化シーケンス管理を行う処理主体が無くなってしまう。

【0038】

この点、図1(A)、図1(B)では初期化シーケンス管理部34が、初期化シーケンス管理機能を有しないSATAのデバイス4に代わって初期化シーケンス管理を代行して、初期化シーケンス処理を実行する。

【0039】

具体的には、図1(A)に示すように、データ転送制御装置に設けられたCSEL端子(マスタ・スレーブ設定端子)が例えばLレベルに設定され、データ転送制御装置がマスタ側に設定された場合には、初期化シーケンス管理部34は、ハードリセット後にスレーブ検知処理と自己診断処理を行う。

【0040】

一方、図1(B)に示すように、CSEL端子が例えばHレベルに設定され、データ転送制御装置がスレーブ側に設定された場合には、初期化シーケンス管理部34は、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行う。

【0041】

このようにすれば、ホスト2上で動作するドライバソフトウェアは、マスタ、スレーブの区別の概念の無いSATAのデバイス4を、マスタ、スレーブの区別が可能なPATAのデバイスのように扱うことが可能になり、利便性を大幅に向上できる。

【0042】

2.詳細な構成例

図2にデータ転送制御装置の詳細な構成例を示す。PATAI/F10はタスクファイル・レジスタTFR12、転送コントローラ14を含む。ここでTFR12は、PATAとSATAのバスブリッジ用に擬似的に設けられたレジスタである。このTFR12を設けることで、ホスト2は、SATAのデバイス4を、あたかもPATAのデバイスのように扱ってデータのリードやライトを行うことが可能になる。即ちホスト2は、既存のPATA用のファームウェアやソフトウェアを使用して、SATAのデバイス4を制御できるようになる。

【0043】

転送コントローラ14は、PATA用の信号XCS〜XPDIAGを用いてPATA(IDE)のインターフェースを実現したり、データ転送用の制御信号を用いて、データバッファ70との間のデータ転送を制御する。

【0044】

データバッファ70は、メモリコントローラ72、FIFOメモリ(FIFORAM)74を含む。メモリコントローラ72は、FIFOメモリ74のデータの書き込み制御や読み出し制御を行う。またPATAI/F10やSATAI/F50との間で、例えばREQ信号やACK信号などの制御信号を用いたデータ転送制御を行う。

【0045】

SATAI/F50は、シャドウ・タスクファイル・レジスタSFR52、トランスポートコントローラ110、リンクコントローラ150、物理層回路200を含む。

【0046】

トランスポートコントローラ110、リンクコントローラ150、物理層回路200は、各々、SATA規格のトランスポート層、リンク層、物理層の処理を行う回路である。

【0047】

シャドウ・タスクファイル・レジスタSFR52はSATAで規格化されているレジスタである。即ちSATAでは、従来のPATA(IDE)との間でソフトウェアレベルでの互換性が維持されており、タスクファイル・レジスタが2つ存在することが特徴になっている。即ちホスト(HBA)側のシャドウ・タスクファイル・レジスタとデバイス側の本来のタスクファイル・レジスタである。

【0048】

一方、PATAI/F10に設けられたTFR12はSATAで規格化されるレジスタではなく、PATAとSATAのブリッジ用に設けられた擬似的なレジスタである。ホスト2は、TFR12をPATAのタスクファイル・レジスタとして認識してアクセスし、レジスタ値を書き込んだり、レジスタ値を読み出す。すると本実施形態のデータ転送制御装置が、TFR12のレジスタ値をSFR52に転送したり、SFR52のレジスタ値をTFR12に転送するなどの処理を行う。

【0049】

このようにすれば、ホスト2が、PATAのTFR12にレジスタ値を書き込むと、そのレジスタ値がSATAのSFR52に転送されて書き込まれ、SATAバスを介してFIS(Frame Information Structure)によりデバイス4に転送されるようになる。またデバイス4からのFISによりSFR52に書き込まれたレジスタ値が、TFR12に転送されてホスト2に読み出されるようになる。従ってホスト2は、SATAのデバイス4を、あたかもPATAのデバイスのように扱ってデータのリードやライトを行うことが可能になり、PATAとSATAのブリッジ機能を効率良く実現できる。

【0050】

なおTFR12とSFR52の間のレジスタ値の転送は次のような手法により実現できる。即ちTFR12のレジスタ群のビット(全ビット)とSFR52のレジスタ群のビット(全ビット)を、シーケンスコントローラ30を介して信号線により接続しておく。そしてレジスタ値の転送を行う場合には、シーケンスコントローラ30が転送トリガ信号を生成し、この転送トリガ信号に基づいて、TFR12のレジスタ値をSFR52に転送したり、SFR52のレジスタ値をTFR12に転送すればよい。

【0051】

3.PATAI/F

次に、PATAI/F10のデータ転送処理について、図2の構成及び図3(A)〜図4(B)の信号波形を用いて説明する。

【0052】

XCS[1:0]は、PATAの各レジスタにアクセスするために使用するチップセレクト信号である。DA[2:0]は、データ又はデータポートにアクセスするためのアドレス信号である。DMARQ、XDMACKは、DMA転送に使用される信号である。データ転送の準備が整った時にデバイス側がDMARQをアクティブ(アサート)にし、これに応答して、ホスト側がXDMACKをアクティブにする。

【0053】

XDIOWは、レジスタ又はデータポートの書き込み時に使用するライト信号である。XDIORは、レジスタ又はデータポートの読み出し時に使用するリード信号である。IORDYは、デバイス側のデータ転送の準備が整っていない時のウェイト信号等に使用される。

【0054】

INTRQは、デバイス側が、ホスト側に対して割り込みを要求するために使用される信号である。このINTRQがアクティブになった後、ホスト側がデバイス側のTFR12のステータスレジスタの内容を読むと、所定時間後にデバイス側はINTRQを非アクティブ(ネゲート)にする。このINTRQを用いることで、デバイス側は、コマンド処理の終了をホスト側に通知できる。

【0055】

図3(A)、図3(B)は、PIO(Programmed I/O)リード、PIOライトの信号波形例である。PATAのTFR12のステータスレジスタのリードは図3(A)のPIOリードにより行い、コマンドレジスタへのライトは図3(B)のPIOライトにより行う。例えばホスト2によるATAコマンドの発行は、PIOライトにより実現できる。

【0056】

図4(A)、図4(B)は、DMAリード、DMAライトの信号波形例である。データ転送の準備ができると、デバイス側(データ転送制御装置)が、DMARQをアクティブにする。そして、それを受けて、ホスト側が、XDMACKをアクティブにして、DMA転送を開始する。その後、XDIOR(リード時)又はXDIOW(ライト時)を使用して、データDD[15:0]のDMA転送を行う。

【0057】

4.SATAI/F

次にSATAI/F50のデータ転送処理について説明する。図5はSATAの送信側のデータ転送処理の流れを示し、図6は受信側のデータ転送処理の流れを示している。

【0058】

図5に示すように送信側のトランスポートコントローラ(トランスポート層)では、シャドウ・タスクファイル・レジスタに書き込まれたコマンドやデータポートに入力されたデータによりFIS(Frame Information Structure)が生成される。ここでFISは、フレームのペイロード部であり、Dword(32ビット)単位で構成される。またフレームは、ホストとデバイスの間で交換される情報ユニットであり、SOF(Start Of Frame)プリミティブと、FISと、FISに対して計算されたCRC(Cyclic Redundancy Check)と、EOF(End Of Frame)プリミティブにより構成される。

【0059】

送信側のリンクコントローラでは、FISに対するCRCが演算されてFISの最後尾に付加される。そしてFIS及びCRCとスクランブルデータとの排他的論理和(XOR)をとるスクランブル処理が行われる。このようにスクランブルされたFIS及びCRCに対して、8b/10bのエンコードが行われる。ここで8b/10bエンコードは、8ビットのデータを10ビットの伝送キャラクタに変換するデータ伝送符号化のアルゴリズムであり、符号列内の1と0の数を揃え、連続的な伝送を保証する。そして8b/10bエンコード後のFIS及びCRCに対してSOF、EOFなどのプリミティブが付加される。

【0060】

送信側の物理層回路では、リンクコントローラからのパラレルデータがシリアルデータに変換され、小振幅の差動信号としてSATAバスに送信される。

【0061】

図6に示すように受信側の物理層回路では、SATAバスを介して受信したシリアルデータがパラレルデータに変換される。

【0062】

受信側のリンクコントローラでは、FIS及びCRCに付加されたプリミティブに対するデコードが行われる。またFIS及びCRCに対する8b/10bのデコードが行われる。即ち10ビットの伝送キャラクタが8ビットのデータに変換される。次に、スクランブルされたFIS及びCRCとスクランブルデータとの排他的論理和をとるデスクランブル処理が行われる。そしてFISの最後尾に付加されたCRCがチェックされる。

【0063】

受信側のトランスポートコントローラでは、FISのコマンドがシャドウ・タスクファイル・レジスタに書き込まれ、ステータスや割り込みが出力されると共に、データがデータポートを介して出力される。

【0064】

なお図7にATAのタスクファイル・レジスタのフォーマット例を示す。タスクファイル・レジスタはコントロールブロックレジスタとコマンドブロックレジスタを有し、チップセレクト信号XCS0、XCS1が、Hレベル(ネゲート)、Lレベル(アサート)である場合にはコントロールブロックレジスタが選択され、Lレベル、Hレベルである場合にはコマンドブロックレジスタが選択される。またコマンドブロックレジスタには、ステータスレジスタ(Status)やATAコマンドレジスタ(ATA Command)が設けられる。

【0065】

また図8(A)〜図8(D)に、SATAI/F50により送受信されるFISのフォーマット例を示す。図8(A)はホストからデバイスへのレジスタFIS、図8(B)はデバイスからホストへのレジスタFIS、図8(C)はPIOセットアップFIS、図8(D)はDMAアクティベートFISのフォーマットである。

【0066】

5.初期化シーケンス

次に、本実施形態の初期化シーケンス処理手法について具体的に説明する。

【0067】

5.1 CSEL端子

PATAデバイスのシステムでは、PATAバスに対して最大で2台のデバイスを接続でき、これらの2台のデバイスのうちの一方がマスタになり、他方がスレーブになる。そして各デバイスは、自身がマスタなのかスレーブなのかを、ジャンパピンの設定又はケーブルセレクトの設定により判断する。またPATAバスに対して2台のデバイスを接続した場合にも、同じアドレスが2台のデバイスで共有して使用される。従って、ATAレジスタ(タスクファイル・レジスタ)に対してホストから書き込み動作があった場合には、マスタ及びスレーブの両方のデバイスが、PATAのデータDD[15:0](図2参照)のバスからそのデータを受け取り、各デバイスは、DEVビット等に基づいて、そのデータが自身に宛てたデータなのか否かを判断する。またATAレジスタに対するホストからの読み出し動作があった場合には、マスタ、スレーブの各デバイスは、その時点でのDEVビットの状態と自身のデバイス番号を比較し、一致した場合にのみ、アクセスされたATAレジスタの内容をデータDD[15:0]のバスに出力する。

【0068】

このようにPATAデバイスにおいては、マスタ、スレーブの区別の概念があり、例えばATAのマスタ側にHDD等のデバイスを接続し、スレーブ側にCD、DVD等の光ディスクドライブのデバイスを接続するなどのシステム構成が可能になる。

【0069】

ところが、SATAデバイスにはマスタ、スレーブの区別の概念が無く、SATAデバイスはマスタとして取り扱われる。従って、データ転送制御装置にPATAとSATAのブリッジ機能を持たせた場合に、何ら工夫をしないと、例えばSATAデバイスをマスタとしてのみ取り扱うことができるマスタ専用のデータ転送制御装置になってしまう。従って、例えば光ディスクドライブなどのSATAデバイスを、スレーブとして、本実施形態のデータ転送制御装置を介してPATAバスにブリッジ接続するようなシステム構成等を実現できないという問題がある。

【0070】

そこで本実施形態では、マスタ・スレーブの設定端子(決定端子)であるCSEL端子をデータ転送制御装置に設けている。そしてデータ転送制御装置は、このCSEL端子の状態(電圧設定状態)により、自身がマスタ側なのかスレーブ側なのかを判断するようにしている。

【0071】

例えば図9(A)では、CSEL端子がLレベル(GNDレベル)に設定されており、この場合には本実施形態のデータ転送制御装置3は、自身がマスタ側に設定されたと判断する。そしてデータ転送制御装置3とそれに接続されるSATAデバイス4により、PATAのマスタ側が構成される。これにより、本実施形態のデータ転送制御装置3を含むPATAのマスタ側と、PATAのスレーブ側とが、PATAバスに接続されるシステム構成を実現できる。

【0072】

一方、図9(B)では、CSEL端子がHレベル(VDDレベル)に設定されており、この場合には本実施形態のデータ転送制御装置3は、自身がスレーブ側に設定されたと判断する。そしてデータ転送制御装置3とそれに接続されるSATAデバイス4により、PATAのスレーブ側が構成される。これにより、PATAのマスタ側と、本実施形態のデータ転送制御装置3を含むPATAのスレーブ側とが、PATAバスに接続されるシステム構成を実現できる。

【0073】

以上のように本実施形態では、PATAとSATAのブリッジ機能を有するデータ転送制御装置3に対して、マスタ・スレーブの設定端子であるCSEL端子を設けているため、例えば本来はマスタ、スレーブの区別の概念が無く、マスタとしてのみ取り扱われるSATAデバイス4を、データ転送制御装置3を介してPATAバスにブリッジ接続して、PATAのスレーブ側を構成することが可能になる。この結果、例えばSATAインターフェースを有する光ディスクドライブなどを、スレーブとして、PATAバスにブリッジ接続するシステム構成等を実現でき、利便性を大幅に向上できる。

【0074】

5.2 初期化シーケンス管理の代行

前述のように、SATAデバイスにはマスタ、スレーブの区別の概念が無く、SATAデバイスはマスタとしてのみ取り扱われる。従って、SATAデバイスは、マスタ、スレーブを区別するための初期化シーケンス管理機能を有しない。従って、このようなSATAデバイスを、PATAとSATAのブリッジ機能を有するデータ転送制御装置を介してPATAバスにブリッジ接続した場合に、初期化シーケンスの処理を行う処理主体が存在しなくなってしまうという問題がある。

【0075】

そこで本実施形態では、図1(A)、図1(B)の初期化シーケンス管理部34が、PATAにおける初期化シーケンス管理機能を有しないSATAデバイス4に代わって初期化シーケンス管理を代行する。例えば初期化シーケンス管理部34は、ハードリセット後、デバイス存在検知期間(10ms)内にSATAデバイス4の存在が検知された場合に、初期化シーケンス処理を実行する。具体的にはハードリセット後に、ホスト側であるSATAI/F50はOOBシーケンスにおけるCOMRESETを発行し、SATAデバイス4からのCOMINITを検出する。そして初期化シーケンス管理部34は、デバイス存在検知期間(10ms)内にSATAデバイス4からのCOMINITが検知された場合には、SATAデバイス4が存在すると判断して、本実施形態の初期化シーケンス処理を実行する。

【0076】

更に具体的には初期化シーケンス管理部34は、図9(A)のようにCSEL端子(マスタ・スレーブ設定端子)によりデータ転送制御装置3がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行う。一方、図9(B)のようにCSEL端子によりデータ転送制御装置3がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号の制御と自己診断信号の制御を行う。

【0077】

このようにすれば、SATAデバイス4が初期化シーケンス管理機能を有しない場合にも、データ転送制御装置3が、この初期化シーケンス管理を代行して、スレーブ検知等のPATAにおける初期化シーケンス処理を実行できる。従って、マスタとしてのみ取り扱われるSATAデバイス4を、例えばデータ転送制御装置3を介してPATAバスにブリッジ接続して、PATAのスレーブ側を構成した場合に、PATA規格に準拠した適正な初期化シーケンス処理を実行できるようになる。

【0078】

次に初期化シーケンス処理の詳細について図10、図11を用いて説明する。図10はホスト側の動作を説明するためのフローチャートであり、図11はデバイス側の動作を説明するためのフローチャートである。

【0079】

図10に示すようにホスト側は、ハードリセット信号をアクティブ(アサート状態)にした後、非アクティブ(ネゲート状態)にする(ステップS21、S22)。そしてステータスレジスタのBUSYビットが1から0にクリアされるのをウェイトし、0にクリアされるとホストアイドル状態に移行する(ステップS23、S24)。

【0080】

一方、図11に示すようにデバイス側は、ハードリセットが行われると、リリースバスステートに移行し、CSEL(CSEL端子、CSEL信号)がLレベルか否かを判断する(ステップS31、S32、S33)。即ち自身がマスタ側に設定されているか、スレーブ側に設定されているかを判断する。

【0081】

そしてCSELがLレベルに設定され、自身がマスタ側に設定されていると判断した場合には、XDASPウェイトステートに移行した後、サンプルXDASPステートに移行する(ステップS34、S35)。このサンプルXDASPステートでは、自身の初期化及び自己診断処理を行うと共に、スレーブ側からのスレーブ検知信号XDASPをサンプルしてモニタする。

【0082】

そして信号XDASPがLレベル(アクティブ)であると判断した場合には、スレーブの存在が検知されたと判断して、サンプルXPDIAGステートに移行する(ステップS36、S37)。このサンプルXPDIAGステートでは、スレーブ側からの自己診断信号XPDIAG(スレーブの自己診断結果の通知信号)をサンプルしてモニタする。

【0083】

そして信号XPDIAGがLレベル(アクティブ)であると判断した場合には、スレーブ側の自己診断がパスしたと判断し、タスクファイル・レジスタのエラーレジスタのビット7を0に設定する(ステップS38、S39)。一方、信号XPDIAGがHレベル(非アクティブ)であると判断した場合には、スレーブ側の自己診断がフェイルしたと判断し、エラーレジスタのビット7を1に設定する(ステップS40)。なおステップS36で、信号XDASPがHレベルであると判断された場合には、スレーブが非存在であると判断すると共に、エラーレジスタのビット7を0に設定する(ステップS41)。そしてセットステータスステートに移行し(ステップS42)、自己診断処理を完了すると共に、タスクファイル・レジスタのステータスレジスタのBUSYビットを0にクリアする。そしてデバイスアイドル状態に移行する(ステップS43)。

【0084】

一方、ステップS33でCSELがHレベルに設定され、自身がスレーブ側に設定されていると判断した場合には、セットXDASPステートに移行する(ステップS44)。このセットXDASPステートでは、スレーブ検知信号XDASPをLレベル(アクティブ)にすると共に、自身の初期化及び自己診断処理を行う。このようにスレーブ側がスレーブ検知信号XDASPをLレベルにすることで、ステップS36に示すようにマスタ側はスレーブの存在を検知できる。

【0085】

次に、セットステータスステートに移行する(ステップS45)。そして自己診断信号XPDIAGをLレベル(アクティブ)又はHレベル(非アクティブ)にすると共に、タスクファイル・レジスタのステータスレジスタのBUSYビットを0にクリアし、デバイスアイドル状態に移行する(ステップS46)。このようにスレーブ側が信号XPDIAGをLレベルにすることで、ステップS39に示すようにマスタ側はスレーブ側の自己診断がパスしたと判断できる。またスレーブ側が信号XPDIAGをHレベルにすることで、ステップS40に示すようにマスタ側はスレーブ側の自己診断がフェイルしたと判断できる。

【0086】

そして本実施形態では、初期化シーケンス管理部34は、CSEL端子がLレベルに設定され、自身がマスタ側に設定されたと判断した場合には、図11のステップS34〜S43に示すように、スレーブ検知処理と自己診断処理を行う。即ち、信号XDASPに基づいてスレーブが検知されたか否かを判断すると共に、マスタ側の自己診断処理や信号XPDIAGに基づくスレーブ側の自己診断結果の確認処理を行う。

【0087】

また初期化シーケンス管理部34は、CSEL端子がHレベルに設定され、自身がスレーブ側に設定されたと判断した場合には、図11のステップS44〜S46に示すように、スレーブ検知信号XDASP、自己診断信号XPDIAGの制御を行う。即ち、スレーブ検知信号XDASPをLレベルにして、スレーブの存在をマスタ側に通知する。また自己診断信号XPDIAGをLレベルにしたり、Hレベルにして、スレーブ側の自己診断結果をホスト側に通知する。

【0088】

以上のような初期化シーケンス処理を初期化シーケンス管理部34に代行させることで、マスタとしてのみ取り扱われるSATAデバイスに、マスタ、スレーブの区別の概念を導入できると共に、PATAの規格にしたがった適正な初期化シーケンス処理を実現できる。

【0089】

5.3 DEVビットの設定

前述したようにPATAでは、データDD[15:0]やアドレスDA[2:0]のバスは、マスタとスレーブで共用される。従って、マスタ及びスレーブの両方が、データDD[15:0]のバスからのコマンド、パラメータをタスクファイル・レジスタを介して受け取ることになる。そして、マスタへ宛てたものであるか、スレーブへ宛てたものであるかは、デバイス/ヘッドレジスタのDEVビットにより判断する。具体的にはDEVビットが0である場合にはマスタに宛てたものであると判断し、DEVビットが1である場合にはスレーブに宛てたものであると判断する。

【0090】

一方、SATAデバイスは、常にマスタとして取り扱われる。従ってSATAデバイスは、DEVビットが0に設定されたコマンド、パラメータだけを、自身に宛てたものとして受け取ることになる。

【0091】

ところが、図9(B)に示すように、CSEL端子をHレベルにしてスレーブ設定にした場合には、ホスト2はSATAデバイス4をスレーブと見なしている。従って、SATAデバイス4に対してコマンドやパラメータを送る場合には、DEVビットをスレーブ設定である1に設定する。従って、自身がマスタであると認識しているSATAデバイス4は、これらのコマンドやパラメータを受け取れなくなってしまう。そこで本実施形態では、以下のようなDEVビット設定手法を採用している。

【0092】

例えば図12(A)では、CSEL端子(CSEL信号)がLレベルに設定され、データ転送制御装置がマスタ側に設定されている。そしてホスト2がマスタへのATAコマンドを発行している。この場合には、シーケンスコントローラ30は、TFR12のレジスタ値(コマンド、パラメータ)をそのままSFR52に転送する。するとSATAI/F50は、SFR52のレジスタ値に基づいて、レジスタFIS(Host to Device)等を生成して、SATAデバイス4に送信する。

【0093】

このとき、TFR12のデバイス/ヘッドレジスタのDEVビット=0(マスタ設定)も、TFR12からSFR52にそのまま転送されて、SATAデバイス4に送信される。そしてSATAデバイス4は、自身をマスタとして認識しているため、ホスト2からのコマンドやパラメータを、問題なく受け取ることができる。

【0094】

また図12(B)では、データ転送制御装置がマスタ側に設定されているときに、ホスト2からのATAコマンドに対応するFIS(例えばレジスタFIS、PIOセットアップFIS、DMAアクティベートFIS等)を、SATAI/F50がSATAデバイス4から受信している。この場合には、シーケンスコントローラ30は、SFR52のレジスタ値をTFR12にそのまま転送する。そしてホスト2は、SATAデバイス4からのステータス等を受け取る。

【0095】

このとき、SFR52のデバイス/ヘッドレジスタのDEVビット=0(マスタ設定)も、SFR52からTFR12にそのまま転送される。従って、PATAI/F10は、マスタ側であるSATAデバイス4からのステータス等を、PATAのDD[15:0]のバスに適正に出力できるようになる。

【0096】

一方、図13(A)では、CSEL端子がHレベルに設定され、データ転送制御装置がスレーブ側に設定されている。そしてホスト2がスレーブへのATAコマンドを発行している。この場合には、シーケンスコントローラ30は、デバイス/ヘッドレジスタのDEVビットを1(スレーブ設定)から0(マスタ設定)に書き換えて、TFR12のレジスタ値をSFR52に転送する。するとSATAI/F50は、SFR52のレジスタ値に基づいて、レジスタFIS(H to D)等を生成して、SATAデバイス4に送信する。

【0097】

このとき、SATAデバイス4は、自身をマスタとして認識しているが、本実施形態ではDEVビットを1(スレーブ設定)から0(マスタ設定)に書き換えているため、ホスト2からのコマンドやパラメータを問題なく受け取ることができる。

【0098】

また図13(B)では、データ転送制御装置がスレーブ側に設定されているときに、ホスト2からのATAコマンドに対応するFISを、SATAI/F50がSATAデバイス4から受信している。この場合には、シーケンスコントローラ30は、SFR52のデバイス/ヘッドレジスタのDEVビットを0(マスタ設定)から1(スレーブ設定)に書き換えて、SFR52のレジスタ値をTFR12に転送する。そしてホスト2は、SATAデバイス4からのステータス等を受け取る。

【0099】

このとき、ホスト2は、SATAデバイス4をスレーブとして認識しているが、本実施形態ではDEVビットを0(マスタ設定)から1(スレーブ設定)に書き換えているため、SATAデバイス4からのステータス等を問題なく受け取ることができる。

【0100】

以上のように本実施形態では、CSEL端子の状態に応じた適正な値に、デバイス/ヘッドレジスタのDEVビットを書き換えている。従って、CSEL端子によりデータ転送制御装置をスレーブ側に設定した場合にも、ホスト2と、自身をマスタと認識しているSATAデバイス4との間で、コマンド、パラメータやステータスの適正な転送処理を実現できる。

【0101】

次に本実施形態のDEVビットの設定手法について図14、図15のフローチャートを用いて更に詳細に説明する。

【0102】

図14では、ホスト2がマスタへのATAコマンドを発行している(ステップS51)。そしてCSEL端子がLレベルか否かを判断し(ステップS52)、Lレベルである場合には、図12(A)で説明したようにTFR12のレジスタ値をそのままSFR52に転送する(ステップS53)。そしてSATAデバイス4へのコマンドの転送及び実行が行われる(ステップS54)。

【0103】

次に、SATAデバイス4からステータス返送のためのFIS(レジスタFIS等)を受信すると(ステップS55)、図12(B)で説明したようにSFR52のレジスタ値をそのままTFR12に転送する(ステップS56)。

【0104】

一方、ステップS52でCSEL端子がHレベルであると判断された場合には、ホスト2により発行されたATAコマンドは非実行になる(ステップS57)。即ち、ホスト2が発行したATAコマンドはマスタへ宛てたものであり、CSEL端子はスレーブ側に設定されているため、スレーブ側であるデータ転送制御装置は、このATAコマンドの実行処理を行わない。

【0105】

図15では、ホスト2がスレーブへのATAコマンドを発行している(ステップS61)。そしてCSEL端子がLレベルか否かを判断し(ステップS62)、LレベルではなくHレベルである場合には、図13(A)で説明したようにTFR12のデバイス/ヘッドレジスタのDEVビットを0(マスタ設定)に書き換えて、TFR12のレジスタ値をSFR52に転送する(ステップS63)。そしてSATAデバイス4へのコマンドの転送及び実行が行われる(ステップS64)。

【0106】

次に、SATAデバイス4からステータス返送のためのFIS(レジスタFIS等)を受信すると(ステップS65)、図13(B)で説明したようにSFR52のデバイス/ヘッドレジスタのDEVビットを1(スレーブ設定)に書き換えて、SFR52のレジスタ値をTFR12に転送する(ステップS66)。

【0107】

一方、ステップS62でCSEL端子がLレベルであると判断された場合には、ホスト2により発行されたATAコマンドは非実行になる(ステップS67)。即ち、ホスト2が発行したATAコマンドはスレーブへ宛てたものであり、CSEL端子はマスタ側に設定されているため、マスタ側であるデータ転送制御装置は、このATAコマンドの実行処理を行わない。

【0108】

6.コマンドライト検出によるレジスタ値の転送処理

次に、TFR12とSFR52の間でのレジスタ値の転送処理の具体的に説明する。

【0109】

本実施形態ではシーケンスコントローラ30は、図16(A)に示すようにTFR12にパラメータ(コマンドのパラメータ)が書き込まれた後、図16(B)に示すようにTFR12にATAコマンドが書き込まれたことを条件に、TFR12からSFR52へのレジスタ値の転送(更新)を行っている。具体的には、ATAコマンドがTFR12に書き込まれた場合に、コマンドライト検出信号がアクティブになる。シーケンスコントローラ30は、このようにコマンドライト検出信号がアクティブになった場合に、図12(A)、図12(B)で説明したTFR12からSFR52へのレジスタ値の転送処理を行う。更に、このようにコマンドライト検出信号がアクティブになった場合に、図13(A)、図13(B)で説明したDEVビットの書き換え処理も行う。

【0110】

即ちホスト2は、ATAコマンドを書き込む前に、そのATAコマンドに関連するパラメータをPATAバスを介してTFR12に書き込む。このようにパラメータの書き込みが行われたタイミングでは、シーケンスコントローラ30は、TFR12からSFR52へのレジスタ値の転送処理やDEVビットの書き換え処理を行わない。

【0111】

そして、ホスト2がパラメータの書き込み後にATAコマンド(例えばPIOリード、PIOライト、DMAリード、DMAライト、ノーデータコマンド等)をTFR12に書き込むと、コマンドライト検出信号がアクティブになってシーケンスコントローラ30に出力される。するとシーケンスコントローラ30は、TFR12に書き込まれたパラメータやATAコマンドのレジスタ値を、SFR52に転送して書き込む。またこの際にDEVビットの書き換え処理も行う。

【0112】

このようにすれば、レジスタ値の転送処理等を、ATAコマンドの書き込み時に一斉に行うことが可能になる。従って、転送処理を簡素化できると共に、転送処理に必要な信号線の数も減らすことができ、回路の小規模化や処理の簡素化を図れる。

【0113】

即ちパラメータの書き込み時にもレジスタ値を転送する手法を採用すると、複数回のレジスタ値の転送処理が必要になってしまい、処理が繁雑化する。またパラメータの書き込みの検出信号も必要になり、信号線の数も増える。

【0114】

一方、従来のPATA(IDE)用に作成されたホスト2のソフトウェアでは、パラメータを書き込んだ後に、ATAコマンドを書き込む手順となっているのが一般的である。図16(A)、図16(B)では、この点に着目し、ホスト2のソフトウェアがパラメータを書き込んだ後、ATAコマンドを書き込んだタイミングで、TFR12からSFR52へのレジスタ値の転送を行っている。これにより、従来のPATA用のソフトウェアをそのまま用いることができると共に、転送処理を簡素化でき、データ転送制御装置を小規模化できる。

【0115】

更に具体的にはレジスタ値の転送処理は以下のような手法により実現できる。

【0116】

例えば図16(C)のG1、G2に示すように、TFR12のレジスタ群の各ビット(全ビット)とSFR52のレジスタ群の各ビット(全ビット)は、シーケンスコントローラ30(信号線)を介して接続される。即ちTFR12のコントロールブロックレジスタやコマンドブロックレジスタ(ステータスレジスタ、コマンドレジスタ)などのレジスタ群から出力された信号(信号線)は、シーケンスコントローラ30に入力される。そしてこれらの信号は、シーケンスコントローラ30を介してSFR52に出力される。またSFR52のコントロールブロックレジスタやコマンドブロックレジスタなどのレジスタ群から出力された信号(信号線)も、シーケンスコントローラ30に入力され、シーケンスコントローラ30からTFR12に出力される。

【0117】

そしてシーケンスコントローラ30は、レジスタ値の転送トリガ信号(書き換えトリガ信号)TRG1、TRG2を生成し、生成され転送トリガ信号TRG1、TRG2に基づいて、TFR12、SFR52の間でのレジスタ値の転送を行う。例えばTFR12のレジスタ値を書き換える場合には、トリガ信号TRG1をアクティブにして、SFR52(或いは一時保存レジスタ)からのレジスタ値をTFR12に書き込む。またSFR52のレジスタ値を書き換える場合には、トリガ信号TRG2をアクティブにして、TFR12からのレジスタ値をSFR52に書き込む。なおこれらのトリガ信号TRG1、TRG2は、図16(B)で説明したコマンドライト検出信号等に基づいて生成できる。

【0118】

図16(C)のようにすれば、トリガ信号TRG1、TRG2をアクティブにするだけという簡素な制御で、レジスタ値の転送を実現できるため、回路の小規模化や処理の簡素化を図れる。またシーケンスコントローラ30は、転送されるレジスタ値をモニタできるため、よりインテリジェントなレジスタ値の転送制御を実現できる。

【0119】

7.受信FISの種類による転送シーケンス制御

本実施形態のようにブリッジ機能を有するデータ転送制御装置では、ホスト2が発行したATAコマンドに応じた転送シーケンス制御を行う必要がある。そして転送シーケンス制御の内容をデータ転送制御装置が知るためには、ATAコマンドをデコードする必要があり、そのために、コマンドデコーダやパラメータテーブルが必要になる。即ちホスト2が発行したコマンドをデコードし、転送方向(リード、ライト)や転送種別(PIO(Programmed I/O)、DMA)を判別し、内部転送シーケンスを決定する。

【0120】

しかしながら、このようなコマンドデコーダを設けると、データ転送制御装置のロジック回路の大規模化やメモリ容量の増加に繋がる。またATAコマンドのデコードを行うためには、デコードのためのコマンドテーブルを持たなければならないが、データ転送制御装置の開発終了後に、規格において新規コマンドの追加が発生した場合には、データ転送制御装置の回路修正を行わない限り、新規コマンドをサポートできなくなる。例えばATAPIでは、ブルーレイディスクなどの新しい規格の光ディスクドライブが追加されると、パラメータテーブルの変更が必要になる。従って、開発が終了している既存のデータ転送制御装置を使用できず、パラメータテーブル(テーブルメモリ)を変更するための回路修正が必要になり、余分な開発期間や開発コストがかかってしまう。更にベンダーにユニークな特殊コマンドに対しても、対応することが難しい。

【0121】

この場合にデータ転送制御装置にCPU(処理部)を内蔵させ、パラメータテーブルの変更をファームウェア等の書き換えにより実現すれば、新規コマンドが増えたり、コマンドの内容が変更された場合にも、これに対応できる。

【0122】

しかしながら、データ転送制御装置にCPUを内蔵させると、CPU上で動作するファームウェアの開発や、CPUの動作確認のためのデバッグツールの開発などが必要になってしまい、開発期間の長期化や高コスト化を招く。

【0123】

このような問題を解決するための図17(A)〜図18(C)に示す手法では、ホストが発行したコマンドをデコードすることなくデバイスに転送し、デバイスから返送されてきたFISの情報に基づいて、発行されたコマンドについての転送シーケンスを制御する。即ちATAコマンドのデコードを、データ転送制御装置が行うのではなく、SATAデバイスに行わせる。そしてデータ転送制御装置は、ATAコマンドをデコードせずに(一部をデコードしてもよい)、SATAデバイスにそのまま転送し、SATAデバイスの反応を観察することで、自身の転送シーケンスを決定して実行する。

【0124】

具体的には図17(A)に示すようにホスト2がPATAバスを介してATAコマンド(転送コマンド)を発行すると、PATAI/F10がこのコマンドを受ける。そしてSATAI/F50は、発行されたATAコマンドを含むレジスタFIS(Host to Device)を作成して、SATAバスを介してデバイス4に送信する。

【0125】

デバイス4側のSATAI/F(図示せず)は、レジスタFISを受信すると、デコード処理を行い、レジスタFIS(ATAコマンド)に対応するFISを送信し、このFISをSATAI/F50が受信する。

【0126】

シーケンスコントローラ30(転送シーケンサ、ブリッジシーケンサ)は、レジスタFISに対応するFISをSATAI/F50がデバイス4から受信すると、ホスト2から発行されたATAコマンドの転送シーケンス制御として、受信したFISの種類に応じた転送シーケンス制御を行う。

【0127】

より具体的には図17(B)ではホスト2はPIOリードのATAコマンドを発行している。この場合にはデバイス4は、転送方向がリード方向であるPIOセットアップFISを送信する。即ちPIOのデータ転送の直前にデバイス4がホスト2に転送するFISであるPIOセットアップFISを、デバイス4が送信し、SATAI/F50が受信する。このPIOセットアップFISは、データ転送の初期ステータス(Status)及びステータス終了値(E_Status)を有する。

【0128】

このように受信FISがPIOセットアップFISであり、PIOセットアップFISにより指定される転送方向がリード方向である場合には、シーケンスコントローラ30は、PIOリードの転送シーケンス制御を行う。即ちシーケンスコントローラ30は、PIOリードの転送シーケンスのための制御信号(転送方向設定信号、転送開始信号、転送停止信号等)をSATAI/F50、データバッファ70、PATAI/F10に出力する。これにより、デバイス4から読み出されたデータが、SATAI/F50、データバッファ70、PATAI/F10を介してホスト2に転送される。

【0129】

図17(C)では、ホスト2はPIOライトのATAコマンドを発行している。この場合にはデバイス4は、転送方向がライト方向であるPIOセットアップFISを送信し、SATAI/F50が受信する。

【0130】

このように受信FISがPIOセットアップFISであり、PIOセットアップFISにより指定される転送方向がライト方向である場合には、シーケンスコントローラ30は、PIOライトの転送シーケンス制御を行う。即ちシーケンスコントローラ30は、PIOライトの転送シーケンスのための制御信号をPATAI/F10、データバッファ70、SATAI/F50に出力する。これにより、ホスト2からのデータが、PATAI/F10、データバッファ70、SATAI/F50を介してデバイス4に転送される。

【0131】

図18(A)では、ホスト2はDMAリードのATAコマンドを発行している。この場合にはデバイス4はデータFISを送信する。即ちデバイス4はデータ転送のためのFISであるデータFISを送信し、SATAI/F50が受信する。

【0132】

このように受信FISがデータFISである場合には、シーケンスコントローラ30は、DMAリードの転送シーケンス制御を行う。これにより、デバイス4から読み出されたデータが、SATAI/F50、データバッファ70、PATAI/F10を介してホスト2にDMA転送される。

【0133】

図18(B)では、ホスト2はDMAライトのATAコマンドを発行している。この場合にはデバイス4はDMAアクティベートFISを送信する。即ちDMAの実行準備が出来ていることをホスト2に知らせるためのDMAアクティベートFISを、デバイス4が送信し、SATAI/F50が受信する。

【0134】

このように受信FISがDMAアクティベートFISである場合には、シーケンスコントローラ30は、DMAライトの転送シーケンス制御を行う。これにより、ホスト2からのデータが、PATAI/F10、データバッファ70、SATAI/F50を介してデバイス4にDMA転送される。

【0135】

図18(C)では、ホスト2はノーデータコマンドのATAコマンドを発行している。この場合にはデバイス4はレジスタFIS(Device to Host)を送信し、SATAI/F50が受信する。このように、ATAコマンドに対応する受信FISが、デバイス4からホスト2へのレジスタFISである場合には、シーケンスコントローラ30は、ホスト2から発行されたATAコマンドはノーデータコマンドであると判断する。そしてレジスタFISのレジスタ値を、SATAI/F50のシャドウ・タスクファイル・レジスタからPATAI/F10のタスクファイル・レジスタに反映させる。

【0136】

以上のように、図17(A)〜図18(C)の手法によれば、ホスト2が発行したATAコマンドをデコードしなくても、デバイス4からの受信FIS情報に基づいて、発行されたATAコマンドの種別を判断して、そのATAコマンドに対応する転送シーケンス制御を実現できる。従って、コマンドデコーダの回路を節約でき、データ転送制御装置の小規模化を図れる。また、規格において新規コマンドの追加が発生しても、データ転送制御装置の回路修正を行うことなく、これに対応できる。またデータ転送制御装置にCPUを内蔵させなくても済むため、CPU上で動作するファームウェアの開発やデバッグツールの開発が不要になり、開発期間を短縮化でき、開発コストを低減できる。なおデータ転送制御装置にATAコマンドの一部をデコードする回路を設けたり、CPU(処理部)を内蔵させる変形実施も可能である。

【0137】

そして図17(A)〜図18(C)の手法を実現するために、本実施形態では、シーケンスコントローラ30が、TFR12とSFR52の間でのレジスタ値の転送処理を行っている。具体的には図12(A)に示すように、ホスト2によりマスタへのATAコマンドが発行され、CSEL端子がマスタ側であるLレベルに設定されている場合に、TFR12のレジスタ値をSFR52にそのまま転送する。即ちシーケンスコントローラ30は、TFR12のレジスタ値をデコードすることなく、SFR52にそのままコピーする。また図12(B)に示すように、発行されたATAコマンドに対応するFISを受信した場合には、シーケンスコントローラ30は、SFR52のレジスタ値をそのままTFR12に転送(コピー)する。このようにすれば、コマンドデコード処理などの負荷が重い処理を行うことなく、ホスト2からのコマンド、パラメータ等をデバイス4に転送したり、デバイス4からのステータス等をホスト2に転送することが可能になる。

【0138】

一方、ホスト2によりスレーブへのATAコマンドが発行され、CSEL端子がスレーブ側であるHレベルに設定されている場合に、図17(A)〜図18(C)の手法を実現するためにTFR12とSFR52の間でレジスタ値をそのまま転送すると、誤った転送処理が行われてしまう。

【0139】

そこで図13(A)では、TFR12からSFR52にレジスタ値をそのまま転送するのではなく、DEVビットをマスタ設定である0に書き換えて転送している。また図13(B)では、SFR52からTFR12にレジスタ値をそのまま転送するのではなく、DEVビットをスレーブ設定である1に書き換えて転送している。

【0140】

このようにすれば、図17(A)〜図18(C)の手法を採用した場合にも、ホスト2と、自身をマスタと認識しているSATAデバイス4との間で、コマンド、パラメータ、ステータス等の適正な転送処理を実現できる。

【0141】

8.PIO転送、DMA転送

次に本実施形態のデータ転送制御装置により実現されるPIO転送、DMA転送の詳細について図19〜図22を用いて更に具体的に説明する。

【0142】

図19はPIOリードの転送シーケンス図である。ホスト2によりPIOリードのコマンドが発行されると、図19のA1に示すようにTFR12のステータスレジスタがD0hに設定される。即ちPATAI/F10によりBUSYビットが1にセットされ、デバイス4がビジー状態であることがホスト2に知らされる。そしてシーケンスコントローラ30によりTFR12のレジスタ値がSFR52に転送(コピー)される。するとA2に示すように、SATAI/F50は、SFR52のレジスタ値に基づいてPIOリードコマンドを含むレジスタFIS(Host to Device)を作成し、SATAバスを介してデバイス4に送信する。

【0143】

このレジスタFISを受信したデバイス4は、A3に示すようにPIOセットアップFISを送信する。この場合に図8(C)のPIOセットアップFISのステータス(Status)には58hが設定され、エンドステータス(E_Status)にはD0hが設定される。ここでD0hではBUSYビットが1にセットされ、58hではDRQビットが1にセットされる。また50hではBUSYビット及びDRQビットが共に0にクリア(解除)される。またエンドステータスは例えばSATAI/F50の一時保存レジスタに保存される。

【0144】

シーケンスコントローラ30は、デバイス4からPIOセットアップFISを受信し、その方向パラメータD(図8(C)参照)がデバイスからホストへの方向である場合には、ホスト2が発行したコマンドはPIOリードであると判断する。そしてSFR52からTFR12にレジスタ値を転送し、A4に示すようにTFR12のステータスレジスタを58hに設定して、DRQビットを1にセットする。これによりホスト2に対する割り込みINTRQが発生する。なおINTRQの代わりにホスト2によるポーリングを採用してもよい。

【0145】

そしてデバイス4からデータFISを受信し、ホスト2がデータをリードすると、A5に示すように、PIOセットアップFISのエンドステータスであるD0hがTFR12のステータスレジスタに設定され、BUSYビットが1にセットされる。即ちSATAI/F50の一時保存レジスタに保存されたエンドステータス(D0h)が、TFR12のステータスレジスタに転送されて書き込まれる。これにより、デバイス4がビジー状態であることがホスト2に知らされる。

【0146】

以上のようにして各セクタのPIOリードが繰り返される。そしてA6に示すように最後のセクタのPIOセットアップFISではエンドステータスが50h又は51hになっている。従ってA7に示すようにこのエンドステータス50h又は51hがTFR12のステータスレジスタに設定され、DRQビットがクリアされる。これにより、全てのデータ転送が完了したことがホスト2に知らされる。

【0147】

図20はPIOライトの転送シーケンス図である。ホスト2によりPIOライトのコマンドが発行されると、B1に示すようにBUSYビットが1にセットされる(D0h)。そしてTFR12のレジスタ値がSFR52に転送され、B2に示すようにPIOライトコマンドを含むレジスタFISがデバイス4に送信される。

【0148】

このレジスタFISを受信したデバイス4は、B3に示すようにPIOセットアップFISを送信する。そしてシーケンスコントローラ30は、デバイス4からPIOセットアップFISを受信し、その方向パラメータD(図8(C)参照)がホストからデバイスへの方向である場合には、ホスト2が発行したコマンドはPIOライトであると判断する。そしてSFR52からTFR12にレジスタ値を転送し、B4に示すようにTFR12のステータスレジスタを58hに設定して、DRQビットを1にセットする。これによりホスト2に対する割り込みINTRQが発生する。

【0149】

そしてホスト2がデータをライトすると、B5に示すように、PIOセットアップFISのエンドステータスであるD0hがTFR12のステータスレジスタに設定される。

【0150】

以上のようにして各セクタのPIOライトが繰り返される。そしてB6に示すように最後のセクタの転送が終わると、デバイス4がレジスタFISを送信する。するとこのレジスタFISのステータス(50h又は51h)が、SFR52からTFR12に転送されて、B7に示すようにDRQビットがクリアされる。

【0151】

図21はDMAリードの転送シーケンス図である。ホスト2によりDMAリードのコマンドが発行されると、C1に示すようにBUSYビットが1にセットされる(D0h)。PIO転送とは異なりDMA転送では、データ転送中にBUSYビットが1にセットされたままになる。そしてTFR12のレジスタ値がSFR52に転送され、C2に示すようにDMAリードコマンドを含むレジスタFISがデバイス4に送信される。

【0152】

このレジスタFISを受信したデバイス4は、C3に示すようにデータFISを送信する。シーケンスコントローラ30は、デバイス4から受信したFISがデータFISである場合には、ホスト2が発行したコマンドはDMAリードであると判断する。そしてC4に示すようにDMARQがアサートされて、DMA転送が開始し、デバイス4のデータがホスト2にリードされる。

【0153】

そしてDMA転送が終了し、デバイス4がレジスタFISを送信すると、C5に示すように、SFR52のレジスタ値がTFR12に転送されて、BUSYビットがクリアされる(50h又は51h)。

【0154】

図22はDMAライトの転送シーケンス図である。ホスト2によりDMAライトのコマンドが発行されると、D1に示すようにBUSYビットが1にセットされる(D0h)。そしてTFR12のレジスタ値がSFR52に転送され、D2に示すようにDMAライトコマンドを含むレジスタFISがデバイス4に送信される。

【0155】

このレジスタFISを受信したデバイス4は、D3に示すようにDMAアクティベートFISを送信する。シーケンスコントローラ30は、デバイス4から受信したFISがDMAアクティベートFISである場合には、ホスト2が発行したコマンドはDMAライトであると判断する。そしてD4に示すようにDMARQがアサートされて、DMA転送が開始し、ホスト2のデータがデバイス4にライトされる。

【0156】

そしてDMA転送が終了し、デバイス4がレジスタFISを送信すると、D5に示すように、SFR52のレジスタ値がTFR12に転送され、BUSYビットがクリアされる(50h又は51h)。

【0157】

9.SATAI/Fの構成

図23にSATAI/F50の構成例を示す。なおSATAI/F50の構成は図23に限定されず、その構成要素の一部を削除したり、他の構成要素を追加するなどの種々の変形実施が可能である。例えば物理層回路200を設けない構成としてもよい。

【0158】

SATAでは、データは32ビット(4バイト)単位で処理される。この32ビットのデータが、リンクコントローラ150により8b/10bでエンコードされて40ビットのデータになり、物理層回路200に送られる。物理層回路200は、この40ビットのデータをシリアル化してSATAのケーブルに送信する。受信も逆の手順で、シリアルデータが物理層回路200で40ビットのデータに変換され、リンクコントローラ150で32ビットのデータに変換され、トランスポートコントローラ110に送られる。

【0159】

トランスポートコントローラ110はトランスポート層の制御を行うものである。具体的にはトランスポートコントローラ110は、上位層(アプリケーション層)からFISの送信要求が来た時に、以下の処理を行う。

【0160】

まずトランスポートコントローラ110は、FISタイプの要件に基づいてFISの内容を収集する。また送信する情報をFISのタイプ毎に定義フォーマットに配置する。次にリンクコントローラ150に対して送信要求を通知する。これによりリンクコントローラ150はX_RDYの送信処理を行う。そして相手ノードからのR_RDYを受信し、リンクコントローラ150から受信のアクノリッジが来ると、トランスポートコントローラ110はFISをリンクコントローラ150に転送する。そして送信FIFO120のフロー管理を行い、必要なフロー制御をリンクコントローラ150に通知する。その後、リンクコントローラ150から送信結果を受信すると、必要に応じて上位層に送信結果を通知する。

【0161】

トランスポートコントローラ110は、リンクコントローラ150からFISを受信した時には、以下の処理を行う。

【0162】

トランスポートコントローラ110は、リンクコントローラ150からFISを受信すると、受信したFISのタイプを判別する。そしてFISのタイプに応じた適切なレジスタやFIFOにデータを転送する。そして受信FIFO122のフロー管理を行い、必要なフロー制御をリンクコントローラ150に通知する。その後、リンクコントローラ150及び上位層(アプリケーション層)に受信結果を通知する。

【0163】

リンクコントローラ150はリンク層の制御を行うものである。具体的にはリンクコントローラ150は、送信時には以下の処理を行う。

【0164】

まずリンクコントローラ150はトランスポートコントローラ110からのデータ(FIS)を受け取る。そしてFISのCRCを生成し、FISの最後尾に付加する。次にデータのスクランブルを行い、その後、8b/10bのエンコードを行う。そしてSATA通信のプロトコルにしたがったプリミティブ、FISの送信を行う。そして送信結果をトランスポートコントローラ110に通知する。

【0165】

リンクコントローラ150は受信時には以下の処理を行う。即ちリンクコントローラ150は物理層回路200から、8b/10bエンコードキャラクタを受信する。そして8b/10bエンコードキャラクタをデコードし、デコードしたプリミティブを処理部等に通知する。次にデコードしたFISのデスクランブル処理を行い、CRCをチェックする。そしてトランスポートコントローラ110にデータを渡す。またデコード結果やCRCのチェック結果をトランスポートコントローラ110に通知する。

【0166】

物理層回路200は物理層を実現するアナログフロントエンド回路である。この物理層回路200は、シリアルデータ(シリアルストリーム)の送受信や、シリアルデータからパラレルデータへの変換や、パラレルデータからシリアルデータへの変換を行う。また8b/10bのK28.5キャラクタの検出や、OOB(Out Of Band)信号の検出と送信を行う。またデバイスステータス(デバイスの有無、転送状態、パワー状態)の提供や、通信制御用のインターフェース(転送レート制御、ループバック)の提供を行う。またオプションでパワーマネージメントも行う。

【0167】

物理層回路(PHY)200はトランスミッタ(ドライバ)210、レシーバ220、OOB検出回路230などを含む。

【0168】

トランスミッタ210は、差動信号線(差動信号線ペア)TX+/−を介してシリアルデータ(パケット)の送信を行い、レシーバ220は、差動信号線(差動信号線ペア)RX+/−を介してシリアルデータ(パケット)の受信を行う。TX+/−、RX+/−のSATAバス(広義にはシリアルバス)では、振幅電圧+/−250mVのNRZ差動信号によるシリアルストリーム転送が行われる。

【0169】

OOB検出回路230はOOB信号の検出処理を行う。このOOB信号は、SATAインターフェースのリセット/初期化、通信の確立や、スピード・ネゴシエーションをつかさどる信号である。

【0170】

リンクコントローラ150は、リンクステート制御回路160、フレーム生成回路190、フレームデコード回路192を含む。

【0171】

リンクステート制御回路160は、リンクコントローラ150のステート制御を行う。例えばリセットステート、アイドルステート、送信ステート、受信ステート等のステート間の遷移処理等を行う。

【0172】

フレーム生成回路190は、トランスポートコントローラ110からの送信データ(FIS)や、リンクステート制御回路160からの送信制御信号などに基づいてフレームの生成処理を行う。具体的には、トランスポートコントローラ110からのFISのCRCを演算したり、スクランブル処理を行ったり、8b/10bエンコード処理を行ったり、プリミティブを生成して付加する処理などを行う。

【0173】

フレームデコード回路192は、受信したフレームの解析(分解)処理を行い、受信解析信号(パワーダウンリクエスト信号等)をリンクステート制御回路160に出力する。具体的には、FISに付加されたプリミティブを解析したり、8b/10bのデコード処理を行ったり、デスクランブル処理を行ったり、CRCを演算してチェックする処理などを行う。

【0174】

トランスポートコントローラ110は、割りこみコントローラ118、DMA制御回路119、送信FIFO120、受信FIFO122、FIS生成回路130、FISデコード回路132、トランスポートステート制御回路140を含む。

【0175】

割り込みコントローラ118は、デバイス4からの受信FIS情報などを知らせるための割り込み信号を生成する。DMA制御回路119は、FISに含まれる送信データや受信データ(コンテンツ・データ)のDMA転送を制御する。送信FIFO120は、DMA制御回路119からの送信データのバッファとなるFIFOである。受信FIFO122は、リンクコントローラ150からの受信データのバッファとなるFIFOである。FIS生成回路130はFISの生成を行う回路であり、FISデコード回路132はFISの解析を行う回路である。トランスポートステート制御回路140は、トランスポートコントローラ110のステート制御を行う。

【0176】

10.シーケンスコントローラ

図24にシーケンスコントローラ30の構成例を示す。シーケンスコントローラ30はレジスタ更新部32、初期化シーケンス管理部34、パラメータ書き換え部36、DMAモード設定記憶部38、転送制御部40を含む。なおシーケンスコントローラ30の構成は図24に限定されず、その構成要素の一部を削除したり、他の構成要素を追加するなどの種々の変形実施が可能である。

【0177】

レジスタ更新部32はTFR12(タスクファイル・レジスタ)、SFR52(シャドウ・タスクファイル・レジスタ)のレジスタ値の更新処理を行う。具体的にはTFR12のレジスタ値をSFR52に転送してSFR52のレジスタ値を更新したり、SFR52のレジスタ値をTFR12に転送してTFR12のレジスタ値を更新する。

【0178】

例えばTFR12にホスト2によりATAコマンドが書き込まれると、PATAI/F10はコマンドライト検出信号をアクティブにする。そしてコマンドライト検出信号がアクティブになると、レジスタ更新部32はTFR12のレジスタ値をSFR52に転送する処理を行う。

【0179】

またSATAI/F50は、デバイス4から受信したFISをデコードし、デコード結果に基づいて、FISの種類を知らせるための割り込み信号(広義には受信FIS情報)を生成して出力する。レジスタ更新部32は、この割り込み信号に基づいて受信FISの種類を判別して、SFR52からTFR12へのレジスタ値の転送処理などを行って、レジスタ値の更新処理を行う。

【0180】

初期化シーケンス管理部34は、HRST(ハードリセット)、SRST(ソフトリセット)に伴う初期化シーケンスを管理する。具体的には、マスター、スレーブなどの設定をモニタして、PATAの初期化シーケンスを管理する。

【0181】

パラメータ書き換え部36は、ホスト2がデバイス4に対してアイデンティファイ・デバイス・コマンドを発行し、デバイス4からデバイス情報のパラメータを受信した場合に、パラメータの書き換え処理を行う。即ち転送速度などのパラメータを自身が対応可能なパラメータに書き換える。

【0182】

DMAモード設定記憶部38は、ホスト2がセットフューチャー・コマンドを発行した場合に、セットフューチャー・コマンドを解析して、DMA転送のモード設定を記憶する。

【0183】

転送制御部40はデータ転送制御装置の転送シーケンスを制御するものであり、モニタ部42、制御信号生成部44を含む。モニタ部42は、PATAI/F10からのコマンドライト検出信号や、SATAI/F50からの割り込み信号(受信FIS情報)などの信号をモニタする。そして制御信号生成部44は、モニタ結果に基づいて、転送方向設定信号、転送開始信号、転送停止信号などの制御信号を生成し、PATI/F10、データバッファ70、SATAI/F50に出力して、転送シーケンス制御を実行する。なおデータバッファ70に対しては転送開始信号、転送停止信号は出力せず、転送方向設定信号を出力する。

【0184】

11.電子機器

図25に本実施形態の電子機器の構成例を示す。この電子機器は、本実施形態で説明したデータ転送制御装置310とホスト302とデバイス304を含む。ホスト302とデータ転送制御装置310はPATAバスを介して接続され、データ転送制御装置310とデバイス304はSATAバスを介して接続される。なお本実施形態の電子機器の構成は図25に限定されず、その構成要素の一部を省略したり、他の構成要素を付加する変形実施が可能である。

【0185】

同図においてデバイス304は、HDD(ハードディスクドライブ)等のストレージデバイスや、光ディスクドライブ(CD、DVD)等である。

【0186】

ホスト302は、処理部330(CPU)、ROM340、RAM350、表示部360、操作部370を含むことができる。処理部330(CPU)はデータ転送制御装置310や電子機器の全体制御を行う。なおデータ転送制御装置310を制御する処理部と、電子機器を制御する処理部とを別々に設けてもよい。ROM340は制御プログラムや各種データを記憶する。RAM350は処理部330やデータ転送制御装置310のワーク領域やデータ格納領域として機能する。表示部360は種々の情報をユーザに表示する。操作部370はユーザが電子機器を操作するためのものである。

【0187】

本実施形態の電子機器によれば、ホスト302がSATAI/Fを有していない場合にも、データ転送制御装置310を介してSATAのデバイス304をホスト302に接続して、あたかもPATAのデバイスのように扱うことが可能になる。

【0188】

なお、本実施形態を適用できる電子機器としては、カーナビゲーションシステム、車載用オーディオ機器、HDDレコーダ、ビデオカメラ、携帯型音楽プレーヤ、携帯型映像プレーヤ、ゲーム装置、又は携帯型ゲーム装置等の種々のものが考えられる。

【0189】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。またデータ転送制御装置、電子機器の構成、動作も本実施形態で説明したものに限定に限定されず、種々の変形実施が可能である。また本実施形態では、SATAへの本発明の適用例について説明したが、本発明は、SATAと同様の思想に基づく規格や、SATA(SATA I、SATA II、SAS)を発展させた規格等にも適用できる。

【図面の簡単な説明】

【0190】

【図1】図1(A)、図1(B)は本実施形態のデータ転送制御装置の構成例。

【図2】本実施形態のデータ転送制御装置の詳細な構成例。

【図3】図3(A)、図3(B)はPIOリード、PIOライトの信号波形例。

【図4】図4(A)、図4(B)はDMAリード、DMAライトの信号波形例。

【図5】SATAの送信側のデータ処理の説明図。

【図6】SATAの受信側のデータ処理の説明図。

【図7】タスクファイル・レジスタのフォーマット例。

【図8】図8(A)〜図8(D)はFISのフォーマット例。

【図9】図9(A)、図9(B)はCSEL端子の設定手法の説明図。

【図10】初期化シーケンス処理を説明するためのフローチャート。

【図11】初期化シーケンス処理を説明するためのフローチャート。

【図12】図12(A)、図12(B)は本実施形態のDEVビットの設定手法の説明図。

【図13】図13(A)、図13(B)は本実施形態のDEVビットの設定手法の説明図。

【図14】本実施形態のDEVビットの設定手法を説明するためのフローチャート。

【図15】本実施形態のDEVビットの設定手法を説明するためのフローチャート。

【図16】図16(A)〜図16(C)は本実施形態のレジスタ値転送手法の説明図。

【図17】図17(A)〜図17(C)は本実施形態のシーケンス制御手法の説明図。

【図18】図18(A)〜図18(C)は本実施形態のシーケンス制御手法の説明図。

【図19】PIOリードの転送シーケンス図。

【図20】PIOライトの転送シーケンス図。

【図21】DMAリードの転送シーケンス図。

【図22】DMAライトの転送シーケンス図。

【図23】SATAI/Fの構成例。

【図24】シーケンスコントローラの構成例。

【図25】電子機器の構成例。

【符号の説明】

【0191】

2 ホスト、4 デバイス、10 PATAI/F、

12 タスクファイル・レジスタ(TFR)、14 転送コントローラ、

30 シーケンスコントローラ、32 レジスタ更新部、

34 初期化シーケンス管理部、36 パラメータ書き換え部、

38 DMA転送設定記憶部、40 転送制御部、

42 モニタ部、44 制御信号生成部、50 SATAI/F、

52 シャドウ・タスクファイル・レジスタ(SFR)、70 データバッファ、

72 メモリコントローラ、74 FIFOメモリ、

110 トランスポートコントローラ、118 割りこみコントローラ、

120 送信FIFO、122 受信FIFO、130 FIS生成回路、

132 FISデコード回路、150 リンクコントローラ、

160 リンクステート制御回路、190 フレーム生成回路、

192 フレームデコード回路、200 物理層回路、210 トランスミッタ、

220 レシーバ、230 OOB検出回路

【特許請求の範囲】

【請求項1】

パラレルATAとシリアルATAのバスブリッジ機能を有するデータ転送制御装置であって、

パラレルATAバスに接続され、ホストとの間のインターフェースを行うパラレルATAインターフェースと、

シリアルATAバスに接続され、初期化シーケンス管理機能を有しないシリアルATAのデバイスとの間のインターフェースを行うシリアルATAインターフェースと、

転送シーケンス制御を行うシーケンスコントローラを含み、

前記シーケンスコントローラは、

前記シリアルATAの前記デバイスに代わって初期化シーケンス管理を代行する初期化シーケンス管理部を含み、

前記初期化シーケンス管理部は、

マスタ・スレーブ設定端子によりデータ転送制御装置がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行い、前記マスタ・スレーブ設定端子によりデータ転送制御装置がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行うことを特徴とするデータ転送制御装置。

【請求項2】

請求項1において、

前記パラレルATAインターフェースは、タスクファイル・レジスタを有し、

前記シリアルATAインターフェースは、

前記タスクファイル・レジスタとの間でレジスタ値が転送されるシャドウ・タスクファイル・レジスタを含み、

前記シーケンスコントローラは、

データ転送制御装置がマスタ側に設定されているときに、前記ホストがマスタへのATAコマンドを発行した場合には、前記タスクファイル・レジスタのレジスタ値をそのまま前記シャドウ・タスクファイル・レジスタに転送し、

データ転送制御装置がスレーブ側に設定されているときに、前記ホストがスレーブへのATAコマンドを発行した場合には、前記タスクファイル・レジスタのデバイス/ヘッドレジスタのDEVビットをマスタ設定に書き換えて前記タスクファイル・レジスタのレジスタ値を前記シャドウ・タスクファイル・レジスタに転送することを特徴とするデータ転送制御装置。

【請求項3】

請求項2において、

前記シーケンスコントローラは、

データ転送制御装置がマスタ側に設定されているときに、前記ホストからのATAコマンドに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合には、前記シャドウ・タスクファイル・レジスタのレジスタ値を前記タスクファイル・レジスタにそのままに転送し、

データ転送制御装置がスレーブ側に設定されているときに、前記ホストからのATAコマンドに対応するFISを前記シリアルATAインターフェースが前記デバイスから受信した場合には、前記シャドウ・タスクファイル・レジスタのデバイス/ヘッドレジスタのDEVビットをスレーブ設定に書き換えて前記シャドウ・タスクファイル・レジスタのレジスタ値を前記タスクファイル・レジスタに転送することを特徴とするデータ転送制御装置。

【請求項4】

請求項2又は3において、

前記パラレルATAインターフェースは、

ATAコマンドが前記タスクファイル・レジスタに書き込まれた場合に、コマンドライト検出信号をアクティブにし、

前記シーケンスコントローラは、